# REFERENCE MANUAL INPUT/OUTPUT INTERFACE \$100 AND \$500 SYSTEMS

Original Issue October, 1976

Revision A March, 1977

Revision B August, 1977

Revision C September, 1978

## LIST OF EFFECTIVE PAGES

## TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS: 128 CONSISTING OF THE FOLLOWING:

|   | CONDITING OF THE POPULATION                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                        |                                                                         |             |               |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|---------------|

|   | Page<br>No.                                                                                                                                                                                                                                                          | Change<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                    | Page<br>No.                                                                                                                                                            | Change<br>No.                                                           | Page<br>No. | Change<br>No. |

|   | Title A B C i ii thru iv v vi 1-1 thru 1-7 1-8 1-9 1-10 1-11, 1-12 1-13, 1-14 1-15 1-16 1-17 1-18, 1-19 1-20 1-21, 1-22 1-23 1-24 2-1 2-2 2-3 2-4 2-5 thru 2-9 2-10 thru 2-15 2-16, 2-17 2-18 3-1 thru 3-8 4-1 4-2 4-3 thru 4-16 4-17, 4-18 4-19 4-20 4-21 thru 4-26 | Rev C Rev C Original Rev A Rev C Rev B Rev C Rev B Rev C Rev B Original Rev B Original Rev B Original Rev B Original Rev B Rev C Rev B Original | 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7, 5-8<br>5-9<br>5-10 thru 5-16<br>A-1<br>A-2<br>A-3, A-4<br>A-5, A-6<br>A-7 thru A-10<br>A-11 thru A-14<br>A-15 thru A-26 | Rev A Rev B Rev A Rev B Rev A Rev B Rev B Original Rev C Original Rev C |             |               |

| 1 |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                        |                                                                         |             |               |

Insert Latest Revision Pages. Destroy Superseded Pages.

#### **CAUTIONARY NOTICE**

While the Manufacturer has attempted to detail in this manual all areas of possible danger to personnel in connection with the use of this equipment, personnel should use caution when installing, checking out, operating and servicing this equipment, especially when power is on. As with all electronic equipment, care should be taken to avoid electrical shock in all circuits where substantial currents or voltages may be present, either through design or short circuit. Caution should be observed also in lifting and hoisting equipment especially regarding large structures during installation.

The Manufacturer is specifically not liable for any damage or injury arising out of a worker's failure to follow the instructions contained in this manual, or his failure to exercise due care and caution in the installation, operation, checkout and service of this equipment.

### PROPRIETARY DATA

This document, the design contained herein, the detail and invention are considered proprietary to Harris Corporation. As the property of Harris Corporation it shall be used only for reference, contract or proposal work by this corporation or for field repair of Harris products by Harris service personnel, customers, or end users.

No disclosure, reproduction, or use of any part thereof may be made except by written permission from Harris Corporation.

## **CONTENTS**

| Section |       | rage                                                    |    |

|---------|-------|---------------------------------------------------------|----|

| ı       | INTRO | DUCTION                                                 |    |

|         | 1-1   | Scope                                                   |    |

|         | 1-2   | Related Publications                                    |    |

|         | 1-3   | Purpose                                                 |    |

|         | 1-4   | Input/Output Structure                                  |    |

|         |       | 1-4.1 General Description                               |    |

|         |       | 1-4.2 Equipment Cabinet                                 |    |

|         |       | 1-4.3 I/O Channel Card                                  |    |

|         | 1-5   | Input/Output Channel Conventions                        |    |

|         |       | 1-5.1 Instructions                                      |    |

|         |       | 1-5.1.1 Output Command Word (OCW)                       |    |

|         |       | 1-5.1.2 Output Data Word (ODW)                          |    |

|         |       | 1-5.1.3 Output Address Word (OAW)                       |    |

|         |       | 1-5.1.4 Input Data Word (IDW)                           |    |

|         |       | 1-5.1.5 Input Status Word (ISW)                         |    |

|         |       | 1-5.1.6 Input Address Word (IAW)                        |    |

|         |       | 1-5.1.7 Input Parameter Word (IPW)                      |    |

|         |       | 1-5.2 Disconnect Control                                |    |

|         |       | 1-5.3 Channel Busy Control                              |    |

|         |       | 1-5.4 Synchronization                                   |    |

|         |       | 1-5.4.1 PIOC and UBC Channel - Unit Synchronization 1-8 |    |

|         |       | 1-5.4.2 IBC Channel - Unit Synchronization              |    |

|         |       | 1-5.4.3 XBC Channel - Unit Synchronization              |    |

|         |       | 1-5.5 Memory Transfer Priority Control                  |    |

|         |       | 1-5.6 Error Actions and Sequences                       |    |

|         |       | 1-5.7 Daisy Chain Capability                            | 0  |

|         |       | 1-5.8 Link Capability                                   |    |

|         | 1-6   | Timing                                                  |    |

|         |       | 1-6.1 CPU Clock Timing                                  | -  |

|         |       | 1-6.2 Instruction Timing                                |    |

|         |       | 1-6.3 Memory Transfer Cycle Timing                      |    |

|         | 1-7   | Input/Output Channel Interfaces                         |    |

|         | • •   | 1-7.1 General Information                               | 1  |

|         |       | 1-7.2 Computer - I/O Channel Interface                  |    |

|         |       | 1-7.2.1 DB47 - DB00 (Data Bus Data Bits)                |    |

|         | •     | 1-7.2.2 C01 - C10, L0207B (Timing Clocks) 1-1           | 8  |

|         |       | 1-7.2.3 IORDY (Input/Output Ready) 1-1                  | 8  |

|         |       | 1-7.2.4 IOMCR (Input/Output Memory Cycle Request) 1-1   |    |

|         |       | 1-7.2.5 REQOK (Request Okayed)                          |    |

|         |       | 1-7.2.6 CBO                                             |    |

|         |       | 1-7.2.7 CB1                                             |    |

|         |       | 1-7.2.8 PE (Parity Error)                               |    |

|         |       | 1-7 2.9 UNIT3 - UNIT0 (Unit Code Bits) 1-1              |    |

|         |       | 1-7.2.10 IR04 and IR05 (Instruction Register Bits) 1-1  |    |

|         |       | 1-7.2.11 CHAN4 - CHAN0 (Channel Code Bits)              |    |

|         |       | 1-7.2.12 OVRRD (Override Bit)                           |    |

|         |       | 1-7.2.13 ABF5 - ABF0 (Absolute Function Bits)           | 18 |

|         |       |                                                         |    |

| Section |         | Pa                                                      | age        |

|---------|---------|---------------------------------------------------------|------------|

| 1       | INTROD  | UCTION (Cont'd.)                                        |            |

|         |         | 1-7.2.14 MCLRB (Master Clear)                           |            |

|         |         | 1-7.2.15 HOLDB (Hold)                                   |            |

|         |         | 1-7.2.16 MAB19 - MAB00 (Memory Address Bits)            |            |

|         |         | 1-7.2.17 BLKP7 - BLKP0 (Block Priority Levels)          |            |

|         |         | 1-7.2.18 IHREQ (Inhibit Requests)                       | 19         |

|         |         | 1-7.2.19 +5V, GND, -12V (Power and Ground)              |            |

|         |         | 1-7.3 I/O Channel - External Unit Controller Interface  |            |

|         |         | 1-7.3.1 DFU23 - 00+ (Data From Unit Bits)               |            |

|         |         | 1-7.3.2 31 007 001 (Otalas 1 10111 01111 01111 01111    | -19        |

|         |         | 1-7.3.3 O-DTU23 - 00+ (Data To Unit Bits)               |            |

|         |         | 1-7,3.4 O-D13C1 (D13C01111CC1)                          | -19        |

|         |         | 1-7.3.5 C(101 ( (Oo)meet) :                             | -19        |

|         |         | 1-7.3.0 O-01103 - 001 (Office Field)                    | -19        |

|         |         | 1-7.3.7 O-MOE: (Master Clear).                          | -19        |

|         |         | 1-7.3.6 O-CDITI (Command Buta Horo)                     | -19        |

|         |         | 1-7.3.9 O-ODITI (Output Duta Horo)                      | -19        |

|         |         | 1-7.3.10 ODAGI (Output Buta Assertes)                   | -19        |

|         |         | 1-7.3.11 DAVI OT (Data Available 1 Tolli Otto)          | -22        |

|         |         | 1-7.3.12 DATO+ (Data Accepted To Sint)                  | -22        |

|         |         | 1-7.3.13 III O' (Input interrupt i ioin oins)           | -22        |

|         |         | 1-7,3,14 OOIL (Oline Output Interrupt Linears)          | -22        |

|         |         | 1-7,3.15 EGDET (Etiable Statistic Barret Empt)          | -22<br>-22 |

|         |         | 1-7.5.10                                                | -22        |

|         |         | 1-7.4 Interrupt interrupe                               | -22        |

|         | 1-8     | Input/Output Granner Gubing requirements                | -22        |

|         |         | 1-6.1 Computer - 1/O Charmers Interface                 | -22        |

|         |         | 1-0.2 I/O Chamier - External Offic Controller internace | -22        |

|         |         | 1-0.2.1 Dasie riequirements                             | -22        |

|         |         | 1-0.2.2 Duisy Grant Hoganismost                         | -24        |

|         |         | 1-0.2.5 Link frequirements                              | -24        |

|         |         | 1-0.5 Chainler - Friority Interrupt interrupe           | -24        |

|         | 1-9     | Maintenance Accessories                                 | 27         |

| п       | 8-BIT P | ROGRAMMED INPUT/OUTPUT CHANNEL                          |            |

|         | 2-1     | General                                                 | 2-1        |

|         | 2-2     | Physical Description                                    | 2-1        |

|         | 2-3     | Channel Interraces                                      | 2-1        |

|         |         | 2-3.1 CFO-Chamler interface                             | 2-1        |

|         |         | 2-3.2 Channel - External Only Controller Interface :    | 2-1        |

|         |         | 2-3.5 Internal Controller Internace                     | 2-1        |

|         |         | 2-3.4 Chairner Controller - Office interfaces           | 2-1        |

|         |         | 2-3.5 Interrupt interraces                              | 2-1        |

|         | 2-4     | Interrupt Control                                       | 2-1<br>2-2 |

|         | 2-5     | Disconnect Control                                      | 2-9        |

|         | 2-6     | Programmed Transfer Operations                          | 2-9        |

| Section |         |                |                                          | Page        |

|---------|---------|----------------|------------------------------------------|-------------|

| H       | 8-BIT F | PROGRAMM       | MED INPUT/OUTPUT CHANNEL (Cont'd.)       |             |

|         |         | 2-6.1          | Output Command Word (OCW) Instructions   | 2-9         |

|         |         | 2-6.2          | Output Data Word (ODW) Instructions      | 2-9         |

|         |         | 2-6.3          | Input Data Word (IDW) Instructions       | 2-9         |

|         |         | 2-6.4          | Input Status Word (ISW) Instructions     | 2-16        |

|         |         | 2-6.5          | Output Address Word (OAW) Instructions   | 2-16        |

| ш       | INTEG   | RAL BLOC       | K CONTROLLER INPUT/OUTPUT CHANNEL        |             |

|         | 3-1     | General .      |                                          | 3-1         |

|         | 3-2     | Input/Out      | rout Conventions                         | 3-1         |

|         |         | 3-2.1          | Channel/Unit Addressing Scheme           | 3-1         |

|         |         | 3-2.2          | Commanded Modes                          | 3-1         |

|         |         | 3-2.3          | Programmed Transfers                     | 3-1         |

|         |         | 3-2.4          | Transfer Handshakes                      | 3-1         |

|         |         | 3-2.5          | Memory (Block) Transfers                 | 3-1         |

|         |         | 3-2.0          | 3-2.5.1 Parameter Registers              | 3-3         |

|         |         |                | 3-2.5.2 Terminate/Restart Registers      |             |

|         |         |                | 3-2.5.3 Memory Access Priority Structure |             |

|         |         |                | ned Transfer Operations.                 |             |

|         | 3-3     | _              | OCW Instruction Execution                | 3-4         |

|         |         | 3-3.1          | ISW Instruction Execution                |             |

|         |         | 3-3.2          | OAW Instruction Execution                |             |

|         |         | 3-3.3          | Transfer Operations                      |             |

|         | 3-4     | Memory         | Transfer Operations                      | 3-4         |

|         | 3-5     |                | Timing                                   |             |

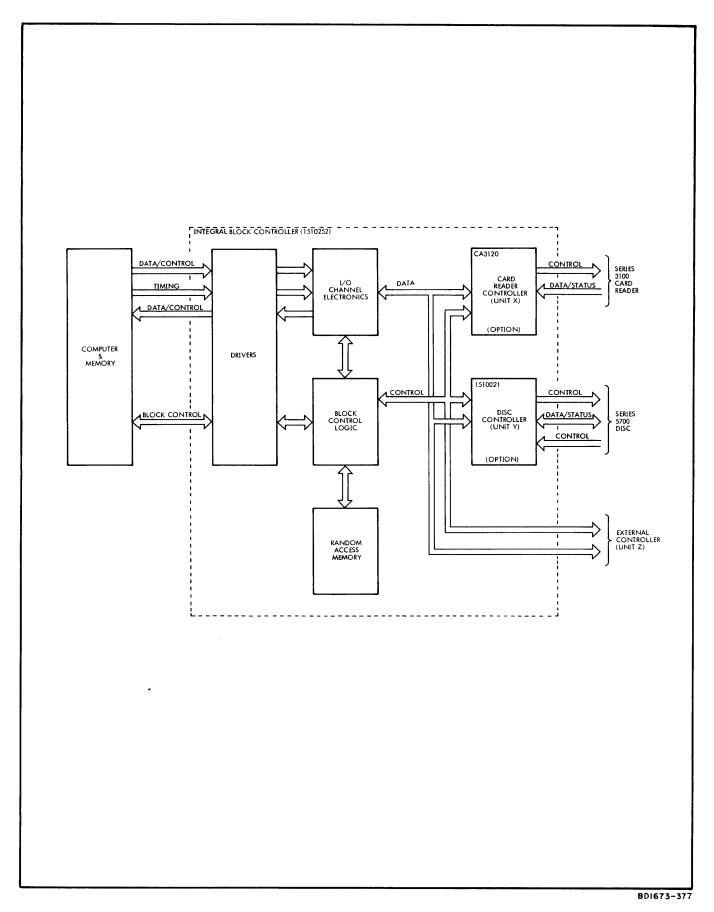

|         | 3-6     | -              | Description                              |             |

|         |         | 3-6.1          | Channel - CPU Interface                  |             |

|         |         | 3-6.2          | Channel - Internal Controller Interface  |             |

|         |         | 3-6.3          | Controller-Unit Interface                | <b>J</b> -5 |

| IV      | UNIV    | ERSAL BLO      | OCK CONTROLLER INPUT/OUTPUT CHANNEL      |             |

|         | 4-1     | General        |                                          | 4-1         |

|         | 4-2     | Physical       | Description                              |             |

|         | 4-3     |                | utput Conventions.                       | . 4-4       |

|         | 4-3     | 4-3.1          | Time Sharing                             | . 4-4       |

|         |         | 4-3.1          | Channel - Unit Address Scheme            | . 4-4       |

|         |         | 4-3.2<br>4-3.3 | Instructions                             | . 4-4       |

|         |         | 4-3.3<br>4-3.4 | Handshake Sequences                      | . 4-4       |

|         |         | 4-3.4<br>4-3.5 | Memory Transfer Priority                 | . 4-6       |

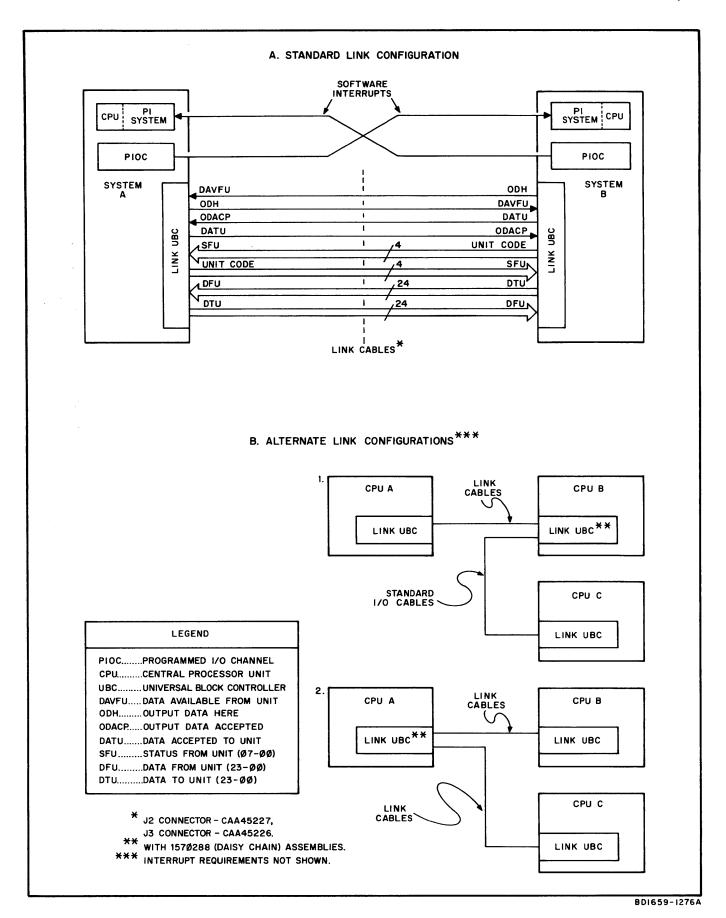

|         |         | 4-3.5<br>4-3.6 | Link Operations                          | . 4-6       |

|         |         |                | med Transfer Operations                  | . 4-6       |

|         | 4-4     | _              |                                          | . 4-6       |

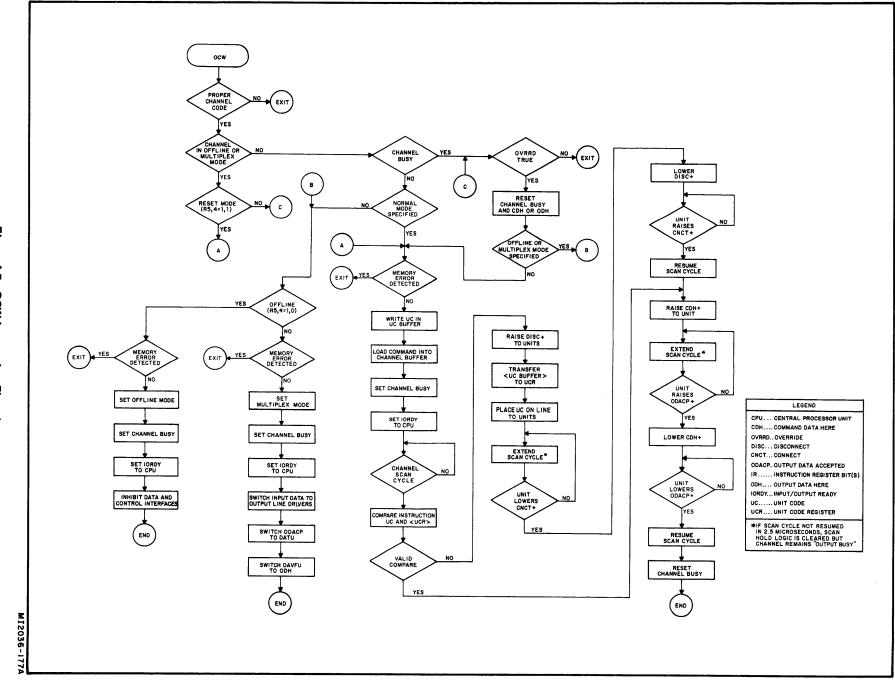

|         |         | 4-4.1          | OCW Instructions                         | . 4-6       |

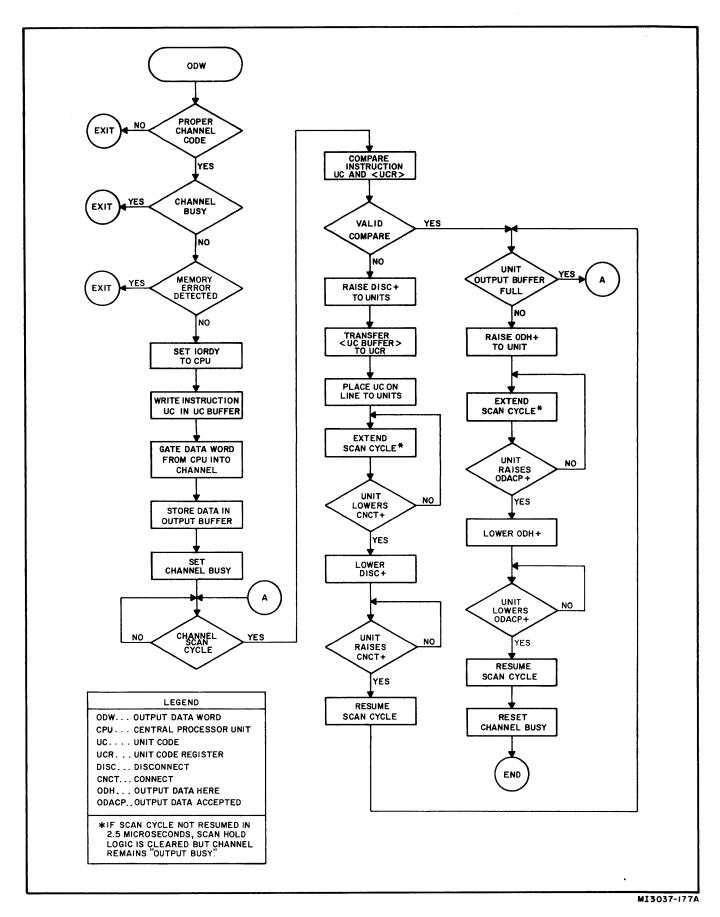

|         |         | 4-4.2          |                                          | . 4-1       |

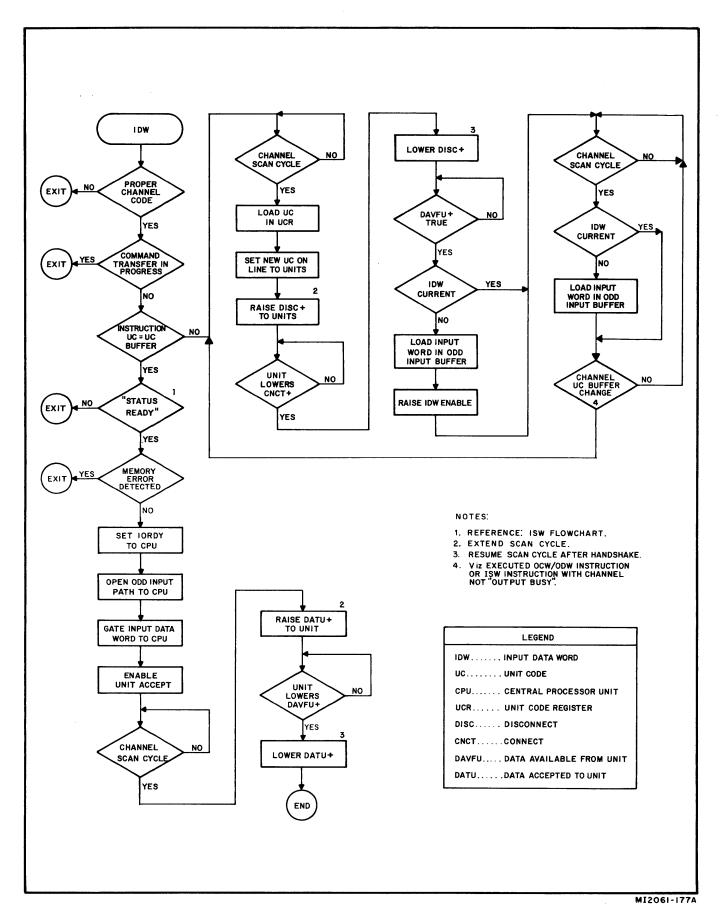

|         |         | 4-4.3          | IDW Instructions                         | 4-1         |

|         |         | 4-4.4          | ISW Instructions                         |             |

|         |         | 4-4.5          | OAW Instructions.                        | . 4-1       |

|         |         | 4-4.6          | IAW/IPW Instructions                     | . 71        |

| Section |            |                                                       | Page     |

|---------|------------|-------------------------------------------------------|----------|

| IV      | UNIVE      | ERSAL BLOCK CONTROLLER INPUT/OUTPUT CHANNEL (Cont'd.) |          |

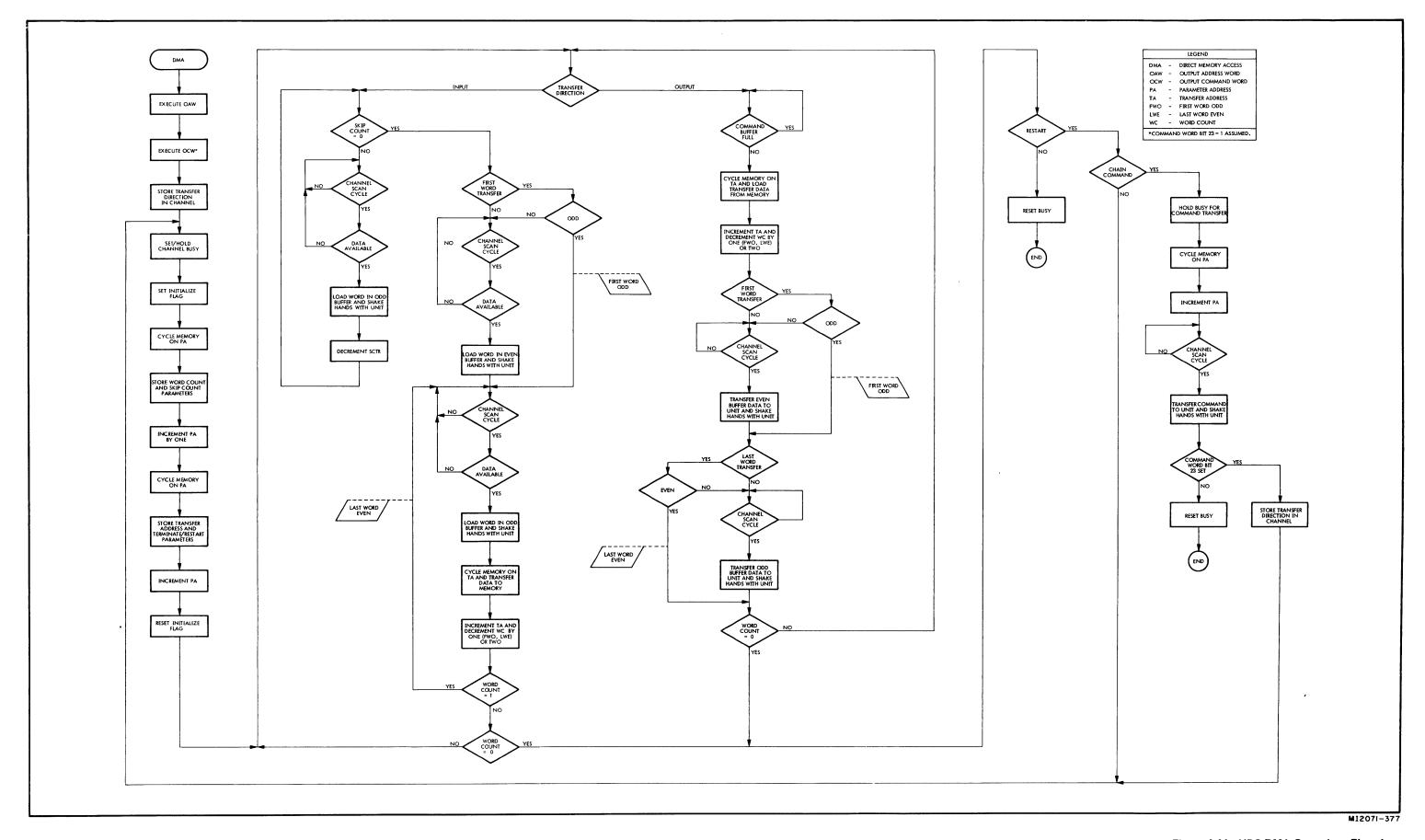

|         | 4-5        | Memory Transfer (DMA) Operations                      | <br>4-15 |

|         |            | 4-5.1 Initialize Sequences                            | 4-15     |

|         |            | 4-5.2 Memory Transfers - Output                       | <br>4-15 |

|         |            | 4-5.3 Memory Transfers - Input                        | <br>4-16 |

|         |            | 4-5.4 Restart Sequences                               | <br>4-16 |

|         | 4-6        | Locked Scan Operations                                | 4-16     |

|         | 4-0<br>4-7 | Isolation Interface Operations                        | 4-25     |

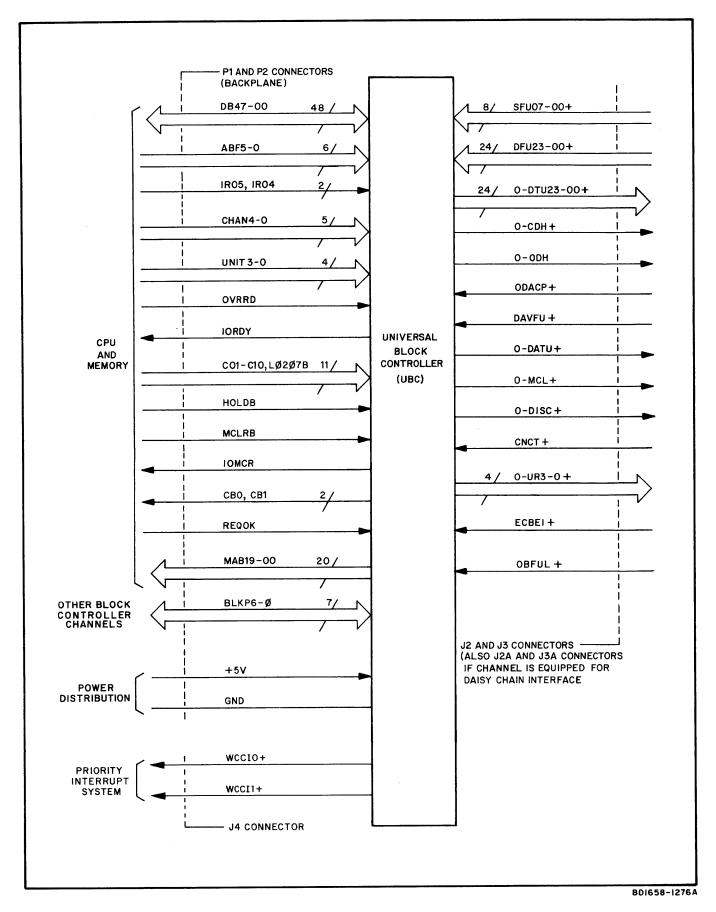

|         | • •        | Channel Interfaces                                    | 4-25     |

|         | 4-8        |                                                       | <br>7 20 |

| V       | EXTE       | RNAL BLOCK CONTROLLER (XBC) INPUT/OUTPUT CHANNEL      |          |

|         | 5-1        | General                                               | <br>5-1  |

|         | 5-2        | Input/Output Conventions                              | <br>5-2  |

|         |            | 5-2.1 Channel - Unit Address Scheme                   | <br>5-2  |

|         |            | 5-2.2 Commanded Modes                                 | <br>5-2  |

|         |            | 5-2.3 Programmed Transfers                            | <br>5-2  |

|         |            | 5-2.4 Memory Transfers                                | <br>5-2  |

|         |            | 5-2.5 Transfer Handshakes                             |          |

|         |            | 5-2.6 Channel Busy Conditions                         | <br>5-3  |

|         |            | 5-2.7 Disconnect Sequence Control                     | <br>5-3  |

|         |            | 5-2.8 Memory Transfer Priority Control                | <br>5-3  |

|         |            | 5-2.9 Memory Address Extension                        | <br>5-4  |

|         |            | 5-2.10 Status Identification (ID) Code                | <br>5-4  |

|         | 5-3        | Programmed Transfer Operations                        | <br>5-4  |

|         | 5-5        | 5-3.1 OCW Instructions                                |          |

|         |            | 5-3.2 OAW/ODW Instructions                            |          |

|         |            | 5-3.3 ISW Instructions                                |          |

|         | 5-4        | Memory Transfer Operations                            |          |

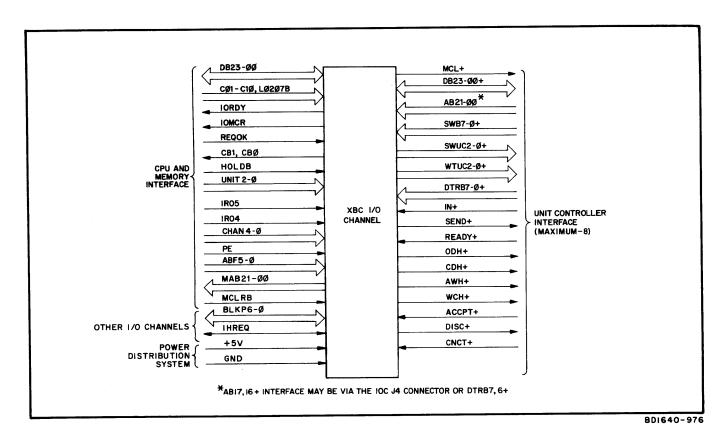

|         | 5-4<br>5-5 | XBC Channel Interfaces.                               |          |

|         | 5-5        | 5-5.1 Channel - CPU and Memory Interface              |          |

|         |            |                                                       |          |

|         |            | 5-5.2 Channel - Unit Controller Interface             |          |

|         |            |                                                       |          |

|         |            |                                                       |          |

|         |            |                                                       |          |

|         |            |                                                       |          |

|         |            |                                                       | 5-13     |

|         |            | 5-5.2.6 WTUC2 - WTUC0+ (Word Transfer Unit Co         | 5-13     |

|         |            | 5-5.2.7 DTRB7 - DTRB0+ (Data Transfer Request         | 5-13     |

|         |            | 5-5.2.8 IN+ (Transfer Direction)                      |          |

|         |            | 5-5.2.9 SEND+ (Channel Ready)                         | 5-13     |

|         |            |                                                       | <br>     |

|         |            | 5-5.2.11 ODH+ (Output Data Here)                      |          |

|         |            | 5-5.2.12 CDH+ (Command Data Here)                     |          |

|         |            | 5-5.2.13 AWH+ (Address Word Here)                     |          |

|         |            | 5-5.2.14 WCH+ (Word Count Here)                       |          |

|         |            | 5-5.2.15 ACCPT+ (Accepted)                            | <br>5-14 |

| Section |                                                                  | Page   |

|---------|------------------------------------------------------------------|--------|

| V       | EXTERNAL BLOCK CONTROLLER (XBC) INPUT/OUTPUT CHANNEL             |        |

|         | 5-5.2.16 DISC+ (Disconnect)                                      |        |

|         | 5-5.3 Channel Cabling Requirements                               |        |

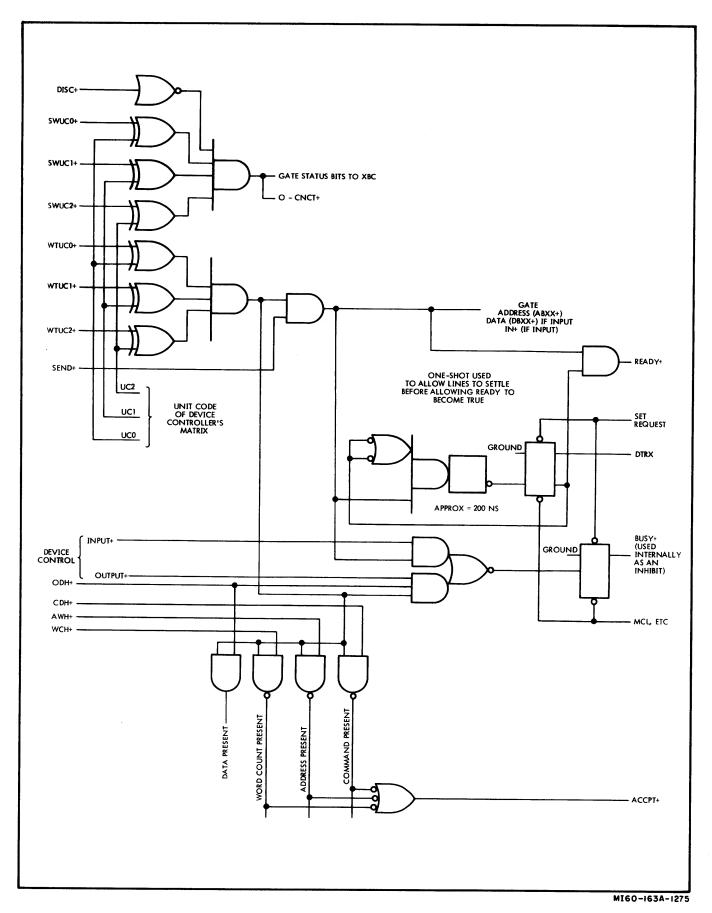

|         | 5-6 Typical Unit Controller                                      |        |

|         | APPENDIX                                                         |        |

|         | A-1 General                                                      | . A-1  |

|         | ILLUSTRATIONS                                                    |        |

| Figure  |                                                                  | Page   |

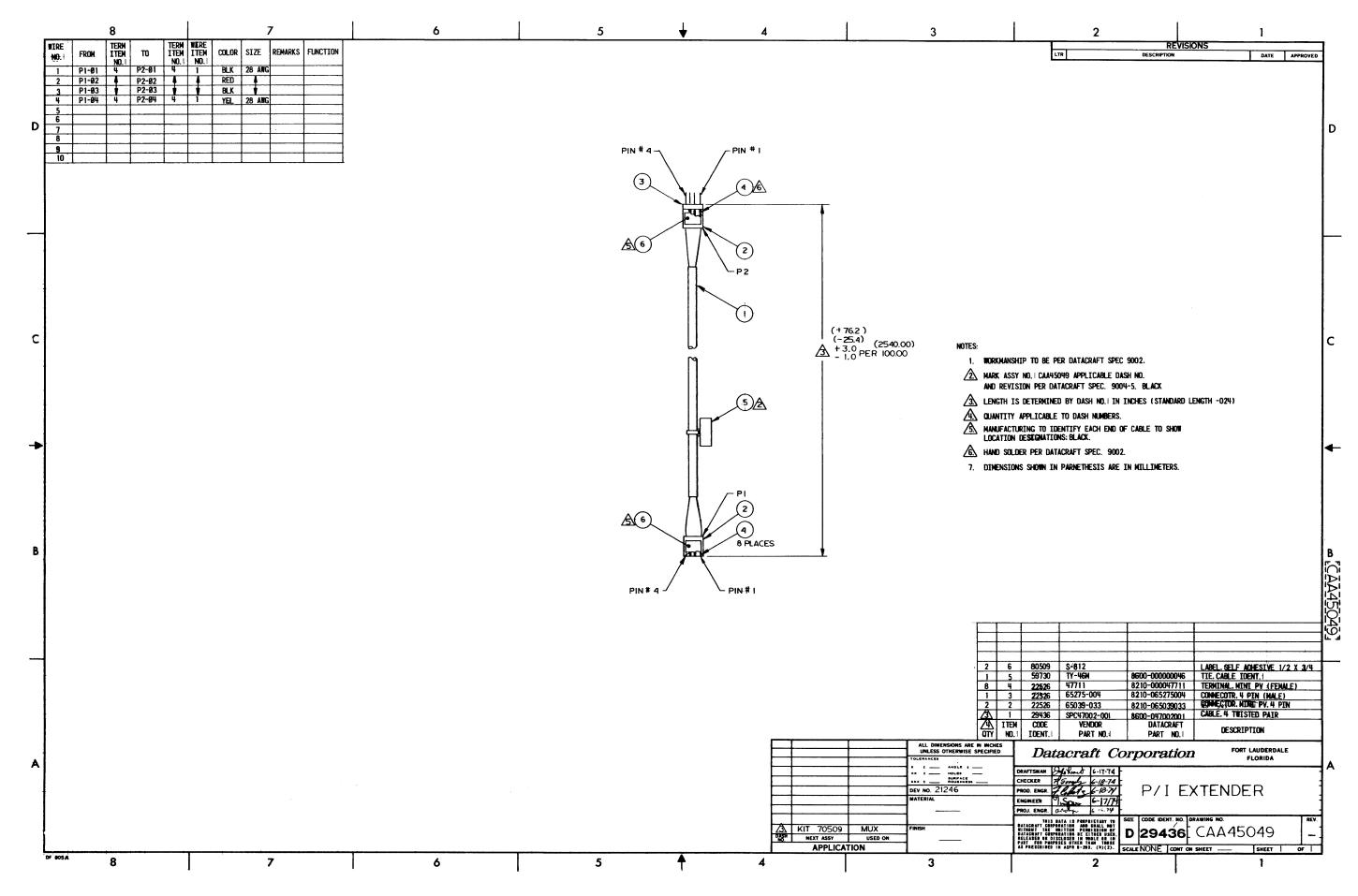

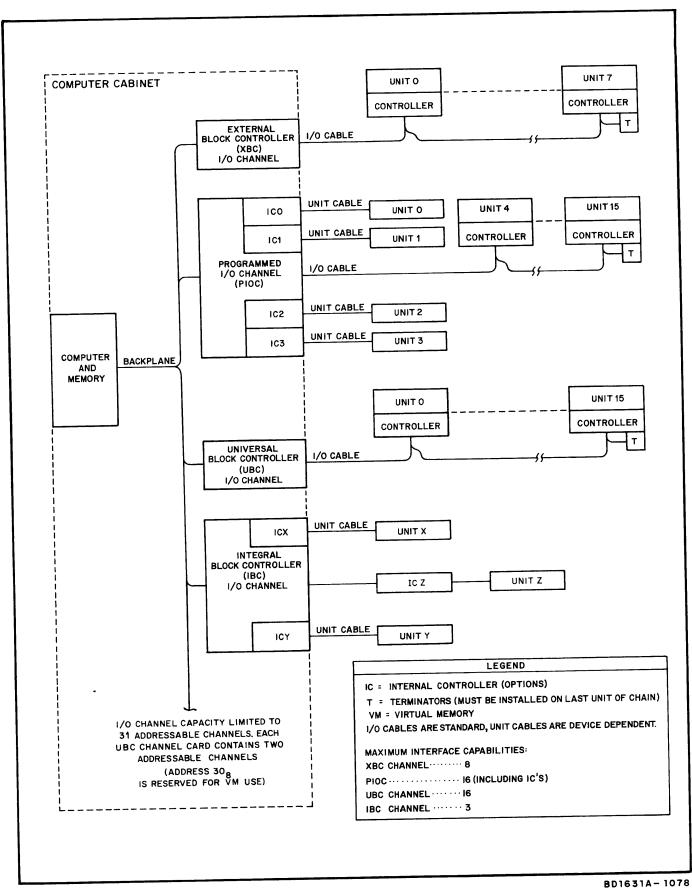

| 1-1     | Computer Input/Output Structure                                  | . 1-3  |

| 1-2     | Computer Cabinet                                                 |        |

| 1-3     | I/O Channel Outline Diagram                                      |        |

| 1-4     | I/O Instruction Formats                                          | . 1-6  |

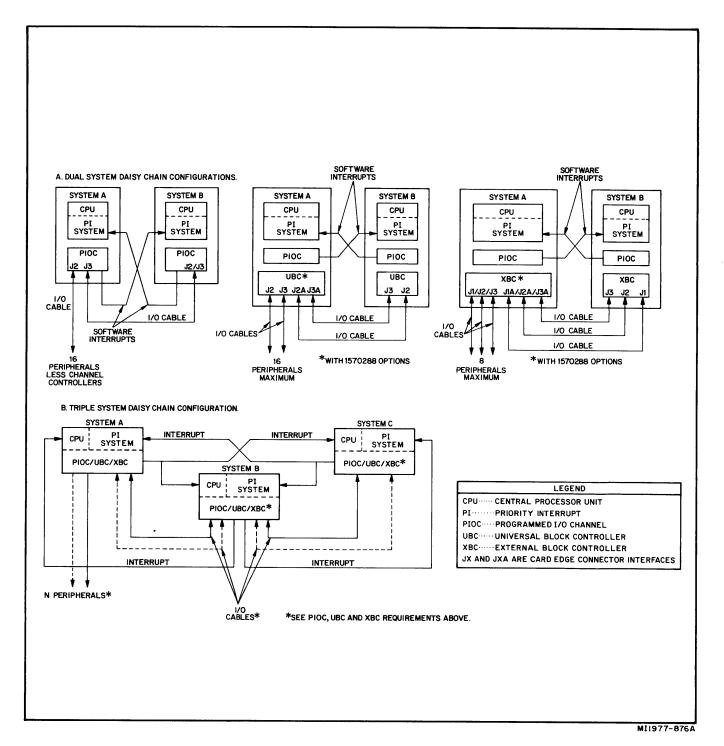

| 1-5     | Daisy Chain Channel Configuration                                | . 1-10 |

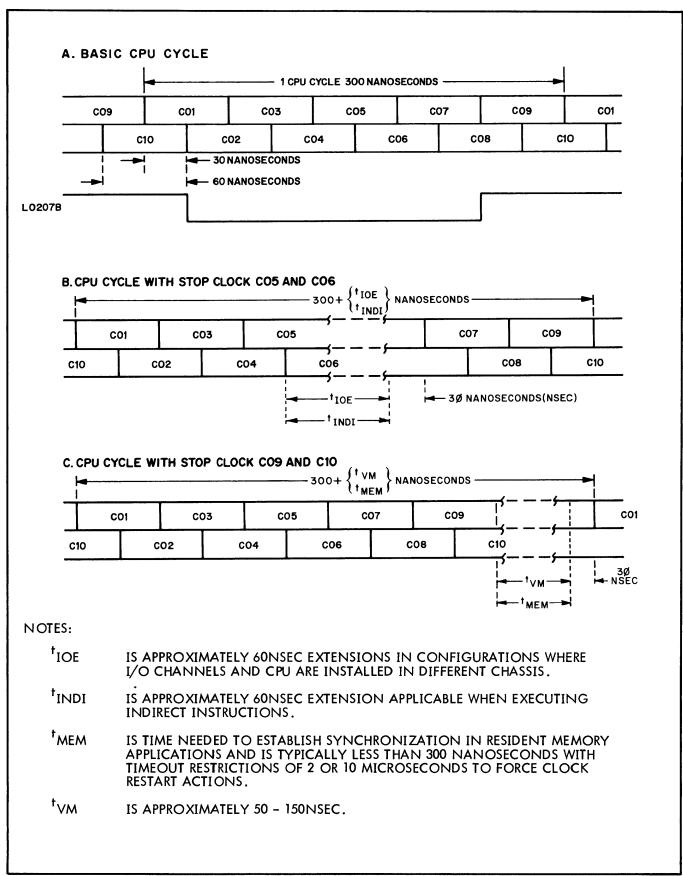

| 1-6     | Computer Main Timing                                             | . 1-12 |

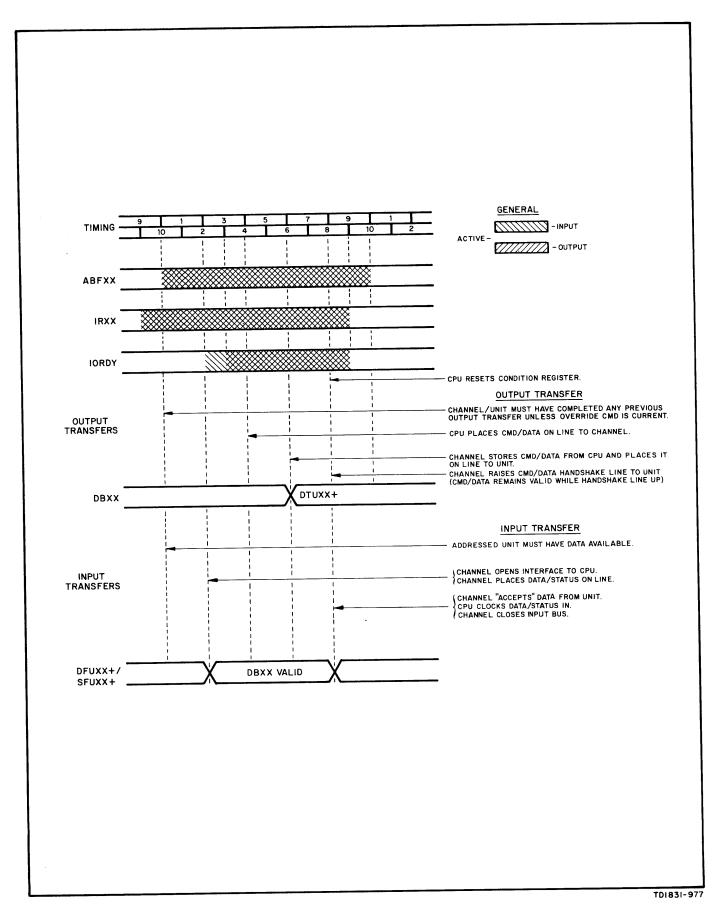

| 1-7     | I/O Instructions Timing Conventions                              | . 1-13 |

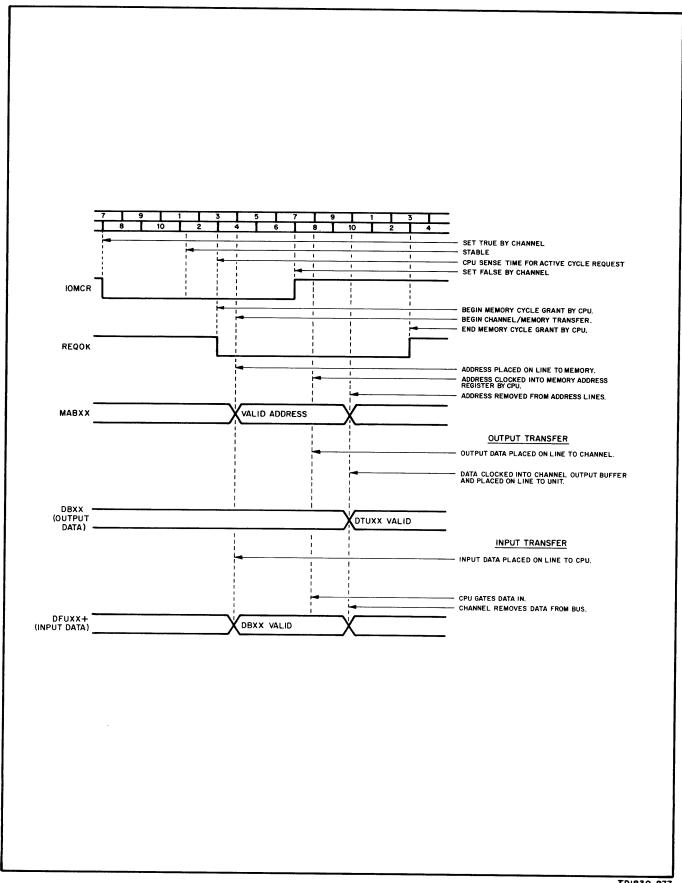

| 1-8     | Memory Transfer (Block Control) Timing Conventions               | . 1-14 |

| 1-9     | Standard Interfaces for I/O Usage                                | . 1-15 |

| 2-1     | PIOC Simplified Block Diagram                                    | . 2-2  |

| 2-2     | PIOC Outline Diagram                                             | . 2-3  |

| 2-3     | PIOC Interfaces                                                  |        |

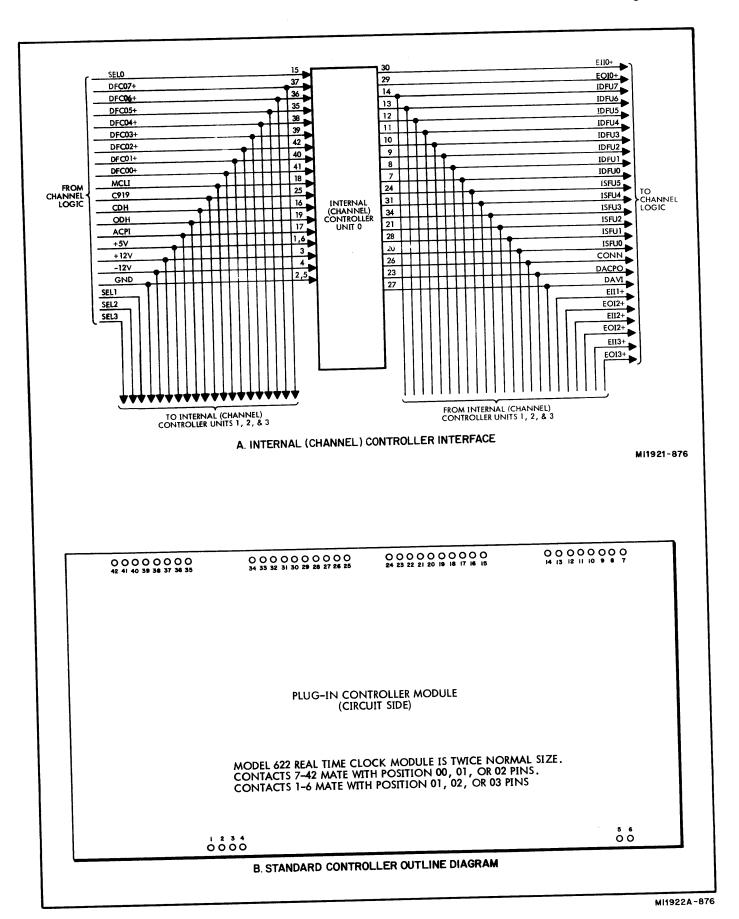

| 2-4     | Internal Controller Interface                                    |        |

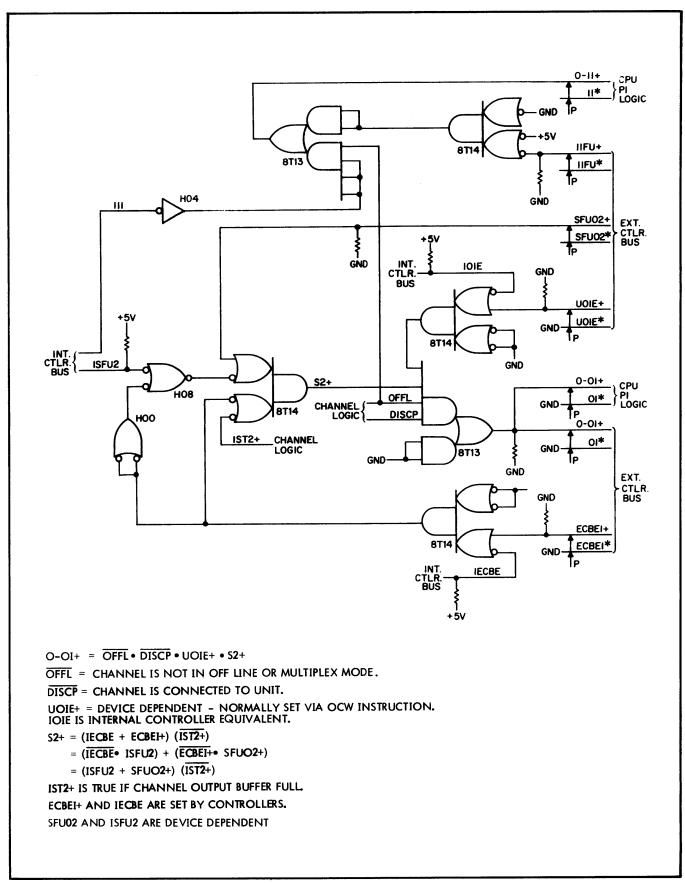

| 2-5     | PIOC Interrupt Generator                                         |        |

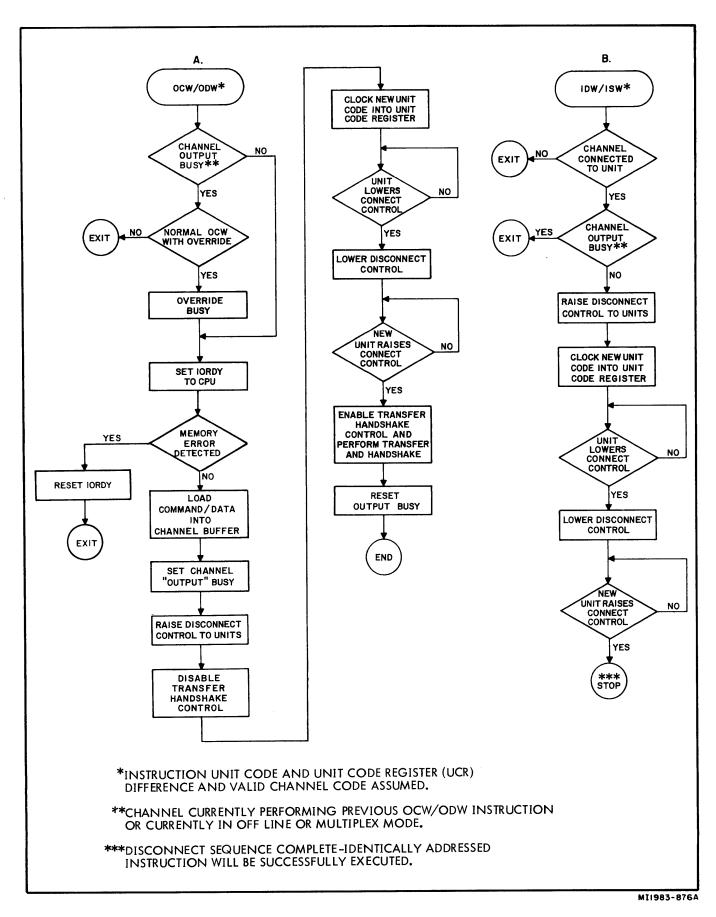

| 2-6     | Disconnect Sequence Flowcharts                                   |        |

| 2-7     | Disconnect Sequence Timing                                       |        |

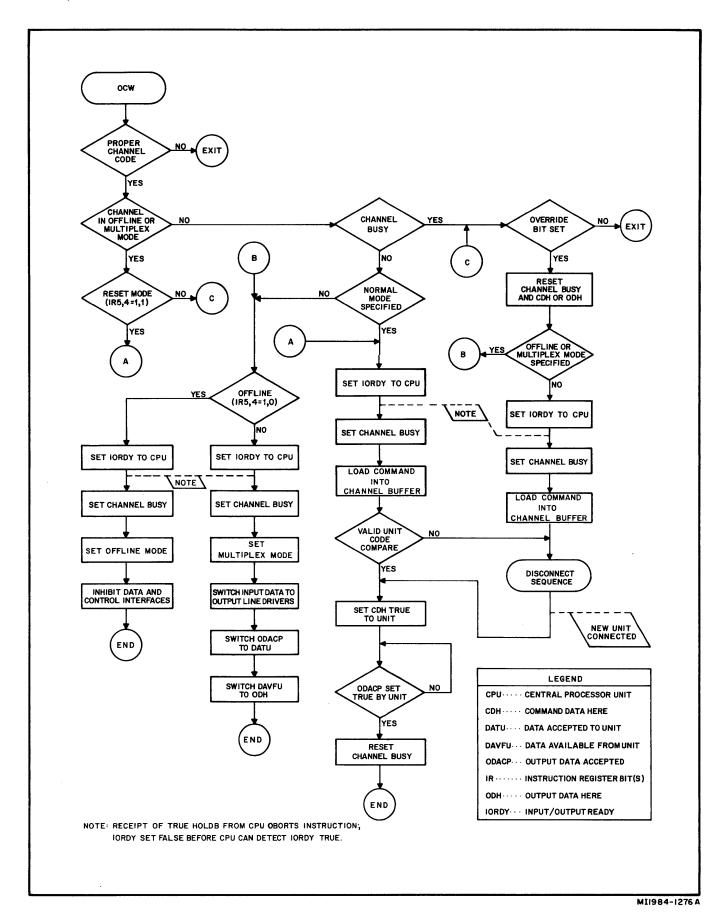

| 2-8     | OCW Instruction Flowchart                                        |        |

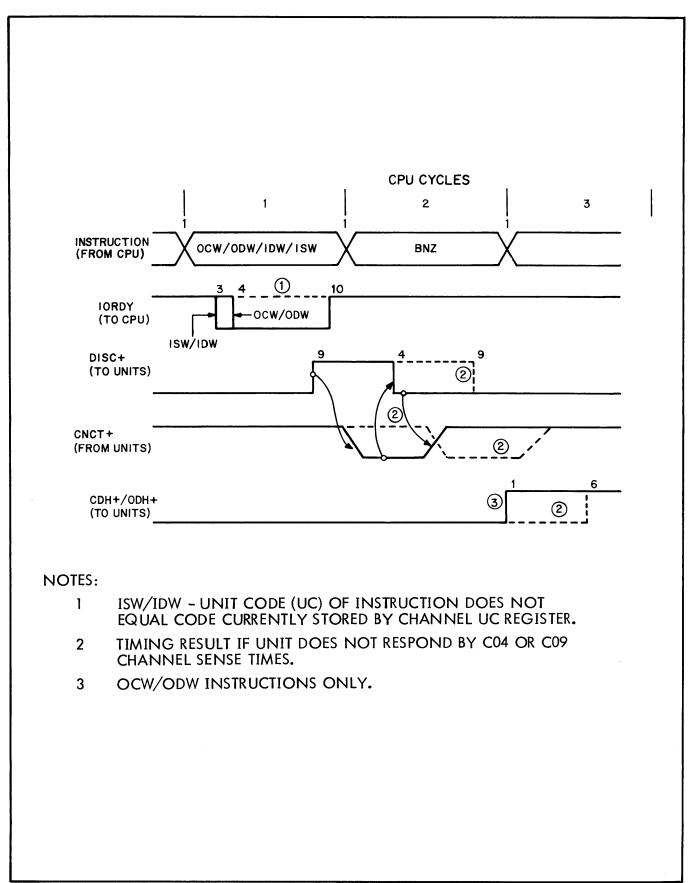

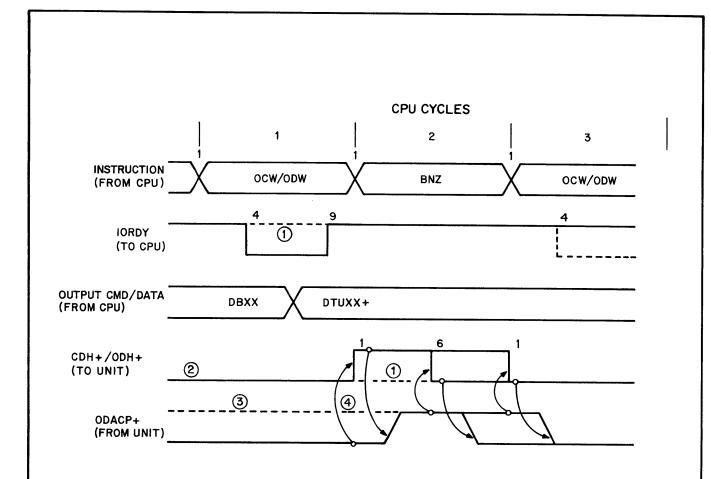

| 2-9     | OCW/ODW Instruction Timing                                       |        |

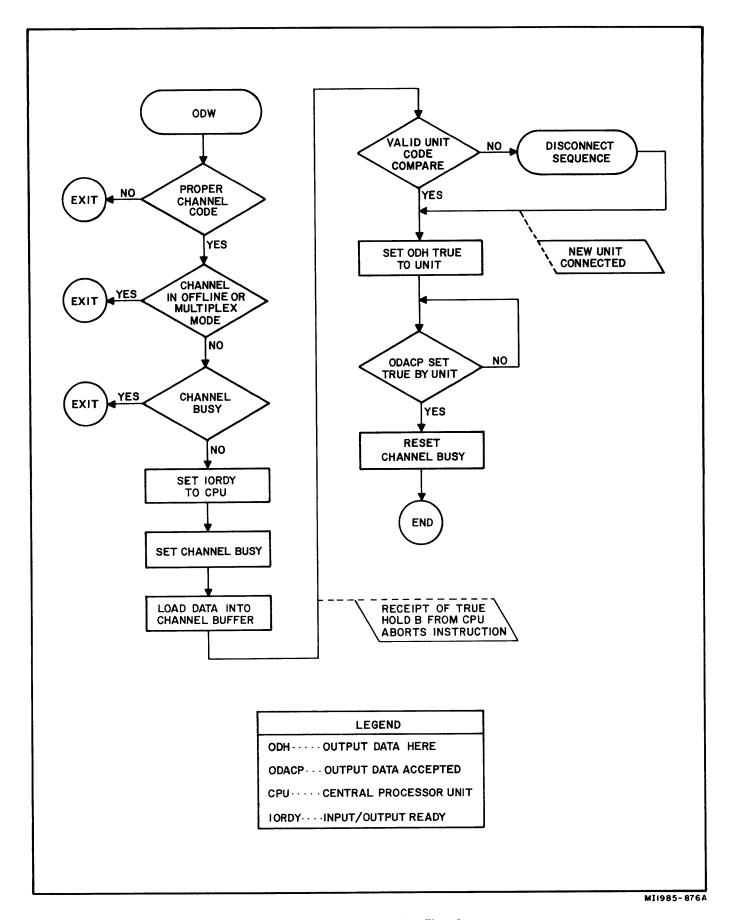

| 2-10    | ODW Instruction Flowchart                                        | · 2-14 |

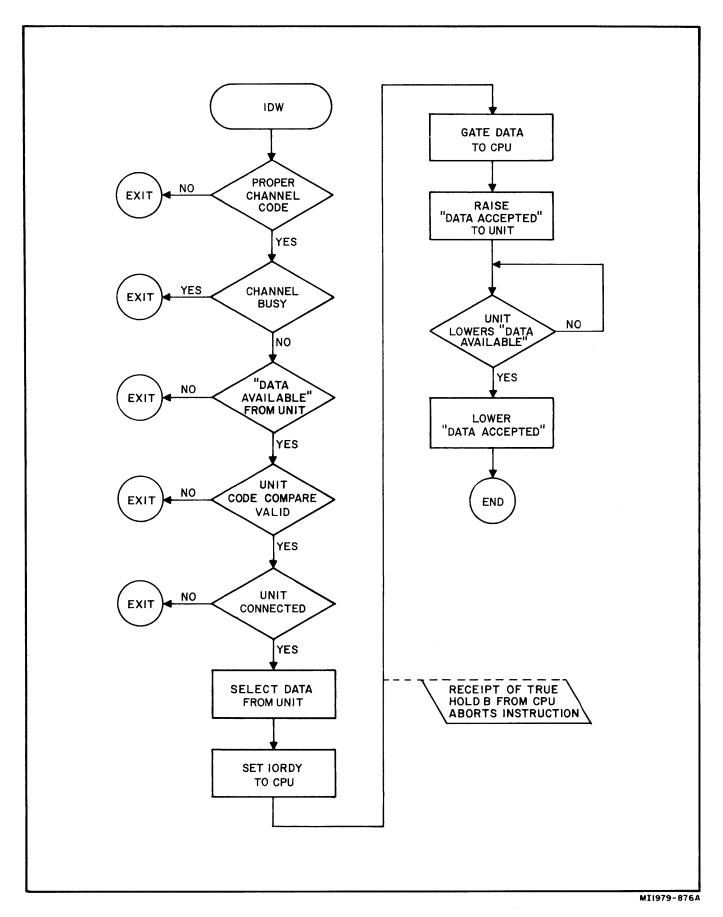

| 2-11    | · IDW Instruction Flowchart                                      |        |

| 2-12    | IDW/ISW Instruction Timing · · · · · · · · · · · · · · · · · · · |        |

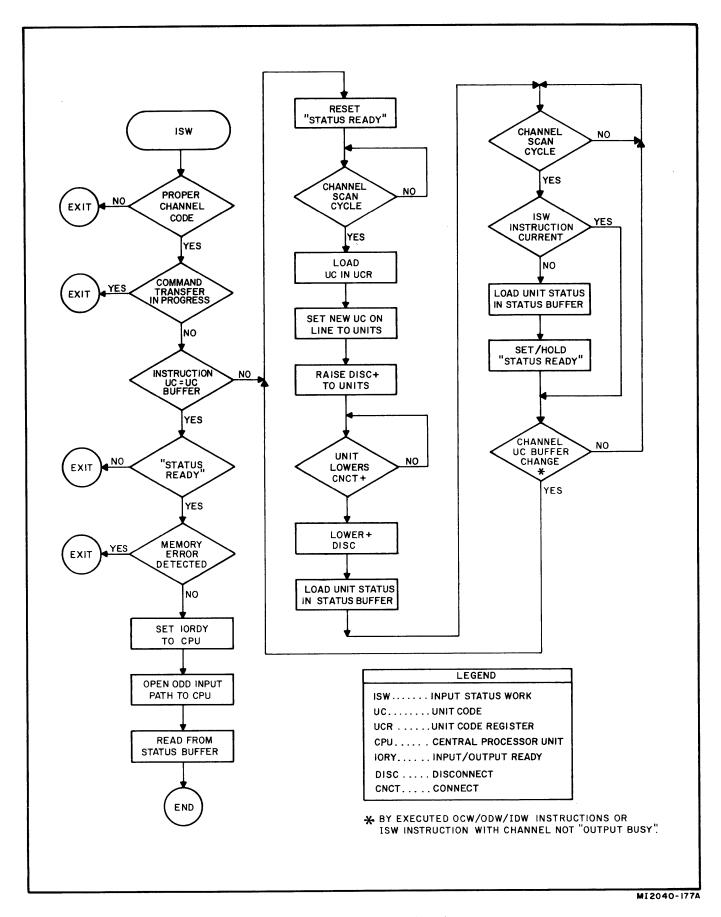

| 2-18    | ISW Instruction Flowchart                                        | . 2-18 |

| 3-1     | IBC Channel Simplified Block Diagram                             | . 3-2  |

| 3-2     | IBC Channel Command/Parameter Word Formats                       |        |

| 3-3     | IBC Channel Outline Drawing                                      | . 3-5  |

| 3-4     | IBC Channel — CPU Interface                                      | . 3-6  |

| 3-5     | IBC Channel — Controller Interface                               | . 3-7  |

|         |                                                                  |        |

## ILLUSTRATIONS (Cont'd.)

| Figure       |                                                        | Page   |

|--------------|--------------------------------------------------------|--------|

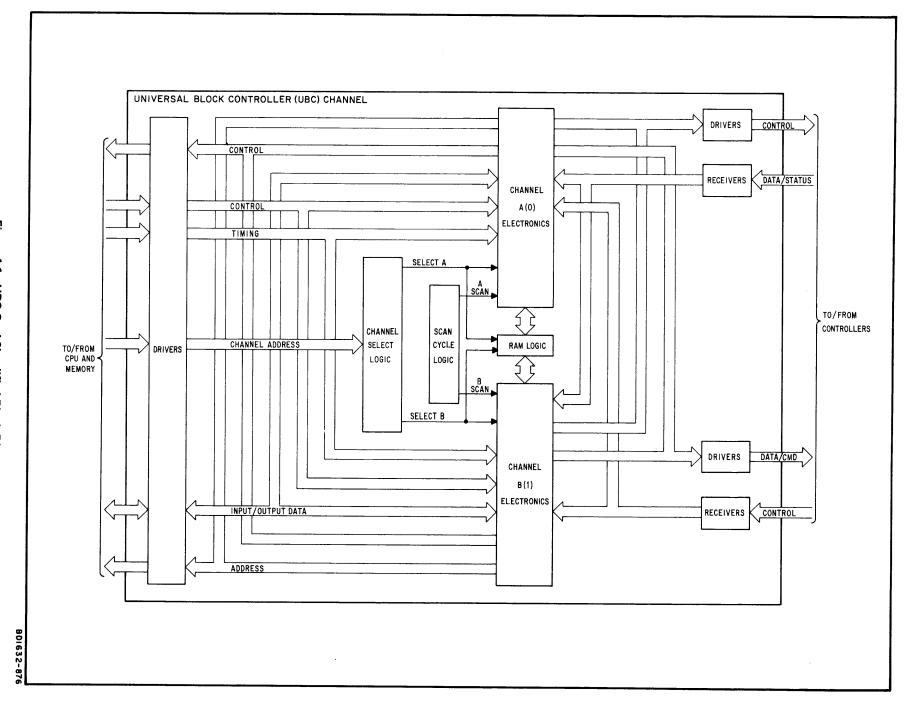

| 4-1          | UBC Card Simplified Block Diagram                      | 4-2    |

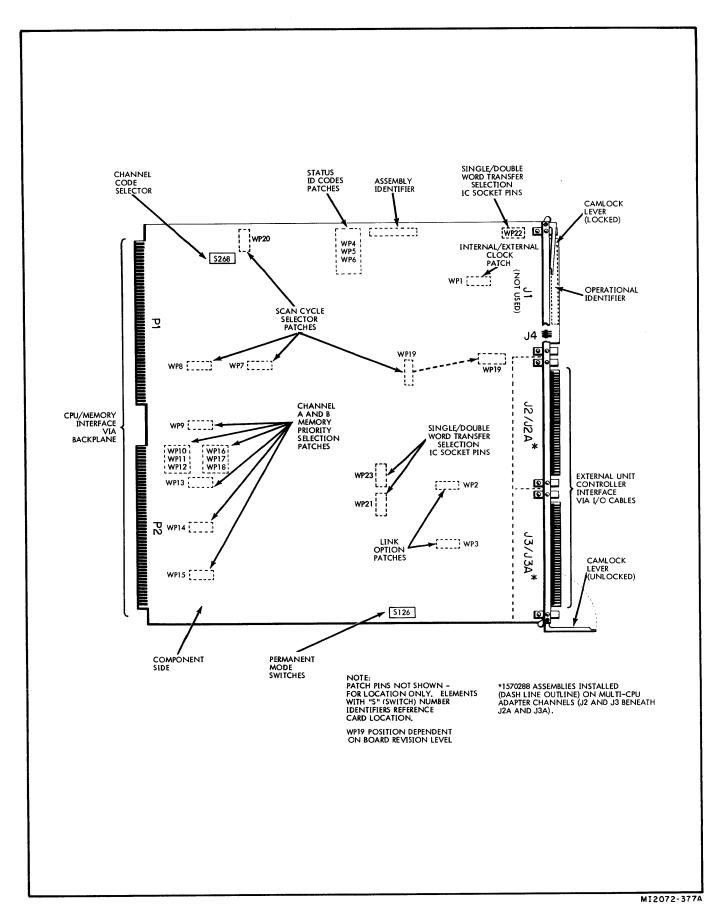

| 4-2          | UBC Card Outline Diagram                               | 4-3    |

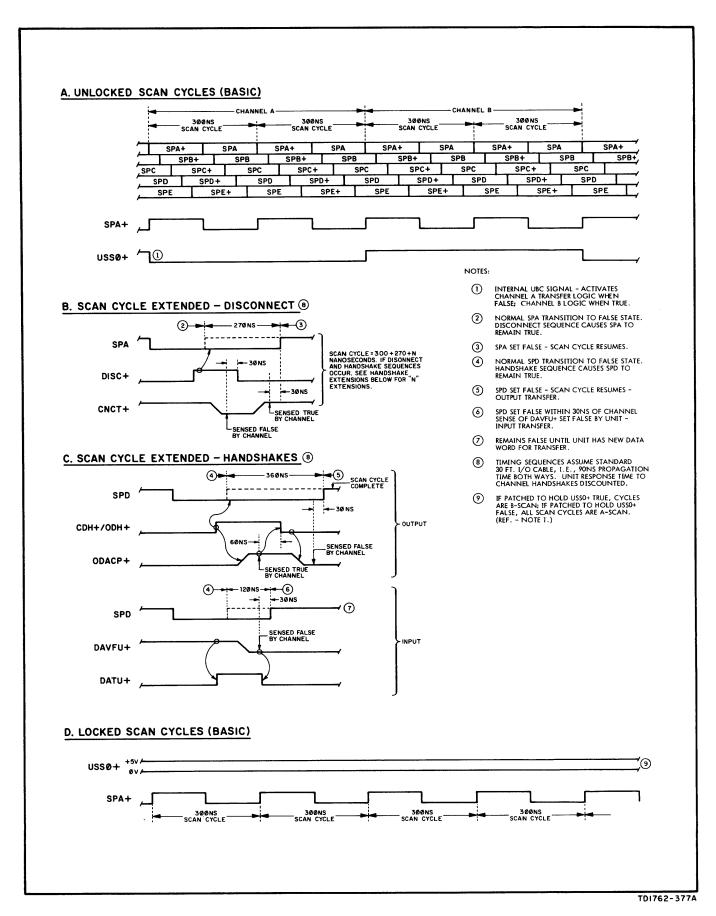

| 4-3          | UBC Scan Cycle Timing                                  | 4-5    |

| 4-4          | UBC Link Configurations                                | 4-7    |

| 4-5          | OCW Instruction Flowchart                              | 4-8    |

| 4-6          | OCW/ODW Instruction Timing                             | 4-9    |

| 4-7          | ODW Instruction Flowchart                              | 4-10   |

| 4-8          | IDW Instruction Flowchart                              | 4-12   |

| 4-9          | IDW/ISW Instruction Timing                             | 4-13   |

| 4-10         | ISW Instruction Flowchart                              | 4-14   |

| 4-11         | UBC DMA Operations Flowchart                           | 4-17   |

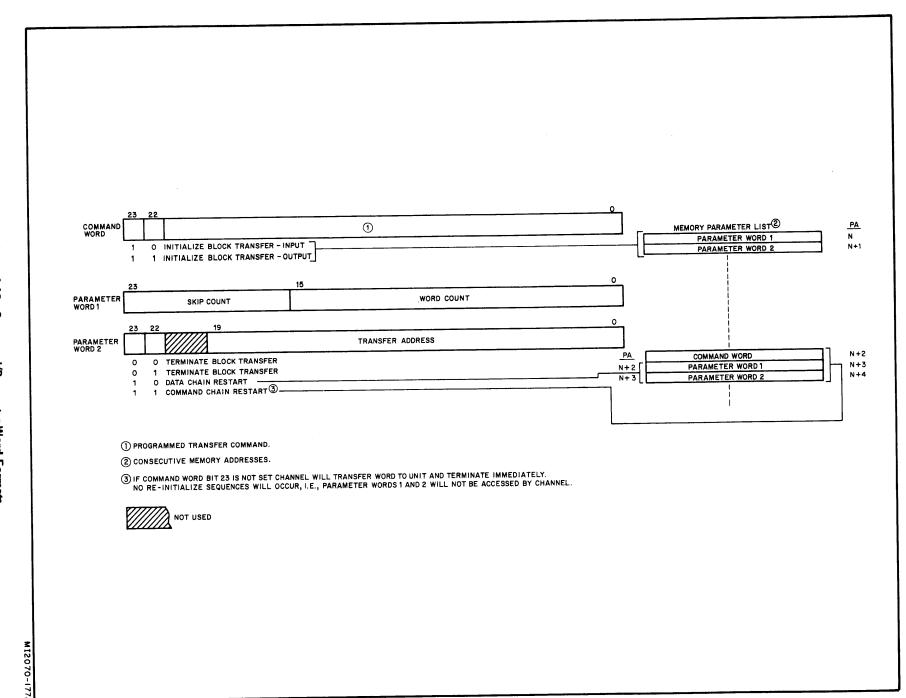

| 4-12         | Command/Parameter Word Formats                         | 4-19   |

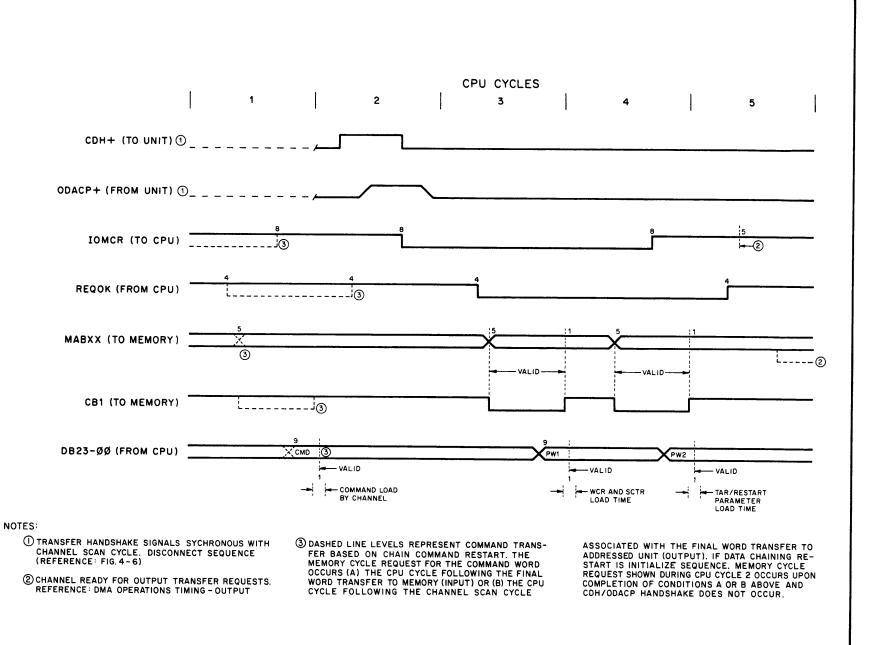

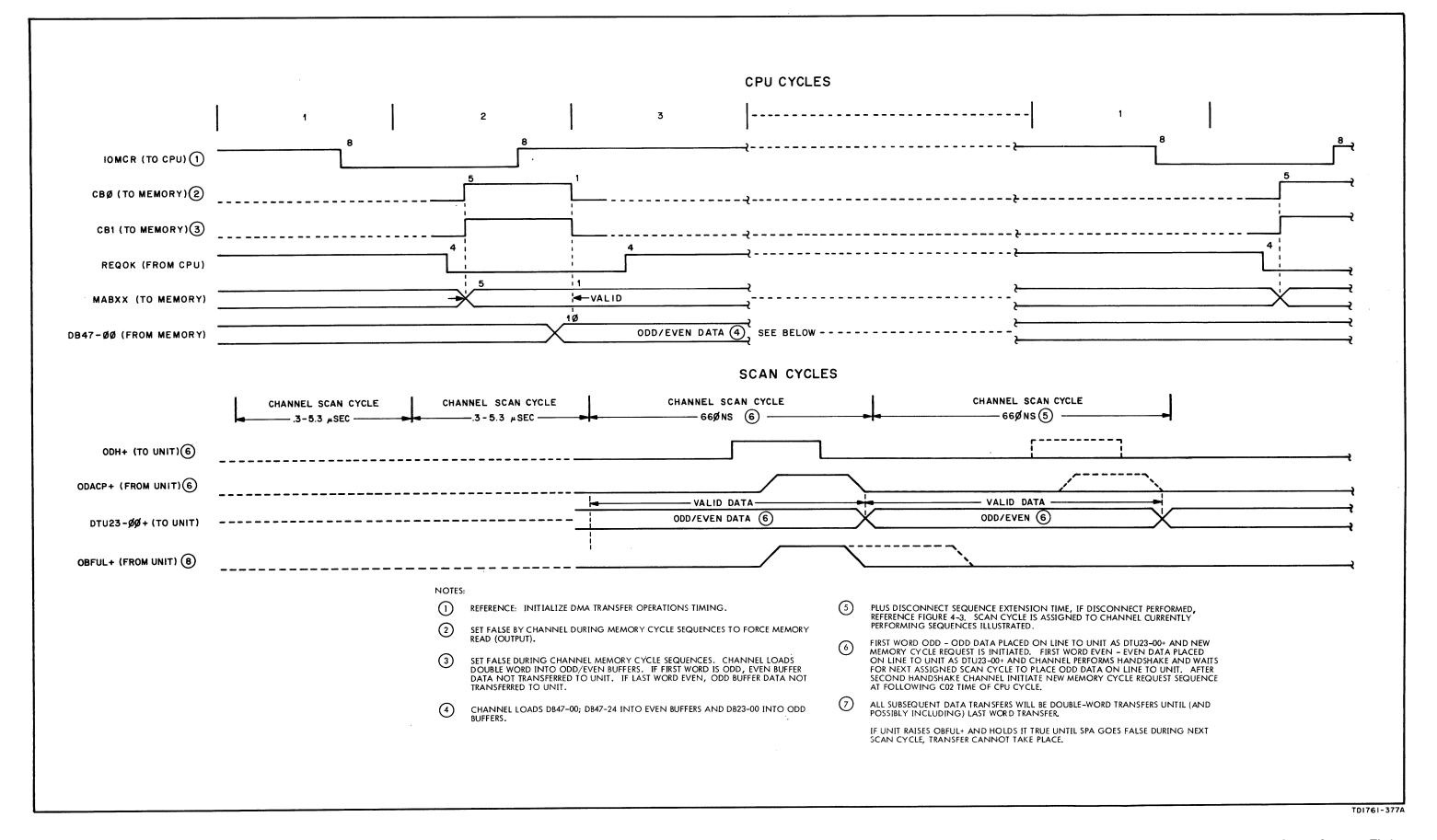

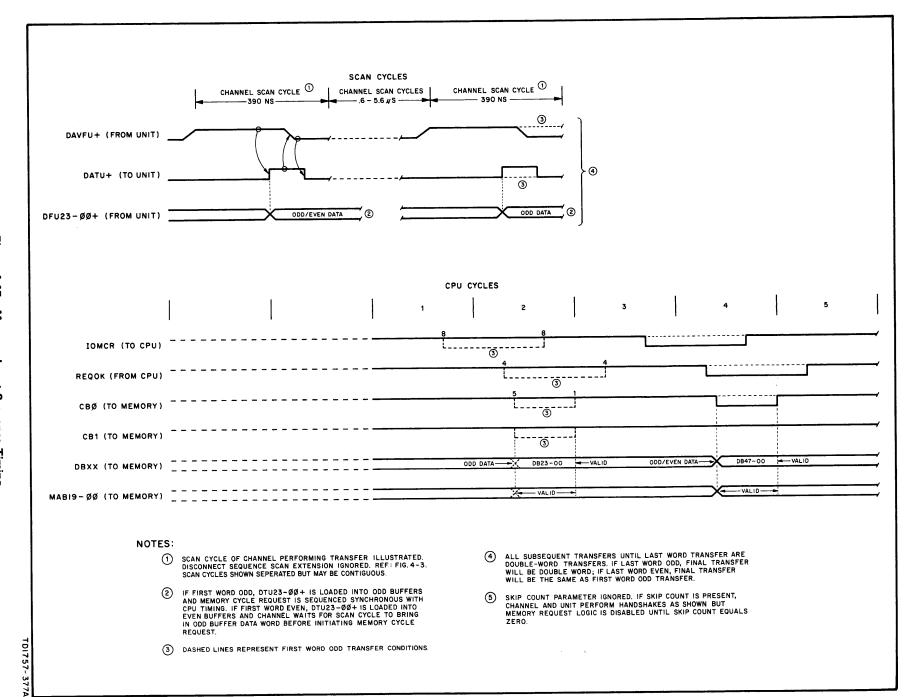

| 4-12         | Initialize Sequence Timing.                            | 4-20   |

| 4-14         | Memory Output Sequence Timing                          | 4-21   |

| 4-15         | Memory Input Sequence Timing                           | 4-23   |

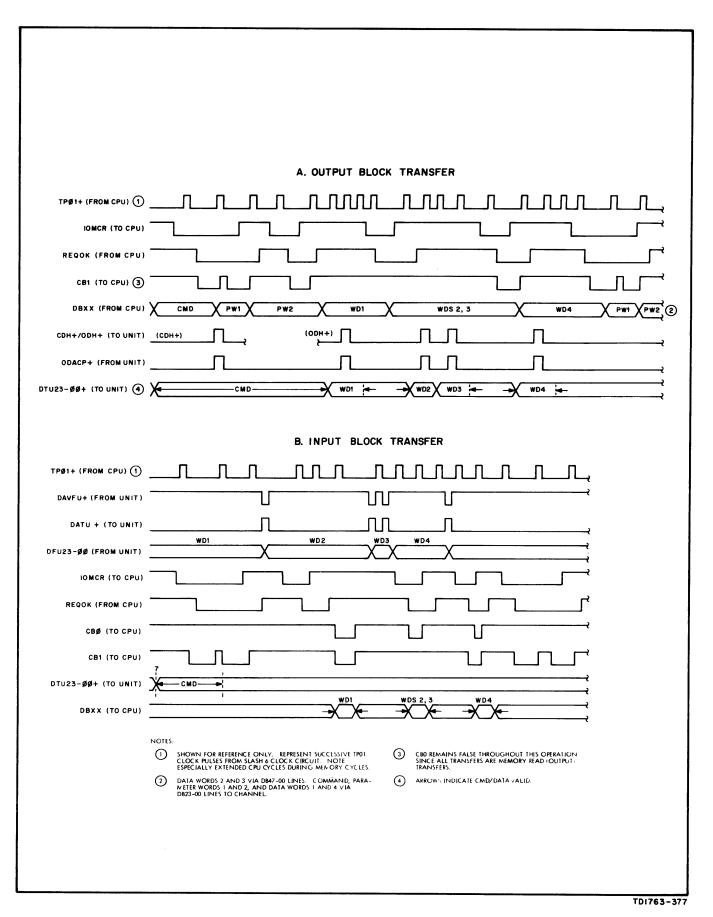

| 4-15<br>4-16 | Lock Scan DMA Operations Timing                        | 4-24   |

| 4-10<br>4-17 | UBC Card Interface Diagram                             | 4-26   |

| 4-17         | OBC Card Interface Diagram                             |        |

| 5-1          | XBC Channel Simplified Block Diagram                   | 5-1    |

| 5-2          | XBC Instruction Formats                                | 5-2    |

| 5-3          | Auto Disconnect Sequence Flowchart                     | 5-3    |

| 5-4          | Memory Address Interface                               | 5-4    |

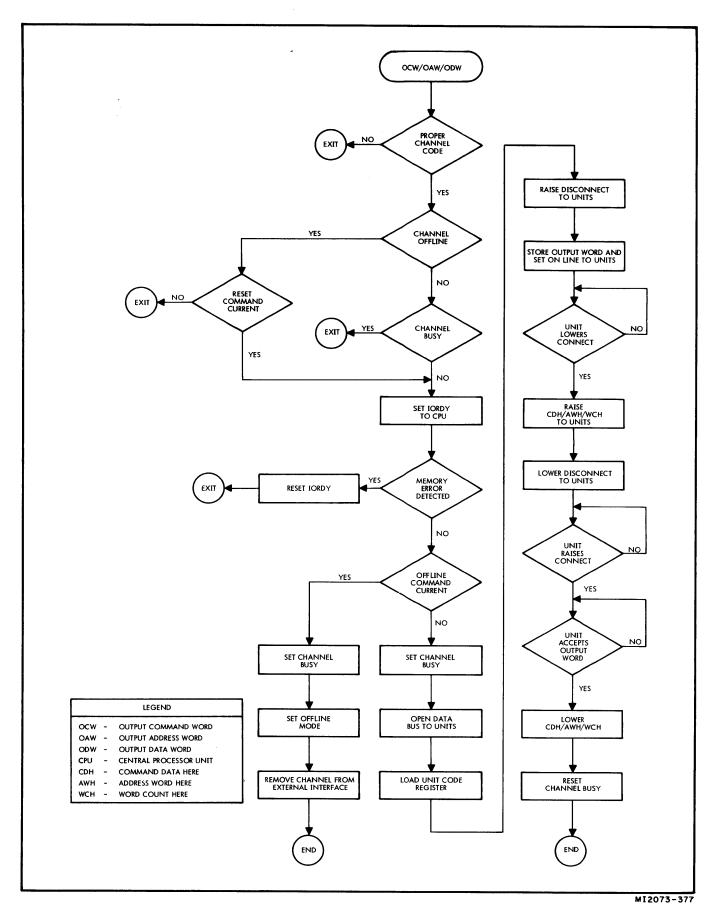

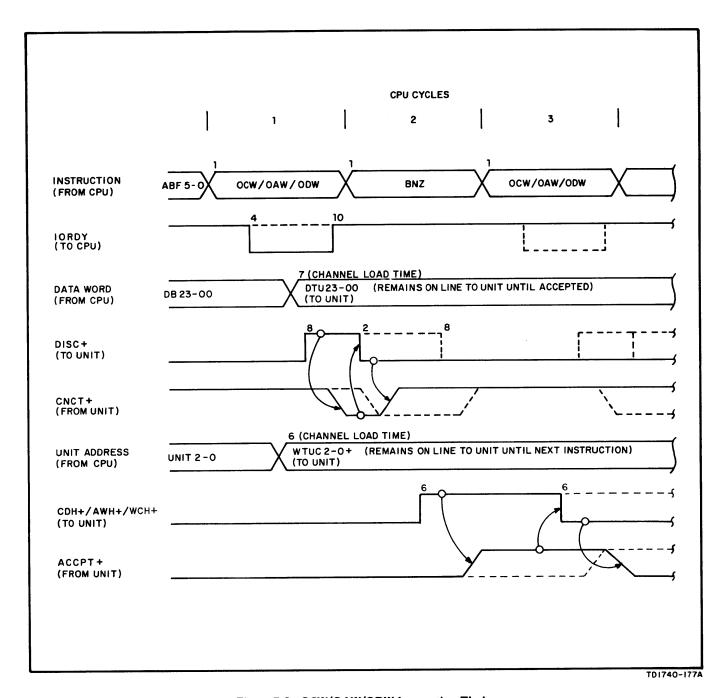

| 5-5          | OCW/OAW/ODW Instruction Flowchart                      | 5-5    |

| 5-6          | OCW/OAW/ODW Instruction Timing                         |        |

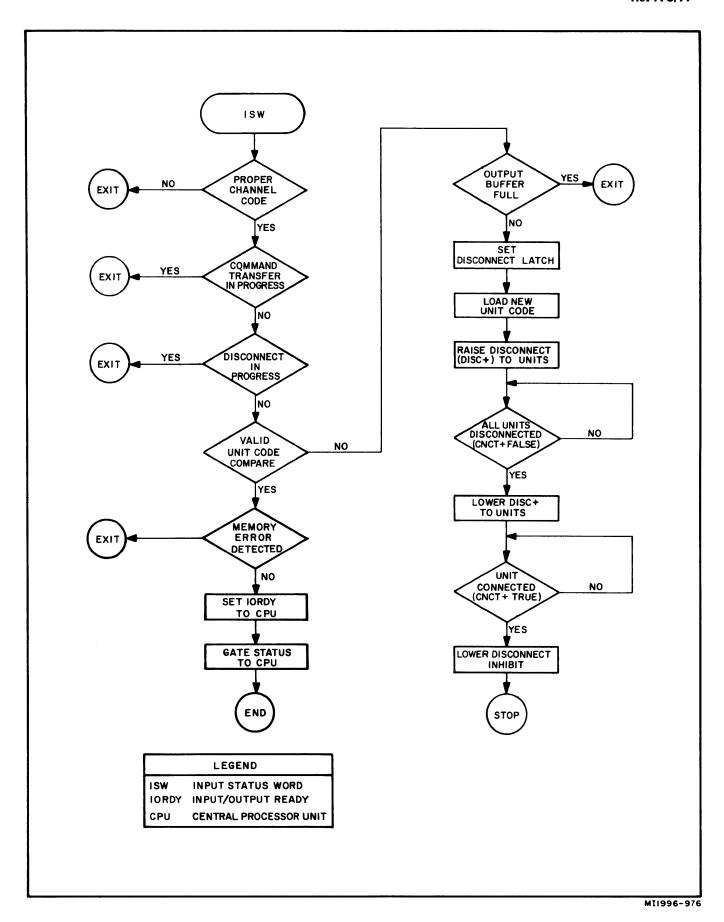

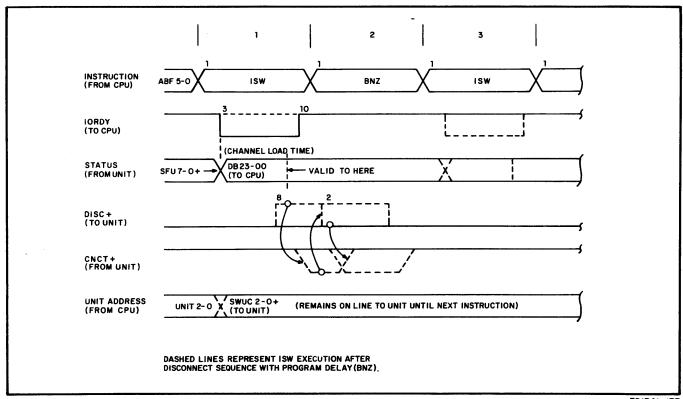

| 5-7          | ISW Instruction Flowchart                              | 5-7    |

| 5-8          | ISW Instruction Timing                                 | 5-8    |

| 5-9          | XBC DMA Operations Flowchart                           | 5-9    |

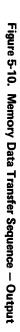

| 5-10         | Memory Data Transfer Sequence — Output                 | 5-10   |

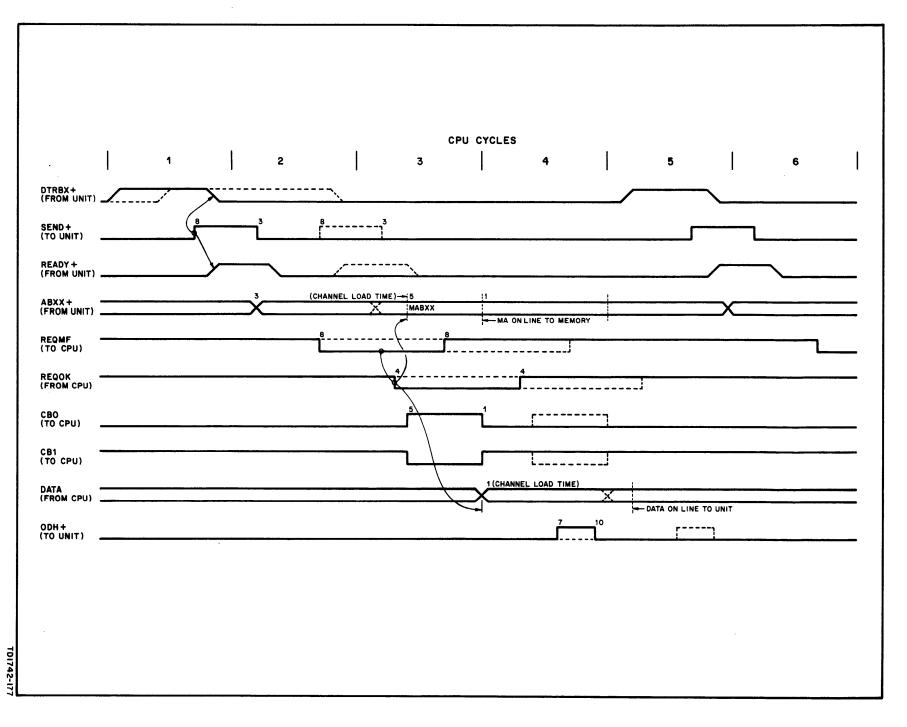

| 5-11         | Memory Data Transfer Sequence — Input                  | 5-11   |

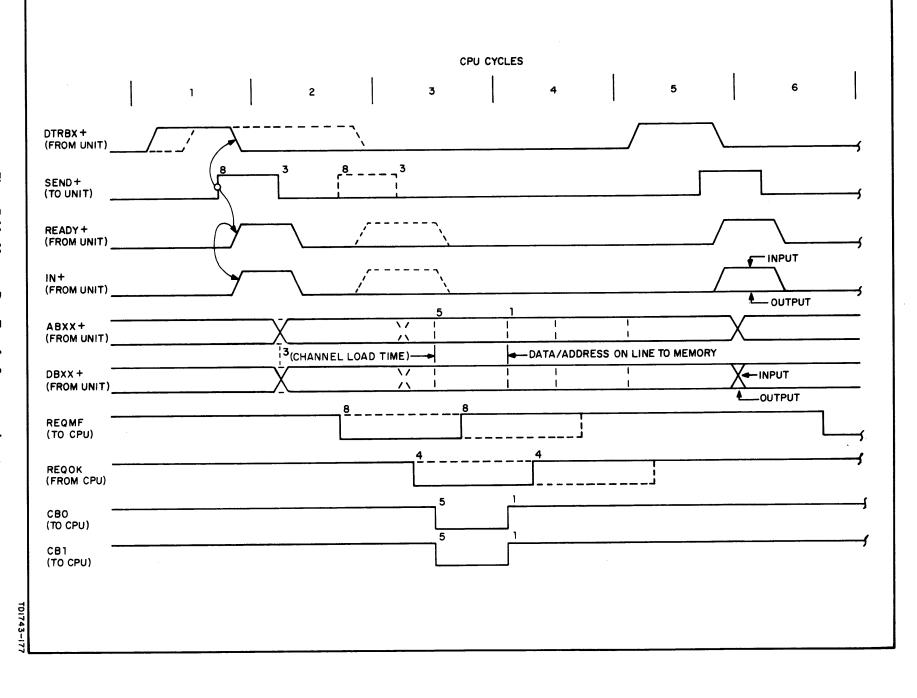

| 5-12         | Error Cycle Sequence                                   | 5-12   |

| 5-13         | XBC Channel Interface                                  | 5-13   |

| 5-14         | Typical Unit Controller Interface Logic                | 5-16   |

| A-1          | I/O Channel Card Edge Interface, UBC and PIOC (Note 1) | . A-2  |

|              | TAD! 50                                                |        |

|              | TABLES                                                 |        |

| Table        |                                                        | Page   |

| 4.4          | CPU — Channel Interface*                               | . 1-16 |

| 1-1          | CPU — Channel Interrace                                |        |

| 1-2          | Interrupt Interface — Options Board                    |        |

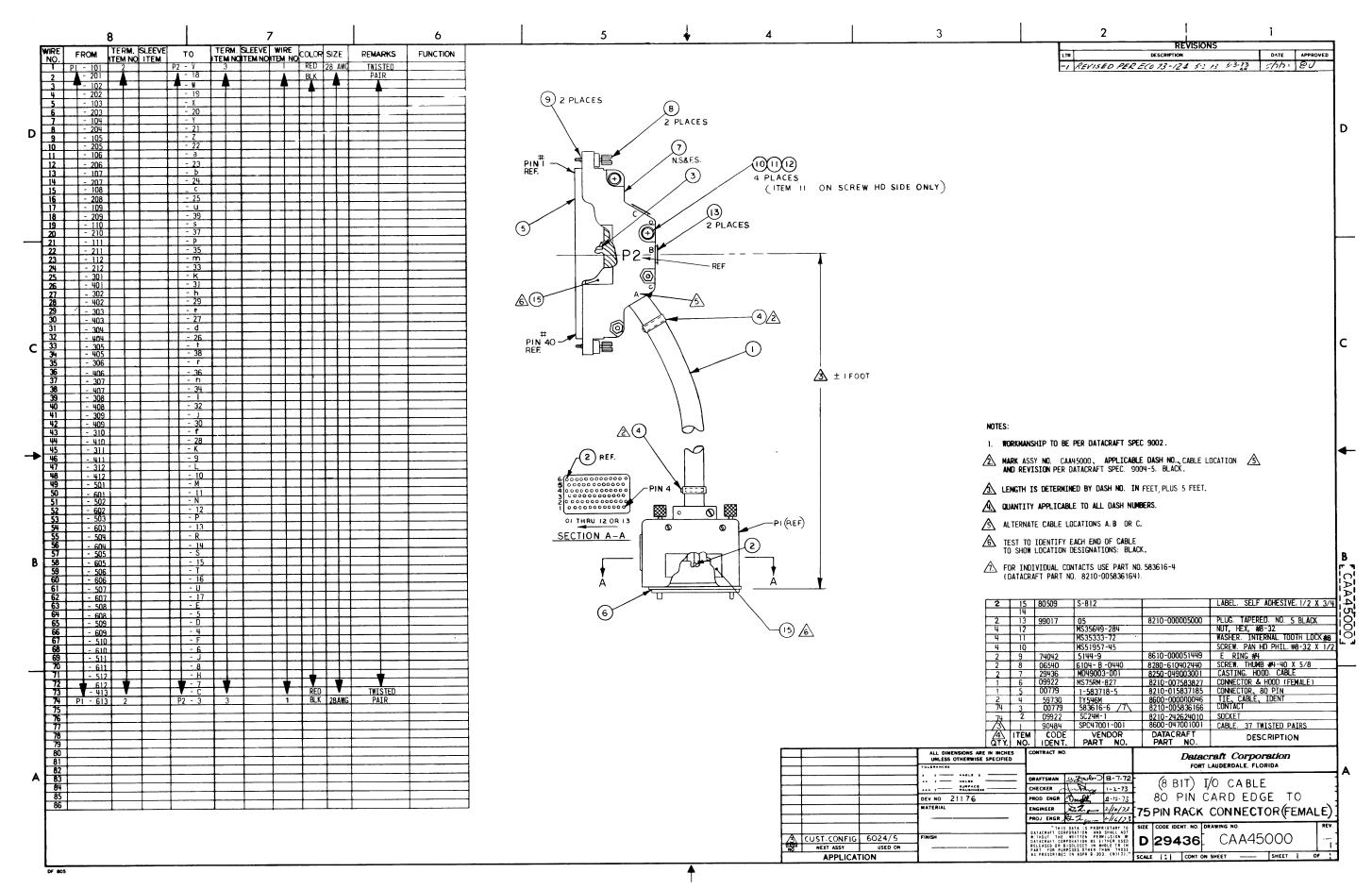

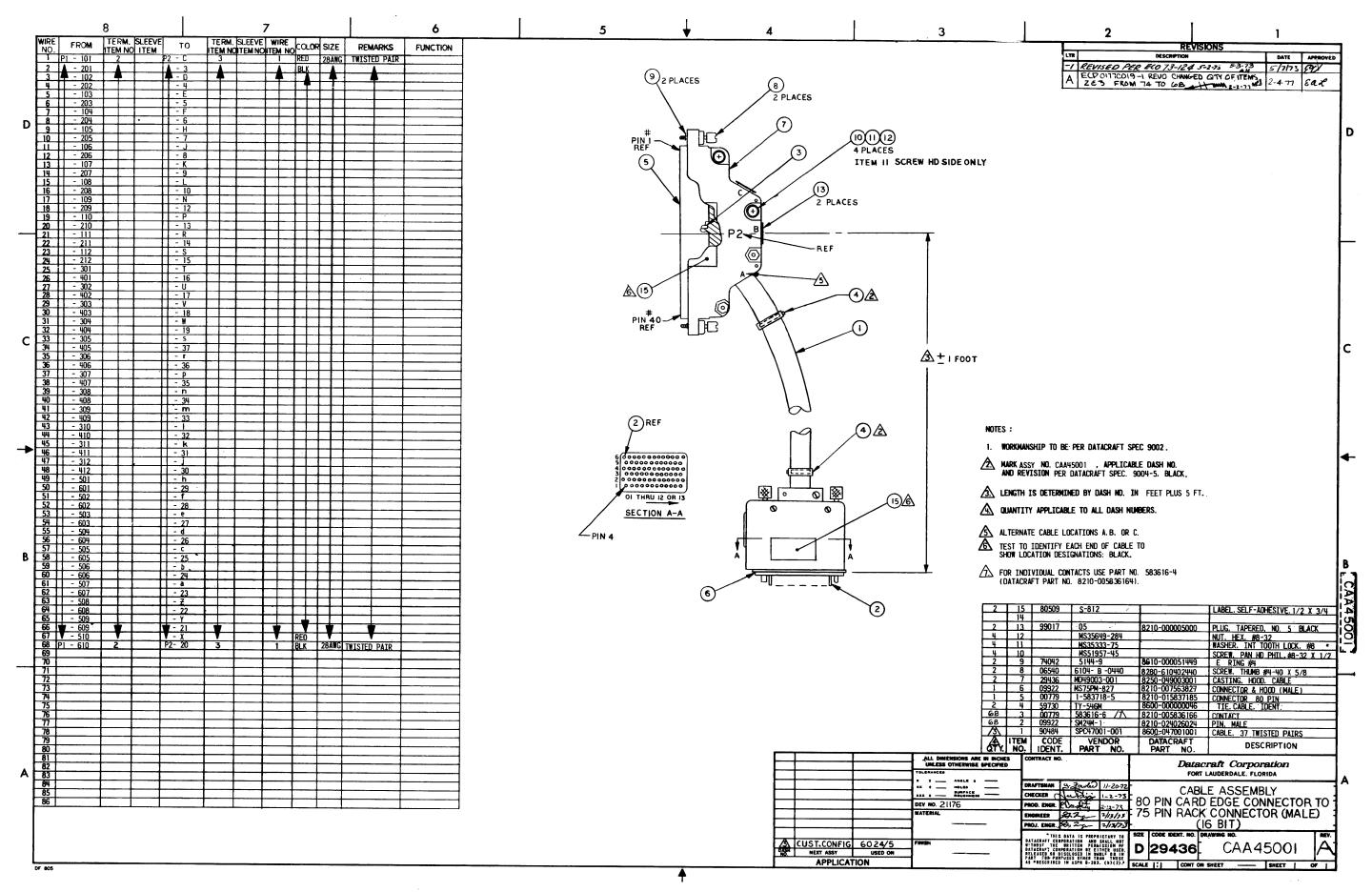

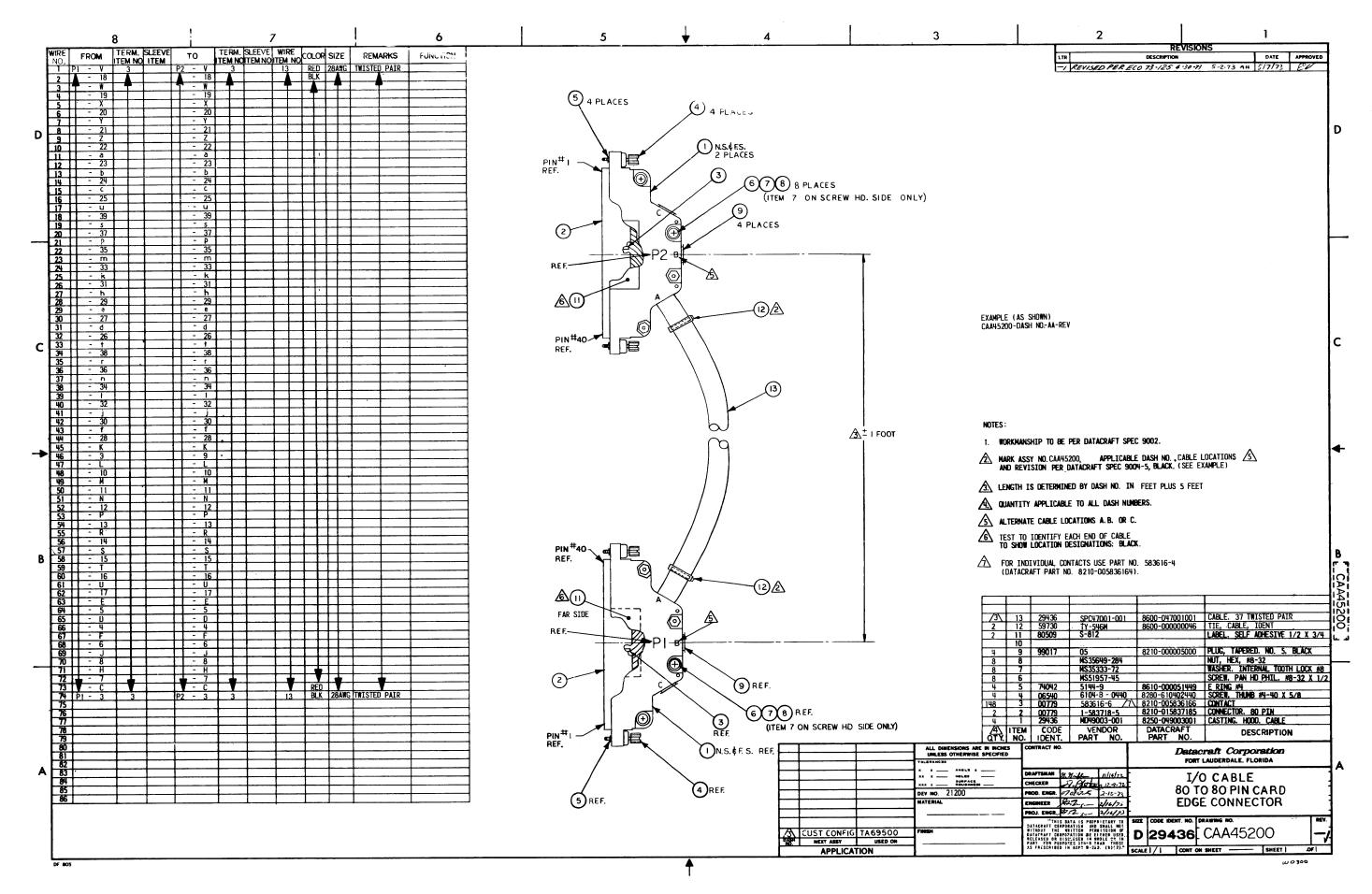

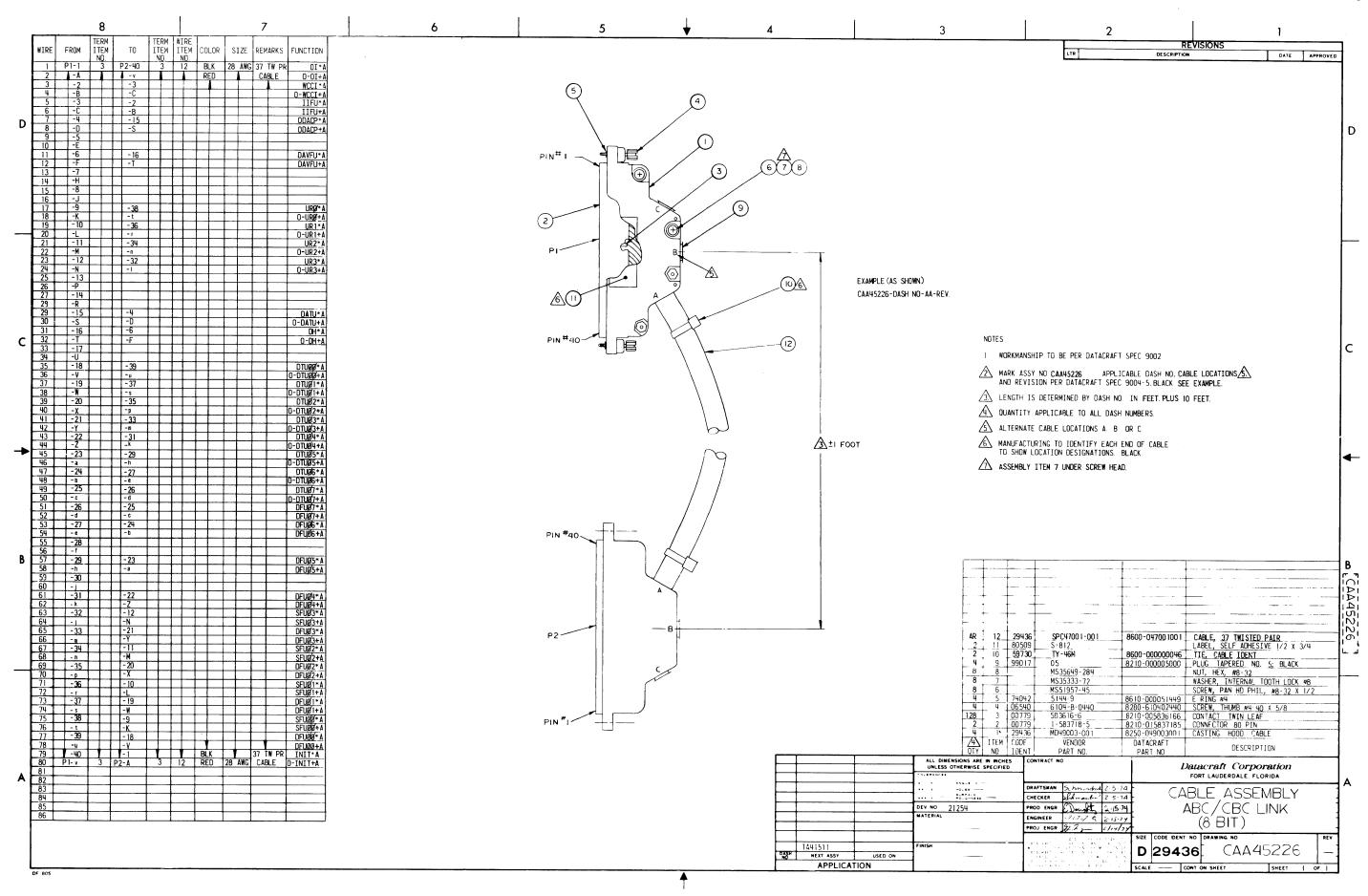

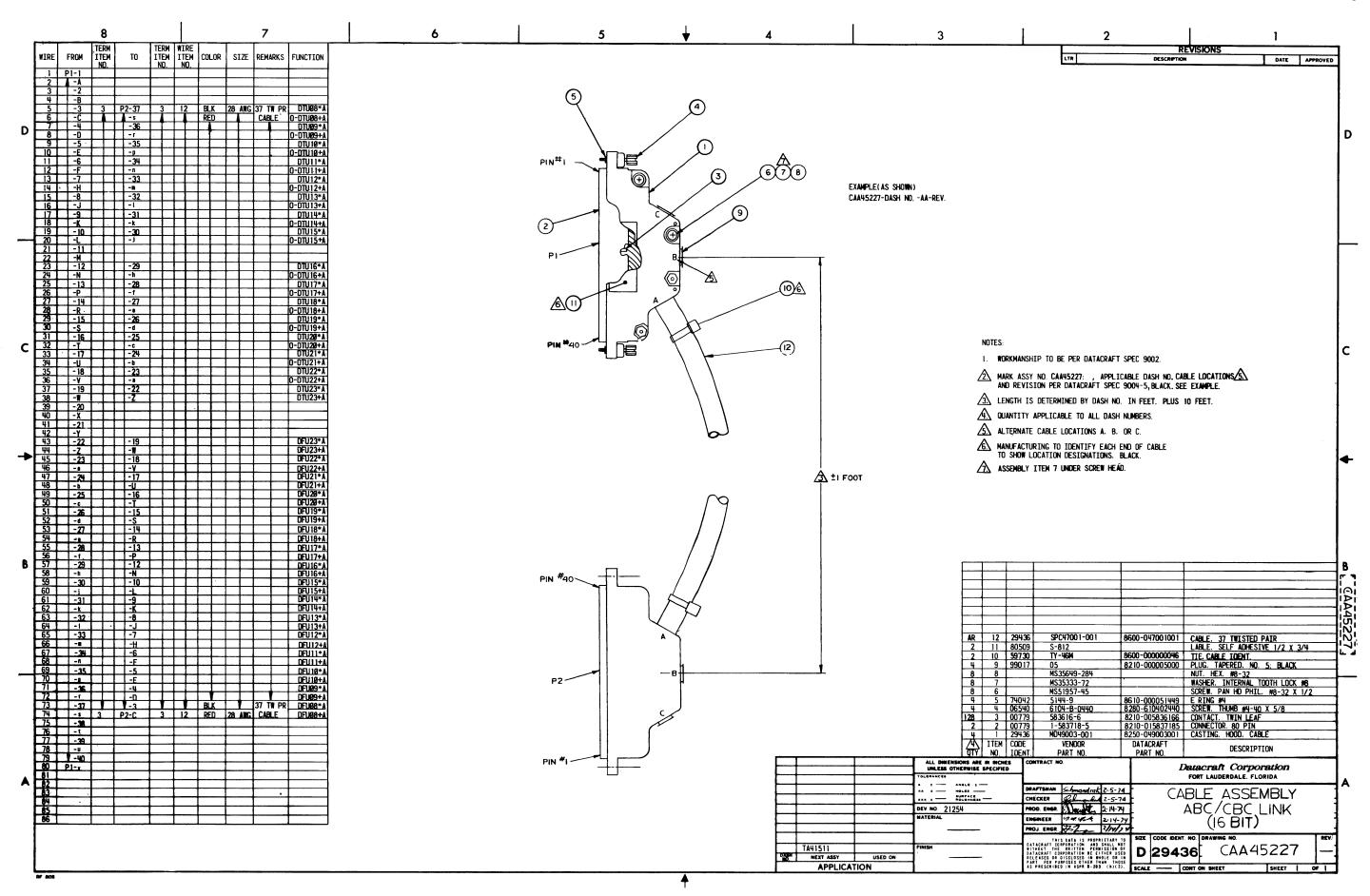

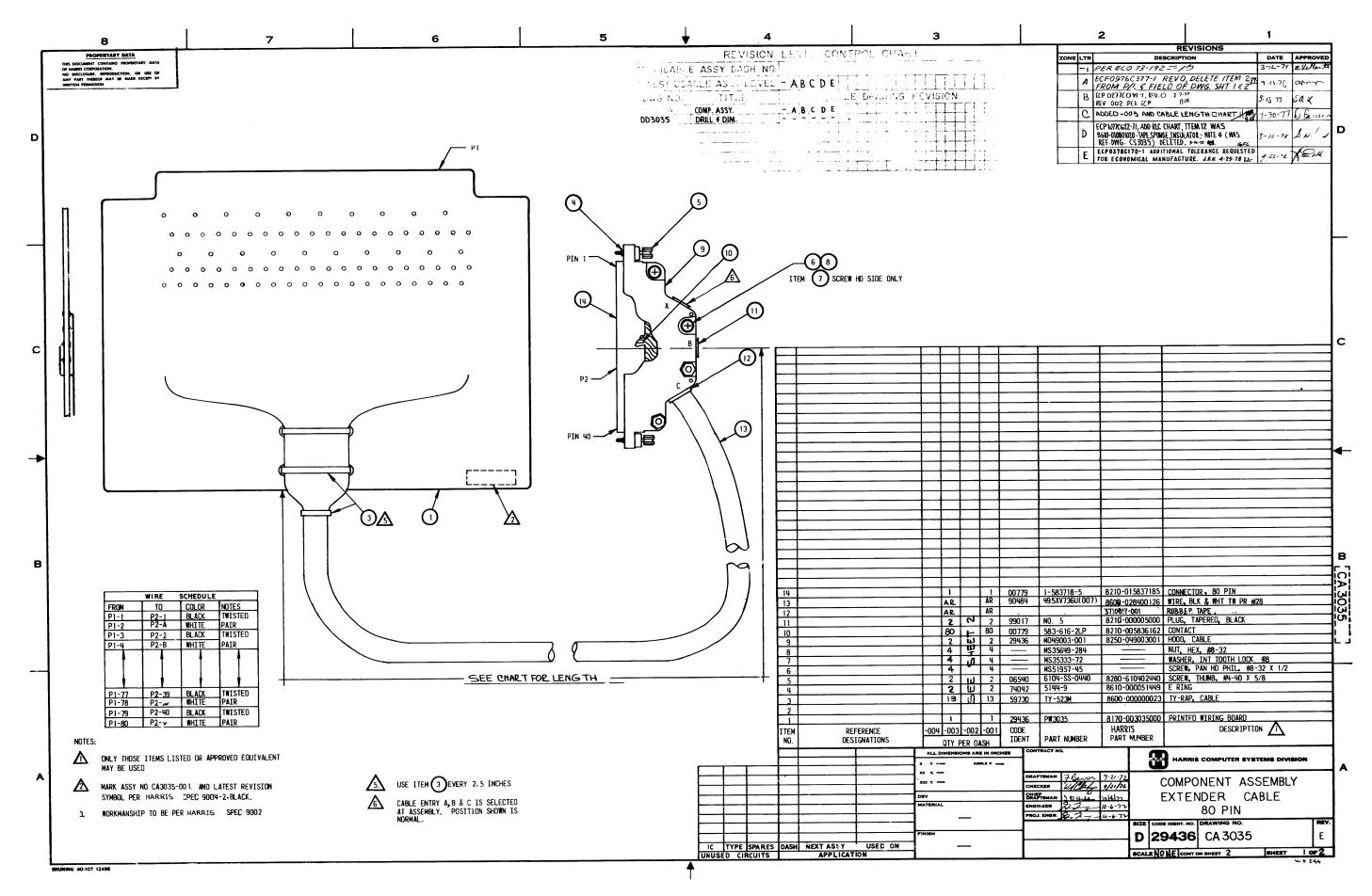

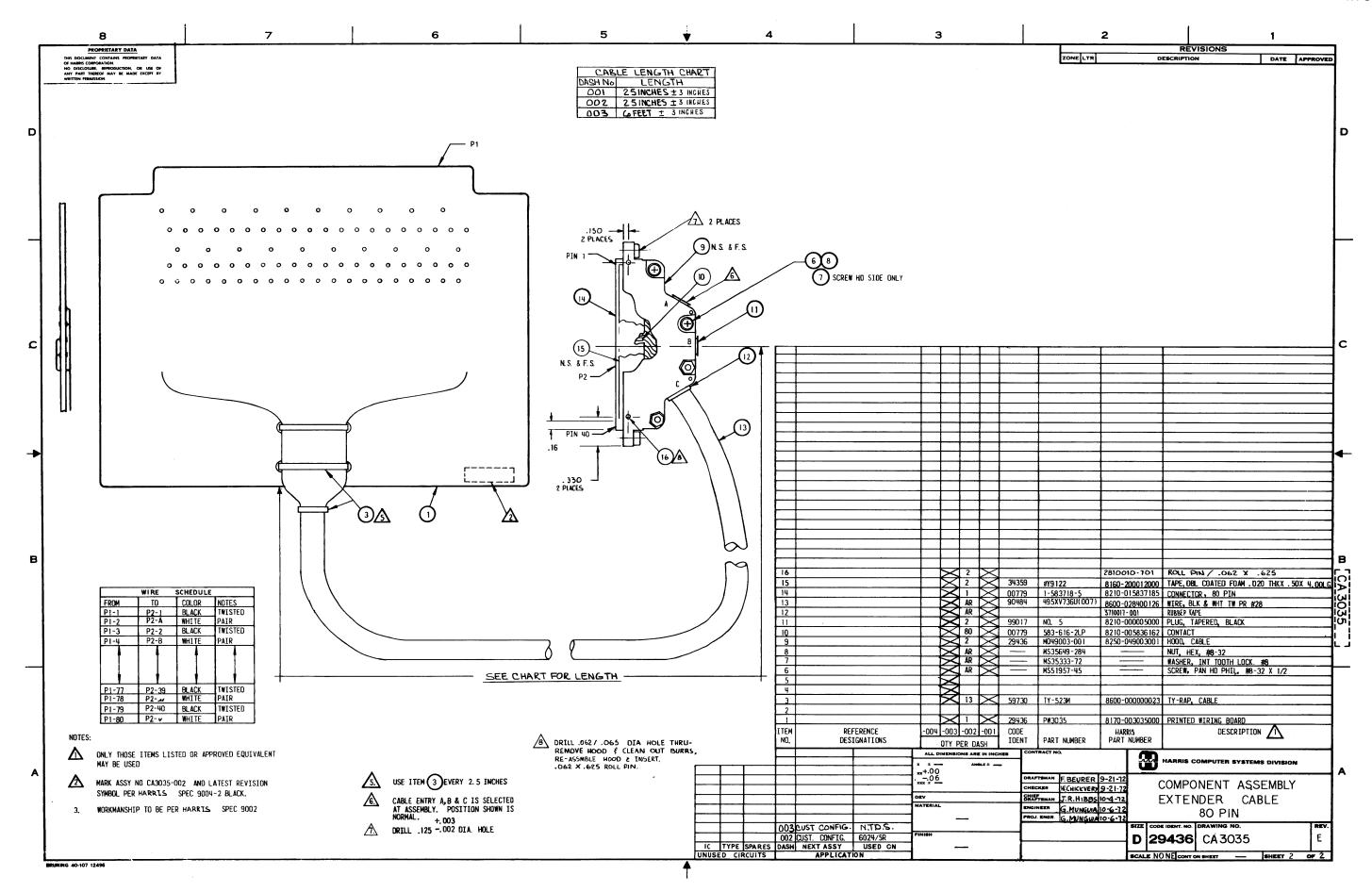

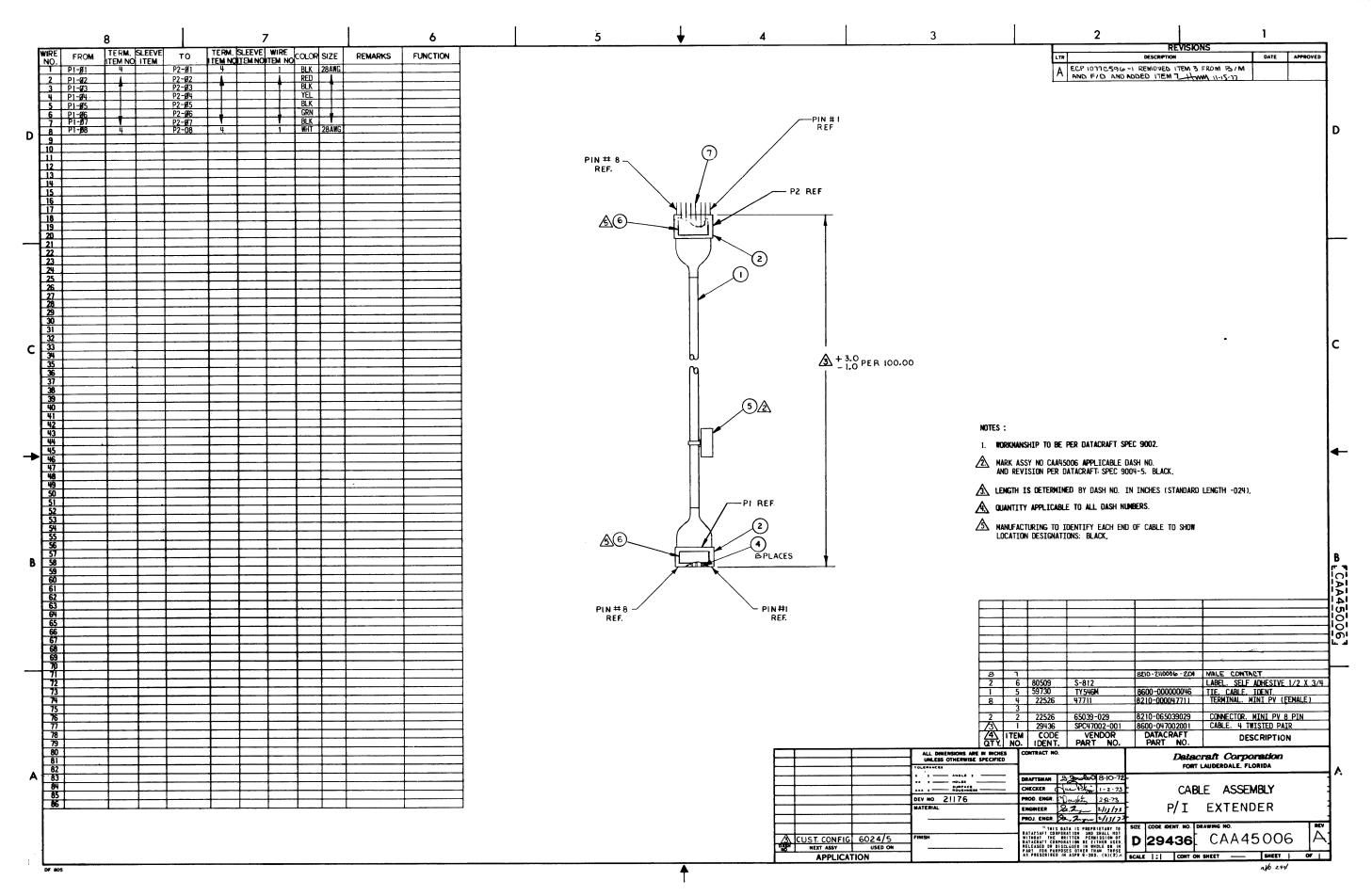

| 1-3          | I/O Channel — Unit Controller Cables                   | . 1-23 |

| 1-4          | 1/O Channel — Ontt Controller Cables                   |        |

| 2-1          | External and Internal I/O Interface Signal Equivalents |        |

| 2-2          | PIOC Interrupt Interface                               | . 2-7  |

| 3-1          | IBC Channel-Unit Controller Interface                  | . 3-8  |

| 5-1          | XBC Channel — Unit Controller Interface                | . 5-15 |

## SECTION I

#### 1-1 SCOPE

This manual describes the operational and interface characteristics of the input/output channels (IOC's) used in S100 and S500 computer systems designed and manufactured by the Computer Systems Division of Harris Corporation (HCSD), Fort Lauderdale, Florida. Section I of this manual is devoted to basic I/O conventions. Various IOC's that may be configured in S100 or S500 systems are described later, with a section of this manual devoted to each channel type. Departures from the standard I/O conventions are also treated in subsequent sections. The following I/OC's are covered in this manual.

| Channel | Name                                                                     | S100<br>, <u>Model</u> | S500<br>Model |

|---------|--------------------------------------------------------------------------|------------------------|---------------|

| PIOC    | Programmed Input/Output<br>Channel (with integrated<br>unit controllers) | 645                    | 845           |

| IBC     | Integral Block Controller                                                | 649                    | 849           |

| UBC     | Universal Block Controller                                               | 647                    | 847           |

| XBC     | External Block Controller                                                | 648                    | 848           |

## 1-2 RELATED PUBLICATIONS

The following Harris publications contain information relative to S100 and S500 System I/O operations and should be consulted for detailed information.

| Publication | Title                                                                 |

|-------------|-----------------------------------------------------------------------|

| 0800003     | Technical Manual, SLASH 6 Digital Computer (S100)                     |

| 0800008     | Technical Manual, Model 8<br>Digital Computer (S500)                  |

| 0830003     | Reference Manual, SLASH 6 Digital Computer Systems                    |

| 0830005     | Reference Manual, Series 100<br>Computer Systems S115, S125, and S135 |

| 0830006     | Reference Manual, Series 500<br>Computer Systems                      |

| 0820014     | Technical Manual, 8-Bit Programmed Input/Output Channel (PIOC)        |

| 0820015 | Technical Manual, Integral Block<br>Controller (IBC) I6O Channel  |

|---------|-------------------------------------------------------------------|

| 0820016 | Technical Manual, Universal Block<br>Controller (UBC) I/O Channel |

| 0820018 | Technical Manual, External Block<br>Controller (XBC) I/O Channel  |

#### 1-3 PURPOSE

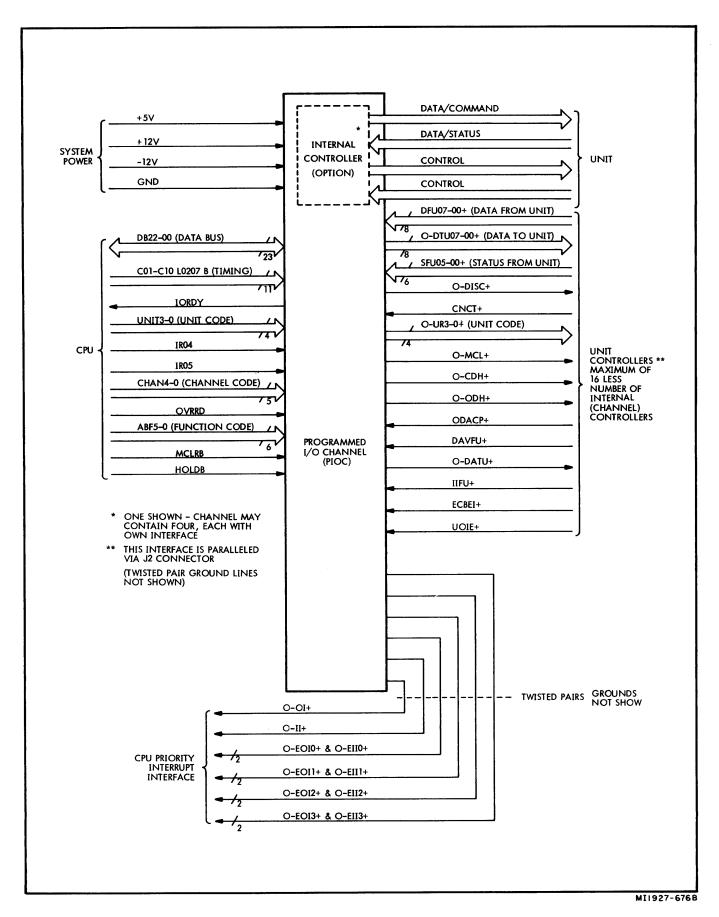

The I/O channels provide control needed by the Central Processor Unit (CPU) to communicate with all system peripherals. A channel may be assigned up to sixteen peripheral, or unit, controllers with which it communicates. Some IOCs also have the capability to have the unit controllers mounted on the channel cards.

The interface with external controllers is via channel card edge connectors which allow cabling for either an 8- or a 24-bit party line bus, depending on the channel's transfer capability. The cabling consists of twisted pairs with a characteristic impedance of 100 Ohms. Cabling requirements for the external controller interface is specified in the section coverage for the affected channels. However, the interface is via standard Harris cables; the interface is described later in this section and the cable configurations are identified.

The channels are designed to perform either single word transfer (also designated programmed transfer) or memory transfer operations. (Memory transfer operations are also designated as block control and direct memory access, DMA, operations.) In programmed transfer operations the channel is instructed by the CPU to communicate with the peripherals for the purpose of transferring an 8- or 24-bit word to (output instructions) or from (input instructions) a controller/unit combination on the channel's I/O interface. Programmed transfer operations are also used to initialize applicable channels for memory transfer operations in which the CPU relinquishes data transfer control to the channel or units on the channel's interface. The channel then proceeds under self control to transfer blocks of data to or from memory via "cycle stealing" conventions. The channel may be capable of re-initializing itself to perform further block data transfers under the command constraints originally loaded (data chaining) or may access a new command from memory and perform further block data transfers (command chaining) under the new command constraints.

All of the I/O channels designed for S100 or S500 installation are capable of programmed transfer operations; the PIOC channel is restricted to this type of operation. The UBC, IBC, and XBC channels are designed to perform memory transfer, i.e., block controller (BC) operations.

#### 1-4 INPUT/OUTPUT STRUCTURE

#### 1-4.1 General Description

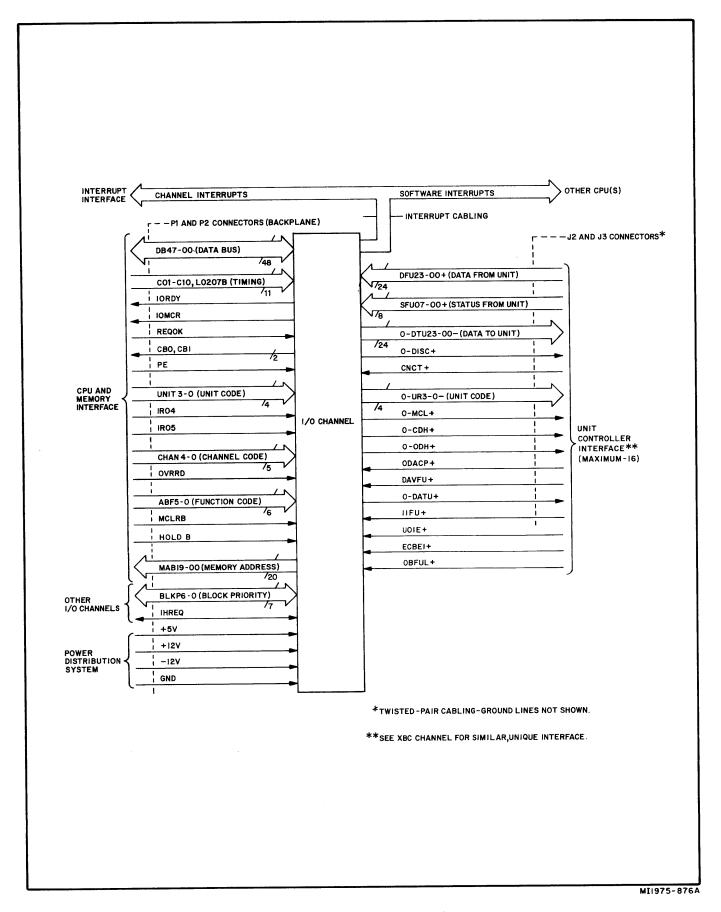

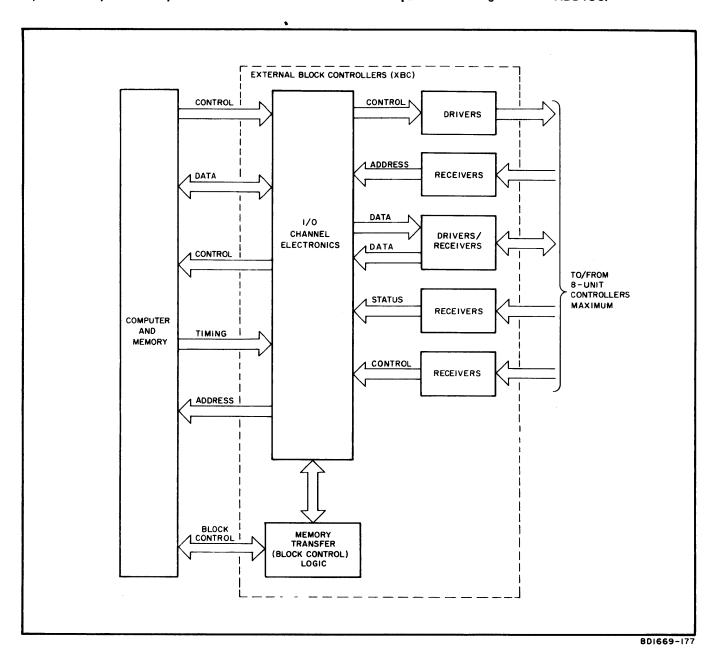

A simplified block diagram of the computer I/O structure is shown in Figure 1-1. The maximum capabilities of each I/O channel type are illustrated. Not shown, however, is the multiple — CPU configuration that allows a CPU to access units on another CPU's I/O interface and vice versa. This "daisy chain" capability is discussed later in this section.

#### 1-4.2 Equipment Cabinet

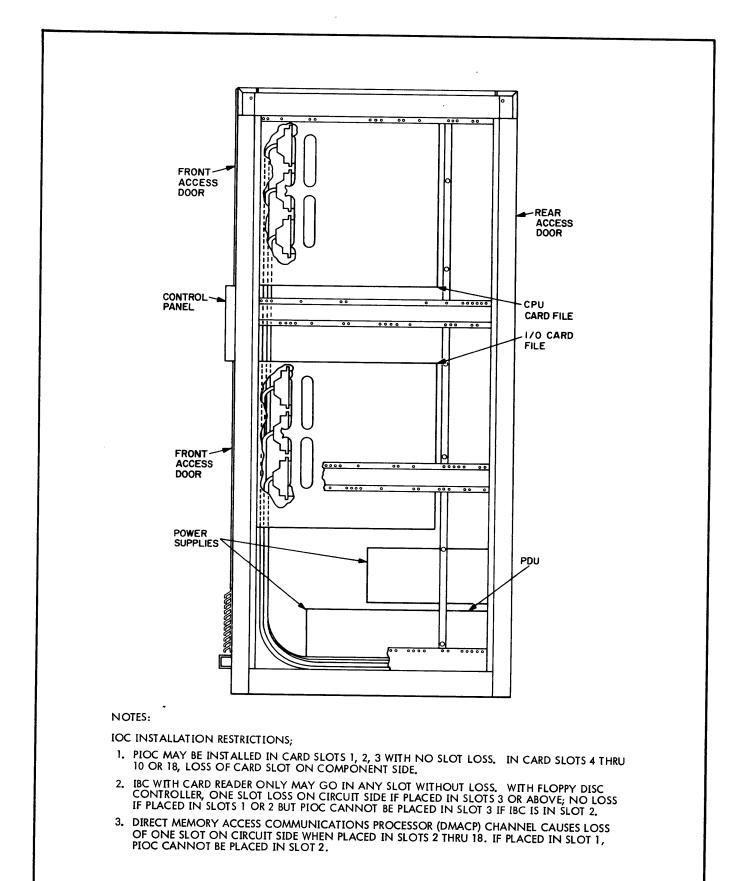

The computer equipment cabinet consists of a standard 19-inch rack to hold chassis assemblies, power supplies, and the control panel. Figure 1-2 illustrates the basic cabinet configuration. I/O channel cards are always installed in the lower chassis assembly because of the requirement for routing external cabling through the bottom of the rack. Channel card installation restrictions are included in Figure 1-2.

#### 1-4.3 I/O Channel Card

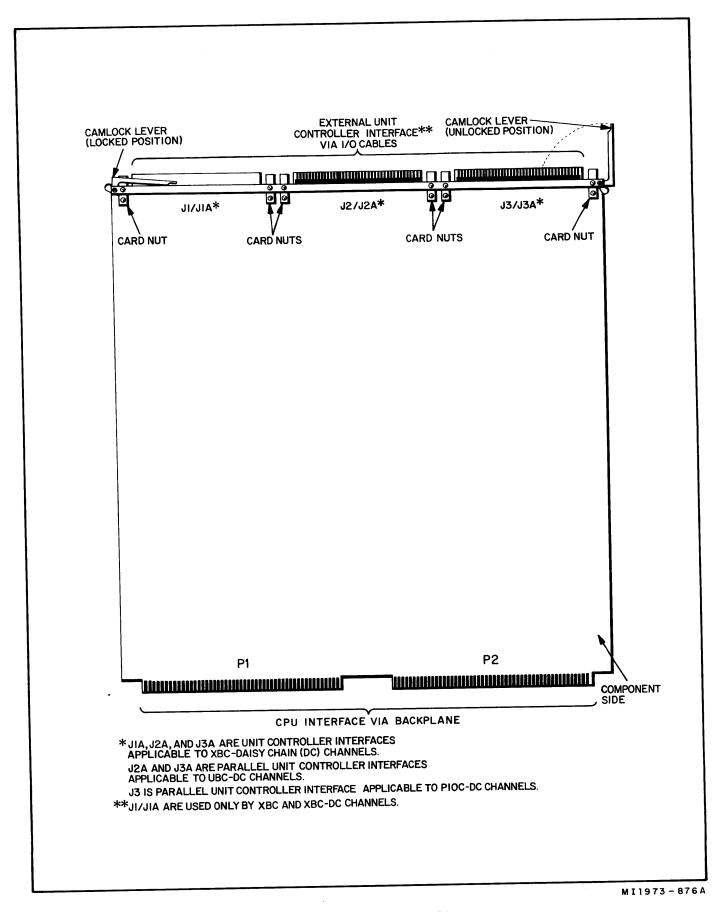

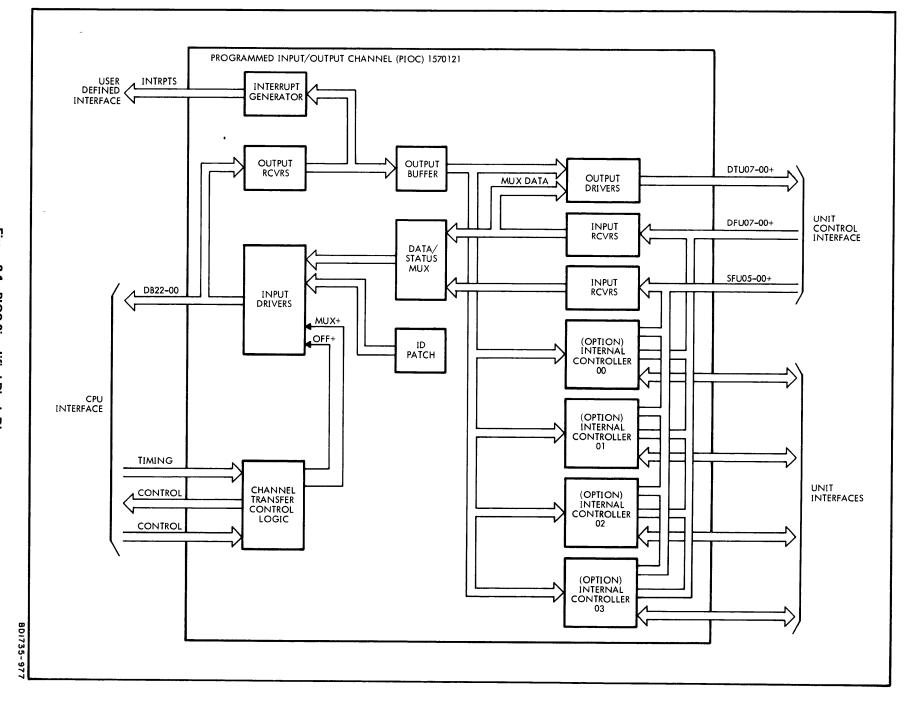

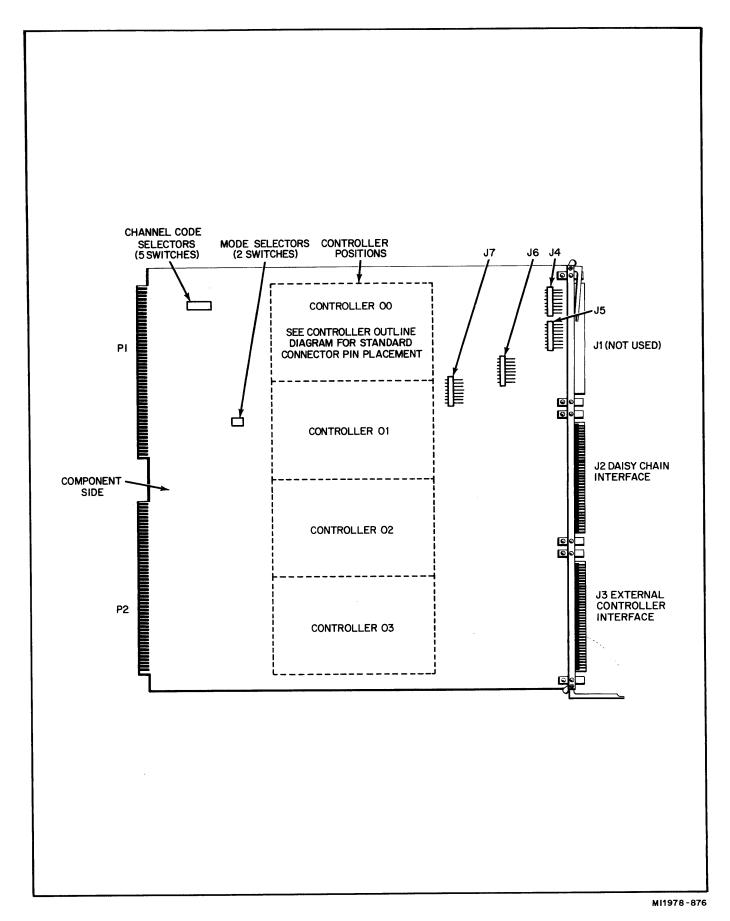

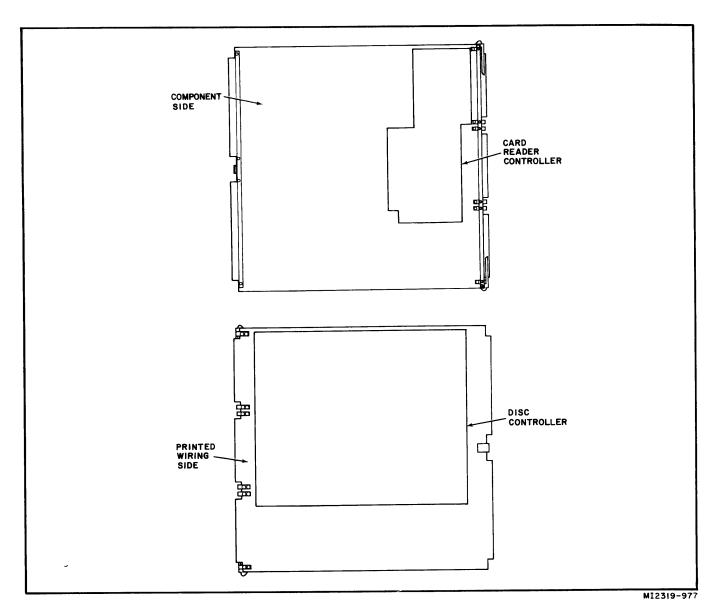

An I/O channel consists of a single circuit card containing the logic and interface needed to perform assigned I/O functions. A channel card (Figure 1-3) is approximately 15.7 inches (39.9 cm) high by 16.5 inches (41.9 cm) wide; a card's total thickness varies with function. (The PIOC and IBC cards have the capability to hold internal controllers on one or both sides of the channel card and thicknesses therefore vary with the particular system.)

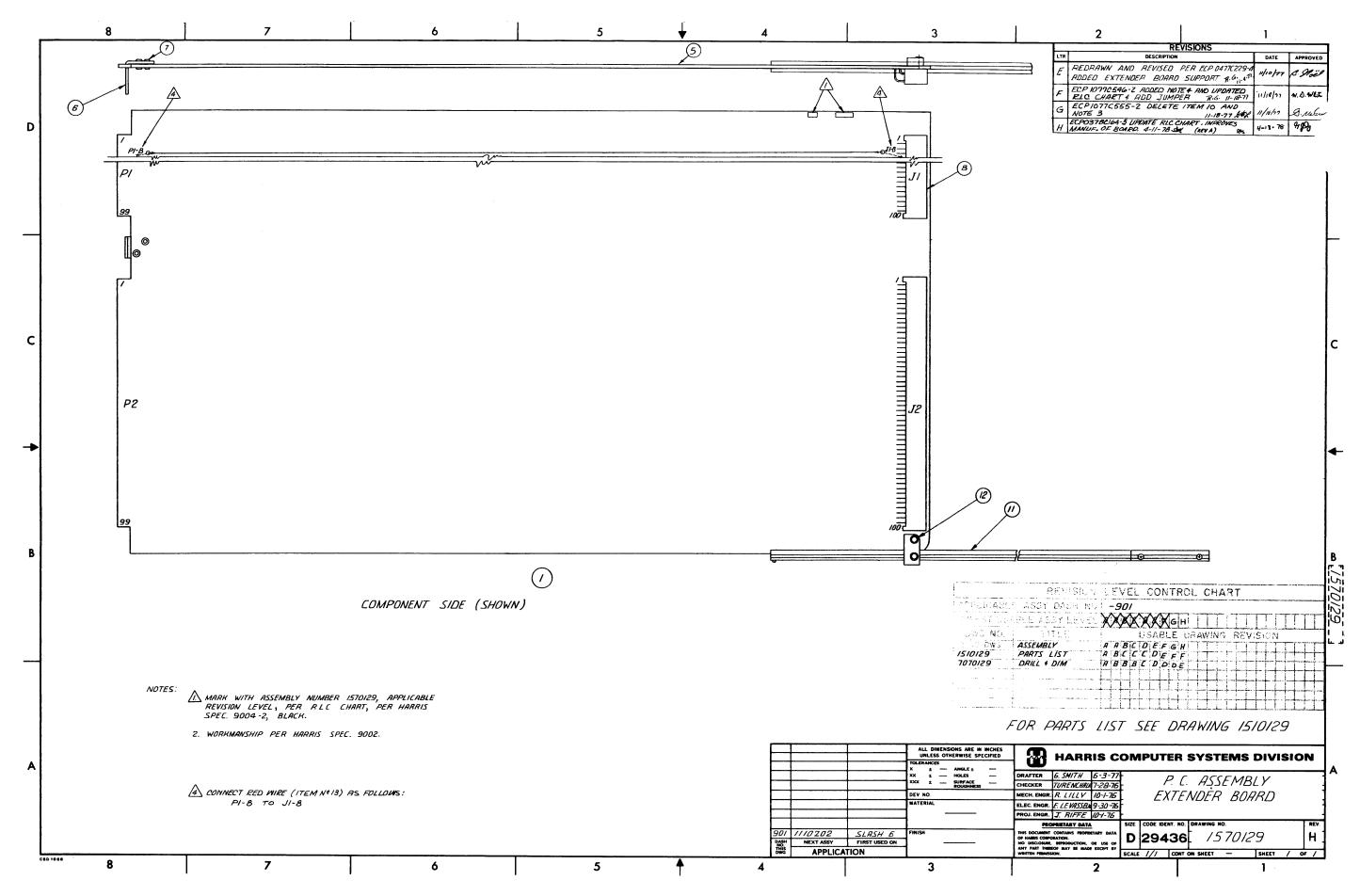

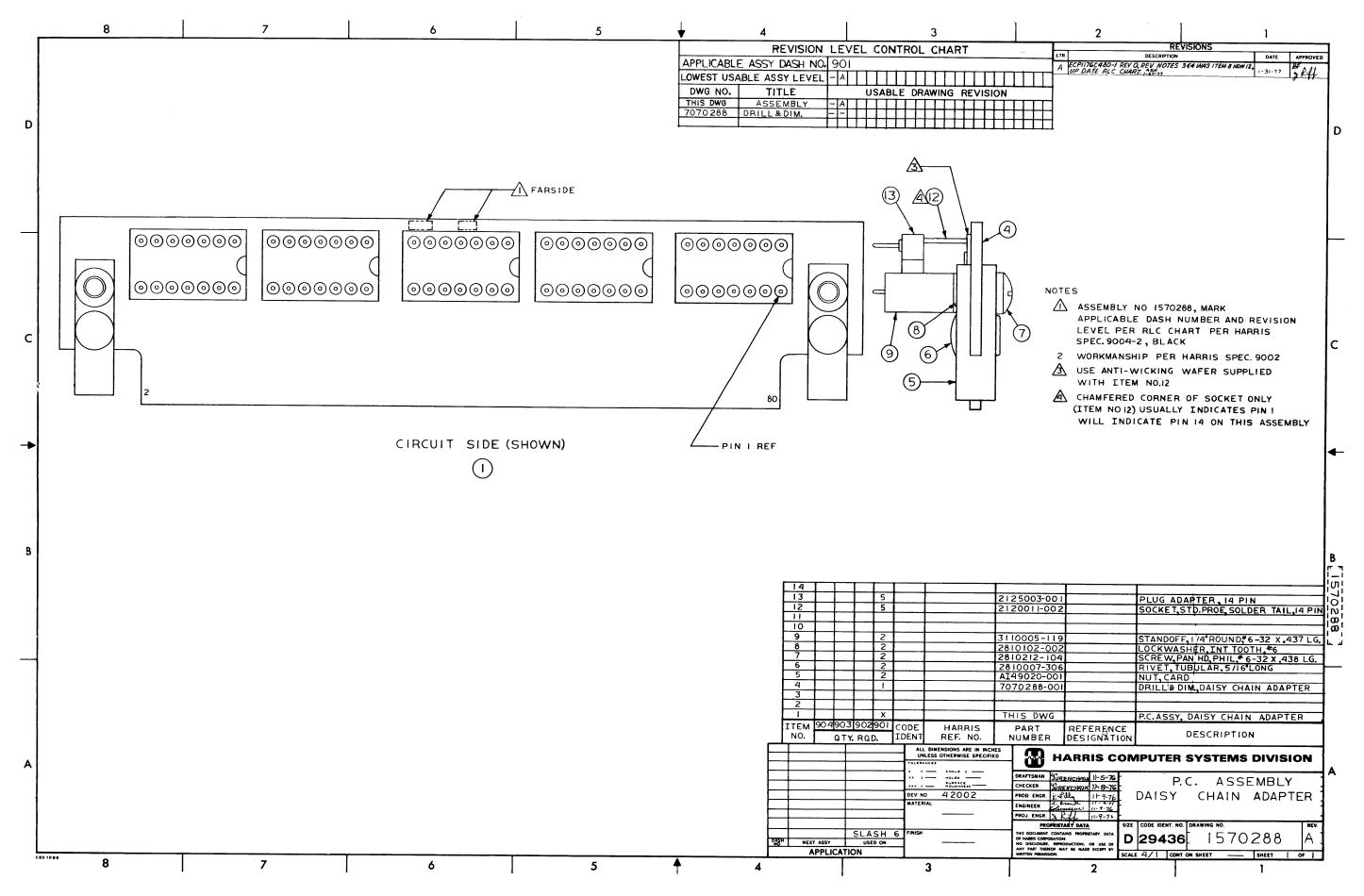

A channel card may consist of two or more layers of laminated board material. Channel logic components are located on one side of a channel card and printed wiring is located on the opposite side. (IBC channels also provide connector interface on the printed wiring side for controller installations.) All I/O channel cards contain two 100-pin edge connectors for interface to the CPU and memory via the backplane. Each card has three 80-pin edge connectors at the opposite edge of the card for external I/O interface. The IBC channel card's only external I/O interface is via self-contained controllers. (Figure 1-3 illustrates I/O channel cards' usage of these connectors for I/O interface purposes. The multi-CPU adaptor, or daisy chain, interface is made via the installation of 1570288 assemblies at each J1, J2, or J3 connector.)

The channel cards contain cam lock levers at the top and bottom of the card at the outer (I/O) interface edge. The levers provide a means of locking the channel cards in place via ejector springs on the card file assembly. Card nut installations at each I/O connector end provides a means for securing I/O cables.

## 1-5 INPUT/OUTPUT CHANNEL CONVENTIONS

#### 1-5.1 Instructions

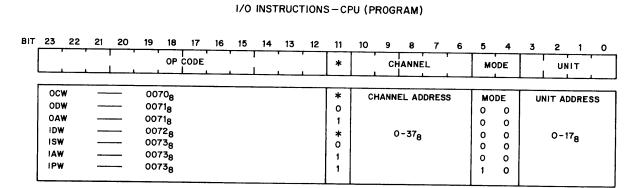

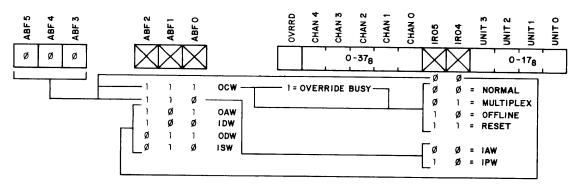

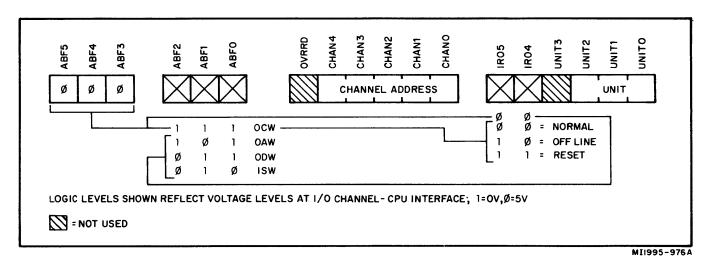

The I/O channels execute instructions for the purpose of providing communications control between the CPU or memory and the units on the channels' I/O interfaces. Six ABsolute Function bits (ABF5-0) are used to determine the basic instruction. Three additional bits may be used to modify the basic instruction; the three bits are two Instruction Register bits (IR05 and IR04) and the override (OVRRD) bit. The nine bits are set via CPU action in response to the current program and each channel is equipped with decoder circuits which activate control circuits to execute the instructions. Figure 1-4 illustrates

Figure 1-1. Computer Input/Output Structure

MI1972-876B

Figure 1-2. Computer Cabinet

Figure 1-3. I/O Channel Outline Diagram

OP CODE 00708 USES BIT 11 FOR OVERRIDE CONTROL AND BITS 5 AND 4 FOR MODE CONTROL -SEE BELOW. OP CODE 00718 USES BIT 11 TO SPECIFY ODW/OAW INSTRUCTIONS.

OP CODE 00728 USES BIT 11 FOR CPU CHARACTER MERGE FUNCTION BUT HAS NO I/O CHANNEL IMPACT.

OP CODE 00738 USES BIT 11 TO SPECIFY ISW/IAW INSTRUCTIONS AND BIT 5 TO SPECIFY IAW/IPW INSTRUCTIONS.

#### I/O INSTRUCTIONS-CHANNELS

LOGIC LEVELS SHOWN REFLECT VOLTAGE LEVELS AT I/O CHANNEL-CPU INTERFACE; 1=0V,Ø=5V.

#### **APPLICATIONS**

| INSTRUCTION                                                                       | PIOC                            | IBC                          | UBC                             | XBC                           |

|-----------------------------------------------------------------------------------|---------------------------------|------------------------------|---------------------------------|-------------------------------|

| OCW - NORMAL MODE - OFFLINE MODE - MULTIPLEX MODE - RESET MODE - OVERRIDE CONTROL | YES<br>YES<br>YES<br>YES<br>YES | YES<br>NO<br>NO<br>NO<br>YES | YES<br>YES<br>YES<br>YES<br>YES | YES<br>YES<br>NO<br>YES<br>NO |

| ODW                                                                               | YES                             | NO                           | YES                             | YES                           |

| OAW                                                                               | YES                             | YES                          | YES                             | YES                           |

| IDW                                                                               | YES                             | NO                           | YES                             | NO                            |

| ISW                                                                               | YES                             | YES                          | YES                             | YES                           |

| IAW                                                                               | NO                              | YES                          | YES                             | NO                            |

| IPW                                                                               | NO                              | YES                          | YES                             | NO                            |

MI1976-876A

Figure 1-4. I/O Instruction Formats

program codes and the resulting functions. Note that six basic instructions are formed by the ABF bits with IR05 modifying one basic instruction to derive two instructions.

The ABF bits are from the CPU microprocessor and the IR and OVRRD bits from the Instruction Register which also provides the channel address bits (CHAN4-0) and unit address bits (UNIT3-0). The channel address is a requirement for all I/O instructions and the unit address is required only if the transfer is to/from a unit on the channel's interface or to a circuit within the channel, such as a parameter storage area, reserved for unit requirements.

## 1-5.1.1 Output Command Word (OCW)

The OCW instruction is used to transfer an 8- or 24-bit command word from the CPU A register to a unit on the channel's interface. The OCW instruction is also used to place a channel in either the off line or multiplex mode, to return to normal command constraints from an off line or multiplex mode (via a reset command), to override a current busy condition and return the channel to program control via an override command, or to initialize a channel for memory transfer operations.

When placed in the off line mode, the channel is set busy to the CPU and a "daisy chain" channel in a second CPU communicates with a unit on the interface. The multiplex mode allows a "master" on the channel's interface to communicate with a "slave" via the channel's input and output drivers and to use its handshake lines to facilitate transfers. The channel is set busy and will not respond to most programmed instructions. The reset mode is used to overcome the busy condition set by off line or multiplex mode commands and thereby return the channel to normal OCW mode constraints.

The override mode may be used to override the "output busy" state of a channel in order to return the channel to new command constraints. This type of command is normally used to overcome channel-unit hangups; the channel may be placed in any mode via an override command.

Two I/O channels, UBC and IBC types, are initialized for memory transfer operations via OCW commands if the command word has its bit 23 set. The initialize sequence in these cases results in the channel accessing transfer parameters from memory under self control and then proceeding with the transfer operations. The XBC channel, also capable of memory transfer operations, performs no parameter access operations, and the PIOC is not designed for memory transfer operations.

## 1-5.1.2 Output Data Word (ODW)

The ODW instruction is used to transfer an 8- or 24-bit data word from the CPU A register to an addressed unit via an I/O channel. The channel sets itself busy during the transfer and remains busy until it has performed a handshake sequence with the unit to verify completion of the transfer.

## 1-5.1.3 Output Address Word (OAW)

The OAW instruction is used by UBC and IBC channels to transfer a starting address of memory transfer control parameters. The channel uses the word from the CPU A register as a memory address during a subsequent initialize sequence (see OCW, above). The channel stores the address word and does not transfer it to a unit. In XBC channel operations the channel transfers the word to an addressed unit. In this case the word consists of a transfer address for storage location of subsequent memory transfer data words. The unit modifies the address word, as necessary, during subsequent transfer operations.

The PIOC executes the OAW instruction to raise interrupts to another CPU or CPUs. This is generally done to access a daisy chain interface. If a UBC channel is a part of the system and the channel is configured for link operations, the PIOC may be used for interrupt purposes to signal entry into these operations.

### 1-5.1.4 Input Data Word (IDW)

The IDW instruction is used to transfer an 8- or 24-bit data word from a unit to the CPU A register.

## 1-5.1.5 Input Status Word (ISW)

The ISW instruction is used to transfer 6 or 8 bits of status from a unit to the CPU A register. An I/O channel appends up to 3 bits to the word as follows:

| Input Bit | Status         | Application    |

|-----------|----------------|----------------|

| 23        | channel busy   | UBC only       |

| 22        | off line mode  | PIOC, UBC, XBC |

| 21        | multiplex mode | PIOC, UBC      |

## 1-5.1.6 Input Address Word (IAW)

The IAW instruction is used to transfer the current contents of the channel's transfer address register (TAR) to the CPU A register. The IAW instruction provides an indication of progress in memory transfer operations.

## 1-5.1.7 Input Parameter Word (IPW)

The IPW instruction is used to transfer the current contents of the channel's parameter address register (PAR) to the CPU A register. The IPW instruction provides an indication of progress in "chaining" transfers in which a channel is automatically restarted to perform multiple block transfers under self control.

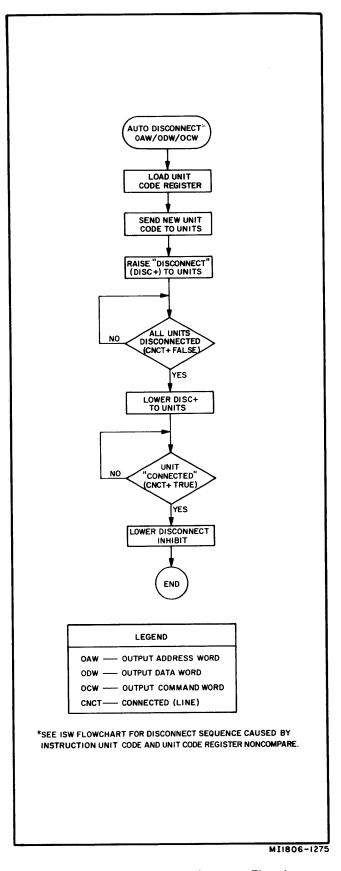

#### 1-5.2 Disconnect Control

The PIOC, UBC, and XBC channels contain logic circuits to ensure that the unit addressed in an I/O instruction is "connected" to the channel's I/O interface before a transfer is made. A unit code register (UCR) a comparator, and a disconnect sequence circuit provide this function. Instructions which contain the unit address and thereby may result in a disconnect sequence are as follows:

| OCW | PIOC, UBC, XBC |

|-----|----------------|

| ODW | PIOC, UBC, XBC |

| OAW | XBC            |

| IDW | PIOC, UBC      |

| ISW | PIOC, UBC, XBC |

|     |                |

If the channel is capable of executing the instruction but the unit address differs from that stored in the UCR, a disconnect sequence is performed. The channel raises the "Disconnect" (DISC+) line and the currently-connected unit responds by dropping the "Connect" (CNCT+) line. (A unit cannot hold the CNCT+ line true while DISC+ is true.) The channel then clocks the current unit address into its UCR and lowers DISC+. The unit address is sensed by the proper unit and it responds by raising CNCT+.

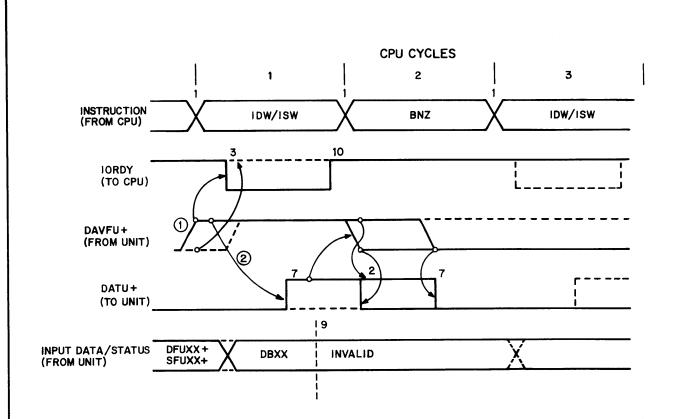

If the transfer direction is output, the channel will have loaded the output word and will immediately perform a handshake with the unit for transfer purposes upon completion of the disconnect sequence. If an input transfer, the channel cannot perform the disconnect sequence within the current instruction cycle. The instruction must then be repeated for a successful execution. A programmed delay such as a Branch on Not Zero (BNZ) may be employed to provide repetition of the instruction.

The XBC channel automatically performs a disconnect sequence for all output instructions and the PIOC and UBC do likewise for override commands. In all other instructions, a noncomparison of the unit code in the instruction word and the UCR contents is the initial condition. Because of timing differences in disconnect sequences, the applicable sequences are illustrated in sections devoted to the channels.

#### 1-5.3 Channel Busy Control

With few exceptions, a channel sets itself busy during an instruction sequence and will not respond to a new instruction until the sequence is completed. Channels capable of being set to the off line or multiplex modes are set busy and will respond only to ISW instructions and OCW instructions with commanded override or reset specifications. While a channel is busy performing an OCW sequence, the ODW, ISW, and IDW instructions cannot be executed. This sequence also inhibits execution of OAW, IAW, and IPW sequences in IBC channels. PIOC and UBC channels execute the OAW instruction unconditionally and the UBC channel executes IAW and IPW instructions unconditionally.

A channel verifies its ability to execute most instructions in its repertoire. Verification consists of setting the "Ready" line (IORDY) to the CPU to set the condition (C) register's "Condition Zero" (CZERO) signal true. This the CPU interprets as a successful execution and the program counter is advanced to the next instruction. This occurs whether or not the program delay feature is implemented.

The IBC and XBC channels set themselves busy during memory transfer sequences, but the condition exists only for the duration of the current transfer. A channel on the UBC card, on the other hand, is set busy during the initialize sequence of memory transfer operations and remain busy until the operation is terminated.

#### 1-5.4 Synchronization

All I/O channels are synchronized to the CPU via clock inputs from the master timing circuits of the CPU. The IBC and UBC channels contain internal clocks for use in channel sequences, but all main events are synchronous with CPU timing.

Units operating on an I/O channel's interface operate asynchronously. The units are synchronized to channel timing via "handshake" conventions as described below.

## 1-5.4.1 PIOC and UBC Channel - Unit Synchronization

The PIOC and UBC channels raise their "Command Data Here" (CDH) lines when the channels are holding a command for an addressed unit. The unit responds by raising its "Output Data Accepted" (ODACP) line and the channels lower the CDH line. The unit must then respond by lowering the ODACP line. If an ODW execution causes the channels to raise their "Output Data Here" (ODH) lines, the unit responds via the ODACP line. The channel then lowers ODH and the unit must lower its ODACP line. The UBC uses these same handshake lines for memory transfer data and command transfers.

For input purposes, the unit must have raised its "Data Available from Unit" (DAVFU) line prior to the IDW instruction for the channel to execute. If so, the channel loads the input data and raises its "Data Accepted to Unit" (DATU) line. The unit then lowers DAVFU and the channel lowers DATU. The UBC channel uses the same input handshake lines for input memory data transfer sequences.

The channels do not sequence channel-unit handshake sequences for ISW, OAW, IAW, or IPW instructions. (IAW and IPW instructions are not executed by PIOC channels.)

## 1-5.4.2 IBC Channel - Unit Synchronization

The IBC performs a modified handshake with a unit in either programmed or memory transfer sequences. In programmed transfer operations the channel pulses a control line and this action either loads the transfer word (OCW) or provides unit multiplexer actions as follows:

- A. CDH (Command Data Here) for OCW instructions.

- B. GSI (Gate Status In) for ISW instructions.

A unit on the channel's interface initiates memory transfer operations by raising its "Data Transfer Request" (DTR)

line. The channel, acting on previously stored transfer specifications, either requests a memory cycle for the transfer word (output) or loads the data from the unit and pulses its "Accepted Input" (ACPI) line (input). When the channel is performing output transfers and has accessed the word from memory, it places the data on line and pulses the ODH line. This causes the unit to load the data word and lower its DTR line. In input transfers the unit lowers the DTR line when the channel set ACPI true; the unit then enters a new sequence to provide the next data word and the channel requests a memory cycle to transfer the previously-loaded data word.

The OAW, IAW, and IPW instructions involve channel - CPU A register transfers and therefore require only the IORDY verification.

### 1-5.4.3 XBC Channel - Unit Synchronization

The XBC channel and units sequence handshakes during output programmed transfers. The channel raises the following handshake lines during the indicated instructions:

- A. CDH line (Command Data Here) for OCW

- B. AWH line (Address Word Here) for OAW

- C. WCH line (Word Count Here) for ODW

The unit responds by raising its "Accepted" (ACCPT) line and the channel lowers its handshake line. The unit then follows by lowering ACCPT.

In memory transfer operations the unit initiates the transfer sequence by raising its "Data Transfer Request" (DTR) line and the channel raises its SEND line when able to respond. The unit answers by raising its READY line, and lowering the DTR line. The transfer direction is determined by the unit's IN line. If true, the channel pulses an internal load line to store the data word and transfer address from the unit. The channel sets its memory request logic and lowers the SEND line. If false, the channel requests a memory cycle and, when granted, places the data on line to the unit and pulses its ODH line to automatically load the data in the unit. During the operation the channel lowers SEND and the unit lowers READY to complete the handshake.

The XBC channel performs no handshake for ISW instructions. The input is automatic if the channel is able to execute the instruction; status is always on line to the channel.

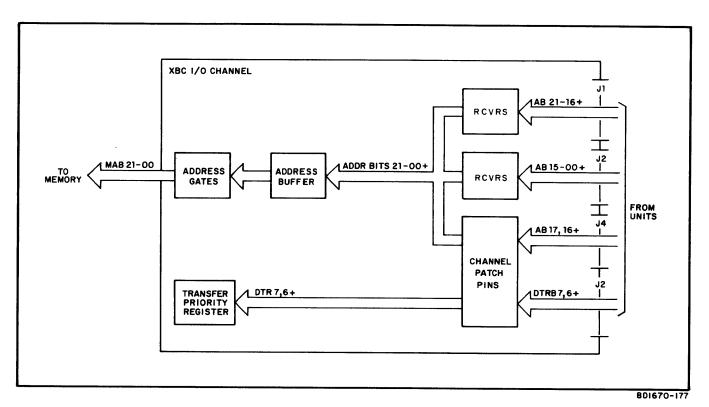

#### 1-5.5 Memory Transfer Priority Control

This convention is applicable to channels which are designed for memory transfer operations; IBC, UBC, and XBC channels. Each of the channels is equipped with

encoder/detector circuits that are activated when the channel requests a memory cycle for the purpose of accessing memory for read/write operations. The encoder sets a channel's priority on the bidirectional "block priority" bus consisting of 7 bits (BLKP6-0) and a channel detector senses the bus. When two or more channels make the memory request, the lines reflect the code of the highest priority current. All other channels are thereby inhibited from sensing the "request granted" (REQOK) by their respective detector circuits. Only the channel whose priority code agrees with the encoded lines can detect REQOK and thereby perform a memory transfer sequence. This removes the current code from the lines and the next highest priority requesting channel's request is set on the lines during subsequent requests.

The memory transfer priority structure consists of 32 levels with priority (P) level 1 having the highest priority and P32 the lowest. In general practice, those channels serving higher speed devices such as discs, mag tapes, etc. are assigned lower P levels, i.e., higher prioritites, than channels serving devices such as teletypes, etc. The selection of priority levels is either by switch modules (IBC and XBC channels) or by patch pins (UBC channels).

### 1-5.6 Error Actions and Sequences

All I/O channels sense one line signifying detected error conditions and IBC and XBC channels sense two discrete lines for this purpose. The first, the HOLDB, line is set true by the CPU when it has been notified by memory that the current word being fetched has failed parity. An I/O channel may be in the process of executing the CPU-channel transfer portion of an instruction and the transfer word currently in the processoof transfer from/to the CPU A register is valid. However, the HOLDB line causes the channel to reset its instruction control logic, aborting transfer actions. This causes the IORDY line to return to a false state before it can set the C register condition. This then is translated by the CPU as a "non-execution" and the instruction is therefore repeated.

In addition, IBC and XBC channels contain a feature associated with the memory priority conventions. The channels automatically set an "Inhibit Request" (IHREQ) line if an output memory transfer word has caused memory to set the "Parity Error" (PE) line, i.e., the current transfer word fails parity. This causes the transfer channel to cease the current sequence and initiate a new memory request for a repeat of the error word. The IHREQ line disables memory request action by any other IBC or XBC channel. UBC channels are not currently configured to perform this function. If a UBC channel is requesting a memory cycle concurrent with an IBC or XBC "error" sequence, its memory is not inhibited and the "cycle granted" signal falls under memory priority conventions described above.

#### 1-5.7 Daisy Chain Capability

The PIOC channels are equipped with the capability to perform "daisy chain" operations and the UBC and XBC channels may be modified to perform daisy chain operations. When equipped to be daisy chained a channel either has a parallel interface to its units or its output cables are installed to a daisy chain channel in another computer system. Figure 1-5 illustrates daisy chain configurations.

In daisy chain configurations two or more CPUs share units via an I/O interface made common by daisy chain installations. Normally, each CPU is equipped with a PIOC for the purpose of generating Software interrupts structured to daisy chain operations. A CPU, wishing to communicate with a unit on the common interface, generates the necessary interrupt to cause the other CPU(s) to set their daisy chained channels off line. This then allows the primary channel to exercise the shared unit without interference.

Figure 1-5. Daisy Chain Channel Configurations

#### 1-5.8 Link Capability

The link capability allows DMA channels in two or more CPUs to perform memory-to-memory transfers between themselves under self control. This capability may be combined with the daisy chain convention above to join more than two channels for link purposes. The link capability is exercised only by UBC channels and is described in Section IV.

#### 1-6 TIMING

#### 1-6.1 CPU Clock Timing

The I/O channels are synchronized to CPU timing for events which are associated with transfer sequences. A channel may contain a clock circuit for internal sequences, but these sequences only occur between events set by CPU timing. Figure 1-6 illustrates the clock inputs available for I/O operations via the backplane. The clock signals are outputs of the CPU clock circuit and consist of ten symmetrical, overlapping clock pulses and one timing pulse that is true from the leading edge of the CO2 clock pulse until the trailing edge of the CO7 clock pulse (i.e., the leading edge of CO9). This timing strobe is designated LO207B and is used to enable the bidirectional CPU channel data bus for input transfer operations.

Two stop clock actions can occur to extend the basic clock cycle of CPU timing. Both actions occur due to the fact that the CPU and memory operate asynchronously and must be synchronized for any transfers to/from memory.

#### 1-6.2 Instruction Timing

The computer is structured to perform each type of programmed I/O transfer, input or output, in identical fashion. The I/O channels implement this convention by performing transfer sequences alike. Figure 1-7 illustrates major events involved in the CPU — channel sequences of performing programmed transfer operations. The figure may be used as an inclusive diagram for all programmed transfers between the CPU and channel. Any channel-unit transfers involved are asynchronous and therefore device dependent; however, a channel will respond to a unit handshake within one-half CPU cycle, maximum.

#### 1-6.3 Memory Transfer Cycle Timing

Major events occuring during memory transfer sequences are illustrated on Figure 1-8.

#### 1-7 INPUT/OUTPUT CHANNEL INTERFACES

#### 1-7.1 General Information

An I/O channel interfaces with the CPU via two card edge connectors, P1 and P2, each of which provides 100 pins for interface purposes. The interface is standard and available to all channels, but some of the I/O channels, because of limited capabilities, do not use all of the signals. Figure 1-3 illustrates an outline drawing of a typical I/O channel for

connector identification purposes. The J connectors each provide 80 pins for I/O interface purposes. No attempt is made to illustrate the 8-pin Berg connectors used basically for interrupt interface purposes. Refer to interface descriptions of each channel for applications. It should also be noted that the J1 connector is used only by XBC channels.

Three channel cards are capable of being placed in daisy chain systems; this type of utilization normally requires a parallel external I/O interface. For the PIOC cards the capability is automatically included by wiring the normal 8-bit interface of J3 outputs to the J2 pins. UBC channels, being 24-bit channels, require wiring to two parallel plugs, J2A and J3A and XBC channels which utilize all three edge connectors for I/O purposes therefore require a parallel interface for each, designated J1A, J2A, J3A.

#### 1-7.2 Computer - I/O Channel Interface

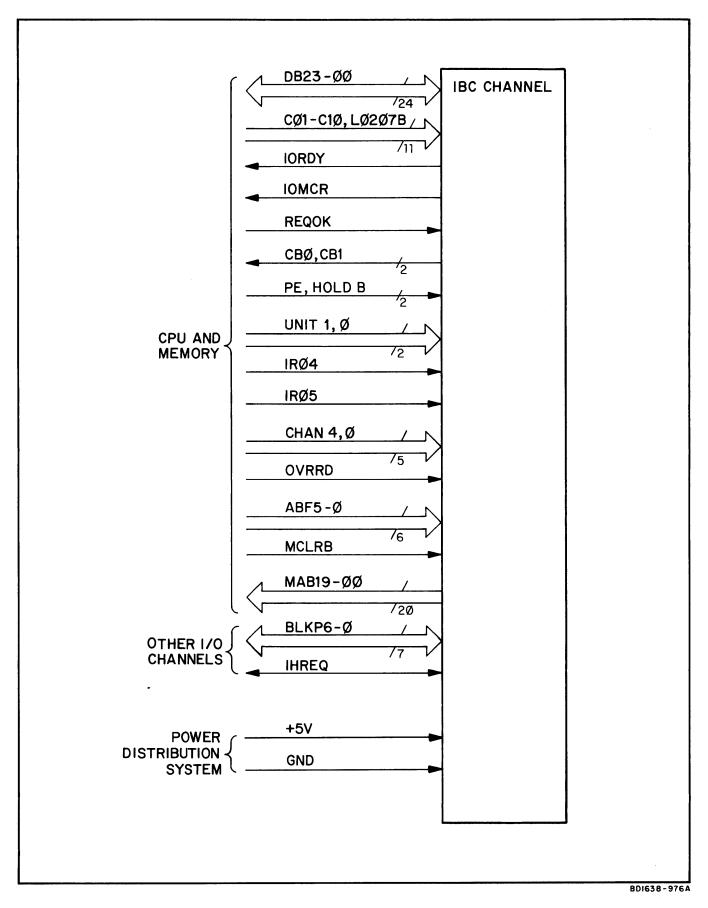

The computer interfaces with the I/O channels via the backplane and associated P1 and P2 edge connectors (Reference: Figure 1-9). Table 1-1 lists the signals on the backplane available for I/O operations. Note that the signals are functionally grouped and their functions are described in paragraphs below.

The entire CPU-I/O channel interface is buffered via Texas Instrument SN74S240 and SN74S241 line drivers. The drivers feature 3-state outputs and are arranged in an eight-per-chip configuration with four gates on each chip enabled by a discrete control input. The SN74S240 drivers present an inverted output; the SN74S241 drivers are noninverting. The latter type may have its input and output pairs tied together to form a bidirectional bus, as is the case for the data bus between the CPU and I/O channels. Characteristics of the drivers are as follows:

#### SN74S240

| Input                        | Output                 |

|------------------------------|------------------------|

| 0.0 — +0.8V (Logic 0)        | +2.0 - +5.0V (Logic 1) |

| +2.0 - +5.0V (Logic 1)       | 0.0 - +0.8V (Logic 0)  |

| +0.8 — +2.0V (indeterminate) | +2.0 - +0.8V           |

#### SN74S241

| Input                        | Output                 |

|------------------------------|------------------------|

| 0.0 - +0.8V (Logic 0)        | 0.0 - +0.8V (Logic 0)  |

| +2.0 - +5.0V (Logic 1)       | +2.0 - +5.0V (Logic 1) |

| +0.8 - +2.0V (indeterminate) | +0.8 — +2.0V           |

For circuit details of the SN74S240 and S241 drivers refer to the Linear and Interface Circuits Data Book, Texas Instruments Incorporated.

#### 1-7.2.1 DB47 - DB00 (Data Bus Data Bits)

These 48 data lines form the bidirectional data bus to carry

MI1974-477C

Figure 1-6. Computer Main Timing

Figure 1-7. I/O Instructions Timing Conventions

TD1830-977

Figure 1-8. Memory Transfer (Block Control) Timing Conventions

Figure 1-9. Standard Interfaces for I/O Usage

Table 1-1. CPU — Channel Interface\*

| Connector-Pin | Signal | Connector-Pin | Signal | Connector-Pin | Signal |

|---------------|--------|---------------|--------|---------------|--------|

| P1-76         | DB47   | P1-69         | DB20   | P1-87         | C07    |

| P1-75         | DB46   | P1-68         | DB19   | P1-88         | C08    |

| P1-74         | DB45   | P1-67         | DB18   | P1-89         | C09    |

| P1-73         | DB44   | P1-66         | DB17   | P1-90         | C10    |

| P1-64         | DB43   | P1-65         | DB16   | P1-92         | L0207B |

| P1-63         | DB42   | P1-54         | DB15   | P1-19         | IORDY  |

| P1-62         | DB41   | P1-53         | DB14   | P1-22         | IOMCR  |

| P1-61         | DB40   | P1-52         | DB13   | P1-60         | REQOK  |

| P1-58         | DB39   | P1-51         | DB12   | P2-70         | СВО    |

| P1-57         | DB38   | P1-50         | DB11   | P2-76         | CB1    |

| P1-56         | DB37   | P1-49         | DB10   | P2-73         | PE     |

| P1-55         | DB36   | P1-48         | DB09   | P1-14         | UNITO  |

| P1-46         | DB35   | P1-47         | DB08   | P1-15         | UNIT1  |

| P1-45         | DB34   | P1-36         | DB07   | P1-16         | UNIT2  |

| P1-44         | DB33   | P1-35         | DB06   | P1-17         | UNIT3  |

| P1-43         | DB32   | P1-34         | DB05   | P1-20         | IR04   |

| P1-40         | DB31   | P1-33         | DB04   | P1-21         | IR05   |

| P1-39         | DB30   | P1-32         | DB03   | P1-9          | CHAN0  |

| P1-38         | DB29   | P1-31         | DB02   | P1-10         | CHAN1  |

| P1-37         | DB28   | P1-30         | DB01   | P1-11         | CHAN2  |

| P1-28         | DB27   | P1-29         | DB00   | P1-12         | CHAN3  |

| P1-27         | DB26   | P1-81         | C01    | P1-13         | CHAN4  |

| P1-26         | DB25   | P1-82         | C02    | P1-18         | OVRRD  |

| P1-25         | DB24   | P1-83         | C03    | P2-11         | ABF0   |

| P1-72         | DB23   | P1-84         | C04    | P1-12         | ABF1   |

| P1-71         | DB22   | P1-85         | C05    | P2-13         | ABF2   |

| P1-70         | DB21   | P1-86         | C06    | P2-14         | ABF3   |

<sup>\*</sup> This list represents the total backplane interface available for I/O channel cards - individual channel interface is restricted to channel's capabilities.

Table 1-1. CPU - Channel Interface\* (Cont'd.)

| Connector-Pin | Signal | Connector-Pin | Signal   | Connector-Pin       | Signal  |

|---------------|--------|---------------|----------|---------------------|---------|

| P2-15         | ABF4   | P2-36         | MAB07    | P2-28               | IHREQ   |

| P2-16         | ABF5   | P2-35         | маво6    | P1-1,3<br>-97,-99   | +5      |

| P1-91         | MCLRB  | P2-34         | маво5    | P2-1,-3<br>-97,-99  |         |

| P1-24         | HOLDB  | P2-33         | МАВ04    | P1-5,-23            |         |

| P2-68         | MAB19  | P2-32         | мавоз    | -41,-59,-77,<br>-95 | GND     |

| P2-67         | мав18  | P2-31         | маво2    | P2-5,-23<br>-41,-59 |         |

| P2-66         | MAB17  | P2-30         | маво1    | -77,-95             |         |

| P2-65         | MAB16  | P2-29         | мавоо    | P1-4,-98<br>P2-4,98 | -12V    |

| P2-54         | MAB15  | P2-7          | BLKP0    | P1-2,-100           | +12V    |

| P2-53         | MAB14  | P2-8          | BLKP1    | P2-2,-100           |         |

| P2-52         | MAB13  | P2-9          | BLKP2    | P1-78               | UBCDMA  |

| P2-51         | MAB12  | P2-10         | BLKP3    |                     |         |

| P2-50         | MAB11  | P2-25         | BLKP4    |                     |         |

| P2-49         | MAB10  | P2-26         | BLKP5    |                     |         |

| P2-48         | маво9  | P2-27         | BLKP6    |                     |         |

| P2-47         | мавов  | P2-58         | BLKP7    |                     |         |

|               |        |               | <u> </u> |                     | <u></u> |

<sup>\*</sup> This list represents the total backplane interface available for I/O channel cards — individual channel interface is restricted to channel's capabilities.

data between memory and a UBC channel; the IBC and XBC channels utilize only DB23-00 (i.e., are not capable of 48-bit "double word" transfers). DB23-00 are used by all channels in programmed transfers to carry data, command, address and status information. The PIOC channels are restricted to a maximum of 8 bits on this interface except for ISW transfers; refer to Section II for PIOC usage.

#### 1-7.2.2 C01 - C10, L0207B (Timing Clocks)

The lines carry clock pulses from the CPU master clock and timing generator for I/O timing purposes. (Reference: Figure 1-6.)

#### 1-7.2.3 IORDY (Input/Output Ready)

This line is set to its true state by the channel it is able to execute a programmed transfer instruction. The signal is used to set the CZERO flip-flop in the CPU C register during the current instruction, thereby advancing the CPU P register.

#### 1-7.2.4 IOMCR (Input/Output Memory Cycle Request)

This line is set true by the channel to request a memory cycle for the purpose of performing a memory transfer operation.

#### 1-7.2.5 REQOK (Request Okayed)

This line is set true by the CPU in response to a memory cycle request (IOMCR, above) if it is not in an error cycle or power fail safe sequence.

#### 1-7.2.6 CB0

This line is set by the channel in conjunction with the memory address bits (MAB19-00) to either write data into or read data from memory. CB0 true = write; CB0 false = read.

#### 1-7.2.7 CB1

This line is set by a UBC channel in conjunction with CB0 to cause memory to write either 24 bits or a 48-bit double word into memory. CB1 true = 24-bit memory write; CB1 false = 48-bit memory write.

#### 1-7.2.8 PE (Parity Error)

This signal is set true by memory if it has detected an error in the current output transfer. Refer to HOLDB and IHREQ, below for channel impact of PE.

#### 1-7.2.9 UNIT3 - UNIT0 (Unit Code Bits)

These bits are set into programmed transfer instruction to designate a unit on the interface. The channel stores the unit code in its unit code register and, if necessary, performs a disconnect sequence to connect the addressed unit to its I/O interface. The bits allow the CPU to address any one of up to sixteen unit controllers on a channel's I/O interface.

#### 1-7.2.10 IR04 and IR05 (Instruction Register Bits)

These bits are used in conjunction with certain instructions to set the I/O channel in one of four modes if the channel is designed to respond to the mode control bits or to modify

input address sources Reference: Paragraph 1-5.1 for applications.

#### 1-7.2.11 CHAN4 - CHAN0 (Channel Code Bits)

These code bits are set into programmed transfer instruction to designate one of 32-possible I/O channels for the operation. Only the channel whose address matrix coincides with the channel address will respond to the instruction.

#### 1-7.2.12 OVRRD (Override Bit)

This bit is set true by the CPU in OCW instructions to assume immediate control over the addressed channel, placing the channel under current program control. The channel responds to the override command even if currently busy.

#### 1-7.2.13 ABF5 - ABF0 (Absolute Function Bits)

These bits are set by the CPU to designate the current instruction. For I/O purposes the most-significant octal byte (ABF3, 4, and 5) is set false, with the type of instruction set by the least-significant byte (AFB0, 1, 2). Reference Figure 1-4. for the I/O instruction and absolute function bit codes.

#### 1-7.2.14 MCLRB (Master Clear)

This line is set true by the CPU under the following conditions:

- A. the MASTER CLEAR switch on the computer console is activated,

- B. system power up or down (manual or power failure)

The MCLRB line clears the entire I/O channel/unit controller interface.

#### 1-7.2.15 HOLDB (Hold)

This signal is an extension of the PE signal and is set true by the CPU if its current fetch operation is an error word. The signal causes an I/O channel to immediately abort a CPU A register — channel transfer by resetting the IORDY line.

#### 1-7.2.16 MAB19 - MAB00 (Memory Address Bits)

The memory address lines carry the address of the word currently being transferred between the channel and memory. The address bits are used only in memory transfer operations and interface with memory via the I/O channel.

#### 1-7.2.17 BLKP7 - BLKP0 (Block Priority Levels)

These signals are set by a channel in memory request actions during memory transfer operations and are used to resolve contention for memory cycle requests. Each channel is manually set for a priority level and the highest priority channel currently requesting a memory cycle is activated for the transfer operation while all lower priority channels are inhibited.

#### 1-7.2.18 IHREQ (Inhibit Requests)

This signal is set true by a channel if the current output memory transfer has caused memory to set PE true. IHREQ prevents other block controller channels from requesting a memory cycle while renewing the request from the active channel

## 1-7.2.19 +5V, GND, - 12V, +12V (Power and Ground)

These lines are power and return interface with power supplies in the system rack. The I/O channels use only the +5V and GND busses, but self-contained controller assemblies may be furnished with -12V and +12V via the channel.

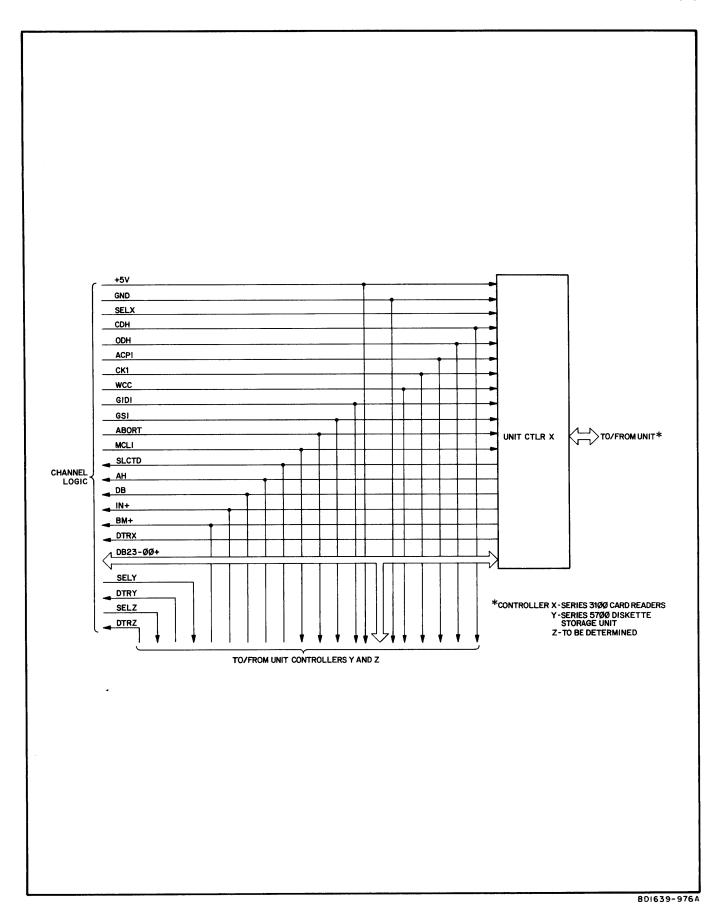

## 1-7.3 I/O Channel - External Unit Controller Interface

The I/O channels normally interface with any external unit controllers via the J2 and J3 connectors at the card edge. (Reference: Figures 1-3, 1-9) Table 1-2 lists the signals on the interfaces applicable to PIOC, IBC, and UBC channels; refer to Section V for the XBC interface. Note that the signals are functionally grouped and their functions are described below. Note also that the primary function of the J3 connectors in providing the necessary data/control/status interface for communications with a standard 8-bit device. The J2 connector expands the interface to allow for 24 bits (data) and 8 bits (status). The PIOC card contains the "daisy chain" capability and uses the J2 Connector in a parallel 8-bit interface for this purpose.

All signal transfers between the I/O channel and unit controller pass through line drivers and line receivers. A line driver is used for each signal going to the unit controllers. A line receiver is used for each signal coming from the unit controllers. The primary function of these circuits is to condition the input/output signals so that they reflect the proper impedance and ensure maximum signal transfer.

The output line drivers (Signetics 8T13 or TI SN75121N) in the I/O channel are used to drive output lines of up to 200 feet to the unit controllers. The unit controller should be equipped with line drivers for each input line returning to the I/O channel. The output characteristics of the line drivers are:

V out (Logic 1) = +2.4V min., +5.0V max.

Vout (Logic 0) = 0.0V min., +0.4V max.

I out (Logic 1) = 75 A., max.

I out (Logic 0) = 800 A., max.

The input line receiver (Signetics 8T14 or TI SN75122N) presents a high impedance load at the line driver circuit and allows the transmission line to be terminated in its characteristic impedance. The input characteristics of the line receiver are:

V in (Logic 1) = +2.6V min., +5.0V max.

V in (Logic 0) = 0.0V min., +0.4 max.

Refer to vendor manuals for other characteristics or schematics. The following paragraphs describe the functions of the I/O interface signals.

## 1-7.3.1 DFU23 - 00+ (Data From Unit Bits)

This bus represents the input data lines from the unit controllers. The bus may carry 8 or 24 bits, depending on channel/unit capabilities.

## 1-7.3.2 SFU07 - 00+ (Status From Unit Bits)

This bus represents the input status lines from the unit controllers. The bus may carry 6 or 8 bits, depending on channel/unit capabilities.

## 1-7.3.3 O-DTU23 - 00+ (Data To Unit Bits)

This bus represents the output command or data lines from the channel. The bus may carry 8 or 24 bits, depending on channel/unit capabilities.

#### 1-7.3.4 O-DISC+ (Disconnect)

This signal is set true by the channel when an I/O instruction specifies a unit different from the one currently connected. This signal goes to all units and causes, the connected unit to lower its CNCT+ signal. No unit can set the CNCT+ signal true while DISC+ is true.

### 1-7.3.5 CNCT+ (Connect)