# REFERENCE MANUAL HARRIS 800 GENERAL PURPOSE DIGITAL COMPUTER

Original Issue August, 1979

Copyright © 1978 by Harris Corporation, Computer Systems Division. All rights reserved. This publication or any part thereof is intended for use with Harris products by Harris personnel, customers, and end-users, and shall be used only for installation, operation, and maintenance of Harris products. It may not be reproduced in any form without the written permission of the publisher.

The information contained in this document is believed to be correct at the time of publication. It is subject to change without notice. Harris makes no warranties, express or implied, concerning the information contained in this document.

Printed in U.S.A.

# LIST OF EFFECTIVE PAGES

# TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS: 178 CONSISTING OF THE FOLLOWING:

| Page                                                                                                                                                                                                                   | Change                                                                                                                                                                                                                  | Page | Change | Page | Change |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|--------|

| No.                                                                                                                                                                                                                    | No.                                                                                                                                                                                                                     | No.  | No.    | No.  | No.    |

| Title A i thru vi 1-1 thru 1-13 1-14 Blank 2-1 thru 2-20 3-1 thru 3-5 3-6 Blank 4-1 thru 4-21 4-22 Blank 5-1 thru 5-8 6-1 thru 6-3 6-4 Blank 7-1 thru 7-17 7-18 Blank 7-19 thru 7-87 7-88 Blank A-1 thru A-7 A-8 Blank | Original |      |        |      |        |

Insert Latest Revision Pages. Destroy Superseded Pages.

# **CONTENTS**

| Section |                                                         | Page   |

|---------|---------------------------------------------------------|--------|

| 1       | INTRODUCTION                                            |        |

|         | SCOPE OF MANUAL                                         | . 1-1  |

|         | HARRIS 800 SYSTEMS                                      |        |

|         | BASIC COMPUTER ORGANIZATION                             | . 1-2  |

|         | Basic Operation                                         |        |

|         | Central Processing Unit (CPU)                           |        |

|         | Scientific Arithmetic Unit (SAU) Functions              |        |

|         | Memory Units                                            |        |

|         | Input/Output Operation                                  |        |

|         | Priority Interrupt System                               |        |

|         | MAINTENANCE AID PROCESSOR                               | . 1-5  |

|         | SWITCH PANEL                                            |        |

|         |                                                         |        |

|         | DATA TERMINALS                                          | . 1-6  |

|         |                                                         |        |

|         | Priority Interrupts                                     |        |

|         | 120 Hertz Clock                                         |        |

|         | Interval Timer                                          | . 1-7  |

|         | 100 kHz Real Time Clock                                 | . 1-7  |

|         | Power Fail Alarm                                        |        |

|         | Bootstraps                                              |        |

|         | Bit Processor                                           |        |

|         | Stall Alarm                                             |        |

|         | Address Trap                                            |        |

|         | Input/Output and Communications Processor Channels      |        |

|         | Programmed Input Output Channel (PIOC)                  |        |

|         | Buffered Block Channel (BBC)                            |        |

|         | Direct Memory Access Communications Processor (DMACP-8) |        |

|         | External Block Channel (XBC)                            |        |

|         | Integral Block Channel (IBC)                            |        |

|         | Input/Output Expansion Unit                             | . 1-9  |

|         | Interprocessor Communication Facility                   |        |

|         | Multi-Channel Adapter                                   | . 1-10 |

|         | PERIPHERAL EQUIPMENT                                    |        |

|         | SOFTWARE                                                | . 1-10 |

|         | Language Processors                                     |        |

|         | Utility Programs                                        | . 1-10 |

|         | Remote Job Entry Support Packages                       |        |

|         | Remote Batch Terminal Host Packages                     |        |

|         | Data Base Management System                             | . 1-10 |

|         | SUMMARY OF CHARACTERISTICS                              | . 1-11 |

|         | Memory System                                           | . 1-11 |

|         | Addressing                                              |        |

|         | Input/Output Capability                                 |        |

|         | Priority Interrupt Structure                            | . 1-13 |

|         | Power Fail Protection                                   | . 1-13 |

|         | Electrical Requirements                                 | . 1-13 |

|         | Environmental Requirements                              | . 1-13 |

|         |                                                         |        |

| Section |                                       | Page   |

|---------|---------------------------------------|--------|

| 11      | CENTRAL PROCESSING UNIT               |        |

| •       | GENERAL DESCRIPTION                   | . 2-1  |

|         | PRINCIPAL CPU REGISTERS               |        |

|         | A and B Registers                     |        |

|         | E Registers                           |        |

|         | D Registers                           |        |

|         | I, J, and K Registers                 |        |

|         | Condition Code Registers              |        |

|         | C Register                            |        |

|         | Y Register                            |        |

|         | Program Address Register              |        |

|         | Instruction Buffer                    |        |

|         | VIRTUAL MEMORY DESCRIPTION            |        |

|         | Introduction                          |        |

|         | Virtual Memory Instruction Set        |        |

|         | Principal Virtual Memory Registers    |        |

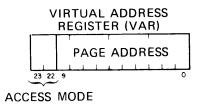

|         | Virtual Address Register (VARs)       |        |

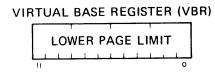

|         | Virtual Base Register (VBR)           |        |

|         |                                       |        |

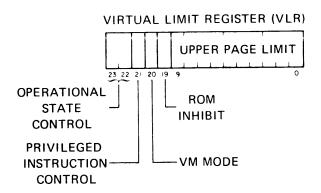

|         | Virtual Limit Register (VLR)          | . 2-4  |

|         | Virtual Usage Registers (VURs)        | . 2-4  |

|         | Virtual Not-Modified Registers (VNRs) | . 2-4  |

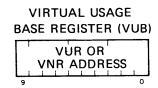

|         | Virtual Usage Base Register (VUB)     | . 2-4  |

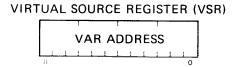

|         | Virtual Source Register (VSR)         |        |

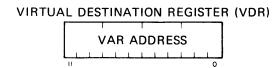

|         | Virtual Destination Register (VDR)    |        |

|         | Virtual Demand Page Register (VPR)    |        |

|         | Demand Paging                         |        |

|         | Instruction Trap                      |        |

|         | Paging System Control                 |        |

|         | CPU OPERATIONAL CONTROL               |        |

|         | CPU Modes of Operation                |        |

|         | Compatibility Mode                    |        |

|         | Address Extension Mode                | . 2-7  |

|         | CPU Operational States                |        |

|         | ADDRESSING FUNCTIONS                  |        |

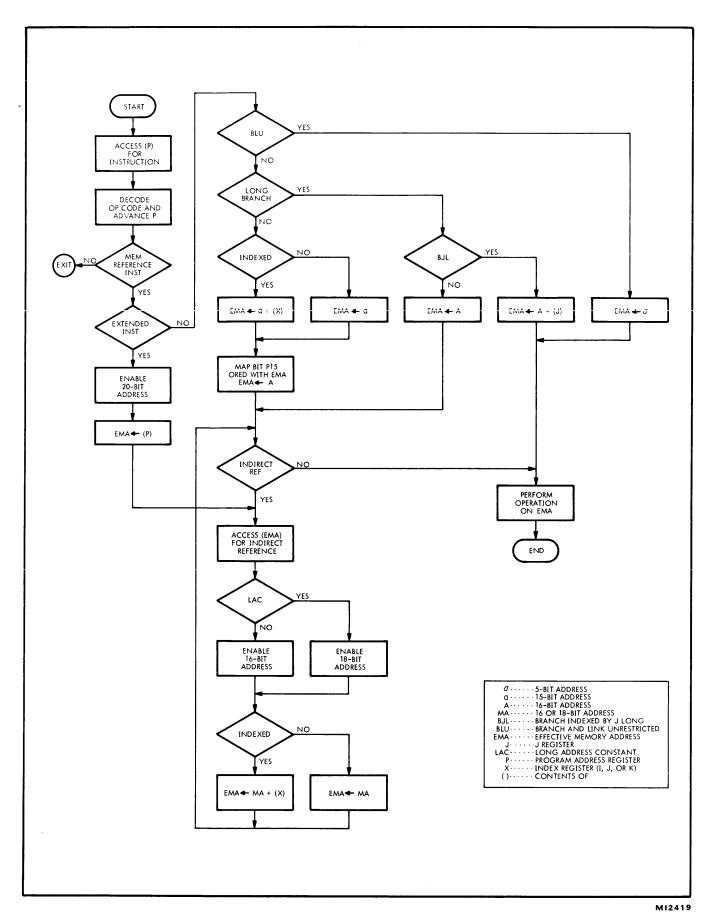

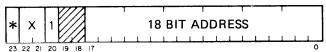

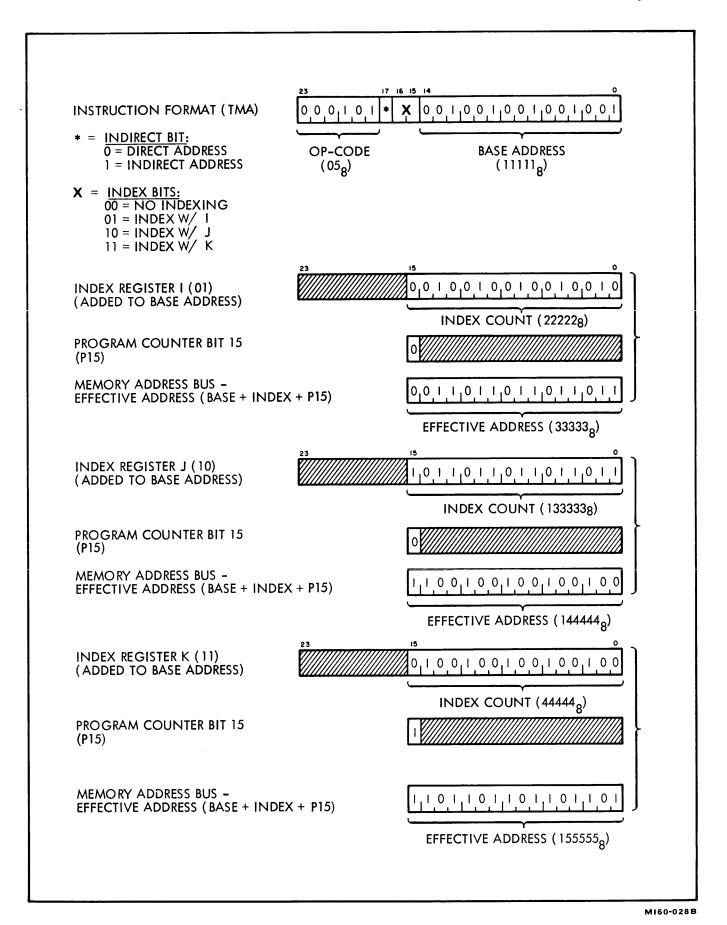

|         | Compatibility Mode Addressing         | . 2-8  |

|         | Direct Addressing                     |        |

|         | Indirect Addressing                   |        |

|         | Indexing                              |        |

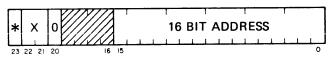

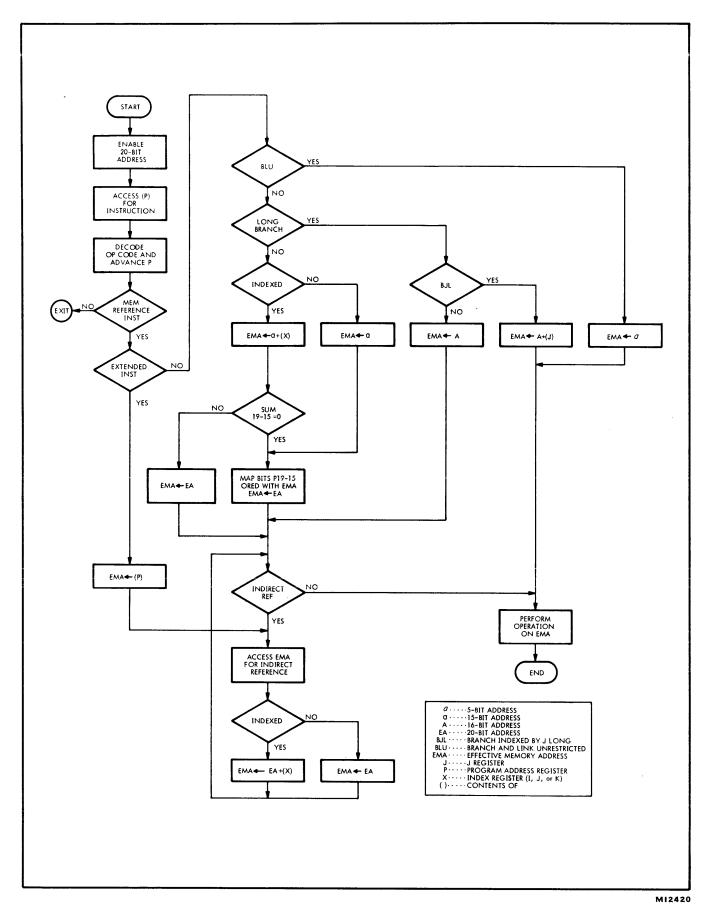

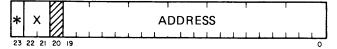

|         | Address Extension Mode Addressing     | . 2-10 |

|         | Direct Addressing                     |        |

|         | Indirect Addressing                   | . 2-13 |

|         | Indexing                              |        |

|         | Address Translation                   |        |

|         | 120 HERTZ CLOCK                       |        |

|         | INTERVAL TIMER                        |        |

|         | General Description                   |        |

|         | Timer Register                        | 2-16   |

| Section |                                 | Page            |

|---------|---------------------------------|-----------------|

| 11      | CENTRAL PROCESSING UNIT (CONT.) |                 |

|         | Operational Description         | . 2-16          |

|         | Program Control                 |                 |

|         | REAL TIME CLOCK                 | . 2-16          |

|         | General Description             |                 |

|         | Operational Description         |                 |

|         | Command and Status Word Formats |                 |

|         | Program Control                 |                 |

|         | Preset Count Loading            |                 |

|         | Automatic Count Restart         |                 |

|         | Snapshot Output                 |                 |

|         | Selection Sampling              |                 |

|         | FIRMWARE BOOTSTRAPS             |                 |

|         | BIT PROCESSOR                   |                 |

|         | General Description             |                 |

|         |                                 |                 |

|         | Bit Processor Registers         |                 |

|         | Operational Description         | . 2-18          |

|         | Program Control                 | . 2-18          |

|         | Bit Processor Instruction Set   | . 2-19          |

|         | STALL ALARM                     |                 |

|         | ADDRESS TRAP                    |                 |

|         | General Description             | . 2-20          |

|         | Query Register                  | . 2-20          |

|         | Operational Description         | . 2-20          |

|         | Program Control                 | . 2-20          |

| Ш       | MEMORY SYSTEM                   |                 |

|         | GENERAL DESCRIPTION             | 2.1             |

|         | MEMORY MODULES                  | . J-1<br>2.1    |

|         | 64K MOS Memory Module           | . 3-1           |

|         | 64K MOS Memory Module           | . 3-1           |

|         | Read and Write Operations       | . J·I           |

|         | Fast Access Operation           | . 3-2           |

|         | MAIN MEMORY                     | . 3-2           |

|         | EXTENDED MEMORY UNIT.           | . 3-2           |

|         | SHARED MEMORY UNIT              | . 3-2           |

|         | General Description             | . 3-2           |

|         | Programming Considerations      | . 3-2           |

|         | Semaphore Operation             | . 3-2           |

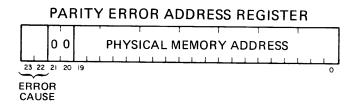

|         | ERROR CORRECTING AND REPORTING  | . 3-3           |

|         | Error Correction                | . 3-3           |

|         | Error Reporting                 | . 3-3           |

|         | Parity Errors and Interrupts    | 3-3             |

|         | Parity Error Address Register   | 3-3             |

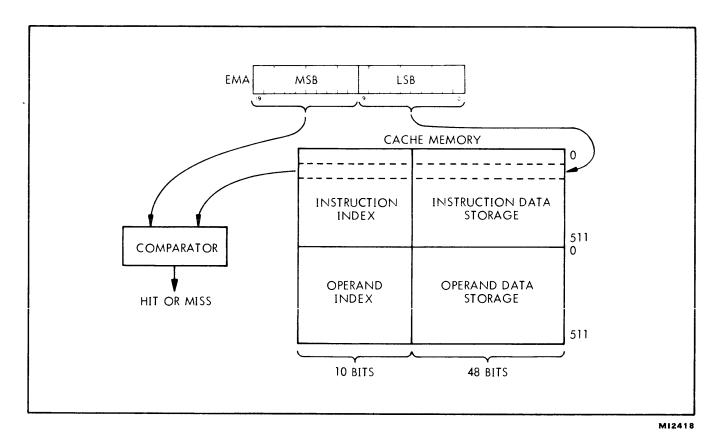

|         | CACHE MEMORY                    | 3-4             |

|         | Operational Description         | 3-4             |

|         | Algorithm for Filling Cache     | 3-4             |

|         | Programming Considerations      | 3-4             |

|         |                                 | J- <del>4</del> |

| Section |                                        | Page   |

|---------|----------------------------------------|--------|

| IV      | INPUT/OUTPUT CHANNELS                  |        |

|         | GENERAL DESCRIPTION                    | . 4-1  |

|         | BASIC I/O CONCEPTS                     |        |

|         | Addressing                             |        |

|         | Disconnect/Connect Sequences           |        |

|         | Block I/O Channel Priority             |        |

|         | Synchronization (Handshake) Conditions |        |

|         | Output Transfer Synchronization        | . 4-4  |

|         | Input Transfer Synchronization         | 4-4    |

|         | PIOC Synchronization                   | . 4-4  |

|         | XBC Synchronization                    | . 4-4  |

|         |                                        | . 4-5  |

|         |                                        | . 4-5  |

|         | BBC Synchronization                    | . 4-5  |

|         | Timing                                 |        |

|         | Block Transfer Memory Access           | . 4-5  |

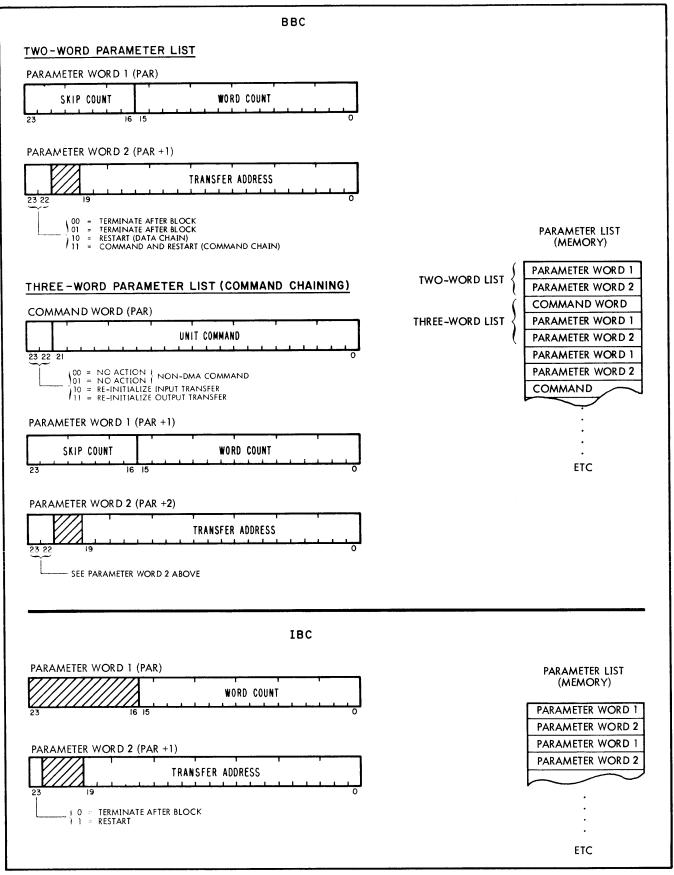

|         | Block Transfer Parameters              | . 4-5  |

|         | BBC Parameter Words                    | . 4-5  |

|         | XBC Parameter Words                    | . 4-7  |

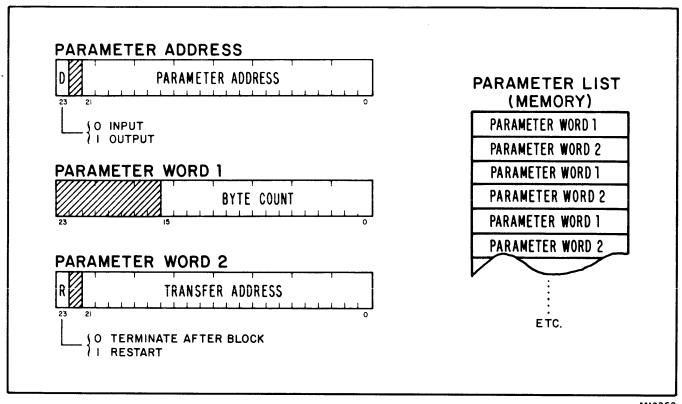

|         | IBC Parameter Words                    | . 4-7  |

|         | DMACP-8 Parameter Words                | . 4-7  |

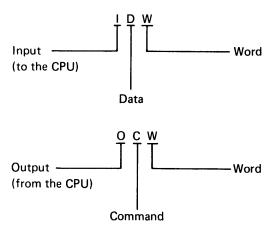

|         | INPUT/OUTPUT INSTRUCTIONS              | . 4-8  |

|         | I/O Commands                           | . 4-8  |

|         | I/O Status Word                        | . 4-9  |

|         | Programmed Data Transfers              | . 4-11 |

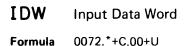

|         | Input Data Word                        | . 4-11 |

|         | Output Data Word                       | . 4-11 |

|         | Address Transfers                      | . 4-11 |

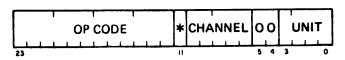

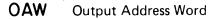

|         | Output Address Word                    | . 4-11 |

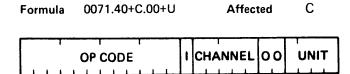

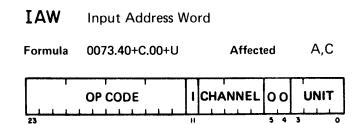

|         | Input Address Word                     | . 4-13 |

|         | Input Parameter Word                   | . 4-13 |

|         | INTERRUPT CONTROL                      |        |

|         |                                        | . 4-14 |

|         | I/O CHANNEL JUMPER CONTROLS            |        |

|         |                                        | 4-14   |

|         | Single-Word Instruction Execution      | 4-14   |

|         | OCW/ODW                                | 4-14   |

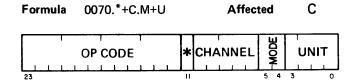

|         | IDW                                    |        |

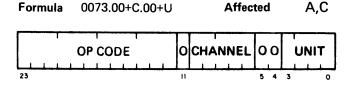

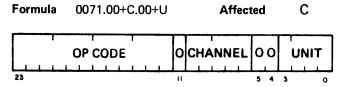

|         | ISW                                    | . 4-14 |

|         | OAW                                    | . 4-14 |

|         | IAW/IPW                                | . 4-15 |

|         | Block-Transfer Operations              | . 4-15 |

|         | BBC Block Transfers                    | . 4-15 |

|         | XBC Block Transfers                    | . 4-15 |

|         | IBC Block Transfers                    | . 4-20 |

|         | DMACP-8 Channel Block Transfers        | . 4-20 |

|         | Program Lists                          | . 4-20 |

|         | IBC Applications                       | . 4-20 |

|         | VPC Application                        | 4-21   |

| Section |                                                       |     |       |     | Page           |

|---------|-------------------------------------------------------|-----|-------|-----|----------------|

| V       | PRIORITY INTERRUPT SYSTEM                             |     |       |     |                |

|         | GENERAL DESCRIPTION                                   |     |       |     | . 5-1          |

|         | INTERRUPT ORGANIZATION                                |     |       |     |                |

|         | Priority Conventions                                  |     |       |     |                |

|         | Executive Traps (Group 0)                             |     |       |     |                |

|         | External Interrupts (Groups 1, 2, and 3)              |     |       |     |                |

|         | Dedicated Memory Locations                            |     |       |     |                |

|         | OPERATION AND CONTROL                                 |     |       |     | . D-I          |

|         |                                                       |     |       |     |                |

|         |                                                       |     |       |     |                |

|         | Executive Traps Control                               |     |       |     | . 5-3          |

|         | External Interrupts Control                           |     |       |     |                |

|         |                                                       |     |       |     | . 5-5          |

|         | Operational State Zero Interrupt Processing           |     |       |     | . 5-5          |

|         | Operational States One and Three Interrupt Processing |     |       | • • | . 5-6          |

| VI      | SCIENTIFIC ARITHMETIC UNIT OPERATION                  |     |       |     |                |

|         | GENERAL DESCRIPTION                                   |     |       |     | . 6-1          |

|         | FLOATING-POINT DATA FORMAT                            | • • | • • • |     | . 6-1          |

|         | SAU REGISTERS                                         |     |       |     |                |

|         | OPERATION AND CONTROL                                 |     |       | • • | . 6-1          |

|         | Data Transfers                                        |     |       | • • | . 6-1          |

|         | SAU Instructions                                      |     |       | • • | . 0-1          |

|         | SAU INTERRUPT                                         |     |       | • • | . 6-1          |

| V/II    |                                                       | • • |       | • • | . 6-1          |

| VII     | INSTRUCTION SET                                       |     |       |     |                |

|         | INTRODUCTION                                          |     |       |     | . 7-1          |

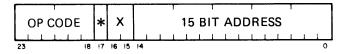

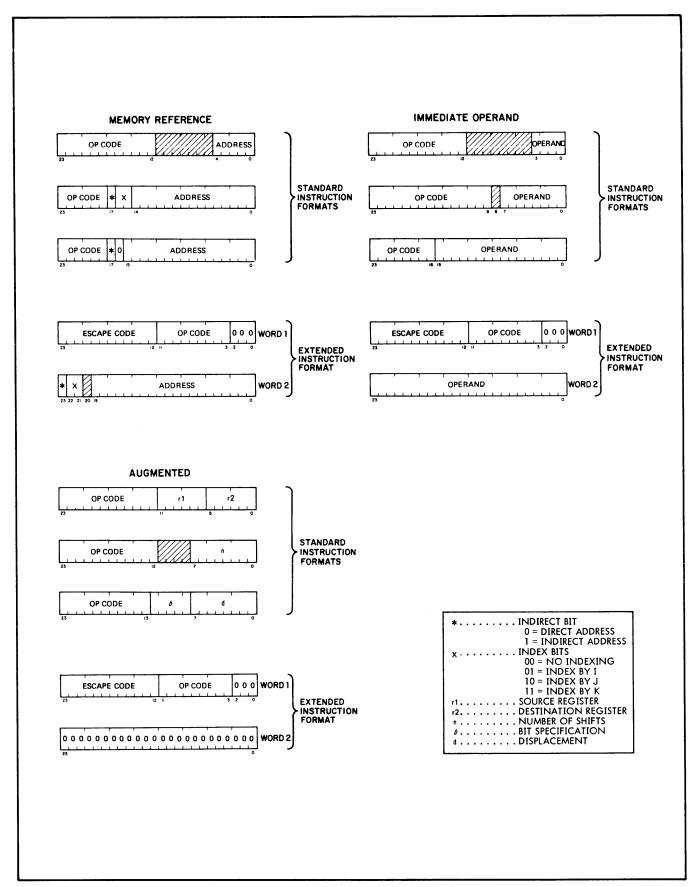

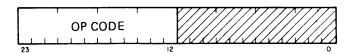

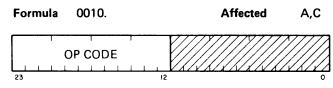

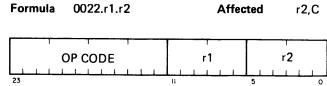

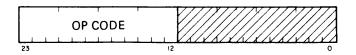

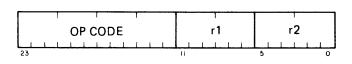

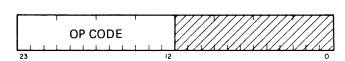

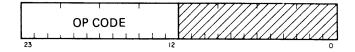

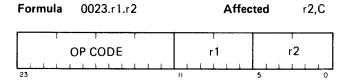

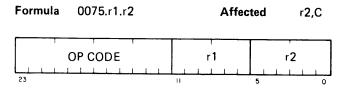

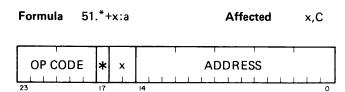

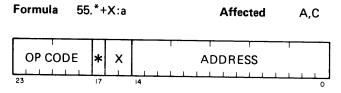

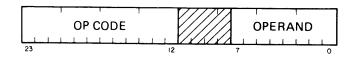

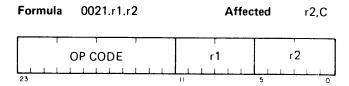

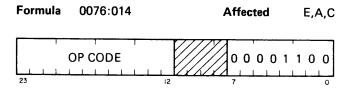

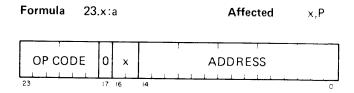

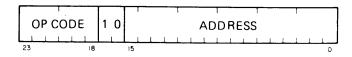

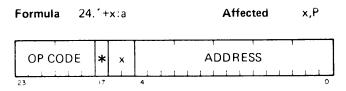

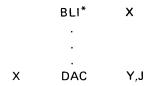

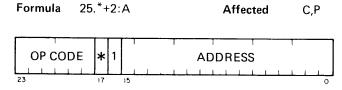

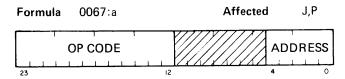

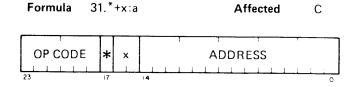

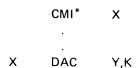

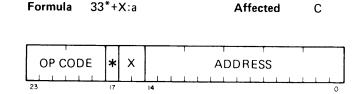

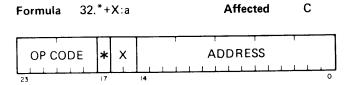

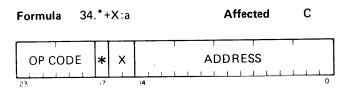

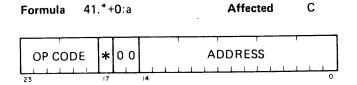

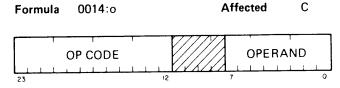

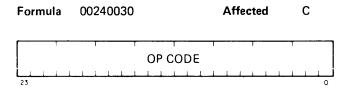

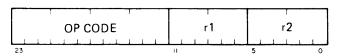

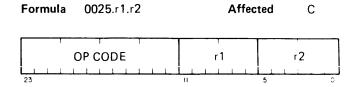

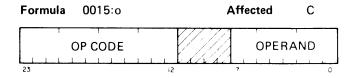

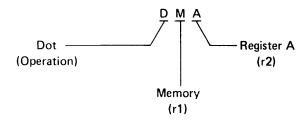

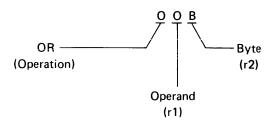

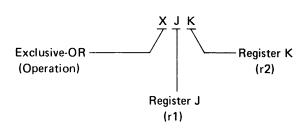

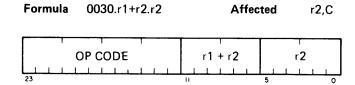

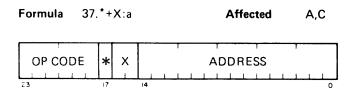

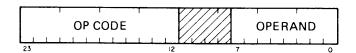

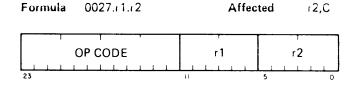

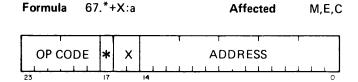

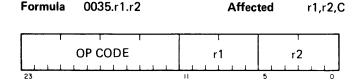

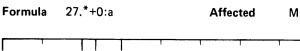

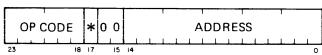

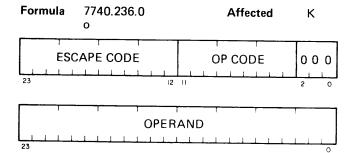

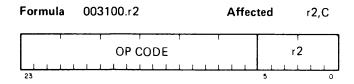

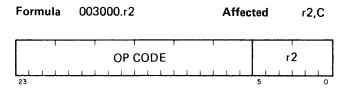

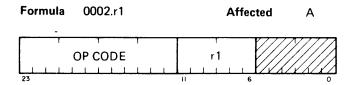

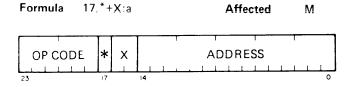

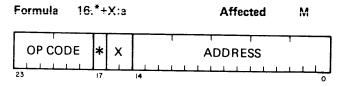

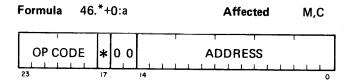

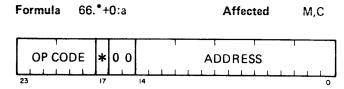

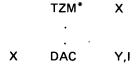

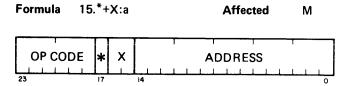

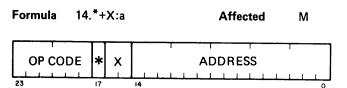

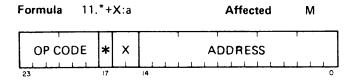

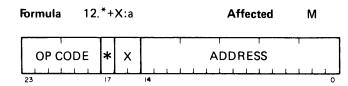

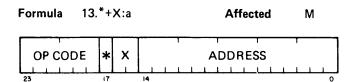

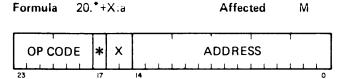

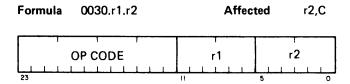

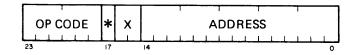

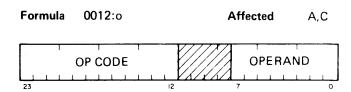

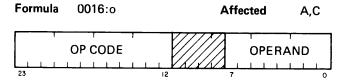

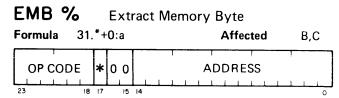

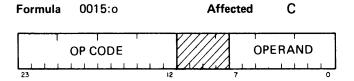

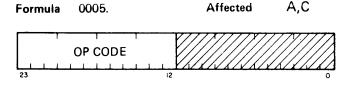

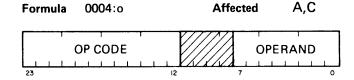

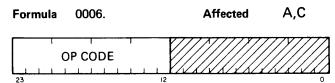

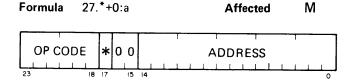

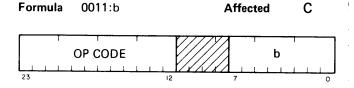

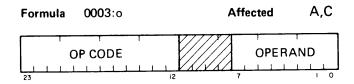

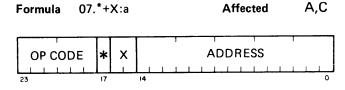

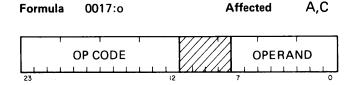

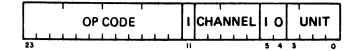

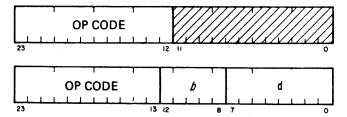

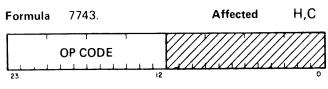

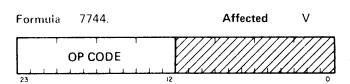

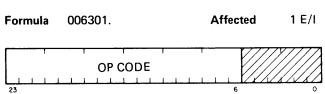

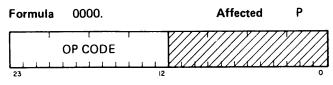

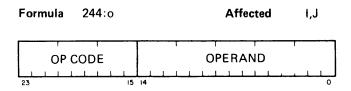

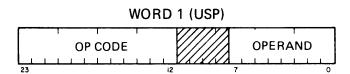

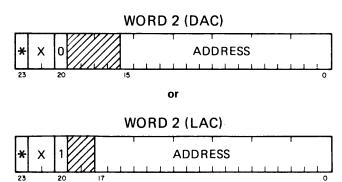

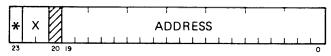

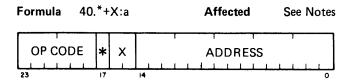

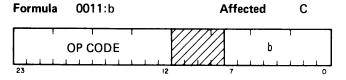

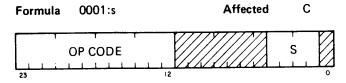

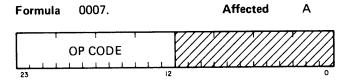

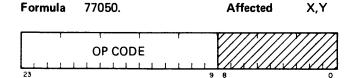

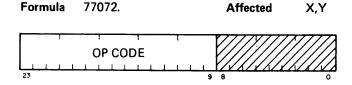

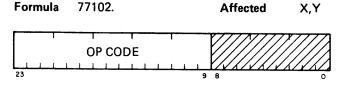

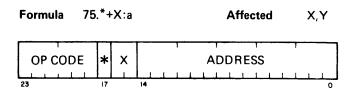

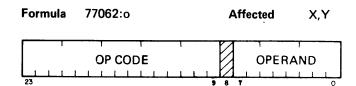

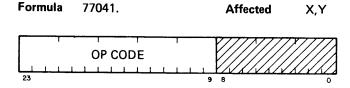

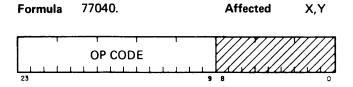

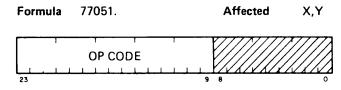

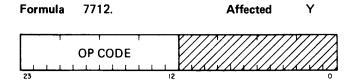

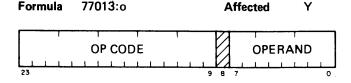

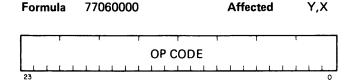

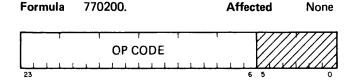

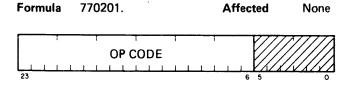

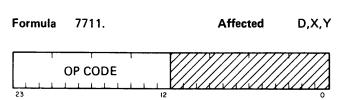

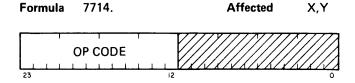

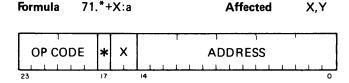

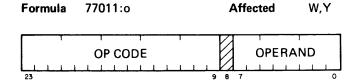

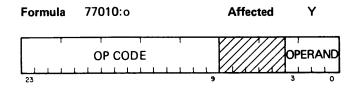

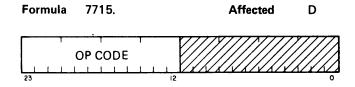

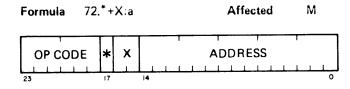

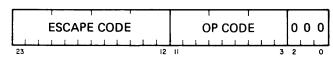

|         | INSTRUCTION TYPES AND FORMATS                         |     |       |     | . , .<br>. 7-1 |

|         | Introduction                                          |     |       |     |                |

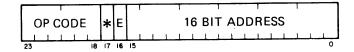

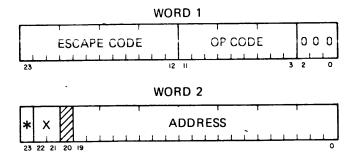

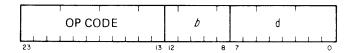

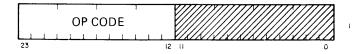

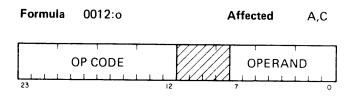

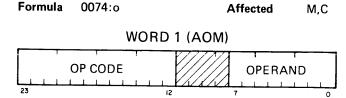

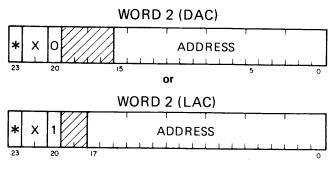

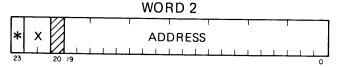

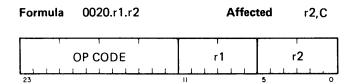

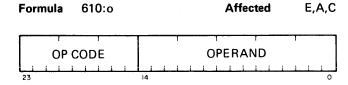

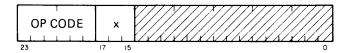

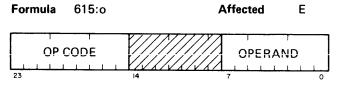

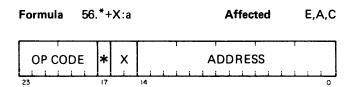

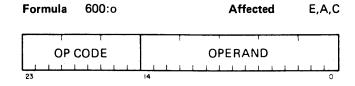

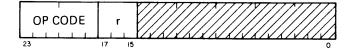

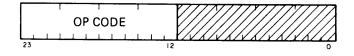

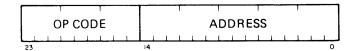

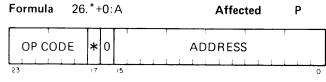

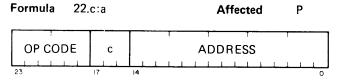

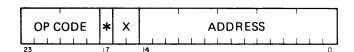

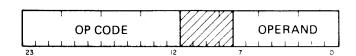

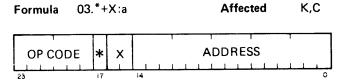

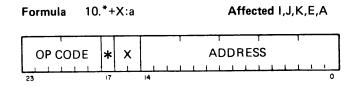

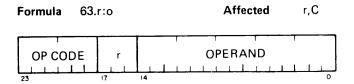

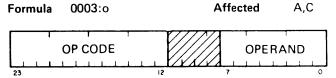

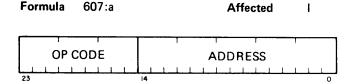

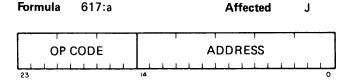

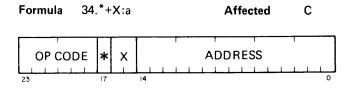

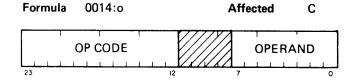

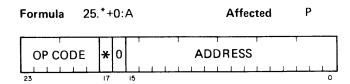

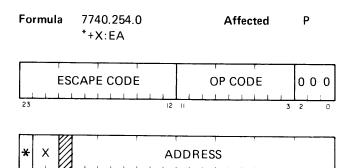

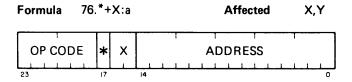

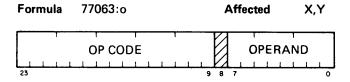

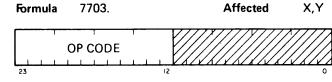

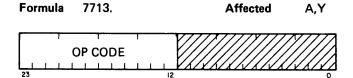

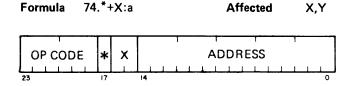

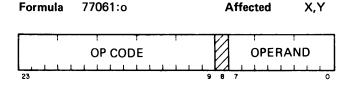

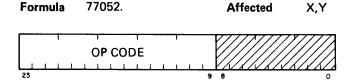

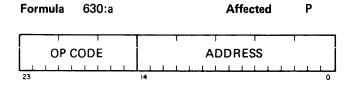

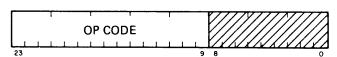

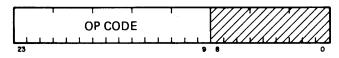

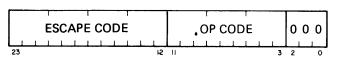

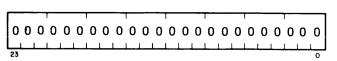

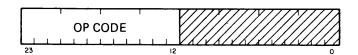

|         | Standard Instruction Format                           |     |       |     | . 7-1<br>. 7-1 |

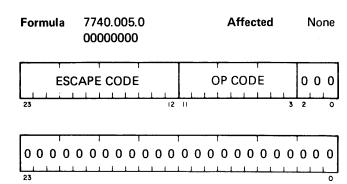

|         | Extended Instruction Format                           |     |       |     | . /-1<br>. 7-1 |

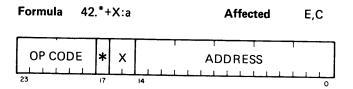

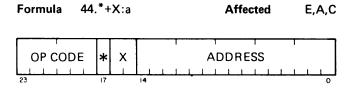

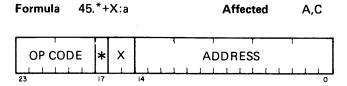

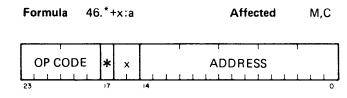

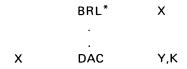

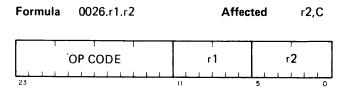

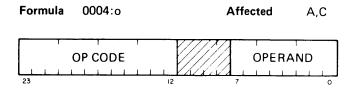

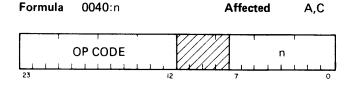

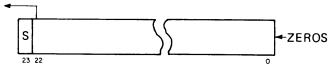

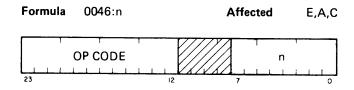

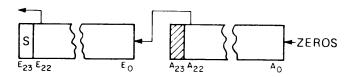

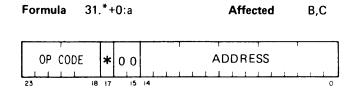

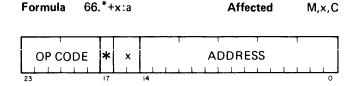

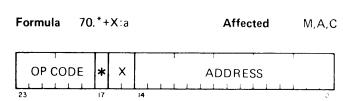

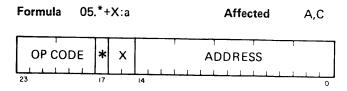

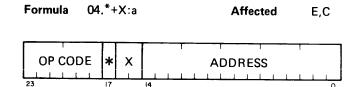

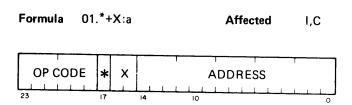

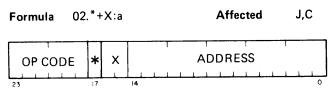

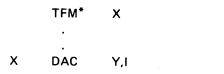

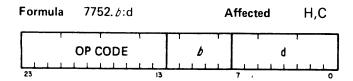

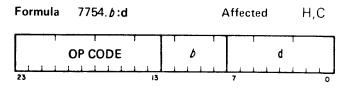

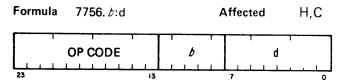

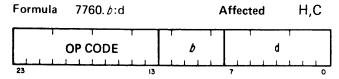

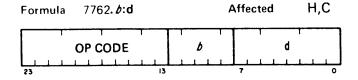

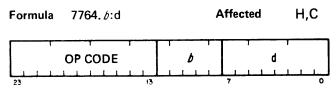

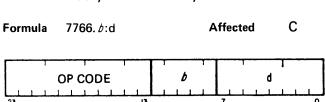

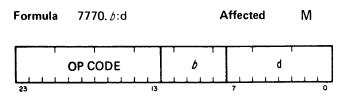

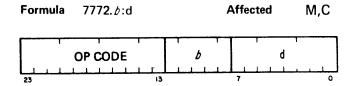

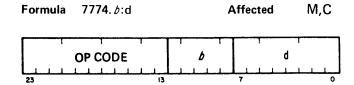

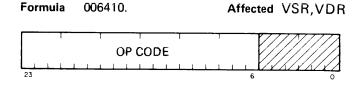

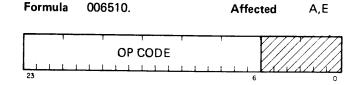

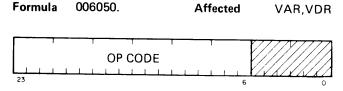

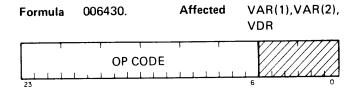

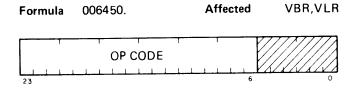

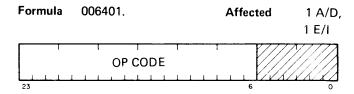

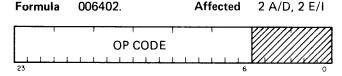

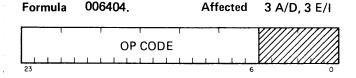

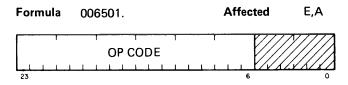

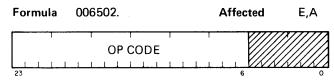

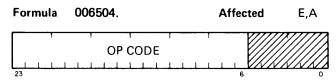

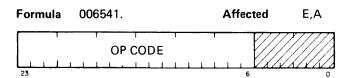

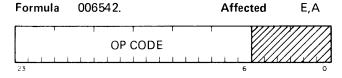

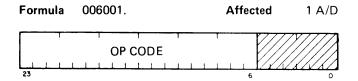

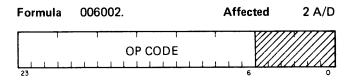

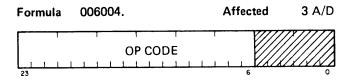

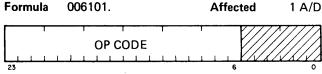

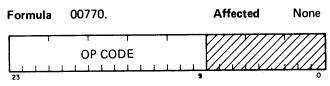

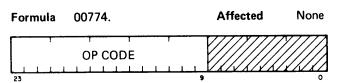

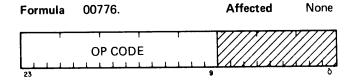

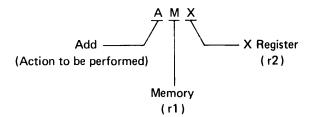

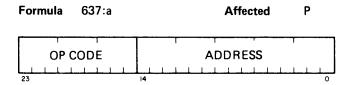

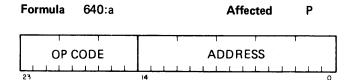

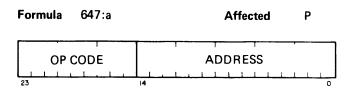

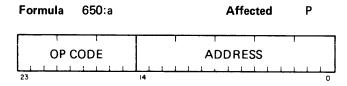

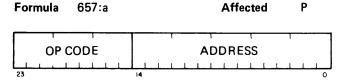

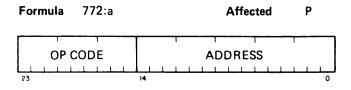

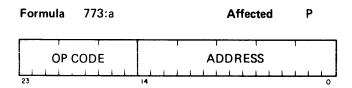

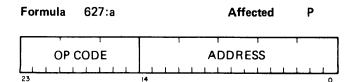

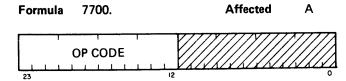

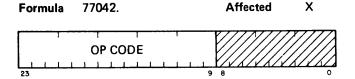

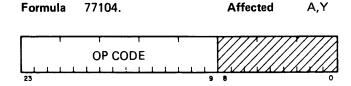

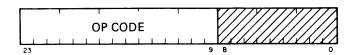

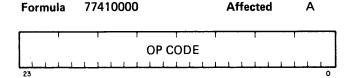

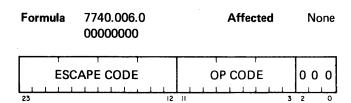

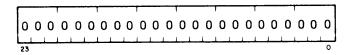

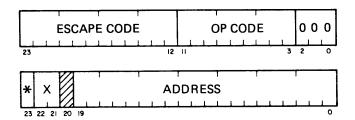

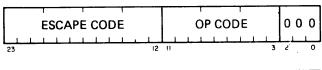

|         | INSTRUCTION FORMULA                                   |     |       |     | . 7-1          |

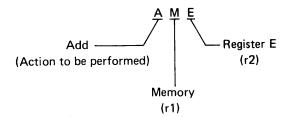

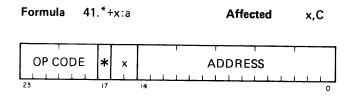

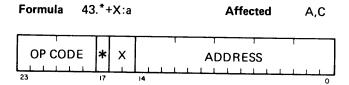

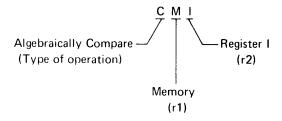

|         | INSTRUCTION DESCRIPTIONS                              | • • |       |     | . 7-3<br>. 7-4 |

|         |                                                       |     |       |     |                |

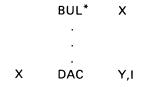

|         | Arithmetic Instructions                               |     |       |     | . 7-4          |

|         |                                                       |     |       |     | 7-16           |

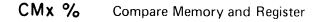

|         | Compare Instructions                                  |     |       |     | . 7-25         |

|         |                                                       |     |       |     | 7-28           |

|         |                                                       |     |       |     | 7-30           |

|         | Transfer Instructions                                 |     |       |     | 7-33           |

|         | Byte Processing Instructions                          |     |       |     | 7-43           |

|         | Input/Output Instructions                             |     |       |     | 7-49           |

|         | Bit Processor Instructions                            |     |       |     | 7-53           |

|         | Virtual Memory Instructions                           |     |       |     | 7-57           |

|         | Priority Interrupt Control Instructions               |     |       |     | 7-60           |

|         | Miscellaneous Instructions                            |     |       |     | 7-69           |

|         | Scientific Arithmetic Unit Instructions               |     |       |     | 7-72           |

|         | Decimal Arithmetic Instructions                       |     |       |     | 7-83           |

|         | Diagnostic Instructions                               |     |       |     |                |

| APPENDI | X A – INSTRUCTION INDEX                               |     |       |     | Α-1            |

# **ILLUSTRATIONS**

| igure                                                                                        |                                                                                                                                                                                                                                                                                                                   | Page                                                                                                          |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1-1.                                                                                         | Major Functional Units                                                                                                                                                                                                                                                                                            | . 1-3                                                                                                         |

| 2-1.<br>2-2.<br>2-3.<br>2-4.<br>2-5.<br>2-6.<br>3-1.<br>4-1.<br>4-2.<br>4-3.<br>4-4.<br>4-5. | Data Formats                                                                                                                                                                                                                                                                                                      | . 2-2<br>. 2-9<br>. 2-11<br>. 2-12<br>. 2-14<br>. 2-15<br>. 3-5<br>. 4-2<br>. 4-6<br>. 4-7<br>. 4-9<br>. 4-12 |

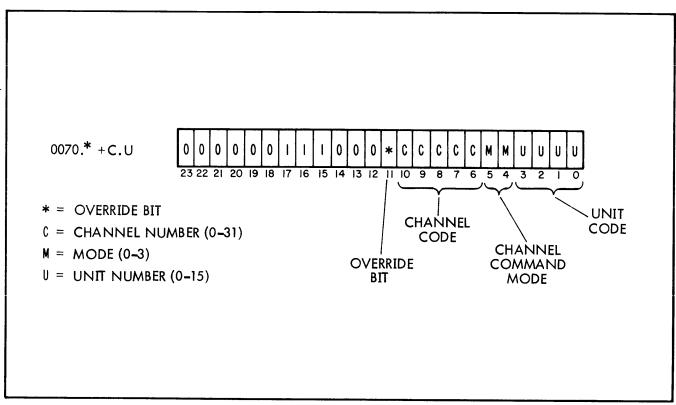

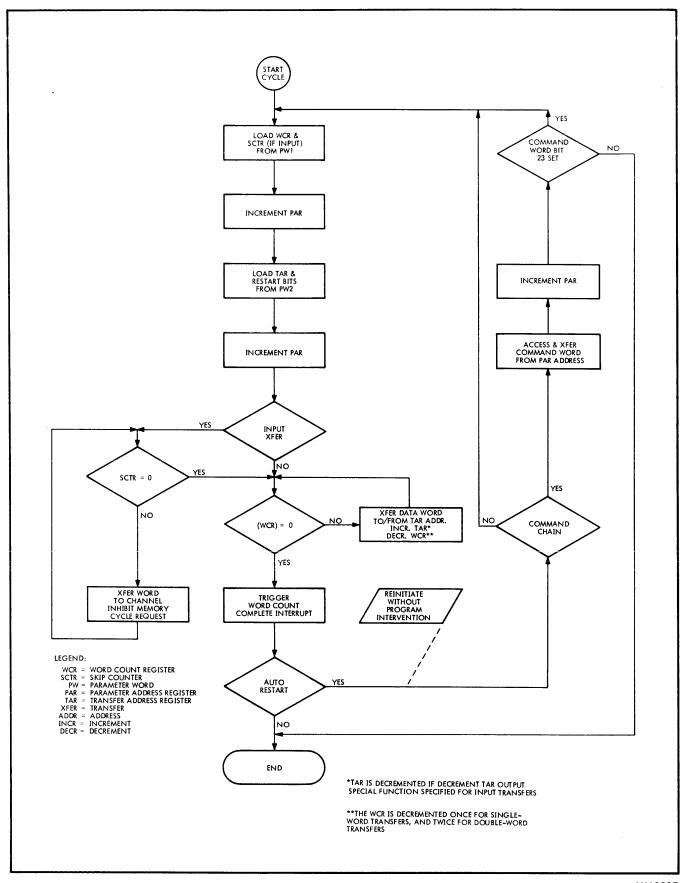

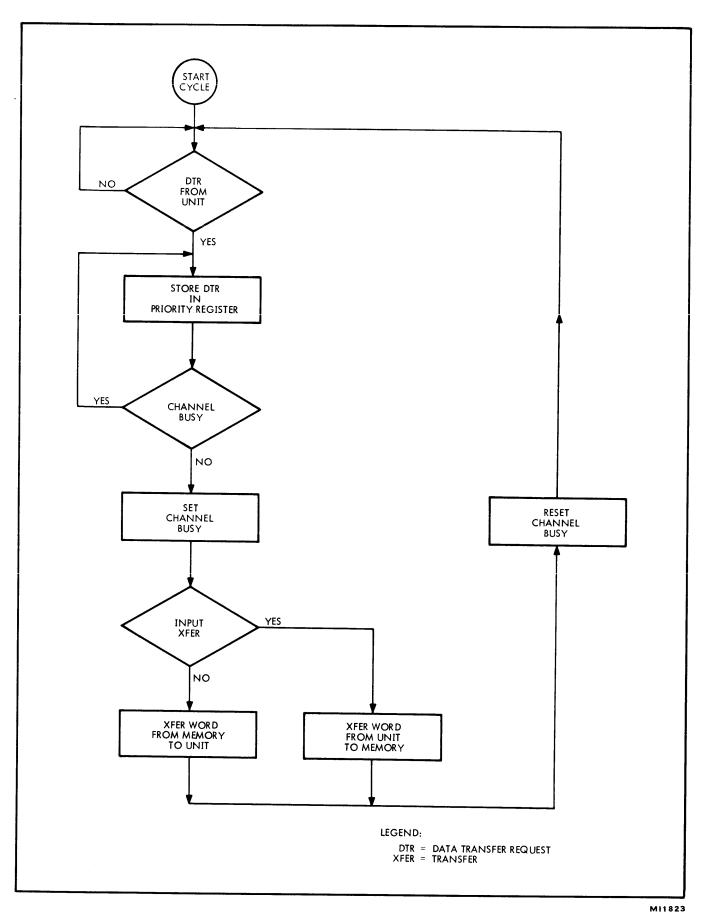

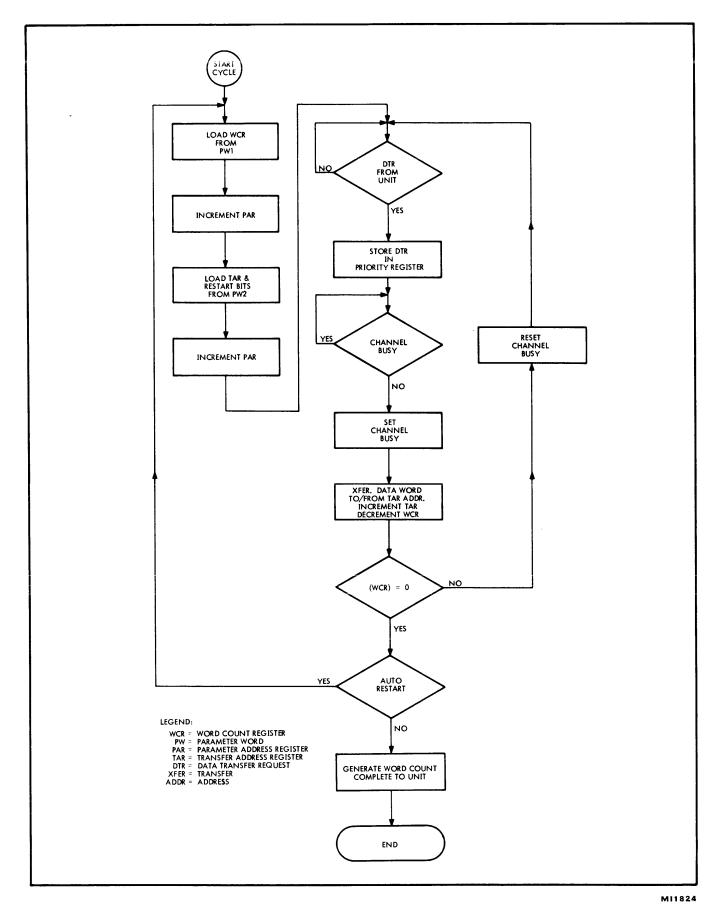

| 4-6.<br>4-7.<br>4-8.<br>4-9.                                                                 | BBC Block Transfer Sequence; Simplified Flow Diagram                                                                                                                                                                                                                                                              | . 4-17<br>. 4-18                                                                                              |

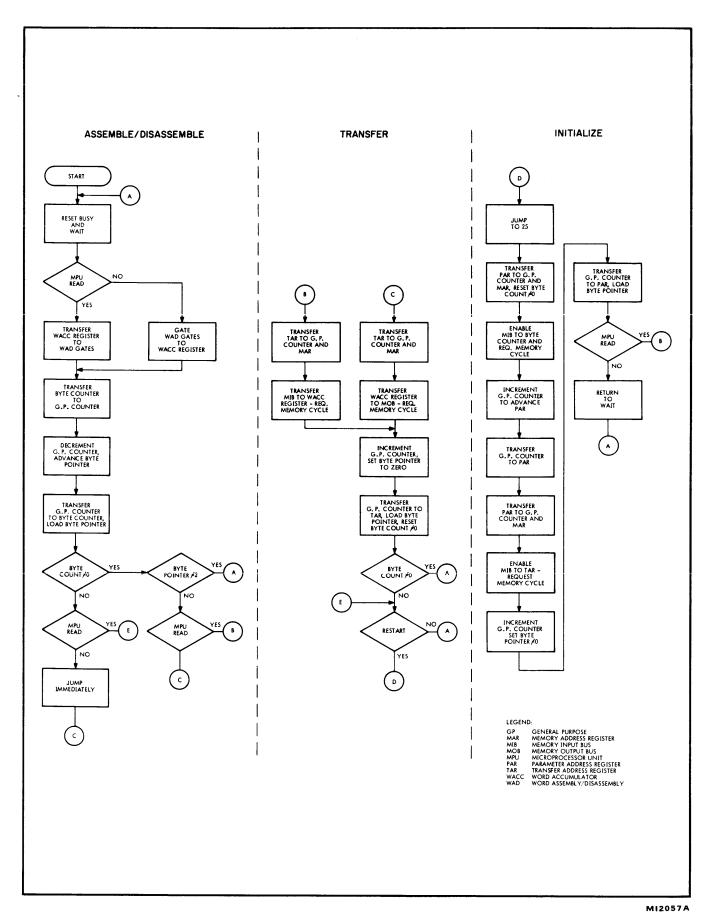

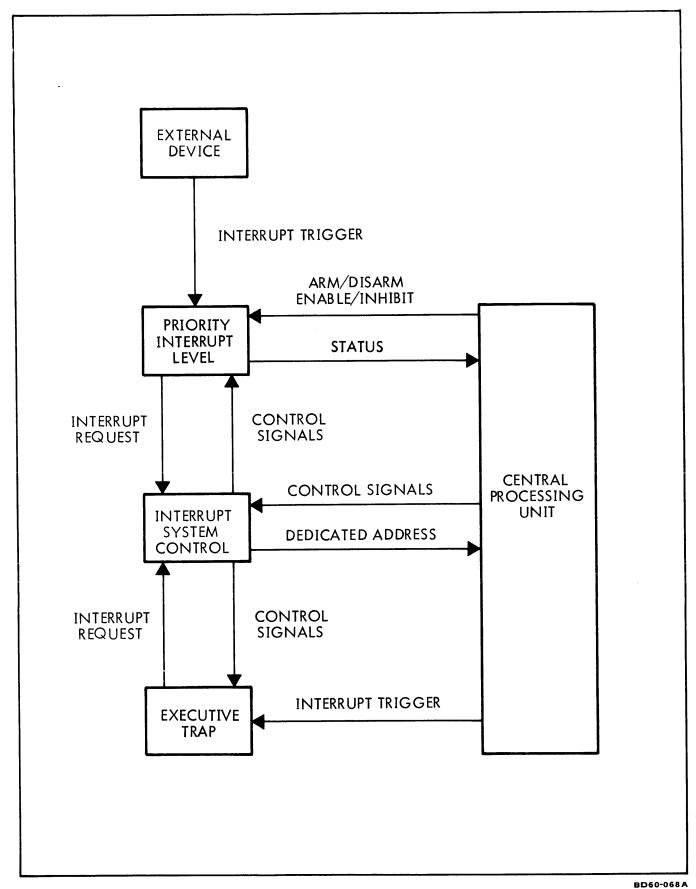

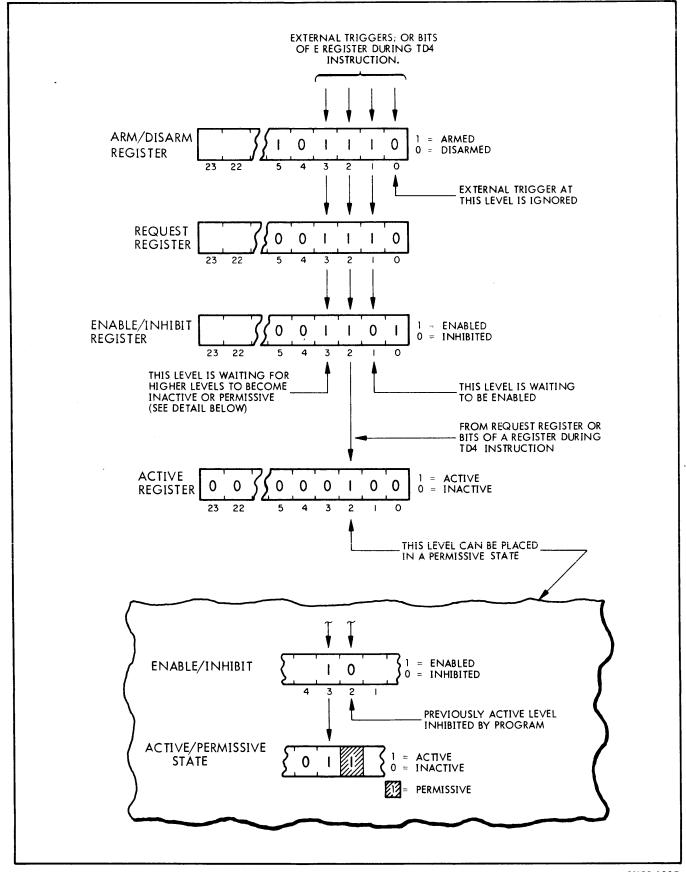

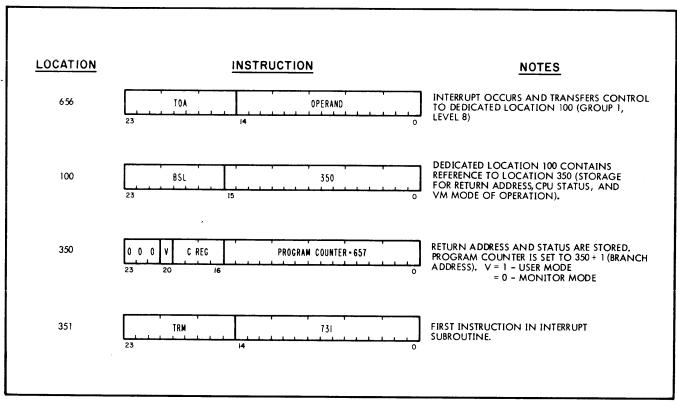

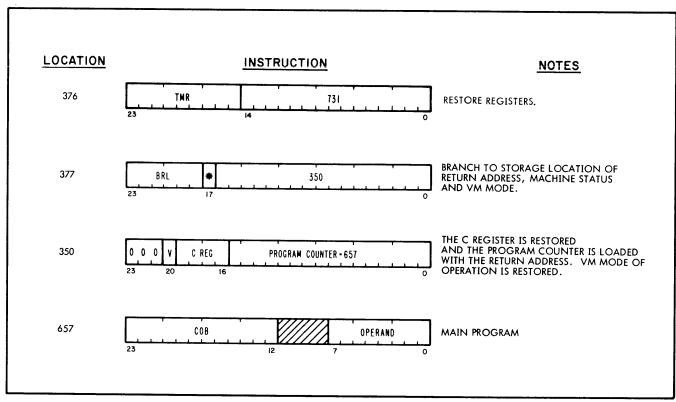

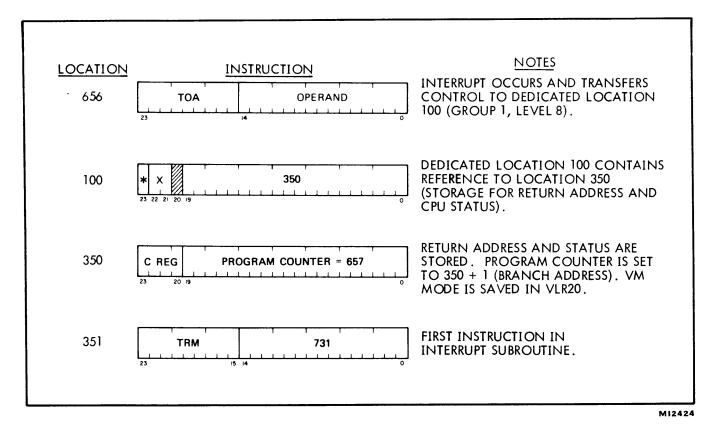

| 5-1.<br>5-2.<br>5-3.<br>5-4.<br>5-5.<br>5-6.                                                 | Functional Block Diagram, Priority Interrupt System  External Interrupt Control  Interrupt Subroutine Entry, Operational State Zero  Interrupt Subroutine Exit, Operational State Zero  Interrupt Subroutine Entry, Operational States One and Three  Interrupt Subroutine Exit, Operational States One and Three | . 5-4<br>. 5-7<br>. 5-7<br>. 5-8                                                                              |

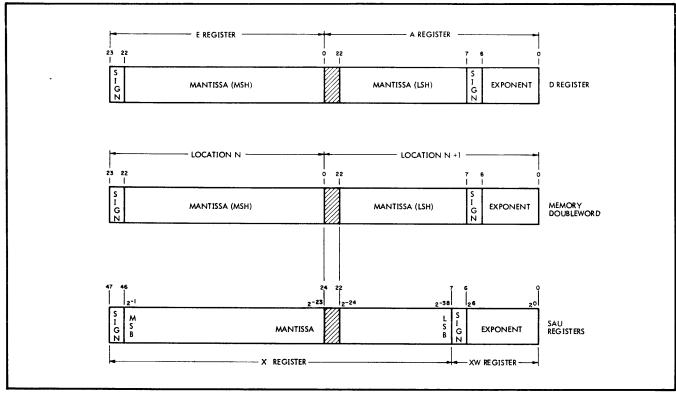

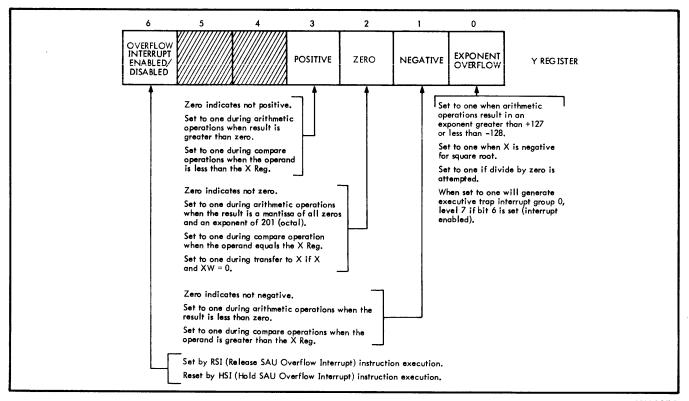

| 6-1.<br>6-2.                                                                                 | Floating-Point Data Formats                                                                                                                                                                                                                                                                                       | . 6-2<br>. 6-2                                                                                                |

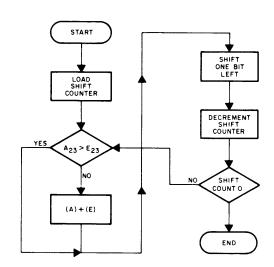

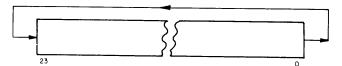

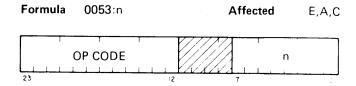

| 7-1.<br>7-2.                                                                                 | Typical Instruction Word Formats                                                                                                                                                                                                                                                                                  | . 7-2<br>. 7-17                                                                                               |

|                                                                                              | TABLES                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| Table                                                                                        |                                                                                                                                                                                                                                                                                                                   | Page                                                                                                          |

| 2-1.                                                                                         | VPR Status Bits Definitions and Functions                                                                                                                                                                                                                                                                         | . 2-5                                                                                                         |

| 4-1.<br>4-2.                                                                                 | Peripheral Unit Interrupt Control                                                                                                                                                                                                                                                                                 | . 4-13<br>. 4-14                                                                                              |

| 7-1.                                                                                         | Summary of Extended Instructions Derived from Standard Instructions                                                                                                                                                                                                                                               | . 7-3                                                                                                         |

# SECTION I

## **SCOPE OF MANUAL**

This manual contains reference material for the Harris 800 Computer Systems designed and manufactured by Harris Corporation, Computer Systems Division. Included are descriptions of the overall computer organization, central processing unit (CPU), memory configurations, priority interrupt system, input/output (I/O) channels, and instruction set. Various hardware features and options are also described; application and programming examples are provided where appropriate.

The material in this manual is oriented toward the user/programmer with a knowledge of computer fundamentals and terminology.

## **HARRIS 800 SYSTEMS**

This family is comprised of high-performance, disc-oriented, virtual memory computer systems for performing concurrent time-sharing, batch, remote job entry and real-time processing. The Harris 800 Computer Systems are building-block systems; each may be expanded to support a variety of applications and performance levels. Upgrades between systems are also available. Harris 800 systems provide cost-effective solutions for distributed data processing, transaction oriented processing, and communications applications. Data Base Management and Inquiry software is available for fast, efficient file maintenance and information retrieval. These multi-use systems are ideal for scientific, commercial, and real-time applications since they provide true multi-programming and multi-lingual capabilities.

The Harris 100, 500, and 800 systems comprise a series of compatible data processing systems. These systems include a family of central processors, peripheral devices and programming support systems. The processors share a common code structure and instruction formats. They differ primarily in memory capacity, computational speed, the number of instructions, and input-output throughput. Harris 800 systems are products based on the experience gained with 100 and 500 systems. Since an 800 is upward compatible from 100 or 500 systems, a move from 100 or 500 systems to 800 systems is relatively easy.

Harris 800 instructions, character codes, interrupt facilities, and programming features are functionally the same as corresponding features on 100 and 500 processors. Harris 800 systems provide the capability of running 100 and 500 operating systems, as well as operating systems designed specifically for the advanced 800 features, with a minimum impact on application programs and data. Users' programs which run on 100 and 500 systems will also run on 800 systems.

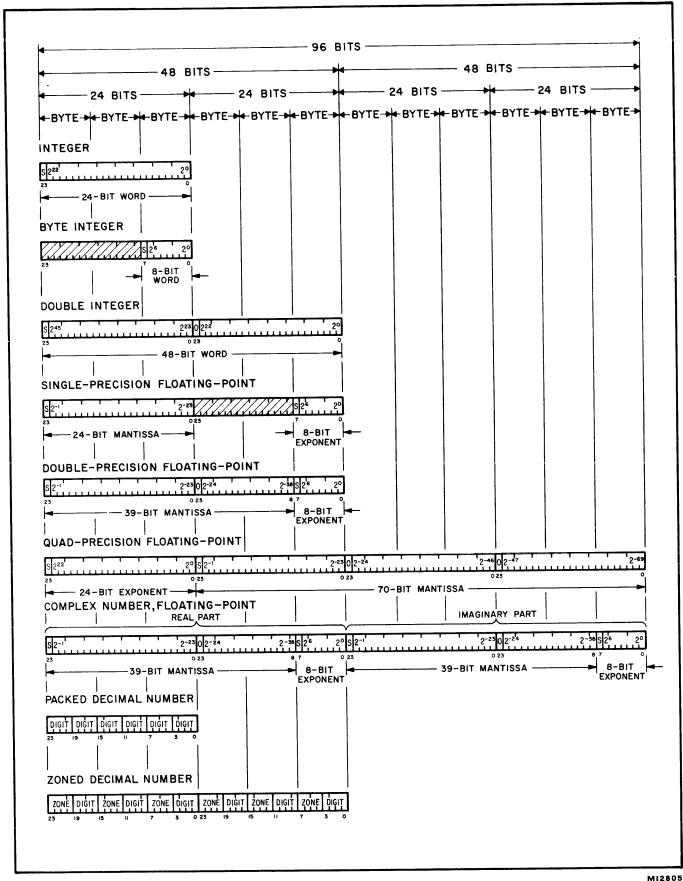

Harris 800 systems use the same standard instruction set as 100 and 500 systems. A decimal feature has been added which includes pack, unpack, decimal add, and decimal subtract instructions. The scientific instruction set executes floating-point operations on 48-bit operands which employ an 8-bit exponent and a 39-bit mantissa. Should greater precision be required, extended floating-point operations can be invoked. These operations employ a 24-bit exponent and 70-bit mantissa.

Another major aspect of the 800 is the capability to attach a wide variety of I/O devices through several types of block channels. Like the 100 and 500 systems, channels are provided for the attachment of large numbers of communication devices. Most of the 800 I/O channels and peripherals are upward compatible from 100 and 500 systems.

The increased performance of the 800 is achieved by increasing the width of data paths and incorporating a pipelining technique into the architecture. Data transfers between memory and available I/O channels proceed on a 48-bit basis. Most instruction fetches and many operand fetches are 48-bit transfers as well. Pipelining provides simultaneous instruction execution, address processing, and instruction and operand fetches. It provides prefetch of both operands and instructions. Several instructions are processed simultaneously. When conditional branch instructions are executed, instructions for both decision paths are prefetched and preprocessed so that minimal time is lost after the decision is made.

# BASIC COMPUTER ORGANIZATION

#### **Basic Operation**

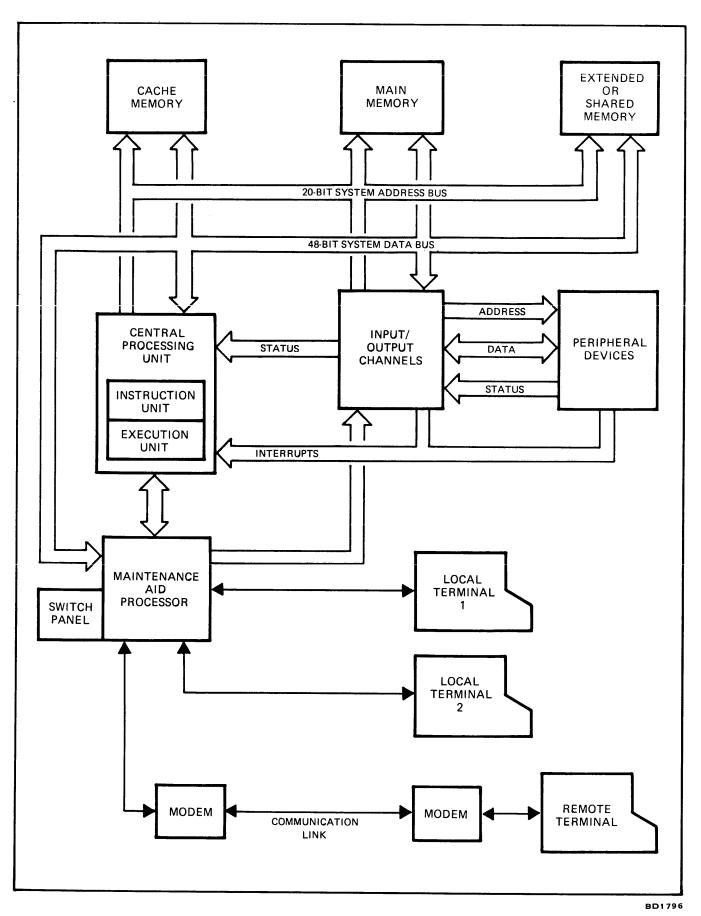

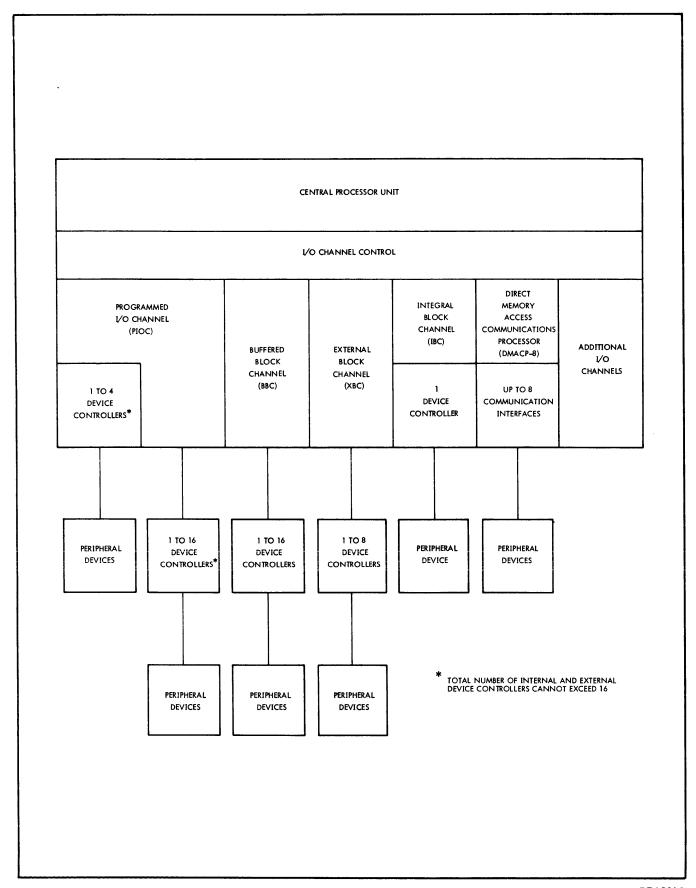

Figure 1-1 illustrates the functional relationship between major units of a typical system. The major functional units include the central processing unit (CPU) consisting of an Instruction Unit and an Execution Unit, main memory, cache memory, shared memory, extended memory, priority interrupt system, input/output (I/O) channels, Maintenance Aid Processor (MAP), and switch panel.

The computer has a variable word length, a multi-access bus structure, and an integral memory system. Operations are performed on, and from, 48-bit and 24-bit data and instruction words. In addition, the computer is capable of selective byte manipulation and performs Boolean functions on single, selected bits. Two's complement arithmetic is performed on parallel, binary, fixed-point or floating-point operands. Fixed-point capabilities include hardware multiply, divide, and square root functions, as and subtract 48-bit add well as Double-precision (48-bit) floating-point operations employ 8-bit exponent and 39-bit mantissa, quad-precision operations employ a 24-bit exponent and a 70-bit mantissa. Decimal addition and subtraction are additional arithmetic functions included. Decimal arithmetic is performed on data in packed format. In this format, two decimal digits are placed in one byte. Decimal pack and unpack capability is included in the instruction set.

Data or instruction words may be retrieved from or stored in memory, retained in one of the CPU registers, or received from and transmitted to peripheral devices via the I/O channels. Prior to execution, instructions must be loaded into, and subsequently retrieved from, physical memory. Main memory is accessed on a 48-bit boundary. This arrangement permits an instruction prefetch which reduces the effective access time of the memory system. In addition, the CPU employs an asynchronous cycle that automatically adjusts to the timing of the addressed memory module. If, for example, memory contention occurs, the CPU waits at a predetermined point until memory becomes available.

Memory may be accessed at the 48-bit, 24-bit, 8-bit (byte), and bit levels by the standard instruction set. Memory is divided into thirty-two, 96K byte sections (map 0 through map 31). If the system is in the Compatibility Mode, up to 96K bytes per section may be directly addressed and up to 768K bytes can be accessed

by indirect and indexed address references; executable code is restricted to 192K bytes at any given time. When in the Address Extension Mode, up to 3M bytes of memory may be accessed directly, and executable code may be located anywhere in memory and is not limited in size.

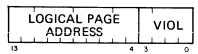

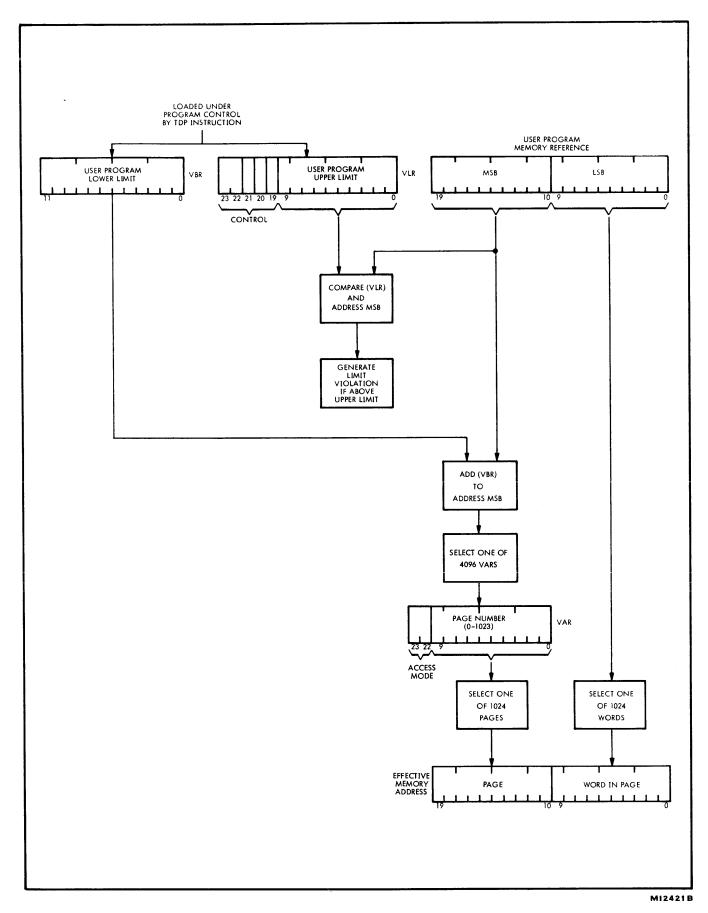

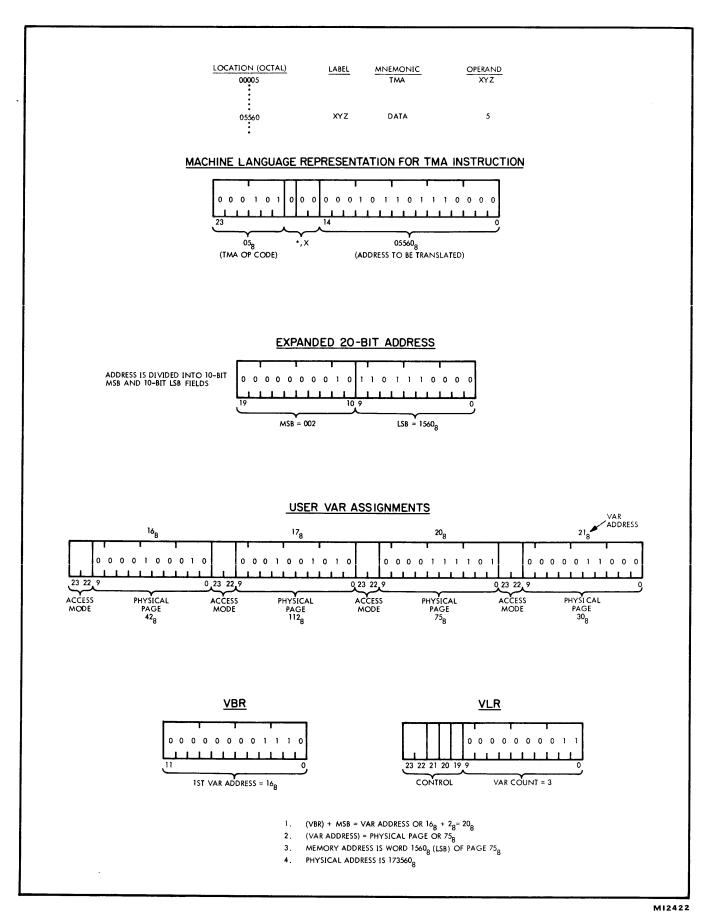

When virtual memory is enabled, two addressing modes are employed, User and Monitor. Addresses generated in the User Mode (called logical addresses) are translated into physical memory addresses by the virtual memory hardware. The logical address is translated to the physical address by selecting the appropriate 3K byte physical "page" and the offset within the page. The division of main memory into physical pages allows a program to be located in non-contiguous areas of memory, and to be transferred (in page increments) between memory and an external mass storage device under system control. When the virtual memory hardware detects a reference to a page which is not currently resident in main memory, a page fault occurs. This supports a demand-page technique which allows portions of a program to be absent from memory while the program is running. The occurrence of a page fault initiates a system process which transfers the referenced page to physical memory. The paging logic is disabled in the Monitor Mode, thus addresses generated in the Monitor Mode are used directly as physical main memory addresses.

#### **Central Processing Unit (CPU)**

Included in the CPU are several general and special-purpose registers, an arithmetic section, timing and control logic, memory interface logic, and I/O channel interface circuits. Special paging registers and control logic are provided for virtual memory operation.

Five general-purpose registers are included in a basic CPU. These registers are employed in a variety of logical, arithmetic, and manipulative operations such memory-to-register, and register-to-memory, the instructions. Three of register-to-register general-purpose registers can be used for indexing in memory addressing functions. One register serves as the register during input/output communication operations. A 48-bit register is formed by combining two general-purpose registers, and a byte register is created by using the eight least-significant bits of one general-purpose register. With the Interval Timer included in the CPU, the Timer (T) Register becomes a sixth general-purpose register in the Monitor Mode of operation. In the User Mode, the T Register can not be loaded but can be read.

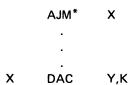

Figure 1-1. Major Functional Units

Among the special-purpose registers are those associated with integral CPU functions such as addressing, instruction decoding, and temporary storage during data manipulation. Additional special-purpose registers are those supplied with the Bit (Boolean) Processor, Interval Timer (T Register for timing applications), and the Address Trap.

The arithmetic section consists primarily of a 48-bit arithmetic logic unit (ALU) and several buses to permit data manipulation between the various registers and the ALU. Arithmetic functions performed include addition, subtraction, multiplication, division, and square root computation.

Instruction execution sequences are established and directed by the timing and control logic associated with includes This logic Instruction Unit. crystal-controlled clock generator that provides precise timing for all instruction functions. Instruction words of 24 or 48 bits are prefetched and retained in an instruction buffer. As many as four instructions may be prefetched and stored in the buffer. The control logic decodes these instruction words and provides the internal commands necessary for execution. In the User Mode of logic operates in operation, the paging control conjunction with the basic CPU timing to implement address translation and demand paging techniques.

CPU-memory interface circuits consist of address and and parity buses and registers. data-handling generation/checking or error checking and correction logic. Memory interface circuits include a 48-bit data register that retains both the read and write data, a 20-bit address register to define the location to be accessed in up to 3,072K bytes of physical memory, data multiplexing logic to control read and write data handling, and address multiplexing and control logic for selecting the proper memory segment and a location within that segment. Data to be written (stored) in memory is applied via the 48-bit system data bus. Address inputs are applied to the memory interface via the system address bus. The address source may be the CPU, one of the block transfer channels, communications processor, or, in the User Mode of operation, the paging logic addressing circuits.

Communications between the CPU and the I/O channels are conducted via the channel interface logic in the CPU. This logic makes use of the system buses and one of the general-purpose registers in order to implement data and

address flow between the CPU and I/O channels. channel-unit 1/0 channel conducts an Although and asynchronously, communications independently operations such as channel-unit input/output selection and activation, function commands, and status testing are initiated under program control.

# Scientific Arithmetic Unit (SAU) Functions

The Execution Unit provides floating-point arithmetic capability. A special repertoire of instructions is provided for performing floating-point computations. The E Unit contains the X, XW and Y Registers for manipulating 48-bit quantities and for reporting arithmetic status (condition) after the operation is completed. Data and condition information may be displayed on the Map Terminal. An executive trap is provided with the E Unit for detection of overflow/underflow conditions. Refer to Section VI for a more detailed description of the E Unit execution of SAU instructions.

#### **Memory Units**

The memory system consists of main memory, extended memory, cache memory, and shared memory units. The Maintenance Aid Processor, I/O block channels, communication processors, and the CPU communicate directly with all memory modules. Each memory module contains the address decode logic necessary to determine when a particular module is selected. The CPU provides the required hand-shaking signals with the memory module to ensure proper data transfer.

Storage of information, both instruction and data words, is the function of main memory which may be located in the CPU or in the Extended Memory Unit. The basic memory module is a 192K byte MOS memory module which features single bit error correction. A system can be configured with up to 3,072K bytes of memory when the Extended Memory Unit is attached.

Cache memory provides fast access to data stored in the memory system. The 6K byte cache stores up to 1,024 memory word addresses and the information (instruction or data) contained therein. Data storage in cache is structured as two, 512 word sections, where each word is 48 bits wide. One section stores only instructions, and the other section stores only operands. When the CPU accesses the memory system, the address word is presented to the main memory and the cache. If the requested address and information is present in cache, the information is placed on the 48-bit data bus. If the cache

does not contain the requested address and information, the data is provided from main memory and the cache is updated to contain it. Cache memory effectiveness is significantly affected by program structure.

Shared memory is configured using the basic 192K byte (MOS) memory modules. Maximum memory available to a single CPU is 3,072K bytes which includes the combination of main memory and shared memory.

Refer to Section III for additional details concerning the memory system.

#### Input/Output Operation

Input/Output (I/O) operations consist of data, address, command, or status transfers between selected peripheral devices and the CPU or memory. Programmed and direct memory access (DMA) data transfers are supported. All such operations are initiated under program control and are conducted, asynchronously, by an I/O or communications processor channel. Various types of channel modules may be installed in a system. All channels in the system can be active simultaneously, and each channel may communicate with up to 16 controllers, however, only one device can transfer data at one time.

An I/O operation is initiated by selecting and activating a channel, and one of its assigned peripheral devices, through the execution of a computer input/output instruction. (The instruction set includes seven input/output instructions.) A specific I/O operation may involve preparing a peripheral device for a subsequent communication, determining the operational status of a device, or initiating a data transfer. Once activated, the channel provides complete functional control over the operation.

Data may be transferred on a single word basis (i.e., one data word per instruction) or automatically, in blocks of n words per operation. Block data transfers are performed by the Direct Memory Access Communication Processor (DMACP-8), External Block Channel (XBC), Integral Block Channel (IBC), or Buffered Block Channel (BBC). Each available type of I/O channel and communications processor permits data transfers to (input) and from (output) the computer. Data transfers between memory and the DMACP-8, XBC, or IBC are in a 24-bit parallel format, and between memory and the BBC in a 48-bit parallel format.

I/O operations may also be conducted on an interrupt basis through the use of interrupt logic in the channel(s). The channel interrupt system can be placed under program control and selectively enabled or disabled by an input/output instruction. Peripheral device functions may be connected directly to the computer priority interrupt system, bypassing the channel interrupt logic.

#### **Priority Interrupt System**

The interrupt system is a multi-level vectored structure that allows additional program control of input/output devices and internal CPU operations, and immediate recognition of special external conditions on the basis of priority. Receipt and recognition of an interrupt trigger permits normal program flow to be diverted to a subroutine that services the interrupt and returns the program to its normal sequence at the point where the interruption occurred.

#### MAINTENANCE AID PROCESSOR

The Maintenance Aid Processor (MAP), together with the terminal connected to the MAP, replace the conventional computer control panel. The MAP and terminal provide an intelligent interface between the operator and the computer.

Normal operator functions provided by the MAP Terminal include facilities for manually starting and halting operations, entering data into memory and various registers, and selecting memory and registers for display. System status and other important functions can be displayed via the MAP and its connected terminal. Master clear and initial program load (bootstrap) functions are also provided.

In addition to the normal operator functions, the MAP provides special maintenance functions. Special support hardware operates in conjunction with the MAP to provide selective monitoring and control of the computer logic. A maintenance bus provides access to all essential internal computer hardware not otherwise accessible. Maintenance functions include the capabilities to perform a limited master clear, step through instructions and microinstructions, control the CPU clock, and read/write non-programmable CPU registers. I/O channel read and write control, program and memory address compare breakpoint control, and power supply voltage monitoring are additional functions performed by the MAP.

#### SWITCH PANEL

Four switches are located on the Switch Panel; one keylock switch and three toggle switches. The keylock switch is used to lock and disable any of the maintenance features that may affect computer operations. It also enables or disables the Stall Alarm, and enables or disables diagnostic testing of the 192K byte MOS memory modules. Additionally, the keylock switch enables selection of a local or remote terminal for connection to the MAP.

The toggle switches provide for alternating the functions of the local terminals, connecting the MAP to a selected local terminal, and enabling the 192K byte MOS memory modules for a diagnostic mode of operation. Memory module interleaving, error correction and rewrite, and fast access functions are disabled when the diagnostic mode is selected.

#### **DATA TERMINALS**

Two local data terminals are provided with each system. A similar data terminal is available for remote diagnostic operations. All terminals are of the console type, consisting of a CRT and keyboard.

One of the local terminals is dedicated to operator communications (OPCOM). An operator using OPCOM commands at this terminal can display information about the system and exert control over the program, I/O, and user configurations. The second local terminal is used as a MAP Terminal. A switch on the Switch Panel allows for interchanging the assigned functions of the local terminals, i.e., either terminal can be designated as the OPCOM Terminal, while the second terminal is designated as the MAP Terminal. When the system is powered up, the MAP Terminal is automatically connected to the MAP. A command issued to the MAP from the MAP Terminal disconnects the MAP and connects the terminal to the CPU as a User Terminal. The MAP Terminal can be switched from the user function to the MAP function from the Switch Panel.

System maintenance is facilitated through the use of a remote terminal located at a diagnostic site. When a system error occurs, a remote MAP Terminal at the diagnostic site can be connected to the system. An auxiliary communications link is available for each system to implement this function. The remote terminal is connected to the MAP with the keylock switch. This function permits the engineer at the remote location to

examine the system for errors, and allows him to load, run, and control diagnostics from the remote terminal. The diagnostics can be run concurrently with other system activities.

## STANDARD AND OPTIONAL FEATURES

Harris 800 systems contain various hardware features. Many options are also available to enhance system performance. A brief description of standard features and options are provided in the following paragraphs. Unless otherwise indicated, additional details pertaining to system features and options are contained in Section II.

A listing of the standard hardware that is provided with a typical system is as follows:

- Central Processor with hardware multiply/ divide/square root, power supplies, and two cabinets

- Scientific Arithmetic Functions

- 960K bytes of MOS Memory with error correction

- 6K byte Cache Memory

- 12,288K bytes of Virtual Memory address space

- Maintenance Aid Processor with CRT Console

- System Console CRT with Keyboard and Controller

- Switch Panel

- 16 Priority Interrupt Levels

- 120 Hertz Clock

- Power Fail Alarm

- Firmware Bootstraps

- Bit Processor

- Stall Alarm

- Executive Traps

- Interval Timer

- Address Trap

- Programmed Input Output Channel (PIOC)

- Direct Memory Access Communications Processor (DMACP-8) Channel with four asynchronous ports

- Buffered Block Channel (BBC) (2)

A summary of optional hardware items that could be added to the foregoing system follows:

- 100 kHz Real Time Clock

- Programmed Input Output Channels (PIOCs)

- External Block Channels (XBCs)

- Integral Block Channels (IBCs)

- Buffered Block Channels (BBCs)

- Direct Memory Access Communications Processor (DMACP-8) Channels

- 56 Priority Interrupt Levels

- Memory Extension Unit

- Shared Memory Unit

- I/O Expansion Unit

- Interprocessor Communication Facility

- Multi-Channel Adapter

#### **Priority Interrupts**

Four priority interrupt groups are available; groups 0, 1, 2 and 3. Group 0 is reserved for internal CPU functions and is comprised of eight executive trap interrupt levels. All executive trap levels are associated with specific functions.

Groups 1, 2, and 3 are reserved for external interrupts; each group may have up to 24 levels. A basic system is supplied with 16 external interrupt levels. Fifty-six additional external interrupt levels are available.

Complete details pertaining to the priority interrupt system are contained in Section V.

#### 120 Hertz Clock

Continuously generated interrupt triggers are placed under software control by enabling or disabling the associated external interrupt level. By this method, the 120 Hertz Clock may be used for various timing operations. The clock continuously transmits 120 interrupt trigger pulses per second for 60 Hertz power, and 100 interrupt trigger pulses per second for 50 Hertz power.

#### Interval Timer

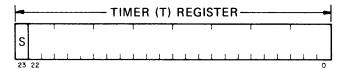

The programmable Interval Timer functions as an internal CPU timer that provides a method for regulating operating program segments and recording other intervals. Depending on the instruction used for its activation, the

Interval Timer clocks either CPU time or clock (real) time. In addition to its timing applications, the Interval Timer provides the user with an additional 24-bit general-purpose register that may be accessed through the standard instruction set when in the Monitor Mode of operation. The T Register may not be modified when in the User Mode.

#### 100 kHz Real Time Clock

This option provides the programmer with general purpose clock pulses that are independent of the mainframe clock pulses. With an accuracy of .05%, the real time clock pulses are available whether the CPU is in standby or not. The timing pulses can be used to measure user's program running time, or to generate periodic interrupts. Programming is accomplished through normal input/output commands. One or two real time clocks may be installed on the Programmed Input Output Channel (PIOC) boards.

#### Power Fail Alarm

The Power Fail Alarm Module monitors the ac line voltage and generates power down signals to the CPU and memory modules in the event of an ac power failure or sustained low ac line voltage. An executive trap interrupt is triggered and, to prepare the CPU for an orderly restart, the major CPU registers and control logic are cleared. A one millisecond interval is available between the time of the interrupt and final shutdown. Once the ac line voltage is restored to a normal level, an executive trap is triggered and a restart signal is sent to the MAP. This signal causes the MAP firmware to interrogate the system status and reinstate the operation, if appropriate.

#### **Bootstraps**

Automatic program loading from a selected peripheral device is provided by the Bootstrap feature. Through the use of the MAP Terminal, the appropriate bootstrap program is loaded into memory. Once loaded, the bootstrap program will automatically load a minimum of one record from the appropriate device. Programs provide for loading from disc, magnetic tape, or punched cards.

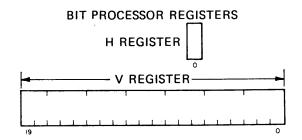

#### **Bit Processor**

Capability is provided by the Bit Processor for selectively changing, testing, or performing logical operations on a single bit in memory. A special group of instructions enables implementation of these functions.

#### Stall Alarm

Certain operations in the instruction set and other internal conditions prohibit the recognition of external interrupts. A series of these instructions or conditions could, therefore, produce a situation where external interrupts are, in effect, "locked out". The Stall Alarm monitors all instructions and conditions in this interrupt-prohibiting category. If a series of these instructions or conditions have not been completed before the elapse of a predetermined time period, they are terminated and an executive trap interrupt is generated. The subsequent interrupt processing routine may then examine the situation and take any necessary corrective action. The Stall Alarm includes the appropriate control logic and is furnished with the associated executive trap interrupt.

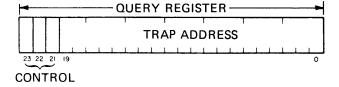

#### Address Trap

This feature provides for an executive trap interrupt to occur at a specified address and under certain conditions. The Address Trap is used as an on-line debugging aid for use in applications such as breakpoint tracing. An address may be defined under program control so that when the address is referenced, an interrupt will be generated at the assigned executive level. The Address Trap may be enabled or disabled under program control. The Query Register provided with the Address Trap may not be modified when the virtual memory is in the User Mode of operation.

# Input/Output and Communications Processor Channels

A variety of I/O and communications processor channel types are available with a system. Each channel is designed for a particular input/output data transfer application. Multiple channels of a given type may be used as the application demands. A brief description of each type follows. A more detailed discussion of the channels is provided in Section IV.

#### Programmed Input Output Channel (PIOC)

This is an I/O channel capable of implementing a single-word, eight-bit, parallel data transfer between the CPU and a suitable peripheral device. This channel has provisions for installing up to four unit interface controllers on the I/O circuit board. In addition, the PIOC can drive up to 12 additional remote device controllers. This board also contains a programmable Interrupt Generator which may be used in multi-processor installations. If required, one or two Real Time Clocks

may be installed on the board. Units which may be interfaced to the PIOC include teletypes (with or without cassette), line printers, CRT terminals, RS 232 asynchronous controllers, and communications multiplexers.

#### **Buffered Block Channel (BBC)**

The Buffered Block Channel performs and controls automatic data transfers between main memory and any of up to 16 external high-speed peripheral controllers. Data is transferred between main memory and the BBC in a 48-bit parallel word format, and between the BBC and peripheral controllers in a 24-bit parallel word format. Data transfers between the BBC and a peripheral controller may be performed simultaneously with transfers between the BBC and memory.

Data and command chaining is supported as well as programmed input/output transfers. After a block of data is transferred, the data chaining capability permits a subsequent data block to be automatically transferred without program intervention. Command chaining enables the channel to automatically access memory for a command word upon completion of the current block transfer. A new block of data is then automatically transferred under new command restraints. In addition to the standard forward motion read and write operations, the BBC can also perform a read reverse operation which alleviates the need for rewinding magnetic tapes if the controller supports this feature. For this function, the 24-bit input data words from the peripheral controller are assembled in reverse order by the BBC and are then transferred to memory in 48-bit parallel format. Addressing and transfer block sizes are established under program control. Once initiated, all BBC DMA operations proceed automatically.

A large internal buffer (48-bits wide by 16 words deep) in the BBC allows peripheral transfer rates to be maintained during periods when the CPU inhibits memory access by the channel. The internal buffer and a dual priority scheme make most BBC memory requests occur in groups. This function increases CPU performance by increasing the effective bandwidth.

A special function is provided which enables the BBC to generate odd parity on command and data transfers to designated controllers, and check for odd parity on data transfers from the units. Parity errors occurring during block or programmed word transfers are reported with a status word.

# Direct Memory Access Communications Processor (DMACP-8)

The DMACP-8 is a multiport communications processor channel dedicated to serial data communications and provides direct access to main memory for up to eight devices. These communication devices can be either asynchronous or synchronous. Up to eight asynchronous interfaces can be used, or one synchronous and up to four asynchronous interfaces can be accommodated. The one synchronous interface takes the place of four synchronous interfaces. Each interface is termed a port.

Standard interfaces available with the DMACP-8 are RS-232C, 20 ma current loop, and Harris Differential. Asynchronous devices supported are Harris Standard CRT Terminals, interactive CRTs, teletypewriters, Bell Asynchronous Modems, and Bell compatible modems up to 19.2 kilobaud. Also supported are Ti 700 devices with or without cassettes. Synchronous devices supported are Bell Synchronous RS-232C Modems, and Bell compatible synchronous modems with transfer rates up to and including 50 kilobaud.

Programmed data transfers or block data transfers of 24-bits are performed between the DMACP-8 and CPU. Programmed word transfers are used for status check, initialization, and control of the DMACP-8. Block mode operations are used for data transfers between main memory and the communication devices attached to the ports. These transfers are under control of the microprocessor installed on the DMACP-8 board and require no intervention by the CPU. Transfers between the DMACP-8 and main memory are in the form of 24-bit words, while transfers between the DMACP-8 and communication devices are in the form of 8-bit bytes.

#### External Block Channel (XBC)

The External Block Channel provides for direct memory access operations between memory and up-to-eight user-defined external controllers. Any one of the eight controllers connected to the XBC may initiate memory transfer sequences. Since controllers may be self-starting, no CPU commands are required to perform DMA transfers. If required, however, controllers may be activated by generating commands to the XBC by means of the input/output instructions. Parameters required for block transfers, such as block length and memory transfer address, may be furnished by either the controller or the CPU. Once a controller is activated for memory transfer operations, the controller initiates word transfer sequences and controls the operational parameters. Data is

transferred between main memory and the controllers in a 24-bit parallel word format.

#### Integral Block Channel (IBC)

An Integral Block Channel provides automatic data transfers between main memory and one self-contained controller. The controller is dedicated to a block mode card reader. The IBC is initialized by the CPU to perform DMA transfers under self-control. Data chaining provides for the transfer of subsequent blocks of data without program intervention. Data transfers between memory and the controller are in a 24-bit parallel word format.

#### Input/Output Expansion Unit

Available as an option, the input/output expansion unit increases the input/output capacity of a system. The maximum number of input/output channels supported by a system is 31. I/O expansion is implemented by adding a cabinet assembly to the basic system. The cabinet contains a power distribution unit, power supplies, and a 22-slot chassis assembly. A pair of PC boards plus cables is also provided which is used to connect the expansion unit to the basic system. The I/O expansion unit may be used to expand the I/O capabilities of computer systems located in the field.

# Interprocessor Communication Facility

The Interprocessor Communication Facility (ICF) provides direct communications capability between interconnected computers in a dual computer installation. Memory-to-memory transfers are made under the control of a DMA channel installed in each CPU. Either channel in the link may control the transfer. The computer link is particularly useful in real-time control applications involving dual computers.

Two Harris 800 CPUs may be linked together, or the CPU in an 800 system may be interconnected to a CPU in either a Harris 100 or 500 system. The ICF is implemented with two dedicated Buffer Block Channels, link cables, and four Priority Interrupt Generators. The interconnected systems may be separated by as much as 120 feet. Software interrupts generated by the Priority Interrupt Generators are normally used to initialize link operations.

This option is not supported by VULCAN except for the priority interrupt structure. Establishment of control is user implemented and requires user code.

#### Multi-Channel Adapter

Usually used in a multiple computer configuration, the Multi-Channel Adapter allows peripheral devices to be shared by two or more computers. CPUs share units via an I/O interface made common by daisy chain installations. Normally, each CPU is equipped with an interrupt generator for the purpose of generating software interrupts required for daisy chain operations. When a CPU wants to communicate with a unit on the common interface, it generates an interrupt to cause the other CPU(s) to set their daisy chained channels off-line. The CPU generating the interrupt can then exercise the shared unit without interference. This feature is not supported by VULCAN except for the priority interrupt structure. Proper establishment of control is user implemented and requires user code. If simultaneous access is made to a unit on the common interface, the results are indeterminate.

#### PERIPHERAL EQUIPMENT

Harris 800 systems can be expanded and enhanced by selection from a variety of peripheral equipment offered for each system, including:

- Moving Head Discs (40, 80, and 300M Bytes)

- Magnetic Tapes (45 and 75 ips)

- Card Readers (300, 600 and 1000 cpm)

- Key Punch/Card Punch (35 cpm)

- Line Printers (300, 600 and 900 lpm)

- Electrostatic printer/plotter (300, 500, 1000 and 1200 lpm)

- Paper Tape Devices

- Console Devices, Local and Remote Terminals

- Supplementary equipment to meet most custom requirements

#### **SOFTWARE**

The Virtual Memory Manager (VULCAN) operating system is a priority-structured, demand paged, multi-programming operating system. VULCAN concurrently supports multi-stream batch processing, interactive terminal time-sharing, transaction-oriented

processing, multiple remote job entry and real-time operations. Under VULCAN, the virtual memory hardware/software system is transparent to the user. Up to 3M bytes per user is available, all of which may be executable code.

#### Language Processors

- FORTRAN 77

- FORTRAN IV Compiler with extensions

- Extended BASIC

- COBOL Compiler

- RPG II Compiler

- SNOBOL 4 Interpreter

- FORGO (Diagnostic Load-and-Go FORTRAN Compiler)

- APL Interpreter

- Harris MACRO Assembler

#### **Utility Programs**

- Sort/Merge

- VISP (Indexed Sequential File Handler)

- ACUTIL (System Accounting)

- Cross Reference

- VBUG (Symbolic Debugger)

#### Remote Job Entry Support Packages

- IBM HASP II M/L

- IBM 2780

- CDC 200 UT

- UNIVAC 1004

#### Remote Batch Terminal Host Packages

- IBM HASP II M/L

- IBM 2780

#### Data Base Management System

- TOTAL\*

- T-ask\*

<sup>\*</sup> TOTAL and T-ask are registered trademarks of CINCOM Systems, Inc.

# SUMMARY OF CHARACTERISTICS

The major operating characteristics and pertinent technical specifications of the Harris 800 Computer Systems are summarized below.

Computer Organization . . . . . . . . Microprogrammed general-purpose digital computer.

Multi-level instruction pipelining.

Overlapped address preparation and memory access.

Multi-access central bus structure.

Buffered I/O channels.

Arithmetic . . . . . . . . . . . . . . . . . Parallel, binary, two's complement fixed and floating

point; includes hardware multiply, divide, square root,

and hardware floating point processor.

Decimal addition and subtraction on packed operands.

### Memory System

#### Main Memory

Type . . . . . . N-Channel MOS

Minimum Size . . . . 192K bytes

Maximum Size . . . . 3M bytes

Increment . . . . . 192K bytes

Word Length . . . . . 48 bits

Parity. . . . . . . One bit error correct

#### Cache Memory

Storage Configuration . . . Divided into two, 3K byte sections. One section

stores only instructions, and the other section

stores only operands.

## **Shared Memory**

Type . . . . . . . N-Channel MOS

Minimum Size . . . . . 192K bytes

Maximum Size . . . . . 3M bytes

Increment . . . . . . 192K bytes

Word Length . . . . . 48 bits

Parity. . . . . . . . One bit error correct

Number of Ports (maximum) . 6

Port Access . . . . . . Asynchronous, ring priority

#### Addressing

Compatibility Mode . . . . . . . Immediate

Direct to 96K bytes

Direct to 192K bytes via long address instructions

Indirect to 768K bytes (data only)

Indexed to 192K bytes

Address Extension Mode . . . . Immediate

Direct to 3M bytes Indirect to 3M bytes Indexed to 3M bytes

# Input/Output Capability

Programmed Data Transfers . . . . To/from CPU register, 8 or 24 bits

Automatic Data Transfer . . . . Direct memory access via IBC, XBC, DMACP-8,

and BBC, 24 or 48 bits

# Single Channel Maximum Transfer Rates (per sec.)

|                                                             | <u>Input</u> | <u>Output</u>          |

|-------------------------------------------------------------|--------------|------------------------|

| IBC                                                         | 80K bytes    | 80K bytes              |

| XBC (no mainframe contention) . (with mainframe contention) |              | 2M bytes<br>1.2M bytes |

| BBC                                                         | 3.7M bytes   | 3.7M bytes             |

| DMACP-8                                                     | 8.1K bytes   | 8.1K bytes             |

#### Input/Output Command Modes

| Normal                  | Normal operation for each channel type.                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Multiplex               | Channel released to master/slave peripheral units.<br>Not available on IBC, XBC, DMACP-8, or BBC.                                           |

| Output Special Function | Enables read reverse, channel-to-unit parity checking, channel internal turnaround, and unit master clear function. Applicable only to BBC. |

| Offline                 | Channel drivers turned off allowing second CPU to share devices without need for peripheral switches. Not available on IBC.                 |

| Reset                   | Resets Multiplex or Offline Mode. Channel restored online and unit selected. Not available on IBC.                                          |

**Priority Interrupt Structure**

Internal . . . . . . . . . . . . . . . . . Maximum of eight executive traps. Multi-level

vectored structure.

External . . . . . . . . . . Sixteen priority interrupt levels, standard. Optionally

expandable to 72 priority interrupt levels. Multi-level

vectored structure.

Control . . . . . . . . . . . . . . External interrupts may be individually armed, disarmed,

enabled, inhibited or triggered under program control.

Power Fail Protection . . . . . . . . Power fail alarm, standard.

**Electrical Requirements**

220/240, single phase, 3-wire (foreign)

Frequency . . . . . . . . . . . . . 60  $\pm$  2 Hz (50  $\pm$  2 Hz, optional)

Current (maximum) . . . . . 46 amps.

**Environmental Requirements**

Temperature

Operating . . . . . . . . . . . . . . . . .  $50^\circ$  F to 113 $^\circ$  F (10 $^\circ$  C to 45 $^\circ$  C), ambient air

Humidity

Operating . . . . . . . . . 20% to 80%, relative (non-condensing)

Storage . . . . . . . . . . . . 20% to 90%, relative (non-condensing)

Altitude

Operating . . . . . . . . -1,000 to 6,000 ft. (-305 to 1,829 m)

Cooling . . . . . . . . . . Forced air provided by internal fans on each chassis

# SECTION II CENTRAL PROCESSING UNIT

#### **GENERAL DESCRIPTION**

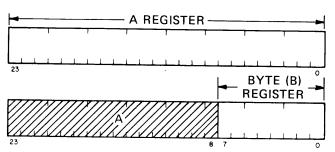

The Central Processing Unit (CPU) is a single-address parallel word-oriented, stored-program processor. Operations performed by the CPU include data transfers, arithmetic, computation, and logical manipulation. These operations are defined by instructions stored in, and retrieved from, physical memory. The specified operation is performed on single-word, double-word, byte, or single bit operands stored in memory or contained in one of the CPU registers. Data word formats, as defined by both hardware and software, are illustrated in Figure 2-1.

In addition to the general and special-purpose registers, the CPU contains an arithmetic section that performs the actual computation and logical manipulation of operands, and a control section that retrieves and decodes instructions from memory and directs the functional processes of the system. The control section also includes the paging logic that implements the memory address translation and demand-paging operations. The CPU contains interface elements for communications with the other computer elements; e.g., memory, the I/O channels, and the MAP Terminal.

# PRINCIPAL CPU REGISTERS

The following paragraphs provide a brief description of the principal registers in a CPU. Registers associated with the priority interrupt system and SAU functions are described elsewhere, in the appropriate sections of this manual.

#### A and B Registers

Serving as the principal arithmetic accumulator, the 24-bit A Register also functions as the input/output communication register during programmed (single-word) transfers between the CPU and peripheral devices. The A Register has complete arithmetic and shift capability. Bits 7-0 of A form an 8-bit pseudo-register, termed the B (Byte) Register. Both the A and B registers are accessible to the user by means of the instruction set and the MAP Terminal.

#### E Register

Employed as an extension of the A Register for increased arithmetic and shift capability, the 24-bit E Register also functions as a general-purpose storage element during various instructions. The E Register is accessible through both the instruction set and the MAP Terminal.

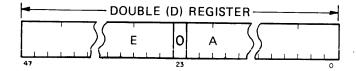

#### **D** Register

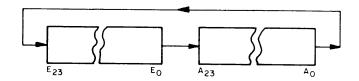

The D (Double) Register is a 48-bit pseudo register formed by combining A and E to provide double-precision arithmetic and shift capability. The A and E Registers form the least- and most-significant halves, respectively, of the 48-bit double-precision quantity. A23 is reset for most instructions. Several instructions provide direct access to the D Register; MAP Terminal entry, however, must be accomplished by accessing the E and A Registers in the proper format.

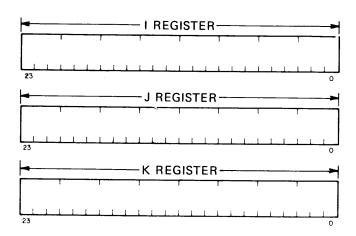

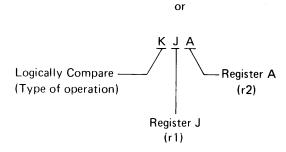

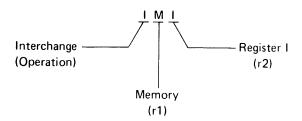

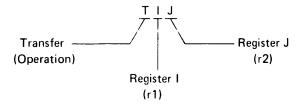

## I, J, and K Registers

Each of these is an independent, 24-bit general-purpose register that can also be employed as an index register for address modification. The I, J, and K Registers are directly accessible through the instruction set and the MAP Terminal.

Figure 2-1. Data Formats

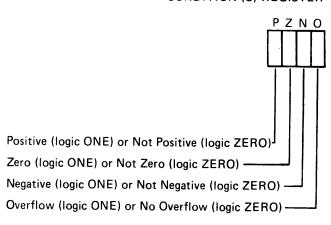

#### **Condition Code Register**

Condition codes indicate the nature of the results of an instruction. The significance of the condition code bits depends on the particular instruction just executed. Condition codes are loaded into a condition register. Two such registers are provided; a C Register and a Y Register.

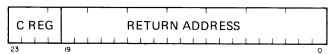

#### C Register

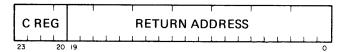

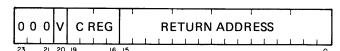

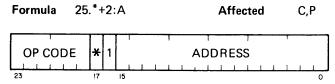

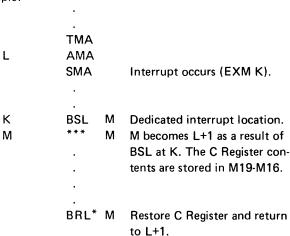

A 4-bit element that stores the results of specific operations, the C (condition) Register is accessible by means of several instructions. Condition codes generated by all instructions, except SAU and decimal instructions, are loaded into the C Register. This register is termed the C or Condition Register throughout this manual and throughout related Harris 800 manuals. Display of the C Register is provided by the MAP Terminal.

CONDITION (C) REGISTER

#### Y Register

Condition codes generated by the SAU and decimal arithmetic instructions are loaded into the Y (condition) Register. A detailed description of this register is provided in Section VI. This register is termed the Y Register throughout this, and related, Harris 800 manuals.

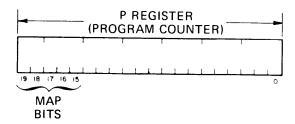

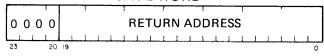

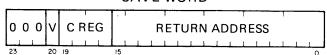

# Program Address Register

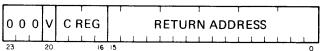

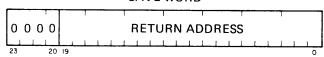

Also called the Program Counter, the 20-bit Program Address (P) Register retains the memory address from which the current instruction was fetched. In the Compatibility Mode of operation, bits 19 through 16 are not used and a maximum of 65,536 memory locations can be accessed via the P Register. In the Address Extension Mode, all 20 bits are used and a maximum of 1,048,576 locations can be accessed. In the Compatibility Mode, bit 15 is used as a map bit, and when in the Address Extension Mode, bits 19 through 15 serve as map

bits. The register can be loaded with a Branch and Link instruction. Contents of the register can be saved with a BSL instruction in the Compatibility Mode, or a BSL or BSX instruction in the Address Extension Mode. The contents of the P Register can be modified through the execution of any of several branch instructions. The MAP Terminal provides direct entry and display for the P Register.

#### Instruction Buffer

Once an instruction has been fetched from memory, it is retained in the Instruction Buffer during decoding and execution. The Instruction Buffer is not programmable. The buffer holds up to four prefetched instructions.

#### VIRTUAL MEMORY DESCRIPTION

#### Introduction

Paging is a hardware addressing scheme that allows a program's memory area to be discontiguous. Program segments may be absent from physical memory while other portions of the program are being executed. This aspect of the paging operation, termed "demand-paging", also allows the computer to execute programs larger than the available physical memory; hence, the term "virtual memory". The following paragraphs discuss the paging hardware and describe the basic functions of the VM.

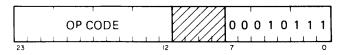

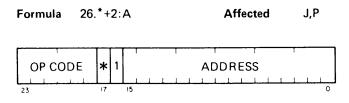

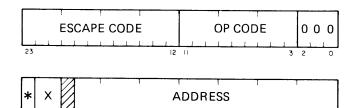

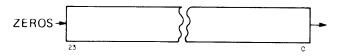

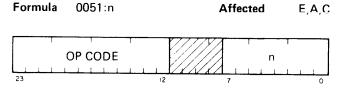

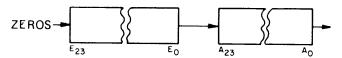

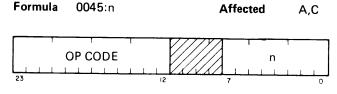

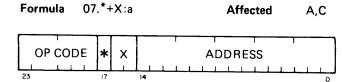

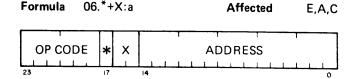

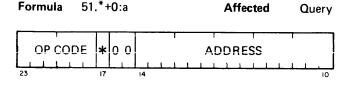

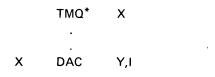

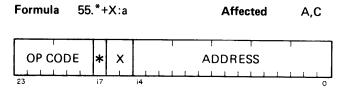

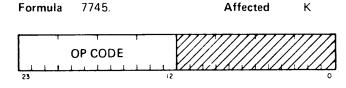

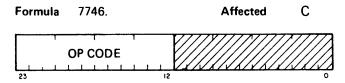

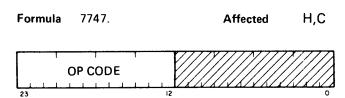

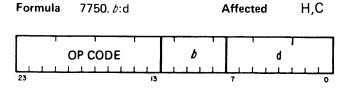

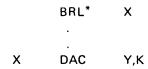

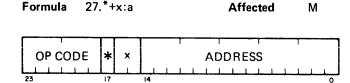

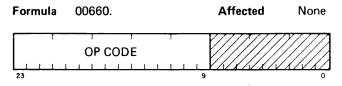

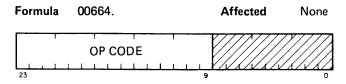

#### Virtual Memory Instruction Set