# **HONEYWELL**

66/DPS, 68/DPS & DPS 8

DATANET

6641/6651/6661/6678

OPERATION

# 66/DPS, 68/DPS & DPS 8

# DATANET 6641/6651/6661/6678 OPERATION ADDENDUM B

# **SUBJECT**

Changes and Corrections to the Manual

#### SPECIAL INSTRUCTIONS

This is the second addendum to AY34, Revision 2, dated May 1980. Insert the attached pages according to the collating instructions on the back of this cover. Change bars in the margins indicate technical changes and additions. These changes will be incorporated into the next revision of the manual.

# Note:

Insert this cover behind the manual cover to indicate the updating of the manual with Addendum B.

ORDER NUMBER

AY34-02B

June 1981

31624 1.8681 Printed in U.S.A.

Honeywell

# **COLLATING INSTRUCTIONS**

To update this manual, remove old pages and insert new pages as follows:

| Remove                   | Insert                   |

|--------------------------|--------------------------|

| 1-1, 1-2 $\sqrt{/}$      | 1-1, 1-2 $^{\checkmark}$ |

| 1-3, 1-4 <sup>-/</sup> / | 1-3, 1-4                 |

| 3-17, 3-18 <sup>1</sup>  | 3-17, 3-18               |

| C-5. C-6                 | C-5 C-6                  |

# **Contents**

| Section 1. System Description      |      |                                           | 2-14 |

|------------------------------------|------|-------------------------------------------|------|

| System Components                  | 1-1  | Control Panel                             | 2-15 |

| Central Processor                  | 1-2  | Mechanical Adjustments                    | 2-16 |

| Memory                             | 1-2  | Operation                                 | 2-17 |

| Cache Memory                       | 1-2  | Applying Power                            | 2-17 |

| Page Control Logic Unit (PCLU)     | 1-2  | Removing Power                            | 2-17 |

| System Bus                         | 1-3  | Forms Loading                             | 2-17 |

| Input/Output Multiplexer (IOM)     | 1-4  | Ribbon Cartridge Replacement              | 2-18 |

| I/O Bus                            | 1-4  | Print Test                                | 2-19 |

| Peripheral Interface Adapter (PIA) | 1-4  | Operator Maintenance                      | 2-20 |

| System Support Controller (SSC)    | 1-4  | Diskette Unit                             | 2-20 |

| Direct Interface Adapter (DIA)     | 1-4  | Controls                                  | 2-20 |

| Channel Interface Base (CIB)/      |      | Operation                                 | 2-20 |

| General Purpose Communication      |      | Applying Power                            | 2-20 |

| Base (GPCB)                        | 1-4  | Removing Power                            | 2-20 |

| System Software                    | 1-5  | Diskette Unit Loading                     | 2-21 |

| Built-in Tests                     | 1-5  | Diskette Unit Unloading                   | 2-21 |

|                                    |      | Operator Maintenance                      | 2-21 |

| Section 2. System Operation        |      | Care and Handling of Diskette             | 2-21 |

| Power Distribution Unit            | 2-1  | Power Up/Power Down/System Initialization |      |

| Control                            | 2-1  | Procedures                                | 2-22 |

| Central Processor Control Panel    | 2-1  | Initial Power Up Procedure                | 2-22 |

| Register Display                   | 2-3  | Complete Power Down Procedure             | 2-22 |

| Octal/Hex Keypad                   | 2-3  | Normal Power Up Procedure                 | 2-22 |

| Power Switch                       | 2-3  | Normal Power Down Procedure               | 2-23 |

| Panel Security Keylock Switch      | 2-3  | System Initialization Procedure           | 2-23 |

| Indicators                         | 2-3  |                                           |      |

| Push Buttons                       | 2-3  | Section 3. Fault Isolation and            |      |

| Operation                          | 2-4  | Diagnostics                               |      |

| Trap Mode                          | 2-4  | Initial Fault Analysis                    | 3-1  |

| Display Memory                     | 2-5  | Quality Logic Tests                       | 3-2  |

| Change Memory                      | 2-7  | QLT Operating Procedures                  | 3-3  |

| Display Registers                  | 2-7  | Accessing and Checking Boards             | 3-3  |

| Change Registers                   | 2-8  | Extended QLTs                             | 3-6  |

| Stop Program Execution             | 2-8  | Operating Procedures                      | 3-7  |

| Execute Single Instruction(s)      | 2-8  | T&D Guidelines                            | 3-7  |

| Turn On Elapsed Timer              | 2-9  | DATANET Offline Tests                     | 3-8  |

| Turn Off Elapsed Timer             | 2-9  | Loading Procedures                        | 3-11 |

| Check Timer Operation              | 2-9  | Operating Procedures                      | 3-12 |

| Basic Console                      | 2-9  | T&D Options                               | 3-23 |

| Controls                           | 2-9  | END OF MESSAGE (CARRIAGE                  |      |

| Keyboard                           | 2-9  | RETURN on Teleprinter)                    | 3-23 |

| Control Keys                       | 2-10 | ATYPE, APRINT                             | 3-23 |

| Autoshutdown                       | 2-11 | ALTER XXXXX                               | 3-23 |

| Operation                          | 2-11 | BYPASS                                    | 3-24 |

| Applying Power                     | 2-11 | CONFIG                                    | 3-24 |

| Removing Power                     | 2-11 | DELETE                                    | 3-25 |

| Paper Loading                      | 2-11 | DUMP                                      | 3-25 |

| Ribbon Replacement                 | 2-12 | HALT                                      | 3-25 |

| Operator Maintenance               | 2-13 | HOLD xx                                   | 3-25 |

| Heavy-Duty Console                 | 2-13 | LOOP/NO LOOP                              | 3-25 |

| Controls and Indicators            |      | ODUMP (BOS Only)                          | 3-25 |

|                                    | 2-14 | PDUMP (BOS Only)                          | 3-25 |

iii AY34

| PRG xx                             | 3-25         | [                      | Test End Request                                                    | 3-4]         |

|------------------------------------|--------------|------------------------|---------------------------------------------------------------------|--------------|

| PRINT                              | 3-25         | 5                      | Standard Test Options                                               | 3-4]         |

| PTAL/RTAL                          | 3-25         |                        | Special Test Options                                                | 3-42         |

| RESET                              | 3-26         | (                      | Common Control Mnemonics                                            | 3-42         |

| RUN                                | 3-26         |                        | Special Control Mnemonics                                           | 3-43         |

|                                    |              |                        |                                                                     |              |

| SEQ (BOS Only)                     | 3-26         | nonty                  | ying the Response Center                                            | 3-43         |

| SKIP/NOSKIP                        | 3-26         |                        |                                                                     |              |

| SLOOP/NSLOOP                       | 3-26         |                        | ndix A. System Configuration                                        |              |

| SNAP/NOSNAP                        | 3-26         | ]                      | Form                                                                |              |

| START                              | 3-26         |                        |                                                                     |              |

| TEST xx                            | 3-26         | Appe                   | ndix B. Channel Fault Status Bit                                    |              |

|                                    | 3-26         |                        | Definitions                                                         |              |

| TRA xxxxx                          |              | ,                      | Deminions                                                           |              |

| TYPE/PRINT                         | 3-26         |                        |                                                                     |              |

| Dumps                              | 3-27         |                        | ndix C. Programming                                                 |              |

| XDUMP XXXXX YYYYY                  | 3-27         |                        | Considerations                                                      |              |

| Errors                             | 3-27         | CPI L                  | I/O Conflict on DN66                                                | C-1          |

| PAS Standard Error Message         | 3-27         |                        |                                                                     |              |

|                                    | 0-21         | MISULU                 | ction Counter during Faults                                         | C-1          |

| PAS Unexpected Fault Error         | 0.00         | New I                  | Instructions                                                        | C-1          |

| Message                            | 3-28         |                        | T&D Instructions                                                    | C-1          |

| PAS Abbreviated Error Message      | 3-28         | $\mathbf{C}\mathbf{A}$ | QC — Copy Accumulator and                                           |              |

| IDS Standard Error Message         | 3-28         |                        | Quotient to Channel 533200 <sub>8</sub>                             | C-1          |

| Explanation of IOS Standard Error  |              | 9                      | Summary                                                             |              |

| Printout                           | 3-28         | Ĭ                      |                                                                     | C-2          |

| Additional IOS Error Messages      | 3-30         |                        |                                                                     | <b>U-Z</b>   |

| Additional IOS Error Messages      |              |                        | Q — Copy Channel to Quotient                                        | ~ ~          |

| Nonstandard Errors                 | 3-30         |                        | $(533300_8)$                                                        | C-2          |

| Extra Interrupt                    |              | 5                      | Summary                                                             | C-2          |

| Too Many Options                   | . 3-31       | I                      | ndicators                                                           | C-2          |

| Halts in DIS Instruction           | 3-31         |                        | A — Copy Register to A                                              |              |

| L/P Trouble                        | 3-31         | 0.20                   | ·                                                                   | C-2          |

| Partial Online (POL) Tests         |              | CA                     |                                                                     | C-Z          |

| Leading Durandaman                 | 0-01         | CA                     | R — Copy A to Register                                              | ~ ~          |

| Loading Procedures                 | 3-31         |                        | ` '                                                                 | C-2          |

| Operating Procedures               | 3-32         | S                      |                                                                     | C-2          |

| Restrictions/Limitations           | 3-32         | Page A                 |                                                                     | C-3          |

| Bootloading                        | 3-36         | PIĂ B                  |                                                                     | C-4          |

| Normal Execution                   | 3-36         | РΙΔ Т                  |                                                                     | C-4          |

| Program Input                      | 3-36         | Abaol                  | uto Addressing                                                      |              |

|                                    | 3-36         | Absor                  |                                                                     | C-4          |

| Communication with the FNP         |              | Store                  |                                                                     | C-4          |

| POL Offline T&D (Monitor)          | 3-36         | Initial                |                                                                     | C-4          |

| 3BT Operator Interface             | 3-36         | Option                 | nal ASYNC Baud Rates and                                            |              |

| Execution Sequence of Primitive,   |              |                        |                                                                     | C-5          |

| Loader, I/O Package and            |              |                        | Generation for Communication                                        | 0 0          |

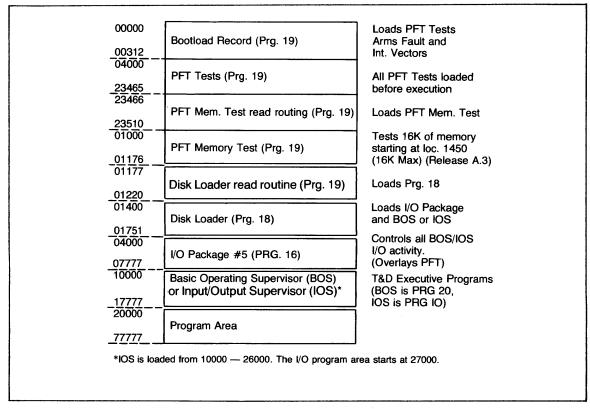

| Executive                          | 3-37         | -                      |                                                                     | 0 =          |

|                                    |              |                        |                                                                     | C-5          |

| Interface Sequence (FNP Initiated) | 3-38         |                        |                                                                     | C-5          |

| Write To/Read From L66 Console and |              |                        | from ASYNC Terminals                                                | C-5          |

| Print Operations                   | 3-38         | Last C                 | Communications Character                                            |              |

| Interface Sequence (L66 Initiated) | 3-38         | Т                      | Transmission                                                        | C-6          |

| Options Request at L66 Console     | 3-38         | Subch                  |                                                                     | C-6          |

| Communications Online Testing      | 0-00         | Auto                   | - · · · · · · · · · · · · · · · · · · ·                             |              |

|                                    | 0.00         | Auto .                 | baud Detection (154.5 Baud)                                         | C-6          |

| System (COLTS)                     | 3-39         |                        |                                                                     |              |

| Loading Procedures                 | 3-39         |                        | <b>77.</b>                                                          |              |

| Operating Procedures               | 3-39         |                        | Figu                                                                | ıres         |

| HMLC Subchannel Wraparound         | 3-39         |                        |                                                                     |              |

| IOM Channel Adapters               | 3-39         | 1-1                    | DATANET Network Processor                                           | 1-1          |

| Keyboard Type Devices              | 3-39         | 1-2                    | DATANET System Components                                           | 1-3          |

|                                    |              |                        |                                                                     |              |

| VIP/TTY Devices                    | 3-39         | 2-1                    | DATANET Rack Layout                                                 | 2-2          |

| VIP Direct Access Log-On           |              | 2-2                    | DATANET Control Panel                                               | 2-2          |

| Procedure                          | 3-39         | 2-3                    | Basic Console                                                       | 2-10         |

| TTY Direct Access Log-On           |              | 2-4                    | Keyboard Layout                                                     | 2-10         |

| 1 1 1 Direct fleecost nog on       |              |                        | iio, soura Bu, out                                                  |              |

|                                    | 3-40         |                        |                                                                     | 2-19         |

| Procedure                          | 3-40<br>3-40 | 2-5                    | Installation of Paper Roll                                          | 2-12<br>2-13 |

| Procedure                          | 3-40         | 2-5<br>2-6             | Installation of Paper Roll Ribbon Installation                      | 2-13         |

| Procedure                          | 3-40<br>3-40 | 2-5<br>2-6<br>2-7      | Installation of Paper Roll  Ribbon Installation  Heavy-Duty Console | 2-13<br>2-14 |

| Procedure                          | 3-40         | 2-5<br>2-6             | Installation of Paper Roll                                          | 2-13         |

iv AY34

| 2-10 | Paper Positioning Controls      | 2-16       | 3-16 | I/O T&D (PRG M2) Console        |      |

|------|---------------------------------|------------|------|---------------------------------|------|

| 2-11 | Paper Loading                   | 2-18       |      | Printout                        | 3-21 |

| 2-12 | Ribbon Cartridge Replacement    | 2-19       | 3-17 | Console Typeout for Multi       |      |

| 2-13 | Diskette Media Handling         | 2-21       |      | I/O T&D MI                      | 3-22 |

| 3-1  | Fault Isolation Overview        | 3-1        | 3-18 | DN66 T&D Memory Map             | 3-22 |

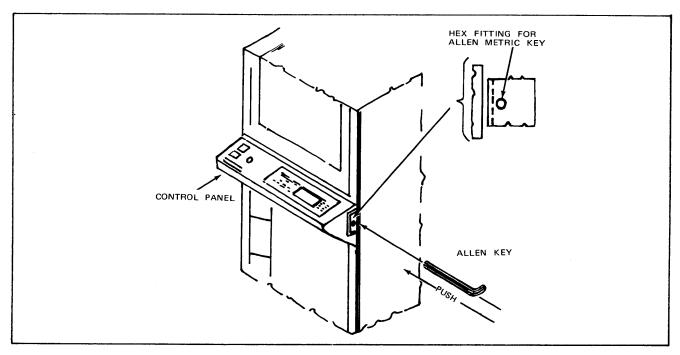

| 3-2  | Opening Control Panel           | <b>3-4</b> | 3-19 | Example of Host Console         |      |

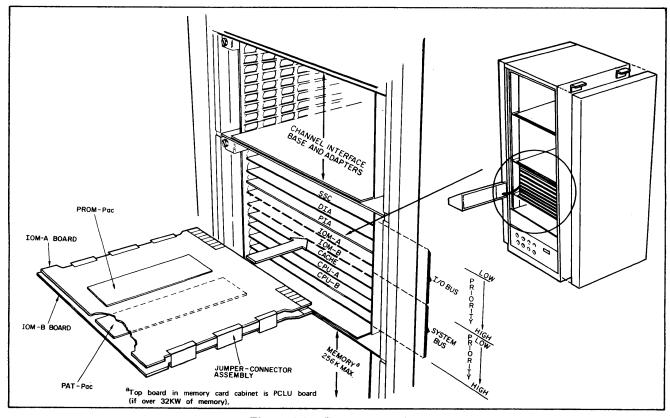

| 3-3  | Board Locations                 | 3-4        |      | Typeout for POL T&D IOS         | 3-32 |

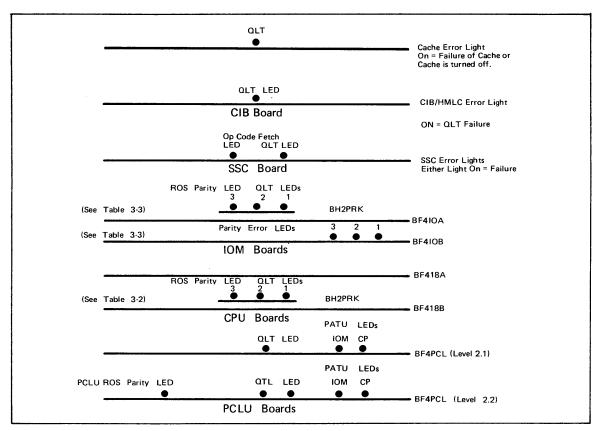

| 3-4  | QLT and Error LED Locations     | 3-5        | 3-20 | Example of Host Console Typeout |      |

| 3-5  | T&D Overview                    | 3-8        |      | for POL T&D BOS                 | 3-34 |

| 3-6  | BOS Console Typeout Including   |            | 3-21 | Example of Host Console Typeout |      |

|      | Cache PRG 80                    | 3-13       |      | for POL T&Ds 80 (Cache)         |      |

| 3-7  | Memory T&S 86 Testing 64K       |            |      | and 86 (Memory)                 |      |

|      | Memory                          | 3-14       | C-1  | Subchannel ID Codes             | C-6  |

| 3-8  | Console Typeout for Console T&D |            |      |                                 |      |

|      | CO                              | 3-15       |      | 75                              |      |

| 3-9  | Console Typeout for DIA T&D,    |            |      | Ta                              | bles |

|      | DA and DI                       | 3-16       |      |                                 |      |

| 3-10 | Console Typeout for EIA-HMLC    |            | 2-1  | Summary of Control Panel        |      |

|      | T&Ds H1-H4                      | 3-17       |      | Operations                      | 2-6  |

| 3-11 | Console Typeout for T&D H1 with |            | 2-2  | Multicopy Adjustment Level      |      |

|      | Active Channel Table Printed    |            | 3-1  | QLT Fault Table                 |      |

|      | Out                             | 3-18       | 3-2  | CP Error Light Combinations     | 3-5  |

| 3-12 | Console Typeout for BSC-HMLC    |            | 3-3  | IOM Error Light Combinations    | 3-5  |

|      | T&Ds HA, HB, H5, H6             | 3-19       | 3-4  | PCLU Error Light                |      |

| 3-13 | Console Printouts for HMLC-HDLC |            |      | Combinations                    | 3-6  |

|      | T&Ds H7-H9                      | 3-20       | 3-5  | DATANET Offline Test &          |      |

| 3-14 | Console Typeout for Extended    |            |      | Diagnostic Programs             |      |

|      | Addressing T&D EA               | 3-21       | 3-6  | DN66 Configuration Chart        | 3-18 |

| 3-15 | Console Typeout for Diskette    |            | B-1  | Channel Fault Status Bit        |      |

|      | T&D KD                          | 3-21       |      | Definitions                     | B-1  |

V

AY34

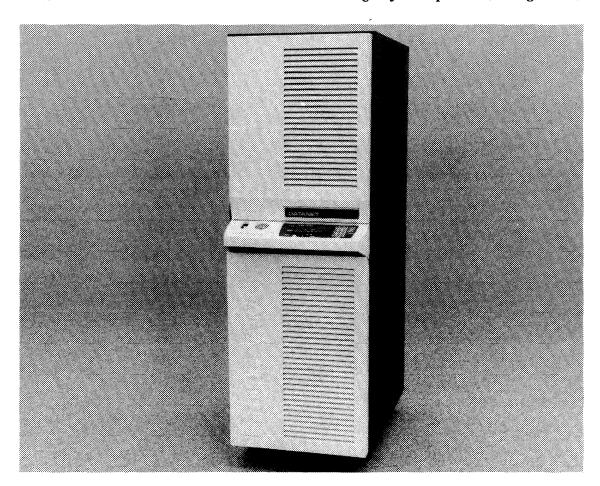

The DATANET Network Processor encompasses a whole family of compact, powerful network processors which can provide Honeywell 66/DPS, 68/DPS and DPS 8 systems with large-volume network communications power. Based on Honeywell's minicomputer technology for reduced space, greater reliability, and easier serviceability, the DATANET is logically compatible with the system software and user-generated programs of the DATANET 6600 family of network processors (see Figure 1-1).

The DATANET provides the variety of interfaces required by the elements and protocols of a distributed system, as well as a facility for dialog with the central system. By performing the tasks of message management and message handling, the processor relieves the central system for other processing functions. The resources of the central system are called upon only when the message is submitted for information processing. However, some networking functions (e.g., a message switch) can be accommodated by the processor without any involvement of the host processor.

#### SYSTEM COMPONENTS

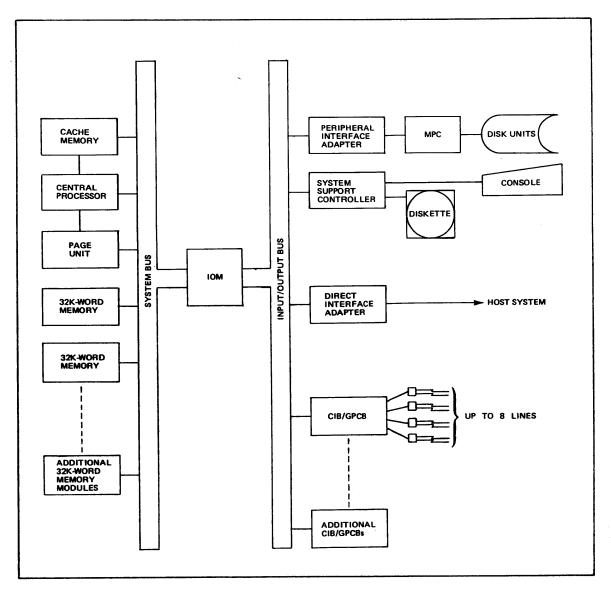

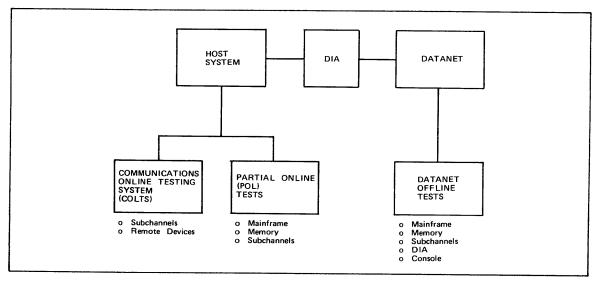

The DATANET consists of combinations of the following major components (see Figure 1-2):

Figure 1-1. DATANET Network Processor

- Central Processor

- Memory

- Cache Memory (if present)

- Page Unit (if present)

- System Bus

- Input/Output Multiplexer

- I/O Bus

- Peripheral Interface Adapter (if present)

- System Support Controller

- Direct Interface Adapter

- Channel Interface Base (CIB)/General Purpose Communication Base (GPCB)

#### CENTRAL PROCESSOR

The central processing unit is a solid-state, interrupt-driven, 18-bit machine operating asynchronously under firmware control. Its instruction repertoire is designed for efficient processing of a wide variety of communication network applications and is fully upward-compatible with the instruction sets of other Level 66 or Level 68 network processors. The processor design accommodates a high-speed cache memory which, together with the appropriate configuration and optimum instruction mix, provides an execution rate of up to 1,000,000 instructions per second — nearly double that of other DATANETs.

Standard features include a flexible bus structure, power failure/automatic restart, EDAC (Error Detection and Correction) memory, processor faults (internal interrupts), program interrupts (external interrupts), a real-time clock, and a watchdog timer.

#### **MEMORY**

The high-speed, random access, semiconductor memory subsystem performs all storage functions without restrictions on address sequences, data patterns, or repetition rates. Memory features include single- and double-fetch, self-contained initialize and refresh logic, and standard EDAC functionality. The DATANET may be configured with up to 256K words maximum.

#### **CACHE MEMORY**

The cache memory (if present) provides intermediate high-speed storage, which improves the performance of the central processor unit by decreasing the time required to receive (i.e., fetch) instructions and data from main memory. This decrease in time is achieved both by anticipatory main memory reads and by storage of previously used data and instructions for future iterations of the currently executing program.

The cache memory contains copies of selected (recently referenced) memory locations. It has a system bus interface which allows it to make memory read references on behalf of the central processor unit and to monitor the system bus, copying main memory write data if it currently contains a copy of the location addressed. The cache memory also has a private interface allowing it to communicate with the central processor unit to which it is dedicated. It receives memory read requests across this interface, thereby becoming committed to locate the data for the central processor unit in its local cache array or in main memory. In either case, the requested data is delivered to the CP for processing. The cache memory overlaps its read requests to main memory and is invisible to software.

# PAGE CONTROL LOGIC UNIT (PCLU)

The PCLU (if present) enhances the DATANET system by providing a mechanism for memory protection and for accessing over 64K bytes of memory. The PCLU uses software-generated page address tables to expand a 15-bit (16K-byte) CP program address into an 18-bit 512K-byte) absolute address. The tables are also used to determine the access rights assigned each 256-location (page) of memory.

Figure 1-2. DATANET System Components

#### SYSTEM BUS

The system bus allows communication between the CP, memory, and the input/output multiplexer. The system bus is bidirectional, permitting any two units to communicate with each other at a given time. The transfer of information between units forms a master/slave relationship (i.e., the unit requesting and receiving access to the bus becomes the master; the unit being addressed by the master becomes the slave). If the communication requires a response, the responding slave unit assumes the role of master and the requesting unit (previous master) becomes the slave.

All information transfers are from master to slave and each transfer is referred to as a bus cycle. This cycle is the period of time in which the requester (master) asks for use of the bus. If no other unit of a higher priority is making a bus request, use of the bus is granted to the requester (master). The master then transmits its information to the slave and the slave acknowledges the communication.

Communication between a master and slave requires a response from the slave when the slave is transferring data (e.g., a memory read command). In this case, the request for information requires one bus cycle and the transmission of information back to the requester requires an additional bus cycle to complete the task.

The granting of time on the bus is done on a priority basis. If two components on the bus simultaneously request time, the one with the higher priority will be granted the time. This priority is determined by the physical position of the component on the bus. On the system bus, the lower the physical position, the higher the priority. The priority is established relative to the rate at which the components transfer and/or receive data.

#### **INPUT/OUTPUT MULTIPLEXER (IOM)**

The IOM performs all operations required for the transfer of data between input/output devices and the DATANET memory. The advanced technology of the DATANET gives it a transfer rate of 2,000,000 bytes per second. The IOM is the interface between the system bus (to processor and memory) and the I/O bus (to which the various I/O devices are connected). Attached to the I/O bus are the System Support Controller for the console and diskette; the Direct Interface Adapter (DIA), which provides connection to the central system; the Channel Interface Bases/General Purpose Communication Bases, through which the network devices enter the system; and the Peripheral Interface Adapter (PIA), which provides connection to the central system's mass storage processor. Internally, the IOM operates asynchronously in an interrupt-driven fashion.

#### I/O BUS

The I/O bus is basically the same as the system bus, differing only in the units that interface on the bus and the operations that take place between the units.

The I/O bus allows communication between the I/O controllers and adapters to the system through the IOM. Operations on the I/O bus are initiated by the IOM or DIA, depending on the activity that is required.

The components on the bus are positioned relative to their priority. The highest priority component is placed at the bottom of the I/O bus next to the IOM; the lowest priority component is placed at the top of the I/O bus farthest from the IOM. The I/O bus is at the top of the chassis; the system bus is at the bottom of the chassis.

#### PERIPHERAL INTERFACE ADAPTER (PIA)

The PIA, which is an option, provides the interface between the DATANET input/output bus and the central system's mass storage processor. Up to two PIAs can be installed in a system; however, the software will utilize only one PIA. The PIA provides the disk access required by the NPS (Network Processing Supervisor) software.

#### SYSTEM SUPPORT CONTROLLER (SSC)

The SSC is a peripheral controller for the console and diskette. The console is used to control and monitor DATANET activity. The diskette unit is used to load the system offline test and diagnostics (T&Ds).

#### **DIRECT INTERFACE ADAPTER (DIA)**

The DIA provides the interface between the DATANET input/output bus and the Level 66 or 68 host system for the transfer of data and control information. The DATANET controls all transactions and normal data transfer activities through the DIA except for "initiate bootload" or program interrupts from the central system. A second DIA can be installed in a system; however, the software will utilize only one DIA.

#### CHANNEL INTERFACE BASE (CIB)/GENERAL PURPOSE COMMUNICATION BASE (GPCB)

The CIB/GPCB enables low-, medium-, and high-speed data communications terminals and subsystems operating at data transfer rates of up to 72,000 bits per second to be connected to the system. Combinations of half-duplex and full-duplex transmission modes, as well as synchronous and asynchronous transmissions, are supported. The CIB/GPCB provides the line interfacing arrangements necessary to accommodate terminals with various transfer rates, bit orders, bits per character, information codes, character sets, message formats, and communica-

tions control procedures. The CIB/GPCB enables the connection of up to eight communications lines depending upon the functions required. Additional CIB/GPCBs can be configured.

The CIB/GPCB accepts up to 4 (or up to 2 double-size) communications adapters in any combination. A dual channel can connect two lines. The various communications adapters are as follows:

- 20 mA Current Loop dual

- RS-232-C Synchronous dual

- RS-232-C Asynchronous dual

- Automatic Call Unit dual

- MIL-STD-188C broadband

- MIL-STD-188C synchronous

- MIL-STD-188C asynchronous, dual

- MIL-STD-188C HDLC

- Bisynchronous dual

- Broadband

- Broadband CCITT-V.35

- HDLC voicegrade

- Bisynchronous broadband

- Broadband HDLC

- HDLC CCITT-V.35

- Direct Connect asynchronous

- Direct Connect synchronous

#### Note:

Direct connect capability is via cable.

#### SYSTEM SOFTWARE

Either the Remote Terminal Supervisor (GRTS I/3I; GRTS II Rel. 1) or the Network Processing Supervisor (NPS), Release NT2 (or greater), depending upon network requirements, can control the operation of the DATANET Network Processor and provide a software interface to the central system. GRTS I/II is a high-performance, low-overhead system for users who do not need the full networking capabilities of NPS. Both systems support remote job entry, message concentration, transaction processing, and time sharing dimensions. NPS offers completely unique device control parameterization facilities and other outstanding customization features. By utilizing a DATANET Network Processor channel to the central system's mass storage processor, NPS can provide journalization and message switching capabilities.

# **BUILT-IN TESTS**

A portion of the firmware on the CP, memories, IOM, Channel Interface Bases, and System Support Controller boards is reserved for two types of hardware verification routines called Quality Logic Tests (QLTs) and Extended QLTs (E-QLTs). Their purpose is to verify basic data paths and to provide a go/no-go visual identification of a hardware failure

The QLTs are automatically executed as part of the normal system initialization procedure. Unsuccessful completion of any QLT turns on the CHECK indicator on the CP control panel and an LED (light-emitting diode) indicator on the specific board failing the QLT. (Access to QLT indicators on the boards is described in Section 3.) The QLTs do not affect memory or programmable registers. The QLTs will truncate the most significant bit of the Instruction Counter (A0); however, its true value will be shown in the hex display before truncation. The operator should make note of A0 after the QLTs. In addition, on the

Channel Interface Base boards, each of the eight lines has program-usable loop-back of data transmit to data receive to facilitate diagnosis.

The Extended QLTs are executed under the guidelines described in Section 3. The E-QLTs provide greater checking capability than the QLTs in that the E-QLTs allow communications between various system components in their testing scheme. However, since E-QLTs destroy memory and register contents, a dump should be taken first. Instead of an LED lighting on a specific board (as with the QLTs), the control panel display is used. Its interpretation dictates the action to be taken.

AY34

# Section 2

# System Operation

DATANET Network Processor operation is controlled by the software except for occasional operator interventions. The operator duties and responsibilities in regard to the DATANET system are normally governed by the rules and regulations in effect for the Series 60 Level 66 or Level 68 system on the site. All subsystem maintenance required on the equipment is performed by the Honeywell Field Engineer, except routine site cleaning which is the responsibility of the operating personnel. The operator is also required to execute the E-QLTs and to load and run the system test and diagnostic programs. These procedures are explained in Section 3.

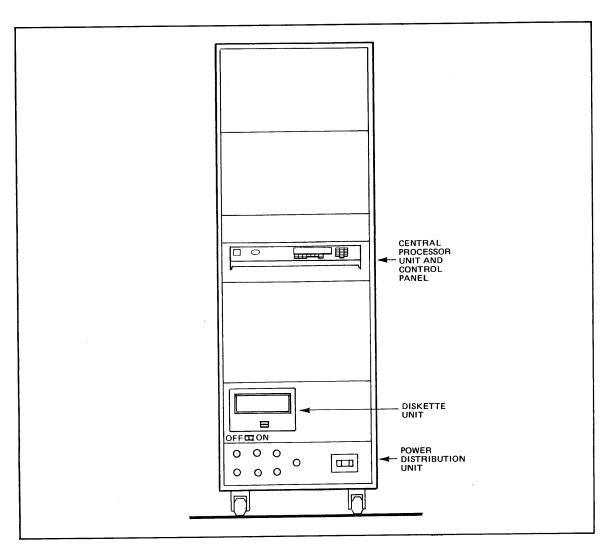

To operate the DATANET, the operator must know how to operate the following controls and equipment (see Figure 2-1):

- Power Distribution Unit

- Central Processor Control Panel

- Console (Basic or Heavy-Duty)

- Diskette Unit

It is also the operator's responsibility to routinely do the following:

- Power up the system

- Initialize the system

- Power down the system

#### **POWER DISTRIBUTION UNIT**

For the system to operate, all power supplies and the Power Distribution Unit (PDU) must be turned on.

Power is applied to the system in the following order:

- 1. Power Distribution Unit

- 2. Central Processor Unit

- 3. Peripherals (Console and Diskette Unit)

The PDU is located in the bottom of the rack (see Figure 2-1).

#### CONTROL

ON/OFF Switch

The operator must set the PDU ON/OFF switch to the ON position. This action must be taken before power is applied to the central processor.

# **CENTRAL PROCESSOR CONTROL PANEL**

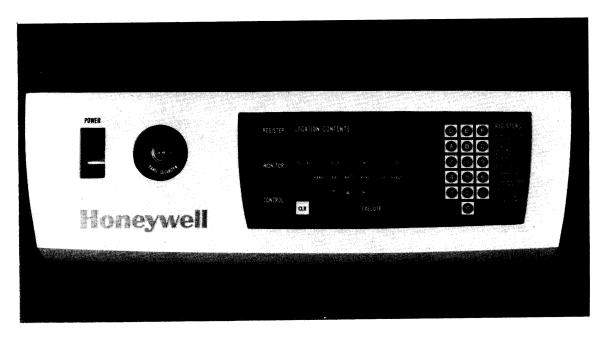

The DATANET has a control panel that provides for the following (see Figures 2-1 and 2-2):

- Powering up and initializing the system

- Starting and stopping the CP

- Entering and displaying registers/memory information

- Single stepping a program

- Bootloading a program

- Master clearing the system

- Indicating CP status

Figure 2-1. DATANET Rack Layout

Figure 2-2. DATANET Control Panel

#### REGISTER DISPLAY

The register display is divided into two sections — one labeled LOCATION and the other CONTENTS.

- LOCATION A 2-digit display which indicates the specific CP register selected. The display consists of a left hexadecimal digit indicator and a right octal digit indicator.

- CONTENTS A 6-digit octal display which indicates the contents of the selected register.

#### OCTAL/HEX KEYPAD

The octal/hex keypad consists of 16 keys and is divided into two groups — an octal digit key cluster and a hex alphabetic key cluster.

- Octal Digit Key Cluster The digits 0-7 are used to enter address or data into the CONTENTS and LOCATION displays.

- Hex Alphabetic Key Cluster The digits 8-F are used to enter digits into the LOCA-TION display.

#### **POWER SWITCH**

The power switch is used to apply or remove ac power to or from the system. In the up position, power is on; in the down position, power is off.

#### PANEL SECURITY KEYLOCK SWITCH

The left (locked) position disables panel switches and push-buttons except for POWER. The right (unlocked) position enables panel switches and push buttons.

#### **INDICATORS**

INT

The indicators are long-life, light-emitting diodes (LEDs).

DC ON Indicates that dc power is applied to the system.

CHECK Indicates that the system is performing or has been unable to successfully complete its QLTs after a system initialization.

Indicates that the control panel interrupt is active. If indicator stays lit, the system is in a "hung" or non-interruptible "fault" state. (Refer

to "System Initialization Procedure").

CP Indicates that the CP is executing instructions.

CHANGE Indicates that key cluster information may be entered into the CON-

TENTS display.

TRAP Indicates that the CP is in the trap mode.

WRITE Indicates that the CP is in the write mode.

READ Indicates that the CP is in the read mode.

STOP/STEP Indicates that the CP is in the stop mode.

**READY** Indicates that the CP is in the ready mode.

#### **PUSH BUTTONS**

CLR Press to initialize the system.

(Master Clear)

S Press to allow key cluster information to be entered into the LOCATION

(Select) display.

C Press to allow key cluster information to be entered into the

(Change) CONTENTS display.

Т Press to place the CP in a constant panel interrupt mode after every (Trap) interruptible instruction to allow the CP to stop for a variety of

predetermined comparisons.

Note:

Not for normal operator use; for reference purposes only.

W Press to place the CP in the write mode so that CONTENTS informa-

(Write) tion is written into CP registers or into main memory.

Press to place the CP in the read mode so that the contents of the CP R (Read)

registers or main memory are read and displayed in the CONTENTS

display.

Press to remove the CP from the run, ready, write, or read mode and

(Stop/Step) place it into the stop mode.

R Press to place the CP in the ready mode.

(Run)

$\mathbf{E}$ Press to place the CP in the run mode, allowing it to execute instruc-

(Execute) tions and interrupts according to its internal state.

#### **OPERATION**

The functions that can be performed from the control panel are: displaying/changing memory. displaying/changing registers, executing single instructions, restarting programs, and master clearing the processor. Before any operation is performed from the control panel (except for powering up/down), it must first be unlocked using the panel security key.

Table 2-1 lists the various operations that can be performed via the operator control panel. The table lists the five operating modes, all the DATANET registers that an operator can select, and the resulting operation that can be performed.

#### TRAP MODE

Trap mode is a special mode which enables the field engineer or a programmer to stop on an address or a data pattern.

It is possible to trap on a special value of the instruction counter, index register 1, 2, or 3, A register, Q register, indicator register or a given value at location "X" in memory.

When the specified condition is met the CP will go into stop mode. However, if an interrupt occurs, the CP (if not in inhibited mode) will continue operation.

#### CAUTION

Trap mode causes the DATANET system to run 10 times slower, and heavily loaded systems may cause other unknown problems.

#### **Examples:**

Instruction Counter: stop if IC=001000 Select A0, change, 001000, trap, execute.

Index Register: stop if X = 001000

Select A1 (respectively A2, A3), change, 001000, trap, execute.

A Register, Q Register, Indicator Register: stop if \_\_ Select A4 (respectively A5, A6) change, 001000, trap, execute.

Main Memory: stop if location 000100=123456 Select Co, change, 000100, write, execute. Select C1, change, 123456, trap, execute.

#### **Notes:**

- 1. If running a program and compare is made the STOP/STEP LED will come on.

- 2. When the CP is in stop mode, if an interrupt comes along it could send the CP into run mode again.

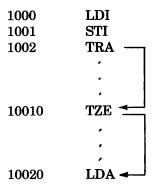

- 3. CP can only compare addresses between interruptible instruction. For example:

Any attempt to trap on instruction counter=10010 will fail because all the above instructions except LDA are non-interruptible. Conversely, if the LDI was loading the indictors with the "compared" value, the CP would stop only at the end of the LDA at 10020 and the instruction counter would indicate 10021 because it would be the first interruptible instruction where the condition is met.

#### **DISPLAY MEMORY**

Any memory location may be accessed and displayed from the control panel by entering the memory address to be accessed into register C0 (actually memory location 000634) and then reading or writing that location by selecting C1. Sequential memory locations can be read or written by selecting C2 instead of C1 for incrementing memory locations, or C3 for decrementing memory locations.

- 1. Press Select.

- 2. Press octal/hex-pad keys C0. This enters the 2-digit selection code for the memory address register.

- 3. Press Change. This places the processor in change mode preparatory to keying in the address of the memory location to be displayed. The CHANGE indicator lights when the Change control key is pressed.

- 4. Key in, via the octal hex-pad keys, the 6-digit octal value representing the address of the memory location to be read. This address appears in the CONTENTS field of the REGISTER display.

- 5. Press Write.

- 6. Press Execute.

- 7. Press Select.

- 8. Key in, via the octal/hex-pad keys, the 2-digit selection code for the desired memory data register (C1, C2, C3, C4, C5, C6, or C7).

- 9. Press Read.

TABLE 2-1. SUMMARY OF CONTROL PANEL OPERATIONS

| Mode  | Regis<br>(hex)     | ter<br>(octal)                       | Operation                                                                                                                                                                              |

|-------|--------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP  | B<br>A, C,<br>or D | 0                                    | Bootstrap with timer on Bootstrap with timer off Step submode — executes single instructions with subsequent pressings of Stop key                                                     |

| RUN   |                    |                                      | Run mode                                                                                                                                                                               |

| READ  | A                  | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Read Instruction Counter Read Index Register 1 Read Index Register 2 Read Index Register 3 Read Accumulator Read Quotient Register Read Indicator/Select Register Display parity error |

|       | С                  | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Read "AOR" unpaged Read MM Read MM unpaged AOR + 1 Read MM unpaged AOR - 1 Read "AOR" paged Read MM paged Read MM paged Read MM paged AOR + 1 Read MM paged AOR - 1                    |

| WRITE | A                  | 0<br>1<br>2<br>3<br>4<br>5<br>6      | Write Instruction Counter <sup>a</sup> Write Index Register 1 Write Index Register 2 Write Index Register 3 Write Accumulator Write Quotient Register Write Indicator/Select Register  |

|       | С                  | 0<br>1<br>2<br>3<br>4<br>5<br>6      | Write "AOR" unpaged Write MM unpaged AOR + 1 Write MM unpaged AOR - 1 Write MM unpaged AOR - 1 Write "AOR" paged Write MM paged Write MM paged AOR + 1 Write MM paged AOR - 1          |

|       | D                  | 0<br>1<br>2<br>3                     | Turn timer on Turn timer off <sup>a</sup> Run Extended QLTs <sup>a</sup> Turn Cache off <sup>a,b</sup>                                                                                 |

| TRAP  |                    |                                      | Trap mode                                                                                                                                                                              |

<sup>&</sup>lt;sup>a</sup>Do not perform this operation while running system software.

#### **Notes:**

- 1. The operator should never write into register C4 and then read/write into any of the following registers: C1, C2, C3, C5, C6, or C7. Rather, write into C0, then read C4 for the correspondence between paged and unpaged addresses.

- 2. Memory address register C0 is at times loaded with an invalid memory address by the T&Ds; therefore, never perform a read operation of C0 before writing in a valid memory address; otherwise, an illegal memory operation fault will occur.

- 3. A Master Clear resets the Pager to zero and it is not possible to page again.

<sup>&</sup>lt;sup>b</sup>This operation will also light the CHECK LED.

10. Press Execute. This loads the data contents of the selected memory location into the selected register and displays it in the CONTENTS field of the REGISTER display.

#### Note:

If an increment or decrement memory data register code was entered in step 8, subsequent pressings of the  $\underline{\mathbf{E}}$ xecute key will increment or decrement the display as appropriate.

#### **CHANGE MEMORY**

Any memory location may be accessed and changed from the control panel. As mentioned previously, the memory address register (C0) is the only visible register that can be used to access memory locations from the control panel.

The following procedure describes a method for changing the contents of one memory location and, as an option, changing the contents of subsequent memory locations.

- 1. Press Write. This places the processor in write mode and instructs that the contents of the memory location addressed by the memory address register (C0) are to be changed. The WRITE indicator lights when the Write control key is pressed.

- 2. Press Select. This places the processor in select mode as a necessary preliminary to selecting the memory address register. This step is not necessary unless the CHANGE indicator is lit.

- 3. Press octal/hex keys C0. This enters the 2-digit selection code for the memory address register. Digits C0 appear in the LOCATION field of the REGISTER display.

- 4. Press Change. This places the processor in change mode preparatory to keying in the address of the memory location to be changed. The CHANGE indicator lights when the Change control key is pressed.

- 5. Key in, via the octal/hex keys, the 6-digit octal value representing the address of the memory location to be changed. This address appears in the CONTENTS field of the REGISTER display.

- 6. Press Execute.

- 7. Press Select. This returns the processor to select mode as a necessary preliminary to selecting the memory data register. The CHANGE indicator turns off when the Select control key is pressed.

- 8. Press octal/hex keys. This enters the 2-digit selection code for the memory data register. The digits appear in the LOCATION field of the REGISTER display.

- 9. Press Change. This places the processor in change mode preparatory to keying in the data for the memory location that is to be changed. The CHANGE indicator lights when the Change control key is pressed.

- 10. Key in, via the octal/hex keys, the 6-digit octal value representing the new data that is to be entered into the memory location to be changed. The data entered appears in the CONTENTS field of the REGISTER display.

- 11. Press Execute. This loads the new data contents into the selected memory location.

- 12. If successive memory locations are to be changed, repeat steps 10 and 11 for each sequential memory location to be changed.

#### **DISPLAY REGISTERS**

The contents of any of the visible registers may be displayed on the control panel. A register may be displayed when the processor is in any mode.

The following procedure describes a method for displaying the contents of a register. The same procedure applies regardless of the processor mode.

1. Press Select. This places the processor in select mode as a necessary preliminary to selecting the register to be displayed.

- 2. Key in, via the octal/hex keys, the 2-digit selection code for the desired register to be displayed. The selection code appears in the LOCATION field of the register display.

- 3. Press Read.

- 4. Press Execute. This displays the data contents of the selected register in the CONTENTS field of the REGISTER display.

#### **CHANGE REGISTERS**

The contents of software-visible registers may be changed from the control panel. The following procedure describes a method for changing the contents of a register.

- 1. Press  $\underline{W}$  rite. The WRITE indicator lights when the Write control key is pressed.

- 2. Press Select. This places the processor in the select mode as a necessary preliminary to selecting the register to be changed.

- 3. Key in, via the octal/hex keys, the 2-digit selection code for the desired register to be changed. The selection code appears in the LOCATION field of the REGISTER display.

- 4. Press Change. This places the processor in change mode preparatory to keying in the data to the register that is to be changed. The CHANGE indicator lights when the Change control key is pressed.

- 5. Key in, via the octal/hex keys, the octal value representing the new data that is to be entered into the selected register. The data entered appears in the CONTENTS field of the REGISTER display.

- 6. Press Write.

- 7. Press Execute.

#### STOP PROGRAM EXECUTION

While a program is running, program execution can be stopped at any time by pressing Stop and Execute. The STOP/STEP indicator lights and the RUN, READY, and CP indicators turn off. When this action is initiated, the processor completes the execution of the current instruction and enters the stop mode. After this mode is achieved, the following conditions exist.

- 1. The processor is automatically placed in a step mode (i.e., ready to execute one instruction at a time).

- 2. The instruction counter (A0) contains the instruction to be executed next.

Note that when a program is running and a DIS instruction is encountered (RUN indicator remains lit, but the CP indicator turns off), the processor does *not* enter the stop mode, but rather enters an idle condition. In this condition, the DIS instruction is continuously re-executing and the processor is subject to external interrupts, etc. The <u>S</u>top control key must be pressed in order to set the processor into a stop mode.

# **EXECUTE SINGLE INSTRUCTION(S)**

When running a program, it may be desirable to stop processing and step through the execution of one or more instructions. This procedure is accomplished from the control panel, as follows:

- 1. Press Stop and Execute. (Refer to the previous procedure, "Stop Program Execution," for relevant information concerning processor/panel status after a stop mode is achieved.)

- 2. Determine whether the processor has stopped at a point (address) from which you wish to begin executing single instructions. Display and view the contents of the instruction counter (A0) using the procedure previously described for displaying registers.

At this point memory address register (C0) contains an address incremented by 1 from the address of the instruction to be executed next.

#### **TURN ON ELAPSED TIMER**

- 1. Press Select.

- 2. Key-in, D0.

- 3. Press Write.

- 4. Press Execute. (Timer is now turned on.)

#### TURN OFF ELAPSED TIMER

- 1. Press Select.

- 2. Key-in, D1.

- 3. Press Write.

- 4. Press Execute. (Timer is now turned off.)

#### CHECK TIMER OPERATION

- 1. Press Select.

- 2. Key-in, C0.

- 3. Press Change.

- 4. Key-in, 000451.

- 5. Press Select.

- 6. Press Write.

- 7. Press Execute

- 8. Key-in, C1.

- 9. Press Read.

- 10. Press Execute several times. Note that the display should change each time Execute is pressed. If not, timer is turned off. However, if the timer is not running and has not been turned off (assuming the control panel is operational), either the IOM is hung or a breakdown in communication between the IOM and CP has occurred since the last Master Clear. To determine if the IOM is hung, attempt to turn the timer on twice from the control panel. If the INT indicator does not light after the second Execute, the IOM is not hung.

#### **BASIC CONSOLE**

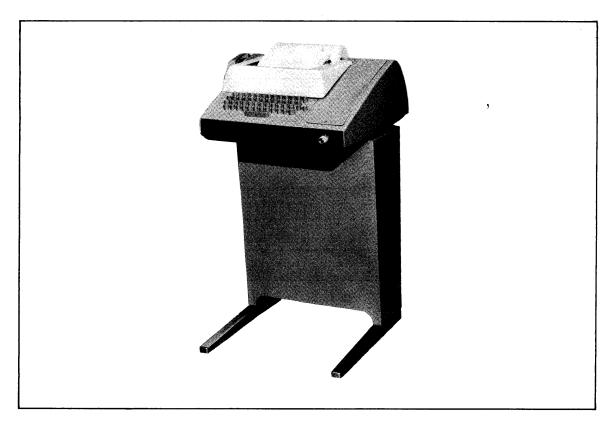

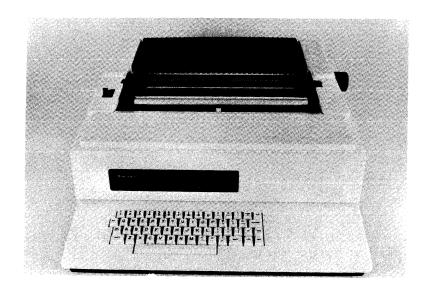

The basic console (see Figure 2-3) has a 64-character ASCII code set, prints at 10 characters per second and has 72 print positions. It uses a paper roll 8.5 in. (21.6 cm) wide and 5 in. (12.7 cm) in diameter. The basic console is also equipped with an automatic shutdown feature which can extend console life and reduce maintenance costs.

#### **CONTROLS**

Console controls are described below.

# **KEYBOARD**

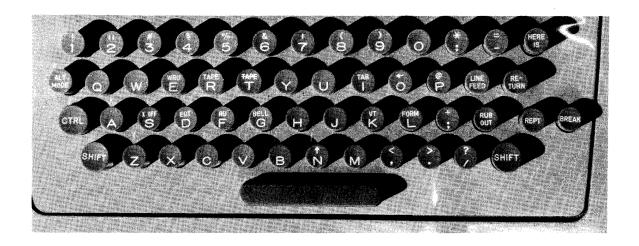

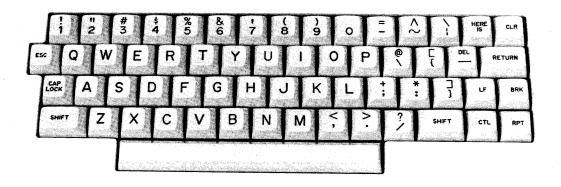

The teleprinter keyboard (see Figure 2-4) is similar to a standard typewriter keyboard. The keys are interlocked so that only correct combinations may be pressed simultaneously. Some of the ASCII keys are inscribed with words such as FORM and EOT for control functions. When a key is pressed, it generates a printable ASCII character.

Figure 2-3. Basic Console

Figure 2-4. Keyboard Layout

# **CONTROLKEYS**

The control keys used for normal teleprinter operation include the following:

LINE/OFF/LOCAL

This switch, located on the right side of the front panel, is the main power switch for the device.

- In the OFF position, the device is disabled.

- In the LINE position, the device is enabled to send to or receive from the central processor in the full-duplex mode.

- In the LOCAL position, the device is offline in the half-duplex mode.

CTRL(Control) Pressing the control key does not generate any code, but allows some

of the keys to generate nonprintable function characters. When CTRL is pressed, inappropriate keys (mostly those having uppercase char-

acters) are locked out.

SHIFT Pressing the SHIFT key causes all the ASCII keys to generate their

associated uppercase characters.

LINE FEED Pressing the LINE FEED key causes the paper to advance vertically.

The carriage does not return to the left margin (see RETURN).

RETURN Pressing the RETURN key generates a carriage return character.

The type unit returns to the left margin but the paper does not advance vertically. The RETURN key should be used with the LINE

FEED key to advance the paper vertically.

RUBOUT Pressing the RUBOUT key generates an octal code 377 each time.

For example, by backspacing a paper tape and punching RUB OUT over an error, the error is converted to octal code 377 and is ignored

upon subsequent reading.

REPT (Repeat) Pressing the repeat key simultaneously with another key causes the

normal action of the other key to be repeated as long as the two keys

are pressed.

ALT MODE Pressing the ALT MODE key produces an octal code of 375. When

ALT MODE is pressed simultaneously with the CTRL key, an octal

code of 275 is produced.

BREAK Pressing the BREAK key interrupts output on the console from the

system.

#### **AUTOSHUTDOWN**

The basic console is equipped with an automatic shutdown feature which turns the device off in the absence of activity from the central processor for a 1-minute period (when operating with the control switch set to the LINE position).

The central processor activates the console whenever activity is awaiting transmittal. The operator can also activate the device by pressing the BREAK key.

#### **OPERATION**

Operating procedures for the teleprinters are described below.

#### **APPLYING POWER**

Set LINE/OFF/LOCAL switch to LINE or LOCAL position.

#### **REMOVING POWER**

Set LINE/OFF/LOCAL switch to OFF position.

#### **PAPER LOADING**

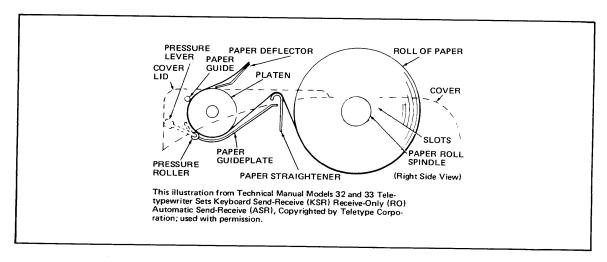

To install a new paper roll, follow these directions. Figure 2-5 illustrates the components discussed in the text.

- 1. Set LINE/OFF/LOCAL switch to OFF position.

- 2. Install a new paper roll in the unit by inserting the spindle into the new paper roll.

- 3. Place the roll in the recess provided at the rear of the cover. The ends of the spindle extending from both ends of the roll should rest in the associated slots (see Figure 2-5 for paper feed direction).

- 4. Raise the clear plastic lid over the typing unit.

- 5. Fold and crease the leading edge of the paper to present a smooth threading edge for feeding.

- 6. Release the tension of the typing unit platen by moving the pressure lever.

- 7. Push the paper under the platen roller as far as possible and move the pressure lever backwards to reapply roller tension.

- 8. Push the platen knob to feed the paper forward until it can be passed under the unit paper guide.

- 9. If necessary, again release the tension on the pressure rollers and straighten the paper.

- 10. Reapply roller tension.

- 11. Close the cover.

- 12. Set LINE/OFF/LOCAL switch to LINE or LOCAL position.

Figure 2-5. Installation of Paper Roll

#### RIBBON REPLACEMENT

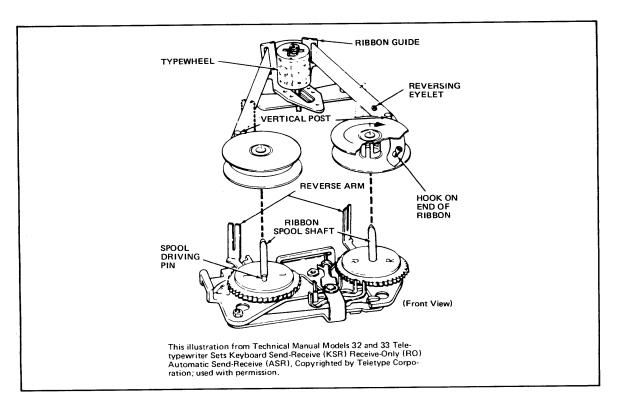

To install a new ribbon, follow these directions. Figure 2-6 illustrates the components discussed in the procedures.

- 1. Set LINE/OFF/LOCAL switch to OFF.

- 2. Raise the cover lid.

- 3. Pull both spools off the friction spindles.

- 4. Wind the ribbon onto one of the spools.

- 5. Discard the old ribbon.

- 6. Unwrap a new ribbon and engage the hook at the end of the ribbon in the hub of the empty spool.

- 7. Wind a few turns of ribbon onto the empty spool in the direction indicated by the arrow in the hub. Be sure that the reversing eyelet has been wound onto the empty spool.

- 8. Place the spools on the shafts so that the ribbon feeds to the rear from the right side of the right spool and from the left side of the left spool.

- 9. Turn each spool slightly until the spool driving pin engages the hole in the spool.

- 10. Guide the ribbon around the right vertical post and through the slot in the reverse arm.

- 11. Place the ribbon in the ribbon guide behind the typewheel.

- 12. Guide the ribbon through the left side of the reverse arm and around the vertical post.

- 13. Rotate the spool to take up any slack.

- 14. Set LINE/OFF/LOCAL switch to LINE.

Figure 2-6. Ribbon Installation

#### **OPERATOR MAINTENANCE**

Operator maintenance includes such preventive maintenance as normal checking and cleaning performed periodically on a routinely scheduled basis. This maintenance will keep the teleprinter in the best operating condition.

The following list is a general guide to operator maintenance:

- Always plug the device into a 3-wire grounded outlet.

- Ensure that all covers are secured and closed during operation.

- Never operate the teleprinter without paper.

- · Avoid leaning on or placing objects on any part of the teleprinter.

- Turn the power OFF before replacing paper or ribbons.

- Never put food or beverages on or near the device.

- Keep the outside covers clean and free of debris.

- Clean and dust the inside areas of the print, punch, and reader mechanisms.

# **HEAVY-DUTY CONSOLE**

The heavy-duty console (see Figure 2-7), which is required for NPS operation, has a 64-character ASCII code set and prints at 120 characters per second. It also has 132 print positions. It uses a paper stock with standard continuous fanfold paper forms with feed holes on each edge with or without margin perforations. The accepted forms length is 3.0 in. to 17 in. (7.63 cm to 43.2 cm). The accepted forms width is 4.0 in. to 15 in. (10.16 cm to 38.1 cm).

# **CONTROLS AND INDICATORS**

Console controls and indicators are described in the following paragraphs.

#### **KEYBOARD**

The 64-character keyboard is shown on Figure 2-8.

Figure 2-7. Heavy-Duty Console

Figure 2-8. Keyboard Layout

# **CONTROLKEYS**

The control keys used for normal operation include the following:

CTL Pressing the CTL (control) key generates the control function codes of

the ASCII code set.

RPT Pressing the RPT (repeat) key simultaneously with another key

causes repeated generation of the other key as long as both are

pressed.

LF Pressing the LF (line feed) key advances the last line upwards one

line position.

BRK Pressing the BRK (break) key allows the operator to generate an

interrupt to the system.

RETURN Pressing the RETURN key causes the carriage to return to the first

character position of the same line that it is positioned on.

DEL Pressing the DEL (delete) key together with the SHIFT key

generates an ASCII hex code of 1F.

CLR Pressing the CLR (clear) key generates an ASCII hex code of 0C. The

same code can also be generated by pressing the CTL key together

with the L key.

HERE IS This key is not used.

ESC Pressing the ESC (escape code) key generates an ASCII hex code of

1B. The same code can also be generated by simultaneously pressing

the CTL, SHIFT, and [ (left bracket) keys.

CAPLOCK Pressing the CAPLOCK key locks the keyboard in an uppercase-only

operating mode.

#### **CONTROL PANEL**

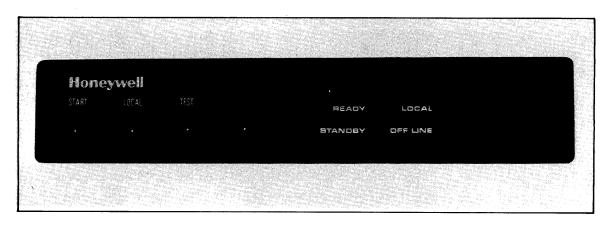

The console control panel is shown in Figure 2-9. The controls and indicators include the following:

MAIN POWER Pressing this switch (located on the rear of the console) applies or

removes power to or from the device.

START Pressing the START button causes a transition from the standby

state to ready state and enables communication with the system.

STOP Pressing the STOP button causes a transition from the ready state to

standby state. It is also used to reset to local condition.

LOCAL Pressing the LOCAL button allows the console to be used indepen-

dently from the system (STANDBY lights).

TEST Pressing the TEST button (preceded by LOCAL) causes a printout of

the complete (uppercase and lowercase) character set. Refer to

PRINT TEST procedures.

READY Indicates that the console is in ready state, logically connected to the

system, and ready to communicate with the system.

STANDBY Indicates that the device is powered up, physically connected to the

system, but not ready to communicate with the system.

LOCAL Indicates that the console is in the local mode and can be operated

independently of the system.

OFFLINE Indicates that the console is powered up but not physically connected

to the system.

SHIFT Pressing the SHIFT key with an applicable key generates its asso-

ciated uppercase character.

Paper-Out Sensor A sensor, placed on the left tractor, is provided to detect depletion of

the forms supply. Upon detection of a paper-out condition, printing is

stopped and STANDBY lights.

Figure 2-9. Control Panel

#### **MECHANICAL ADJUSTMENTS**

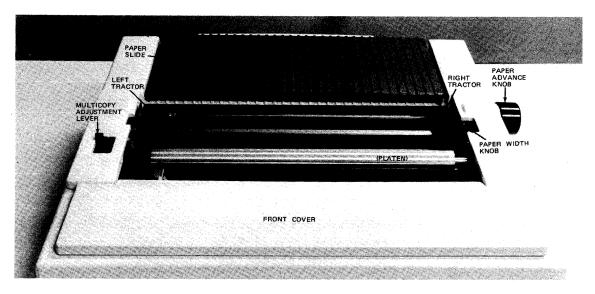

There are several mechanical adjustments located in the printer mechanism (Figure 2-10) for the control of printing and paper feeding.

Paper Width Knob Used to lock/unlock the right tractor so it may be adjusted to accom-

modate the paper width.

Paper Advance Knob Used to manually advance paper one or more lines.

Multicopy Adjustment Lever Used for manual adjustment of the platen in relationship to the print head. The lever is designed with five individual settings (1 through 5) which correspond to the thickness of the applicable form (single through 4-ply). The lever should be checked whenever forms are changed or when the device is turned on to ensure the proper setting. See Table 2-2.

Figure 2-10. Paper Positioning Controls

TABLE 2-2. MULTICOPY ADJUSTMENT LEVEL

| Media Thickness                                  | Lever Position |

|--------------------------------------------------|----------------|

| 0.07 mm to 0.11 mm<br>(0.003 in. to 0.0043 in.)  | 1              |

| 0.12 mm to 0.22mm<br>(0.0051 in. to 0.0087 in.)  | 2              |

| 0.23 mm to 0.32 mm<br>(0.0091 in. to 0.0126 in.) | 3              |

| 0.33 mm to 0.42 mm<br>(0.0130 in. to 0.0165 in.) | 4              |

| 0.43 mm to 0.52 mm<br>(0.0169 in. to 0.0205 in.) | 5              |

#### **OPERATION**

Operating procedures for the heavy-duty console are described below.

#### **APPLYING POWER**

- 1. Set power switch on rear of console to ON (STANDBY lights).

- 2. Refer to "Forms Loading" procedure; otherwise press the START button (READY lights).

#### REMOVING POWER

- 1. Press the STOP button.

- 2. Set power switch on rear of console to OFF (STANDBY turns off).

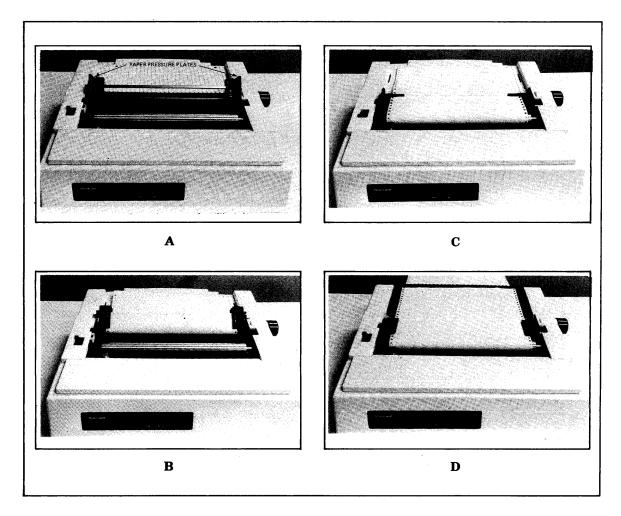

#### **FORMS LOADING**

- 1. Press the STOP button (if not already stopped).

- 2. Remove the paper slide.

- 3. Move the right tractor to accommodate the paper being used by adjusting the paper width knob.

- 4. Swing the tractor assembly upwards and open the bottom pressure plates (Figure 2-11A).

#### Note:

The following procedures are best performed from the rear of the console.

- 5. Feed the paper under the tractor assembly, fit it on the tractors (the leading edge of the paper should not extend beyond the tractors at this point), and close the pressure plates (Figure 2-11B).

- 6. Lower the tractor assembly.

- 7. Adjust the Multicopy Adjustment Lever to position 5.

- 8. Open the top pressure plates.

- 9. Turn the platen knob and feed the paper under the platen. Enough paper should be fed to attach the paper on the top tractors.

- 10. Position the paper in the top tractors (Figure 2-11C) and close the top pressure plates.

- 11. Position the form on the upper tractors and flip down the left and right tractor face plates to secure the form.

- 12. Replace the paper slide to its original position.

- 13. Adjust the Multicopy Lever to a setting that corresponds to the form just loaded (Figure 2-11D).

# 14. Press the START button.

# Note:

If the paper is not properly positioned, the initial loading under the lower tractors may be difficult. If the form does not catch under the tractor properly, begin form loading again with the paper repositioned under the tractors. It may be necessary to apply some pressure to multipart forms as they have a tendency to separate while being introduced.

Figure 2-11. Paper Loading

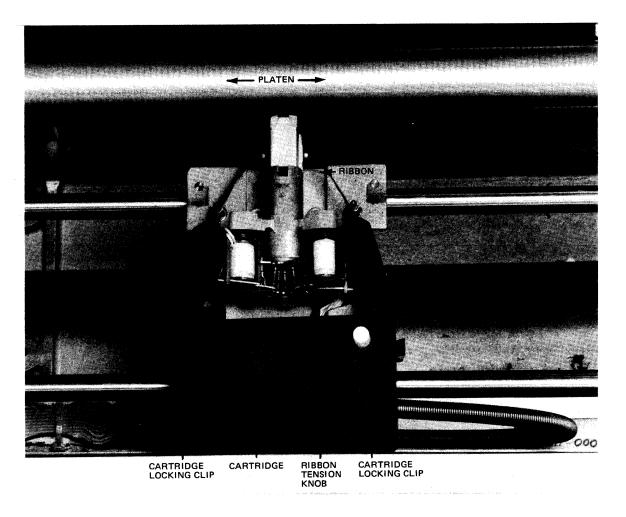

# RIBBON CARTRIDGE REPLACEMENT

Ribbons are supplied as operator-replaceable cartridges. The cartridge (M3918—1/4" or M3917—3/8") is positioned on the print mechanism (see Figure 2-12) by the operator, on a reference pin which ensures proper positioning and plastic clips which ensure locking.

Figure 2-12. Ribbon Cartridge Replacement

The operator replaces the cartridge as necessary to ensure high-quality printing. Cartridge loading includes the following steps:

- 1. Remove power from the console.

- 2. Lift off the cover over the print mechanism.

- 3. Slacken ribbon tension via the ribbon tension knob.

- 4. Remove worn ribbon cartridge.

- 5. Slacken ribbon tension on new ribbon cartridge.

- 6. Position the ribbon between the platen and the print head mechanism.

- 7. Gently draw the cartridge away from the print mechanism.

- 8. Carefully position the cartridge on the reference pin and plastic locking clips.

- 9. Adjust ribbon tension.

- 10. Replace cover.

- 11. Apply power to the console.

# **PRINTTEST**

To check print quality and print the entire character set, do the following:

- 1. Press the STOP button.

- 2. Press the LOCAL button.

- 3. Press the TEST button.

- 4. Press the START button (printing begins).

- 5. Press the STOP button to terminate the print test.

#### **OPERATOR MAINTENANCE**

Operator maintenance includes such preventive maintenance as normal checking and cleaning performed periodically on a routinely scheduled basis. This maintenance will keep the console in the best operating condition thereby reducing the possibility of downtime.

The following list is a general guide to operator maintenance:

- Always plug the console into a 3-wire grounded outlet.

- Ensure that all covers are closed and secured during operation.

- Never operate the console without paper.

- Avoid leaning on or placing objects on any part of the console.

- Turn power OFF before replacing paper or ribbon cartridge.

- Never put food or beverage on or near the console.

- Keep outside covers clean and free of debris.

- Clean and dust the inside areas of the print mechanism.

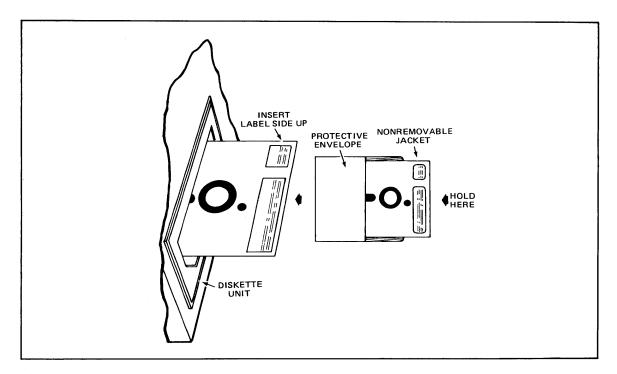

#### **DISKETTE UNIT**

The single, rackmounted diskette unit is used by the operator solely to load the system offline test and diagnostic (T&D) programs which are recorded on the magnetic oxide coated surface of the Mylar disk (or diskette). The T&D programs for the DATANET are contained on three separate diskettes.

The flexible disk is packaged in an 8-inch-square protective nonremovable jacket. Both diskette and jacket contain a center hole with an access slit that extends from the center to the outer edge. When loaded and operative, the magnetic heads on the diskette unit come into physical contact with the recording surface of the diskette. The jacket becomes immobile and is held stationary while the diskette unit spindle automatically engages the diskette and rotates it at a speed of 360 rpm.

#### **CONTROLS**

Diskette unit controls include the following:

POWER ON/OFF This two-position switch is used to either apply or remove power. In

non-tabletop configurations, power is applied from the control panel

of the central processor.

Access Cover Button Pressing this button opens the diskette unit access cover to enable

either the insertion or removal of the diskette. The access cover is

closed manually.

#### **OPERATION**

Operating procedures for the diskette units are described below.

#### **APPLYING POWER**

Set POWER switch to ON position.

#### **REMOVING POWER**

Set POWER switch to OFF position.

#### Note:

Remove diskette before powering on/off or its programs may be erased.

#### **DISKETTE UNIT LOADING**

Prior to loading, visually check the condition of the flexible disk. It should not be torn, folded, or creased. Do not use a damaged diskette.

1. Remove the diskette from its protective envelope (Figure 2-13).

#### Note:

Diskette remains inside its nonremovable jacket.

- 2. Press the access cover button on the diskette unit.

- 3. Carefully insert the diskette squarely and completely into the diskette unit.

- 4. Close the access cover. (The diskette unit spindle automatically engages the diskette and the device is ready for operation.)

Figure 2-13. Diskette Media Handling

#### **DISKETTE UNIT UNLOADING**

- 1. Press the access cover button on the diskette unit.

- 2. Grasp the diskette jacket and remove it from the diskette unit.

- 3. Close the access cover if no other diskette is to be inserted.

- 4. Return the diskette back into its envelope.

#### **OPERATOR MAINTENANCE**

Preventive maintenance includes the checks and cleaning done periodically on a scheduled basis, even though diskette unit operation may be satisfactory and not in need of attention.

#### CARE AND HANDLING OF DISKETTE

Proper handling and storage of a diskette will increase its life expectancy and reduce the possibility of errors. Observe the following rules for proper media handling and storage.

• Keep the diskette clean. Handle with care since dust and dirt smudges, especially on the recording surfaces, can reduce the intensity and accuracy of reading or recording signals.

- Write on labels *before* adhering them to the nonremovable jacket since writing pressure from a pencil or pen on the jacket may damage the diskette. It is preferable to use felt-tipped pens to minimize contamination.

- Place labels so that they do not obstruct the index sensing hole or adhere the diskette to its

jacket.

- It is best not to smoke in the computer room or near the device but, if you must, be extremely careful as smoke and ashes are dirt. Hot ashes are destructive to disks. Food and drink should not be placed on or near the device.

- To reduce the problem of damaged or defective diskettes, never bundle them during storage. Avoid the use of elastic bands or paper clips and store each in its envelope when not in use. Do not stack diskettes on top of other packages.

- Store diskettes in an environment that is the same as the diskette unit operating environment. The recommended environment is from 50°F to 115°F (10°C to 46°C) with a relative humidity of 5% to 90%. Abrupt changes in relative humidity must be avoided.

- Do not expose diskettes to direct sunlight or intense heat.

# POWER UP/POWER DOWN/SYSTEM INITIALIZATION PROCEDURES INITIAL POWER UP PROCEDURE

#### Note:

Diskette media should not be inserted in unit until after step 5.

- 1. Open lower front cabinet door.

- 2. Set Power Distribution Unit ON/OFF switch to the ON position.

- 3. Close lower front cabinet door.

- 4. Insert key into panel security keylock switch and turn key to the maximum clockwise position to unlock the control panel.

- 5. Set control panel POWER switch to the on position (up). DC ON indicator lights. System is now powered up.

#### Note:

Power up console next.

#### **COMPLETE POWER DOWN PROCEDURE**

- 1. Power down console and diskette (diskette media should be removed first).

- 2. Set control panel POWER switch to the off (down) position. DC ON indicator turns off.

- 3. Open lower front cabinet door.

- 4. Set Power Distribution Unit ON/OFF switch to the OFF position.

- 5. Close lower front cabinet door. System is now completely powered down.

# **NORMAL POWER UP PROCEDURE**

#### Note:

Diskette media should not be inserted in unit until after step 2.

- 1. Insert key into panel security keylock switch and turn key to maximum clockwise position to unlock the control panel.

- 2. Set control panel POWER switch to the on position (up). DC ON indicator lights. System is now powered up.

#### Note:

Power up console next.

# **NORMAL POWER DOWN PROCEDURE**

- 1. Power down console and diskette (diskette media should be removed first).

- 2. Set control panel POWER switch to the off (down) position. DC ON indicator turns off. System is now powered down.

#### SYSTEM INITIALIZATION PROCEDURE

- 1. Be sure STOP/STEP indicator is lit. If it isn't, press the S (Stop/Step) key.

- 2. Press CLR (Master Clear) key. This initiates running of QLTs (approximately 10-20 seconds).

- 3. Wait for CHECK indicator to turn off. If it doesn't, refer to "Quality Logic Test" description in Section 3. System is now initialized and ready for operation.

# Fault Isolation and Diagnostics

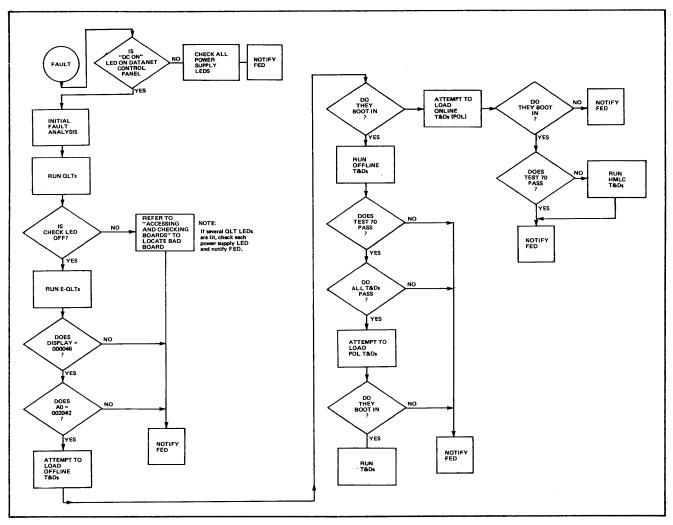

This section describes the fault isolation process and the operation of the various test and diagnostics (T&Ds) that an operator must be familiar with. Figure 3-1 shows the proper path to follow.

Figure 3-1. Fault Isolation Overview

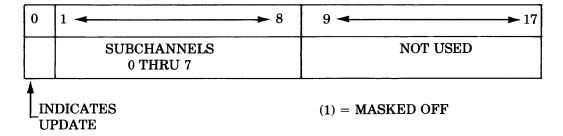

#### **INITIAL FAULT ANALYSIS**