Honeywell

COMPUTER CONTROL

# H632 CENTRAL PROCESSOR DESCRIPTION

November 1968

COPYRIGHT 1968, by Honeywell Inc., Computer Control Division Framingham, Massachusetts. Contents of this publication may not be reproduced in any form in whole or in part, without permission of the copyright owner. All rights reserved.

Printed in U.S.A.

Published by the Publications Department, Honeywell Inc. Computer Control Division

# CONTENTS

|                                                  | Page |

|--------------------------------------------------|------|

| SECTION I<br>INTRODUCTION                        |      |

| Scope of Manual                                  | 1-1  |

| Applicable Documents                             | 1-1  |

| Functional Description                           | 1-2  |

| SECTION II<br>GENERAL DESCRIPTION                |      |

|                                                  | 2-1  |

| Machine Structure                                | 2-1  |

| Registers and Logic Networks                     |      |

| Logic Domains                                    | 2-6  |

| Control Gating and Data Flow/Cycle Phase         | 2-8  |

| Sequencing and Control                           | 2-8  |

| Logic Elements                                   | 2-8  |

| Normal CP Operating Sequence                     | 2-15 |

| CP Interfaces                                    | 2-20 |

| MPC Interface                                    | 2-21 |

| Memory Interface                                 | 2-21 |

| Control Panel and Power Control Interconnections | 2-25 |

| Cable PACs                                       | 2-25 |

| SECTION III<br>DETAILED THEORY                   |      |

| Start-Stop, Timing and Control Logic             | 3-1  |

| System Initialize                                | 3-1  |

| CP Initialize                                    | 3-7  |

| Start-Stop Logic                                 | 3-7  |

| Timing Oscillator and Clock Distribution         | 3-13 |

| Timing Level Generator                           | 3-13 |

| Interrupt Register and Control                   | 3-16 |

| Trap Control Logic                               | 3-18 |

| Memory Interface                                 | 3-20 |

| Interface Signals and Cabling                    | 3-23 |

| CP/MAD/IOP/Memory Handshake                      | 3-23 |

| System Initialize and Startup                    | 3-26 |

| Cycle Initiate Logic                             | 3-29 |

| IOP Break-In                                     | 3-30 |

| CP Inactive (Cycle Request Removed)              | 3-33 |

| Panel Halts                                      | 3-33 |

# CONTENTS (Cont)

|                                          | Page          |

|------------------------------------------|---------------|

| Look-Ahead                               | 3-34          |

| Principles of Operation                  | 3-34          |

| Detailed Theory of Operation             | 3-43          |

| Instruction Counter                      | 3-49          |

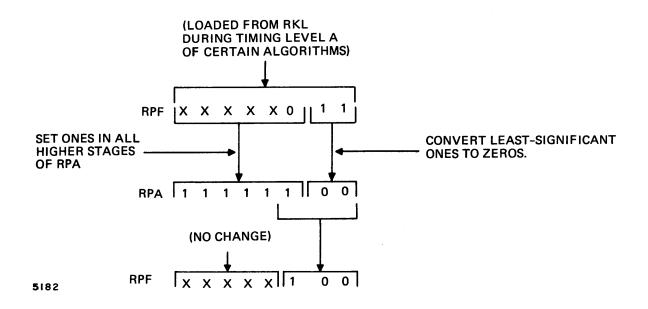

| Loading RP                               | 3-50          |

| Up-Counter Algorithm                     | 3-50          |

| Cycle Counter                            | 3-52          |

| Structure                                | 3-52          |

| Theory                                   | 3-52          |

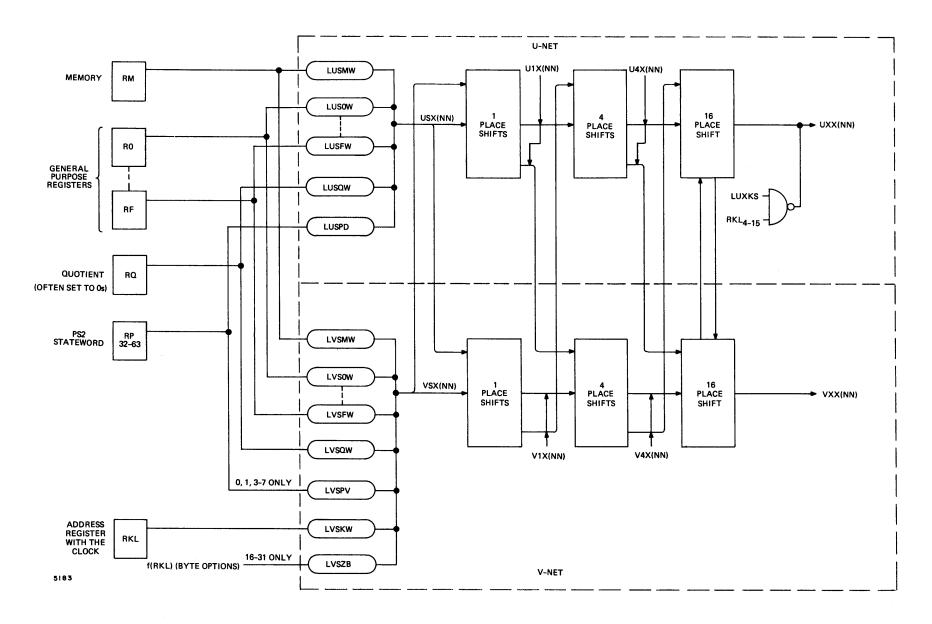

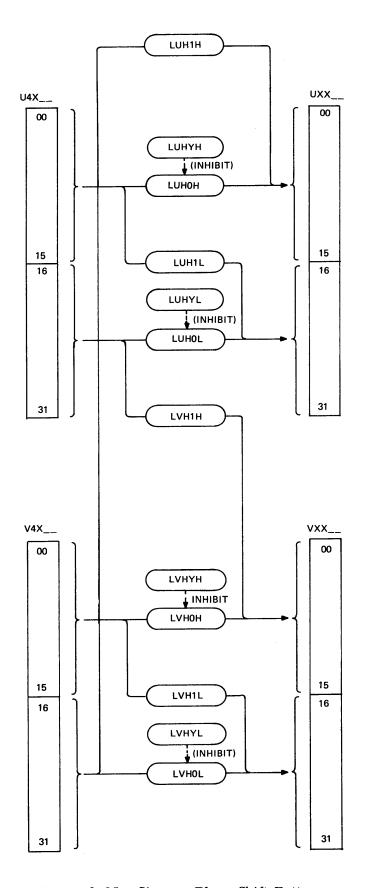

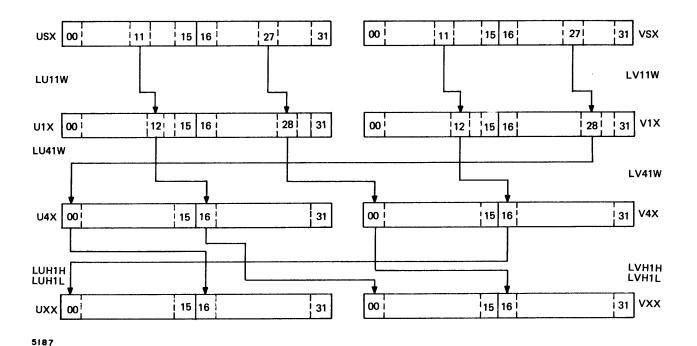

| Shift Network                            | 3-53          |

| Input Selection                          | 3-53          |

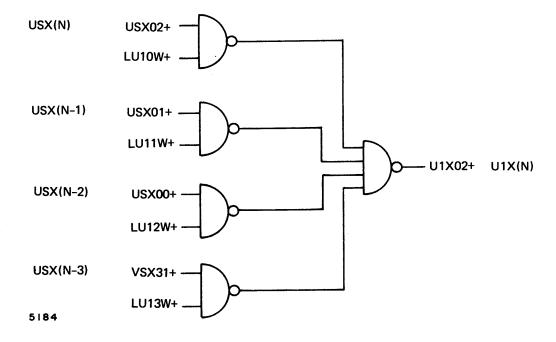

| One-Place Shift Gates                    | 3-55          |

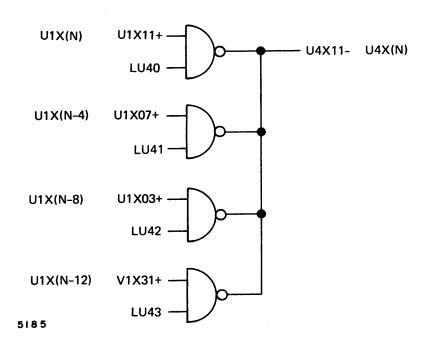

| Four-Place Shift Gates                   | 3-56          |

| Sixteen-Place Shifting                   | 3 <b>-</b> 56 |

| Unshifted Data Transfers                 | 3-58          |

| Shifting Example                         | 3-58          |

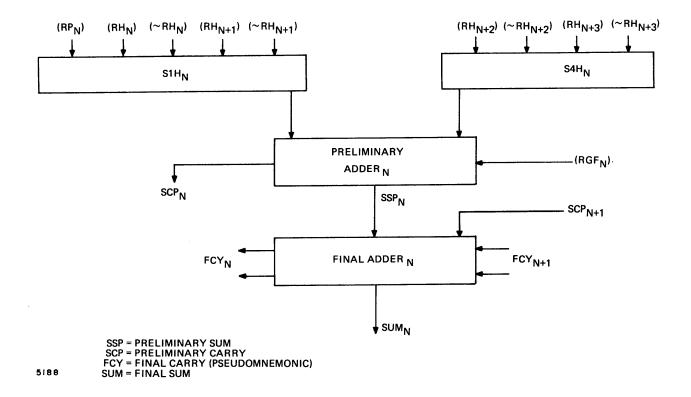

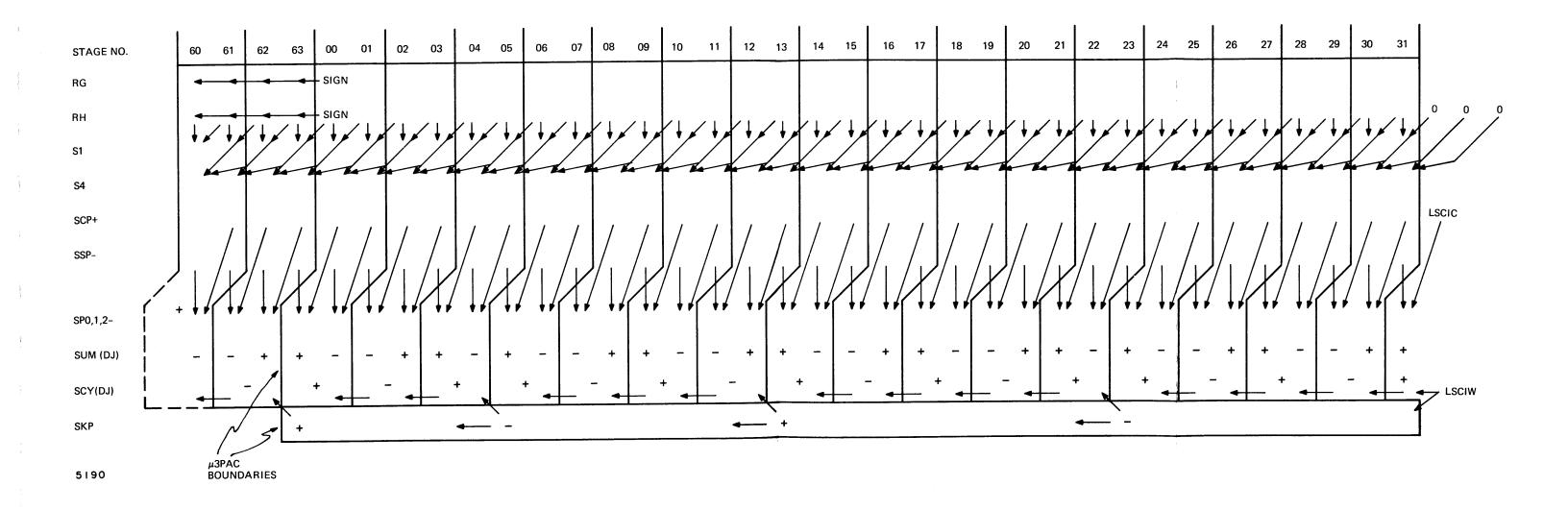

| Adder                                    | 3-58          |

| Summands and Summand Selection           | 3-58          |

| Results                                  | 3-59          |

| Method of Implementation                 | 3-60          |

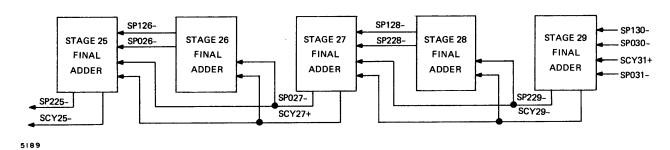

| Skip-Carry Network                       | 3-65          |

| Adder Structure                          | 3-66          |

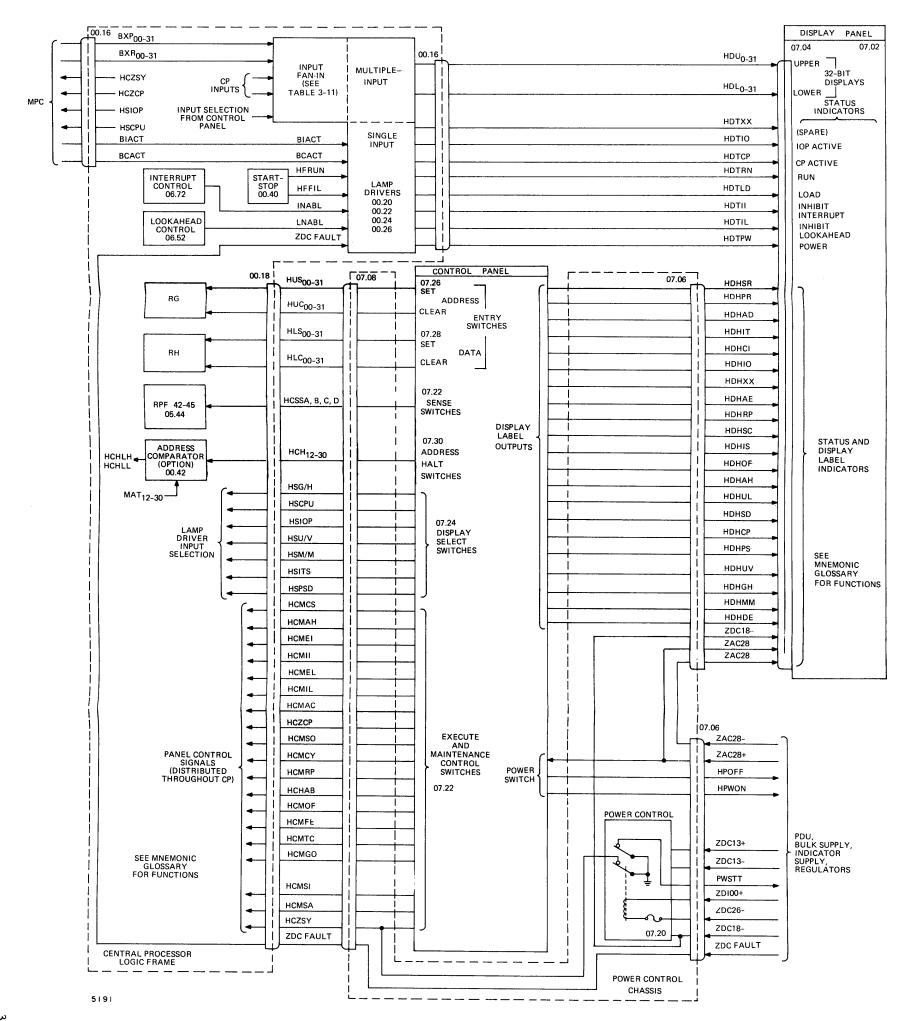

| Console Control and Display Panels       | 3-66          |

| Address/Data Entry Switches              | 3-66          |

| Address Halt Keys                        | 3-73          |

| Sense Keys                               | 3-73          |

| Execute and Maintenance Control Switches | 3-73          |

| Display Select Switches                  | 3-73          |

| Direct-Wired Status and Display Labeling | 3-73          |

| Lamp Drivers and Display Selection       | 3-73          |

| Control Panel Power Switching            | 3-74          |

| MPC Interconnections                     | 3-74          |

# ILLUSTRATIONS

|       |                                                                            | Page          |

|-------|----------------------------------------------------------------------------|---------------|

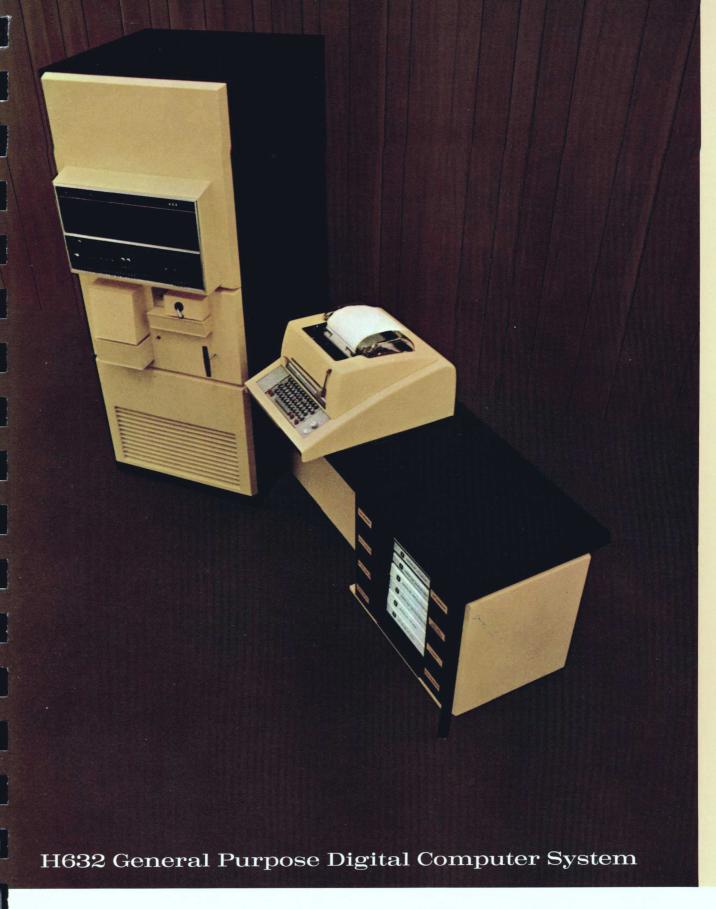

| 1 - 1 | Typical Series 32 General Purpose Computer System                          | 1-3           |

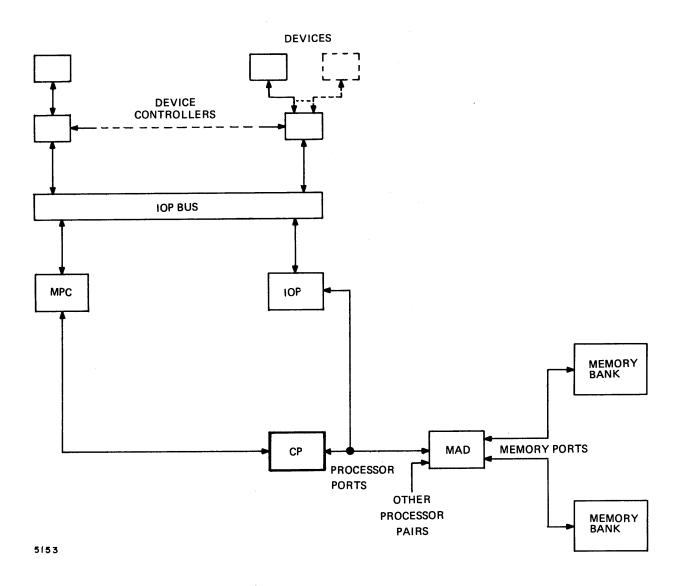

| 2-1   | Central Processor Block Diagram                                            | 2-3           |

| 2-2   | Typical Control Logic Structure: Logic Domains                             | 2-7           |

| 2-3   | Control Gating Development and Data Flow in Each Logic Cycle Phase         | 2-9           |

| 2-4   | Sequencing and Control Logic Block Diagram                                 | 2-11          |

| 2-5   | Simplified Central Processor Timing Signals                                | 2-14          |

| 2-6   | Central Processor Sequence of Operations                                   | 2-17          |

| 2-7   | Central Processor Interface Connection Summary                             | 2-23          |

| 2-8   | Cable PAC Applications (2 Parts)                                           | 2-26          |

| 3-1   | Time Sharing of Execution Functions with Sequencing and Control Functions  | 3-3           |

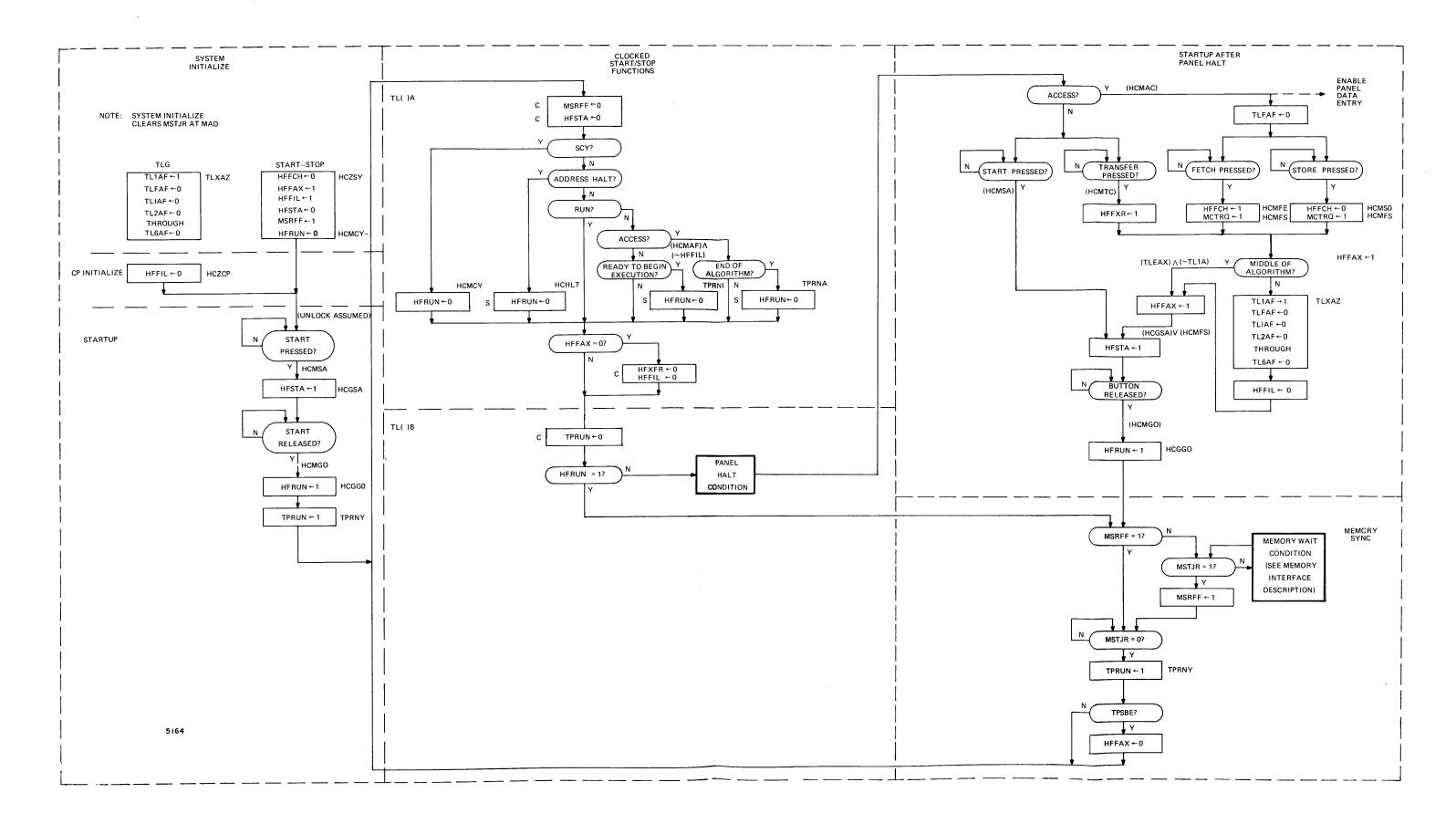

| 3-2   | System Initialize and Central Processor Initialize Flow Chart              | 3-5           |

| 3-3   | Start-Stop Logic Flow Chart                                                | 3-9           |

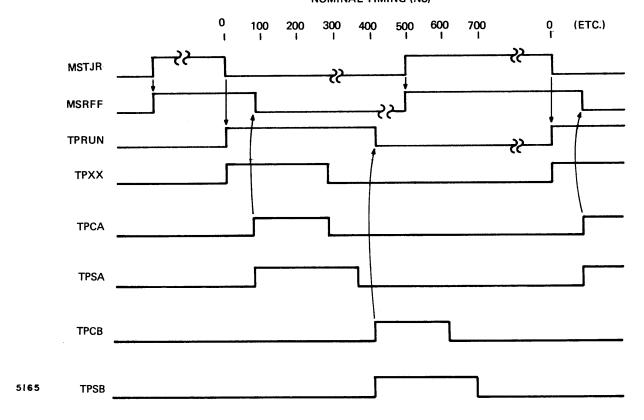

| 3-4   | Clock Oscillator Timing                                                    | 3-14          |

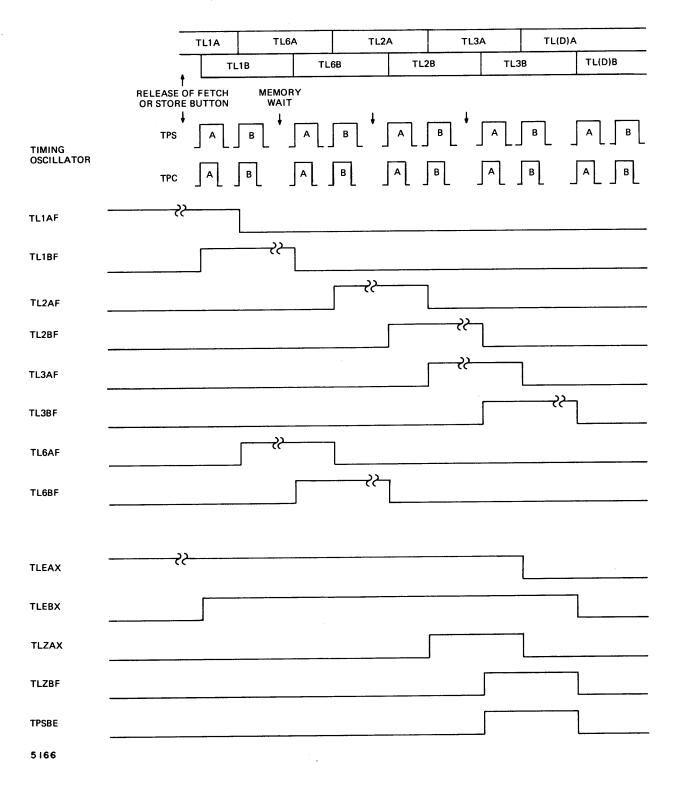

| 3-5   | Timing Level Generator Signals During Access (Example)                     | 3-15          |

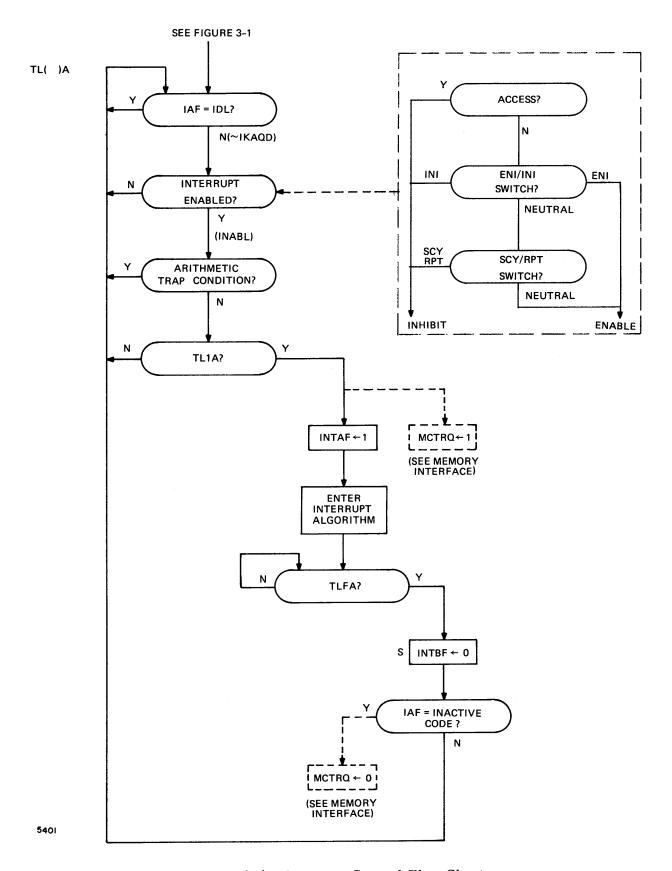

| 3-6   | Interrupt Control Flow Chart                                               | 3-17          |

| 3-7   | Trap Control Flow Chart                                                    | 3-19          |

| 3-8   | Memory Interface Signals                                                   | 3-21          |

| 3-9   | Overall Memory Interface Timing Read Cycle                                 | 3-24          |

| 3-10  | CP Logic Functions Related to Memory Cycles                                | 3-26          |

| 3-11  | Memory Interface Logic Signals During System Initialize and Startup        | 3-27          |

| 3-12  | Memory Interface Logic Signals (Write Cycle)                               | 3-30          |

| 3-13  | Memory Interface Logic Signals During IOP Break-In                         | 3-31          |

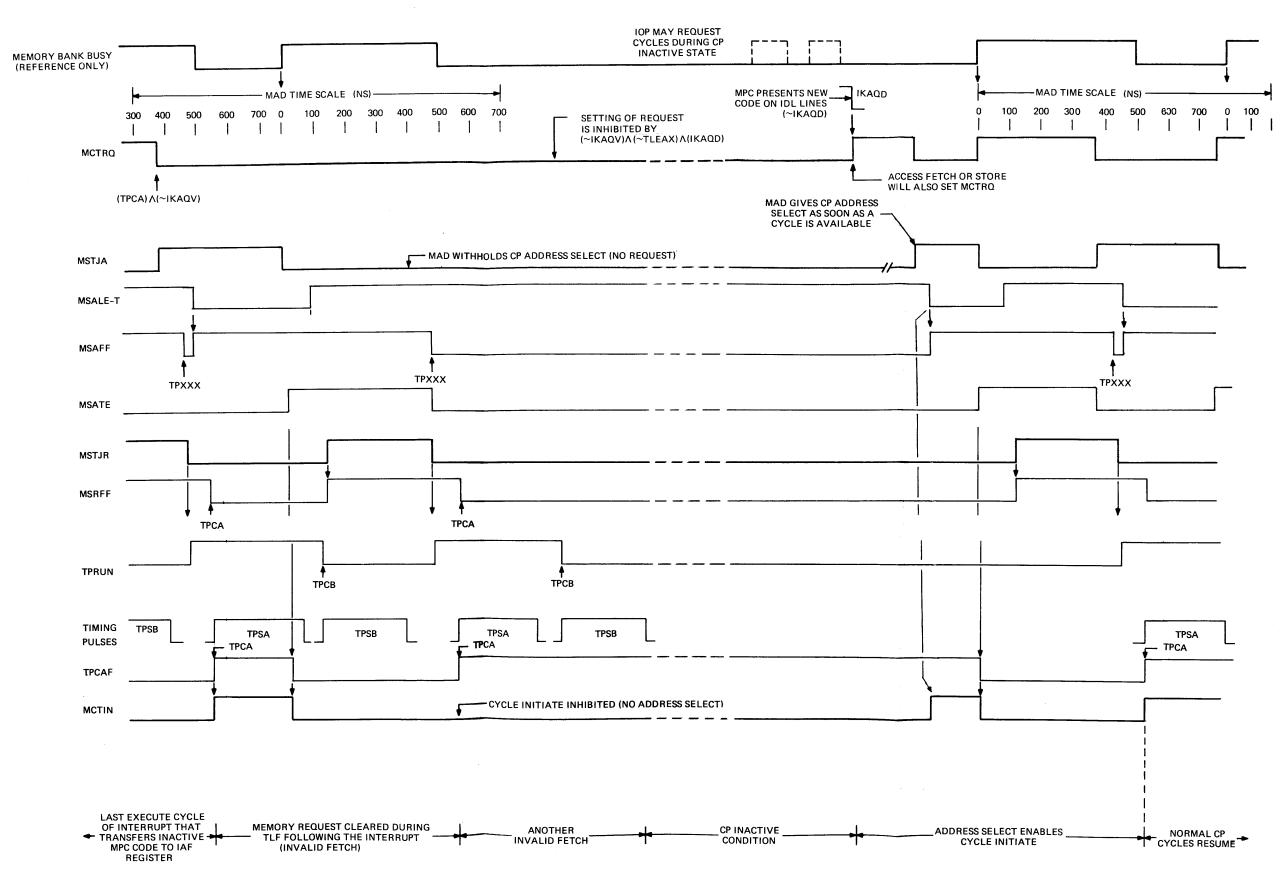

| 3-14  | Memory Interface Logic Signals During Central Processor Inactive Condition | 3-35          |

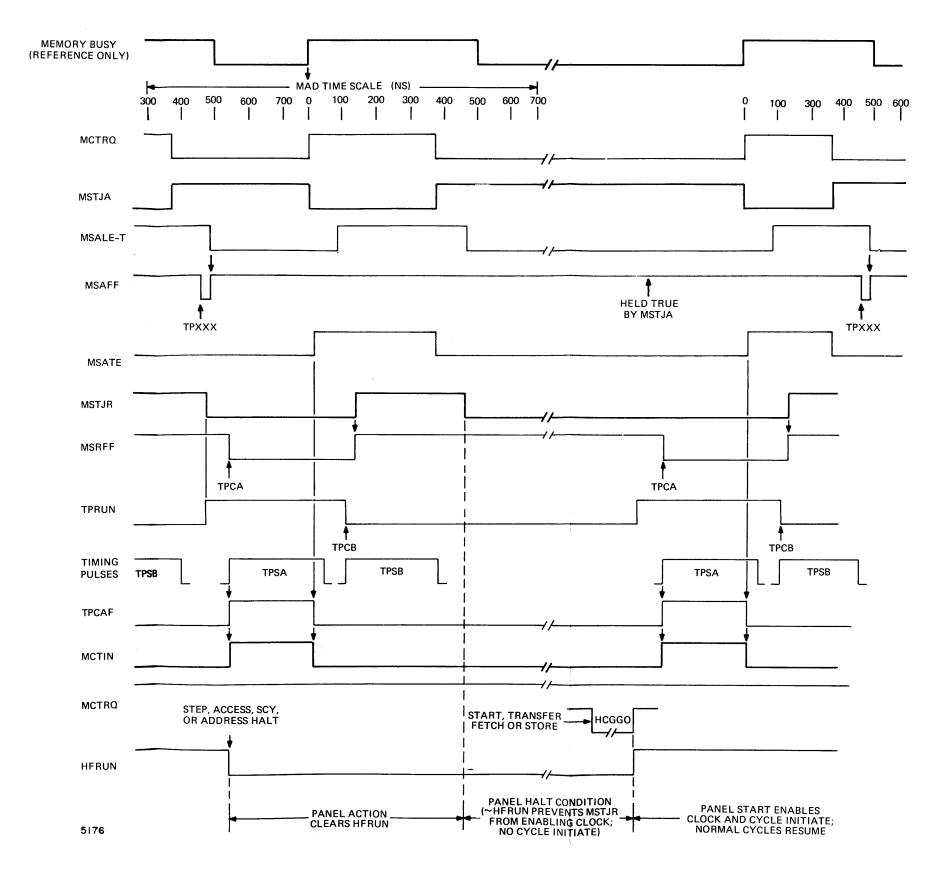

| 3-15  | Memory Interface Logic Signals During Panel Halt                           | 3-37          |

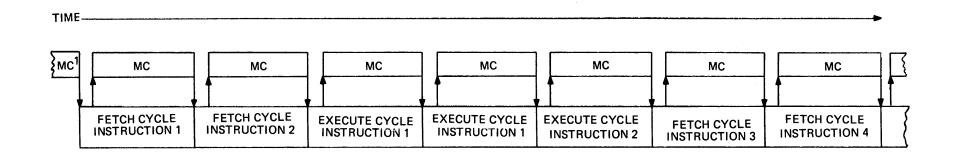

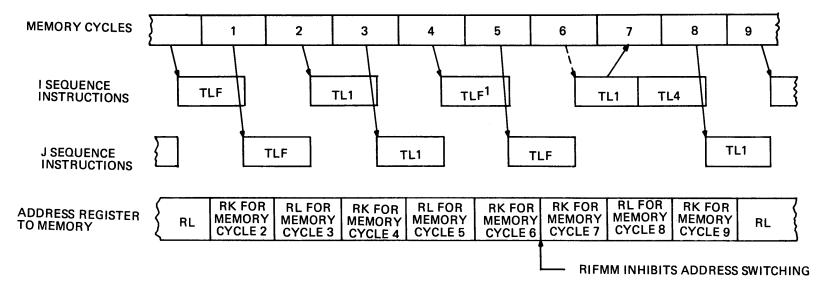

| 3-16  | Instruction Processing Cycle Alternation                                   | 3-39          |

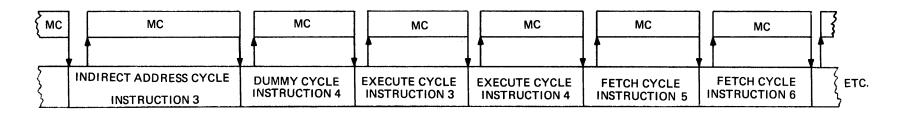

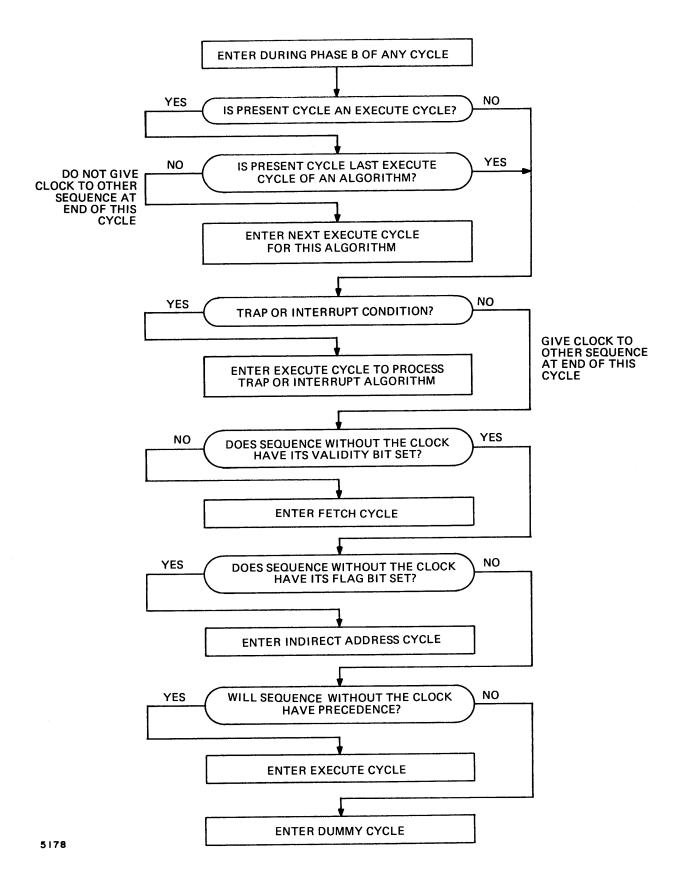

| 3-17  | Cycle Entry Decisions                                                      | 3-41          |

| 3-18  | Memory Address Switching Principles                                        | 3-44          |

| 3-19  | Timing for TIC, TSP and TIP Look-Ahead Controls                            | 3-46          |

| 3-20  | Memory Address Switching Details                                           | 3-47          |

| 3-21  | Instruction Counter Operation                                              | 3-51          |

| 3-22  | Shift Network Block Diagram                                                | 3-54          |

| 3-23  | One-Place Shift Gates (Typical)                                            | 3-55          |

| 3-24  | Four-Place Shift Gates (Typical)                                           | 3 <b>-</b> 56 |

| 3-25  | Sixteen-Place Shift Patterns                                               | 3-57          |

| 3-26  | Shifting Example: 21-Place Right or 43-Place Left Rotation                 | 3-58          |

| 3-27  | Typical Adder Stage Block Diagram                                          | 3-61          |

| 3-28  | Final Carry Signals Block Diagram                                          | 3-63          |

| 3-29  | Adder Structure                                                            | 3-67          |

| 3-30  | Console Data Distribution                                                  | 3-69          |

# TABLES

|      |                                                                                                                | Page          |

|------|----------------------------------------------------------------------------------------------------------------|---------------|

| 1-1  | Standard H632 Documentation                                                                                    | 1-2           |

| 2-1  | CP Start/Stop Condition Summary                                                                                | 2-21          |

| 3-1  | Trap Condition Table Entries                                                                                   | 3-20          |

| 3-2  | Adder Inputs and Definitions                                                                                   | 3 <b>-</b> 59 |

| 3-3  | Truth Table for SSP <sub>N</sub> and SCP <sub>N</sub>                                                          | 3-61          |

| 3-4  | Truth Table for SPR <sub>N</sub> , SPO <sub>N</sub> , SPO <sub>N</sub> and SP2 <sub>N</sub>                    | 3-62          |

| 3-5  | Truth Table for Stage 25 Type - Final Carry Generation Where Carry = (SCY <sub>N</sub> ) V (SP2 <sub>N</sub> ) | 3-63          |

| 3-6  | Truth Table for Stage 27 Type Carry Generation Where Carry - $(SCY_N) \land (\sim SP_N)$                       | 3-63          |

| 3-7  | Truth Table for Stage 28 Type Final Sum Generation                                                             | 3-64          |

| 3-8  | Truth Table for Stage 27 Type Final Sum Generation                                                             | 3-64          |

| 3-9  | Truth Table for Stage 26 Type Final Sum Generation                                                             | 3-65          |

| 3-10 | Truth Table for Stage 25 Type Final Sum Generation                                                             | 3-65          |

| 3-11 | Display Lamp Driver Input Summary                                                                              | 3-71          |

# SECTION I

#### SCOPE OF MANUAL

Technical information on the H632 Central Processor appears in this manual and in the following two companion volumes:

- a. H632 Central Processor Instructions (Flow charts and analyses of all instructions and control algorithm, and mnemonic glossary).

- b. H632 Central Processor Diagrams (Logic and power distribution diagrams, PAC layout drawings, and mechanical coding diagrams).

This manual emphasizes the hardware implementation of H632 Central Processor functions described from a general operational viewpoint in the H632 Reference Manual. The main CP logic elements are discussed on a block-diagram basis, and unusual or complex logic structures, such as the adder, are described in detail. While all the H632 CP data-processing instructions and algorithms are analyzed by flow charts and analysis tables in the Central Processor Instructions manual, this manual provides additional detail on the sequencing and control functions that operate in addition to, and simultaneously with, the actual data-processing algorithms. These functions include power turn-on; system and CP initializing; panel start-stop and control of operating mode; interface synchronization of the CP, Memory Access Director (MAD), Multiprocess Controller (MPC), I/O Processor (IOP), and the memory system, and instruction overlap.

#### APPLICABLE DOCUMENTS

All manuals provided as standard documentation with each Series 32 Digital Computer System are listed in Table 1-1. Additional copies of any manual in Table 1-1 may be obtained by contacting a local Honeywell Inc., Computer Control Division representative or by writing directly to:

Honeywell Inc.

Computer Control Division

Old Connecticut Path

Framingham, Massachusetts 01701

Table 1-1.

Standard H632 Documentation

| Title                                | Doc. No.  |

|--------------------------------------|-----------|

| System Manuals                       |           |

| H632 Reference Manual                | 130071960 |

| H632 Operator's Manual               | 130071967 |

| H632 Modular Products Manual Vol. I  | 130071974 |

| H632 Modular Products Manual Vol. II | 130072932 |

| System Component Manuals             |           |

| H632 Central Processor Instructions  | 130071962 |

| H632 Central Processor Diagrams      | 130071968 |

| H632 Memory Access Director          | 130072037 |

| H632 Multiprocess Controller         | 130072042 |

#### FUNCTIONAL DESCRIPTION (Figure 1-1)

The Central Processor (CP) is a 32-bit general-purpose, stored-program digital computer. It performs all of the Series 32 system computation (arithmetic and logic) and data-processing functions, exclusive of input/output transfers (direct CP input/output capability is optional).

The CP has the standard capability of processing eight levels of programming, each level having an assigned priority. The MPC specifies which level the CP is to be acting upon. The CP is equipped (as is the IOP) with a control process order which it delivers to the MPC. The control process order requests the MPC to affect a change of state in the CP process which issued the order and/or another CP or IOP process. Thus, the CP has the capability of affecting the activity state of any of the system processes.

Transfers between memory and input/output devices are, as a rule, performed by the IOP into and out of a processor port shared by the CP and IOP. Thus, the CP can be devoted to purely computation tasks.

Figure 1-1. Typical Series 32 General Purpose Computer System

#### SECTION II GENERAL DESCRIPTION

#### MACHINE STRUCTURE

# Registers and Logic Networks (See Figure 2-1.)

Addressable Registers. -- There are 16 32-bit general registers, designated R0 through RF (second character is hexadecimal). The general registers can be accessed by the instruction word address field when the effective address is equal to or less than  $F_{16}$ , or by the instruction word R-field. The general registers can be used as operand and result locations. Registers R1 through R7 can also be specified by the instruction word X-field and serve as index registers.

Inputs to the general registers are from the adder or the RG or RT register. The contents of the general registers are gated out to the U and V shift network.

Auxiliary Registers. -- The auxiliary registers supply operands to the logic networks (the U and V shift network and the adder) and are used to retain partial results.

Register RG is a 36-bit register. Some of its functions are as follows. It retains augend, minuend, product, or dividend/remainder in arithmetic operations. It provides address storage during control panel operations and buffer storage during the <u>direct read</u> operation (optional). The main input path to RG is via the U and V shift network. The RG register output is hardwired (ungated) to the adder. The contents of RG can be gated to any one of the general registers.

Register RH is a 36-bit register. Some of its functions are as follows. It retains addend, subtrahend, multiplicand, or divisor in arithmetic operations. It also provides data storage during control panel operation. The input path to RH is via the U and V shift network. The contents of RH can be gated only to the adder.

Register RQ is a 33-bit register. RQ holds the multiplier or divisor during multiplication or division. RQ is used at various times to inject zeros into the U and V shift network. The input path to RQ is from the RT register. The contents of RQ can be gated to the U and V shift network.

Register RT is a 33-bit register. Generally, RT serves as temporary storage for intermediate results. It also is used as a buffer during the optional direct write operation. The input path to RT is via the shift network. The contents of RT can be gated to any general register or the RQ register.

Figure 2-1. Central Processor Block Diagram Memory Interface Registers. -- There are three memory interface registers: RM, RK, and RL. Register RM is a 32-bit register for holding data received from memory. The input to RM is from memory. The contents of RM are gated to the U and V shift network.

The RK and RL registers are 32 bits each. The RK register holds the addresses for the I-sequence, and RL holds the addresses for the J-sequence (the I and J sequences are explained in the paragraph on Look-Ahead). The input path to either RK or RL is via the  $RP_{04\rightarrow30}$  register or the adder. The contents of either RK or RL are gated to the memory address lines and to the V shift network.

Instruction Registers. -- There are two 14-bit instruction registers, RI and RJ, belonging to the I and J sequences, respectively. Bits 4-7 hold the instruction R-field, which is used to specify one of the general registers. Bits 8 through 14 hold the 2-digit hexadecimal operation code. Bit 0 holds the flag indicator. Bit VI holds the validity indicator. Bit MM is a specialized indicator set by a certain group of instructions. Bits 0, VI, and MM are used as look-ahead controls and are explained in the paragraph on Look-Ahead. The input path to RI or RJ is via the input level of the U and V shift network. The contents of RI or RJ are delivered to various control areas under control of the look-ahead logic.

<u>Program Status Registers.</u> -- There are two program status registers which dynamically retain the status of the program currently being processed by the CP. These registers are designated  $RP_{04\rightarrow30}$  and  $RP_{32\rightarrow63}$ . The  $RP_{04\rightarrow30}$  register is a double-rank register containing the memory address of the next instruction. The  $RP_{32\rightarrow63}$  register retains the following data:

- a. Bits 32 and 33 Condition code, an indication of the result of a comparison operation.

- b. Bit 35 Floating-point normalize mask. When set, inhibits normalization of addition, subtraction, and difference results.

- c. Bit 36 Floating-point underflow mask. When set, enables entry to trap algorithm upon sensing underflow condition during floating-point operations.

- d. Bit 37 Floating-point overflow mask. When set, enables entry to trap algorithm upon sensing overflow condition during floating-point operations.

- e. Bit 38 Fixed-point halfword overflow mask. When set, enables entry to trap algorithm upon sensing a halfword overflow condition.

- f. Bit 39 Fixed-point word overflow mask. When set, enables entry to trap algorithm upon sensing a word overflow condition.

- g. Bits 42-45 Sense switch flip-flops. Used to suppress sense switch contact bounce.

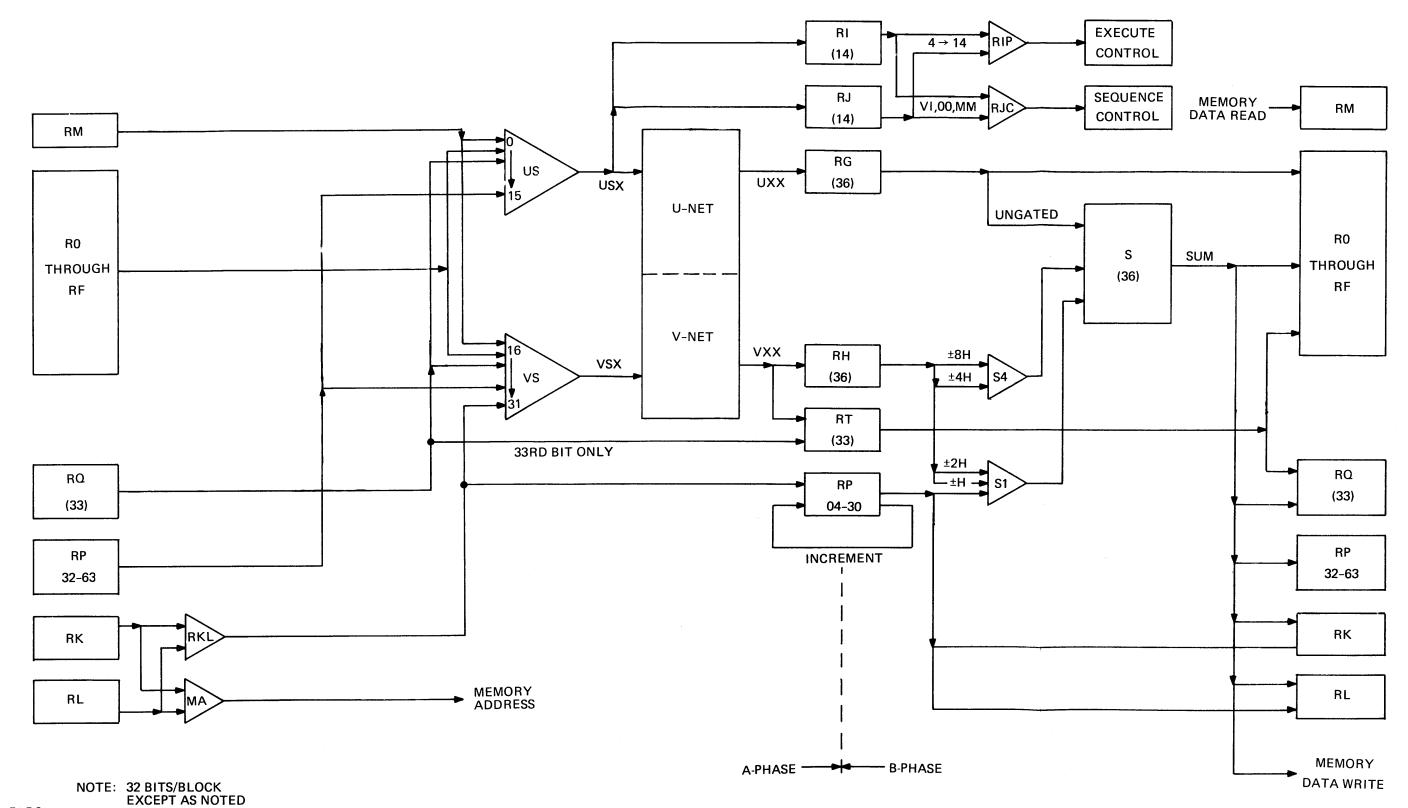

Logic Networks. -- The U and V shift network and the adder are the two logic networks for performing arithmetic, shift, and logic operations on the CP data. Most data transfers from one register to another are via the shift network or adder.

The U and V shift network is 64 bits long and is made up of several layers, or levels. Each level is capable of performing a shift of a certain number of places. The shift network always shifts right and is capable of rotating a doubleword operand 0 through 63 places. The high-order 32 bits of the shift network are designated U, and the low-order 32 bits are designated V.

The adder has 36 stages numbered in order of significance as follows: 60 through 63 and 00 through 31. The adder has a skip-carry or carry-anticipation feature. The RG register is hardwired to the adder. The other data paths to the adder are designated S1 and S4. The adder performs addition and subtraction. The exclusive-OR function is performed by suppressing adder carries.

### NOTE

The inclusive-OR and AND logical functions are performed by algorithm manipulations which are illustrated in the algorithm flow charts.

#### Logic Domains

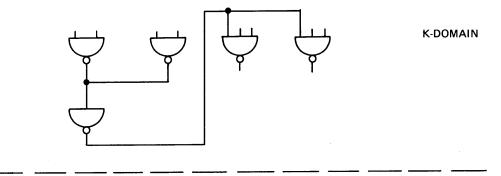

Figure 2-2 shows the structure of the basic CP control logic domains and their relationship to each other. Note that the letter assigned to each domain is the first character of all mnemonics in that domain.

The K-domain consists of variable gating structures used to develop the various keying conditions (such as overflow) required by the A-domain.

The A-domain consists of AND gates used for developing control minterms. The inputs to the A-domain are primarily from the decoders (operation code, R-field, X-field), the timing level generator logic, the K-domain, and the R-domain. Basically, an A-domain gate is selected by an operation code and a specific time (or cycle phase).

The C-domain develops the actual control signals used to gate data into the R-domain registers. Generally, the C-domain structure is as follows. The first level of C-domain gates function as OR gates receiving inputs from the A-domain. The OR-gate output enables a particular AND gate which has a timing requirement; i.e., a set or clear pulse of phase A or B. If the AND gate has a clearing function, its output is sent directly to the R-domain. If the AND gate has a setting function, it is inverted to an assertion signal and then sent to the R-domain.

The R-domain consists of register stages and input gates. Generally, data is ANDed with a C-domain control to set a register stage.

#### NOTE

The flow charts in the H632 Central Processor Instruction Manual illustrate events in the first level of C-domain gates (OR gates). The flow chart analysis tables specify which A-domain signal and function (gate) enabled the C-domain OR gate.

INPUTS FROM: TL, D, R, K, ETC.

Figure 2-2. Typical Control Logic Structure: Logic Domains

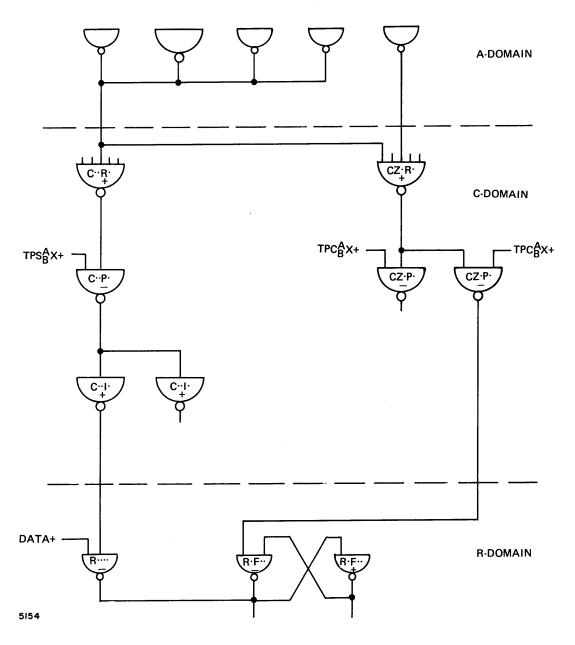

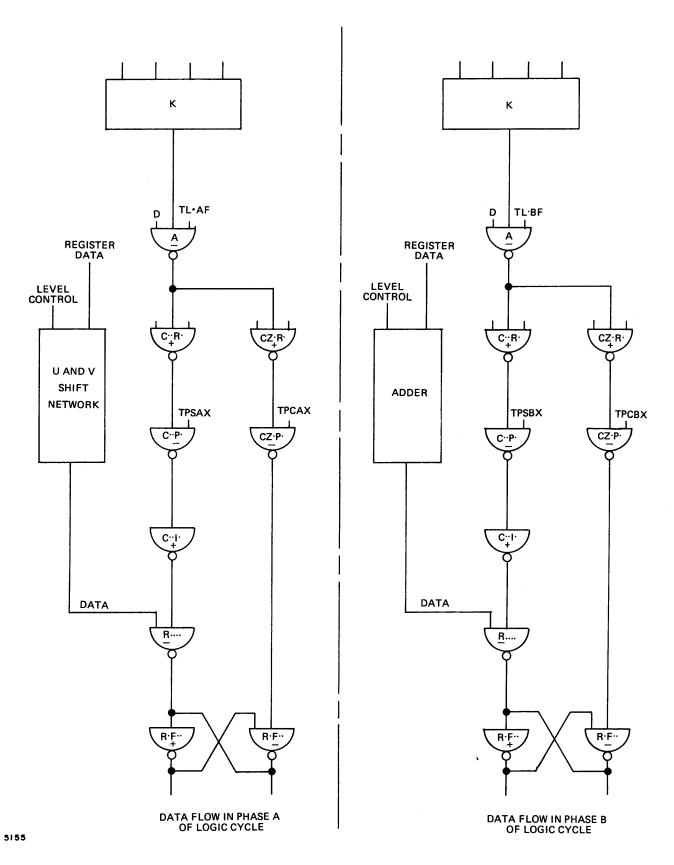

### Control Gating and Data Flow/Cycle Phase

Figures 2-1 and 2-3 show the data flow during the two phases of each logic cycle. During phase A, data is transferred through (and possibly manipulated by) the U and V shift network and then gated into one of the auxiliary registers. If the cycle is a fetch cycle, the instruction is transferred into the proper instruction register at this time.

In phase B, the contents of the appropriate auxiliary register (or registers) are gated into the adder, and the adder output, or result, is gated into an appropriate register or presented to the memory data lines.

#### SEQUENCING AND CONTROL

#### Logic Elements

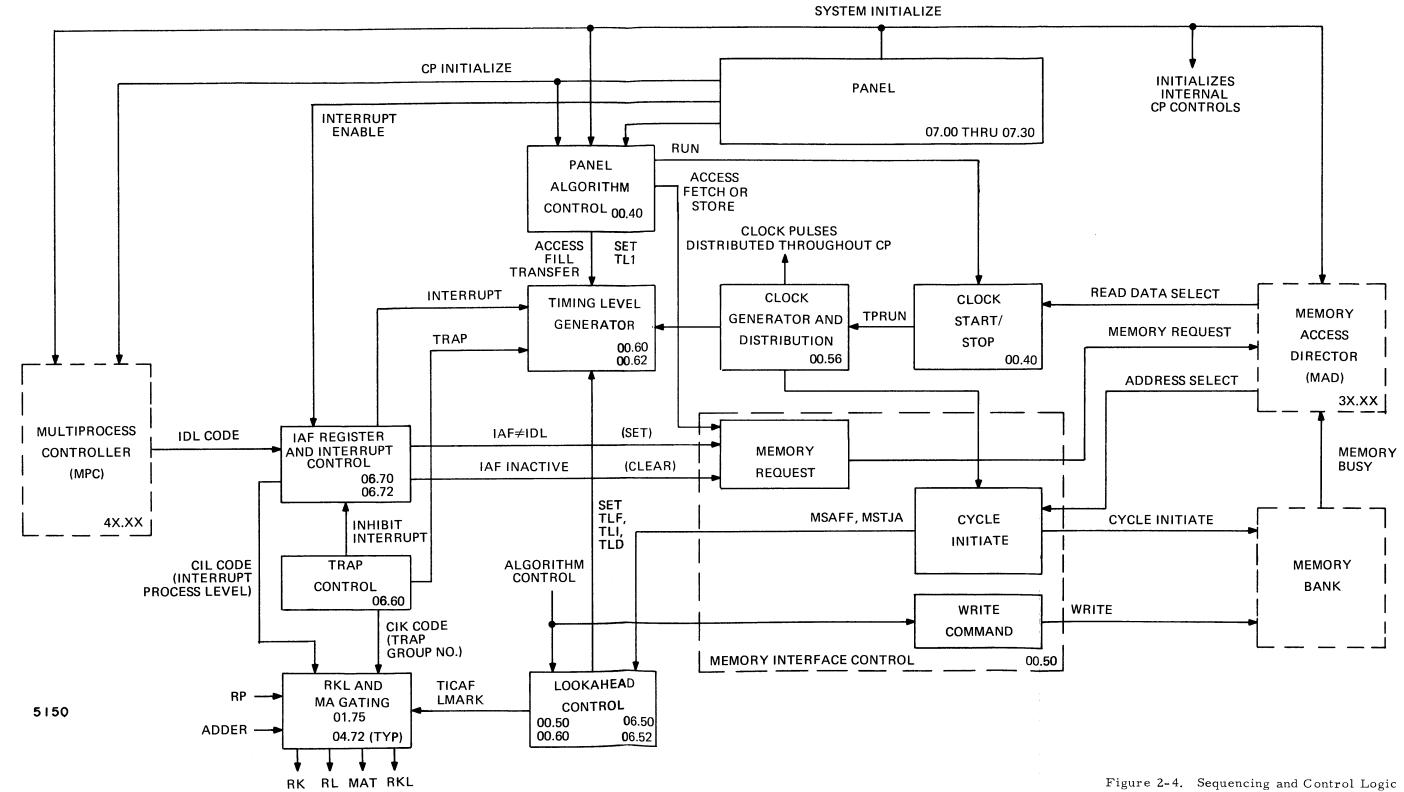

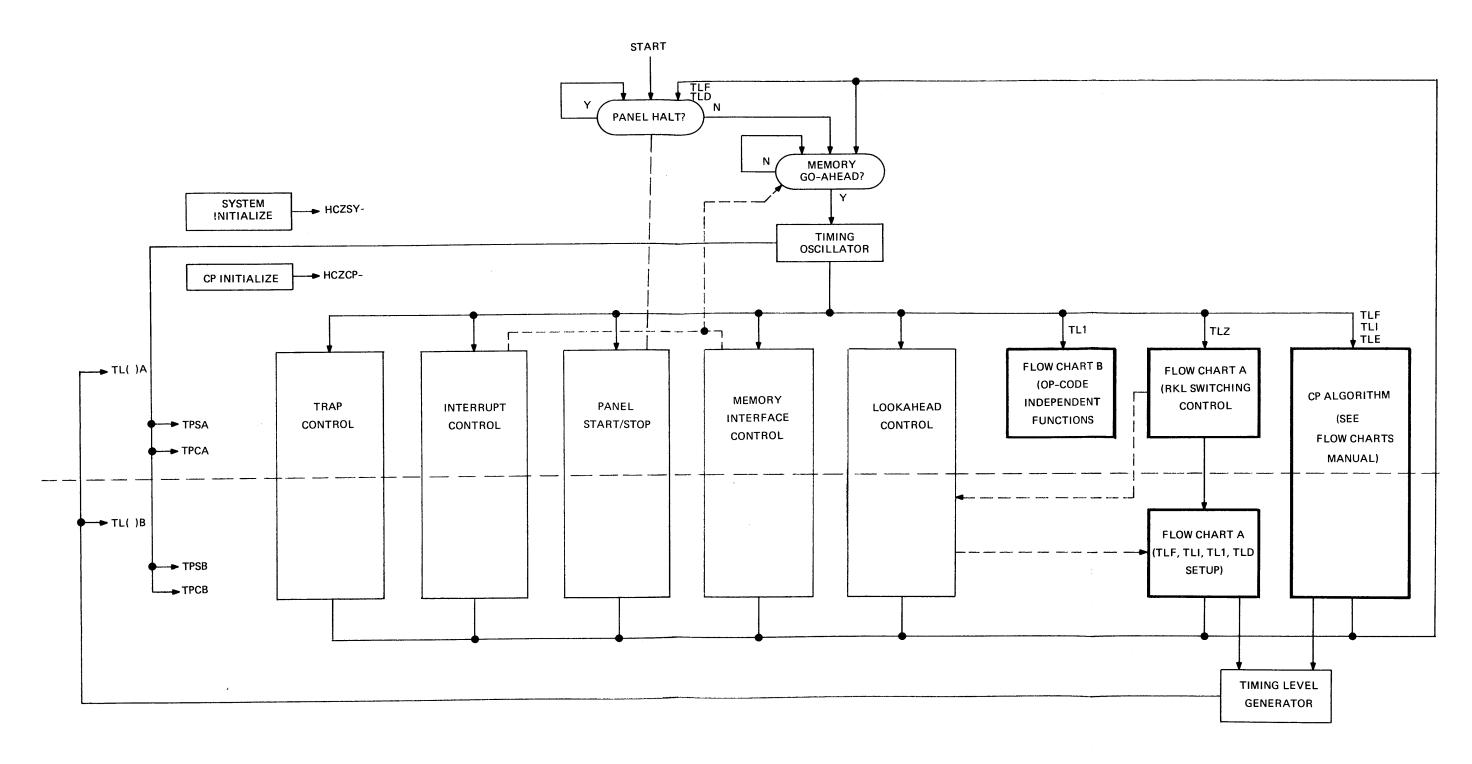

The logic domains described previously perform the data transfer operations that execute all CP algorithms. In addition, sequencing and control logic provides the timing signals and conditional control signals that determine the CP operating sequence from algorithm to algorithm. Figure 2-4 is a simplified block diagram showing the sequencing and control logic structures and the main logic signals used for communication between them.

<u>Panel Functions</u>. -- The panel functions control initializing, startup, panel-directed halts, and the algorithms associated with the panel (access, fill, transfer).

IAF Register and Interrupt Control. -- The interrupt (IAF) register stores the current process level code and compares it to the code on the MPCs IDL lines. When the codes differ, an interrupt algorithm is set up. During the interrupt, the new code is transferred from IDL to IAF. The code in the IAF register, both before and after updating, is applied to RKL, to specify dedicated program stateword locations. When the interrupt is to an inactive process level, the memory request is cleared, and the CP enters the inactive condition. When the MPC supplies a new, valid code, the memory request is set; another interrupt restores active operation.

Memory Interface Control. -- When the CP memory request is set and MAD is granting the CP the next memory cycle, MAD responds with address select, and the CP generates cycle initiate, starting the memory cycle. Memory busy synchronizes events in MAD. During consecutive memory cycles, the CP waits for the trailing edge of read data select before enabling the next set of CP clock pulses. The A-phase clock pulse triggers cycle initiate for the next memory cycle.

When an interrupt brings the inactive process level code into the IAF register, the memory request is cleared. Since MAD does not return an address select, the CP cannot generate cycle initiate. MAD also withholds read data select, so the CP clock is not started. This suspension of operation is the "CP inactive" condition. In this state the CP requests memory cycles only when a fetch or store operation is initiated at the panel.

Figure 2-3. Control Gating Development and Data Flow in Each Logic Cycle Phase

Block Diagram

When MAD is giving memory cycles to the other processor, the CP does not receive address select, and so cannot generate cycle initiate. These brief suspensions of operation (one to five consecutive cycles) are the "memory wait" condition.

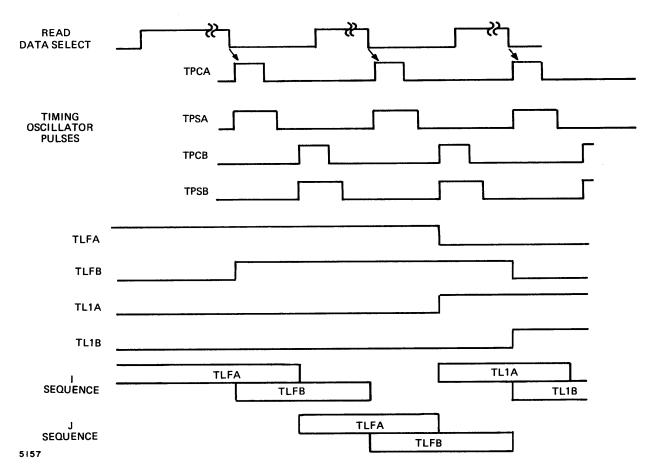

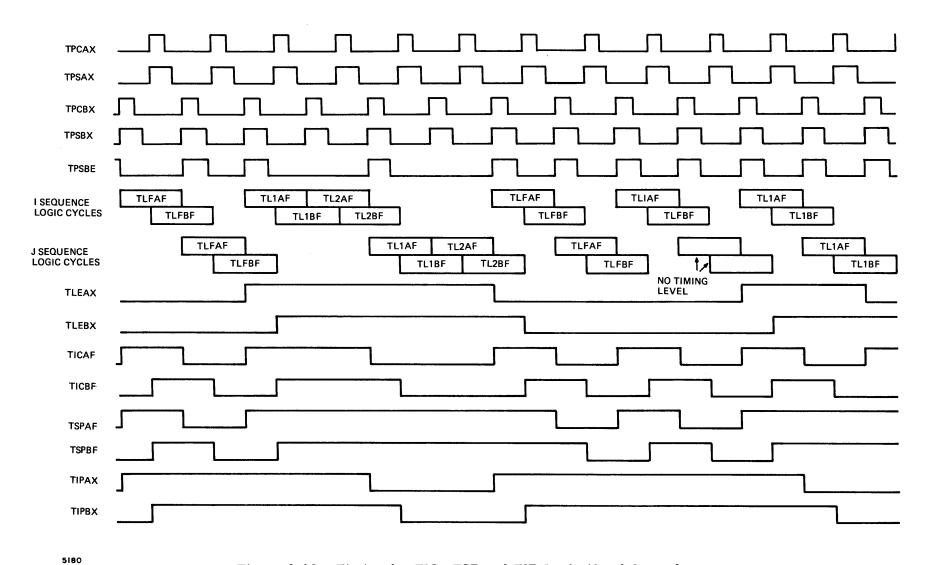

Clock and Timing Level Generator. -- The basic system timing signals are illustrated in Figure 2-5. After each memory cycle, a set of timing pulses (TPCA, TPSA, etc.) is produced by the timing oscillator. The timing pulses gate signals to and from the CP registers and also control the timing level generator.

During each set of timing pulses, one timing level is in effect in the timing level generator. Timing levels are generated in A and B pairs: TLFA-TLFB, TLlA-TLlB, etc. The timing levels enable data gating paths in the A-domain according to the requirements of the algorithm in effect. The timing pulses are applied in the C-domain to actually gate the data to the destination. Phase A timing pulses (TPCA, TPSA) gate data through paths enabled by phase A levels (TLFA, TLlA). Similarly, phase B pulses gate data transfers enabled by phase B levels. In general, TPS pulses perform register setting actions, while the shorter TPC pulses are used for clearing. During each TPSA pulse, the next B-phase timing level is set.

Look-Ahead Control. -- When the CP is in the normal run condition, the sequencing of timing levels is under control of the look-ahead logic, except during the execution phase of an algorithm, when the algorithm itself specifies which execute cycle to enter.

The look-ahead feature permits the concurrent fetch and effective address formation of two sequential instructions. Figure 2-5 illustrates a typical example of a cycle sequence under look-ahead control. The two instructions are each assigned to a sequence (I or J), and each sequence has its own address and instruction register. Figure 2-5 shows a fetch cycle for the I-sequence instruction, followed by a fetch cycle for the J-sequence. Assuming there is no indirect addressing required, the I-sequence enters its execute phase of one or more execute cycles. After the I-sequence instruction is executed, the J-sequence is executed. Generally, the look-ahead feature provides for maximum use of memory. It includes control for cycle entry, gating to and from the instruction and address registers, and guarding against possible conflicts between the two instructions being processed.

Trap Control. -- The trap control logic conditions the timing level generator to set up the trap algorithm when errors are detected after certain arithmetic instructions, or when an unimplemented instruction is fetched. A code is generated which specifies a group number appropriate to the type of trap in effect. The trap group number is used to address a dedicated location during the trap algorithm. Interrupts are inhibited until an arithmetic trap condition has been processed.

RKL and MA Gating. -- This logic selects and distributes memory addresses for the I and J sequences, under control of the look-ahead logic. The CIL and CIK codes specify dedicated memory locations during traps and interrupts.

Figure 2-5. Simplified Central Processor Timing Signals

#### Normal CP Operating Sequence

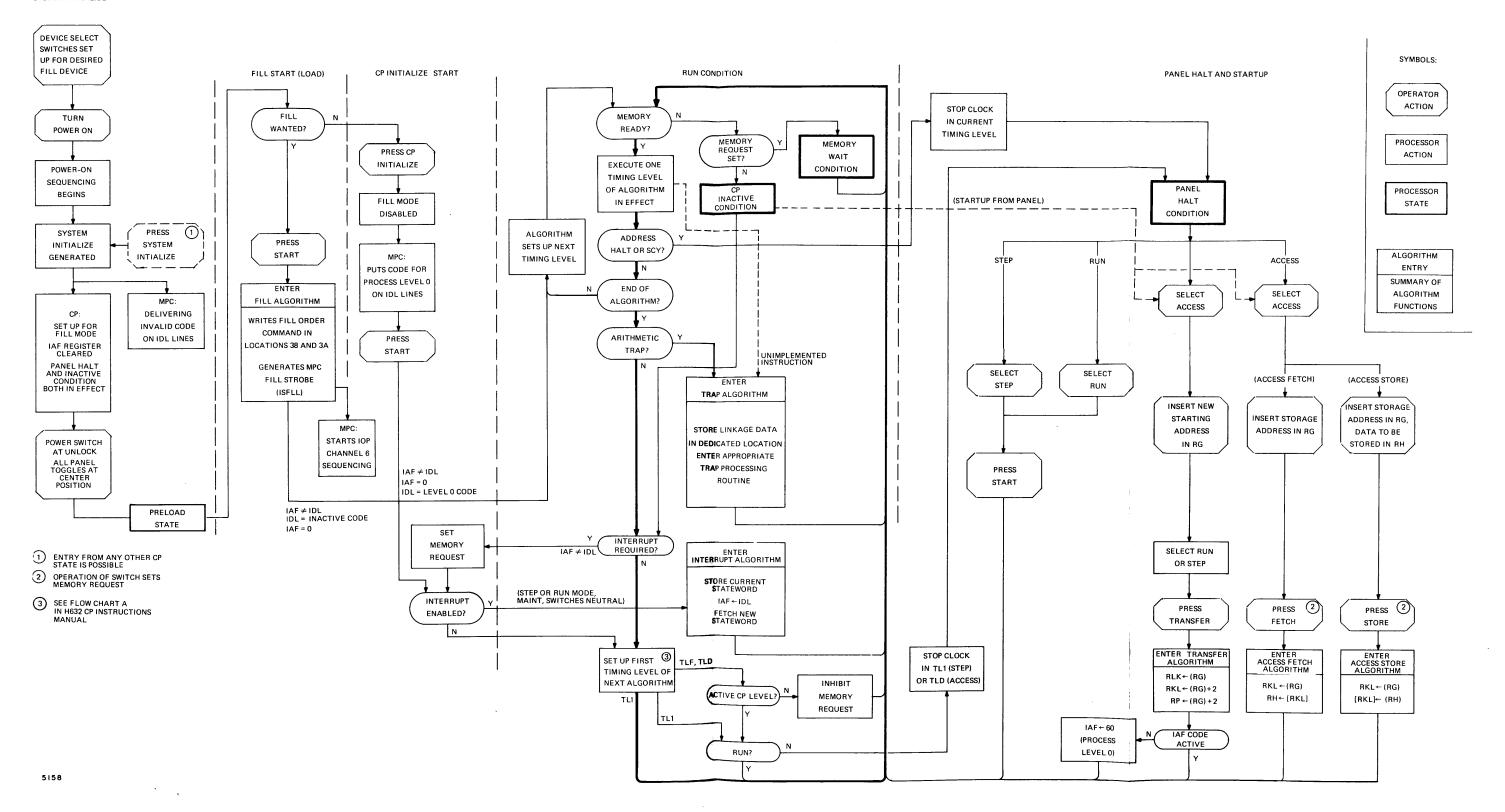

The normal sequence of events from power-on through continuous operation, and the entry points to the CP inactive, memory wait, and panel halt conditions are illustrated in Figure 2-6.

System Initialize. -- Turning the POWER control switch to ON starts the primary power sequence which energizes the system dc power supplies. During the power-on sequence, a time delay relay simulates action of the SYSTEM INITIALIZE button for about a second. In the system initialized state, the CP is prepared to enter the fill mode and is in both a panel halt and the CP inactive condition. (This condition can be reinstated at any time by pressing the SYSTEM INITIALIZE button.) System initialize also transfers a code from the DEVICE SELECT switches on the panel to the RH register. The code specifies the input device that will supply the load program.

Fill Start. -- The CP is prepared to enter the fill (LOAD) algorithm as soon as the START button is pressed. The fill algorithm writes fill order commands in memory locations dedicated to IOP channel 6, and generates the MPC fill strobe which causes the MPC to start IOP channel 6 sequencing.

Immediately after the fill algorithm, because the MPC IDL code is the inactive code and the IAF register is cleared, the CP enters an interrupt. The only significant effect of this interrupt is to transfer the inactive code to the IAF register and clear the memory request. The CP then waits in the inactive condition. If the IOP bootstrap program so specifies, the MPC assigns a new and active CP process level by changing the IDL code. The resulting interrupt starts the CP running at the new process level.

<u>CP Initialize Start.</u> -- If the fill operation is not required, the CP INITIALIZE button is pressed. This clears the fill mode and causes the MPC to place the code for CP process level 0 on the IDL lines. When the START button is pressed, the CP interrupts to process level 0 and starts running.

Continuous Running. -- After a start, in the RUN mode, the CP runs continuously, fetching and executing instructions at the process level specified by the IAF register. The memory request remains set as long as the code in IAF is valid. If MAD is granting memory cycles to the CP, the CP initiates the next memory cycle, executes the current timing level of the algorithm in effect, and sets up the next timing level. Instruction execution continues until there is a trap or interrupt, or until a panel operation causes a halt. After an interrupt to an invalid process level, the CP enters the inactive condition.

Memory Wait. -- Even though the IAF code is valid and the CP is generating cycle request, operation may be suspended because MAD is giving memory cycles to a processor of higher priority. This appears to the CP as a withholding of address select and read data select. Once the other processor has released MAD, the waiting CP memory request

Figure 2-6. Central Processor Sequence of Operations

is recognized and both address select and read data select are restored to normal operation. The CP resumes continuous running. A memory wait condition is possible before each clock cycle of the trap, interrupt, and panel algorithms, as well as the CP execution algorithms.

When the IOP breaks in, the CP is held up in a memory wait for from three to six memory cycles; the IOP then releases control to the CP for at least one cycle.

When a memory wait occurs because the CP has removed its cycle request (CP inactive condition), operation stops until a change in the IDL code from the MPC causes an interrupt or the operator causes a panel start.

Address Halt and SCY Halt. -- During every timing level, if an address halt is present or the panel SCY/RPT switch is at SCY (single cycle), the CP clock stops and the CP enters the panel halt condition. The address halt results when the address for the next memory cycle matches an address manually set into the ADDRESS HALT keys on the panel. A switch at the left of the address keys permits disabling the address halt function. (This feature is an option.)

Traps. -- After a fetch cycle, if the fetched operation code is for an instruction that is not implemented in the system, the CP proceeds automatically to the trap algorithm. A trap can also be entered at the end of the execution of certain arithmetic instructions. After the trap algorithm, instruction fetching and execution resume.

Interrupts. -- The MPC may, asynchronously, change the code on the IDL lines at any time. At the end of each algorithm, when the resulting inequality between the IDL and IAF codes is detected, the CP enters the interrupt algorithm (provided an interrupt is enabled). Statewords of the current process are stored, the new process code is brought into IAF, and the statewords corresponding to that process are fetched. After the interrupt, processing continues at the location specified by the new stateword, provided the MPC code is valid.

<u>CP Inactive Condition.</u> -- After an interrupt, if the inactive code is in IAF, the <u>memory request</u> is cleared. Since no memory cycle occurs, the CP clock stops, and the CP inactive condition is in effect. This condition holds until the MPC delivers an active IDL code, which sets the <u>memory request</u> and causes an interrupt. After the interrupt, processing resumes at the new process level. During the CP inactive condition, the CP can be started from the panel for the duration of the panel access fetch or store algorithm.

Panel Halt. -- The CP may be halted at any time without destroying data by placing the execute control key at STEP or ACCESS. The CP completes the algorithm in effect, performs any waiting traps or interrupts, and then stops the clock. Startup must be controlled from the panel.

Access Mode. -- When the CP is stopped in the access mode, data and addresses may be inserted in RG and RH through the panel ADDRESS/DATA keys, as required for access store, access fetch, and transfer operations. For access fetch or store, startup is initiated by the FETCH or STORE buttons. After completing the selected algorithm, the CP stops in another panel halt.

Transfer. -- For a transfer, the step or run mode must be selected after setting up the starting address in the access mode. When the TRANSFER button is pressed, the transfer algorithm is performed. If the step mode is in effect, the CP enters another panel halt. If the run mode is selected, the CP fetches the instruction at the transfer location and continues running. If a transfer is attempted while the code in IAF is invalid, the transfer algorithm forces the code for process level 0 into the IAF register. After the transfer, the CP enters an interrupt and stores the transfer address in the dedicated location for process level 0. Because the interrupt is to an invalid level, operation then ceases in the CP inactive condition. When the MPC next commands the CP to operate at process level 0, another interrupt fetches the former transfer address, and the CP proceeds from that point in process level 0.

Resuming Continuous Instruction Processing. -- Continuous operation can be resumed from a panel halt by selecting the run mode and pressing START.

Single Instruction Operation. -- When the step mode is selected, the CP performs one full instruction algorithm, plus any waiting traps or interrupts, and then returns to the panel halt condition.

Identifying CP Status at Panel. -- The current status of the CP can be determined by inspecting a few indicators on the console. See Table 2-1.

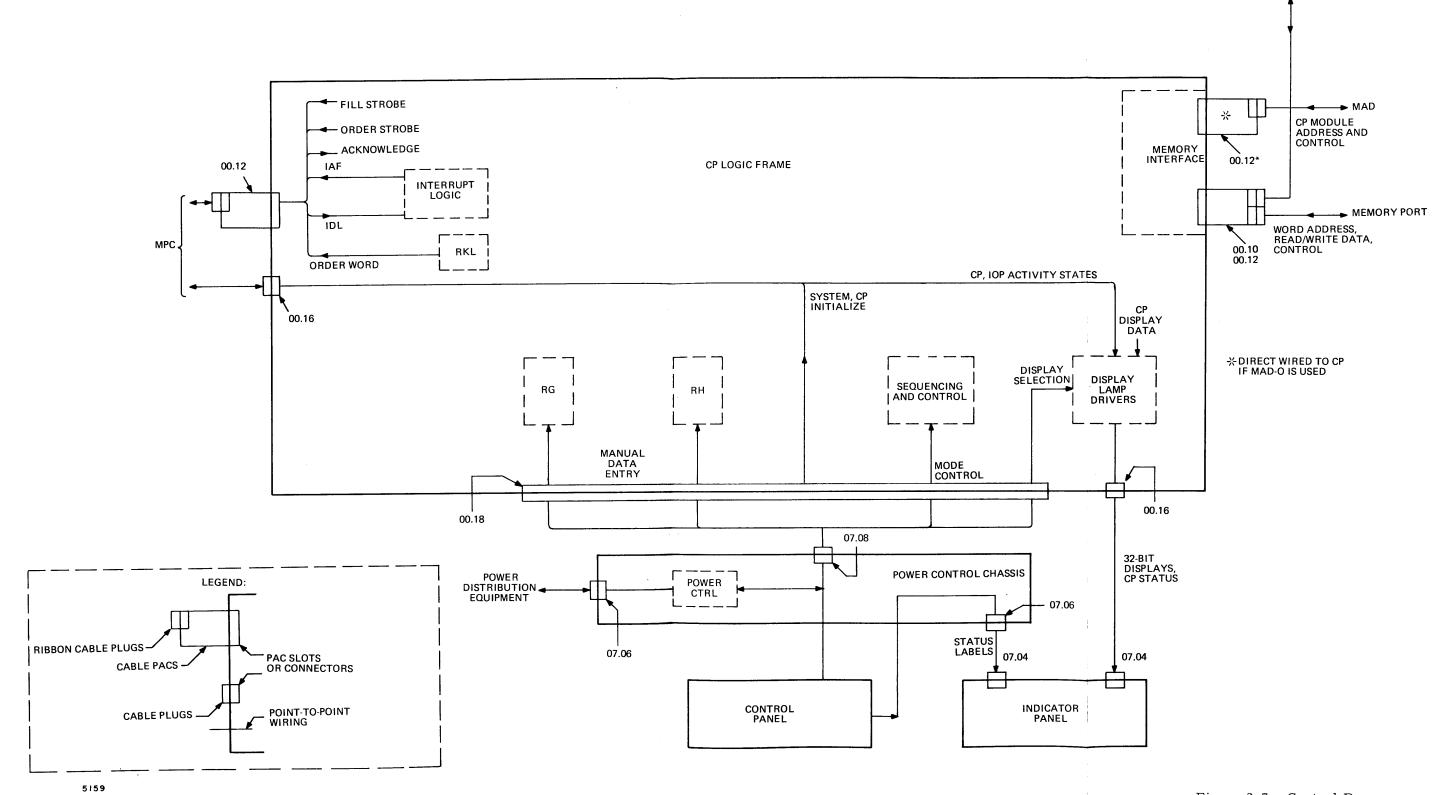

#### **CPINTERFACES**

The CP logic frame is interfaced directly to the MPC and to MAD and the memory system. In addition, there is a connection to the IOP, actually a tandem connection to the main data/address bus to the memory port. (Either the CP or the MPC controls the bus through the bidirectional cable PACs.)

The control panel, indicator panel, and power control chassis (considered a part of the CP) interconnect to the CP logic frame through connectors. Interconnections to the system power distribution equipment are brought in through the power control chassis.

Figure 2-7 summarizes the methods of interconnection (cable PACs, connectors, or direct wiring). Wire-by-wire connection details and signal mnemonics appear in the logic diagrams specified in the illustration.

Table 2-1.

CP Start/Stop Condition Summary

|                                         | Panel Indicators   |     |                           |                                                        |

|-----------------------------------------|--------------------|-----|---------------------------|--------------------------------------------------------|

| CP Condition                            | CP ACTIVE          | RUN | TLG                       | Other                                                  |

| System Initialize                       | OFF                | OFF | TLl                       | LOAD                                                   |

| CP Initialize                           | ON                 | OFF | No change                 |                                                        |

| Normal Run                              | ON                 | ON  | Changing                  |                                                        |

| Panel Halt:                             |                    |     |                           |                                                        |

| Step                                    |                    | OFF | TLl                       |                                                        |

| Access                                  |                    | OFF | None (TLD)                |                                                        |

| SCY or Address Halt                     |                    | OFF | Any                       |                                                        |

| CP Inactive                             | OFF                | ON  | TLF                       |                                                        |

|                                         | Unusual Conditions |     |                           |                                                        |

| Memory Wait                             | ON                 | ON  | Any                       | (See Note)                                             |

| Wait for Control<br>Process Acknowledge | ON                 | ON  | TL6                       | Op code = \$30<br>(See Note)                           |

| Indirect Hangup                         | ON                 | ON  | TLF & TLI<br>or TLI alone | R-field and Op code<br>not changing<br>(Program Error) |

| Indefinite Execute Loop                 | ON                 | ON  | Changing                  | Op code = \$4A<br>(Program Error)                      |

#### NOTE

Normally, these waits are a few microseconds or less. If the CP pauses long enough for the condition to be seen at the panel, there is a hardware fault.

### MPC Interface

The MPC has two interface connections to the CP. One exchanges process level codes and delivers an order code word and strobe during control process instructions. Sampling of the IDL code and gating from the IAF register to the MPC are discussed under Interrupt in Section III. See the Control Process Instruction Flow Chart and Analysis for detail on the order code word, order strobe, and acknowledgment.

The other interface supplies IOP and CP activity state data for display at the control panel; see the Console Control and Display Panel description in Section III.

### Memory Interface

Interconnections to the Memory Access Director and to the memory port (shared with the IOP) are discussed in the Memory Interface description in Section III.

Figure 2-7. Central Processor Interface Connection Summary

# Control Panel and Power Control Interconnections

See the Console Control and Display Panel description in Section III for details.

## Cable PACs

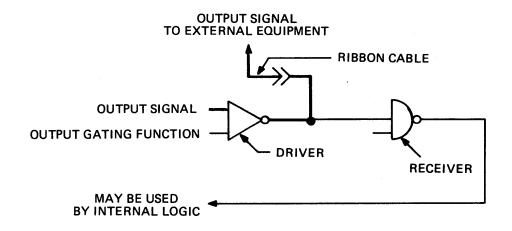

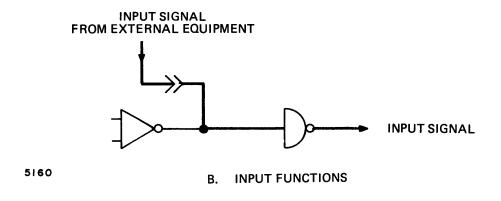

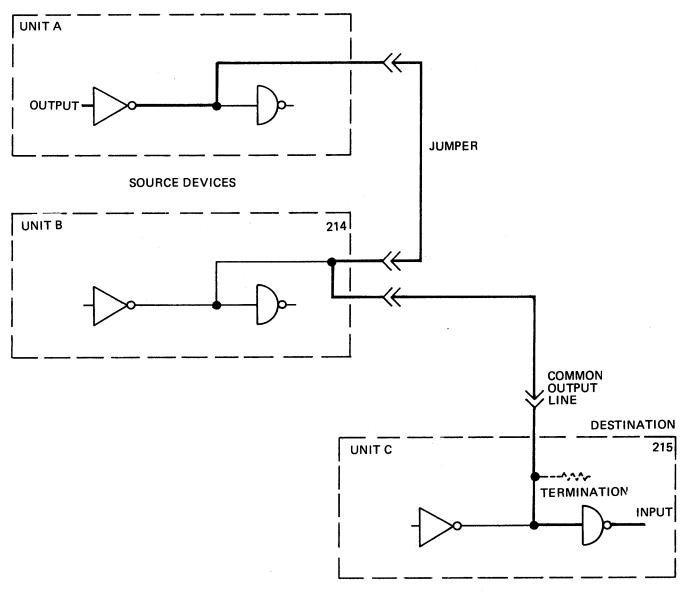

Special cable PACs are used for one-way and bidirectional information transfer at the CP, at MAD, at the IOP, at the memory port interface and at all IO controllers. Each PAC contains ten driver-receiver circuits of the type illustrated in Figure 2-8. The circuits permit gated data transfer in either direction along a single interconnecting cable. On some PACs (type CC-214) each circuit is wired to the same pin on two identical ribbon cable connectors. This permits data to be placed on, or read from, a given line by different devices. (See Figure 2-8C.) Memory address, read/write data, and control lines from both the IOP and CP are applied to common lines in this way.

Type CC-215 cable PACs have a single connector only; each receiver circuit contains resistors which terminate a cable or chain of cables.

### A. OUTPUT FUNCTIONS

Figure 2-8. Cable PAC Applications (Sheet 1 of 2)

5161

Figure 2-8. Cable PAC Applications (Sheet 2 of 2)

#### SECTION III DETAILED THEORY

Figure 3-1 maps the functions that are active in the CP during execution of an algorithm. The primary functions (bold outlines) are the operational CP algorithms (fetch, indirect cycle, instructions, panel functions, trap, and interrupt) which execute the actual program. These primary functions are described in detail in the flow charts and instruction analyses of the H632 Central Processor Instructions manual.

Secondary functions (single-weight lines) operate during the same timing levels as the primary algorithm to anticipate interrupts, detect trap conditions, control the memory interface, permit operator control at the proper time, and control the cycle look-ahead function. These sequencing and control functions are described in this section with the use of detailed flow charts or timing diagrams.

START-STOP, TIMING, AND CONTROL LOGIC

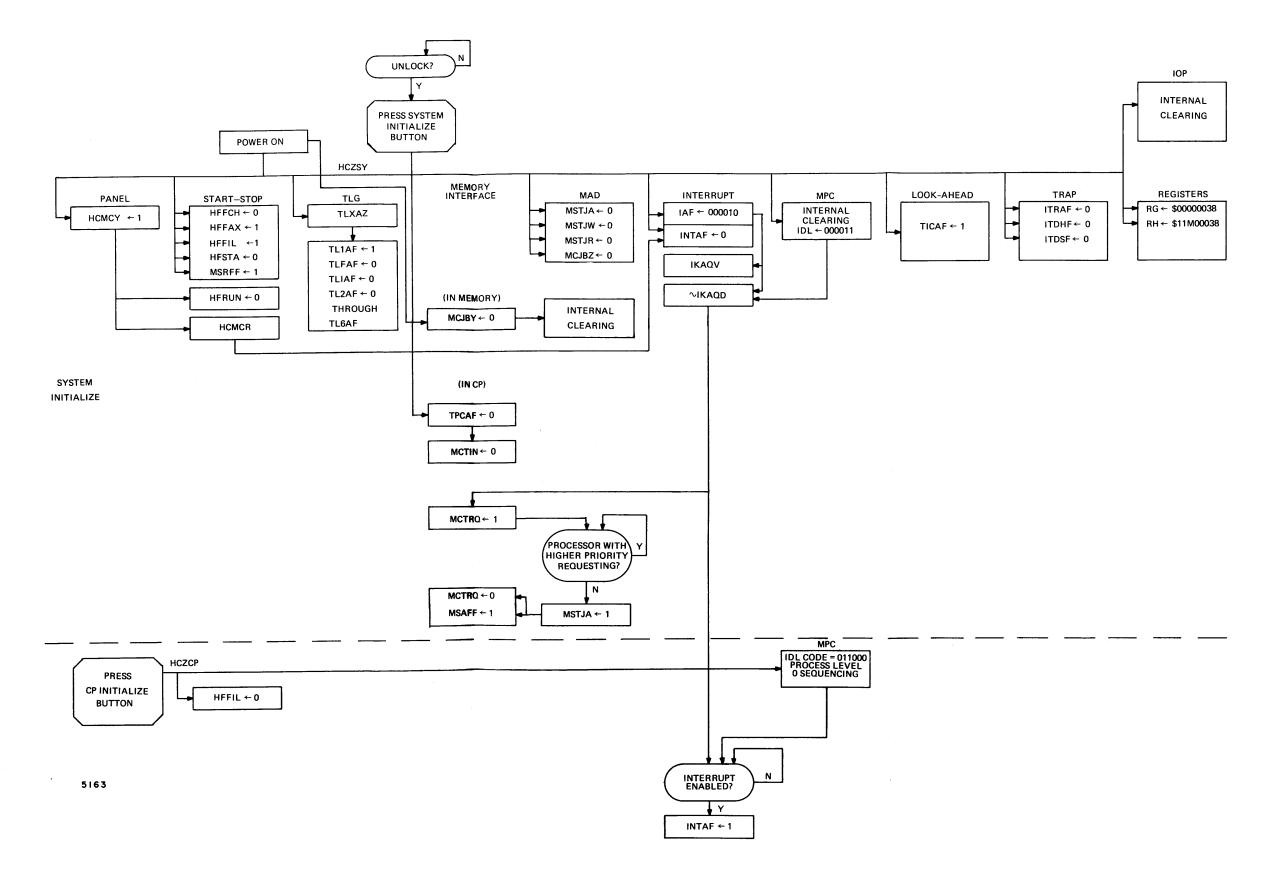

### System Initialize (See Figure 3-2.)

Turning power on or pressing the SYSTEM INITIALIZE pushbutton (with the power switch at UNLOCK) presets a known starting condition in the CP sequencing and control logic, and also in MAD, the MPC, and the IOP.

Start-Stop Logic. -- The fill flip-flop is set and conditions are set up for a panel-halt condition (the clock will not run until a manual start from the panel is executed). Once started from the panel, the CP enters the fill algorithm.

Timing Level Generator. -- The TLXAZ signal clears all timing level flip-flops except TL1A, in preparation for the fill algorithm (or an interrupt, after CP initialize).

Memory Interface. -- System initialize clears TPCAF, disabling cycle initiate. The memory busy line is cleared in memory during power turn-on.

Memory Access Director (MAD). -- Pressing the SYSTEM INITIALIZE pushbutton clears the main CP interface data and address select signals. The memory busy line also initializes MAD internal timing circuits.

5162

Figure 3-1. Time Sharing of Execution Functions with Sequencing and Control Functions

Figure 3-2. System Initialize and Central Processor Initialize Flow Chart

Multiprocess Controller (MPC). -- The system initialize condition forces code 000011 (the inactive code) on the IDL lines from MPC to the CP.

Interrupt Logic. -- The system initialize condition sets an inactive level code in the IAF register and clears the interrupt flip-flop. The difference between the IDL code from MPC and the IAF register code is detected by IKAQD, and the memory request flip-flop is set. The memory request is received by MAD; if no higher priority processor is requesting a memory cycle, MAD responds with address select. The CPs memory request is cleared by address select.

Trap Logic. -- The three trap-condition flip-flops are cleared.

Registers. -- In preparation for a fill operation, register RG is loaded with \$00000038 (the CS1 location for IOP process level 6), and register RH is loaded with \$11M00038. The latter is a fill order transmission command addressed to device 000 of controller 1M (M is the code manually set into the panel device select keys).

Look-Ahead Logic. -- The system initialize condition sets the TICAF flip-flop.

<u>Input/Output Processor (IOP)</u>. -- Internal logic is preset to a known starting condition (no effect on CP).

CP Initialize (See Figure 3-2.)

The CP INITIALIZE button clears the fill flip-flop in the start-stop logic and also forces the code for process level 0 on the IDL lines from the MPC. The interrupt flip-flop is set (unless interrupt is disabled from the panel).

Start-Stop Logic (See Figure 3-3.)

The start-stop logic (LBD 00.40) controls an orderly computer startup after system or CP initialize and controls stopping of the clock oscillator in the step or access mode, during an address halt (optional), or when the single-cycle (SCY) maintenance mode is selected. Continuous running and startup depend on a go-ahead from the memory interface logic.

System Initialize. -- Power turn-on or pressing the SYSTEM INITIALIZE button sets the fill flip-flop (HFFIL) and initializes the start-stop controls for a halt condition. (HFSTA and HFRUN are cleared.) The timing level generator is set up in TL1A. The mode key is assumed to be in RUN, with the power switch at UNLOCK.

Figure 3-3. Start-Stop Logic Flow Chart

Startup from System of CP Initialize. -- In a normal operating sequence, if a fill operation is desired, the START button is pressed and released. Because MAD and the memory are also initialized, the TPRUN flip-flop is set as soon as the RUN flip-flop (HFRUN) is set. The CP is then running in the fill algorithm.

After a CP initialize, the fill flip-flop is cleared. When START is pressed and released, the CP is running in an interrupt algorithm. The interrupt is followed by normal continuous running and execution of the program level brought in by the interrupt.

Continuous Running. -- Program execution of the current process level continues until the step mode is selected or an interrupt brings a different MPC code to the IAF register.

While the run mode is in effect and the process level in IAF is valid, the start-stop logic maintains clock synchronization with the memory interface. The memory-wait flip-flop (MSRFF) is cleared during TPCA. Both the leading and trailing edges of read data select (MSTJR) must be received in order for the clock to proceed. The leading edge is stored by MSRFF. (After a system or CP initialize, MSRFF is waiting-set.) Ordinarily, MSRFF is set during timing level B, but the trailing edge of MSTJR does not occur until after TPCB. As a result, TPRUN is cleared by TPCB. As soon as MSTJR ends (the memory go-ahead), TPRUN is set, and another cycle of clock pulses is generated.

Memory Wait. -- When MAD has given another processor access to the memory bank (or an inactive MPC code has removed the CP memory request), the CP waits with the clock stopped. MSRFF and TPRUN are cleared and MSTJR is zero. When MAD returns control to the CP (or when an active MPC code is received), read data select is received, MSRFF and TPRUN are set, and normal running resumes. (See the Memory Interface description.)

Panel Halt. -- Continuous running can be stopped from the panel by placing the mode key in STEP or ACCESS, by selecting the SCY maintenance mode, or by using the ADDRESS HALT option.

In the step mode, when the CP has fetched an instruction and formed its effective address, the run flip-flop (HFRUN) is cleared during TPSA. During TPSB, TPRUN is cleared, stopping the clock in the panel halt condition with TLlA set.

In the access mode, during the last execution cycle of the algorithm, the run flip-flop is cleared by TPSA. HCMAC prevents setup of the next fetch cycle. During TPCB, TPRUN is cleared and the CP stops in dummy timing level TLD (no timing level set).

In any timing level, if SCY is on or an address halt is present, HFRUN is cleared. During the following TPCB, TPRUN is cleared and the panel halt is in effect.

Step Startup. -- When the START button is pressed and released, HCGGO sets the run flip-flop. If MSRFF and MSTJR are in a memory go-ahead condition, the TPRUN flip-flop is set and one full algorithm is executed. A normal step halt occurs with TLlA of the next algorithm set up and waiting to be executed.

Transfer Startup. -- If TRANSFER is pressed instead of START, HFFXR and HFFAX are set as the effective op code for the transfer algorithm, and TLIA is set up in the timing level generator. TPRUN is set as in START (if there is a memory go-ahead), and the CP performs the transfer algorithm.

After a transfer from the step halt condition, a normal step halt occurs with TLlA of the next algorithm waiting to be executed. If transfer is initiated in the run mode, continuous operation resumes at the new instruction location.

Access Fetch and Store. -- With the mode key in ACCESS, startup is controlled by the FETCH or STORE button. When the FETCH button is pressed, the HFFCH and HFFAX flip-flops are set as the effective op code for the access fetch algorithm and TLlA is set up in the TLG. When the FETCH button is released, HCGGO starts the clock (assuming a memory go-ahead), and the access fetch algorithm is performed. During the last execution cycle of the algorithm (TLZAX), HFRUN is cleared, and the clock is stopped in the panel halt condition.

When the STORE button is pressed and released, the start-stop logic operates as in access fetch, except that the HFFCH flip-flop is cleared to provide the effective op code for the access store algorithm.

If the panel RPT (repeat) maintenance switch is on, the access fetch and store algorithms do not generate TLZAX; access continues until the RPT switch is turned off.

Clearing the Console Algorithms. -- Any operation of the transfer, fetch, or store buttons sets HFFAX, which serves as a part of the effective op code for panel algorithms. One other start-stop control flip-flop (such as HFXFR, for transfer) contributes to the op code. System initialize also sets HFFAX to enable the fill algorithm.

At the end of any panel algorithm, TPSBE clears HFFAX. During the following TPCA, HFXFR and HFFIL are cleared so that no console algorithm is in effect.

Returning to Continuous Run. -- When the run mode is selected after a step or an access operation, startup can be controlled either by the START or TRANSFER button. If the START button is used, the CP fetches and begins execution of the current instruction. If the TRANSFER button is used, the transfer algorithm is executed, and continuous instruction processing begins at the address manually inserted in RG. (See Normal CP Operating Sequence in Section II for information on attempted transfer in the CP inactive condition.)

Single-Cycle Operation. -- If SCY (single-cycle) operation is selected by use of the maintenance panel switch, the HFRUN flip-flop is cleared unconditionally. After every operation of the START, TRANSFER, FETCH, or STORE button, the HFRUN flip-flop is set, then cleared every TPCA time, when the HFSTA flip-flop is cleared. This mode permits the operator to step through the current algorithm one clock cycle at a time.

The first time the TRANSFER, FETCH or STORE button is pressed, TLXAZ sets the timing level generator to TL1A. Thereafter, each operation of the button steps the CP through one clock cycle of the selected algorithm. The (TLEAX) \( \lambda \tau \text{TL1A} \) input to TLXAZ prevents setup of TL1A again until the algorithm is complete.

Address Halt (Optional). -- This optional logic (shown on LBD 00.42) compares the current memory address on the MAT lines with the settings of the ADDRESS HALT keys on the panel. When the addresses match, HCHLL and HCHLH cause entry to the panel halt condition by clearing HFRUN.

# Timing Oscillator and Clock Distribution (LBD 00.56)

Once it is triggered by TPRUN from the start-stop logic, the timing oscillator PAC generates one set of clock pulses: clear A, set A, clear B and set B. The basic signals are produced by the TPCAX, TPSAX, TPCBX and TPSBX gates, controlled by the three delay lines. Idealized timing is shown in Figure 3-4. TPCBX clears the TPRUN flip-flop preventing more clock pulses until the "panel run" and "memory go-ahead" conditions are in effect.

The four basic signals are fanned out through load-balancing resistors to distributing gate PACs, one in each quadrant of the central processor frame. The active signals (TPSA1, etc.) are wired from the distributing gates to logic circuits nearby. The delay lines can be adjusted so that the active signals approach the timing shown in Figure 3-4 in spite of gate and propagation delays.

The TPXXX signal clears MSAFF and also provides for an early clear of the write flip-flop (MCTWR) in cases where a memory write cycle is followed by a read cycle. (See the Memory Interface description.)

# Timing Level Generator (LBD 00.60)

The timing level generator consists of the flip-flops that store the current CP timing state, and the logic gates that determine the next timing state. Timing levels are divided into two phases, A-phase and B-phase. At any given time, no more than one A-phase and one B-phase flip-flop are set.

Sequencing from state to state is triggered by the timing oscillator pulses. A fetch cycle, for example, starts with TLFA set. The next TPSA clock pulse executes the TLFA functions and sets up the TLFB flip-flop. The following TPSB clock pulse executes the TLFB functions and sets up the next A-phase timing level.

Entry into the TLFA, TLIA, and TL1A states is controlled by instruction look-ahead, interrupts, and trap conditions. More details appear under those headings and in flow chart A of the Central Processor Instructions manual.

#### **NOMINAL TIMING (NS)**

Figure 3-4. Clock Oscillator Timing

Execution of every algorithm starts in TLlA. Some instructions complete execution during a single cycle. Algorithms that require more execution cycles arbitrarily select a sequence of other timing states (TL2A-TL2B, etc.).

Figure 3-5 illustrates a series of timing levels during execution of a console access fetch or store algorithm. Timing level TLlA is set up when the console FETCH or STORE button is pressed (or also by a <u>system initialize</u>). When the switch is released, HCGGO starts the timing oscillator and the timing pulses advance the timing levels. The access fetch/store algorithms arbitrarily proceed from TLlA to TL6, TL2, and TL3. If the console RPT (repeat) button is off, the algorithm ends in a panel halt after TL3, as illustrated. (With the RPT button on, TL2 and TL3 repeat indefinitely.)

In the access mode, TLFAF is inhibited by HCMAC, so the algorithm ends with no timing level flip-flop set. This is the "dummy" timing level called "TLD" elsewhere in this manual and in the Central Processor Instructions manual. Dummy timing levels are also set up during overlapped instruction execution, to resolve precedence conflicts between the I and J sequences. (See description of Look-Ahead.)

Figure 3-5. Timing Level Generator Signals During Access (Example)

Figure 3-5 illustrates signals that keep track of the execution portion of an algorithm. The TLEAX flip-flop is set during TLlA of each algorithm and kept set through the last execution A-phase. The TLEBX flip-flop is kept set during all B-phases of the algorithm. The last execution cycle of each algorithm is identified by the TLZAX signal, which permits the TLZBF flip-flop to be set by the next TPSA pulse. The TLZBJ and TPSBE signals contribute to the TLlA, TLIA, and TLFA setup logic to be discussed under "Look-Ahead."

The notation at the top of Figure 3-5 represents the current timing state of the CP in relation to other internal or external events.

# Interrupt Register and Control (LBD 06.70 and 06.72)

IAF Register. -- The interrupt register stores the currently active CP process level and compares it with the process level code from the MPC. When the codes are unequal, IKAQD goes false and causes an interrupt during the next timing level (if interrupt is enabled). During TL3 of the interrupt, the MPC code on the IDL lines is transferred into the IAF register. (Thereafter, the MPC and IAF codes are equal; IKAQD is true until the MPC changes its code again.)

Interrupt Controls (See Figure 3-6). -- When a change in the MPC code is detected by the interrupt register during any timing level except TLlA, IKAQD sets INTAF (provided interrupt is enabled and no arithmetic-exception trap condition is present). INTAF enables the timing level generator to enter TLlA during the last execution cycle of the instruction in progress, or during a dummy cycle, F-cycle, or I-cycle. During TLlA of the interrupt algorithm, INTBF is set. INTBF serves as the equivalent of an interrupt op code, enabling the minterms which execute the interrupt algorithm.

Enabling Interrupt. -- In normal run or step operation, with all maintenance switches at the neutral center position, interrupt is enabled from the panel. In the access mode, interrupt is inhibited; since addresses are set up manually, the active process level is unimportant. The maintenance switches affect interrupt as follows:

ENI/INI at INI Permits single-instruction stepping without interruption to another process level

SCY/RPT at SCY Permits single-clock-cycle stepping without interrupt to another process level

SCY/RPT at RPT Prevents interrupt during repetition of algorithms

ENI/INI at ENI Enables interrupt in spite of SCY to permit single-cycle checkout of the interrupt algorithm itself

Even when interrupt is enabled from the panel, an arithmetic-exception trap condition postpones the interrupt until the trap operation is complete.

<u>CIL Gates.</u> -- Under control of the interrupt algorithm, the code in IAF is transferred through the CIL 24 through 29 gates to RKL, to identify the location of the program statewords for the interrupted and interrupting process levels.

Figure 3-6. Interrupt Control Flow Chart

Inactive Code Detector. -- The IKAQV decoder monitors IAF 24, 25 and 28 for an inactive code of the form 00XX1X. When the MPC inactive code (000011) has been stored in IAF by an interrupt, IKAQV becomes false. When the interrupt is over and the TLG enters TLF, the memory request flip-flop (MCTRQ) (LBD 00.50) is cleared. The CP waits in the CP inactive condition until a new MPC code is received. IKAQD then becomes false, sets the memory request flip-flop, and starts another interrupt by setting INTAF (assuming interrupt is enabled from the panel).

IKAQV also modifies the transfer algorithm when IAF contains an inactive code.

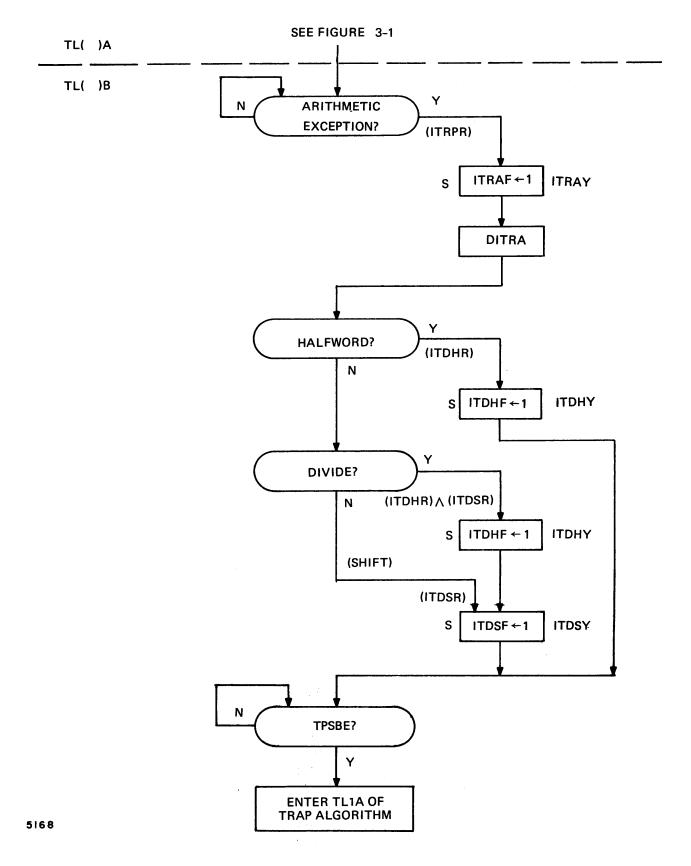

# Trap Control Logic (LBD 06.60) (See Figure 3-7.)

Arithmetic Exception. -- When an arithmetic exception occurs, the ITRAF flip-flop is set during TPSB. At the end of the instruction, flow chart A detects ITRAF and sets up TLlA of the trap algorithm. ITRAF takes precedence over a waiting interrupt by preventing INTAF (LBD 06.72) from setting. The ITDHF and ITDSF flip-flops are set at the same time as ITRAF to further subdivide the type of arithmetic trap.

During TLlA of the trap algorithm, ITRBF is set. ITRAF and ITRBF generate DITRA and DITRB, which serve as effective op codes during the trap algorithm. ITRAF is cleared during TL6B of the trap algorithm. ITRBF is cleared during the following TL1A.

<u>Unimplemented and Undefined Operations</u>. -- Also contributing to DITRA and DITRB are terms generated when unimplemented or undefined operation codes are detected:

| DIUNA, B | Undefined Operation                    |

|----------|----------------------------------------|

| DIFLA, B | Unimplemented Floating Point Operation |

| DIEXA, B | Unimplemented Extended Operation       |

| DIBBA, B | Unimplemented Byte Operation           |

These terms do not set ITRAF and so do not take precedence over waiting interrupts. When an undefined or unimplemented instruction is fetched, the CP proceeds with the trap algorithm rather than an instruction algorithm.

Trap Condition Class Code Generation. -- Early in the trap algorithm, the CP accesses a dedicated location to obtain a pointer to one of four class entry tables. The address of the dedicated location is encoded when CIKRC enables ITCOV, ITCUN, and ITCEB, which control CYK24 through CYK30 on LBD 01.75. The four class codes are generated as follows:

| _  |                                                     |    |    |     |     |    | <u> </u> |    |      |            |

|----|-----------------------------------------------------|----|----|-----|-----|----|----------|----|------|------------|

|    | Trap Class                                          | 24 | 25 | 26  | 27  | 28 | 29       | 30 | (31) | Hex Equiv. |

| I  | Arithmetic Exception (ITCOV)                        | 0  | 0  | 0   | 1   | 0  | 0        | 0  | 0    | 10         |

| п  | Unimplemented Floating Point (ITCUN)                | 0  | 0  | 0   | 1   | 0  | 0        | 1  | 0    | 12         |

| ш  | Unimplemented Extended or Byte<br>Operation (ITCEB) | 0  | 0  | . 0 | . 1 | 0  | l        | 0  | 0    | 14         |

| IV | Undefined Operation (ITCUN, ITCEB)                  | 0  | 0  | 0   | 1   | 0  | 1        | 1  | 0    | 16         |

Figure 3-7. Trap Control Flow Chart

Addressing Trap Condition Table Locations. -- Later in the trap algorithm, one of the locations in the selected trap class entry table is accessed to obtain to the trap processing routine. The offset from the initial table address is produced when CIKRO enables a code on CIK27 through CIK30. These signals drive CYK27 through CYK30 on LBD 01.75. The code is related to trap class subdivisions in Table 3-1.

Table 3-1.

Trap Condition Table Entries

|               | Trap Condition Class |         |         |         |  |  |

|---------------|----------------------|---------|---------|---------|--|--|

| Bits 27-31 of | I                    | II      | III     | IV      |  |  |

| Table Address | Arithmetic Exception | Op Code | Op Code | Op Code |  |  |

| 00000         | X                    | X       | X       | X       |  |  |

| 00010         | X                    | x       | x       | x       |  |  |

| 001 00        | -                    | E2      | E0      | -       |  |  |

| 00110         | -                    | C2      | C0      | -       |  |  |

| 01 000        | Overflow on fullword | 82      | В0      | Α0      |  |  |

| 01 01 0       | Overflow on shift    | 92      | 90      | 80      |  |  |

| 01100         | Overflow on halfword | F2      | F0      | A2      |  |  |

| 01110         | Zero division        | D2      | D0      | 82      |  |  |

| 10000         | <del>-</del>         | A6      | 24      | -       |  |  |

| 10010         | •<br>•               | 86      | -       | -       |  |  |

| 10100         | -                    | . E6    | 26      | -       |  |  |

| 10110         | -                    | C6      | 06      | -       |  |  |

| 11000         | -                    | В6      | 2C      | 20      |  |  |

| 11010         | -                    | 96      | 28      | 00      |  |  |

| 11100         | <del>-</del> .`      | F6      | 2E      | 22      |  |  |

| 11110         | -                    | D6      | 2.A     | 02      |  |  |

Note: Locations marked "X" are loaded by trap; locations marked "-" are reserved.

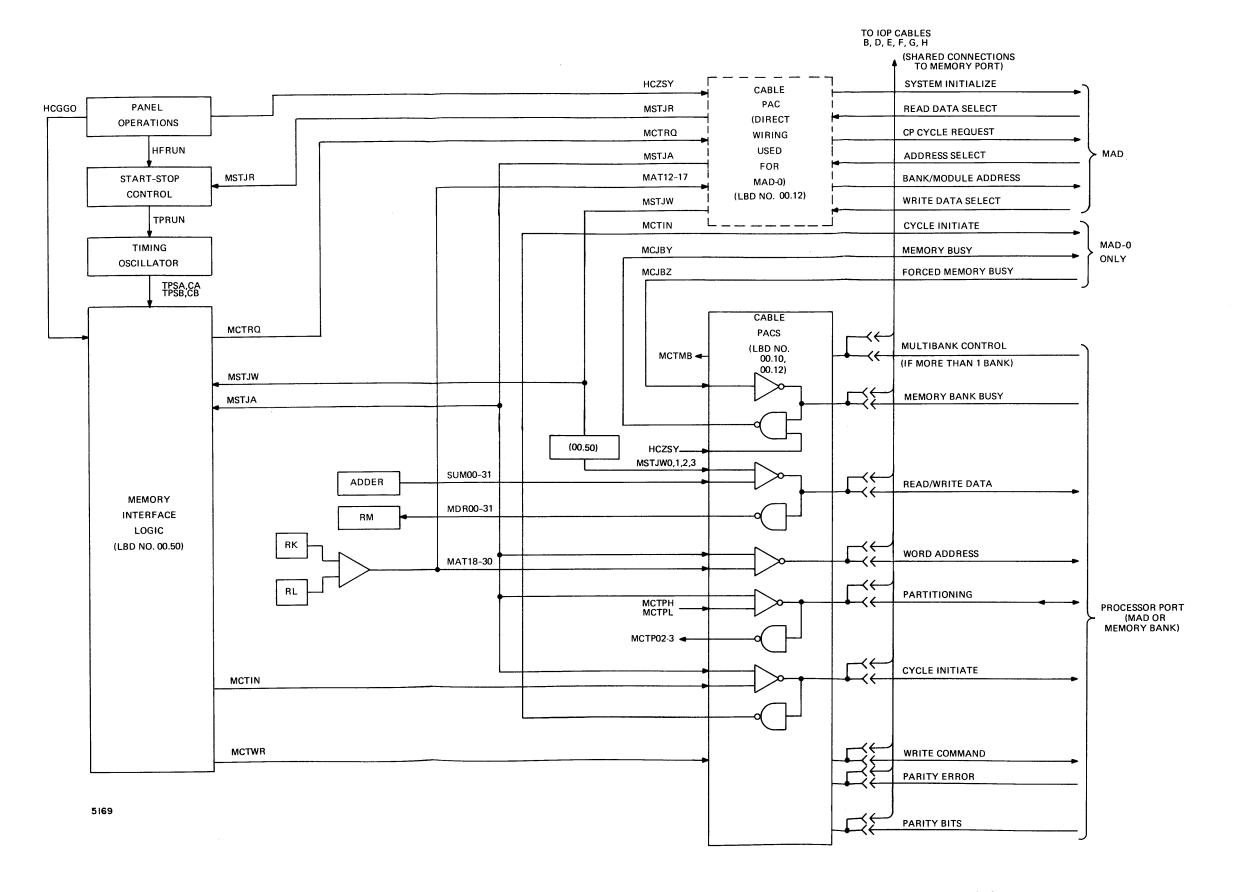

#### MEMORY INTERFACE

The CP memory interface consists of the control logic on LBD 00.50 and the control lines exchanged with MAD and a processor port. Logic elements in the CP which are related to the handshake between the CP start-stop and timing logic, MAD, the processor port, and IOP are illustrated in Figure 3-8.

Figure 3-8. Memory Interface Signals

#### Interface Signals and Cabling

The CP supplies the bank/module portion of the memory address and a cycle request to MAD, which responds with address and data select signals when the CP is selected for a memory cycle. MAD decodes the module portion of the address and sends the memory bank individual module select lines. MAD also checks the address and generates a "forced memory busy" when an illegal bank or nonexistent module address is present. The forced busy allows the memory/MAD/processor cycle to proceed until a legal bank and existing module are specified.

In a system containing MAD-0, the CP/MAD-0 interface connections are direct-wired; no cables are required. Systems using a larger version of MAD (capable of handling more than two processors or more than one memory bank) use cabled connections from CP to MAD.

Two processors (usually a CP and an IOP) share a processor port through common cables. Both processors are capable of placing data, addresses, and control signals on the lines, or reading data from memory. MAD referees conflicts between the two processors and allows only one to use a memory port during each cycle. In systems using MAD-0, the processor port cables go directly to the memory bank; in larger systems with more than one memory bank, the shared processor port cables go to MAD for switching from bank to bank. Signals on the processor port connections include the word address, read/write data, write command, cycle initiate, partitioning control, memory busy, and optional parity signals.

### CP/MAD/IOP/Memory Handshake

In a typical system the CP competes with the IOP for the use of a processor port. The MAD (Memory Access Director), oversees the process and makes sure that only one processor at a time is using a given port or a given memory bank.

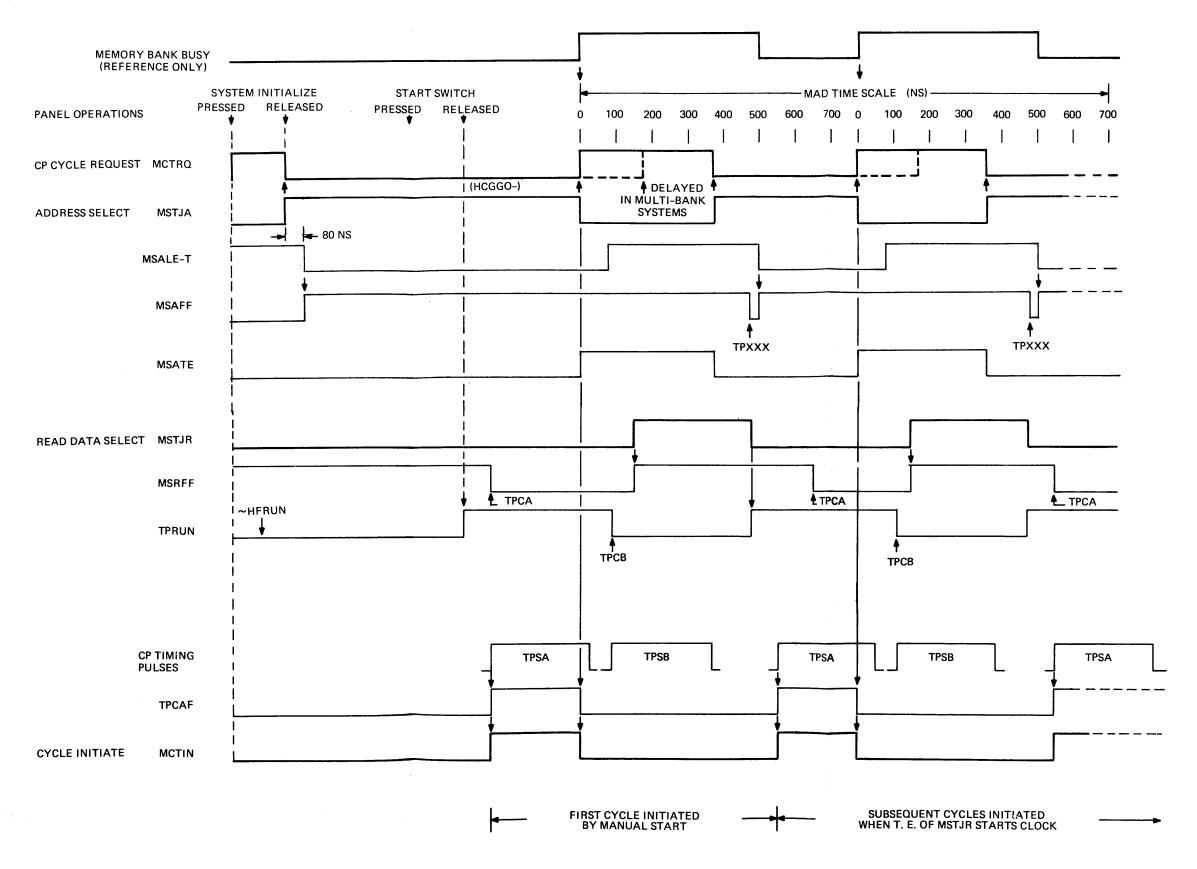

When the CP has access to a processor port, there is a three-way "handshake" among the CP, MAD, and the memory. After a CP inactive period or a system initialize, the cycle starts when the MPC sends the CP an active process code that differs from the current CP process code in the IAF register. The CP responds by turning on its cycle request to MAD. MAD returns an address select, which prepares the CP to generate cycle initiate (after a system initialize, the first cycle initiate is postponed until the clock is started from the panel). Then, both MAD and the CP wait for the memory to respond with memory busy, which indicates that a memory cycle is underway.

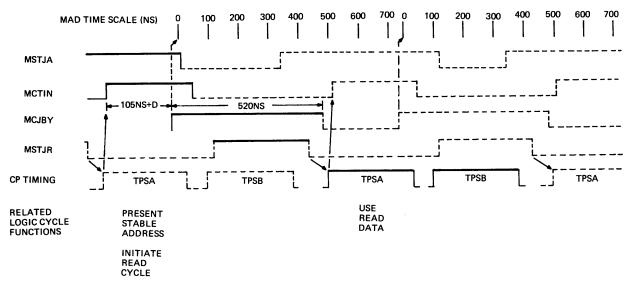

Memory and Logic Cycle Timing: -- Relative timing of the interface signals during two consecutive cycles is illustrated in Figure 3-9. Since the memory specifications guarantee that read data will be available at a specified time after memory busy, MAD generates a read data select at that time, to gate read data to the CPs RM register. At the end of read data select, the CP (conditional on receipt of a second address select) generates another cycle initiate and enables one set of pulses from the timing oscillator. The current timing level of the algorithm in effect is executed. MAD independently generates another address select, for the next cycle, and both MAD and the CP wait for memory busy.

A. READ CYCLE

NOTE: D = GATE AND CABLE DELAYS FOR MCTIN FROM CP TO MEMORY AND FOR MCJBY FROM MEMORY TO MAD.

B. WRITE CYCLE

Figure 3-9. Overall Memory Interface Timing

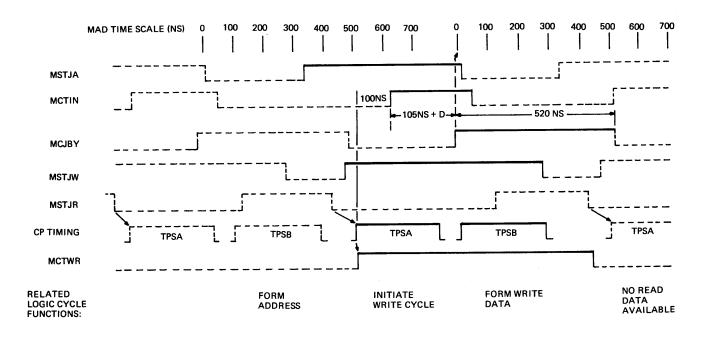

MAD also generates a write data select shortly after address select (Figure 3-9). Under control of the algorithm the CP may send memory a write command, which causes the memory to store the data gated to the memory by write data select. During a write operation, cycle initiate is delayed for about 100 ns in order to allow write data, gated through the adder, to stabilize.

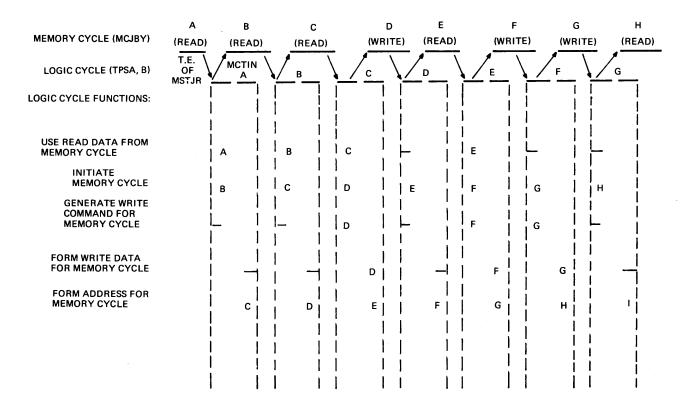

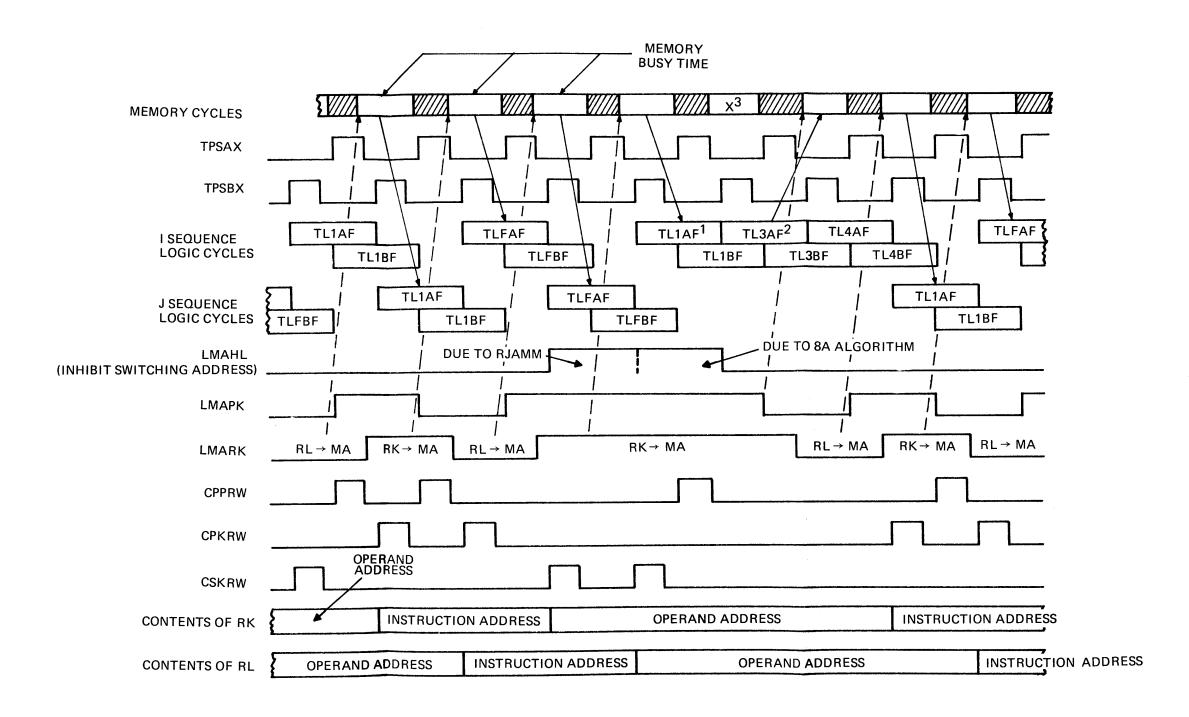

CP Logic Functions Related to Memory Cycles. -- Figure 3-10 illustrates a typical series of overlapped memory and logic cycles. Memory busy (MCJBY) represents the memory cycle, and the CP timing pulses (TPSA, B) represent the CP logic cycle. Memory and logic cycles are correlated in terms of read data; logic cycle A can use the read data from memory cycle A, etc.

Read data is gated into the CPs RM register by MSTJR toward the end of each read cycle. The data cannot be used until the next logic cycle. Thus, the data at the address formed during logic cycle A and applied to memory during logic cycle B is available for use in TM during logic cycle C, etc.

Write commands are formed early in the logic cycle that initiates a write memory cycle (see logic cycle E). Write data is gated through the adder during the same logic cycle and is stable during timing level B; for this reason, a write cycle initiate is delayed for about 100 ns to allow the write data to stabilize.

During each cycle the CP supplies an address from the RKL network either from the I-sequence address register (RK) or the J-sequence address register (RL). Usually the RKL network selects RK and RL alternately, but a number of special conditions govern the alternation. A detailed discussion of these conditions and the switching logic (LMAHL) appears in the paragraph on Look-Ahead. From the standpoint of the overall memory/MAD/CP cycle, it is unimportant whether the address is obtained from RK or RL. Because the address is required early in each logic cycle it must be formed and stable in RKL before a memory cycle is initiated. As a result, the address for memory cycle C is formed during logic cycle A, etc.

IOP Break-In, CP Inactive Condition, and Panel Halts. -- If the IOP requests a memory cycle while the CP is running, MAD prevents the CP from generating cycle initiate (by withholding address select), stops the CP clock (by withholding read data select) and generates address and data select signals for IOP. The latter communicates with memory over the interface lines shared with the CP through the cables.

When the MPC sends the CP the inactive process level code, the CP removes its cycle request to MAD after interrupting to the inactive process level, and enters the inactive condition. The IOP retains free access to MAD and memory. If no processor is requesting, MAD idles as well.

If the CP enters a panel halt the clock is stopped and the CP does not generate cycle initiate. If the halt occurs while a valid process code is in IAF, the CP address select is set and memory is not available to the IOP until the CP is started. However, if the CP is in the inactive condition during the halt, IOP can receive memory cycles.

Figure 3-10. CP Logic Functions Related to Memory Cycles

#### System Initialize and Startup

Startup of the CP from a system initialize and a series of memory cycles are shown in Figure 3-11. Timing oscillator output pulses are shown in relation to the memory interface signals. Relative timing is based on nominal MAD and memory cycle times. The waveforms are idealized; events which are shown as simultaneous are actually staggered in a practical system because of gate and cabling delays. Read cycles are assumed. Write cycles are discussed later.

System Initialize. -- A system initialize (HCZSY) clears MSTJR and MSTJA in MAD and sets MSRFF in the clock control (LBD 00.40). Because TPCAF is cleared, cycle initiate is held off. The CP is waiting only for a manual start to set TPRUN and start the timing oscillator.

Figure 3-11. Memory Interface Logic Signals

During System Initialize and Startup

Startup and Normal Consecutive Cycles. -- Since the system initialize forces code 000011 on the MPC IDL lines and also sets an inactive code (000010) in the IAF register, ~IKAQD sets the CP memory request (MCTRQ). As soon as MAD receives the request it sets address select, which clears the request. When the console START, TRANSFER, FETCH, or STORE button is activated and released, TPRUN is set, enabling the timing oscillator to develop one cycle of timing signals. TPCA then sets TPCAF, which enables cycle initiate.

From the time TPCA enables cycle initiate, about 200 ns elapse before the memory busy signal from the memory bank reaches the CP. (The actual time can vary because of cable delays.) Memory busy is, effectively, "time 0" for MAD; address select is cleared and a fixed timing sequence begins. In the CP, ~MSTJA generates MSATE, which clears TPCAF, turning off cycle initiate.

A memory request for the next cycle is set when address select goes false. In multi-bank systems, the request is delayed for about 180 ns to give MAD time to do the necessary bank or processor switching.

During the MAD cycle, read data select for the memory cycle in progress is turned on and off. The leading edge sets MSRFF in the start-stop logic; the trailing edge permits the TPRUN flip-flop to set, provided the panel run flip-flop is still on. In turn, TPRUN enables the next cycle of clock pulses and another cycle initiate.

# Cycle Inititate Logic

Logic shown on LBD 00.50 generates the cycle initiate (MCTIN) signal in the correct synchronous relationship with MSTJA and MSTJR from MAD and allows an additional delay during write cycles.

Read Cycles. -- During a read cycle the logic contains provisions to make sure that cycle initiate is held false until both the trailing edge of the previous MSTJR and the delayed leading edge of the new cycle's MSTJA. Normally, MAD generates MSTJA for the new cycle first, so that the effective control for MCTIN is the MSTJR trailing edge. The MSALE-T delay ensures address stability when MSTJA enables the first cycle initiate after an IOP break-in, by withholding cycle initiate until the address gated through the CP/memory cable PACs is stable.

The basic control for MCTIN is the TPCAF flip-flop; the flip-flop is set by TPCAX, which is initiated by the end of MSTJR. (TPCAX is also applied directly to the MCINR gate to produce MCTIN without the flip-flop turn-on delay.) The MCINW gate is disabled during read cycles (MCTWR is false) and has no effect on MCTIN. If MSALE-T has returned to ground before TPCAX, the MSALE+T gate also has no effect on MCTIN timing. However, if MSTJA for the next cycle is late, the MSAXX+T gate holds MCTIN false until the end of the MSALE-T delay.

The MSATE signal, controlled by the MSAFF flip-flop, occurs on the trailing edge of address select. MSATE clears TPCAF (which, in turn, inhibits cycle initiate) in preparation for the next cycle.

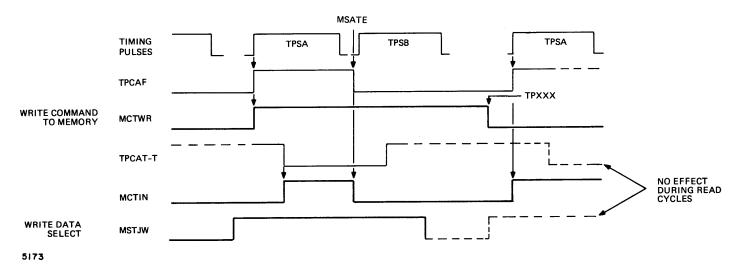

Write Cycles (See Figure 3-12). -- During TPSA, if specified by the algorithm, the MCTWR (write command) flip-flop is set. Because write data is applied to memory through the adder, the cycle initiate is delayed for about 100 ns after TPCA to ensure that the adder output is stable. To do this the MCINW gate holds MCTIN false until the end of the TPCAT-T delay. Cycle-initiate is turned off as usual when MSATE clears TPCAF. The MCTWR flip-flop is cleared by the special TPXXX output of the clock oscillator PAC in order to clear the write command sufficiently ahead of the next cycle initiate.

Figure 3-12. Memory Interface Logic Signals (Write Cycle)

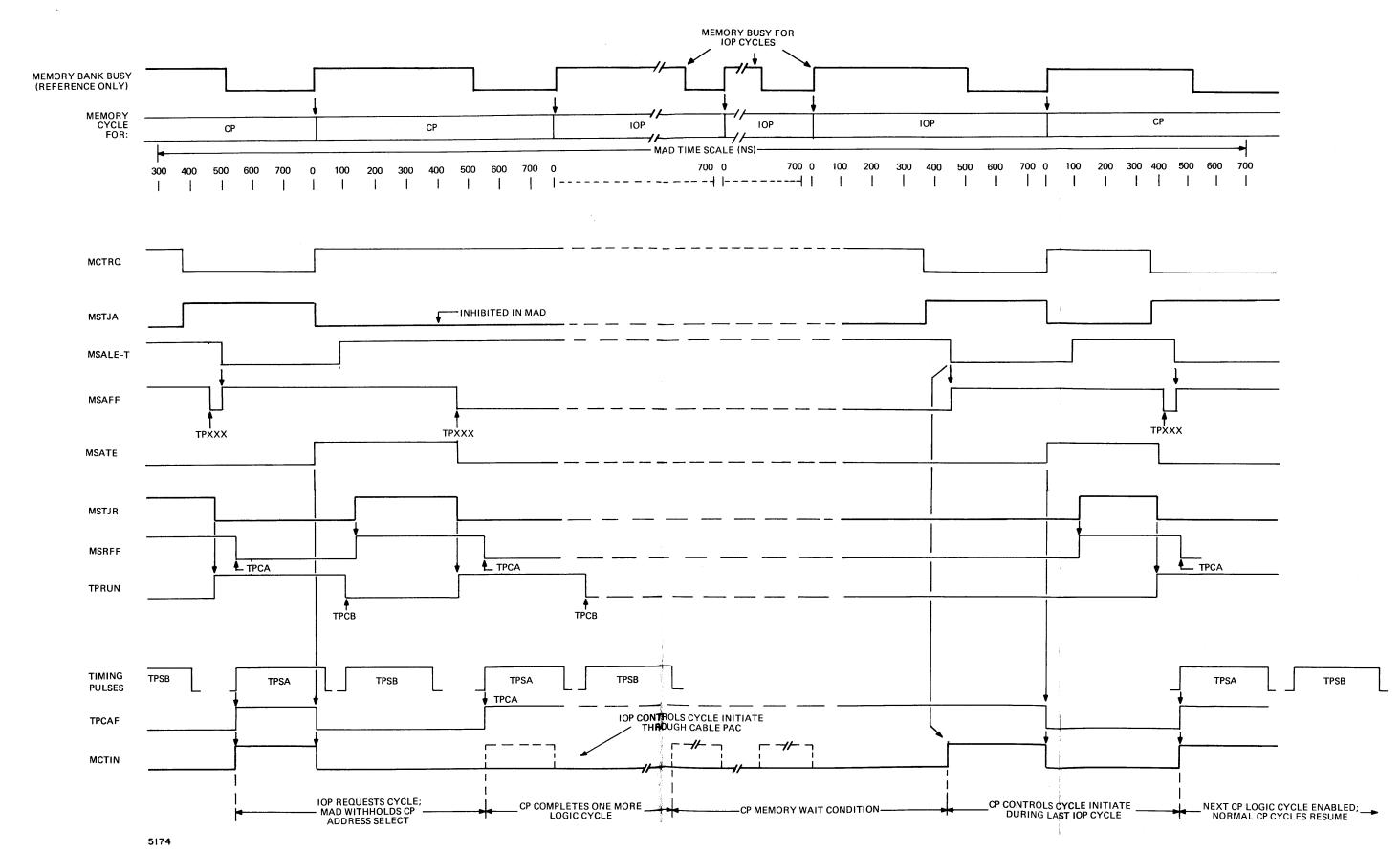

#### IOP Break-In

When the IOP requests a memory cycle, either for a data transfer or to execute a command, it breaks into normal CP running as shown in Figure 3-13. An IOP cycle-request conditions the MAD logic to withhold address-select from the CP and give it to the IOP instead. Because the CP does not receive an address-select, MSALE-T is held high and MCTIN is inhibited even after TPCAF is set. The IOP responds to the MAD address- and read-data-select by controlling the cycle-initiate line to memory through the bus shared by the CP. The memory busy line pulses as usual but under IOP control. The MSAFF flip-flop is held on by the absence of delayed CP address-select (MSALE-T) during IOP cycles. As a result, MSATE is prevented and the TPCAF flip-flop stays set for the duration of IOP control.

Figure 3-13. Memory Interface Logic Signals

During IOP Break-In

The IOP typically requires several consecutive cycles. When it is through with memory, it removes its cycle-request to MAD, which responds with the usual address select to the CP (MSTJA). Because TPCAF is still set, a CP cycle-initiate is generated as soon as MSTJA passes through the MSALE-T delay. Thereafter, the CP resumes normal control and the MSAFF flip-flop and MSATE signal are cycled as usual. While the IOP has control, the CP is in the memory-wait condition.

# CP Inactive (Cycle Request Removed) (Figure 3-14)

When the MPC delivers the inactive process-level code on IDL 24-29, the CP enters the interrupt algorithm as usual, storing the statewords of the previously active process and entering the inactive code in the IAF register, negating IKAQV (LBD 06.72). After the interrupt, the CP enters TLF and performs a meaningless fetch; no programs are associated with the inactive process level. During the fetch cycle, the absence of IKAQV permits MCTRQ to be cleared, and inhibits TSOAX (LBD 06.52) to prevent setting the validity bit of the sequence that initiated the fetch. (See paragraph on Look-Ahead.)

Because address-select and cycle-initiate are already present, MAD and the CP complete the current cycle except that MAD withholds the next address-select. The end of MSTJR triggers the CP clock for one more logic cycle (also an inactive fetch) but the absence of address-select prevents cycle-initiate. The CP enters the CP inactive condition.