### Model 632-0001<sup>-</sup> Series 32 Technical Bulletin

Digital Computer System

#### INTRODUCTION

**General Description** — The H632, first member of the Honeywell Series 32 family of 32-bit real-time computer systems, is a fully integrated-circuit general-purpose digital computer system providing the performance, flexibility and reliability required for a wide variety of small-to-large-scale real-time scientific and control problems.

An advanced concept of modular system integration and coordination permits efficient use of specialized processor capabilities in multiprocessor / multiprogrammed configurations. The H632 is modular in design and construction to facilitate expansions and extensions of basic functions. This modularity permits the user to select an H632 configuration specifically suited for his particular requirements. It also allows for easy field expansion of the system as the requirements grow.

Outstanding features of the H632 system are:

- Unsurpassed system performance

- On-line/real-time operational environment

- Total systems orientation

- Extensive software package

- Complete line of peripheral equipment

- Multiprocessor/multiprogramming capability

- Flexible priority communication structure in systems modules

- Modular construction facilitates systems configurations and field expansion

- Reliability enhanced by extensive use of integrated circuits

- Asynchronous organization allows for the time sharing of systems modules

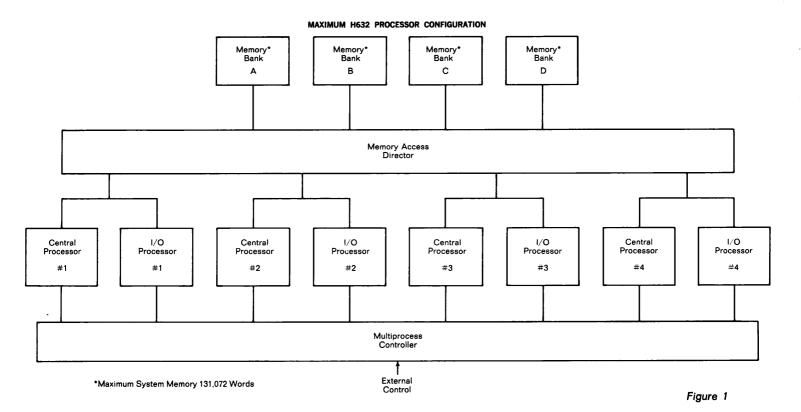

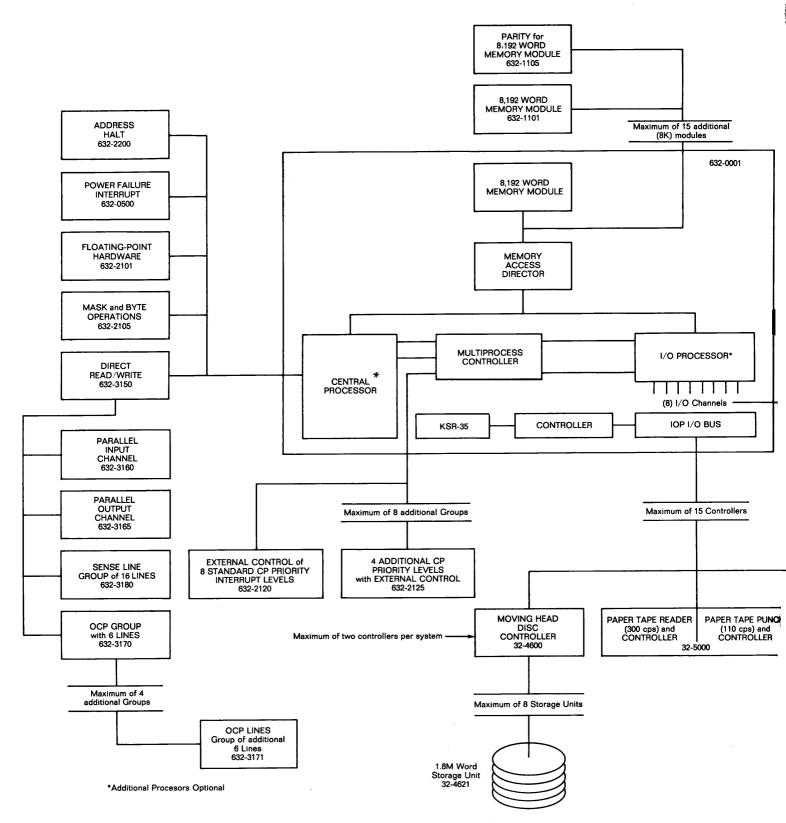

- Multiprocessing Every H632 system is a multiprocessor system, with separate central processor of high computational capacity, and input/output processor with extensive input/output capabilities. In a single H632 system, processing capability may be enhanced by including up to four central processors and up to four input/output processors. Primary storage may be configured to permit simultaneous access of up to four independent memory banks, and the sharing of memory banks among processors. Conflicting access requirements can thus be minimized, permitting each of the processors to execute programs of near-maximum rate, while retaining the capability to access common programs and data when required. (See Figure 1 for maximum H632 processor configuration.)

- Multiprogramming Facilitates the time-sharing of specialized processor capability among loosely related or totally unrelated real-time jobs. Both H632 central processors and input/output processors are multiprogrammable. Each of eight independent programs may either be a candidate for central processor execution, or be waiting for some external event to initiate its candidacy for execution. The highest priority candidate is automatically selected for execution. Similarly, each of eight concurrently active I/O channel programs may require program execution or data transfer; the I/O processor services these requirements in order of their urgency. Multiprogramming capability may be expanded with up to 40 central processor priority-selected programs, and up to 16 I/O processor concurrent channel programs.

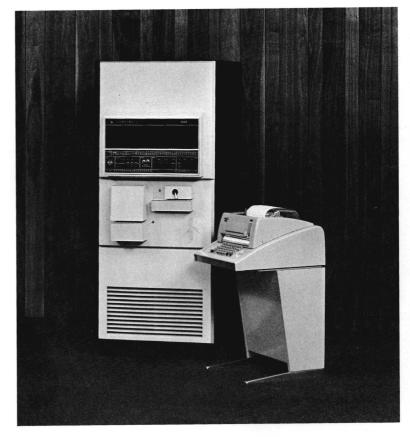

- \*Model 632-0001 does not include punched paper tape reader and punch, as shown in photo above.

# Honeywell

### Digital Computer System

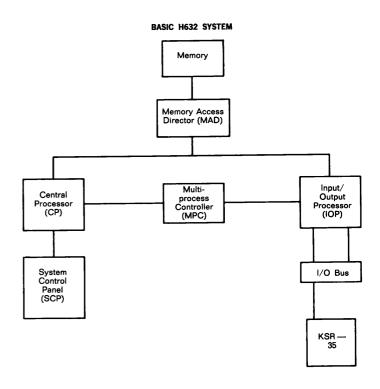

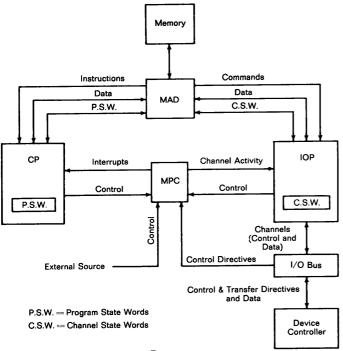

System Organization — The basic (Figure 2) H632 system, Model No. 632-0001, consists of 8,192 words of primary storage; a Central Processor (CP); an Input/Output Processor (IOP); a KSR-35 I/O typewriter connected to the IOP via a device controller; the system coordinating elements — Memory Access Director (MAD) and Multiprocess Controller (MPC); and a System Control Panel (SCP).

An H632 system is implemented by combining the five basic systems modules.

- 1. Primary Storage The standard memory module for the H632 contains 8,192 words, each having 32 bits. Memory can be expanded from the basic 8,192 words to 131,072 words in 8,192-word modules. Depending on the Memory Access Director selected, memory can be organized in banks, each bank containing one or more 8,192-word modules and a separate bus system to which one or more processors may have access. Up to four banks are permitted on an H632 System, provided total memory does not exceed 131,072 words. Features are:

- Coincident-current, random access ferrite core

- 32-bit word

- Parity option

- 850-ns cycle time

- Expandable from the basic 8,192-word system to 131,072 words with pluggable memory modules

- All major functions performed with monolithic integrated circuits

- Low power consumption

- Standard product line ICM-500 memory system

- 2. Memory Access Director (MAD) The Memory Access Director controls the access paths between core memory and the CP and IOP. The MAD resolves simultaneous memory access requests issued by two or more processors. By proper selection and connections of MAD units, shared and/or private memory banks may be achieved. Features are:

- Multiprocessor access to multimemory banks allows simultaneous operations

- Establishes common and/or private memory in mulprocessor/multimemory bank systems

- Resolves simultaneous access requests

- Allows for asynchronous CP, IOP and memory operations

- 3. Central Processor (CP) The H632 Central Processor is a general-purpose, multiprogrammable, word-oriented, scientific data processor with limited optional I/O capability. There are eight standard program levels, optionally expandable to 40. The CP performs all data manipulation, arithmetic, logical, and comparison operations; and issues orders requesting changes in activity states of various program levels. Features are:

- 32-bit word-oriented

- Two's complement arithmetic

- Direct addressability of 65,536 32-bit words or 131,072 16-bit halfwords

- Bit, byte, halfword, word, doubleword, and immediate operand addressing

- Storage-to-Register, Register-to-Storage, Register-to-Register and Immediate Operand Operations

- 16 general-purpose high-speed, 32-bit flip-flop registers which may be used as:

accumulators

index registers (7)

mask register (1)

temporary storage

- Multilevel indexing and indirect addressing

- Instruction look-ahead

- Automatic trapping of arithmetic faults, unimplemented optional instructions, undefined instructions, and error conditions

- 144 high-speed instructions, including

Load and store operations

Logical operations

Fixed-point arithmetic operations

Compare operations

Shift operations

Bit-testing and bit-modification operations

Jump and Execute operations

Control operations

Floating point operations (optional)

Mask and byte operations (optional)

Direct read/write (optional)

Typical Instruction Execution Times (Times include instruction and operand fetch and indexing if required.)

Load word  $-1.7 \mu s$ Add word  $-1.7 \mu s$ Multiply word  $-8.1 \mu s$

Floating add  $-5.1 \mu s$

Floating multiply — 9.4  $\mu$ s

■ Central Processor Options

Floating-point operations

Mask and byte operations

Additional interrupt levels

Direct read/write

Parallel input channels

Parallel output channels

Sense-line groups

Output-control pulse groups

Figure 2

- 4. Input/Output Processor (IOP) The H632 Input/Output Processor is an independent, multiprogrammable processor with highly developed I/O facilities and limited data processing capability. It is word oriented and provides direct interpretation of I/O commands fetched from memory concurrently with CP operation. Data is also directly transferred between memory and the selected device(s) without CP intervention. Modular I/O control capabilities of the H632 permit utilization of a full range of peripherals. The communication path to any device controller may be over any IOP channel. The standard IOP has eight I/O channels, optionally expandable to 16 channels. Features are:

- Simultaneous independent operation with the CP on a cycle-stealing basis

- Provision for a direct data path between memory and peripheral devices

- Programmable real-time I/O with command and datachaining capability

- High-speed, word-oriented, up to 200 kHz word-transfer rate

- Eight channels standard, expandable to 16 channels

- Word, halfword, or byte transfers

- Dynamic channel/controller assignment

- Multiplexer/selector capability

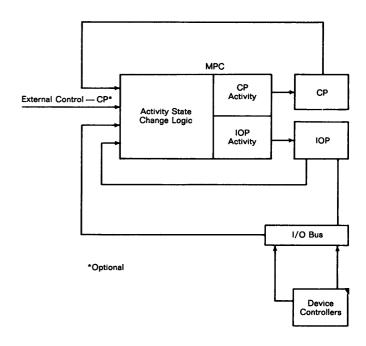

5. Multiprocess Controller (MPC) — Each H632 processor (CP and IOP) can be time-shared among several programs. The MPC provides logical control over the interaction between CP, IOP, and external interrupts, and serves as a clearing house for interprocess and intraprocess state control in the system.

The activity states of all programs in all processors are recorded within the MPC. Orders to change the state of a process are transmitted to it. Simultaneous service requests for program execution are resolved by the MPC. The MPC identifies the active process of highest priority for each processor in the system. This information is then transmitted to the appropriate processor for action. Features are:

- Provides system coordination/control in multiprogram/multiprocessor environments

- Indicates current highest-priority task to the CP and

- Resolves simultaneous service requests

- External interrupt and control (optional)

System Peripheral Options — All options have USASCII compatible operating modes.

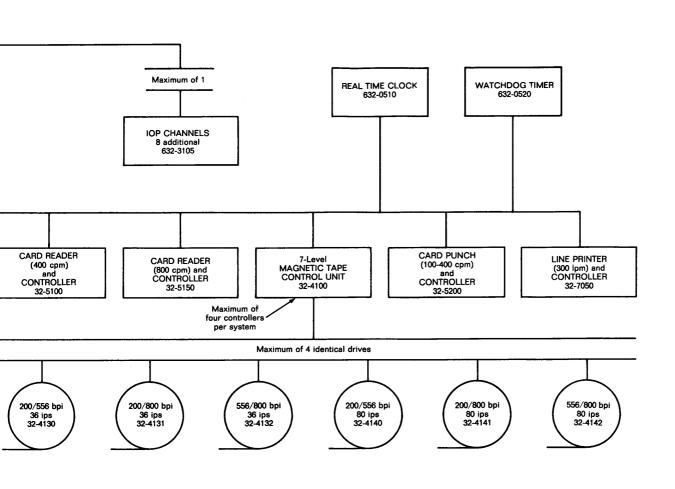

### Seven-level magnetic tape

36-ips, 200/556 bpi, 7.2-20.0 kHz character transfer rate 36-ips, 200/800 bpi, 7.2-28.8 kHz character transfer rate 36-ips, 556/800 bpi, 20.0-28.8 kHz character transfer rate 80-ips, 200/556 bpi, 16.0-44.4 kHz character transfer rate 80-ips, 200/800 bpi, 16.0-64.0 kHz character transfer rate 80-ips, 556/800 bpi, 44.4-64.0 kHz character transfer rate

### Card Reader

400 cards per minute, 80-column card 800 cards per minute, 80-column card

### Card Punch

100 to 400 cards per minute, 80-column card

High-Speed Paper Tape

300-character-per-second reader

110-character-per-second punch

### Mass Storage

Moving head disc unit

1.8 million to 28.8 million words

Average latency — 12.5 ms Access times — 1 track seek 30 ms

200 track seek 165 ms

Word transfer rate - 39 kHz

Line Printer

300 lines per minute, 120 columns/line

Real-Time Subsystems

Real-time clock

Watchdog timer

Power failure interrupt

### **Custom Options**

- High-speed line printer

- High-speed magnetic tapes

- Nine-channel magnetic tapes

- Fixed head disc system

- Analog/digital and digital/analog converters

- Series 32/Series 16 adapter

- Graphic displays

- Alphanumeric displays

- Single-line communications controllers

- Multiline communications controllers

Systems Software — The extensive H632 software package consists of:

#### Assembler

- Nested macros

- Pseudo-operations for control, storage assignment, data definition, and conditional assemblies

- Absolute and relocatable coding

- Extensive error flagging

- Symbol table output including usage table

- Side-by-side listing

### Fortran IV

- Standard ASA form including math library

- Extensions to include in-line code, multiple subscripts, implied Hollerith count, zero/negative subscripts and DO loop parameters, multiple subroutine entry points and nonstandard returns

- Extensive error flagging

- Automatic subroutine linkage

- Compatible for all source program translations

- Memory map

- Produces relocatable "load mode" programs

### Subroutine Library

- Fixed-point and floating-point math libraries

- I/O library

### Debug Package

System Editor - for editing standard library, user subprogram library, and user source files.

OS-1 — for interpreting control commands which initiate execution of system and user programs.

Unit Record Control — provides for run-time assignment of peripheral I/O devices and device modes and the management of files of I/O information.

### Trap Package

Media Conversion

Test and Maintenance Routines

**Technology** — Some of H632 technological highlights

- μ-PAC monolithic integrated-circuit modules

- Machine-wired back planes

- Conventional manufacturing processes

- Cable connection of all systems modules

- H632 parallel machine organization permits use of moderate-speed circuitry and wide reliability performance margins

- High packing density up to 32K-word system with CP, IOP, control console, paper tape reader (300 cps) and paper tape punch (110 cps) fit into a single rack

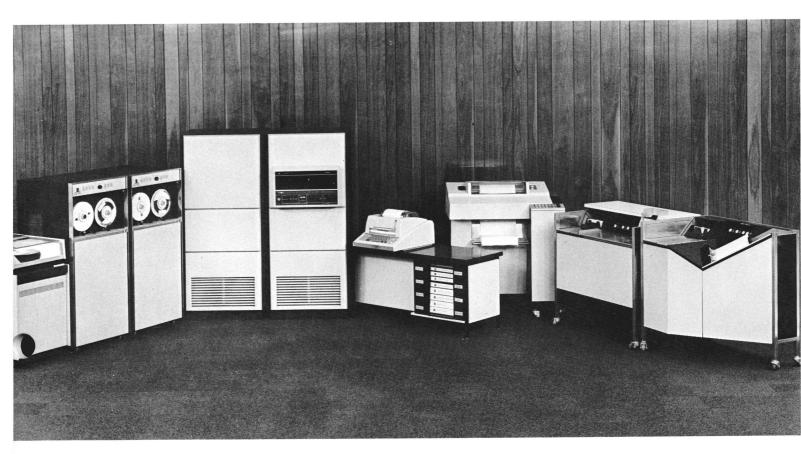

System Configurator — (See Figure 3).

### H632 System Configuration

Figure 3

### **PRIMARY STORAGE**

General Description — Primary storage is the high-speed random-access storage which is directly accessible to H632 System processors. The primary storage subsystem provides system processors with the accessibility of 8,192 to 131,072 32-bit storage cells. A small number of these cells (256) are dedicated to specific system storage requirements; the remainder may be occupied by programs and/or data.

Primary storage consists of from one to 16 core memory storage modules, each providing 8,192 individual 32-bit storage cells. Each 32-bit cell is identified by a unique 17-bit binary number. Four bits are used to select the module within which the cell resides; the remaining 13 bits identify the cell within the module.

**Operation** — Memory modules are cable-connected to the Memory Access Director (MAD), which controls memory accesses. A memory address is furnished to the MAD by the processor requesting a memory access. The MAD interprets this address as a module address and an address within the module.

The latter address is then transmitted to the selected module. Upon receipt of this address a memory access is performed and the content of the cell is transmitted or modified according to the operation being performed by the processor under consideration.

**Information Units** — Physically, H632 primary storage is simply an array of 32-bit storage cells. For processing purposes, it is convenient to further refine the structure of the stored data by definition of fixed-length information units, or *fields*. Explicitly recognized fields within the H632 System are:

The *one-bit field* is represented by a binary digit, or *bit*, either 0 or 1.

The four-bit field is represented by a hexadecimal digit, or hex digit; hex digits beyond 9 are : A,B,C,D,E, and F.

The byte, an eight-bit field is represented by two hex digits.

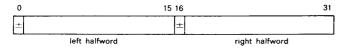

The halfword, a 16-bit field, is represented by four hex digits.

The word, a 32-bit field is represented by eight hex digits.

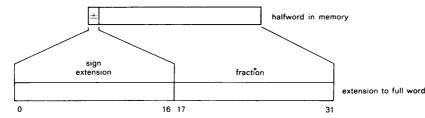

The double word, a 64-bit field, is represented by two words.

Bit positions within a field are assigned consecutive numbers, from left to right, starting with 0. When a word is to be explicitly recognized as such in storage, it is required to occupy a single storage cell.

A four-bit field, to be explicitly referenced in storage, is required to be in one of the eight nonoverlapping hexdigit positions of a word occupying a single storage cell. Similarly, a byte must be one of the four nonoverlapping bytes of a word occupying a single storage cell; a halfword must be one of the two nonoverlapping halfwords of a word occupying a single storage cell. Doublewords may occupy any two consecutively numbered storage cells.

### **MEMORY ACCESS DIRECTOR (MAD)**

**General Description** — The Memory Access Director (MAD) consists of interface logic which controls communications between processors and memory.

**Operation** — The communication between processors and memory is controlled by a request-response dialogue between the processor and the MAD. In order to access memory with the next available memory cycle, a processor sends an Access Request signal to the MAD. Upon the determination that memory is available for use by the processor, an Address Select signal is transmitted to the processor requesting access. Upon receipt of the Address Select signal the processor sends a word address and a Cycle Initiate signal to the memory via the MAD. Since the control of the Address and Cycle Initiate timing rests entirely with the processor, it regulates the memory data transfer rate. Cycle Request and Address Select signals are asynchronous with respect to one another.

Up to two processors may be connected to a MAD processor port. The processors sharing the port also time share a cable system on a memory cycle-stealing basis; therefore, only one of these processors may access memory at a time. Signals generated by the MAD inform the selected processor that it has exclusive use of the bus on which data is transmitted. Once an Access Request has been received and acted upon by the MAD, memory cannot be accessed by any other processor until the selected processor has initiated and completed an access.

In each MAD, the memory module addresses are specified independently and uniquely for each processor. Since two processors may share a MAD processor port, priority logic is required to resolve scheduling conflicts. This priority determination is made within the MAD. Processors sharing a port have fixed priorities relative to one another, with the IOP having higher priority than the CP.

### **CENTRAL PROCESSOR (CP)**

**General Description** — The H632 Central Processor is a modified single-address, 32-bit-word-organized, stored-program computer with 16 addressable high-speed registers. It performs operations — data transfers, arithmetic, logical, and control — according to instructions fetched from a list of instruction words (the program) residing in primary storage.

**Operation** — The CP issues memory access requests to the MAD. If memory is not being accessed by another processor (typically an IOP), the CP access request will be acknowledged. The contents of the addressed memory location are then presented to the CP for processing. If the memory word accessed was an instruction, the various subfields of the instruction word are processed and operations are performed according to instruction definition. After instruction decoding, the operand address, where needed, is formed. Memory is again accessed under control of the MAD and the instruction operand is presented to the CP for processing.

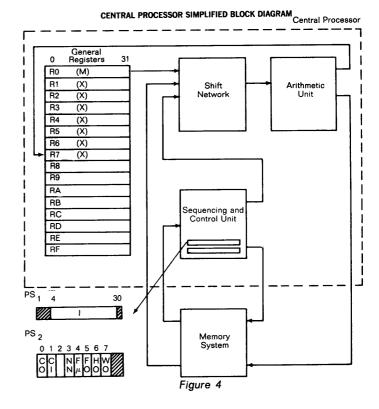

**Internal Organization** — Figure 4 is a simplified block diagram of the H632 Central Processor.

The CP contains 16 general registers, an arithmetic and logical unit (ALU), a sequencing and control unit (SCU), and two program stateword registers (PS $_{\rm l}$  and PS $_{\rm 2}$ ). The ALU performs arithmetic, logical, and shift operations on data supplied from primary storage or retained in the 16 addressable registers. The SCU fetches and interprets instructions and controls the functions of the ALU throughout instruction execution.

General Registers — The 16 addressable 32-bit registers are numbered, in hexadecimal notation, 0 through F, and referred to as R0 through RF.

R0 is a special register, implicitly referenced in masking operations, reference to which is subject to certain restrictions.

R1 through RF are general registers, usable by all instructions as operand or result locations.

R1 through R7 can also serve as index registers in address formation.

Shift Network — Contains a parallel shift network which performs data transformations.

Arithmetic Unit — Contains four auxiliary registers which supply operands to the processing networks, retain partial results, and satisfy several interface requirements.

Sequencing and Control Unit. — Controls the interface of the CP with primary storage, retains and acts on the basic control information required for program sequencing and execution. The SCU is capable of preparatory interpretation of one instruction while controlling the execution of another. This "instruction look-ahead" feature permits high-speed operation with conservative speed circuitry.

*Program Status* — Dynamically retained in two registers which contain all H632-defined portions of the Series 32 program status double word, as follows:

I, Instruction address, identifying the storage cell containing the next instruction to be fetched and executed

$C_0C_1$ , Condition codes, retaining an indication of the result of a compare operation

NN, FU, FO, Floating-point mode controls HO, WO, Fixed-point mode controls

Instructions — The H632 possesses a repertoire of 144 high-speed, systems-optimized instructions. With the H632 structure, the user can work directly with various data sizes: words (32 bits), halfwords (16 bits), bytes (8 bits), hex digits (4 bits), single bits and doublewords (64 bits).

### The CP allows for:

Storage-to-register operations (e.g., add a word in memory to a word in a register and place the result back in the register), register-to-storage operations (e.g., add a word in memory to a word in register and place the result back in memory), register-to-register operations, and immediate operand operations.

The H632 CP offers 11 different classes of instructions:

- 1 Load/Store

- 2 Logical

- 3 Fixed-Point Arithmetic

- 4 Compare

- 5 Shift

- 6 Bit

- 7 Jump and Execute

- 8 Control

- 9 Floating Point (Optional)

- 10 Mask and Byte (Optional)

- 11 Direct Read/Write (Optional)

A complete listing of the standard instruction repertoire is shown in Table 1.

Data Formats — An operand fetched from memory is presented to the CP in the form of a 32-bit word. The whole word (32 bits), or some portion of the word (16 bits, eight bits, four bits, or a single bit) is then processed according to that particular instruction definition. Number representation is binary. Arithmetic processing is by two's complement arithmetic. In processing halfwords, sign extension is used. Thus, a 16-bit binary fraction is extended to 32 bits before any arithmetic operation is performed.

In some special cases, sign extension is inhibited or sign interpretation is ignored, enabling operations on unsigned numbers. The CP also has the ability to use immediate operands. In this type of instruction, the address field of the instruction (including bit 15) is interpreted as a 17-bit two's complement binary number. Sign extension is performed prior to any arithmetic operation, facilitating operations involving constants to be performed wthout using additional storage.

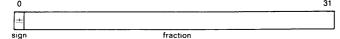

### Fixed-Point Single-Precision Fraction

The range of numbers represented in this format is from -1 to +1 —  $2^{-31}$  inclusive.

### Halfword Format

Halfwords are extended to full words for processing.

#### Doubleword Format

The range of numbers represented in this format is from -1 to +1 -  $2^{-62}$ .

Bit 63 is ignored in operands.

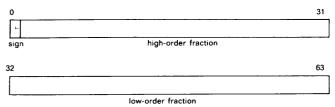

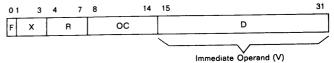

Instruction Formats — There are five types of instruction word formats. They are:

Memory Reference

Shift

Bit

Immediate

Control Process

The formats for these classes of instructions are as follows:

### Memory Reference

- F indirect address flag. When set to a 1, indirect addressing is performed.

- X index register specifier. This three-bit field indicates which of the general registers, R1 through R7, is to be used as an index register. If this field is zero, no indexing is performed. Indexing takes place before indirect addressing.

- R general register specifier. This four-bit field indicates which of the general registers, R0 through R15, is to be used in the execution of the instruction.

- OC operation code. This seven-bit field specifies the code of the instruction or operation to be performed.

Displacement Address — This 17-bit field allows for the direct addressability of 131,072 halfwords or 65,536 words. Word operations ignore bit 31 in address information.

When the effective halfword address is less than 16, a general register rather than a memory location is referenced, providing *register-to-register* operations.

When memory is expanded beyond 65,536 words, one must then consider the memory as being divided into sectors of 32,768 words each. A 131,072-word memory system will have four sectors. In this case bit 15 of the instruction no longer is considered to be part of the D field, but is defined as being a sector-indicator. If the sector bit (bit 15) of the current instruction is zero, reference is made to sector zero of the memory (first 32,768 words). If the sector bit of the current instruction is one, reference is made to the current program sector.

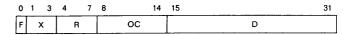

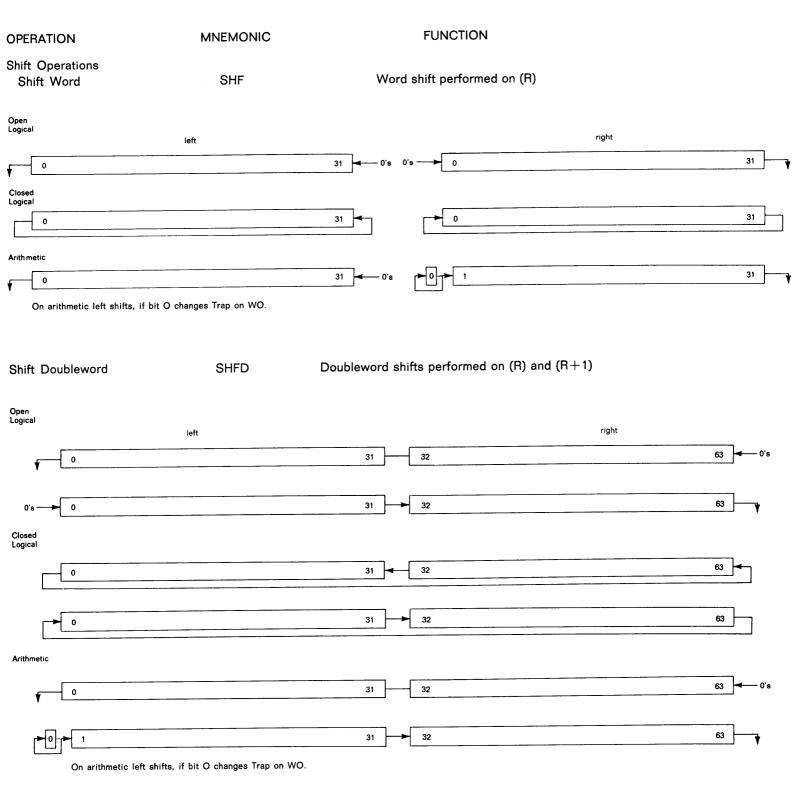

### Shift

| 0 | 1   | 3 | 4 | 7 | 8 |    | <br> | <br>19 | 24 | 25 |    | 31 |

|---|-----|---|---|---|---|----|------|--------|----|----|----|----|

| F | \ \ | ( | 1 | R |   | ос |      | TS     |    |    | SD |    |

- R—general register specifier. The R field specifies the general register on which the shift operation is to be performed. For doubleword shifts, left shifts are towards register R as specified, right shifts are towards register R + 1 (if R = 15, R + 1 is defined to be equal to R0).

- OC operation code. Indicates single- or doubleword shift operation.

- TS type of shift. This field indicates the type of shift to be performed:

- a. closed logical

- b. unpack

- c. open logical

- d. arithmetic

- SD shift distance and direction. This field is interpreted as a seven-bit two's complement integer defining the shift distance and direction. Positive shifts are to the right; negative shifts are to the left.

If indexing or indirect addressing are called for within a shift operation, bits 16-19 and 25-31 of the effective address are used as TS and SD specifiers.

Bit — For bit operations, the Memory Reference format is applicable with the exception of R-field interpretation. The R-field is used to refer to a single bit within the halfword pointed to by the effective halfword address, rather than being used as a register designator.

If the effective halfword address is greater than 0 and less than 16, the most significant 16 bits of the addressed general register may be tested and/or modified. If the effective halfword address is zero, the first 16 bits of Program Stateword two may be tested and/or modified. The sense switches may be tested when the effective halfword address equals zero and the R field is A, B, C or D.

### Immediate

Bits 15-31 of the effective address are used as an operand rather than as the address of the operand location in memory. The V field (bits 15-31) is sign extended (bit 15 copied into bits 0-14) before it is used as an operand.

If an immediate operation is performed using indexing or indirect addressing, sign extension is performed as follows: if bits 4-15 of the effective address are all zeros, bits 0-3 are made zeros; if bits 4-15 of the effective address are not all zeros, bits 0-15 are made all ones. The effective address is then used as the value of an operand.

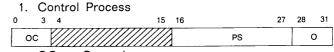

### Control Process

Bits 16-31 of the effective address are transmitted as an order to the MPC.

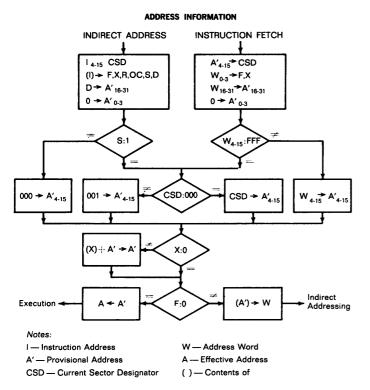

Addressing — The CP processes each instruction in two phases. The first phase, instruction fetch and address formation, is performed identically for all instructions. The second phase, instruction execution, is unique for each instruction. This section deals strictly with the first phase.

Instruction Fetch — An Instruction Address, I, maintained by the CP, points to a cell in main storage which contains the next instruction to be executed.

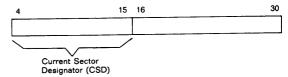

Format — Instruction Address Counter (I)

Figure 5

Since instructions are contained in full 32-bit words, bit 31 of the instruction address is always interpreted as being equal to zero. A portion of the instruction address may be used in the formation of the effective address of the operand of the instruction being processed. This portion is referred to as the Current Sector Designator, CSD, and indicates the sector, a block of 32,768 words of storage, which is currently being pointed to by I.

Address Formation — When execution of an instruction (including any trap-action by the processor) is complete, and any required interrupt action by the processor has been taken, the processor's next task is "sequential instruction-fetch." A sequentially fetched instruction is taken from the word whose address is *I*. Sequential fetch of an instruction includes the incrementation of *I* by 1 after effective address-formation is completed and before any further change in *I* required in the execution phase.

After an instruction has been fetched, a provisional address is formed (see Figure 5) using the D field of the instruction word and, conditionally, CSD. For systems with 65,536 words or less of memory, one need not concern himself with the sector bit. For these systems, bits 15-31 of the instruction are used as a direct address field.

For systems with more than 65,536 words of memory, the user must think of his system as consisting of three or more (four maximum) sectors, with each sector being equal to 32,768 words. For these systems, the D field of the instruction references a particular word, either in sector zero (S-bit = 0) or in the current program sector (S-bit = 1).

The exception to this is when an instruction with the S-bit = 1 is being executed out of sector zero. In this case, the D field specifies a location within sector 1 and not within the current sector zero.

If the index specifier, field X, is non-zero, the contents of register No. X are added to the provisional address. If the X field is equal to zero, the provisional address is unmodified.

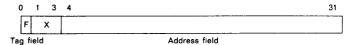

If the Flag-bit, F, is zero, the effective address A is used in the execution phase. If F is 1, the provisional address is used as an indirect address to address a word in main storage or in a general register, from which an address word, W, is fetched. A new provisional address is then formed from the address word and conditionally, a new CSD. This new provisional address may be indexed or used as an indirect address reference as discussed above. Indirect address words have this format:

Indexing occurs prior to indirect addressing in address formation. Multilevel indexing and/or indirect addressing is permitted.

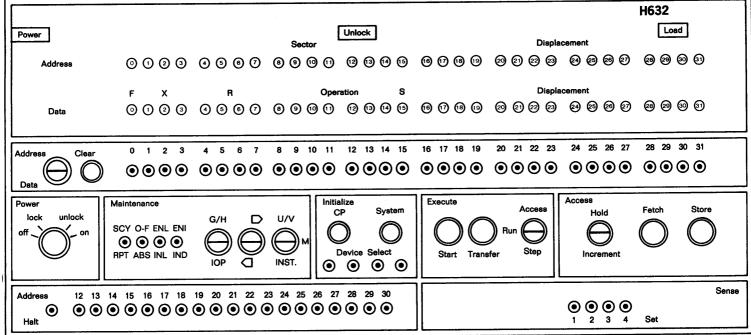

## H632 SYSTEM CONTROL PANEL

Figure 6

Trap System — Exceptional conditions, arising during instruction fetch and/or execution, cause trapping. The resulting change in program execution is dependent upon the condition that has caused trap action to occur. There are four general classes of trap conditions (a dedicated memory location is associated with each class):

### Class

- I Arithmetic Exception

- II Unimplemented Instructions

- III Unimplemented Instructions

- IV Undefined Instructions

Class I traps occur when word or halfword overflow have occurred as the result of fixed-point arithmetic operation.

Class II and III traps occur when the execution of an unimplemented instruction is attempted. An example of this would be the attempted execution of a floating-point operation without the floating-point option. This class of trap may be used to simulate unimplemented instructions.

Class IV traps occur when the execution of an undefined instruction is attempted.

System Control Panel — The H632 System Control Panel (Figure 6) consists of a comprehensive set of indicators, displays, and controls used to indicate, and allow for the modification of, the state of the system.

The control panel provides these capabilities:

State Indicators — Indicate the state of the following system conditions:

- a. A. C. Power

- b. D. C. Power

- c. Load

- d. Run

- e. CP Status

- f. IOP Status

- g. Single Cycle

- h. Repeat

- i. Access Memory Locations O-F

- . Inhibit Interrupt

- k. Inhibit Look Ahead

- Address Halt (Optional)

Binary Displays (upper and lower) — allow for the display of:

- a. Memory Address, Memory Data Register

- b. Program Stateword 1, Program Stateword 2

- c. U- and V-networks

- d. Instruction Register and Timing

- e. CP Activity States

- f. IOP Activity States

### System Control

- a. Power Switch

- b. CP Initialize

- c. System Initialize

- d. Device Selection

### Display Entry — Data Entry

- a. Address/Data Switch

- b. Clear Switch

- c. Binary Entry Switches

### Execute Control

- a. Access/Run/Step

- b. Start

- c. Transfer Control

### Storage Access

- a. Fetch

- b. Store

- c. Hold/Increment

### Maintenance Display Control

- a. Group Select

- b. Group I

- 1. U- and V-networks

- 2. Memory Address and Memory Data

- 3. Instruction Register and Timing

- c. Group II

- 1. G and H Registers

- 2. IOP Activity States

- 3. CP Activity States

### Maintenance Function Control

- a. Look-Ahead

- enable/inhibit

- b. Repeat

- single cycle/repeat

- c. Interrupt

- enable/inhibit

- d. Addressing

0-F

### Address Halt Control and Switch Register (Optional)

Sense Switches — Four are provided. Sense switches are tested by using bit testing instructions.

### Table 1 -- H632 Central Processor Instruction Repertoire

### Notes

| +        | Halfword overflow possible   |

|----------|------------------------------|

| ∰<br>EWA | Word overflow possible       |

| EWA      | Effective word address       |

| EHA      | Effective halfword address   |

| EDA      | Effective doubleword address |

|          | _                            |

( ) Contents of

I Instruction address

R General Register specified in instruction

Λ Logical AND Logical OR

Logical exclusive OR

Replaces

SE Sign extended

ZE Zeros extended

Absolute value

C.C. Condition code indicators

V° Value (bits 15-31) of instruction address field (EHA). Points to the bit, specified by the value of the

R field in the instruction, in the halfword being addressed

EA Effective address (word or halfword according

to instruction)

| OPERATION                                                                                                                                                                                                                                                                                                                                                                                               | MNEMONIC                                                                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load/Store Operations  Load Word  Load Halfword  Load Value  Store Word  Store Halfword  Load Doubleword  Store Doubleword  Load Unsigned Halfword  Store Unsigned Halfword  Swap Word  Swap Halfword  Store Registers  Load Address                                                                                                                                                                    | LDW LDH LDV STW STH LDD STD LDUH STUH SWW SWH STR LDR LEA                              | $(EWA) \rightarrow (R)$ $(EHA)_{SE} \rightarrow (R)$ $V_{SE} \rightarrow (R)$ $(R) \rightarrow (EWA)$ $(R) \rightarrow (EHA) +$ $(EDA) \rightarrow (R,R+1)$ $(R,R+1) \rightarrow (EDA)$ $(EHA)_{ZE} \rightarrow (R)$ $(R) \rightarrow (EHA)$ $(R) \rightarrow (EHA)$ $(R) \rightarrow (EWA)$ $(EWA) \rightarrow (R)$                                                                                                                                                                                                                                                                                                                                                                                 |

| Logical Operations OR Word OR Halfword OR Value OR Word to Storage OR Halfword to Storage Exclusive OR Word Exclusive OR Halfword Exclusive OR Value Exclusive OR Word to Storage Exclusive OR Halfword to Storage Exclusive OR Halfword to Storage AND Word AND Word AND Halfword AND Value AND Word to Storage AND Halfword to Storage Fill Word Fill Halfword Clear Word Invert Word Invert Halfword | ORW OHR ORV ORS ORHS XOW XOH XOV XOS XOHS ANW ANH ANV ANS ANHS FLW FLH CLW CLH IVW IVH | (EWA) V (R) $\rightarrow$ (R)<br>(EHA) <sub>SE</sub> V (R) $\rightarrow$ (R)<br>V <sub>SE</sub> V (R) $\rightarrow$ (R)<br>(EWA) V (R) $\rightarrow$ (EWA)<br>(EHA) <sub>SE</sub> V (R) $\rightarrow$ (EHA) +<br>(EWA) $\forall$ (R) $\rightarrow$ (R)<br>(EHA) <sub>SE</sub> $\forall$ (R) $\rightarrow$ (R)<br>(EWA) $\forall$ (R) $\rightarrow$ (EWA)<br>(EWA) $\forall$ (R) $\rightarrow$ (EWA)<br>(EHA) <sub>SE</sub> $\forall$ (R) $\rightarrow$ (EHA) +<br>(EWA) $\land$ (R) $\rightarrow$ (R)<br>(EHA) <sub>SE</sub> $\land$ (R) $\rightarrow$ (R)<br>(EWA) $\land$ (R) $\rightarrow$ (R)<br>(EWA) $\land$ (R) $\rightarrow$ EWA<br>(EHA) <sub>SE</sub> $\land$ (R) $\rightarrow$ EHA +<br>1's $\rightarrow$ (EWA)<br>1's $\rightarrow$ (EWA)<br>0's $\rightarrow$ (EWA)<br>One's complement (EWA) $\rightarrow$ (EWA)<br>One's complement (EWA) $\rightarrow$ (EWA) |

| OPERATION                             |             | ММ      | IEMONIC                                            |                        | FUNCTION                                                                                                  |                |         |  |

|---------------------------------------|-------------|---------|----------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------|----------------|---------|--|

| Fixed-Point Arithmetic                |             |         |                                                    |                        |                                                                                                           |                |         |  |

| Operations                            |             |         |                                                    |                        |                                                                                                           |                |         |  |

| Add Word                              |             |         | ADW                                                |                        | + (R) → (R) <del> </del>                                                                                  |                |         |  |

| Add Halfword                          |             |         | ADH                                                |                        | + (R) → (R) +                                                                                             |                |         |  |

| Add Value                             |             |         | ADV                                                |                        | [R) → (R)                                                                                                 |                |         |  |

| Add Word to Storage                   |             |         | ADS                                                |                        | + (R) → (EWA) +                                                                                           |                |         |  |

| Add Halfword to Sto<br>Subtract Word  | orage       |         | ADHS<br>SBW                                        |                        | (R) → (EHA) +<br>(EWA) → (R)++                                                                            |                |         |  |

| Subtract Word                         |             |         | SBH                                                |                        | EHA) <sub>se</sub> → (R) +                                                                                |                |         |  |

| Subtract Value                        |             |         | SBV                                                |                        | V <sub>SE</sub> → (R)                                                                                     |                |         |  |

| Subtract Word from                    | Storage     |         | SBS                                                | (EWA)                  | – (R) <del>→</del> (EWA) <del>   </del>                                                                   |                |         |  |

| Subtract Halfword fr                  | om Stora    | ge      | SBHS                                               | (EHA) <sub>se</sub>    | — (R) <del>→</del> (EHA) +                                                                                |                |         |  |

| Difference Word                       |             |         | DFW                                                |                        | (EWA) 1→ (R)                                                                                              |                |         |  |

| Difference Halfword                   |             |         | DFH<br>DFV                                         |                        | (EHA) <sub>se</sub> 1 → (R)                                                                               |                |         |  |

| Difference Value Difference Word to S | Storage     |         | DFS                                                |                        | $V_{SE} 1 \rightarrow (R)$<br>$V_{SE} \rightarrow (EWA)$                                                  |                |         |  |

| Difference Halfword                   |             | e       | DFHS                                               |                        | $_{\rm SE} - (R) 1 \rightarrow (EHA) +$                                                                   |                |         |  |

| Multiply Word                         | io otorug   | •       | MLW                                                |                        | EWA) → (R,R+1) 7                                                                                          |                |         |  |

| Multiply Halfword                     |             |         | MLH                                                | $(R) \times ($         | $EHA)_{SE} \rightarrow (R,R+1) + Low or$                                                                  | der in         | R+1   + |  |

| Multiply Value                        |             |         | MLV                                                | $(R) \times \setminus$ | $I_{SE} \rightarrow (R,R+1)$                                                                              |                |         |  |

| Divide Word                           |             |         | DVW                                                | (R,R+1                 | $) \div (EWA) \rightarrow (R,R+1)$ quoti                                                                  | ent in         | R+1     |  |

| Divide Halfword<br>Divide Value       |             |         | DVH<br>DVV                                         | (H,H+1<br>(P.R±1       | ) $\div$ (EHA) <sub>SE</sub> $\rightarrow$ (R,R+1) rema<br>) $\div$ V <sub>SE</sub> $\rightarrow$ (R,R+1) | ınaer          | in H    |  |

| Augment Word                          |             |         | AGW                                                |                        |                                                                                                           |                |         |  |

| Augment Halfword                      |             |         | AGH                                                |                        |                                                                                                           |                |         |  |

| Diminish Word                         |             |         | DMW                                                |                        | -1 <del>→</del> (ÈWA) ++                                                                                  |                |         |  |

| Diminish Halfword                     |             |         | DMH<br>NGW                                         |                        | -1 → (EHA) +                                                                                              |                |         |  |

|                                       | Negate Word |         |                                                    |                        | omplement (EWA) → (EWA)                                                                                   |                |         |  |

| Negate Halfword                       |             |         | NGH                                                | two's co               | omplement (EHA) <sub>SE</sub> $\rightarrow$ (EHA) $+$                                                     | -              |         |  |

| OPERATION M                           | INEMONI     | С       |                                                    | FUNCTION               | N                                                                                                         |                |         |  |

| Compare Operations *                  |             |         |                                                    |                        |                                                                                                           | C <sub>o</sub> | Cı      |  |

| Compare Word                          | CMW         |         | (EWA) with (R)                                     |                        | 7                                                                                                         |                |         |  |

| Compare Halfword                      | CMH         |         | (EHA) <sub>SE</sub> with (R)                       |                        |                                                                                                           | _              | _       |  |

| Compare Value<br>Test Word            | CMV<br>TSW  |         | V <sub>SE</sub> with (R)                           |                        | (EA)=(R)                                                                                                  | 0              | 0       |  |

| Test Word Test Halfword               | TSH         |         | (EWA) with 0<br>(EHA) <sub>se</sub> with 0         |                        | ⊢(EA)>(R)<br>(EA)<(R)                                                                                     | 0<br>1         | 1<br>0  |  |

| Collate Word                          | UCM         |         | (EWA) with (R) as un                               | sianed nos.            | (LA) < (11)                                                                                               |                | U       |  |

| Collate Halfword                      |             |         | (EHA) <sub>ZE</sub> with (R) as u                  |                        | .                                                                                                         |                |         |  |

| Collate Value                         | UCMV        | compare | Vze with (R) as unsig                              | ned nos.               | _                                                                                                         |                |         |  |

| Compare Register                      | CIS         | compare | (R) with (EWA) and                                 |                        | $(EA) \le (R) \le (EA+1)$                                                                                 | 0              | 0       |  |

| with Word                             |             |         | and set condition co                               | ode                    | $(EA) \ge (R) \ge (EA + 1)$                                                                               | 0              | 0       |  |

| Interval<br>Compare Register          | CISH        | compare | (R) with (EHA) and (                               | ΈΗΛ <b>⊥ 1</b> )       | (EA) < (R); (R) > (EA+1)                                                                                  | 0<br>1         | 1<br>0  |  |

| with Halfword                         | CIOII       | compare | and set condition co                               |                        | (EA) > (R); (R) < (EA+1)                                                                                  | ı              | U       |  |

| Interval                              |             |         |                                                    |                        | _                                                                                                         |                |         |  |

| Compare Word in                       | CIW         | compare | (EWA) with (R) and (                               | (R+1)                  | $R \leq (EA) \leq (R+1)$                                                                                  | 0              | 0       |  |

| Storage with                          |             |         | and set condition                                  |                        | $(R) \ge (EA) \ge (R+1)$                                                                                  | 0              | 0       |  |

| Interval<br>Compare Halfword          | CIL         | 00m=5== | (EUA) with (D) : 1                                 | (D   1)                | (R) < (EA); (EA) > (R+1)                                                                                  | 0              | 1       |  |

| in Storage with                       | CIH         | compare | (EHA) <sub>SE</sub> with (R) and and set condition | (n + 1)                | (R)>(EA); (EA)<(R+1)                                                                                      | 1              | 0       |  |

| Interval                              |             |         | and out condition                                  |                        | _                                                                                                         |                |         |  |

|                                       |             |         |                                                    |                        |                                                                                                           |                |         |  |

$<sup>\</sup>ensuremath{^{\star}}$  for compare operations set conditions according to result

Unpack: clear the register towards which the shift is to occur to zero then perform a doubleword open logical shift.

```

OPERATION

MNEMONIC

FUNCTION

Bit Operations

Clear Bit

CLB

0 \rightarrow (EHA)_R

Fill Bit

FLB

1 \rightarrow (EHA)_R

Invert Bit

IVB

one's complement of (EHA)_R \rightarrow (EHA)_R

SKZ

Skip on Zero

if (EHA)_R = 0, I+1 \rightarrow I

Skip on Zero and Zero Bit

SKZC

if (EHA)_R = 0, I+1 \rightarrow I; 0 \rightarrow (EHA)_R (regardless of outcome)

Skip on Zero and Fill Bit

SKZF

if (EHA)_R = 0, I+1 \rightarrow I; 1 \rightarrow (EHA)_R (regardless of outcome)

Skip on Zero and Invert Bit

SKZI

if (EHA)_R = 0, I+1 \rightarrow I; one's complement (EHA)_R \rightarrow (EHA)_R

(regardless of outcome)

Skip on Bit

SKB

if (EHA)_R = 1, 1+1 \rightarrow 1

Skip on Bit and Zero Bit

SKBC

if (EHA)_R = 1, I+1 \rightarrow I; 0 \rightarrow (EHA)_R (regardless of outcome)

if (EHA)_R = 1, I+1 \rightarrow I; 1 \rightarrow (EHA)_R (regardless of outcome)

Skip on Bit and Fill Bit

SKBF

Skip on Bit and Invert Bit

SKBI

if (EHA)_R = 1, I+1 \rightarrow I; one's complement (EHA)_R \rightarrow (EHA)_R

(regardless of outcome)

Jump and Execute Operations

if (R) = 0, EWA \rightarrow I

Jump if Equal to Zero

JEZ

if C_0 C_1 = 00, EWA\rightarrow 1

Jump if Equal

JΕ

if (R) \neq 0, EWA \rightarrow 1

Jump if Not Equal to Zero

JNEZ

if C_0 C_1 \neq 00, EWA \rightarrow I

Jump if Not Equal

JNE

Jump if Greater than Zero

JGZ

if (R)>0, EWA \rightarrow1

Jump if Greater

JG

if C_1 = 1, EWA \rightarrow 1

JLEZ

if (R) < 0, EWA \rightarrow I

Jump if Less than or Equal to Zero

JLE

if C_1 = 0, EWA \rightarrow I

Jump if Less than or Equal

JLZ

Jump if Less than Zero

if (R) <0, EWA \rightarrow I

Jump if Less

JL

if C_0 = 1, EWA \rightarrow I

JGEZ

Jump if Greater than or

if (R) \geq 0, EWA \rightarrow I

Equal to Zero

Jump if Greater than or Equal

JGE

if C_0 = 0 EWA \rightarrow I

Jump if Even

JEV

if (R)_{31} = 0, EWA \rightarrow I

Jump if Odd

JOD

if (R)_{31} = 1, EWA \rightarrow 1

Jump if Implication

JIM

if C_0 C_1 = 11, EWA \rightarrow I

if C_0 C_1 = 11, EWA \rightarrow I

Jump if No Implication

JNIM

JIН

(R) +1 \rightarrow (R); EWA \rightarrowI unless (R)<sub>15</sub> changes

Jump on Register Incre-

mented by Halfword

JDH

(R) -1 \rightarrow (R); EWA \rightarrowI unless (R)<sub>15</sub> changes

Jump on Register Decre-

mented by Halfword

Jump on Register Incre-

JIW

(R) +2 \rightarrow (R); EWA \rightarrowI unless (R)<sub>15</sub> changes

mented by Word

Jump on Register Decre-

JDW

(R) -2 \rightarrow (R); EWA \rightarrowI unless (R)_{15} changes

mented by Word

Jump on Register Incre-

JID

(R) +4 \rightarrow (R); EWA \rightarrowI unless (R)<sub>15</sub> changes

mented by Doubleword

JDD

(R) -4 \rightarrow (R); EWA \rightarrow I unless (R)<sub>15</sub> changes

Jump on Register Decre-

mented by Doubleword

R is interpreted as follows:

[if (R)_{2,3} = 0, (R) + 1 \rightarrow (R)]

JIB

Jump on Register Incre-

[if (R)_{2,3} = 0, (R) +2 \rightarrow (R)]_{2|3|}

30 31 0 1

mented by Field

if (R)_{2,3} = 0, (R) -1 \rightarrow (R)

if (R)_{2,3} = 0, (R) -2 \rightarrow (R)

Jump on Register Decre-

JDB

jump unless (R)<sub>30</sub> changes if (R)<sub>15</sub> changes, 0 \rightarrow (R)_{0-31}

mented by Field

1→ (R), EWA → I

Link and Jump

LNJ

JMP

EWA → I

Jump

Link and Execute

LNK

I → (R) then execute (EWA)

Execute

XEC

execute (EWA)

Control Operations

Load Program Stateword

LPS

(EWA, EWA+1) → PS1, PS2

Exchange Program

(EWA, EWA+1) ₹ PS1, PS2

SWS

Stateword

Control Process

CP

transmit EWA to Multiprocess Controller

```

#### **H632 SYSTEM INFORMATION FLOW**

Figure 7

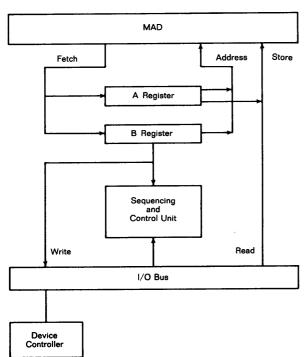

### SIMPLIFIED IOP BLOCK DIAGRAM

Figure 8

### **H632 INPUT/OUTPUT PROCESSOR**

General Description — The word-oriented H632 Input/ Output Processor (IOP) has highly developed I/O facilities and limited arithmetic processing capabilities. The IOP performs all I/O operations in the basic H632 System. In the basic system, the IOP performs memory accesses, on a cycle-stealing basis, to a memory bank shared with the CP. Command fetch and execution, as well as the transfer of data between memory and a peripheral device, are accomplished without CP intervention.

**Operation** — The IOP issues memory access requests to the MAD. If memory is not being accessed by another processor, the IOP request will be acknowledged, and the contents of the addressed memory location will be presented to the IOP for processing. If the memory access was a command fetch, the various subfields of the command word are processed and operations are performed in accordance with command definition. If the memory access was a data-transfer request, a transfer is made under the direction of the controller initiating the request.

Figure 7 shows the lines of communications for instructions, commands, orders and other information in the basic H632 System. Note that the IOP and IOP I/O bus deal with information from the MPC as well as with information from memory and device controllers. The MPC issues service requests for channel program command execution on behalf of the highest priority sequencing channel. The device controllers issue control directives to the MPC and IOP to change program states and transfer device status. The IOP may also issue orders to the MPC change program state as does the CP.

Internal Organization — The IOP contains two 32-bit registers (A and D), a sequencing and control unit, and an I/O bus distribution system. Figure 8 shows a simplified block diagram of the IOP.

A and D Registers

The A and D registers are used in:

- a. Command interpretation and execution

- b. Output of data

- c. Channel stateword modification

Sequencing and Control Unit (SCU) — The SCU controls the interface of the IOP with primary storage via the MAD, with the MPC, and with the various device controllers. It also retains and acts on the basic control information required for program sequencing and command execution.

Data transfers between memory and peripheral devices are accomplished over data channels. Associated with each IOP channel is a pair of Channel Statewords retained in dedicated memory locations. The standard H632 IOP provides eight channels, optionally expandable to 16 channels. Since the IOP contains independent I/O channels and corresponding channel programs, multiprogrammed/multichannel operations may be performed.

I/O = Input/Output

O = Output

I = Input

= Number of lines

Figure 9

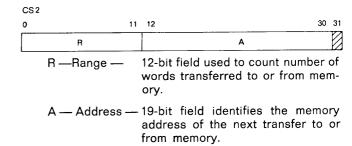

Channel Statewords — Each channel program is characterized by an activity state indicator retained by the MPC and by two channel statewords retained in memory.

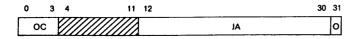

Channel Stateword format:

CS1

0 7 8 11 12 30 31

S — Status — Eight-bit field coded to represent the status of the device most recently serviced by this channel.

C — Count — Four-bit field used by the channel program to count iteration of program loops.

P — Pointer — 19-bit field which identifies the memory address of the next command in the associated channel program.

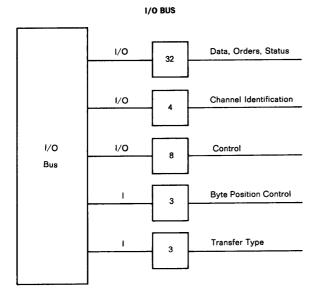

$I/O\ Bus\ System$  — Provides the communication path for data and control between the IOP and device controllers.

Figure 9 shows I/O bus signal lines. Device controllers are connected to this bus.

The various operations are performed as a result of controller responses to IOP commands and IOP responses to controller directives.

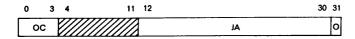

Commands — In performing I/O operations, a sequence of IOP commands, referred to as a channel program, will be executed. Commands may be stored in any contiguous area of memory. The Pointer field of CS1 points to the location of the next command to be executed in servicing the channel under consideration.

### Commands are:

OC — Op code

PS — Process selection —

Effect of execution: The command word itself is transmitted to the IOP bus. PS is interpreted by the MPC as the process identification and the function to be performed on it.

of the word at SA. Bits 12-31 are not modified.

SA

5. Store Range and Address

OC — Op code

| 2. Order Transmit 0 3 4 10 11 23 24 30 31                                                                                                                                                        | 6. Load Range and Address 0 11 12 30 3                                                                                                                                                                                                                             | 31      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| OC CR DV FN O                                                                                                                                                                                    | RN DA                                                                                                                                                                                                                                                              | 1       |

| OC — Op code CR — Controller identification DV — Device FN — Function to be performed Effect of execution: The command word itself is transmitted to the IOP bus.                                | OC — Op code  RN — Range  DA — Data address  Effect of execution: The one's complement of RN replaces R, and DA replaces A, in CS2. Bit 31 of CS2 is set to 1. Note that bit 31 is a 1 in this command.                                                            | C       |

| 3. Store Status  0 3 4 11 12 30 31  OC SA O  OC— Op code  SA— Storage address  Effect of execution: The status field of CS1 is stored in bits 0-7 of the word at SA. Bits 8-31 are not modified. | 7. Store Count 0 3 4 7 8 11 12 30 3  OC Op code CT SA  OC—Op code CT—Storage address Effect of execution: The count field of CS1 is stored in bits 8-11 of the word at SA, leaving bits 0-7 and 12-31 unmodified. The count field in CS1 is then replaced with CT. | 31<br>O |

| 4. Store Range 0 3 4 11 12 30 31  OC //////// SA 0                                                                                                                                               | Jump Format<br>0 3 4 11 12 30 3                                                                                                                                                                                                                                    | 31      |

| OC — Op code SA — Storage address Effect of execution: R of CS2 is stored in bits 0-11                                                                                                           | OC — Op code MK — Mask                                                                                                                                                                                                                                             | 0       |

logical product of S and MK equals zero.

JA - Jump address

8. Jump on Status Reset

Effect of execution: JA replaces P in CS1 if the

SA — Storage address

Effect of execution: R and A of CS2 are stored in bits 0-30 of the word at SA; bit 31 of the word at SA is made a 1.

9. Jump on Status Set Effect of execution: JA replaces P in CS1 if the logical product of MK and the one's complement of S equals zero.

30 31

### 10. Jump on Status not Reset

Effect of execution: JA replaces P in CS1 if the logical product of S and MK is not equal to zero.

### 11. Jump on Status not Set

Effect of execution: JA replaces P in CS1 if the logical product of MK and the one's complement of S is not equal to zero.

### 12. Jump on Count Zero

### OC - Op code

Effect of execution: Increment the count field of CS1; if the count field is then equal to zero, JA replaces P in CS1.

### 13. Jump on Count Non-Zero

### OC — Op code

Effect of execution: Increment the count field of CS1; if the count field is then not equal to zero, JA replaces P in CS1.

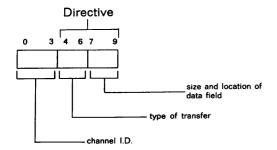

Service Requests — In addition to executing commands, the IOP responds to service requests generated by device controllers and the MPC. Upon IOP receipt and acknowledgement of the service request, the originator of the request furnishes information containing a channel number and a directive. The IOP then performs the operation encoded in the directive for the identified channel.

### Service request format

There are two types of directives—control and transfer: Control Directives — This type of directive is related to the state of channels, the status of controllers, and command execution rather than to data transfers.

### 1. Execute Command

P in CS1 of the identified channel is used as an address to fetch a command from memory; P is then incremented. The command fetched is executed as specified above. Should the command that was fetched not be executable (i.e., an order transmission command not accepted by a controller), P will be decremented, resulting in a value equal to the initial value. Both the MPC and device controller may issue this directive.

### 2. Change State

This directive is ignored by the IOP, and is responded to by the MPC. A typical device controller would cause the assigned channel and all waiting channels to become sequencing when the controller is available for reassignment. This directive is issued by a device controller.

### 3. Change Status

Status information supplied by the initiating controller is transferred to S in the CS1 of the identified channel. This directive could be issued by a controller that has detected some error condition that has occurred in the device it is serving. Note that the channel identification is supplied with this directive. This implies that controllers must retain the assigned channel number during engagement. This directive is issued by a device controller.

### 4. Change State and Status

This directive combines the two directives listed above. A typical controller would generate this directive upon completion of an I/O transfer. Thus, the status of the device would be transmitted to the channel stateword and the state of the channel(s) could be altered.

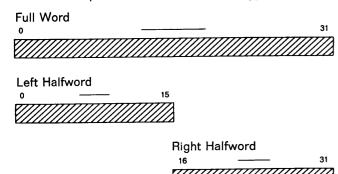

Transfer Directives — Transfer directives, issued by device controllers, are concerned with data transfers. Encoded within the directive are the identification of the channel over which the transfer is to take place and the type of transfer to be performed. The directive also specifies the size and location within a computer word of the data field to be transferred. Eight-bit byte, 16-bit halfword, and 32-bit fullword transfers may be performed. The IOP uses fields A (data address) and R (range) from the identified channels CS2, in servicing requests for data transfer.

### Transfer directives are:

### 1. Input

Data supplied by the controller replaces the selected field in the word pointed to by A.

2. Output

Data from the selected field of the word pointed to by A is transferred to the controller.

3. Input and Count Down

Data supplied by the controller replaces the selected field in the word pointed to by A. A is then decremented by one and R is incremented by one. If R then contains all ones, an Execute Command operation is automatically performed for the identified channel.

4. Input and Count Up

Data supplied by the controller replaces the selected field in the word pointed to by A. A and R are then incremented by one. If R then contains all ones, an Execute Command operation is automatically performed for the identified channel.

5. Output and Count Up

Data from the selected field of the word pointed to by A, is transferred to the controller. A and R are then incremented by one. If R then contains all ones, An Execute Command operation is automatically performed for the identified channel.

As stated above the size and location of the data field to be transferred is specified in the transfer directive.

The IOP can perform transfers on these types of data:

Left-most Byte

Next to Left-most Byte

8 — 15 ////////

Next to Right-most Byte

Right-most Byte

No Transfer

Channel Activity States — There are four possible states that an IOP data channel may assume.

- Engaged In the engaged state, the channel is asassigned to, and under the direction of, a specific device controller. Engagement can occur when an Order Transmit command is executed by the IOP and the order issued by the IOP is accepted by the controller to which it was directed. When engagement occurs, the device controller assumes the responsibility for issuing directives to effect data transfers and request subsequent command execution for the corresponding channel program.

- Sequencing In the sequencing state, the channel is not assigned to a controller and the corresponding channel program requires command execution. The MPC issues the service request for command execution on behalf of the highest priority sequencing channel.

- Waiting In the waiting state, a channel requires engagement to a controller that is temporarily busy. Transition to this state may occur when an Order Transmit is not accepted by a busy controller.

- Stopped A channel is in the stopped state if it is in none of the above states.

Modes of Operation — By issuing an MPC directed order, Control Process, control over the mode of IOP operations is achieved.

- Selector

- The MPC may direct all but one channel to assume the waiting or stopped state. The remaining channel and assigned controller can then operate in a selector mode.

Multiplexer — The MPC and controller may direct all channels to assume the sequencing state.

Data transfers would then take place on a priority basis in a multiplexed mode.

### MULTIPROCESS CONTROLLER (MPC)

General Description — The Multiprocess Controller (MPC) serves as a clearing house for all interprocess and intraprocess state control requests in the H632 System. The MPC has the coordinating responsibility for the processes (programs) operating in the processors it administers.

Operation — Control of the states of the various processes (CP Program Levels and IOP Channel Activity) is accomplished through orders issued to the MPC either by IOP command, CP instructions or by signals received from device controllers. An external interrupt source may also be used to initiate/modify CP activity. (See Figure 10.)

CP Program Levels - can be in one of the following states:

Stopped - disabled

Enabled - conditioned to respond to an interrupt

Sequencing — program running if highest priority; pend-

ing running, if not

Committed — sequencing with a backed-up interrupt

request

CP program states can be modified by any and all processors (CP and IOP) in the system, and optionally by some external source. The H632 CP can have a maximum of 40 program levels.

IOP Program Levels (channel programs) — can be in one of the following states:

Stopped - none of the below

Waiting - for a busy controller to become available

Sequencing — program running if highest priority, pending running, if not

- under the control of an I/O device con-Engaged

troller

The standard IOP is capable of executing up to eight channel programs concurrently (optionally expandable to 16).

IOP program states can be modified by any and all processors (CP and IOP) in the system as well as by device controllers connected to the IOP.

#### SIMPLIFIED MULTIPROCESS CONTROLLER (MPC) BLOCK DIAGRAM

Figure 10

Interprocess and Intraprocess Level Control - Both the CP and the IOP can execute a Control Process instruction (command), the net effect of which is the transmittal of a 12-bit number to the MPC. This number is interpreted by the MPC as follows:

16-23 - identifies a target processor and process level (or channel) whose activity state is to be affected.

24 and 25 — is an interprocess order which defines the change to be made to the target process.

26 and 27 — is an intraprocess order which defines a change to be made to the activity state of the process which transmitted the order.

The MPC is responsible for determining the priorities of service requests and for furnishing each CP and IOP with a code identifying the sequencing process of highest priority.

The MPC also maintains indicators of the state of CP processes and IOP channel activity. These indicators can be displayed on the system control panel.

### PRINTER/KEYBOARD

Introduction — The character printer/keyboard provides the basic communication link between the operator and the H632 System. This feature consists of a KSR-35 character printer/keyboard and controller which can send and receive information in USASCII code at a maximum rate of ten characters per second.

The controller provides the necessary interface logic between the IOP and the KSR-35. It controls the sequencing of the KSR-35 and the data flow and format through the use of orders received from the IOP.

**Operation** — The KSR-35 controller executes these orders issued to it by the IOP:

Input from keyboard, packing 1 byte/word Input from keyboard, packing 4 bytes/word Output to printer, unpacking 1 byte/word Output to printer, unpacking 4 bytes/word Stop

Output without printing until stop

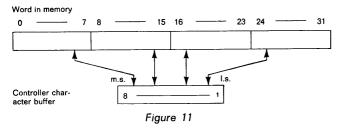

An output order allows the transfer of information directly from memory to the printer. The controller will continue to request service from the IOP until a stop order is received. An input order to the controller may be used to transfer information from the keyboard directly to memory. This order may be terminated by the depression of the carriage return key or by a stop order. In addition to directing the flow of information, the input and output orders specify character packing and unpacking (refer to Figure 11).

The stop order is used to terminate output activity and may be used to terminate input activity. The output without printing order is useful as a 100 ms timing interval for carriage control functions (i.e., carriage return, vertical and horizontal tab functions).

The KSR-35 controller maintains status codes to indicate these conditions to the IOP:

- 1. Device presence

- 2. Incorrect keyboard parity

- 3. IOP response failure within 13.6 ms of request

- Premature termination to indicate that a stop order was used to terminate an input order prior to detection of a carriage return code

- 5. Keyboard interrupt

- 6. Position of last byte transferred

- 7. Normal device

When the printer or keyboard is operating at maximum speed, the controller will request service from the IOP every 100 ms. To maintain a printing rate of ten characters per second, a request for service initiated by the keyboard must be honored by the IOP within 13.6 ms. Failure to honor this request will result in loss of data. In the event that data is lost, an error status will be sent to the IOP at the end of the current order.

When the KSR-35 controller is non-busy (not assigned to a channel), hard copy will not be produced when a key is depressed. When the controller is in the output mode, hard copy will not be affected when a key is depressed. In either case, the keyboard interrupt status code will be set. The IOP will be notified of this when the next status transfer is made.

Controller — One character printer will be provided per controller. Mode of operation will be on-line only. Controller-to-IOP interface is half duplex; controller-to-device interface is full duplex. The controller is located within the basic main frame cabinet.

### **632-0001 SYSTEM SPECIFICATIONS SUMMARY**

CENTRAL PROCESSOR

Type: Parallel, binary, solid-state

Addressing: Single address (modified), with mul-

tilevel indexing and indirect ad-

dressing

Numeric

Representation: Two's complement

Circuitry: Integrated

Typical Execution

Times: (including instruction and operand fetch with indexing)

Add — 1.7  $\mu$ s

Subtract — 1.7  $\mu$ s

Multiply — 8.1  $\mu$ s

Divide — 28.05  $\mu$ s

Instruction 118 standard instructions