TITLE:

43A239854

HONEYWELL INFORMATION ENGINEERING PRODUCT SPECIFICATION, PART 1 6000B INPUT/OUTPUT MULTIPLEXER (IOM) CENTRAL

SYSTEMS INC. TOS, LADE.

Total Pages 135

Page 1

L16-90 CHIP NCO

REVISION RECORD

REVISION LETTER

DATE

PAGES AFFECTED

**APPROVALS**

AUTHORITY

CO ZEB-00-1784

- HES RECEIVED STOM DCS 34-

1 THRU 98F. A ISSUED OCT 1 2 1972

Sep. 25, 1973

OCT 17 1973 B Rev.

Rev.Sh. 1,8,17,18,22,

24,26,62,63,71,73,74;

Ret.& Rev.Sh. 11,12, 20, 21, 28, 29, 31, 68, 69,

81,86,87

C Rev. DCT 0 4 1974

\$ 92, Rev. Sh. 1, Ret. & Rev. Sep. 12, 1974 CO PHAOXB022 Sh. 4; Changed Shts. 93

thru 97 to Shts. A2 thru A6;

Added Sh. Al, B1 thru B2OF;

Deleted Sh. 98F

JUL 15 1975 D Rev.

Rev. Sh. 1

RE 1 2/2/25 CO PHAD XBOSI

Rev. & Ret. Shs. B1 thru B20🏞

Shts. 21 & 27

Added B21 thru B37F

# HONEYWELL PROPRIETARY

The information contained in this document is proprietary to Honeywell Information Systems Inc. and is intended for internal Honeywell use only. Such information may be distributed to others only by written permission of an authorized Honeywell official. This restriction does not apply to vendor proprietary parts that may be disclosed in this

### Rev. A

Page 2

|     | CONTENTS                                                              | Page             |

|-----|-----------------------------------------------------------------------|------------------|

|     |                                                                       |                  |

| 1.0 | GENERAL DESCRIPTION                                                   | 5                |

|     | 1.1 Data Channels                                                     | 6                |

|     | 1.2 Overhead Channels                                                 | 6                |

|     | 1.2.1 Bootload Channel                                                | 6                |

|     | 1.2.2 Connect Channel                                                 | 6                |

|     | 1.2.3 System Fault Channel                                            | 7                |

|     | 1.2.4 Wraparound Channel                                              | 7                |

|     | 1.2.5 Snapshot Channel                                                | 7                |

|     | 1.2.6 Scratchpad Access Channel                                       | 7                |

|     | 1.2.7 Special Status Channel                                          | 7                |

|     | 1.3 Scope of this Document                                            | 8                |

|     | 1.4 Applicable Documents                                              | 8                |

|     | 1.5 Definitions                                                       | 9                |

|     | 1.5.1 Tally Runout (TRO)                                              | 9                |

|     | 1.5.2 Pre-Tally Runout (PTRO)                                         | 9                |

|     | 1.5.3 List Pointer Word (LPW)                                         | 9<br>9<br>9<br>9 |

|     | 1.5.4 Data Control Word (DCW)                                         | 9                |

|     | 1.5.5 Peripheral Control Word (PCW)                                   |                  |

|     | 1.5.6 Status Control Word (SCW)                                       | 9                |

| 2.0 | FUNCTIONAL CAPABILITIES                                               | 10               |

|     |                                                                       | 10               |

|     | 2.1 Basic Characteristics 2.1.1 General                               | 10               |

|     | 2.1.2 Relationship to 6000 IOM                                        | 11               |

|     | 2.2 Configurations                                                    | 12               |

|     | 2.2.1 Basic IOM Central                                               | 12               |

|     | 2.2.2 Options                                                         | 12               |

|     | 2.3 Data Transfer Rates                                               | 13               |

|     | 2.4 Concurrent Operation                                              | 14               |

| •   | 2.5 Data Formats                                                      | 14               |

| 3.0 | SOFTWARE AND CUSTOMER INTERFACE REQUIREMENTS                          | 16               |

| 3.0 |                                                                       | 17               |

|     | 3.1 Software Interface                                                | 18               |

|     | 3.1.1 Connects                                                        | 18               |

|     | 3.1.2 Control Words                                                   | 18               |

|     | 3.1.3 Program Interrupts                                              | 19               |

|     | 3.2 Control Word Formats                                              | 19               |

|     | 3.2.1 List Pointer Words (LFW & LFW Extension)                        | 24               |

|     | 3.2.2 Peripheral Control Words (PCW)                                  | 26               |

|     | 3.2.3 Data Control Word DCW)                                          | 32               |

|     | 3.2.4 Status Control Word (SCW) 3.2.5 Channel and Device Status Words | 33               |

|     |                                                                       | 35               |

|     |                                                                       | 37               |

|     | 3.2.7 Interrupt Multiplex Word (IMW)                                  | ٠,               |

CE 301-1 (6-71

Rev. A

Page 3

|     |      |                                                              | rage   |

|-----|------|--------------------------------------------------------------|--------|

|     | 3.3  | Boundary Checking                                            | 42     |

|     | 3.3  | 3.3.1 Notation                                               | 42     |

|     |      | 3.3.2 Check Performed                                        | 42     |

|     |      | 3.3.3 Address Result                                         | 43     |

|     | 3 /  | Channel Numbering                                            | 43     |

|     |      | Mailboxes and Store Map                                      | 44     |

|     | 3.5  | 3.5.1 Channel Mailbox Base Address Switches                  | 46     |

|     |      | 3.5.2 Interrupt Multiplex Base Address Switches              | 46     |

|     | 2 6  | System Fault Channel                                         | 47     |

|     |      | Connect Channel                                              | 48     |

|     |      | Snapshot Channel                                             | 49     |

|     | 3.8  | Snapshot Channel (MAC)                                       | 52     |

|     | 3.9  | Wraparound Channel (WAC) 3.9.1 Peripheral Control Word (PCW) | 53     |

|     |      | 3.9.1 Peripheral Control word (10w)                          | 54     |

|     |      | 3.9.2 Data Word                                              | 55     |

|     |      | 3.9.3 Status Word                                            | 56     |

|     |      | Bootload Channel                                             | 60     |

|     | 3.11 | Scratchpad Access Channel                                    | 62     |

|     | 3.12 | Maintenance Panel and Configuration Switches                 | 62     |

|     |      | 3.12.1 Fault Location Aids                                   | 63     |

|     |      | 3.12.2 Base Addresses                                        | 63     |

|     |      | 3.12.3 Software Operating System Control                     | 64     |

|     |      | 3.12.4 Configuration Switches                                | 65     |

|     | 3.13 | Special Status                                               | 66     |

| 4.0 | HARI | OWARE INTERFACE REQUIREMENTS                                 |        |

|     | 4 1  | Storage Interfaces                                           | 66     |

|     | 7.1  | 4.1.1 System Controller                                      | 66     |

|     |      | 4.1.2 Scratchpad Storage                                     | 66     |

|     | 1. 2 | Priority                                                     | 66     |

|     |      | Channel Service                                              | 67     |

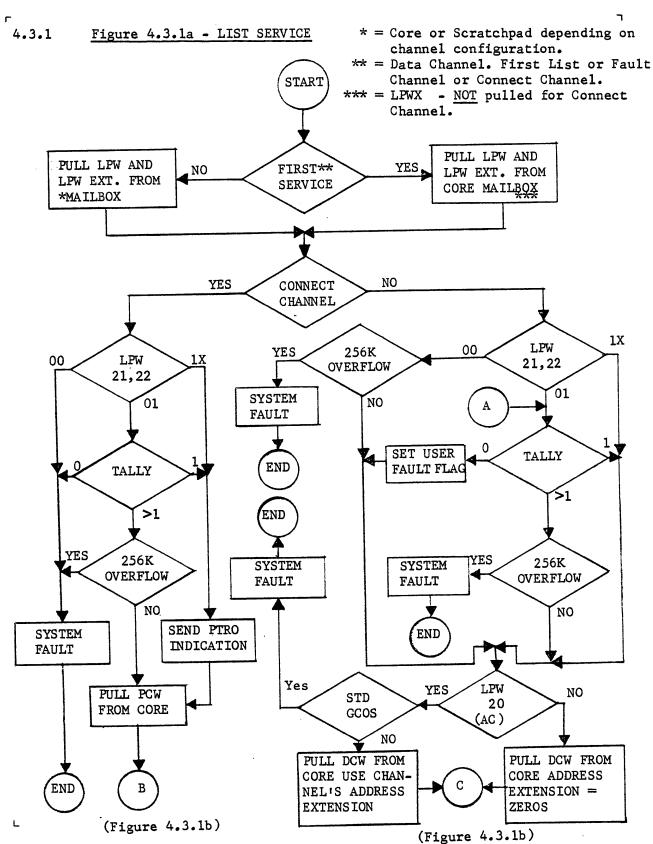

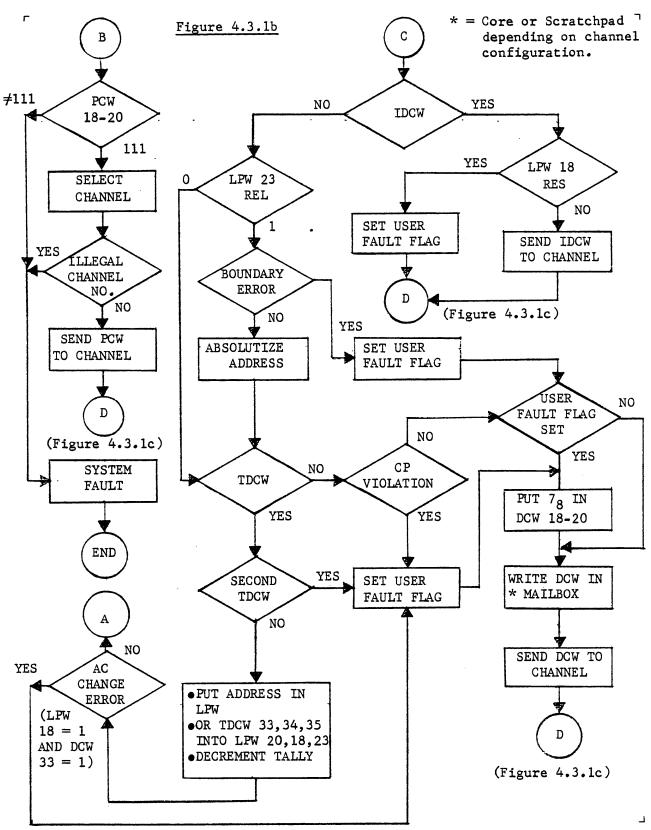

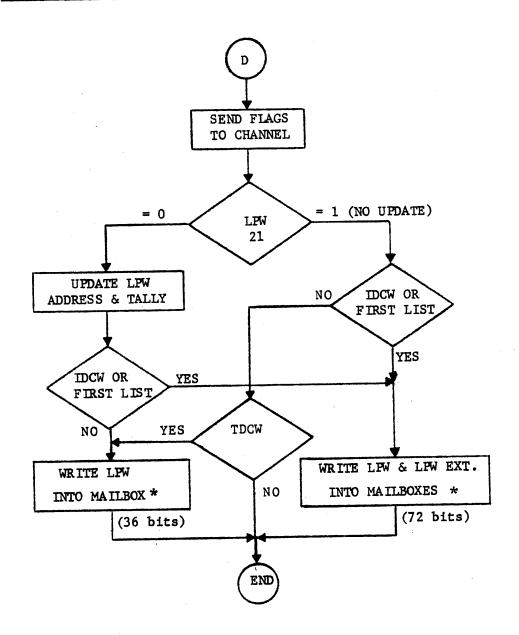

|     | 4.5  | 4.3.1 List Service                                           | . 67   |

|     |      | 4.3.2 Backup List Service                                    | 71     |

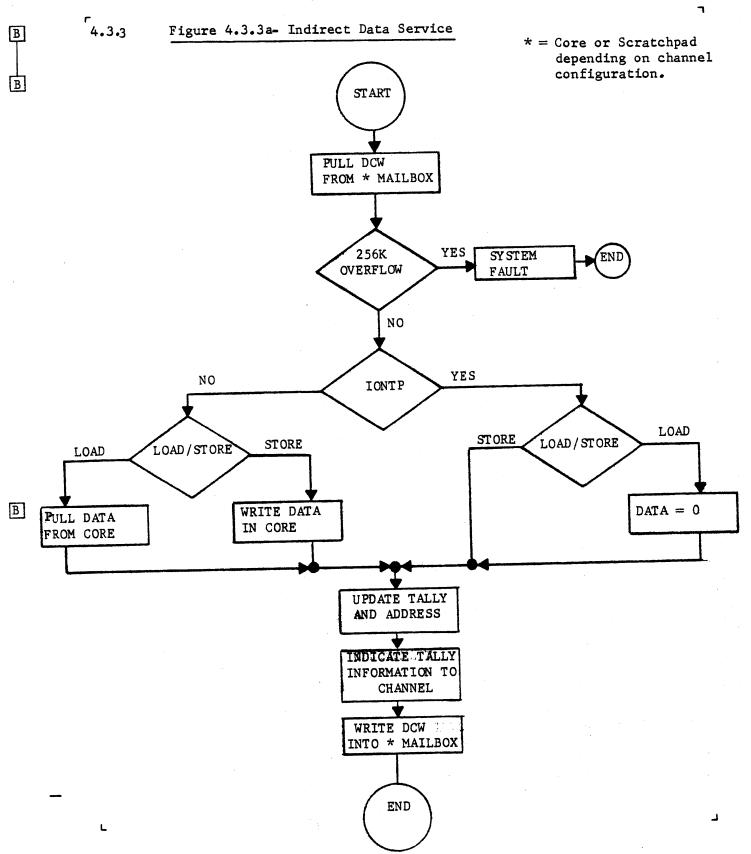

|     |      | 4.3.3 Indirect Data Service                                  | 71     |

|     |      | 4.3.4 Direct Data Service                                    | 72     |

|     |      | 4.3.5 Status Service                                         | 72     |

|     |      | 4.3.6 Program Interrupt Service                              | 75     |

|     | , ,  | 7.3.0 Program Interity                                       | 77     |

|     |      | Parity and Data Integrity                                    | 77     |

|     | 4.5  | Faults                                                       | 78     |

|     |      | 4.5.1 System Faults                                          | 82     |

|     |      | 4.5.2 Use/Channel Faults                                     | 84     |

|     |      | 4.5.3 Fault Definitions                                      | 85     |

|     | 4.6  | 224 Address Development Summary                              | 85     |

|     |      | 4.6.1 Mailbox Addresses - Any Mode                           | 86     |

|     |      | 4.6.2 PCW List Addresses - Any Mode                          | 86     |

|     |      | 4.6.3 DCW List Addresses                                     | 86     |

|     |      | 4.6.4 Data Addresses                                         |        |

|     |      | 4.6.5 Status Lists, Interrupt Multiplex Words, a             | ing 57 |

|     |      | System Fault Word Addresses - Any Mode                       |        |

В1

CE 301-1 (6-71)

APPENDIX B

Page 5

#### GENERAL DESCRIPTION 1.0

The IOM Central controls access to storage for the various channels of the IOM by providing appropriate services to the channels, one at a time.

The IOM has eight generic types of channels:

- o Data Channel

- o Connect Channel

- o Fault Channel

- o Wraparound Channel

- o Bootload Channel

- . o Snapshot Channel

- o Scratchpad Access Channel

- o Special Status Channel

Each channel has assigned to it four (4) 36 bit mailbox words. use of these words vary with the type of channel. The words are listed below in the order that they appear in a memory map (lowest address first) and the definitions appear later in the text.

List Point Word (LPW) List Pointer Word Extension Status Control Word (SCW) Working Storage for Data Control Word (DCW)

The data channels are "payload" channels; they are responsible for information transfer with all external peripheral devices and adapters. The other seven types of channels are "overhead" channels; they perform specialized internal functions necessary for successful operation of the IOM.

The IOM Central includes a scratchpad storage to hold various channel control words. The scratchpad is a high speed store accessible to the IOM Central and the scratchpad access channel. It is used to reduce the time required for performing various services to channels, by storing control words for from 16 to 32 payload channels. The LPW, LFW extension and DCW (see paragraph 3.2) for each channel will normally be stored in scratchpad memory, unless scratchpad is not provided for a particular group of channels (see paragraph 2.2.2).

Following the introduction to the various functions, a description of a typical operation is included at the beginning of Section 3.0.

Rev.A

Page 6

### 1.1 DATA CHANNELS

Each data channel controls the flow of instructions, data and status between the IOM Central and a peripheral (or special) control unit. A data channel can use either of two basic methods of data transfer; direct or indirect. When the direct method of data transfer is used, the data channel specifies the core location (address) for each storage access. When the indirect method of data transfer is used, the IOM Central relieves the data channel of the task of addressing at the price of additional accesses by the IOM to: (a) core, or (b) scratchpad storage. The indirect data channel must, however, specify its channel number, which determines the location of its control words. Each time the indirect data channel makes an access request, the IOM Central obtains from core (or from the scratchpad) the appropriate control word, which defines the address for the data transfer and a tally specifying the amount of data to be transferred.

Each type of interface to a peripheral (or specials) control unit requires a particular type of data channel, so that in general there are several types of data channels, each of which is referenced in paragraph 1.4, Applicable Documents.

Data can be transferred between the IOM Central and either core storage or an indirect data channel in byte sizes of 9, 36 and 72 bits.

### 1.2 OVERHEAD CHANNELS

An overhead channel is a non-optional part of the IOM Central that provides a specific function and has some of the characteristics of a payload channel (i.e., uses the interface bus, competes with payload channels for service, has channel numbers, uses some mailboxes, etc.).

### 1.2.1 Bootload Channel

The bootload channel consists of non-destructive storage implemented as an IOM channel. When activated, it forces a limited number of interrupt vectors and control words to be stored in core storage, reads a record, and places the system into operation. The read is initiated by a Connect (\$CON) signal the IOM issues to itself.

### 1.2.2 Connect Channel

The connect channel controls the distribution of instructions which initiate the operation of any addressable channel capable of receiving instructions.

ı

L

Rev. A

Page 7

### 1.2.3 System Fault Channel

The system fault channel is responsible for reporting the occurrence of system fault conditions to the software. System faults are abnormal conditions resulting from the failure of hardware or system software. (System software consists of programs supplied for the purpose of controlling the operation of the computer system. System software does not include customer or application programs. Abnormal conditions in customer programs are reported by the affected data channel, and are classed as user faults rather than system faults, insofar as it is practical).

### 1.2.4 Wraparound Channel

The wraparound channel is a special channel intended for use by test and diagnostic software. By means of instructions issued to the wraparound channel by the software, the wraparound channel will cause the IOM Central to perform any specific type of service on behalf of any payload channel number designated in the instruction. The wraparound channel includes a data register and a status register which can be loaded and stored by means of appropriate services so that most data paths and control sequences in the IOM Central can be checked under program control.

#### 1.2.5 Snapshot Channel

The snapshot channel is a special channel for use by test and diagnostic software. It permits the software to sample particular signals in the IOM Central on the occurrence of events selected by the software.

## 1.2.6 Scratchpad Access Channel

The scratchpad access channel is a special channel used by the operating system and test and diagnostic software. It permits the software to read or write from the scratchpad.

## 1.2.7 Special Status Channel

The special status channel is a special channel which may be accessed by data channel adapters to store status associated with a special interrupt.

Rev. 🎮 B

Page 8

### 1.3 SCOPE OF THIS DOCUMENT

This document defines the functional and operational characteristics of the IOM Central and its overhead channels. This document does not define the various payload channels beyond the characteristics of their common interface to the IOM Central. For information about the payload channels refer to the Engineering Product Specifications for these channels.

### 1.4 APPLICABLE DOCUMENTS

EPS-1, 6000 System (58001123).

EPS-1, 6000 System Controller (43A219602)

EPS-1, IOM Common Peripheral Channel (43A219605)

EPS-1,6000B IOM Direct Channel (43A239853)

EPS-1, IOM Peripheral Subsystem Interface Adapter (43A177880)

EPS-1, Console Channel Adapter (43A232500)

General Design Requirements for 655/355 (43A177851)

655 Maintainability Design (43A219617)

Option Application Data List (43B240276)

B

Rev. A

Page 9

1.5 DEFINITIONS

### 1.5.1 Tally Runout (TRO)

In this document, a tally runout is a fault, defined as an exhausted LFW tally field (the contents of LFW bits 24 - 35 equal to zero), and LFW bits 21 and 22 set to 0, 1, respectively, at the time the LFW is taken from its mailbox in core or in scratchpad.

#### 1.5.2 Pre-Tally Runout (PTRO)

A pre-tally runout is defined as a tally in either a DCW or an LPW which will be reduced to zero by the current channel service (DCW during data service, LPW during list service).

### 1.5.3 List Pointer Word (LPW)

A word containing an address "pointing" to a list of control words, either DCW's or PCW's. NOTE: Only an LFW for a Connect Channel may legally point to a PCW.

## 1.5.4 Data Control Word (DCW)

A word containing an address indicating the first or current word of data in a list of data. IDCW, TDCW, IOTP, IONTP, and IOTD are variations of DCW's.

#### 1.5.5 Peripheral Control Word (PCW)

A word containing the number of the channel to be connected and, for CPI, an instruction or operation to be performed by a peripheral subsystem.

### 1.5.6 Status Control Word (SCW)

A word containing an address indicating the first or current empty position in a list of status words used by a particular channel.

#### 1.5.7 First List Service

A flag supplied by the channel to the IOM on the first list service following a connect. It directs the IOM to access the core LPW and LPWE mailboxes whether or not this channel has a scratchpad.

Rev. A

Page 10

### 2.0 FUNCTIONAL CAPABILITIES

#### 2.1 BASIC CHARACTERISTICS

### 2.1.1 General

The 6000B IOM will have the following characteristics:

- The ability to operate in a GCOS III mode with no Operating System or Slave software programming interface difference over the 6000 IOM design.

- The capability of operating in an Extended GCOS or MULTICS mode where addressable memory space to  $2^{24}$  locations is possible.

- The ability to change MODE by a manually operated configuration switch.

- The capability of interfacing up to eight (8) 6000B or 6000 System Controllers. There shall be one three position switch for each pair of ports. The following pairs of ports may be interlaced:

Ports A and B Ports C and D Ports E and F Ports G and H

The interlace mode may either be two (address bit 22) or four (address bit 21) word blocks.

- Provision for control word scratchpad storage for at least 24 payload channels.

- The ability to indicate with a configuration switch per port, that either all or half of the address range assigned to a memory port is available.

- The ability to support 36, 72 or 9 bit byte channels.

Rev. B

Page 11

### 2.1.2 Relationship to 6000 IOM

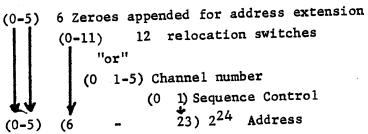

The following variations from the standard 6000 IOM are required for address extension to  $2^{24}$  locations:

- Control word mailboxes, interrupt multiplex words, PCW lists, system fault word lists, and status queues will reside in the first 256K core. DCW's may reside in either the first 256K block or in the same 256K block as the data (depending upon LPW bit 20).

- Transactions which cause addresses to be incremented will not be allowed to occur across modulo 256K (absolute) boundaries. That is, overflow past 2<sup>18</sup> is not allowed.

- The "address extension" (i.e., the 6 most significant bits of a 24-bit address field) will be used for all data transfers and, depending on LPW 20, may also be used when fetching a DCW during a list service. It will be obtained from the following sources:

- 1) From bits (12-17) of a PCW directed to a data channel in the Extended GCOS mode.

Restrictions: None.

2) During a list service from bits (12-17) of an IDCW directed to a data channel provided IDCW 21=1.

Restrictions: None.

Rev. B

Page 12

#### 2.2 CONFIGURATIONS

### 2.2.1 Basic IOM Central

The basic IOM Central has one connect channel, one system fault channel, one wraparound channel, one snapshot channel, one bootload channel, one scratchpad access channel, and one special status channel. No payload channels, system controller ports or scratchpads are included. Space is provided for 36 payload channel boards, one of which is used for the wraparound channel.

### 2.2.2 Options

- The 6000B IOM cabinet must be capable of supporting all the options listed in the Option Application Data List, 43B240276. A subset of these includes: from one to eight Ports to connect to 6000B or 6000 System Controllers.

- Provisions for adding space for 19 additional payload channel boards to the basic IOM.

- Payload Channels: The following payload channels may be used with the IOM:

6000B IOM Common Peripheral Channel (2 board spaces per channel required)

6000B IOM Peripheral Subsystem Interface Adapter (3 board spaces per channel required)

6000B IOM Direct Channel (1 board space per channel required)

6000B IOM Console Channel Adapter (3 board spaces required for each two channels)

Scratchpad: Scratchpads may be supplied for storage of control words. Scratchpads are added in groups of 16 channels. A maximum of 32 payload channels may be handled by the scratchpads.

When scratchpad modules are used, the channels whose control words are stored in the scratchpad will be determined on the basis of channel number, as follows:

The first optional scratchpad module is used for storage of control words for channels numbered  $010_8$ - $027_8$ .

The second optional scratchpad module is used for storage of control words for channels numbered  $030_g-047_g$ .

١

Rev. A

Page 13

#### 2.3 DATA TRANSFER RATES

The IOM Central will be capable of performing only one storage access cycle at any one time, regardless of the number of System Controllers to which it may be connected. When connected to a 6000B System Controller which is kept extremely busy by competition from processors and/or other IOM's, the IOM must be capable of requesting the next access cycle quickly enough to obtain every fourth cycle of the same bank of core storage.

The following conditions are assumed in specifying the data transfer rate capability:

- The referenced System Controller and core store are continuously busy.

- 2) Several channels of the same type are operating simultaneously to achieve the stated maximum transfer rate. (No single channel is required to be serviced at the stated maximum rate.)

- 3) Statement of the quantity of words per second further assumes a channel operating in double precision; 72 bits or two 36-bit words per access.

- 4) Data transfers in each direction (Reads and Writes) are equally probable.

- 5) Nominal circuit delay times are assumed.

- 6) Turn around times at IOM interface with 50 foot cables will be assumed as follows: (a) \$INT to \$DA with 0.5 microsecond memory = 820 nanoseconds; (b) \$INT to \$DA with 1.2 microseconds memory = 1500 nanoseconds.

Based on these assumptions, the following minimum capability of data transfer rates (total data throughput) are required of the IOM Central:

- 1) Using a 6000B System Controller and store, and indirect data channels operating without a scratchpad: one data access every 4.5 microseconds, or 440,000 words per second when using a 0.5 microsecond store and one data access every 9.3 microseconds or 215,000 words per second when using a 1.2 microsecond store.

- 2) Using a 6000B System Controller and store, and either direct channels or indirect channels operating with a scratchpad: one data access every 2.0 microseconds, or 1,000,000 words per second when using a 0.5 microsecond store and one data access every 3.2 microseconds or 625,000 words per second when using a 1.2 microsecond store.

٦

L

Rev. A

Page 14

#### 2.4 CONCURRENT OPERATION

The time required for the IOM Central to perform an indirect data service (and consequently for other types of service) is intended to be substantially less than the time required for the requesting channel to accumulate or disperse the data. As a result, the IOM Central will be time shared by a number of channels operating concurrently. The IOM Central provides appropriate services to the channels, one at a time. Such concurrent operation of channels will be successful only if the fraction of available service time used by each channel, summed over all concurrently operating channels is less than one, and if there is a sufficient amount of buffering in each concurrently operating channel.

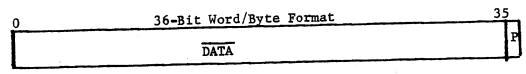

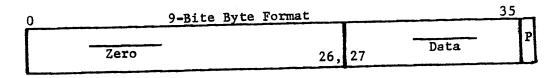

### 2.5 DATA FORMATS

An indirect data channel may work with byte sizes of 9, 36 or 72 bits. The IOM Central is capable of packing successive 9 bit bytes received from an indirect data channel into successive 9 bit byte positions, left to right, in a 36-bit word. It also may unpack 9 bit bytes from successive byte positions in a 36-bit word, left to right, for transmission to an indirect data channel. The Common Peripheral Channel will perform its own packing and unpacking.

Evolving system configurations and peripheral data transfer rates emphasize the need to <u>fully</u> utilize the available 6000B system controller interface, not only to maximize IOM thruput but to minimize I/O interference with storage access by system processors. The use of a 72 bit interface can result in a thruput increase when operating with a channel capable of buffering the 72-bit data width. The IOM Central design will incorporate the 72-bit data transfer capability.

Thus for indirect data channels the data in core store can be formatted as

- o one 9-bit character per access

- o one 36-bit word per access

- o two 36-bit words per access

The formatting chosen for programming purposes must be consistent with the character size used by the indirect data channel. The 3-bit codes shown in the following formats identify the various character positions within a word. Each type of indirect data channel determines which of the three formats can be used. A 36-bit channel will access one 36-bit word per access, and a 72-bit channel may access either one or two 36-bit words per access, depending upon the address and tally requirements.

نـ

Rev. A

Page 15

## 2.5 DATA FORMATS (continued)

All direct channels are word channels; a word channel may be either direct or indirect.

A word channel transfers one or two 36-bit words at a time, although each 36-bit word may be effectively subdivided into characters by the channel.

| 0       | 5   | 6           | 11 12  | 17       | 18        | 23    | 24  | 29 | 30  | 35 |

|---------|-----|-------------|--------|----------|-----------|-------|-----|----|-----|----|

| Ť       | 000 | 001         | 01     | .0       | 011       |       | 100 |    | 101 |    |

| <u></u> |     |             | Six 6- | Bit Char | racters P | er Wo | ord |    |     |    |

| 0       |     | 8 9         |        | 17       | 18        |       | 26  | 27 |     | 35 |

| Ť       | 000 |             | 001    |          |           | 010   |     |    | 011 |    |

| L       |     |             | Four 9 | Bit Cha  | racters I | Per W | ord |    |     |    |

| 0       |     |             |        | 17       | 18        |       |     |    |     | 35 |

| Ť       |     | 000         |        |          |           |       | 00  | l  |     |    |

|         |     |             | Two 18 | -Bit Cha | racters   | Per W | ord |    |     |    |

| 0       |     |             |        |          |           |       |     |    |     | 35 |

| ۲       |     |             |        |          | 000       |       |     |    |     |    |

| L       |     |             | One    | 36-Bit   | Word Per  | Acce  | ss  |    |     |    |

| _       |     | •           |        | •        | 35 36     |       |     |    |     | 71 |

| ٥       |     |             |        |          |           |       |     |    |     |    |

| L       |     | <del></del> | Two 3  | 6-Bit Wo | ords Per  | Acces | s   |    |     |    |

Rev. A

Page 16

## 3.0 SOFTWARE AND CUSTOMER INTERFACE REQUIREMENTS

The following is a description of a typical operation of the IOM and an indirect data channel, such as a Common Peripheral Channel. Exceptions to this description arise at many places, but discussion of these is held for detailed description further into the EPS.

The software must prepare several control words, in addition to a buffer area for data to be transferred. Data Control Words indicating the locations of each data area must be placed in a DCW list. A List Pointer Word (LPW) indicating the location of the DCW list must then be placed in the core LPW mailbox for the channel to be used.

For the purpose of this discussion, assume that channel 020g, a payload channel, is to be issued an instruction to transfer data (Write) to the peripheral attached to its interface. A Status Control Word placed in the same channel's SCW mailbox area points to an area of core set aside to receive the status words resulting from the peripheral instructions to be issued. A Peripheral Control Word containing the necessary channel and peripheral instruction codes is placed in another area of core, with a second word containing the channel number (020) of the channel under discussion. The LFW mailbox for the connect channel is provided with a pointer to a list of such PCW's, allowing several payload channels to be initiated with a single connect instruction. As described later, the entire mailbox area is a contiguous block of words, four per channel, relocatable by means of switches on the IOM Configuration Panel.

Operation in the IOM begins with the receipt of the \$CON from a system controller, issued as a result of a connect instruction. The \$CON causes the connect channel to request the IOM to perform a List Service. The IOM uses the LFW from the Connect Channel mailbox to obtain the PCW referencing channel 020. The Connect Channel LFW is updated and replaced in core after each payload channel has been given its PCW. The channel, which is here assumed to be receptive, stores the PCW from the connect channel, and initiates communication with its attached peripheral.

Rev. A B

Page 17

## 3.0 SOFTWARE AND CUSTOMER INTERFACE REQUIREMENTS (continued)

When the channel has determined that its peripheral is receptive to the instruction, the channel will request the IOM to perform a first list service, using the LPW in channel 020 core mailbox to obtain a DCW. The DCW is checked for several conditions, including absolutizing the address when specified, and placed in either\* the core or scratchpad mailbox for channel 020. This particular DCW should be either an IOTP or an IOTD (I/O Transfer and Proceed or I/O Transfer and Disconnect). The LFW is updated and placed in both core and scratchpad mailboxes for channel 020. The channel now requests a data service of IOM, specifying an indirect data load. The IOM uses the DCW nel 020 to obtain the first word or word pair from the data area in core specified by the DCW. The address and tally fields are updated and checked, and the DCW returned to the mailbox in core\* or in scratchpad. The channel sends a release to the peripheral when its output buffers are full.

The peripheral will subsequently request the data to be sent over its interface data lines. By a succession of Data and List Service requests, the channel will continue to supply data until one of the following types of events occur: (1) An abnormal status condition such as a parity error; (2) The peripheral has reached a termination condition; (3) All DCW's in the list including the final IOTD are exhausted.

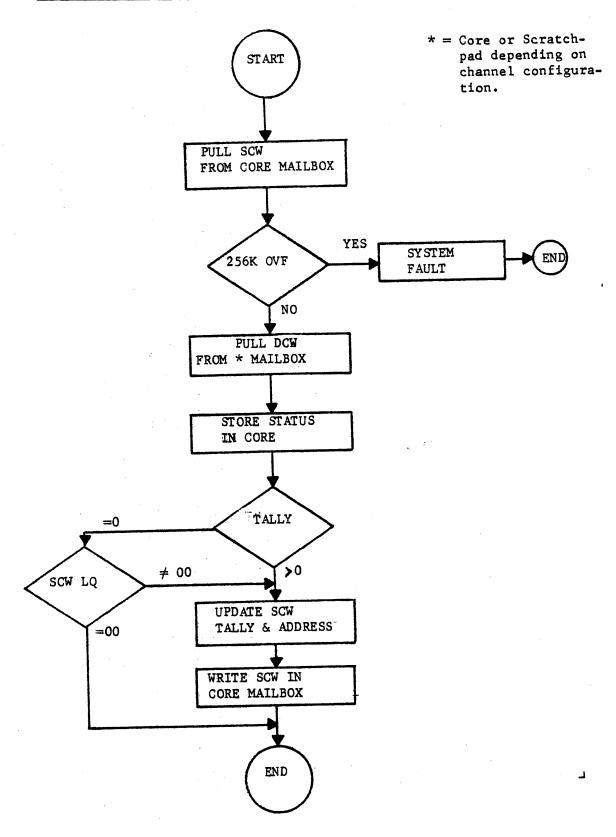

Anything which causes the end of operation with the peripheral, with the exception of a system fault, will cause the channel to request the IOM to do a status service. Using the Status Control Word for channel 020, the IOM will store status in the status queue indicated by the SCW, update the SCW and restore it to the core mailbox.

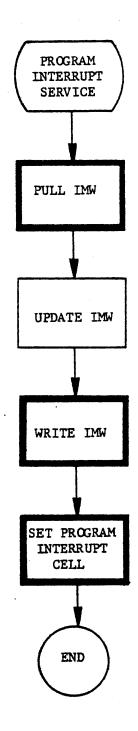

Following the status service, the channel will request the IOM to do a multiplex interrupt service. Using a combination of configuration switches and interrupt level indication in the service request, the IOM will retrieve one of 32 interrupt multiplex words, set a bit to indicate which channel is causing the interrupt and restore the word, then finally set the corresponding interrupt cell in the system controller. This will inform the software that the sequence of operations is concluded.

### 3.1 SOFTWARE INTERFACE

The IOM is responsible for moving information between core storage and various peripheral devices as controlled by demand from the peripheral control units associated with the peripheral devices. These operations do not occur continuously, but are initiated by connects, controlled by control words, and their completions are indicated by program interrupts.

\*To the scratchpad if the scratchpad (option) is in; otherwise to core.

В

Rev. B

Page 18

#### 3.1.1 Connects

\_

The software initiates a new activity in the IOM by executing a CIOC (Connect) instruction directed to a System Controller port that is attached to the IOM. When a processor executes such an instruction, the System Controller sends a \$CON signal to the IOM Central, which activates its connect channel. The connect channel initiates the operation of one or more channels as described in paragraph 3.7, Connect Channel.

### 3.1.2 Control Words

The IOM Central makes use of four 36-bit control words for each indirect channel:

- o List Pointer Word (LPW)

- o List Pointer Word Extension (LPW extension)

- o Status Control Word (SCW)

- o Data Control Word (DCW)

Refer to paragraph 3.2 for descriptions and locations of these control words.

## 3.1.3 Program Interrupts

The IOM must inform the processor of the completion of a previously initiated activity or of the occurrence of other special events such as special interrupts from a peripheral, marker interrupts\* from a channel, termination of an activity because of abnormal status, or fault conditions requiring attention of the software.

The IOM accomplishes this by setting a predetermined program interrupt cell in the system controller that contains the IOM base address. The system controller then causes a program interrupt in a processor so that appropriate action can be taken by the software. Each IOM has access to its own set of eight interrupt cells in the maximum set of 32 cells. The selection of the interrupt level, and the cell associated with the level, is determined by the channel. This is further described in paragraph 3.2.7.

L

<sup>\*</sup>The marker interrupt indicates the normal completion of a PCW or an IDCW in a DCW list. This interrupt is under control of the Marker and Continue bits in the PCW or IDCW.

Rev. A

Page 19

#### 3.2 CONTROL WORD FORMATS

The software is responsible for generating certain control words and for making these control words available to the IOM hardware by placing the control words in appropriate locations in core storage. The control words that the software is responsible for are:

- o List Pointer Words (LPW see paragraph 3.2.1)

- o Peripheral Control Words (PCW see paragraph 3.2.2)

- o Data Control Words (DCW see paragraph 3.2.3)

- o Status Control Words (SCW see paragraph 3.2.4)

The IOM hardware is responsible for generating certain words and for making these words available to the software by placing them in appropriate locations in core storage. These may also be regarded as control words, since the correct operation of the IOM can only occur when there is appropriate interaction between the IOM hardware and the software. The response words that the IOM Central Hardware is responsible for are:

- o Status Words (see paragraph 3.2.5)

- o Fault Words (see paragraph 3.2.6)

- o Interrupt Multiplex Words (IMW see paragraph 3.2.7)

## 3.2.1 List Pointer Words (LPW and LPW Extension)

The LFW is used to define the location and length of a list of

- o PCW's to be issued by the connect channel, or

- o DCW's to control the operation of a data channel.

The LPW, together with the LPW extension, also includes fields which control

- o the updating of the LPW

- o checking of DCW's for validity.

The software must generate an LPW and LPW extension for the specific data channel and place them in the appropriate locations in the core storage mailbox area before initiating the operation of that data channel by means of a PCW. The software must also generate an LPW for the connect channel and place it in the mailbox area before executing a CIOC instruction to initiate the operation of the connect channel.

Rev. B

Page 20

L

## 3.2.1 List Pointer Words (LPW and LPW Extension) (continued)

After the operation of a channel has been initiated, the IOM Central hardware must place into the LPW extension (in core and in scratchpad when available) the absolute address of each Instruction DCW which it encounters while servicing the list. (These are described in paragraph 3.2.3.)

The LPW and LPW extension have the formats shown below:

LPW

#### LPWX

| 0    | 8 9   | 17      | 35                     |

|------|-------|---------|------------------------|

| Lowe | er c. |         | ointer to first DCW of |

| Bour | nd S. | Lze Mos | t Recent Instruction   |

Rev. D

Page 21

## 3.2.1 List Pointer Words (LPW and LPW Extension) (continued)

The various fields are defined as follows:

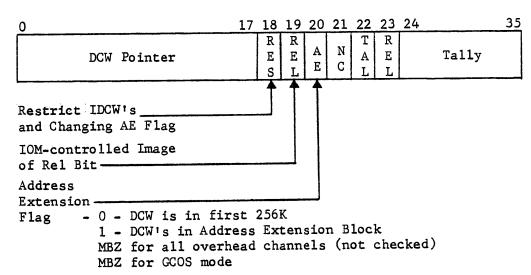

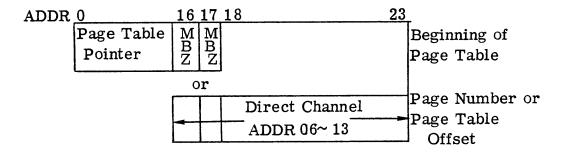

DCW (or PCW) Pointer (LPW 0-17) - Provides the least significant 18 bits of a 24 bit address of the DCW or PCW list. The most significant six address bits of the DCW depend on the state of LPW 20 (see below). Updating of this field is controlled by the NC (no change), TAL (Tally Control) and tally fields as shown in Table 3.2.1. When updating is called for, the IOM Central increments this field by one (two if the channel is the connect channel) during each list service.

Restricted Bit (LPW 18) - Provides the software with a way to restrict the use of Instruction DCW's by users without having to scan all DCW lists. If this bit is one and an Instruction DCW is encountered by the IOM Central, it will abort the I/O transaction and indicate a User Fault: Instruction DCW in Restricted Mode to the channel. If bit 18 is a zero, the list is unrestricted and Instruction DCW's will be allowed. (Bit 18 of the LPW for the connect channel must be set to zero by the software to preserve future compatibility and will be ignored by the IOM Central.) When the IOM Central encounters a Transfer DCW (TDCW) during a list service, it will at that time logically OR TDCW bit 34 into LPW bit 18 to provide the software with a way to switch immediately from unrestricted to restricted operation dynamically. Any subsequent encounter with an IDCW (Instruction DCW) will cause a user fault for that channel if the LPW bit 18 has been set to 1 by the TDCW. There will be no way to switch dynamically from restricted to unrestricted operation. Only replacing the LPW and issuing a CIOC for the restricted channel will restore the unrestricted operation. In addition, only unrestricted users may have TDCW 33 = 1 (i.e., change LPW 20). Note: An exception occurs during a Reverse List Service where LPW Bit 18 is unconditionally reset.

REL (LPW 19) - Reserved for storage of REL flag (bit 23) condition at the time an IDCW was fetched, or whenever a first-list service was performed.

AE (LPW 20) - Is defined as the Address Extension flag. This bit defines when a DCW list shall be located in the first 256K of core (LPW 20 = 0), or that it shall be in the 256K block specified via address extension (LPW 20 = 1). This bit may be changed from a zero to a one via a transfer type DCW, and will be reset to zero during a Reverse List Service if the system is an Extended GCOS system. In a Multics system this bit (if set) will follow the state of LPW bit 19. A system fault will be reported if LPW 20 = 1 in standard GCOS mode.

٦

Rev. B

Page 22

## 3.2.1 List Pointer Words (LFW and LFW Extension) (continued)

NC - No Change (LPW 21) - Provides the software with a way to control the updating of the LPW (both address and tally fields) as shown in Table 3.2.1. When set to a one, bit 21 inhibits the updating of the address and tally fields of the LPW. It forces a PTRO to be indicated for a Connect Channel service regardless of the state of LPW bit 22.

TAL - Tally Indication Control (LPW 22) - Provides the software with a way to control the recognition of PTRO (Pre-Tally Run-Out) condition by all channels as shown in Table 3.2.1. When set to a one, bit 22 allows the recognition of PTRO and TRO; when zero, these conditions are not indicated, and a tally of zero will not cause a fault indication. For the connect channel, the combination TAL and NC = 0 will cause a system fault. This bit is overridden by LPW bit 21, NC.

REL (LPW 23) - Provides the software with a way to control the interpretation of DCW addresses for indirect channels by the IOM as absolute or relative. Depending on whether this bit is zero or one, each DCW address is treated as absolute or relative, respectively. The IOM Central converts relative addresses to absolute and checks them for boundary errors (see description of lower bound and size fields of LPW). Bit 23 of the LPW for the connect channel will be ignored by the IOM Central. When the IOM Central encounters a TDCW during a list service it will logically OR TDCW bit 35 into LPW bit 23 to provide software with a way to switch immediately from absolute to relative operation dynamically. On a reverse list service bit 19 of the LPW will replace bit 23. There will be no way to switch from relative to absolute operation except by a new LFW and connect (CIOC). For direct channels which use list service to obtain a DCW, no conversion of addresses in the DCW is possible; the program must provide absolute addresses, and LPW bit 23 should be zero for future compatibility.

Tally (LPW 24-35) - Defines the number of PCW's or DCW's remaining in the list. Updating of this field by the IOM Central is controlled by the NC, TAL, and the value of the tally, as shown in Table 3.2.1. When updating is called for, the IOM Central decrements this field by one during each list service. Upon detecting a TRO condition for a channel as defined in Table 3.2.1, the IOM Central will indicate a User Fault: LPW TRO to the channel. (A System Fault: LPW TRO will be indicated if the list service is for the connect channel.) The tally is decremented when a transfer DCW is encountered and is decremented again when the next DCW is pulled after the transfer has occurred.

The payload channel never gets a PTRO indication. It must determine when to stop requesting list service on the basis of information in DCW or on the basis of some external influence.

В

Rev. A

Page 23

# UPDATING OF LFW ADDRESS AND TALLY AND INDICATION OF PTRO AND TRO

| / & |   |   | Triple British      |                  |                 |                            | <sup>ti</sup> ,/ |

|-----|---|---|---------------------|------------------|-----------------|----------------------------|------------------|

| a.  | 0 | 0 | any                 | yes              | no              | no                         |                  |

| b.  | 0 | 1 | 2-to 4095<br>1<br>0 | yes<br>yes<br>no | no<br>yes<br>no | no<br>no<br>yes<br>(fault) |                  |

| c.  | 1 | X | any                 | no               | yes<br>(forced) | no                         |                  |

Table 3.2.1

- \* before updating

- \*\* Note that this refers to connect channel list service.

- X Indicates a "don't care" condition.

The anticipated uses of these cases is as follows: Case a. is expected to be used by GCOS for Common Peripheral interface payload channels; a tally of zero is not a fault since the tally field will not be used by GCOS for that purpose. Case b. is the configuration expected of standard operation with real-time applications, and/or direct data channels. Case c. will be used normally only with the connect channel servicing common Peripheral-type payload channels. If case a. is used with the Connect channels, a "System Fault:Tally Control Error, Connect Channel" will be generated. Case c. will be used in the Bootload program.

Rev. A B

Page 24

١

## 3.2.1 List Pointer Words (LFW and LFW Extension) (continued)

Lower Bound (LFW Ext. 0-8 and Size (LFW Ext. 9-17) - Provide the software with a way of effectively setting up a base address register for each data channel. During a list service, if the REL bit (LFW 23) is one, the IOM Central checks the address and tally of the new DCW for possible boundary errors and, provided there is no boundary error, converts the relative address to an absolute address which is then placed in the DCW mailbox (or scratchpad). No checking or conversion is performed by the IOM Central if the REL bit is zero.

Pointer to First DCW of Most Recent Instruction (LPW Ext. 18-35) - Will be updated by the IOM Central during the first list service after a PCW, and during any list service which encounters an Instruction DCW. Each time that this field is updated, the IOM Central will copy the DCW pointer field of the LPW (or the transfer DCW, if one is encountered) into this field of the LPW extension in core, and in scratchpad when available. Thus, if the most recent instruction was a PCW, this field will point to the first data DCW; if the most recent instruction was an Instruction DCW, this field will point to the Instruction DCW. It is possible for the software to determine how many instructions were executed by the IOM before an abnormal termination, by examining this field of the LPW extension in the core mailbox after termination. This field will be used as the DCW Pointer (LPW 0-17) on a reverse list service.

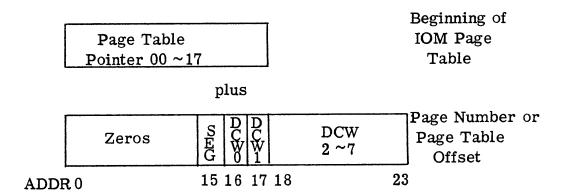

3.2.2 Peripheral Control Words (PCW)

The PCW is used by the Connect Channel to initiate the operation of a channel, or to mask (turn off) the operation of a channel that was previously initiated. The software can issue one or more PCW's with a single CIOC instruction by arranging the PCW's in a list and setting up an LPW for the Connect Channel to define the location and length of the list.

A non-PCW word (bits 18-20 not =111) encountered during a list service by the connect channel will cause a system fault. The PCW list should not contain more than one PCW for any one channel, unless the EPS-1 for that channel explicitly permits such operation.

Each PCW fills two words of core and must occupy a y-pair, that is, a pair of words obtained by a double-precision core access. A list of PCW's must occupy sequential y-pairs.

В

L

Rev. A

Page 25

## 3.2.2 Peripheral Control Words (PCW) (continued)

The PCW for all payload channels has the format shown below. The PCW for the snapshot channel is shown in paragraph 3.8; the PCW for the wraparound channel is in 3.9.1; and the PCW for the scratchpad access channel in 3.11.

The software must be aware of the channel type and peripheral subsystem characteristics before writing more than one PCW for the same channel in the PCW list. In order to issue more than one command to the common peripheral channel for instance, subsequent commands must appear in the DCW list as IDCW's.

| 0        |                | 11 | 12 | _17                   | 18  | - 2  | 20 | 21 | 22   |         |             | 35 |

|----------|----------------|----|----|-----------------------|-----|------|----|----|------|---------|-------------|----|

| <u> </u> | ANNEL INFORMAT |    |    | ADDRESS<br>EXTENS ION |     | 111  |    | M  |      | CHANNEL | INFORMATION |    |

|          |                |    |    | Even                  | Wor | rd   |    |    |      |         |             |    |

| 0 1      | 23 89          |    |    |                       |     |      |    |    |      |         |             | 35 |

| MB2      | CHANNEL        |    |    |                       |     | MUS' | r  | BE | ZERO | (MBZ)   |             |    |

|          | NUMBER         |    |    | Odd                   | Wo  | rd   |    |    |      |         |             |    |

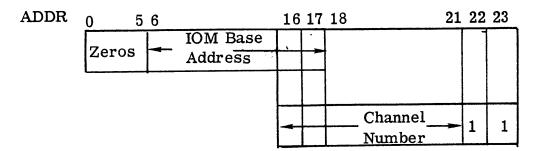

All 36 bits of the even word of the PCW are sent to the channel whose channel number is specified in the Odd Word of the PCW. Bits 18-20 of the Even Word must be  $111_2$  or  $7_8$  to identify the word as a PCW.

Bits 12-17 contain the address extension which is maintained by the channel for subsequent use by the IOM in generating a 24-bit address for list or data services for the extended address modes.

A channel will change from the normal condition to a masked condition as a result of a System Initialize, a system fault flag from the IOM Central, or as a result of a PCW with bit 21 = 1. This masked condition is a state in which a channel will not request service in spite of a need for such service that may be generated in the channel. A channel will change from the masked condition to normal as a result of a PCW with bit 21 = 0.

Rev. X B

Page 26

## 3.2.2 Peripheral Control Words (PCW) (continued)

The interpretation of channel information fields (even word of the PCW) by the channels will be specified separately for each type of channel in the EPS-1 for that channel. In general, a channel uses the information for such things as device instruction, device code, or address, mask, channel instruction, record count, single character, storage address (direct channels), and peripheral storage address. The even word of the PCW is sent to the channel specified without rearrangement.

The odd word is used only by IOM Central, and is not sent to the channel. A 9-bit field is reserved for channel number, but only 6 bits are implemented. The six-bit channel number is extracted from the odd PCW word and is output to the channels on lines separate from those used to output the even PCW word. Bits 0, 1 and 2 must be zero, for future compatibility; these and bits 9-35 are not used by the IOM.

### 3.2.3 Data Control Word (DCW)

The IOM Central recognizes five different types of DCW's. These are:

- Instruction DCW (IDCW)

Transfer DCW (TDCW)

I/O Transfer & Disconnect (IOTD)

- I/O Transfer & Proceed (IOTP)

- I/O Nontransfer & Proceed (IONTP)

The software or user program must generate appropriate DCW's for each data channel, and arrange the DCW's for each channel in a list. The list of DCW's for a channel must occupy sequential storage locations, except where one list is linked to another list by a TDCW. Boundary checks are made for DCW's (if REL bit = 1). Refer to paragraph 3.3 for a description of boundary checking.

В

Rev. D

Page 27

#### 3.2.3.1 Instruction DCW

The IDCW provides the software and unrestricted user programs with the ability to imbed instructions for peripheral devices at appropriate predetermined places in the DCW list.

The format of the IDCW is similar to the format of the PCW. There is no counterpart in the IDCW for the PCW Odd Word (which specifies the number of the channel that is to receive the PCW).

|   | 0           | 11 | 12 1      | .7 | 18  | 20 | 21 | 35             |

|---|-------------|----|-----------|----|-----|----|----|----------------|

|   | INTERPRETED | BY | ADDRESS   |    | 111 |    | E  | INTERPRETED BY |

| ı | CHANNEL     |    | EXTENSION |    | 111 |    | С  | CHANNEL        |

The only field in the IDCW that is interpreted by the IOM Central is bits 18-20, which must be coded 1112 or 78, to identify the DCW as an IDCW. When the IDCW is encountered during a list service, all 36 bits of the IDCW are sent to the data channel. If EC - Bit 21 = 1, the channel will replace the present address extension with the new address extension in bits 12-17. The address extension will be unaltered if EC - Bit 21 = 0. In Multics and NSA systems, EC - Bit 21 is inhibited from the payload channel if LPW bit 23 = 1. The interpretation of the remainder of the IDCW by the data channel will be specified separately for each type of channel in the EPS-1 for the channel. In general, a channel uses the information for such things as device instruction, channel instruction, record count, single character, core address (direct channels), and peripheral storage address.

Rev. B

Page 28

#### 3.2.3.2 Transfer DCW

The TDCW provides the software and the user with the ability to change control bits and to link one DCW list to another DCW list. The format of the TDCW is shown below. Bits 24-32 are not used by IOM Central.

| 0        |             | 17   | 18         | 20 2 | 21 | 23   | 24  |       | 3233   | 34          | <u>35</u>   |

|----------|-------------|------|------------|------|----|------|-----|-------|--------|-------------|-------------|

|          | DCW POINTER |      | Not<br>111 |      | 0  | 10   |     | MBZ   | E<br>C | R<br>E<br>S | R<br>E<br>L |

| <u> </u> |             | OR'd | with       | LPW  | 20 | into | LPW | 20 —  |        |             |             |

|          |             | ORid | with       | LPW  | 18 | into | LPW | 18 —— |        |             |             |

|          |             | OR¹d | with       | LPW  | 23 | into | LPW | 23    |        |             | _           |

DCW Pointer (0-17) - Specifies bits 6-23 of the address (absolute or relative, depending on the REL bit in the LPW) of the next DCW. The IOM Central absolutizes the address, if necessary, and places bits 6-23 of the absolute address in the DCW Pointer Field of the LPW, so that subsequent DCW's will be obtained from the new list. The most significant six bits (address extension) of the next DCW address are implied to be zero if LPW 20 = 0. If LPW 20 = 1, the address extension will be the present address extension held by the channel.

Bits 18-20 - Some code other than 111.

Bit 21 - Must be zero.

Bits 22-23 - Must coded  $10_2$  to identify the DCW as a TDCW.

Bits 24-32 - Must be zero.

Bit 33 - In All but STD GCOS Mode may be used to conditionally change LPW 20 from a zero to a one. That is, if TDCW 33 = 1 and if bit 18 of the present LPW is zero (unrestricted), LPW 20 will be set to a one. This will allow (system) software to control when the address extension bits from the PCW or IDCW will be used for accessing the users DCW list. Transfer DCW 33 = 1 and LPW 18 = 1 (restricted) is a user fault. In STD GCOS, if TDCW 33 = 1, LPW 20 will be set to a one and cause a system fault.

Rev. B

Page 29

3.2.3.2 Transfer DCW (continued)

<u>Bit 34</u> - Is logically ORed into LPW bit 18 by the IOM to provide the program with a way to switch from unrestricted to restricted operation.

<u>Bit 35</u> - Is logically ORed into LPW bit 23 by the IOM to provide the program with a way to switch from absolute to relative operation.

A status of "User Fault: Two Sequential TDCW's" will be indicated to the channel and the I/O transaction will be aborted if the DCW Pointer field of a TDCW points to another TDCW. (See paragraph 4.5.)

- 3.2.3.3 I/O Transfer and Disconnect (IOTD)

- I/O Transfer and Proceed (IOTP)

- I/O Non-Transfer and Proceed (IONTP)

Each of these three types of DCW's defines a block of data in core which may be transferred. The DCW format is shown below.

| 0            | 17 | 18 | 20 | 21     | 22  | 23 | 24 | 3.5   | <u> </u> |

|--------------|----|----|----|--------|-----|----|----|-------|----------|

| DATA ADDRESS |    | CI | ?  | N<br>U | TYI | PE |    | TALLY |          |

Data Address (0-17) - Specifies the least significant 18 bits of the starting address of the block of data, and is treated as either absolute or relative, depending on the REL bit in the LPW. The address extension, Bits 0-5, is obtained from the channel and appended to form a 24-bit address. If the LPW REL bit is a one, the address is absolutized and tested for boundary errors. The data address field of an IONTP type of DCW is not used to access core, but is updated normally by the IOM Central.

L

Rev. A

Page 30

3.2.3.3 I/O Transfer and Disconnect (IOTD)

I/O Transfer and Proceed (IOTP)

I/O Non-Transfer and Proceed (IONTP) (continued)

<u>CP-Character Position (18 - 20)</u> - Specifies the position of the first character within the first word of the block. The byte size, defined by the channel, determines what CP values are valid:

6 bit byte 000,001,010,011,100,101

9 bit byte 000,001,010,011

18 bit byte 000,001

36 bit byte any except 111

For word channels which assemble bytes into words, or disassemble words into bytes, the CP field is sent from IOM Central to the channel during list service, and is zeros when placed in the DCW mailbox for subsequent data services for that channel. Only full words are tallied for word channels.

For sub-word channels (limited to 9-bit byte channels), which depend on IOM Central for packing and unpacking words, the IOM Central will increment the CP field each indirect data access until a word is filled or emptied (indicated by being inremented to a value greater than is shown above for that byte size). When this occurs, the CP field is restored to zero, and the address field in the DCW is incremented, then the DCW is replaced in the mailbox.

A User Fault! Channel Character Size! will be indicated to the channel, if a character position value greater than those indicated above for that channel size is detected by IOM Central during list service.

A CP value of 78 indicates an IDCW, and is valid for all channel sizes during a list service. It will cause a system fault during a data service.

NOTE: A character position value of 110<sub>2</sub> will be passed to the channel if the channel indicates that it is a word channel, (e.g., the IOM Central does not detect this as a fault). It is the responsibility of the channel to indicate a fault and the EPS-1 for the specific channel should be referenced.

Rev. B

Page 31

3.2.3.3 I/O Transfer and Disconnect (IOTD)

I/O Transfer and Proceed (IOTP)

I/O Non-Transfer and Proceed (IONTP) (continued)

Mod 64 Bit (21) - Data DCW 21 was defined on the 655 IOM to be used, if a sub-word (character) channel were defined, to specify the manner of DCW tally update. That is, tally updating would be done once per word or once per character. For the 6000B IOM, tally will be on a word basis if a 9-bit character channel is ever defined. This bit is logically disabled from interrogation by the payload channels in the 6000B IOM.

Type (22-23) must be coded to identify the type of DCW.

- 00 IOTD I/O Transfer and Disconnect. The current device instruction is ended (terminated) when the channel detects the tally run-out condition of the tally.

- 01 IOTP I/O Transfer and Proceed. The current device instruction proceeds to a new DCW when the channel detects the tally run-out condition of the tally.

- See Section 3.2.3.2 on Transfer DCW (TDCW).

- 11 IONTP Same as IOTP except that no core accesses are made.

If data is being read from a peripheral device, the block of data is discarded. If data is being written to a peripheral device, the IOM Central generates a block of zeros.

Rev. A

Page 32

3.2.3.3 I/O Transfer and Disconnect (IOTD)

I/O Transfer and Proceed (IOTP)

I/O Non-Transfer and Proceed (IONTP) (continued)

Tally (24 - 35) - Defines the number of words in the data block. An initial tally of  $0000_8$  will be interpreted as  $10000_8$  or  $4096_{10}$  by the IOM Central. When a 72 bit transfer takes place, the IOM Central must decrement the Word Tally by  $\underline{2}$  each data service.

## 3.2.4 Status Control Word (SCW)

The SCW defines the location and length of a status queue in core storage. The status queue consists of a number of sequential y-pairs, into which the IOM will store status as status events occur. Since each channel has its own SCW, there is a separate status queue for each channel. The SCW has the format shown below.

| 0                | 7 18 19 | 20 23 | 24 35 |

|------------------|---------|-------|-------|

| Absolute Address | ъ       | MBZ   | Tally |

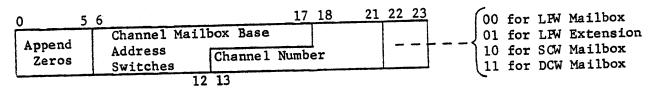

Status Queue Address (0 - 17) - Provides the least significant 18 bits of the next absolute address of the status queue to be used by the IOM, or the starting address, as determined by the software. The IOM will append 6 zeros as the most significant address bits for all operating modes. The IOM Central will store status in the y-pair defined by the status queue address field. Consequently the software should insure that the status queue address is even. The IOM Central will increment the status queue address by two each time that status is stored in the queue, except when the tally is zero (before updating), or for a circular queue (see below).

<u>List/Queue Control (18 - 19)</u> - Will be interpreted for all modes as follows:

- a) SCW (18 19) = 00 will result in the generation of a status list.

- b) SCW (18 19) = 01 will result in the generation of a 4 entry (8 word) circular queue.

- c) SCW (18 19) = 10 will result in the generation of a 16 entry (32 word) circular queue.

- d) SCW (18 19) = 11 is reserved for future expansion and should not be used.

Page 33

### 3.2.4 Status Control Word (SCW) (continued)

Circular queue addresses will be incremented after each entry until an entry is made in the queue tail. After the queue tail entry is made, the address will rotate back to the head of the queue.

The tally of the SCW will be decremented for each status entry in either list or queue mode, but the suppression of address changes will not occur when the tally has been decremented to zero if circular status is called for.

Bits 20 - 23 are not used, and must be set to zero by the software. These bits are not examined by IOM Central.

<u>Tally (24 - 35)</u> defines the number of unoccupied y-pairs (72-bits) in the status queue. The IOM Central will decrement the tally by one each time that status is stored in the queue, except when the tally is zero (before updating). As a result, if tally = N, the status queue actually consists of N + 1 y-pairs. The (N + 1)th y-pair corresponds to a tally of zero, and is therefore subject to being overlaid by subsequent status. SCW TRO is not a fault condition. In the circular queue mode the tally will continue to be decremented when it reaches zero.

#### 3.2.5 Channel and Device Status Words

When the IOM Central performs a status service for a channel, it will store two words into the y-pair defined by the SCW for the channel. These two words will have the following format.

| 0  |                                            |    |                       |     |    |       | 24                  | 29      | 30           | 35   |

|----|--------------------------------------------|----|-----------------------|-----|----|-------|---------------------|---------|--------------|------|

|    | CHANNEL AND DEVI                           | CE | STATUS                |     |    |       | ADDRESS<br>TENS ION |         | CH &<br>STAT | 1    |

|    |                                            |    | Even W                | ord |    |       |                     |         |              |      |

| 0. |                                            | 17 | 18                    | 20  | 21 | 22 23 | 24                  |         |              | 35   |

|    | NEXT ABSOLUTE ADDRESS<br>BITS 6-23 OF DATA |    | CHAR<br>POS I<br>TION | :-  | R  | AC    |                     | DCW TAI | LY RES       | IDUE |

| -  |                                            |    | Odd W                 | ord |    |       |                     |         |              |      |

Rev. A

Page 34

## 3.2.5 Channel and Device Status Words (continued)

#### **EVEN WORD:**

Channel and Device Status (0 - 35) will be generated by the channel and sent to the IOM Central during the status service. The IOM Central will obtain the address extension bits from the channel's Transaction Command (for status service), and will "OR" them into bits 24-29 of the status word supplied by the channel; therefore, the channel must insure that bits 24-29 of the even status word are zero. The IOM Central will store the channel and device status word in the even word of the y-pair defined by the Status Control Word.

The Common Peripheral Channel Status is shown for illustrative purposes only and reference should be made to the EPS-1 for the Common Peripheral Channel for explanation of the fields shown.

| 0 | 1 | 2 5                  | 6 11           | 12          | 13          | 14 15       | 16 | 17  | 18 20                  | 21 23                  | 24 29                               | 30 35              |

|---|---|----------------------|----------------|-------------|-------------|-------------|----|-----|------------------------|------------------------|-------------------------------------|--------------------|

| T | P | MAJOR<br>STA-<br>TUS | SUB-<br>STATUS | S<br>S<br>* | M<br>R<br>K | S<br>S<br>* | I  | A   | IOM<br>CHAN.<br>STATUS | IOM<br>CENT.<br>STATUS | ADDRESS<br>EXTEN-<br>S ION<br>(0-5) | RECORD<br>RES IDUE |

| _ | L | 1200                 |                |             | L           |             | E  | ven | Word                   | OR"ed int              | o Status W                          | ord by IOM         |

\*SS = Software Status

#### ODD WORD:

The IOM Central will obtain the DCW for the channel (from the core mailbox or from the scratchpad, as appropriate) and store this DCW residue in the odd word of the y-pair defined by the SCW. The information in the DCW residue (as a result of updating by the IOM Central during data services) must meet the following requirements so that it can be properly interpreted by software.

Rev.A

Page 35

## 3.2.5 Channel and Device Status Words (continued)

Next Absolute Address (0 - 17) contains bits 6 - 23 of the absolute address of the word which would have been read or written next had the transaction continued.

Character Postion (18 - 20) is the character number into which or from which the next character of data would have been transmitted if the transaction had continued. (Word channels will always fill out a word with zeros and store a whole word if the transaction stops while reading at a character count other than zero, but the last actual character position + 1 will be indicated in this field.) The IOM Central will obtain the character count residue from the channel during a status service, and logically OR it into the DCW residue word before storing it as status.

Read (21) will be a one if a peripheral read (core write) operation was to be performed. Otherwise it will be zero. The IOM Central will obtain the read bit from the channel during a status service, and place it into the DCW residue word before storing it as status.

Action Code (22 - 23) is the Action Code of the last DCW obtained for this channel.

Tally Residue (24 - 35) is the residue of the DCW tally, representing the number of words which were not accessed.

#### 3.2.6 System Fault Word

A system fault word is stored as data by the system fault channel at the location indicated in the fault channel DCW mailbox when a system fault is detected by the IOM Central. The system fault word has the following format:

| c | 8   | . 9            | 17 | 18 | 20           | 21     | 22     | 23 | 25  | 26          | 29 | 30 |              | 35 |

|---|-----|----------------|----|----|--------------|--------|--------|----|-----|-------------|----|----|--------------|----|

| ſ | MBZ | CHANNEL NUMBER |    | •  | VICE<br>UEST | M<br>0 | D<br>P | N  | 1BZ | COR<br>S TO | RE |    | I/O<br>FAULT |    |

| l |     |                |    |    |              | D.     |        |    |     | FAU<br>COD  |    |    | CODE         |    |

Channel Number (9 - 17) indicates the channel that was being serviced when the system fault was detected.

Rev. A

Page 36

## 3.2.6 System Fault Word (continued)

Service Request (18 - 20), MOD (21) and DP (22) indicate the type of operation that was being performed for the specified channel when the system fault occurred. The following table lists the interpretation of these bits.

|              |              |              |              |            | ·                                                                 |

|--------------|--------------|--------------|--------------|------------|-------------------------------------------------------------------|

| SR 0<br>(18) | SR 1<br>(19) | SR 2<br>(20) | MOD<br>(21)  | DP<br>(22) |                                                                   |

| 0            | 0            | 0            | · . <b>X</b> | X          | INV - Invalid                                                     |

| 0            | 0            | 1            | 1            | 0          | LST - List Service, "FIRST"                                       |

| 0            | 0            | 1            | 0            | X.         | LST - List Service, "SECOND"                                      |

| 0            | 0            | 1            | 1            | 1          | LST - List Service, "BACK-UP"                                     |

| 0            | 1            | 0            | х            | X          | STA - Status Service                                              |

| 0            | 1            | 1            | х            | Х          | PI - Program Interrupt Service                                    |

| 1            | 0            | 0            | 0            | 0          | <pre>ILD - Indirect Data Load Service,     Single Precision</pre> |

| 1            | 0            | 0            | 0            | 1          | ILD - Indirect Data Load Service, Double Precision                |

| 1            | 0            | 1            | 0            | 0          | IST - Indirect Data Store Service,<br>Single Precision            |

| 1.           | 0            | . 1          | 0            | 1          | IST - Indirect Data Store Service, Double Precision               |

| 1            | 1            | 0            | 0            | 0          | DLD - Direct Data Load Service,<br>Single Precision               |

| . 1          | 1            | 0            | 0            | 1          | DLD - Direct Data Load Service,<br>Double Precision               |

| 1            | 1            | 0            | 1            | 0          | DRC - Direct Read Clear Service                                   |

| 1            | 1            | .1           | 0            | 0          | DST - Direct Data Store Service,<br>Single Precision              |

| 1.           | 1            | 1            | 0            | 1          | DST - Direct Data Store Service, Double Precision                 |

|              |              |              |              |            |                                                                   |

Table 3.2.6

Store Fault Code (26 - 29) indicates the particular type of store fault. (Codes defined in paragraph 4.5.)

I/O Fault Code (30 - 35) indicates the particular type of I/O fault. (Codes defined in paragraph 4.5.)

Page 37

### 3.2.7 Interrupt Multiplex Word (IMW)

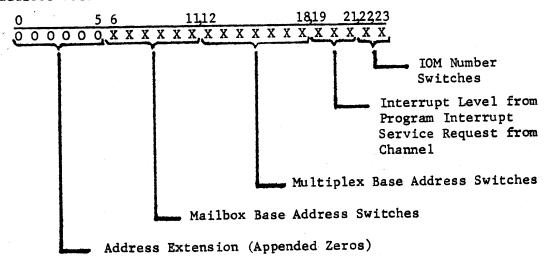

The IOM has the ability to set any of the 32 program interrupt cells located in the system controller containing the base address of the IOM. It should be noted however that for any given IOM identity switch setting, the IOM can set only 8 of these program interrupt cells. The use of this interrupt provision is restricted by system assignment of program interrupt cells. The IOM uses the 32 interrupt cells in conjunction with the 32 core locations in the IOM mailbox area to establish a channel's identity. There is a one-to-one correspondence in address between the program interrupt cells and the IMW words.

The IOM Central pulls the IMW from the core location having the address determined as follows:

One IMW is provided for each program interrupt cell which can be set by the IOM Central. The particular one of the 32 words in the IMW area, and the interrupt cell in the System Controller, are determined by two factors:

- a) The IOM number, as set by the IOM number switches on the maintenance panel, will determine the two least significant bits of the IMW address. This provides one word for each of four possible IOM's at each of eight interrupt levels. The switches are further described in paragraph 3.5.2.

- b) The interrupt level as determined by the logic in each channel. The channel will wire, patch, or logically manipulate bit positions 13-15 of the data presented with a program interrupt service request, providing as many as eight possible interrupt levels for each channel from the total of 32 levels. Note that this interrupt level becomes bits 19-21 of the IMW address once the IOM has appended an address extension of zeros.

Rev. A

Page 38

### 3.2.7 Interrupt Multiplex Word (IMW) (continued)

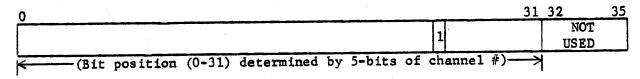

Thirty-two of the 36 bit positions are used in each of the 32 IMW words to indicate which channel caused the program interrupt. The appropriate IMW is pulled with a Read-Clear access cycle, a "one" is ORed into the IMW in the bit position specified by the channel, and then the IMW is returned to core with a Clear-Write cycle.

The IOM Central then sets the program interrupt cell that was specified by the channel.

The bit position within the IMW which is to be set to a <u>one</u> is determined by the binary value of the five least significant bits in the channel number field of the program interrupt service request presented by the channel. In the event that more than 32 channels are used on a single IOM, the higher numbered channels will be required to use a different program interrupt level.

Any special purpose channels designed in the future with a requirement to set bits in some IMW which do not correspond to its own channel number, may still logically manipulate bits 22 - 26 on one or more Program Interrupt requests, to set any of 32 bits in any of 8 words in the IMW area.

Upon interruption, the supervisory program may examine the core location corresponding to the interrupt cell causing the interrupt to determine which of the channels caused the interrupt. The floating normalize instruction may be used effectively for this purpose.

Any program interrupt cell may still be used as a discrete interrupt by some special purpose channel in which case the program would not need to consult the table. Figure 3.2.7 depicts the relationship between the interrupt cell number, IOM channels and the multiplex queue.

#### INTERRUPT MULTIPLEX WORD

Rev. A

Page 39

### 3.2.7 Interrupt Multiplex Word (IMW) (continued)

Note:

It is important that the system programmer realize that the Interrupt Multiplex Word (IMW) update by the IOM requires 2 cycles, a Read - CLear (RCL) followed by a Clear - WRite (CWR). That is, the process of determining which channel caused an interrupt is similar to the gating function. The software must interrogate the IMW with an instruction that causes the RCL cycle and transfers the information to the processor (e.g. LDAC, LDQC). There is no other instruction that can provide this capability without the possibility of losing information. This hardware technique implies that the software may find an IMW of "zero" when responding to an interrupt. (i.e. the IOM has performed the RCL and has yet to perform the CWR.) If the software does find an IMW (at the appropriate level) of "zero" it must read it again (via the RCL). This process of repeated fetching should not be an arbitrary loop but rather a procedure that would detect a failure should the IOM not perform the CWR cycle.

When the software fetches the IMW, it may have an indication of more than one channel interrupt. It is interesting to note that after the software processes these interrupts (if any) an interrupt present signal may still be present. That means that when the waiting interrupt is processed, the interrupt handler may find a legitimate "zero" value IMW. This situation should not be interpreted as an IOM error but rather the interrupt should be effectively ignored by the software.

Rev. A

Page 40

## MAP OF IMW AREA

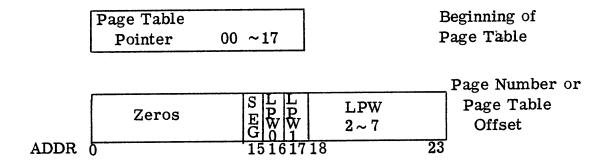

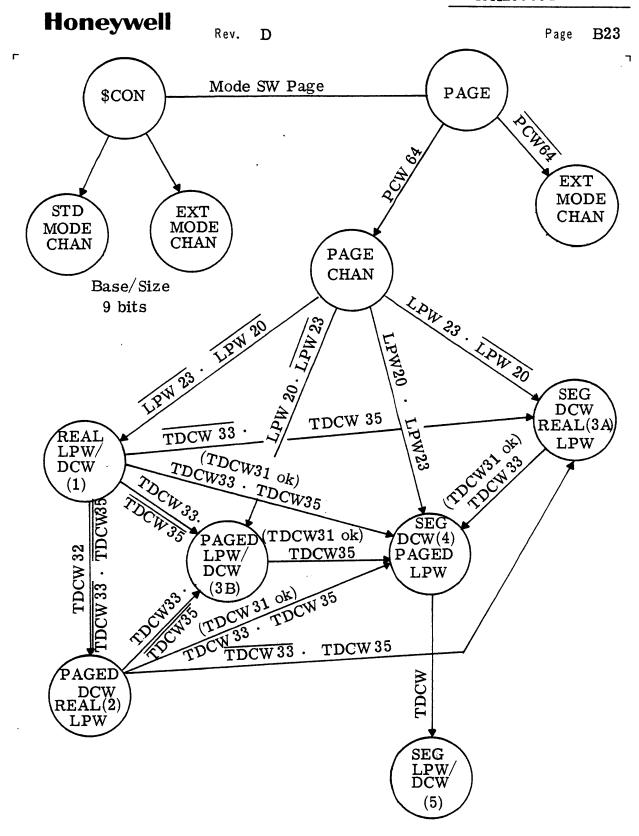

| DEC. | OCT. | NO. | LEVEL |                                                       |