| Honeywell                                                       |                                                  | SPEC. NO.       |       | SHEET | REV |

|-----------------------------------------------------------------|--------------------------------------------------|-----------------|-------|-------|-----|

| HONEYWELL INFORMATION SYSTEMS                                   |                                                  | 60132445        |       | 1/71  | F   |

| LOC.<br>Billerica, MA<br>U.S.A                                  |                                                  | PROJECTION      | CODE  | В3    |     |

| PREPARED BY DATE A. Hirtle  APPROVED BY DATE See Approval Sheet | TITLE ENGINEERING PRODUCT S LEVEL 66 FEP COUPLER | PECIFICATION, P | ART I |       |     |

## REVISION RECORD

| REV.       | AUTHORITY | DATE     | SIGNATURE | SHEETS AFFECTED                               |

|------------|-----------|----------|-----------|-----------------------------------------------|

| A          | BLCD68461 | 12-02-76 |           | 1, 1.1, 2 through 50                          |

| В          | BLCD77129 | 02-04-77 |           | 1, 1.1, 2 through 77                          |

| C          | BLCD77457 | 05-06-77 | i. dit-   | 1, 1.1, 2, 2.1, 2.2, 2.3, 2.4, 3 through 87F  |

| . <b>D</b> | BLCD77707 | 07-22-77 | aux       | 1, 1.1, 2, 2.1, 2.3, 2.4, 3 through 87F       |

| E          | BLCD77969 | 10-04-77 | acs       | 1, 1.1, 2, 2.1, 2.2, 2.<br>2.4, 3 through 87F |

| F          | BLCD78166 | 11-23-77 | ach       | 1, 1.1, 2, 2.1, 2.2, 2.3, 2.4, 3 through 71F  |

# NOTE

This EPS-1, if not revised within one year, should be considered obsolete and therefore reference should be made to the appropriate Product Manual.

# HONEYWELL PROPRIETARY

The information contained in this document is proprietary to Boneywell Information Systems lie, and is intended for internal Honeywell use only. Such information may be distributed to oth is only by written permission of an authorized Honeywell official. This restriction does not apply to vendor proprietary parts that may be disclosed in this document.

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60132445  | 1.1   | F    |

# HONEYWELL INFORMATION SYSTEMS SYSTEMS ENGINEERING - BOSTON

ENGINEERING PRODUCT SPECIFICATION (EPS - 1) SUBSYSTEM LEVEL

TITLE: LEVEL 66 FEP COUPLER

VERSION: APPROVAL DATE: 11/23/77

PRODUCT CALENDAR REFERENCE: \_\_\_\_\_\_

5A0503

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60132445  | 2     | F    |

# CONTENTS

| Section |              |                                |                                         |                                     | Page             |

|---------|--------------|--------------------------------|-----------------------------------------|-------------------------------------|------------------|

| I       | INTROD       | Scope<br>Applicab              | le Document                             | s                                   | 3<br>3<br>3      |

|         | 1.3          | Definition                     | ons                                     |                                     | 4                |

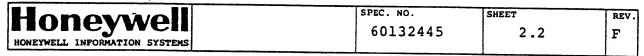

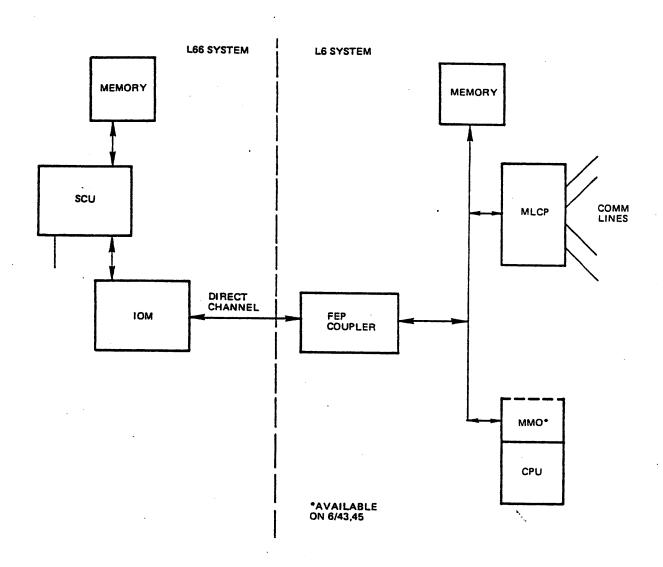

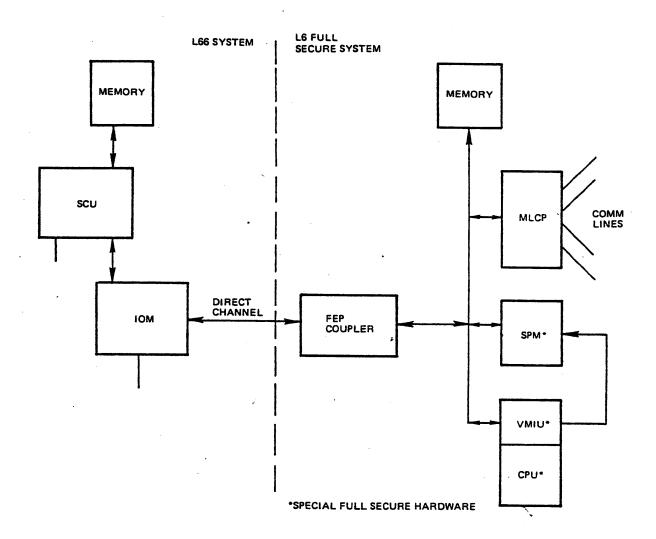

|         | ARCHIT       | General (Operation 2.2.1 2.2.2 | ns Overview<br>Control In<br>Typical Op | tercommunication<br>eration         | 5<br>5<br>6<br>6 |

|         |              | 2.2.3                          | Data Trans                              | fer Architecture and                |                  |

|         |              | 2 2 4                          | Intercommu                              |                                     | 10               |

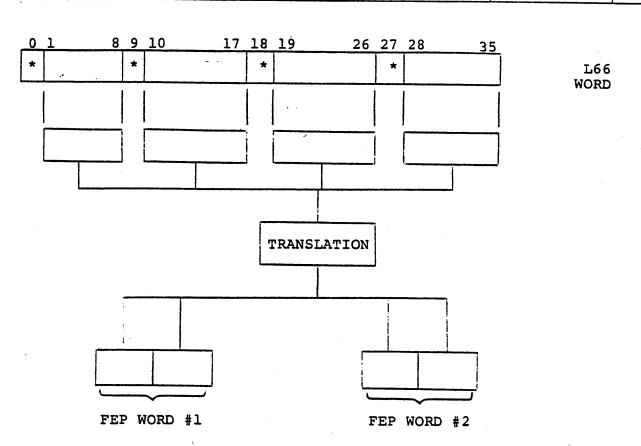

|         |              | 2.2.4                          | Mailbox an                              | d DCW Formats                       | 11               |

| III     | FUNCTION 3.1 | ONAL DESCI                     | RIPTION                                 |                                     | 15<br>15         |

|         | 3.2          |                                | es and Conf                             | igurations                          | 15               |

|         | 3.3          | Data Tra                       | nsfer Modes                             | J                                   | 16               |

|         |              | 3.3.1                          |                                         | ormats                              | 16               |

|         |              | 3.3.2                          |                                         | ation Modes                         | 16               |

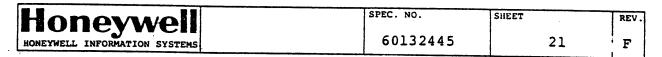

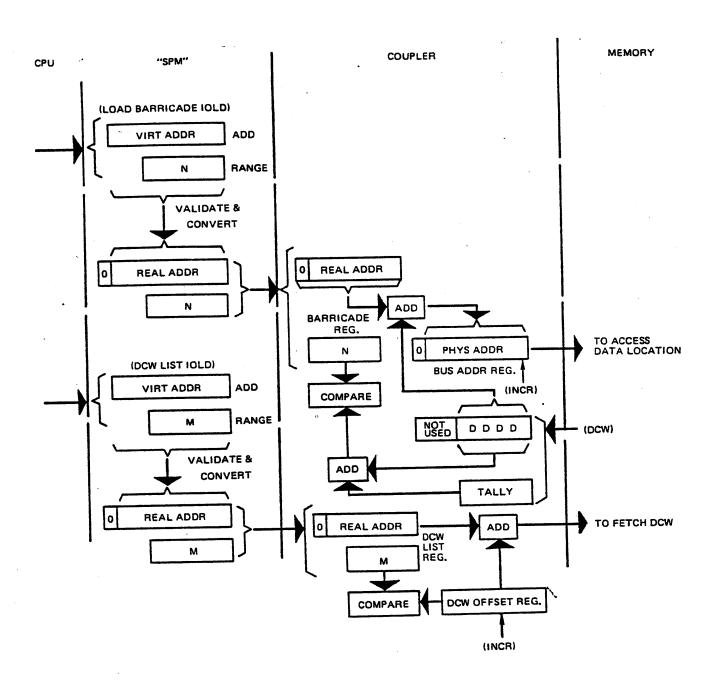

| •       | 3.4          | Hardware                       | Organizati                              | on                                  | 20               |

|         |              | 3.4.1<br>3.4.2                 | Address, Co                             | ters (L66 and L6) Ontrol and Status | 20               |

|         |              |                                | Registers                               |                                     | 20               |

|         | •            |                                | 3.4.2.1                                 | L66 Bus Address Register            | 20               |

|         |              |                                | 3.4.2.2                                 | L6 Bus Address Register             | 20               |

|         |              |                                | 3.4.2.3                                 | L6 DCW List Register                | 20               |

|         |              |                                | 3.4.2.4                                 | Barricade Registers                 | 20               |

|         |              |                                | 3.4.2.5<br>3.4.2.6                      | DCW Offset Register                 | 20               |

|         |              |                                | 3.4.2.0                                 | Checking Logic and Status           |                  |

|         |              |                                | 3.4.2.7                                 | Registers                           | 20               |

|         |              |                                | 3.4.2.8                                 | Task Register Tally Register        | 21               |

|         |              | 3.4.3                          |                                         | ion Registers and Switches          | 21<br>21         |

|         |              |                                | 3.4.3.1                                 | L66 Mailbox Address                 | 21               |

|         |              |                                | 3.4.3.2                                 | Coupler Channel Number              | ~ ~              |

|         |              |                                |                                         | Switches                            | 22               |

| Honeywell                     | SPEC. NO. | SHEET | REV. |

|-------------------------------|-----------|-------|------|

| HONEYWELL INFORMATION SYSTEMS | 60132445  | 2.1   | F    |

# CONTENTS

| Section   Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _       |     |       |             |                          |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------|-------------|--------------------------|------|

| 3.4.3.4 Configuration Register A 22 3.4.5 Rate Throttle 23 3.5.1 Commands Issued by Central System 23 3.5.2 Commands Issued by L6 FEP 25 3.5.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWS 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 30 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 L66 S1 3.6.1.5 Test Data Transfer From L6 to L66 S2 3.6.2.1 Interrupt L66 31 3.6.2.2 Task Register 32 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect & Interrupt 34 3.6.4.2 Disconnect & Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L6 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Section |     |       |             | <b>I</b>                 | Page |

| 3.4.4 Transaction Timer  3.4.5 Rate Throttle  3.5.2 Rate Throttle  3.5.1 Commands Issued by Central System  3.5.2 Commands Issued by L6 FEP  3.5.3 Status Pending State  29  3.6 Command Functionality  30  3.6.1 L66 PCWs  30  3.6.1.2 Bootload L6  30.6.1.2 Bootload L6  31  3.6.1.3 Interrupt L66  31  3.6.1.4 Test Data Transfer From  L66 to L66  31  3.6.1.5 Test Data Transfer From  L66 to L6  31  3.6.2.1 Interrupt Control  31  3.6.2.2 Task Register  32  3.6.2.3 Interrupt L66  32  3.6.2.4 Read DCW Offset Register  32  3.6.2.5 Configuration Register A 32  3.6.2.6 Read Status Register 1/2  3.6.2.7 Read Device ID  33  3.6.2.8 Output Control  33  3.6.3.1 DCW List  3.6.3.2 Load Barricade Register  33  3.6.3.1 DCW List  3.6.3.3 Input Stored Boot  33  3.6.4.1 Disconnect  34  3.6.4.2 Disconnect  35  3.6.4.2 Disconnect  36  3.6.4.3 Store Configuration Status  36  3.6.4.4 Data Transfer from L6  to L66  3.6.4.5 Data Transfer from L6  to L66  3.6.4.6 Read and Clear L66; OR to  Store L6  3.6.4.7 Interrupt L6  3.6.4.8 Jump  3.6.4.9 No Operation  36  3.6.4.10 Stall  36  3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |     |       | 3.4.3.3     | L6 Interrupt Control     | 22   |

| 3.4.5 Rate Throttle 23 3.5 Operations 3.5.1 Commands Issued by Central System 23 3.5.2 Commands Issued by L6 FEP 25 3.5.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWs 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 30 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 L6 to L6 to L6 31 3.6.2.1 Interrupt Control 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3 L6 IOLD Orders 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 134 3.6.4.2 Disconnect 134 3.6.4.2 Disconnect 134 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L6 to L66 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |     |       |             |                          |      |

| 3.5 Operations 3.5.1 Commands Issued by Central System 23 3.5.2 Commands Issued by L6 FEP 25 3.5.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWs 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 30 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L66 to L6 3.6.1.5 Test Data Transfer From L66 to L6 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 31 3.6.4.2 Disconnect 31 3.6.4.2 Disconnect 31 3.6.4.3 Store Configuration Status 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 5.6.4.5 Data Transfer from L66 to L66 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.5 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |     |       |             |                          |      |

| 3.5.1 Commands Issued by Central System 23 3.5.2 Commands Issued by L6 FEP 25 3.5.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWs 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 30 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L66 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2.1 Interrupt Control 31 3.6.2.1 Interrupt L66 32 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect Interrupt 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 53 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |     |       |             | :le                      |      |

| 3.5.2 Commands Issued by L6 FEP 25 3.5.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWs 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 31 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3 L6 IOLD Orders 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 11 Interrupt 34 3.6.4.2 Disconnect 1 Interrupt 34 3.6.4.1 Disconnect 2 Interrupt 34 3.6.4.2 Disconnect 1 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L66 to L66 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.5 Store L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 3.5 |       |             |                          | 23   |

| 3.6.3 Status Pending State 29 3.6 Command Functionality 30 3.6.1 L66 PCWs 30 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 30 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 3.6.1.1 Interrupt Control 31 3.6.2 L6 IO Orders 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.7 Read Device ID 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.1 DCW Commands 34 3.6.4.1 Disconnect 33 3.6.4.2 Disconnect 1 Interrupt 34 3.6.4.2 Disconnect 2 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 35 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |     |       |             |                          |      |

| 3.6   Command Functionality   30   3.6.1   L66 PCWs   30   3.6.1.2   Bootload L6   30   3.6.1.2   Bootload L6   31   3.6.1.3   Interrupt L66   31   3.6.1.4   Test Data Transfer From L6 to L66   31   3.6.1.5   Test Data Transfer From L66 to L6   31   3.6.2.1   Interrupt Control   31   3.6.2.2   Task Register   32   3.6.2.2   Task Register   32   3.6.2.3   Interrupt L66   32   3.6.2.4   Read DCW Offset Register   32   3.6.2.5   Configuration Register   32   3.6.2.6   Read Status Register   1/2   32   3.6.2.6   Read Status Register   1/2   32   3.6.2.8   Output Control   33   3.6.2.8   Output Control   33   3.6.3.1   DCW List   33   3.6.3.2   Load Barricade Register   33   3.6.3.2   Load Barricade Register   34   3.6.4.1   Disconnect   Interrupt   34   3.6.4.2   Disconnect   Interrupt   34   3.6.4.2   Disconnect   Interrupt   34   3.6.4.2   Disconnect   Interrupt   34   3.6.4.3   Store Configuration Status   34   3.6.4.4   Data Transfer from L66   to L66   35   36   36   36   36   36   36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |     |       |             |                          |      |

| 3.6.1 L66 PCWs  3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 31 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L66 to L66 34 3.6.4.5 Data Transfer from L66 to L6 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 2 6 |       |             |                          |      |

| 3.6.1.1 Interrupt L6 30 3.6.1.2 Bootload L6 31 3.6.1.3 Interrupt L66 31 3.6.1.4 Test Data Transfer From L6 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 8 Interrupt 34 3.6.4.2 Disconnect 8 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.1 Disconnect 8 Interrupt 34 3.6.4.2 Disconnect 8 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 3.6 |       |             | ÷ y                      |      |

| 3.6.1.2 Bootload L6 3.6.1.3 Interrupt L66 3.6.1.4 Test Data Transfer From L6 to L66 3.6.1.5 Test Data Transfer From L66 to L6 3.6.2.1 Interrupt Control 3.6.2.2 Task Register 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 3.6.2.8 Output Control 3.6.3.1 DCW List 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 3.6.4.1 Disconnect 3.6.4.2 Disconnect Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L66 to L6 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 3.6.4.9 No Operation 3.6 3.6 3.6 3.6 3.6 3.6 3.6 3.6 3.6 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |     | 3.0.1 |             | Intormint I6             |      |

| 3.6.1.3 Interrupt L66 3.6.1.4 Test Data Transfer From L6 to L66 3.6.1.5 Test Data Transfer From L66 to L6 3.6.2.1 Interrupt Control 3.6.2.2 Task Register 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 3.6.2.7 Read Device ID 3.6.2.8 Output Control 3.6.3.1 DCW List 3.6.3.1 DCW List 3.6.3.2 Load Barricade Register 3.6.3.3 Input Stored Boot 3.6.4.1 Disconnect 3.6.4.1 Disconnect Interrupt 3.6.4.2 Disconnect Interrupt 3.6.4.3 Store Configuration Status 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L6 to L66 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 3.6.4.9 No Operation 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |     |       |             |                          |      |

| 3.6.1.4 Test Data Transfer From L6 to L66 31 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2 L6 IO Orders 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 8 Interrupt 34 3.6.4.2 Disconnect 8 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L66 to L66 34 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |       |             |                          |      |

| L6 to L66   31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |     |       |             |                          | 21   |

| 3.6.1.5 Test Data Transfer From L66 to L6 31 3.6.2 L6 IO Orders 31 3.6.2.1 Interrupt Control 31 3.6.2.2 Task Register 32 3.6.2.3 Interrupt L66 32 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.1 Disconnect 4 Interrupt 34 3.6.4.2 Disconnect 5 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |     |       | 3.0.1.4     |                          | 31   |

| L66 to L6 31  3.6.2 L6 IO Orders 31  3.6.2.1 Interrupt Control 31  3.6.2.2 Task Register 32  3.6.2.3 Interrupt L66 32  3.6.2.4 Read DCW Offset Register 32  3.6.2.5 Configuration Register A 32  3.6.2.6 Read Status Register 1/2 32  3.6.2.7 Read Device ID 33  3.6.2.8 Output Control 33  3.6.3.1 DCW List 33  3.6.3.1 DCW List 33  3.6.3.2 Load Barricade Register 33  3.6.3.3 Input Stored Boot 33  3.6.4.1 Disconnect 34  3.6.4.2 Disconnect Interrupt 34  3.6.4.2 Disconnect Interrupt 34  3.6.4.3 Store Configuration Status 34  3.6.4.4 Data Transfer from L6  to L66  3.6.4.5 Data Transfer from L66  to L6  3.6.4.6 Read and Clear L66; OR to  Store L6  3.6.4.7 Interrupt L6  3.6.4.8 Jump 35  3.6.4.9 No Operation 36  3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |       | 3.6.1.5     | ·                        | J_   |

| 3.6.2 L6 IO Orders 3.6.2.1 Interrupt Control 3.6.2.2 Task Register 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect 34 3.6.4.2 Disconnect 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |     |       |             | •                        | 31   |

| 3.6.2.1 Interrupt Control 3.6.2.2 Task Register 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 3.6.2.8 Output Control 3.6.3.1 DCW List 3.6.3.2 Load Barricade Register 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 3.6.4.1 Disconnect 3.6.4.2 Disconnect 3.6.4.2 Disconnect Interrupt 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L66 to L6 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 3.6.4.9 No Operation 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     | 3.6.2 | L6 IO Order |                          |      |

| 3.6.2.2 Task Register 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.1 Disconnect 11 3.6.4.2 Disconnect 11 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L66 to L66 35 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |     |       | 3.6.2.1     | Interrupt Control        |      |

| 3.6.2.3 Interrupt L66 3.6.2.4 Read DCW Offset Register 32 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 DCW List 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L66 35 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •       |     |       |             |                          |      |

| 3.6.2.5 Configuration Register A 32 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3 L6 IOLD Orders 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6  5.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |     |       | 3.6.2.3     |                          | 32   |

| 3.6.2.6 Read Status Register 1/2 32 3.6.2.7 Read Device ID 33 3.6.2.8 Output Control 33 3.6.3.1 L6 IOLD Orders 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.1 Disconnect 14 3.6.4.2 Disconnect 15 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 50 51 51 51 51 51 51 51 51 51 51 51 51 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |       |             | Read DCW Offset Register |      |

| 3.6.2.7 Read Device ID 3.6.2.8 Output Control 3.6.2.8 Output Control 3.7 Seed Device ID 3.6.2.8 Output Control 3.7 Seed Device ID 3.8 Seed Beer ID 3. Seed Beer ID 3.8 Seed Beer ID 3. Seed Beer ID 3. See |         |     |       |             |                          |      |

| 3.6.2.8 Output Control 33 3.6.3 L6 IOLD Orders 33 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4.1 Disconnect 34 3.6.4.1 Disconnect Interrupt 34 3.6.4.2 Disconnect Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |     |       |             | Read Status Register 1/2 |      |

| 3.6.3 L6 IOLD Orders 3.6.3.1 DCW List 3.6.3.2 Load Barricade Register 3.6.3.3 Input Stored Boot 3.6.4.1 Disconnect 3.6.4.2 Disconnect Interrupt 3.6.4.3 Store Configuration Status 3.6.4.4 Data Transfer from L6 to L66 3.6.4.5 Data Transfer from L66 to L6 3.6.4.6 Read and Clear L66; OR to Store L6 3.6.4.7 Interrupt L6 3.6.4.8 Jump 3.6.4.9 No Operation 3.6.4.10 Stall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |     |       |             |                          |      |

| 3.6.3.1 DCW List 33 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 14 3.6.4.2 Disconnect 15 Interrupt 16 3.6.4.3 Store Configuration Status 17 3.6.4.4 Data Transfer from L6 to L66 35 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |     |       |             |                          |      |

| 3.6.3.2 Load Barricade Register 33 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect 1 Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |     | 3.6.3 |             |                          |      |

| 3.6.3.3 Input Stored Boot 33 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |     |       |             |                          |      |

| 3.6.4 DCW Commands 34 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect \(\ell\) Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •       |     |       |             |                          |      |

| 3.6.4.1 Disconnect 34 3.6.4.2 Disconnect & Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ~       |     | 2 6 1 |             | <del>-</del>             |      |

| 3.6.4.2 Disconnect & Interrupt 34 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |     | 3.0.4 |             |                          |      |

| 3.6.4.3 Store Configuration Status 34 3.6.4.4 Data Transfer from L6 to L66 34 3.6.4.5 Data Transfer from L66 to L6 35 3.6.4.6 Read and Clear L66; OR to Store L6 35 3.6.4.7 Interrupt L6 35 3.6.4.8 Jump 35 3.6.4.9 No Operation 36 3.6.4.10 Stall 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |     |       |             |                          |      |