#### SECTION II

#### MEMORY SYSTEMS

#### PREFACE

This section presents the Theory of Operation, Assembly Drawing, Parts list, and Schematic for each of the Hewlett-Packard memory products. The memory products are divided into two types of memory systems: Standard Performance Memory Systems and High Performance Memory Systems. Each of the systems is available either with or without fault control memory controllers. Table 1 and Table 2 list the components associated with each of the memory systems. An Installation and Service Manual for each of the memory systems is available and should be used in conjunction with the material provided in this Engineering and Reference Document. The titles and part numbers of the manuals are:

Standard Performance Memory Systems Installation And Service Manual, part no. 5955-4310.

High Performance Memory Systems Installation And Service Manual, part no. 5955-4311.

Table 1. Standard Performance Memory System Products

|                  |                                                                               | +           |

|------------------|-------------------------------------------------------------------------------|-------------|

| PRODUCT NO.      | DESCRIPTION                                                                   | PART NO.    |

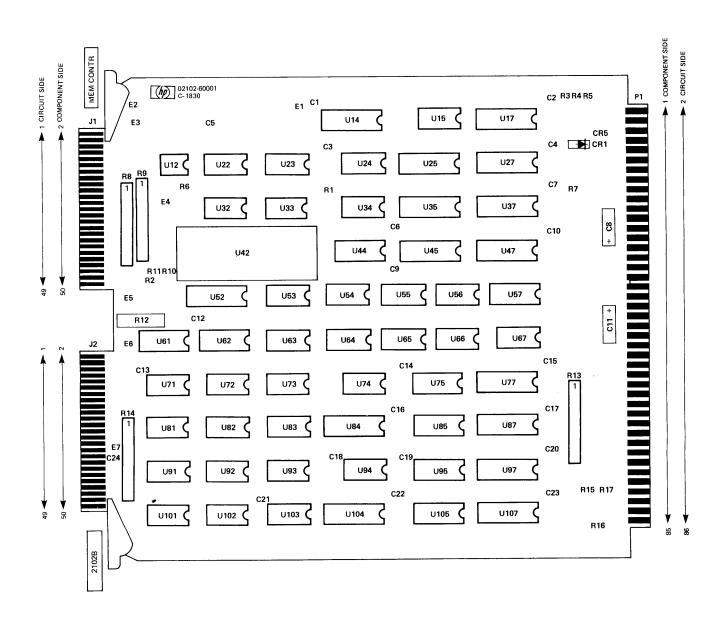

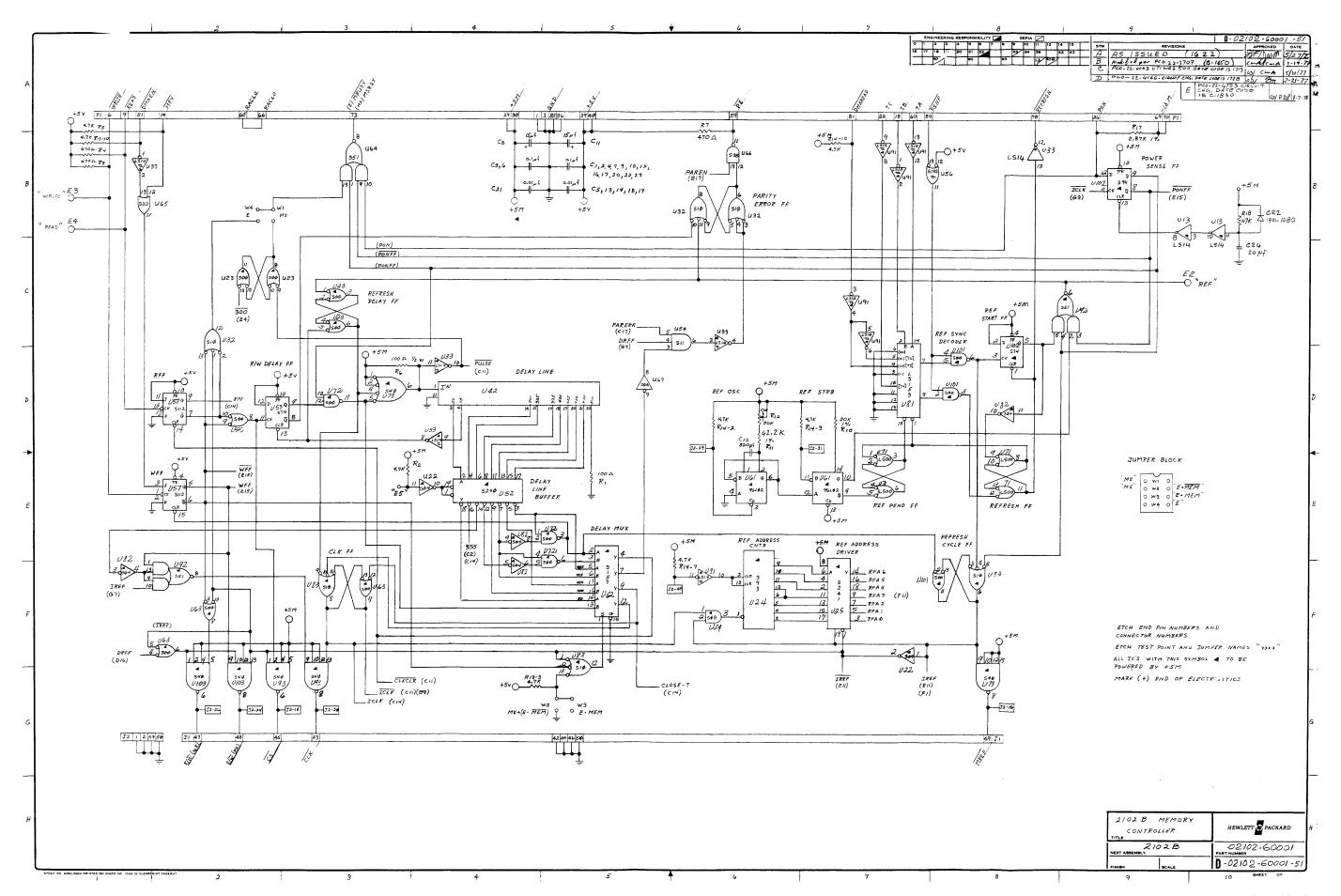

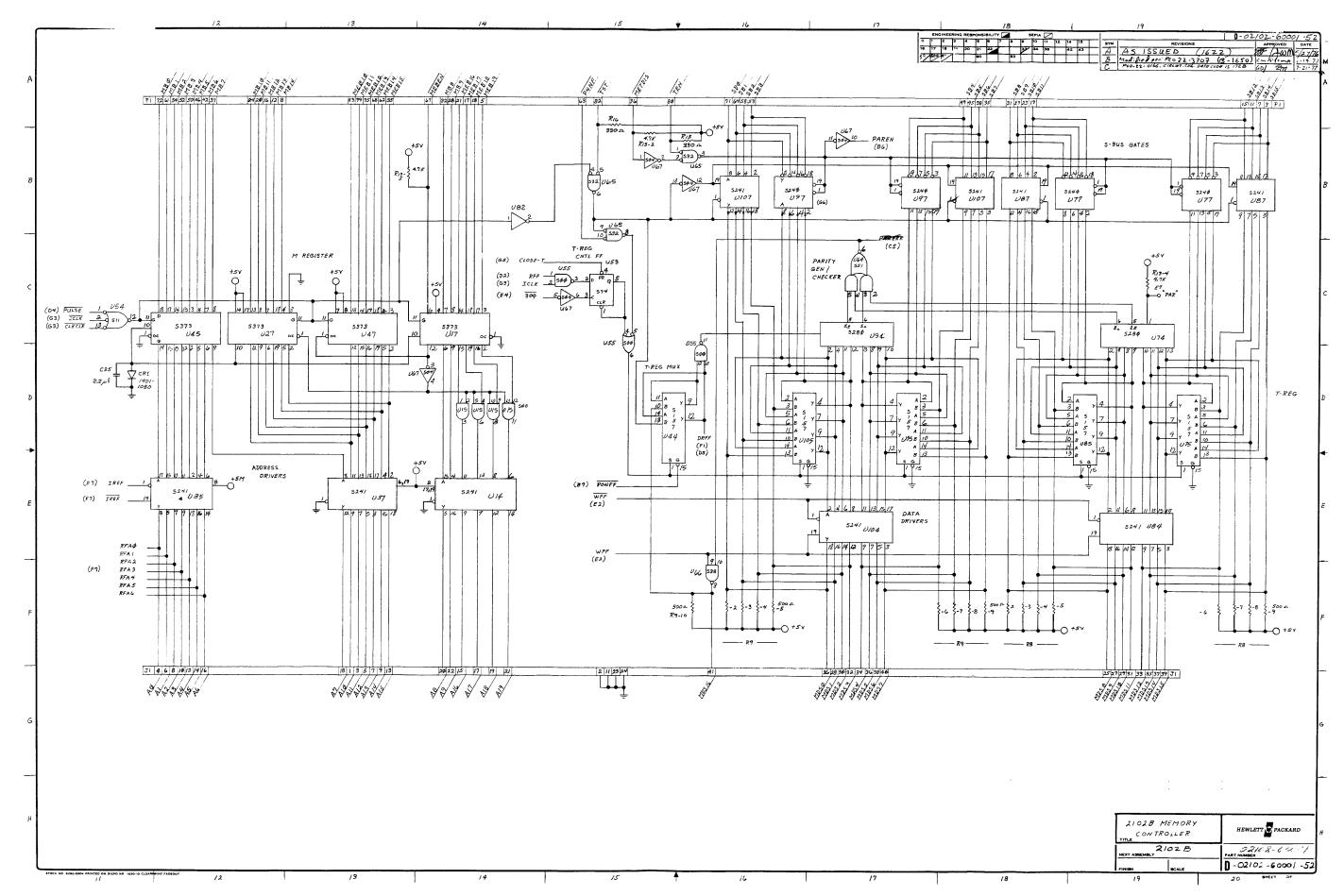

| 2102B            | Standard Performance Memory Controller                                        | 02102-60001 |

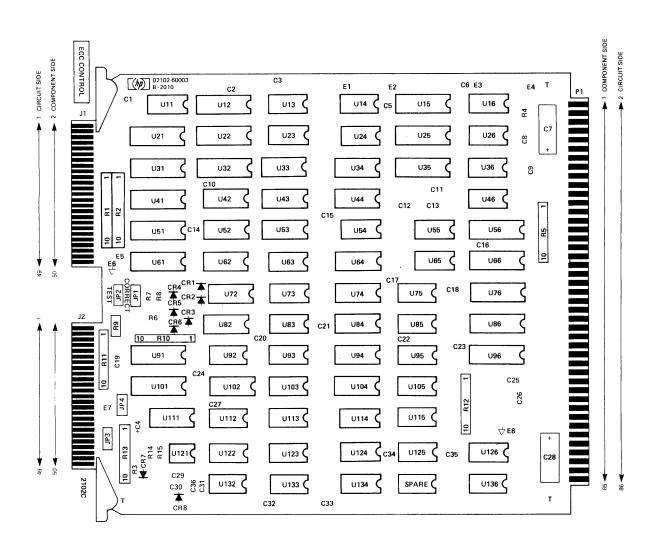

| 2102C            | Standard Performance Fault Control<br>Memory Controller                       | 02102-60003 |

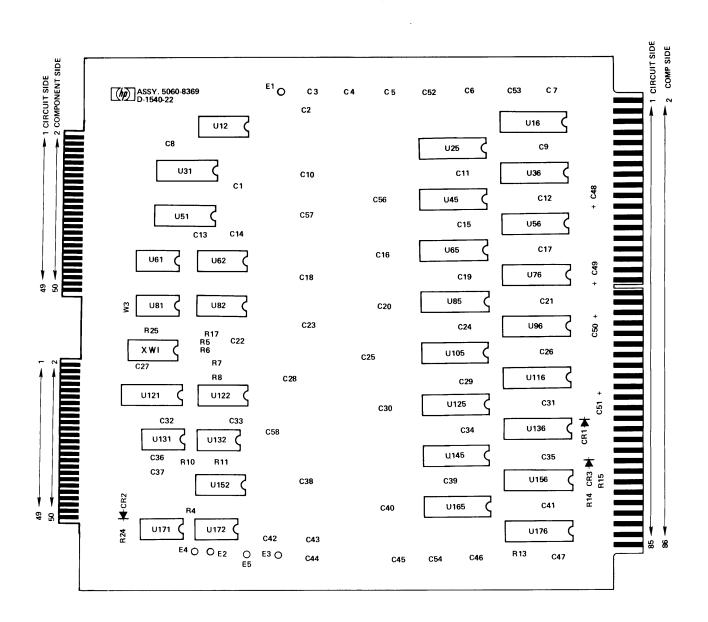

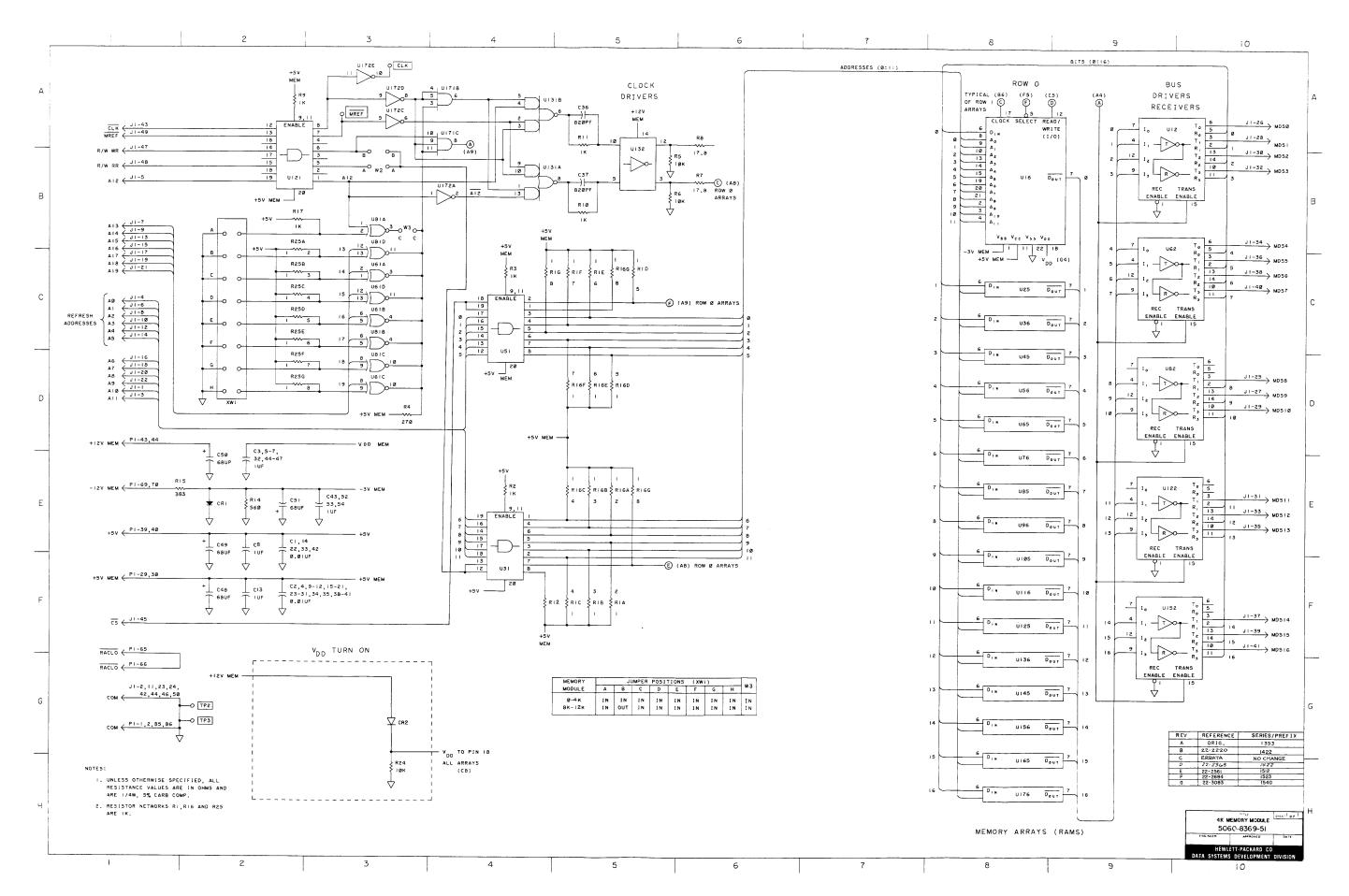

| 12994A           | 8K byte (4K word) Memory Module                                               | 5060-8369   |

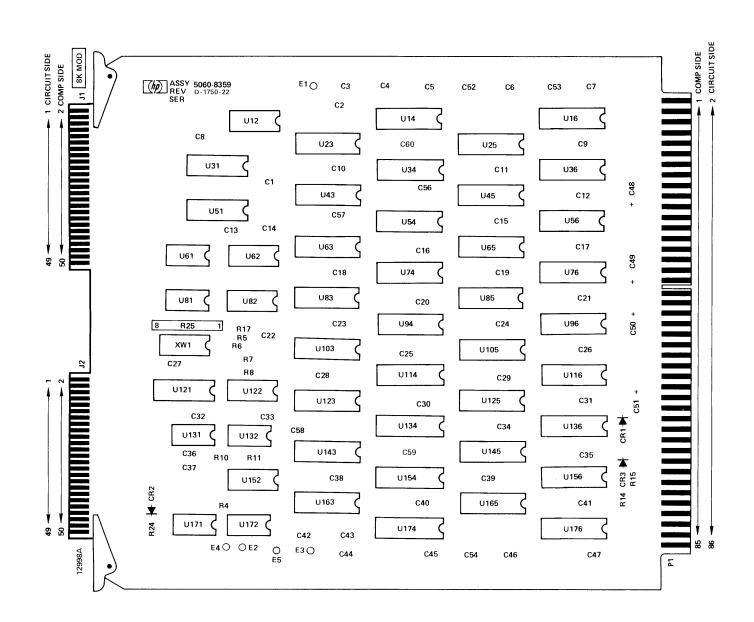

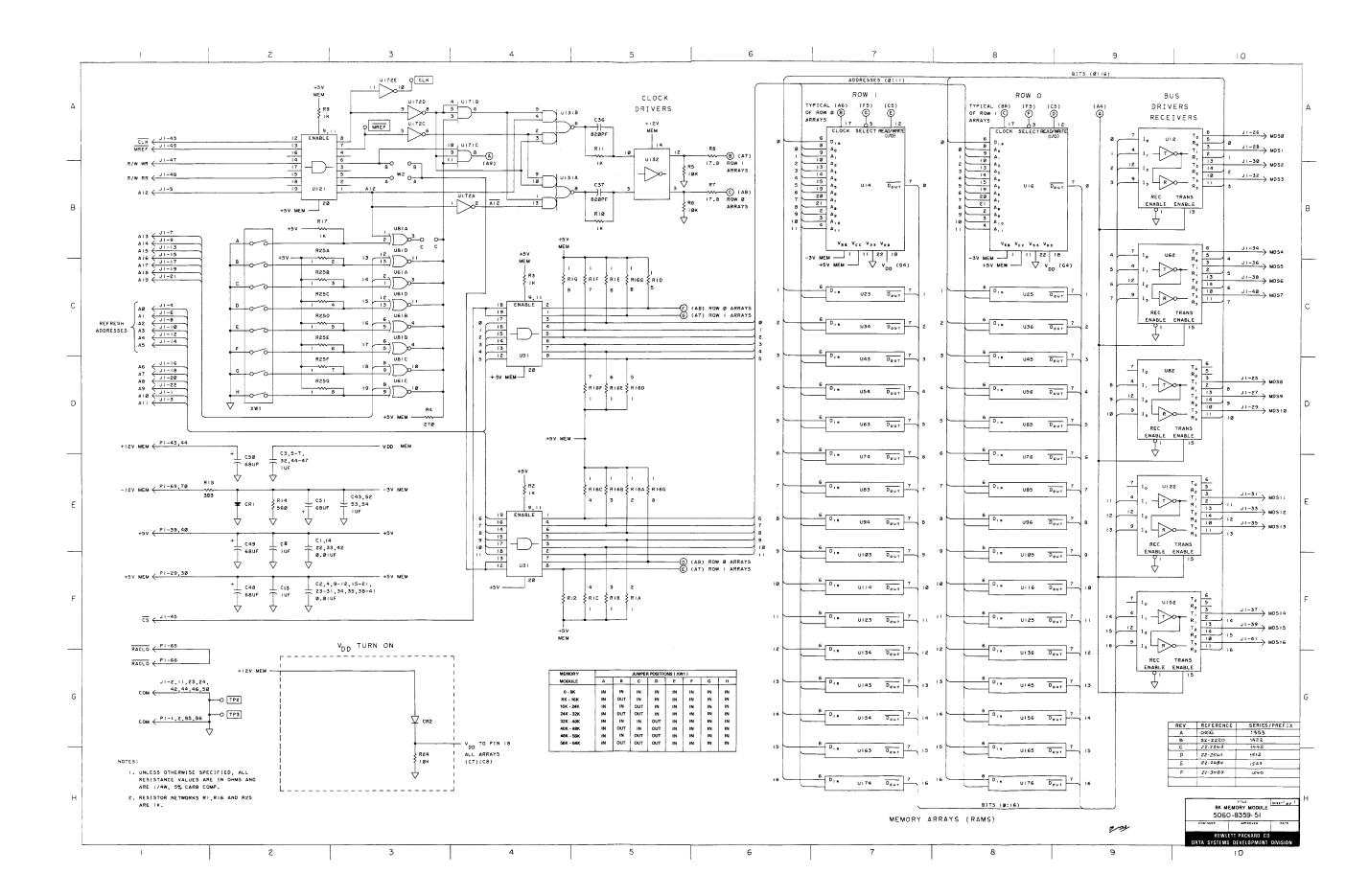

| 12998A           | 16K byte (8K word) Memory Module                                              | 5060-8359   |

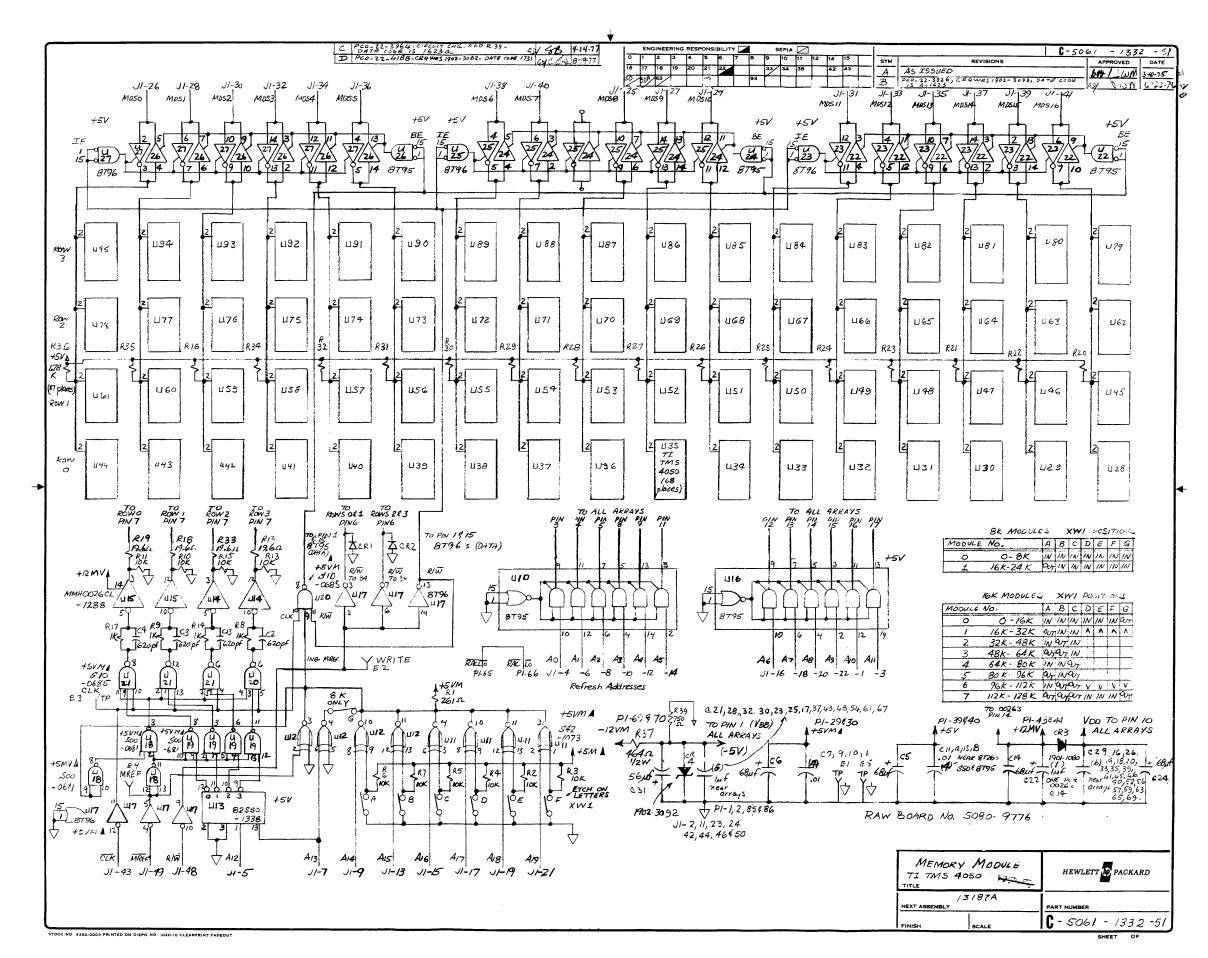

| 13187A           | 32K byte (16K word) Memory Module                                             | 5060-1332   |

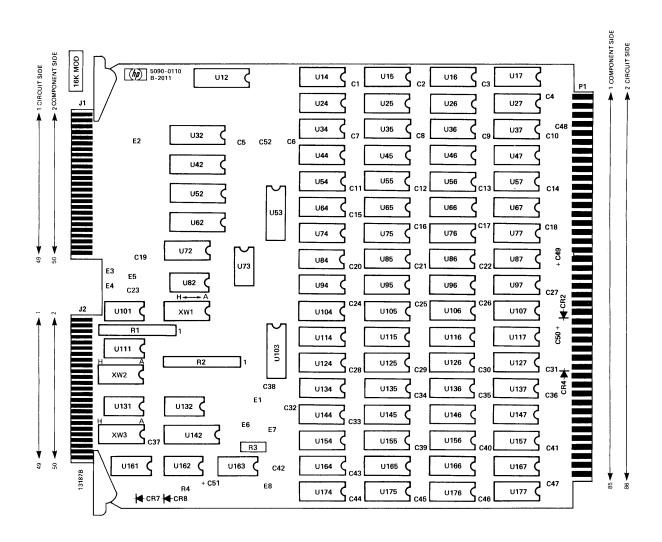

| 13187B           | 32K byte (16K word) Memory Module                                             | 13187-60001 |

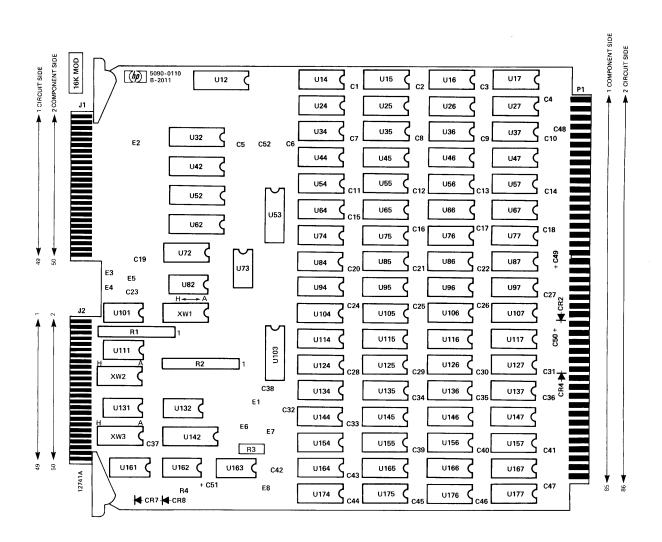

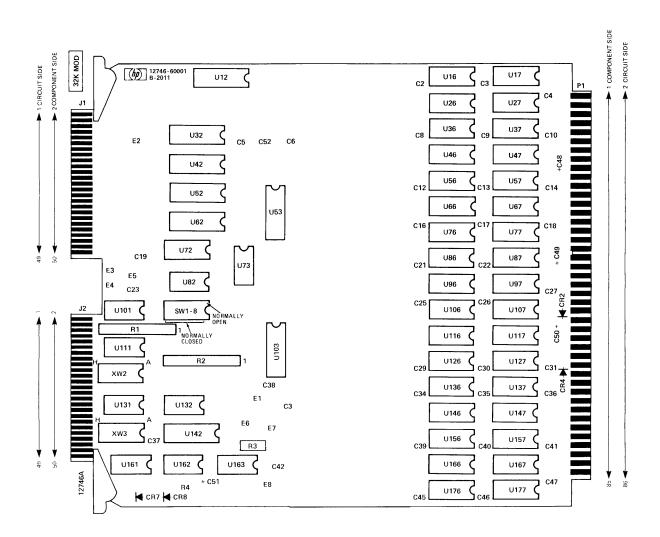

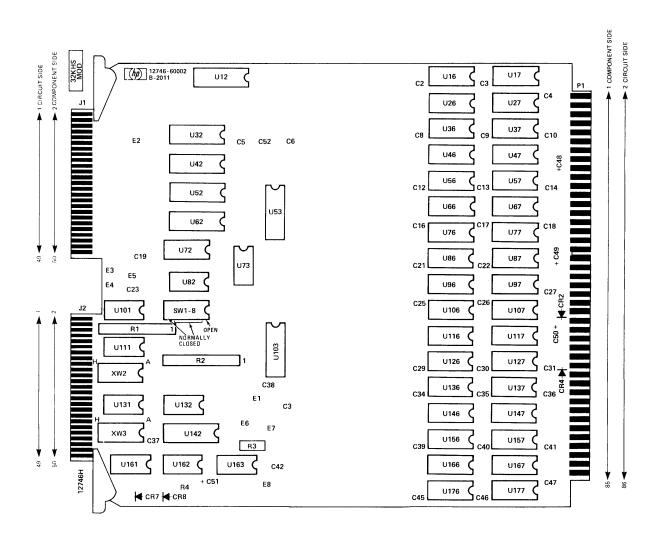

| 12746A *         | 64K byte (32K word) Memory Module                                             | 12746-60001 |

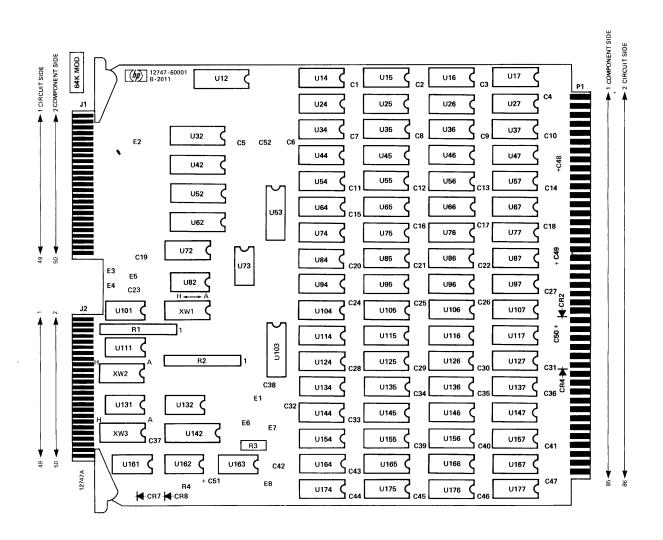

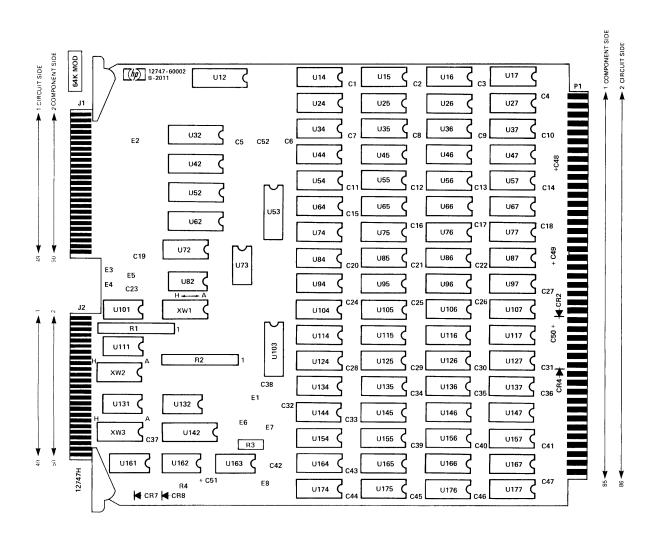

| 12747A           | 128K byte (64K word) Memory Module                                            | 12747-60001 |

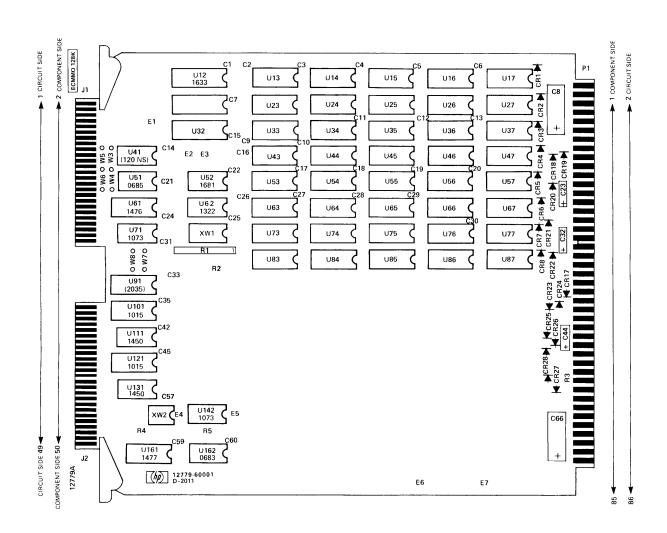

| <br>  12779A<br> | 256K byte (128K word) Standard<br>  Performance Check Bit Array   12779-60001 |             |

| 12780A           | 512K byte (256K word) Standard<br>  Performance Check Bit Array               | 12780-60001 |

Table 2. High Performance Memory System Products

| PRODUCT NO. | DESCRIPTION                                                 | PART NO.    |

|-------------|-------------------------------------------------------------|-------------|

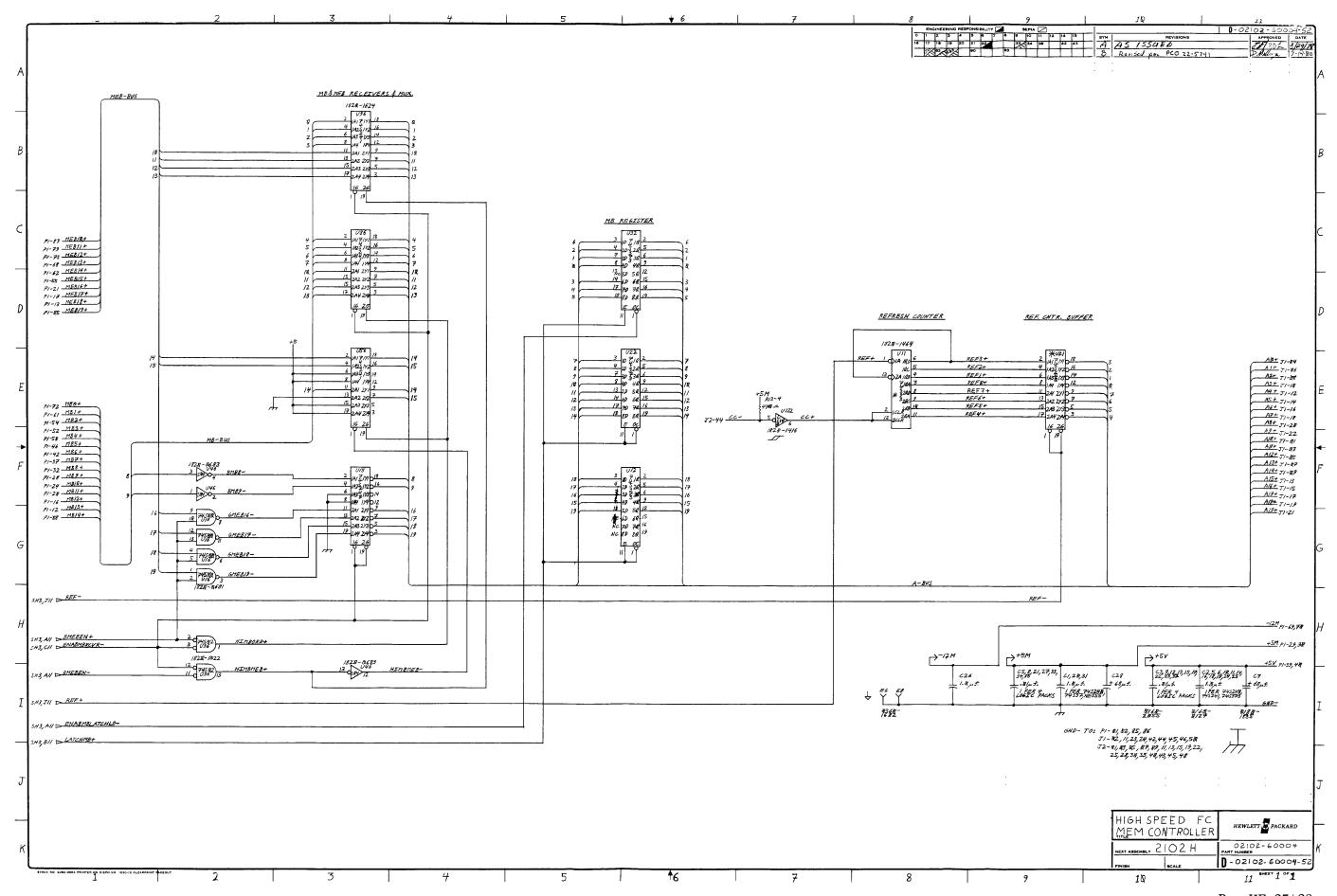

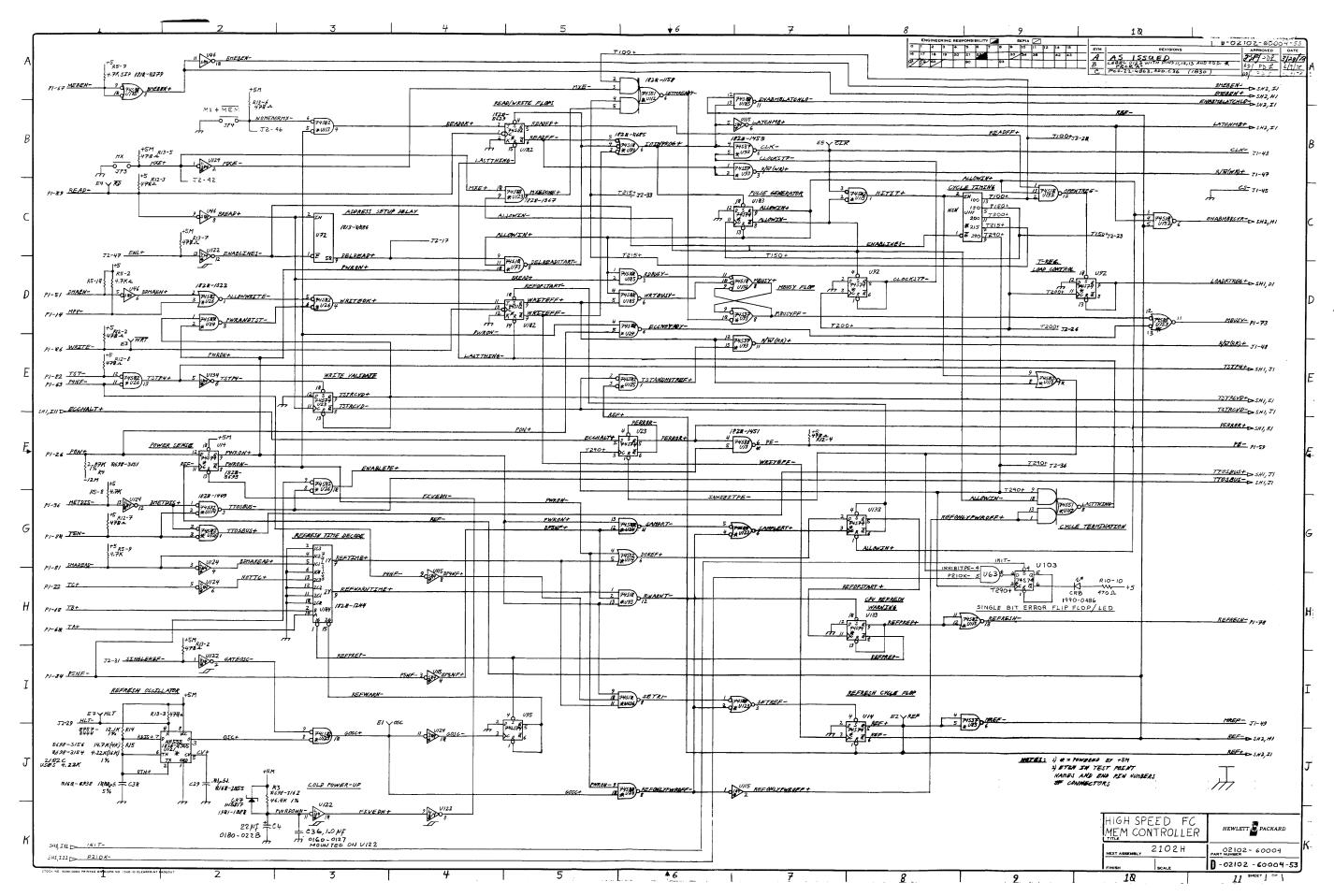

| 2102E       | High Performance Memory Controller                          | 02102-60002 |

| 2102н       | High Performance Fault Control Memory   02102-              |             |

| 12741A      | 32K byte (16K word) High Performance<br>Memory Module       | 12741-60001 |

| 12746H **   | 64K byte (32K word) High Performance   12746-60002          |             |

| 12747н      | 128K byte (64K word) High Performance   12747-60002         |             |

| 1 27 7 9 Н  | 256K byte (128K word) High Performance<br>Check Bit Array   | 12779-60002 |

| 12780Н      | 512K byte (256K word) High Performance<br>  Check Bit Array | 12780-60002 |

<sup>\*</sup> The 12746A is a half-loaded (64K byte) 12747A (128K byte) Memory Array Board. These boards are used with the Standard Perfomance 2102B or 2102C Memory Controllers, and are identical in operation.

<sup>\*\*</sup> The 12746H is a half-loaded (64K byte) 12747H (128K byte) Memory Array Board. These boards are used with the High Performance 2102E or 2102H Memory Controllers, and are identical in operation.

# MEMORY CONTROLLERS

### HP 2102A MOS MEMORY SYSTEM

THEORY OF OPERATION

#### NOTE

This document is part of the HP 1000 M, E, and F-Series Computers Engineering and Reference Documentation and is not available separately.

### CONTENTS

| Par | agraph Page                                 | • |

|-----|---------------------------------------------|---|

| 1   | Introduction                                | 5 |

| 2   | General Theory of Operation                 | 5 |

| 3   | Description                                 | 5 |

| 4   | Read Cycle                                  | 5 |

| 5   | Write Cycle                                 | 3 |

| 6   | Refresh Cycle                               | 3 |

| 7   | Detailed Theory of Operation                | 3 |

| 8   | Memory Addressing                           |   |

| 9   | Signal Description                          |   |

| 10  | Functional Unit Identification              |   |

| 11  | Pre-Cycle Conditions10                      |   |

| 12  | Read Cycle10                                |   |

| 13  | Write Cycle                                 |   |

| 14  | Refresh Cycle                               |   |

| 15  | Functional Component Description            |   |

| 16  | Memory Controller PCA Functional Components |   |

| 17  | Read Flip-Flop                              |   |

| 18  | Write Flip-Flop                             |   |

| 19  | R/W Delay Flip-Flop                         |   |

| 20  | MSRDY FF                                    |   |

| 21  | Clock Flip-Flop                             |   |

| 22  | Delay Line                                  |   |

| 23  | M-Register Control Flip-Flop                |   |

| 24  | M-Register Input Gates                      |   |

| 25  | M-Register                                  |   |

| 26  | T-Register Control Flip-Flop                |   |

| 27  | T-Register                                  |   |

| 28  | S-Bus Gates                                 |   |

| 29  | Memory Gates                                |   |

| 30  | T-Register Multiplexer                      |   |

| 31  | Parity Circuits                             |   |

| 32  | Refresh Oscillator                          |   |

| 33  | Strobe B Flip-Flop                          |   |

| 34  | Strobe A Flip-Flop                          |   |

| 35  | Refresh Decoder                             |   |

| 36  | Refresh Flip-Flop                           |   |

| 37  | Refresh Transmit FF                         |   |

| 38  | Refresh Delay FF                            |   |

| 39  | Row-Select Counter                          | 1 |

## **CONTENTS** (continued)

| 40 | Power Sense Flip-Flop            |

|----|----------------------------------|

| 41 | Memory PCA Functional Components |

| 42 | PCA Select Circuits              |

| 43 | Control Circuits                 |

| 44 | Memory Integrated Circuits       |

| 45 | Bus Drivers/Receivers            |

| 46 | Memory Protect Violations        |

| 47 | Normal Read Cycle30              |

| 48 | DCPC Read or Write Cycle         |

| 49 | Normal Write Cycle               |

### **TABLES**

| Γable | Title                                                | Page |

|-------|------------------------------------------------------|------|

| 1     | Memory System Signals                                | 7    |

| 2     | Identification of Memory Controller Functional Units | 9    |

| 3     | Identification of Memory PCA Functional Units        | 10   |

| 4     | Read Cycle Events                                    |      |

| 5     | Write Cycle Events                                   | 15   |

| 6     | Refresh Cycle Events                                 |      |

#### 1. INTRODUCTION

This document provides theory of operation for the 2102A MOS Memory System used in the 21MX Computer Series and is divided into two sections; general theory of operation and detailed theory of operation. The general theory gives an overview of memory system operations. The detailed theory describes significant events occurring during memory system operations and the functional components which produce them.

#### 2. GENERAL THEORY OF OPERATION

The general theory of operation consists of a description of the memory system and a brief description of each of the three memory cycles.

#### 3. Description

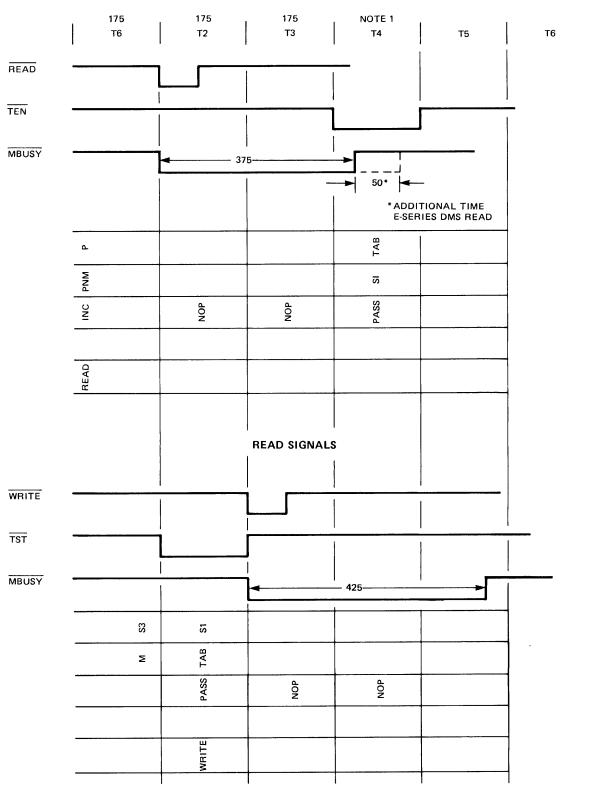

The memory system consists physically of one memory controller PCA and one or more memory PCA's. The system functions in three cycles: read, write and refresh. Each type of cycle requires two input/output (I/O) "T" periods (650 nanoseconds).

The read cycle reads out a 16-bit data word from the memory address supplied to it by the CPU and supplies it to the S-bus. The write cycle writes a 16-bit data word into the memory address supplied to it by the CPU. In write mode the controller derives a parity bit from the data word supplied to it and stores the parity bit, with the 16-bit data word, in memory. When the data is retrieved in read mode, the controller again derives the parity of the 16-bit word and checks it against the parity bit supplied from memory. If they disagree, the CPU is notified with an error signal.

The memory is composed of semiconductor integrated circuits (IC's) which require refreshing at least every 2 milliseconds. This is done with a refresh cycle which occurs, automatically, approximately every 32 microseconds. Each refresh cycle refreshes 1/64th of the memory so that the total memory is refreshed, according to requirement, every 2 milliseconds.

The refresh cycle is performed, normally, in I/O "T" periods 2 and 3 but, when it occurs while memory is under DCPC control, it is performed in periods 4 and 5. This leaves periods 2 and 3 for the DCPC read cycle.

The refresh cycle is performed automatically, without external stimulation. When a refresh cycle is started, the CPU is notified so that read and write cycles are inhibited until the refresh cycle is complete.

#### 4. Read Cycle

The read cycle is initiated when the Read signal from the CPU becomes active. The memory address, from the CPU, is supplied to the M-register (on the controller) and memory. It is stored in the M-register to be

continually supplied to memory until the data is read out from the stored memory address. The 16-bit data word is read out from memory and stored in the T-register and the parity bit is supplied to the parity circuits. The parity circuits check parity and, after the result of the check is ready, the S-bus gates are opened to enable passage of the memory data word to the S-bus. Also the parity error status is generated to the CPU. Then the controller and memory circuits are restored to the ready-for-new-cycle state.

#### 5. Write Cycle

A write cycle begins with data supplied to memory and to the T-register and parity circuits on the memory controller. The T-register stores the data and a parity bit is derived from it by the parity circuits. The address into which the data is to be written is supplied to memory and the M-register and the Write signal to the memory controller is activated by the CPU. Then the memory controller enables writing into memory and the M-register stores the address and becomes the address source for memory. The controller opens the memory gates to pass the data from the T-register to memory and the data is written into the selected address of memory.

#### 6. Refresh Cycle

A refresh cycle is initiated automatically by an oscillator on the controller PCA. When a refresh cycle starts, reading or writing is disabled by the controller and the CPU is notified that a refresh cycle is in process. A 0-to-63 counter on the controller PCA selects a different row of memory elements to be refreshed by each refresh cycle. Essentially, in a refresh cycle, the controller only indicates the row of memory elements to be refreshed. Refreshing of the memory elements is performed within the memory IC.

#### 7. DETAILED THEORY OF OPERATION

The detailed theory of operation consists of a description of how a word of memory is addressed, a description of memory signals, identification of the functional units on the memory controller and memory PCA's, a description of the initial conditions before a read or write cycle starts, and a detailed description of a read cycle, a write cycle, and a refresh cycle.

#### 8. Memory Addressing

Memory for a 21MX computer is contained on one or more PCA's. Each PCA contains either one or two rows of memory IC's. There are 17 IC's in a row, one IC for each bit of the 17-bit memory word. A one-row PCA is referred to as a 4K PCA. The two-row PCA is referred to as an 8K PCA. The 4K and 8K descriptions refer to the approximate number of 17-bit memory words the PCA is capable of storing.

Note: The word "row" is used, in this discussion, to refer to two different items:

- a. A group of 17 memory IC's arranged in a row on a PCA.

- b. A row of 64 memory elements within an IC.

Each IC contains a 64-row by 64-column matrix of memory elements for a total of 4,096 (approximately 4K) memory elements within each IC. A row of 17 such IC's is capable of storing 4,096 17-bit memory words, with each bit of the memory word stored in a separate IC dedicated to that bit. The bits are stored in identical elements in the IC's; that is, the same column and row are addressed on each IC to form the 17-bit word.

A 20-bit address word is used to select a 17-bit word stored in memory. To select a memory word, four items must be identified; the PCA, the row of IC's on the PCA (row 1 or 2), the row of elements within each IC, and the column of elements within each IC. These items and the bits of the memory address used to identify them are listed below.

| MEMORY ADDRESS BITS | ITEM IDENTIFIED                   |

|---------------------|-----------------------------------|

| 13 through 19       | PCA                               |

| 12                  | Row (1 or 2) of IC's on the PCA   |

| 6 through 11        | Column of elements within each IC |

| 0 through 5         | Row of elements within each IC    |

Bits 6 through 11, which identify the column of memory elements, form a 6-bit binary word. The same is true of bits 0 through 5 which identify the row of memory elements. The column and row words are supplied to each IC and are decoded within each IC to select the single designated memory element.

For purposes of refreshing memory, only the 64 rows on each IC are addressed; (it isn't necessary to address each individual memory element for refreshing).

#### 9. Signal Description

Table 1 lists all control and status signals used in the memory and provides a brief description of their function.

Table 1. Memory System Signals

| SIGNAL | FUNCTION                                                                                                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read   | Initiates a memory read cycle.                                                                                                                                                                                       |

| Write  | Initiates a memory write cycle.                                                                                                                                                                                      |

| MPV    | Indicates a memory protect violation to the controller. In a DCPC operation, it has no effect. In a normal read operation, an all "1"s word is supplied to the S-bus. In a normal write mode, no write cycle occurs. |

| DMAEN  | Indicates that a DCPC read or write cycle is going to occur. The DCPC is free to read and write in the protected area of memory.                                                                                     |

|        |                                                                                                                                                                                                                      |

Table 1. Memory System Signals (continued)

| SIGNAL         | FUNCTION                                                                                                                                                                                                                                                                                |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMAREAD        | Delays a refresh cycle which might be ready to begin until time periods T4 and T5. (The refresh cycle normally occurs during T2 and T3.) This leaves T2 and T3 for the DCPC read cycle.                                                                                                 |

| P4NF and P5NF  | The last two of six time periods occurring in a T period. P4NF, together with TST, enables read in of data into the T-register in a write cycle. The P5NF which occurs in time period T6 (or T3, if a DCPC read cycle is beginning), enables the refresh cycle to begin, if one is due. |

| TA, TB, and TC | These signals are a binary word which, when decoded, indicate the current T period.                                                                                                                                                                                                     |

| PON            | Indicates that the power supply is receiving ac line power and is operating properly. When PON becomes inactive, reading and writing is inhibited and refresh cycles occur every 32 microseconds, independent of conditions external to the memory system.                              |

| TEN            | Opens the S-bus gates to pass data from the T-register to the S-bus after the Read signal has become inactive in a read cycle.                                                                                                                                                          |

| TST            | Together with the P4NF signal, enables the T-register to store the data from the S-bus in a write operation.                                                                                                                                                                            |

| R/W RR         | Either this signal or R/W WR is jumpered, on the memory PCAs, to select read mode or write mode for the memory IC's. The IC, when enabled by active CLK and CS signals, will read when the jumpered signal is high and write when it is low.                                            |

| R/W WR         | Either this signal or R/W RR is jumpered, on the memory PCA, to select read mode or write mode for the memory IC's. The IC, when enabled by active CLK and CS signals, will read when the jumpered signal is high and write when it is low.                                             |

| CS and CLK     | Both signals are required to enable the memory IC's to read or write. Reading or writing is selected by the R/W RR or R/W RW signal.                                                                                                                                                    |

| MREF           | Informs memory that a refresh cycle is in progress. Used, on the memory PCA, together with the CLK signal, to activate the CLOCK input to the memory IC's during a refresh cycle.                                                                                                       |

| A0 thru A5     | These six bits of the memory address word are used, by the refresh circuits, to select the row of memory elements to be refreshed. The bits are in the form of a binary code which is decoded, in the IC, to identify the row of memory elements.                                       |

| MSRDY          | Indicates, to the CPU, that the memory system is available for another memory cycle.                                                                                                                                                                                                    |

| REFRESH        | Indicates, to the CPU, that a refresh cycle is about to begin. Read and write cycles are inhibited during a refresh cycle.                                                                                                                                                              |

| PE             | Indicates, to the CPU, that the data word read from memory, during the current cycle, contains a parity error.                                                                                                                                                                          |

| METDIS         | Signal generated by DMS for read protection.                                                                                                                                                                                                                                            |

#### 10. Functional Unit Identification

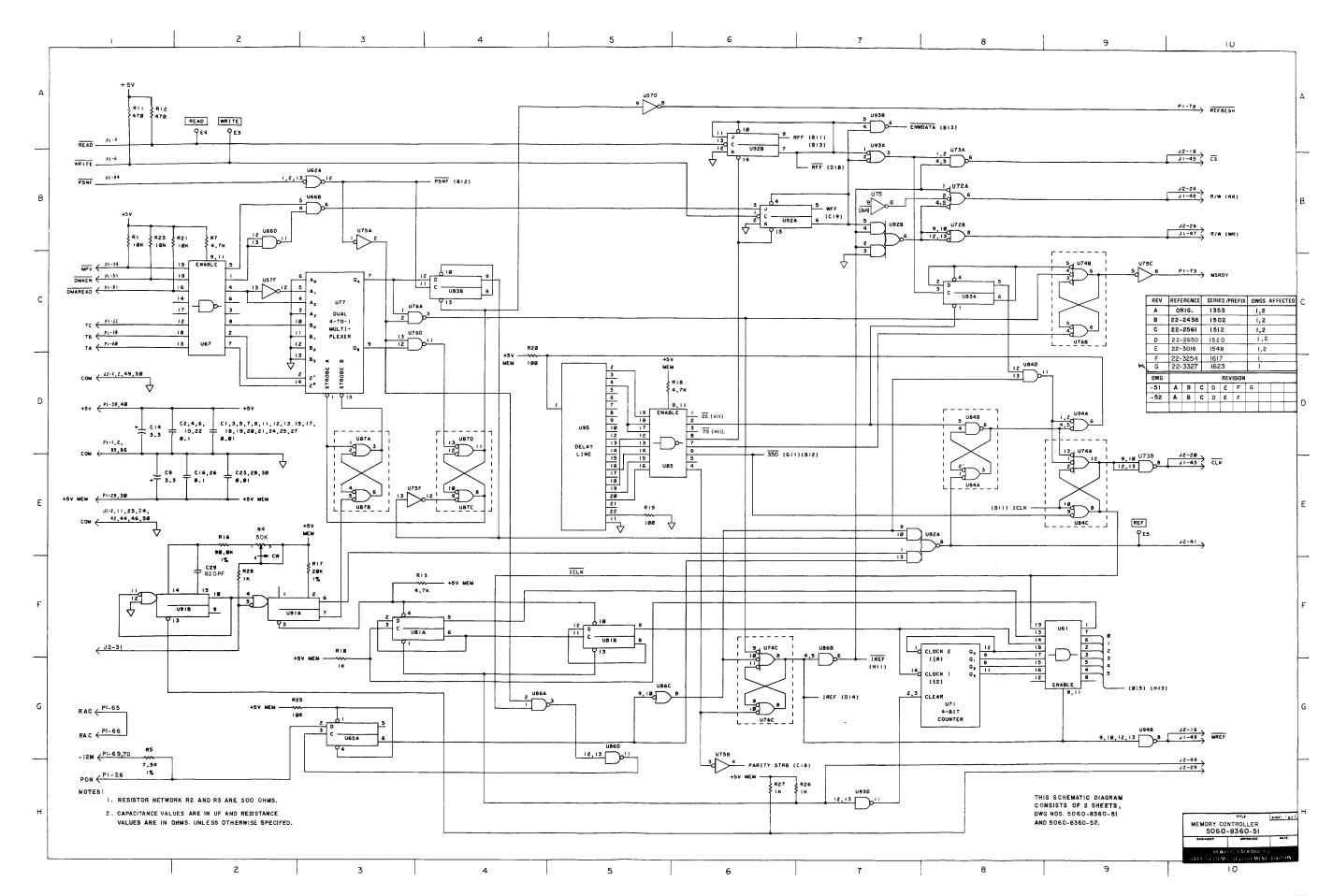

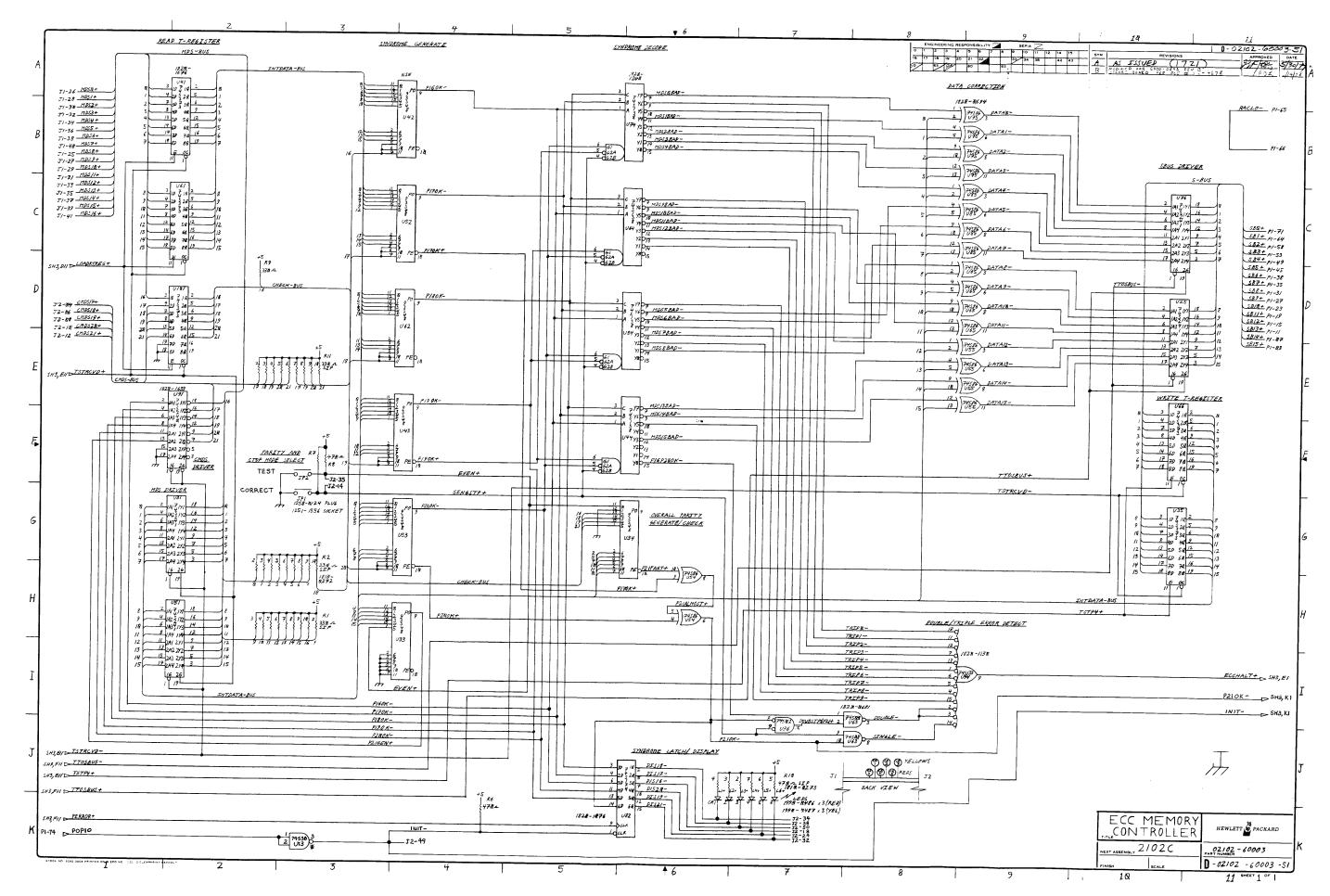

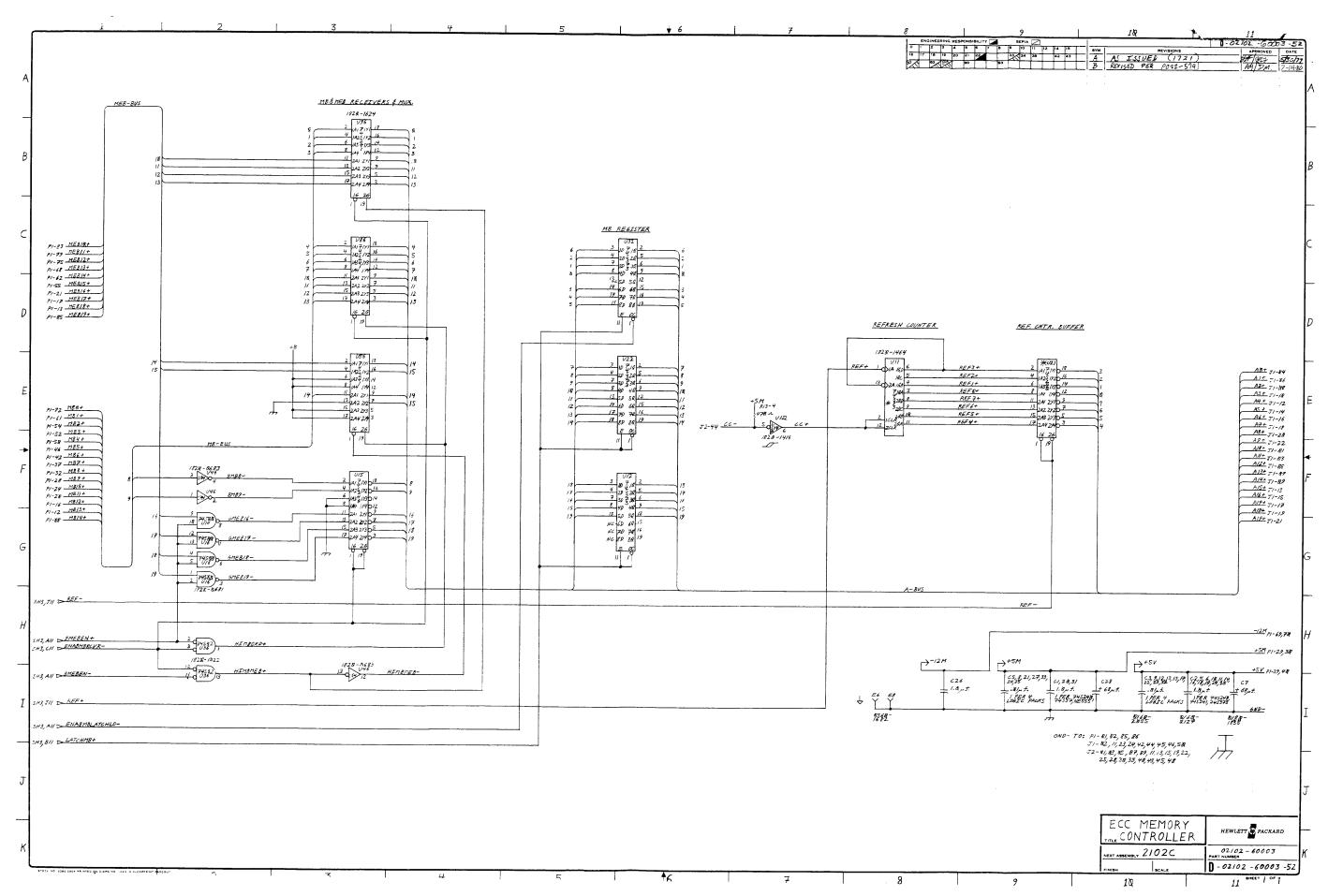

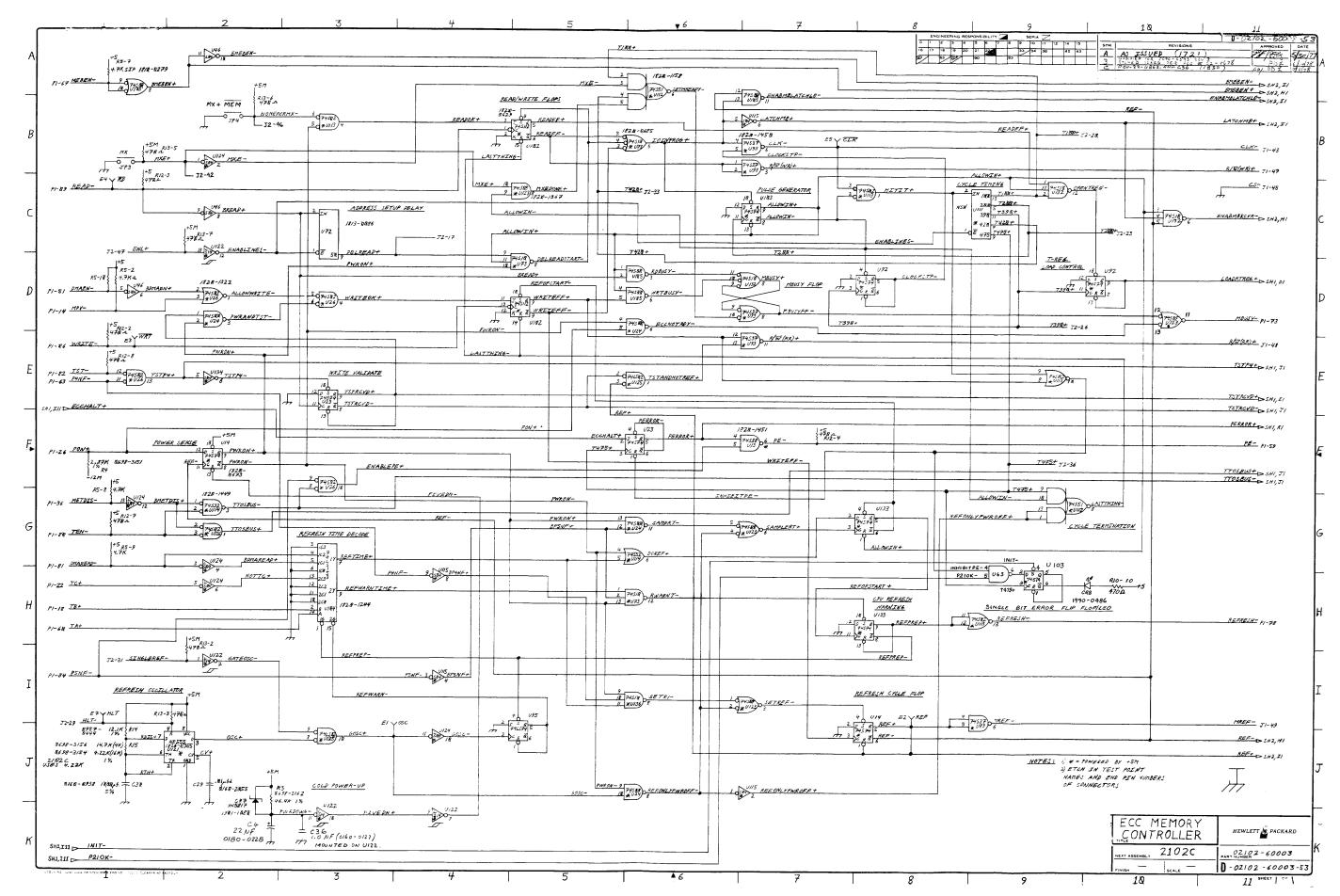

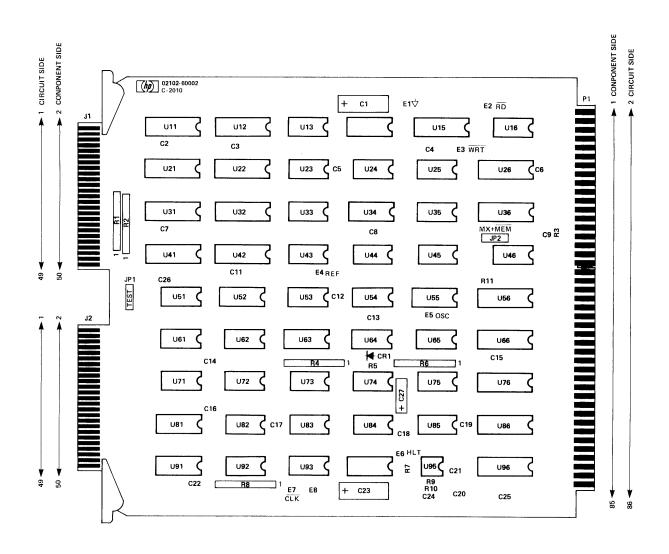

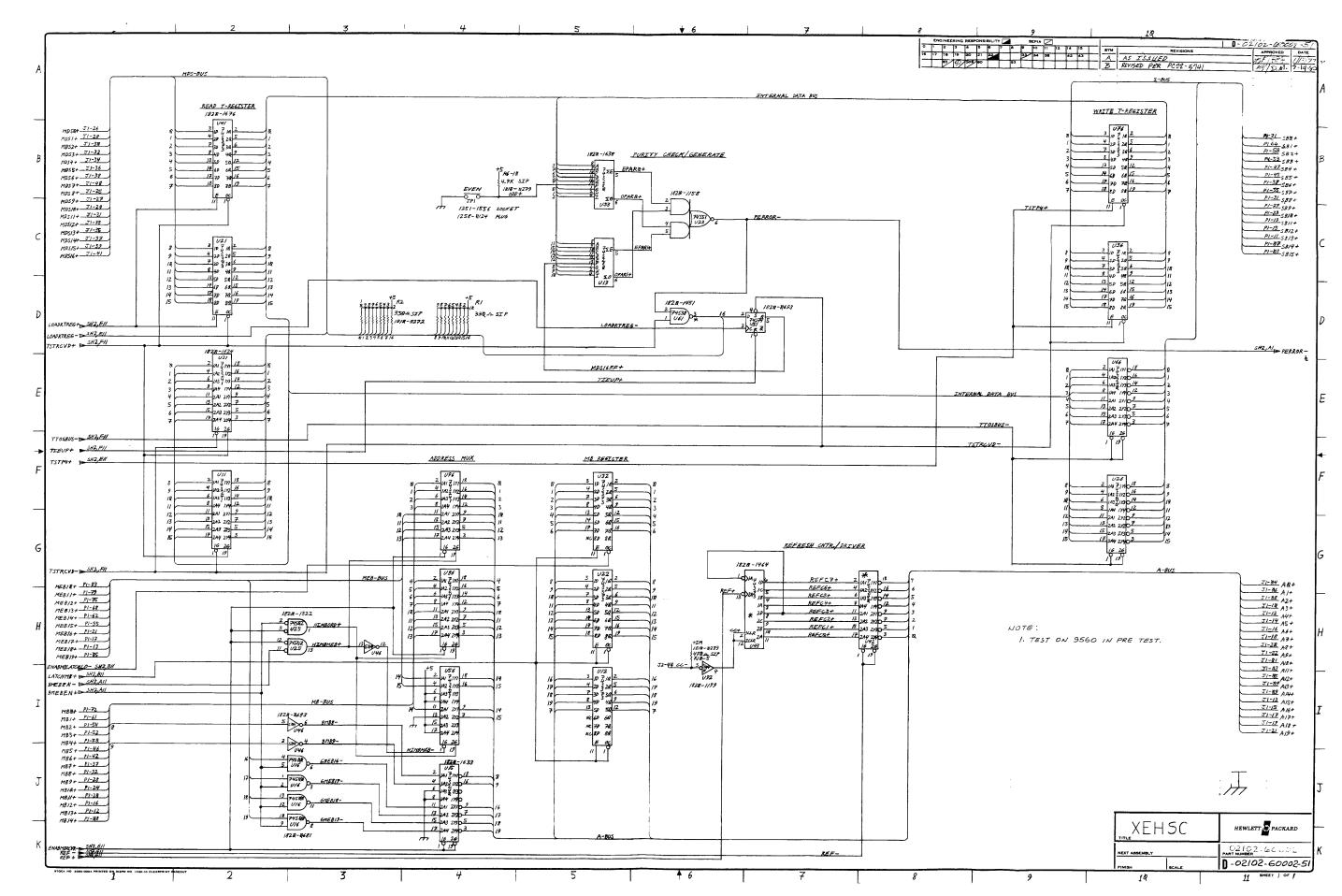

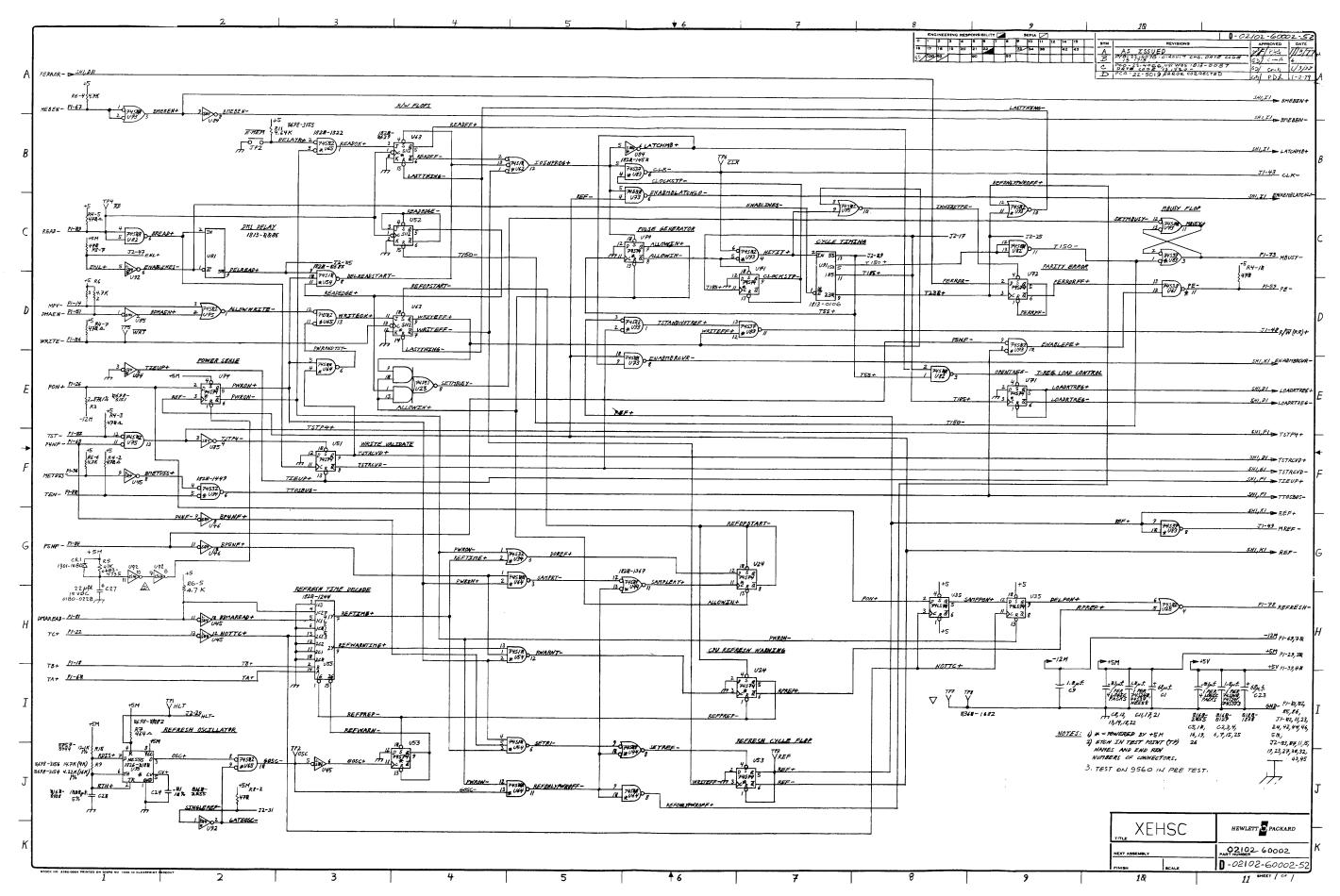

In the following discussion, it is necessary to refer to the functional units of the memory system, such as flip-flops, multiplexers, and registers by name. Since the functional units aren't identified by name on the logic diagrams, they are listed in tables 2 and 3, along with their reference designations, to enable use of the logic diagrams in following the discussion.

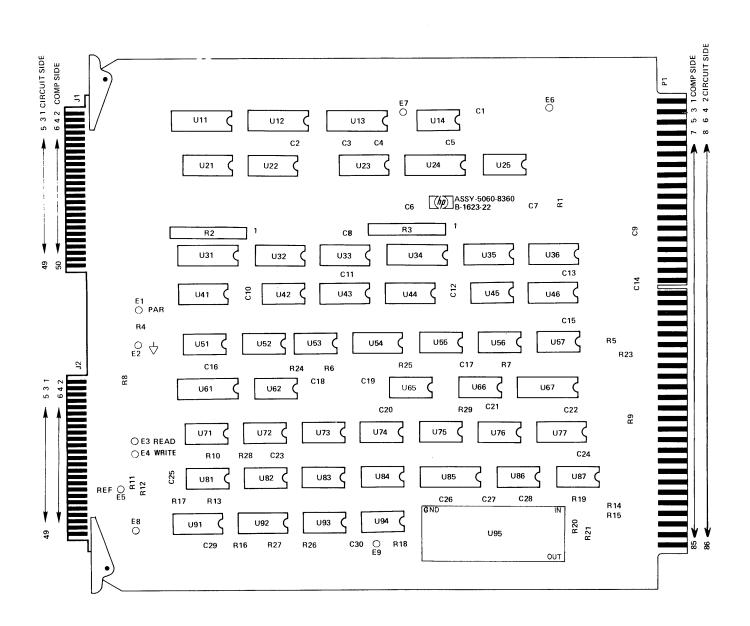

Table 2. Identification of Memory Controller Functional Units

| NAME                   | REFERENCE DESIGNATION  |

|------------------------|------------------------|

| Read flip-flop (FF)    | U92B                   |

| Write FF               | U92A                   |

| R/W Delay FF           | U83A                   |

| MSRDY FF               | U74B and U76B          |

| Clock FF               | U74A and U84C          |

| Delay Line             | U95                    |

| M-register Control FF  | U51A and U51B          |

| M-register input gates | U11, U12, U13, and U24 |

| M-register             | U21, U22, and U23      |

| T-register Control FF  | U65B                   |

| T-register             | U32, U35, U41, and U45 |

| S-bus gates            | U33, U36, U43, and U46 |

| Memory gates           | U31 and U34            |

| Parity circuits        | U42 and U45            |

| T-register multiplexer | U54                    |

| Refresh oscillator     | U91A and U91B          |

| Strobe A FF            | U87C and U87D          |

| Strobe B FF            | U87A and U87B          |

| Refresh decoder        | U77                    |

| Refresh FF             | U83B                   |

| Refresh Delay FF       | U84A and U84B          |

| Refresh Transmit FF    | U74C and U76C          |

| Row select counter     | U81A, U81B, and U71    |

| Refresh drivers        | U61                    |

| Power Sense FF         | U65A                   |

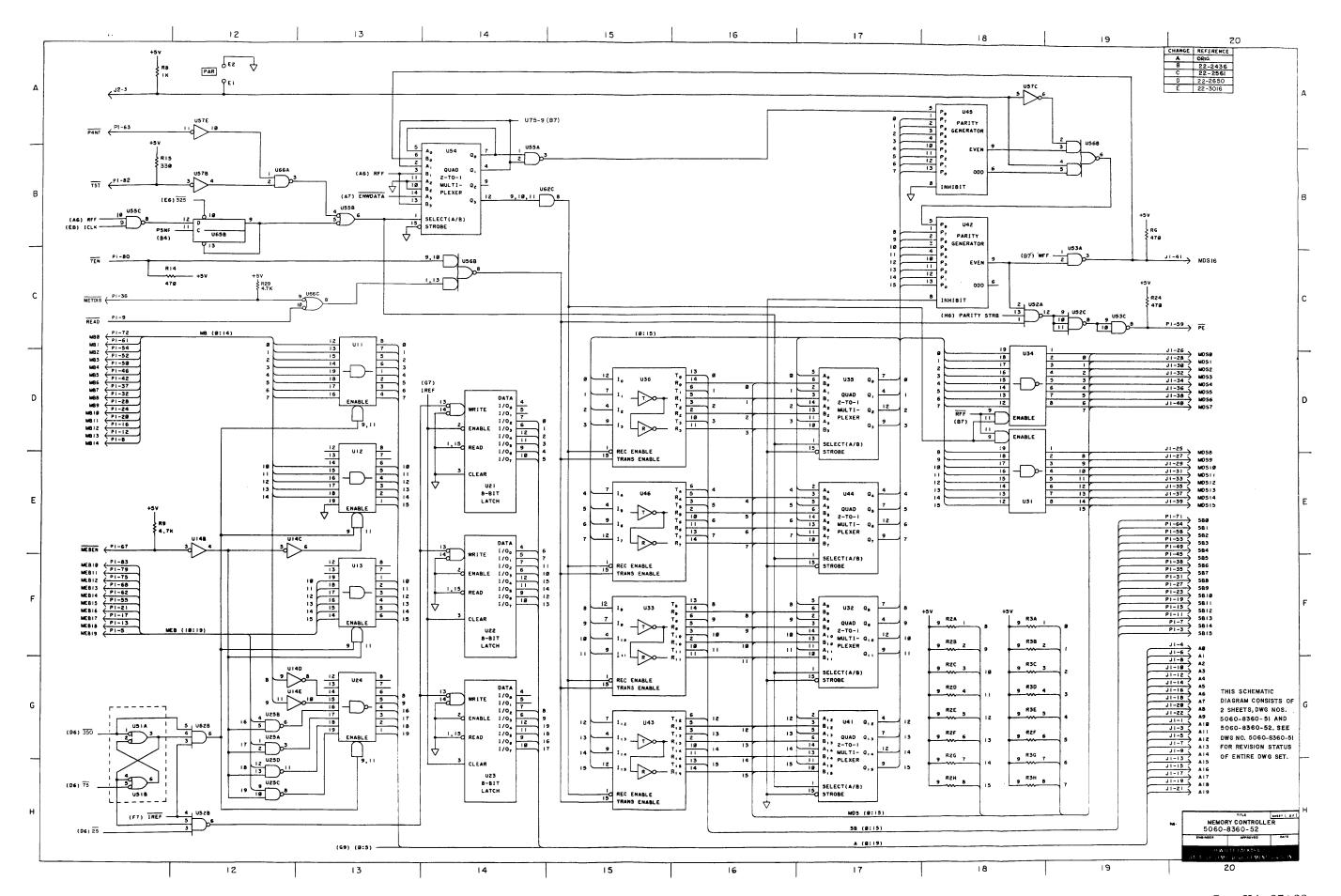

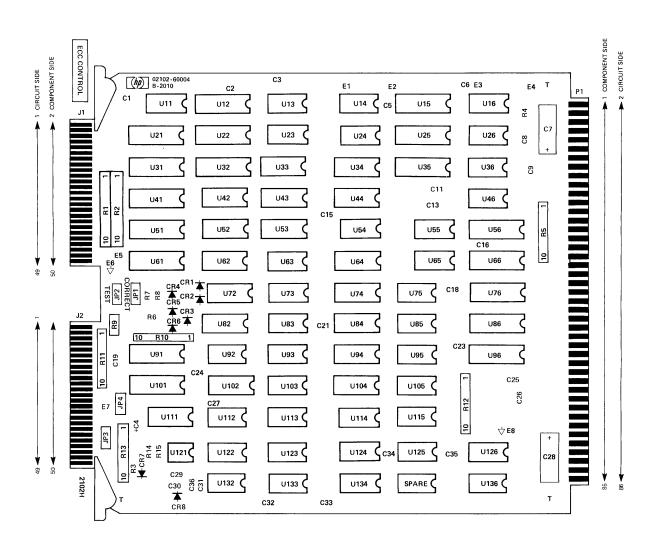

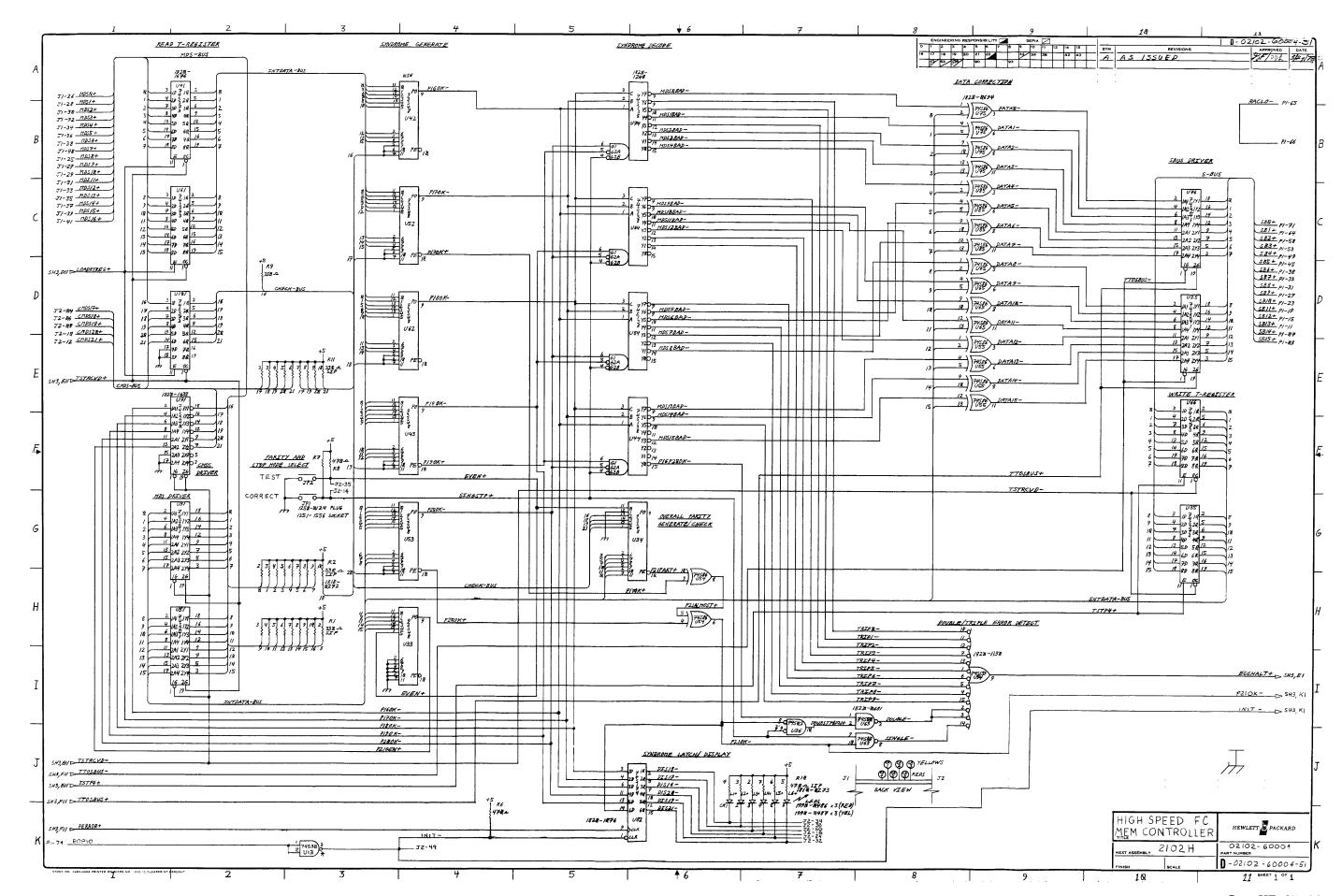

Table 3. Identification of Memory PCA Functional Units

| NAME                  | REFERENCE DESIGNATION                   |

|-----------------------|-----------------------------------------|

| PCA select circuits   | XW1, U61A thru U61D, and U81A thru U81D |

| Control circuits      | U121, U171B, U171C, U131A, and U131B    |

| Bus drivers/receivers | U12, U62, U82, U122, and U152           |

#### 11. Pre-Cycle Conditions

When no cycle is in progress, the following conditions exist in the memory system:

- a. The M-register input gates are open so that any memory address supplied by the CPU passes through the gates to the M-register and to memory.

- b. The M-register is ready to accept any address supplied but will not store it until early in a read or write cycle.

- c. The memory IC's are disabled for both reading and writing.

- d. The memory address, for a read or write cycle is supplied to the M-register and memory either before or approximately at the time the Read or Write signal from the CPU becomes active.

- e. The T-register is not receptive to data from either memory or the S-bus.

- f. The S-bus gates are disabled for passage of data from the T-register, or memory, to the S-bus and for passage of data from the S-bus to the T-register and memory.

- g. The memory gates are disabled for passage of data from the T-register to memory.

- h. The MSRDY signal to the CPU is active (high) indicating the memory system is ready for a cycle.

#### 12. Read Cycle

Information concerning events occurring in a read cycle are presented briefly, in table form, in table 4 and in narrative form in the paragraphs following the table.

Table 4. Read Cycle Events

| CAUSE                                                                                                                                                                                                        | EVENT                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read signal, from CPU, active (low).                                                                                                                                                                         | The Read FF (U92B) is set.                                                                                                                                                                                                                                                            |

| Read FF set.                                                                                                                                                                                                 | The R/W Delay FF (U83A) is set, the MSRDY FF is reset, and the MSRDY signal, which has been active, becomes inactive.                                                                                                                                                                 |

| Read FF set and no refresh cycle.                                                                                                                                                                            | The CS signal to memory IC's becomes active (low).                                                                                                                                                                                                                                    |

| R/W Delay FF set and PON signal from power supply active (high).                                                                                                                                             | The delay line (U95) is pulsed and begins, generating pulses at fixed delay intervals.                                                                                                                                                                                                |

|                                                                                                                                                                                                              | 2. The Clock FF (U74A and U84C) is set (pin U74-12 high).                                                                                                                                                                                                                             |

| Clock FF set.                                                                                                                                                                                                | 1. The CLK signal to memory is active (low).                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                              | 2. The ICLK signal is active (low).                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                              | 3. The ICLK signal is active (high).                                                                                                                                                                                                                                                  |

| Memory address available to memory PCA's, CS and CLK signals active, R/W WR signal high, and the signal jumpered on the memory PCA's to select read or write mode (either the R/W WR or R/W RR signal) high. | The memory supplies the data from the selected address to the T-register and the S-bus gates. However, the S-bus gates are not yet enabled to pass data to the S-bus.                                                                                                                 |

| 25 pulse from delay line (pin U85-1)                                                                                                                                                                         | The M-register stores the address present at its input and applies it steadily to memory.                                                                                                                                                                                             |

| 75 pulse from delay line (pin U85-2).                                                                                                                                                                        | The R/W Delay FF is reset ending the input pulse to the delay line.                                                                                                                                                                                                                   |

| 75 pulse from delay line (pin U85-3)                                                                                                                                                                         | The M-register control FF (U51A and U51B) is reset. This closes the M-register input gates, isolating the M-register and memory from the address supplied by the CPU. However, the address is stored in the M-register, which supplies it to memory.                                  |

| 275 pulse from delay line (pin U85-7).                                                                                                                                                                       | The MSRDY FF is set and the MSRDY signal to the CPU becomes active (high). It remains high until the next cycle.                                                                                                                                                                      |

| Read FF set, Clock FF set (ICLK signal active), and end of next P5 CPU time period occurs.                                                                                                                   | The T-Register Control FF (U65B) is set. (This FF is active in the reset condition.)                                                                                                                                                                                                  |

| T-Register Control FF reset (active).                                                                                                                                                                        | The B inputs are selected on the T-register and the T-register multiplexer (U54).                                                                                                                                                                                                     |

|                                                                                                                                                                                                              | The T-register, with its B inputs selected, accepts the 16-bit memory data word from memory.                                                                                                                                                                                          |

|                                                                                                                                                                                                              | 3. The T-register multiplexer supplies the parity bit (bit 16) from memory to the parity circuits through Nand gate U55A.                                                                                                                                                             |

|                                                                                                                                                                                                              | 4. Starting at this time, the parity circuits compare the parity which they derive from the data in the T-register with the parity bit supplied by memory and prepare an indication (the PE signal) of agreement or error. (The PE signal is supplied to the CPU later in the cycle.) |

Table 4. Read Cycle Events (continued)

| CAUSE                                                                                        | EVENT                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 350 pulse from delay line (pin U85-6)                                                        | The T-Register Control FF is set (made inactive). This selects the A inputs on the T-register and T-register multiplexer and causes the T-register to store the 16-bit data word from memory and supply it steadily to the parity circuits and S-bus gates.                                                                                                                                                                                      |

|                                                                                              | <ol><li>With its A inputs selected, the T-register multiplexer stores the<br/>parity bit (bit 16) from memory and supplies it steadily to the<br/>parity circuits.</li></ol>                                                                                                                                                                                                                                                                     |

|                                                                                              | 3. The Clock FF is reset. This deactivates the ICLK and ICLK signals and the CLK signal to memory. With the CLK signal inactive, the memory IC's stop supplying data to the T-register and S-bus gates. However, the data is now stored in the T-register.                                                                                                                                                                                       |

|                                                                                              | 4. The M-register Control FF is set. This stops the M-register from supplying the address stored in it to memory and opens it to accept any new address supplied from the M-register input gates. (These events result from a low output from gate U52B,) However, the M-register input gates won't open to pass new address information to the M-register until the 350 pulse becomes inactive (approximately 125 nanoseconds after it begins). |

| 400 pulse from delay line (pin U85-8).                                                       | The Read FF is reset. This enables the S-bus gates (ENWDATA signal through T-register multiplexer) to pass new data from the S-bus to the T-register and memory (but neither are in a condition to receive data).                                                                                                                                                                                                                                |

| TEN signal from CPU becomes active (low) and Read signal from CPU is inactive (high).        | The S-bus gates are enabled for transmission of data from the T-register to the CPU by gate U56B.                                                                                                                                                                                                                                                                                                                                                |

| 450 pulse from delay line (pin U85-4), TEN signal from CPU active, and Read signal inactive. | The PE signal is enabled by the Parity Strobe signal, at gate U52A, to indicate to the CPU whether or not a parity error exists in the data being transmitted to the CPU.                                                                                                                                                                                                                                                                        |

| TEN signal becomes inactive.                                                                 | The S-bus gates are disabled for transmitting data from the T-<br>register to the S-bus.                                                                                                                                                                                                                                                                                                                                                         |

| 350 pulse becomes inactive (high).                                                           | The M-register input gates are opened to pass any address supplied by the CPU to memory and the M-register.                                                                                                                                                                                                                                                                                                                                      |

A read cycle is initiated when the Read signal from the CPU becomes active (low), setting the Read FF. This closes the S-bus gates to isolate memory and the T-register from any signals on the S-bus. The transition of the Read FF output, from reset to set, activates (low level) the  $\overline{\text{CS}}$  signal to memory and sets the R/W Delay FF. This resets the MSRDY FF, deactivating (low) the MSRDY signal to the CPU to inform it that a memory cycle is in process. Also, the delay line is pulsed to start its sequence of delayed output signals.

The Clock FF is set, by the set condition of the R/W Delay FF, to activate the  $\overline{CLK}$  signal to the memory IC's. The reset condition of the Write FF makes the R/W WR signal to the memory PCA's high. This and

the active  $\overline{\text{CLK}}$  signal enable the bus driver/receivers, on the memory PCA selected by the memory address to pass data from the memory IC's on the selected PCA to the B inputs of the T-register and the S-bus gates. (By this time, the memory address is supplied to memory and the M-register, from the CPU through the open M-register input gates.) The active  $\overline{\text{CLK}}$  and  $\overline{\text{CS}}$  signals from the controller enable the memory IC's on the selected PCA to read or write. Reading, rather than writing, is selected by the high condition of either the R/W WR or R/W RR signal from the controller. (One of these signals is jumpered on the memory PCA's to select read or write for the memory IC's. Both signals are high at this time.) With all three read conditions met, the data is read out of the IC's at the selected memory address and supplied to the S-bus gates and the B inputs of the T-register. However, the S-bus gates are not yet enabled to pass the data word to the S-bus.

The delay line, which was pulsed when the R/W Delay FF was set, activates the  $\overline{25}$  pulse 25 nanoseconds after being pulsed. This causes the M-register to store the address supplied to it, through the M-register input gates, from the CPU. With the address stored, it supplies it steadily to all memory PCA's.

When the  $\overline{75}$  delay line signal (pin U85-2) becomes active, 75 nanoseconds after the delay line is pulsed, the R/W Delay FF is reset, ending the input pulse to the delay line. This pulse continues passing through the delay line, activating the delay line signals with its leading edge and deactivating them with its trailing edge.

When the  $\overline{75}$  signal from the delay line becomes active (low), the M-register control FF is reset, closing the M-register input gates. From this point on, the memory is no longer dependent on the CPU M-register.

The  $\overline{275}$  delay line signal (pin U85-7) sets the MSRDY FF to activate the MSRDY signal to the CPU. This notifies the CPU that the memory system is ready for a new memory cycle.

The end of the first P5 time period occurring after the Clock FF is set resets the T-register control FF. (The T-register control FF is active when reset.) This selects the B inputs to the T-register and T-register multiplexer. With its B inputs selected, the T-register passes the data from memory to the S-bus gates and the parity circuits. The parity circuits derive the parity of the 16-bit data word and compare it to the parity bit supplied to them from memory through the T-register multiplexer. The result of this comparison is supplied to the CPU, as the  $\overline{\text{PE}}$  signal, later in the cycle.

When the 350 delay line signal becomes active (low), the T-Register Control FF is set (made inactive), selecting the A inputs to the T-register and T-register multiplexer. With its A inputs selected, the T-register stores the 16-bit data word and applies it steadily to the S-bus gates and the parity circuits (the memory gates are closed, isolating memory from the contents of the T-register). The T-register multiplexer stores the parity bit supplied it from memory and applies it steadily to the parity circuits through gate U55A.

Activation of the  $\overline{350}$  signal also resets the clock FF. This deactivates the CLK signal to the memory IC's ending readout. However, the data word is now stored in the T-register.

The M-Register Control FF is set again by the active 350 signal but the M-register input gates remain closed until the 350 signal becomes inactive, later in the cycle.

The Read FF is reset when the  $\overline{400}$  delay line signal (pin U85-8) becomes active. This activates the  $\overline{\text{ENWDATA}}$  signal which passes through the T-register multiplexer to enable passage of data through the S-bus gates to memory and the T-register. However, the T-register is disabled from receiving data and although data can be supplied direct to the memory IC's, it cannot be read into them.

When the TEN signal from the CPU becomes active (low), providing the Read FF is reset, transmission of the data word from the T-register, through the S-bus gates, to the S-bus is enabled. From this time until the TEN signal is deactivated the data is transmitted to the CPU.

When the 450 delay line signal becomes active, the  $\overline{\text{Parity Error}}$  ( $\overline{\text{PE}}$ ) signal is enabled to communicate to the CPU whether or not a parity error was found in the data word being supplied to the CPU.

The M-register input gates are opened when the  $\overline{350}$  delay line signal becomes inactive (high). Then any address supplied to the controller passes through to memory and the M-register. This completes the cycle and leaves the memory system ready for the next cycle.

#### 13. Write Cycle

A synopsis of write cycle events is supplied in table 5. The paragraphs following the table supply a more complete description of events in narrative form.

Table 5. Write Cycle Events

| CAUSE                                                                                                                                                                                                 | EVENT                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| READ and WRITE FF's both clear.                                                                                                                                                                       | ENWDATA will be active (low) enabling S-bus data into the B inputs of the T-register multiplexer and to the memory.                                                                                                                                                                                               |  |  |  |  |  |

| TST and P4NF signals from CPU both active (low)                                                                                                                                                       | Selects the B input of the T-register multiplexer, sending the S-bus data to the parity generators and the A inputs of the T-register multiplexer.                                                                                                                                                                |  |  |  |  |  |

| TST active (low) and P4NF inactive (high)                                                                                                                                                             | Selects the A inputs of the T-register, latching the S-bus date. This stores the S-bus data in the T-register.                                                                                                                                                                                                    |  |  |  |  |  |

| Write signal from CPU active (low) and the address supplied to memory is not located in a protected area of memory or, if it is, this cycle is under the control of the dual-channel port controller. | The Write FF is set.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Write FF set.                                                                                                                                                                                         | <ol> <li>Transmission of data from the S-bus to the T-register and<br/>memory is inhibited (ENWDATA goes high) (gate U62C).</li> </ol>                                                                                                                                                                            |  |  |  |  |  |

|                                                                                                                                                                                                       | <ol><li>The memory gates are opened to enable passage of data from<br/>the T-register to memory.</li></ol>                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                                                                                                                       | <ol><li>Transmission of the parity bit to memory is enabled (gate<br/>U53A).</li></ol>                                                                                                                                                                                                                            |  |  |  |  |  |

|                                                                                                                                                                                                       | <ol> <li>The R/W Delay FF is set, resetting the MSRDY FF. This de-<br/>activates the MSRDY signal to the CPU.</li> </ol>                                                                                                                                                                                          |  |  |  |  |  |

|                                                                                                                                                                                                       | 5. The $\overline{\text{CS}}$ signal to the memory IC's is activated (gate U73A).                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                                                                                                                                                                                       | 6. The R/W RR and R/W signals to memory became low (gates U72A and B).                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                                                                                                                                                                                       | 7. The low condition of the R/W RR signal disables the bus drivers<br>on the memory PCA, inhibiting transmission of data from<br>memory to the T-register, parity circuits, and S-bus gates (gate<br>U171C on memory PCA). Also, writing into the memory IC's is<br>selected and reading out of them is disabled. |  |  |  |  |  |

Table 5. Write Cycle Events (continued)

| CAUSE                                                  | EVENT                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W Delay FF set and PON signal from power             | 1. The Clock FF is set (U83A and U84D).                                                                                                                                                                                                                                                                                                                                                                                                         |

| supply is active (high)                                | <ol><li>The delay line is pulsed, initiating its sequence of pulses<br/>delayed by fixed time intervals (gate U94A).</li></ol>                                                                                                                                                                                                                                                                                                                  |

| Clock FF set.                                          | 1. The $\overline{\text{CLK}}$ signal to all memory PCA's becomes active (low).                                                                                                                                                                                                                                                                                                                                                                 |

|                                                        | <ol><li>The PCA and row decoding logic enables the CLK signal (high)<br/>to only the selected row of memory IC's.</li></ol>                                                                                                                                                                                                                                                                                                                     |

|                                                        | 3. With the $\overline{\text{CS}}$ and CLK signals active, the selected memory ICs are enabled for reading or writing. Writing is selected by the low condition of the R/W RR or R/W WR signal (whichever is jumpered on the memory PCA, to pin 12 of the memory ICs). The address is already supplied to the memory PCA's through the M-register input gates on the controller PCA. Whatever is in the T-register will be written into memory. |

| 25 pulse, from delay line, active (low) (pin U85-1)    | The M-register stores the address supplied to it through the M-register input gates and supplies it steadily to the memory.                                                                                                                                                                                                                                                                                                                     |

| 75 pulse, from delay line, active (low) (pin<br>U85-2) | <ol> <li>The R/W Delay FF is reset ending the input pulse to the delay<br/>line.</li> </ol>                                                                                                                                                                                                                                                                                                                                                     |

|                                                        | 2. The MSRDY FF is enabled for reset by the next $\overline{275}$ pulse from the delay line.                                                                                                                                                                                                                                                                                                                                                    |

| 75 pulse, from delay line, active (low) (pin<br>U85-3) | <ol> <li>The M-Register Control FF is reset. This closes the M-register<br/>input gates so that the address is no longer supplied from the<br/>CPU to the M-register (gate U62B). However, the address is<br/>already stored in the M-register.</li> </ol>                                                                                                                                                                                      |

| 275 pulse, from delay line, active (low) (pin U85-7).  | The MSRDY FF is set, activating the MSRDY signal to the CPU. This indicates to the CPU the memory is ready for another cycle.                                                                                                                                                                                                                                                                                                                   |

| 350 pulse, from delay line, active (low) (pin          | 1. The M-Register Control FF is set.                                                                                                                                                                                                                                                                                                                                                                                                            |

| U85-6)                                                 | <ol> <li>The M-register stops supplying the address to memory and becomes receptive to any new address supplied to it through the M-register input gates. However, the M-register input gates aren't open yet and won't be until all the memory and controller circuits are returned to the idle state (when the 350 pulse ends) (gate U62B).</li> </ol>                                                                                        |

|                                                        | 3. The Clock FF is reset. This stops the memory from writing.                                                                                                                                                                                                                                                                                                                                                                                   |

| 400 pulse, from delay line, becomes active (low)       | 1. The Write FF is reset.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| (pin U85-8)                                            | <ol> <li>The S-bus gates open for passage of data from the S-bus to<br/>the memory and the T-register (ENWDATA signal low at<br/>pin U54-12).</li> </ol>                                                                                                                                                                                                                                                                                        |

|                                                        | <ol> <li>The memory gates close, inhibiting passage of data from the<br/>T-register to memory (gate U62C). Also, the parity bit is<br/>blocked from passing to the memory at gate U53A.</li> </ol>                                                                                                                                                                                                                                              |

Table 5. Write Cycle Events (continued)

| CAUSE                       | EVENT                                                                                                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (cont) 400 pulse            | <ol> <li>The R/W WR signal to the memory PCA's becomes high. Also,<br/>the R/W RR signal becomes high provided no refresh cycle is<br/>starting.</li> </ol> |

| 350 pulse becomes inactive. | The M-register input gates open to pass any new address to memory and the M-register. This completes the write cycle.                                       |

The write cycle begins when the CPU activates  $\overline{\text{TST}}$ . At CPU time period P4, the S-bus data is allowed to pass through the T-register multiplexer to the A inputs of the T-register multiplexer and to the parity circuits. At the end of P4, the T-register stores the S-bus data.

The address into which data is to be written, is present at the memory IC's as soon as the CPU supplies it to the M-register input gates. These gates are always open (except during refresh cycles) to enable address information to be supplied to memory and the M-register between cycles.

The Write signal from the CPU sets the Write FF if the address is not in the protected area of memory (MPV not active (high)) or if this write cycle is requested by the dual-channel port controller (DCPC can access any address in memory). If the address is in the protected area of memory and this is not a DCPC write cycle, the Write FF will not be set (gate U66B) and no memory cycle will occur.

Shortly after the Write FF is set, the MSRDY signal to the CPU is deactivated and writing into memory is enabled by signals from the controller (R/W and  $\overline{CS}$ ).

The M-register then stores the address supplied to it through the M-register input gates and applies the address steadily to the memory.

The S-bus gates close and the memory gates open to supply the contents of the T-register and the parity bit to the memory through the bus driver/receivers on the memory PCA's. (These bus driver/receivers are always enabled to receive data).

The clock FF is set, activating the  $\overline{\text{CLK}}$  signal to the memory PCA's. The module and row decoding on the memory PCA's will enable the CLK signal to only one row of memory IC's. Writing begins as soon as the CLK signal reaches the memory ICs. These conditions remain stable for enough time to ensure reliable writing of the data and parity bit into the proper address in memory.

After enough time has elapsed for read-in of the data into memory, the MSRDY signal to the CPU becomes active to notify the CPU that the memory system is ready for another cycle. This signal then remains active until shortly after the next cycle is started. After another time period, the M-register stops supplying the address to memory and becomes receptive to a new address. However, the M-register input gates don't open to allow passage of a new address from the CPU to the memory and M-register until after the controller and memory circuits are recovered from the present cycle.

At approximately the time the M-register stops supplying the address to the memory, writing into memory is inhibited by deactivation of several required signals from the controller. Then the Write FF is reset and the S-bus gates are enabled to pass data from the S-bus to the memory and T-register again. They remain

in this condition until the next cycle. The M-register input gates are opened later to enable any address supplied by the CPU, for the next cycle, to be applied to me mory and the M-register. This completes the write cycle.

#### 14. Refresh Cycle

Events occurring during a refresh cycle are described briefly in table 6.

Table 6. Refresh Cycle Events

| CAUSE                                                                                                                                                                                                                                            | EVENT                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PON active (high) and Pulse (negative) output<br>from refresh oscillator (gate U91-pin 7) and<br>Strobe A FF reset (gate U87-pin 8 high).                                                                                                        | Strobe B FF is set (gate U87-pin 3 low), activating the strobe B input to the refresh decoder to enable its $\Omega_B$ output (pin 9).                                                                                                                                                                                                                                                                   |  |  |  |

| Occurrence of CPU time period P5 of the                                                                                                                                                                                                          | 1. Strobe A FF set (gate U87-pin 11 high).                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| next T4 time period following enabling of                                                                                                                                                                                                        | 2. Refresh FF released from clamped reset condition.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| refresh decoder Q <sub>B</sub> output (gate U77-pin 9)                                                                                                                                                                                           | 3. REFRESH signal to CPU becomes active (low).                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                                                                                                                                                                                                                  | 4. Strobe A input to the refresh decoder becomes low, enabling the $\Omega_A$ (pin 7) output of the refresh decoder.                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                                                                                                  | <ol> <li>Strobe B FF is reset (gate U87-pin 8 low) making the Strobe E input to the refresh decoder high and disabling the QB output (pin 9) of the refresh decoder. (The Strobe B FF remains reset until the next refresh cycle — approximately 32 microseconds later).</li> </ol>                                                                                                                      |  |  |  |

| DMAREAD signal not active and occurrence of next T6 time period.                                                                                                                                                                                 | Refresh decoder Q <sub>A</sub> output (gate U77-pin 7) becomes high.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| $\overline{\text{DMAREAD}}$ signal not active, occurrence of time period P5 of T6 and refresh decoder $Q_A$ output high. (When the $\overline{\text{DMAREAD}}$ signal is inactive, the refresh cycle is performed during time period T2 and T3). | <ol> <li>MSRDY FF set, deactivating the MSRDY signal to the CPU.</li> <li>Refresh Transmit FF set, activating (low) the MREF signal to the memory, disabling the M-register input gates, disabling M-register IC U21, resetting (outputs low) M-register IC's U22 and U23, activating the R/W RR signal to memory, disabling the CS signal to memory and enabling the refresh address driver.</li> </ol> |  |  |  |

| DMAREAD signal active, and occurrence of next time period T3.                                                                                                                                                                                    | Refresh decoder $\Omega_{	extsf{A}}$ output (gate U77-pin 7) becomes high.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| $\overline{\text{DMAREAD}}$ signal active, and occurrence of P5 of T3 and refresh decoder $\Omega_A$ output high. (When the $\overline{\text{DMAREAD}}$ signal is active, the refresh cycle is performed during time period T4 and T5,)          | <ol> <li>MSRDY FF set, deactivating the MSRDY signal to the CPU.</li> <li>Refresh Transmit FF set, activating (low) the MREF signal to the memory, disabling the M-register input gates, disabling M-register IC U21, resetting (outputs low) M-register IC's U22 and U23, activating the R/W RR signal to memory, disabling the CS signal to memory and enabling the refresh address driver.</li> </ol> |  |  |  |

Table 6. Refresh Cycle Events (continued)

| CAUSE                                                                                                                                                 | EVENT                                                                                                                                                                                                                                                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Refresh decoder $\Omega_A$ output high (DMAREAD active and T3 or $\overline{DMAREAD}$ not active and T6) and occurrence of the end of time period P5. | Refresh FF is set, resetting the Strobe A FF (gate U87-pin 8 high), disabling the $\Omega_A$ output of the refresh decoder, and deactivating the $\overline{\text{REFRESH}}$ signal to the CPU.                                                              |  |  |  |  |

| Strobe A FF is reset.                                                                                                                                 | Refresh FF is reset and clamped reset. (The Strobe A FF is not set again until the next refresh cycle — approximately 32 microseconds later).                                                                                                                |  |  |  |  |

| PON signal from power supply is active (high) and refresh FF set.                                                                                     | Refresh Delay FF set (gate U84-pin 3 high)                                                                                                                                                                                                                   |  |  |  |  |

| PON signal from power supply inactive (low and occurrence of a pulse (positive) from the refresh oscillator (gate U91-pin 6).                         | Refresh Delay FF set (gate U84-pin 3 high).                                                                                                                                                                                                                  |  |  |  |  |

| Refresh Delay FF set.                                                                                                                                 | <ol> <li>Delay line pulsed, initiating its sequence of output signals at<br/>fixed time intervals from the time it was pulsed.</li> </ol>                                                                                                                    |  |  |  |  |

|                                                                                                                                                       | <ol> <li>Clock FF set, activating (low) the CLK signal to memory.         The selected row of memory addresses are refreshed from this time until the Clock FF is reset later in the cycle.     </li> </ol>                                                  |  |  |  |  |

| Clock FF set.                                                                                                                                         | The PON signal, from the power supply, is disabled from affecting operation of the memory controller until the memory IC's are disabled by deactivation of the CLK signal (when the Clock FF is reset).                                                      |  |  |  |  |

| 25 signal from delay line                                                                                                                             | (The effect of the $\overline{25}$ signal on the M-register has already been performed by the active $\overline{IREF}$ signal which became active when the Refresh Transmit FF was set.)                                                                     |  |  |  |  |