# **OPERATING AND SERVICE MANUAL**

# 12587B

ASYNCHRONOUS DATA SET INTERFACE KIT (FOR 2100, 2114, 2115, AND 2116 COMPUTERS)

Card Assembly 12587-60004, Rev. 1101

Note

Retain this manual with the applicable computer system documentation.

Printed: JUL 1973

Table of Contents

# **TABLE OF CONTENTS**

| Secti | on                                   | Page        | Section       | n                 |                                    | Page   |

|-------|--------------------------------------|-------------|---------------|-------------------|------------------------------------|--------|

| I     | GENERAL INFORMATION                  |             | 4             | <b>1-</b> 8.      | Data Reception                     | . 4-1  |

| _     | 1-1. Introduction                    | 1-1         |               | <del>1</del> -10. | Line Status Checks                 | . 4-1  |

|       | 1-3. Description                     |             |               | <del>1</del> -12. | Detailed Circuit Description       |        |

|       | 1-5. Identification                  |             | 4             | 1-14.             | Input/Output System Controls       |        |

|       | 1-7. Specifications                  |             | 4             | <del>1</del> -18. | Control Word Register              |        |

|       | Tr. Specifications                   |             |               | <b>1-20</b> .     | 8-Bit Shift Register               |        |

| II    | INSTALLATION                         |             |               | 1-25.             | Bit Register/Counter               |        |

|       | 2-1. Introduction                    | 2-1         |               | 4-31.             | Clock and Synchronize Circuit      |        |

|       | 2-3. Unpacking and Inspection        |             |               | 1-38.             | Control Logic                      |        |

|       | 2-5. Preparation for Use             |             |               | 1-44.             | Line Status                        | -      |

|       | 2-9. Installation                    |             |               |                   |                                    |        |

|       | 2-11. Reshipment                     |             |               |                   |                                    |        |

|       |                                      |             | V I           | MAIN              | ΓENANCE                            |        |

| III   | PROGRAMMING                          |             |               | 5-1.              | Introduction                       | . 5-1  |

|       | 3-1. Introduction                    | 3-1         |               | 5-3.              | Preventive Maintenance             |        |

|       | 3-4. Control Word Format             |             |               | 5-5.              | Diagnostics                        |        |

|       | 3-7. Data Word Format                |             |               | 5-7.              | Troubleshooting                    | . 5-1  |

|       | 3-9. Interface Card Operation        |             |               | 5-9.              | Test Program                       |        |

|       | 3-11. Timing                         |             |               | 5-11.             | Timing Diagrams                    |        |

|       | 3-13. Sample Program                 |             |               | 5-13.             | Logic Equations                    |        |

| IV    | THEORY OF OPERATION                  |             |               |                   |                                    |        |

|       | 4-1. Introduction                    | 4-1         | VI I          | REPLA             | ACEABLE PARTS                      |        |

|       | 4-3. Overall Functional Description. | 4-1         | (             | 3-1.              | Introduction                       | . 6-1  |

|       | 4-6. Data Transmission               | 4-1         | (             | 6-4.              | Ordering Information               | . 6-1  |

|       | LIS                                  | T OF ILLU   | JSTRA         | TIO               | NS                                 |        |

| Figu  | re Title                             | Page        | Figure        |                   | Title                              | Page   |

| 1-1.  | HP 12587B Asynchronous Data          |             | 5-7.          | Tim               | ning Diagram for the Transmit Mode |        |

|       | Set Interface Kit                    |             |               | W                 | ith the Bit Register/Counter       |        |

| 2-1.  | Preset Code Jumpering Instructions   |             |               | at                | the Count of "2"                   | . 5-6  |

| 3-1.  | Transmit Control Word                |             | 5-8.          | Tim               | ing Diagram for Transmitting Data  | . 5-7  |

| 3-2.  | Receive Control Word                 | 3-3         | 5-9.          | Tim               | ing Diagram for the Justify Cycle  |        |

| 4-1.  | Interface Card Functional            |             |               |                   | ith the Bit Register/Counter       |        |

|       | Block Diagram                        | $\dots 4-2$ |               |                   | the Count of "0"                   | . 5-7  |

| 4-2.  | Typical Control Word and Data        |             | 5-10.         |                   | ing Diagram for a Control          |        |

|       | Word Formats                         | 4-4         | <b>J</b> -10. |                   | ord to Receive Data                | . 5-8  |

| 4-3.  | Typical Serial Character Bit Stream  | 4-4         | 5-11.         |                   |                                    |        |

| 4-4.  | Flowchart of Interface Card          |             |               |                   | ing Diagram for Receiving Data     | . 5-9  |

|       | Operating Sequence                   | $\dots 4-7$ | 5-12.         |                   | ing Diagram for the Receive Mode   |        |

| 5-1.  | Test Connector Wiring Diagram        |             |               |                   | ith the Bit Register/Counter       |        |

| 5-2.  | Test Program Waveform                | $\dots 5-2$ |               |                   | the Count of "1"                   | . 5-9  |

| 5-3.  | Timing Diagram for Transmission      |             | 5-13.         |                   | ing Diagram for the Transmit Mode  |        |

|       | of a Character Bit Stream            | $\dots 5-4$ |               |                   | ith the Bit Register/Counter       |        |

| 5-4.  | Timing Diagram for Reception of      |             | _             |                   | the Count of "1"                   | . 5-10 |

|       | a Character Bit Stream               | 5-4         | 5-14.         |                   | egrated Circuit Diagrams           |        |

| 5-5.  | Timing Diagram for a Control Word    |             |               |                   | nd Characteristics                 | . 5-14 |

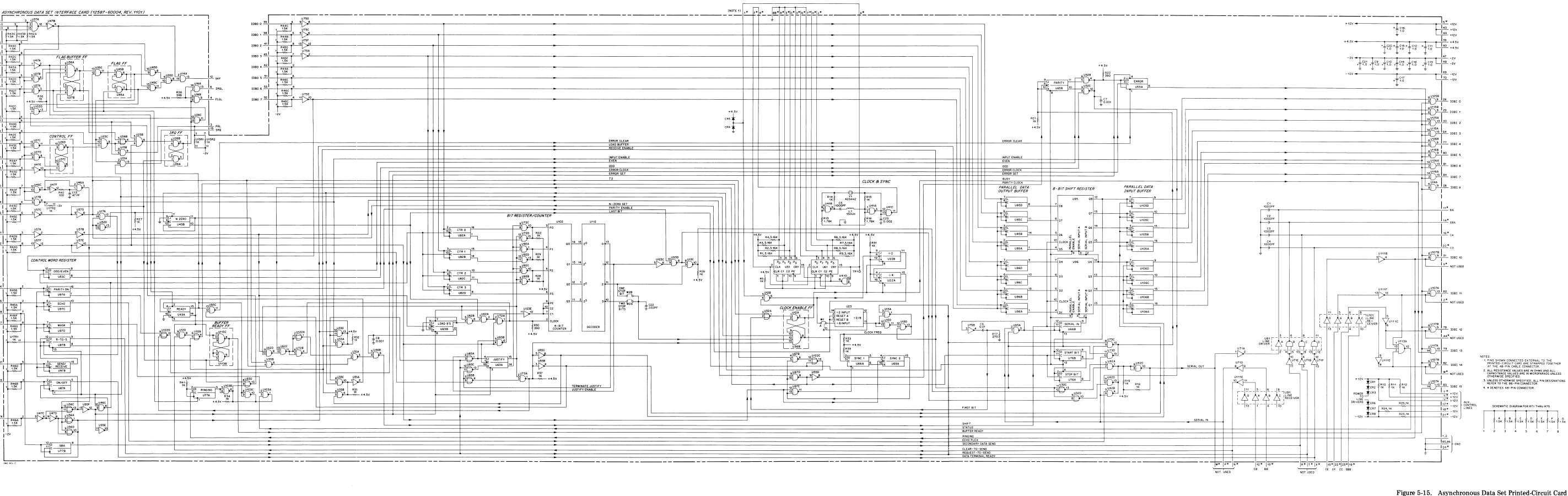

|       | to Transmit Data                     | 5-5         | 5-15.         |                   | nchronous Data Set Printed-Circuit |        |

| 5-6.  | Timing Diagram for an Initial        |             |               |                   | ard Logic and Parts                |        |

|       | Power-On Sequence                    | $\dots 5-6$ |               | L                 | ocation Diagrams                   | . 5-17 |

List of Tables 12587B

# **LIST OF TABLES**

| Table | Title                             | Page | Table | Title                                  | Page  |

|-------|-----------------------------------|------|-------|----------------------------------------|-------|

| 1-1.  | Interface Kit Specifications      | 1-2  | 5-1.  | Test Connector Signal Information      | . 5-2 |

| 2-1.  | Jumper Connections for Common Bit |      | 5-2.  | Interconnecting Cable Pin Index        |       |

|       | Transfer Rates                    | 2-2  | 5-3.  | Test Program                           | . 5-3 |

| 3-1.  | Control Word Bit Functions        |      | 5-4.  | Logic Equations                        |       |

| 3-2.  | Two's Complement of Bits          |      | 5-5.  | Interface Card Replaceable Parts       |       |

|       | Per Character                     | 3-2  | 6-1.  | Numerical Listing of Replaceable Parts |       |

| 3-3.  | Data Word Bit Functions           | 3-2  | 6-2.  | Reference Designations                 |       |

| 3-4.  | Typical Program                   | 3-4  |       | and Abbreviations                      | . 6-3 |

| 4-1.  | Control Word Register Functions   |      | 6-3.  | Code List of Manufacturers             |       |

12587B Section I

# **SECTION I**

# **GENERAL INFORMATION**

# 1-1. INTRODUCTION.

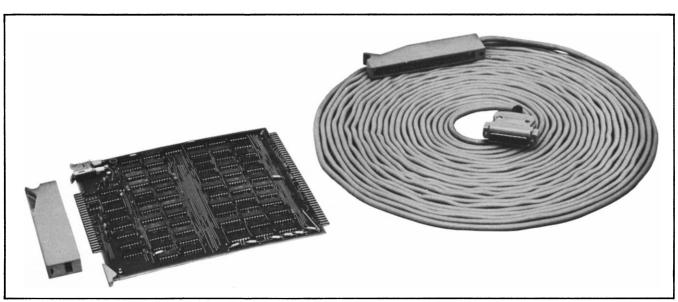

1-2. This operating and service manual covers general information, installation, programming, theory of operation, maintenance, and replaceable parts for the Hewlett-Packard 12587B Asynchronous Data Set Interface Kit. (See figure 1-1.)

#### 1-3. DESCRIPTION.

1-4. The HP 12587B Asynchronous Data Set Interface Kit includes a single plug-in printed-circuit card that allows Hewlett-Packard 2100, 2114, 2115, and 2116 Computers to input or output control signals and data signals via commoncarrier data transmission equipment. The control signals conform to signals that are defined by Electronic Industries Association Standard RS-232-B. The control signals ensure a communication link between two data sets and prepare a Bell Telephone System 103 or 202 Data Set, or equivalent, for data transmission or reception. In the transmit mode, the interface kit converts parallel data output from a computer to serial data that is compatible with the data set. In receive mode, the interface kit converts serial data output from a data set to parallel data for computer input. The interface kit adds a parity bit when required and start and stop bits to the serial data during transmission and removes start and stop bits from the serial data while receiving. If selected, a parity check may be performed by the interface kit. The interface kit includes the following items:

- a. Asynchronous data set card (part no. 12587-60004).

- b. Interconnecting cable assembly, 50 feet (part no. 12587-60006).

- c. Test connector (part no. 12587-60009).

- d. Operating and service manual (part no. 12587-90006).

#### 1-5. IDENTIFICATION.

1-6. Printed-circuit card revisions are identified by a letter, a date code, and a division code stamped on the board (e.g., A-1005-22). The letter code identifies the version of the etched trace pattern on the unloaded board. The date code (four middle digits) refers to the electrical characteristics of the loaded board. The division code (last two digits) identifies the Hewlett-Packard division that manufactured the board. If the date code stamped on the printed-circuit board does not agree with the date code shown on the title page of this manual, there are differences between your board and the board described in this manual. These differences are described in manual supplements available at the nearest HP Sales and Service Office.

# 1-7. SPECIFICATIONS.

1-8. Specifications for the interface kit are listed in table 1-1.

2156-2

Figure 1-1. HP 12587B Asynchronous Data Set Interface Kit

Table 1-1. Interface Kit Specifications

| CHARACTERISTICS                      | SPECIFICATIONS                                                                                                                                                        |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function:                            | Asynchronous device operating in the half duplex mode that converts parallel data to serial data for transmission and converts received serial data to parallel data. |  |

| Compatibility:                       | Used with Bell Telephone System 103 or 202 type data sets, or equivalent.                                                                                             |  |

| Interface Requirements:              | Conforms to Electronic Industries Association Standard RS-232-B.                                                                                                      |  |

| Data Transfer Rate to/from Data Set: | Adjustable with jumpers to discrete rates between approximately 26 and 3,110 bits per second.                                                                         |  |

| Character Size:                      |                                                                                                                                                                       |  |

| (Input/Output of Computer)           | 1 to 8 bits                                                                                                                                                           |  |

| Power Consumption from Computer:     |                                                                                                                                                                       |  |

| +4.5-volt supply:                    | 1.6A                                                                                                                                                                  |  |

| +12-volt supply:                     | 80 mA                                                                                                                                                                 |  |

| -2-volt supply:                      | 70 mA                                                                                                                                                                 |  |

| -12-volt supply:                     | 45 mA                                                                                                                                                                 |  |

12587B Section II

# SECTION II INSTALLATION

# 2-1. INTRODUCTION.

2-2. This section contains information on unpacking, inspection, preparation for use, installation, and reshipment of the interface kit.

#### 2-3. UNPACKING AND INSPECTION.

2-4. If the shipping carton is damaged upon receipt, request that the carrier's agent be present when the kit is unpacked. Inspect the kit for damage (cracks, broken parts, etc.). If the kit is damaged and fails to meet specifications, notify the carrier and the nearest HP Sales and Service Office immediately. (Sales and Service Offices are listed at the back of this manual.) Retain the shipping container and the packing material for the carrier's inspection. The HP Sales and Service Office will arrange for the repair or replacement of the damaged kit without waiting for any claims against the carrier to be settled.

#### 2-5. PREPARATION FOR USE.

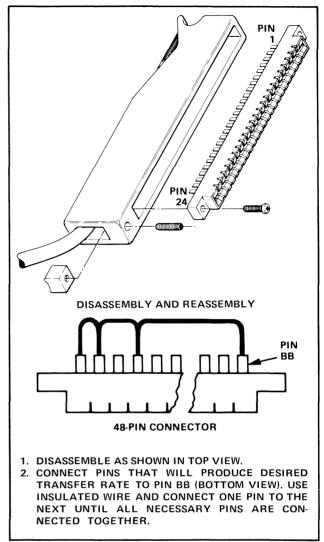

- 2-6. The interface kit is prepared at the factory to provide a data transfer rate of 1200 bits per second. If the bit transfer rate of the terminal used is not 1200 bits per second, the transfer rate of the interface kit must be changed. This is done by changing the position of jumper W1 on the circuit board and/or changing jumpers on the cable connector that connects to the circuit board. The jumpers on the cable connector are used to provide an 8-bit binary number to which the programmable scaler on the circuit card is preset. Pins J, H, 7, 6, D, C, 3, and B correspond to bit positions  $2^7$  through  $2^0$  respectively.

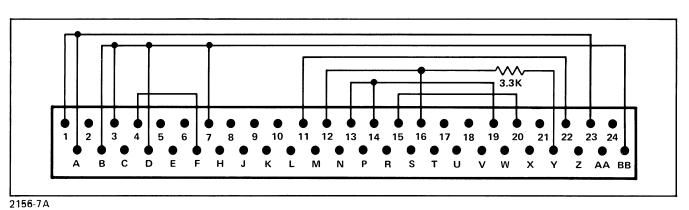

- 2-7. Some common bit transfer rates and associated preset codes are given in table 2-1. If the preset code for a selected transfer rate contains a "0" in a given column, jumper the pin shown at the bottom of that column to pin BB (ground). If a given column contains a "1", do not jumper the listed pin to ground. For example, if a bit transfer rate of 600 bits per second is desired, locate 600 in the TRANSFER RATE column of table 2-1. The table shows that jumper W1 on the circuit card must be placed in position A and that the programmable scaler must be preset to 10101000 (168 decimal). The  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^4$ , and  $2^6$  columns contain "0's" so the corresponding pins, B, 3, C, 6, and H respectively, must be connected to pin BB (ground). Pin jumpering is done on the 48-pin cable connector as shown in figure 2-1.

- 2-8. If the required bit transfer rate is not given in table 2-1, the preset code for the required rate can be found by using the following formula:

PRESET CODE (rounded off to the nearest decimal integer) =

$$256 - \frac{423,000}{X \cdot R}$$

when: 256 is the count capacity of the programmable scaler:

423,000 is the oscillator frequency in pulses per second:

X is 8 if jumper W1 is in position A, or 64 if W1 is in position B. Position A allows an approximate range of discrete transfer rates of 207 to 3,110 bits per second; position B allows an approximate range of discrete transfer rates of 26 to 388 bits per second;

R is required transfer rate.

#### Note

For proper operation, the transfer rate of the interface kit must be within  $\pm 0.5$  percent of the transfer rate of the terminal used and at least one of the four most significant bits (pins J, H, 7 and 6) must be a "0".

Convert the decimal result to binary form, and jumper each pin that has a "0" in its corresponding bit position to pin BB. Use table 2-1 to determine which pin corresponds to each bit position.

Example: To set the interface kit transfer rate to 300 bits per second (300 bits per second is shaded in table 2-1), place jumper W1 in position B and solve the equation as follows:

PRESET CODE (in decimal) =

$$256 - \frac{423,000}{64 \cdot 300}$$

=  $256 - 22,080$  =  $234$  =  $11101010$

Bit positions  $2^0$ ,  $2^2$ , and  $2^4$  contain "0's". Table 2-1 shows that pins B, C, and 6 on the 48-pin cable connector correspond to these three bit positions, so pins B, C, and 6 must be jumpered to pin BB to provide a 300 bit-per-second transfer rate.

#### 2-9. INSTALLATION.

2-10. After the bit transfer rate of the interface kit has been set to the correct value for the terminal used, install the kit as follows:

Section II 12587B

| Table 2-1. | Jumper Connections for Common Bit |

|------------|-----------------------------------|

|            | Transfer Rates                    |

| TRANSFER         |                | *PRESET CODE |                       |                       |                       |                       |                       |                       |                       |

|------------------|----------------|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| RATE<br>BITS/SEC | W1<br>POSITION | 27           | <b>2</b> <sup>6</sup> | <b>2</b> <sup>5</sup> | <b>2</b> <sup>4</sup> | <b>2</b> <sup>3</sup> | <b>2</b> <sup>2</sup> | <b>2</b> <sup>1</sup> | <b>2</b> <sup>0</sup> |

| 45               | В              | 0            | 1                     | 1                     | 0                     | 1                     | 1                     | 0                     | 1                     |

| 50               | В              | 0            | 1                     | 1                     | 1                     | 1                     | 1                     | 0                     | 0                     |

| 75               | В              | 1            | 0                     | 1                     | 1                     | 1                     | 1                     | 1                     | 1                     |

| 110              | В              | 1            | 1                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     |

| 134.5            | В              | 1            | 1                     | 0                     | 0                     | 1                     | 1                     | 0                     | 1                     |

| 150              | В              | 1            | 1                     | 0                     | 1                     | 0                     | 1                     | 0                     | 0                     |

| 165              | В              | 1            | 1                     | 0                     | 1                     | 1                     | 0                     | 0                     | 0                     |

| 200              | В              | 1            | 1                     | 0                     | 1                     | 1                     | 1                     | 1                     | 1                     |

| 220              | В              | 1            | 1                     | 1                     | 0                     | 0                     | 0                     | 1                     | 0                     |

| 300              | В              | 1            | 1                     | 1                     | 0                     | 1                     | 0                     | 1                     | 0                     |

| 330              | В              | 1            | 1                     | 1                     | 0                     | 1                     | 1                     | 0                     | 0                     |

| 440              | А              | 1            | 0                     | 0                     | 0                     | -1                    | 0                     | 0                     | 0                     |

| 600              | А              | 1            | 0                     | 1                     | 0                     | 1                     | 0                     | 0                     | 0                     |

| 880              | А              | 1            | 1                     | 0                     | 0                     | 0                     | 1                     | 0                     | 0                     |

| 900              | А              | 1            | 1                     | 0                     | 0                     | 0                     | 1                     | 0                     | 1                     |

| 1050             | Α              | 1            | 1                     | 0                     | 0                     | 1                     | 1                     | 1                     | 0                     |

| 1200             | А              | 1            | 1                     | 0                     | 1                     | 0                     | 1                     | 0                     | 0                     |

| 1760             | Α              | 1            | 1                     | 1                     | 0                     | 0                     | 0                     | 1                     | 0                     |

| 2400             | Α              | 1            | 1                     | 1                     | 0                     | 1                     | 0                     | 1                     | 0                     |

| 48-Pin Coi       | nnector Pins   | J            | Н                     | 7                     | 6                     | D                     | С                     | 3                     | В                     |

<sup>\*</sup> If selected code has a "0" in a given column, connect pin listed at bottom of that column to pin BB. (Pins 6, C, and B in shaded example above). For proper operation, at least one of the four most significant bits (pins J, H, 7, and 6) must be a "0".

If code has a "1" in a given column, ensure that a jumper does not connect pin at bottom of column to pin BB,

Figure 2-1 shows how to connect jumpers.

# a. Halt computer and turn computer power off.

- b. Gain access to computer card cage and insert the interface card in an unused I/O slot. Make sure that every higher priority slot has either an interface card or a priority jumper card installed.

- c. Connect the 48-pin connector of the kit interconnecting cable to the interface card. Pass other end of cable out rear of computer.

- d. Close computer door or replace panel and connect the interconnecting cable 25-pin connector to rear of data set.

- e. Verify proper operation of the interface kit by performing the diagnostic test using the Send/Receive Interface Test diagnostic tape. Refer to the Diagnostic Program Procedure (part no. 12587-90005 for the 2100 Computer or part no. 12587-90002 for the 2114, 2115, and 2116 Computers) in the Manual of Diagnostics for operating procedures.

2156-3

Figure 2-1. Preset Code Jumpering Instructions

#### 2-11. RESHIPMENT.

- 2-12. If an item of the kit is to be shipped to Hewlett-Packard for service or repair, attach a tag to the item identifying the owner and indicating the service or repair to be accomplished. Include the accessory number of the kit.

- 2-13. Package the item in the original factory packaging material, if available. If the original material is not available, standard factory packaging material can be obtained from a local Hewlett-Packard Sales and Service Office.

- 2-14. If standard factory packaging material is not used, wrap the item in Air Cap TH-240 cushioning (or equivalent) manufactured by Sealed Air Corp., Hawthorne, N.J., and place in a corrugated carton (200 pound test material). Seal the shipping carton securely and mark it "FRAGILE" to assure careful handling.

# Note

In any correspondence, identify the kit by number. Refer any questions to the nearest Hewlett-Packard Sales and Service Office.

# SECTION III PROGRAMMING

# 3-1. INTRODUCTION.

- 3-2. This section contains assembly language programming information for the interface kit. A sample assembly-language program, with explanatory comments, is included.

- 3-3. For information concerning software systems used with the computer, software interfacing, and operating procedures, refer to the applicable software manuals provided with the computer documentation.

# 3-4. CONTROL WORD FORMAT.

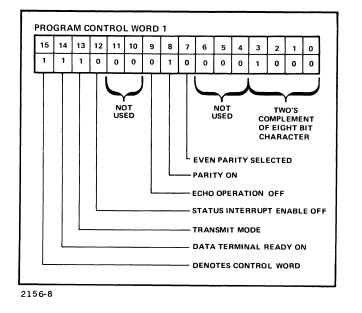

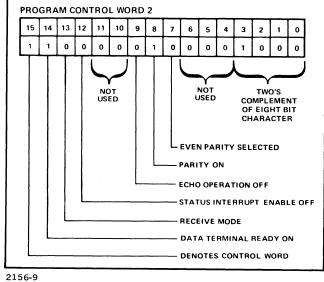

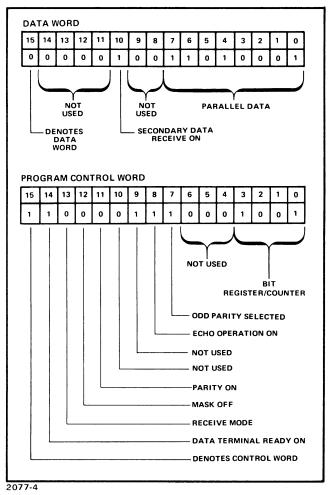

- 3-5. The computer must output control words to set the interface card to the desired operating parameters. The control word, for example, sets the interface card to the receive or transmit mode, selects parity check or no parity check, etc. Table 3-1 lists the function of each bit in a control word. Use the information in table 3-1 to establish control words to effect desired program operation.

- 3-6. Bits 0 through 3 of each control word that specifies a transmit or receive operation must contain the two's complement of the number of bits in each character. Table 3-2 shows the condition of bits 0 through 3 for character lengths of one to nine bits.

#### 3-7. DATA WORD FORMAT.

3-8. Bits 0 through 7 of a data word are reserved for the actual data character. Bits 8 through 15 of a data word provide control and status check functions. Functions of bits 8 through 15 in a computer output data word are different than the functions of the same bits in an input data word. Table 3-3 lists functions of bit 0 through bit 15 for both input and output data words.

# 3-9. INTERFACE CARD OPERATION.

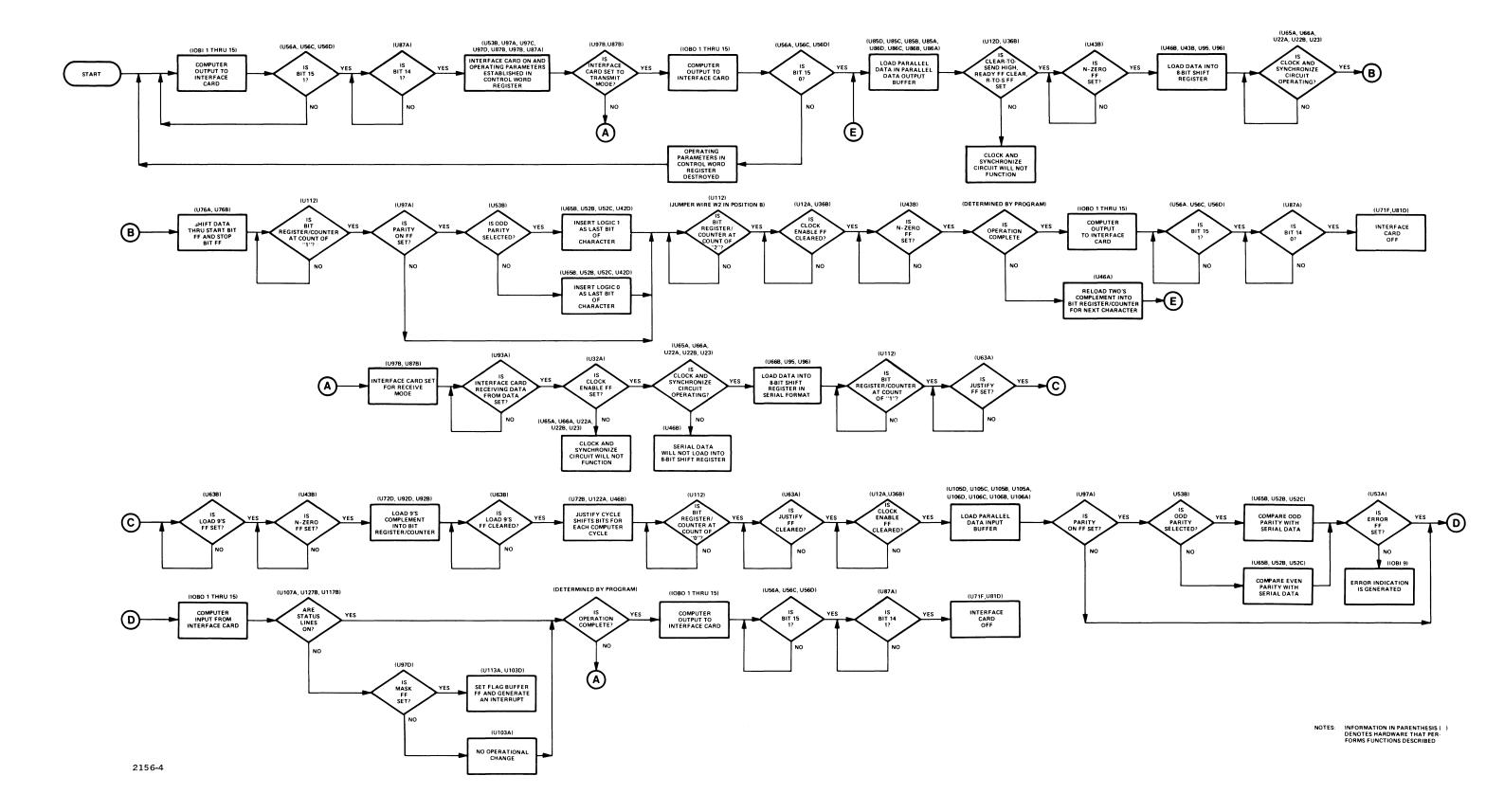

3-10. Section IV of this manual contains theory of operation for the interface card. A flowchart, figure 4-4, is provided to show the sequence of operations of the interface card. Use the flowchart and the functional descriptions in section IV as an aid to programming.

#### 3-11. TIMING.

3-12. Timing diagrams that are useful for programming data transfers are provided in section V of this manual.

Diagrams that show interface card operation in response to a control word, to reception of data, and to transmission of data are included.

Table 3-1. Control Word Bit Functions

| BIT<br>POSITION | BIT<br>VALUE | BIT FUNCTION                                                                                      |  |

|-----------------|--------------|---------------------------------------------------------------------------------------------------|--|

| 0 thru 3        | -            | Two's complement of bits per character, (Refer to table 3-2.)                                     |  |

| 4,5,6           |              | Not used.                                                                                         |  |

| 7               | 0            | Selects even parity when parity is used.                                                          |  |

|                 | 1            | Selects odd parity when parity is used.                                                           |  |

| 8               | 0            | Parity check and generation is not used.                                                          |  |

|                 | 1            | Parity check and generation is used.                                                              |  |

| 9               | 0            | Echo operation not used.                                                                          |  |

|                 | 1            | Echo operation used. (Received data retransmitted to originator.)                                 |  |

| 10              | 0            | Not used,                                                                                         |  |

|                 | 1            | Not used.                                                                                         |  |

| 11              | _            | Not used.                                                                                         |  |

| 12              | 0            | Loss of one of three line status checks (CF, CC, SBB) in input word does not cause a Flag signal. |  |

|                 | 1            | Loss of one of three line status checks (CF, CC, SBB) in input word causes a Flag signal.         |  |

| 13              | 0            | Sets the interface card to the receive mode.                                                      |  |

|                 | 1            | Sets the interface card to the transmit mode.                                                     |  |

| 14              | 0            | Turns off interface card by disabling<br>Data Terminal Ready Signal to the<br>data set.           |  |

|                 | 1            | Turns on interface card by enabling<br>Data Terminal Ready Signal to the<br>data set.             |  |

| 15              | 0            | Not used.                                                                                         |  |

|                 | 1            | Denotes a control word.                                                                           |  |

Table 3-2. Two's Complement of Bits Per Character

| BITS 0-3 OF CONTROL WORD<br>(BINARY) |       |       |       | BITS PER CHARACTER<br>(SEE NOTE) |

|--------------------------------------|-------|-------|-------|----------------------------------|

| BIT 3                                | BIT 2 | BIT 1 | BIT 0 |                                  |

| 1                                    | 1     | 1     | 1     | 1                                |

| 1                                    | 1     | 1     | 0     | 2                                |

| 1                                    | 1     | 0     | 1     | 3                                |

| 1                                    | 1     | 0     | 0     | 4                                |

| 1                                    | 0     | 1     | 1     | 5                                |

| 1                                    | 0     | 1     | 0     | 6                                |

| 1                                    | 0     | 0     | 1     | 7                                |

| 1                                    | 0     | 0     | 0     | 8                                |

| 0                                    | 1     | 1     | 1     | 9                                |

Note: The bits-per-character value includes one parity bit but does not include start or stop bits. The start and stop bits are generated (output) and deleted (input) by the interface card. If parity is not used, decrease the bits-per-character value by one and use the corresponding two's complement.

# 3-13. SAMPLE PROGRAM.

- 3-14. An example of a typical program using the interface kit is provided in table 3-4. The program is written for a Bell Telephone System 202 Data Set and accomplishes the following:

- a. Initializes the interface card.

- b. Uses the reverse channel capability of the 202 Data Set to indicate that the data set is prepared to receive data.

- c. Alternately sends and receives 10 8-bit characters.

- 3-15. The program includes operating instructions and comments that explain the instructions, and figures 3-1 and 3-2 show the function of each bit in the two control words used in the program.

Table 3-3. Data Word Bit Functions

| BIT<br>POSITION | BIT<br>VALUE | BIT FUNCTION IN<br>INPUT DATA WORD                                                                             | BIT FUNCTION IN<br>OUTPUT DATA WORD                           |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 0 thru 7        | _            | Received information (one character right justified).                                                          | Transmitted information (one character).                      |

| 8               | _            | Not used.                                                                                                      | Not used.                                                     |

| 9               | 0            | No errors detected (Error FF set).                                                                             | Not used.                                                     |

|                 | 1            | Parity error detected or the interface card was not serviced resulting in a lost character.                    | Not used.                                                     |

| 10              | 0            | Another data set is not attempting to establish a connection with data set associated with the interface card. | Disables Secondary<br>(Supervisory) Data<br>Send signal line. |

|                 | 1            | Data set is ringing (CE signal) indicating another data set is attempting to establish a connection.           | Enables Secondary<br>(Supervisory) Data<br>Send signal line.  |

| 11              | 0            | A distant data set carrier signal is not detected; therefore, the data set cannot receive data.                | Not used.                                                     |

|                 | 1            | The Carrier Detect (CF) signal of a distant data set is present and the data set can receive data.             | Not used.                                                     |

| 12              | 0            | The data set is not prepared to transmit or receive data.                                                      | Not used.                                                     |

|                 | 1            | A Data Set Ready (CC) signal indicates the data set is ready to transmit or receive data.                      | Not used.                                                     |

12587B Section III

Table 3-3. Data Word Bit Functions (Continued)

| BIT<br>POSITION | BIT<br>VALUE | BIT FUNCTION IN<br>INPUT DATA WORD                                                                                                                                                                          | BIT FUNCTION IN<br>OUTPUT DATA WORD |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 13              | 0            | The interface card is not busy.                                                                                                                                                                             | Not used.                           |

|                 | 1            | The interface card is in the process of transmitting or receiving data.                                                                                                                                     | Not used.                           |

| 14              | 0            | Secondary (Supervisory) Data Receive signal line disabled.                                                                                                                                                  | Not used.                           |

|                 | 1            | Secondary (Supervisory) Data Receive signal line enabled.                                                                                                                                                   | Not used.                           |

| 15              | 0            | Interface card is not prepared for a forthcoming send or receive operation.                                                                                                                                 | Denotes data word.                  |

|                 | 1            | Interface card parallel data output buffer is cleared of data and is ready to accept another character (transmit mode) or parallel data input buffer contains data to input to the computer (receive mode). | Not used.                           |

Figure 3-1. Transmit Control Word

Figure 3-2. Receive Control Word

#### Table 3-4. Typical Program

```

0001

ASMB . A . B . L

0002

ORG 100B

0003

0004

PROGRAM SENDS TO AND RECEIVES FROM

0005

0006

A COMPUTER, TERMINAL, OR TELEPHONE.

0007

0008

0009

MINIMUM EQUIPMENT NEEDED IS:

0010

202 TYPE DATASET, 12587B INTERFACE AND CABLES,

0011

2100 SERIES COMPUTER.

0012

TO RUN THE PROGRAM WITHOUT A TERMINAL OR ANOTHER COMPUTER.

0013

DELETE THE "JSB STC" AND THE "STA B.I" IN THE

0014

0015

RECEIVE SECTION.

0016

0017

1)

LOAD ADDRESS 100B.

0018

0019

21

PRESS "PRESET" AND "RUN".

0020

0021

FROM THE 202 DATASET TELEPHONE, CALL A NEARBY

3)

TELEPHONE (IT DOESN'T HAVE TO BE A DATASET).

0022

0023

PRESS THE DATA BUTTON. IT SHOULD STAY LIT

0024

4)

INDICATING THAT THE DATASET IS RECEIVING THE

0025

0026

DATA TERMINAL READY INDICATION FROM THE COMPUTER.

0027

5) LISTEN ON THE NORMAL TELEPHONE TO DETERMINE THE

0028

EFFECTS OF THE LINE TURNAROUNDS. THE PROGRAM SHOULD

0029

0030

OSCILLATE BETWEEN SEND AND RECEIVE.

0031

0032

TO RUN THE PROGRAM WITH TWO COMPUTERS.

0033

0034

START THE PROGRAM IN EACH AND ESTABLISH

0035 #

A DATA CONNECTION BETWEEN THE 202 DATASETS.

IF THE PROGRAM HANGS UP, THEN BOTH ENDS ARE

0036 *

0037 #

IN THE RECEIVE MODE. RESTART ONE COMPUTER

0038 *

AT LOCATION 100B AND OSCILLATION BETWEEN

SEND AND RECEIVE SHOULD TAKE PLACE.

0039

0040

0041

TO RUN THE PROGRAM WITH A TERMINAL, START THE

0042

PROGRAM AND ESTABLISH A DATA CONNECTION WITH

0043

0044

THE TERMINAL. TYPE A LINE FOLLOWED BY THE ETX

0045

CHARACTER, AND THE COMPUTER SHOULD TYPE IT BACK.

0046

0047

0048

202 NOTES

0049

0050

BEFORE "REQUEST TO SEND" IS TURNED OFF AT

THE END OF TRANSMISSION. A ONE MILLISECOND

0051 #

0052 #

DELAY IS REQUIRED TO ALLOW THE LAST DATA

0053 *

BIT TO CLEAR THE DATA SET. THE DELAY IS PROVIDED

0054

BY THE PAD CHARACTER FOLLOWING THE ".ETX".

0055 #

```

Table 3-4. Typical Program (Continued)

```

0056

LINE TURNAROUND IS 200 MILLISECONDS DURING WHICH

0057

TIME THE INTERFACE HOLDS OFF TRANSMISSION.

0058

DURING TRANSMISSION, CARRIER DETECT IS THE DATASET'S

0059

OWN CARRIER, SECONDARY RECEIVED DATA IS THE DISTANT

0060

0061

STATIONS'S REVERSE CHANNEL.

0062

DURING RECEPTION, CARRIER DETECT IS THE DISTANT

0063

STATIONS'S CARRIER, SECONDARY RECEIVED DATA IS THE

0064

DATASET'S OWN REVERSE CHANNEL.

0065

0066

DURING LINE TURNAROUND, CARRIER DETECT AND

0067

SECONDARY RECEIVED DATA GO OFF, AND THEN BACK ON.

0068

0069

0070

0071

0072

SWITCH PARAMETERS WHEN DEVICE NOT BUSY.

0073

SEND

JSB BUSY

0074

LDA CW1

OCTAL 160410-SEND MODE, EVEN PARITY

0075

OTA SC

8 BIT CHARACTER.

0076

PLACE TWO'S COMPLEMENT OF THE

0077

LDA LENG

CMA+INA+SZA+RSS NUMBER OF CHARACTERS TO BE SENT

0078

IN "COUNT". OMIT IF 00 CHARACTERS.

0079

JMP ETX

STA COUNT

0080

LDB ADDR

B REGISTER CONTAINS CHARACTER POINTER.

0081

0082

0083

LOOP1 LDA B,I

CHARACTER IS IN LOWER BYTE.

0084

AND MSK

ISOLATE.

0085

OTA SC

SEND CHARACTER.

0086

JSB STC

WAIT FOR FLAG SET.

BUMP CHARACTER POINTER.

0087

INB

0088

ISZ COUNT

INCREMENT AND TEST COUNT.

0089

JMP LOOP1

0090

0091

ETX

LDA .ETX

SEND END OF TRANSMISSION CODE.

OTA SC

0092

0093

JSB STC

0094

0095

LDA MSK

CHARACTER BEFORE .ETX IS BEING TRANSMITTED.

0096

OTA SC

.ETX IS WAITING IN BUFFER.

0097

JSB STC

PAD GETS .ETX OUT BEFORE TURNAROUND.

0098

0099

RECV

JSB BUSY

CHANGE PARAMETERS WHEN NOT BUSY.

0100

LDA CW2

OCTAL 140410-RECEIVE MODE, EVEN PARITY

0101

OTA SC

8 BIT CHARACTER.

LDA SBA

0102

OCTAL 2000. REVERSE CHANNEL ON

0103

OTA SC

INDICATES READY TO RECEIVE.

0104

0105

CLA

ZERO CHARACTER COUNTER.

STA LENG

0106

0107

LDB ADDR

B IS POINTER TO CHARACTER.

0108

0109

LIA SC

RESET READY FLIP-FLOP.

0110

```

Table 3-4. Typical Program (Continued)

```

JSB STC

WAIT FOR CHARACTER.

0111

LS

LIA SC

0112

0113

AND MSK

ISOLATE CHARACTER.

IF ETX THEN GO BACK TO SEND SECTION.

0114

CPA .ETX

0115

JMP EXIT

0116

STA B,I

STUFF IN BUFFER.

0117

INB

0118

ISZ LENG

0119

JMP L2

GET NEXT CHARACTER.

JMP SEND

0120

0121

CLA

TURN OFF REVERSE CHANNEL.

0122

EXIT

0123

OTA SC

0124

THIS ROUTINE

LIA SC

L3

FOLLOWS THE SWITCH OF REVERSE

0125

RAL

CHANNEL FROM THE LOCAL STATION

0126

SSA

0127

JMP L3

TO THE DISTANT STATION.

0128

LIA SC

0129

ROUTINE WILL NOT ALLOW TRANSMISSION

0130

RAL

SSA, RSS

UNTIL REVERSE CHANNEL

0131

JMP L4

0132

IS ON.

0133

JMP SEND

0134

BUSY

NOP

0135

LIA SC

0136

GET STATUS

ROTATE BUSY BIT TO BIT 15

0137

RAL, RAL

0138

SSA

IF 0 THEN OK TO SWITCH MODE.

0139

JMP BUSY+1

0140

JMP BUSY . I

0141

NOP

0142

STC

WAIT FOR OPERATION

STC SC+C

0143

SFS SC

0144

COMPLETION

JMP #-1

0145

FLAG.

JMP STC+I

0146

0147

0148

EQU 0

Α

0149

EQU 1

В

0150

EQU 15B

I/O SLOT OF 12587B.

SC

0151

LENG

DEC 10

0152

COUNT NOP

0153

ADDR

DEF BUFFR

0154

OCT 3

THIS WOULD BE LF, 12B, FOR TTY.

•ETX

OCT 160410

0155

CWI

OCT 140410

0156

CW2

OCT 2000

0157

SBA

OCT 177

0158

MSK

BUFFR EQU *

0159

0160

REP 10

NOP

0161

0162

0163

0164

0165

END

```

12587B Section IV

# **SECTION IV**

# THEORY OF OPERATION

# 4-1. INTRODUCTION.

4-2. This section contains an overall functional description and a detailed circuit description for the interface card. Located at the back of this section is a flow chart (figure 4-4) that illustrates the operating sequence of the interface card.

#### 4-3. OVERALL FUNCTIONAL DESCRIPTION.

- 4-4. The interface kit includes a single plug-in printed-circuit card that provides parallel-to-serial or serial-to-parallel data conversion. The interface card also provides data set control signals which conform to Electronic Industries Association Standard RS-232-B. The data conversion function and data set control signals allow a computer to transmit or receive data via common-carrier data transmission lines.

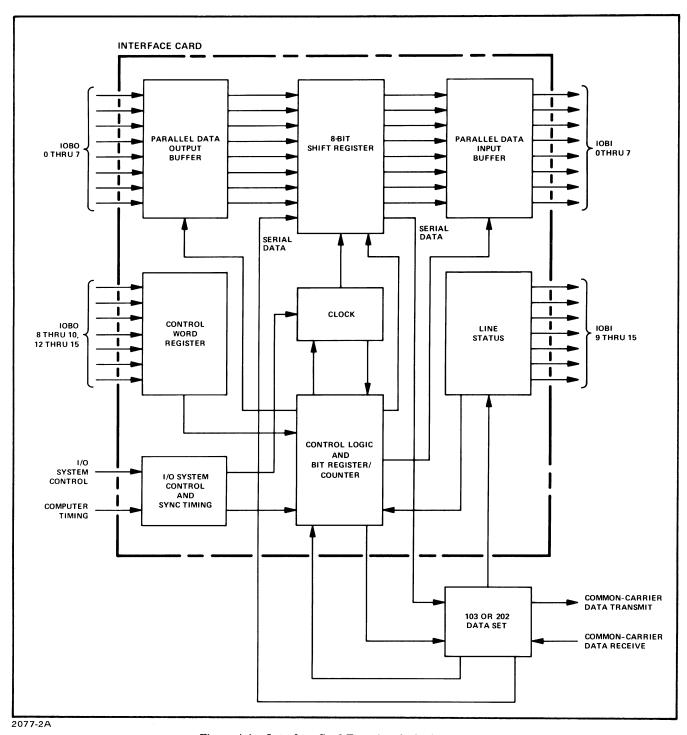

- 4-5. Figure 4-1 is a functional block diagram showing the operational relationship of the computer, the data set, and the interface card. Three functions are achieved by the interface card: data transmission, data reception, and line status checks. The following paragraphs describe each function.

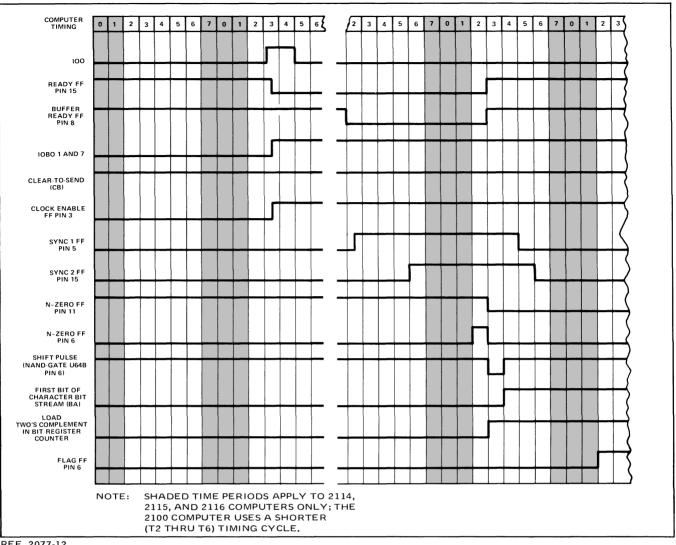

# 4-6. DATA TRANSMISSION.

In the transmit mode, parallel data is output from the computer to the interface card, and is converted to serial data. The serial data is transmitted over commoncarrier equipment by the data set. In operation, a control word from the computer sets the interface card control logic for the transmit mode. The control logic places the data set in the transmit mode and prepares the parallel data output buffer for a load operation. Parallel data is output from the computer to the parallel data output buffer. If the 8-bit shift register is clear and Clear-to-Send (CB) is enabled, the control logic allows the contents of the parallel data output buffer to enter the 8-bit shift register. The clock (synchronized with the computer timing) is enabled and shifts the contents of the 8-bit shift register to the data set in serial format. The bit register/counter section of the control logic disables the clock when one character bit stream is transmitted serially. (The parity bit, if selected, and start and stop bits are added by the interface card.) The data set transmits the serial data over common-carrier lines.

# 4-8. DATA RECEPTION.

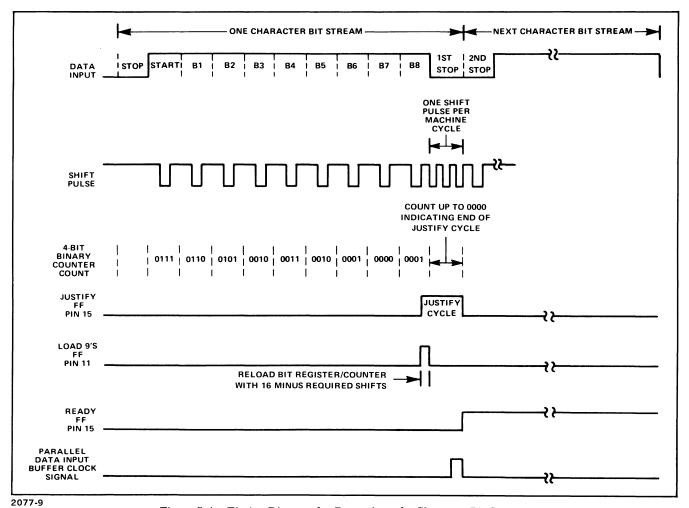

4-9. In the receive mode, serial data is transferred from the data set to the interface card and is converted to parallel data. The parallel data is then input to the computer. In operation, a control word from the computer sets the interface card control logic for the receive mode. The control logic notifies the data set that the interface card is ready to accept data. The first bit (start bit) of serial data enters the 8-bit register and enables the clock. The clock shifts the subsequent serial data bits into the 8-bit shift register. The bit register/counter right justifies the data. The control logic checks parity (if selected) and transfers the contents of the 8-bit shift register to the parallel data input buffer. The data in the parallel data input buffer is then transferred to the computer.

#### 4-10. LINE STATUS CHECKS.

4-11. Three of the common-carrier lines (Data Set Ready, Secondary Data Receive, and Carrier Detect) connecting the transmit and receive data sets are monitored by the interface card. The line status check signals are transferred from the interface card to the computer. When selected by the program, an absence of any one of the line status check signals generates an interface card Flag signal.

#### 4-12. DETAILED CIRCUIT DESCRIPTION.

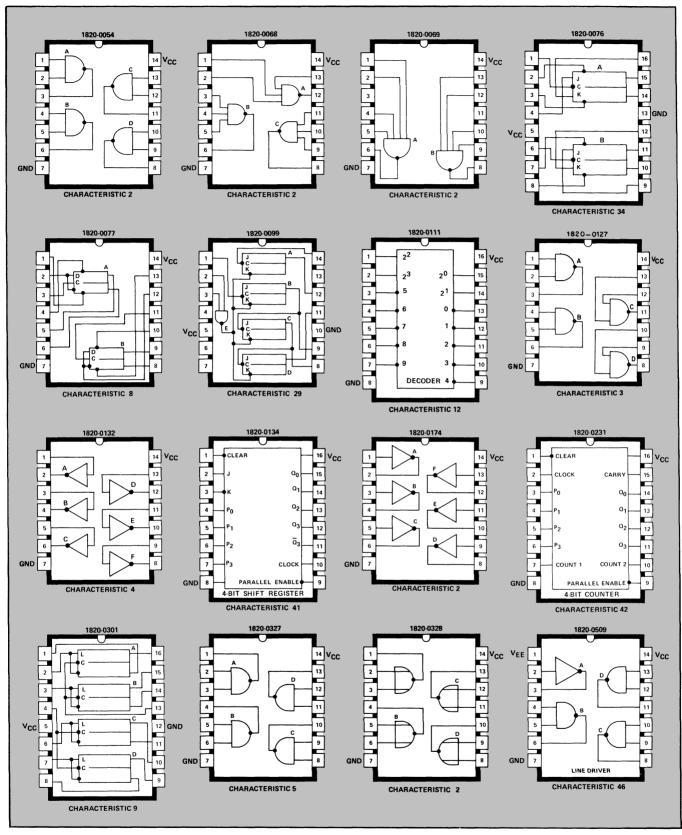

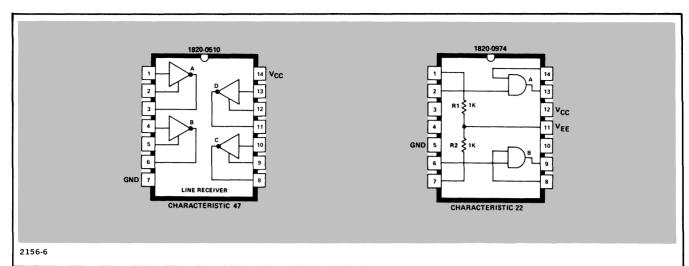

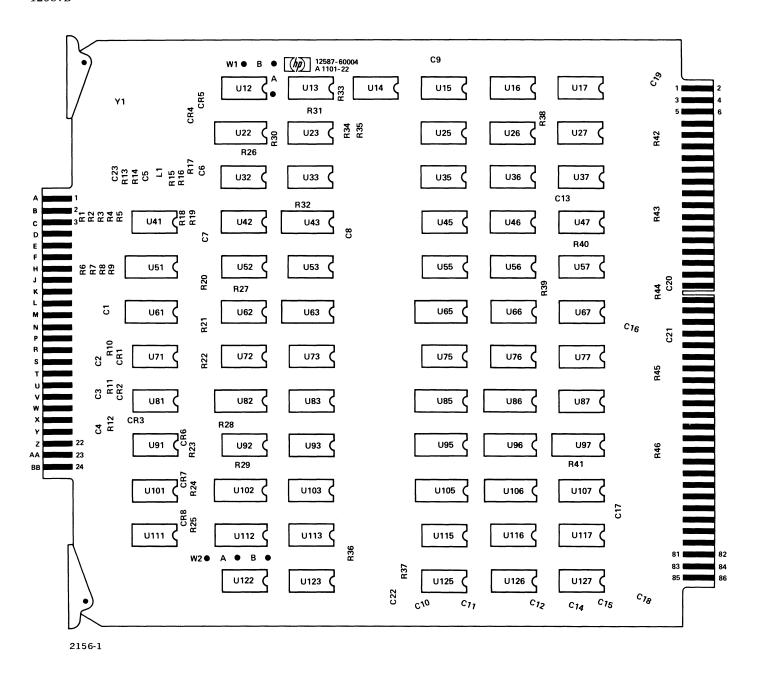

4-13. The following paragraphs contain a detailed circuit description for the interface card. The description covers the I/O system controls, the control word register, the 8-bit shift register, the bit register/counter, the clock and synchronize circuit, the control logic, and line status. See the logic diagram for the interface card (figure 5-14) when referencing the detailed circuit description.

# 4-14. INPUT/OUTPUT SYSTEM CONTROLS.

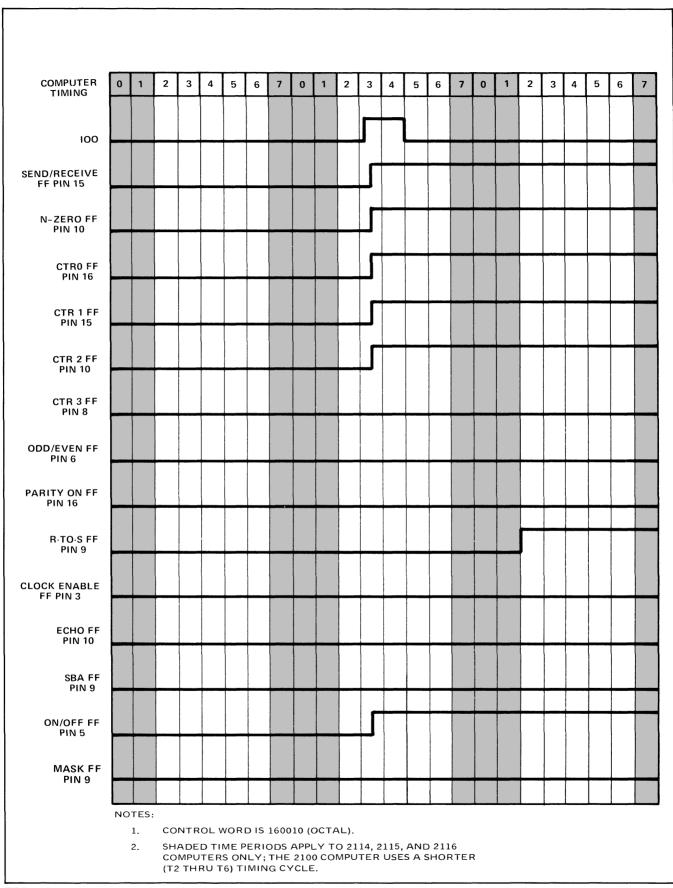

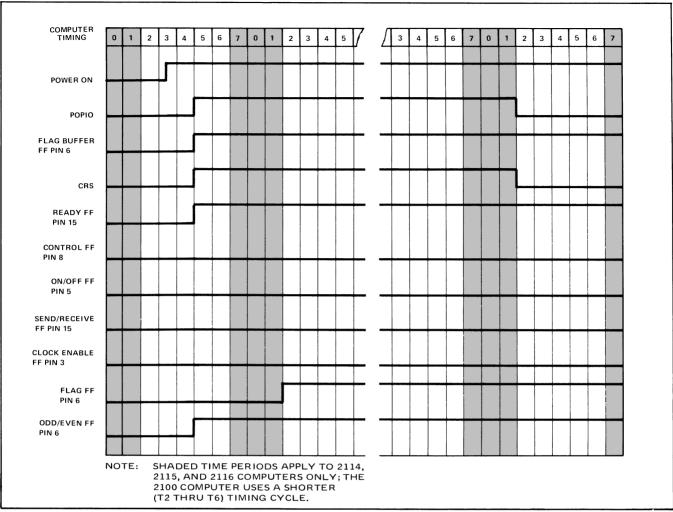

- 4-15. When power is initially applied by the POWER switch of the computer, the Interrupt System Enable FF on the I/O control card is cleared, which disables the computer interrupt system. Initial power disables the interface card with the POPIO and CRS signals. The CRS signal clears the Control FF, Clock Enable FF, and On/Off FF. The POPIO signal sets the Flag Buffer FF and Ready FF. The output signals from these flip-flops clear the Parity FF, Start Bit FF, Justify FF, Load 9's FF, and set the N-Zero FF, Stop Bit FF, and Flag FF at computer time T2 (ENF).

- 4-16. After initialization, a STF instruction with the select code of 00 (octal) sets the Interrupt System Enable FF and the computer IEN signal enables the I/O control card. The interface card will not interrupt until a STC,CLF instruction with the select code of the interface card is output from the computer. The select code, the IOG(B) signal, and the STC signal set the Control FF. The Control FF enables an interrupt, but does not affect the functioning of the data set associated with the interface card. The CLF signal clears the Flag Buffer FF and the Flag FF.

12587B

Figure 4-1. Interface Card Functional Block Diagram

4-17. When the interface card generates a Flag signal, the set output from the Control FF, combined with the IEN signal and set-side output of the Flag FF, sets the IRQ FF at computer time T5 (SIR) if the PRH signal is true. This causes a program interrupt, which usually occurs at the end of the current phase of computer operation. At the next time T2, the IRQ FF clears, allowing any higher-priority device to use the requested interrupt. If no higher-priority device requests an interrupt, the IRQ FF sets again

at time T5 (SIR signal). The FLG and IRQ signals indicate the service request address of the interface card, and the computer services the card.

# 4-18. CONTROL WORD REGISTER.

4-19. The control word register consists of seven flipflops and a gate network. Signal inputs from the computer to the control word register set the interface card for the 12587B Section IV

|              |                                      | FUNCTION                                                                                        |                                                                                                |  |  |

|--------------|--------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| IOBO<br>LINE | FLIP-FLOP                            | LOGIC 0 INPUT                                                                                   | LOGIC 1 INPUT                                                                                  |  |  |

| 7            | Odd/Even                             | Even parity selected                                                                            | Odd parity selected                                                                            |  |  |

| 8            | Parity On                            | Parity check disable                                                                            | Generate and check parity                                                                      |  |  |

| 9            | Echo                                 | Echo disabled                                                                                   | Echo enabled                                                                                   |  |  |

| 12           | Mask<br>(Status Interrupt<br>Enable) | Data Set Ready (CC), Carrier Detect (CF), and Secondary Data Receive (SBB) interrupts disabled. | Data Set Ready (CC), Carrier Detect (CF), and Secondary Data Receive (SBB) interrupts enabled. |  |  |

| 13           | Send/Receive and<br>Request-to-Send  | Receive mode                                                                                    | Send mode                                                                                      |  |  |

| 14           | On/Off                               | Data Terminal Ready (CD) signal disabled to data set.                                           | Data Terminal Ready (CD)<br>signal enabled to data set.                                        |  |  |

| 15           | Gate Network                         | Signal input on IOBO lines is data.                                                             | Signal input on IOBO lines is control.                                                         |  |  |

desired operating mode. Table 4-1 lists each input line from the computer to the card (IOBO lines 7 through 15), the associated flip-flop in the control word register, and the function of each flip-flop. In operation, a logic 1 from the output of gate U47B (LSCM, IOGB, and LSCL) combines with a logic 1 IOO signal, allowing capacitor C6 to charge through resistor R64. When the IOO signal changes to a logic 0 (at the end of computer time T4), a short negative-going pulse appears at the output of gate U46A and enables the decoding of bit 15. If input signal IOBO 15 is a logic 1 (denoting a control word), the output of gate U56C provides a clock signal at the clock input of the control word register flip-flops. To prevent the control word from entering the parallel data output buffer, a logic 1 at pin 8 of gate U56D disables the gate and a parallel data output buffer clock signal is not produced. However, should input signal IOBO 15 be a logic 0 (denoting data), U56D and U56A would produce a parallel data output buffer clock signal and the control word register flip-flops would be inhibited. The control word also contains the word size of the parallel data. The word size information is coupled to the bit register/counter by IOBO lines 0 through 3. Typical program word formats for a control word and data word are shown in figure 4-2.

# 4-20. 8-BIT SHIFT REGISTER.

4-21. The 8-bit shift register consists of two 4-bit shift register integrated circuits that provide parallel-to-serial or serial-to-parallel data conversion. This is accomplished by switching the inputs of the 8-bit shift register between two sources. A logic 0 Parallel Enable signal loads parallel data

into the shift register for a parallel-to-serial data conversion (transmit mode for the interface card). A logic 1 Parallel Enable signal loads serial data into the shift register for a serial-to-parallel data conversion (receive mode of operation for the interface card).

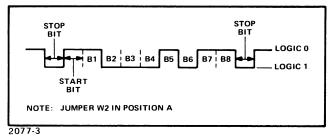

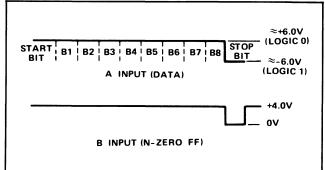

PARALLEL-TO-SERIAL DATA CONVERSION. Parallel-to-serial data conversion occurs in the following manner. Parallel data from the computer enters the 8-bit shift register via the eight flip-flops of the parallel data output buffer. The converted serial data is output from the 8-bit shift register at pin 12 of integrated circuit U95. The serial data is clocked through the Start Bit FF and the Stop Bit FF. With the Stop Bit FF set and the Start Bit FF cleared at the beginning of a transmit operation, the serial data from the 8-bit shift register will be preceded by a stop bit and a start bit. (See figure 4-3.) The stop bit provides a separation of transmitted and received data when changing the operating mode. The start bit signifies the beginning of a character bit stream. Serial data is supplied, through U42A, U42C, and U71A, to line driver U81A which applies the character bit stream to the data set.

4-23. SERIAL-TO-PARALLEL DATA CONVERSION. Serial-to-parallel data conversion begins with the reception of a character bit stream from the data set. Line receiver U91B accepts the data bits and applies them, through U71D, to U93A. Because the Request-to-Send FF is cleared, the inverted data bits are output from gate U93A. The first data bit of the character bit stream from U93A sets the Clock Enable FF. With the Parallel Enable signal a logic 1 and the clock operating, the bits are shifted through

Figure 4-2. Typical Control Word and Data Word Formats

the Serial In FF to the 8-bit shift register. After the bits are shifted into the 8-bit shift register and placed in the right justified position (least significant bit located at output pin 12 of integrated circuit U95), a clock pulse from the bit register/counter loads the parallel data into the Parallel Data Input Buffer FFs. The data is input to the computer from the parallel data input buffer.

4-24. PARITY COMPUTATION. Parity computation is accomplished with the Parity On FF and the Odd/Even FF of the control word register, the Parity FF, and the Error FF. Operation of the interface card without the use of parity is possible by not setting the Parity On FF during the control word output. In the transmit mode, each bit of the

Figure 4-3. Typical Serial Character Bit Stream

character bit stream is applied to the Parity FF by gate U73C. The output of the Parity FF and the output of the Odd/Even FF are compared by gates U52B and U52C to determine the logic level of the parity, and the result is inserted as the last bit of the character bit stream by gate U42D. (The Odd/Even FF is set or cleared by the IOBO 7 line during the output of the control word from the computer. A logic 1 causes odd parity and a logic 0 causes even parity.) In the receive mode, gate U73D applies each bit of the character bit stream to the Parity FF. The output of the Parity FF and the output of the Odd/Even FF are compared by gates U52B and U52C. If the logic levels of the flip-flops do not agree, a fault is detected and the Error FF is cleared. The Error FF remains clear only for that one particular character bit stream.

#### Note

If the Ready FF remains set due to the failure of the program to service the interface card, the Error FF is held clear indicating the loss of the preceding character bit stream.

# 4-25. BIT REGISTER/COUNTER.

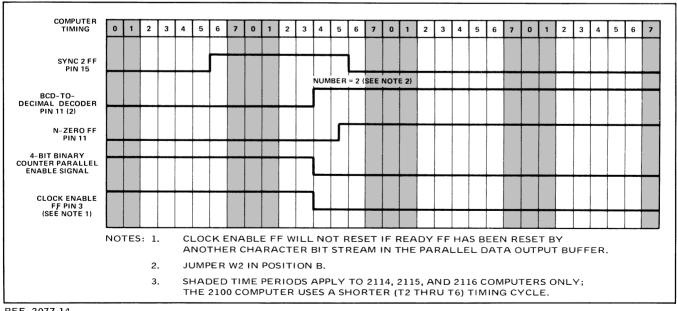

4-26. The bit register/counter consists of a four flip-flop register (CTR 0 through CTR 3) and associated gating, a 4-bit binary counter (U102), a BCD-to-decimal decoder (U112), a Load 9's FF and a Justify FF. The bit register/counter controls the shifting of one complete character bit stream from the 8-bit shift register during the transmit mode of operation and right justifies a character bit stream in the 8-bit shift register during the receive mode of operation. The number of shifts required for proper operation is determined by the two's complement portion of the control word from the computer. (Refer to paragraph 4-19 and figure 4-1.)

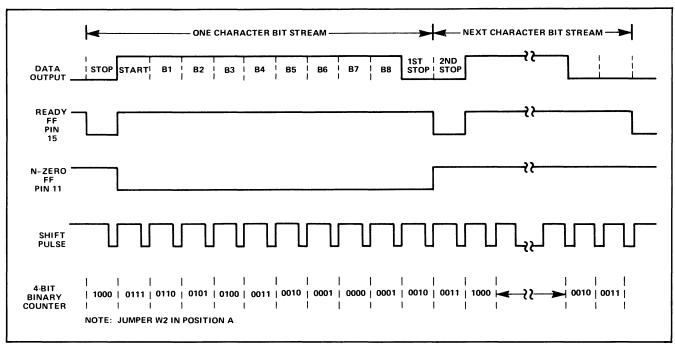

4-27. TRANSMIT MODE. In the transmit mode, the register portion of the bit register/counter is loaded with the two's complement (a negative number) of the total number of bits that constitutes one complete character bit stream. The counter portion of the bit register/counter counts forward to one, adds the parity bit if the control word register Parity FF is set, and provides the desired number of stop bits to complete the character bit stream. In operation, a combination of IOO and IOBO 15 signals provides a clock signal to load FFs CTR 0 through CTR 3 with the complement of the two's complement of the character bit stream. (The complement of the two's complement is derived from inversion by gates U75A through U75D.) Because the Justify FF is cleared during the transmit mode, gates U72C, U92A, and U92C apply the information contained in FFs CTR 0 through CTR 3 to 4-bit binary counter U102 in the two's complement form. The information loads into the 4-bit binary counter when the Parallel Enable signal becomes a logic 0. At each clock signal from gate U72B, the 4-bit binary counter counts forward and the BCD count is decoded by BCD-to-decimal decoder U112. When the number "1" is decoded at pin 12 of U112, the computer parity (if selected by the control 12587B Section IV

word) is added to the serial data by gate U42D. With jumper wire W2 in the B position and the count at "2" (pin 11 of U112), the Clock Enable FF is cleared which disables the clock circuit. The stop bit at the start of the next character bit stream provides a one stop bit separation between data. If W2 is in the A position, the count is allowed to reach "3" (pin 3 of U112) and one stop bit is placed in the character data stream before the clock circuit is disabled. This stop bit combined with the stop bit at the start of the next character bit stream provides the two stop bit separation between data. After the clock circuit is disabled, a clock signal from gate U122C is applied to the Error FF to check for errors, and the N-Zero FF is set by a logic 0 signal from gate U52D. (Setting the N-Zero FF indicates the character bit stream has been transmitted.) The signal from the clear-side output of the N-Zero FF clears the Parity FF and provides a logic 0 Parallel Enable signal to the 4-bit binary counter and the 8-bit shift register. A logic 0 Parallel Enable signal reloads the 4-bit binary counter with the two's complement of the next character bit stream that was stored in the CTR 0 through CTR 3 FFs during the output of the control word. The 8-bit shift register is loaded from the parallel data output buffer and another character bit stream is transmitted.

- 4-28. RECEIVE MODE. In the receive mode, bits 0 through 3 of the control word (the two's complement of the number of bits in one complete character) are inverted and loaded into the register portion of the bit register/counter. Because the clear side of the N-Zero FF holds a low level (logic 0) on U102 pin 9, these bits, inverted back to the two's complement, are loaded into the 4-bit counter portion of the bit register/counter.

- 4-29. When the first bit of the character bit stream is received from the data set, the Clock Enable FF sets as described in paragraph 4-23. As each bit of received data is clocked into the 8-bit shift register, the 4-bit counter increments by one. When the 4-bit counter "wraps around" and U112 BCD-to-decimal decoder reaches the count of "1". gate U83A sets the Justify FF and gate U93B sets the Load 9's FF. The set outputs of these flip-flops provide a low enabling signal to the 4-bit counter and allow loading the 4-bit counter from the clear sides of CTR 0 through CTR 3 FFs. This number equals the required number of justifying shifts subtracted from 16. At computer time T3, the Load 9's FF is cleared and the justify cycle begins. Time T3 and a high (logic 1) from the Justify FF combine at gate U62D to produce a 4-bit counter clock signal from gate U72B that increments the counter every machine cycle. At the same time, gate U122A causes an 8-bit shift register clock signal. A justify shift, therefore, occurs every machine cycle.

- 4-30. When the output of the BCD-to-decimal decoder equals the count of "0" (pin 13 of U112), the Justify FF clears, ending the justify cycle. Gate U73A clears the Clock Enable FF and provides a clock signal to the Error FF to check for errors. The Clock Enable FF disables the clock circuit and sets the N-Zero FF. Setting the N-Zero FF indicates that data is justified. The clear-side output of the

N-Zero FF clears the Parity FF and reloads the two's complement of the next character bit stream into the 4-bit binary counter.

#### 4-31. CLOCK AND SYNCHRONIZE CIRCUIT.

- 4-32. The clock and synchronize circuit provides a shift signal to the 8-bit shift register and an increment signal to the bit register/counter that coincides with the computer timing but is not the same time interval as a machine cycle. Once each shift cycle, three computer timing signals (T2, T3, and T5) provide synchronization. The clock and synchronize circuit consists of a crystal-controlled oscillator, a programmable scaler, a Clock Enable FF, a frequency divider, and two synchronizing flip-flops.

- 4-33. CRYSTAL-CONTROLLED OSCILLATOR. The clock oscillator is a free-running, crystal-controlled oscillator consisting of U41A, U41B, U41C, and crystal Y1. Frequency of oscillation is 423,000 pulses per second. The oscillator output is connected to pin 4 of the 48-pin connector. Pin 4 is externally wired to pin F of the 48-pin connector; pin F is connected to the input of the programmable scaler.

- 4-34. PROGRAMMABLE SCALER. The programmable scaler consists of two, 4-bit binary counters (U51 and U61) connected to form a scaler with a 256-count capacity. The scaler can be preset to any number from 0 through 239 with external jumpers (see table 2-1). The scaler counts pulses from the crystal-controlled oscillator and generates one output pulse at U61 pin 15 each time the preset number of counts plus the accumulated pulses from the oscillator equal 255. When count 255 occurs, an output pulse is applied to U12B pin 5, and gate U41D enables the scaler preset lines. The next pulse from the oscillator sets the scaler to its preset value. By presetting the scaler to the appropriate value, the oscillator frequency can be divided by any number between 2 and 256.

- CLOCK ENABLE FF. The set-side output of the Clock Enable FF combines with the oscillator signal at gate U12B to initiate the frequency divider. Due to the Clock Enable FF, the first half of the first cycle from U12B will always be a logic 0. The clear-side output of the Clock Enable FF clears the frequency divider, clocks the Request-to-Send FF, and sets the N-Zero FF. The Clock Enable FF is set during the receive mode by the output of the first bit of a character bit stream from gate U93A. In the transmit mode, the Clock Enable FF is set if the Request-to-Send FF is set, the Ready FF is cleared, and the data set Clear-to-Send signal is a logic 1. The Clock Enable FF is cleared by a Clear Control (CRS) signal or by the bit register/counter. Because the Clock Enable FF is set only when the interface card is shifting data, the set-side output of the Clock Enable FF is also used as a Busy signal (IOBI line 13) to the computer.

- 4-36. FREQUENCY DIVIDER. The output of the programmable scaler is reduced in frequency to the bit transfer rate of the interface card by the frequency divider. The frequency divider consists of a Divide-by-2 FF, a Divide-by-4

Section IV 12587B

FF, and a Divide-by-2/8 FF. This circuit divides the programmable scaler output by 8 when jumper W1 is in the A position and by 64 when W1 is in the B position. Table 2-1 shows how to position jumper W1 and how to preset the programmable scaler to effect a desired data transfer rate.

4-37. SYNCHRONIZING FLIP-FLOPS. The synchronizing flip-flops, Sync 1 FF and Sync 2 FF, provide a shift and increment signal that is coincident with the computer timing signals. The Sync 1 FF input signal is from the frequency divider and the Sync 2 FF input is the SIR signal at time T5 of the computer cycle. In the transmit mode, the first half cycle of the bit shift frequency from gate U13A sets positive-edge-trigger Sync 1 FF. With a logic 1 at the J-input and a logic 0 at the K-input of the Sync 2 FF, gate U57E sets the Sync 2 FF at the end of computer time T5. The set output of the Sync 2 FF combines with ENF, T3B, and SIR computer signals to provide computer time periods T2, T3, and T5 from gates U67B, U67D, and U67C, respectively. The leading edge of T5 from U67C clears the Sync 1 FF and the trailing edge of T5 clears the Sync 2 FF; consequently, only one set of T2, T3, and T5 computer timing signals are available for a single bit shift cycle. In the receive mode, the only operational change is that the Sync 1 FF is set during the last half of the bit shift frequency from gate U13D. For this reason, the character bit stream is transmitted at the start of a bit shift cycle and received in the center of a bit shift cycle.

#### 4-38. CONTROL LOGIC.

- 4-39. The control logic monitors and controls the input and output sequence of data conversion by the interface card. The control logic consists of the N-Zero FF, the Ready FF, the Ringing FF, and the Buffer Ready FF.

- 4-40. N-ZERO FF. The N-Zero FF initializes the control logic after the last bit of the current character bit stream has been transmitted or received. After the last bit of the character bit stream is processed, the setting of the N-Zero FF produces the Parallel Enable signal for the 8-bit shift register and bit register/counter, clears the Parity FF, sets the Stop Bit FF, and clears the Start Bit FF. The N-Zero FF is set each time the Clock Enable FF is cleared.

- 4-41. READY FF. The Ready FF signals the computer via the flag circuit that the interface card is ready to input data to the computer or that the card is ready to transmit another character bit stream to the data set. In the receive mode, the Ready FF is cleared by an LIA/B or MIA/B instruction: in the transmit mode, the Ready FF is cleared by an OTA/B instruction. An input or output instruction such as LIA,C or OTA,C clears the Ready FF and the Flag FF; however, an attempt to clear the Flag FF without

executing an input or output instruction will result in another Flag signal. (The set condition of the Ready FF holds the Flag FF set until the interface card is serviced.)

#### Note

In the transmit mode, the Ready FF may be set if the parallel data output buffer is ready to accept new data. This does not indicate that the 8-bit shift register is empty; the 8-bit shift register may be processing the data received from the parallel data output buffer.

- 4-42. RINGING FF. The Ringing FF detects if common-carrier equipment is attempting to contact the data set associated with the interface card. In operation, the Ringing (CE) signal from the data set associated with the interface card is buffered by line receiver U101D, inverted by U111B, and applied as a clock signal to the Ringing FF. The resulting set output from the Ringing FF sets the Flag Buffer FF. A CLF instruction from the computer clears the Ringing FF.

- 4-43. BUFFER READY FF. The Buffer Ready FF retains the set condition of the Ready FF long enough for an LIA/B or MIA/B instruction to couple the condition of the Ready FF to the computer. The retention capability is necessary because any of these instructions will clear the Ready FF if the interface card is in the receive mode. The Buffer Ready FF is set by the Ready FF and is cleared by an ENF (T2) signal from the computer. The set output of the Buffer Ready FF is connected to IOBI line 15.

# 4-44. LINE STATUS.

4-45. The line status circuit consists of three line receivers, the Mask FF of the control register, and associated gates. The line status circuit monitors the signal lines that connect the data set associated with the interface card to the common-carrier equipment. During each computer input instruction, the Data Set Ready (CC), Secondary Data Received (SBB), and Carrier Detect (CF) signals are coupled to the computer by the receivers. During normal operation, the output of the line receivers cause a logic 0 output from gate U113A. If the Mask FF is set by the control word and one of the line signals goes off, the output of U113A sets the interface card Flag Buffer FF and the interface card generates an interrupt. If the Mask FF is not set, the Flag Buffer will not be set; however, the line signals are part of the input word to the computer.

12587B Section V

Figure 4-4. Flowchart of Interface Card Operating Sequence

# SECTION V MAINTENANCE

# 5-1. INTRODUCTION.

5-2. This section contains information on the diagnostics and troubleshooting for the interface card.

# 5-3. PREVENTIVE MAINTENANCE.

5-4. Detailed preventive maintenance procedures and schedules are given in the Installation and Maintenance Manual for the computer. There are no separate preventive maintenance procedures for the interface kit.

# 5-5. DIAGNOSTICS.

5-6. Complete diagnostic program operating procedures are contained in the Manual of Diagnostics. Refer to procedure part number 12587-90002 when using a 2114, 2115, or 2116 Computer or procedure part number 12587-90005 when using a 2100 Computer.

#### 5-7. TROUBLESHOOTING.

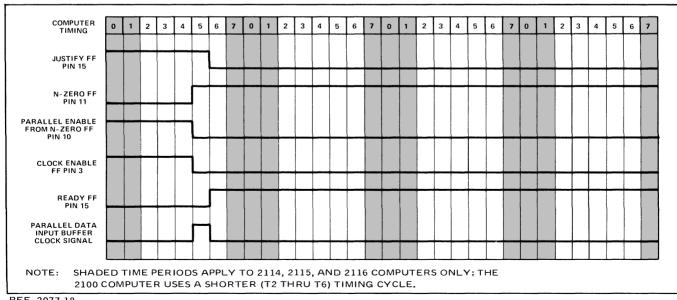

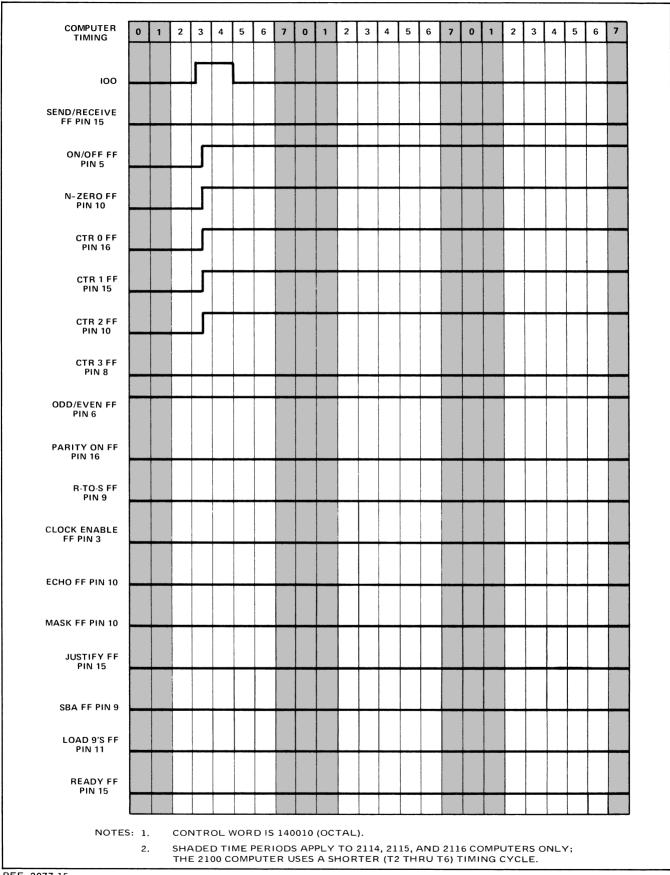

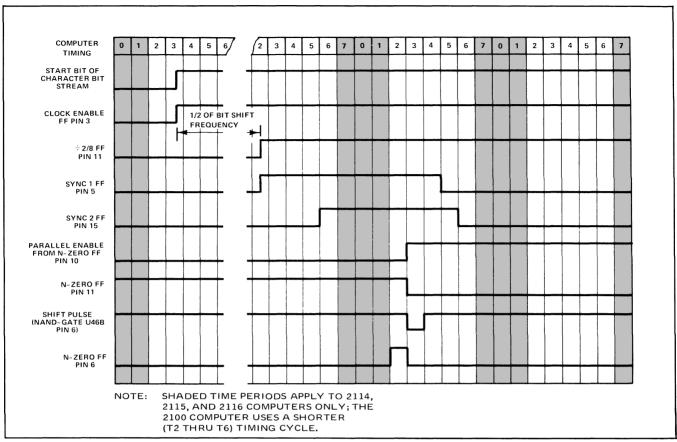

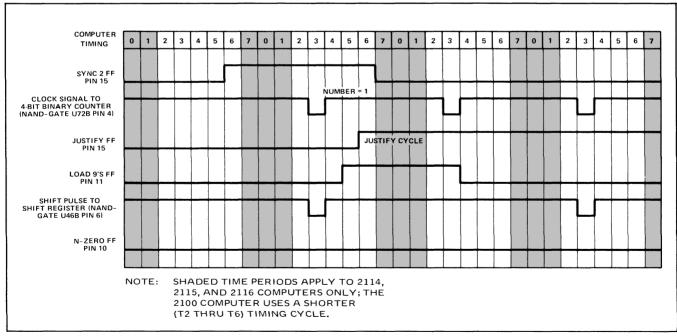

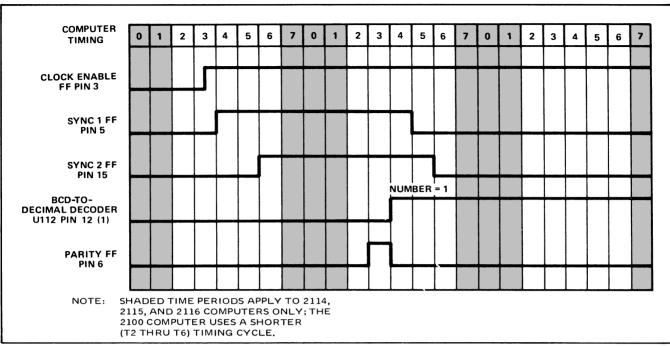

5-8. Troubleshooting the interface card is accomplished by performing the diagnostic test described in the Manual of Diagnostics and analyzing the error halts that occur as the test is being run. Figure 5-1 and table 5-1 contain wiring and signal information for the test connector that is used to run the diagnostic test. After analyzing the error halts, see figure 5-15 of this manual for the logic and parts location diagrams of the interface card and table 5-2 for interconnecting cable pin functions. Refer to the appropriate computer documentation for additional information on backplane wiring, signal data, etc., not included in this manual. To further isolate trouble, perform the following test program, check the timing diagrams in this section, and refer to the list of equations provided in table 5-4.

# 5-9. TEST PROGRAM.

5-10. The test program sets the interface card for the transmit mode of operation, then transmits the information in the computer switch register (bits 0 through 7) in a serial character bit stream. An HP 180A Oscilloscope (or equivalent) with X10 probes and the card extender are required to perform the test. To conduct the test, proceed as follows:

#### **CAUTION**

Turn the power off at the computer before removing or replacing interface cards or damage may result.

- a. Plug interface card with test connector attached into card extender and insert card extender in appropriate slot in computer. A resistor is attached to the test connector on the Request to Send function to cause a slight delay and eliminate a race condition.

- b. Set oscilloscope sensitivity adjustment of A input to read 1 V/CM and connect A input to pin 11 of 48-pin connector.

- c. Set oscilloscope sensitivity adjustment of B input to measure 0.2 V/CM and connect B input to pin 11 of gate U122C on interface card. (The signal at U122C pin 11 is the clear-side output of the N-Zero FF.) Connect external sync of oscilloscope to same location as the B input and set external sync adjustment to trigger on the positive signal.

- d. Using computer front-panel controls, load test program shown in table 5-3. Return to address 100 (octal) and press computer RUN switch.

- e. Adjust TIME/DIV and variable time base adjustment of oscilloscope until one character bit stream appears on screen of oscilloscope. (See figure 5-2.)

Figure 5-1. Test Connector Wiring Diagram

|      | CARD OUTPUT SIGNALS |                     |                  | CARD INPUT SIGNALS                               |                             |              |  |      |

|------|---------------------|---------------------|------------------|--------------------------------------------------|-----------------------------|--------------|--|------|

| ІОВО | EIA STANDARD        |                     | EIA STANDARD     |                                                  | EIA STANDARD TEST CONNECTOR | EIA STANDARD |  | ІОВІ |

| BIT  | CIRCUIT             | NAME                | PINS             | NAME                                             | CIRCUIT                     | BIT          |  |      |

| 10   | SBA                 | Secondary Data Send | 14 — 19          | Secondary Data Receive                           | SBB                         | 14           |  |      |

|      |                     |                     | L_ <sub>13</sub> | Serial Data Input                                | ВВ                          |              |  |      |

| 13   | CA                  | Request-to-Send     | 16 —— 12         | Clear-to-Send                                    | СВ                          | -            |  |      |

| 14   | CD                  | Data Terminal Ready | 20 —— 15         | Ringing                                          | CE                          | 10           |  |      |

| -    | _                   | Internal Clock      | 1 23             | Data Set Ready                                   | CC                          | 12           |  |      |

| _    | BA                  | Serial Data Output  | 11 ——— 22        | Carrier Detect                                   | CF                          | 11           |  |      |

| _    | _                   | Internal Oscillator | 4 —— F           | Programmable Scaler                              |                             | _            |  |      |

| _    | -                   | Ground              | BB B 3 D 7       | Programmable<br>Scaler<br>Preset (1200 bits/sec) | _                           | _            |  |      |

Table 5-1. Test Connector Signal Information

#### Note

Figure 5-2 is for an interface card operating with jumper W2 in position B (only one stop bit at the end of the character bit stream). If two stop bits were selected (W2 in position A), the N-Zero FF output would coincide with the last stop bit.

- f. Switch bits 0 through 7 of computer switch register off and on, one at a time, and check resulting waveform. Each waveform bit should be near -6 volts when respective switch register bit is in the logic 1 (on) position.