# HP 1000 A400 Computer

# **Engineering and Reference Documentation**

# HP 1000 A400 Computer

### **Engineering and Reference Documentation**

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

**WARNING:** This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

Data Systems Operation 11000 Wolfe Road Cupertino, CA 95014

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THE MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1990 by HEWLETT-PACKARD COMPANY

# **Printing History**

The Printing History below identifies the edition of this manual and any updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this printing history page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as all updates.

To determine what manual edition and update is compatible with your current software revision code, refer to the Manual Numbering File or the Computer User's Documentation Index. (The Manual Numbering File is included with your software. It consists of an "M" followed by a five digit product number.)

| First Edition | Jul 1990 |  |

|---------------|----------|--|

### **Preface**

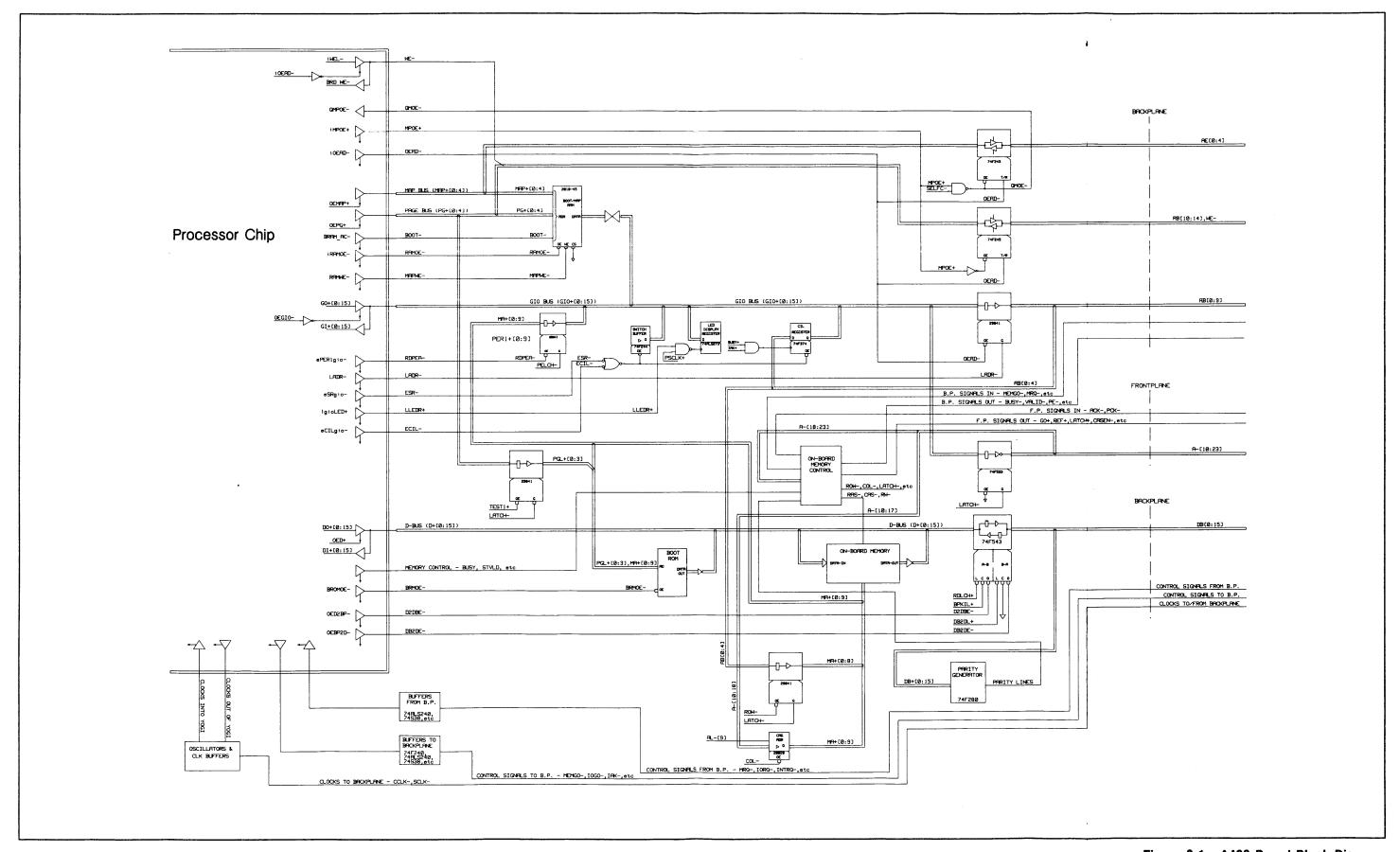

This manual contains engineering and reference information for the HP 1000 A400 computer. Information is provided in this manual for each section of the A400 Board (the processor chip, the on-board memory and memory controller, and the on-board I/O), optional memory array cards, backplane, and power supply. I/O interface cards are not covered in this document since the detailed information is provided in other manuals.

This manual is organized into the following chapters:

Chapter 1 - HP 1000 A400 Computer

Chapter 2 - A400 Board General Description

Chapter 3 - Processor Chip

Chapter 4 – Memory Control

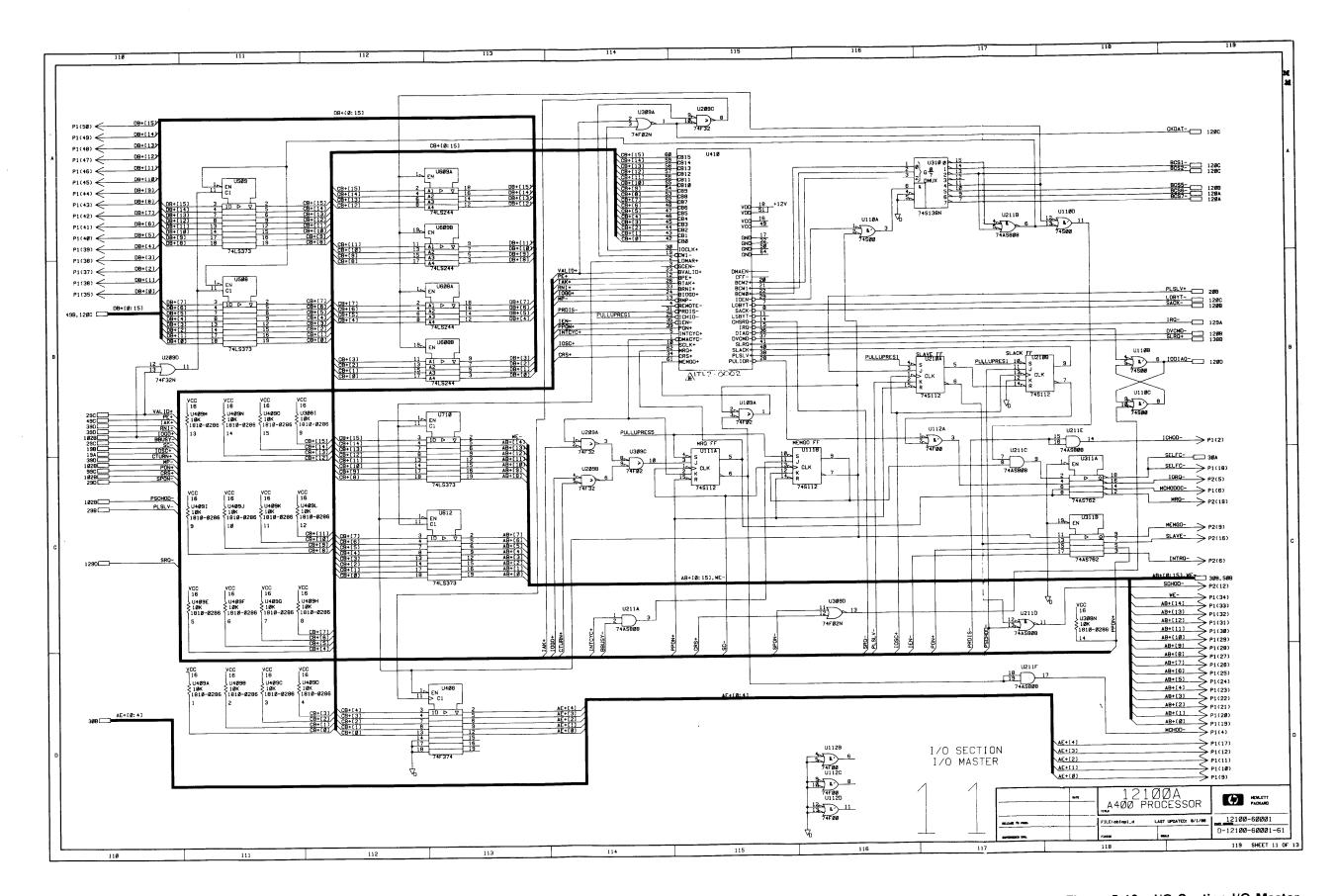

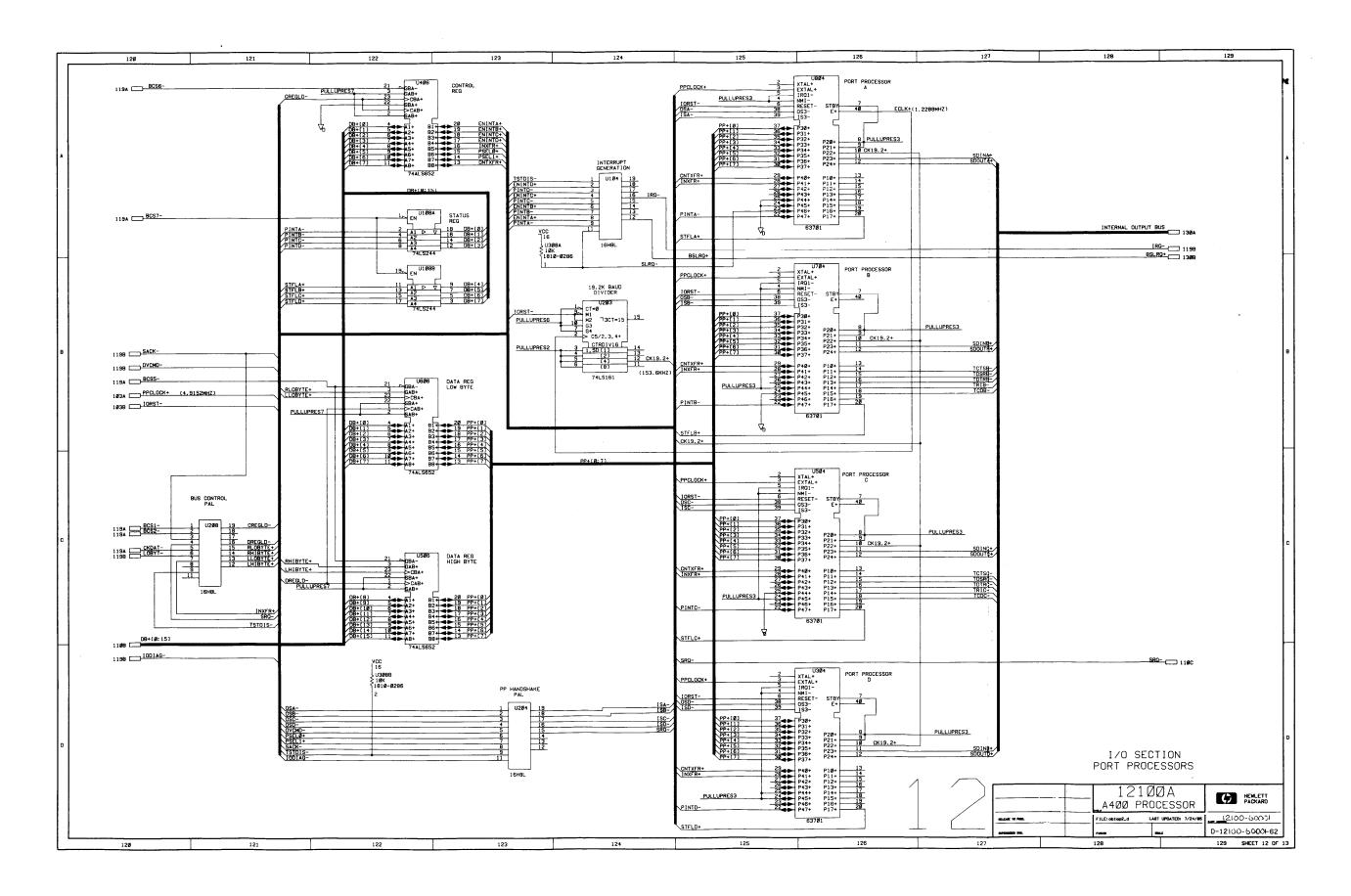

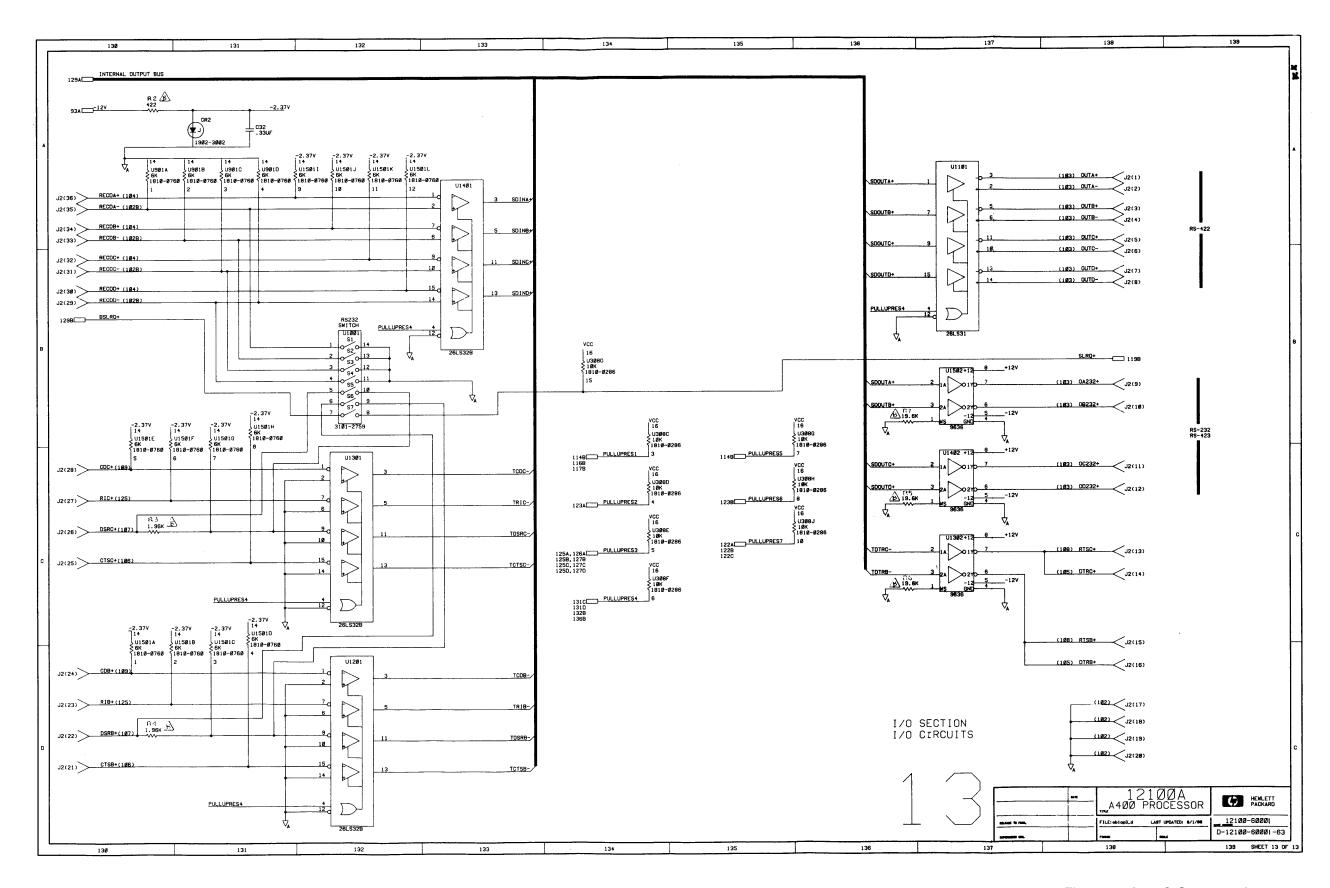

Chapter 5 - On-Board I/O

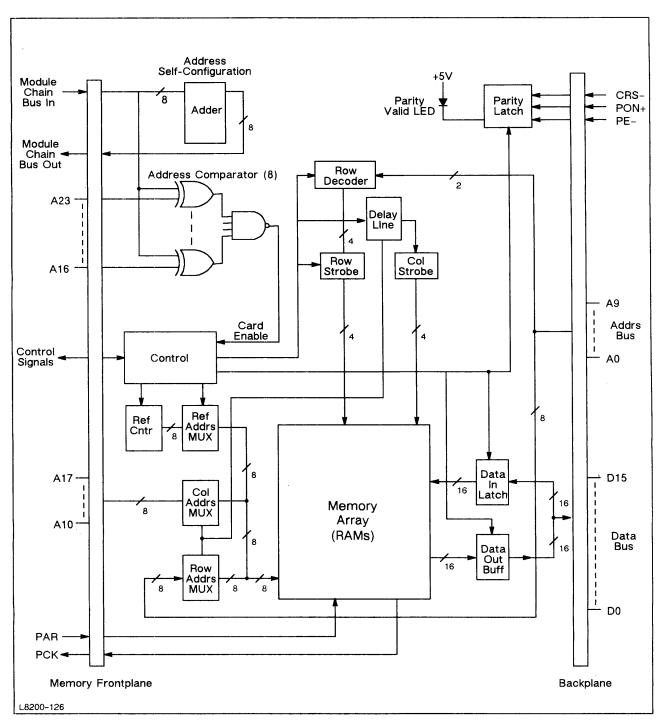

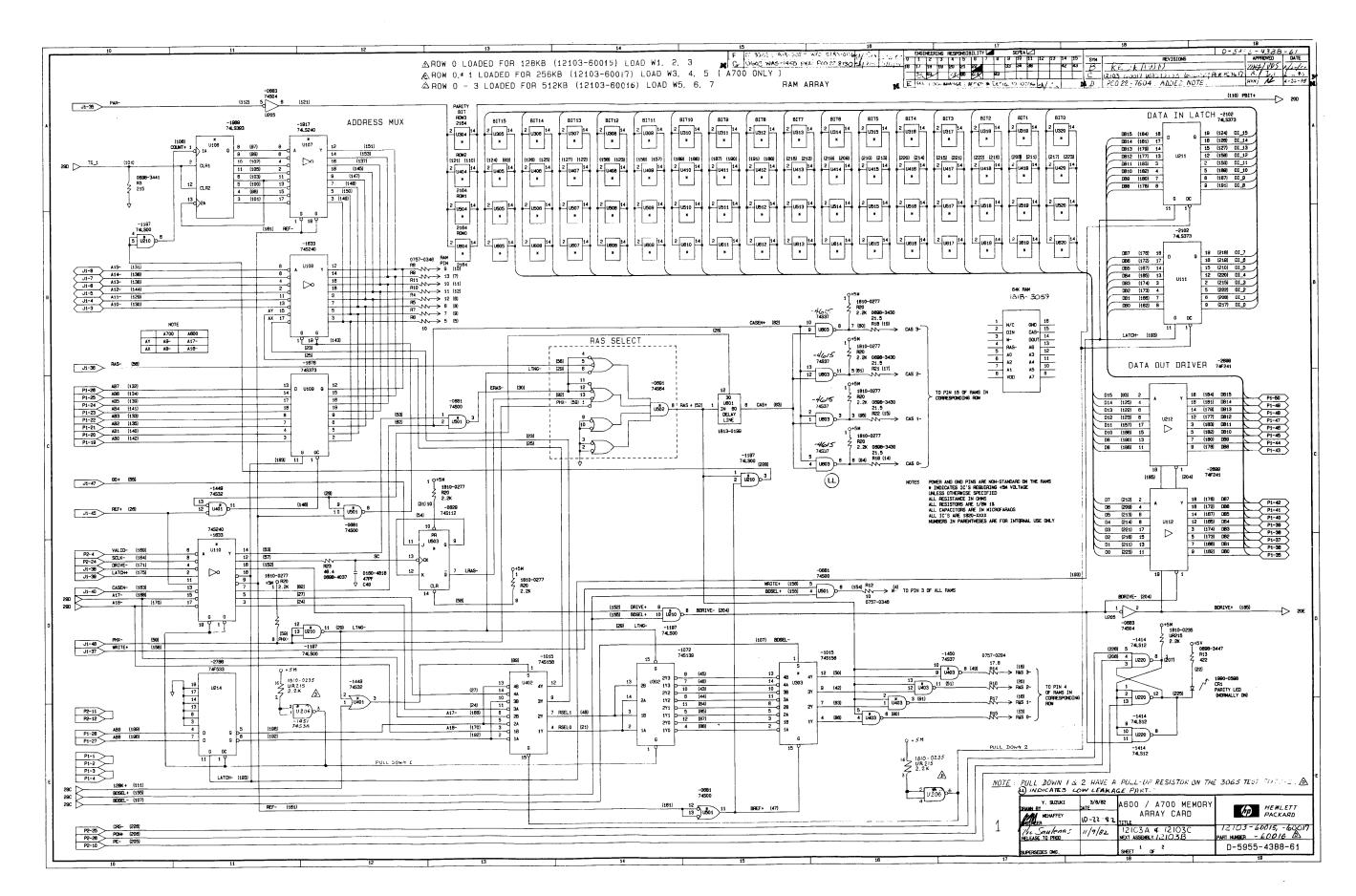

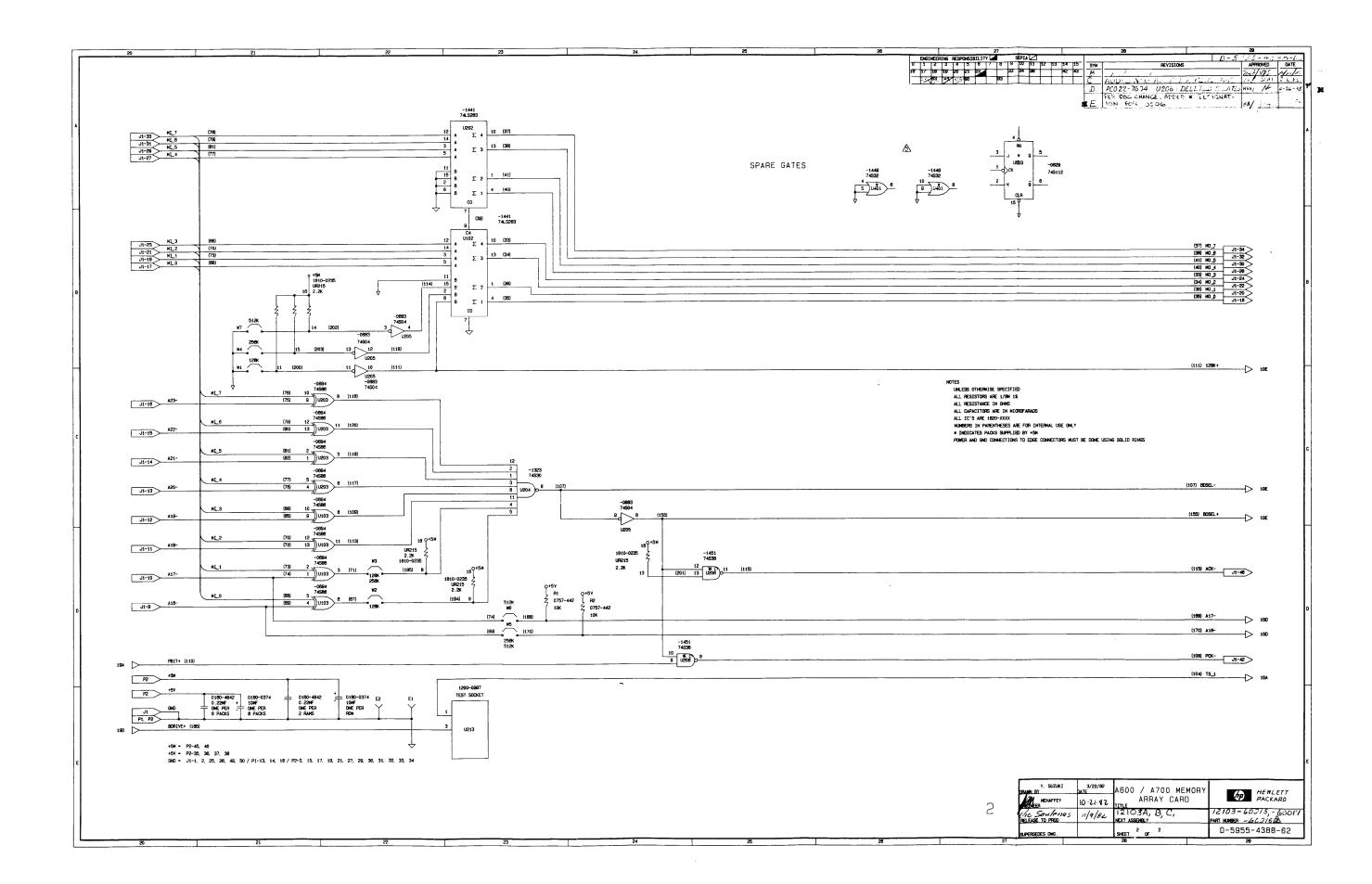

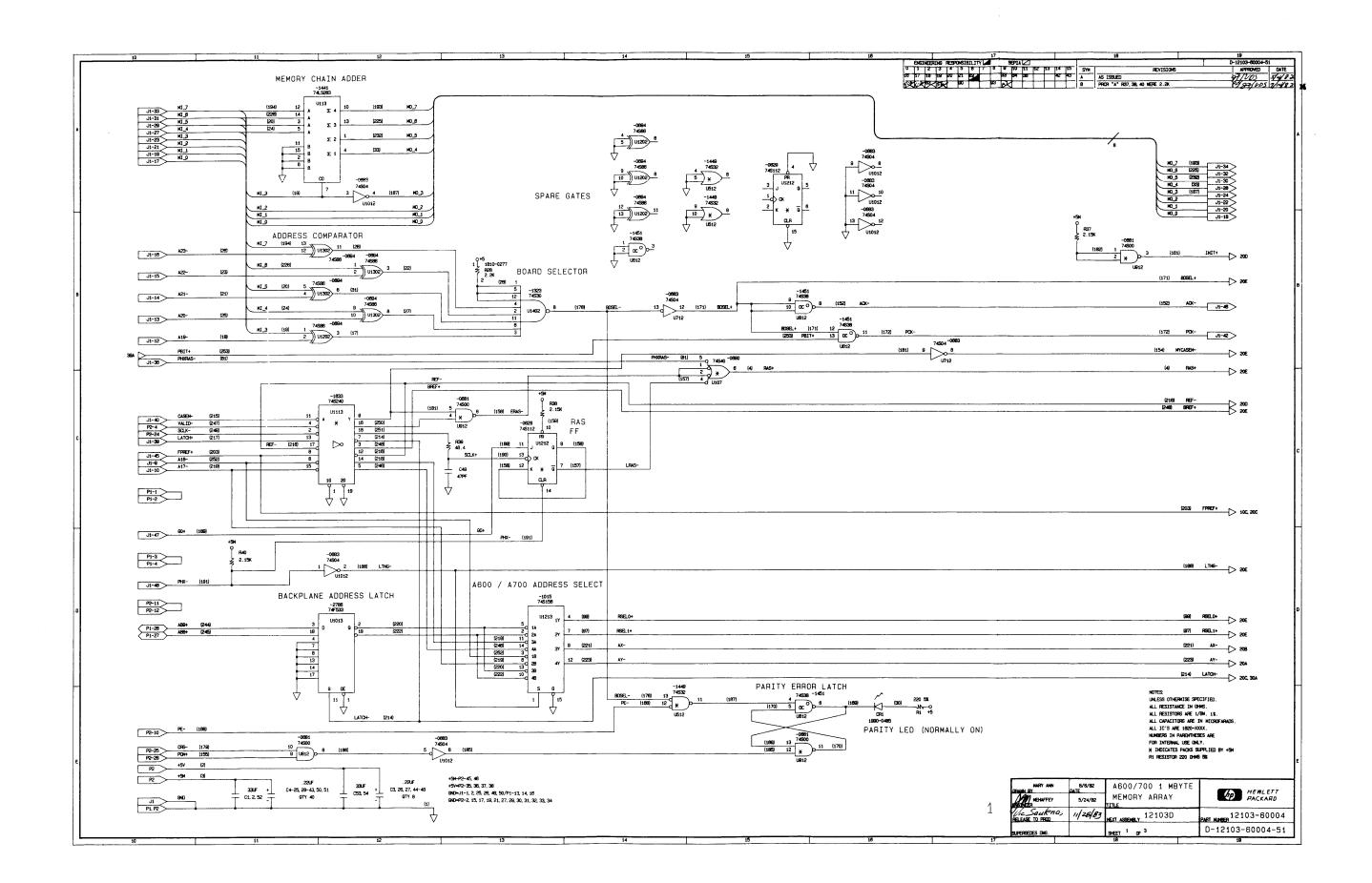

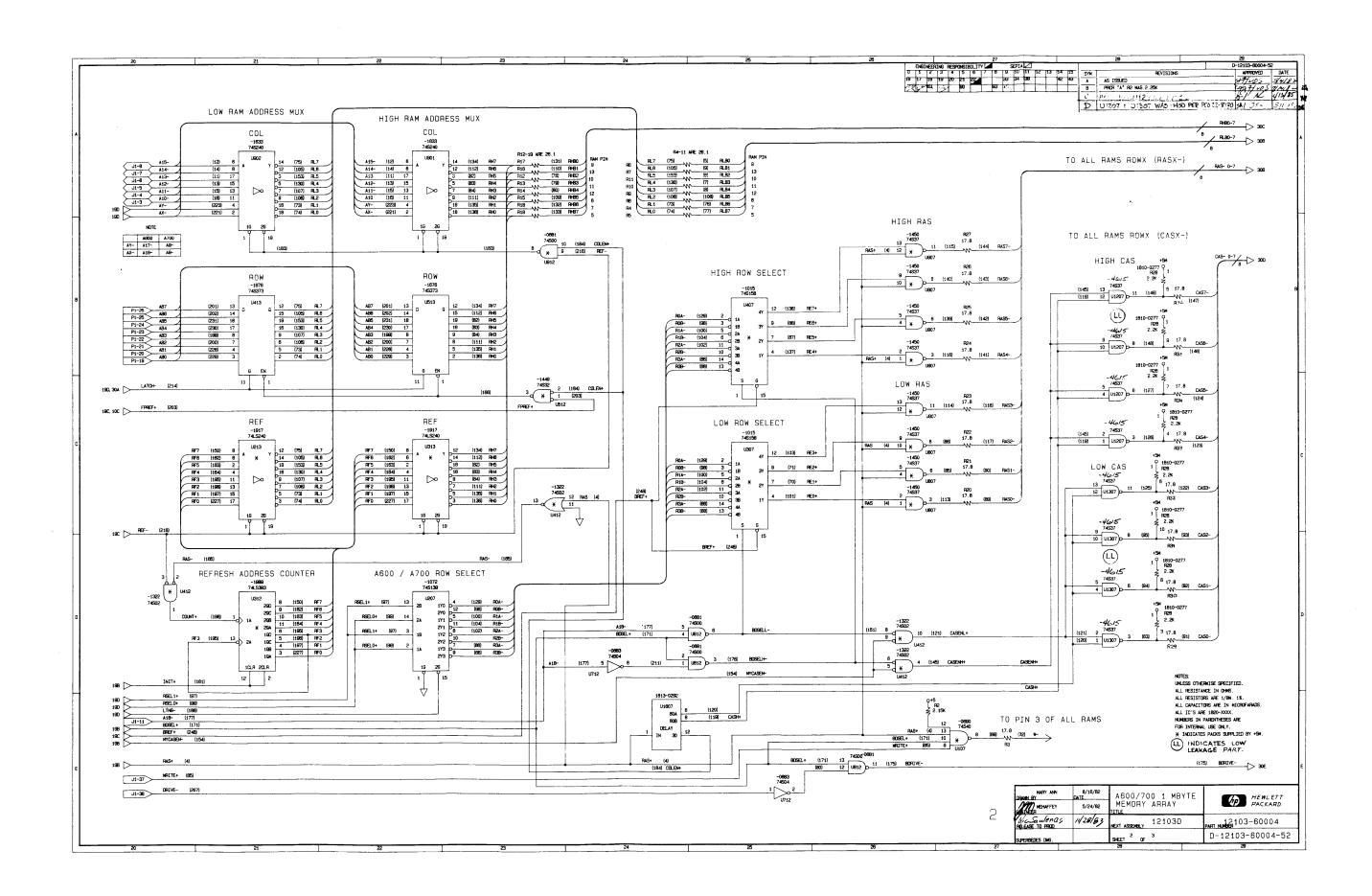

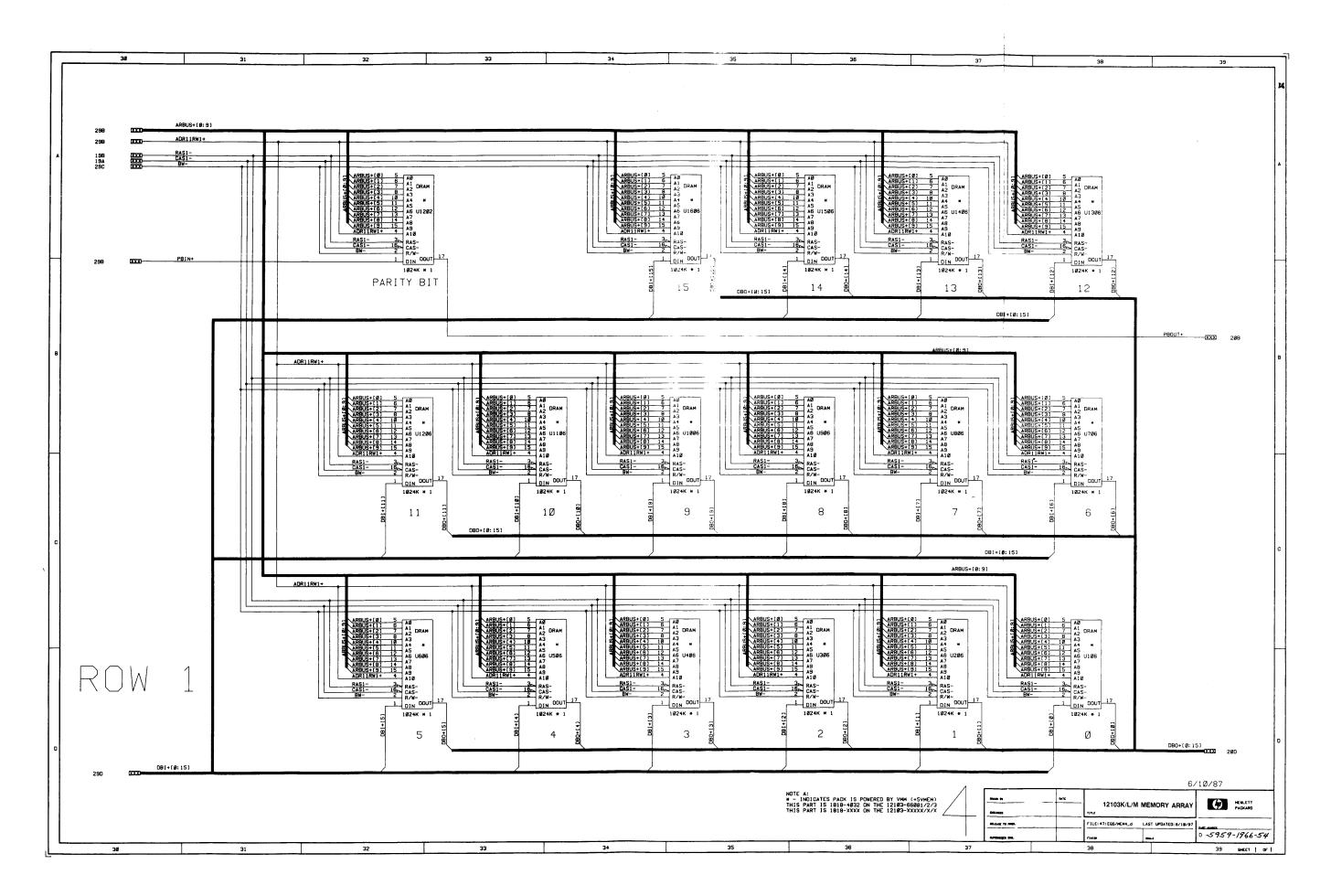

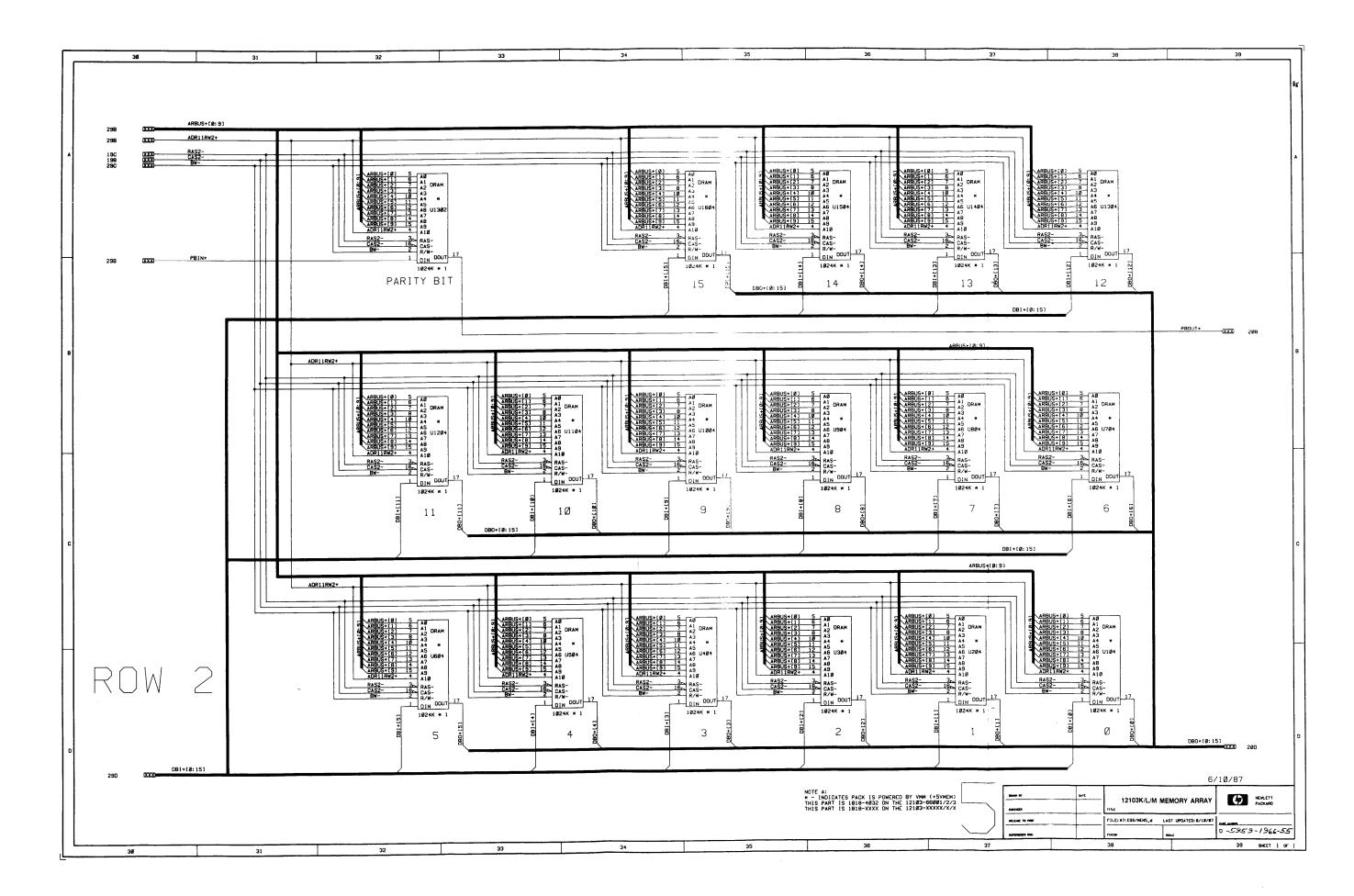

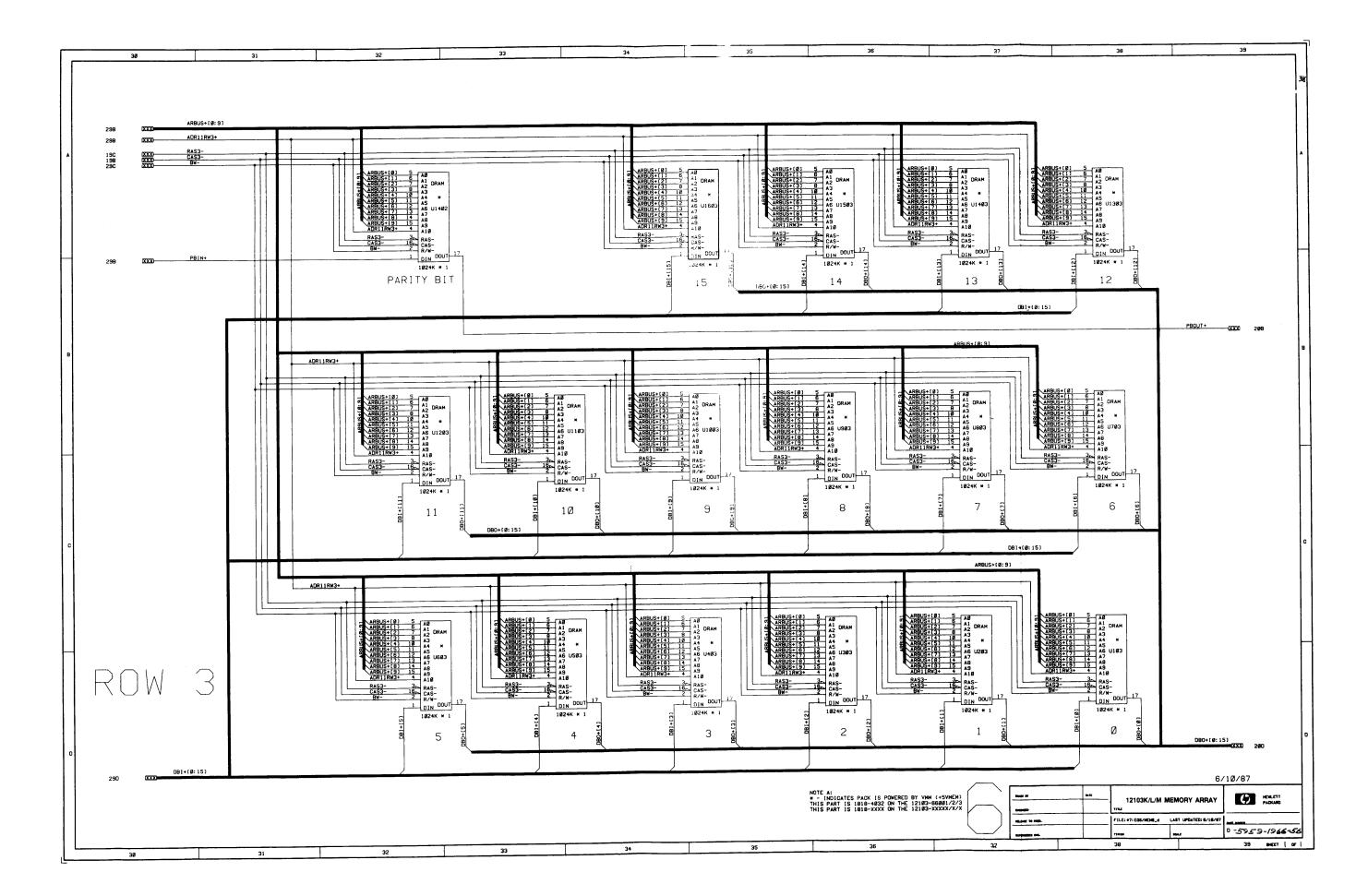

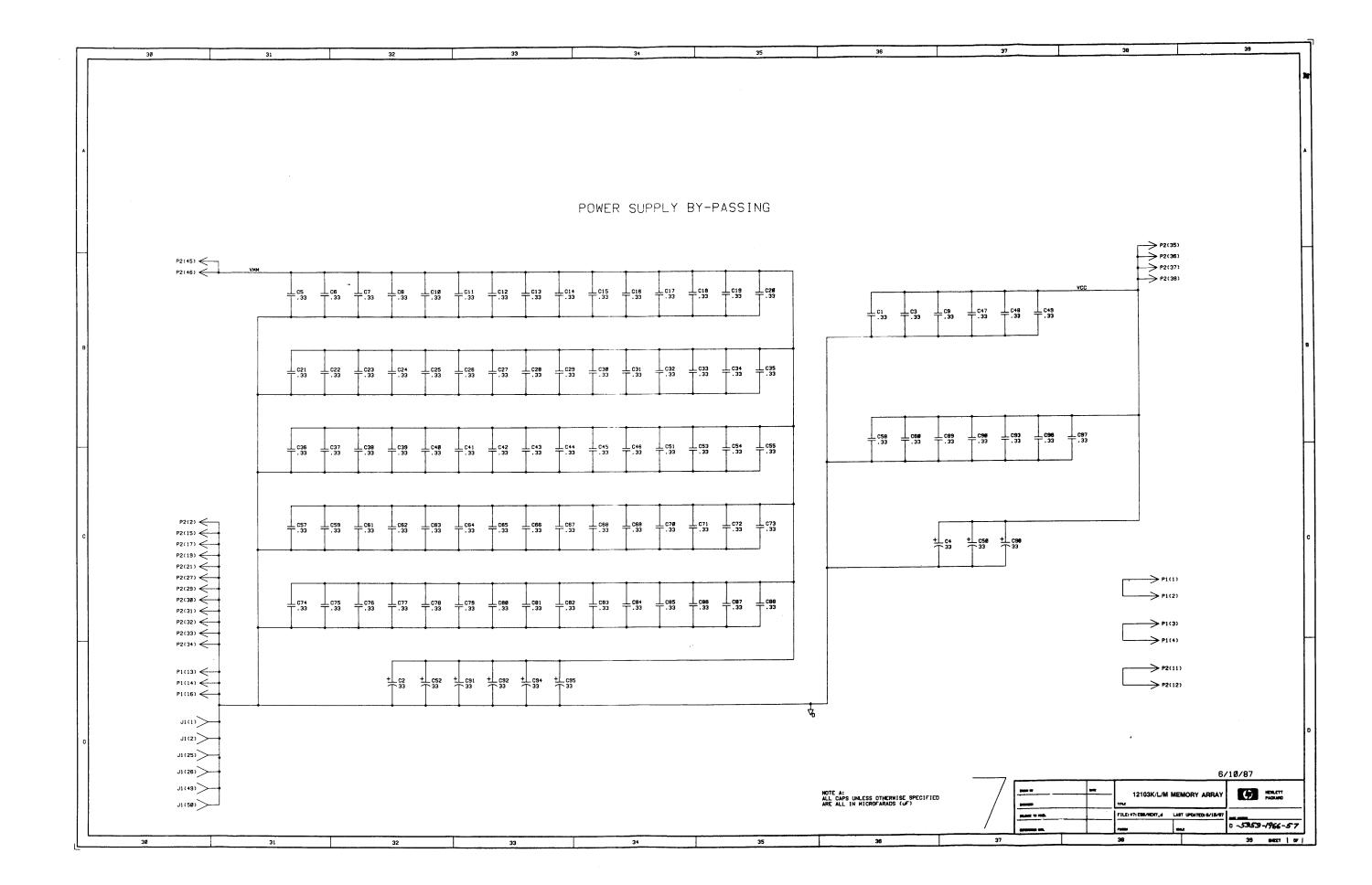

Chapter 6 – Memory Arrays

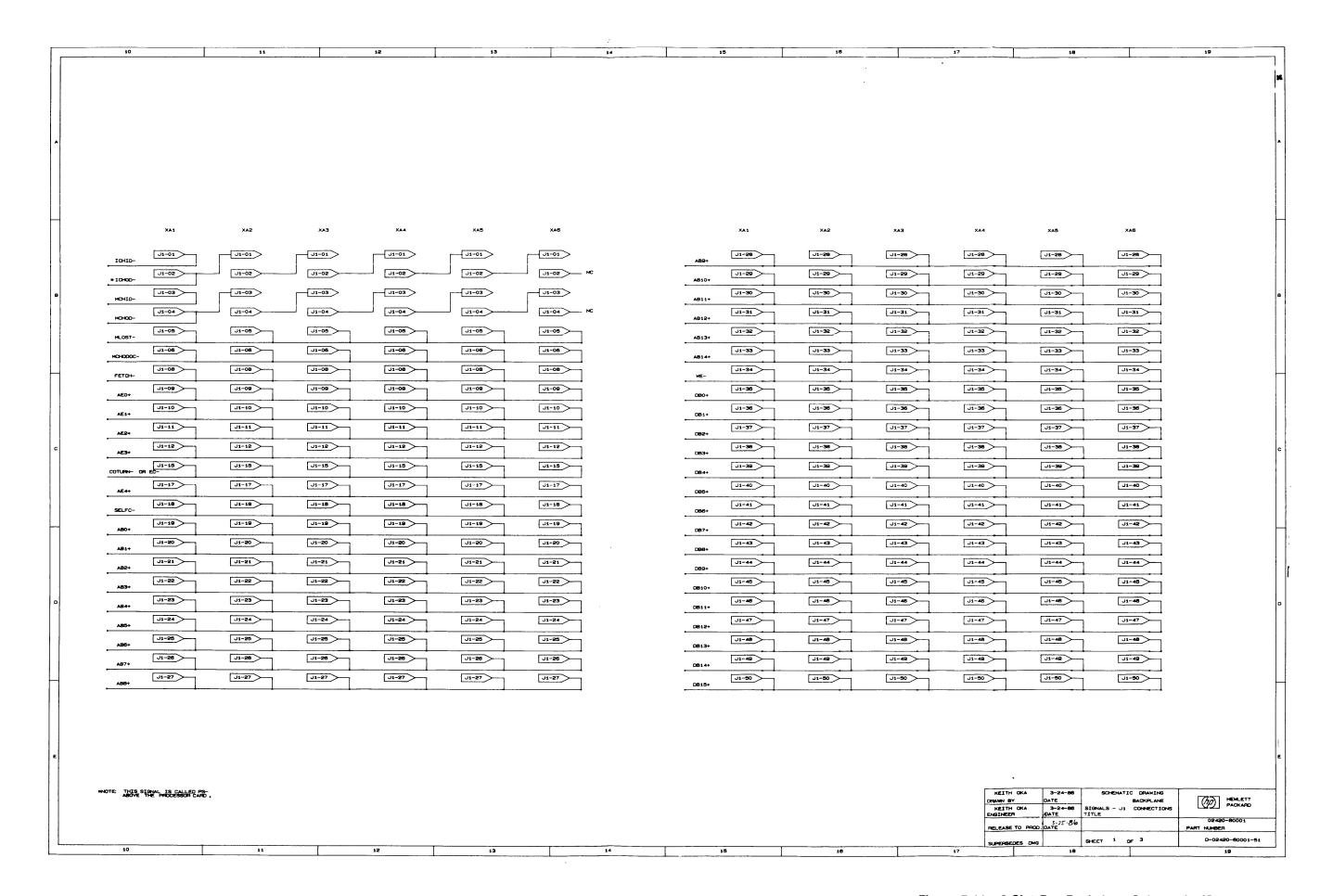

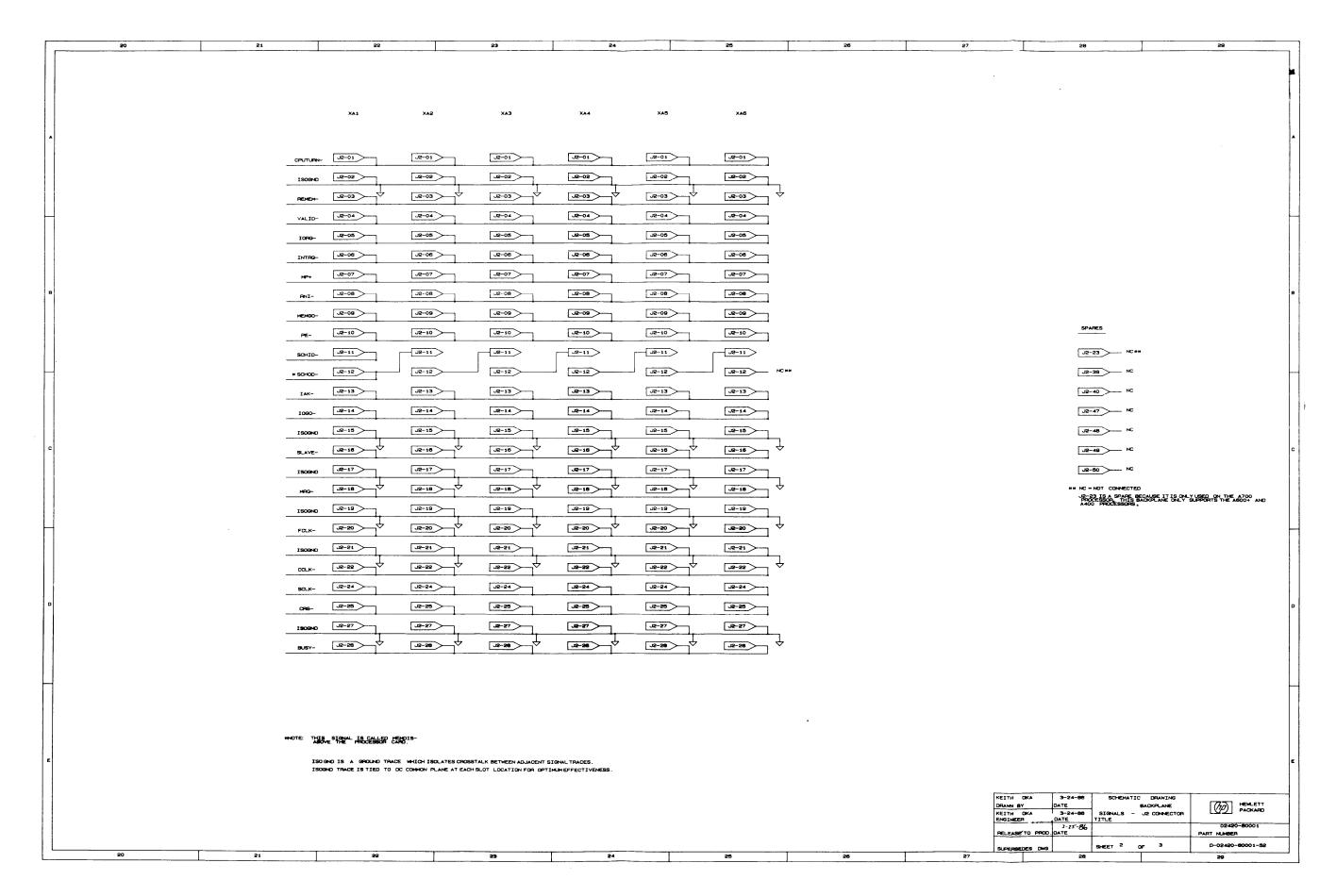

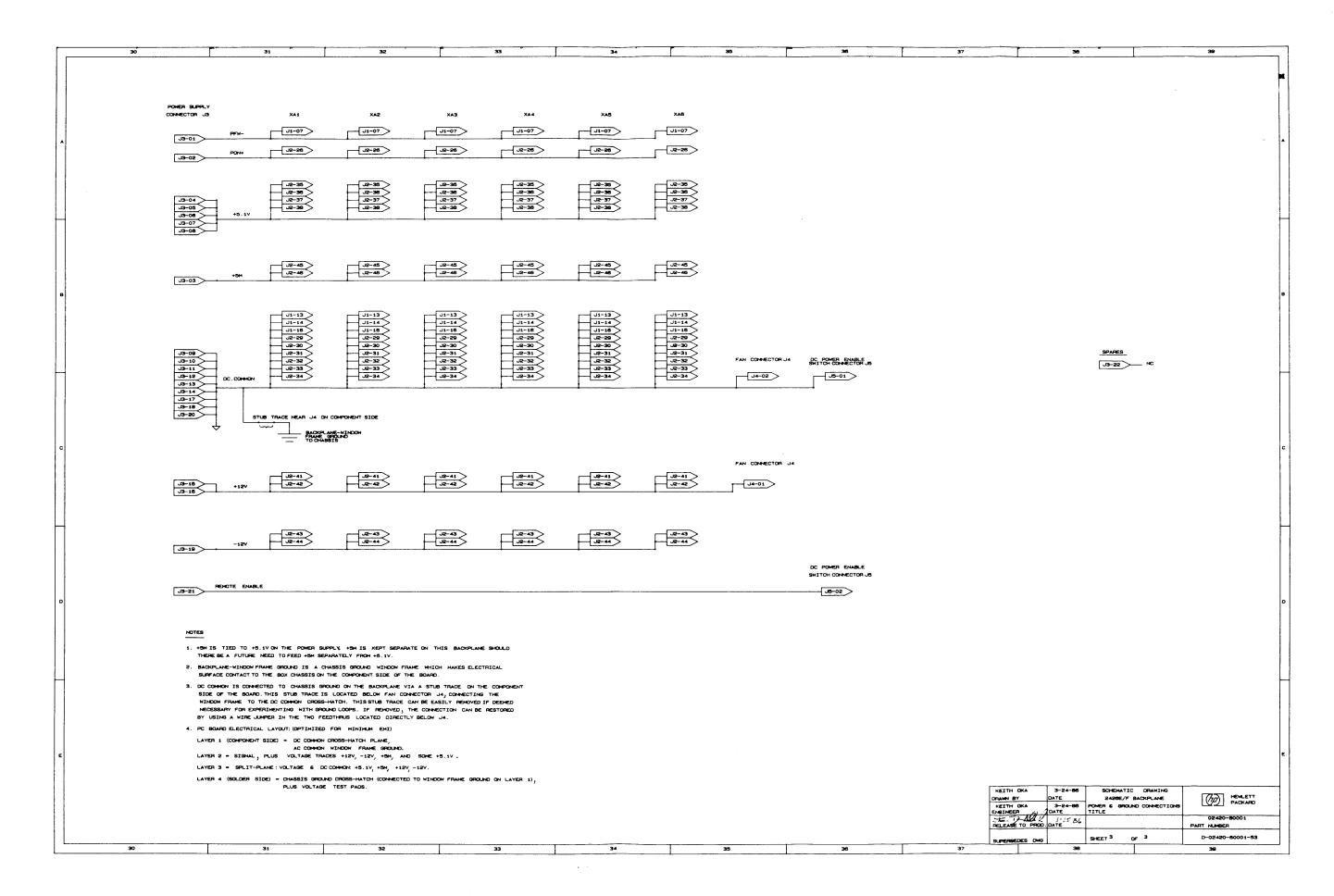

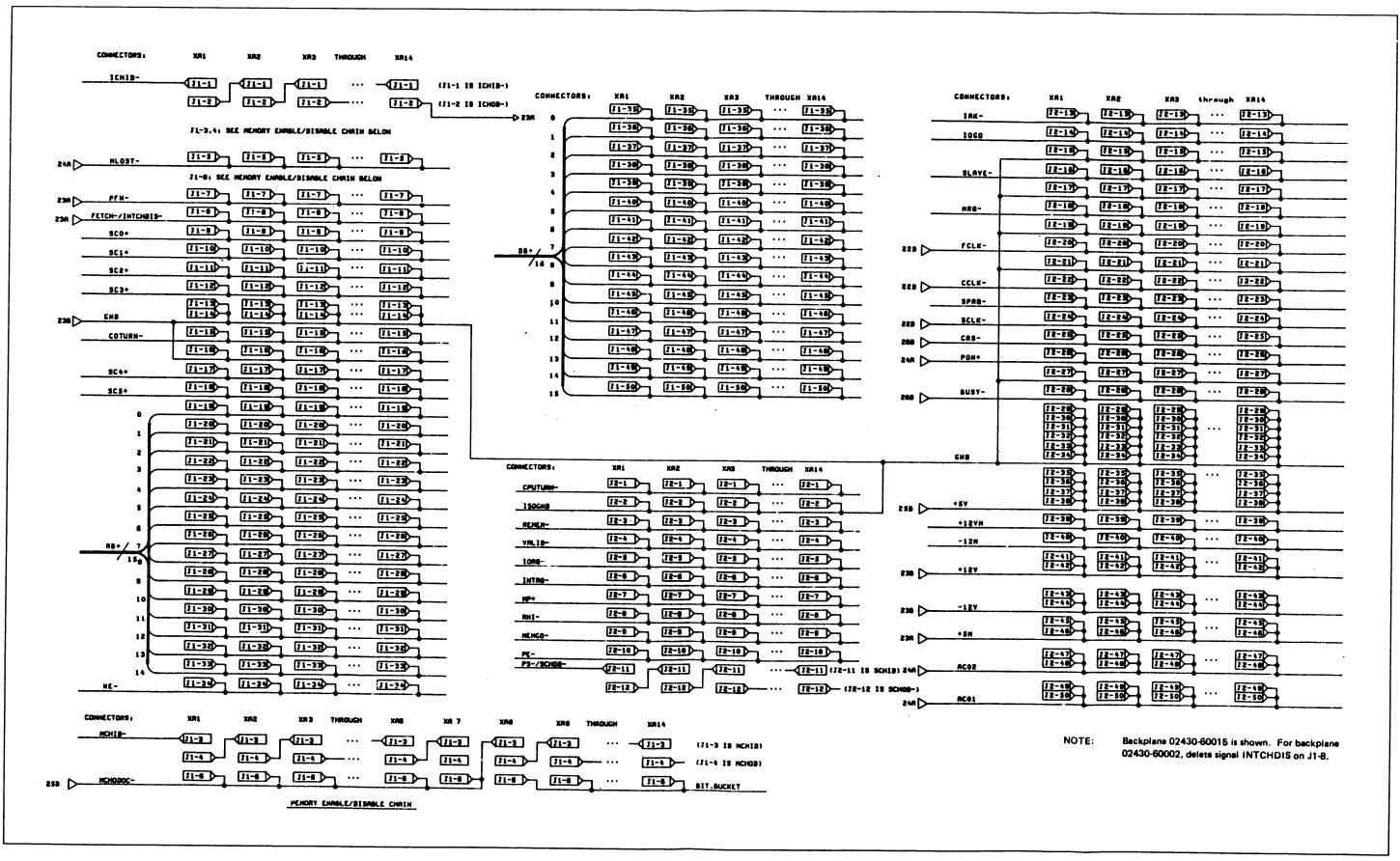

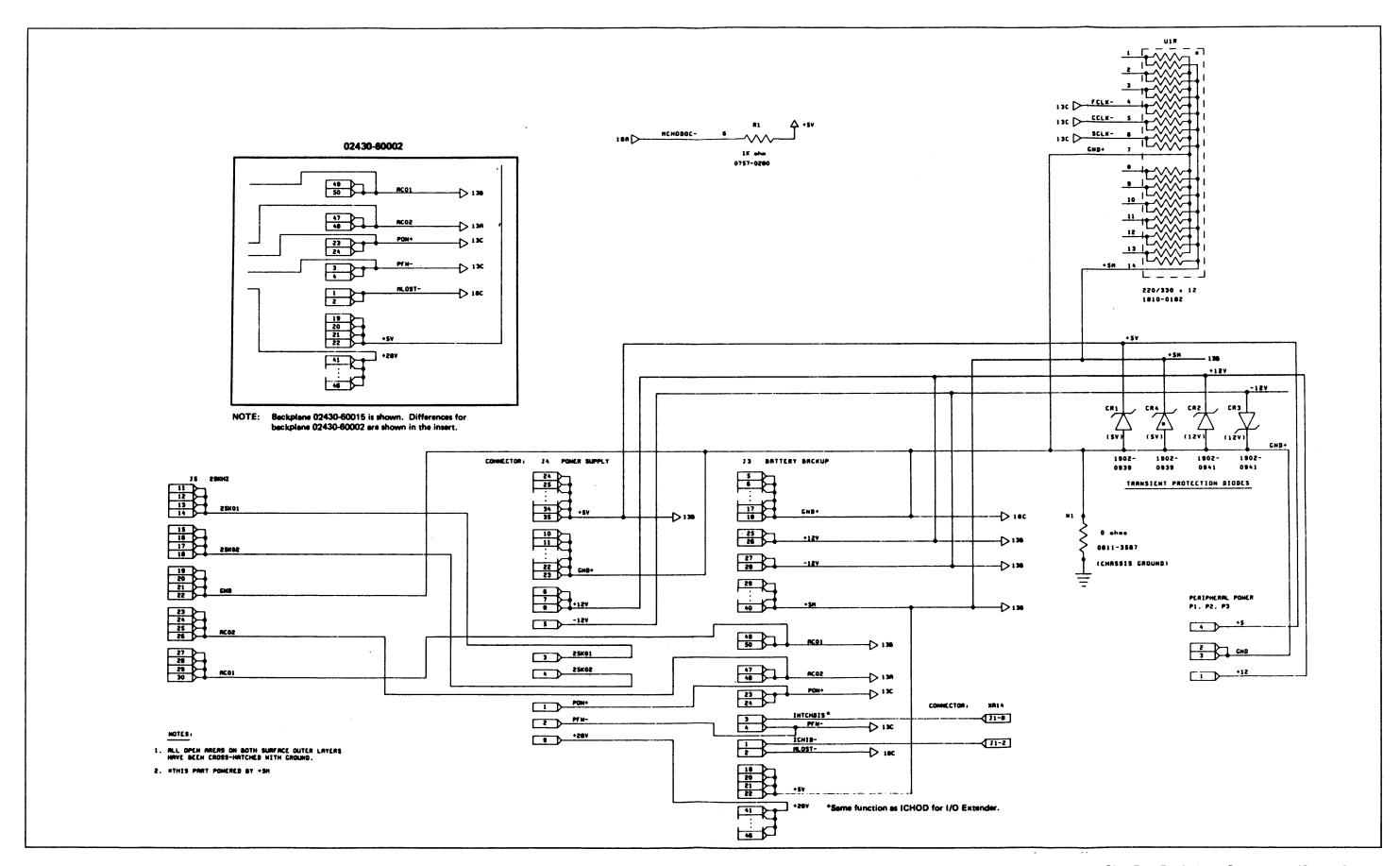

Chapter 7 - Backplane (Including I/O Requirements and Signal Timing)

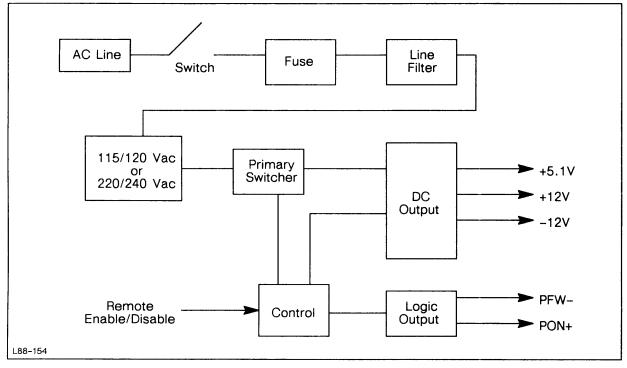

Chapter 8 – Power Supply

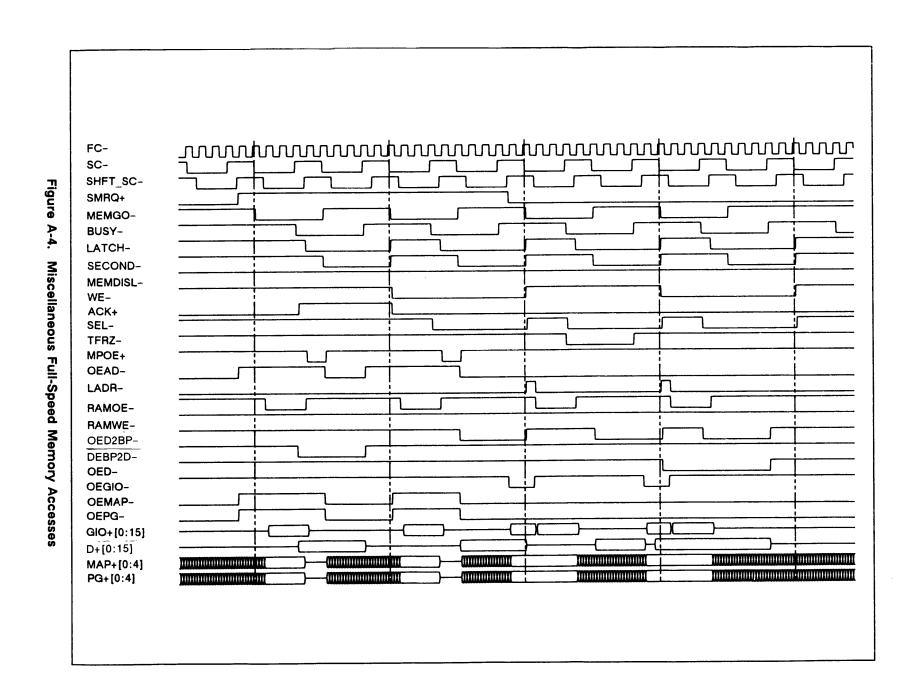

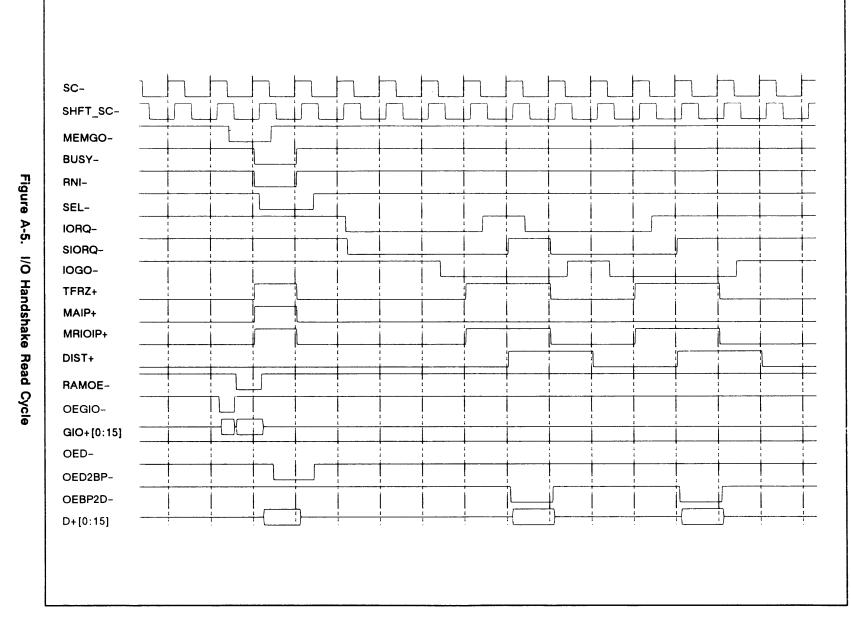

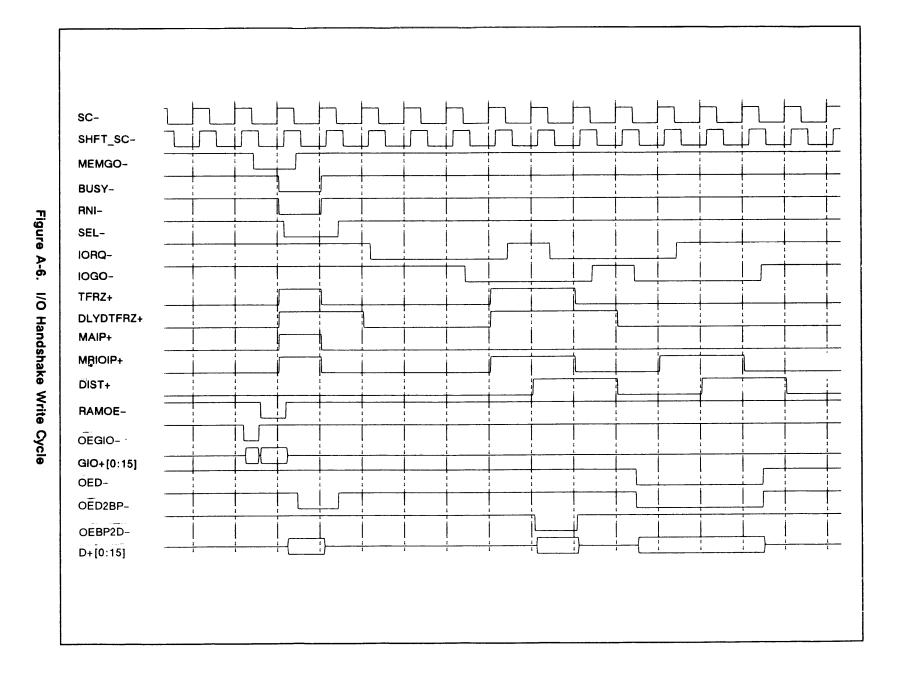

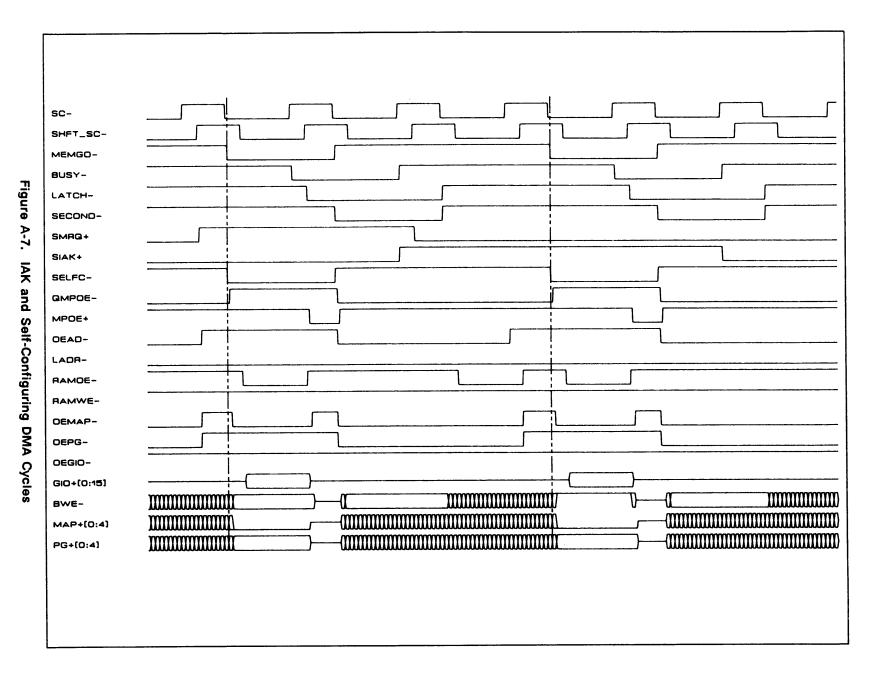

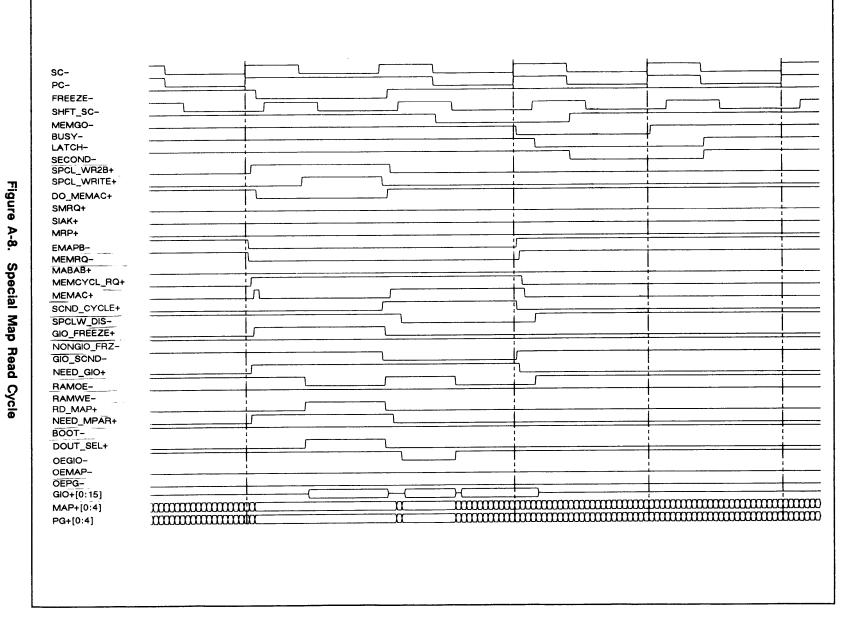

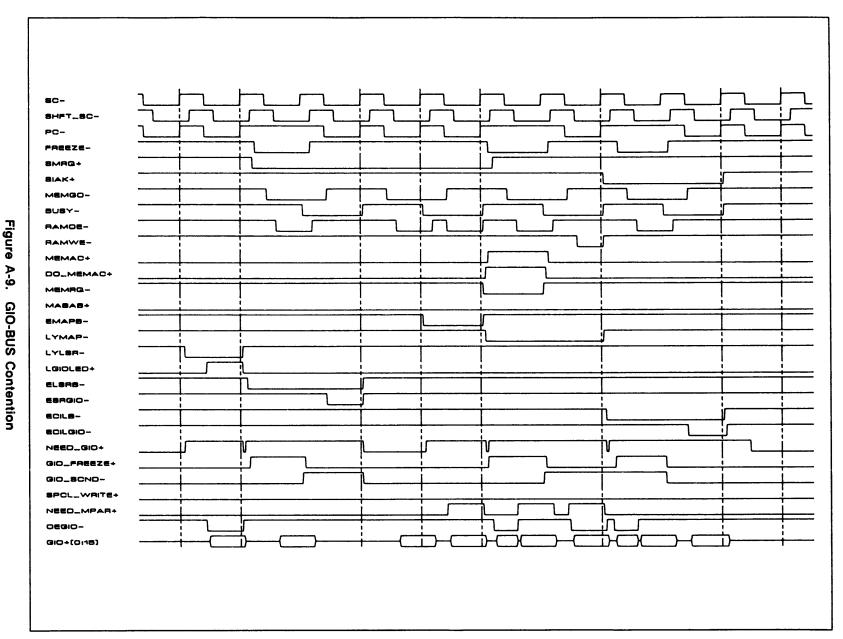

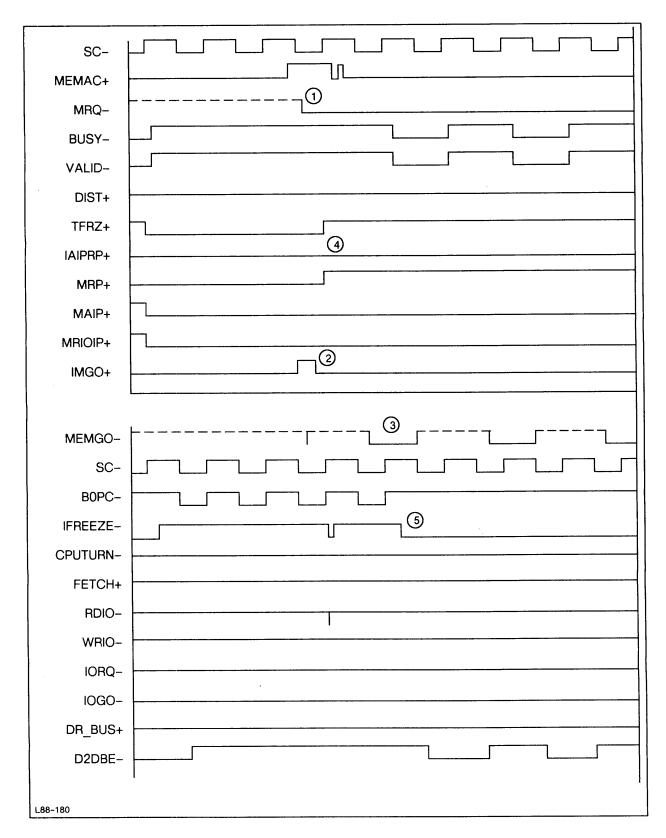

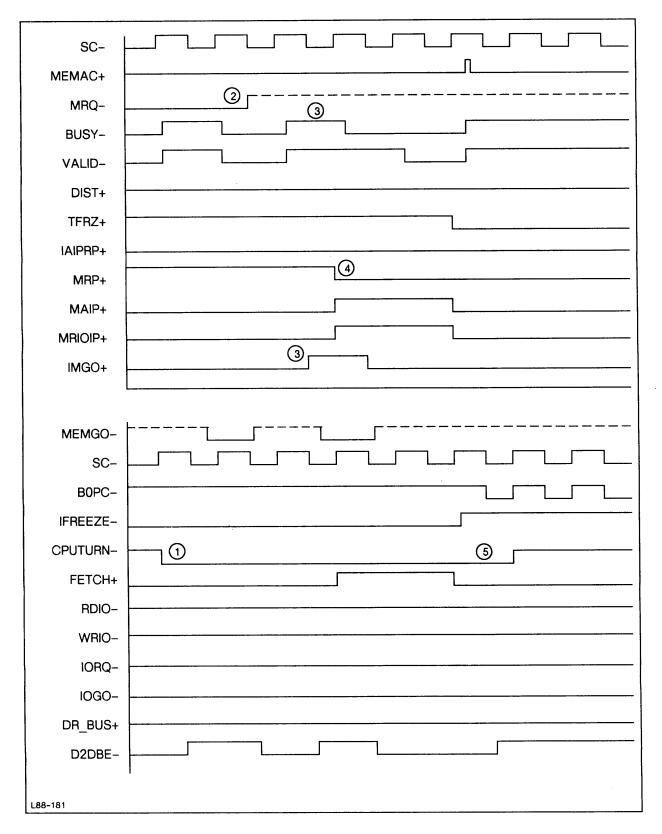

Appendix A - Bus Control Timing Diagrams

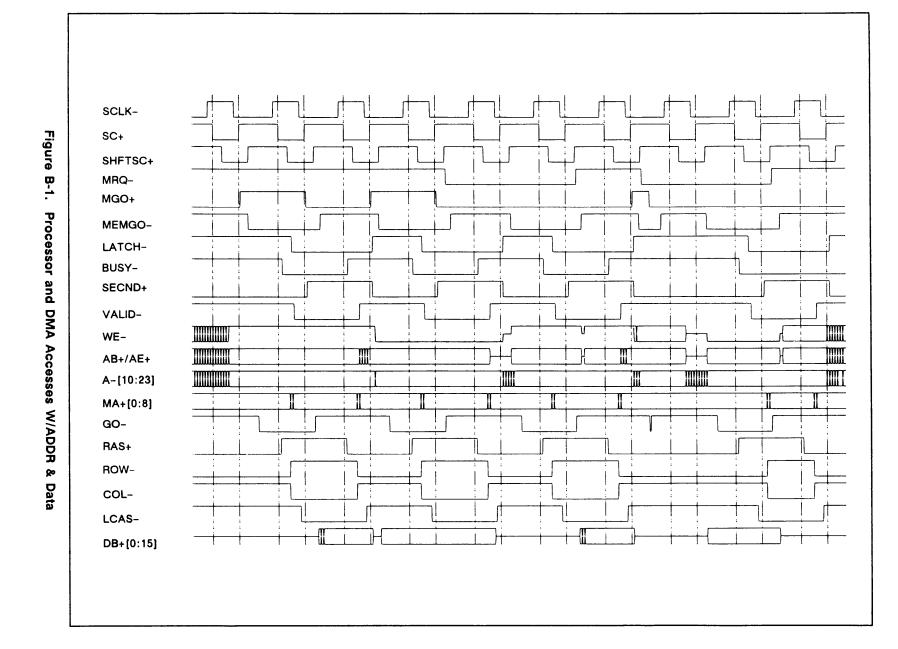

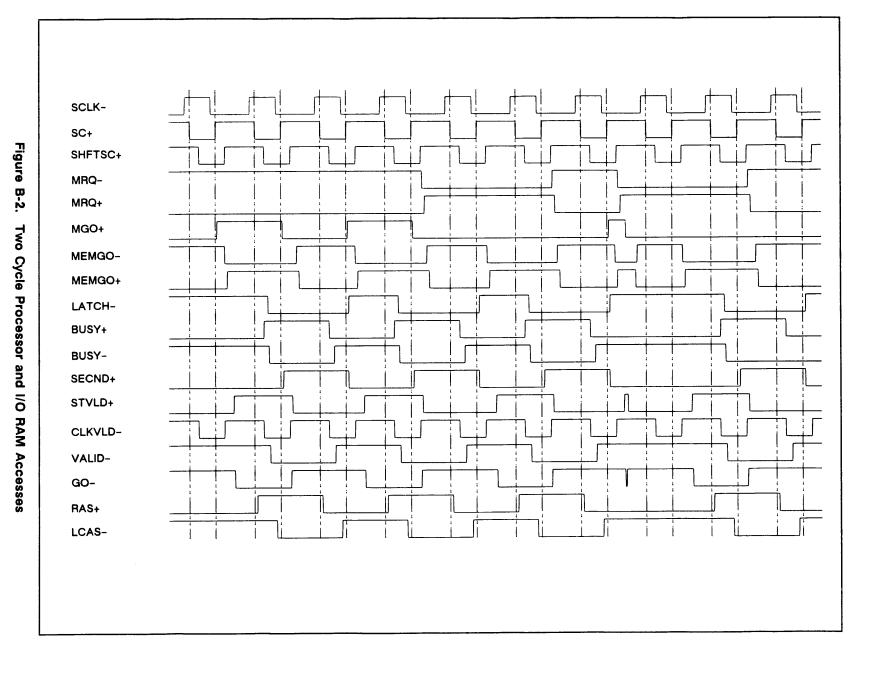

Appendix B - Memory Control Timing Diagrams

Appendix C - Processor Memory Access Cases

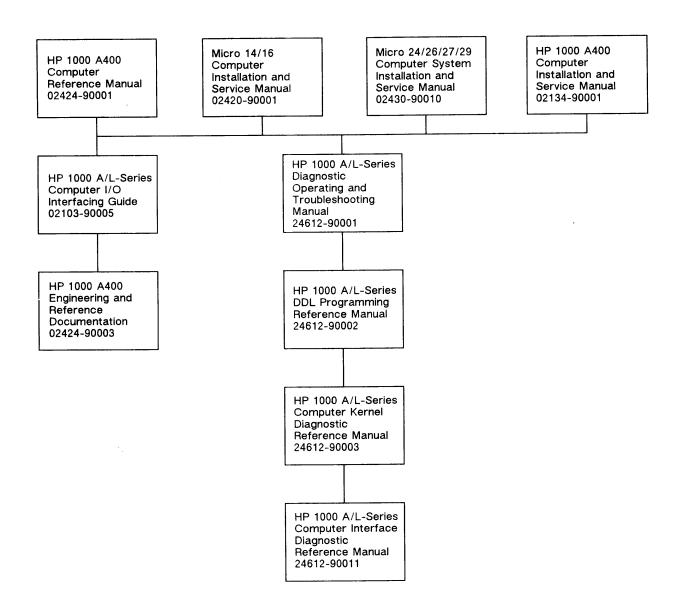

#### **Documentation Map**

# **Table of Contents**

| Chapter 1<br>HP 1000 A400 Computer                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Introduction Physical Description System Environment Description of Operation The VLSI Processor Chip The On-Board I/O System Support Features Virtual Control Panel (VCP) Self-Test Capability User Microprogramming Power and Cooling Requirements DC Power Regulation Provided by the Power Supplies Cooling Requirements Environmental Specifications Card Cage and Backplane Assemblies | 1-1<br>1-3<br>1-3<br>1-4<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-5<br>1-6                          |

| Chapter 2 A400 Board Operation                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

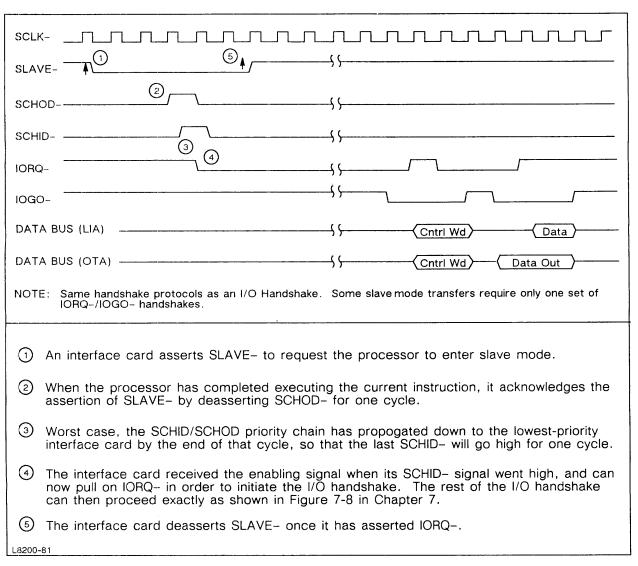

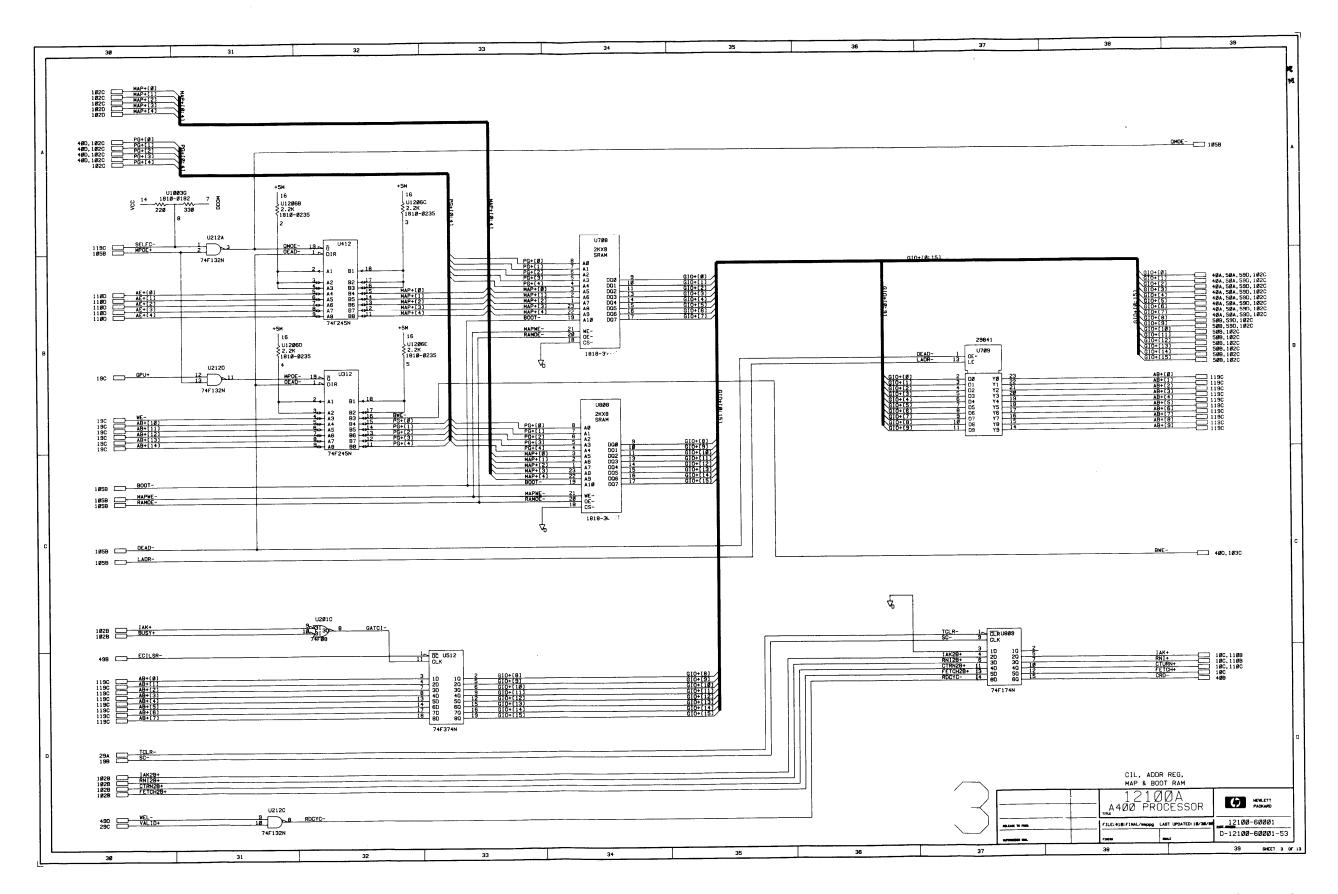

| Board Design Philosophy High-Level Organization Conventions The D-Bus The GIO-Bus Map/Boot SRAM Offset Address Latch and GIO-Bus Usage During a Memory Access Parity Error Register (PER) Central Interrupt Latch (CIL) Switch Register LED Register The Map-Bus The PG-Bus Clock Generation Control Store Backplane Buffers Virtual Control Panel (Slave Mode) Processing Battery Back-Up   | 2-1<br>2-1<br>2-2<br>2-2<br>2-5<br>2-6<br>2-6<br>2-7<br>2-7<br>2-7<br>2-10<br>2-11<br>2-11<br>2-12 |

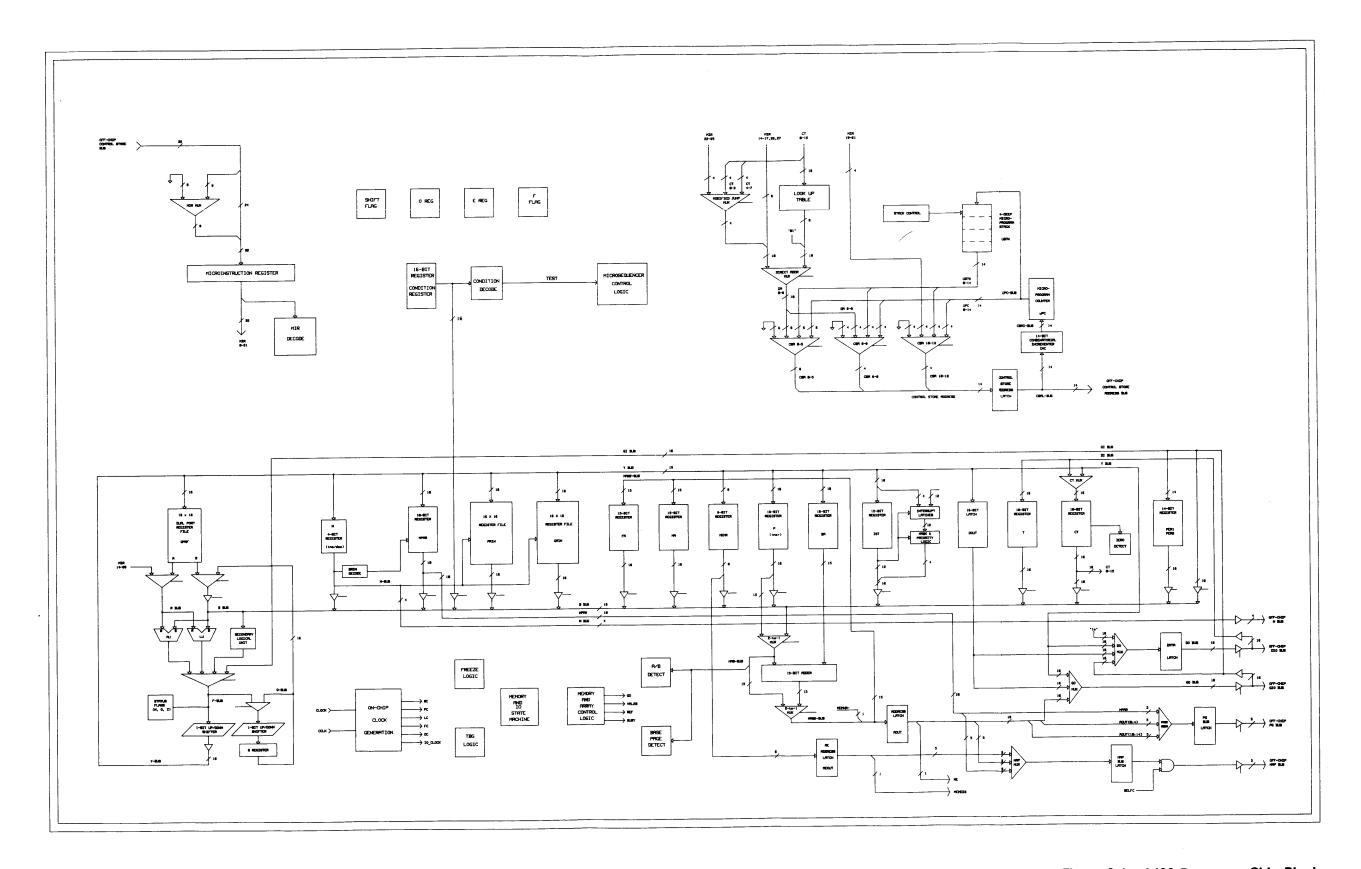

# **Chapter 3 Processor Chip Theory of Operation**

| Conventions                                  | 3-2  |

|----------------------------------------------|------|

| Error Correction Support                     | 3-2  |

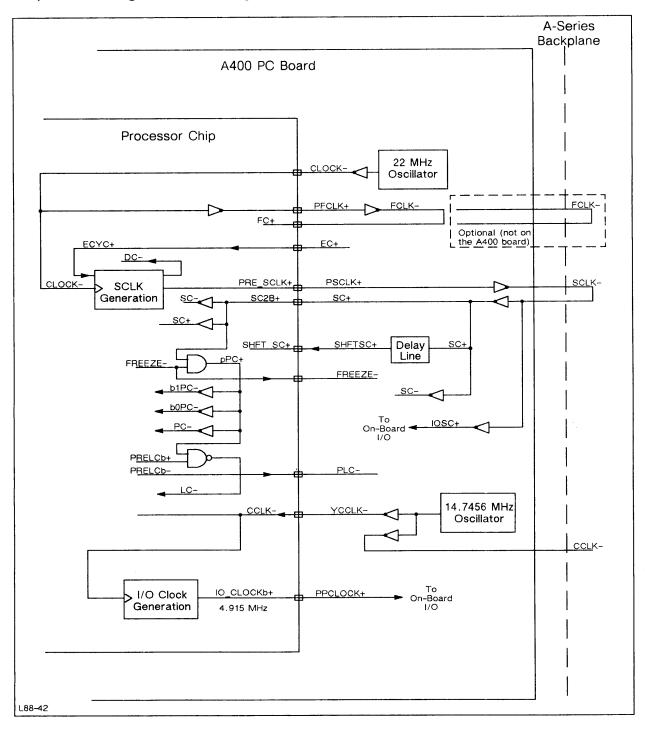

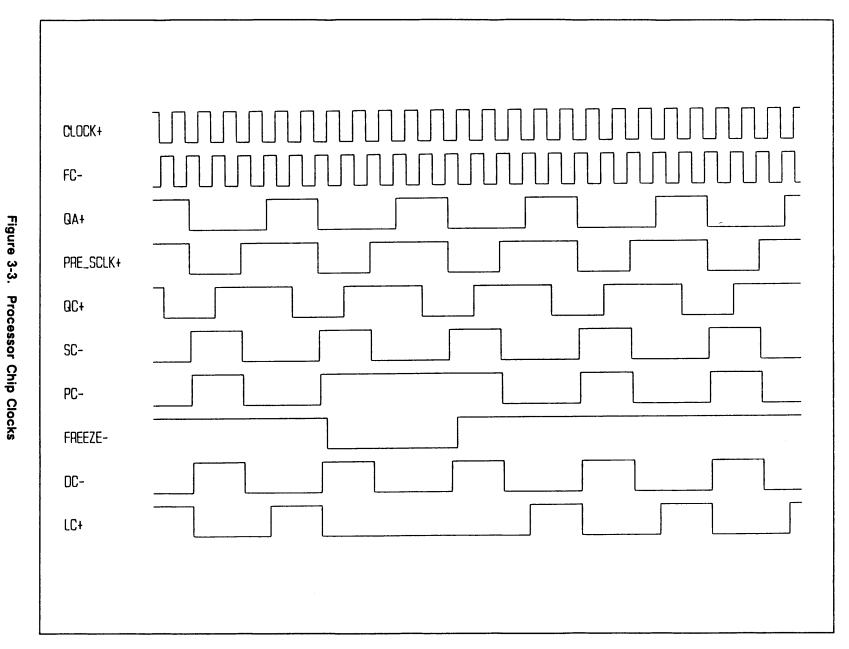

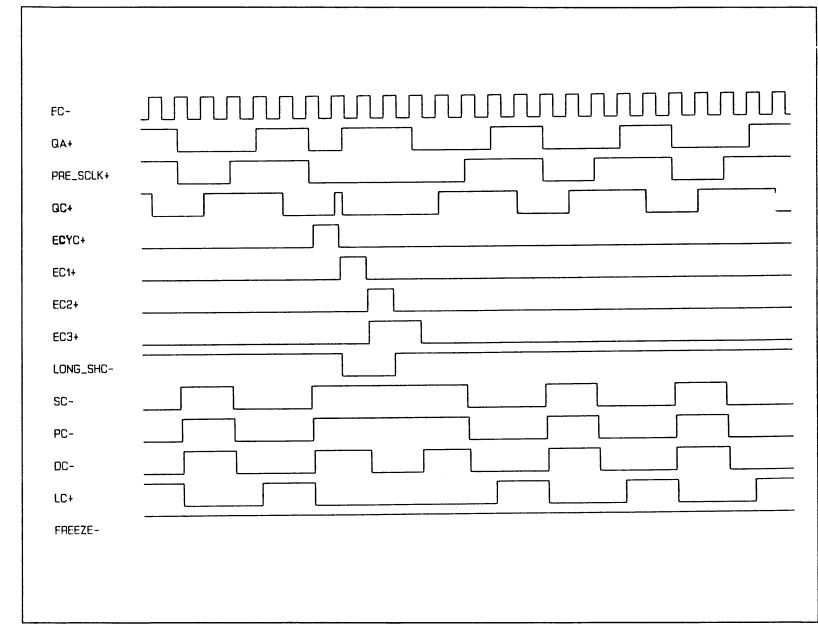

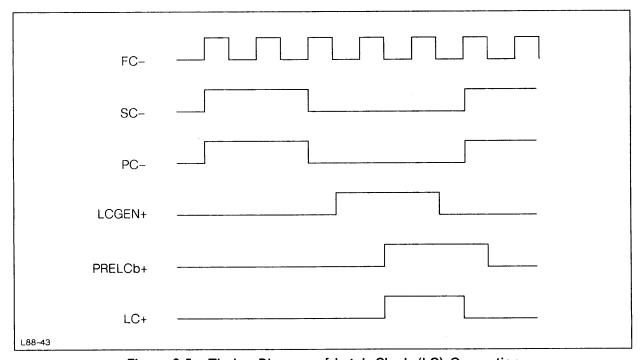

| Clock Generation                             | 3-5  |

| General Description                          | 3-5  |

| Theory of Operation                          | 3-5  |

| Microinstruction Register (MIR) and Decoders | 3-11 |

| General Description                          | 3-11 |

| Theory of Operation                          | 3-12 |

| OP-Field                                     | 3-15 |

| SP0/SP1/SP2-Field Decode                     | 3-15 |

| ABUS-Field Decoding                          | 3-17 |

| BBUS-Field Decoding                          | 3-18 |

| STORE-Field Decoding                         | 3-19 |

| MRG Instruction Decoder                      | 3-20 |

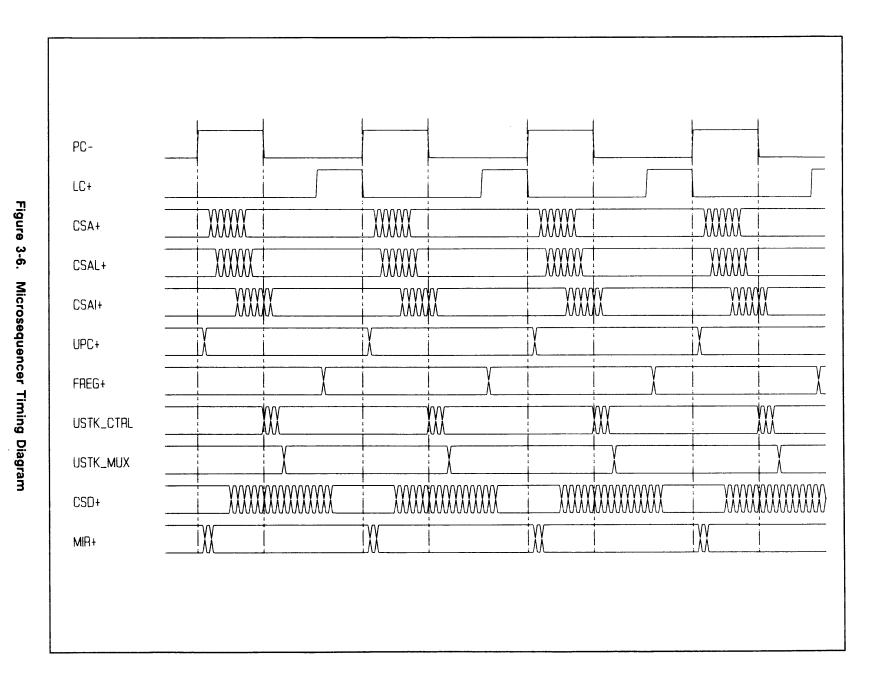

| Microsequencer                               | 3-21 |

| General Description                          | 3-21 |

| Theory of Operation                          | 3-22 |

| Sequencer Multiplexer and Control            | 3-22 |

| Incrementer                                  | 3-25 |

| Microprogram Counter (mPC)                   | 3-26 |

| Four-Deep Stack                              | 3-26 |

| Direct Address Generation                    | 3-27 |

| Look-Up Table                                | 3-28 |

| Control Store                                | 3-30 |

| Condition Register                           | 3-33 |

| General Description                          | 3-33 |

| Theory of Operation                          | 3-33 |

| The PON and IORQ Synchronizers               | 3-35 |

| Macro O- and E-Registers                     | 3-35 |

| The General Purpose Flag (F)                 | 3-36 |

| The Shift Flag (SF)                          | 3-37 |

| The Double Word Flag (DW)                    | 3-37 |

| Counter                                      |      |

| General Description                          | 3-37 |

| Theory of Operation                          | 3-38 |

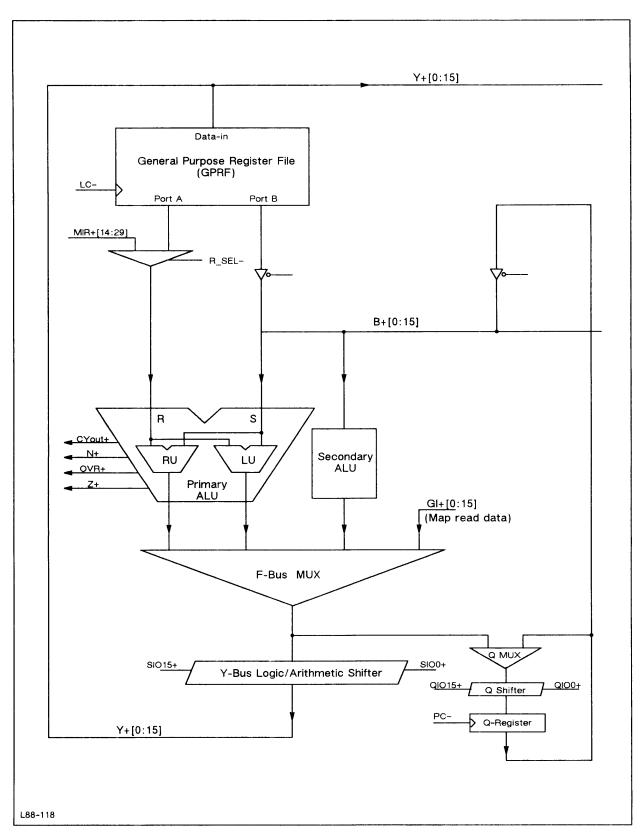

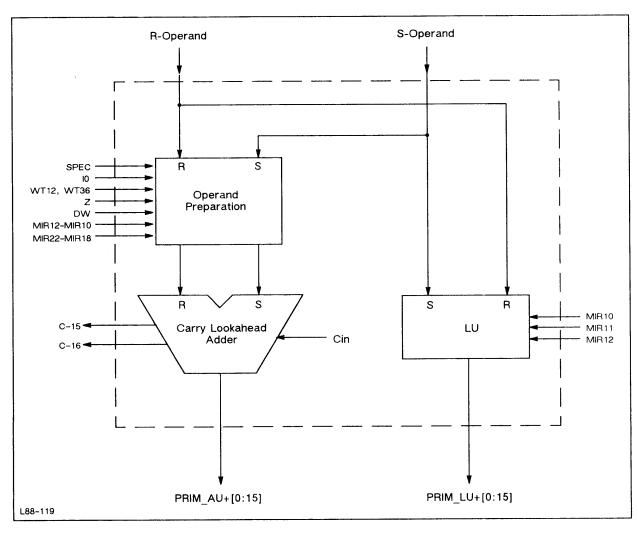

| Arithmetic and Logical Unit (ALU)            | 3-40 |

| General Description                          | 3-40 |

| Theory of Operation                          |      |

| Primary ALU R-Operand Selection              |      |

| Primary ALU Logic                            | 3-43 |

| General Purpose Register File (GPRF)         | 3-51 |

| The Q-Register and the Q-Register Shifter    | 3-52 |

| ALU Status Flags                             | 3-53 |

| Carry-In Generation                          | 3-54 |

| Instruction Bits I5-I8 Generation            |      |

| Secondary Logical Unit                       | 3-57 |

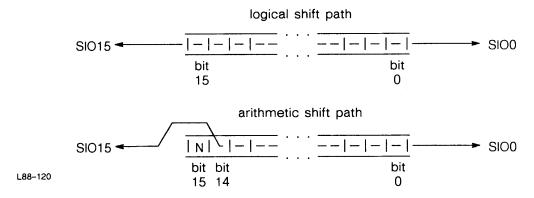

| Shift Linkage                                         | 3-59 |

|-------------------------------------------------------|------|

| Register Files                                        | 3-61 |

| General Description                                   | 3-61 |

| Theory of Operation                                   | 3-61 |

| PŘIN and GRIN Register Files                          | 3-61 |

| The N (Index) Register                                | 3-62 |

| Map Address Register (MPAR)                           | 3-63 |

| The Central Interrupt Latch (CIL)                     | 3-63 |

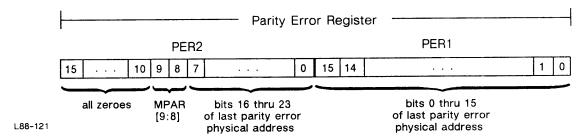

| Parity Error Register                                 | 3-63 |

| Memory Accessing                                      | 3-64 |

| General Description                                   | 3-64 |

| Direct Memory Access (DMA)                            | 3-64 |

|                                                       | 3-65 |

| Address Generation Logic                              | 3-65 |

| The T Pagiston                                        |      |

| The T-Register                                        | 3-65 |

| Memory Address Bus (MAB) Generation                   | 3-66 |

| Base Register Logic                                   | 3-67 |

| Memory Address and Data Latches                       | 3-68 |

| Memory and I/O State Machine and Control Logic        | 3-70 |

| General Description                                   | 3-70 |

| Theory of Operation                                   | 3-72 |

| MEMAC+ Generation                                     | 3-73 |

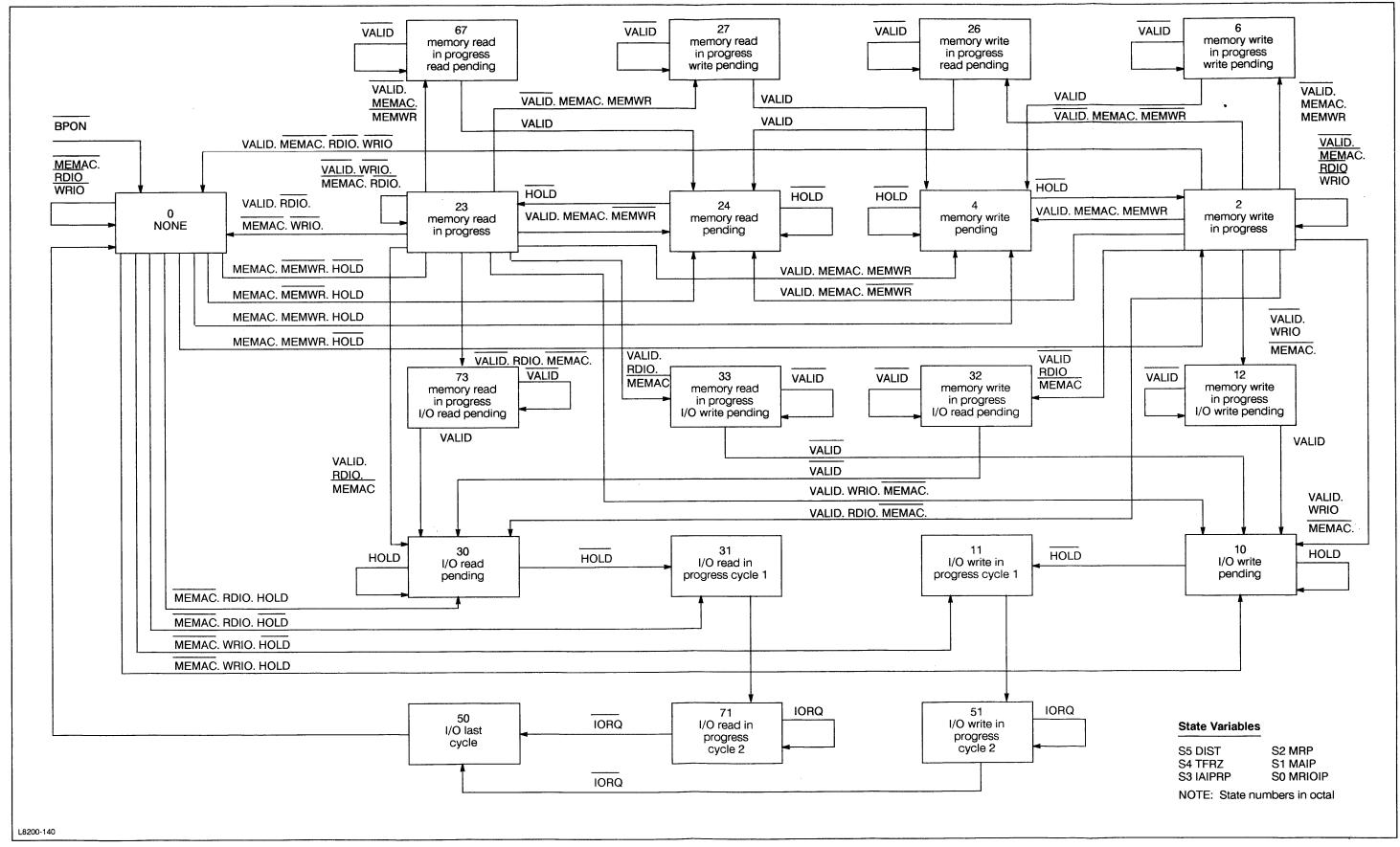

| Memory and I/O State Machine                          | 3-74 |

| Processor Chip Theory of Operation                    | 3-76 |

| MEMGO Circuitry                                       | 3-80 |

| A/B Fetch                                             | 3-81 |

| A/B-Register Detect Logic                             | 3-81 |

| CPUTURN Logic                                         | 3-82 |

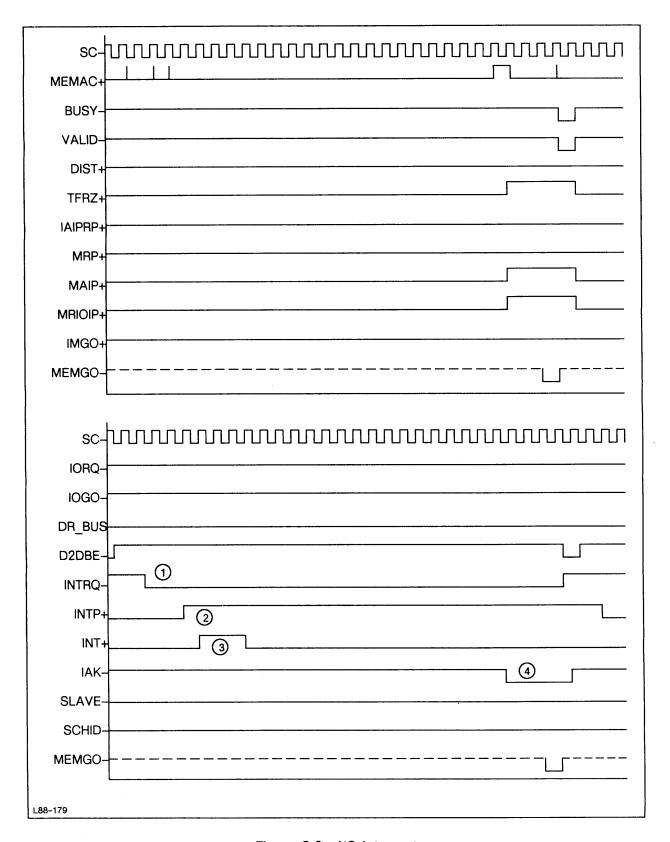

| Interrupt System                                      | 3-82 |

| General Description                                   | 3-82 |

| System Level and I/O Interrupts                       | 3-82 |

| Micromachine Interrupt Level                          | 3-82 |

| Theory of Operation                                   | 3-83 |

| Integrant Status (ICT) Posistor                       |      |

| Interrupt Status (IST) Register                       | 3-84 |

| Interrupt Sources                                     | 3-85 |

| Freeze Logic                                          | 3-87 |

| Time Base Generator (TBG)                             | 3-88 |

| Processor Chip Portion of Memory Controller Circuitry | 3-89 |

| General Description                                   | 3-89 |

| Theory of Operation                                   | 3-89 |

| GO- Generation                                        | 3-89 |

| BUSY- Generation                                      | 3-91 |

| VALID- Generation                                     | 3-91 |

| Refresh Circuitry                                     | 3-93 |

| Processor Chip I/O Control                            | 3-94 |

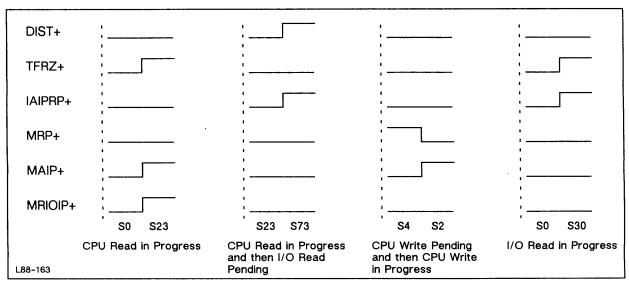

| Bus Control Functional Description                    | 3-95 |

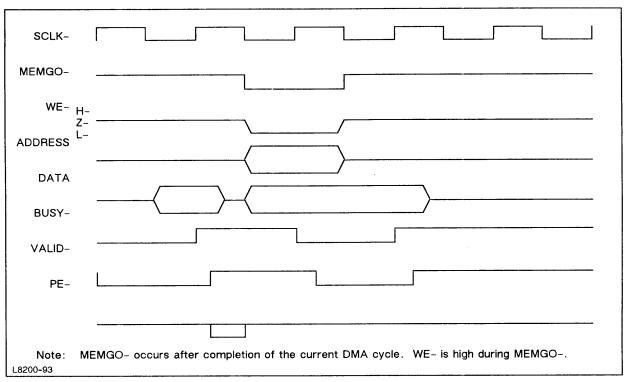

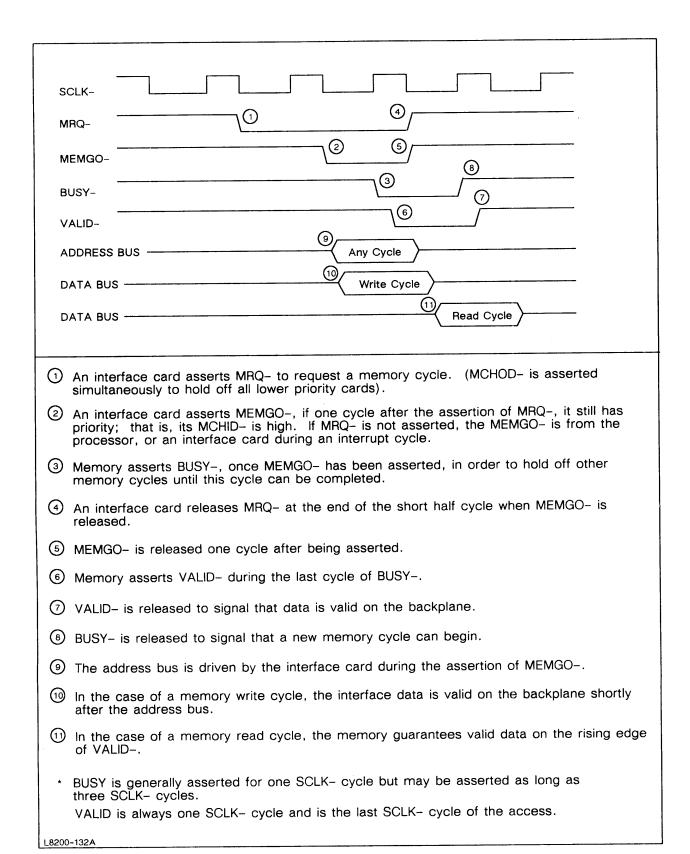

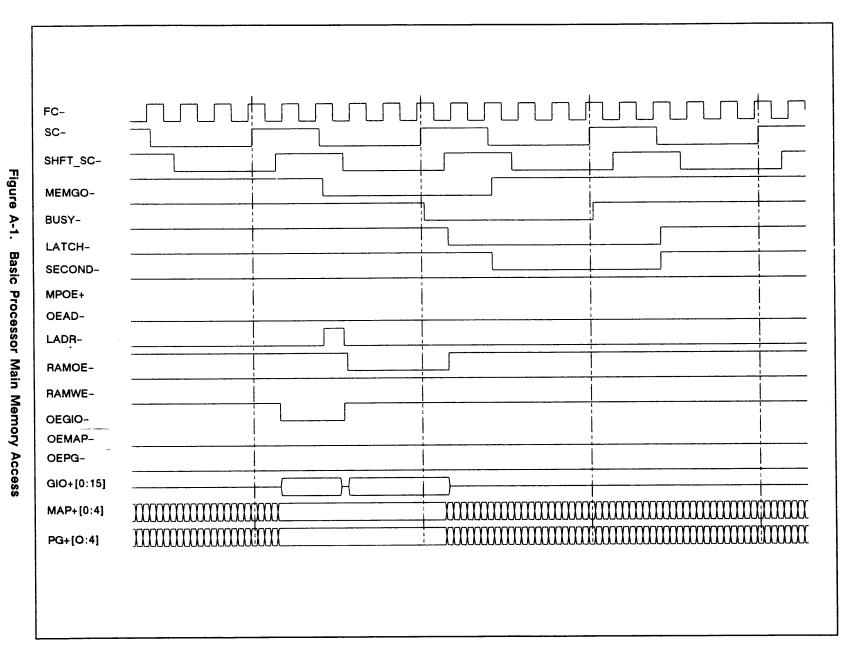

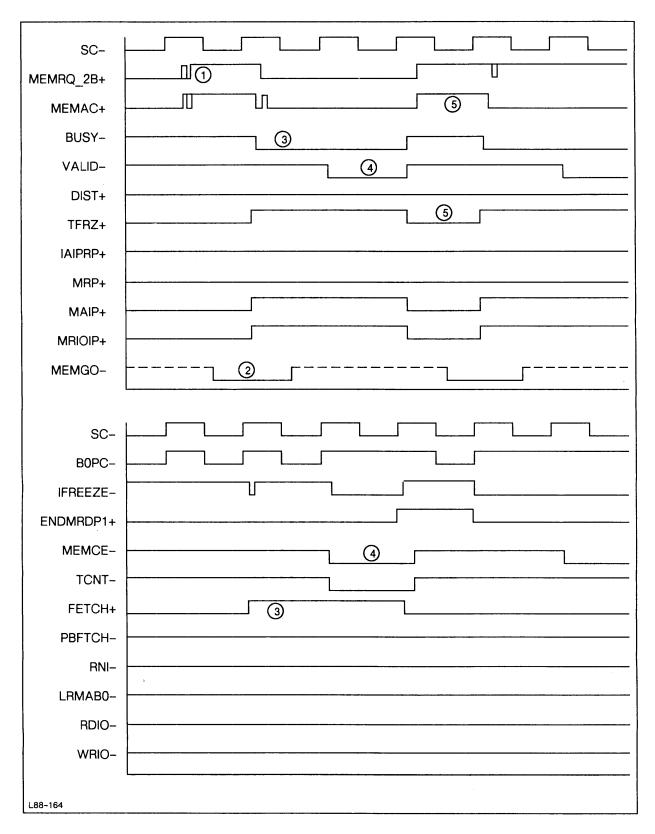

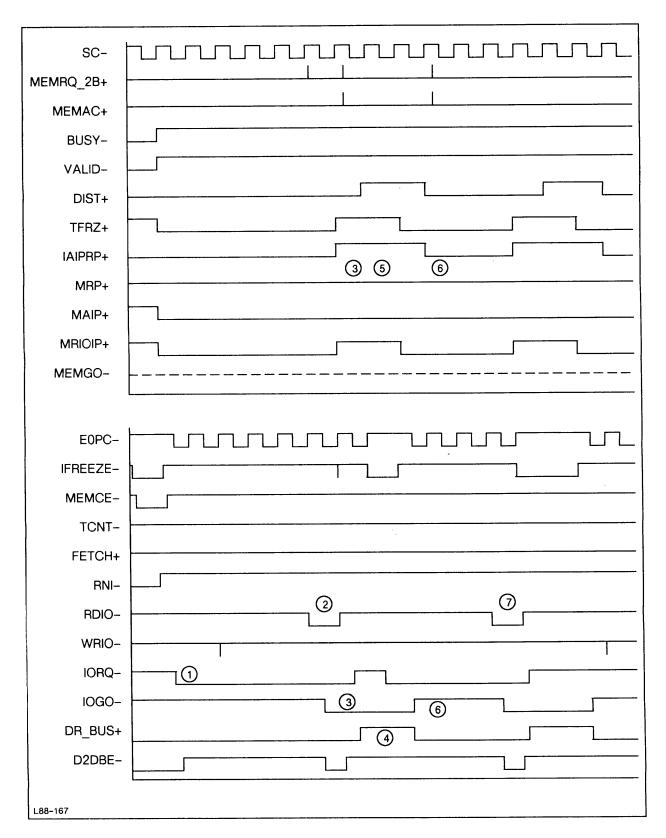

| Processor Main Memory Access                          | 3-97 |

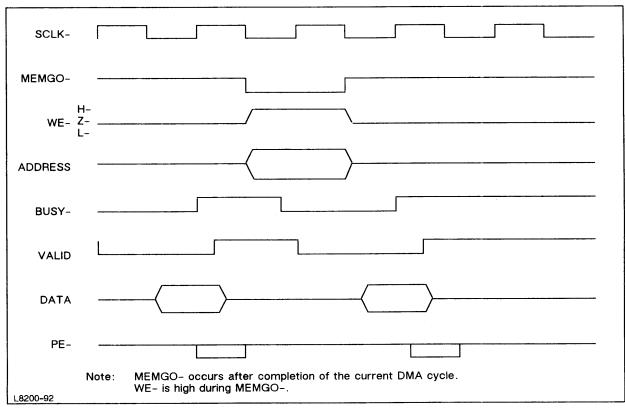

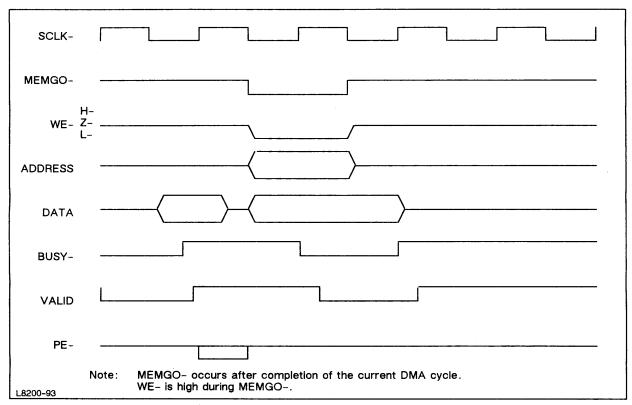

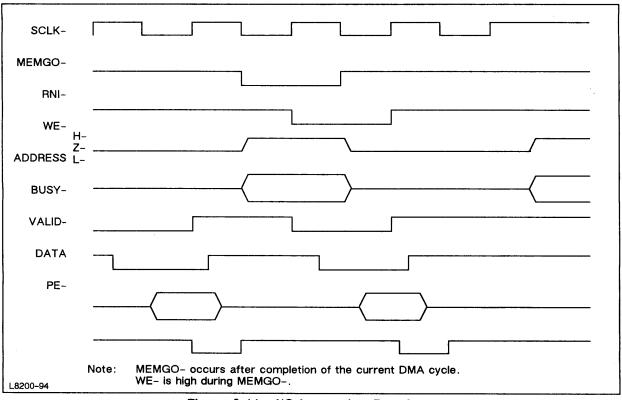

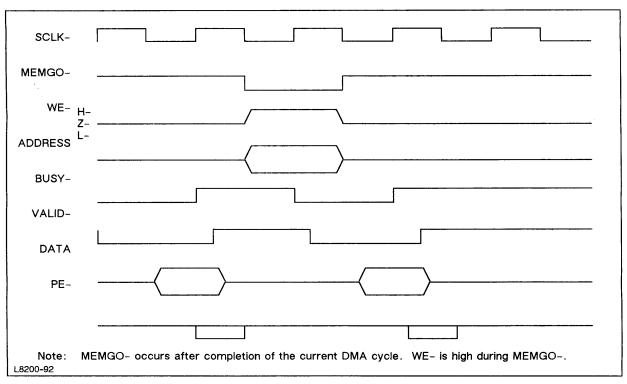

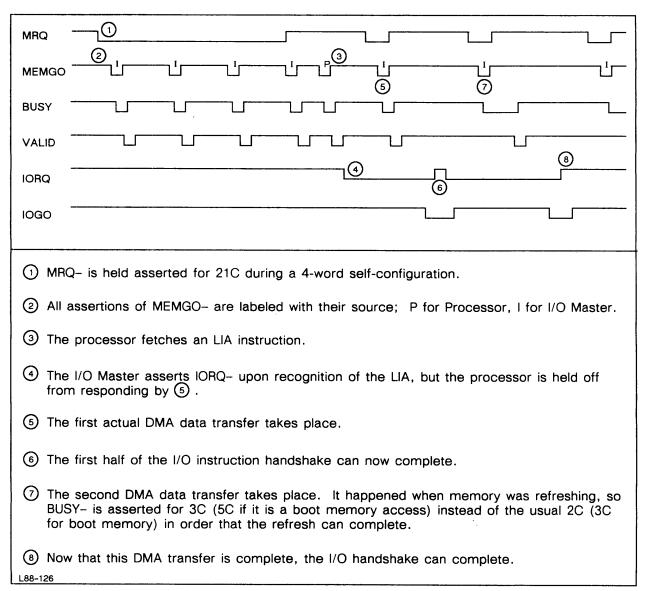

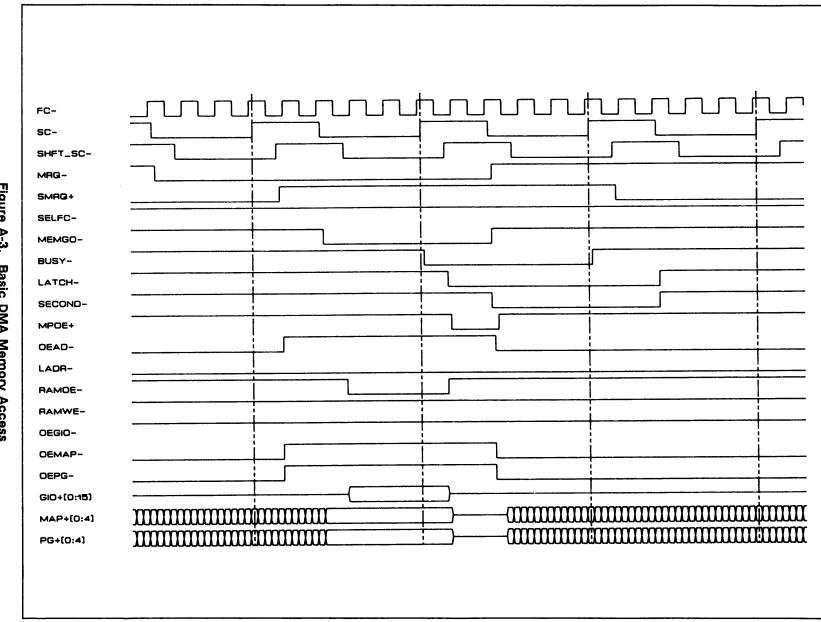

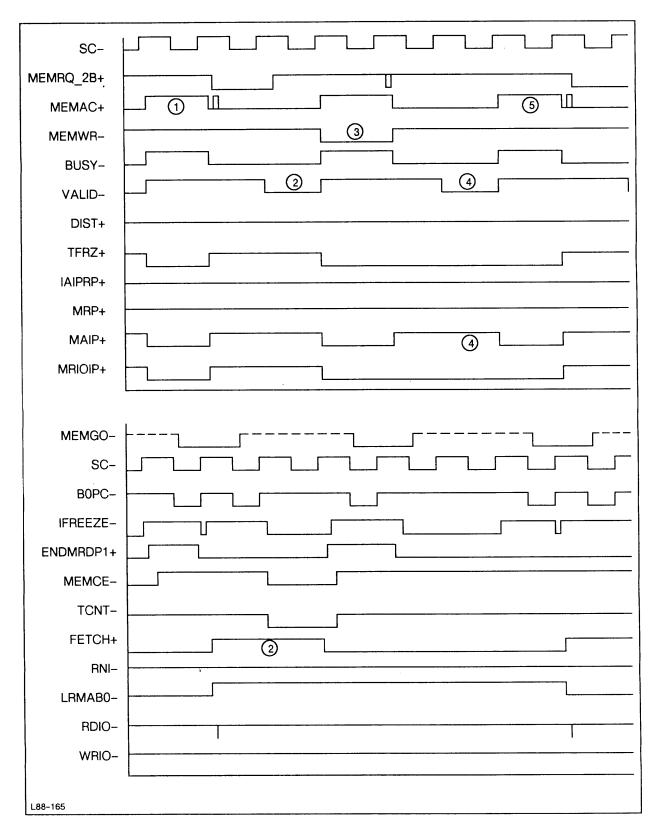

| DMA Memory Access                                     | 3-98 |

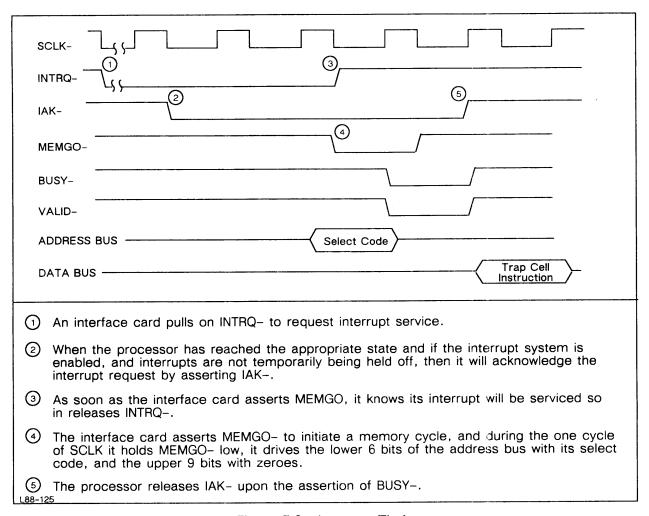

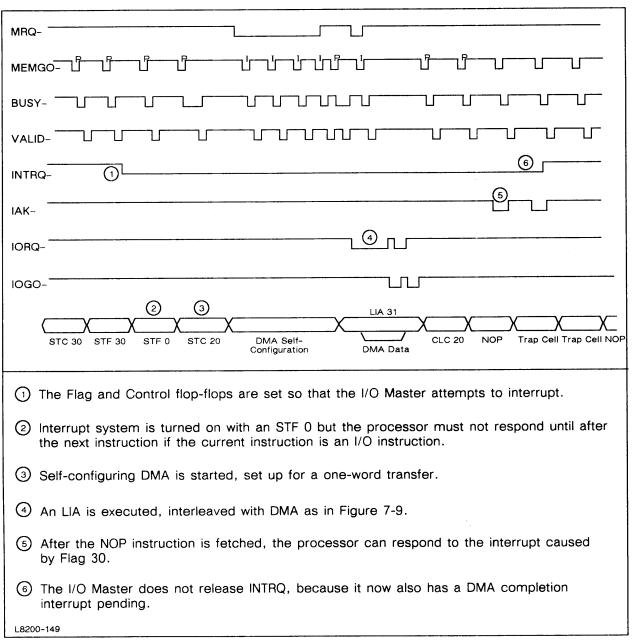

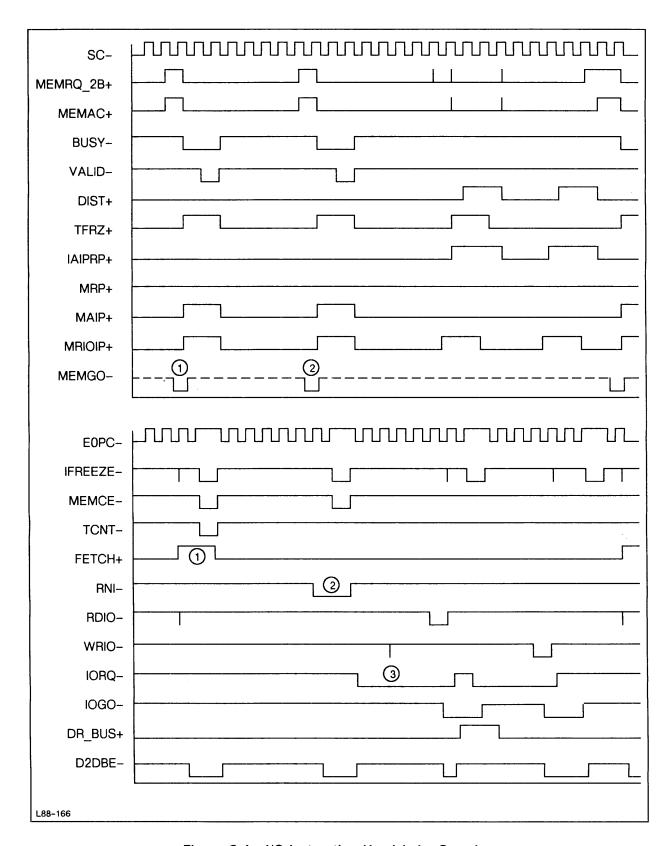

| Interrupt Acknowledge Access                          | 3-98 |

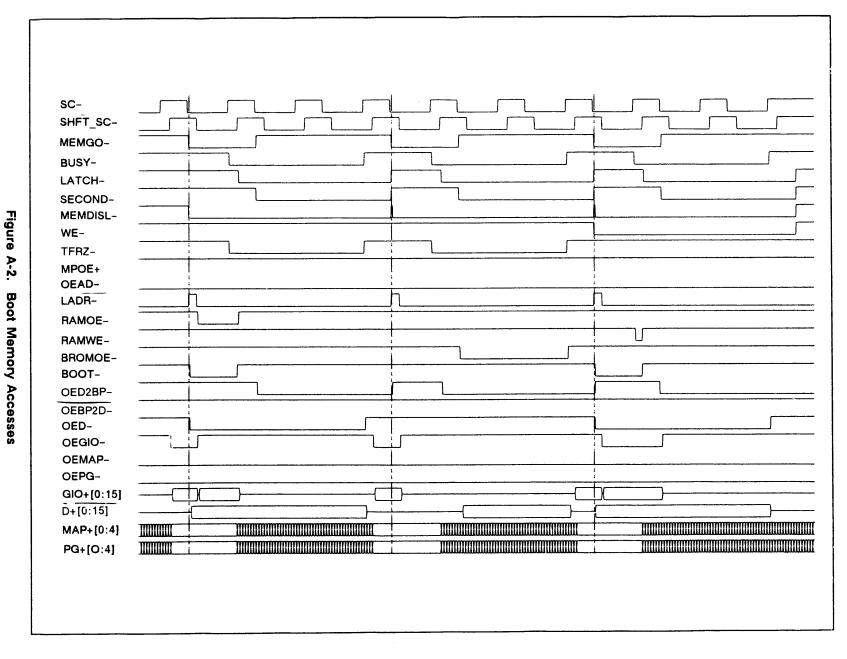

| Boot RAM Access                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-33                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

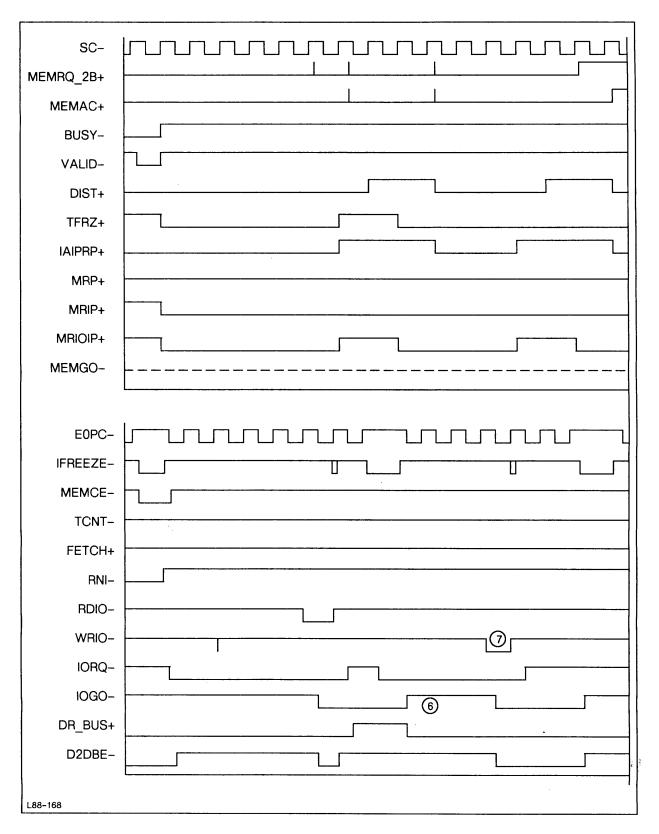

| Boot ROM Access                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-99                                                                                                  |

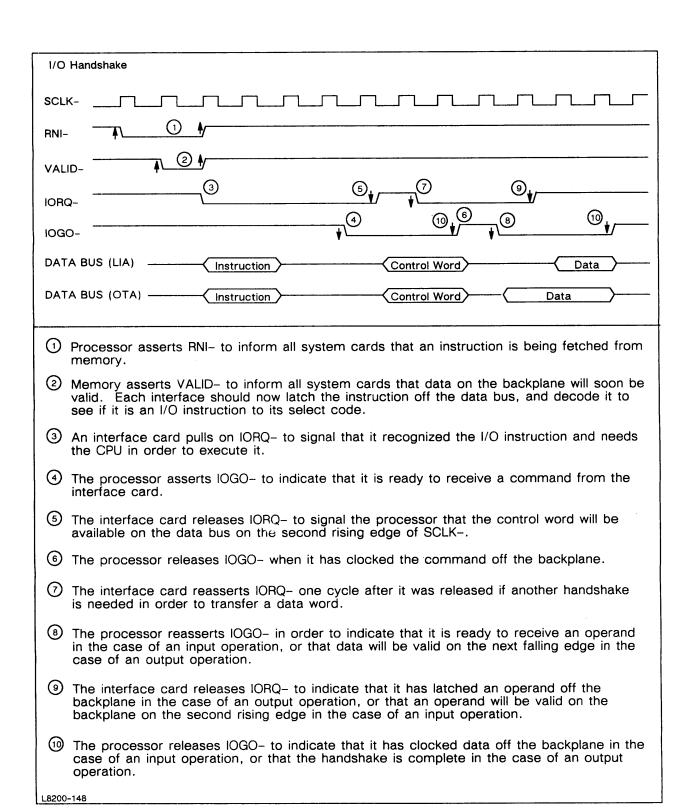

| I/O Handshake Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-100                                                                                                 |

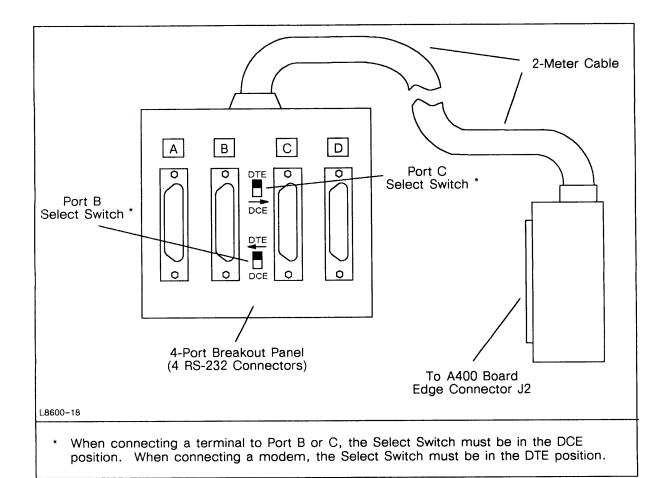

| General Purpose I/O (GIO) Bus                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-100                                                                                                 |

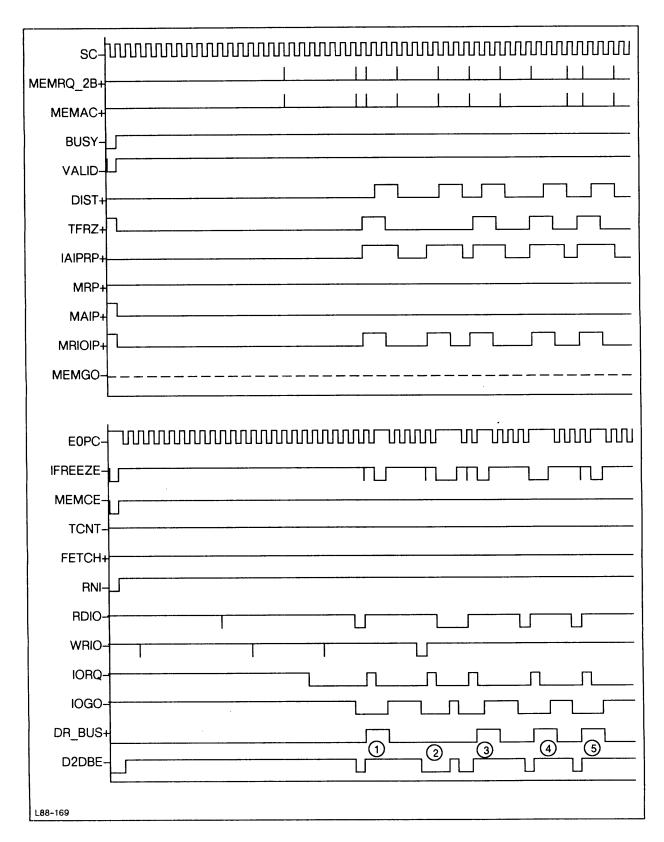

| GO-bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-100                                                                                                 |

| The GI-bus                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-103                                                                                                 |

| External GIO-bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-104                                                                                                 |

| The Data Input/Output Bus (D-Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-109                                                                                                 |

| The DO-Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-109                                                                                                 |

| The DI-Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-111                                                                                                 |

| External D-bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-111                                                                                                 |

| The Map-Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-114                                                                                                 |

| External Map-Bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-116                                                                                                 |

| The Page-Bus (PG-bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-117                                                                                                 |

| External PG-bus Control                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-117                                                                                                 |

| The GIO Freeze Condition                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.118                                                                                                 |

| Signal Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-110                                                                                                 |

| Clasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 120                                                                                                 |

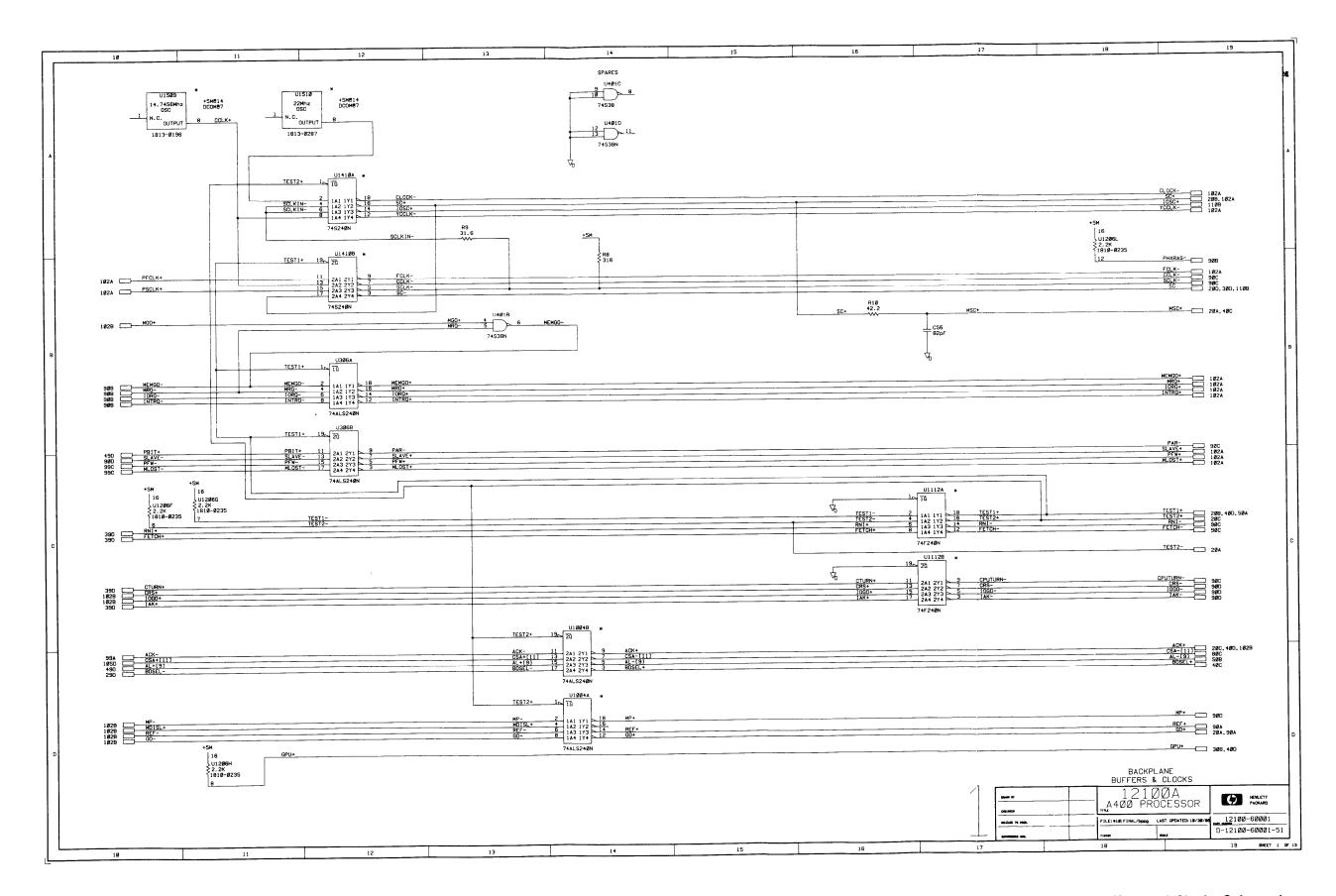

| Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 120                                                                                                 |

| Memory Handshake Signals                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2 1 2 1                                                                                               |

| Memory and I/O State Machine (MIOSM) Signals                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-121                                                                                                 |

| Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-121                                                                                                 |

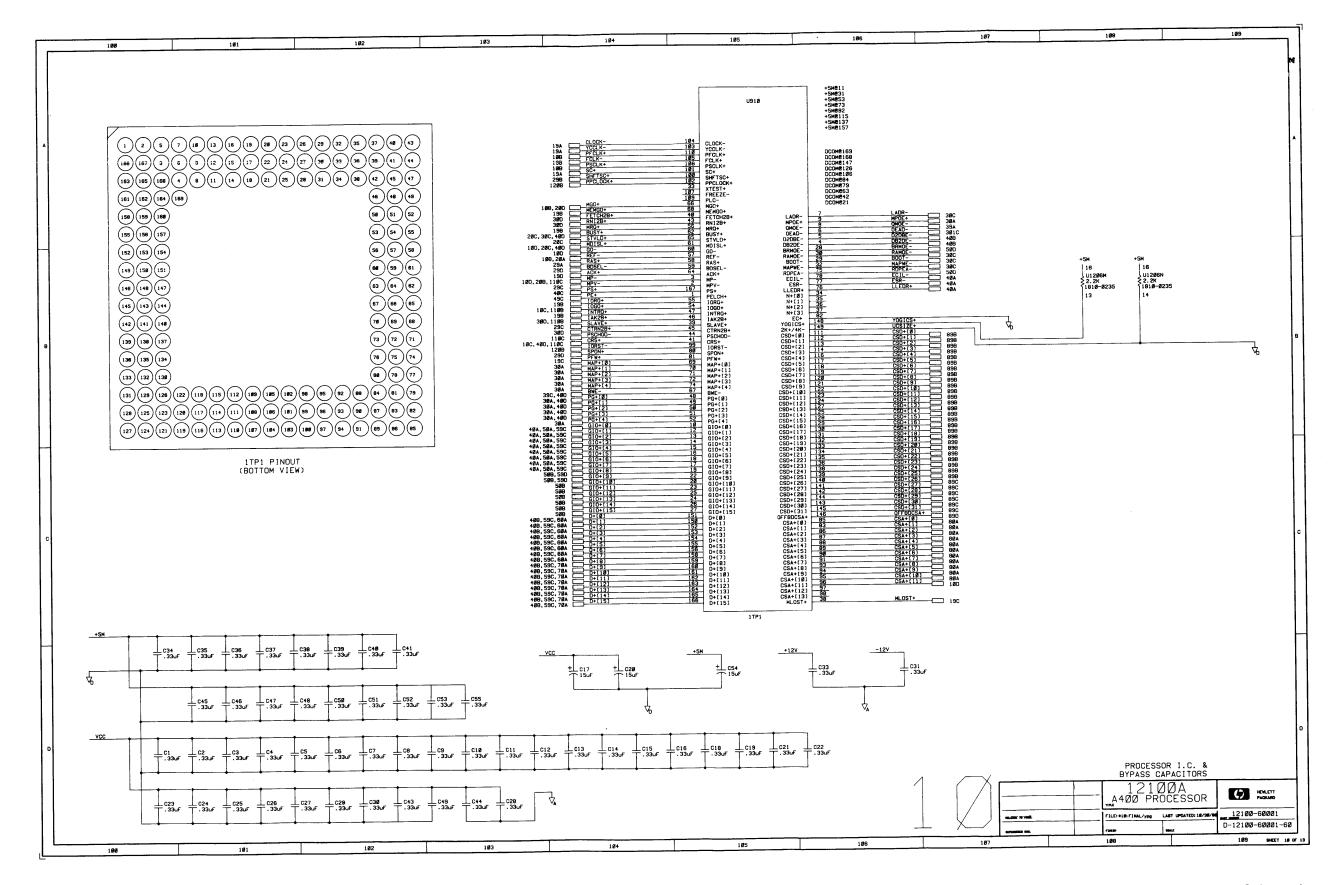

| Processor Chip Pads                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-122                                                                                                 |

| Input Pad Control                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-122                                                                                                 |

| Processor Chip Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-124                                                                                                 |

| Processor Chip Pin Listing                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-124                                                                                                 |

| Trocessor emp i in Eisting                                                                                                                                                                                                                                                                                                                                                                                                                                             | J 12.                                                                                                 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <i>J</i> 12.                                                                                          |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | , T.                                                                                                  |

| Chapter 4 A400 Memory Control                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| Chapter 4 A400 Memory Control  Introduction                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                                                                   |

| Chapter 4 A400 Memory Control  Introduction System Environment                                                                                                                                                                                                                                                                                                                                                                                                         | 4-1<br>4-1                                                                                            |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics                                                                                                                                                                                                                                                                                                                                                                | 4-1<br>4-1<br>4-1                                                                                     |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation                                                                                                                                                                                                                                                                                                                                                | 4-1<br>4-1<br>4-1<br>4-1                                                                              |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity                                                                                                                                                                                                                                                                                                                                  | 4-1<br>4-1<br>4-1<br>4-1<br>4-2                                                                       |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing                                                                                                                                                                                                                                                                                                                | 4-1<br>4-1<br>4-1<br>4-2<br>4-2                                                                       |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity                                                                                                                                                                                                                                                                                                                                  | 4-1<br>4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3                                                         |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements                                                                                                                                                                                                                                                                      | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3                                                         |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate                                                                                                                                                                                                                                                                                             | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3                                                  |

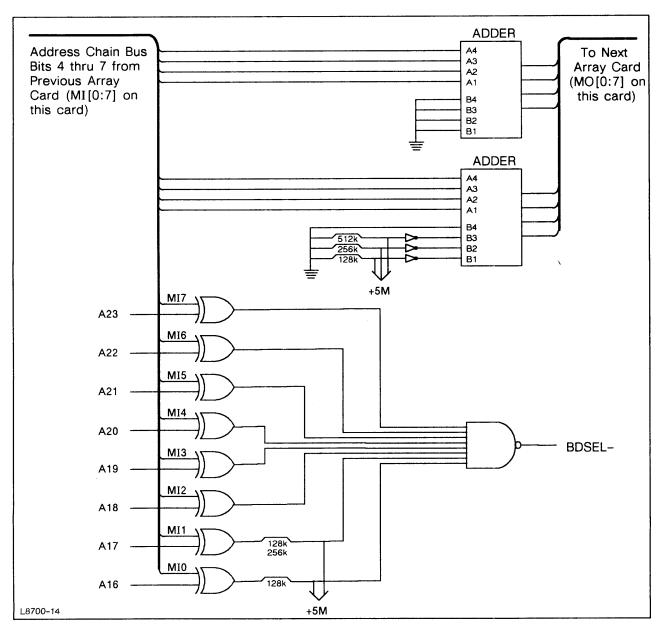

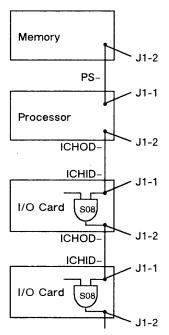

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain                                                                                                                                                                                                                              | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3                                           |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface                                                                                                                                                                                                                                          | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4                                           |

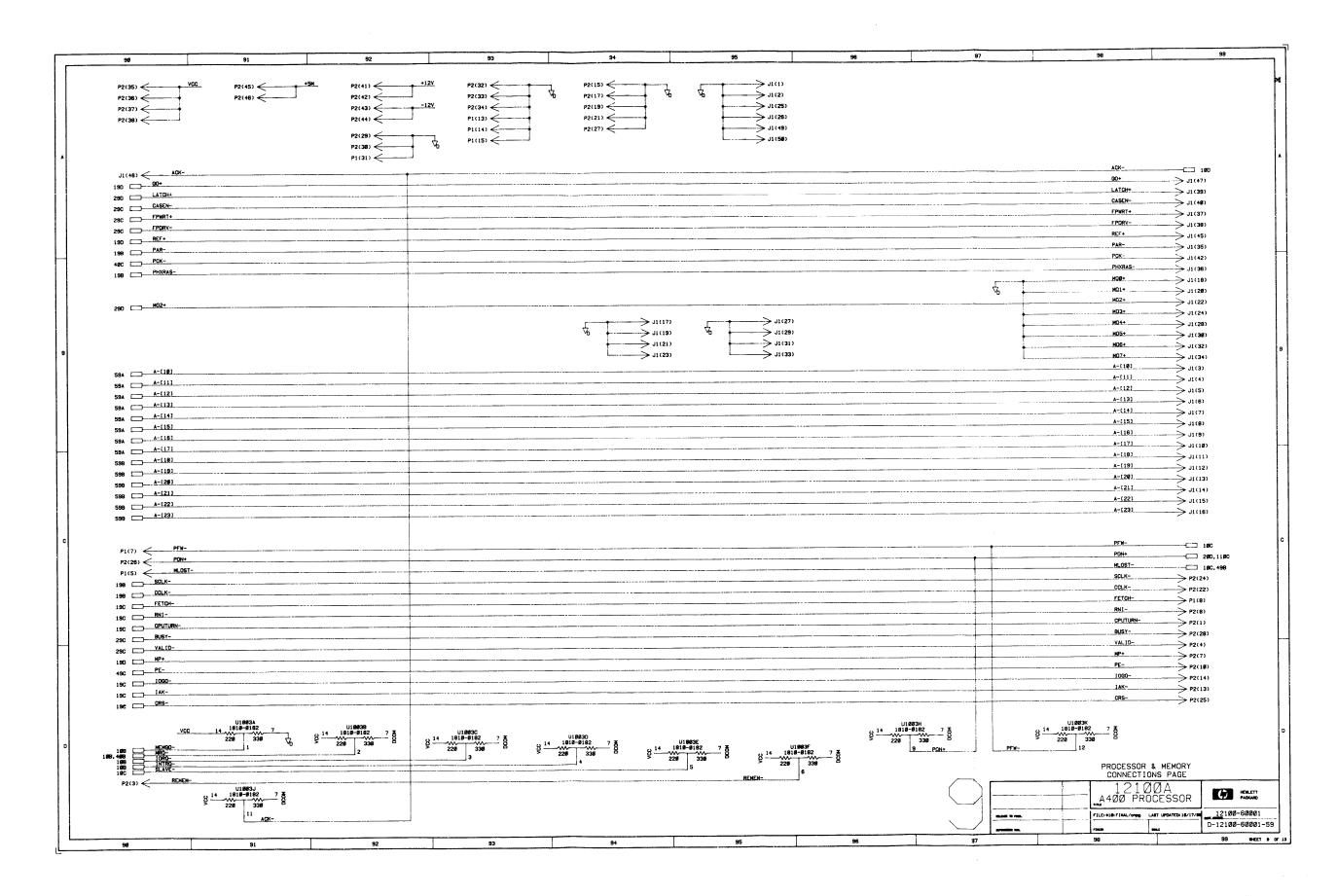

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface                                                                                                                                                                              | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-5                                    |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface                                                                                                                                                                              | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-5                                    |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory Data Transfer to I/O                                                                                                                                                  | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-5<br>4-6                             |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory Data Transfer to I/O Memory System Operating Characteristics                                                                                                          | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-6                             |

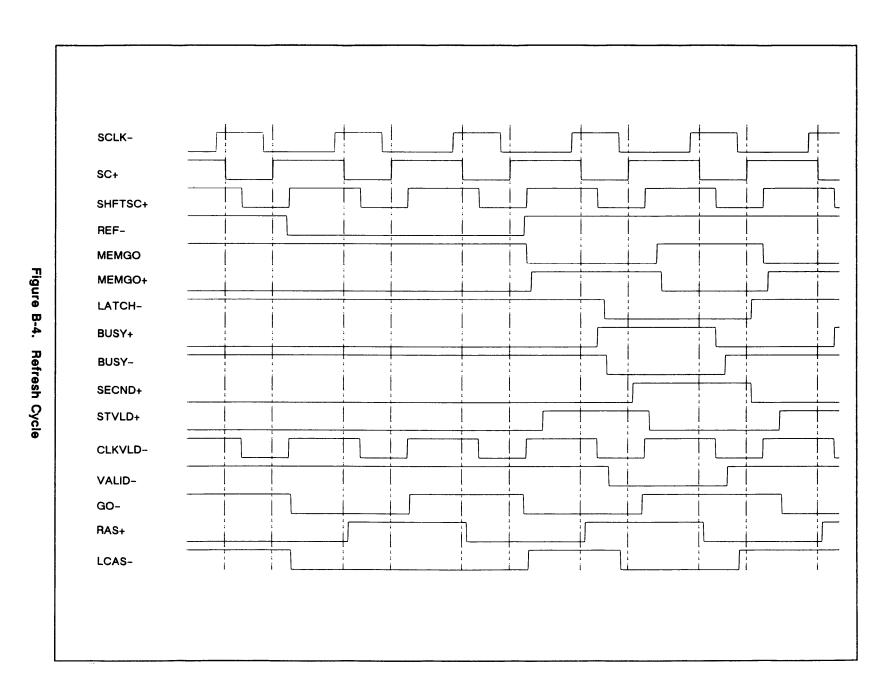

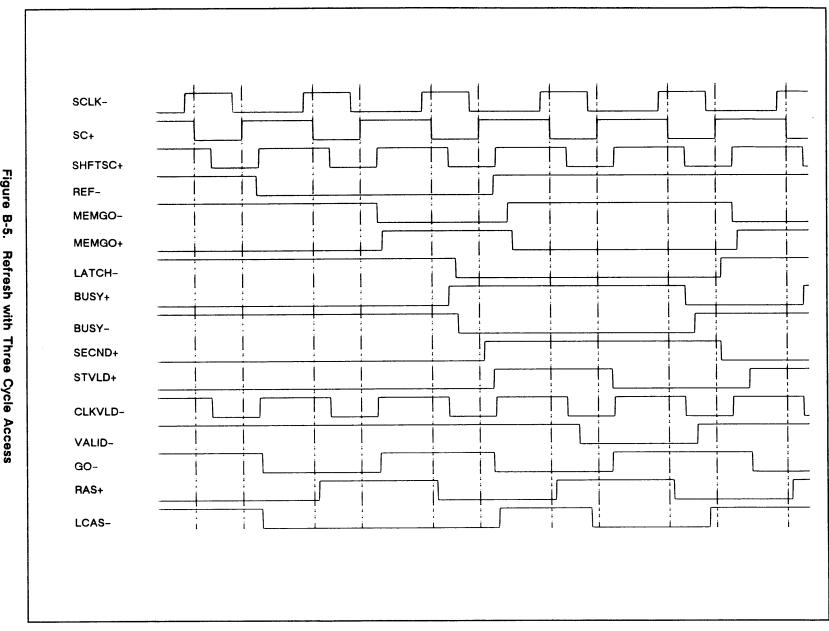

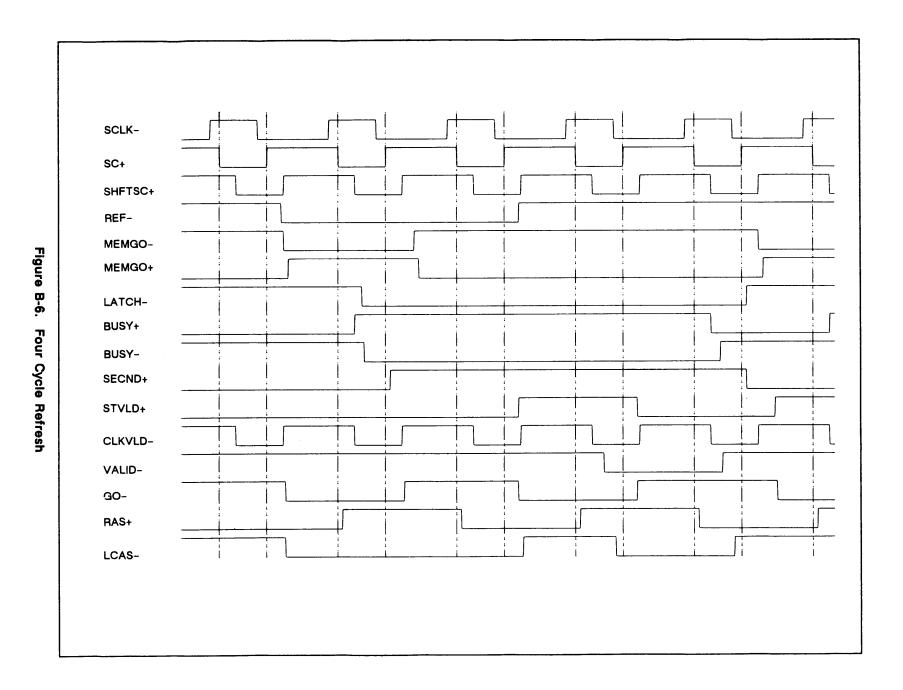

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory Data Transfer to I/O  Memory System Operating Characteristics Refresh Operations                                                                                      | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-6<br>4-6                      |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory Data Transfer to I/O  Memory System Operating Characteristics Refresh Operations Power Fail Considerations                                                            | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-6<br>4-6                      |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory System Operating Characteristics Refresh Operations Power Fail Considerations Interrupt Conditions                                                                    | 4-1<br>4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4<br>4-5<br>4-6<br>4-6<br>4-6<br>4-7               |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory Data Transfer to I/O  Memory System Operating Characteristics Refresh Operations Power Fail Considerations Interrupt Conditions  Memory System Functional Description | 4-1<br>4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-6<br>4-6<br>4-7<br>4-7        |

| Chapter 4 A400 Memory Control  Introduction System Environment Memory System Functional Characteristics Basic Operation Data Capacity Memory Addressing Data Transfer Rate Interface Requirements Memory Frontplane Interface MI/MO Chain Array Frontplane Handshakes Backplane Interface Memory System Operating Characteristics Refresh Operations Power Fail Considerations Interrupt Conditions                                                                    | 4-1<br>4-1<br>4-1<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3<br>4-4<br>4-6<br>4-6<br>4-6<br>4-7<br>4-7<br>4-7 |

| Read/Write Protect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-8                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

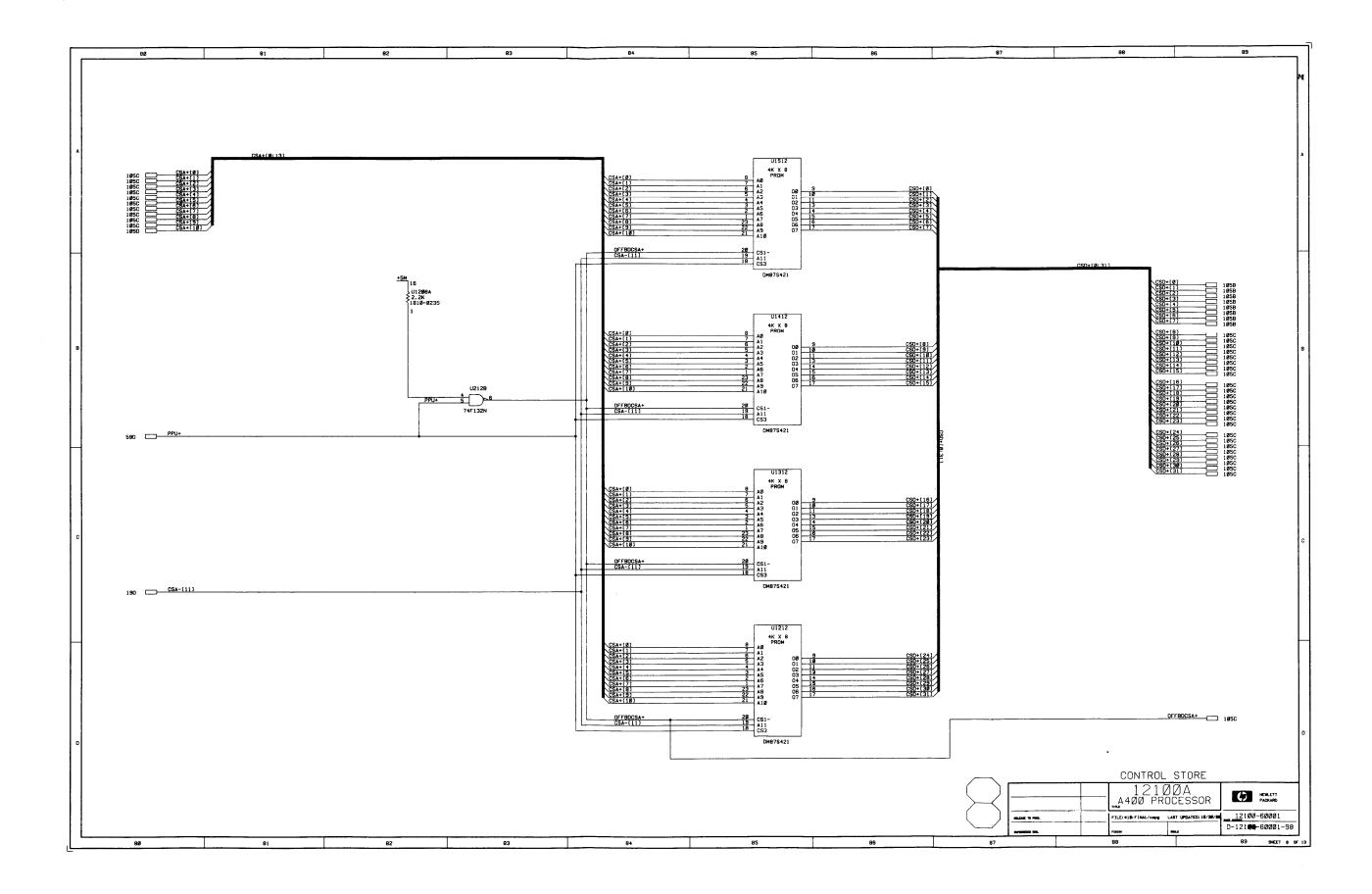

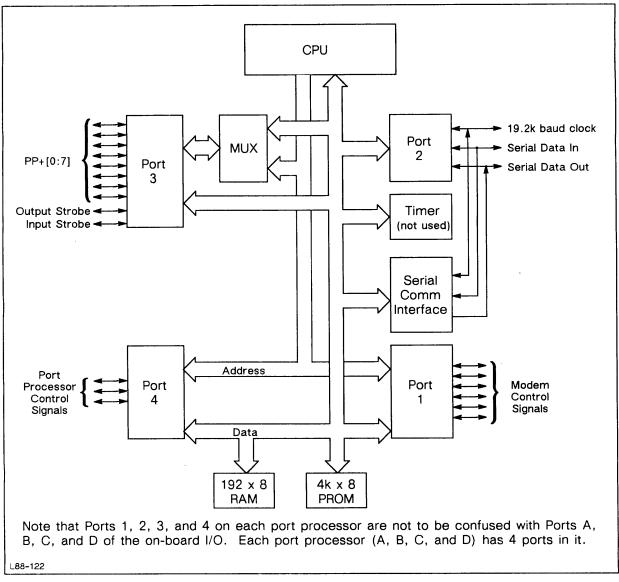

| Controller RAM and PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-9                                                                                 |

| Memory Interrupt Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-9                                                                                 |

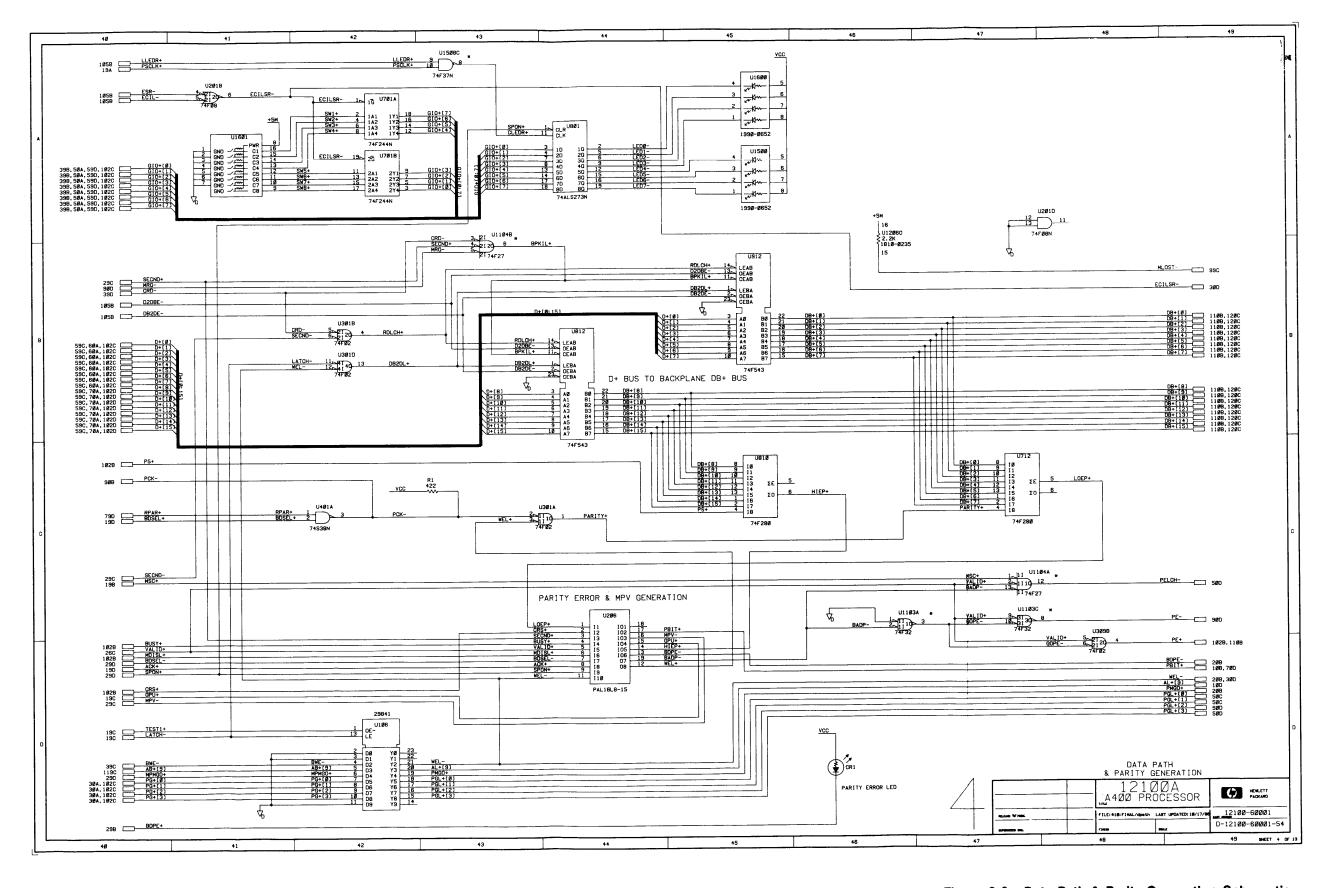

| Parity Generation and Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9                                                                                 |

| Refresh Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-10                                                                                |

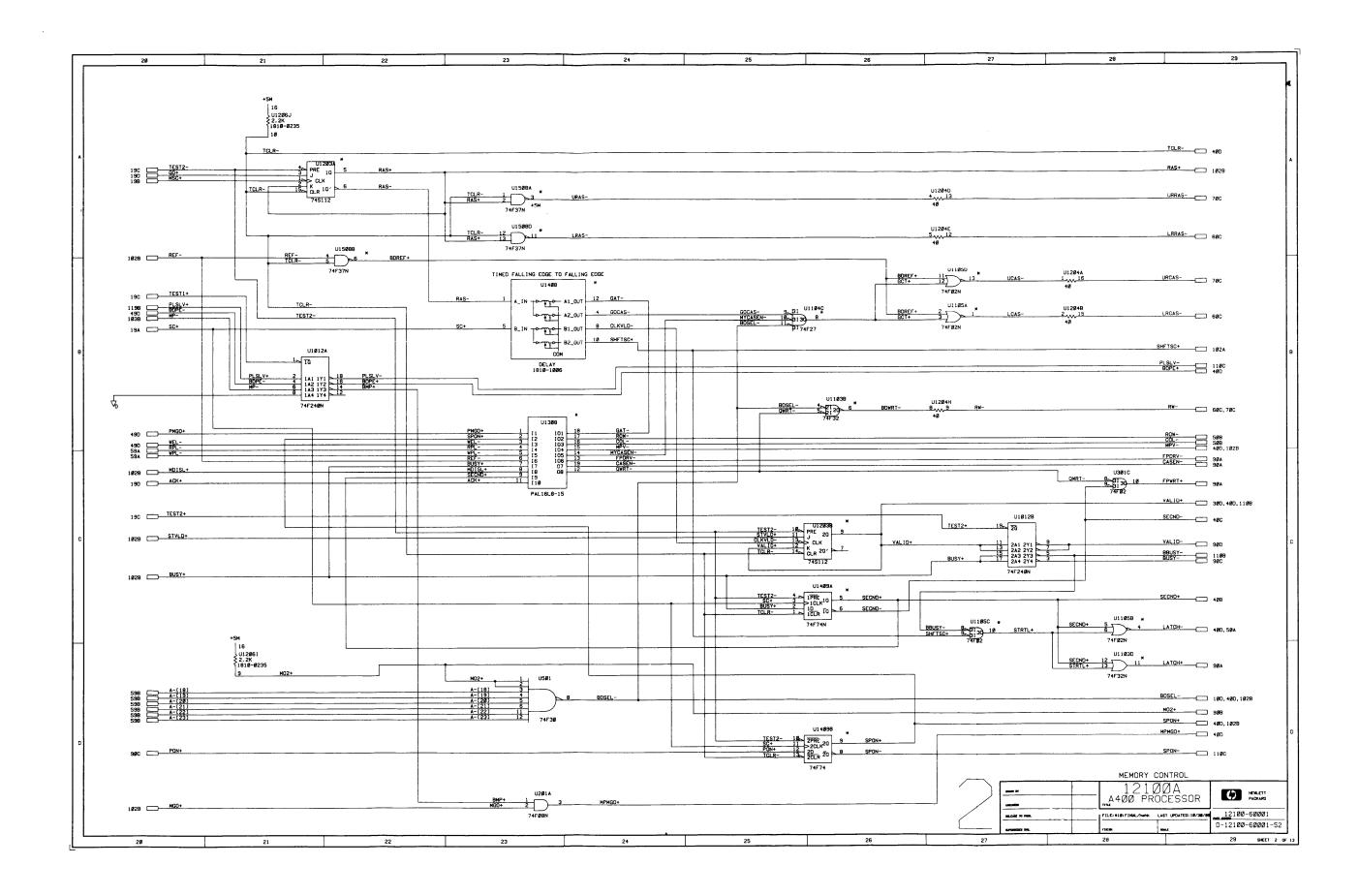

| Memory Control Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-10                                                                                |

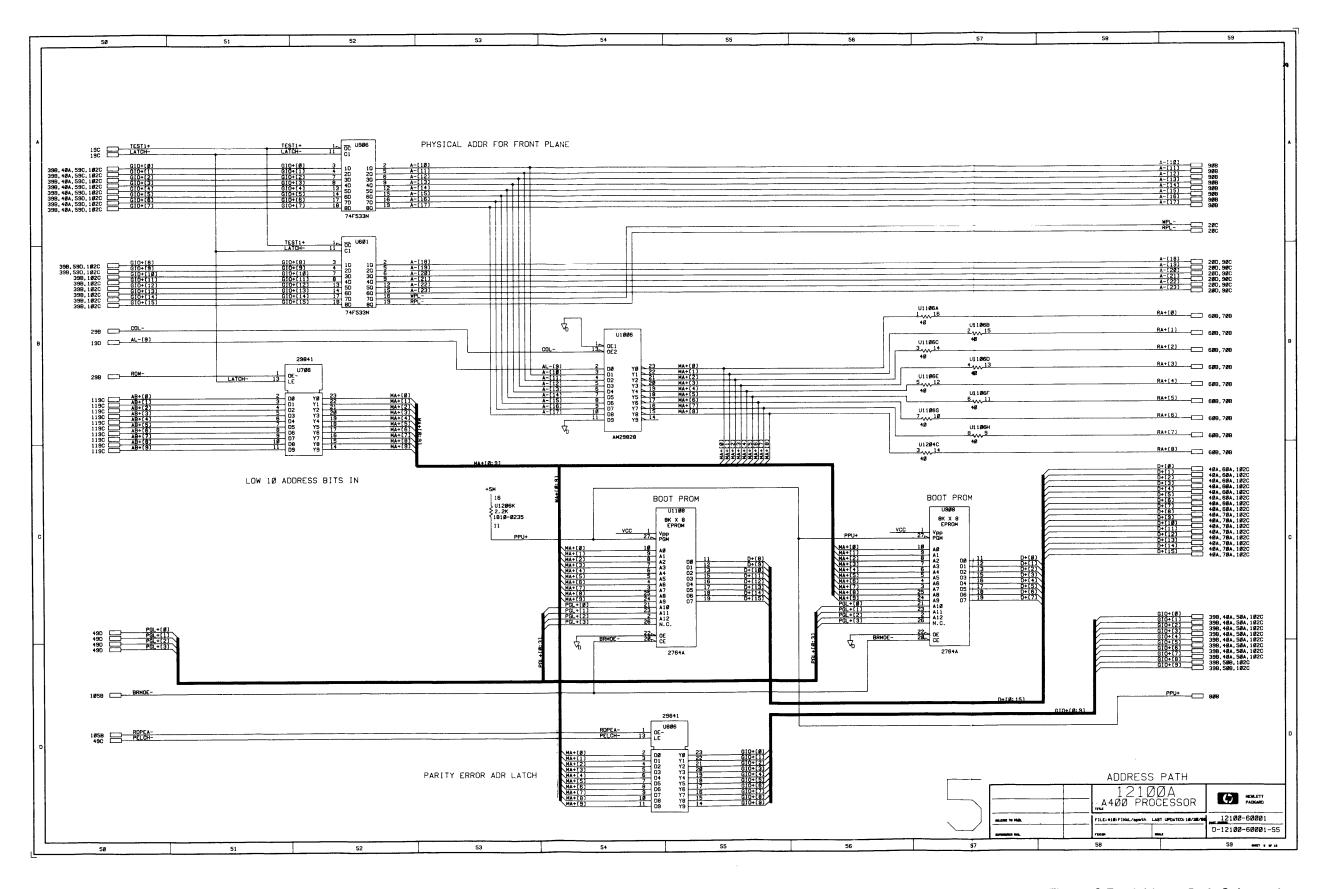

| Data and Address Buses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-11                                                                                |

| Memory Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-11                                                                                |

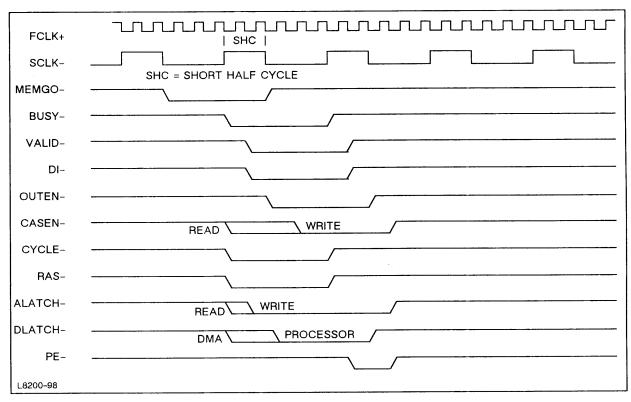

| Two-Cycle Main Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-11                                                                                |

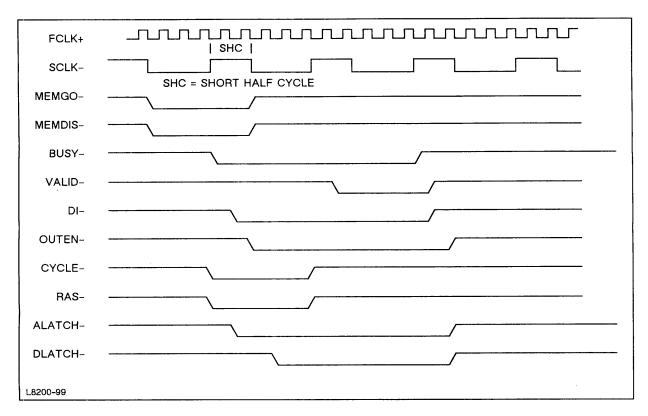

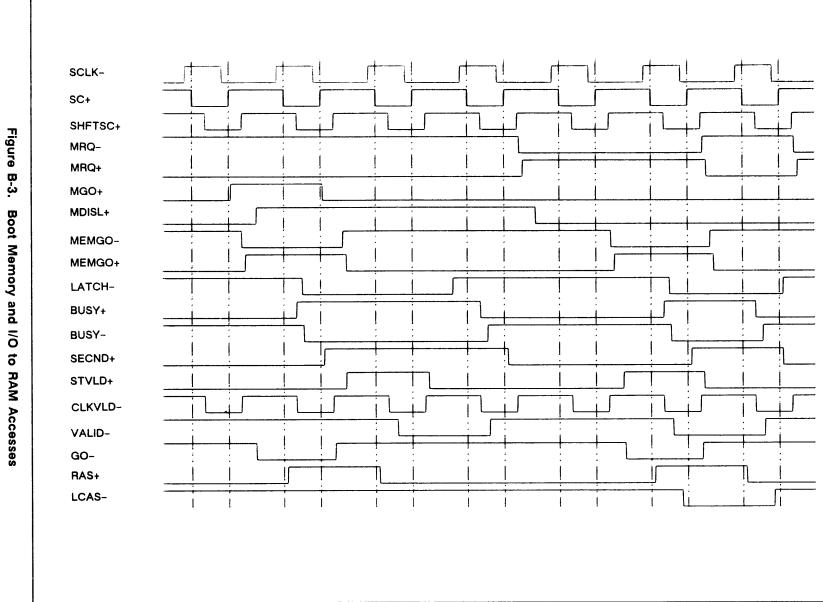

| Three-Cycle Boot Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-12                                                                                |

| Offset Address Latch and GIO-Bus Usage During a Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-14                                                                                |

| Self-Configuration Map Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-15                                                                                |

| General Control Signals for Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-15                                                                                |

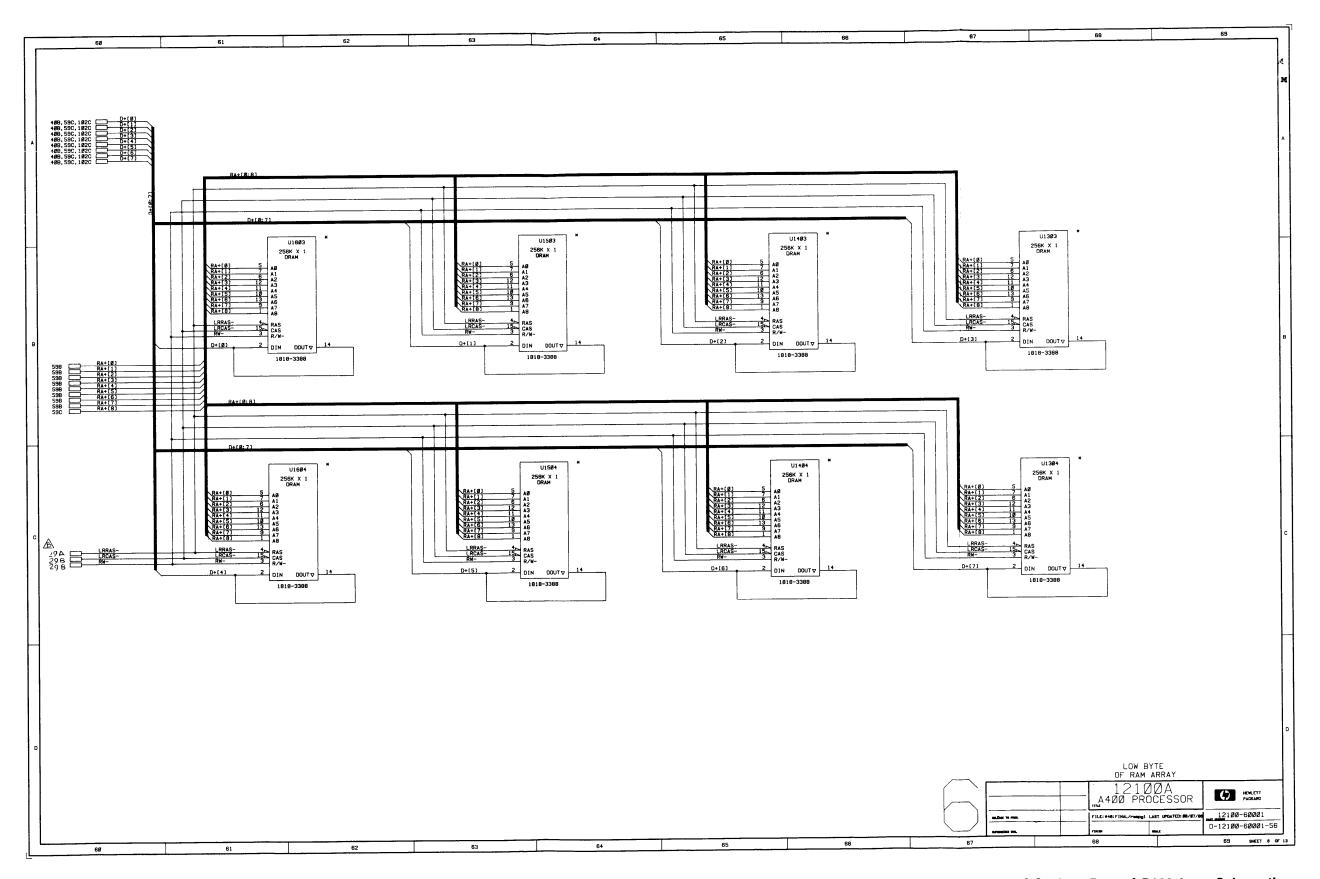

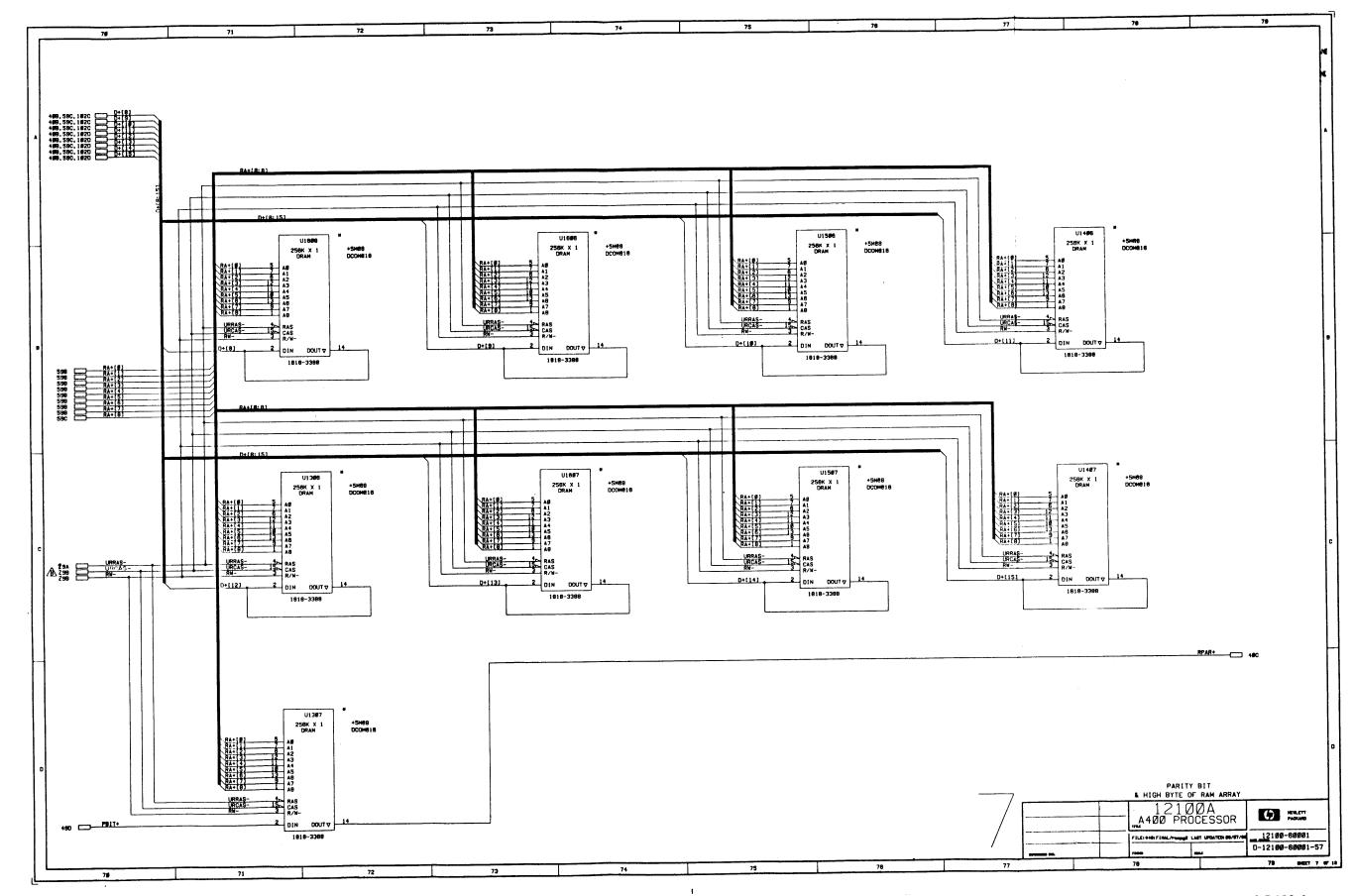

| On-Board Memory (DRAM) Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-16                                                                                |

| DRAM Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-16                                                                                |

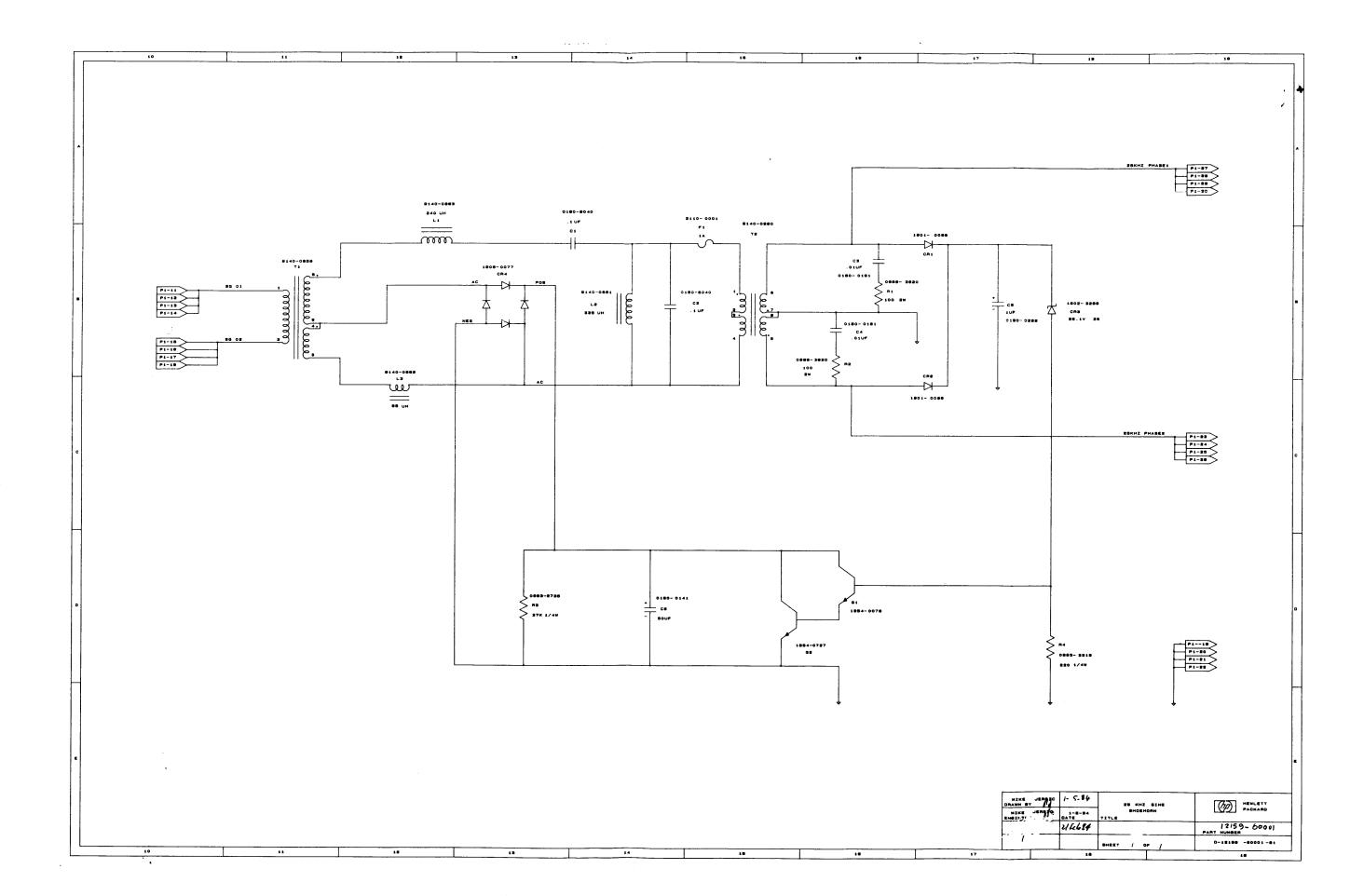

| Parity Error Register (PER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-20                                                                                |