### **HP 1000 A-Series Computer Systems**

## HP 12009A HP-IB Interface

**Reference Manual**

Hewlett-Packard Company Roseville Networks Division 8000 Foothills Boulevard Roseville, California 95678 Manual Part Number: 12009-90001

E1288

Printed in U.S.A. December 1988

## **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual updates.

| Edition 1 |  |  |  |  |  |  |  |  |  |  |  |   | J | aı | n | ua | ry | 19 | 80 |  |

|-----------|--|--|--|--|--|--|--|--|--|--|--|---|---|----|---|----|----|----|----|--|

| Edition 2 |  |  |  |  |  |  |  |  |  |  |  |   |   |    |   | Ju | ĺγ | 19 | 84 |  |

| Edition 3 |  |  |  |  |  |  |  |  |  |  |  | D | e | ce | n | nb | er | 19 | 88 |  |

## **Notice**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD COMPANY MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard Company.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1988 by HEWLETT-PACKARD COMPANY

## **Safety Considerations**

#### General

This product and related documentation must be reviewed for familiarization with safety markings before operation.

### **Safety Symbols**

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal. This symbol is sometimes used in the manual to indicate circuit common connected to a grounded chassis.

### W arning

The warning sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a warning sign until the indicated conditions are fully understood and met.

#### Caution

The caution sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a caution sign until the indicated conditions are fully understood and met.

#### Caution

#### Static Sensitive Devices.

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous way such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices.

When handling or servicing equipment containing sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static sensitive devices should attempt to service the cards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling and devices. Cautions are included throughout this manual where handling and maintenance involve static sensitive devices.

#### Safety Earth Ground

This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

#### **Before Applying Power**

Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

#### Servicing

#### Warning

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

#### Warning

#### Eye Hazard

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

## **Contents**

| ] | ntroduction                      |   |

|---|----------------------------------|---|

| I | Functional Description           | 1 |

| I | Equipment Supplied               | 3 |

| I | dentification                    | 3 |

| 5 | Specifications                   | 4 |

|   | Electrical Characteristics 1-4   |   |

|   | Physical Characteristics 1-      | 5 |

| ( | Capabilities                     | 5 |

| 5 | Supported Functions              | 5 |

|   | Handshaking                      | 7 |

| I | Device Functions                 | 7 |

|   | Bus Lines                        | 3 |

|   | Control Lines                    | • |

|   | Data Lines (DIO1-DIO8)           | J |

|   | Transfer Lines                   | ) |

| 1 | Data Transfer Timing             | 1 |

|   | Electrical Characteristics 1-13  | 3 |

|   | Cable Characteristics            |   |

|   | nstallation                      |   |

| ] | Requirements                     |   |

|   | Power Requirements               |   |

|   | Interface Requirements           |   |

|   | Backplane to HP-IB Card          |   |

|   | Switch Selectable Options        | ĺ |

|   | HP-IB Address Selection 2-       | 5 |

|   | Select Code Selection            | 5 |

|   | System Controller Selection 2-:  |   |

|   | Data Settling Time Selection 2-: | 5 |

| ] | installation                     | 5 |

|   | Checkout                         | 7 |

|   | Load Resistor Pack               | 7 |

| 1 | interconnecting Cables           | 3 |

|   |                                  | 3 |

|   | Cabling Length Restrictions      | _ |

|   | Other Cabling Considerations     |   |

| • | Programming                                    |

|---|------------------------------------------------|

|   | Overview                                       |

|   | I/O Master Section                             |

|   | HP-IB Bus Interface Section                    |

|   | Register Descriptions                          |

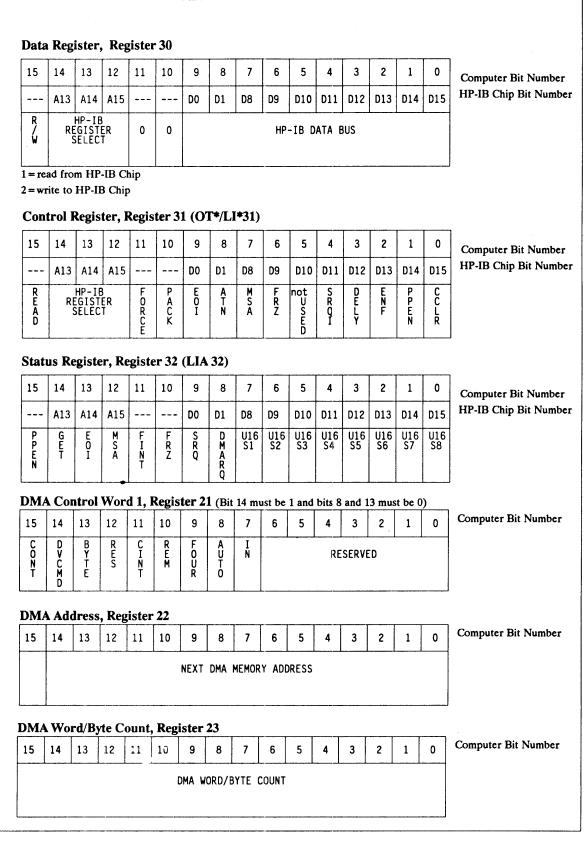

|   | Data Register, Register 30 (OT*/LI*30) 3-9     |

|   | Control Register, Register 31 (OT*/LI*31) 3-10 |

|   | Status Register, Register 32 (LI*/OT*32) 3-11  |

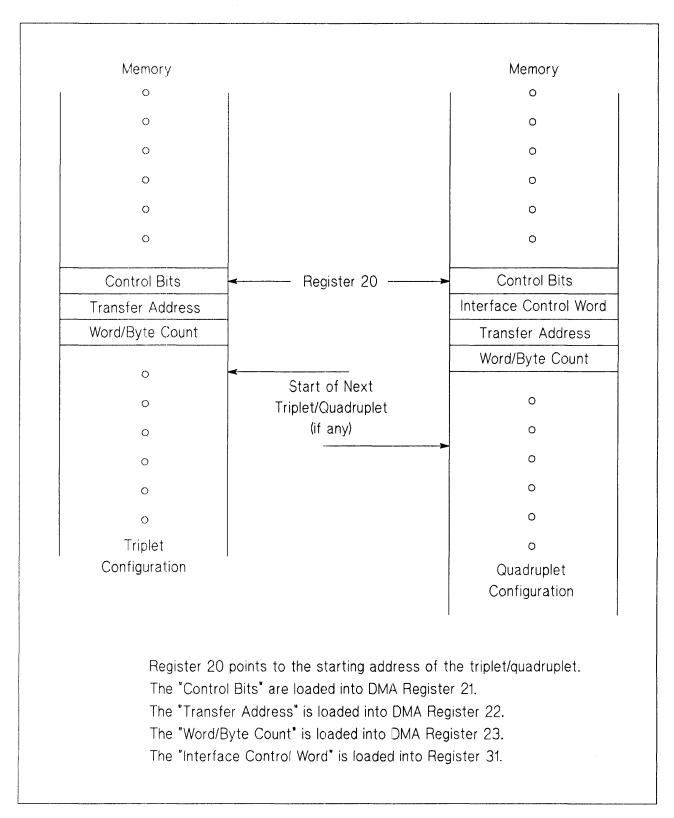

|   | DMA Self-Configuration, Register 20            |

|   | DMA Control Word 1, Register 21 3-13           |

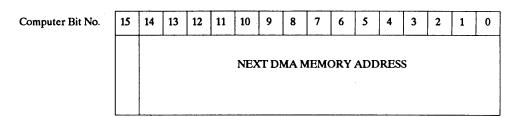

|   | DMA Address, Register 22                       |

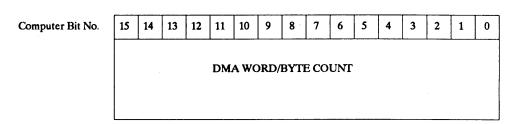

|   | DMA Word/Byte Count, Register 23               |

|   | Summary                                        |

|   | Programmed Input/Output                        |

|   | Direct Memory Access (DMA)                     |

|   | Types of DMA Transfers                         |

|   | DMA Control and Status Words                   |

|   | DMA Transfer Operation                         |

|   | DMA Self-Configuration Feature                 |

|   | Byte Mode Transfers                            |

|   | Word Mode Transfers                            |

|   | DMA Control                                    |

|   | Example                                        |

|   | HP-IB Card Programming Characteristics         |

|   | Initialization (Power On and I/O Clear)        |

|   | System Controller and Controller-In-Charge     |

|   | Bus Controller Device                          |

|   | Interrupts                                     |

|   | Card Flag Interrupts                           |

|   | Programming Examples                           |

|   | HP-IB Chip Register Definitions                |

|   | Register 0, Outbound FIFO/Inbound FIFO         |

|   | Outbound FIFO                                  |

|   | Inbound FIFO                                   |

|   | Register 1, Status                             |

|   | Register 2, Interrupting Conditions            |

|   | Register 3, Interrupt Mask                     |

|   | Register 4, Parallel Poll Mask/First ID byte   |

|   | Register 5, Parallel Poll/Second ID Byte       |

|   | Register 6, Control                            |

|   | Register 7, HP-IB Address                      |

|   | Offline Diagnostics                            |

|   |                                                |

| 4 | Theory of Operation                                 |

|---|-----------------------------------------------------|

|   | General Description                                 |

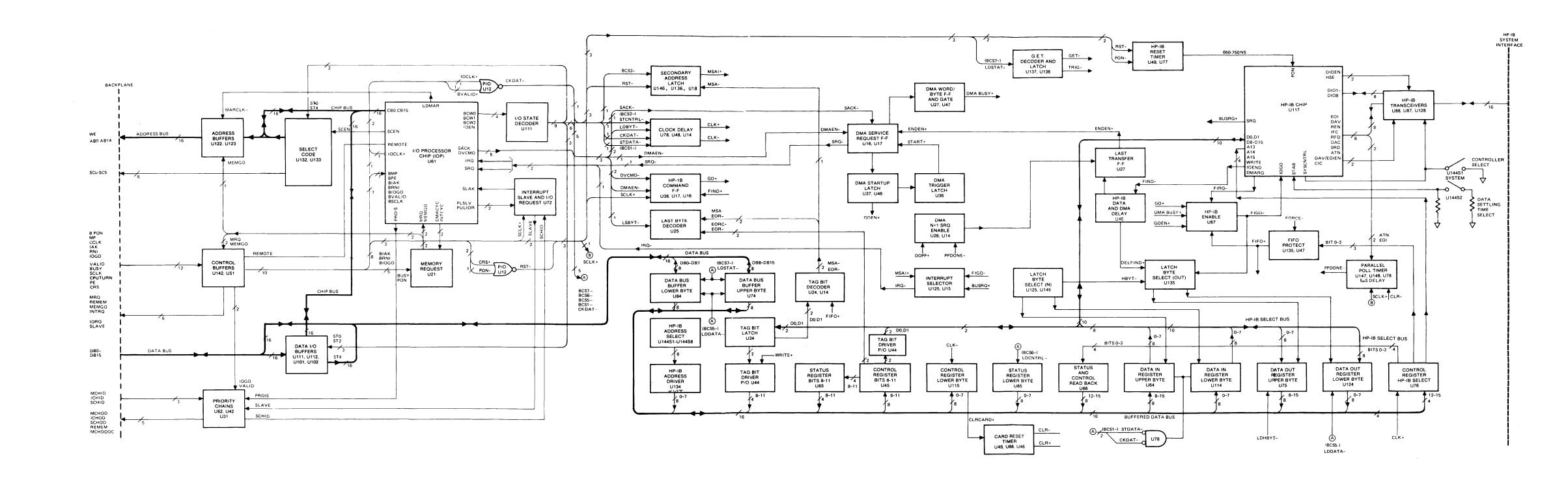

|   | Block View                                          |

|   | Functional View                                     |

|   | Non-DMA Transfers                                   |

|   | Output Transfers                                    |

|   | Input Transfers                                     |

|   | DMA Transfers 4-9                                   |

|   | DMA Word Mode Transfers                             |

|   | DMA Byte Mode Transfers                             |

|   | DMA I/O Master Handshake 4-10                       |

|   | Control Word Transfers 4-11                         |

|   | Status Word Transfers                               |

|   | HP-IB Bus Operation                                 |

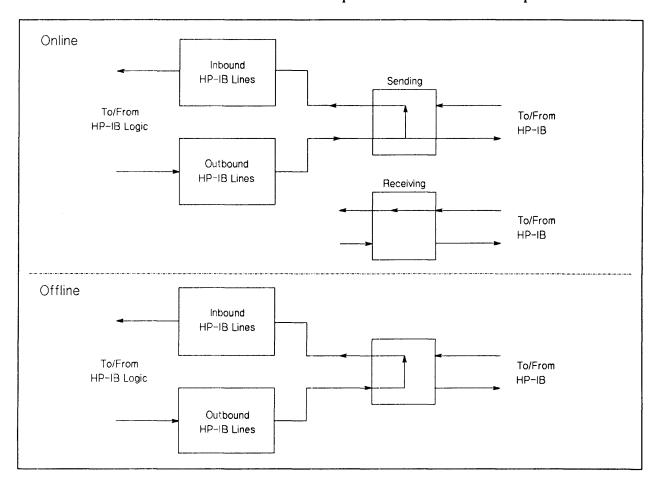

|   | Transceiver Operation                               |

|   | HP-IB Chip Options                                  |

|   | HP-IB Error Detection                               |

|   | Responding to an HP-IB Error 4-16                   |

|   |                                                     |

| 5 | Maintenance                                         |

|   | Preventive Maintenance                              |

|   | Troubleshooting                                     |

|   |                                                     |

| 6 | Replaceable Parts                                   |

|   | Component Parts                                     |

|   | Ordering Information                                |

|   |                                                     |

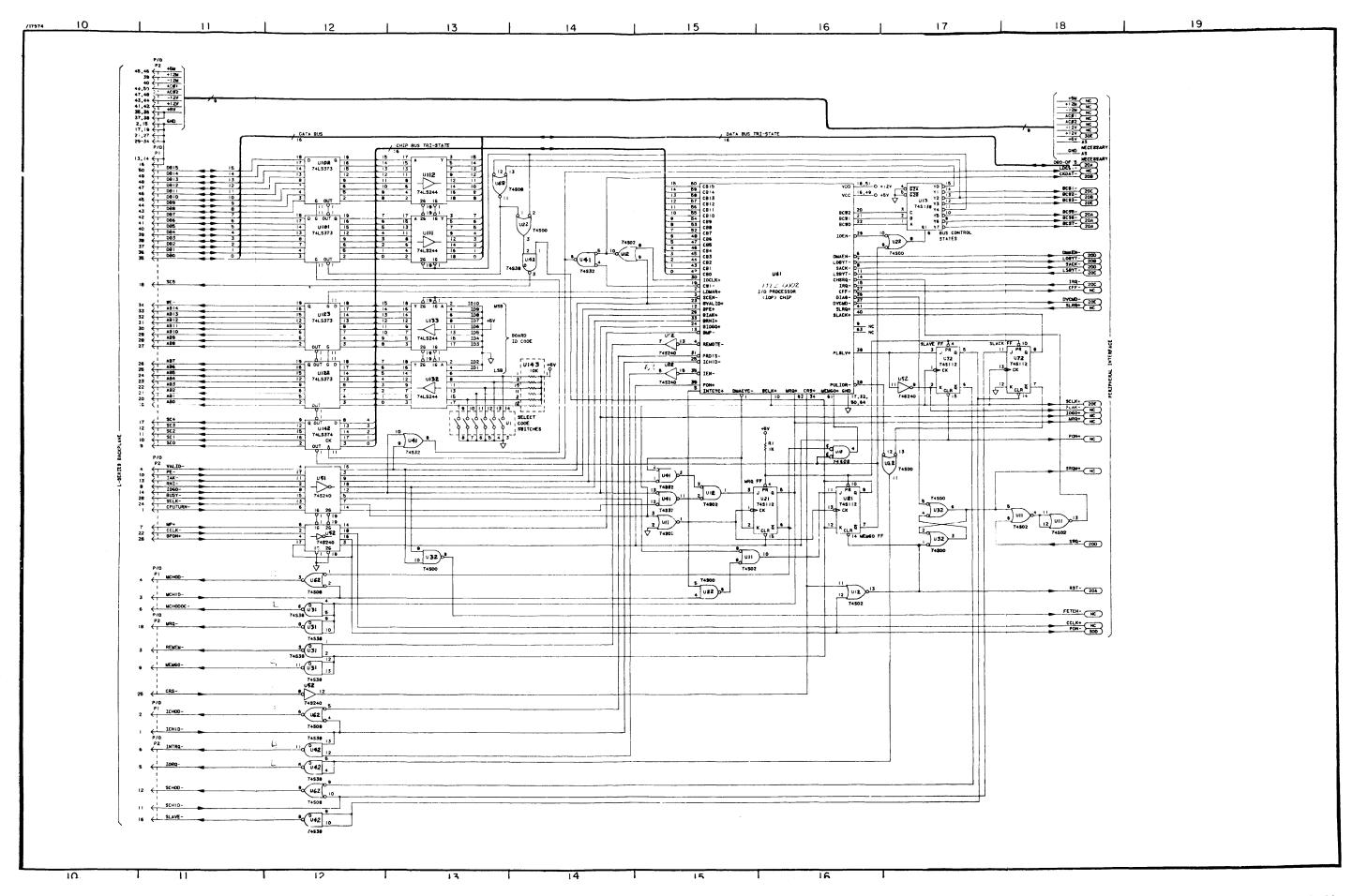

| 7 | Service Diagrams                                    |

|   | General Information                                 |

|   | Integrated Circuit Base Diagrams 7-2                |

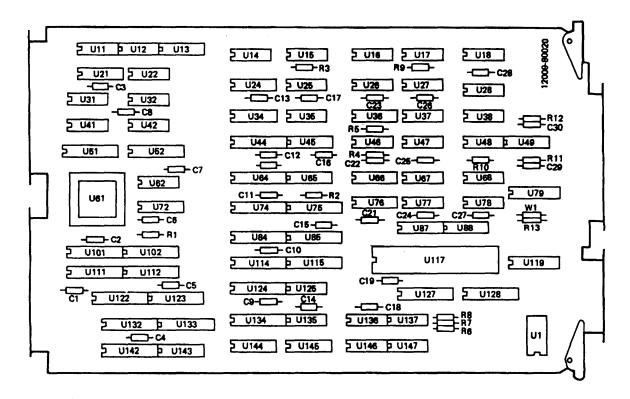

|   | HP-IB Interface Card Component Location Diagram 7-7 |

|   | HP-IB Interface Card Functional Block Diagram       |

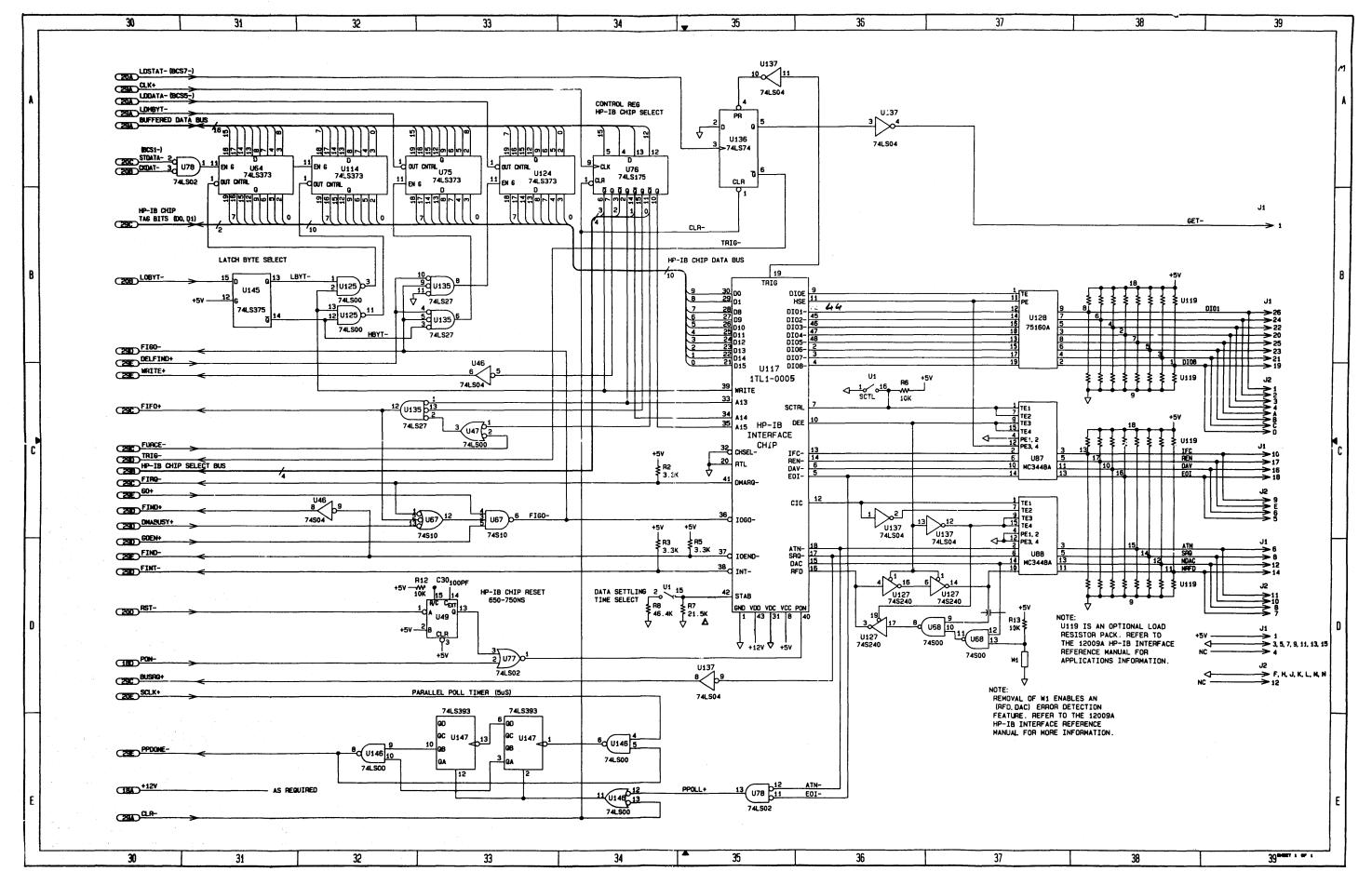

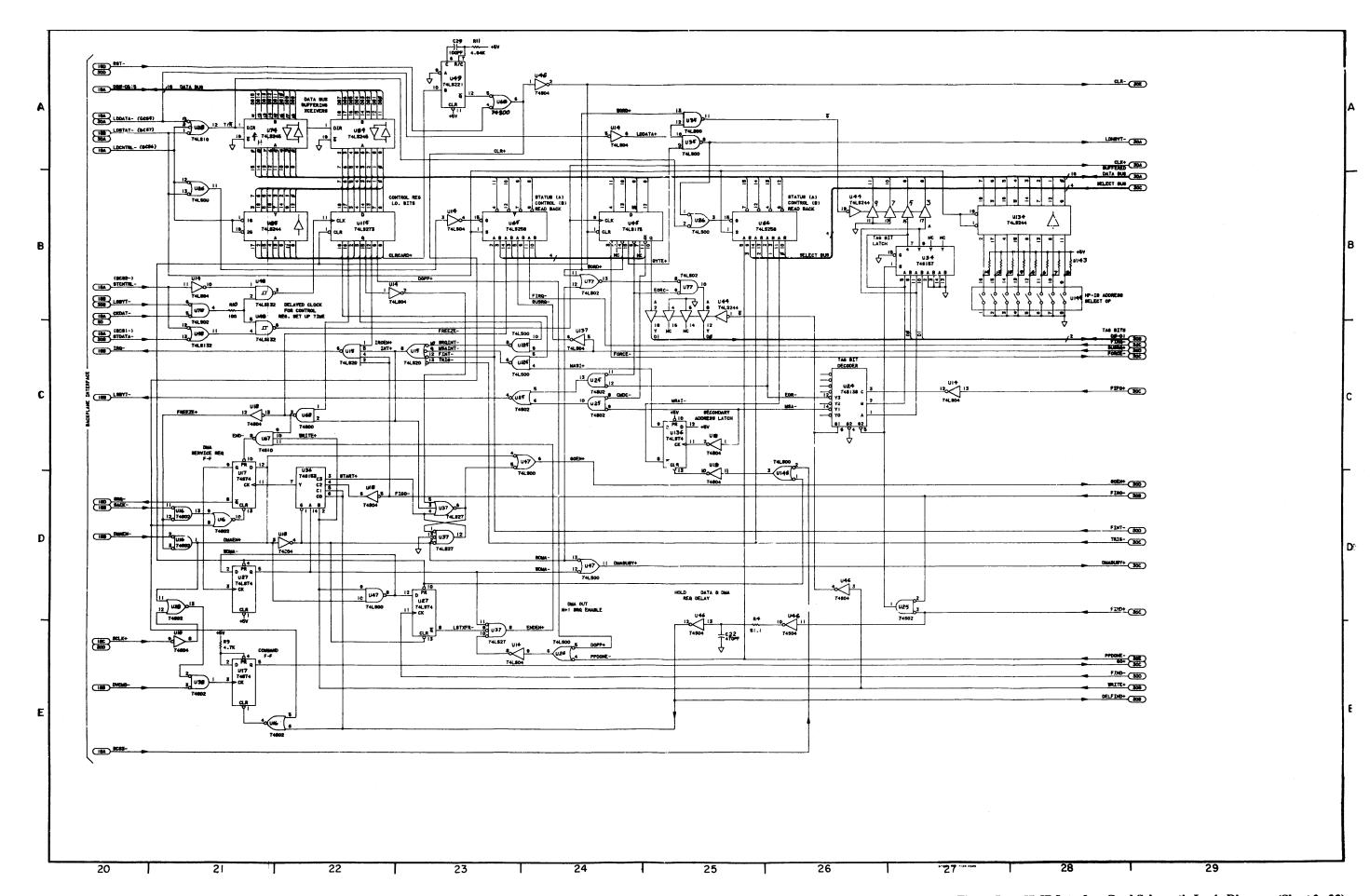

|   | HP-IB Interface Card Schematic Logic Diagram7-11    |

|   |                                                     |

Index

## Introduction

This manual provides general information, installation instructions, programming instructions, theory of operation, maintenance instructions, parts information, and service diagrams for the HP 12009A Hewlett-Packard Interface Bus (HP-IB) Interface Card.

# **Functional Description**

The Hewlett-Packard Interface Bus (HP-IB) is Hewlett-Packard's implementation of the IEEE Standard 488-1978 and Supplement 488-1978A-1980.

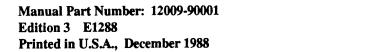

The HP-IB card provides an interface between HP 1000 A-Series computer systems and HP-IB compatible peripheral devices such as disk drives, tape drives, printers, and plotters. Up to 14 peripheral devices can connect to one HP-IB card. The peripheral devices connected to the card comprise an HP-IB system. Several systems can interface to the A-Series computer.

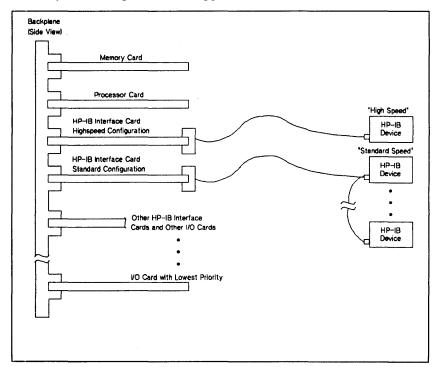

The HP-IB card plugs into a single slot in the A-Series backplane and is assigned a unique select code. The HP-IB card connects by cable to the HP-IB device or system. To the A-Series computer, this card is an I/O card under its software control. To the HP-IB system, this card might be a System Controller depending on the setting of a switch-selectable option. (See "Device Functions" in this chapter for a description of System Controller.) Figure 1-1 shows the HP-IB card in a typical A-Series system environment.

Two integrated circuits on the card are used to interface the card to the computer backplane and the card to the peripheral devices. The I/O Processor manages I/O functions. The HP-IB Interface Controller performs data and control signal interactions with the HP-IB devices. Through these two integrated circuits, the HP-IB card relieves the CPU of most HP-IB protocol processing.

The HP-IB card supports either high speed (IEEE Std 488-1978, paragraph 5.2.3) or low speed devices.

Figure 1-1. HP-IB Interface in a Typical Computer System Environment

# **Equipment Supplied**

The standard HP 12009A HP-IB Interface Card consists of the following items:

| Description                         | Part Number |

|-------------------------------------|-------------|

| HP-IB Interface Card                | 12009-60020 |

| Interconnecting Cable               | 12009-60014 |

| HP-IB Interface Reference<br>Manual | 12009-90001 |

| High-Speed Operation Tag            |             |

#### **Options Available**

Option 001 replaces interconnecting cable, part number 12009-60014, with a 4-meter cable, part number 12009-60015.

### **Identification**

Five digits and a letter (12009A in this case) identify Hewlett-Packard products used with HP computers. The five digits identify the product and the letter shows the revision level of the product.

A part number marked on the card identifies the HP-IB interface card. A letter and a four digit date code (for example, E-2420) appear with the part number. The letter identifies the version of the etched circuit on the card. The date code identifies the electrical characteristics of the assembled card.

A name and part number identify the manual. The name, part number, and publication date appear on the title page. If the manual is revised, the publication date changes.

## **Specifications**

## **Electrical Characteristics**

#### **HP-IB Bus Signal Lines**

| DIO1 | Data Input/Output 1 |

|------|---------------------|

| •    | •                   |

| •    | •                   |

| DIO8 | Data Input/Output 8 |

| DAV  | Data Valid          |

| NRFD | Not Ready for Data  |

| NDAC | Not Data Accepted   |

| IFC  | Interface Clear     |

| ATN  | Attention           |

| SRQ  | Service Request     |

| REN  | Remote Enable       |

| EOI  | End or Identify     |

#### Logic Levels

```

High > 2.4 V

Low < 0.4 V

For all signals, Low = True

```

#### **Line Termination**

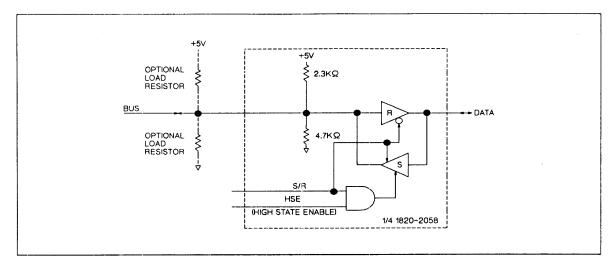

Each of the bus signal lines is terminated with 2.3 K $\Omega$  to Vcc, and 4.7 K $\Omega$  to logic common (digital ground) without the load resistor pack.

#### **Line Drivers**

Each of the bus signal lines is driven with a circuit with the following typical characteristics:

Type: Tri-state, Open Collector

Output Voltage Low State: < 0.4 V at 48 mA Output Voltage High State: 2.5 V at -5.2 mA

#### Line Receivers

Each of the bus signal lines is received with a circuit having the following typical characteristics:

Type: Schmitt Trigger

Threshold Positive Transition: 1.75 V

Threshold Negative Transition: 1.1 V

Input Current Low State: -1.3 mA at 0.4 V

Input Current High State: 0.7 mA at 5.5 V

#### **DMA Transfer Rates**

Low Speed: 500 Kbytes

High Speed:

Random Instruction Mix: 930 Kbytes Worst Case Instruction Mix: 735 Kbytes

(Worst Case is a Jump Instruction in which the target address is its own address.)

#### **Maximum Cable Length**

Standard Operation: 2 meters per device connected with a 20-meter maximum length and a settling time of more than 500 nanoseconds.

High Speed Operation: 2 meters per device connected with a 15-meter maximum length and a settling time of less than 350 nanoseconds.

#### **Operating Temperature**

0°C to 55°C

#### Power Requirements (at 25°C)

|         | Curr                  | ent                 | Power Dissipated      |                     |  |  |

|---------|-----------------------|---------------------|-----------------------|---------------------|--|--|

| Voltage | w/o Load<br>Resistors | w/Load<br>Resistors | w/o Load<br>Resistors | w/Load<br>Resistors |  |  |

| + 5 V   | 2.02 A                | 2.10 A              | 10.61 W               | 1103 W              |  |  |

| + 12 V  | 32 mA                 | 84 mA               | 0.40 W                | 1.06 W              |  |  |

|         |                       | Total power:        | 11.01 W               | 12.09 W             |  |  |

## Physical Characteristics

#### **Card Dimensions**

Width: 17.15 cm (6.75 in.) Length: 28.91 cm (11.38 in.)

#### **Connector**

30-pin printed circuit board edge connector (cable supplied has standard HP-IB connector on the device end)

## **Capabilities**

The HP-IB card can handle its own direct memory access (DMA) and can decode instructions from the CPU. Data moves over the HP-IB bidirectionally in 8-bit bytes. Data can be simultaneously transferred in three ways: (1) from a device to the computer and other devices, (2) from the computer to one or more devices, and (3) from one device to other devices under the direction of the computer.

A device may be capable of remote control operation. A system may have some devices operating under remote control, while other devices obey their front and rear panel controls (LOCAL). All devices must be addressable.

Corresponding pins of the HP-IB connectors of all devices are connected in parallel, making a parallel communication network. This permits information to flow in any direction on the bus and allows any device to talk directly with another device without going through a central control unit.

# **Supported Functions**

The interface card supports the following functions as defined by the IEEE Standard 488-1978.

#### **Controller Functions**

| C1 | System Controller                                                                                                       |

|----|-------------------------------------------------------------------------------------------------------------------------|

| C2 | Send Interface Clear and Take Charge                                                                                    |

| C3 | Send Remote Enable                                                                                                      |

| C4 | Respond to Service Request                                                                                              |

| C5 | Send Interface Messages, Receive Control, Pass Control, Pass Control to Self, Parallel Poll, Take Control Synchronously |

#### **Controlled Device Functions**

| Service Request               |

|-------------------------------|

| Remote Local                  |

| Parallel Poll (see Section 3) |

| Device Clear                  |

| Device Trigger                |

|                               |

#### **Utility Functions**

| SH1        | Source Handshake                             |

|------------|----------------------------------------------|

| AH1        | Acceptor Handshake                           |

| <b>T</b> 1 | Basic Talker, Serial Poll, Talk Only         |

| TE1        | Basic Extended Talker, Serial Poll Talk Only |

| L1         | Basic Listener, Listen Only Mode             |

| LE1        | Basic Extended Listener, Listener Only Mode  |

### Handshaking

Devices connected to the bus must be addressed by the controller before they can function. Addressing determines which device "talks" and which devices "listen." Data moves in a bit parallel, byte serial format using an interlocked handshake technique. This technique assures that the talker does not remove data before the listener has finished using the data. It also ensures that data is not lost when devices having different speeds communicate on the same bus.

### **Device Functions**

Devices connected to the bus can function in one or more of the following ways:

Talker — Any device that is capable of sending or transmitting information on the bus. There can be only one talker at a time on the bus.

**Listener** – Any device that can receive or accept information on the bus. There may be up to 14 listeners at the same time.

Talker-Listener — Any device that can both send and receive information on the bus. For example, a counter is a talker when sending data and a listener when it is being programmed.

Controller — Any device programmed to manage the flow of information between devices connected to the bus. The controller can address one of the devices as a talker and one or more of the others as listeners. A system can have more than one controller, but only one controller may be active at a time. (The Controller-in-Charge may be the System Controller.)

**System Controller** — At the time the system is configured, the system designer must designate one device as the System Controller. This device performs all the functions of a controller and can gain absolute control of the HP-IB.

## **Bus Lines**

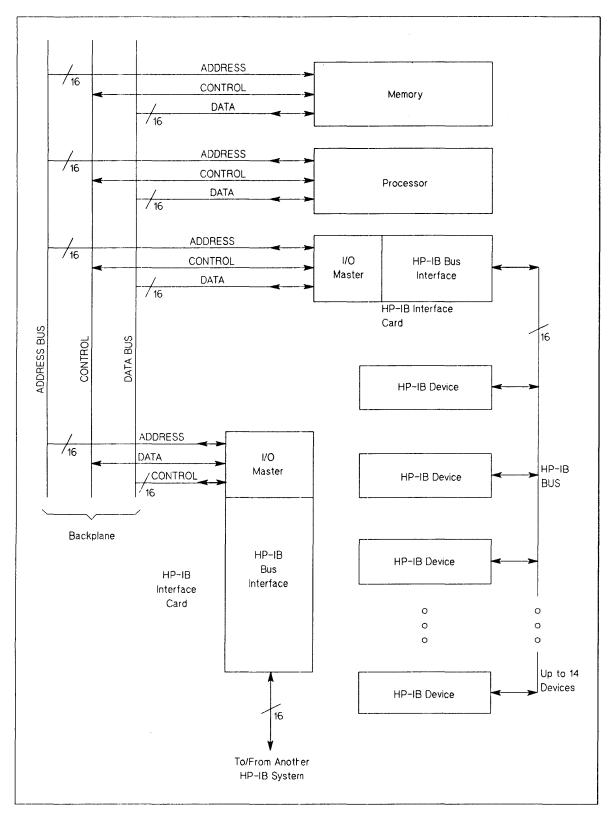

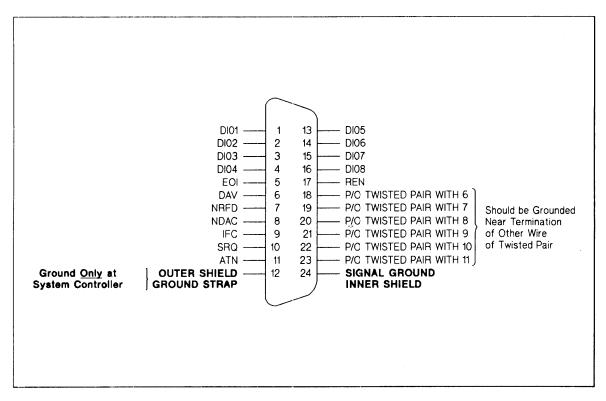

The HP-IB structure consists of 16 signal lines shown in figure 1-2. There are eight additional bus conductors: one ground, one cable shield, and six twisted-pair commons for six of the signal lines.

Each signal line has a name and mnemonic acronym that describes the message being carried on that line. There are three types of lines: Control (management), Data, and Transfer (handshake).

Figure 1-2. HP-IB Bus Structure

#### **Control Lines**

#### **Note**

All devices connected to the bus, including the controller, must conform to these descriptions.

Five control lines manage the flow of information over the data and transfer lines. They communicate control and status information between the active controller and the devices connected to the bus. All devices must use ATN and IFC. A device may or may not use REN, SRQ, and EOI.

ATN (Attention) is driven by the active controller. All other devices must monitor ATN at all times.

When the controller sets ATN to its low (active or true) state, the bus is in Command Mode. In Command Mode, the controller is the talker and all devices are listeners. The controller may send commands or address those devices that are to communicate. The controller may also send "universal commands" while the bus is in Command Mode..

When the controller sets ATN to its high (inactive or false) state, the bus is in Data Mode. The device addressed to talk and those addressed to listen now communicate on the Data Lines.

The controller may set ATN any time but it is usually at the end of a transfer (handshake) cycle so that data is not lost.

The System Controller uses IFC (Interface Clear) to initialize the bus. Only the System Controller can drive IFC and it must be monitored by all other devices on the bus. When the System Controller sets IFC low (active or true) for at least 100 microseconds, the following takes place: (1) all talkers and listeners stop, (2) serial poll mode is disabled, and (3) control returns to the HP-IB controller. When IFC is high, it has no effect on the bus operation. The System Controller may set IFC low at any time.

REN (Remote Enable) is for operating devices under remote control. Only devices capable of remote operation use REN and monitor it at all times. Devices that do not use REN terminate the line in a resistive load. Only the System Controller may assert REN and may change its state at any time.

A device sets SRQ (Service Request) low (active or true) to indicate that it wants the attention of the controller. Only the controller senses SRQ. SRQ may be set low by a device at any time except when IFC is in the low state. Some devices do not use SRQ but terminate it in a resistive load.

EOI (End or Identify) indicates the end of a character string. When the bus is in Data Mode (ATN high), the addressed talker may indicate the

end of its data by setting EOI low (active or true) at the same time it places the last byte on the Data Lines.

## Data Lines (DIO1-DIO8)

Eight Data Lines transfer data such as input, output, program code, addresses, control information, and status information. This data is passed one character (byte) at a time under control of the Transfer Lines.

#### **Transfer Lines**

Three Transfer (handshake) Lines execute the transfer of information on the data lines. All devices use these lines. An interlocked handshake technique allows asynchronous data transfer without timing restrictions on any device connected to the bus. The transfer of each byte occurs at the speed of the slowest device. The three transfer lines are: NRFD, NDAC, and DAV.

NRFD (Not Ready For Data) shows that all listeners are ready to accept data. NRFD is controlled by the listeners and sensed by the talker. When NRFD is high (inactive or false), all listeners are unconditionally ready for data and the talker may put a byte of information on the data lines.

When the controller sets ATN low (active or true), all devices must respond within 200 nanoseconds. If a device is "Ready for Data" it sets NRFD high, otherwise it sets NRFD low. When the controller sets ATN high, only those devices addressed to listen will respond.

NDAC (Not Data Accepted) indicates the acceptance of information on the data lines. NDAC is controlled by listeners and sensed by the talker. When NDAC is high (inactive or false), all listeners have accepted the byte of information on the data lines and the talker may remove that byte of information.

When the controller sets ATN low (active or true), all devices must set NDAC high within 200 nanoseconds. When the controller sets ATN high, devices addressed to listen will set NDAC high within 200 nanoseconds.

DAV (Data Valid) indicates that the information on the data lines is valid. DAV is driven by the talkers and sensed by the listeners. When DAV is low (active or true), the states of data lines DI01 through DI08 are valid and may be accepted by all listeners.

After placing the bus in Command Mode (setting ATN low), the controller must wait at least one microsecond before setting DAV low. In either Command or Data Mode, a talker designed with open-collector circuits must not set DAV low for at least two microseconds after placing valid data at its output connector. Those designed with tri-state logic must wait at least 500 nanoseconds if operating at low speed and 350 nanoseconds if operating at high speed.

Table 1-1 summarizes these conditions.

**Table 1-1. Transfer Line Conditions**

|                  | ATN Low (Command Mode)                                                                    | ATN High (Data Mode)                                                                               |

|------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| N<br>R<br>F<br>D | LOW: One or more units not ready for data. HIGH: All units ready for data                 | LOW: One or more listeners not ready for data HIGH: All addressed listeners ready for data         |

| N<br>D<br>A<br>C | LOW: One or more units have<br>not accepted data<br>HIGH: All units have<br>accepted data | LOW: One or more listeners have not accepted data HIGH: All addressed listeners have accepted data |

| D<br>A<br>V      | LOW: Controller has valid<br>data on DIO lines<br>HIGH: Controller's data is<br>not valid | LOW: The addressed talker has valid data on lines HIGH: The addressed talker data is not valid     |

<sup>\*</sup> Note: Low = active or true; High = inactive or false

## Data Transfer Timing

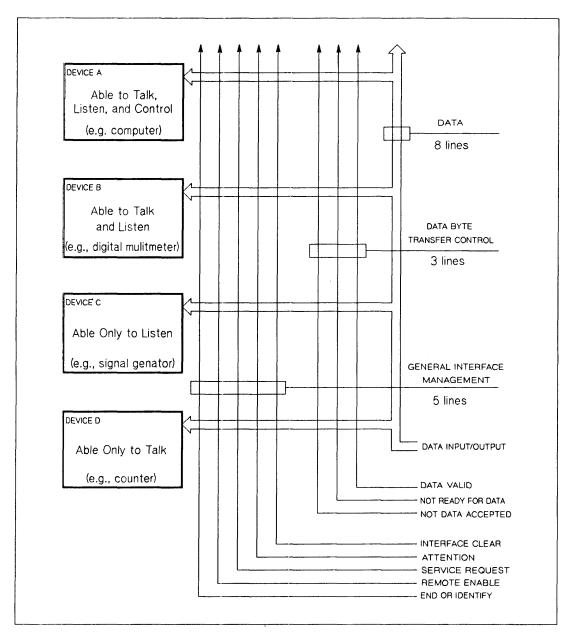

The transfer of data on the bus is asynchronous and therefore places no restrictions on the data rates of devices connected to the bus. The transfer is under the control of three lines, DAV, NRFD, and NDAC. The talker drives the Data Lines and DAV (Data Valid). The listeners drive NRFD (Not Ready for Data) and NDAC (Not Data Accepted).

The assertive, or active, state of both NRFD and NDAC is low. Since all devices on the bus have their corresponding lines connected together (for example, NRFD), all listeners must be in a high state before the line goes high. This wired-AND condition allows a talker to recognize when the slowest listener has accepted a byte of data and is ready for the next byte.

Figure 1-3 shows the timing and levels required to transfer a byte of data. The transfer is initiated by all listeners signifying they are ready for data by setting NRFD high (t-2). When the talker recognizes NRFD is high and has placed valid data on the data lines, it sets DAV low (t<sub>0</sub>). When the listeners sense that DAV is low and have finished using the data, they set NDAC high (t<sub>1</sub>).

#### Sequential Requirements of the Three Wire Transfer

#### **Events**

t-2: Listener becomes ready to accept data.

t-1: Talker has put data on the lines.

to: Indicates data is valid.

t<sub>1</sub>: Listener has accepted the data and no longer requires it held valid.

t2: Talker indicates the data is no longer valid and may change it.

t3: Listener indicates it is ready for new data.

t4: A new cycle begins (equivalent to t0).

t-1 to to: Time that data is put on lines before DAV is set low.

\* A composite of the DIO1 through DIO8 lines for illustrative purposes. The curved lines indicate transfer (handshake) signal sequence.

Figure 1-3. Transfer Timing

A listener may set NRFD low when it recognizes that DAV is low and must do so before or at the same time it sets NDAC high. The talker may return DAV to its high state after it detects that NDAC is high (t<sub>2</sub>). When it recognizes that DAV is high, a listener may set NDAC low and must do so before or at the same time it sets NRFD to its high state (t<sub>3</sub>).

# Electrical Characteristics

All 16 bus lines are compatible with TTL integrated circuits. Each line is terminated within the transceiver circuits into a resistive network consisting of a 2.3 K ohm resistor to +5 V and a 4.7 K ohm resistor to logic common. Typically, the required bus terminations are internally provided by the transceiver circuits. An optional load resistor, U119 (storage location U79) forms an external divider consisting of 330 ohm resistors to +5 V and 680 ohm resistors to logic common that can be used to provide the drive for high speed operation.

Each driver/receiver pair (see figure 1-4) forms a complete interface between the bus and a device. Either the driver or the receiver of each channel is enabled by its corresponding Send/Receive (S/R) input with the disabled output of the pair forced to a high impedance state. An additional option allows the driver to be operated in an open-collector or active pull-up configuration. The receivers have input hysteresis to improve the noise margin and their input loading follows the bus standard.

### -Cable Characteristics

In addition to the cable assemblies shipped with HP 12009A products, bus cables are available for connecting devices into a system. These have an overall shield to reduce susceptibility to external noise, and use a mixture of individual wires and twisted pairs to reduce crosstalk. The connectors on both ends of the cables are identical, terminated in two 24-pin connectors, one male and one female. The pin connections of these connectors are shown in figure 1-5.

Figure 1-4. Typical HP-IB Transceiver (Driver/Receiver) Circuit

The driver/receiver pairs provide the following: Driver: When a talker, it is capable of sinking 48 mA at 0.4 V Receiver: When a listener, it requires -1.3 mA at 0.4 V to drive

Figure 1-5. HP-IB Cable Connector Pin Connections

## Installation

This section gives information about installing and checking the operation of the HP 12009A HP-IB card.

## Requirements

#### **Power Requirements**

The HP-IB card gets its operating power from the computer's power supply through the backplane. Before installing the card, determine if the additional current drain will overload the power supply. If the card was installed at the factory, the required calculations have been made and an overload will not occur. See "Specifications" in chapter 1 for the current and voltage requirements for the HP-IB card.

#### **Interface Requirements**

#### **Backplane to HP-IB Card**

All interactions between the HP-IB card, the central processor card, and the memory card occur on the backplane through either of two connectors, P1 or P2. Tables 2-1 and 2-2 list connections from the backplane to the HP-IB card.

#### Switch Selectable Options

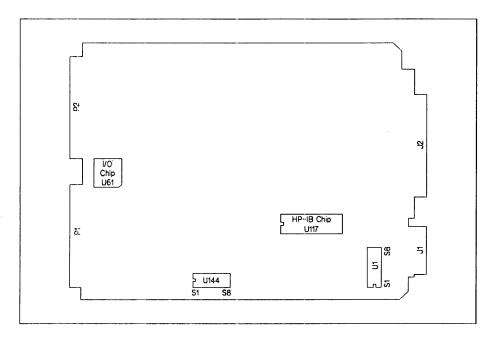

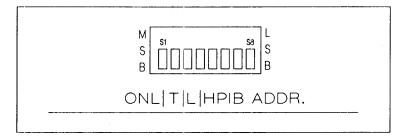

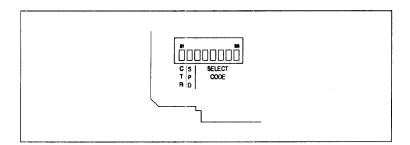

Two Dual In-line Package (DIP) switches (U1 and U144) set switch selectable options. Figure 2-1 shows the locations of the two DIP switches. Each DIP switch assembly contains eight independent switches. Switches S1 through S8 on U144 correspond to Address Select Bits 0 through 7. Switches S3 through S8 on U1 determine the select code for the card.

Table 2-1. Backplane Connections, Connector P1

| P1-        | Signal Name | Signal Definition                       |

|------------|-------------|-----------------------------------------|

| 1          | ICHID-      | Interrupt Chain In Disable              |

| 2          | ICHOD-      | Interrupt Chain Out Disable             |

| 3          | MCHID-      | Memory Chain In Disable                 |

| 4          | MCHOD-      | Memory Chain Out Disable                |

| 5          | MLOST-      | Memory Lost                             |

| 6          | MCHODOC-    | Memory Chain Out Disable Open Collector |

| 7          | PFW-        | Power Fail Warning                      |

| 8          | SPARE 1     | Reserved                                |

| 9          | SCO         | Address Extension Bus Bit 0             |

| 10         | SC1         | Address Extension Bus Bit 1             |

| 11         | SC2         | Address Extension Bus Bit 2             |

| 12         | SC3         | Address Extension Bus Bit 3             |

| 13         | GND         | Ground                                  |

| 14         | GND         | Ground                                  |

| 15         | SPARE 2     | Reserved                                |

| 16         | GND         | Ground                                  |

| 17         | SC4         | Address Extension Bus Bit 4             |

| 18         | SC5         | Self Configure                          |

| 19         | AB0         | Address Bus Bit 0                       |

|            |             |                                         |

|            |             |                                         |

|            | •           |                                         |

| <b>3</b> 3 | AB14        | Address Bus Bit 14                      |

| 34         | WE-         | Write Enable                            |

| 35         | DB0         | Data Bus Bit 0                          |

|            |             | •                                       |

|            |             | •                                       |

|            | •           | •                                       |

| 50         | DB15        | Data Bus Bit 15                         |

|            |             |                                         |

|            |             |                                         |

Table 2-2. Backplane Connection, Connector P2

| P2       | - Signal Name | Signal Definition                 |

|----------|---------------|-----------------------------------|

| 1        | CPUTURN-      | Processor Turn                    |

| 2        | GND           | Ground                            |

| 3        | Remem-        | Remote Memory                     |

| 4        | VALID-        | Data Valid                        |

| 5        | IORQ-         | I/O Handshake Request             |

| 6        | INTRQ-        | Interrupt Request                 |

| 7        | MP            | Memory Protect                    |

| 8        | RNI-          | Read Next Instruction             |

| 9        | MEMGO-        | Memory Cycle Initiation           |

| 10       | PE-           | Pairty Error                      |

| 11       | SCHID-        | Slave Chain In Disable            |

| 12       | SCHOD-        | Slave Chain Out Disable           |

| 13       | IAK-          | Interrupt Acknowledge             |

| 14       | IOGO-         | I/O Handshake Request Acknowledge |

| 15       | GND           | Ground                            |

| 16       | SLAVE-        | Slave Request                     |

| 17       | GND           | •                                 |

|          |               | Ground                            |

| 18       | MRQ-          | Memory Request                    |

| 19       | GND           | Ground                            |

| 20       | FCLK-         | Fast Clock                        |

| 21       | GND           | Ground                            |

| 22       | CCLK-         | Communications Clock              |

| 23       | PINT-         | Priority Interrupt                |

| 24       | SCLK-         | System Clock                      |

| 25       | CRS-          | Control Reset                     |

| 26       | PON           | Power On                          |

| 27       | GND           | Ground                            |

| 28       | BUSY-         | Memory Busy                       |

| 30       | GND           | Ground                            |

|          | •             | •                                 |

|          | •             | •                                 |

| 34       | GND           | Ground                            |

| 35       | +5 V          |                                   |

| 36       | +5 V          |                                   |

| 37       | +5 V          |                                   |

| 38       | +5 V          |                                   |

| 39       | +12 M         |                                   |

| 40       | –12 M         |                                   |

| 41       | +12 V         |                                   |

| 42       | +12 V         |                                   |

| 43       | +12 V         |                                   |

| 44       | -12 V         |                                   |

| 45       | +5 M          |                                   |

| 46       | +5 M          |                                   |

| 40       | AC02          |                                   |

| 47       | AC02<br>AC02  |                                   |

| 48<br>49 |               |                                   |

|          | AC01          |                                   |

| 50       | AC01          |                                   |

Figure 2-1. Major Component Locations

Figure 2-2. Switches U144S1 through U144S8

Figure 2-3. Switches U1S1 through U1S8

#### **HP-IB Address Selection**

When loaded into the HP-IB Chip's Register 7 under software control, switches U144S1 through U144S8 (see figure 2-2) determine the HP-IB address and related control functions. Switch functions are:

Switch U144S1 (Bit 7) — Puts the HP-IB Chip online when set to the open (up) position.

Switch U144S2 (Bit 6) — Puts the HP-IB Chip into the "Talk Always" mode when set to the open (up) position.

Switch U144S3 (Bit 5) — Puts the HP-IB Chip into "Listen Always" mode when set to the open (up) position.

Switches U144S4 through U144S8 (Bits 4 through 0) — The value of these five bits determines the HP-IB address to which the HP-IB Chip will respond. An open switch represents a logic 1 and a closed switch represents a logic 0. U144S4 is the Most Significant Bit (MSB) and U144S8 is the Least Significant Bit (LSB).

#### **Select Code Selection**

Switches U1S3 through U1S8 (see figure 2-3) determine the select code for the HP-IB card. An open switch represents a logic 1 and a closed switch represents a logic 0. U1S3 is the Most Significant Bit (MSB) and U1S8 is the Least Significant Bit (LSB).

#### **System Controller Selection**

Switch U1S1 (see figure 2-3) determines if the HP-IB card will be the System Controller for the bus. If the switch is set to the open (up) position, the card will function as the System Controller.

#### Data Settling Time Selection

Switch U1S2 (see figure 2-3) determines the time delay between the assertion of the data on the bus and the assertion of the data position. If the switch is set to the open (up) position, the delay is about 500 nanoseconds. When the switch is set to the closed (down) position, the delay is about 350 nanoseconds. This delay time satisfies IEEE Standard 488-1978 for fast settling time required for high-speed operation.

#### Installation

#### Caution

Some of the components used on the printed circuit card are susceptible to damage by static discharge. Refer to the safety considerations at the front of this manual before handling the card.

Make sure that the computer's power supply can handle the added load. Then follow these steps:

- 1. Set switch U1S1 up if the HP-IB card will be a System Controller, down if not.

- 2. Set switch U1S2 according to mode of operation. Set it up for slow settling time, down for fast settling time. Label all high speed devices. Do not connect high and low speed devices to the same bus.

- 3. Set the select code for the card with switches U1S3 through U1S8. (See "Select Code Selection" earlier in this chapter.)

- 4. Set the address for the card with switches U144S4 through U144S8. (See "HP-IB Address Selection" earlier in this chapter.)

#### Caution

Do not remove jumpers by desoldering unless you have experience and training in this procedure. You can seriously damage the board if you desolder a jumper incorrectly.

- 5. If you require detection of the DAC high/RFD high HP-IB bus error condition (see chapter 4), remove jumper W1 (located between U79 and U119). You can remove the jumper with wire cutters or by desoldering. Do this after an initial checkout. Removal of the jumper causes the HP-IB interface diagnostic to fail unless a peripheral device is connected to the card and powered on.

- 6. Turn off the power to the computer and the I/O device. Insert the HP-IB card into the desired slot in the backplane. Make sure that the components on the card are on the same side as the other interface cards in the backplane. Be careful not to damage the card or any adjacent cards. Press the card firmly into place.

7. Connect the appropriate cable from the bus to the card. There are two connectors (J1 and J2) on the edge of the card (see figure 2-1). Connector J2 connects to the HP-IB cable.

#### Checkout

Perform these steps to verify correct operation of the HP-IB card:

- 1. Run the computer self-test. Refer to the HP 1000 Model 26, 27 and 29 Computer System Installation and Service Manual, part number 02196-90002, or the Micro 1000 Computer System Installation and Service Manual, part number 02430-90001.

- 2. Run the kernel diagnostic. Refer to the *Diagnostic Manual*, part number 24612-90011.

- Run the HP-IB interface diagnostic. Refer to the *Diagnostic Manual*, part number 24612-90011. Note that if jumper W1 has been removed, the diagnostic will fail the on-line test unless a peripheral device is connected to the interface card.

- 4. If the HP-IB card does not operate correctly, contact the nearest Hewlett-Packard Sales and Support Office for information. See the Sales and Support Offices listed with your system documentation.

#### **Load Resistor Pack**

#### Caution

If you install or remove the load resistor incorrectly, you may damage the card.

For low speed operation, remove the load resistor pack. This resistor pack is an 18-pin DIP (Dual Inline Package), and is installed at the factory at location U119. For low speed operation move the resistor pack to U79, a storage location. Pin one of the resistor pack goes in the receptacle just above the "U" of "U79" silk-screened on the printed circuit board.

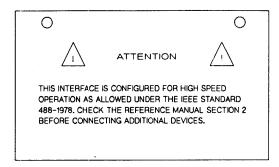

For high speed operation, leave the resistor pack in location U119. When the HP-IB card is configured for high speed operation, attach the high speed operation tag (figure 2-4) to the device end of the HP-IB cable. You can do this by wrapping a twist tie around the cable and through the holes in the tag.

Figure 2-4. HP-IB High-Speed Operation Tag

# Interconnecting Cables

The cable supplied with the card has a 30-contact circuit edge connector on one end and a standard HP-IB connector on the other end. Connect the printed circuit edge connector to J2 (see figure 2-1). Table 2-3 shows the pin connections for the interconnecting cable.

Connect the HP-IB connector end to the peripheral device. Other devices may be added to the bus by using the standard HP-IB cables listed in table 2-4. The cables must be ordered separately.

## Cabling Length Restrictions

Low-Speed Operation (U1S2 OPEN).

For low speed operation, follow these rules:

- All devices on the bus must be low speed devices.

- The total length of cable for one card must be less than or equal to 2

meters times the number of devices connected together. The HP-IB

card counts as one device.

- The total length of cable must not exceed 20 meters.

You may have up to 4 meters of cable between the first 2 devices (2 units times 2 meters per device = 4 meters). You may add units using 2-meter cables up to a total of 10 units (10 units times 2 meters per device = 20 meters). For example, you could have one 4-meter and eight 2-meter cables (4+[8X2]=20). If you want to connect more than 10 devices, you must use cables shorter than 2 meters between some of the devices. For example, 15 devices can be connected using one 4-meter cable and 13 one-meter cables (4+[13X1]=17). You can use other combinations as long as you meet the above rules. Remember to count the HP-IB card as one device.

Table 2-3. HP-IB Interface to Bus Connector (J2)

|                                                                           | J1                                      |                                                                                                                                            | J2                                                                 |        |                                                                                                                                       |

|---------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pin                                                                       |                                         | Name                                                                                                                                       | Pir                                                                | 1      | Name                                                                                                                                  |

| Pin  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 | B T B T B T B T B T B T B T B T B T B T | Name  GET- +5 V COMMON COMMON ATN COMMON SRQ COMMON IFC COMMON NRFD COMMON NRFD COMMON DAV REN EOI DI08 DI05 DI07 DI03 DI06 DI02 DI05 DI01 | Pir  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 A B C D E F H J K L M N P |        | DI01 DI02 DI03 DI04 EOI DAV NRFD NDAC IFC SRQ ATN — — DI05 DI06 DI07 DI08 REN COMMON COMMON COMMON COMMON COMMON COMMON COMMON COMMON |

|                                                                           |                                         |                                                                                                                                            | R<br>S                                                             | B<br>B |                                                                                                                                       |

B = bottom

C = top

Table 2-4. Accessory HP-IB Bus Cables

| Length     | Accessory Number |

|------------|------------------|

| 1 meter    | 10833A           |

| 2 meters   | 10833B           |

| 4 meters   | 10833C           |

| 0.5 meters | 10833D           |

#### **High Speed Operation (U1S2 CLOSED)**

For maximum data transfer rate (nominally 930 K bytes per second), follow these rules:

- All devices expected to talk at the higher rates must use a settling time of 350 nanoseconds or less.

- All devices expected to operate at the higher speeds should use

48 mA three-state drivers.

- The device capacitance on each lead (REN and IFC excepted) should be less than 50 pF per device. In a system configuration, the total device capacitance should be no more than 50 pF for each equivalent resistive load in the system.

- Keep cable links as short as possible according to table 2-4.

Table 2-4. Cabling Guidelines for High Speed Operation

| Number of<br>External<br>Devices | Maximum Total Cable Length (meters) | Maximum Average Cable Length Between Devices (meters) |

|----------------------------------|-------------------------------------|-------------------------------------------------------|

| 1                                | 9                                   | 9                                                     |

| 2                                | 10                                  | 5                                                     |

| 3                                | 11                                  | 3                                                     |

| 4                                | 12                                  | 3                                                     |

| 5                                | 13                                  | 2                                                     |

| 6                                | 14                                  | 2                                                     |

| 7                                | 15                                  | 2                                                     |

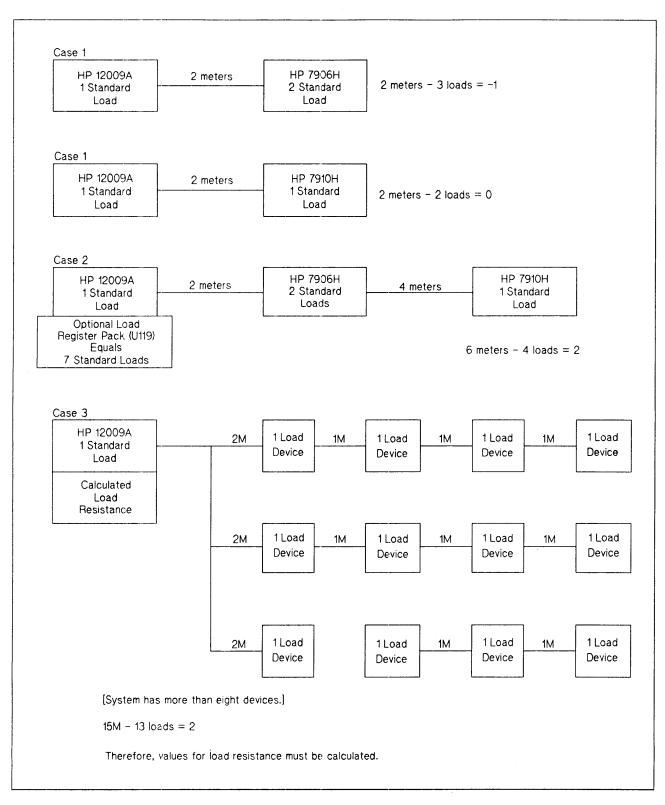

- Normally, no more than eight high speed devices can be in the system (the HP-IB card counts as one device). A normal maximum system is composed of the HP-IB card with its high-speed resistor pack and up to seven peripherals (See case 2 in figure 2-5). Note that the optional load resistor pack adds the equivalent of 7 loads to the outputs to increase drive to external devices.

- All devices on the bus should be powered on.

#### **Note**

If power to the HP-IB card fails while the load resistor pack is installed, the HP-IB bus will be pulled down. That is, the output drive circuitry of any talker on the bus will not be able to bring any bus line to a logic-high state. To the drive circuitry, the unpowered HP-IB card is a low resistance path to ground.

- The following information is provided if you have specialized knowledge and the equipment to verify the correct operation of the system. Use this for high speed configurations with more than eight device load equivalents (usually seven peripherals) and more than eight meters of cable.

- 1. Calculate N as:

M = meters of cable

load = device load equivalents

N = M - load

2. If N > 0 and more than eight devices are present in the HP-IB system, the optional resistor pack supplied with the card will not meet the requirements for the system. Use the following formulas to determine the resistance values:

Resistance to Vcc =

$$\frac{2.3 \text{ K}\Omega}{\text{N}}$$

Resistance to logic common

$$= \frac{4.7 \text{ K}\Omega}{\text{N}}$$

Once you have calculated the correct values for the load resistors you

must have a custom resistor pack manufactured. Hewlett-Packard

does not manufacture custom resistor packs for this product.

In high speed operation, stray resistance and capacitance may adversely affect the settling time of the control and data lines on the HP-IB bus. The result may be intermittent failures and loss of data. If you are using a configuration similar to cases 1 and 3 in figure 2-5 verify the proper operation of the system.

## Other Cabling Considerations

Do not stack more than four HP-IB connectors on one device. If you do, force will be exerted on the panel of the device and may cause damage. A daisy chain configuration will avoid this.

Figure 2-5. HP-IB System Examples

## Reshipment

If you need to ship the HP-IB to Hewlett-Packard for any reason, attach a tag identifying the owner and giving the reason for shipment. Include the part number of the HP-IB.

### Caution

Be sure the packer observes anti-static precautions.

Pack the HP-IB in the original factory packing material, if available. If the original material is not available, use good commercial packing material. Reliable commercial packing and shipping companies have the facilities and materials to repack the item.

## **Programming**

This card can handle its own Direct Memory Access (DMA), decode its own instructions from the central processor, pack and unpack bytes, and support the HP-IB functions listed in chapter 1 of this manual. If the standard interface driver, ID.37, does not provide sufficient control of the above capabilities, you may write your own Interface Driver in assembly language. This chapter provides specific assembly language information about the HP-IB Interface. This chapter is not a tutorial on HP 1000 A-Series assembly language or on the design of interface drivers. Your local Hewlett-Packard Sales and Support office can help you determine what additional manuals you may need.

For additional information, see the RTE-A Programmers Reference Manual, part number 92077-90007.

If you intend to use a high-level language to control the HP-IB Interface, consult the language's user manual for information.

#### **Note**

If your HP 12009A has had the NDAC-NRFD error detection feature enabled (jumper W1 has been cut) you must set up a finite time-out. Have the driver call it on exit.

## **Overview**

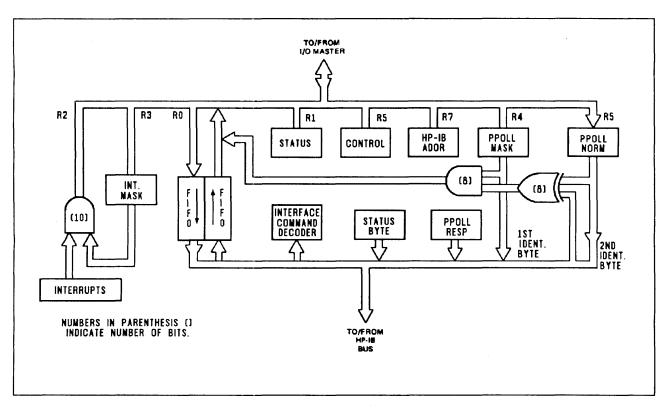

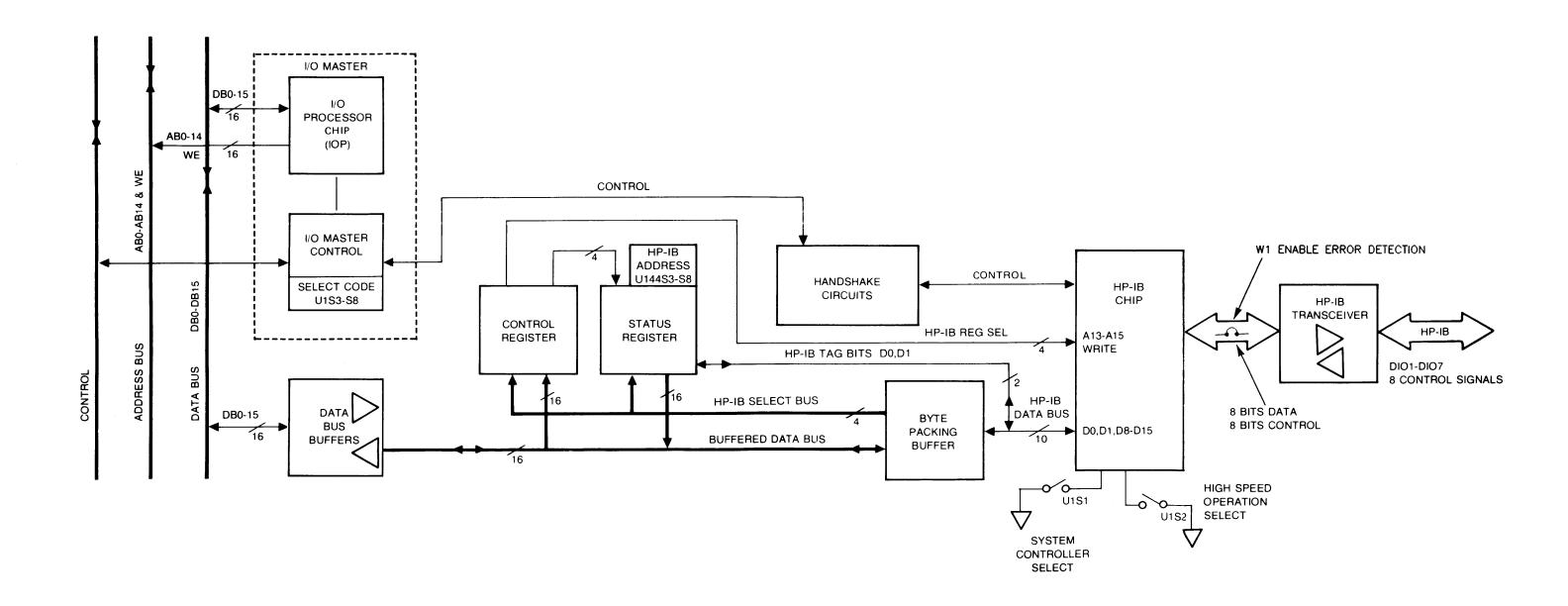

The A-Series Interface card has two sections, an I/O Master section and an HP-IB Bus Interface section.

#### I/O Master Section

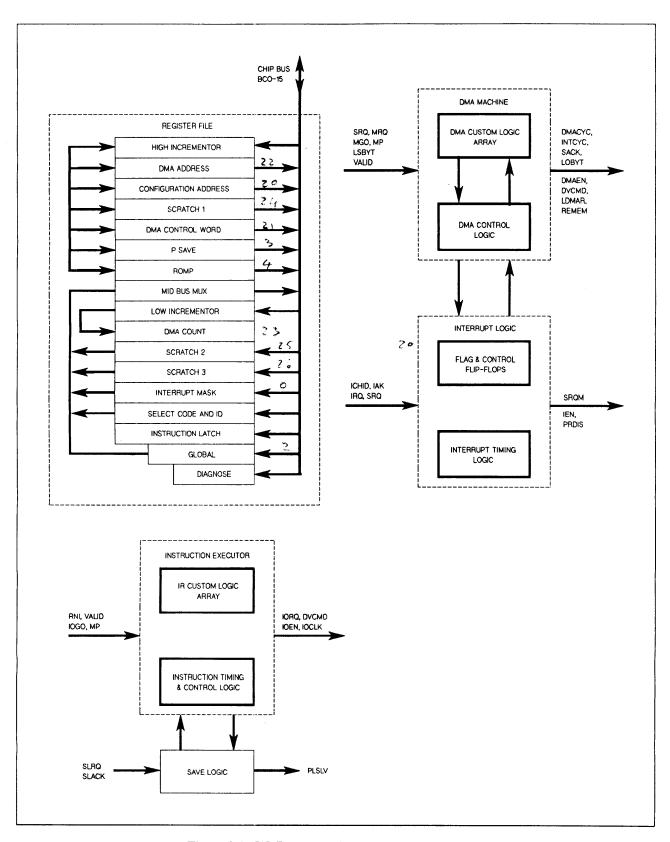

The I/O Master section performs all I/O processing functions for the computer. These functions include I/O instruction recognition and execution and direct memory access (DMA). The I/O Master consists of an I/O Processor (IOP) Chip and associated logic circuitry. See figure 3-1 for a simplified block diagram of the I/O Processor Chip.

#### Global Register

The Global Register (GR) is a 6-bit register located in the I/O Processor Chip and controlled by the CPU. This register may be loaded with an OTA 2 (Output A) or OTB 2 (Output B) I/O instruction, enabled with a CLF 2 (Clear Flag) I/O instruction, and disabled with an STF 2 (Set Flag) I/O instruction. When the Global Register is enabled, any I/O instruction that is executed by the CPU automatically applies to the card whose select

code is in the Global Register. If the HP-IB card is selected, the current I/O instruction is decoded and executed by the HP-IB card.

Using the Global Register to store the select code frees the six least significant bits of the I/O instructions so they can be used to address registers on the HP-IB card. There are three such registers, a Data Register, a Status Register, and a Control Register, in addition to registers which are internal to the I/O Processor Chip.

Data may be transferred to and from the HP-IB card with or without the Global Register enabled. The Global Register must be enabled to access the card's Control and Status registers.

#### I/O Instruction Set

The I/O Master executes the following twelve I/O instructions:

| CLC | Clear Control      |

|-----|--------------------|

| CLF | Clear Flag         |

| LIA | Load Into A        |

| LIB | Load Into B        |

| MIA | Merge Into A       |

| MIB | Merge Into B       |

| OTA | Output A           |

| OTB | Output B           |

| SFC | Skip if Flag Clear |

| SFS | Skip if Flag Set   |

| STF | Set Flag           |

| STC | Set Control        |

|     |                    |

The 6-bit Global Register allows a maximum of 64 (decimal) select codes. The I/O Master executes a portion of these. Select codes 00 through 17 (octal) are reserved for the CPU, leaving 20 through 77 (octal) available for the I/O system. For further information about the I/O instruction set, refer to the Reference Manual for your computer.

#### **Instruction Usage Summary**

Table 3-1 lists all of the I/O Processor instructions. These are recognized by their select codes. There are three conditions relevant to the instruction's execution:

- Is the Global Register (GR) enabled?

- Do the contents of the GR equal the I/O Processor Chip's select code?

- Do the lower six bits of the instruction equal the I/O Processor Chip's select code (IR = SC)?

Figure 3-1. I/O Processor Chip (U61) Block Diagram

Table 3-1. I/O Processor Chip Instructions by Select Code

| interrupt mask ge GR ge  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y<br>Y | Y Y X X X X X X X X X X X X X Y Y Y Y Y                                 | x x x x x x x x x x x x x x x x x x x                                                       | 1,9<br>1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>3                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| ge interrupt mask e interrupt mask e interrupt mask ele GR ble GR l GR ge GR ele GR ele Slave logic ble GR EAK" to front panel EAK" to front panel EAK" to front panel I P SAVE ge P SAVE le P SAVE  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                     | X<br>X<br>X<br>Y<br>Y<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| e interrupt mask  sole GR  sole GR  ge GR  ge GR  sole Slave logic  sole GR  EAK" to front panel  EAK" to front panel  EAK" to front panel  EAK" to front panel  EAKBE SAVE  ge P SAVE  ge P SAVE  ge P SAVE  ge ROM P   | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                     | X<br>X<br>X<br>Y<br>Y<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| ble GR G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                          | X<br>Y<br>Y<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y           | x x x x x x x x x x x x x x x x x x x                                                       | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| ble GR G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                          | X<br>Y<br>Y<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y           | x x x x x x x x x x x x x x x x x x x                                                       | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| GR ge Save logic ge GR ge AK" to front panel ge AK" to front panel ge P SAVE ge ROM P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                          | Y Y X X X X X X X X X X X Y Y Y Y Y Y                                   | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| ge GR ge GR ge GR ge GR ge GR gele Slave logic ble GR  EAK" to front panel EAK" to front panel P SAVE ge ROM P ge R | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                               | Y X X X X X X X X X X Y Y Y Y Y                                         | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 1,9<br>1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |

| e GR ble Slave logic ble GR  EAK" to front panel EAK" to front panel P SAVE EP SAVE P  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                               | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y                     | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 1,2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2        |

| ele Slave logic ele GR  EAK" to front panel EAK" to front panel P SAVE P | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                                    | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y                          | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2          |

| EAK" to front panel EAK" to front panel EAK" to front panel P SAVE P SAV | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y                                    | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y                          | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x                                         | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2          |

| EAK" to front panel EAK" to front panel I P SAVE the P SAVE ROM P ROM P ROM P THE FLG 20 clear IF FLG 20 set TFLG 20 and FLG 21 LG 20 THE DMA self-configuration The EDMA self-configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y<br>Y                                    | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y                          | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x                                                   | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                                                                 |

| EAK" to front panel P SAVE P SAVE P SAVE P SAVE ROM P ROM P ROM P If FLG 20 clear If FLG 20 and FLG 21 LG 20 Ile DMA self-configuration Ile DMA self-configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y<br>Y<br>Y                                    | X<br>X<br>X<br>X<br>X<br>X<br>X<br>Y<br>Y<br>Y                          | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x                                                   | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                                                                 |