## HP 12009A HP-IB Interface

## Reference Manual

## **REFERENCE MANUAL**

## HP 12009A HP-IB INTERFACE

Manual Part No. 12009-90001 Printed in U.S.A. JAN 1980

Card Assembly: 12009-60001 Date Code: A-2001, B-2001

## **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages contain replacement pages or write-in instructions to be merged into the manual by the customer. Manuals will be reprinted as necessary to incorporate all prior updates. A reprinted manual is identical in content (but not in appearance) to the previous edition with all updates incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

| First Edition | <br> | <br> | <br>Jan 198        |

|---------------|------|------|--------------------|

| Update 1      | <br> | <br> | <br>March 198      |

| Update 2      | <br> | <br> | <br>September 198  |

| Reprint       | <br> | <br> | <br>September 1989 |

## NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

## **SAFETY CONSIDERATIONS**

**GENERAL** - This product and relation documentation must be reviewed for familiarization with safety markings and instructions before operation.

### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

## WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

### CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

### CAUTION

## STATIC SENSITIVE DEVICES

When any two materials make contact, their surfaces are crushed on the atomic level and electrons pass back and forth between the objects. On separation, one surface comes away with excess electrons (negatively charged) while the other is electron deficient (positively charged). The level of charge that is developed depends upon the type of material. Insulators can easily build up static charges in excess of 20,000 volts. A person working at a bench or walking across a

floor can build up a charge of many thousands of volts. The amount of static voltage developed depends on the rate of generation of the charge and the capacitance of the body holding the charge. If the discharge happens to go through a semiconductor device and the transient current pulse is not effectively diverted by protection circuitry, the resulting current flow through the device can raise the temperature of internal junctions to their melting points. MOS structures are also susceptible to dielectric damage due to high fields. The resulting damage can range from complete destruction to latent degradation. Small geometry semiconductor devices are especially susceptible to damage by static discharge.

The basic concept of static protection for electronic components is the prevention of static build-up where possible and the quick removal of already existing charges. The means by which these charges are removed depend on whether the charged object is a conductor or an insulator. If the charged object is a conductor such as a metal tray or a person's body, grounding it will dissipate the charge. However, if the item to be discharged is an insulator such as a plastic box/tray or a person's clothing, ionized air must be used.

Effective anti-static systems must offer start-tofinish protection for the products that are intended to be protected. This means protection during initial production, in-plant transfer, packaging, shipment, unpacking and ultimate use. Methods and materials are in use today that provide this type of protection. The following procedures are recommended:

- 1. All semiconductor devices should be kept in "antistatic" plastic carriers. Made of transparent plastics coated with a special "antistatic" material which might wear off with excessive use, these inexpensive carriers are designed for short term service and should be discarded after a period of usage. They should be checked periodically to see if they hold a static charge greater than 500 volts in which case they are rejected or recoated. A 3M Model 703 static meter or equivalent can be used to measure static voltage, and if needed, carriers (and other non-conductive surfaces) can be recoated with "Staticide" (from Analytical Chemical Laboratory of Elk Grove Village, Ill.) to make them "antistatic."

- 2. Antistatic carriers holding finished devices are stored in transparent static shielding bags made by 3M Company. Made of a special three-layer material (nickle/polyester/polyethylene) that is "antistatic" inside and highly conductive outside, they provide a Faraday cage-like shielding which protects devices inside. "Antistatic" carriers which contain semiconductor devices should be kept in these shielding bags during storage or in transit.

Individual devices should only be handled in a static safeguarded work station.

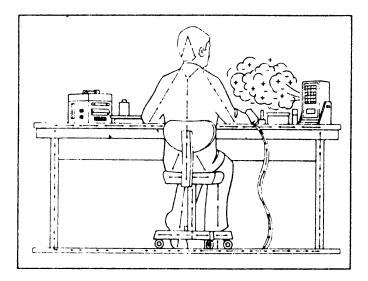

3. A typical static safeguarded work station is shown below including grounded conductive table top, wrist strap, and floor mat to discharge conductors as well as ionized air blowers to remove charge from nonconductors (clothes). Chairs should be metallic or made of conductive materials with a grounding strap or conductive rollers.

SAFETY EARTH GROUND - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER** - Verify that the product is configured to match the available main power source per the input power configuration instructions provided in this manual.

If this product is to be energized via an auto-transformer (for voltage reduction) make sure the common terminal is connected to the earth terminal of the main power source.

#### SERVICING

## WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by qualified personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged even when disconnected from its power source.

To avoid a fire hazard, only fuses with the required current rating and of the specified type (normal blow, time delay, etc.) are to be used for replacement.

## WARNING

## **EYE HAZARD**

Eye protection must be worn when removing or inserting integrated circuits held in place with retaining clips.

## **CONTENTS**

| Section 1 Page                               | Status Register (LI"/O1" 32)                    |

|----------------------------------------------|-------------------------------------------------|

| INTRODUCTION                                 | Direct Memory Access (DMA) Function             |

| Introduction                                 | DMA Control and Status Words 3-8                |

| Description                                  | DMA Self-Configuration, Register 20 3-8         |

| Equipment Supplied                           | DMA Control Word 1, Register 21 3-9             |

| Identification                               | DMA Address, Register 22 3-9                    |

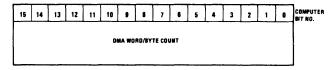

| Reference Manual                             | DMA Word/Byte Count, Register 23 3-9            |

| Specifications                               | DMA Transfer Operation 3-10                     |

| Hewlett-Packard Interface Bus (HP-IB)        | DMA Input Transfer 3-10                         |

| Capabilities 1-5                             | DMA Output Transfer                             |

| HP-IB Supported Functions                    | DMA Transfer Termination 3-10                   |

| Addressing-Talking-Listening-Handshaking 1-5 | DMA Self-Configuration Feature 3-10             |

| Functions of Devices on the HP-IB1-5         | DMA Self-Configuration Initialization 3-10      |

| HP-IB Bus Lines                              | DMA Self-Configuration Operation 3-10           |

| Control Lines                                | DMA Self-Configuration Termination 3-1          |

| Data Lines (DIO1-DIO8)                       | Types of DMA Transfers                          |

| Transfer Lines                               | Byte Mode DMA Input                             |

| Data Transfer                                | Byte Mode DMA Output                            |

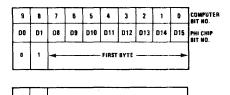

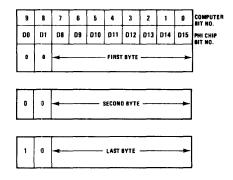

| HP-IB Electrical Characteristics             | DMA Control Word 1 (LI*21 or OT*21) 3-12        |

| HP-IB Physical Characteristics               | Card Control Word and DMA                       |

| 111 -115 Thysical Characteristics            | PHI FIFO DMA Programming                        |

|                                              | HP-IB Interface Card Programming                |

| Section II Page                              |                                                 |

|                                              | Characteristics                                 |

| INSTALLATION                                 | Initialization (Power On and I/O Clear)3-13     |

| Introduction                                 | System Controller and Controller-In-Charge 3-14 |

| Unpacking and Inspection                     | Bus Controller Device                           |

| Preparation for Installation2-1              | Interrupts                                      |

| Computation of Power Requirements 2-1        | Card Flag Interrupts                            |

| Interface Requirements 2-1                   | Programming Examples 3-18                       |

| Backplane To HP-IB Interface Card2-1         | Non-DMA Transfer Example 3-18                   |

| Switch Selectable Options                    | DMA Transfer Example                            |

| HP-IB Address Selection                      | Word Format Summary 3-18                        |

| Select Code Selection                        | PHI Chip Register Definitions 3-15              |

| System Controller Selection                  | Register 0: Outbound FIFO/Inbound FIFO 3-18     |

| Data Settling Time Selection                 | Register 1: Status 3-20                         |

| Installation                                 | Register 2: Interrupting Conditions 3-21        |

| Checkout                                     | Register 3: Interrupt Mask                      |

| Interconnecting Cables                       | Register 4: Parallel Poll Mask/First            |

| Interface Card Cable2-5                      | ID Byte                                         |

| Cabling Length Restrictions                  | Register 5: Parallel Poll/Second ID Byte 3-23   |

| Cabling Configurations                       | Register 6: Control 3-23                        |

| Reshipment 2-6                               | Register 7: HP-IB Address 3-25                  |

|                                              | Offline Diagnostics 3-25                        |

|                                              |                                                 |

| Section III Page                             |                                                 |

| PROGRAMMING                                  |                                                 |

| Introduction 3-1                             | Section IV Page                                 |

| Use Of The Global Register                   | THEORY OF OPERATION                             |

| I/O Instruction Set                          | Introduction                                    |

| Instruction Usage Summary                    | General Description4-1                          |

| HP-IB Capability                             | Theory of Operation Overview                    |

| PHI Chip                                     | Functional Theory of Operation                  |

| Programmed Input/Output3-6                   | Non-DMA Transfers 4-5                           |

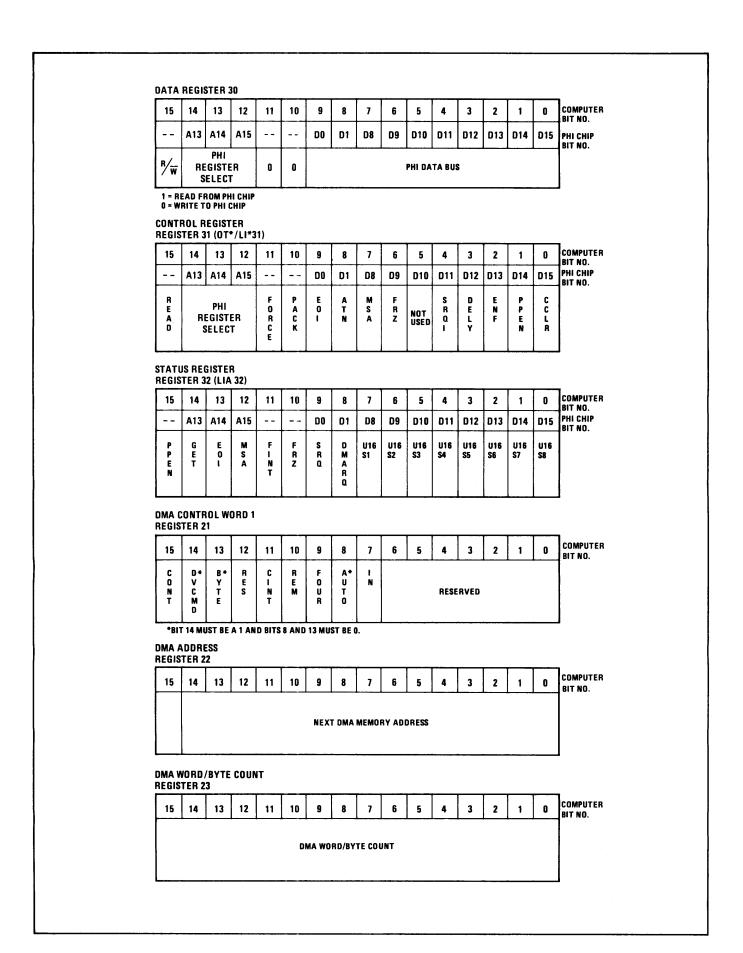

| Data Register (OT*/LI* 30)                   | Output Transfer 4-5                             |

| Control Register (LI*/LI* 31)                | Input Transfer 4-6                              |

|                                              | input itansiei 4-0                              |

# **CONTENTS** (Continued)

| DMA Transfer 4-7                         | Removal And Installation Procedures For The |

|------------------------------------------|---------------------------------------------|

| DMA Word Mode Transfers 4-7              | I/O Processor (IOP) Chip (U67) And The      |

| DMA Byte Mode Transfers 4-7              | PHI Chip (U43)5-1                           |

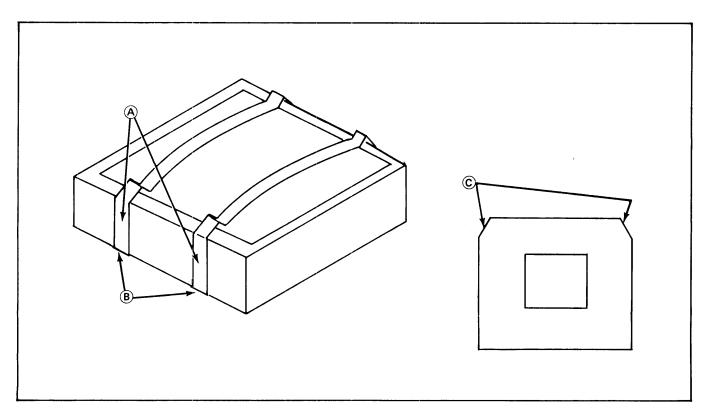

| DMA I/O Master Handshake 4-7             | Removing the SOS Chip From Its Socket 5-1   |

| Control Word Transfer 4-8                | Installing The SOS Chip In Its Socket 5-1   |

| Writing The Control Word Instruction:    | Troubleshooting5-2                          |

| OTA 31 4-8                               |                                             |

| Reading The Control Word Instruction:    |                                             |

| LI* 32 4-9                               | Section VI Page                             |

| Status Word Transfer 4-9                 | REPLACEABLE PARTS                           |

| Reading the Status Register Instruction: | Introduction                                |

| LI* 32 4-9                               | Replaceable Parts                           |

| Conclusion 4-9                           | Ordering Information                        |

| HP-IB Bus Operation4-9                   | Ordering information                        |

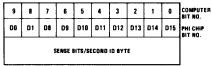

| HP-IB Transceiver Operation 4-9          |                                             |

| PHI Chip Options4-10                     | 0 11 1777                                   |

|                                          | Section VII Page                            |

|                                          | SERVICE DIAGRAMS                            |

| Section V Page                           | Introduction 7-1                            |

| MAINTENANCE                              |                                             |

| Introduction 5-1                         |                                             |

| Preventive Maintenance5-1                | INDEXI-1                                    |

|                                          |                                             |

## **ILLUSTRATIONS**

| Title Pa                                    | age | Title                                    | Page   |

|---------------------------------------------|-----|------------------------------------------|--------|

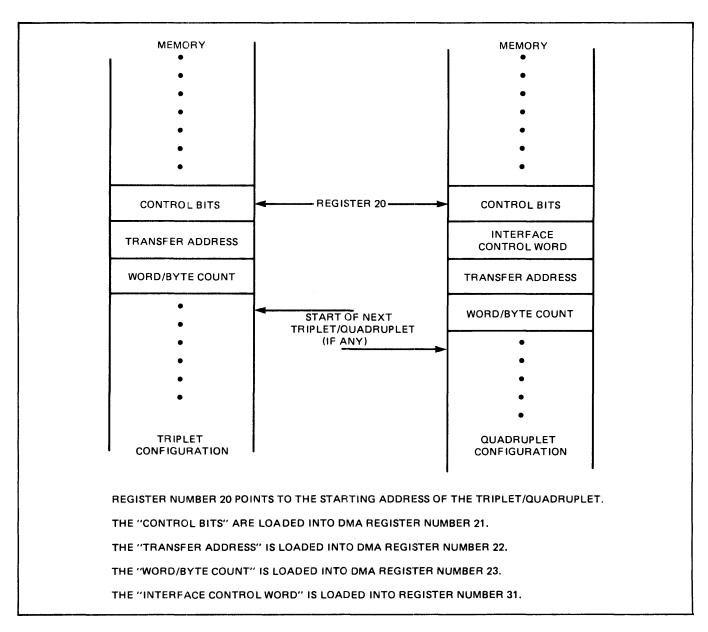

| HP 12009A HP-IB Interface                   | 1-0 | DMA Self-Configuration Formats           | 3-8    |

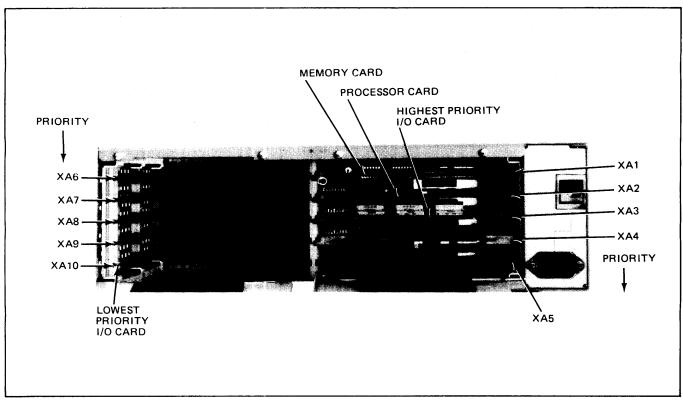

| Typical L-Series Card Cage Layout           | 1-1 | Word Format Reference Summary            | . 3-17 |

| HP-IB Interface in a Typical L-Series       |     | HP-IB Transceiver's On-Line and          |        |

| System Environment                          | 1-2 | Off-Line States                          | . 3-26 |

| HP-IB Bus Structure                         |     | Typical L-Series System                  | 4-2    |

| Transfer Timing                             |     | HP 12009A HP-IB Inteface Simplified      |        |

| Typical HP-IB Transceiver (Driver/Receiver) |     | Block Diagram                            | 4-3    |

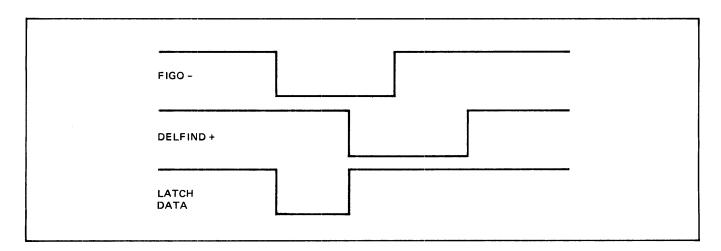

| Circuit                                     | -10 | FIGO- and DELFIND+ Timing Diagram        | 4-6    |

| HP-IB Cable Connector Pin Connections 1     | -11 | SOS Socket with Chip and Retaining Clips | 5-2    |

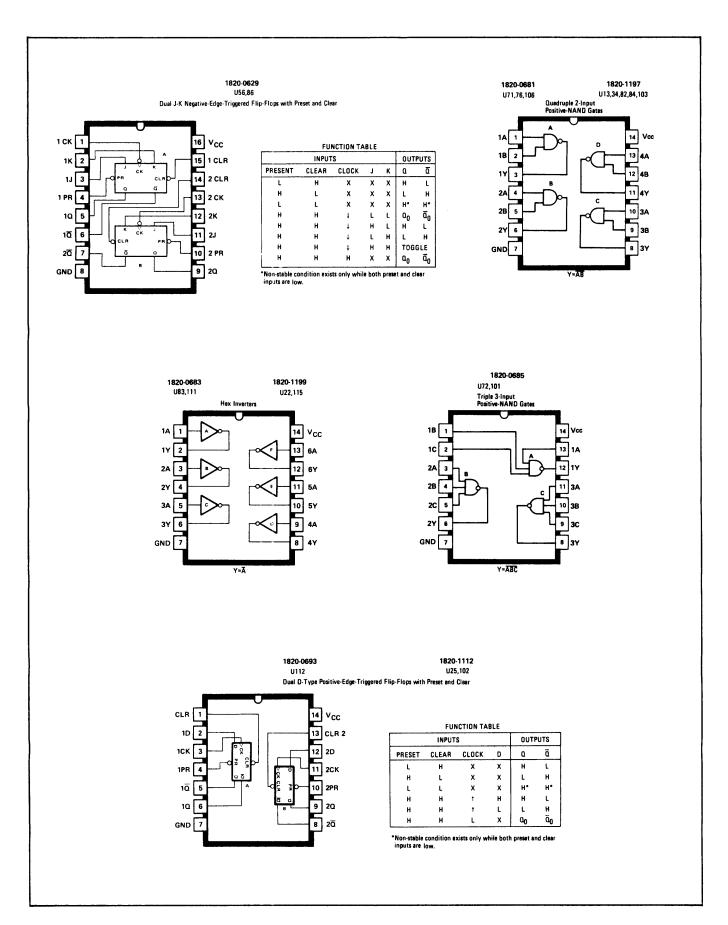

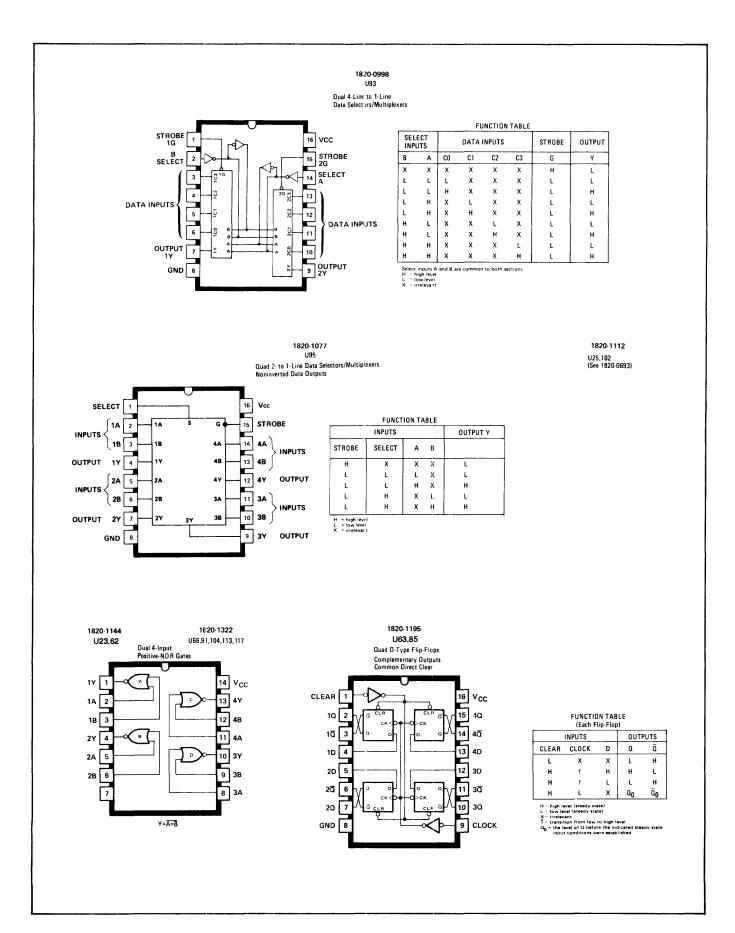

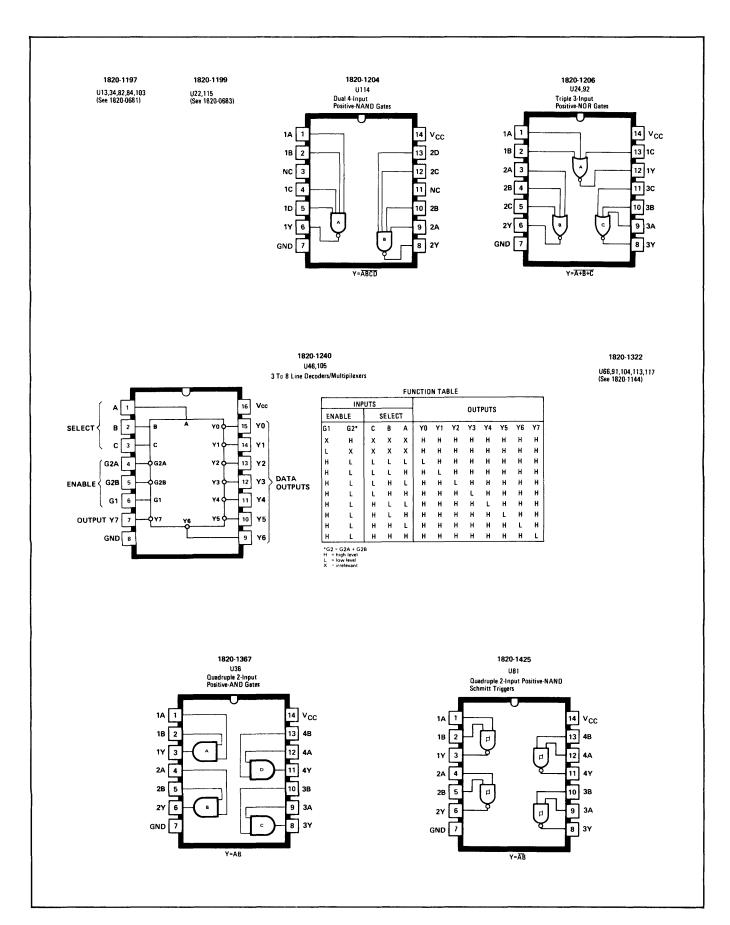

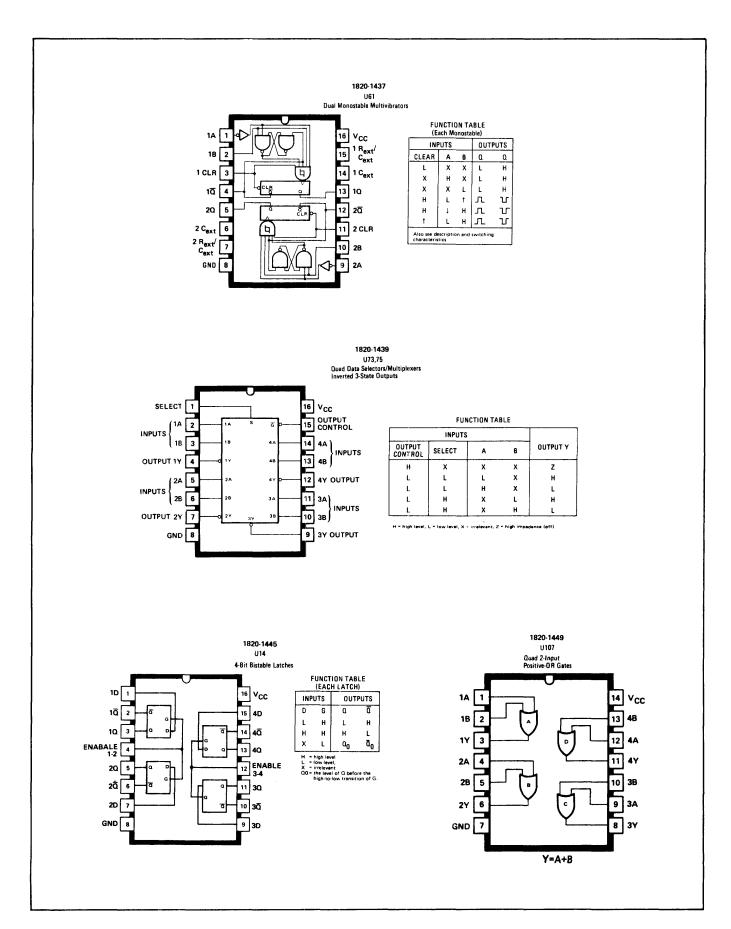

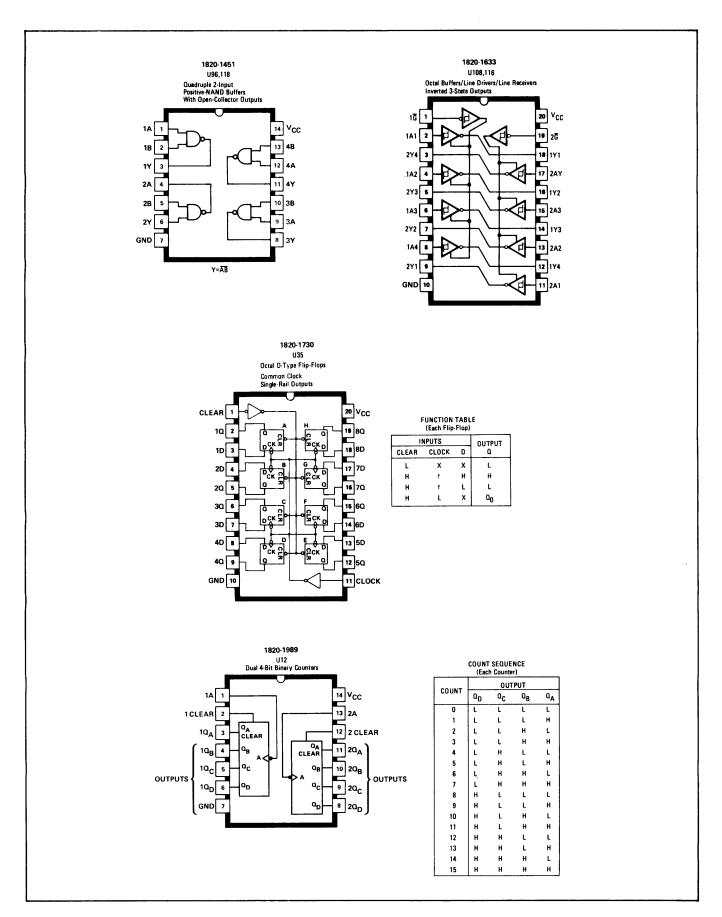

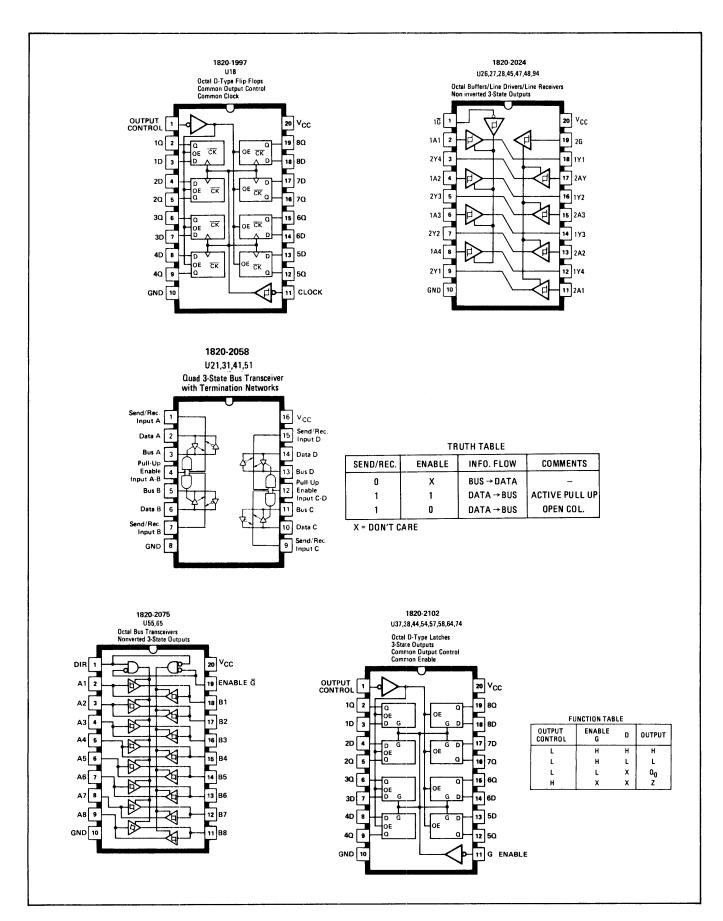

| HP-IB Interface Card HP 12009-60001         | 2-3 | Integrated Circuit Base Diagrams         | 7-2    |

| U16S1-U16S8 HP-IB Address Selector Switches | 2-4 | HP-IB Interface Functional               |        |

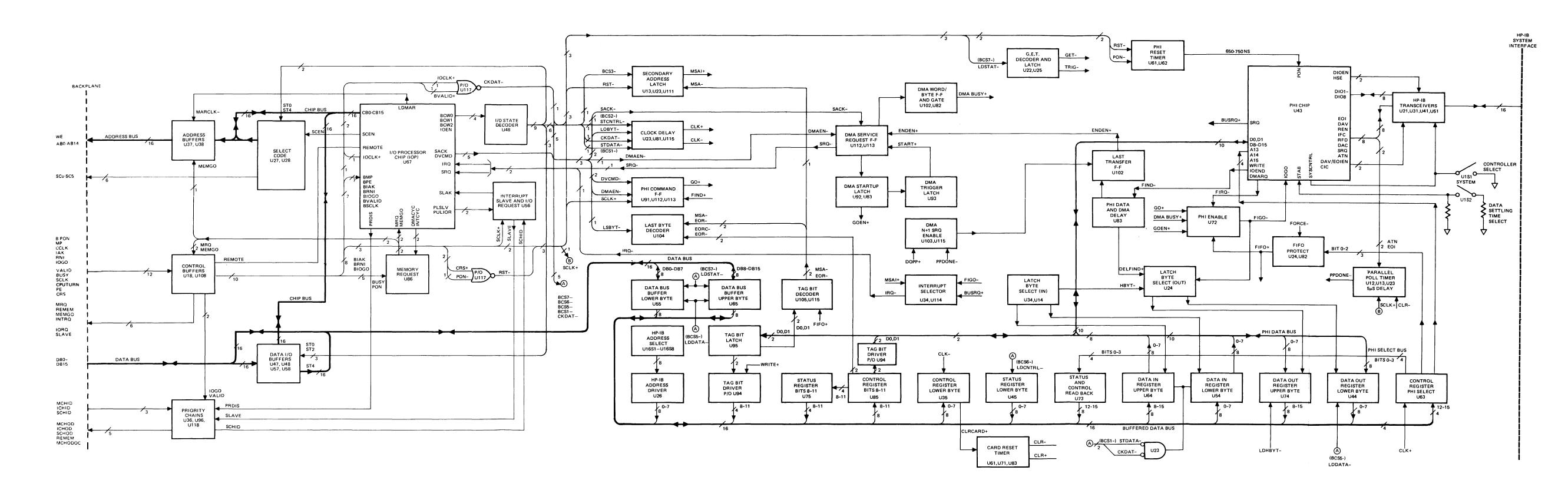

| U1S3-U1S8 Card Select Code Switches         | 2-4 | Block Diagram                            | . 7-11 |

| HP-IB High Speed Operation Card             | 2-6 | HP 12009-60001 HP-IB Interface Card      |        |

| HP-IB System Examples                       | 2-7 | Component Location Diagram               | . 7-12 |

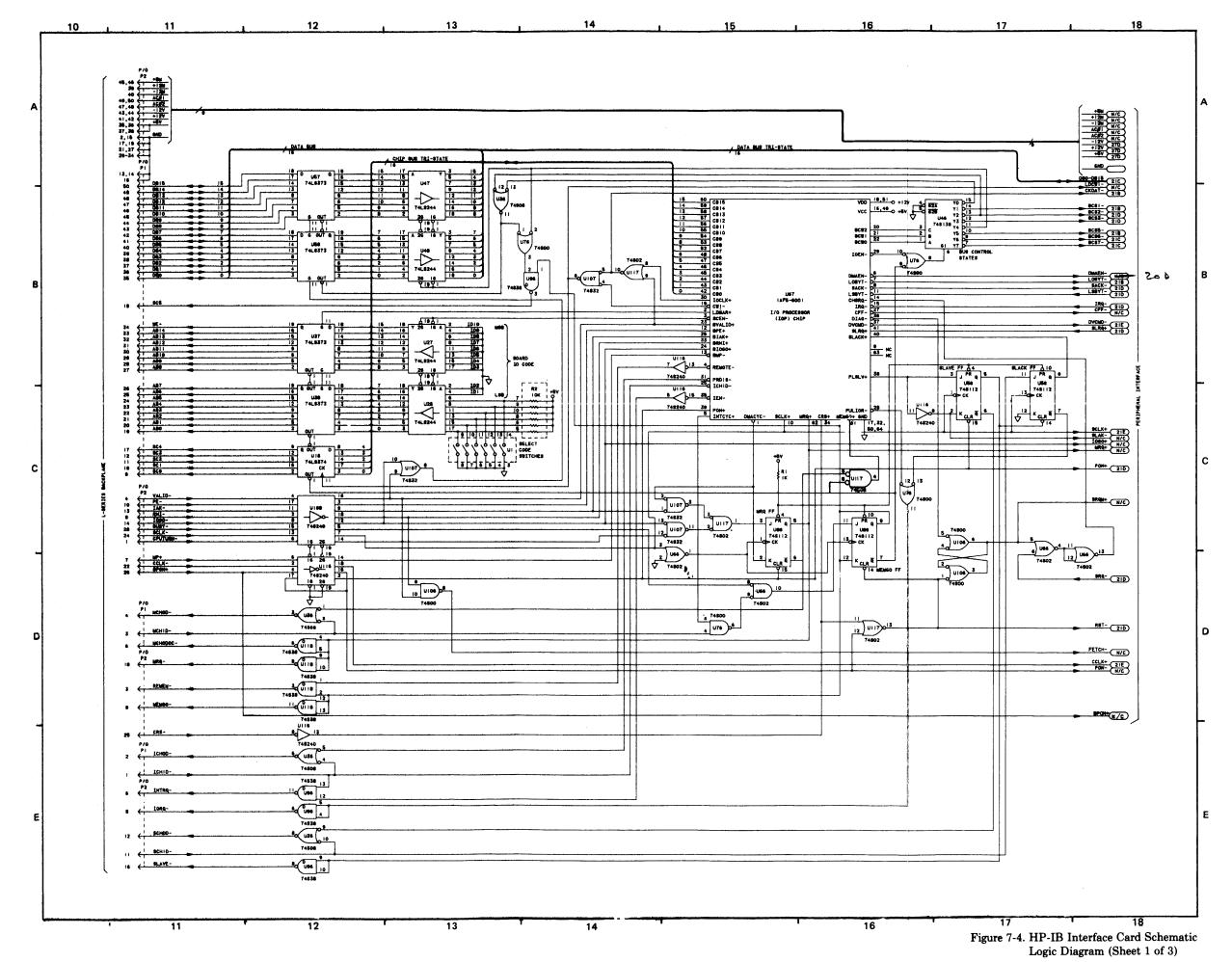

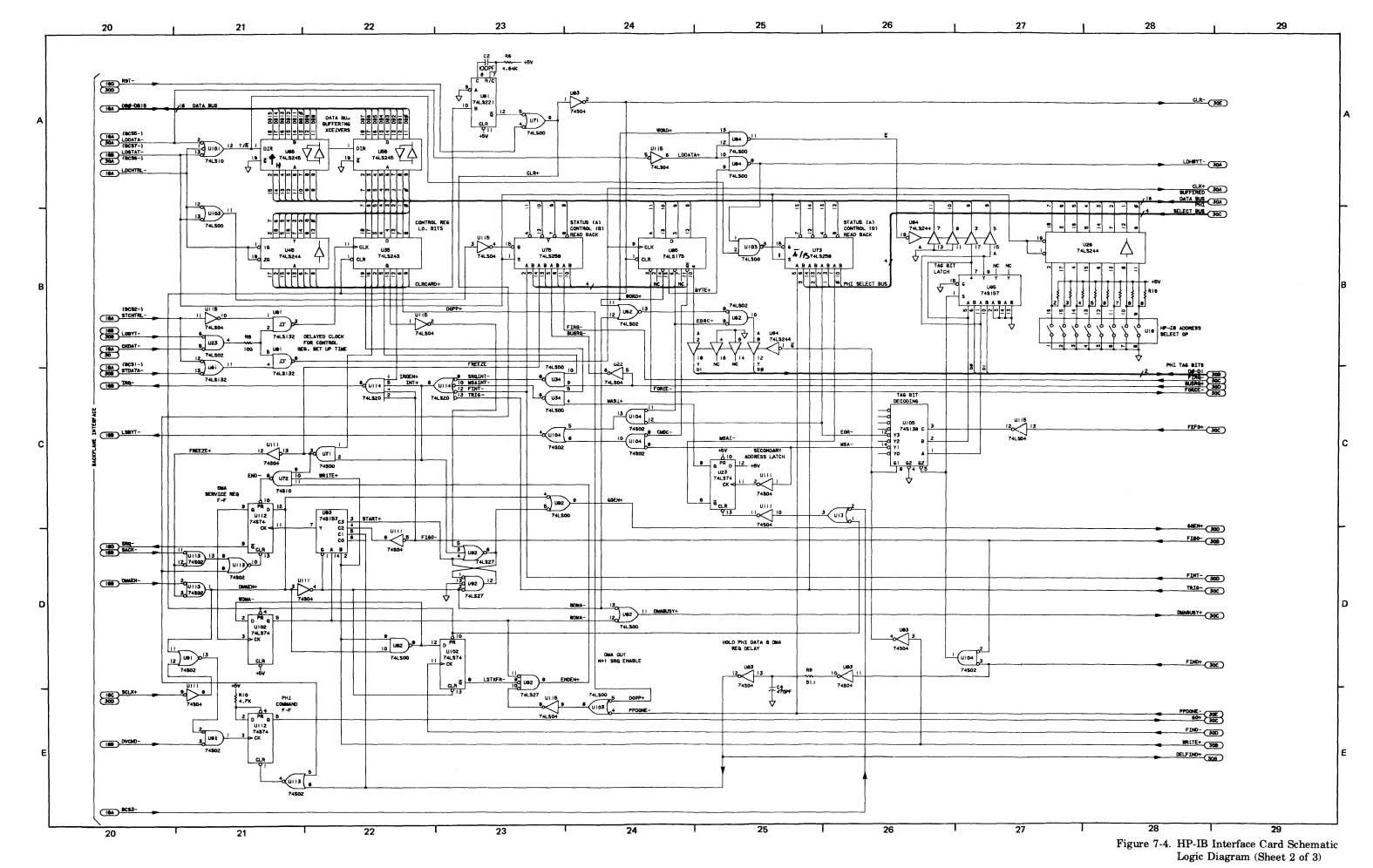

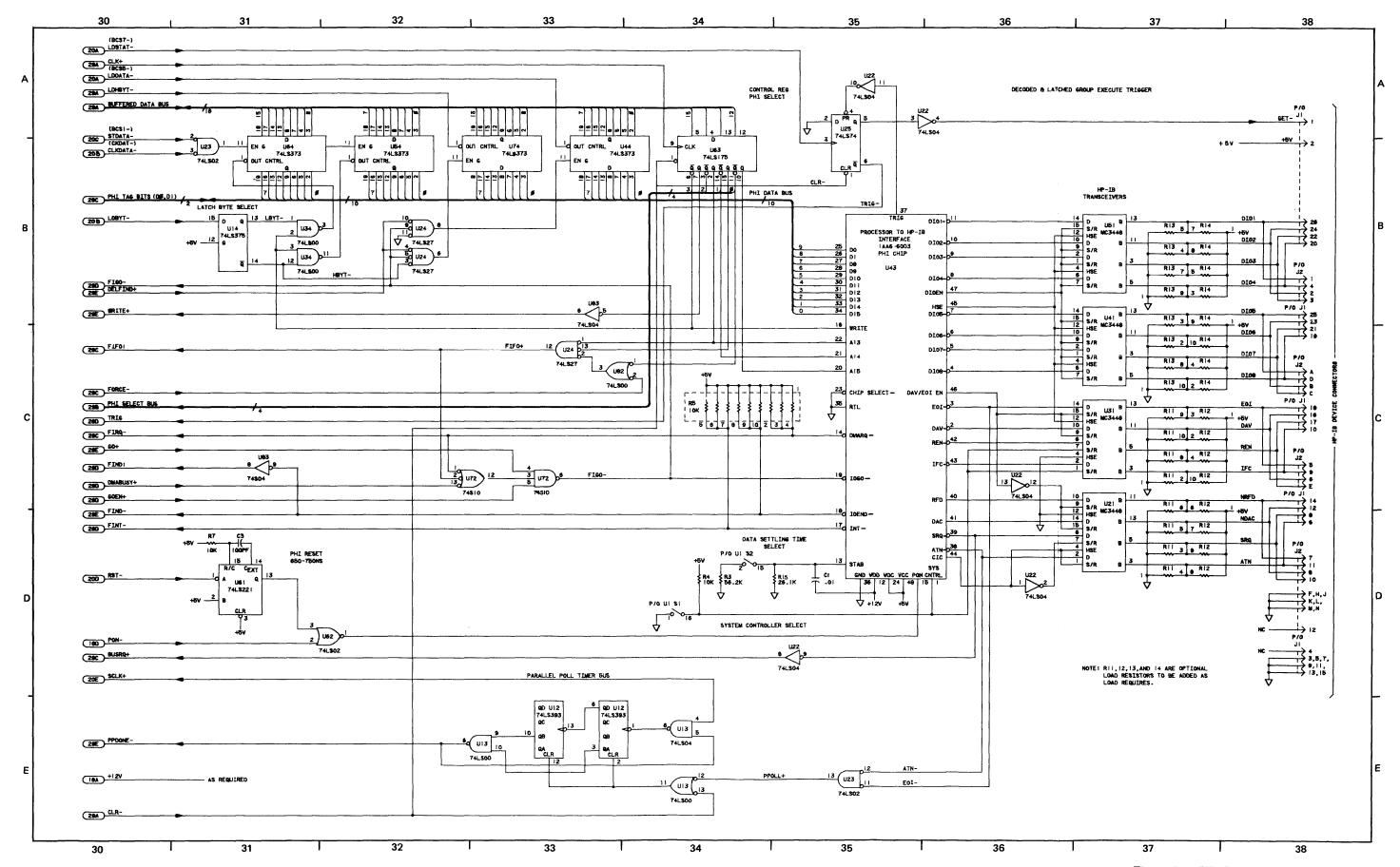

| IOP Chip (U67) Block Diagram                | 3-2 | HP-IB Interface Card Schematic           |        |

| PHI Chip (U43) Block Diagram                | 3-3 | Logic Diagram                            | 7-13   |

|                                             |     |                                          |        |

## **TABLES**

| Title Page                                | Title Page                                     |

|-------------------------------------------|------------------------------------------------|

| Specifications                            | IOP Chip Instructions by Select Code3-4        |

| Relation of ATN and Transfer (Handshake)  | Non-DMA Transfer Example                       |

| Lines (NRFD, NDAC, and DAV)               | DMA Transfer Example                           |

| Summary of Bus Timing                     | PHI Chip Register Selection Code and Names 4-5 |

| Backplane Connections, Connector P1 2-2   | Exchange Board Part Numbers 6-1                |

| Backplane Connections, Connector P22-2    | Reference Designations and Abbreviations 6-2   |

| HP-IB Interface to Bus Connector (J2) 2-5 | Replaceable Parts 6-3                          |

| Accessory HP-IB Bus Cables                | Manufacturer's Code List                       |

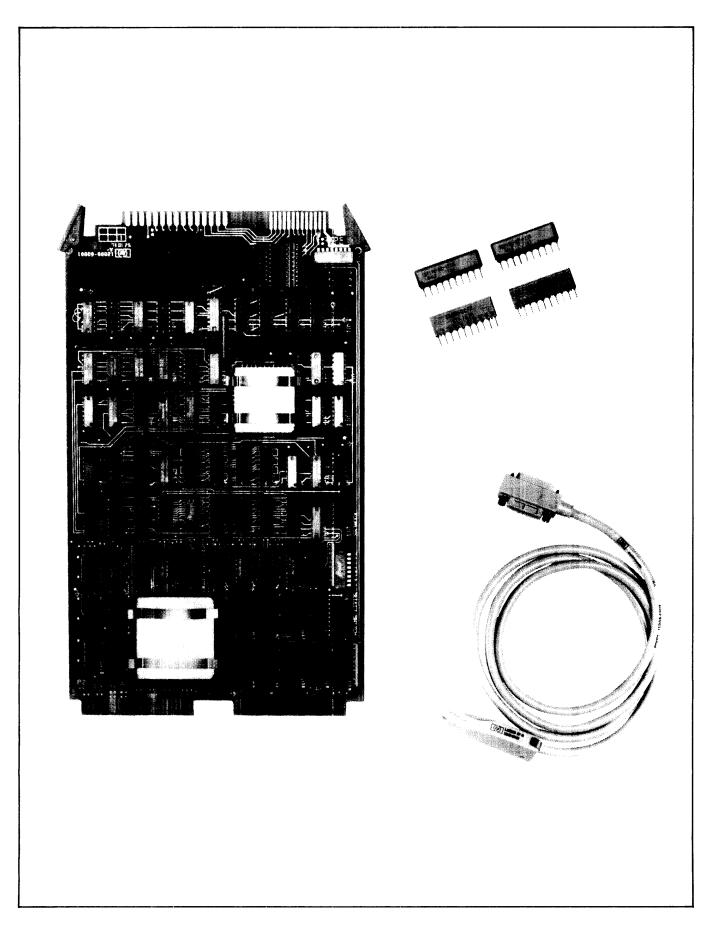

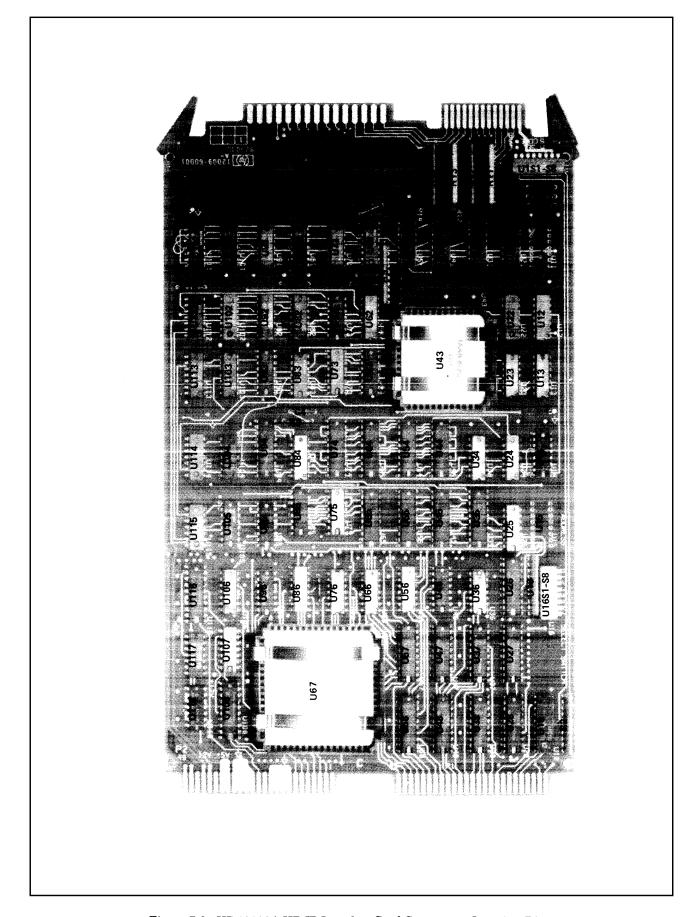

Figure 1-1. HP 12009A HP-IB Interface

## INTRODUCTION

## 1-1. INTRODUCTION

This manual provides general information, installation instructions, programming instructions, theory of operation, maintenance instructions, replaceable parts information, and service diagrams for the HP 12009A HP-IB Interface.

This section contains general information concerning the HP 12009A HP-IB Interface, including a description and specifications.

## 1-2. DESCRIPTION

The Hewlett-Packard Interface Bus (HP-IB) is Hewlett-Packard's implementation of the IEEE Standard 488-1978.

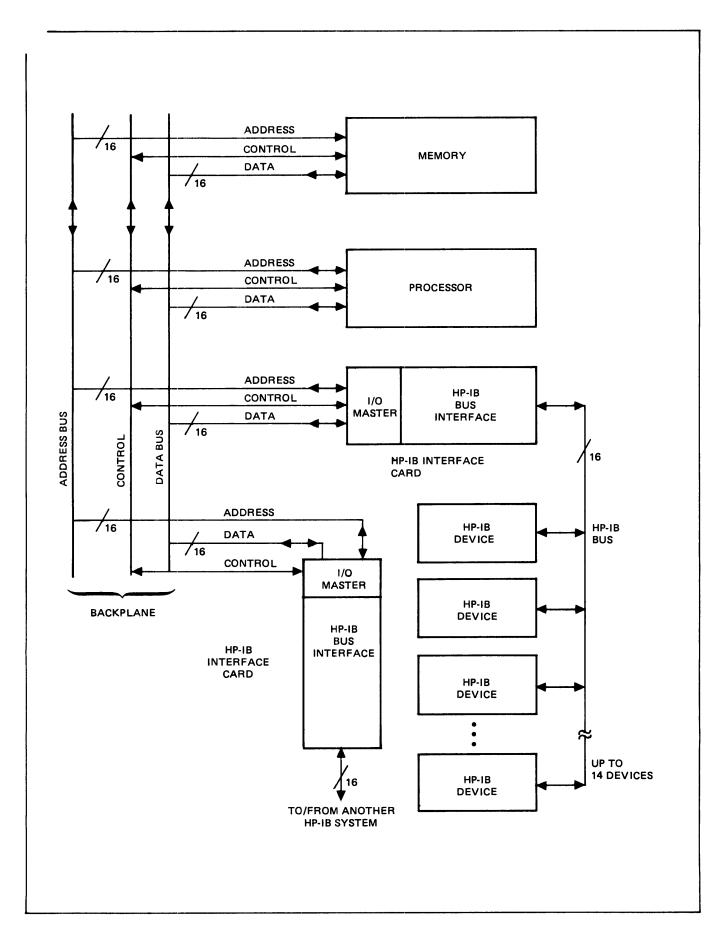

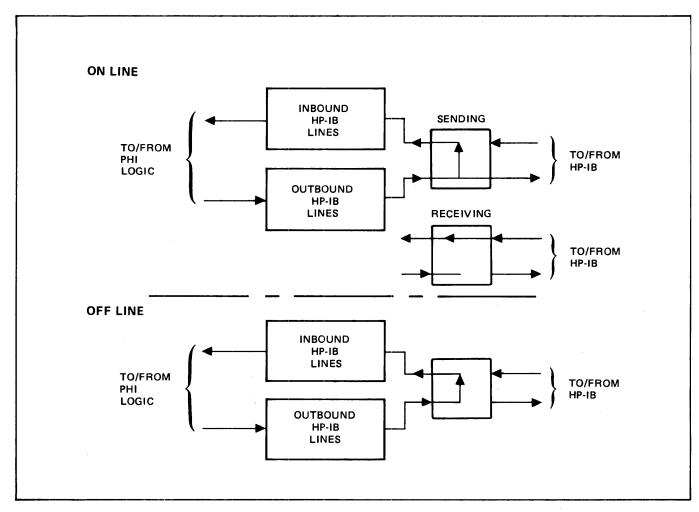

The HP 12009A (see Figure 1-1) provides an interface between the HP 1000 L-Series computers and systems and an HP-IB system of up to 14 devices. Several such HP-IB systems can be interfaced to the L-Series computer, each system requires a separate interface card. The HP-IB card

plugs into a single slot in the L-Series Backplane (see Figure 1-2) and is assigned only one select code. The HP-IB card is connected by cable to the HP-IB device or system. To the L-Series computer, this card is an I/O card and is under its software control at all times. To the HP-IB system, this card may or may not be a system controller depending on the setting of a switch selectable option.

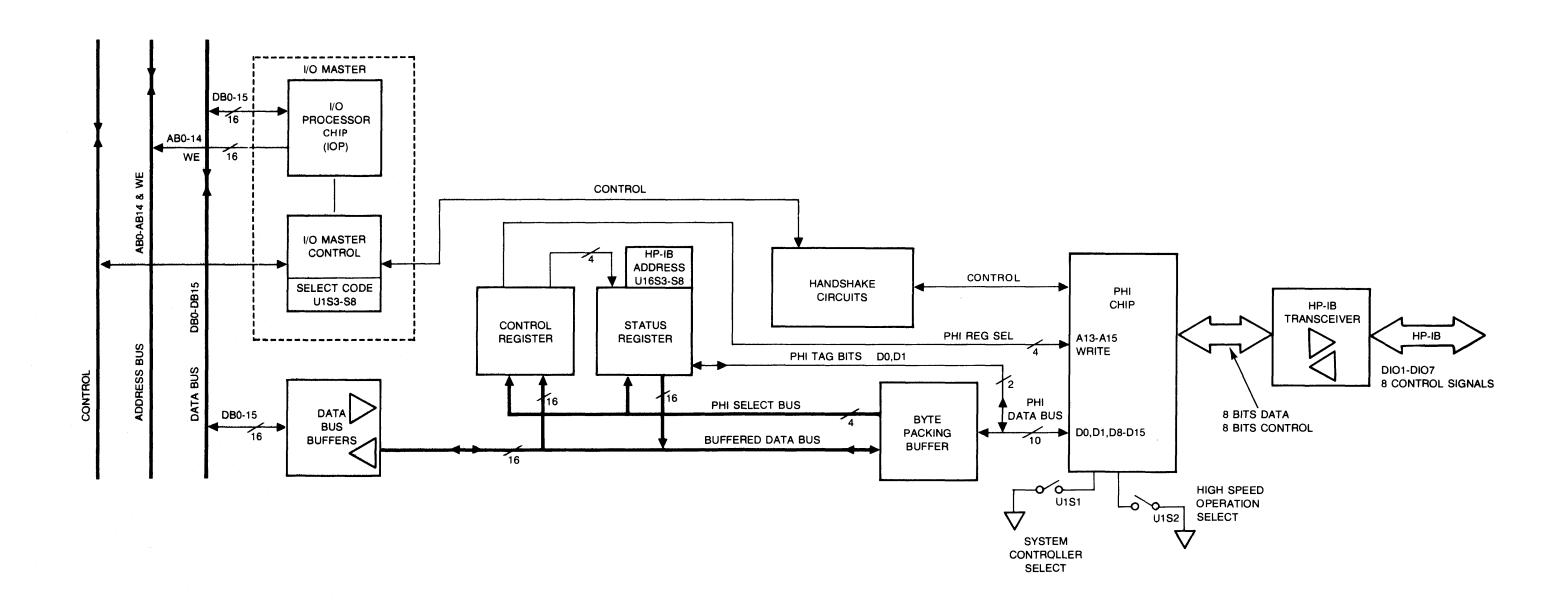

The HP-IB card has the capability of handling its own Direct Memory Access (DMA) and of decoding its own instructions from the CPU. These features are performed by the I/O Master located on the HP-IB card. Figure 1-3 shows the HP-IB card in a typical L-Series system environment.

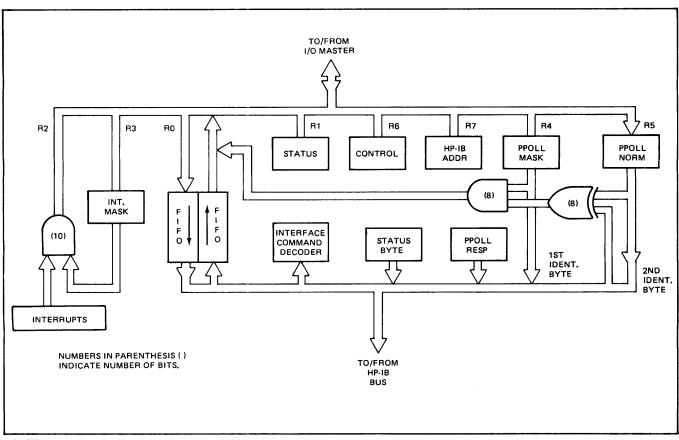

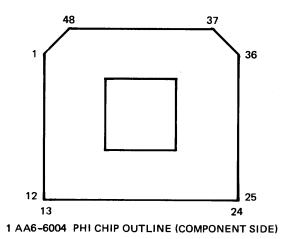

The interfaces to the L-Series backplane and to the HP-IB devices are provided by two LSI SOS integrated circuit chips. The first integrated circuit chip, the I/O processor (IOP) chip, manages all I/O functions of the L-Series computers. The second chip, the PHI (Processor to HP-IB Interface) chip performs all data and control signal interactions with the HP-IB devices. Through the use of these two chips, the HP 12009A HP-IB Interface relieves the CPU of most of the HP-IB protocol processing.

7700-480

Figure 1-2. Typical L-Series Card Cage Layout

Figure 1-3. HP-IB Interface in a Typical L-Series System Environment

The HP-IB Interface can support either high speed (IEEE Std 488-1978 paragraph 5.2.3) or standard speed devices. The selection of either high or standard speed operation is determined by the setting of switch U1S2. The speed of operation depends on the type of device connected to the card.

## 1-3. EQUIPMENT SUPPLIED

The HP 12009A HP-IB Interface consists of the following items (see Figure 1-1):

- a. HP-IB Interface Card, part no. 12009-60001.

- b. Interconnecting cable, part no. 12009-60007.

- HP-IB Interface Reference Manual, part no. 12009-90001 (not shown).

- d. High Speed Operation Card (not shown).

- e. Load Resistor Packs (R11, R12, R13, and R14).

### 1-3.1. OPTIONS AVAILABLE

Option D01: Substitutes interconnecting cable, part number 12009-60007, with a 1.25 meter cable, part number 12009-60009. This option is used in A-Series system configurations only.

## 1-4. IDENTIFICATION

Five digits and a letter (12009A in this case) are used to identify Hewlett-Packard products used with HP computers. The five digits identify the product and the letter indicates the revision level of the product.

The interface card is further identified by a part number marked on the card. In addition, a letter and a date code consisting of four digits (e.g., A-1926) are placed below the part number. The letter identifies the version of the etched circuit on the card. The date code (four digits following the letter) identifies the electrical characteristics of the assembled card. Thus, the complete part number on the HP-IB Interface Card could be as follows:

12009-60001 A-1926A

If the date code stamped on the HP-IB Interface Card is not listed with the date code on the title page of this manual, then there are differences between that card and the card described in this manual. The differences are described in manual supplements available at the nearest HP Sales and Service Office (listed in the back of this manual).

### 1-5. REFERENCE MANUAL

The manual supplied with the interface card is identified by its title and part number. The part number, 12009-90001, is printed on the title page. The publication date also is printed on the title page. If the manual is revised, the publications date is changed. The Print History and List of Effective Pages will reflect the revision date.

### 1-6. SPECIFICATIONS

Table 1-1 lists the specifications of the HP 12009A HP-IB Interface

Table 1-1. Specifications

## **ELECTRICAL CHARACTERISTICS** HP-IB Bus Signal Lines: The Bus consists of the following 16 lines: **DIO1** Data Input/Output 1 DIO8 Data Input/Output 8 DAV Data Valid **NRFD** Not Ready for Data **NDAC** Not Data Accepted Interface Clear **IFC** Attention ATN SRQ Service Request REN Remote Enable EOI End or Identify Logic Levels: High > 2.4V Low < 0.4VAll signals are Low = True except NRFD and NDAC.

### **ELECTRICAL CHARACTERISTICS (Continued)**

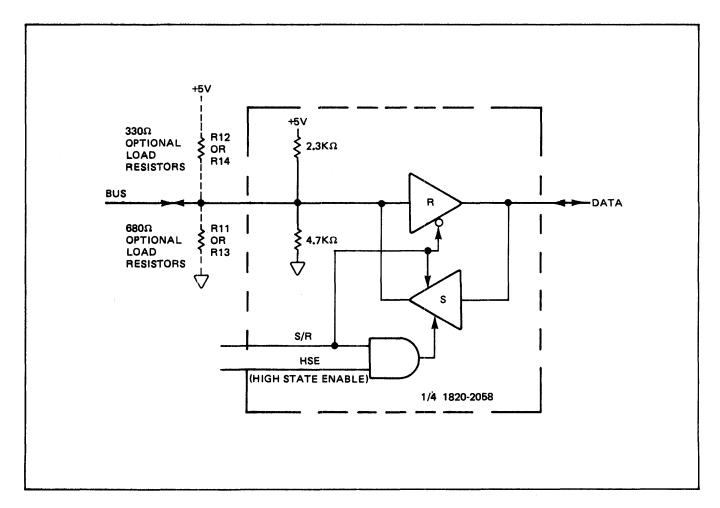

Line Termination: Each of the 16 Bus signal lines is terminated with 2.3k ohm to Vcc and 4.7k ohm to logic common without the optional load resistors.

Line Drivers: Each of the 16 Bus signal lines are driven with a circuit having the following typical characteristics:

Type: Tri-state, Open Collector

Output Voltage Low State: < 0.4V @ 48 mA Output Voltage High State: 2.5V @ -5.2 mA

Line Receivers: Each of the 16 Bus signal lines is received with a circuit having the following typical characteristics:

Type: Schmitt Trigger

Threshold Positive Transition: 1.75V

Threshold Negative Transition: 1.1V

Input Current Low State: -1.3 mA @ 0.4V

Input Current High State: 0.7 mA @ <5.5V

## **DMA Transfer Rates:**

Standard Speed: 500 KBytes

<sup>1</sup>High Speed:

Random Instruction Mix: 930 KBytes

•Worst Case Instruction Mix: 734 KBytes

◆Worst Case: A JMP\* (a Jump Instruction who's target address is it's own address).

### Maximum Cable Length:

Standard Operation: 2 metres per device connected with a 20m maximum length and a settling time of greater

than 500 ns.

<sup>2</sup>High Speed Operation: 2 metres per device connected with a 15m maximum length and a settling time of less

than 350 ns.

Operating Temperature: 0 to +55 Degrees Celsius.

**Power Requirements:** This card requires the following amounts of power from the computer's power supply at 25 degrees Celsius:

| CURRENT |                    |                  | POWER DISSIPATED   |                  |  |

|---------|--------------------|------------------|--------------------|------------------|--|

| Voltage | W/O Load Resistors | W/Load Resistors | W/O Load Resistors | W/Load Resistors |  |

| + 5V    | 2.02 A             | 2.10 A           | 10.61 watts        | 11.03 watts      |  |

| +12V    | 32 mA              | 84 mA            | 0.40 watts         | 1.06 watts       |  |

|         |                    | Total Power      | 11.01 watts        | 12.09 watts      |  |

### PHYSICAL CHARACTERISTICS

### **Card Dimensions:**

Width: 17.15cm (6.750 in.) Length: 28.91cm (11.380 in.)

Connector: 30-pin printed circuit board edge connector (cable supplied has standard Bus connector on outboard end).

<sup>&</sup>lt;sup>1</sup>HP-IB Interface must be in the highest priority I/O slot in Backplane.

<sup>&</sup>lt;sup>2</sup>Refer to Section II, paragraph 2-18 for further information.

## 1-7. HEWLETT-PACKARD INTERFACE BUS (HP-IB) CAPABILITIES

HP-IB provides the capability of connecting from one to 14 compatible devices to the computer via one interface card. Data is transferred over the HP-IB bidirectionally in 8-bit bytes. Data can be transferred from a device to the computer and other devices simultaneously or from the computer to one or more devices simultaneously or from one device to other devices under the direction of the computer.

Some HP-IB features must be used while other features are optional. For example, all devices must be capable of being addressed, but they may or may not be capable of being operated by remote control. A system may have some devices operating under remote control while other devices obey their front and rear panel controls (LOCAL). The same pins of all HP-IB connectors of all devices are connected in parallel making a parallel communication network. This permits information to flow in any direction on the bus and allows any device to talk directly with another device without going through a central control unit.

## 1-8. HP-IB SUPPORTED FUNCTIONS

The interface card is designed to support the following HP-IB Interface Functions as defined by the IEEE Standard 488, 1978. The HP-IB Interface is Hewlett-Packard's implementation of the IEEE Standard 488-1978. These functions are fully supported by the HP 12009A unless otherwise noted.

#### **Controller Functions**

- C1 System Controller

- C2 Send Interface Clear and Take Charge

- C3 Send Remote Enable

- C4 Respond to Service Request

- C5 Send Interface Messages, Receive Control, Pass Control, Pass Control to Self, Parallel Poll, Take Control Synchronously

#### **Controlled Device Functions**

| SR1 | Service Request                                 |

|-----|-------------------------------------------------|

| RL2 | Remote Local                                    |

| PP1 | Parallel Poll (see Section III, paragraph 3-49) |

| DC1 | Device Clear                                    |

DT1 Device Trigger

The following utility functions are proviced to support the above functions.

SH1 Source Handshake

AH1 Acceptor Handshake

- T5 Basic Talker, Serial Poll, Talk Only, Unaddress if My Listener Address

- TE5 Basic Extended Talker, Serial Poll, Talk Only, Unaddress if My Listener Address and My Secondary Address

- L3 Basic Listener, Listen Only Mode, Unaddress if My Talk Address

- LE3 Basic Extended Listener, Listener Only Mode, Unaddress if My Secondary Address and Talker Primary Addressed State

## 1-9. ADDRESSING-TALKING-LISTENING-HANDSHAKING

A technique of addressing is used to determine which device is to "talk" and those devices that are to "listen". Data is sent from one device to another device in a bit parallel byte serial format using an interlocked "Handshake" technique. This technique assures that the sender does not remove data before the receiver has finished using the data. It also ensures that data is not lost when devices having inherently different speeds communicate on the same bus.

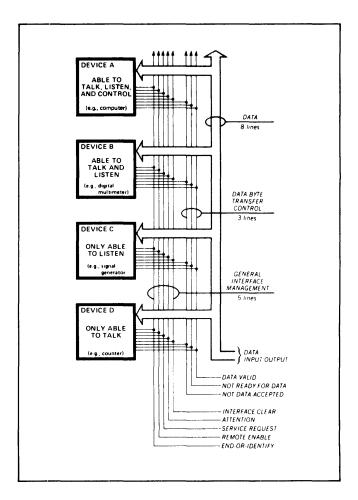

## 1-10. FUNCTIONS OF DEVICES ON THE HP-IB

Devices connected to the bus must be addressed by the Controller before they can function in one or more of the following ways:

**TALKER** — Any device that is capable of sending or transmitting information on the bus. There can be only one talker at a time on the bus.

LISTENER — Any device that is capable of receiving or accepting information on the bus is a listener. There may be up to 14 listeners at the same time on the bus.

TALKER-LISTENER — An device that has the capability of both sending and receiving information on the bus as defined previously is both a talker and listener. For example, a counter is a talker when sending data and a listener when it is being programmed.

CONTROLLER — Any device that has been programmed to have the responsibility of managing the flow of information between devices connected to the bus is a controller. It is capable of addressing one of the devices as a talker and one or more of the others as listeners. The HP-IB permits a system to have more than one controller, but only one controller may be active at a time. (The Controller-in-Charge may be the System Controller.)

SYSTEM-CONTROLLER — The system designer must designate one device as the System Controller at the time

the system is configured. The device performs all the functions of a Controller plus it has the ability to gain absolute control of the HP-IB for programming device modes (asserting IFC and REN), collecting and processing data, etc.

## 1-11. HP-IB BUS LINES

The HP-IB structure consisting of 16 signal lines is shown in Figure 1-4. There are eight additional bus conductors: one ground, one cable shield, and six twisted pair commons for six of the signal lines.

All 16 signal lines have been given names and mnemonic acronyms that describe the message being carried on that line. There are three types of lines: Data (8), Transfer (handshake) (3), and Control (management) (5).

## 1-12. CONTROL LINES

#### NOTE

All devices connected to the bus, including the controller, must conform to these descriptions.

The five control lines are used to manage the flow of information over the data and transfer lines. They communicate control and status information between the active controller and the devices connected to the bus. All devices must use ATN and IFC. A device may or may not use REN, SRQ, and EOI.

ATN (Attention) is driven by the active controller to place the bus in either the COMMAND (low) or DATA (high) mode. All other devices must monitor ATN at all times.

When the controller sets ATN to its low state, the bus is in the Command Mode. The primary purpose of the Command Mode is to permit the controller to send commands or address those devices that are to communicate when the bus is placed in the Data Mode. Also, the controller may send "universal commands" while the bus is in the Command Mode.

When the controller sets ATN to its high state, the bus is in the Data Mode. The device that was addressed to talk and those that were addressed to listen will now communicate on the Data Lines.

ATN may be set low or high at any time by a controller, however, it is usually at the end of a transfer (handshake) cycle so that data is not lost. Timing of the transfer lines with respect to ATN is given in paragraph 1-14.

IFC (Interface Clear) is used by the system controller to initialize the bus. Only the system controller can drive IFC and it must be monitored by all other devices on the bus. When the system controller sets IFC low for at least 100 us the following takes place: all talkers and listeners are stopped, serial poll mode is disabled, and control is returned to the HP-IB controller. When IFC is high it has no effect on the bus operation. The system controller may set IFC low at any time.

REN (Remote Enable) is one of the conditions for operating devices under Remote Control. Only devices capable of remote operation use REN and monitor it at all times. Devices that do not use REN terminate the line in a resistive load. Only the system controller may assert REN and may change its state at any time.

SRQ (Service Request) is driven to its low state by a device to indicate that it wants the attention of the controller. SRQ may be set low by a device at any time except when IFC is in the low state. Only the controller senses SRQ. Some devices do not use SRQ but terminate it in a resistive load.

EOI (End or Identify) may be used to indicate the end of a devices character string. When the bus is in the Data Mode (ATN is high), the addressed talker may indicate the end of its data by setting EOI low at the same time it places the last byte on the Data Lines.

Figure 1-4. HP-IB Bus Structure

## 1-13. DATA LINES (DIO1-DIO8)

The Data Lines are used to communicate all data including input, output, program codes, addresses, and control and status information between devices connected to the bus. This data is passed character (byte) at a time (i.e., byte serial and bit parallel) under control of the Transfer Lines. Unused data lines terminate in a resistive load in the HP-IB Transceiver chips.

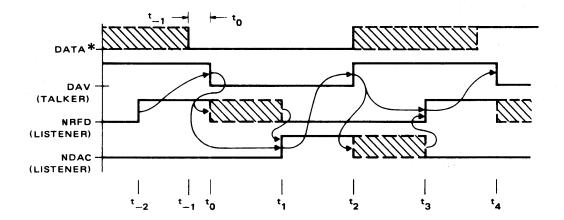

## 1-14. TRANSFER LINES

Three Transfer (handshake) Lines are used to execute the transfer of each byte of information on the data lines. All devices use these lines and employ an interlocked "handshake" technique to pass information. This allows asynchronous data transfer without timing restrictions being placed on any device connected to the bus. The transfer of each byte is accomplished at the speed of the slowest device. The three transfer lines are: NRFD, NDAC, and DAV.

NRFD (Not Ready for Data) is the transfer (handshake) line that indicates all listeners are ready to accept information on the data lines. NRFD is driven by all the listeners (all devices when ATN is low and only by those devices addressed to listen when ATN is high). It is sensed by talkers: the controller when ATN is low, and the device addressed to talk when ATN is high.

When NRFD is high, all listeners are unconditionally ready for data. The talker may, at its own time, put a byte of information on the data lines and set DAV low. When NRFD is low, one or more listeners are not ready for data.

When the controller sets ATN low, all devices must set NRFD to its high state within 200 ns, i.e., if a device is "Ready for Data" it places NRFD to its high state and if it is "Not Ready for Data" it sets NRFD to its low state. When the controller sets ATN high, all devices that have not been addressed to listen will not drive NRFD, those addressed to listen will set NRFD to its high state within 200 ns.

A listener must not set NRFD low until it senses DAV is low. It may do so before or at the same time that it sets NDAC high. It must not return NRFD to its high state until it senses DAV is high and may do so after, or at the same time that it sets NDAC low.

NDAC (Not Data Accepted) is the transfer line that indicates the acceptance of information on the data lines. NDAC is driven by all listeners. That is, all devices when ATN is low and only those devices addressed to listen when ATN is high. It is sensed by the talker and the controller when ATN is low and by the device addressed to talk when ATN is high.

When NDAC is high, all listeners have unconditionally accepted the byte of information that is on the data lines

and no longer need it. The talker may, at its own time set DAV high, remove that byte of information and continue. When NDAC is low, one or more listeners have not accepted the information on the data lines.

When the controller sets ATN low, each device must set NDAC to its high state within 200 ns. When the controller sets ATN high, the devices that have not been addressed to listen will not drive NDAC, those addressed to listen will set NDAC to its high state within 200 ns.

A listener must not set NDAC low until it senses DAV is high. It may do so before or at the same time that it sets NRFD high. It must not return NDAC high until it senses DAV is low and it may do so after or at the same time that it sets NRFD low.

DAV (Data Valid) is the transfer line that indicates the validity of information on the data lines. DAV is driven by the talkers: the controller when ATN is low and the device addressed to talk when ATN is high. ATN is sensed by the listeners and by all devices if ATN is low and by those devices addressed to listen when ATN is high.

When DAV is low, the states of data lines DIO1 through DIO8 are unconditionally valid and may be accepted by all listeners at their own time. DAV can only be driven low if NRFD and IFC are high. When DAV is high, the information on the data lines is not valid. DAV cannot be set high unless NDAC is high and NRFD is low.

The talker has the responsibility of allowing enough time for cable rise time and ringing. It does this with DAV. After placing the bus in the Address Mode (setting ATN low), the controller must wait at least one microsecond before setting DAV low. Of course it must not do so unless NRFD is high. In either the Address or Data Mode, a talker designed with open-collector circuits must not set DAV low for at least two microseconds after placing valid data at its output connector. Those designed with tri-state logic must wait at least 500 ns.

The previous conditions are summarized in Tables 1-2 and 1-3.

## 1-15. DATA TRANSFER

The transfer of data on the bus is asynchronous and therefore, places no restrictions on the data rates of devices connected to the bus. The timing and levels required to transfer a byte of data on the data lines are shown in Figure 1-5. The transfer is under the control of three lines DAV, NRFD, and NDAC. The talker (sender of data) drives the Data Lines and DAV (Data Valid) and the listeners (acceptors of data) drive both NRFD (Not Ready for Data) and NDAC (Not Data Accepted).

The transfer of a byte of data is initiated by all listeners signifying they are ready for data by setting NRFD high.

Table 1-2. Relation of ATN and Transfer (Handshake) Lines (NRFC, NDAC, and DAV)

| MODE             | ATN         | NRFD                                                                     |                                                                                                                                                                                                                                        | NI                                                          | NDAC                                           |                                                             | DAV                                                |  |

|------------------|-------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|--|

| MODE             | AIN         | LOW                                                                      | нідн                                                                                                                                                                                                                                   | LOW                                                         | HIGH                                           | LOW                                                         | нідн                                               |  |

| C<br>O<br>M<br>M | L<br>O<br>W | One or<br>more units<br>not ready<br>for data                            | All units<br>ready for<br>data                                                                                                                                                                                                         | One or<br>more units<br>have not<br>accepted<br>data        | All units<br>have<br>accepted<br>data          | Controller<br>has valid<br>data on<br>DIO lines             | Controllers<br>data is<br>not valid                |  |

| A<br>N<br>D      | VV          | <ol> <li>Sensed by</li> <li>All units se</li> </ol>                      | all units except of controller et NRFD and ND, econds after ATN                                                                                                                                                                        | AC to valid state                                           | e within                                       | 1. Driven by<br>2. Sensed b<br>3. See DAV<br>timing         | y listeners                                        |  |

| D<br>A           | H (         | One or<br>more<br>listeriers<br>not ready<br>for data                    | All<br>addressed<br>listeners<br>ready for<br>data                                                                                                                                                                                     | One or<br>more<br>listeners<br>have not<br>accepted<br>data | All addressed listeners have accepted the data | The<br>addressed<br>talker<br>has valid<br>data on<br>lines | The<br>addressed<br>talker<br>data is<br>not valid |  |

| T<br>A           | ØІ          | <ol> <li>Sensed by</li> <li>All units no</li> <li>All address</li> </ol> | Driven by all units addressed to listen.     Sensed by the unit addressed to talk.     All units not addressed will not drive.     All addressed listeners set both NRFD and NDAC to valid within 200 nanoseconds after ATN goes HIGH. |                                                             |                                                | 2. Sensed by                                                | to TALK. all devices to LISTEN                     |  |

Table 1-3. Summary of Bus Timing

| IFC INTERFACE CLEAR                        | The System Controller must set IFC low for at least 100 microseconds to clear the bus.                                                                                                                                                                                                                                                                                               |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSFER LINES WITH<br>RESPECT TO ATN      | When sending an Address or a Universal Command the controller may set DAV low only after sensing that NRFD is high, and ATN has been low for at least one microsecond.                                                                                                                                                                                                               |

|                                            | When a controller changes ATN from its high to the low state or from low to high, all Listeners (all devices when ATN is low and those addressed to Listen when ATN is high) put both NRFD and NDAC to their high state in less than 200 nanoseconds.                                                                                                                                |

| TRANSFER LINES WITH<br>RESPECT TO THE DATA | After changing the information on one or more Data Lines, the <i>talker</i> (the Controller when ATN is low or the device addressed to talk when ATN is high) must wait before setting DAV low. It waits 2 $\mu$ s if designed with open-collector circuits and 500ns if designed with tristate integrated circuits at standard speed. It must wait 350ns if operated at high speed. |

When the talker recognizes NRFD is high and has placed valid data on the data lines, then it sets DAV low. When the listeners sense that DAV is low and have finished using the data, they set NDAC high. Notice that the assertive or active state of both NRFD and NDAC is high. Since all devices on the bus have their corresponding lines connected together (e.g. NRFD), all listeners must be in a high state before that line goes high. This wired-AND condition allows a talker to recognize when the slowest listener has accepted a byte of data and is ready for the next byte.

Figure 1-5 also shows the timing of the transition to the non-assertive state of these lines. A listener may set NRFD low as soon as it recognizes that DAV has been set low and must do so before or at the same time it sets NDAC high. The talker may return DAV to its high state after it detects that NDAC is high. A listener may set NDAC low as soon as it recognizes that DAV is high and must do so before or at the same time it sets NRFD to its high state.

## 1-16. HP-IB ELECTRICAL CHARACTERISTICS

All 16 bus lines are designed to be compatible with TTL integrated circuits. Each line is terminated within the

## SEQUENTIAL REQUIREMENTS OF THE THREE WIRE TRANSFER

## **EVENTS**

$t_{-2}$  : Listener becomes ready to accept data.

$t_{-1}$  : Talker has put data on the lines.

$t_0$ : Indicates data is valid.

t<sub>1</sub> : Listener has accepted the data and no longer requires it held valid.

t<sub>2</sub>: Talker indicates the data is no longer valid and may change it.

t<sub>3</sub>: Listener indicates it is ready for new data.

$t_4$ : A new cycle begins (equivalent to  $t_0$ ).

$\mathbf{t}_{-1} \ \text{to} \ \mathbf{t}_{0} \quad : \quad \text{Time that data is put on lines before DAV is set low.}$

\* A composite of the DIO1 through DIO7 lines for illustrative purposes. The curved lines indicate transfer (handshake) signal sequence.

Transceiver chips into a resistive network consisting of a 2.3 kohm resistor to +5V and a 4.7 kohm resistor to logic common. Typically, the required bus terminations are internally provided by the Transceiver chips. Optional load resistors (R11, R12, R13, and R14) form an external divider consisting of a 330 ohm resistors to +5V and 680 ohm resistors to logic common that can be used to provide the drive for seven additional loads. Load resistors of other values may be required if the optional load resistors do not supply sufficient drive for specific applications. The selection of these resistors is covered in Section II.

Each driver/receiver pair (see Figure 1-6) forms a complete interface between the bus and a device. Either the driver or the receiver of each channel is enabled by its corresponding Send/Receive (S/R) input with the disabled output of the pair forced to a high impedance state. An additional option allows the driver to be operated in an open collector or active pull-up configuration. The receivers have input hysteresis to improve the noise margin and their input loading follows the bus standard.

The driver/receiver pairs provide the following:

Driver: When a talker, it is capable of sinking 48 mA

at 0.4V.

Receiver: When a listener, it requires -1.3 mA at 0.4V

to drive.

## 1-17. HP-IB PHYSICAL CHARACTERISTICS

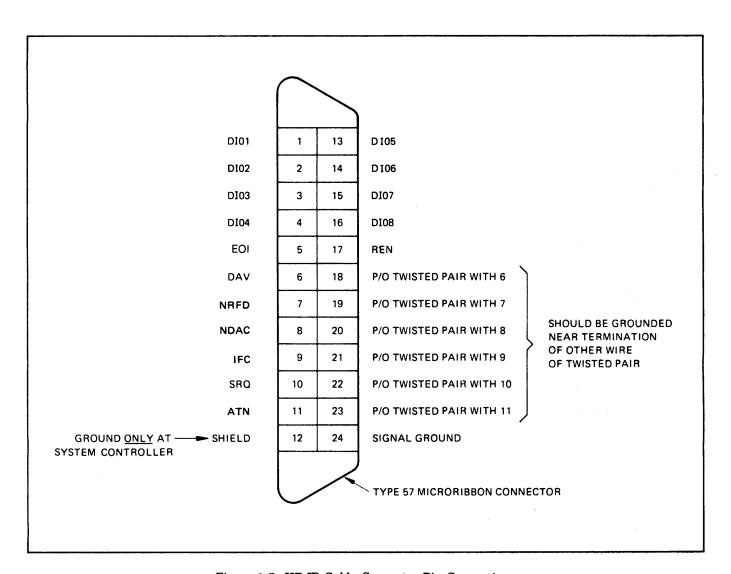

Bus cables are available for connecting devices into a system. These have one overall shield to reduce susceptibility to external noise. The cables use a mixture of individual wires and twisted pairs to reduce crosstalk. The connectors on both ends of the cables are identical as they are terminated in two 24-pin piggy back connectors; one male and one female. The pin connections of these connectors are shown in Figure 1-7.

Figure 1-6. Typical HP-IB Transceiver (Driver/Receiver) Circuit

Figure 1-7. HP-IB Cable Connector Pin Connections

SECTION

## 2-1. INTRODUCTION

This section provides information on unpacking, inspecting, installing, and checking the operation of the HP 12009A HP-IB Interface.

## 2-2. UNPACKING AND INSPECTION

## **CAUTION**

#### STATIC SENSITIVE DEVICES

Use Antistatic handling procedures when handling the printed circuit assemblies.

If the HP-IB Interface is ordered with a computer, the card is installed in the computer at the factory. When this is the case, it is necessary only to check the operation of the peripheral device and the HP-IB Interface, after the peripheral device and the computer are installed. Checkout instructions are furnished in paragraph 2-13. If the HP-IB Interface is ordered separately, inspect the carton containing the card before opening it. If there is evidence of damage, if water stains are visible, or if the box rattles, request that the carrier's agent be present when the box is opened.

Inspect each portion of the package as the parts are unpacked. Look for such damage as cracks, dents, broken components, detached parts, corrosion, water damage, etc. If any part of the package is damaged, retain the carton, packing material, and shipping papers, and immediately notify the carrier and the nearest HP Sales and Service Office. The Sales and Service Office will arrange for repairs or replacement of the damaged parts without waiting for settlement of claims against the carrier. The HP Sales and Service Offices are listed in the back of this manual.

After inspecting all parts and components, refer to paragraph 1-3 to insure that the package is complete. Also, check the part numbers listed on the title page against the part numbers on the components in the package. If the package is incomplete, or if an incorrect component has been supplied, notify the nearest HP Sales and Service Office.

## 2-3. PREPARATION FOR INSTALLATION

## 2-4. COMPUTATION OF POWER REQUIREMENTS

The HP-IB Interface obtains its operating power from the computer's power supply through the backplane. Before installing the card, it is necessary to determine whether the additional current drain will overload the power supply. If the card was installed at the factory, the required calculations have been made and it has been determined that an overload will not occur. The current and voltage requirements for the HP-IB Interface are listed in Table 1-1.

## 2-5. INTERFACE REQUIREMENTS

### 2-6. BACKPLANE TO HP-IB INTERFACE

All interaction between the HP-IB Interface, the Processor Card, and the Memory Card occurs on the backplane. Connections from the backplane to the HP-IB Interface are listed in Tables 2-1 and 2-2.

## 2-7. SWITCH SELECTABLE OPTIONS

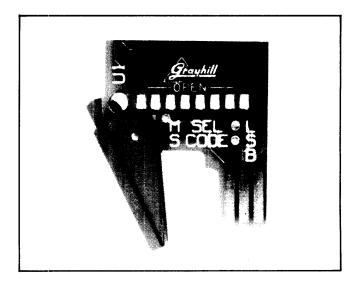

The switch selectable options are as follows: the Select Code (6-bits), the HP-IB Address (8-bits), HP-IB System Controller (1-bit), and the Settling Time Selection (1-bit). The locations of the two DIP switches (U1 and U16) are shown in Figure 2-1. Each DIP switch assembly contains eight independent switches. U16 is labelled from 0 to 7 for the Address Select Bits (see Figure 2-2). The last six switches on U1 (U1S3-S8) determine the Select Code for the card (see Figure 2-3).

### 2-8. HP-IB ADDRESS SELECTION

Switches U16S1 through U16S8 (see Figure 2-2) determine the HP-IB address and related control functions when loaded into the PHI Chip's Register 7 under software control. The switch functions are as follows:

Switch U16S1 (Bit 7)— Puts the PHI Chip "online" when set to the open (up) position.

Table 2-1. Backplane Connections, Connector P1

Table 2-2. Backplane Connections, Connector P2

| P1-      | SIGNAL<br>NAME   | SIGNAL DEFINITION                       |

|----------|------------------|-----------------------------------------|

| 1        | ICHID-           | Interrupt Chain In Disable              |

| 2        | ICHOD-           | Interrupt Chain Out Disable             |

| 3        | MCHID-           | Memory Chain In Disable                 |

| 4<br>5   | MCHOD-<br>MLOST- | Memory Chain Out Disable Memory Lost    |

| 6        | MCHODOC-         | Memory Chain Out Disable Open Collector |

| 7        | PFW-             | Power Fail Warning                      |

| 8        | SPARE 1          |                                         |

| 9        | SC0              | Address Extension Bus Bit 0             |

| 10       | SC1              | Address Extension Bus Bit 1             |

| 11<br>12 | SC2<br>SC3       | Address Extension Bus Bit 2             |

| 13       | GND              | Address Extension Bus Bit 3             |

| 14       | GND              |                                         |

| 15       | SPARE 2          |                                         |

| 16       | GND              |                                         |

| 17       | SC4              | Address Extension Bus Bit 4             |

| 18       | SC5              | Self Configure                          |

| 19       | AB0              | Address Bus Bit 0                       |

| 20<br>21 | AB1<br>AB2       | Address Bus Bit 1 Address Bus Bit 2     |

| 22       | AB3              | Address Bus Bit 3                       |

| 23       | AB4              | Address Bus Bit 4                       |

| 24       | AB5              | Address Bus Bit 5                       |

| 25       | AB6              | Address Bus Bit 6                       |

| 26       | AB7              | Address Bus Bit 7                       |

| 27<br>28 | AB8              | Address Bus Bit 8 Address Bus Bit 9     |

| 29       | AB9<br>AB10      | Address Bus Bit 10                      |

| 30       | AB11             | Address Bus Bit 11                      |

| 31       | AB12             | Address Bus Bit 12                      |

| 32       | AB13             | Address Bus Bit 13                      |

| 33       | AB14             | Address Bus Bit 14                      |

| 34       | WE-              | Write Enable                            |

| 35<br>36 | DB0<br>DB1       | Data Bus Bit 0 Data Bus Bit 1           |

| 37       | DB2              | Data Bus Bit 2                          |

| 38       | DB3              | Data Bus Bit 3                          |

| 39       | DB4              | Data Bus Bit 4                          |

| 40       | DB5              | Data Bus Bit 5                          |

| 41<br>42 | DB6<br>DB7       | Data Bus Bit 6                          |

| 43       | DB7              | Data Bus Bit 7 Data Bus Bit 8           |

| 44       | DB9              | Data Bus Bit 9                          |

| 45       | DB10             | Data Bus Bit 10                         |

| 46       | DB11             | Data Bus Bit 11                         |

| 47       | DB12             | Data Bus Bit 12                         |

| 48       | DB13             | Data Bus Bit 13                         |

| 49<br>50 | DB14<br>DB15     | Data Bus Bit 14 Data Bus Bit 15         |

| 50       | 55,5             | Data Dus Dit 10                         |

|          |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

| i        |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

|          |                  |                                         |

| P2-                 | SIGNAL<br>NAME  | SIGNAL DEFINITION                                       |

|---------------------|-----------------|---------------------------------------------------------|

| 1<br>2              | CPUTURN-<br>GND | Processor Turn                                          |

| 3                   | REMEM-          | Remote Memory                                           |

| 4                   | VALID-          | Data Valid                                              |

| 5                   | IORQ-           | I/O Handshake Request                                   |

| 6                   | INTRQ-          | Interrupt Request                                       |

| 7<br>8              | MP<br>RNI-      | Memory Protect Read Next Instruction                    |

| 9                   | MEMGO-          | Memory Cycle Initiation                                 |

| 10                  | PE-             | Parity Error                                            |

| 11                  | SCHID-          | Slave Chain In Disable                                  |

| 12                  | SCHOD-          | Slave Chain Out Disable                                 |

| 13<br>14            | IAK-<br>IOGO-   | Interrupt Acknowledge I/O Handshake Request Acknowledge |

| 15                  | GND             | O Hallushake Nequest Acknowledge                        |

| 16                  | SLAVE-          | Slave Request                                           |

| 17                  | GND             | M                                                       |

| 18<br>19            | MRQ-<br>GND     | Memory Request                                          |

| 20                  | FCLK-           | Fast Clock                                              |

| 21                  | GND             |                                                         |

| 22                  | CCLK-           | Communications Clock                                    |

|                     | PINT-           | Priority Interrupt                                      |

| 24<br>25            | SCLK-<br>CRS-   | System Clock<br>Control Reset                           |

| 26                  | PON             | Power On                                                |

| 27                  | GND             |                                                         |

| 28                  | BUSY-           | Memory Busy                                             |

| 29                  | GND             |                                                         |

| 30<br>31            | GND<br>GND      |                                                         |

| 32                  | GND             |                                                         |

| 33                  | GND             | -                                                       |

| 34                  | GND             |                                                         |

| 35                  | +5V             |                                                         |

| 36<br>37            | +5V<br>+5V      |                                                         |

| 38                  | +5V             |                                                         |

| 39                  | +12M            |                                                         |

| 40                  | 12M             |                                                         |

| 41                  | +12V            |                                                         |

| 42<br>43            | +12V<br>12V     |                                                         |

| 43                  | -12V<br>-12V    |                                                         |

| 45                  | +5M             |                                                         |

| 46                  | +5M             |                                                         |

| 47                  | ACØ2            |                                                         |

| 48<br>49            | AC#52<br>AC#51  |                                                         |

| <del>49</del><br>50 | ACØ1            |                                                         |

| 55                  |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 | İ                                                       |

|                     |                 |                                                         |

|                     |                 |                                                         |

|                     |                 |                                                         |

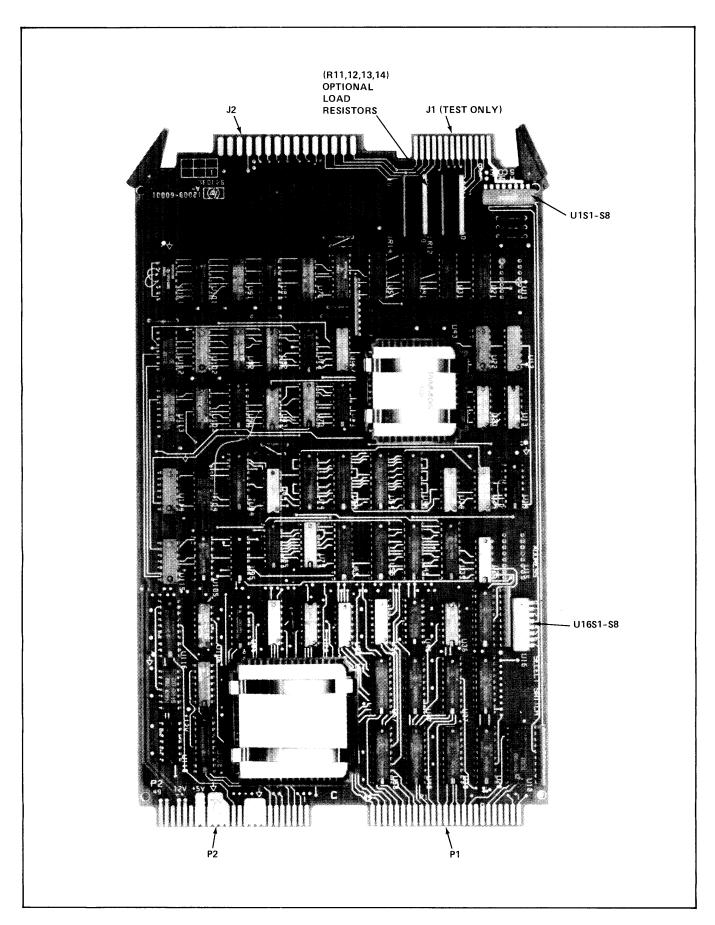

Figure 2-1. HP-IB Interface Card HP 12009-60001

Switch U16S2 (Bit 6)—Puts the PHI Chip into the "TALK ALWAYS" mode when the switch is in the open (up) position.

Switch U16S3 (Bit 5)— Puts the PHI Chip into the "LISTEN ALWAYS" mode when the switch is in the open (up) position.

Switches U16S4 through U16S8 (Bits 4 through 0)- The value of these five bits determine the HP-IB address to which the PHI Chip will respond.

## 2-9. SELECT CODE SELECTION

Switches U1S3 through U1S8 (see Figure 2-3) determine the select code for the HP-IB Interface. An open switch represents a logic 1 and a closed switch represents a logic 0. U1S3 represents the Most Significant Bit (MSB) and U1S8 represents the Least Significant Bit (LSB).

#### 2-10. SYSTEM CONTROLLER SELECTION

The switch U1S1 (see Figure 2-3) determines if the HP-IB Card will be the system controller for the bus. If the switch is put in the open (up) position, the card will function as the system controller.

### 2-11. DATA SETTLING TIME SELECTION

The switch U1S2 (see Figure 2-3) determines the time delay between the assertion of the data on the bus and the assertion of the data valid signal (DAV). With the switch in the normal open (up) position, a delay of approximately 500 ns is realized. When the switch is placed in the closed (down) position, the delay is reduced to approximately 350 ns. This delay time satisfies the IEEE Standard 488-1978 for fast settling time required for high speed operation (refer to paragraph 2-18 for further information on high speed operation).

## 2-12. INSTALLATION

## CAUTION

#### STATIC SENSITIVE DEVICES

Use antistatic handling procedures when handling the printed circuit assemblies.

Figure 2-2. U16S1-U16S8 HP-IB Address Selector Switches

After ensuring that the computer's power supply can handle the added load, (see paragraph 2-4), perform the following steps:

- Set switch U1S1 opened or closed depending on whether or not the HP-IB Interface is going to operate as a system controller (see paragraph 2-10).

- b. Set switch U1S2 opened or closed depending on whether or not the HP-IB Interface is going to require the normal or the fast settling time mode of operation (see paragraphs 2-11 and 2-18). All high speed devices should be appropriately labelled. High and standard speed devices cannot be connected to the same bus.

- c. Set the select code for the HP-IB Interface with switches U1S3 through U1S8 (see paragraph 2-9).

- d. Set the HP-IB Address for the HP-IB Interface with switches U16S4 through U16S8 (see paragraph 2-8).

- e. Turn off the power to the computer and the I/O device. Insert the HP-IB Interface into the desired slot in the backplane. Make sure that the components on the card are on the same side as the other interface cards in the backplane. When installing the card, use care not to damage the card or any adjacent cards. Press the card firmly into place.

- f. Connect the appropriate cable from the bus to the card. There are two connectors (J1 and J2) on the back edge of the card (see Figure 2-1). Connector J2 connects to the HP-IB cable. Connector J1 is only for test purposes.

## 2-13. CHECKOUT

To verify operation of the HP-IB Interface, refer to Section V, paragraph 5-6, steps 1, 2, and 3.

Figure 2-3. U1S3-U1S8 Card Select Code Switches

### 2-14. INTERCONNECTING CABLES

### 2-15. INTERFACE CARD CABLE

A two metre cable (part no. 12009-60007) is supplied with the card. The cable has a 30-contact printed circuit edge connector on one end and a standard piggy-back HP-IB connector on the other end. The printed circuit edge connector is to be connected to J2 (see Figure 2-1). The pin connections for the interconnecting cable are shown in Table 2-3.

The HP-IB connector end is connected to the peripheral device. Other devices may be added to the bus by using the standard HP-IB cables (not supplied), that are listed in Table 2-4.

### 2-16. CABLING LENGTH RESTRICTIONS

2-17. NORMAL OR LOW SPEED OPERATION (U1S2 OPEN). In order to ensure proper operation of the bus, two rules must be observed regarding the total length of bus cables being used. These rules are as follows:

- All devices on the bus must be the same speed (see paragraph 2-12b).

- b. The total length of cable permitted to be used with one interface card must be less than or equal to two metres times the number of device connected together. The interface card is counted as one device.

- The total maximum length of cable must not exceed 20 metres.

Rule (b) implies that there may be up to 4 metres of cable between the first two devices (2 units X 2m/device = 4m). Additional units may be added using 2 metre cables up to a total of 10 units (10 units X 2m/device = 20m); e.g., using one 4m and eight 2m cables (4+[8X2] = 20). If more than 10 devices are to be connected together, cables shorter than two metres must be used between some of the devices. For example, 15 devices can be connected together using one 4m cable and 13 one-metre cables (4+[13X1] = 17). Other combinations may be used as long as the requirements of rules (b) and (c) are met. In making the calculations, remember to count the interface card as one device.

- 2-18. HIGH SPEED OPERATION (U1S2 CLOSED). To achieve the maximum possible data transfer rate (nominally 930 kbytes per second) within a system, the following guidelines should be followed:

- a. All devices expected to talk at the higher rates must use a settling time of 350 nanoseconds or less..

- b. All devices expected to operate at the higher rates should use 48 mA three-state drivers.

Table 2-3. HP-IB Interface to Bus Connector (J2)

J1 (TEST ONLY)

J2 (HP-IB)

| PIN | NAME | PIN | NAME |

|-----|------|-----|------|

| 1   | GET- | 1   | DIO1 |

| 2   | +5V  | 2   | DIO2 |

| 3   | CMN  | 3   | DIO3 |

| 4   | NC   | 4   | DIO4 |

| 5   | CMN  | 5   | EOI  |

| 6   | ATN  | 6   | DAV  |

| 7   | CMN  | 7   | NRFD |

| 8   | SRQ  | 8   | NDAC |

| 9   | CMN  | 9   | IFC  |

| 10  | IFC  | 10  | SRQ  |

| 11  | CMN  | 11  | ATN  |

| 12  | NDAC | 12  | NC   |

| 13  | CMN  | 13  | NC   |

| 14  | NRFD | 14  | NC   |

| 15  | CMN  | 15  | NC   |

| 16  | DAV  | Α   | DIO5 |

| 17  | REN  | В   | DIO6 |

| 18  | EOI  | С   | DIO7 |

| 19  | DIO8 | D   | DIO8 |

| 20  | DIO5 | E   | REN  |

| 21  | DIO7 | F   | CMN  |

| 22  | DIO3 | Н   | CMN  |

| 23  | DIO6 | J   | CMN  |

| 24  | DIO2 | K   | CMN  |

| 25  | DIO5 | L   | CMN  |

| 26  | DIO1 | М   | CMN  |

| 1   |      | N   | CMN  |

|     |      | P   | CMN  |

|     |      | R   | CMN  |

|     |      | S   | NC   |

Table 2-4. Accessory HP-IB Bus Cables

| LENGTH     | ACCESSORY NUMBER |

|------------|------------------|

| 1 metre    | 10833A           |

| 2 metres   | 10833B           |

| 4 metres   | 10833C           |

| 0.5 metres | 10833D           |

- c. The device capacitance on each lead (REN and IFC excepted) should be less than 50 pF per device. In a system configuration the total device capacitance should be no more than 50 pF for each equivalent resistive load in the system.

- d. Interconnecting cable links should be as short as possible with a maximum of 15 m total length per system.

e. There must be at least one equivalent load for each metre of cable. Using the following information, determine the value of load resistors required for your system.

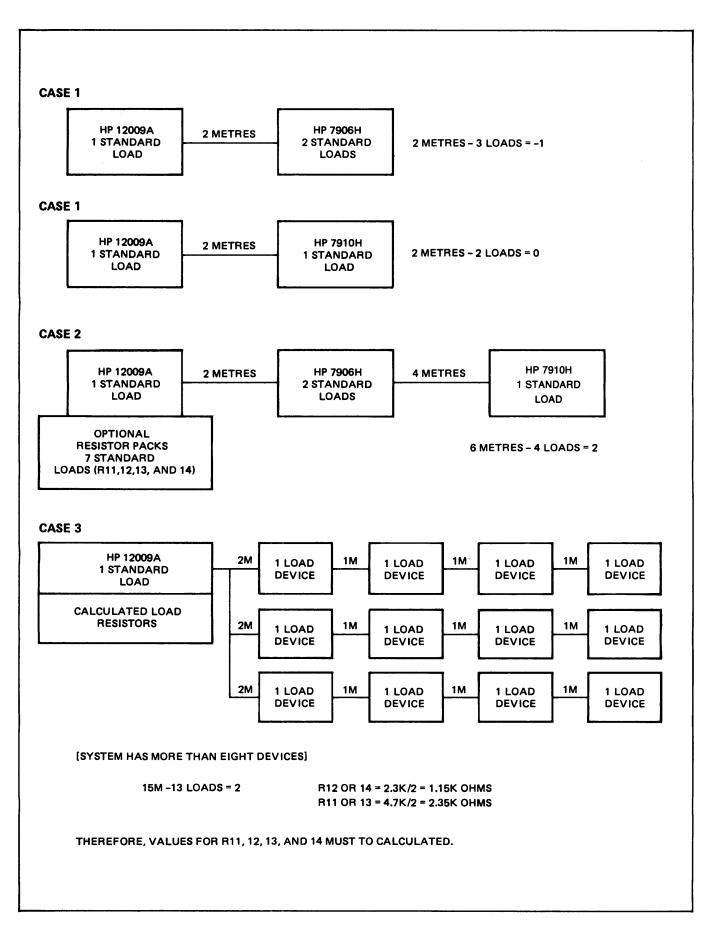

Case 1.

$$m-load = N \le 0$$

As long as N remains less than or equal to 0, the optional load resistor packs are not required.

## Case 2. m-load = N > 0 and less than eight devices are required.

Install optional load resistor packs provided with the card into the sockets provided. Be sure the resistor packs are properly oriented (see Figure 2-1). This will provide the drive for seven equivalent loads. The system is now limited to eight devices on the bus.

## Case 3. m-load = N > 0 and more than eight devices are required.

The optional resistors provided with the card will not meet the requirements for this system. Therefore, the following formulas will have to be used to determine the correct values of the load resistors to be used. Follow the rules closely or the card may be damaged.

R12 or R14 =

$$\frac{2.3 \text{ kohms}}{N}$$

; R11 or R13 =  $\frac{4.7 \text{ kohms}}{N}$

If the power applied to the HP-IB Interface card is lost while the optional resistors are being used, the HP-IB Bus will be pulled down.

Figure 2-5 illustrates four systems, two that illustrate Case 1, one that illustrates Case 2, and one that illustrates Case 3 in selecting the value of the load resistors.

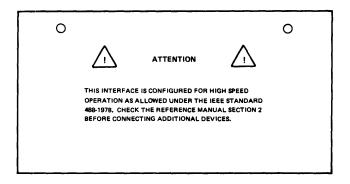

When the HP-IB Card is configured for high speed operation, the High Speed Operation Card (see Figure 2-4) must be attached to the device end of the HP-IB Interface Cable. This card is supplied with the HP-IB Interface (see Section I, paragraph 1-3).

## 2-19. CABLING CONFIGURATIONS

It is recommended that no more than three or four piggyback connectors be stacked together on one device. The resulting structure can exert great force on the panel of the device where the connector is mounted and could cause mechanical damage.

The configuration may be linear (all cables connected end to end) or in a star (all cables branching out from a central point) or any combination of both configurations.

## 2-20. RESHIPMENT

If an item of the package or the complete package is to be returned to the nearest Hewlett-Packard Sales and Service Office for repair, attach a tag to the item identifying the owner and indicating the service to be performed.

Pack the item in the original factory packing material, if available. If the original material is not available, an equivalent type of commerical packaging material should be used. Reliable commerical packing and shipping companies have the facilities and materials to adequately repack the item.

Figure 2-4. HP-IB High Speed Operation Card

Figure 2-5. HP-IB System Examples

## **PROGRAMMING**

## 3-1. INTRODUCTION

This section provides assembly-language programming procedures for the HP-IB Interface. For information on assembly-language programming, refer to the HP 1000 L-Series Reference Manual, part number 02103-90007.

This card has many capabilites such as handling its own Direct Memory Access (DMA), decoding its own instructions from the processor, byte packing and unpacking, and supporting fully the HP-IB functions listed in Section I, paragraph 1-8.

### NOTE

It is recommended that the L-Series user begin driver development utilizing the HP supported driver, part number 92070-16095.

## 3-2. USE OF THE GLOBAL REGISTER

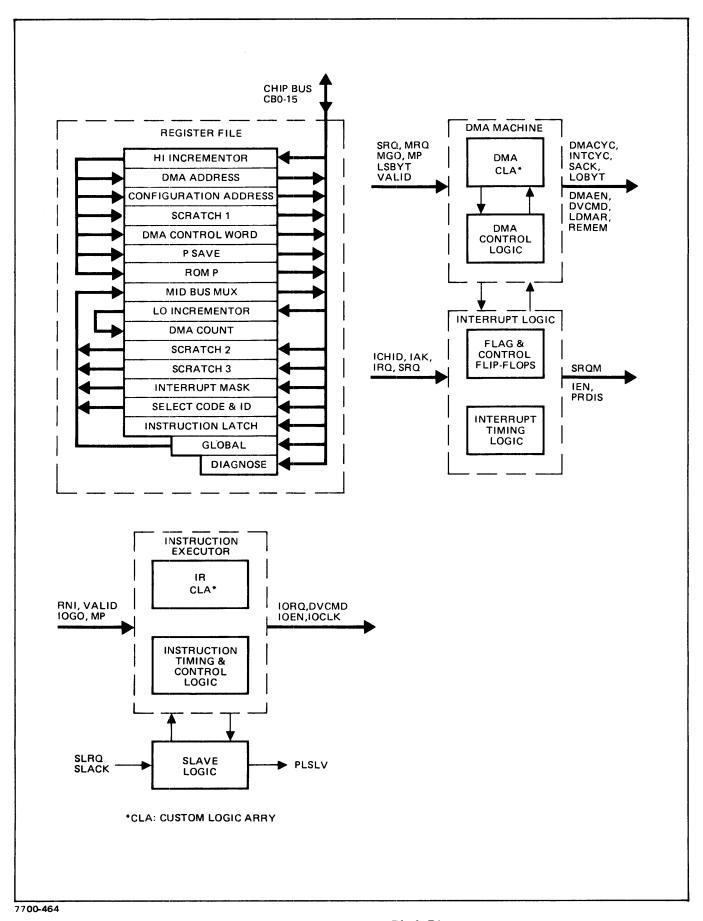

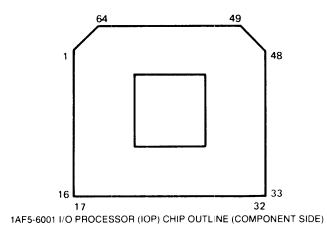

Every L-Series Interface card is comprised of two sections: an I/O Master Section and a Peripheral Device Section. The I/O Master Section performs all of the I/O processing functions for the computer. These functions include I/O instruction recognition and execution, and direct memory accessing (DMA). The I/O Master consists of the I/O Processor (IOP) Chip and its associated logic circuitry. The Global Register (GR) is located in the I/O Processor Chip and is a six-bit register that contains a select code. See Figure 3-1 for a simplified block diagram of the I/O Processor Chip (U67).

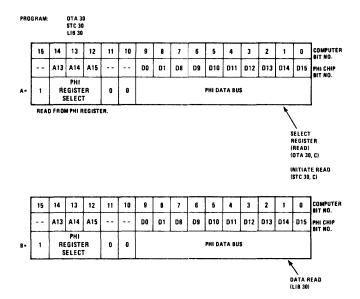

All global registers on all interface cards are controlled by the CPU, thus all global registers contain the same select code. The global register may be loaded with an OTA 2 or OTB 2 I/O instruction, enabled with a CLF 2 I/O instruction, and disabled with an STF 2 I/O instruction. When the global register is enabled, any I/O instruction that is executed by the CPU automatically applies to the card whose select code is in the global register. For the HP-IB card for example, if the global register contains the HP-IB card's select code, the current I/O instruction is decoded and executed by the HP-IB card. Using the global register to store the select code frees the six least significant bits of the I/O instructions. These bits do not need to store the select code of the I/O card to receive the I/O instruction. Thus, these six bits can be used to address a register on the I/O interface cards. On the HP-IB card, there are three such registers: one for data, one for status, and one for control, in addition to registers which are internal to the I/O Processor Chip.

Data may be transferred to and from the HP-IB card with or without the global register enabled. To access the card's control and status registers, however, the global register must be enabled.

## 3-3. I/O INSTRUCTION SET

The I/O Master executes the following twelve I/O instructions:

CLC Clear Control CLF Clear Flag LIA Load Into A Load Into B LIB MIA Merge Into A **MIB** Merge Into B **OTA** Output A Output B OTB SFC Skip if Flag Clear SFS Skip if Flag Set STF Set Flag

Set Control

STC

The six-bit global register allows a maximum of 64 (decimal) select codes. The I/O Master, however, executes only a portion of these. Select code 00 through 17 (octal) are reserved for the CPU, leaving 20 through 77 (octal) available for the I/O system. For further information on the I/O instruction set, refer to the L-Series Reference Manual, part number 02103-90007.

## 3-4. INSTRUCTION USAGE SUMMARY

Table 3-1 lists all of the instructions recognized by the I/O Processor Chip by their select code. There are three conditions relevent to the instruction's execution. These conditions are as follows:

- a. Is the global register (GR) enabled?

- b. Do the contents of the GR equal the I/O Processor Chip's select code, (GR=SC)?

- c. Do the lower six bits of the instruction equal the I/O Processor Chip's select code, (IR=SC)?

This summary indicates which conditions must be met for instruction execution by listing in each column: Y for yes, N for no, and X for don't care.

Figure 3-1. IOP Chip (U67) Block Diagram

## 3-5. HP-IB CAPABILITY