### OPERATING AND SERVICE MANUAL

## 12578A 12578A-01

## DIRECT MEMORY ACCESS COMPUTER ACCESSORY KITS

(FOR 2115A, 2116A, 2116B, AND 2116C COMPUTERS)

Note

This manual should be retained with Volume Two of the computer documentation.

Printed: JUNE 1971 Updated: MARCH 1972

## **TABLE OF CONTENTS**

| Sect | ion   |                                 | Page  | Section    | Pag                               |

|------|-------|---------------------------------|-------|------------|-----------------------------------|

| I    | GENE  | RAL INFORMATION                 |       | 4-2        | 8. DMA Channel 1 Interrupt 4      |

|      | 1-1.  | Introduction                    | 1-1   | 4-3        | 1. DMA Direct Word Input 4-       |

|      | 1-3.  | General Description             |       | 4-3        | 3. DMA Channel 2 Initialization 4 |

|      | 1-8.  | Identification                  |       | 4-4        | 0. DMA Channel 2 Memory Output    |

|      | 1-10. | Current Required from Computers |       |            | Operation 4                       |

|      |       | •                               |       | 4-4        | 4. DMA Channel 2 Interrupt 4      |

| II   | INSTA | LLATION                         |       | 4-4        | 7. DMA Character Byte Outputs 4   |

|      | 2-1.  | Introduction                    | 2-1   | 4-5        | 3. Detailed Description 4         |

|      | 2-3.  | Unpacking and Inspection        | 2-1   | 4-5        | 5. Initialization 4               |

|      | 2-5.  | Factory Installation            | 2-1   | 4-6        | 4. DMA Input Operation 4          |

|      | 2-7.  | Field Installation              | 2-1   | 4-7        | 7. DMA Output Operation 4-1       |

| III  | PROG  | RAMMING                         |       |            |                                   |

|      | 3-1.  | Introduction                    | 3-1   | V MA       | INTENANCE                         |

|      | 3-3.  | Program Word Formats            |       | v NIA      |                                   |

|      | 3-5.  | Typical DMA Program             | 3-2   | 5-1<br>5-3 |                                   |

|      |       |                                 |       | 5-5<br>5-5 |                                   |

| IV   | THEO  | RY OF OPERATION                 |       | 5-5<br>5-7 |                                   |

|      | 4-1.  | Introduction                    | 4 - 1 | 5-7        | . Troubleshooting 5-              |

|      | 4-3.  | Overall Functional Description  | 4-1   |            |                                   |

|      | 4-8.  | Channel Tie-In                  | 4-1   |            |                                   |

|      | 4-16. | DMA Channel 1 Initialization    | 4-2   | VI RE      | PLACEABLE PARTS                   |

|      | 4-22. | DMA Channel 1 Memory Input      |       | 6-1        | . Introduction 6-                 |

|      |       | Operation                       | 4-3   | 6-4        | . Ordering Information 6-         |

## LIST OF ILLUSTRATIONS

| Figure | Title                                  | Page | Figure | Title                                 | Page |

|--------|----------------------------------------|------|--------|---------------------------------------|------|

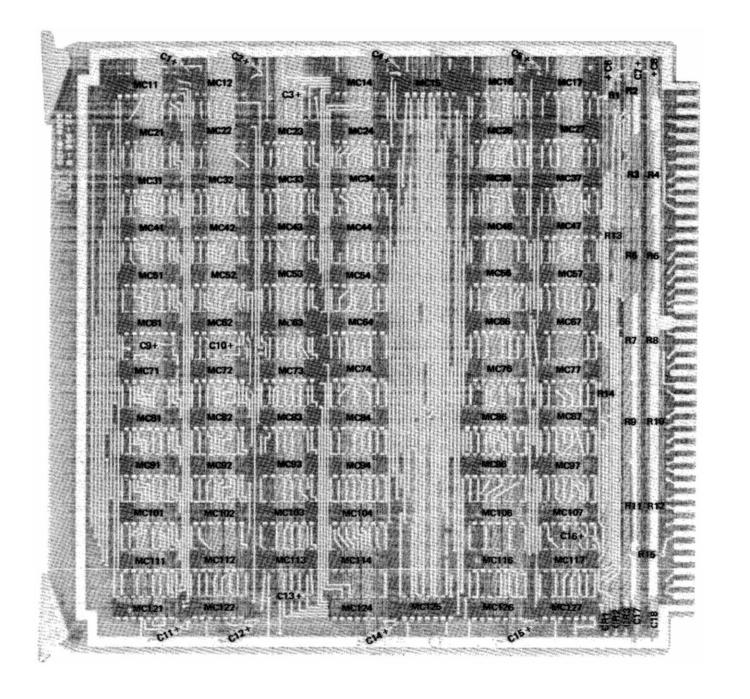

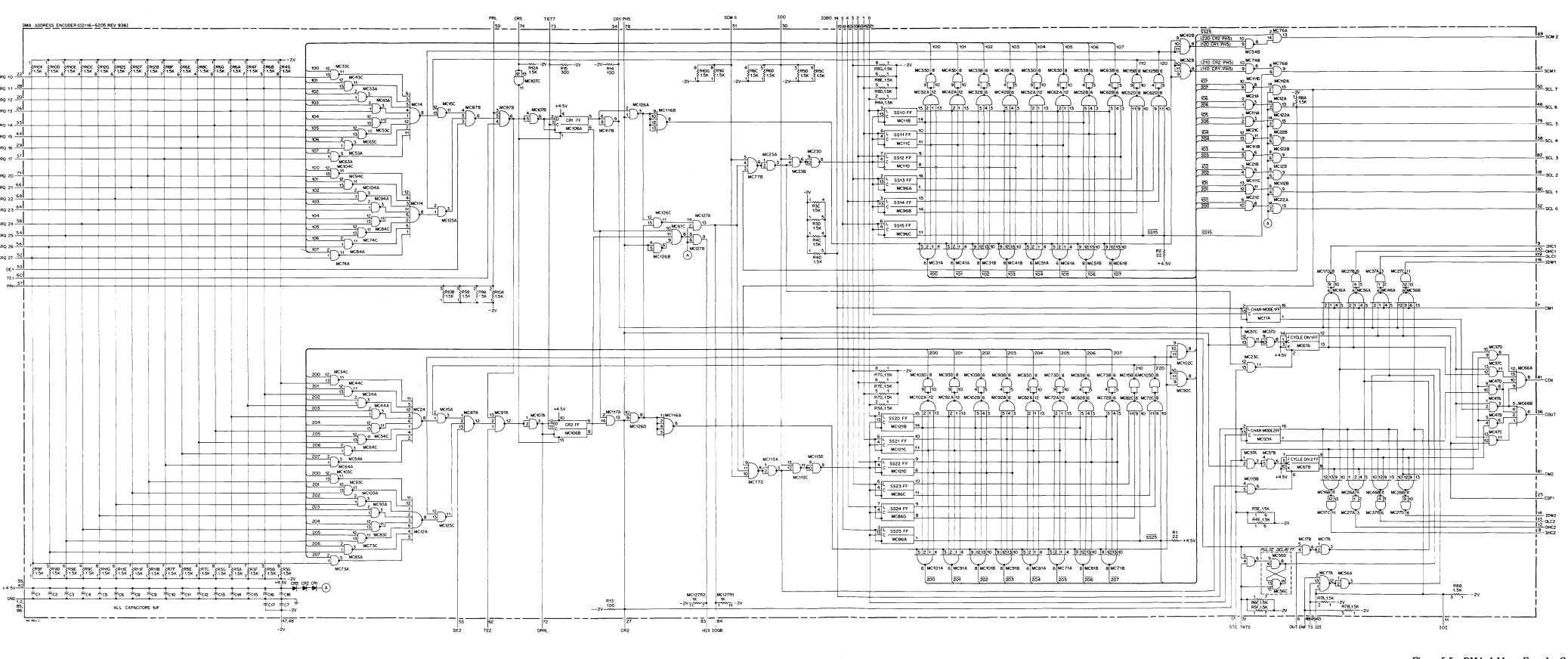

| 3-1.   | DMA Instruction and Control Word       | 0.4  | 5-5.   | DMA Address Encoder Card (02116-6205) |      |

|        | Formats                                |      |        | Logic Diagram and Parts Location      |      |

| 4-1.   | DMA Option Functional Block Diagram    | 4-13 |        | Diagram                               | 5-33 |

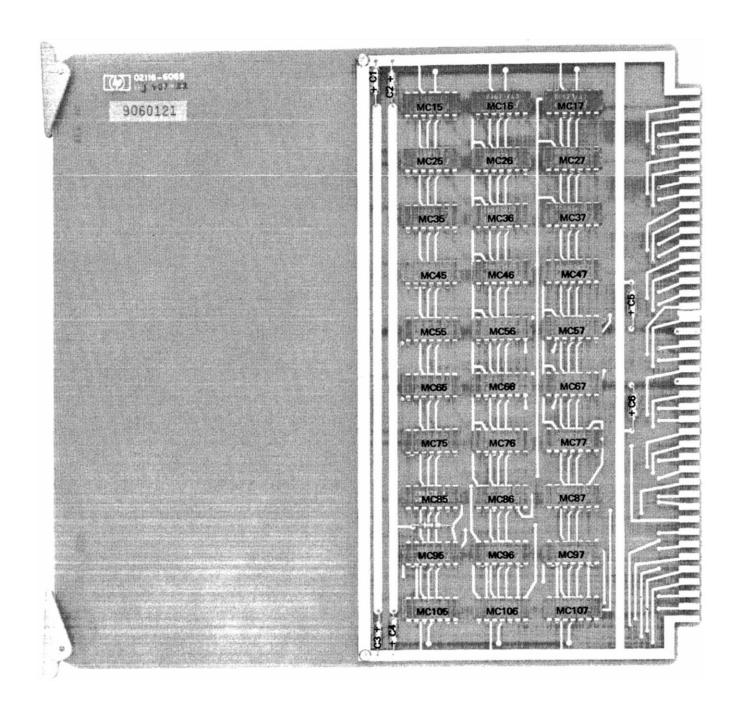

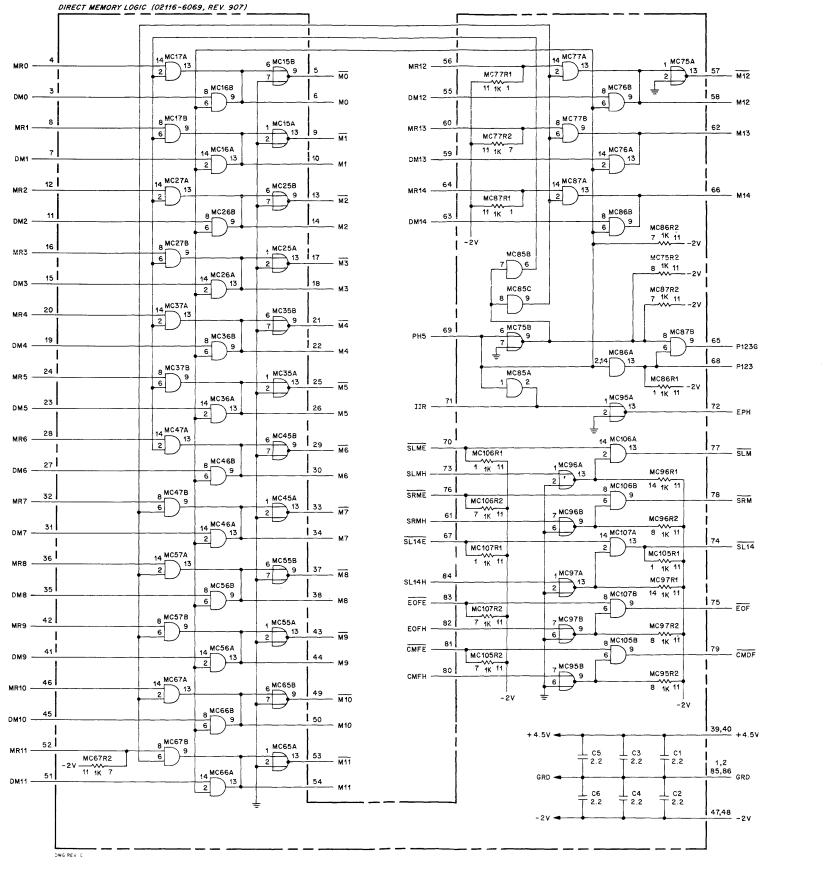

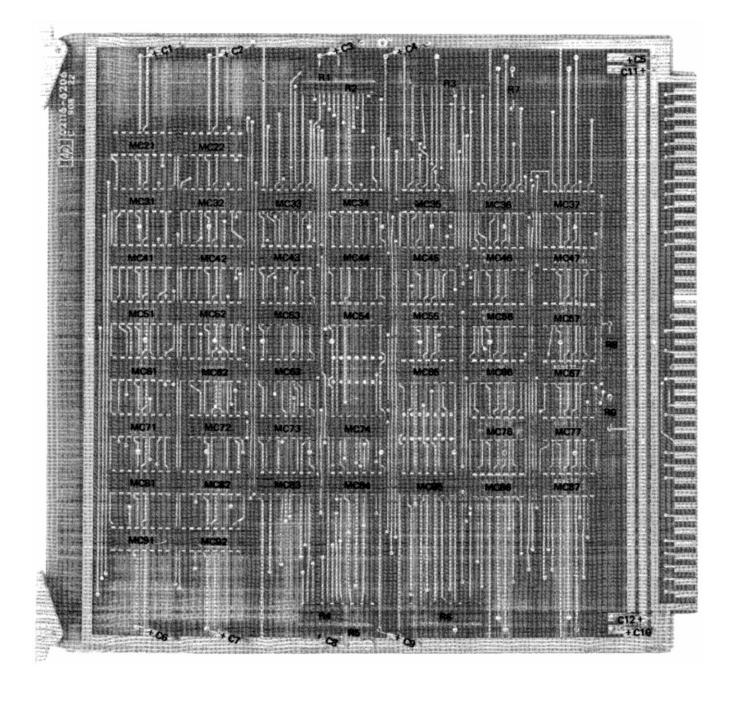

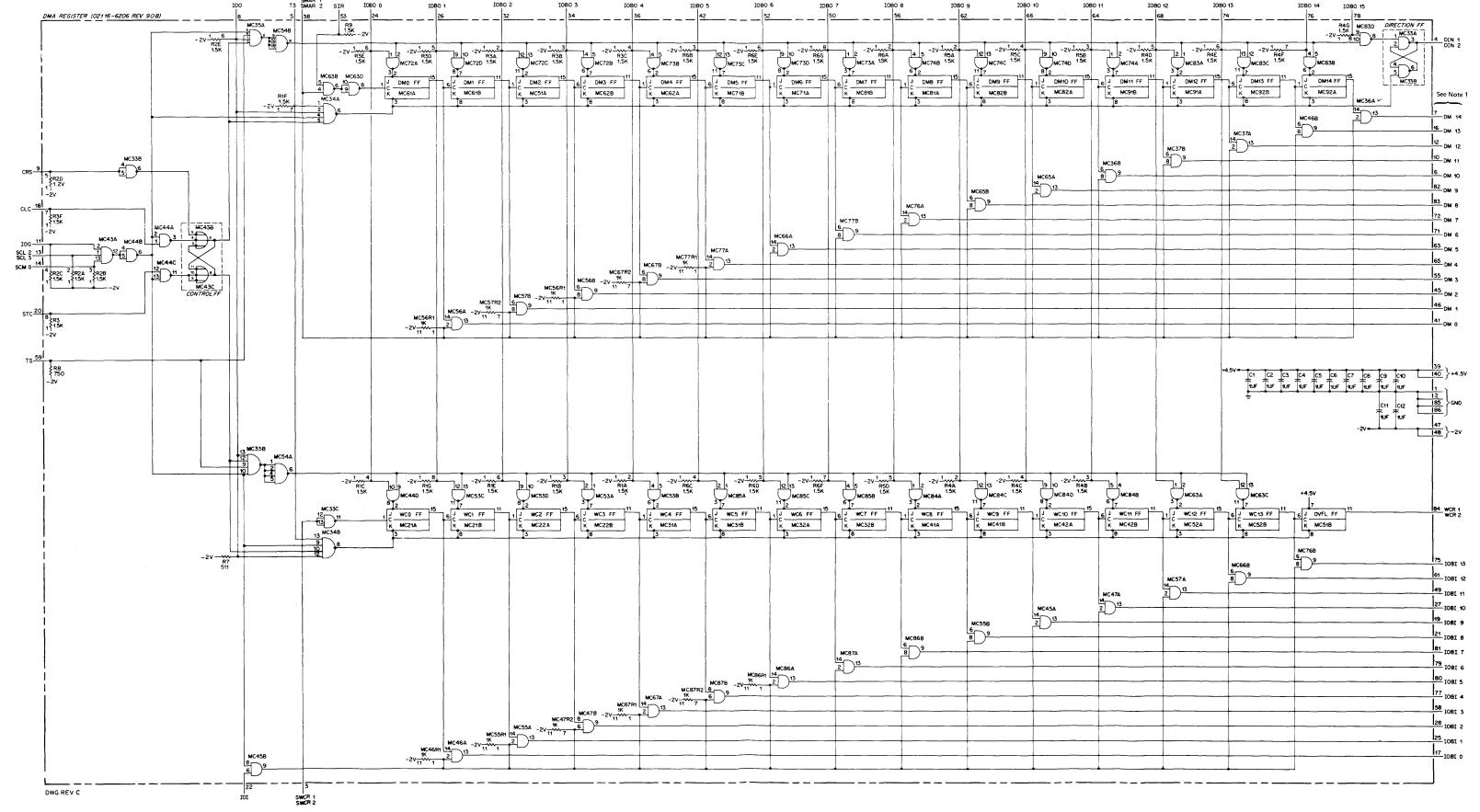

| 5-1.   | DML Card (02116-6069) Logic Diagram    |      | 5-6.   | DMA Register Card (02116-6206) Logic  |      |

|        | and Parts Location Diagram             | 5-25 |        | Diagram and Parts Location            |      |

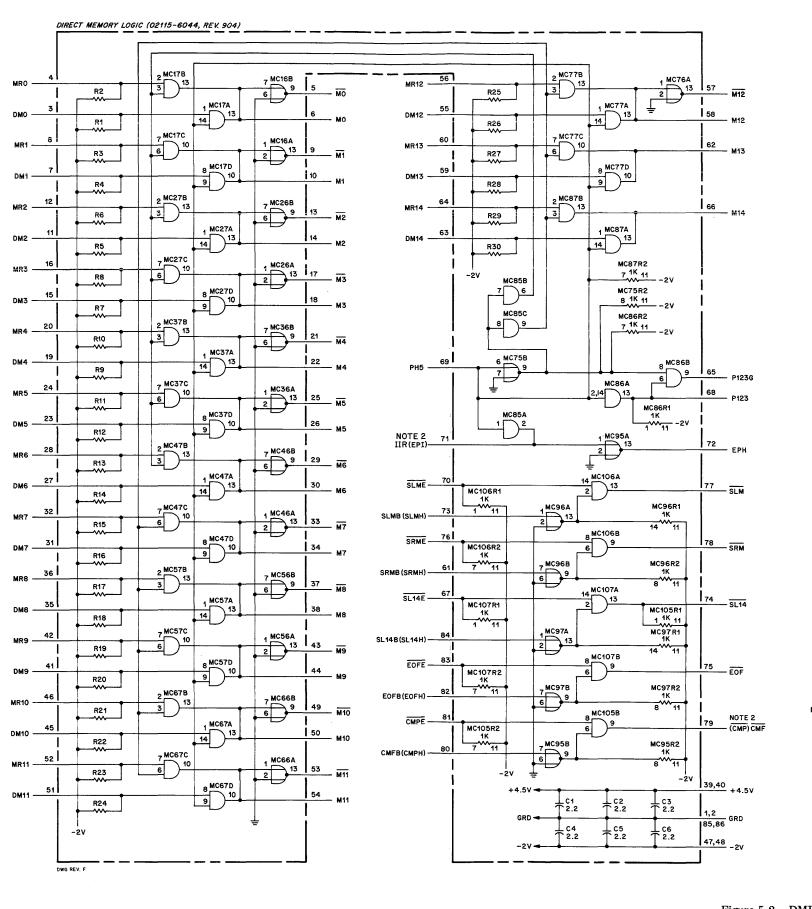

| 5-2.   | DML Card (02115-6044) Logic Diagram    |      |        | Diagram                               | 5-35 |

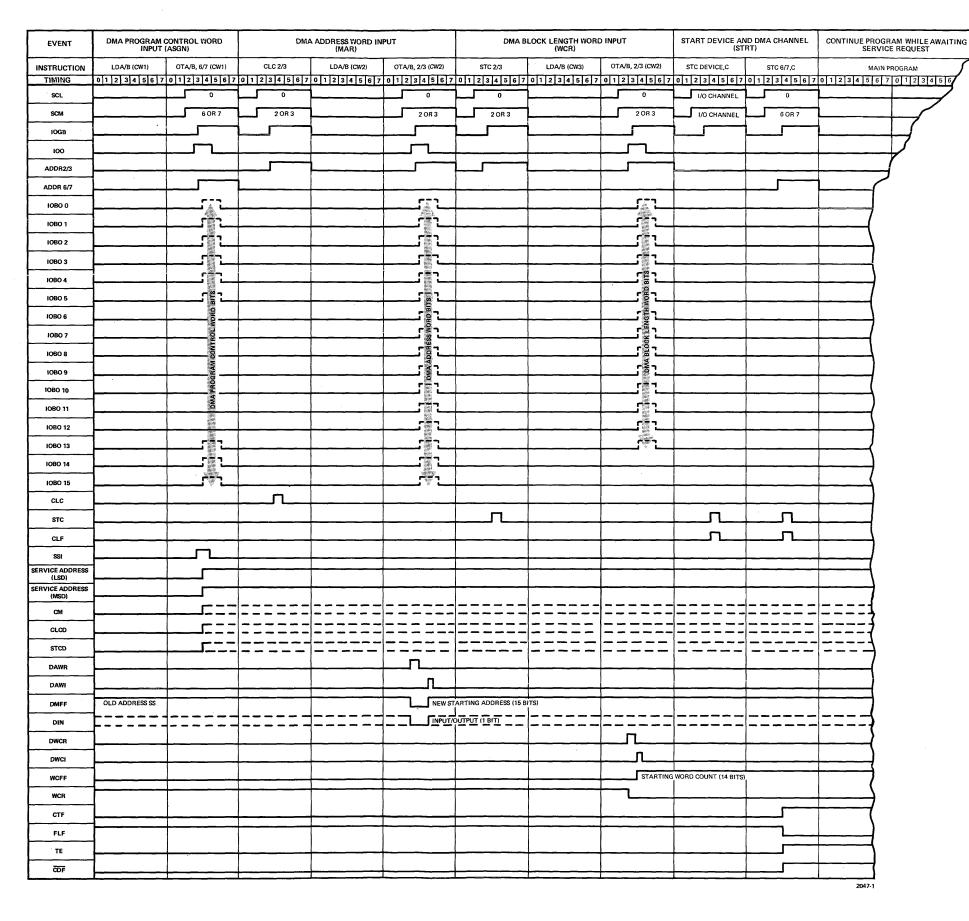

|        | and Parts Location Diagram             | 5-27 | 5-7.   | DMA Initialization Timing Diagram     |      |

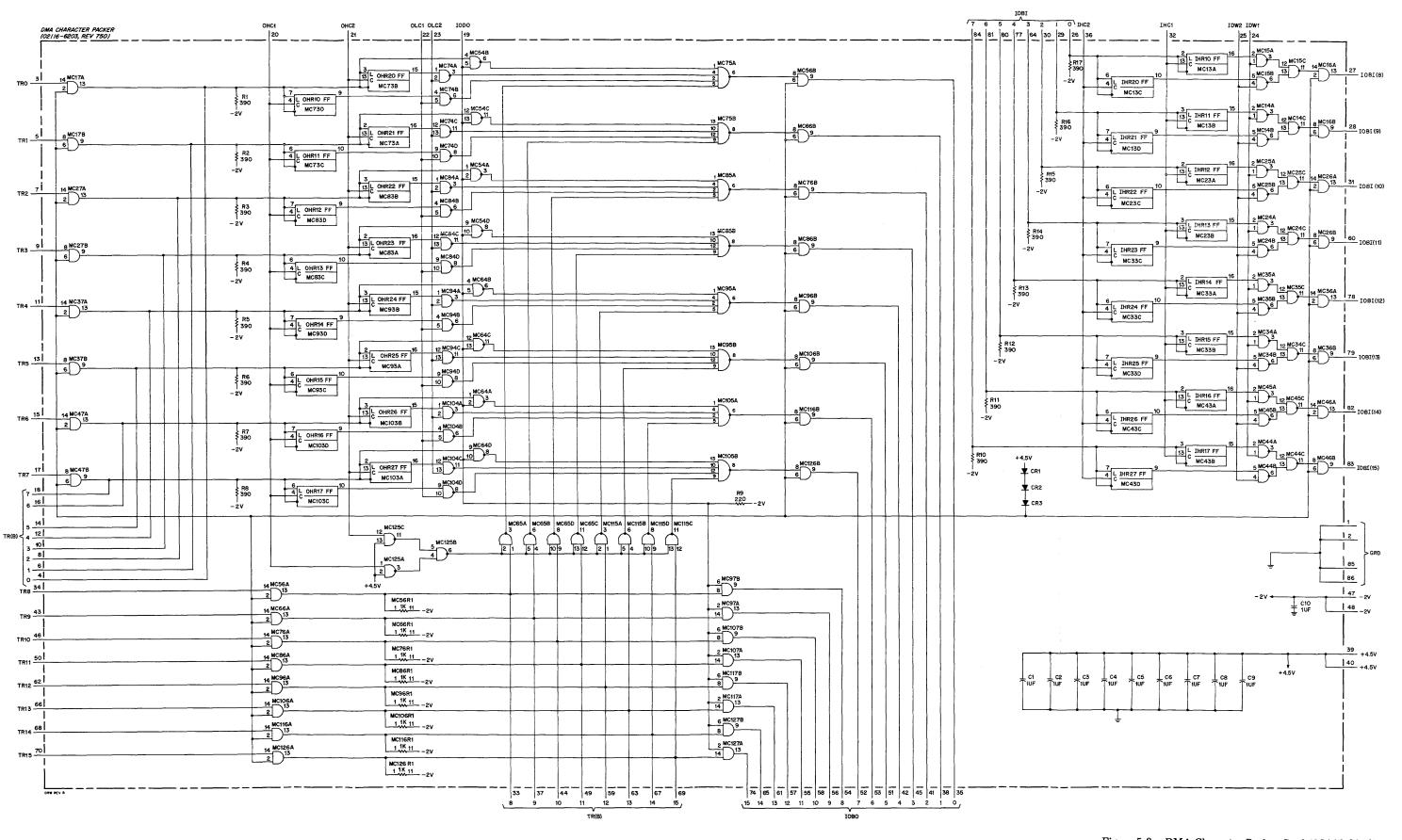

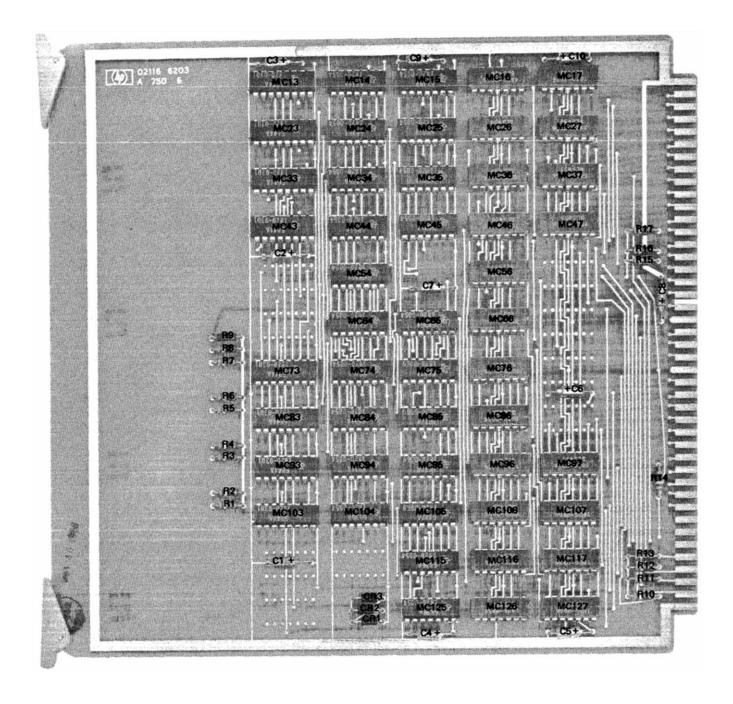

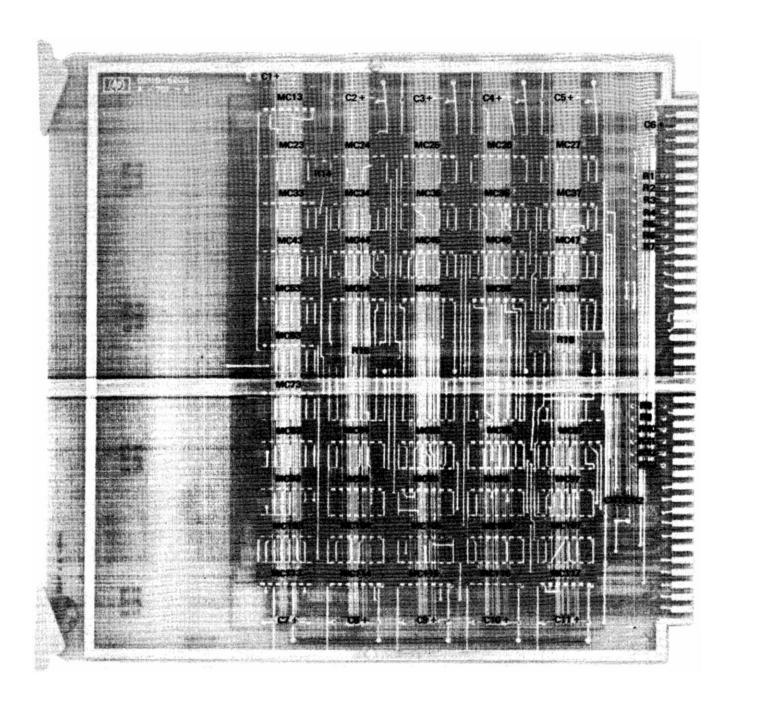

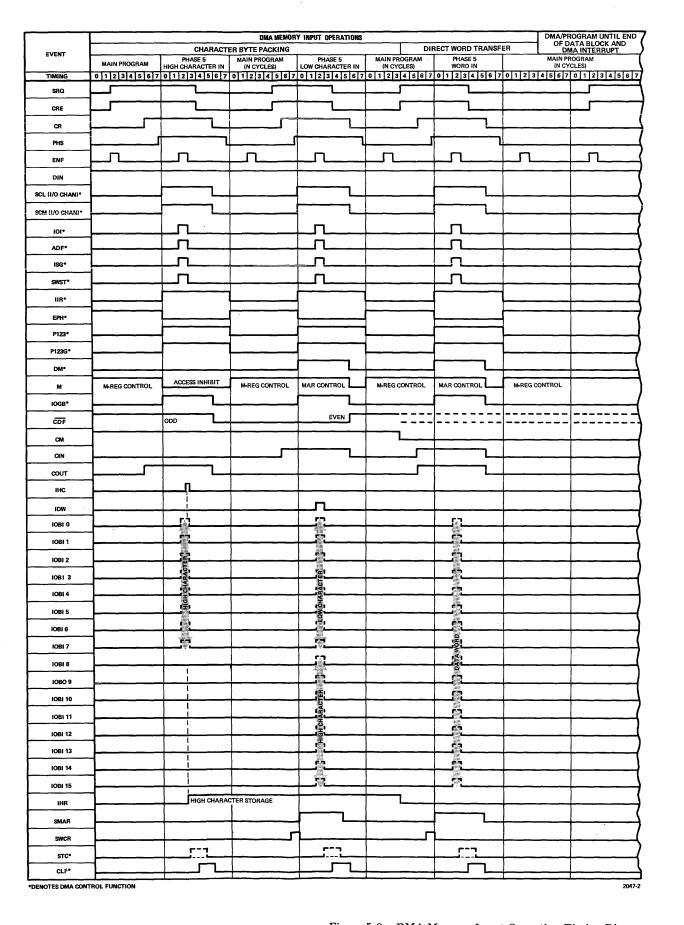

| 5-3.   | DMA Character Packer Card (02116-6203) |      | 5-8.   | DMA Memory Input Operation Timing     |      |

|        | Logic Diagram and Parts Location       |      |        | Diagram                               | 5-39 |

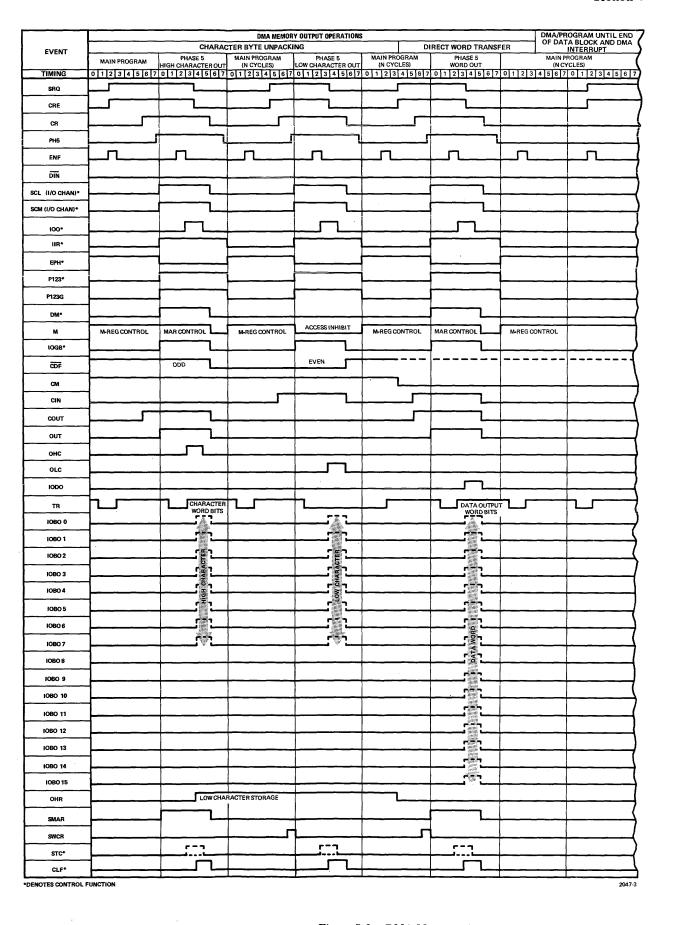

|        | Diagram                                | 5-29 | 5-9.   | DMA Memory Output Operation Timing    |      |

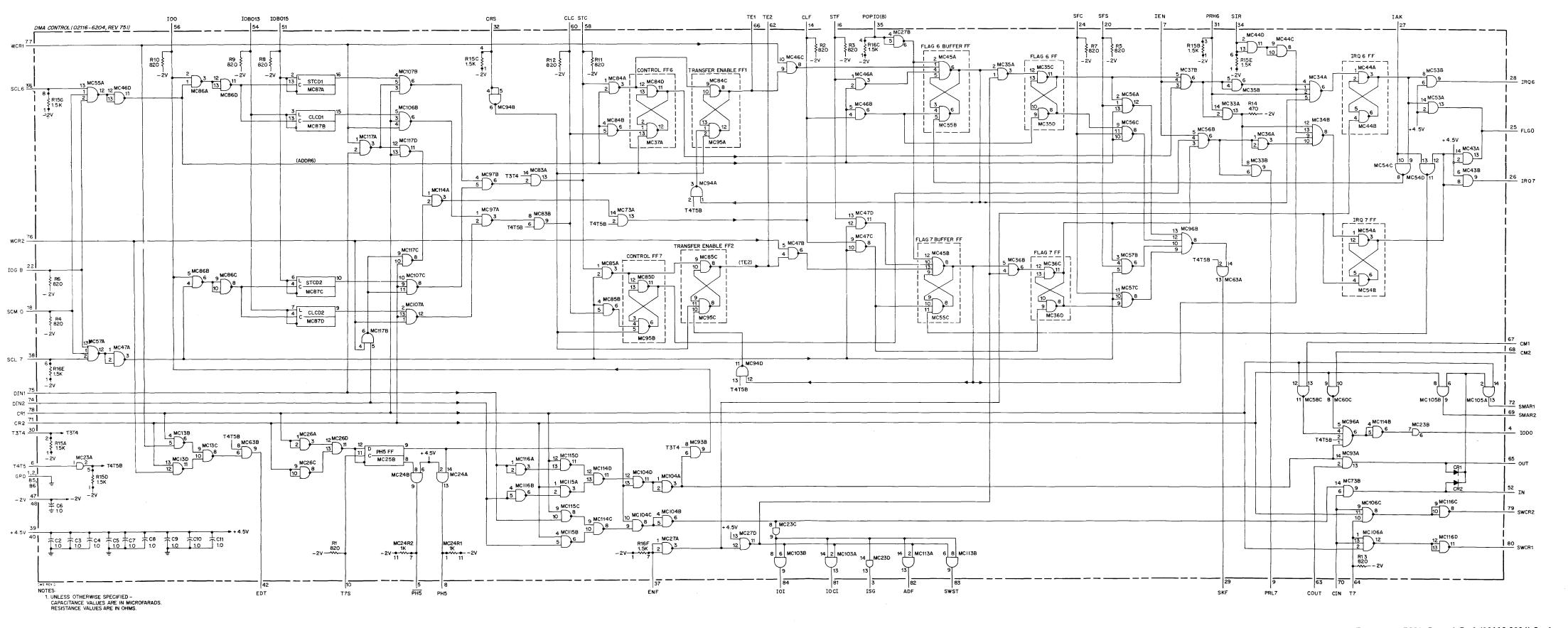

| 5-4.   | DMA Control Card (02116-6204) Logic    |      |        | Diagram                               | 5-41 |

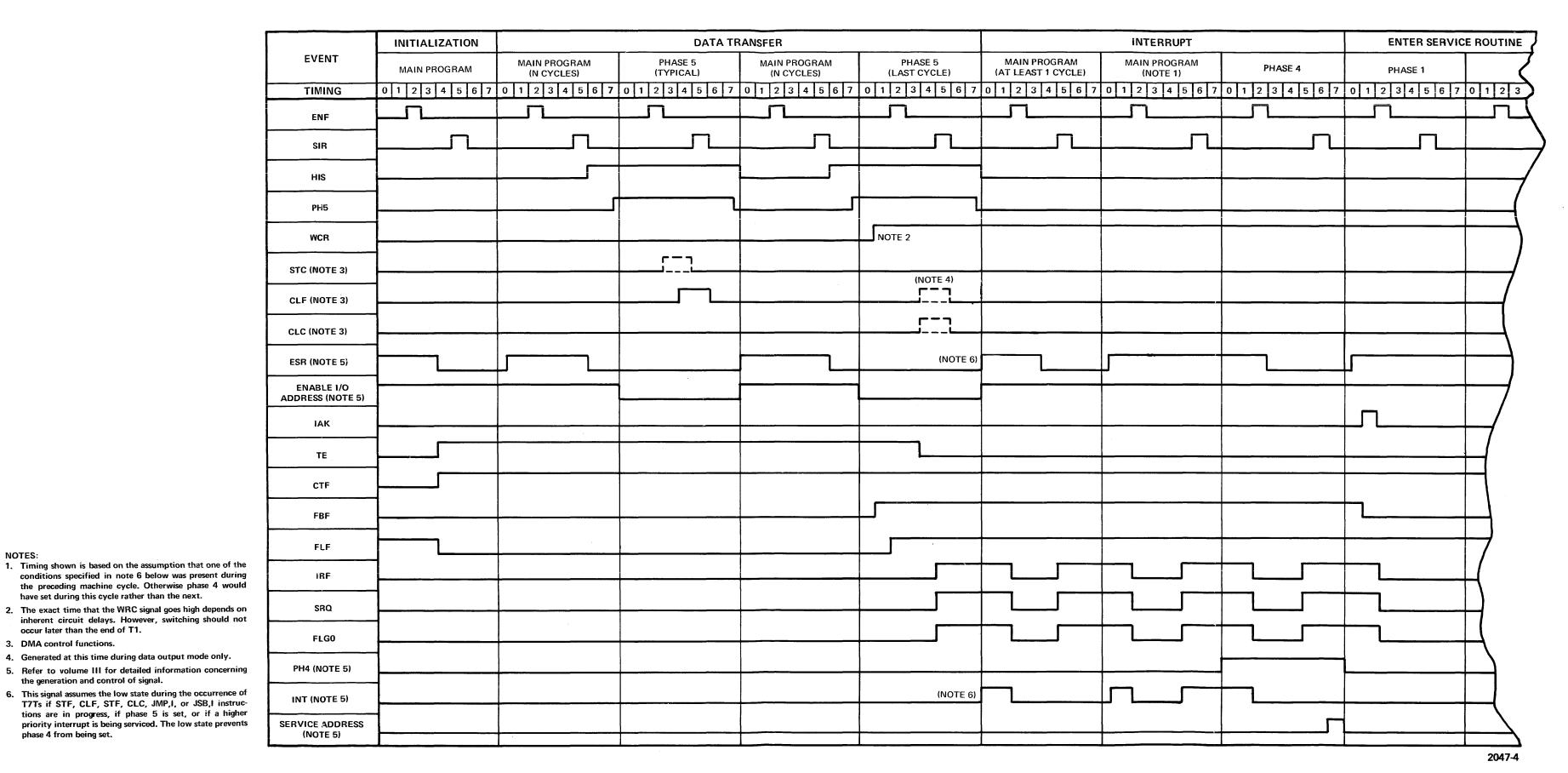

|        | Diagram and Parts Location Diagram     | 5-31 | 5-10.  | DMA Interrupt Timing Diagram          |      |

## **LIST OF TABLES**

| Table | Title                                                                        | Page | Table | Title                                           | Page   |

|-------|------------------------------------------------------------------------------|------|-------|-------------------------------------------------|--------|

| 1-1.  | Plug-In Assemblies Required for Installation and Operation of the DMA Option | 1-1  | 5-6.  | DMA Control Card (02116-6204) Replaceable Parts | . 5-30 |

| 2-1.  | Field Installation Checklist                                                 | 2-2  | 5-7.  | DMA Address Encoder Card (02116-6205)           |        |

| 3-1.  | Typical DMA Program                                                          | 3-2  |       | Replaceable Parts                               | . 5-32 |

| 5-1.  | DMA Performance Test Error Halts                                             | 5-1  | 5-8.  | DMA Register Card (02116-6206)                  |        |

| 5-2.  | DMA Option Input/Output Signals                                              |      | 0 0.  | Replaceable Parts                               | . 5-34 |

|       | and Equations                                                                |      | 6-1.  | Replaceable Parts                               |        |

| 5-3.  | DML Card (02116-6069) Replaceable Parts.                                     | 5-24 |       | <del>-</del>                                    |        |

| 5-4.  | DML Card (02116-6044) Replaceable Parts.                                     | 5-26 | 6-2.  | Reference Designations and                      |        |

| 5-5.  | DMA Character Packer Card (02116-6203)                                       |      |       | Abbreviations                                   | . 6-3  |

|       | Replaceable Parts                                                            | 5-28 | 6-3.  | Code List of Manufacturers                      | . 6-4  |

#### SECTION I

#### **GENERAL INFORMATION**

#### 1-1. INTRODUCTION.

1-2. This operating and service manual covers general information, installation, programming, theory of operation, and maintenance instructions for the Hewlett-Packard 12578A and 12578A-01 Direct Memory Access Computer Accessory Kits for the HP 2115 and HP 2116 Computers.

#### 1-3. GENERAL DESCRIPTION.

02116-6206

02115-6044

02116-6069

02115-6015

02116-6041

or

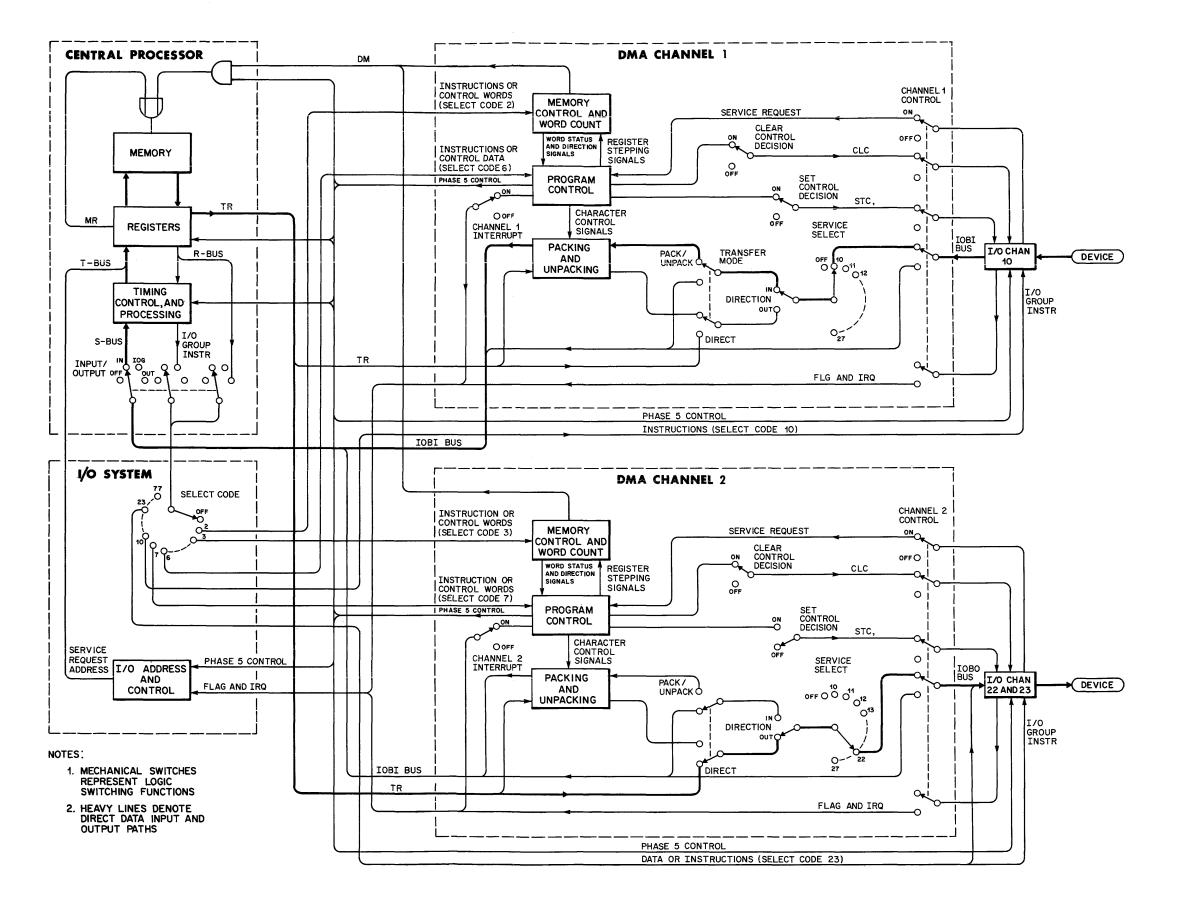

1-4. Direct memory access (DMA) enables the computer to transfer data directly between memory and external devices at a maximum rate of 625,000 16-bit wordsper-second in block lengths from 1 to 16,384 words. The DMA system consists of two separate, independent, high-

priority control channels. Either or both DMA channels may be switched under program control between computer memory and any device normally serviced through the I/O system of the computer mainframe.

1-5. The DMA option consists of five printed circuit cards that plug directly into the computer mainframe. The cards consist of two DMA register assemblies, a DMA control assembly, a DMA address encoder assembly, and a DMA character packer assembly. The combination of these assemblies permits direct data transfer in either direction between an external device and computer memory using one machine cycle per 16-bit word transfer. Refer to table 1-1 for a complete listing of the plug-in assemblies supplied with the DMA option.

A1,

A2

A201

| НР         |                                                         |         | QUANTITY<br>REQUIRED |          |                |

|------------|---------------------------------------------------------|---------|----------------------|----------|----------------|

| PART NO.   | DESCRIPTION                                             | HP 2115 | HP 2116A/B           | HP 2116C | OR<br>SUPPLIED |

| 02116-6203 | Printed Circuit Board Assembly:<br>DMA Character Packer | A23     | A120                 | A5       | 1*             |

| 02116-6204 | Printed Circuit Board Assembly:<br>DMA Control          | A22     | A119                 | A4       | 1*             |

| 02116-6205 | Printed Circuit Board Assembly:                         | Δ91     | Δ118                 | Δ3       | 1*             |

A122.

A123

A20

A18

A116,

A117

2116A-

2116B-

A201

A113:

A20

Table 1-1. Plug-In Assemblies Required for Installation and Operation of the DMA Option

DMA Address Encoder

Printed Circuit Board Assembly:

**DMA** Register

Printed Circuit Board Assembly:

Printed Circuit Board Assembly:

I/O Control

Printed Circuit Board Assembly:

Direct Memory Logic

2\*

1

or

1\*\*

1\*\*\*

1\*\*\*

<sup>\*</sup> Supplied with HP 12578A and HP 12578A-01 Modification Kits.

<sup>\*\*</sup> Either 02115-6044, board revision B-821, B-904, or later, or 02116-6069, board revision J-905, J-907, or later is required. An 02115-6044 board revision B-904, or later, is supplied with HP 12578A-01 Modification Kit.

<sup>\*\*\*</sup> Board revision 822 or later is required, but not supplied with modification kits.

Section I 12578A/01

1-6. To be placed in operation, the two DMA channels must first be initialized for a specific operating mode by instructions and control words in the main program. Data interchange then occurs automatically over DMA channel 1 or DMA channel 2 when a service request command signal is received from an I/O channel programmed to DMA. The DMA channel receiving the service request takes control of the central processor and I/O system, suspends the running program at the end of the current phase, and, during the following machine cycle, generates a special phase 5 memory cycle to read or write a word directly into or out of a predetermined memory location. At the end of the phase 5 memory cycle (one complete machine cycle), control is returned to the central processor and I/O system, and the main program is automatically resumed at the point where it was suspended, without loss of continuity. A new phase 5 cycle is initiated each time the I/O channel signals to DMA that it is ready to input or output another word. When all data in a predetermined block length has been transferred, the DMA channel initiates a normal interrupt to a service subroutine.

1-7. An important feature of DMA is the capability of conserving memory space by packing two 8-bit input characters (bytes) into a 16-bit character word format and storing the word in a single memory location. Character words from memory are divided into two separate eight-bit byte outputs by an unpacking process. Character packing/

unpacking is a program option that is turned on or off by a single control bit during DMA channel initialization, and can be used only with external devices that employ eightbit characters.

#### 1-8. IDENTIFICATION.

1-9. Printed-circuit card revisions are identified by a letter and a date code stamped on the card. The letter code identifies the version of the etched trace pattern on the unloaded card. The date code refers to the electrical characteristics of the loaded card. If the date code stamped on the printed circuit card does not agree with the date code shown on the schematic diagram in section IV of this manual for the DMA card, there are differences between your card and the card described in this manual. These differences are described in change sheets and manual supplements available at the nearest HP Sales and Service Office.

#### 1-10. CURRENT REQUIRED FROM COMPUTER.

1-11. To operate the logic circuits, the plug-in cards require a total of 6.2 amperes from the +4.5-volt computer power supply and 720 milliamperes from the -2-volt computer power supply.

#### SECTION II

#### INSTALLATION

#### 2-1. INTRODUCTION.

2-2. This section contains information on unpacking and inspection, and on field and factory installation of the DMA option.

#### 2-3. UNPACKING AND INSPECTION.

2-4. If the shipping carton is damaged upon receipt, request that the carrier's agent be present when the equipment is unpacked. Inspect the assemblies for damage (scratches, cracks, loose components, etc.). If the equipment is damaged or fails to meet specifications, notify the carrier and the nearest Hewlett-Packard Sales and Service Office immediately. (Sales and Service Offices are listed at the back of this manual.) Retain the shipping container and the padding material for the carrier's inspection. The Hewlett-Packard Sales and Service Office will arrange for the repair or replacement of the damaged instrument without waiting for any claims against the carrier to be settled.

#### 2-5. FACTORY INSTALLATION.

2-6. If purchased as part of an initial computer order or if added to computers bearing serial number prefixes prior to 746-, the DMA option is installed at the factory and is ready for operation upon receipt of the equipment. When the computer is installed, conduct a performance test of the DMA option in accordance with the test instructions presented in the maintenance section of this manual. If test results are satisfactory, the DMA option is ready for normal use.

#### 2-7. FIELD INSTALLATION.

2-8. Field installation of the DMA option consists of incorporating the plug-in assemblies furnished in the DMA modification kit (refer to table 1-1) into the computer. It may be necessary, however, to make other modifications as specified in table 2-1 before incorporating the DMA kit items, depending on the model and serial number prefix of the computer. Note that Modification Kit HP 12578A-01 includes direct memory logic (DML) assembly 02115-6044, revision B-904 or later, for computers not already equipped with either the 02115-6044 assembly or DML assembly 02116-6069, revision J-907 or later. The I/O control assem-

blies specified in tables 1-1 and 2-1 are not supplied with either modification kit and must be ordered separately, if required.

- 2-9. To field install the DMA option, proceed as follows:

- a. Check the serial number prefix of the computer in which the DMA option is to be installed. Then carefully review the information presented in table 2-1 that applies to that prefix. Make sure that the necessary modifications have been made, or that the necessary materials and instructions are at hand to make them, before proceeding with the following steps. If further information or assistance is required, consult the nearest Hewlett-Packard Sales and Service Office listed at the back of this manual.

- b. Check to ensure that when the DMA option cards are added to the computer the current drain on the power supply will not exceed the limits specified in Volume Three.

- c. Set the computer POWER switch to OFF.

- d. Using the cards supplied in the modification kit, configure the computer as indicated in table 1-1.

- e. Recheck the information presented in table 1-1 and table 2-1 to ensure that the computer is configured as specified.

- f. Set the POWER switch to ON and observe whether power turn-on is normal. If normal, conduct a performance test of the DMA option in accordance with the test instructions presented in the maintenance section of this manual. If test results are normal, the DMA option may be programmed for operation.

- g. If the plug-in card assemblies in slots A18 or A20 of the HP 2115A Computer, slots A113 or A201 of the HP 2116A Computer, or slots A20 or A201 of the HP 2116B Computer, were replaced with assemblies of a later revision, return the obsolete assemblies to the nearest Hewlett-Packard Sales and Service Office.

- h. Run the Diagnostic Program Procedure, part no. 12578-90013, contained in the *Manual of Diagnostics* to verify that the DMA accessory kit is operating properly.

Table 2-1. Field Installation Checklist

| T        | 7                            |                                                                                                                                                                                                                                                                                                                                                                        | · · · · · · · · · · · · · · · · · · ·   |

|----------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| MODEL    | *SERIAL<br>NUMBER<br>PREFIX  | MODIFICATIONS REQUIRED FOR INCORPORATION OF DMA OPTION                                                                                                                                                                                                                                                                                                                 | SERIAL NUMBER PREFIX AFTER MODIFICATION |

|          |                              | Note                                                                                                                                                                                                                                                                                                                                                                   |                                         |

|          |                              | For information concerning computers with serial number prefixes other than those specified in this table, consult the nearest Hewlett-Packard Sales and Service Office.                                                                                                                                                                                               |                                         |

| HP 2115A | 744-<br>817-<br>818-<br>819- | <ol> <li>BACKPLANE. Backplane wiring modifications are required prior to installation and operation of the DMA option. These modifications update the subject computers to the 823- configuration. Consult the nearest Hewlett-Packard Sales and Service Office for assistance in making this change.</li> <li>I/O CONTROL CARD. The I/O control card orig-</li> </ol> | 823-                                    |

|          |                              | inally supplied in slot A18 of the subject computers must be replaced with I/O control card 02115-6015, revision 822 or later, to make the I/O system of these computers compatible with the DMA option.                                                                                                                                                               |                                         |

|          |                              | 3. INTERRUPT PRIORITY JUMPER. Jumper-wire W1 on front panel coupler card 02115-6011, located in slot A8, must be removed when the DMA option is incorporated into the subject computers. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to Volume III for detailed information concerning this change.                |                                         |

|          |                              | 4. MODIFICATION KIT. Installation of the items supplied in the HP 12578A-01** Modification Kit completes the DMA modification requirements for the subject computers.                                                                                                                                                                                                  |                                         |

|          | 827-<br>828-                 | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computers to the 831- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>                                   | 831-                                    |

|          |                              | 2. INTERRUPT PRIORITY JUMPER. Jumper-wire W1 on front panel coupler card 02115-6011, located in slot A8, must be removed when the DMA option is incorporated into the subject computers. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change.                | ·                                       |

|          |                              | 3. MODIFICATION KIT. Installation of the items supplied in the HP 12578A-01** Modification Kit completes the DMA modification requirements for the subject computers.                                                                                                                                                                                                  |                                         |

|          |                              |                                                                                                                                                                                                                                                                                                                                                                        |                                         |

Table 2-1. Field Installation Checklist (Continued)

| *SERIAL<br>NUMBER<br>PREFIX | MODIFICATIONS REQUIRED FOR INCORPORATION OF DMA OPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SERIAL NUMBER PREFIX AFTER MODIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 839-                        | <ol> <li>BACKPLANE. Backplane wiring modifications are required prior to installation and operation of the DMA option. These modifications update the subject computer to the 904- configuration. Consult the nearest Hewlett-Packard Sales and Service Office for assistance in making this change.</li> <li>INTERRUPT PRIORITY JUMPER. Jumper-wire W1 on front panel coupler card 02115-6011, located in slot A8, must be removed when the DMA option is incorporated into the subject computer. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 904-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             | 3. MODIFICATION KIT. Installation of the items supplied in the HP 12578A-01** Modification Kit completes the DMA modification required for the subject computer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 904-<br>and<br>above        | <ol> <li>INTERRUPT PRIORITY JUMPER. Same as item 2 for the 839- configuration.</li> <li>MODIFICATION KIT. Same as item 3 for the 839-configuration.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| All prior<br>to 746-        | FACTORY MODIFICATIONS. Computers having serial number prefixes prior to 803- must be returned to the factory for mechanical and electrical modifications before the DMA option can be incorporated.      MODIFICATION AND TO THE METHOD AND THE AND THE AND THE PROPERTY OF THE PROPERTY | 803-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             | 2. MODIFICATION KIT. The items supplied in the HP 12578A-01** Modification Kit are installed in the subject computers at the factory before reshipment to the user.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 746-<br>749-                | 1. BACKPLANE. Backplane wiring modifications are required prior to installation and operation of the DMA option. These modifications update the subject computers to the 803- configuration. Consult the nearest Hewlett-Packard Sales and Service Office for assistance in making this change.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 803-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                             | <ol> <li>I/O CONTROL CARD. The I/O control card originally supplied in slot A201 of the subject computers must be replaced with I/O control card 02116-6041, revision 822 or later, to make the I/O system compatible with the DMA option.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | PREFIX 839- 904- and above  All prior to 746-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NUMBER PREFIX  1. BACKPLANE. Backplane wiring modifications are required prior to installation and operation of the DMA option. These modifications update the subject computer to the 904 configuration. Consult the nearest Hewlett-Packard Sales and Service Office for assistance in making this change.  2. INTERRUPT PRIORITY JUMPER. Jumper-wire W1 on front panel coupler card 02115-6011, located in slot A8, must be removed when the DMA option is incorporated into the subject computer. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change.  3. MODIFICATION KIT. Installation of the items supplied in the HP 12578A-01** Modification Kit completes the DMA modification required for the subject computer.  904- and above  1. INTERRUPT PRIORITY JUMPER. Same as item 2 for the 839- configuration.  2. MODIFICATION KIT. Same as item 3 for the 839-configuration.  All prior to 746- 1. FACTORY MODIFICATIONS. Computers having serial number prefixes prior to 803- must be returned to the factory for mechanical and electrical modifications before the DMA option can be incorporated.  2. MODIFICATION KIT. The items supplied in the HP 12578A-01** Modification Kit are installed in the subject computers at the factory before reshipment to the user.  746- 749- 1. BACKPLANE. Backplane wiring modifications are required prior to installation and operation of the DMA option. These modifications update the subject computers to the 803- configuration. Consult the nearest Hewlett-Packard Sales and Service Office for assistance in making this change.  2. I/O CONTROL CARD. The I/O control card originally supplied in slot A201 of the subject computers must be replaced with I/O control card 02116-6041, revision 822 or later, to make the I/O system com- |

Table 2-1. Field Installation Checklist (Continued)

| MODEL | *SERIAL<br>NUMBER<br>PREFIX | MODIFICATIONS REQUIRED FOR INCORPORATION OF DMA OPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SERIAL NUMBER<br>PREFIX AFTER<br>MODIFICATION |

|-------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|       |                             | <ol> <li>INTERRUPT PRIORITY JUMPERS. If power turn- on card 02116-6095, revision 734- or later, or power-fail interrupt card 02116-6175 is installed in slot A115, a jumper-wire change must be made on either card when the DMA option is installed. This change is required to connect select codes 06 and 07 into the interrupt priority structure. If the power turn-on card resides in slot A115, jumper-wire W9 must be removed from the card. If the power fail interrupt card resides in slot A115, jumper-wire W2 must be removed from the card. Refer to volume III for detailed information concerning this change.</li> <li>MODIFICATION KIT. Installation of the items sup-</li> </ol> |                                               |

|       |                             | plied in the HP 12578A-01** Modification Kit completes the DMA modification requirements for the subject computers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |

|       | 747-<br>750-                | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computers to the 807- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                | 807-                                          |

|       |                             | <ol> <li>I/O CONTROL CARD. The I/O control card originally supplied in slot A201 of the subject computers must be replaced with I/O control card 02116-6041, revision 822 or later, to make the I/O system compatible with the DMA option.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                               |

|       |                             | 3. INTERRUPT PRIORITY JUMPERS. If power turn- on card 02116-6095, revision 734 or later, or power-fail interrupt card 02116-6175 is installed in slot A115, a jumper-wire change must be made on either card when the DMA option is installed. This change is required to connect select codes 06 and 07 into the interrupt priority structure. If the power fail interrupt card resides in slot A115, jumper-wire W2 must be removed from the card. Refer to volume III for detailed information concerning this change.                                                                                                                                                                           |                                               |

|       |                             | <ol> <li>MODIFICATION KIT. Installation of the items supplied in the HP 12578A-01** Modification Kit completes the DMA modification requirements for the subject computers.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |

|       |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

Table 2-1. Field Installation Checklist (Continued)

| MODEL    | *SERIAL<br>NUMBER<br>PREFIX | MODIFICATIONS REQUIRED FOR INCORPORATION OF DMA OPTION                                                                                                                                                                                                                                                                                            | SERIAL NUMBER PREFIX AFTER MODIFICATION |

|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| HP 2116B | 823-<br>824-                | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computers to the 830- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>              | 830-                                    |

|          |                             | 2. INTERRUPT PRIORITY JUMPER. Jumper wire W2 on I/O control card 02116-6041, located in slot A201, must be removed when the DMA option is incorporated into the subject computers. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change. |                                         |

|          |                             | 3. MODIFICATION KIT. Installation of the items supplied in the HP 12578A Modification Kit completes the DMA modification for the subject computers.                                                                                                                                                                                               |                                         |

|          | 842-                        | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computer to the 844- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>               | 844-                                    |

|          |                             | 2. INTERRUPT PRIORITY JUMPER. Jumper-wire W2 on I/O control card 02116-6041, located in slot A201, must be removed when the DMA option is incorporated into the subject computer. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change.  |                                         |

|          |                             | <ol> <li>MODIFICATION KIT. Installation of the items supplied in the HP 12578A Modification Kit completes the DMA modification for the subject computer.</li> </ol>                                                                                                                                                                               |                                         |

|          | 846-                        | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computer to the 852- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>               | 852-                                    |

|          |                             | 2. INTERRUPT PRIORITY JUMPER. Jumper-wire W2 on I/O control card 02116-6041, located in slot A201, must be removed when the DMA option is incorporated into the subject computer. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change.  |                                         |

|          |                             | 3. MODIFICATION KIT. Installation of the items supplied in the HP 12578A Modification Kit completes the DMA modification for the subject computer.                                                                                                                                                                                                |                                         |

Table 2-1. Field Installation Checklist (Continued)

| MODEL    | *SERIAL<br>NUMBER<br>PREFIX   | MODIFICATIONS REQUIRED FOR INCORPORATION OF DMA OPTION                                                                                                                                                                                                                                                                                           | SERIAL NUMBER<br>PREFIX AFTER<br>MODIFICATION |

|----------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|          | 850-                          | <ol> <li>BACKPLANE. Backplane wiring modifications are<br/>required prior to installation and operation of the<br/>DMA option. These modifications update the subject<br/>computer to the 900- configuration. Consult the<br/>nearest Hewlett-Packard Sales and Service Office for<br/>assistance in making this change.</li> </ol>              | 900-                                          |

|          |                               | 2. INTERRUPT PRIORITY JUMPER. Jumper-wire W2 on I/O control card 02116-6041, located in slot A201, must be removed when the DMA option is incorporated into the subject computer. This change connects select codes 06 and 07 into the interrupt system priority structure. Refer to volume III for detailed information concerning this change. |                                               |

|          |                               | <ol> <li>MODIFICATION KIT. Installation of the items<br/>supplied in the HP 12578A Modification Kit com-<br/>pletes the DMA modification for the subject computer.</li> </ol>                                                                                                                                                                    | ·                                             |

|          | 845- and<br>842-<br>and above | <ol> <li>INTERRUPT PRIORITY JUMPER. Same as item 2 for the 850- configuration.</li> <li>MODIFICATION KIT. Same as item 3 for the 850-</li> </ol>                                                                                                                                                                                                 | No Change                                     |

|          |                               | configuration.                                                                                                                                                                                                                                                                                                                                   |                                               |

| HP 2116C | 980-<br>and above             | 1. INTERRUPT PRIORITY JUMPER. Same as item 2 for the HP 2116B 850- configuration.                                                                                                                                                                                                                                                                | No Change                                     |

|          |                               | 2. MODIFICATION KIT. Same as item 3 for the HP 2116B 850- configuration.                                                                                                                                                                                                                                                                         |                                               |

<sup>\*</sup> Refers to serial number prefixes assigned at time of manufacture or prefixes assigned as a result of field changes.

<sup>\*\*</sup> The HP 12578A-01 Modification Kit must be used with computers not equipped with direct memory logic card 02116-6044, revision B-821 or later, or direct memory logic card 02116-6069, revision J-905 or later. If the computer is already equipped with either of these cards, HP 12578A Modification Kit may be used.

<sup>\*\*\*</sup> Computers bearing serial number prefix 850- are used in 2000A System.

#### **SECTION III**

#### **PROGRAMMING**

#### 3-1. INTRODUCTION.

3-2. This section contains programming information for use with the DMA option, including program word formats and a typical DMA program.

#### 3-3. PROGRAM WORD FORMATS.

3-4. The DMA option is programmed using HP assembler language. The instruction, control, and data word formats used in the operation of DMA are shown in figure 3-1 and are defined below.

| IN | PUT | 100 | ITPL | 17 / | NS7 | RU | CTI  | ON   | WO | 70 |     |     |      |        |      |

|----|-----|-----|------|------|-----|----|------|------|----|----|-----|-----|------|--------|------|

| 15 | 14  | 13  | 12   | 11   | 10  | 9  | 8    | 7    | 6  | 5  | 4   | 3   | 2    | 1      | 0    |

|    |     | 10  | GRO  | )UP  |     | IN | ISTR | UCTK | ON | SE | ECT | COL | ES 2 | ,3,6 ( | )R 7 |

|   | <u>DM</u> | <u> </u> | ROC | GRA | M C | ON | TRO  | L   | VOR | 0 |   |      |      |      |      |    |

|---|-----------|----------|-----|-----|-----|----|------|-----|-----|---|---|------|------|------|------|----|

|   | 15        | 14       | 13  | 12  | 11  | 10 | 9    | 8   | 7   | 6 | 5 | 4    | 3    | 2    | 1    | 0  |

| 1 | STC       | SYTE     | CLC |     |     | NO | T US | SED |     |   | - | EVIC | E SI | ELEC | T CO | DE |

| 0 | STC       | WORD     | ac  |     |     |    |      |     |     |   | _ |      |      |      |      |    |

|    | DM        | A  | 100 | RES | 55 H | VOR | 0 |   |   |     |     |      |    |   |   |   |

|----|-----------|----|-----|-----|------|-----|---|---|---|-----|-----|------|----|---|---|---|

| i  | 15        | 14 | 13  | 12  | 11   | 10  | 9 | 8 | 7 | 6   | 5   | 4    | 3  | 2 | 1 | 0 |

| 10 | IN<br>OUT | P  | AGE | ADD | RESS | 3   |   |   |   | WOR | D A | DORE | SS |   |   |   |

| 01 | WA        | 1 8 | 10 | CK | LEA | VGT | H H | OR  | 0    |     |   |   |   |   |   |   |

|----|-----------|-----|----|----|-----|-----|-----|-----|------|-----|---|---|---|---|---|---|

| 1  | 5         | 14  | 13 | 12 | 11  | 10  | 9   | 8   | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|    | NO<br>USE |     |    |    |     |     |     | WOR | D CO | UNT |   |   |   |   |   |   |

| DA | 1TA | INP | UT | 100 | ITP | <u>UT</u> | WO     | 9 <i>0</i> |   |   |   |   |   |   |   |

|----|-----|-----|----|-----|-----|-----------|--------|------------|---|---|---|---|---|---|---|

| 15 | 14  | 13  | 12 | 11  | 10  | 9         | 8      | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|    |     |     |    |     |     |           | 16 - 1 | BITS       |   |   |   |   |   |   |   |

| CHA | 1RA   | CTE  | : R | INP  | UT  | 100 | UTP | UT | WO  | RD   |      |     |     |     |     |

|-----|-------|------|-----|------|-----|-----|-----|----|-----|------|------|-----|-----|-----|-----|

| 15  | 14    | 13   | 12  | 11   | 10  | 9   | 8   | 7  | 6   | 5    | 4    | 3   | 2   | 1   | 0   |