# TECHNICAL SPECIFICATIONS

for

RTE-IV

#### RTE-IV TECHNICAL SPECIFICATIONS

#### SECTIONS

I DISPATCHER

II RTIOC

III EXECUTIVE/MEMORY ALLOCATION

IV SCHEDULAR

V PARITY ERROR

VI SYSTEM LIBRARY

VII EMA FIRMWARE

VIII CONFIGURATOR (CURRENTLY UNAVAILABLE)

IX GENERATOR

X SWTCH (CURRENTLY UNAVAILABLE)

XI LOADR (CURRENTLY UNAVAILABLE)

XII MULTI-TERMINAL MONITOR

XIII ASSEMBLER

TECHNICAL SPECIFICATIONS

FOR

DSP4 - RTE IV DISPATCHER

EJW January 23, 1978 Project 1106

#### TABLE OF CONTENTS

- 1.0 General Overview of Operation

- 2.0 External Communication

- 2.1 System Tables Referenced

- 2.1.1 ID Segment

- 2.1.2 Memory Protect Fence Table

- 2.1.3 Memory Allocation Table

- 2.2 System Base Page Communication

- 2.3 Dispatcher Entry Points

- 2.4 Dispatcher's External Tables and Pointers

- 3.0 Detailed Technical Aspects of Operations

- 3.1 Initialization

- 3.2 Dispatching

- 3.2.1 Memory Resident Programs

- 3.2.2 Disc Resident Programs

- 3.2.3 Disc Resident Map Setup

- 3.3 Swapping

- 3.4 Mother Partition Usage

- 3.5 Clean Up

- FIG. 1 RTE IV ID Segment

- FIG. 2 RTE IV Memory Protect Fence Table

- FIG. 3 RTE IV Memory Allocation Table

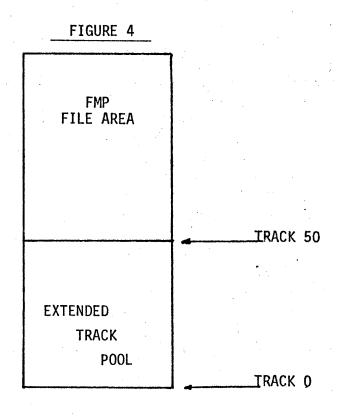

- FIG. 4 RTE IV Memory Allocation Table Entry

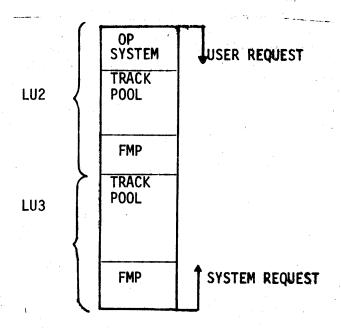

- FIG. 5 RTE IV Mother Partitions

- FIG. 6 RTE IV Dispatcher's Allocated Partition Lists

- FIG. 7 RTE IV User Base Page

# 1.0 GENERAL OVERVIEW OF OPERATION

The Dispatcher module's main function is to control program execution by switching CPU control to the highest priority program in the scheduled list if it is ready to run. The Dispatcher serves as the return point from the operating system back to the user. If there are no programs scheduled, the Dispatcher prepares for execution of the idle loop under the user map and waits for an interrupt to occur. An interrupt is generated by an I/O device, a user program request, or an error condition signal which requires entry into the operating system for a response. The Dispatcher turns control over for program execution until the next interrupt.

In the process of turning control to a user program, the Dispatcher needs to perform a number of smaller tasks. Once it is determined that a program should be executed, the Dispatcher needs to check whether or not the program is present in memory. If the program is not already in memory then it needs to be loaded from the disc. The Dispatcher is responsible for finding an empty partition of the proper type and size, if one was not previously specified. If there are no free partitions, it would be necessary to swap out a dormant program or a lower priority executing program to make the partition available for the load. Then finally the user map and memory protect fence are set up before executing the program.

Other functions of the Dispatcher are to set up the partition list aders at initialization of the operating system and to coordinate e cleaning up of a program's resources and system available memory when a program is aborted.

#### 2.0 EXTERNAL COMMUNICATION

The Dispatcher communicates with the rest of the operating system through the system tables, base page communication area, and suproutine calls to/from the rest of the system. There are no direct paths of communication between the Dispatcher and any user program because there are no functions in the Dispatcher which would be useful to a calling program.

#### 2.1 System Tables Referenced

#### 2.1.1 ID Segment (Figure 1)

An ID segment is used for many things by the Dispatcher. Each ID segment is linked into the scheduled list by word 0. The priority, type, and status are checked to determine whether or not the program may execute. The memory protect fence table index (MPFI) and number of pages are set into word 21 by the system generator or by the relocating loader. The number of pages (which does not include a base page) is the number of pages actually occupied by a program and its largest segment (if any) or the override size specified by the user. The size of an EMA program includes the mapping segment size (still excludes the base page).

The program address bounds in words 22-25 are used by the Dispatcher for loading the program into memory. The program's disc address is in word 26. If the program is swapped cut, the Dispatcher keeps the address of the swap tracks in word 27.

IO Segment word 28 is used by the Dispatcher to determine whether or not a program is using an extended memory area (EMA). If this word is zero, no EMA is used. If the word is non-zero, the ID Extension is checked to see if the default EMA size was chosen. If it was not defaulted then the program size (from word 21) minus the MSEG size is added to the EMA size plus base page to determine the partition size required. If the EMA size was defaulted, the largest Mother partition size, \$MCHN, is used as the partition size required (see Section 3.2.2).

#### 2.1.2 Memory Protect Fence Table (Figure 2)

The Memory Protect Fence table (\$MPFT) a table of addresses used by the Dispatcher to set the correct value for the memory protect fence. This address is stored in the base page word FENCE (1775). Bits 7-9 of word 21 in the ID Segment contain the index into this table.

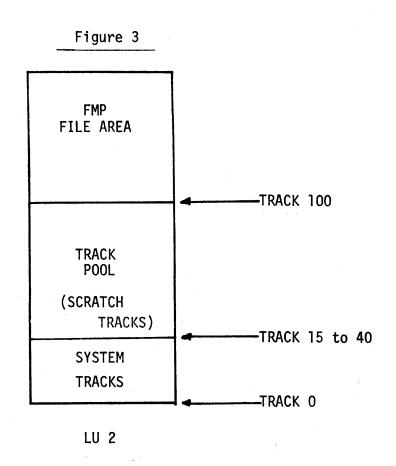

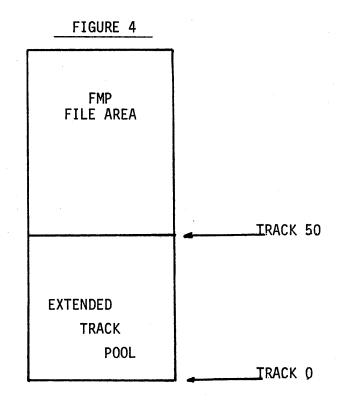

# 2.1.3 Memory Allocation Table (Figure 3)

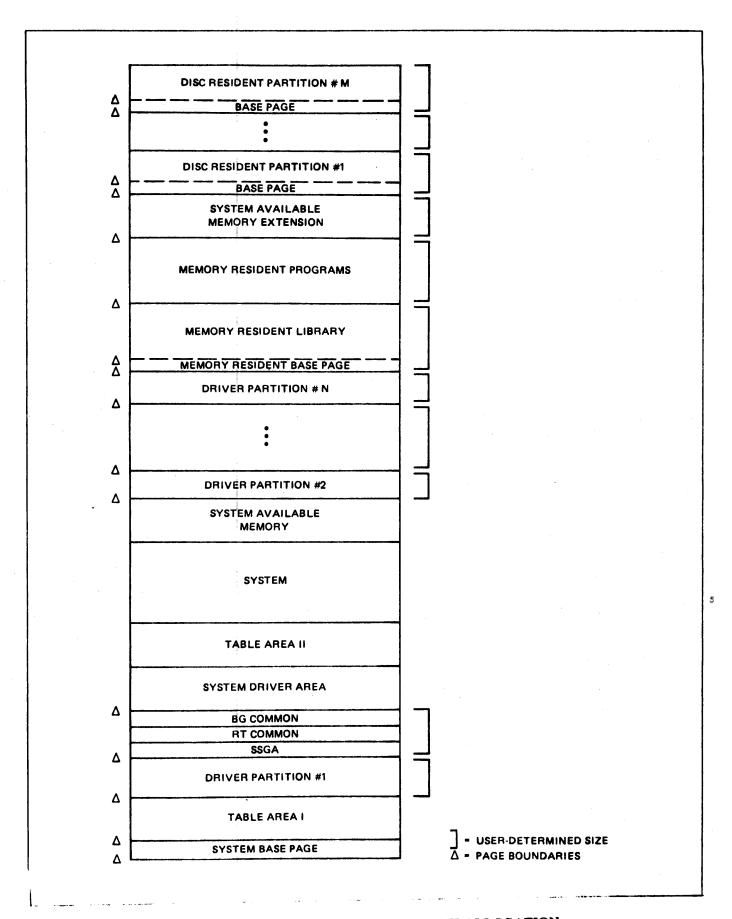

Each partition defined by the user at generation time will have an entry in the Memory Allocation Table. The table starts at the entry point \$MATA and extends upwards toward high memory. The word \$MNP contains the total number of partitions (set by the generator). Each partition entry (see Figure 4) is 7 words long. The MAT Link word contains -1 if the partition is undefined.

There are 3 different types of partitions:

- 1. Real Time Partitions headed by \$RTFR at system start-up.

- 2. Background Partitions headed by \$BGFR at system start-up.

- 3. Mother Partitions headed by SCFR at system start-up.

These 3 lists are set up by the Generator in order of increasing size. The primary purpose for having RT partitions and BG partitions is to keep the two classes of programs, RT and BG, from contending with each other for memory. There are no differences in the two classes of partitions. Mother Partitions are primarily for EMA programs.

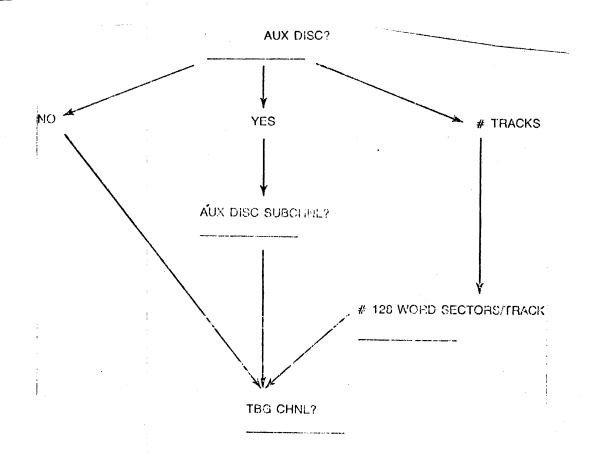

Mother partitions are defined during generation by a "YES" answer to the prompt "SUBFARTITIONS?" when a partition is larger than the maximum addressable space. Although Mother partitions are in a separate list, subpartitions may be linked into either a ther partition (see Figure 5) or linked into a BG or RT ither free or allocated) list. When the subpartitions are part of a Mother partition, the Mother partition's MAT entry word 6 (Subpartition Link Word - SLW) will point to the Link Word (word 0) of the first subpartition whose SLW will point to the link word of the second subpartition and so on. The SLW of the last subpartition will point to the Link Word of the Mother. If no subpartitions were actually defined but the prompt for subpartitions was answered "YES" then the SLW of the Mother partition will point to the Link Word of the same MAT entry.

When a Mother partition is in use, the entire chain of subpartitions is in use and this is indicated by the C bit being set. In this case, all partition status information is kept in the Mother partition MAT entry; i.e.; priority, ID segment address, and Read Completion flag. In addition, the chained partitions are treated as a single entity whil; e the C bit is set. Individual subpartitions are not swappable in this case - the whole Mother partition may be swapped if needed.

The Dispatcher checks for empty partition lists at start-up (see Section 3.1). It there are no Real Time partitions then the header of the RT partitions list will point to the Background partitions. If there are no BG partitions then the RT partitions are used in the BG list. If there are no Mother partitions EG partitions are used unless there are no BG partitions, in which case the RT partitions are used.

The sizes of the largest partition of each type are kept in 3 words:

- 1. \$MPTP size of the largest non-reserved RT partition.

- 2. \$MBGP size of the largest non-reserved BG partition.

- 3. &MCHN size of the largest non-reserved Mother partition.

- 2.2 System Base Page Communication

| * | XIDEX | 1645      | ID EXT addr of current prog or 0              |

|---|-------|-----------|-----------------------------------------------|

| * | ATAMX | 1646      | MAT address of current program or 0           |

| * | XI    | 1647      | Pointer to current program's X-Y save area    |

| * | SKEDD | 1711      | Head of scheduled list                        |

| * | XEQT  | 1717-1733 | Current program's ID Segment pointers         |

|   | SWAP  | 1736      | Swap delay in bits 8-15                       |

|   | BPA2  | 1743      | Last word user base page (add 1 for BP fence) |

|   | LBORG | 1745      | Logical address of Resident Library           |

| * | RTDRA | 1750      | Dynamically set address                       |

| * | AVMEM | 1751      | bounds for partition                          |

| * | BGDRA | 1754      | resident programs                             |

| * | TATLG | 1755      | Dispatcher locks disc tracks for FMGR         |

|   | TATSD | 1756      | #Tracks system disc                           |

|   | SECT2 | 1757      | #Sectors LU2                                  |

|   | SECT3 | 1760      | #Sectors LU3                                  |

| * | FENCE | 1775      | Memory Frotect Fence value for user           |

| * | BGLWA | 1777      | Dynamically set bound                         |

<sup>\*</sup> Set or changed by the Dispatcher.

## 3 Dispatcher Entry Points

ŞALDM

Subroutine, used by SCHEDULER to unlink a partition's MAT entry from the allocated list into the dormant list.

The calling sequence:

<A-reg> has ID Segment Address

JSE \$ALDM

\$BRED

Subroutine, used by SCHEDULER to read in program segments.

The calling sequence:

<B-reg> has ID Segment Address

JSE \$BRED

\$DMAL

Subroutine, used by SCHEDULER to unlink a partition's MAT entry from the dormant list into the allocated list.

The calling sequence:

<A-reg> has ID Segment Address

JSB \$DMAL

MAXP

Subroutine, called by the routine \$PERR when a partition is undefined or by the SCHEDULFR when a partition's "reserved" status is changed by the RS command. This subroutine searches the MAT to determine the values of \$MBGP, \$MRTF and \$MCHN by scanning each MAT entry for the largest partition of the specified type and update the appropriate word. \$MAXP may have to update more than one (and maybe all) if the size words if any of the partition lists were initially empty. This is necessary because the DISPATCHER would have changed the list pointers of the empty list(s) to point to a non-empty list.

The calling Sequence:

JSB \$MAXP <return> SPRCN Subroutine, called by DISPATCHER and SCHEDULER to relink a partition in the allocated list by priority.

Calling sequence:

<A-reg> has ID Segment Address

<B-reg> has new priority

JSE \$PRCN

\$RENT Entry point, JMP there from the DISPATCHER and EXEC for setting up the Resident Library address in the memory protect fence.

\$SMAP Subroutine, called by DISPATCHER and RTIOC to set up the user map. Unused pages are write-protected.

Calling sequence:

<A-reg> has length of program to map in pages <B-reg> has MAT entry address

JSE \$SMAP

Subroutine, called by SPERR to unlink partition MATA entries and undefine the partition where a parity error is detected in it.

Calling sequence:

<E-reg> has MATA address of partition

JSB \$UNPE

\$XCQ Entry point, actual entry for \$XEQ where the main dispatching algorithm is performed.

Subroutine, called by non-privileged drives to set up user map.

Calling sequence:

<A-reg> has ID Segment Addr

JSB \$XDMP (Entry via Table Area II entry point)

\$ZZZZ Entry point, used by DISPATCHER and SCHEDULER as the head of the program about list. This entry point is used as a subroutine during the start-up sequence.

# 1 4 Dispatcher's External Tables and Pointers

All of these entry points are located in Table Area 2 unless otherwise specified.

\$BGFR Pointer, BG free list initialized by the Generator.

SCFR Pointer, free list header of Mother partitions, initialized by Generator.

\$CMST Value, start page number of COMMON area, set up by the Generator.

\$EMRP Address, last word of memory resident program area, set by the Generator.

Value, number of pages occupied by the system, its base page. Both table areas, System Driver Area, driver partition area, Common, and the first 2K of System Available Memory. This word is initialized by the Generator.

\$IDEX Pointer, ID Extension list.

## 3.0 DETAILED TECHNICAL ASPECTS OF OPERATION

This portion of the Technical Specifications is a detailed description of major portions of the DISPATCHER code as outlined in the general overview (Section 1.0). It is assumed that the reader has a good general understanding of the RIE operating system.

#### 3.1 Initialization

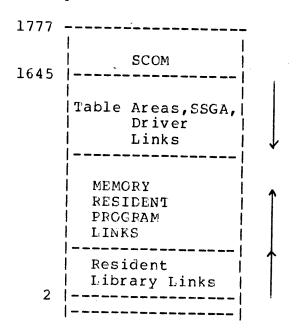

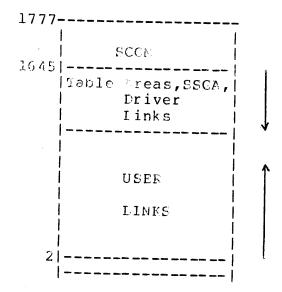

\$ZZZZ serves as the entry point of the initialization subroutine which is executed only once during system initialization. The routine first sets up the starting address of SSGA in \$SGAF for the LXEC. Then \$ZZZZ loads the user map with the memory resident map registers which were built by the Generator in MRMP. Whenever a memory resident program is dispatched, MRMP is used to set up the user map.

Next, the \$ZZZZ routine will set the base page fence so that all addresses between 16XX and 1777 are not mapped. The fence value minus one is contained in base page location BP2 (1743) which is the address of the last available user link.

A number of system dependent address and sizes are calculated and saved so that they may be reused by the DISPATCHER without being recalculated each tim Some of these "constants" include the address of the memory resident library, the number of pages in the memory resident library, the starting register number and the number of registers to be used for mapping chunks of EMA to be swapped.

The partition free lists are also checked by the Dispatcher during the initialization of the system. If the BG free list neader (\$BGFR) is zero, meaning that it is empty, then the RT free list pointer (\$RTFR) is stored into \$BGFR. If there were no RT partitions then the RT free list pointer will be set equal \$BGFR. The maximum unreserved partition size words, \$MRTP and \$MBGP, will be updated accordingly. If the Mother partition list is empty the \$BGFF pointer will be used, assuming that the BG list is not empty since we've already done the check above. \$MCHN will also be updated. However, if it turns out that the BG list is empty because the RT list was empty, then with all three lists empty the \$CHEDULER will report an error on any scheduling attempts. This code is in subroutine LSTIN which is also called by \$MAXP.

The last thing done during initialization is the scheduling of the File Manager program, FMGR. The Dispatcher first locks all of the disc tracks by saving the number of tracks word (TATLG) in the FMGR's first parameter word and then replacing TATLG with -1.

e DISPATCHER'S initialization code is overlayed by the disc triplets which are built for doing program loads and swaps.

#### 3.2 Dispatching

\$XCQ (user map entry point, \$XEQ) is the entry point into the DISPATCHER code which performs the allocation of execution time to programs. The primary objective of \$XCQ is to execute the highest priority program in the scheduled list, SKEDD, if possible.

First the DISPATCHER checks to see if there are any programs which were aborted (see Section 3.5). If no programs were aborted, then the DISPATCHER checks the scheduled list. If there are no programs in the scheduled list, or for some reason the programs in the list can't be executed at this time, the "iale loop" is executed instead of a user program. The base page point-of-suspension word, XSUSP, is set to the idle loop code address and the base page register save area pointers (XA, XE, XEO and XI) are set up to use a two-word dummy save area. The idle loop code (\$IDLE) and dummy save area are located in Table Area I so the user map may be used. The base page word XEQT is cleared to indicate that no program is executing, the memory protect fence register is set to zero and stored in FENCE on base page. Then it exits the system via \$IRT to enable memory protect, the interrupt system and the user map.

If there are programs to be scheduled in the SKEDD list, the DISPATCHER makes the decision to execute a program based on the program's priority, status, type, and address space needs.

If the currently executing program is of equal or higher priority then the program in the scheduled list, execution of the current program is resumed. If the program in the scheduled list is higher, a check is made to see if the program is in memory and if it can be executed. If it can be executed the user map registers are set up with the program's physical page numbers. The program's logical address bounds are set up in RTDRA, AVMEM, BKLRA and BKLWA. The ID Segment pointers are set up in base page at XEQT. The X and Y registers save area address is also set up at XI.

Now that the program is ready to execute, the address of where to begin or resume execution is determined. If the point of suspension address is zero, control is given to the program at the primary entry point. If the point of suspension is non-zero, control is returned to that address. The memory protect fence is set up according to the Memory Protect Fence Table index in the ID Segment. Then control is turned over to the program by exiting through SIRT which enables memory protect, enables the interrupt system, and enables the user map.

The general dispatching procedure described above is slightly ferent for different types of programs.

#### 3.2.1 Memory Resident Programs

If the scheduled program is a Memory Resident Program, the memory protect fence may be set differently since these programs are the only type which may reference the Resident Library. The Dispatcher will clear the Write Protect bit from the Resident Library pages in the Memory Resident Map by clearing the sign bit from those words when the User Map is being set up. All the other registers would remain the same as in the Memory Resident Map Table (\$MRMP) which is never changed. Then the memory protect fence is set at LBORG if the reentrant bit is set in the ID Segment. This code has an entry point of \$RENT for access by the EXEC.

#### 3.2.2 Disc Resident Programs

If the scheduled program is a disc resident program, it needs to be loaded from the disc into a partition which was allocated for it. If a partition was pre-assigned at relocation time, that MAT entry will be checked to see if it is available or if its resident program is swappable. If either case is true, the MAT entry will be set up for the new program and will be linked into the allocated list of the pertinent type. The MAT try will not be modified or relinked if its current resident the program which RTE is trying to dispatch.

If a partition was not specified at load time, the MAT entry for the partition in which the program was last resident will be checked to see if the program is still resident. The MAT entry is first checked to see if the partition still exists. The partition may be undefined if a parity error was detected in one of its pages since the program was last resident there. If the partition still exists and the program was the last occupant in there, the partition is set up to be used and the program is dispatched there after the user map is built (see Section 3.2.3).

If the program is no longer resident in the partition or the partition became undefined, a default partition list will be scanned for a free partition. The default partition types are:

- a. RT program (Type 2) RT partition (\$RTFR)

- b. BG program (Type 4) BG partition (\$BGFR)

- Privileged program (Type 3) BG partition (\$BGFR)

- d. EMA program Mother partition (\$CFR)

For RT, BG and privileged programs, the appropriate free list will be scanned for the smallest free partition in which the program can fit. EMA programs which have a specific EMA size declared will get the smallest free Mother partition. But, EMA programs which let the EMA size default will take on the maximum Mother partition size (\$MCHN). This size minus the program code size is then put into word 29 of the IO segment to prevent the problem where a swapped cut program may be reloaded into a smaller partition if \$MCHN was changed because of a parity error on the partition or it became reserved.

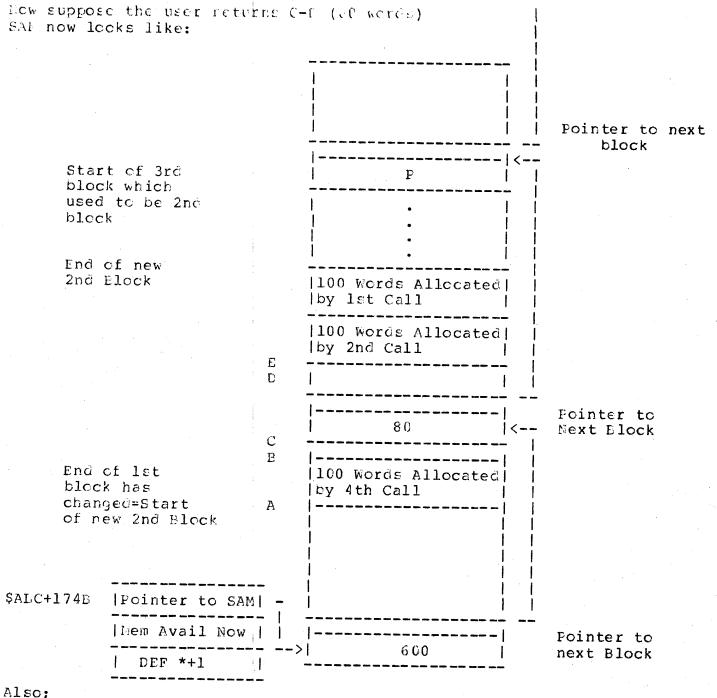

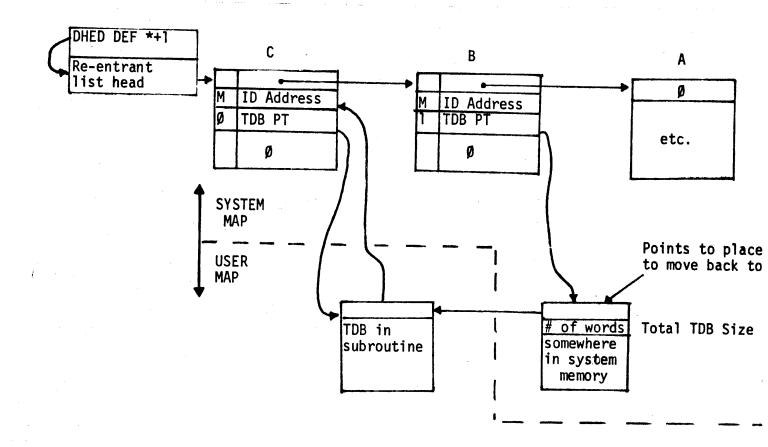

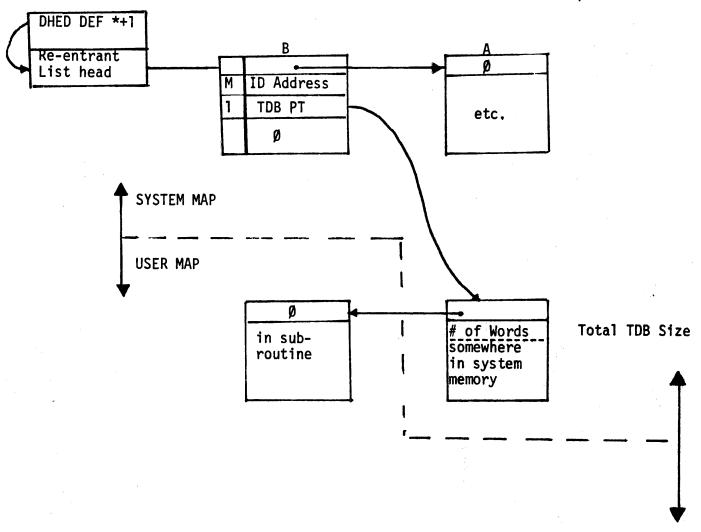

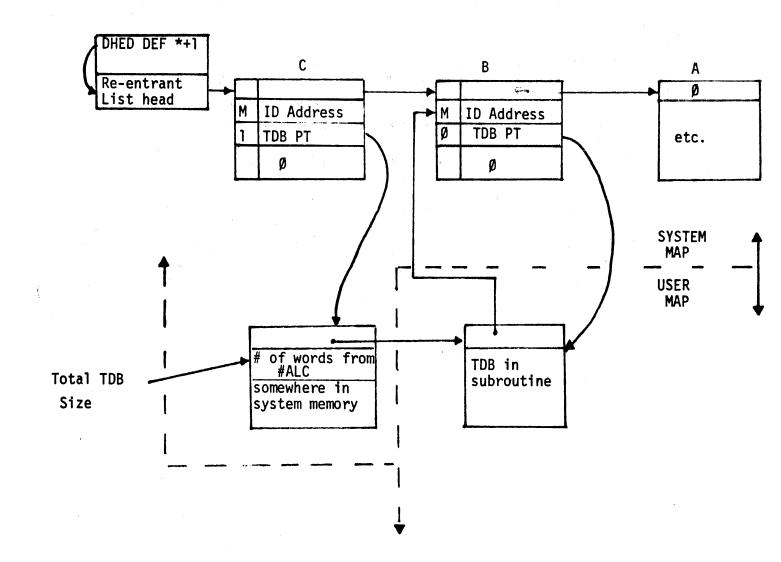

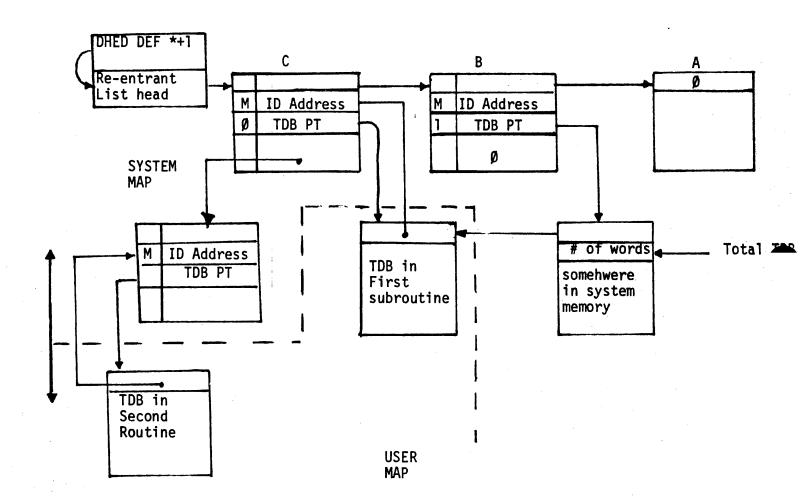

If a free partition is not available, the appropriate dormant list (RTDM, BCDM or CDM) will be scanned for a partition with a swappable program. The dormant lists are a subset of the allocated lists (see Figure 6). The last entry in the dormant list points to the allocated list so if the dormant list is empty, the dormant list just points to the allocated list.

Upon finding a suitable partition, the occupant will be swapped out. The MAT entry will be reset and relinked, and prepared for loading of the disc resident program. If no dormant partition qualifies for the swap, the allocated list (RTPR, BGPR or CPR) will be scanned for the lowest priority program which can be swapped. The same procedure described for the dormant swap will be followed.

### 3.2.3 Disc Resident Map Set Up

Once a partition is allocated for a program, the user map is set up for the program. If the program is being scheduled initially (program's first dispatch) the User Map registers must be loaded by the DISPATCHER and a copy of it saved in the user's protected portion of base page (see Figure 7). If the program is being re-dispatched, to continue after being suspended or after being "bumped" by a higher priority program, the User Map registers are set up by copying them from the saved copy in the protected portion of the user's base page.

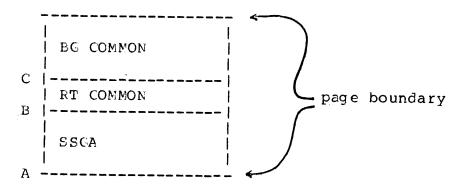

A program's first dispatch is identified by the fact that the point of suspension word (XSUSP) is 0 in the program's ID Segment. The base page register (logical page 0) is loaded with the page value in word 3 of the MAT entry. The next registers are then loaded sequentially with numbers starting at one end incremented by one in each successive register. The number of registers set in this manner depends on the program type or whether or not the program uses COMMON.

of registers set sequentially is determined by one less than the value of \$SDA added to \$SDT2. Actually the number of registers mapped is one less than \$SDA. The next registers mapped (number of registers is determined by \$SDT2) have the write-protect bit set. This maps into the User Map: Table Area 1, the Driver Partition Area, CCMMON (including SSGA), write-protected System Driver Area and write-protected Table Area 2.

If the program is not type 3, the Memory Protect Fence Table Index (in the ID Segment) is checked to see if the program uses any COMMON or SSGA. If COMMON or SSGA is used, the number of registers set up following the base page register is determined by one less than the value in SCMST. If COMMON or SSGA is needed, the value \$SDA -1 is the number of registers to map in Table Area 1, the Driver Partition Area, and COMMON. The user program is mapped in the registers following these registers pointing to the system areas.

The next registers are loaded with the next physical page numbers sequentially following the page used for the user base page. These are loaded into the map registers until the number of registers specified in word 21 of the ID Segment have been set up. The non-standard MSEG bit (bit 15 of word 0 in the ID Segment extension) is set if the program is an EMA program to force the EMA subroutines to remap.

to insure that a program cannot access memory outside of its partition. This mapping is done in \$SMAP which is the only code which loads the user map to describe a specific program. It is also called by RTIOC.

A copy of the user map is saved in the last 32 words of the user's physical base page (see Figure 7). The system's map register for the driver partition (\$DVPT) is used to map in the user's base page. This portion of the base page is not used during the program's execution since the system communication area is always mapped in on the top portion of the user base page.

with all of the above done the program is ready for dispatch.

#### 3.3 Swapping

A program is swapped out of memory to make a partition available for another program to run. The first programs chosen to be swapped are the ones in the dormant list. These programs are the ones which have terminated with either the save resources or serially reusable option. Otherwise, programs with the lowest priority will be checked for swappability.

Programs are not swappable if any of the following are true:

- 1. A memory lock is in effect.

- 2. If has a higher priority than the program to be scheduled.

- 3. It is dormant but is higher priority and is in the time list to be scheduled in less than the minimum permissible amount of time specified in SWAP.

- 4. It is I/O suspended with the buffer in the program area.

When a swap is required, the necessary number of tracks needed to swap the program out are computed and a request is made to \$DREQ for the contiguous disc tracks. The number of tracks is computed by rounding up the number of sectors (to next even sector) needed for the base page and rounding up the number of sectors (to the next even sector) needed for the Main Code. The number of sectors is then converted to tracks and it is then rounded up to the end of a full track. If tracks are not currently available, swapping cannot take place and the DISPATCHER proceeds to check the next program in the scheduled list (if any). If tracks are available, the necessary \$XSIO parameters are computed.

SETUP is the subroutine which creates the parameters for the \$XSIO disc calls. SETUP guarantees that all calls to read or write disc tracks are broken down into groups of smaller I/O requests. Each one of these smaller groups of 3 words each (triplets) define an I/O request which will not cross a track boundary. The triplets have (1) starting memory address of the piece of data, (2) the number of words to transfer, and (3) the starting track and sector address. These triplets are built in memory overlaying the DISPATCHER'S initialization code (code following \$ZZZZ). There may be up to seven triplets for a \$XSIO call (enough for a 32K transfer with 6K words per track). The triplets are terminated by a zero.

There are five separate \$XSIO calls, one for each type load/swap I/O so that each call can be started independently and overlap in time. Disc accesses for each type of partition can be completed at different times depending on their sizes. For each of these calls, there are triplets tables. The following table shows the names used by DISPATCHER.

| Type of  <br>  \$XSIO CALL<br> | Code  <br>Busy  <br>Flag                      | Triplets<br>Area<br>Terminator | <br>  Triplets<br>  Terminator<br>  Address | <br>  Triplets<br>  Area<br>  Pointer |

|--------------------------------|-----------------------------------------------|--------------------------------|---------------------------------------------|---------------------------------------|

| RT BG Mother EMA Segment       | RTSWP <br>BGSWP <br>CHSWP <br>CHSW2 <br>SGSWP |                                |                                             | RTRP BTRP CTRP CTRP2 STRP             |

When a swap out is completed, the disc logical unit track address and number of tracks are stored in the ID Segment (word 27, SMAN).

when a program is loaded (or swapped back) into memory, \$XSIO is called using parameters computed by SETUP. ID Segment value DMAN (word 26) is used for the disc address if the program is not swapped out; and SMAN if the program is swapped out. The program's dispatching status in word 5 cf the MAT entry is cleared to indicate that a program read is in progress. The program's status is changed to I/O suspend via \$LIST. When the read is complete, any swap tracks are released via \$DREL and the program is scheduled via \$LIST. A check is made to see if the read was correct. If not, the program is aborted via \$ABRT which sets it dormant, releases its tracks, and removes it from the time list. If the read was correct, the dispatching status is set to one to indicate program is read in. The program is ready to execute.

When an EMA program needs to be swapped, the swap out to the disc is done in two parts. The program's code up to the page where the mapping segment starts (MSEG) and the program's base page are swapped out first using the CHSWP \$XSIO call. The number of swap tracks needed is computed by adding the number of integral tracks needed for the program code and base page to the number of integral tracks needed for the EMA area. The program is swapped just like any other disc resident program. Note that in the ID Segment word 27, the number of tracks refer to just those used for the program code.

The EMA area is swapped cut next, beginning at the next even sector boundary following the program code's swap tracks. EMA is swapped out in large chunks equal in size to the maximum logical address space in the user map (up to a maximum of 28K words). The User Map registers from \$CMST to the end of the the map, inclusive, define the number of pages in each chunk. The chunk is mapped in the User Map, the triplets are built and then the chunk is swapped out using the CHSW2 \$XSIO call. When the transfer is completed, the next chunk is mapped and swapped. This process repeats until all of the EMA is swapped. A similar process takes place when swapping into memory.

The computation for the number of swap tracks needed must allow an extra sector for each chunk. The number of tracks for the EMA area is saved in word 2 of the program's ID Segment Extension. The number of tracks is needed so that the correct number of tracks can be released when the program terminates or gets aborted.

When a program is swapped out, the program's map is used. program is mapped in, it is necessary for the map to be rebuilt according to the information in the ID segment rather than using a copy of the user map in the protected portion of base page (because it is swapped out on the disc). Programs which do their own mapping must lock itself in memory. Because these programs can't be swapped back with the altered map registers. programs which have been swapped back into memory will have the MSEG registers recalculated and remapped because the program may have been swapped back into a different mother partition (and therefore different physical page numbers). This calculation is performed by determining the number of pages offset from the beginning of the EMA and using the same offset in the new EMA. The physical page number of the first page in the currently mapped MSEG is saved temporarily in the ID segment extension in place of the current MSEG number during the time the program is swapped out. When the program is swapped back into memory, the MSEG pages are remapped after calculating the offset into the new partition. remaining pages remaining in the MSEG which are past the end of the EMA are read-write protected. If no MSEG was mapped at the time of the swap out, the MSEG pages will all be read-write protected when the program is swapped back into memory.

## 3.4 Mother Partition Usage

If a program (any type) is assigned to a Mother partition or an ENA program defaults to any Mother partition, there is more handling involved than is the case with RT or BG partitions. If a Mother partition is used when it is in the free list (\$CFR), each subpartition must be checked. If a subpartition is either free or is occupied by a swappable program the C bit is set in word 4 of the MAT entry to prevent the subpartition from getting used while the Dispatcher continues to check each subpartition. If all of the subpartitions are either free or swappable, a second pass is made on all of the subpartitions to perform the necessary swaps. The subpartitions are unlinked from any lists they might be in. When all of the subpartitions are free, the Mother partition is unlinked from the free list (\$CFR) and linked into the allocated list. The program can then be loaded into the Mother partition.

If any one of the subpartitions has a memory-locked program or a program which is doing I/O in it's own program space the subpartition can't be made available by swapping. All of the C bits must be cleared from each one of the previously scanned subpartitions and the dispatch is terminated. The next program in the scheduled list is examined.

When a program terminates and it was using a Mother partition, the Mother partition is relinked in the free list. All of the subparetitions are linked into the free list of the appropriate type (BG or RT).

When the C-bits are set on the subpartitions (set in chained mode), programs which are assigned to these subpartition will have to wait if the DISPATCHER is still in the process of swapping out any subpartitions. If a program is already in the Mother Partition the normal swappability checks apply.

In the case where a program of lower priority was in the process of loading a Mother Partition and a scheduled program is assigned to a subpartition the loading process is aborted. Then the subpartitions are released from chained mode and relinked into the proper free list. A special check is made (at SMAET) when a Mother Partition load needs to be aborted to free up a specific subpartition. If the partition type is BG and the BGSWP call is busy, the abort is not performed. If the type if RT and the RTSWP is busy, the abort also does not take place. This check prevents a deadlock which could keep the interrupt system off and the busy RT or BG call would not be able to complete. When it is necessary to clear out all the subpartitions for a Mother Partition the CHSWP call is used so that regular RT/BG partitions may continue to be used for other programs.

When a RT or BG program is scheduled and it is not assigned to a partition, a search is made for a partition of the same type which is large enough. If none can be found in the free list, none in the dormant list, and none can be found in the allocated list or it contains non-swappable programs, then the dormant Mother partition list will be searched for one which has a subpartition of the correct type and size. If a suitable subpartition can be found, the dormant program in the Mother partition will be swappe out.

#### 3.5 Glear Up

whenever a program is terminated, either by an EXIC call 6 or aborted by the system because of an error, the program is put into the dormant state and the list processor adds the program's ID Segment into a list headed by \$2222. The linking is through word 8 of the ID Segment (the point of suspension save area) since the program will begin execution at the primary entry point if it is rescheduled. Everytime the system goes to \$XEQ, \$2222 is checked. If it is non-zero the DISPATCHER performs five major clean up tasks.

First, if the program is disc resident, any swap tracks it may have are released. This may happen if a program is aborted while it is swapped out. When tracks are released by \$DREL in the EXEC module it will also call the list processor at \$LIST to reschedule any programs waiting for disc tracks. If the program was an EMA program, it will be necessary to call \$DREL twice; once for the program swap tracks, and once for the EMA swap tracks.

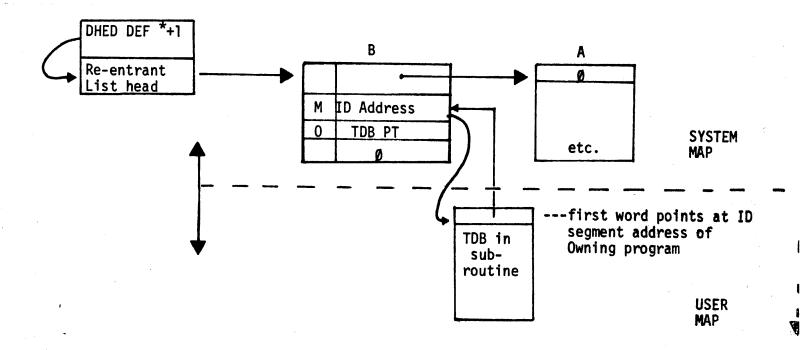

Second, \$ABRE in the \$EXECUTIVE is called to return any reentrant memory the program may have. This may happen if a program terminates or is aborted while in a reentrant subroutine. If \$ABRE returns any memory programs waiting for memory will be reshceduled.

Third, the DISPATCHER calls SWATE in the SCHEDULER to reschedule any programs which were waiting to schedule (EXEC 23,24) this program.

Fourth, the DISPATCHER calls \$TRRN which calls \$ULLU to unlock any LUs which may have been locked by the program. \$TRRN also unlocks any locally locked RNs and deallocates any locally allocated RNs the program may have. Each of these processes may call \$SCD3 to reschedule any programs waiting for these resources.

Fifth and last, if the program is a disc resident program and it is still resident in the partition, the partition is linked into the free list.

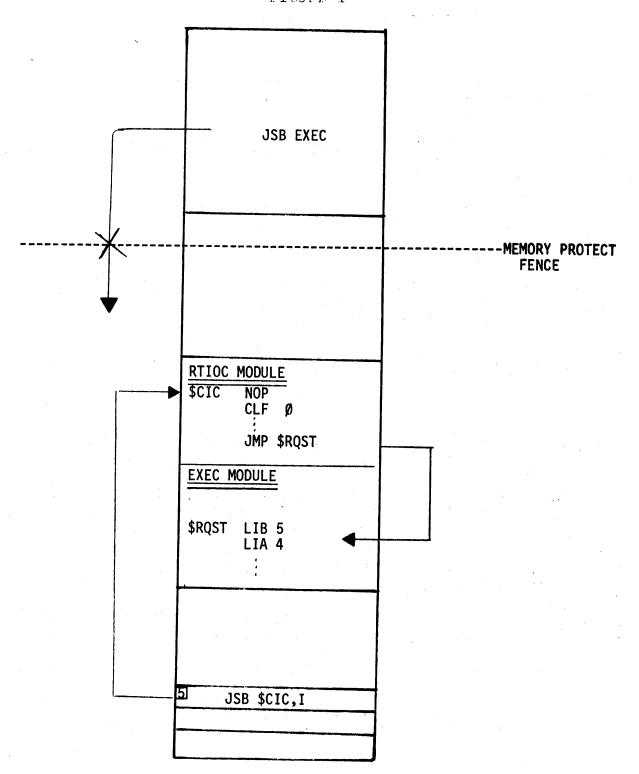

# TECHNICAL SPECIFICATIONS FOR RTE-IV RTIOC

EJW 1/12/78 Project #1106

## 1.0 CENERAL OVERVIEW OF CERRATION

The RTICC module controls all aspects of the system's input and output operations. It serves as the centralized I/C interrupt handler which identifies the source of an interrupt and turns control over to the appropriate processor. All I/O requests are made to this module either by EXIC calls from user programs or by \$XSIO calls from the other parts of the operating system. The I/O requests are passed directly to the appropriate device driver if the driver is available. The I/O module also queues I/O requests for busy drivers or for buffered requests. All the necessary mapping and base page communication area words needed to perform I/O will be done by RTIOC. Upon completion of I/O, the next request (if any) is started and control is returned to any waiting programs. RTIOC also detects and reports errors at various phases of the process and performs any necessary clean-up.

#### 2.0 EXTERNAL COMMUNICATION

RTIOC communicates to the rest of the operating system through table structures, the system's base page communication area, and by sub-routines available only to the system modules.

- 2.1 Tables Used by RTICC

- 2.1.1 Equipment Table (Figure 1,2)

Each I/O controller and device controlled by the IOC/driver relationship is defined by static and dynamic information in the Equipment Table. Each EQT entry is composed of 15 words. If there is an EQT extension, the address of the extension is in EQT word 13 and the size of the extension is in EQT word 12. This table is built by the Generator.

## 2.1.2 Interrupt Table (Figure 3)

A table, ordered by hardware interrupt priority, designates the associated software processor and the procedure for initiating the processor. This table is constructed by the System Generator on information supplied by the user in configuring the system. The table consists of one entry per interrupt source—each entry contains only one word. The contents of each valid entry is the identifier of the processor. System processors are noted by positive values, user processors by negative values, and a zero denotes an unused entry.

## 2.1.3 Device Reference Table (Figures 4,5)

The Device Reference Table provides the user for logical addressing of physical units defined in the Equipment Table. "DRT" consists of two-word entries corresponding to the range of user-specified "logical units," I to n where n is less than or equal to 63 (decimal). All word I's are in one table followed immediately by a second table containing all DRT word 2's. The contents of DRT word I for a given logical unit is the relative position of the EQT entry defining the assigned physical unit, in bits 0-5, and the subchannel of the EQT entry to be referenced by this logical unit number, in bits 11-15. The LU lock flag (the resource number being used for the lock) is in bits 6-10. An unassigned unit contains entry value of zero.

DRT word 2 contains a flag (bit 15) indicating whether a device (lu) is up or down (0/1). If a device is down, then all I/O associated with the device is stacked on the major LU (first LU for this device in the DRT) in bits 0-14 of DRT word 2. If the downed LU is not the major LU, then bits 0-14 of DRT word 2 will contain the LU number of the device's major LU.

Contain logical unit numbers are permanently assigned to racilitate system, user and system support I/C operations. These are:

0 - Bit Bucket

1 - System Teletypewriter

2 - System Disc

3 - Auxiliary Disc

4 - "Standard" Cutput Unit

5 - "Standard" Input Unit

6 - "Standard" List Unit

7

. Assigned by user

## 2.1.4 Track Assignment Table (Figure 6)

The TAT is a table describing the availability of each track on the System Disc and Auxiliary Disc (if included in the configuration). The TAT is ordered by track number and consists of a one-word entry per track. The value of an entry defines its availability.

0 - Available for assignment to user or system

100000 - Assigned to system (or not available)

077777 - Assigned globally

077776 - Assigned to file management package

<IL Segment Address> - The ID Segment address of the assigned user program.

### 2.1.5 IU Switch Table

RTICC will scan a two entry table for each call made for I/O with the DATCH flag set. If the request LU does not refer to a disc and is found, the LU will be switched to the table defined LU. This table will give an LU to LU transform for BATCH programs only. The table format is:

LNT \$LULU \$LULU LEC -N ELP N CC1 -1 Each active word is set with the address Lu in the low 8-bits and the Lo to be used in its place in the high 8-bits. There may be up to N ertries in any order. This table will be generated by the Generator and maintained by the EASCH monitor.

#### 2.1.6 Driver Fartition Map Table (Figure 7)

Dach EQT will have associated with it, a two-word driver man table entry which indicates whether the driver for that EQT is in the System Driver Area (SDA) or is in a driver partition and whether the driver (if it is in SLA) does its own mapping or not. If the driver is in a partition, the entry contains the starting page number of the partition. This page number is put into the appropriate system map or user map registers to map in the driver.

The second word of each entry is used when I/G is started on the correspending driver. The sign bit of the second word indicates whether or not, I/C is being done for a memory resident program. The word is zero for system I/O. The low 10 pits contain the page number of the user's physical pase page if it is a partition resident program. This word is used to save time on setting up the proper map on processing interrupts.

#### 2.2 LTICC Entry Foints

\$51TE Value - non zero if requests are queued on bit bucket SELLC Value - low buffer limit

FELUP Value - high ouffer limit

\$CICO Ertry point - jumps here from \$CIC for interrupt processing \$CKLO Subroutine - check if pelow the buffer limit on the current LCT.

Calling Sequence:

#### JSE SCELO

\$CCN1 Intry point - driver completion return \$CCN2

Intry point - driver continuation return

The code to enter the driver's continuator section must be in all maps since drivers return via the address resulting from a subroutine call. RTIOC will do a JMP SUCOR when ready to enter a driver's continuator section under the user map.

Subroutine - converts an EQT entry number into the actual EQT SCVLO address and calls \$ETEQ to set up the base page EQT pointers.

Entry point - jumps here from SYCIC to skip the CLF and LIA &ChC. in kiloc at scic.

Entry point - jumps here from the system clock routine PLLVI when a device times out.

Subroutine - used to set up a timeout to delay initiation SELAY of an I/O operation on a timed-out EQT.

Calling Sequence:

LEA LOTI JEE SELAY

ŞUMEÇ. ŞUME Value-address of the dummy LCT used for bit bucket operations. Value-Lynamic Mapping System status is saved here when \$CIC is entered. It is used by \$PEFR.

\$LT:VL

Subroutine - Sets up the map registers for entry to a driver after the base page EQT pointers are already built in base page. See Section 3.3.5 for details of \$DEVM. Called by RTICC and EVF43.

Calling Sequence: (ECT1-ECT15 already set up)

JSE \$EEVE

\$LTEQ \$105K

Subroutine-sets up the base page ECT pointers EQT1-FQT15 Intry point - to set an LU or EQT down. This processes any operator DN request (from the scheduler's message processor) that a device (LU) or an I/C slot (EQI) be down. It first determines if an Lu or EQT is being set down. If an LCT is being set down, it checks the validity of the EQT via the <TODNS> subroutine. It also determines if the  $ilde{\mathrm{EQT}}$  (I/C slot) to be set down is associated with the system console. If either error condition exists, it prints an "INPUT ERROR" message and returns to the Scheduler module's message processor. Otherwise it uses <XUPIO> to set all downed LU's on this EQT into the "up" state and uses <\$UNLK> to down the EQT by setting its availability indicator (bits 14-15 of EQT 4) to 01. After suspending in the general wait list any programs queued making unbuffered I/O requests, it returns to the Dispatcher.

If an LU (device) is being set down, it first checks the validity of the LU and whether the user is trying to down LU 1 or an LU pointing to the bit bucket. If one of these error conditions exists, the message "INPUT ERROR" is issued and return is made to the Scheduler module's message processor. If the LU's EQT is down, then the LU is simply marked down (set bit 15 DRT word 2). If the EQT is up, then set the LU and all other LU's associated with the device down and relink any I/O on the device's major - LU (first LU for the device in the DRT). Return is made to the Dispatcher.

- \$ICRC Entrypoint All EXEC calls for I/O related requests are processed here.

- SIGUF Entrypoint To make an EQT available again. This processes any operator request (from the Scheduler's message processor) to set a device "UP". It first checks the validity of the EQT number of the device to be set up via the <IODNS> subroutine. If valid, it next schedules all programs waiting on a downed EQT or LU. Next it uses <XUPIO> to set up all LU's associated with this EQT. <XUPIO> will use <\$XXUP> to relink on to the EQT any I/O found on a downed LU. If the EQT was down or available, the "up" processor will reset the EQT "up" and return to a point in <IGCOM> to start the next request. Otherwise, return is made to the Dispatcher.

- \$IRT Entrypoint Common exit point from the system back to the user. \$IRT is a routine used in exiting from the system back to the user program. It does nothing except clear the memory protect flag in a non-privileged system and restores the registers. In a privileged system, \$IRT clears control on the privileged interrupt card so that when the interrupt system is reenabled for all devices, all devices can interrupt. The exit from \$IRT back to the user program is a "user map enable and jump" instruction. Note that \$IRT always enables the user map. The map is loaded before \$IRT gets control.

- SSYMG Subroutine, system error message output. This routine provides for the output of system messages and error diagnostics on the system console. The routine maintains a "rotating" buffer area consisting of five 10-word blocks; i.e., the maximum length of a message is 18 characters (9 words) plus 1 word preceding the message which contains the character count.

- SUNLE Subroutines, used to unlink I/O requests from the current EQT I/O request queue. This is called when an LU is set down and all of the I/O for that LU is moved to the LU's down queue.

- \$6P Entrypoint jumped to by \$UPIC from Table Area 1 via SJP This entry is used by drivers to automatically "UP" the EQT and is essentially the same code as \$100P.

\*FD1C Subroutine - called by the operating system modules to perform 1/C.

\*\*XAUP Subroutine - takes an I/C queue and positions the I/C requests (by calling the LINK subroutine) in the current LUT queue according to their priority. It returns a flag if an I/C operation should be initiated.

```

2.3 Fase Fage Communication

```

```

ΧI

EQIA

ECT#

DRT

LUMAX

INTEA

INTIG

TAT

KEYVE

EQT1-EQT15

CHAN

TEG

SYSTY

ROCHS

RCRTN

RCP1-RCP7

XEQ1 etc

CFAIN

DUNMY

DATLE

TATSI

SECT2

SECT 3

LCOTK

LCCC

MPTFL

```

These are all located in the System Communication Area of Ease Page.

If the user has is recase, ontry to the driver's continuator section is entered by a JMP \$UCOR. If the system map is used, the simple JSB E,I will be done.

## 3.2 I/C Requests

All input/output operations are performed concurrently with program computation in the overall system. A program is I/C suspended until the transmission or operation is completed unless automatic buffering (output only) was specified for the device or the request was a class 1/U request. In these two cases the buffer is moved to system available memory and the user program is not suspended.

If a program is I/O suspended with the Duffer in the user program area the program is not swappable. If the buffer is in common or system available memory, the program is swappable. A user may call REIO to move his buffer to system available memory and make the I/O call.

The user program making the request is scheduled immediately if return code 4 is used by a driver. The 5 return is made by a driver if it needs FF7 to do the current request but the DMA bit is not set in the EQT.

# 3.2.1 User I/O Requests.

All user I/C requests are channeled to SIGRQ after initial request processing by "EXEC". \$IGRQ performs validity checks on the request parameters and sets the addresses of the referenced EQI entry. (Error conditions and diagnostics are described later.) The buffer address and length is examined for legality for input requests to insure that protected memory is not altered during the transfer. The last page of lower in the User Map are checked for read/write protect status to insure valid memory accesses.

# Disc I/O Requests

If the referenced I/G device is a disc unit, the request is checked to insure that parameters are supplied. If the disc LU number is either 2 or 3, the request is additionally checked to insure that the disc track and sector numbers are legal and that the transfer does not exceed a track ocundary. If the request is output, a referenced track on LU 2 or 3 must belong to the user (i.e., the TAT entry address must equal the LE Segment Address of the user) unless the track is a load-and-go track or a global track.

# Sequests involving Luifered Cutput and Class I/C

If a Write or Control request references a device for which the user designated automatic buffering, a block equal to the buffer size, plus control information (5 words), is requested for allocation in the system available memory area. (Call to \$ALC.) A Class I/O request is also moved into system available memory.

If the block cannot be allocated, the user program is suspende and linked into the memory suspension list. (The memory processor (\$RTN) will cause the user program to be scheduled as soon as a block is released.)

After a block is allocated, the control information (CONWD and buffer length), priority and buffer (if a Write request) are moved into the block. The first word of the block is used for linking into the device list. (See Section 3.3.1.)

# Mormal User Requests and RUIO Requests

The parameters of a user request (which is not buffered as above) are moved into the 5-word temporary area in the ID Segment of the program. Word 1 of the ID Segment is used for linking into the device list. (See Section 3.3.1.)

The user program is suspended with a suspension code of 2 (I/O suspension). This is also done for an REIO call. The only difference is that the buffer address will point to system available memory instead of the user area. The sign bit of the buffer address in the temporary words of the ID segment is set if the buffer is moved as the result of an \$REIO call. This is to tell the system that the driver must process that I/O request under the system map.

# Error Conditions and Diagnostics

Detection of the following error conditions causes a dignostic identifying the error type, a program name and location of the request to be printed on the system teletype. The program is then aborted (\$ABRT in EXEC).

|    | Cone                 | i carina                                                          |

|----|----------------------|-------------------------------------------------------------------|

|    | With Mills Sire year |                                                                   |

| 10 | 0.1                  | Insulficient #10f request parameters.                             |

|    | 02                   | Illegal logical unit #, or less than 5 parameters with A-bit set. |

|    | 0 <b>3</b>           | Illegal ECT reference, select code = U.                           |

|    | 0.4                  | User buffer viclates system (or Real-Time) bouncary.              |

|    | 0.5                  | Illegal disc track or sector # in disc request.                   |

|    | U 6                  | Arite reference to protected track.                               |

|    | + te 7               | friver rejected the request as illegal for the                    |

|    |                      | cevice (unbuffered requests only).                                |

|    | 0.6                  | Disc transfer exceeds track boundary.                             |

|    | 0.9                  | Overflow of load-and-go area.                                     |

|    | 10                   | Class CLT occurred and one GET call outstanding on this class.    |

|    | 11                   | Illegal user map request in System Driver Area.                   |

## System I/O Request Processor <\$XSIO>

A privileged entry is provided at \$X\$10 to allow modules of Real-Time Executive to call for I/C operations without incurring the overhead and procedures involved with user I/C requests. No error checking is performed, the request is linked into the appropriate I/C list at a priority of zero (highest priority) except that disc request may specify a priority, and control is immediately returned to the first word following the request.

Request Format: A system 1/O request differs from the user 1/O request in format and power. Specifically, a system disc call can specify a series of transfers to be performed before the next operation is initiated.

/ completion address can be specified for operation of an open subroutine at the erd of the operation. This tacility is only available to system routines and is useful for resetting flags, etc., because an I/C operation is always buffered to the system. A zero completion address indicates absence of a completion routine.

| vora                            |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Lxt                                           | \$ XD IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                 | •                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | •                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1<br>2<br>3<br>4<br>5<br>0<br>7 | JEB<br>OCH<br>DEF<br>MOP<br>OCH<br>DEF<br>DEC | <pre> <pre> <pre> <pre> <pre> </pre> </pre> <pre> <pre< td=""></pre<></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre></pre> |

For  $\delta$  is in the same field format as the control word in a user request except that the request code replaces the logical unit.

word 8 is set to zero if the request is to be processed under the system map. If the user map is required, the word 8 must contain the ID segment address of the program to be described. Word 8 is 100000 (octal) if the request is to be processed under the User Map as it is currently-without change. Word 8 is set to an ID segment address with the sign bit set if a modified user map is used (e.g., when the Dispatcher is swapping a portion of EDA).

Also, the \$&\$10 call uses the same routine, DRIVR, to set up for and then enter the driver.