# HP 3000 Computer System

# **Machine Instruction Set**

### HP 3000 COMPUTER SYSTEMS

# MACHINE INSTRUCTION SET REFERENCE MANUAL

Manual Part No. 30000-90022 Index No. 3GENL.320.30000-90022

Printed in U.S.A. 2/80

### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the most recent date on which the technical material on any given page was altered. If a page is simply re-arranged due to a technical change on a previous page, it is not listed as a changed page. Within the manual, changes are marked with a vertical bar in the margin.

All Pages in this manual are original third edition issue.

# **PRINTING HISTORY**

New editions incorporate all update material since the previous edition. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover changes only when a new edition is published. If minor corrections and updates are incorporated, the manual is reprinted but neither the date on the title page and back cover nor the edition change.

| First Edition Jun     | e 1976 |

|-----------------------|--------|

| Second Edition Augus  | t 1978 |

| Third Edition Februar | y 1980 |

# **PREFACE**

This manual contains information on the machine instruction set for the HP 3000 Computer Systems. The contents of this manual are organized as follows:

Section I contains general information on traps and interrupts, condition code, and the instruction formats used in the machine instruction description in Sections II through IV.

Section II contains information on the base instruction set furnished with the computer systems.

Section III contains information on the extended instruction set furnished with the computer systems.

Section IV contains information on the language extension instructions furnished with the computer systems.

$Appendix \ A \ is \ an \ alphabetical \ listing \ of \ all \ machine \ instructions \ that \ gives \ the \ page \ on \ which \ the \ instruction \ is \ defined.$

Except where specified, the content of this manual applies equally to all HP 3000 Computer Systems.

v

# STACK OP INSTRUCTIONS

| MNEMONIC | NAME                               | PAGE | MNEMONIC | NAME                               | PAGE |

|----------|------------------------------------|------|----------|------------------------------------|------|

| ADAX     | Add A to X                         | 2-7  | FIXT     | Fix and truncate                   | 2-5  |

| ADBX     | Add B to X                         | 2-7  | FLT      | Float an integer                   | 2-3  |

| ADD      | Add A to B                         | 2-1  | FMPY     | Floating point multiply            | 2-4  |

| ADXA     | Add X to A                         | 2-7  | FNEG     | Floating point negate              | 2-4  |

| ADXB     | Add X to B                         | 2-7  | FSUB     | Floating point subtract D,C - B,A  | 2-4  |

| AND      | Logical AND of A and B             | 2-6  | INCA     | Increment A                        | 2-6  |

| BTST     | Test byte on TOS and set CC        | 2-9  | INCB     | Increment B                        | 2-6  |

| CAB      | Rotate A-B-C                       | 2-8  | INCX     | Increment X                        | 2-6  |

| CMP      | Integer compare B, A and set CC    | 2-2  | LADD ·   | Logical add A + B                  | 2-5  |

| DADD     | Double integer add D,C + B,A       | 2-2  | LCMP     | Logical compare B, A and set CC    | 2-5  |

| DCMP     | Double integer compare and set CC  | 2-3  | LDIV     | Logical divide C,B ÷ A             | 2-5  |

| DDEL     | Double delete TOS                  | 2-9  | LDXA     | Load X into A                      | 2-7  |

| DDIV     | Double integer divide              | 2-3  | LDXB     | Load X into B                      | 2-7  |

| DDUP     | Double duplicate TOS               | 2-9  | LMPY     | Logical multiply B × A             | 2-5  |

| DECA     | Decrement A                        | 2-6  | LSUB     | Logical subtract B - A             | 2-5  |

| DECB     | Decrement B                        | 2-7  | MPY      | Multiply integers, integer product | 2-1  |

| DECX     | Decrement X                        | 2-6  | MPYL     | Multiply integers, long integer    |      |

| DEL      | Delete TOS                         | 2-9  |          | product                            | 2-2  |

| DELB     | Delete B                           | 2-9  | NEG      | Integer negate                     | 2-2  |

| DFLT     | Floating a double integer          | 2-3  | NOP      | No operation                       | 2-10 |

| DIV      | Integer divide B by A              | 2-1  | NOT      | Logical complement TOS             | 2-6  |

| DIVL     | Divide long integer C,B ÷ A        | 2-2  | OR       | Logical OR of A, B                 | 2-6  |

| DMUL     | Double integer multiply            | 2-3  | STAX     | Store A into X                     | 2-7  |

| DNEG     | Double integer negate              | 2-3  | STBX     | Store B into X                     | 2-7  |

| DSUB     | Double integer subtract D,C - B,A  | 2-2  | SUB      | Integer subtract B - A             | 2-1  |

| DTST     | Test double word on TOS and set CC | 2-9  | TEST     | Test TOS and set CC                | 2-9  |

| DUP      | Duplicate TOS                      | 2-9  | XAX      | Exchange A and X                   | 2-8  |

| DXCH     | Double exchange                    | 2-8  | XBX      | Exchange B and X                   | 2-8  |

| DZRO     | Push double zero onto stack        | 2-8  | XCH      | Exchange A and B                   | 2-8  |

| FADD     | Floating point add D,C + B,A       | 2-4  | XOR      | Logical exclusive OR of A, B       | 2-6  |

| FCMP     | Floating point compare and set CC  | 2-3  | ZERO     | Push integer zero onto stack       | 2-8  |

| FDIV     | Floating point divide D,C + B,A    | 2-4  | ZROB     | Zero B                             | 2-8  |

| FIXR     | Fix and round                      | 2-4  | ZROX     | Zero X                             | 2-8  |

# SHIFT INSTRUCTIONS

| MNEMONIC | NAME                          | PAGE | MNEMONIC | NAME                             | PAGE |

|----------|-------------------------------|------|----------|----------------------------------|------|

| ASL      | Arithmetic shift left         | 2-10 | DLSR     | Double logical shift right       | 2-11 |

| ASR      | Arithmetic shift right        | 2-10 | LSL      | Logical shift left               | 2-10 |

| CSL      | Circular shift left           | 2-10 | LSR      | Logical shift right              | 2-10 |

| CSR      | Circular shift right          | 2-11 | QASL     | Quadruple arithmetic shift left  | 2-12 |

| DASL     | Double arithmetic shift left  | 2-11 | QASR     | Quadruple arithmetic shift right | 2-13 |

| DASR     | Double arithmetic shift right | 2-11 | TASL     | Triple arithmetic shift left     | 2-12 |

| DCSL     | Double circular shift left    | 2-11 | TASR     | Triple arithmetic shift right    | 2-12 |

| DCSR     | Double circular shift right   | 2-12 | TNSL     | Triple normalizing shift left    | 2-12 |

| DLSL     | Double logical shift left     | 2-11 |          |                                  | 1    |

# FIELD AND BIT INSTRUCTIONS

| MNEMONIC                  | NAME                                                                                                       | PAGE                         | MNEMONIC | NAME                                                                                      | PAGE                 |

|---------------------------|------------------------------------------------------------------------------------------------------------|------------------------------|----------|-------------------------------------------------------------------------------------------|----------------------|

| DPF<br>EXF<br>SCAN<br>TBC | Deposit field, A bits to B Extract specified field, right-justifiy Scan bits Test specified bit and set CC | 2-14<br>2-14<br>2-13<br>2-13 | _        | Test and complement bit, set CC<br>Test and reset bit, set CC<br>Test and set bit, set CC | 2-14<br>2-13<br>2-13 |

# **BRANCH INSTRUCTIONS**

| MNEMONIC                                       | NAME                                                                                                                                                      | PAGE                                                 | MNEMONIC                                    | NAME                                                                                                                                                                    | PAGE                                         |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| BCC<br>BCY<br>BNCY<br>BNOV<br>BOV<br>BR<br>BRE | Branch on specified CC Branch on carry Branch on no carry Branch on no overflow Branch on overflow Branch unconditionally Branch on TOS even (bit 15 = 0) | 2-16<br>2-15<br>2-15<br>2-15<br>2-15<br>2-16<br>2-15 | BRO<br>CPRB<br>DABZ<br>DXBZ<br>IABZ<br>IXBZ | Branch on TOS odd (bit 15 = 1) Compare range and branch Decrement A, branch if zero Decrement X, branch if zero Increment A, branch if zero Increment X, branch if zero | 2-15<br>2-16<br>2-15<br>2-14<br>2-14<br>2-14 |

# **MOVE INSTRUCTIONS**

| MNEMONIC                                    | NAME                                                                                                                                                                    | PAGE                                         | MNEMONIC                                  | NAME                                                                                                                                                                                                              | PAGE                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| CMPB<br>MABS<br>MDS<br>MFDS<br>MOVE<br>MTDS | Compare bytes in two memory blocks Move using absolute addresses Move using data segments Move from data segment Move words in memory, address +/- Move to data segment | 2-18<br>2-20<br>2-22<br>2-21<br>2-17<br>2-21 | MVB<br>MVBL<br>MVBW<br>MVLB<br>SCU<br>SCW | Move bytes in memory, addresses +/- Move words from DB+ to DL+ area Move bytes while of specified type Move words from DL+ to DB+ area Scan bytes until test or terminal byte Scan bytes while equal to test byte | 2-17<br>2-19<br>2-18<br>2-20<br>2-19<br>2-19 |

# PRIVILEGED MEMORY REFERENCE INSTRUCTIONS

| MNEMONIC    | NAME                                                    | PAGE | MNEMONIC     | NAME                                                                   | PAGE         |

|-------------|---------------------------------------------------------|------|--------------|------------------------------------------------------------------------|--------------|

| LDEA        | Load double word from extended address                  | 2-23 | PSTA<br>SDEA | Privileged store into absolute address Store double word into extended | 2-22         |

| LSEA        | Load single word from extended address                  | 2-23 | SSEA         | address<br>Store single word into extended                             | 2-23         |

| LST<br>PLDA | Load from system table<br>Privileged load from absolute | 2-23 | SST          | address<br>Store into system table                                     | 2-23<br>2-23 |

|             | address                                                 | 2-22 |              |                                                                        | 1            |

# **IMMEDIATE INSTRUCTIONS**

| MNEMONIC                                                    | NAME                                                                                                                                                                                                                          | PAGE                                                         | MNEMONIC                                            | NAME                                                                                                                                                                                | PAGE                                                 |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| ADDI<br>ADXI<br>ANDI<br>CMPI<br>CMPN<br>DIVI<br>LDI<br>LDNI | Add immediate to integer in A Add immediate to X Logical AND immediate with A Compare A with immediate, set CC Compare A with negative immediate Divide immediate into A Load immediate to TOS Load negative immediate to TOS | 2-24<br>2-25<br>2-26<br>2-24<br>2-25<br>2-24<br>2-24<br>2-25 | LDXI<br>LDXN<br>MPYI<br>ORI<br>SBXI<br>SUBI<br>XORI | Load X immediate Load X negative immediate Multiply immediate with A Logical OR immediate with A Subtract immediate from X Subtract immediate from A Logical exclusive OR immediate | 2-24<br>2-25<br>2-24<br>2-25<br>2-25<br>2-24<br>2-25 |

# REGISTER CONTROL INSTRUCTIONS

| MNEMONIC                     | NAME                                                                                             | PAGE                         | MNEMONIC             | NAME                                                                                             | PAGE                 |

|------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|----------------------|--------------------------------------------------------------------------------------------------|----------------------|

| ADDS<br>PSHR<br>RCLK<br>SCLK | Add operand to stack pointer<br>Push specified registers onto stack<br>Read clock<br>Store clock | 2-27<br>2-26<br>2-27<br>2-27 | SETR<br>SUBS<br>XCHD | Set specified registers from stack<br>Subtract operand from stack pointer<br>Exchange DB and TOS | 2-26<br>2-27<br>2-27 |

# PROGRAM CONTROL AND SPECIAL INSTRUCTIONS

| MNEMONIC                                         | NAME                                                                                                                                              | PAGE                                                                         | MNEMONIC                                                                   | NAME                                                                                                                                                                                                                          | PAGE                                                                         |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| DISP EXIT HALT IXIT LLBL LLSH LOCK PAUS PCAL PCN | Dispatch Exit from procedure Halt Interrupt exit Load label Linked list search Lock resource* Pause, interruptable Procedure call Push CPU number | 2-29<br>2-28<br>2-30<br>2-29<br>2-29<br>2-31<br>2-30<br>2-30<br>2-28<br>2-31 | PSEB<br>RCCR<br>RSW<br>SCAL<br>SCLR<br>SINC<br>SXIT<br>TOFF<br>TON<br>UNLK | Pseudo interrupt enable Read system clock counter** Read switch register Subroutine call Set system clock limit** Set system clock interrupt** Exit from subroutine Hardware timer off** Hardware timer on** Unlock resource* | 2-30<br>2-31<br>2-31<br>2-28<br>2-32<br>2-32<br>2-28<br>2-32<br>2-32<br>2-30 |

| PSDB                                             | Pseudo interrupt disable                                                                                                                          | 2-29                                                                         | XEQ                                                                        | Execute stack word  *Series II Computer Systems only.  **Series 30/33 Computer Systems only.                                                                                                                                  | 2-31                                                                         |

# I/O INSTRUCTIONS

| MNEMONIC                                                                | NAME                                                                                                                                                                                                                                            | PAGE                                                                         | MNEMONIC                                                         | NAME                                                                                                                                                                                                                                                      | PAGE                                                                 |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| CIO<br>CMD<br>DUMP<br>HIOP<br>INIT<br>MCS<br>RIO<br>RIOC<br>RMSK<br>SED | Control I/O, direct* Send command to module, direct* Load soft dump program** Hlat I/O program** Initialize I/O channel** Read memory controller** Read I/O, direct* Read I/O channel** Read device mask Set enable/disable external interrupts | 2-34<br>2-35<br>2-35<br>2-37<br>2-36<br>2-36<br>2-34<br>2-37<br>2-33<br>2-33 | SEML<br>SIN<br>SIO<br>SIOP<br>SMSK<br>STRT<br>TIO<br>WIO<br>WIOC | Semaphore load** Set interrupt* Start I/O, block transfer* Start I/O, program** Set device mask Initiate warmstart** Test I/O, direct* Write I/O, direct* Write I/O, channel**  *Series II/III Computer System only. **Series 30/33 Computer System only. | 2-37<br>2-35<br>2-33<br>2-36<br>2-33<br>2-37<br>2-34<br>2-34<br>2-35 |

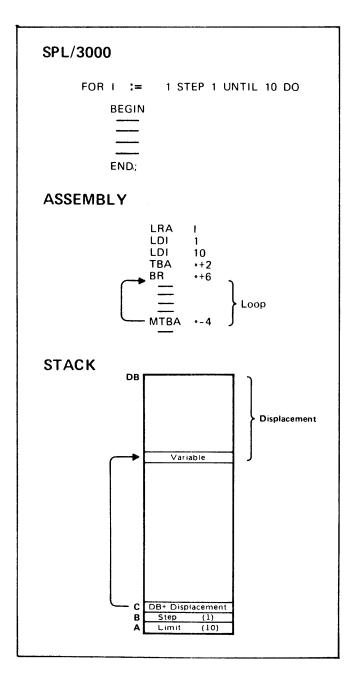

# LOOP CONTROL INSTRUCTIONS

| MNEMONIC | NAME                                        | PAGE | MNEMONIC   | NAME                                                                | PAGE         |

|----------|---------------------------------------------|------|------------|---------------------------------------------------------------------|--------------|

| МТВА     | Modify variable, test against limit, branch | 2-38 | TBA<br>TBX | Test variable against limit, branch<br>Test X against limit, branch | 2-38<br>2-38 |

| MTBX     | Modify X, test against limit, branch        | 2-38 |            |                                                                     |              |

# MEMORY ADDRESS INSTRUCTIONS

| MNEMONIC                                                   | NAME                                                                                                                                                                                               | PAGE                                                         | MNEMONIC                                                 | NAME                                                                                                                                                                                             | PAGE                                                 |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| ADDM<br>CMPM<br>DECM<br>INCM<br>LDB<br>LDD<br>LDPN<br>LDPP | Add memory to TOS Compare TOS with memory Decrement memory Increment memory Load byte onto stack Load double word onto stack Load double from program, negative Load double from program, positive | 2-41<br>2-41<br>2-41<br>2-41<br>2-40<br>2-39<br>2-39<br>2-39 | LDX<br>LOAD<br>LRA<br>MPYM<br>STB<br>STD<br>STOR<br>SUBM | Load X Load word onto stack Load relative address onto stack Multiply TOS by memory Store byte on TOS into memory Store double on TOS into memory Store TOS into memory Subtract memory from TOS | 2-39<br>2-39<br>2-40<br>2-41<br>2-40<br>2-39<br>2-41 |

# **EXTENDED INSTRUCTION SET**

| MNEMONIC                                     | NAME                                                       | PAGE                                   | MNEMONIC                                                  | NAME                                                                                                                                                                                                                                                       | PAGE                                                                             |

|----------------------------------------------|------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Extended-Precision Floating Point            |                                                            |                                        | Decimal Arithn                                            | netic                                                                                                                                                                                                                                                      |                                                                                  |

| EADD<br>ECMP<br>EDIV<br>EMPY<br>ENEG<br>ESUB | Add<br>Compare<br>Divide<br>Multiply<br>Negate<br>Subtract | 3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-1 | ADDD CMPD CVAD CVBD CVDA CVDB DMPY MPYD NSLD SLD SRD SUBD | Decimal add Decimal compare ASCII to decimal conversion Binary to decimal conversion Decimal to ASCII conversion Decimal to binary conversion Double logical multiply Decimal multiply Decimal normalizing left shift Decimal right shift Decimal subtract | 3-5<br>3-6<br>3-3<br>3-4<br>3-4<br>3-5<br>3-8<br>3-8<br>3-7<br>3-7<br>3-7<br>3-7 |

# LANGUAGE EXTENSION INSTRUCTIONS

| MNEMONIC                                             | NAME                                                                                                                                      | PAGE                                                | MNEMONIC                                         | NAME                                                                                                                            | PAGE                                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| ABSD<br>ABSN<br>ALGN<br>CMPS<br>CMPT<br>CVND<br>EDIT | Absolute decimal Absolute numeric Align numeric Compare strings Compare translated strings Convert numeric display Edit more instructions | 4-15<br>4-14<br>4-13<br>4-12<br>4-12<br>4-14<br>4-2 | ENDP<br>LDDW<br>LDW<br>NEGD<br>PARC<br>TR<br>XBR | End of paragraph<br>Load double word<br>Load word<br>Negate decimal<br>Paragraph procedure call<br>Translate<br>External branch | 4-2<br>4-16<br>4-16<br>4-15<br>4-1<br>4-11 |

### SECTION

# **GENERAL INFORMATION**

#### INTRODUCTION 1-1.

This manual contains information on the machine instruction sets of the HP 3000 Computer Systems. Section I contains general information about the instruction sets. Section II describes each of the instructions included in the basic instruction set, Section III describes each of the instructions which are part of the HP 30012A Extended Instruction Set (EIS), and Section IV describes each of the instructions which are part of the language extension set. Appendix A contains an alphabetical listing of all instructions together with the page numbers on which the instructions are to be found.

#### **BASIC INSTRUCTION SET** 1-2.

#### INSTRUCTION DECODING 1-3.

As the CPU executes a user program, it fetches these instructions from memory. A ROM address of a microprogram stored in a microprogram ROM is generated for these instructions. There is a microprogram in ROM for each of the machine instructions. The ROM address is stored in a ROM address register (RAR). The RAR is used first to access the initial microinstruction and is then incremented to point to the next microinstruction. Thus, the entire microprogram for a particular machine instruction is called and executed by the CPU.

#### TRAPS AND INTERRUPTS 1-4.

Only those traps and interrupts which occur as a result of instruction execution over which the user has some control are used in the instruction descriptions provided in Sections II and III. They are defined here by segment #1 segment transfer table number.

- STT #1; BNDV Bounds Violation. An operand or instruction is outside of the legal bounds for a particular mode of addressing.

- b. STT #17; STTV Segment Transfer Table Violation. A variety of conditions can force this trap as follows:

- The STT number in an external program label is greater than the STT length pointed to by PL in the referenced segment. This error can occur in PCAL, LLBL, and the firmware interrupt handler while attempting to set up a new segment.

- In LLBL, the label fetched from PL-N is an internal label and N is greater than 128 (%177). This would require too large an STT number when creating the external label.

- In PCAL and interrupt handler when setting up a new segment, the STT number in the external program label points to an external program label in the new segment.

- In SCAL, (PL-N) is an external label.

- STT #18; CSTV Code Segment Table Violation. An attempt is made to transfer to Segment 0 or 192, or a segment number is greater than the CST length.

- d. STT #19; DSTV Data Segment Table Violation. The data segment number referenced by MFDS. MTDS, or MDS is greater than the DST length or is 0.

- STT #20; STUN Stack Underflow. The process being executed or being transferred to is nonprivileged and SM is less than DB.

- STT #21; MODE Privileged Mode Violation. The code segment being executed is non-privileged (bit 0 of the Status register is 0) and an attempt is made to execute a privileged instruction. This violation also occurs in EXIT if an attempt is made to exit from user to privileged mode or, if exiting from user mode, the External Interrupts bit in the Status register has been altered.

- STT #24: STOV Stack Overflow. SM is greater than Z or may become greater as a result of the current instruction.

- STT #25; ARITH Arithmetic. All User Traps will be executed in the segment #1 routine pointed to by STT #25. The error conditions and their parameters are as follows:

| <u>_</u>                             | Octal      |

|--------------------------------------|------------|

| Interrupt Type                       | Parameters |

| Integer Overflow                     | 000001     |

| Floating Point Overflow              | 000002     |

| Floating Point Underflow             | 000003     |

| Integer Divide-by-Zero               | 000004     |

| Floating Point Divide-by-Zero        | 000005     |

| Extended Precision FP Overflow       | 000010     |

| Extended Precision FP Underflow      | 000011     |

| Extended Precision FP Divide-by-Zero | 000012     |

| Decimal Overflow                     | 000013     |

| Invalid ASCII Digit                  | 000014     |

| Invalid Decimal Digit                | 000015     |

| Invalid Source Word Count            | 000016     |

| Result Word Count Overflow           | 000017     |

| Decimal Divide-by-Zero               | 000020     |

Octal parameters 000010 through 000020 are traps for the Extended Instruction Set and are shown here for completeness only.

- STT #31; ABS CST Absent Code Segment. The absence bit in the CST entry for the referenced segment is set. The interrupt handler and PCAL stack a (second) marker; others including EXIT, IXIT, etc., do not.

- STT #32; TRACE Code Segment Trace. Code segment is being traced.

- k. STT #33; UNCALL Uncallable STT Entry. The uncallable bit in a local label or, if the STT number is 0, in (PL) is set. This trap does not stack a (second) marker.

- STT #34; ABS DST Absent Data Segment. The absence bit in the DST entry for the referenced segment is set.

### 1-5. EXTENDED INSTRUCTION SET

#### 1-6. INSTRUCTION DECODING

Firmware in the main (basic) microprogram interprets the instructions of the extended instruction set. The operation is then like that of the basic instruction set.

#### 1-7. INTERRUPTS

The instructions of the extended instruction set are not interruptable. If these instructions are performed by software simulation procedures, interrupts are recognized in the manner established for the instructions which make up each procedure.

# 1-8. EXTENDED PRECISION FLOATING POINT INSTRUCTIONS

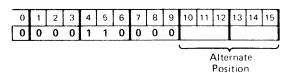

Instruction Commentary 1 in Section III provides information on these instructions.

# 1-9. DECIMAL ARITHMETIC INSTRUCTION SET

Instruction Commentary 2 in Section III provides information on these instructions.

### 1-10. LANGUAGE EXTENSION SET

Firmware in the main (basic) microprogram interprets the instructions of the language extension set. The operation is then like that of the basic instruction set. Instruction Commentary 1, 2, and 3 in Section IV provide additional information on these instructions.

### 1-11. CONDITION CODE

Bits 6 and 7 of the CPU Status register are used for the Condition Code. Although several instructions make special use of the Condition Code, the Condition Code typically indicates the state of an operand (or a comparison result with two operands). The operand may be a byte, word, doubleword, tripleword, or quadrupleword, and may be located on the top of the stack, in the Index register, or in a specified memory location. Three codings are used, 00, 01, and 10. The "11" is not used. Except for the special interpretations, there are four basic patterns, table 1-1, for interpreting these codes.

| PATTERN    | CODE INTERPRETATION                                                                                                                                         |  |  |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Arithmetic | CCA sets CC = CCG (00) if operand greater than 0 = CCL (01) if operand less than 0 = CCE (10) if operand equals 0                                           |  |  |  |  |  |  |  |

| Byte       | CCB sets CC = CCG (00) if numeric (%060-071)<br>= CCL (01) if special character (all others)<br>= CCE (10) if alphabetic (%101-132 and %141-172)            |  |  |  |  |  |  |  |

| Comparison | CCC sets CC = CCG (00) if operand 1 is greater than operand 2<br>= CCL (01) if operand 1 is less than operand 2<br>= CCE (10) if operand 1 equals operand 2 |  |  |  |  |  |  |  |

| Direct I/O | CCD sets CC = CCG (00) if device not ready (busy) = CCL (10) if non-responding device controller = CCE (10) if responding controller and/or device ready    |  |  |  |  |  |  |  |

Table 1-1. Condition Codes

Pattern A is the most common Condition Code pattern. In this CCA pattern, the Condition Code is set to 00 if the operand is greater than zero, to 01 if the operand is less than zero, or to 10 if the operand is exactly zero. Since the usage of this pattern is so common, the three codes 00, 01, and 10 are named to reflect these meanings. Thus 00 is CCG ("Greater"), 01 is CCL ("Less"), and 10 is CCE ("Equal"). These names are primarily used for documentation convenience.

Pattern B for the Condition Code, designated CCB, is used with byte oriented instructions. In the CCB pattern, the Condition Code is set to 00 if the operand byte is an ASCII numeric character, which would be represented by octal values 060 through 071. The code is set to 10 if the byte is an ASCII alphabetic character, which would be represented by octal values 101 through 132 for upper case letters and 141 through 172 for lower case letters. The code is set to 01 if the byte is an ASCII special character represented by the remaining octal values.

Pattern C for the Condition Code, designated CCC, is used with comparison instructions. The code is set to 00 if operand 1 is greater than operand 2, or to 01 if operand 1 is less than operand 2, or to 10 if the operands are equal. In

the instruction definitions, the first mentioned operand is "operand 1". For example, the definition for CMP reads: "The Condition Code is set to pattern C as a result of the integer comparison of the second word of the stack with the TOS." The second word of the stack is therefore operand 1 and the TOS is operand 2.

Pattern D for the Condition Code, designated CCD, is used with some I/O instructions. The code is set to 00 if the device is not ready. This is usually caused by the device being busy. The code is set to 01 if the device controller does not respond. Some examples of what could cause this is power off the device or controller, problems with the device or controller, or waiting for a response to an interrupt request. The last would be used with a Controller Processor. The Condition Code is set to 10 if the device and controller responded and the instruction completed normally.

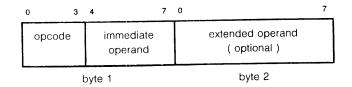

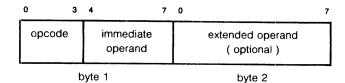

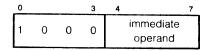

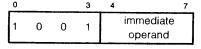

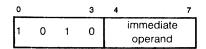

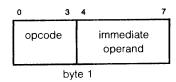

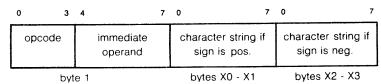

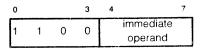

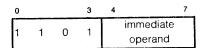

### 1-12. INSTRUCTION FORMATS

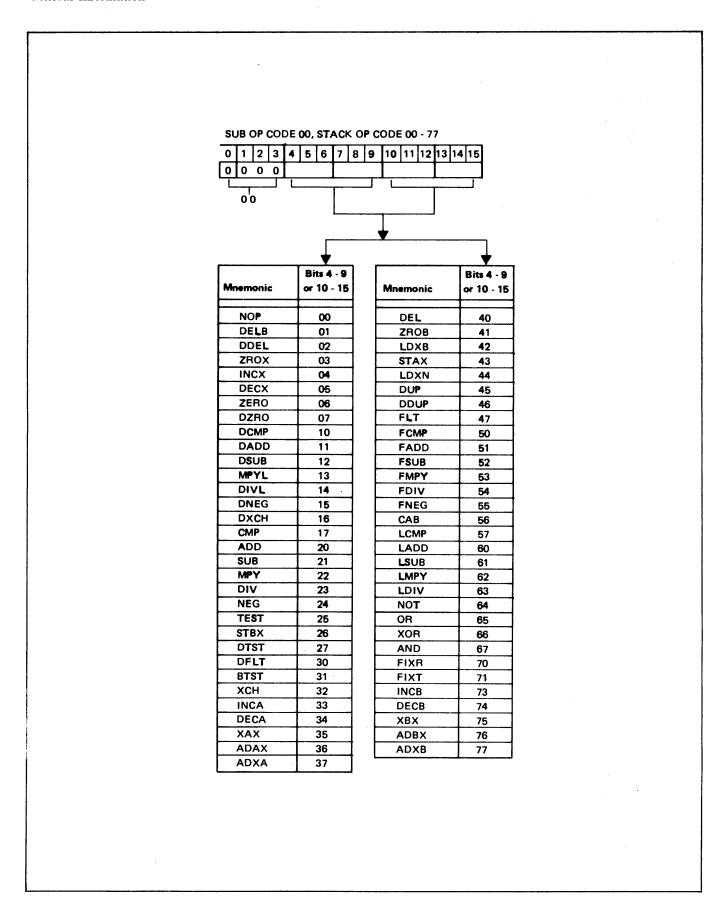

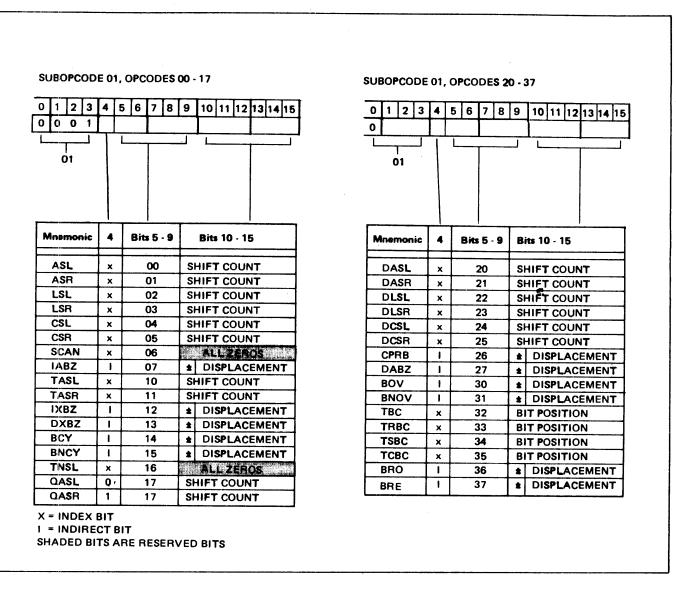

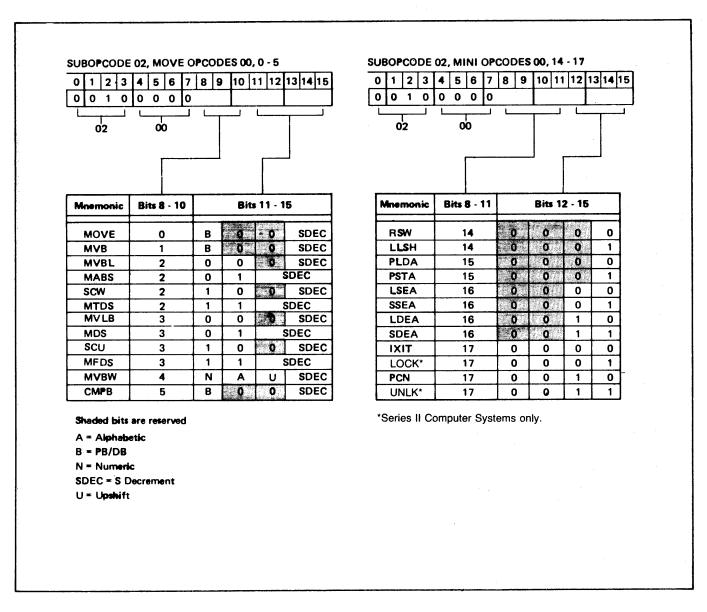

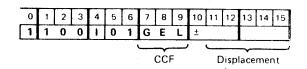

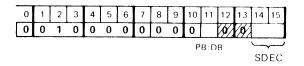

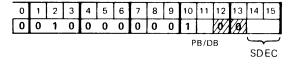

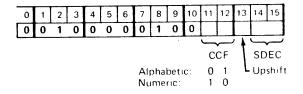

Instruction formats are provided by figures 1-1 through 1-6.

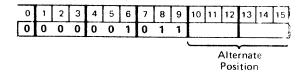

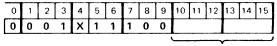

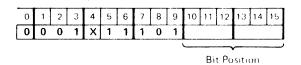

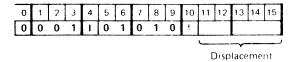

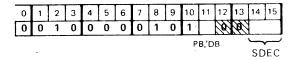

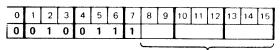

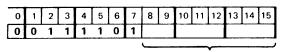

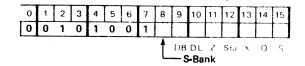

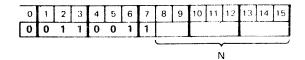

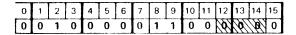

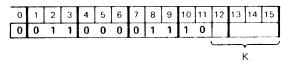

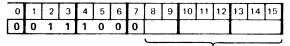

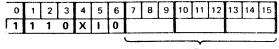

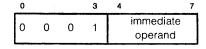

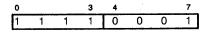

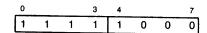

Figure 1-1. Subopcode 00 Formats

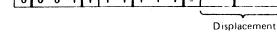

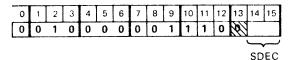

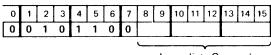

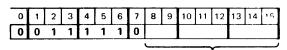

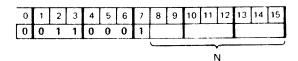

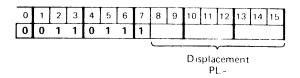

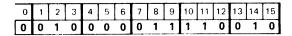

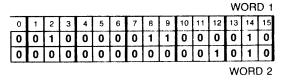

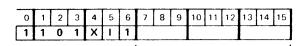

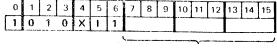

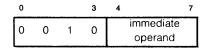

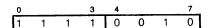

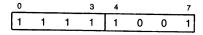

Figure 1-2. Subopcode 01 Formats

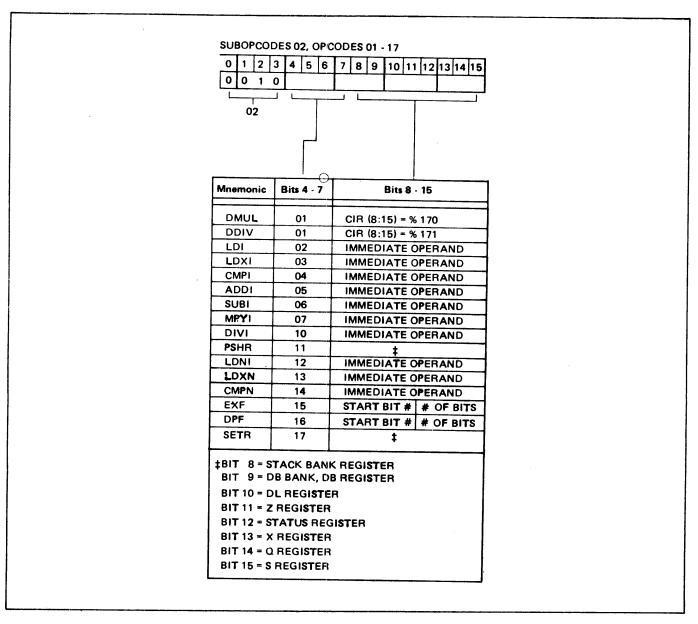

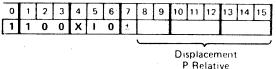

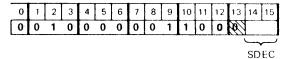

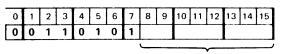

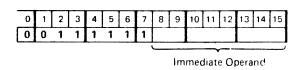

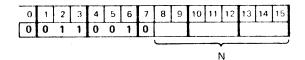

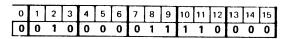

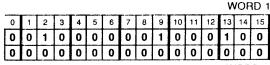

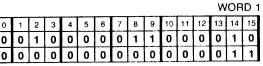

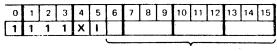

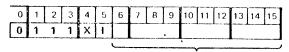

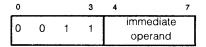

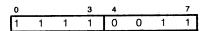

Figure 1-3. Subopcode 02 Formats (Sheet 1 of 2)

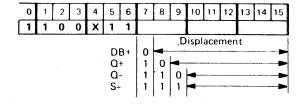

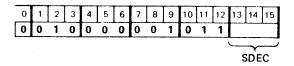

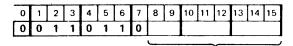

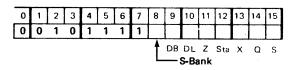

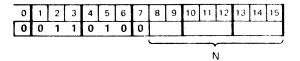

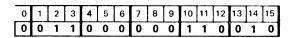

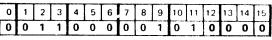

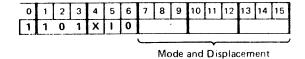

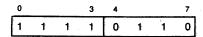

Figure 1-3 Subopcode 02 Formats (Sheet 2 of 2)

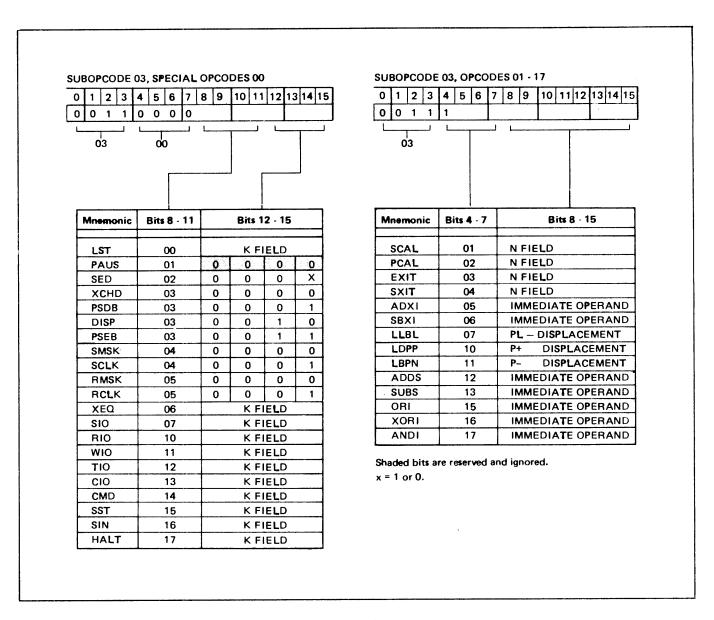

0

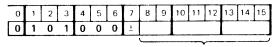

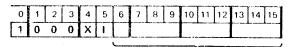

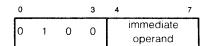

Figure 1-4. Subopcode 03 Formats

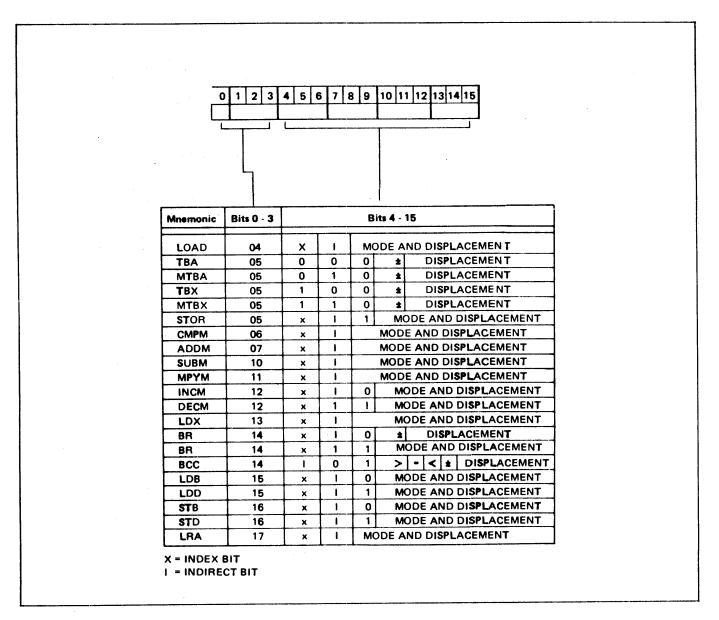

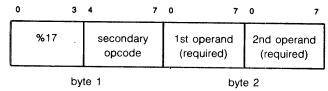

Figure 1-5. Subopcode 04-17 Formats

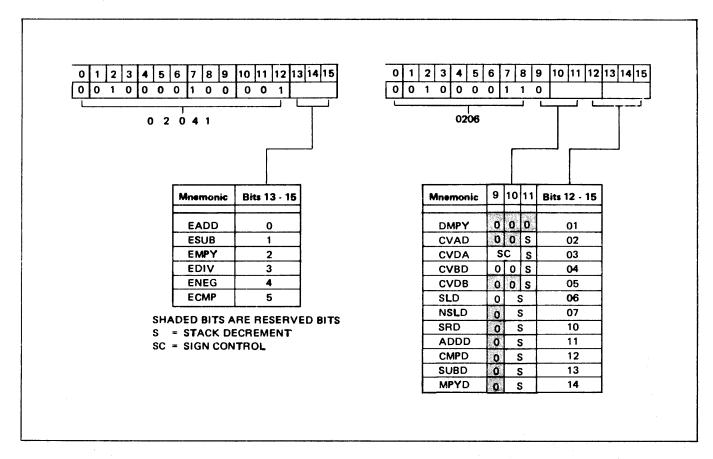

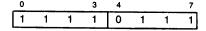

Figure 1-6. Extended Instruction Set Formats

# **INSTRUCTION SET**

SECTION

H

This section defines each of the machine instructions in the computer system instruction set. Where additional information would be helpful in understanding the operation of a particular instruction, an instruction commentary reference is given following the definition. In such cases, refer to the corresponding number under the heading, "Instruction Commentary", at the end of this section.

### STACK OP INSTRUCTIONS

### INTEGER INSTRUCTIONS

MPY

DIV

ADD Add. The top two words of the stack are added in integer

form and are then deleted. The resulting sum is pushed onto the stack.

Stack opcode: 20

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

SUB Subtract. The TOS is subtracted in integer form from the second word of the stack and both words are then deleted.

The resulting difference is then pushed onto the stack.

Stack opcode: 21 Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

Multiply. The top two words of the stack are multiplied in integer form. The two words are deleted and the least significant word of the double length product is pushed onto the stack. If the high order 17 bits of the double length product (including the sign bit of the second word)

Instruction Commentary 1.

Stack opcode: 22

Indicators: CCA, Overflow Traps: STUN, ARITH

Divide. The integer in the second word of the stack is divided by the integer on the TOS. The second word is replaced by the quotient, and the top word is replaced by the remainder.

are not all zeros or all ones, Overflow is set.

Stack opcode: 23

Indicators: CCA on quotient, Overflow

Traps: STUN, ARITH

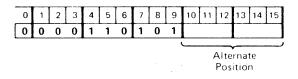

Alternate Position NEG

Negate. The integer in the TOS is replaced by its two's

complement. Stack opcode: 24

Indicators: CCA, Overflow, Carry

Traps: STUN, ARITH

**CMP**

Compare. The Condition Code is set to pattern C as a result of the integer comparison of the second word of the stack with the TOS. Both words are deleted.

Stack opcode: 17 Indicators: CCC Traps: STUN

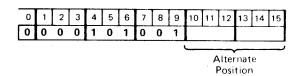

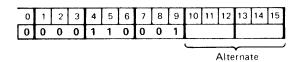

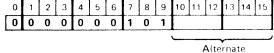

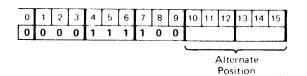

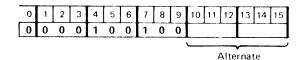

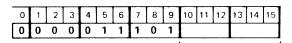

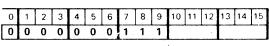

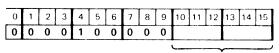

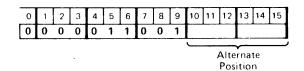

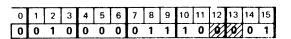

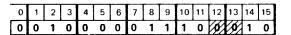

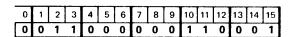

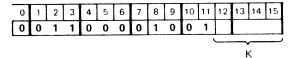

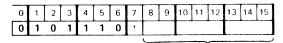

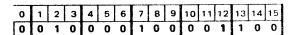

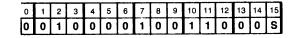

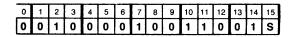

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13   | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|------|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |    |    |    |      |    |    |

|   |   |   |   |   |   |   |   |   | • |    |    |    | rnat |    |    |

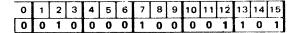

### **DOUBLE INTEGER INSTRUCTIONS**

DADD

DIVL

Double add. The two doubleword integers contained in the top four elements of the stack are added in double length integer form (D,C+B,A) and they are deleted. The doubleword integer sum is pushed onto the stack (B,A).

Stack opcode: 11

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

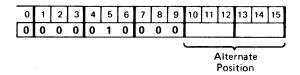

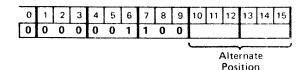

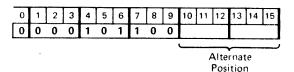

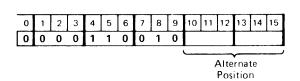

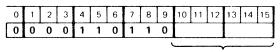

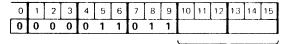

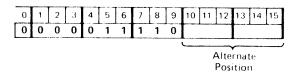

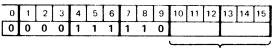

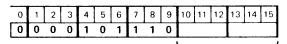

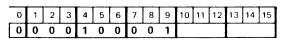

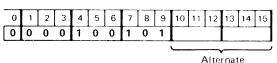

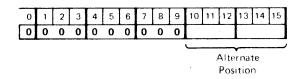

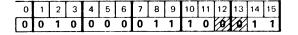

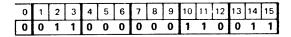

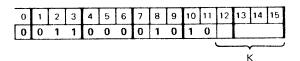

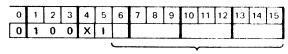

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 0 0 0 0 1 0 0 1

DSUB Double subtract. The doubleword integer contained in

doubleword integer contained in the third and fourth words of the stack (D,C-B,A). The top four words of the stack are deleted and the doubleword integer result is pushed onto the stack (B,A).

the top two words of the stack is subtracted from the

Stack opcode: 12

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

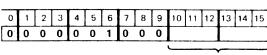

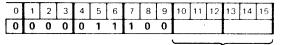

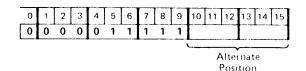

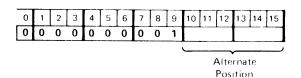

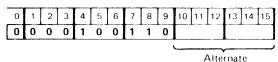

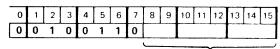

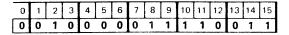

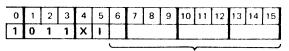

0

0

0

0

0

1

0

1

0

0

0

0

1

0

0

0

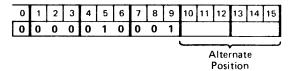

Alternate Position

Position

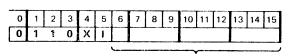

MPYL Multiply long. The top two words of the stack are multiplied in integer form. The words are replaced by the double length product, with the least significant half on the TOS. Overflow is cleared. Carry is cleared if the low order 16 bits represent the true result (i.e., if the high order 17 bits are either all zeros or all ones); otherwise, Carry is set.

Instruction Complementary 1.

Stack opcode: 13

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

Divide long. The doubleword integer in the second and third elements of the stack is divided by the integer in the  $TOS(C,B \div A)$ . The three words are deleted, and the quotient and remainder are pushed onto the stack (quotient in B, remainder in A).

Stack opcode: 14

Indicators: CCA, Overflow Traps: STUN, ARITH

DNEG Double negate. The doubleword integer contained in the top two words of the stack is negated (two's complemented) and replaces the original doubleword integer.

Stack opcode: 15

Indicators: CCA, Overflow Traps: STUN, ARITH

DCMP Double compare. The Condition Code is set to pattern C as a result of the doubleword integer comparison of D,C and B,A. The two double words are deleted from the stack.

Stack opcode: 10 Indicators: CCC Traps: STUN

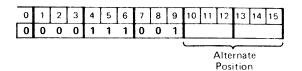

DMUL Double integer multiply. The two's complement double integer contained in D and C is multiplied by the two's complement double integer contained in B and A. The four words are popped from the stack and the least significant doubleword of the product is pushed onto the stack. If the high order 33 bits if the 64-bit product are not all zeros or all ones, overflow is set.

Sub-opcode 2: 01, bits 8-15 = 170

Indicators: CCA Traps: STUN, ARITH

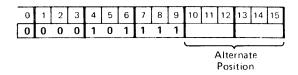

DDIV Double integer divide. The two's complement double integer contained in D and C is divided by the two's complement double integer contained in B and A. The four words are popped from the stack, the 32-bit quotient is pushed into D and C, and the 32-bit remainder is pushed into B and A.

Sub-opcode 2: 01, bits 8-15 = 171 Indicators: CCA on quotient Overflow

Traps: STUN, ARITH

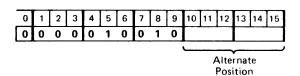

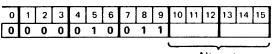

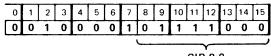

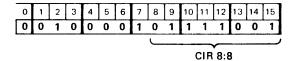

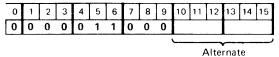

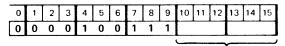

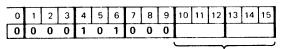

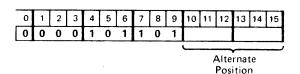

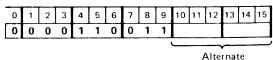

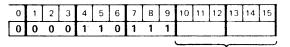

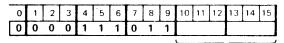

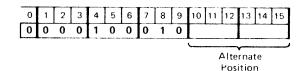

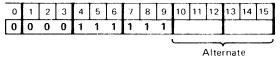

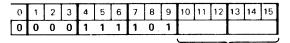

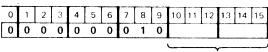

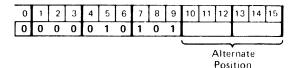

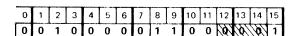

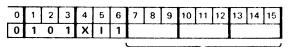

# 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 0 0 1 1 1 0 1 Alternate

Alternate

Position

**CIR 8:8**

### **FLOATING POINT INSTRUCTIONS**

DFLT Double float. Converts the doubleword integer contained in the top two words of the stack to a floating point number with rounding.

Instruction Commentary 2. Stack opcode: 30

Indicators: CCA

Traps: STUN

FLT Float. Converts the integer on the TOS to a 32-bit floating point number with rounding. The TOS is deleted and the doubleword floating point result is pushed onto the stack.

Instruction Commentary 2. Stack opcode: 47 Indicators: CCA

Traps: STUN, STOV

FCMP Floating compare. The Condition Code is set to pattern C as a result of the floating point comparison of D,C with B,A. The two floating point double words are deleted.

Stack opcode: 50 Indicators: CCC Traps: STUN

Position

Alternate Position

Alternate Position FADD Floating add. The two floating point numbers contained in the top four words of the stack are added in floating point form. The top four words of the stack are deleted and the two-word sum is pushed onto the stack.

Instruction Commentary 2.

Stack opcode: 51

Indicators: CCA, Overflow Traps: STUN, ARITH

FSUB Floating subtract. The floating point number contained in the top two words of the stack is subtracted in floating point form from the floating point number contained in the third and fourth words of the stack. The top four words of the stack are deleted and the two-word differ-

ence is pushed onto the stack. Instruction Commentary 2.

Stack opcode: 52

Indicators: CCA, Overflow Traps: STUN, ARITH

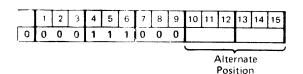

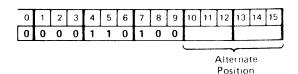

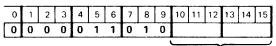

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13   | 14 | 15 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|------|----|----|

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |    |    |    |      |    |    |

|   |   |   |   |   |   |   |   |   | , | _  |    |    | rnat |    |    |

**FMPY**

Floating multiply. The two floating point numbers contained in the top four words of the stack are multiplied in floating point form. The top four words of the stack are deleted and the two-word result is pushed onto the stack.

Instruction Commentary 2. Stack opcode: 53 Indicators: CCA, Overflow Traps: STUN. ARITH 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0 0 0 0 0 1 0 1 0 1 1

Alternate

Position

Indicators: CCA, Overfli Traps: STUN, ARITH

FDIV Floating divide. The floating point number contained in the third and fourth words of the stack is divided by the floating point number contained in the top two words of the stack. The top four words of the stack are deleted and the two-word quotient is pushed onto the stack.

Instruction Commentary 2. Stack opcode: 54 Indicators: CCA, Overflow Traps: STUN, ARITH

FNEG Floating negate. The floating point number contained in the top two words of the stack is negated in floating point form.

Stack opcode: 55 Indicators: CCA Traps: STUN

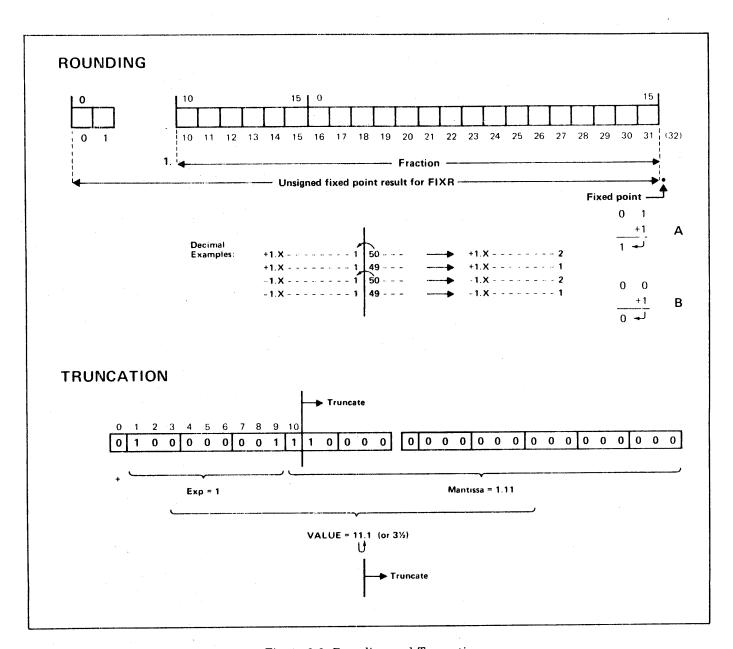

Fix and round. The floating point number contained in the top two words of the stack is converted to fixed point form and rounded to the nearest double word integer. Carry is cleared if the low order 16 bits of the double word result (TOS) represent the true integer value (i.e., if the high order 17 bits are either all zeros or all ones); otherwise Carry is set.

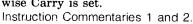

Instruction Commentaries 1 and 2.

Stack opcode: 70

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

FIXT

Fix and truncate. The floating point number contained in the top two words of the stack is converted to fixed point form and truncated to a double word integer. Carry is cleared if the low order 16 bits of the double word result (TOS) represent the true integer value (i.e., if the high order 17 bits are either all zeros or all ones); otherwise Carry is set.

Stack opcode: 71

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

### LOGICAL INSTRUCTIONS

**LCMP**

LSUB

Logical compare. The Condition Code is set to pattern C as a result of the comparison of the second word of the stack with the TOS. The two words are then deleted from the stack.

Stack opcode: 57 Indicators: CCC

Traps: STUN

LADD Logical add. The top two words of the stack are added as 16-bit positive integers, and they are deleted from the stack. The resulting sum is pushed onto the stack.

Stack opcode: 60

Indicators: CCA (as a 2's complement result), Carry

Traps: STUN

Logical subtract. The top word of the stack is subtracted in logical form from the second word and they are de-

leted. The resulting difference is pushed onto the stack.

Stack opcode: 61

Indicators: CCA (as a 2's complement result), Carry

Traps: STUN

LMPY Logical multiply. The top two words of the stack are multiplied as 16-bit positive integers. The words are

replaced by the double length product with the least significant half on the TOS. Carry is cleared if the TOS word of the result represents the true integer value (i.e., if the high order 16 bits are all zeros); otherwise, Carry is

Instruction Commentary 1.

Stack opcode: 62

Indicators: CCA (as a 2's complement result), Carry

Traps: STUN

LDIV Logical divide. The 32-bit positive integer in the second and third words of the stack is divided by the 16-bit positive integer on the TOS (C,B ÷ A). The top three words are deleted. The quotient is pushed onto the stack (B) and then the remainder (A). If overflow occurs, the quotient will be modulo 216.

Stack opcode: 63

Indicators: CCA on quotient (as a 2's complement result),

Overflow

Trap: STUN, ARITH

Position

Position

NOT One's complement. The top word of the stack is converted to its one's complement.

Stack opcode: 64 Indicators: CCA Traps: STUN, ARITH

### **BOOLEAN INSTRUCTIONS**

OR Logical OR. The top two words of the stack are merged by a logical inclusive-OR. The two words are deleted and the result is pushed onto the stack.

Stack opcode: 65

Indicators: CCA on the new TOS

Traps: STUN

XOR Logical exclusive-OR. The top two words of the stack are combined by a logical exclusive-OR. The two words are deleted and the result is pushed onto the stack.

Stack opcode: 66

Indicators: CCA on the new TOS

Traps: STUN

AND Logical AND. The top two words of the stack are combined by a logical AND. The two words are deleted and the result is pushed onto the stack.

Stack opcode: 67

Indicators: CCA on the new TOS

Traps: STUN

Alternate Position

Alternate Position

### INCREMENT/DECREMENT INSTRUCTIONS

INCX Increment X. The content of the Index register is incremented by one in integer form.

Stack opcode: 04

Indicators: CCA, Carry, Overflow

Traps: ARITH

DECX Decrement X. The content of the Index register is decremented by one in integer form.

Stack opcode: 05

Indicators: CCA, Carry, Overflow

Traps: ARITH

INCA Increment A. The TOS is incremented by one in integer form.

Stack opcode: 33

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

DECA Decrement A. The TOS is decremented by one in integer form.

Stack opcode: 34

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

INCB Increment B. The second word of the stack is incremented by one in integer form. The TOS is unaffected.

Stack opcode: 73

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

Alternate Position

Position

Alternate Position

Alternate Position DECB Decrement B. The second word of the stack is decremented by one in integer form. The TOS is unaffected.

Stack opcode: 74

Indicators: CCA, Carry, Overflow

Traps: STUN, ARITH

### INDEX INSTRUCTIONS

STBX Store B into X. The second word of the stack replaces the content of the Index register.

Stack opcode: 26

Indicators: CCA, on the new X

Traps: STUN

ADAX Add A to X. The TOS is added in integer form to the content of the Index register. The sum replaces the content of the Index register, and the TOS is deleted.

Stack opcode: 36

Indicators: CCA on the new X, Carry, Overflow

Traps: STUN, ARITH

ADXA Add X to A. The content of the Index register is added to the TOS, and the sum replaces the TOS.

Stack opcode: 37

Indicators: CCA on the new TOS, Carry, Overflow

Traps: STUN, ARITH

LDXB Load X into B. The second word of the stack is replaced by the content of the Index register. The TOS is unaffected.

Stack opcode: 42

Indicators: CCA on the new B

Traps: STUN

STAX Store A into X. The TOS replaces the content of the Index register, and TOS is deleted from the stack.

Stack opcode: 43

Indicators: CCA on the new X

Traps: STUN

LDXA Load X onto stack. The content of the Index register is pushed onto the stack.

Stack opcode: 44

Indicators: CCA on to the new TOS

Traps: STOV

ADBX Add B to X. The second word of the stack is added in integer form to the content of the Index register, and the result replaces the content of the Index register.

Stack opcode: 76

Indicators: CCA on the new X, Carry, Overflow

Traps: STUN, ARITH

ADXB Add X to B. The content of the Index register is added in integer form to the second word of the stack, and the sum replaces the second word of the stack.

Stack opcode: 77

Indicators: CCA on the new B, Carry, Overflow

Traps: STUN, ARITH

Alternate Position

Position

Position

### **EXCHANGE INSTRUCTIONS**

DXCH Double exchange. The top two doubleword pairs are in-

terchanged on the stack.

Stack opcode: 16

Indicators: CCA on the new TOS double word

Traps: STUN

XCH Exchange A and B. The top two words of the stack are

interchanged.

Stack opcode: 32

Indicators: CCA on the new TOS

Traps: STUN

XAX Exchange A and X. The content of the TOS and the Index

register are interchanged.

Stack opcode: 35

Indicators: CCA on the new TOS

Traps: STUN

CAB Rotate A,B,C. The third word of the stack is removed from the stack, the two top words are compressed onto

the rest of the stack, and the original third word is pushed onto the stack.

Stack opcode: 56

Indicators: CCA on the new TOS

Traps: STUN

XBX Exchange B and X. The second word of the stack is

interchanged with the content of the Index register.

Stack opcode: 75 Indicators: unaffected

Traps: STUN

Position

Alternate Position

Alternate Position

Alternate Position

Alternate Position

### **ZERO INSTRUCTIONS**

ZROX Zero X. The content of the Index register is replaced by

zero.

Stack opcode: 03 Indicators: unaffected

Traps: None

YERO Push zero. A zero word is pushed onto the stack.

Stack opcode: 06 Indicators: unaffected

Traps: STOV

'RO Push double zero. Two words containing all zeros are pushed onto the stack.

Stack opcode: 07 Indicators: unaffected Traps: STOV

ZROB Zero B. The second word of the stack is replaced by zero.

The TOS is unaffected.

Stack opcode: 41 Indicators: unaffected

Traps: STUN

Alternate Position

Alternate Position

Alternate Position

Alternate Position

### **DUPLICATE AND DELETE INSTRUCTIONS**

DELB Delete B. The second word of the stack is deleted and the

stack is compressed. The content of the TOS is

unchanged.

Stack opcode: 01 Indicators: unaffected

Traps: STUN

DDEL Double delete. The top two words of the stack are deleted.

Stack opcode: 02 Indicators: unaffected

Traps: STUN

DEL Delete A. The top word of the stack is deleted.

Stack opcode: 40 Indicators: unaffected

Traps: STUN

DUP Duplicate A. The top word of the stack is duplicated by

pushing a copy of the TOS onto the stack.

Stack opcode: 45 Indicators: CCA Traps: STUN, STOV

DDUP Double duplicate. The double word in the top two words of the stack is duplicated by pushing a copy of it onto the

stack.

Stack opcode: 46

Indicators: CCA on new TOS double word

Traps: STUN, STOV

Alternate Position

Alternate Position

Position

Position

### **TEST INSTRUCTIONS**

TEST Test TOS. The condition code is set to pattern A according to the content of the TOS word.

Stack opcode: 25

Indicators: CCA Traps: STUN

DTST Test double word on TOS. The condition code is set to pattern A according to the contents of the top two words of the stack. Also, Carry is cleared if the low order 16 bits of the doubleword result (TOS) represent the true integer value (i.e., if the high order 17 bits are either all zeros or all ones); otherwise, Carry is set.

Instruction Commentary 1. Stack opcode: 27

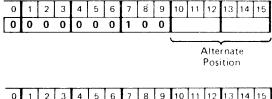

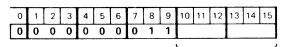

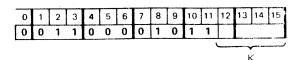

0 1 2 3 4 5 6 7 8 9 10 11 12 13 1

0 0 0 0 0 1 0 1 1 1 1

Alternate Position

Indicators: CCA, Carry Traps: STUN

BTST Test byte on TOS. The Condition Code is set to pattern B according to the contents of the byte contained in the eight least significant bits of the TOS word (bits 8-15).

Stack opcode: 31 Indicators: CCB Traps: STUN

#### NO OP INSTRUCTION

NOP

No operation. The user's program space and data space remain unchanged.

Stack opcode: 00 Indicators: unaffected

Traps: None

### SHIFT INSTRUCTIONS

### SINGLE WORD SHIFT INSTRUCTIONS

All single word shift instructions: Instruction Commentary 3.

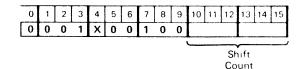

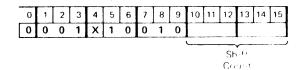

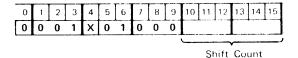

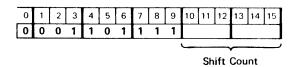

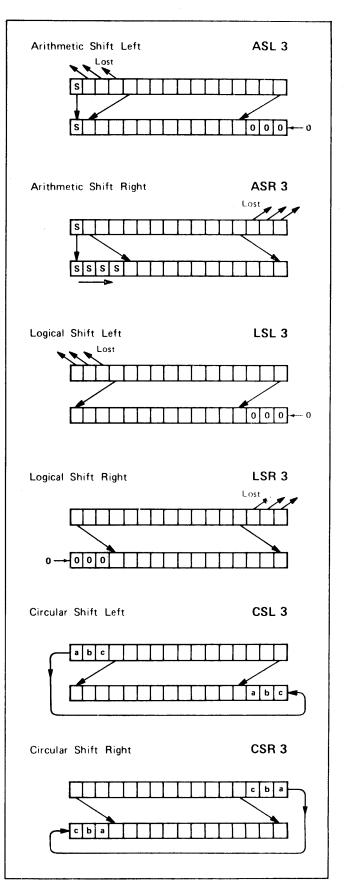

ASL

ASR

Arithmetic shift left. The TOS is shifted left n bits, preserving the sign bit. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified (bit 4), the content of the Index register.

Sub-opcode 1: 00 Indicators: CCA Traps: STUN

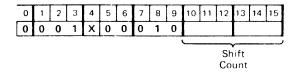

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0 0 0 1 X 0 0 0 0 0 0

Shift

Count

rraps:

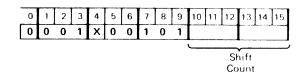

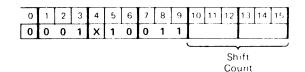

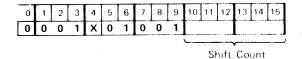

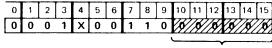

Arithmetic shift right. The TOS is shifted right n places, propagating the sign bit. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

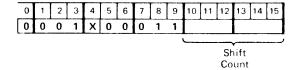

Sub-opcode 1: 01 Indicators: CCA Traps: STUN 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0 0 0 1 X 0 0 0 0 1

Shift

Count

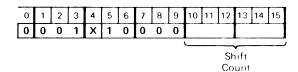

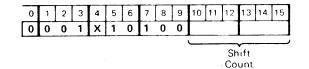

LSL Logical shift left. The TOS

Logical shift left. The TOS is shifted left n bits logically. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 02 Indicators: CCA Traps: STUN

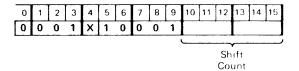

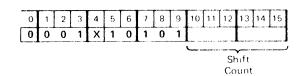

LSR Logical shift right. The TOS is shifted right n bits logically. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 03 Indicators: CCA Traps: STUN

CSL Circular shift left. The TOS is shifted left n bits circularly. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 04 Indicators: CCA Traps: STUN

CSR

Circular shift right. The TOS is shifted right n bits circularly. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 04 Indicators: CCA Traps: STUN

### **DOUBLE WORD SHIFT INSTRUCTIONS**

All double word shift instructions: Instruction Commentaries 3 and 4.

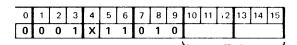

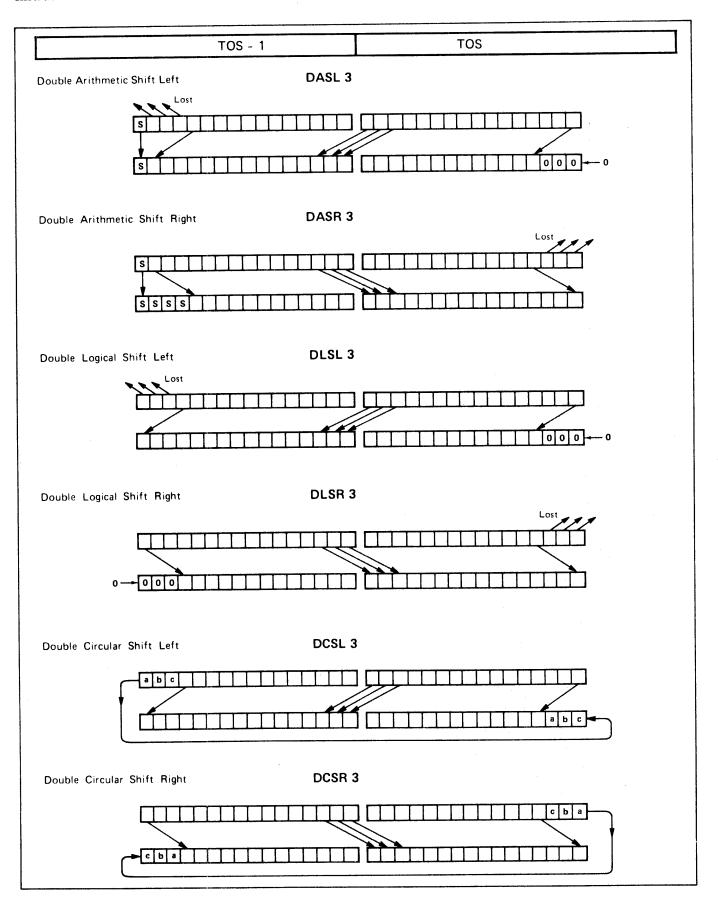

DASL

Double arithmetic shift left. The double word contained in the top two words of the stack is shifted left n bits, preserving the sign bit (bit 0 of B). The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 20 Indicators: CCA Traps: STUN

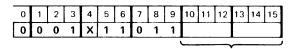

DASR

Double arithmetic shift right. The double word contained in the top two words of the stack is shifted right n bits, propagating the sign bit (bit 0 of B). The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 21 Indicators: CCA Traps: STUN

DLSL

Double logical shift left. The double word contained in the top two words of the stack is shifted left n bits logically. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 22 Indicators: CCA Traps: STUN

DLSR

Double logical shift right. The double word contained in the top two words of the stack is shifted right n bits logically. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 23 Indicators: CCA Traps: STUN

DCSL

Double circular shift left. The double word contained in the top two words of the stack is shifted left n bits circularly. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 24 Indicators: CCA Traps: STUN

DCSR Double circular shift right. The double word contained in the top two words of the stack is shifted right n bits circularly. The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 25 Indicators: CCA Traps: STUN

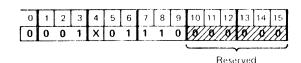

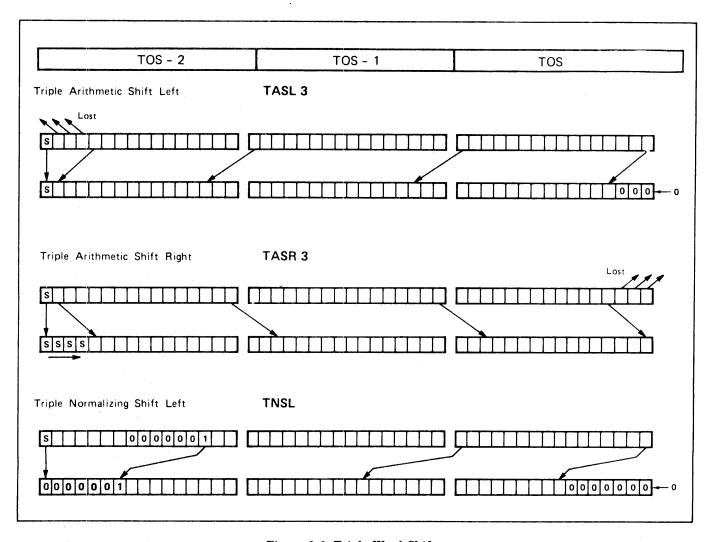

#### TRIPLE WORD SHIFT INSTRUCTIONS

All triple word shift instructions: Instruction Commentaries 3 and 5.

TASL Triple arithmetic shift left. The triple word integer contained in the top three words of the stack is shifted left n bits, preserving the sign bit (bit 0 of C). The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 10

Indicators: CCA on the new TOS triple word

Traps: STUN

TASR Triple arithmetic shift right. The triple word integer contained in the top three words of the stack is shifted right n bits, propagating the sign bit (bit 0 of C). The value of n (modulo 64) is the number specified in the argument field plus, if X is specified, the content of the Index register.

Sub-opcode 1: 11

Indicators: CCA on the new TOS triple word

Traps: STUN

TNSL Triple normalizing shift left. The top three words of the stack are shifted left arithmetically until bit 6 of C is a "1". Bits 0 through 5 of C are cleared ("0"). The shift count is stored in the Index register. The instruction initially clears the Index register unless X is specified ("1" in bit 4 of the instruction).

Sub-opcode 1: 16

Indicators: CCA on final value of top three words

Traps: STUN

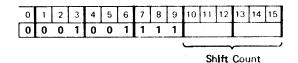

### QUADRUPLE WORD SHIFT INSTRUCTIONS

Quadruple word shift instructions: Instruction Commentaries 3 and 6.

QASL Quadruple arithmetic shift left. The four-word integer contained in the top four words of the stack is shifted left n bits, preserving the sign (bit 0 of word D). The value of n (modulo 64) is the number specified in the shift count plus the contents of the Index register.

Sub-opcode 1: 17, bit 4 = 0

Indicators: CCA on the new TOS quadruple word

Traps: STUN

QASR Quadruple arithmetic shift right. The four-word integer contained in the top four words of the stack is shifted right n bits, preserving the sign (bit 0 of word D). The value of n (modulo 64) is the number specified in the shift count plus the contents of the Index register.

Sub-opcode 1: 17, bit 4 = 1

Indicators: CCA on the new TOS quadruple word

Traps: STUN

### FIELD AND BIT INSTRUCTIONS

SCAN

Scan bits. The TOS is shifted left until bit 0 contains a "1", then is shifted left one more bit. The shift count is left in the Index register, indicating the bit position which contained the "1". The instruction normally sets the Index register to -1 before beginning the shifts. However, if X is specified, the shift count adds on to the existing Index register content. If TOS is all zeros, the count will be 16 if unindexed, or X + 16 if indexed.

Sub-opcode 1: 06

Indicators: CCA on final TOS

Traps: STUN

TBC

Test bit and set Condition Code. One bit of the TOS word is tested and the Condition Code is set to a special pattern depending on the state of the bit. The bit position to be tested is specified by the argument field of the instruction plus, if X is specified, the content of the Index register. If the number specified exceeds 15, the bit position indicated is modulo 16; e.g., bit 0 is tested for counts of 0, 16, 32, 48, etc.

Sub-opcode 1: 32

Indicators: CCE if the bit was "0"

CCL or CCG if the bit was "1"

Traps: STUN

TRBC

Test and reset bit, set Condition Code. The operation of this instruction is identical to that of TBC except that the tested bit is reset to "0" after the test.

Sub-opcode 1: 33

Indicators: CCE if the bit was "0"

CCL or CCG if the bit was "1"

Traps: STUN

$\mathbf{TSBC}$

Test and set bit, set Condition Code. The operation of this instruction is identical to that of TBC except that the tested bit is set to "1" after the test.

Sub-opcode 1: 34

Indicators: CCE if the bit was "0"

CCL or CCG if the bit was "1"

Traps: STUN

Reserved

Bit Position

Bit Position

Bit Position

TCBC

Test and complement bit, set Condition Code. The operation of this instruction is identical to that of TBC except that the tested bit is complemented after the test.

Sub-opcode 1: 35

Indicators: CCE if the bit was "0"

CCL or CCG if the bit was "1"

Traps: STUN

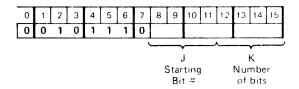

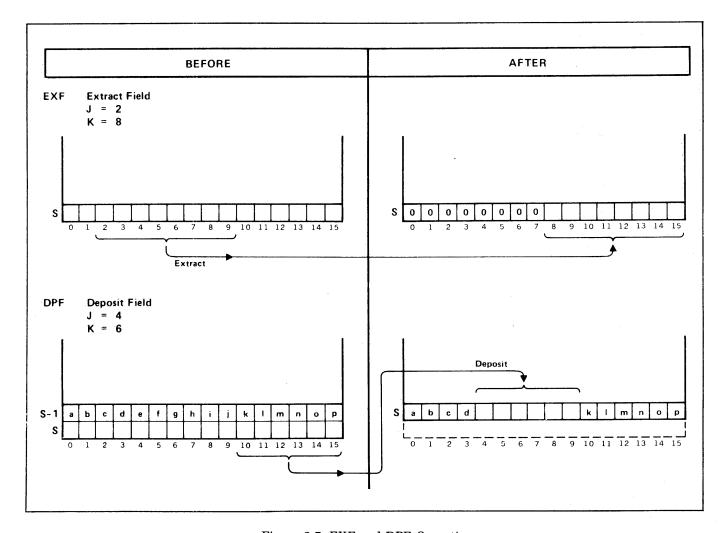

$\mathbf{E}\mathbf{X}\mathbf{F}$

Extract field. A specified set of bits in the TOS are extracted and right justified, and the result, with high order zeros, replaces the TOS. The J field specifies the starting (leftmost) bit number in the source field, and the K field specifies the number of bits to be extracted.

Instruction Commentary 7 Sub-opcode 2: 15

Indicators: CCA on the new TOS

Traps: STUN

DPF

Deposit field. A specified number of the least significant bits of the TOS are deposited in the second word of the stack, beginning at the bit number specified by the J field; the remaining bits of the second word of the stack are unchanged. The K field specifies the number of bits to be deposited. The source operand is deleted from the stack.

Instruction Commentary 7 Sub-opcode 2: 16

Indicators: CCA on the new TOS

Traps: STUN

Starting Number Bit # of bits

### **BRANCH INSTRUCTIONS**

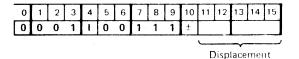

IABZ

Increment A, branch if zero. The TOS is incremented. If the result is then zero, control is transferred to P  $\pm$  displacement; otherwise to P+1.

Sub-opcode 1: 07

Indicators: CCA, Carry, Overflow Addressing modes: P relative (+/-)

Direct or indirect

Traps: STUN, BNDV if user or privileged, ARITH

IXBZ

Increment X, branch if zero. The Index register is incremented if the result is then zero, control is transferred to  $P\pm$  displacement; otherwise to P+1.

Sub-opcode 1: 12

Indicators: CCA, Carry, Overflow Addressing modes: P relative (+/-)

Direct or indirect

Traps: BNDV if user or privileged, ARITH

DXBZ

Decrement X, branch if zero, The Index register is decremented. If the result is then zero, control is transferred to  $P\pm$  displacement; otherwise to P+1.

Sub-opcode 1: 13

Indicators: CCA, Carry, Overflow Addressing modes: P relative (+/-)

Direct or indirect

Traps: BNDV if user or privileged, ARITH

Displacement

DABZ Decrement A, branch if zero. The TOS is decremented. If the result is then zero, control is transferred to P  $\pm$ displacement; otherwise to P+1. Sub-opcode 1: 27 Displacement Indicators: CCA, Carry, Overflow Addressing modes: P relative (+/-)Direct or indirect Traps: STUN, BNDV if user or privileged, ARITH **BCY** Branch on carry. If the Carry bit of the Status register is 8 9 set ("1"), control is transferred to P ± displacement; otherwise to P+1. Sub-opcode 1: 14 Displacement Indicators: Carry cleared Addressing modes: P relative (+/-)Direct or indirect Traps: BNDV if user or privileged **BNCY** Branch on no carry. If the Carry bit of the Status register 8 9 10 11 12 is clear ("0"), control is transferred to  $P \pm displacement$ : otherwise to P+1. Sub-opcode 1: 15 Displacement Indicators: Carry cleared Addressing modes: P relative (+/-)Direct or indirect Traps: BNDV if user or privileged BOV Branch on overflow. If the Overflow bit of the Status 8 register is set ("1"), control is transferred to P± displacement; otherwise to P+1. Sub-opcode 1: 30 Displacement Indicators: Overflow cleared Addressing modes: P relative (+/-) Direct or indirect Traps: BNDV if user or privileged **BNOV** Branch on no overflow. If the Overflow bit of the Status register is clear ("0"), control is transferred to P ± dis-0 placement; otherwise to P+1. Sub-opcode 1: 31 Displacement Indicators: Overflow cleared Addressing modes: P relative (+/-)Direct or indirect Traps: BNDV if user or privileged **BRO** Branch on TOS odd. If the TOS is odd (bit 15 = 1), control 8 9 is transferred to  $P \pm displacement$ ; otherwise to P+1. The TOS is deleted. Sub-opcode 1: 36 Displacement Indicators: unaffected Addressing modes: P relative (+/-)Direct or indirect Traps: STUN, BNDV if user or privileged Branch to TOS even. BRE

| Branch to $105$ even. If the $105$ is even (bit $15 = 0$ ),   |  |

|---------------------------------------------------------------|--|

| control is transferred to $P \pm displacement$ ; otherwise to |  |

| P+1. The TOS is deleted.                                      |  |

P+1. The TOS Sub-opcode 1: 37

Indicators: unaffected

Addressing modes: P relative (+/-)

Direct or indirect

Traps: STUN, BNDV if user or privileged

**CPRB**

Compare range and branch. The integer in the Index register is tested to determine if it is within the interval defined by the upper bound integer on the TOS and the lower bound integer in the second word of the stack. The Condition Code is set by the comparison to a special pattern: CCE if within range, CCL if below range, CCG if above range. If the integer in the Index register is within the specified range, control is then transferred to P  $\pm$  displacement; otherwise to P+ 1. The top two elements of the stack are deleted in either case.

Sub-opcode 1: 26

Indicators: CCE, CCL, CCG

Addressing modes: P relative (+/-)

Direct or indirect

Traps: STUN, BNDV if user or privileged

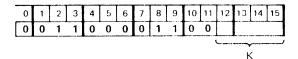

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 0 0 1 1 1 0 1 1 0 ±

Displacement

BR Branch unconditionally. For P relative mode, control is transferred unconditionally to P ± displacement, plus (if specified) the value in X; may be indirect. For DB, Q, and S relative modes, control is transferred indirectly (only) via the location specified by DB, Q, or S ± this displacement; the content of the location so specified is added to

ment; the content of the location so specified is added to PB (plus post-indexing if X is specified) to obtain the effective address for P.

Instruction Commentary 8

Memory opcode: 14, bits 5, 6 = 00, 10, or 11

Indicators: unaffected

Addressing modes: P relative (+/-), direct or indirect

DB+ relative, indirect Q+ relative, indirect Q- relative, indirect S- relative, indirect Indexing available

Traps: BNDV, BNDV on P and P relative if user or

privileged

BCC Branch on Condition Code. The Condition Code in the Status register is compared with conditions named in the CCF field of the instruction. If the named conditions are met, control is transferred to  $P \pm displacement$ ; otherwise to P+1. The displacement is limited to  $\pm 31$ . Control is transferred to the branch address under the following conditions:

If CCF = 0, never branch

= 1, branch if CC = CCL

= 2, branch if CC = CCE

= 3, branch if CC = CCL or CCE

= 4, branch if CC = CCG

= 5, branch if CC = CCG or CCL

= 6, branch if CC = CCG or CCE

= 7, always branch

Memory opcode: 14, bits 5.6 = 01

Indicators: unaffected

Addressing modes: P relative (+/-)

Direct or indirect

Traps: BNDV if user or privileged

### MOVE INSTRUCTIONS

#### NOTE

All Move instructions are interruptable after each word (or byte) transfer and will continue from the point of interrupt when control is returned to the instruction.

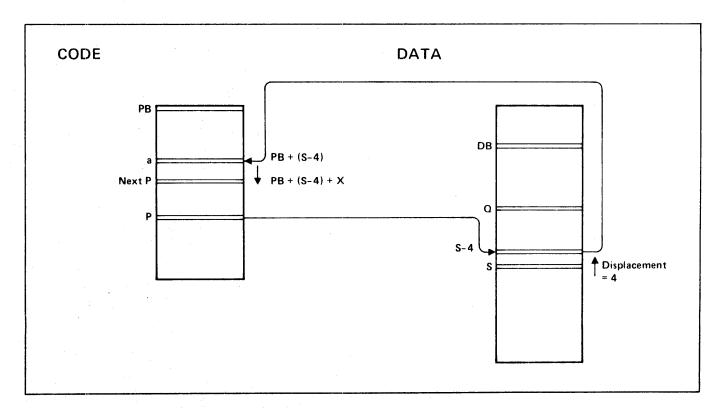

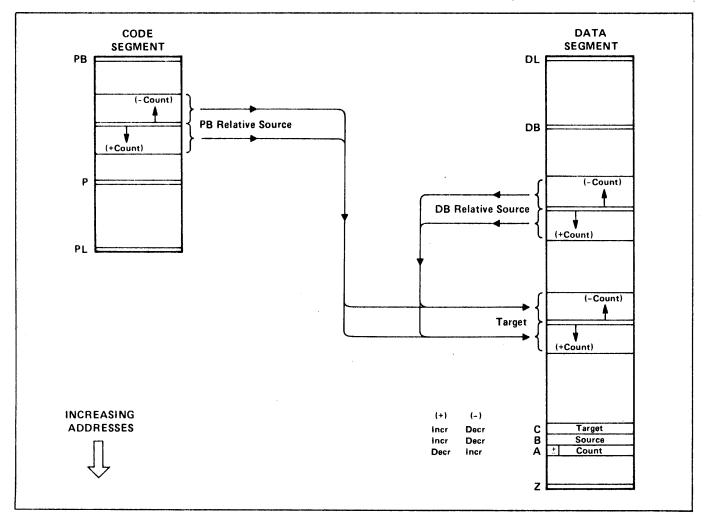

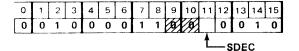

MOVE

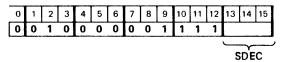

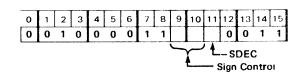

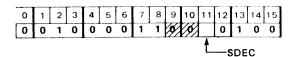

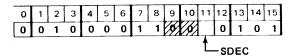

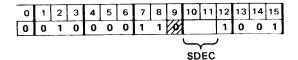

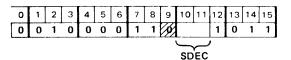

Move words. This instruction transfers a specified number of words from one area of primary memory to another. The instruction expects a signed word count in A, a DB or PB relative displacement for a source address in B, and a DB relative displacement for a target address in C. As long as the word count in A has not been counted to zero, the transferring of data will continue as follows: The content of the memory location specified by DB + B or PB + B is transferred to the location specified by DB + C. If the word count in A is positive, the source and target displacement values in B and C are incremented by one on each transfer, and the word count is decremented by one. If the word count in A is negative, the source and target displacement values in B and C are decremented by one on each transfer, and the word count is incremented by one. Note that the word count is always changed by one toward zero. On completion of the block transfer, the instruction deletes from the stack the number of words specified by the SDEC (S decrement) field of the instruction; the range of this field is 0 through 3.

Instruction Commentary 9 Move opcode: 0 Indicators: unaffected

Addressing modes: DB+ or PB+ for source

DB+ for target

Traps: STUN, STOV, BNDV, BNDV on P relative if user or

privileged

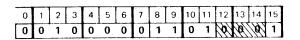

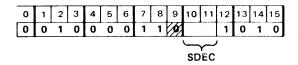

MVB

Move bytes. The MVB instruction transfers a specified number of bytes from one area of primary memory to another. The instruction expects a signed byte count in A, a DB or PB relative displacement for a source byte address in B, and a DB relative displacement for a target byte address in C. As long as the word count in A has not been counted to zero, the transferring of data will continue as follows: The content of the byte address location specified by DB + B or PB + B is transferred to the byte address location specified by DB + C. If the byte count in A is positive, the source and target displacement values in B and C are incremented by one on each transfer, and the byte count is decremented by one. If the byte count in A is negative, the source and target displacement values in B and C are decremented by one on each transfer, and the byte count is incremented by one. Note that the byte count is always changed by one toward zero. On completion of the block transfer, the instruction deletes from the stack the number of words (0, 1, 2, or 3) specified by the SDEC field of the instruction.

Instruction Commentary 9

Move opcode: 1 Indicators: unaffected

Addressing modes: Byte addressing

DB+ or PB+ for source

DB+ for target

Traps: STUN, STOV, BNDV, BNDV on P relative if user or

privileged

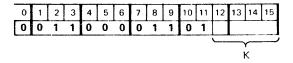

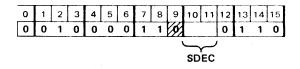

MVBW

Move bytes while of specified type. This instruction transfers an unspecified number of bytes from one area of primary memory to another. The instruction expects a source byte address in the TOS and a DB relative displacement for a target byte address in the second word of the stack. As long as the source byte is of the type specified in the CCF field, it is moved to the target area. The target displacement value in B is incremented by one on each transfer. If the byte to be moved is a lower case letter and the upshift bit is on, the target byte will be an upshifted copy of the source byte. Byte transfers continue until the source byte is not of the proper type. On completion of the block transfer, the instruction deletes from the stack the number of words (0, 1, 2, or 3) specified by the SDEC field of the instruction.

Instruction Commentary 9

Move opcode: 4

Indicators: CCB on the last character scanned Addressing mode: Byte addressing, DB+

Traps: STUN, STOV, BNDV

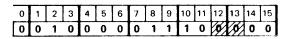

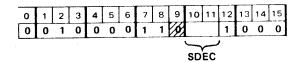

CMPB

Compare bytes. This instruction scans two byte strings simultaneously until the compared bytes are unequal or until a specified number of comparisons have been made. CMPB expects a signed byte count in A, a DB or PB relative displacement for a source byte address in B, and a DB relative displacement for a target byte address in C. As long as the word count in A has not been counted to zero, the comparison proceeds as follows: The content of the byte address location specified by DB + B or PB + B is compared with the content of the byte address location specified by DB + C. If the byte count in A is positive, the source and target displacement values in B and C are incremented by one after each comparison, and the byte count is decremented by one. If the byte count in A is negative, the source and target displacement values in B and C are decremented by one after each comparison, and the byte count is incremented by one. Note that the byte count is always changed by one toward zero. The instruction terminates when either a comparison fails or the byte count in the TOS reaches zero. The Condition Code is set to a special pattern to indicate the terminating condition. On termination, the instruction deletes from the stack the number of words (0, 1, 2, or 3) specified by the SDEC field of the instruction.

Instruction Commentary 9

Move opcode: 5

Indicators: CCE if byte count = 0

CCG if target byte > source byte (final) CCL if target byte < source byte (final)

Addressing modes: Byte addressing

DB+ or PB+ for source

DB+ for target

Traps: STUN, STOV, BNDV, BNDV on P relative if user or

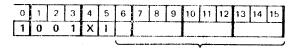

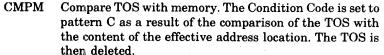

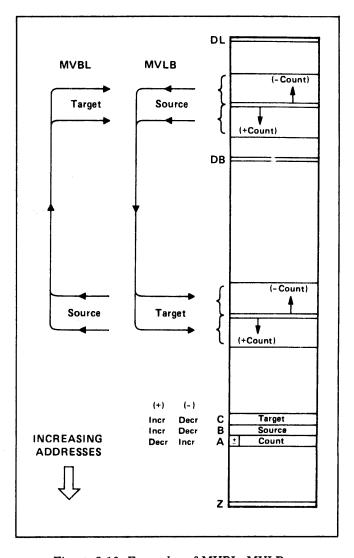

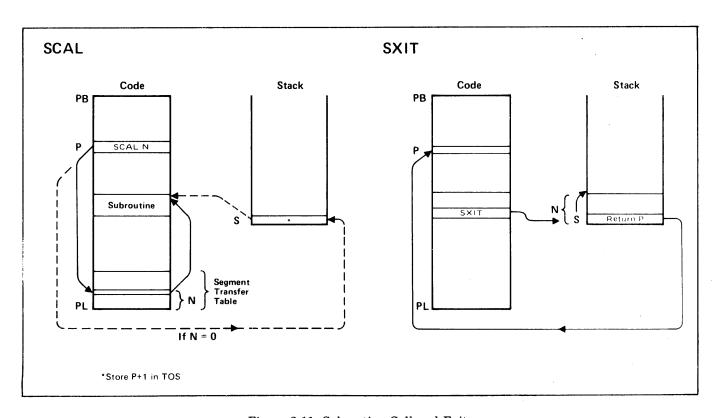

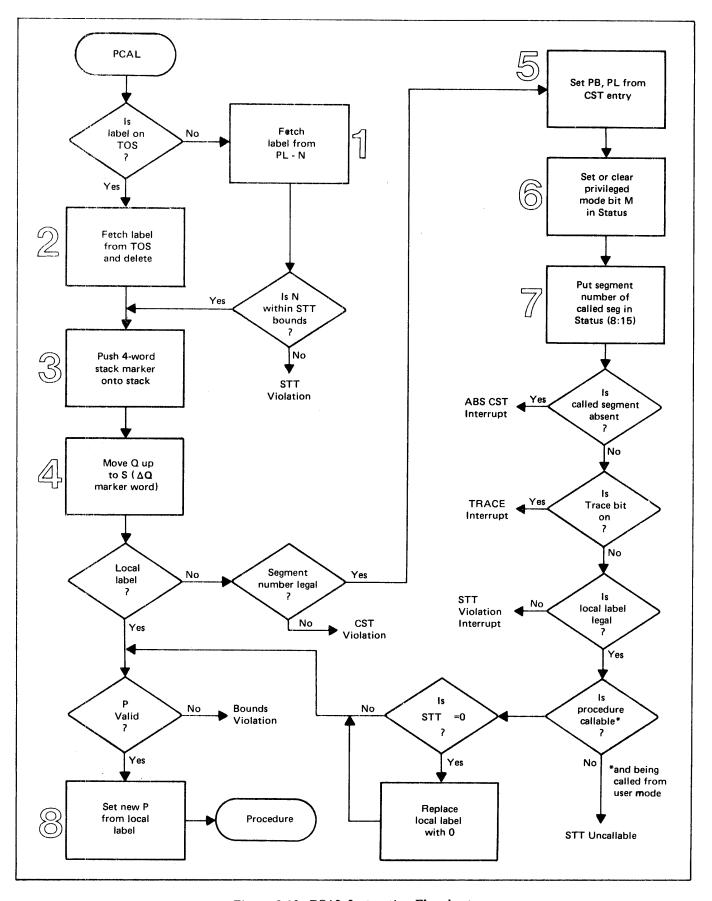

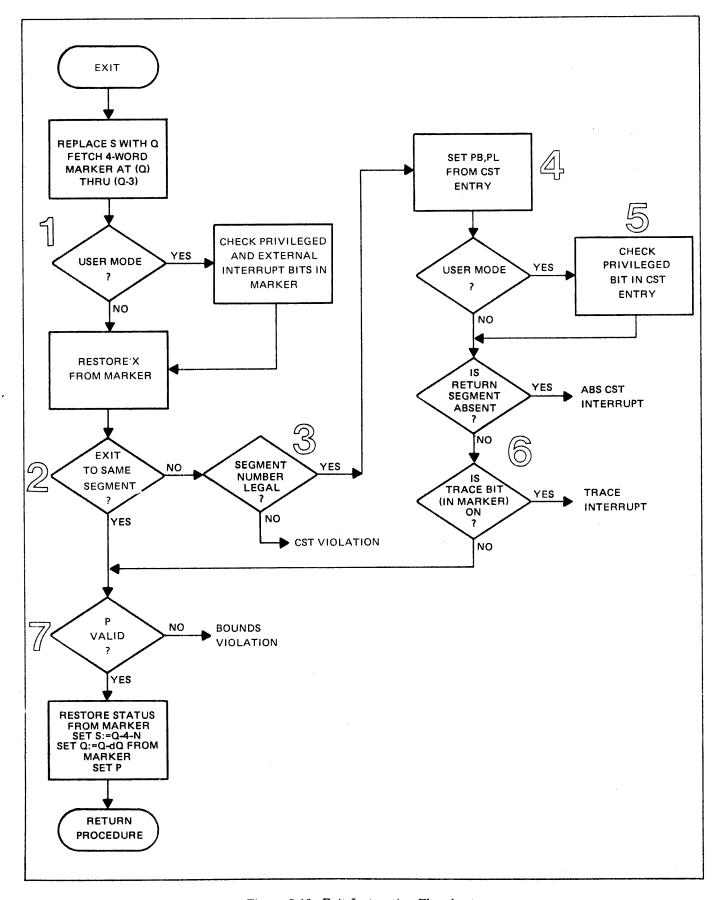

privileged