## HEWLETT PACKARD

# **Series 37 System Processing Unit**

Self-Paced Hardware Training Guide

# HP 3000 Computer Systems Series 37 System Processing Unit

Self-Paced Hardware Training Guide

June, 1984

Computer Support Division 19310 Pruneridge Avenue Cupertino, CA 95014

#### **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

The software code printed alongside the date indicates the version level of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

First Edition...... June 1984

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company.

# **Table of Contents**

|                                                 | Page        |                                 | Page |

|-------------------------------------------------|-------------|---------------------------------|------|

| Introduction                                    | _ i         | Retry Auto-Restart              | 3-9  |

| Prerequisites                                   | _ i         | Load/Start                      | 3-9  |

| Course Objectives                               | _ i         | Dump                            | 3-10 |

| Materials Needed to Take This Course            |             | Help                            |      |

| How to Use This Guide                           |             | Run                             | 3-11 |

| Course Structure                                |             | Speed                           | 3-1  |

| Course Completion Checklist                     |             | Test                            | 3-11 |

|                                                 |             | Test Mode                       | 3-12 |

| Lesson 1                                        |             | Lesson 3 Quiz                   |      |

| Getting Acquainted with the Series 37 SPU       |             | Console Operation Lab           | 3-15 |

| Overview                                        | 1-1         | Maintenance Microcode Lab       | 3-10 |

| Learning Objective                              |             |                                 |      |

| Introduction                                    |             | Lesson 4                        |      |

| Lesson 1 Quiz                                   | 1-4         | Removal and Replacement         |      |

| Lesson I Quiz                                   |             | Overview                        | 4-:  |

| T 0                                             |             | Learning Objectives             | 4-1  |

| Lesson 2                                        |             | Rear Panel                      | 4-2  |

| Installing the Series 37 SPU                    | 2.1         | Removal                         |      |

| Overview                                        | _ 2-1       | Replacement                     |      |

| Learning Objectives                             | 2-1         | RS-232-C Connector Assembly     |      |

| Introduction                                    | _ 2-1       | RS-232-C Boards                 |      |

| HP 32449A Installation Policy                   | 2-1         | I/O Ground Clips                |      |

| Installation Procedure                          | _ 2-2       | Tubaxial Fan                    |      |

| Single Power Source                             | _ 2-2       | Power Supply                    |      |

| RS-232 Peripherals                              | _ 2-2       | Removal                         |      |

| External HP-IB Peripherals                      | 2-2         | Replacement                     |      |

| Installing the HP 32450A and the I/O Extender _ | _ 2-2       | Power Supply Fuse               |      |

| Serial Port Cabling                             | _ 2-2       | 115/230 VAC Reconfiguration     |      |

| HP-IB Cabling                                   | _ 2-3       |                                 |      |

| AC Power                                        |             | Plug-in Boards                  |      |

| Rules for Configuring the Series 37 Card Cage   | _ 2-4       | Removal                         |      |

| Lesson 2 Quiz                                   | _ 2-5       | Replacement                     |      |

|                                                 |             | Front Panel                     |      |

| Lesson 3                                        |             | Removal                         |      |

| Operating the Series 37 SPU                     |             | Replacement                     |      |

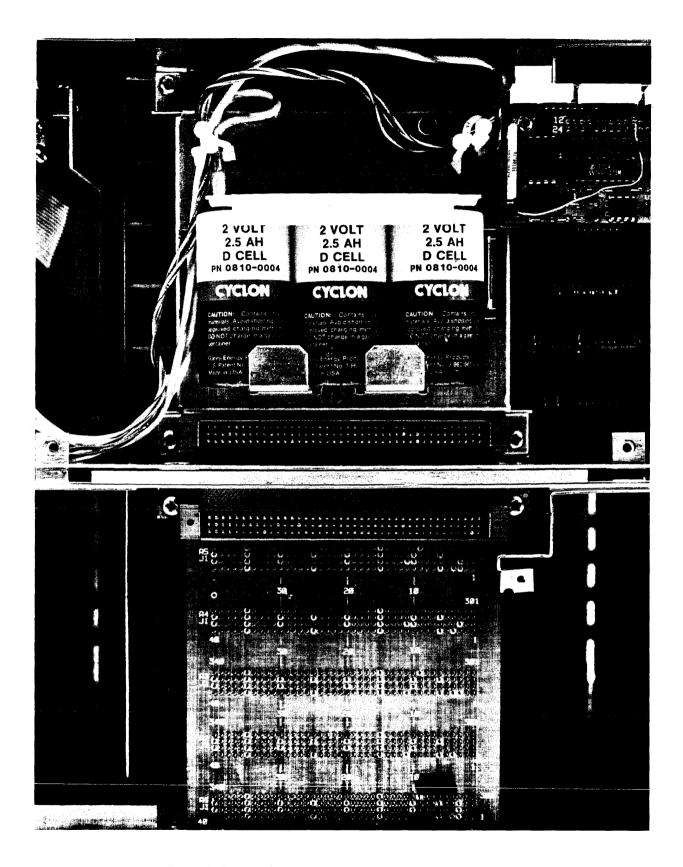

| Overview                                        | _ 3-1       | Battery Pack                    |      |

| Learning Objectives                             | _ 3-1       | Removal                         | 4-1  |

| SPU Front Panel Description                     | 3-1         | Replacement                     |      |

| Front Panel Key Switch                          | _ 3-1       | Battery Holder                  | 4-1  |

| Front Panel Status Indicators                   | 3-1         | Removal                         | 4-1  |

| Front Panel LED                                 | _ 3-2       | Replacement                     | 4-1  |

| I/O Extender Description                        | 3-5         | Backplane                       | 4-1  |

| Comparison of Extender to SPU                   |             | Removal                         | 4-1  |

| Battery Backup                                  |             | Replacement                     | 4-1  |

| I/O Extender Service Note                       |             | Display Panel                   | 4-1  |

| Extender Front Panel Description                |             | Removal                         | 4-17 |

| Minimum Requirements for Terminals              |             | Replacement                     | 4-12 |

| Connecting Hardwired Terminal to Series 37      |             | Display Panel LEDs              | 4-12 |

| Connecting Terminal to Series 37 Modem Port     |             | Mounting Feet                   | 4-1  |

| Maintenance Mode Microcode                      |             | Removal                         | 4-1  |

| Introduction                                    | <del></del> | Replacement                     | 4-1  |

| Microcode Load Sequence                         |             | SPU/Extender Interconnect Cable | 4-1: |

| Power-on Self-Test                              |             | Removal                         | 4-1: |

| Control Module Options                          | 3.0<br>3.0  | Replacement                     | 4-14 |

| Automatic Warmstart                             | 3_0         | -                               |      |

| Automatic warmstart                             |             |                                 |      |

|                                     | Page | i                                                 | Page              |

|-------------------------------------|------|---------------------------------------------------|-------------------|

| SPU Cover Plate                     | 4-14 | Lesson 7                                          |                   |

| Removal                             |      | How the Series 37 SPU Works                       |                   |

| Replacement                         |      | Overview                                          |                   |

| Lesson 4 Quiz                       | 4-16 | Overall Learning Objectives                       |                   |

| Removal and Replacement Lab         | 4-17 | Central Processing Unit (CPU) Description         |                   |

|                                     |      | Learning Objectives                               |                   |

| Lesson 5                            |      | General Description                               |                   |

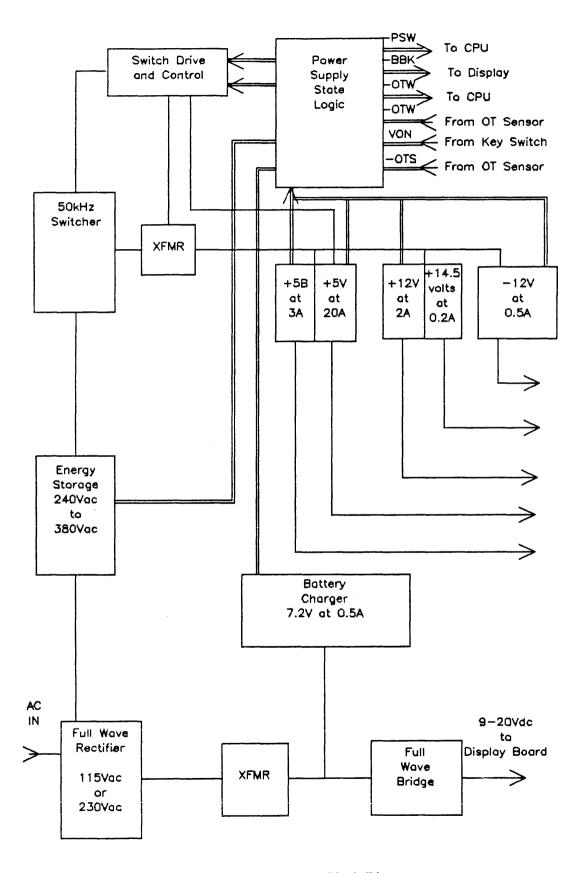

| Power System                        |      | Processor                                         |                   |

| Overview                            |      | Control Store                                     |                   |

| Learning Objectives                 |      | Register File                                     |                   |

| Power System Functional Description |      | Time of Century (TOC) Clock                       |                   |

| General Description                 |      | Interrupt Process                                 | 7-5               |

| DC Overvoltage Protection           |      | Synchronous Intermodule Bus (SIMB)                |                   |

| AC Input Overvoltage Protection     |      | and Monitor                                       |                   |

| Overcurrent Protection              |      | Power Supply Monitor (PSM)                        |                   |

| Overheating Protection              |      | Status Display                                    |                   |

| Fault Resets                        |      | MPE Timer                                         |                   |

| Battery Charger                     |      | Bank Register                                     |                   |

| Battery Backup                      |      | CPU Diagnostic Tools                              |                   |

| Input Power Specifications          |      | CPU Quiz                                          |                   |

| Output Specifications               |      | Memory Board Description                          |                   |

| Output Power Specifications         |      | Learning Objectives                               | . 7-9             |

| Output Control Signals              |      | General Description                               | . 7-9             |

| Power System Timing                 |      | Memory Array Section                              | . 7-9             |

| Signal Line Characteristics         |      | Address Section                                   | . 7-9             |

| Power Supply Diagnostic Tools       | 5-7  | Data Section                                      |                   |

| Lesson 5 Quiz                       | 5-10 | Control Section                                   | . 7-12            |

| Power System Lab                    | 5-11 | Memory Operations                                 | . 7-12            |

|                                     |      | Read (Opcode = 0)                                 | . 7-12            |

| Lesson 6                            |      | Write (Opcode = 1)                                |                   |

| Synchronous Intermodule Bus (SIMB)  |      | Refresh                                           | . 7-13            |

| Overview                            |      | Initialization                                    |                   |

| Learning Objectives                 |      | Memory Logging                                    | . 7-13            |

| Introduction                        |      | Memory Diagnostic Tools                           |                   |

| SIMB Signal Description             |      | Memory Quiz                                       | . 7-15            |

| Opcode Lines                        | 6-2  | Memory Lab                                        | 7-16              |

| Address Lines                       |      | Peripheral Interface Controller (PIC) Description | 7-17              |

| Data Lines                          |      | Learning Objectives                               | _ 7-17            |

| Parity Lines                        |      | General Description                               | 7-17              |

| Module From Lines                   |      | SIMB Interface Logic                              | 7-19              |

| Handshake Lines                     |      | PIC Control Logic                                 | <sub>-</sub> 7-19 |

| Interrupt Lines                     |      | SIMB Control Logic                                | 7-19              |

| Status Lines                        | 6-4  | Internal PIC Requests                             | _ 7-20            |

| Priority Lines                      | 6-4  | Command Execution Logic                           | _ 7-20            |

| Channel Identification Lines        | 6-5  | CSRQ/IRQ Request Logic                            | _ 7-20            |

| Clock Lines                         |      | Configuring the HP-IB                             | _ 7-21            |

| Power Supply Support Lines          | 6-5  | PIC Diagnostic Tools                              | _ 7-21            |

| Bus Monitor Description             | 6-5  | PIC Quiz                                          | _ 7-22            |

| Bus Request Logic                   | 6-5  | PIC Lab                                           |                   |

| Bus Priority                        | 6-7  | Terminal Interface Controller (TIC) Description   |                   |

| I/O System Overview                 | 6-8  | Learning Objectives                               | _ 7-24            |

| Channel Program Execution           | 6-8  | General Description                               | _ 7-24            |

| I/O Usage and Interrupts            | 6-8  | Functional Description                            | _ 7-24            |

| Parallel Poll                       |      | DMA Sequencer                                     | _ 7-26            |

| Lesson 6 Quiz                       | 6-10 | Data Store                                        | _ 7-27            |

|                                     |      | L-BUS                                             | _ 7-27            |

|                                              | Page        |                                                                |             |

|----------------------------------------------|-------------|----------------------------------------------------------------|-------------|

| B-Bus State Machine (BBUSSM)                 | 7-27        | Test Section 3                                                 | A-2         |

| Port Controller Chips (PCC)                  | 7-27        | Test Section 4                                                 | A-2         |

| Serial Link Specifications                   | 7-28        | Test Section 5                                                 | A-2         |

| Service Features                             | 7-29        | Test Section 6                                                 | A-2         |

| TIC Diagnostic Tools                         | 7-30        | Test Section 7                                                 | A-2         |

| TIC Quiz                                     | 7-31        | Test Section 8                                                 | A-2         |

| TIC Lab                                      | 7-32        | Test Section 9                                                 | A-2         |

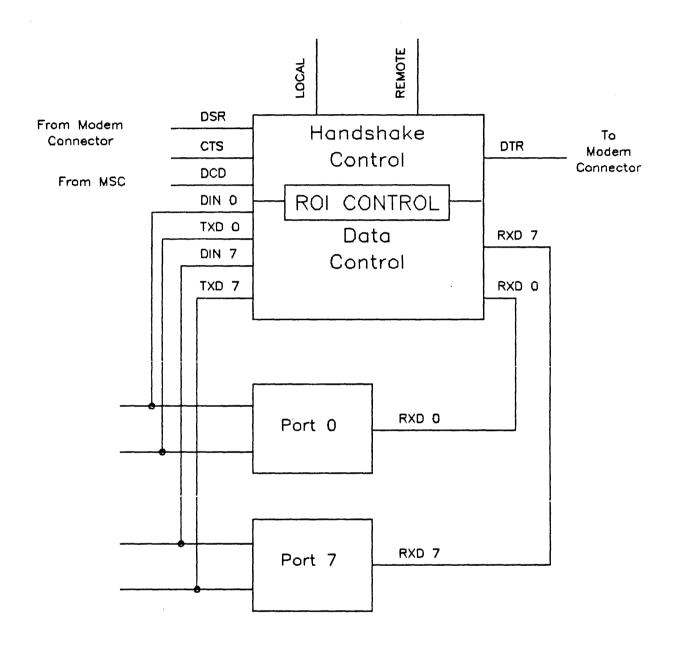

| Remote Operators Interface (ROI)             | 7-33        | Terminal Interface Controller (TIC) Diagnostic                 | A-2         |

| Series 37 ROI Implementation                 | 7-33        | Introduction                                                   | A-2         |

| Establishing a Remote Session                | 7-33        | Required Hardware                                              | A-3         |

| Local/Remote Console Communication           | 7-33        | Test Descriptions                                              | A-3         |

| Configuring the Baud Rate for ROI Operations | 7-35        | System Interface Board (SIB) Tests                             | A-3         |

| ROI and its Effect on the Modem Port         |             | Asynchronous Interface Board (AIB) Tests                       | <b>A-</b> 4 |

| ROI Quiz                                     | 7-37        | Peripheral Interface Controller (PIC) Diagnostics Introduction |             |

| Appendix A                                   |             | Required Hardware                                              |             |

| Diagnostics                                  |             | Test Descriptions                                              |             |

| Introduction                                 | <b>A</b> -1 | -                                                              |             |

| Memory Diagnostic                            |             | Appendix B                                                     |             |

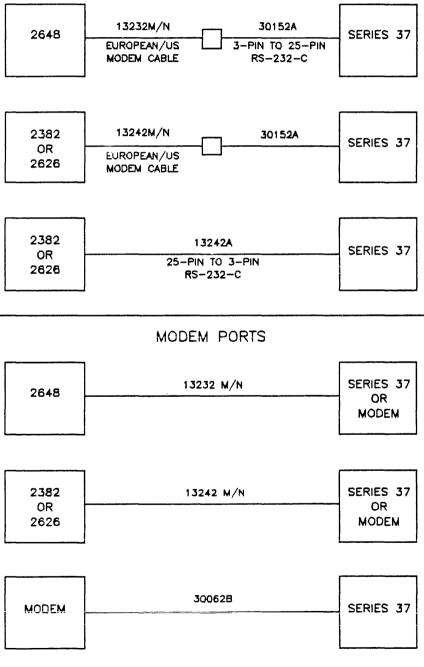

| Introduction                                 | A-1         | Cabling Information                                            |             |

| Required Hardware                            | A-1         | S                                                              |             |

| Test Descriptions                            | A-1         | Appendix C                                                     |             |

| Test Section 1                               | A-1         | Quiz and Lab Answers                                           |             |

| Test Section 2                               | A-1         |                                                                |             |

# Figures and Tables

#### LIST OF FIGURES

| Figure 1-1. | Series 37 SPU Simplified Block Diagram               | 1-3         |

|-------------|------------------------------------------------------|-------------|

|             | SPU Front Panel                                      |             |

|             | Extender Front Panel                                 |             |

| Figure 4-1. | SPU Rear View                                        | 4-4         |

|             | RS-232 Connector Assembly                            |             |

| Figure 4-3. | SPU Rear View, Rear Cover Removed                    | 4 - 6       |

|             | Power Supply Fuse and Configuration Switch           |             |

|             | SPU Front View, Front Cover Removed                  |             |

|             | SPU Front View, Front Cover and Battery Pack Removed |             |

|             | SPU/Extender Front View, Front Covers Removed        |             |

|             | Power System Block Diagram                           |             |

|             | Power System Timing Diagram                          |             |

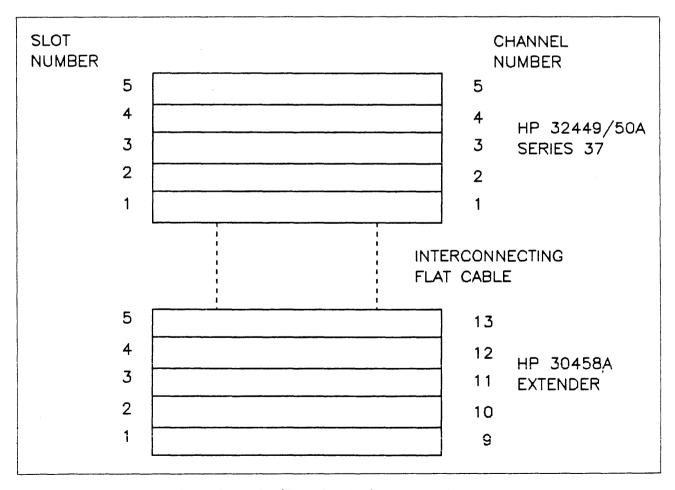

| Figure 6-1. | SPU/Extender Slot/Channel Assignments                | 6-7         |

|             | CPU Block Diagram                                    |             |

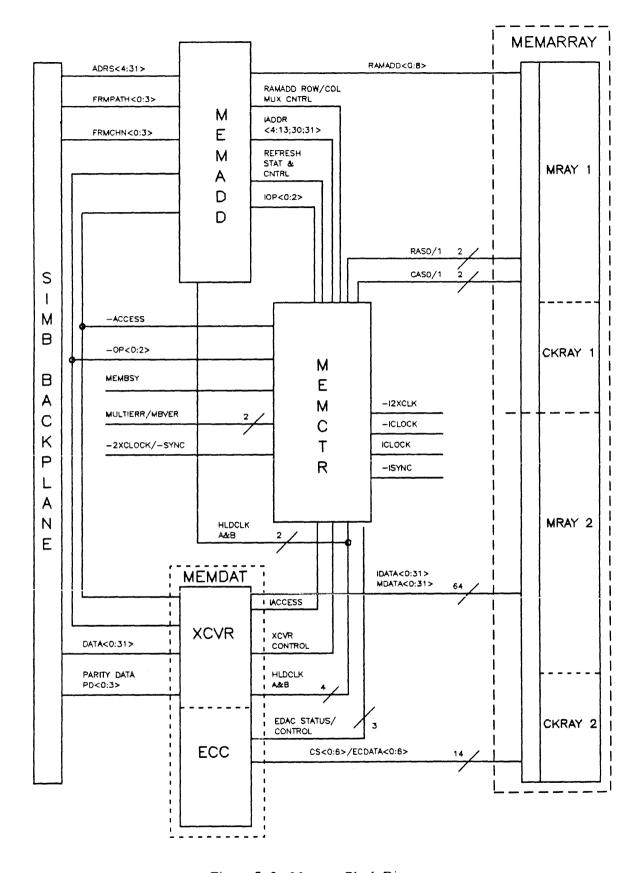

| Figure 7-2. | Memory Block Diagram                                 | 7-10        |

| Figure 7-3. | Memory RAM Location Diagram                          | 7-11        |

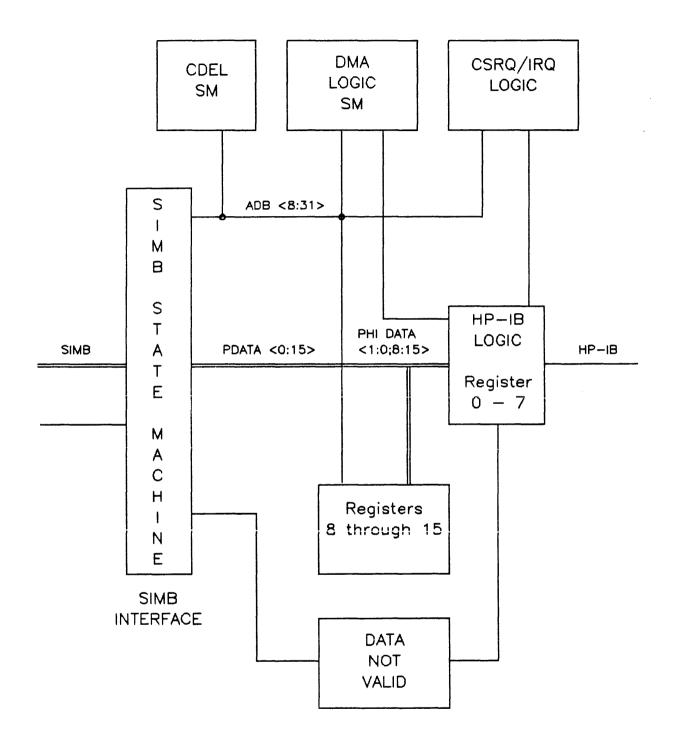

| Figure 7-4. | PIC Block Diagram                                    | 7-18        |

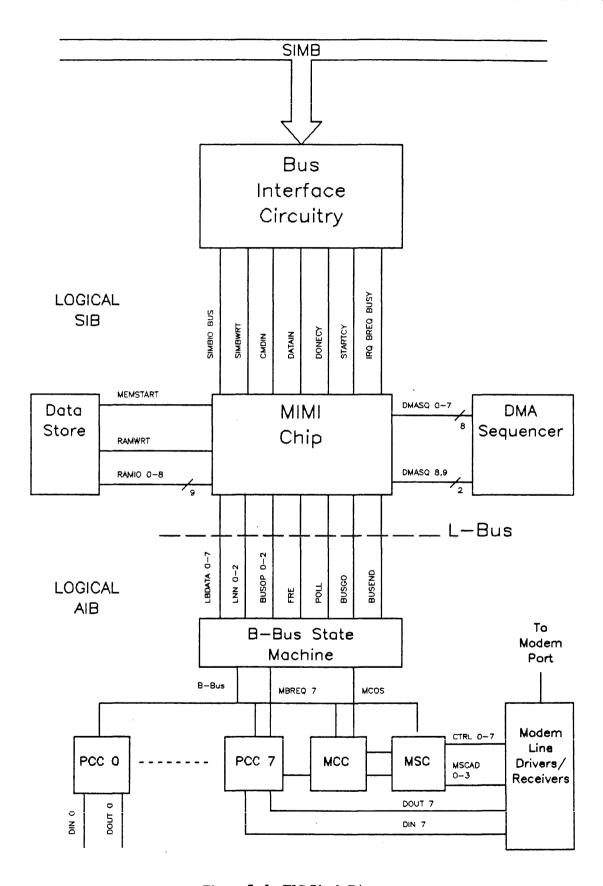

| Figure 7-5. | TIC Block Diagram                                    | 7-25        |

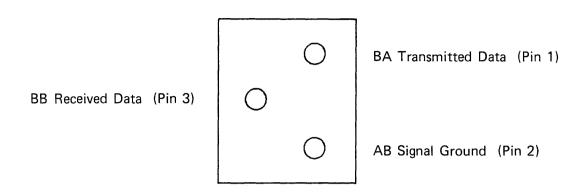

| Figure 7-6. | RS-232 Connector Pin Assignments                     | 7-29        |

| Figure 7-7. | ROI Control Logic Block Diagram                      | 7 - 34      |

| Figure B-1. | Cabling Diagram                                      | <b>B</b> -1 |

|             |                                                      |             |

|             |                                                      |             |

| LIST OF TA  | ABLES                                                |             |

| Table 3-1   | Key Switch Definitions.                              | 3-3         |

|             |                                                      |             |

| Table 3-3   | Front Panel LED Codes and Descriptions               | 3-11        |

|             | Parity Bits and Op Code, Address, and Data Bits      |             |

| ILUIC U I.  | I GIILT DIES GIEG OU COUC. AUGICSS, GIEG DALG DIES   | u = 1       |

### Introduction

The HP 3000 Series 37 System Processor Unit (SPU) is a low-end member of the HP 3000 product line. The simple and highly integrated design allows product training for the CEs to be accomplished with a self-paced course.

The self-paced course is designed to be a self-contained two-day course. It requires only a supported terminal and the Series 37 SPU. On the third day, a TSE gives a lecture. The third day exercises include questions and answers from the contents of the two-day course. It also includes a discussion of MPE and DUS changes and some lab time to become familiar with the entire system.

#### **PREREQUISITES**

Despite its simple design, the Series 37 is a highly complex computer system that requires training beyond that which is possible in a self-study course. The CE 232A course or equivalent experience and six months of field experience are prerequisites of the self-study course. It contains necessary background information, such as HP-IB configurations, basic MPE, and the Diagnostic Utility System (DUS). The Series 37 course covers only the hardware that is unique to the Series 37 SPU.

#### **COURSE OBJECTIVES**

When you have successfully completed this course, you will be able to:

- Operate the Series 37 SPU and identify its unique features

- Configure and install a Series 37 SPU in the mini-rack

- Troubleshoot and repair the Series 37 SPU

- Remove and replace all field replaceable assemblies

- Describe the unique features of the Series 37 Synchronous Intermodule Bus (SIMB)

- Identify the components of the Remote Operators Interface (ROI)

#### MATERIALS NEEDED TO TAKE THIS COURSE

The self-paced program requires that you have the following materials, tools, and equipment (part numbers in parenthesis).

#### Self-Paced Hardware Training Package

- This HP Series 37 Self-Paced Hardware Training Guide (32450 + 49A-90001)

- Final Review Package. (You should give this to your supervisor or administrator before beginning the course). (32450 + 49A-90003)

#### **Tools and Equipment**

- Series 37 SPU

- Terminal

- Optional mini-rack cabinet (30463A)

- One of the following disc drives:

- HP 7945

- HP 7912/14

- HP 7933

- HP 7935

- One of the following tape drives:

- HP 9144

- HP 7974

The following extra boards should be available for running diagnostics:

- Peripheral Interface Controller (PIC) (30459A)

- Terminal Interface Controller (TIC) (30460A)

- Series 37 Board Extractor Tool (30457-80004)

- Load Board (30457-60015)

- Video Cartridge Recorder

- Video cartridge of SPU and Extender installation in Raven cabinet

- Diagnostic Utility System (DUS) on magnetic tape reel or cartridge tape- most current version

- MPE on magnetic tape reel or cartridge tape most current version

- Modem Loopback Connector (30146-60002)

- RS-232-C Loopback Connector (30148-60002)

- Standard 2-meter HP-IB cable

- Hardwired 25 pin-to-3 pin cable (ATP type) (31052-60001)

- Standard terminal modem cable (part number is terminal-dependent)

- Standard hand tools, to include numbers 0, 1, and 2 Posidriv screwdrivers

- Volt-ohmmeter (HP 3465/3466 or equivalent)

- Antistatic Wrist Strap

#### Documentation

HP 3000 Diagnostic Manual Set (30070-60080) - most current version

#### HOW TO USE THIS GUIDE

This self-paced guide contains all of the instruction for this course. It directs you to read the text, to perform lab projects, and to answer questions that test your understanding of the material.

Follow these guidelines for taking this course and using this guide:

- Give the sealed Final Review Package to your supervisor or administrator.

- Study the lessons in sequence.

- Read and observe all warnings and cautions before performing the defined procedures.

- Within each lesson, work through the lesson in the order that the material is presented. Read the introductory material, then perform the lab project and answer the quiz questions. (Lab and quiz answers are included in Appendix C.) If you correctly answer at least 80% of each quiz, proceed to the next lesson. If your score is less than 80%, review the lesson and then answer the questions again.

- After completing the course, answer the questions in the Final Review examination (which you should get from your supervisor or administrator). If your score is less than 80, review the lessons in which you are weakest and then answer the Final Review questions again.

- Keep track of your progress on the Course Completion Summary.

#### NOTE

This guide is intended for use by qualified service personnel only. Normal safety precautions must be observed at all times while servicing electronic equipment.

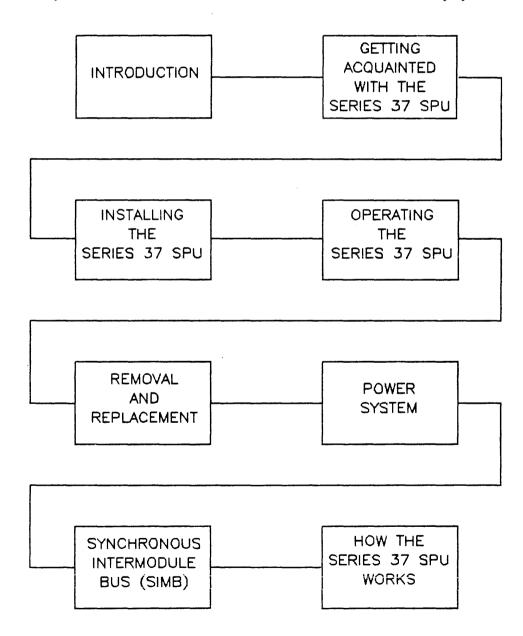

#### **Course Structure**

The sequence below explains the plan of this self-paced guide. The elements of the flowchart are the major points to be covered to repair the Series 37 SPU to the module/component level. This guide does not intend to develop good electronic technicians. It is designed to teach a good technician to repair the Series 37 SPU to the module/component level.

#### WARNING

Always remove power before opening the Series 37 SPU. If servicing requires that the power be on while protective covers are removed, proceed only with extreme caution. Failure to do so can result in severe injury.

## **Course Completion Checklist**

#### HP 3000 Computer Systems Series 37 System Processing Unit Self-Paced Hardware Training Guide

| Lesson Title |                                           | Date<br>Completed | Time<br>Required | Supervisor's<br>Initials |

|--------------|-------------------------------------------|-------------------|------------------|--------------------------|

| 1.           | Getting Acquainted With the Series 37 SPU |                   |                  |                          |

| 2.           | Installation                              |                   |                  |                          |

| 3.           | Operating the Series 37 SPU               |                   |                  |                          |

| 4.           | Removal and Replacement                   |                   |                  |                          |

| 5.           | Power System                              |                   |                  |                          |

| 6.           | Synchronous Intermodule Bus (SIMB)        |                   |                  |                          |

| 7.           | How the Series 37 SPU Works               |                   |                  |                          |

|              | Program Completion I                      | Date              |                  |                          |

| Stu          | dent's Signature                          |                   |                  |                          |

| Co           | mpany Name                                |                   |                  |                          |

| Ad           | dress                                     |                   |                  |                          |

|              |                                           |                   |                  |                          |

|              |                                           |                   |                  |                          |

| Fir          | al Review Administered By:                |                   | Date:            |                          |

If your organization is interested in an HP co-operative support program, complete this form and attach your completed final review package. Contact your local HP sales representative for further information.

# Getting Acquainted With The Series 37 SPU

Lesson

#### **OVERVIEW**

This lesson briefly describes the characteristics of the Series 37 SPU and its position in the HP 3000 product line.

#### LEARNING OBJECTIVES

When you have successfully completed this course, you will be able to:

- Describe the basic configuration of the standard system.

- List the maximum number of users that can be supported.

- Identify the configuration restrictions that apply to the I/O Extender.

#### INTRODUCTION

The HP 3000 Series 37 is a new low-end member of the HP 3000 product line. It is a highly integrated, low priced, high-reliability computer that runs MPE. It offers customers a low priced system that can be upgraded to the top of the product line.

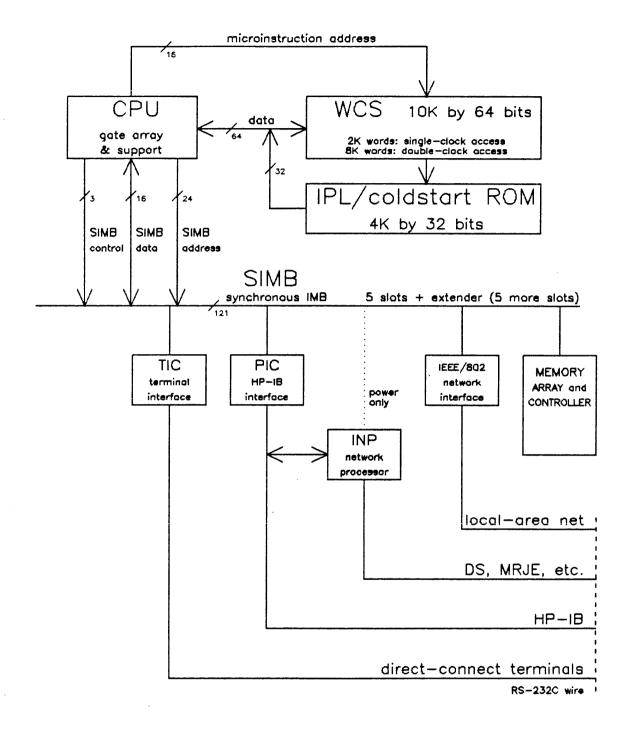

Figure 1-1 is a simplified block diagram of the Series 37 System Processing Unit (SPU). The SPU uses gate array and CMOS VLSI technology extensively to achieve its small size. The Series 37 supports from one to 28 users and up to one megabyte of main memory with the performance of a Series III. The standard Series 37 supports seven users with 512k of main memory and a Peripheral Interface Controller (PIC). The one remaining slot can contain an additional Terminal Interface Controller (TIC), another PIC, or an additional 512k of memory. The system can be extended to 10 slots by adding an I/O Extender. The I/O Extender is physically connected to the Series 37 SPU and can be populated with additional I/O boards. Note that memory is not supported in the Extender.

The Series 37 SPU consists of a five-slot card cage, a power supply, and battery backup circuitry. The boards that make up the SPU are installed in the following slots:

- Slot 5 Central Processing Unit (CPU) \*

- Slot 4 Peripheral Interface Controller (PIC) \*\*

- Slot 3 Optional 512k Memory, TIC, or PIC \*\*\*

- Slot 2 512k Memory \*

#### Getting Acquainted with the Series 37 SPU

#### Slot 1 Terminal Interface Controller (TIC) \*

- \* Must be installed in this slot

- \*\* Must be installed here if there is no I/O Extender.

If there is an I/O Extender in the system, a PIC or

a TIC can be installed, or the slot can be blank.

- \*\*\* This slot can be blank

The Series 37 is small enough to set on a desk top. It can also be racked in a mini-rack with other supported peripherals. The Series 37 is designed to be installed by the customer. At first introduction, it will be installed only by HP personnel. Customer installation will be implemented when there are peripherals available that can be installed by the customer.

Figure 1-1. Series 37 SPU Simplified Block Diagram

#### **LESSON 1 QUIZ**

- 1. How many optional slots are there in the standard system? 1

- 2. What is the maximum number of users that can be supported? 2 8

- 3. Can you install memory in the I/O Extender? >0

# Installing the Series 37 SPU

#### **OVERVIEW**

This lesson describes the HP 32449A installation policy. It also describes how to install the HP 32450A and the I/O Extender. The rules for configuring the Series 37 SPU card cage are also provided.

#### LEARNING OBJECTIVES

When you have successfully completed this lesson, you will be able to:

- Install the HP 32450A.

- Connect the I/O Extender to the HP 32450A.

- Correctly cable the system.

- Configure the SPU and I/O Extender card cages.

#### INTRODUCTION

The Series 37 SPU is the first customer-installable HP 3000. There are two versions of the product. The HP 32450A is CE installable. The HP 32449A is customer installable.

The HP 32449A is an integrated version of the Series 37. It is shipped installed in the mini-rack. It is bundled with the HP 9144A cartridge tape drive and a customer-installable disc drive. The shipment of the tape and disc is coordinated with the shipment of the customer-installable system. The mini-rack is shipped already set up to accommodate these peripherals and a second optional disc drive. No other HP-IB peripherals are supported on the HP 32449A unless they are installed by a CE and unless site preparation has been performed. All other supported peripherals on the system, such as terminals, printers, and plotters, have RS-232 interfaces and are customer installable. Note that the I/O Extender and a second PIC are not supported in the customer-installable configuration.

#### **HP 32449A INSTALLATION POLICY**

There are several reasons why the HP 32449A product is customer installable. The major reasons are described below.

#### Installation Procedure

Installation of the HP 32449A and the peripherals that are customer installable does not require special tools, adjustments, or alignments. The peripherals are lightweight, low-power devices that require no special wiring.

#### Single Power Source

The Series 37 SPU and the customer installable HP-IB peripherals are low-power devices. This allows them to be connected to a single AC power source by means of the power strip in the mini-rack. Because of the single power source, the Series 37 SPU can run on normal office AC power without requiring special wiring or line conditioning. The single power source also eliminates the possibility of transmission errors caused by a ground loop between HP-IB devices.

All of this reduces the need for site preparation. However, sites that do not have normal office environments or those with unstable power may require site preparation, line conditioning, or special AC wiring. The Series 37 SPU should be installed on a dedicated circuit free from copiers, microwave ovens, and heavy motors.

#### RS-232 Peripherals

Because of the nature and speed of an RS-232 interface, the peripherals do not have to be on the same AC circuit, as do HP-IB peripherals. This eliminates the need for site preparation of these peripherals, as long as they are low-power devices.

#### External HP-IB Peripherals

No customer-installable external peripherals are supported on the Series 37. In general, these peripherals are higher powered devices that require additional AC circuits. Because of the current draw and the need for multiple AC circuits, site preparation must be performed to ensure long-term reliability.

#### INSTALLING THE HP 32450A AND THE I/O EXTENDER

The procedure for connecting the I/O Extender to the HP 32450A and the procedure for installing components in the mini-rack are shown on the video tape. The following paragraphs complete the procedure for system installation by providing the external cabling and the AC power specifications.

#### Serial Port Cabling

Refer to Appendix B for the list of supported RS-232 cables. The specifications for the RS-232 are listed at the end of the discussion of the TIC in the "How the Series 37 SPU Works" lesson.

#### HP-IB Cabling

The standard Series 37 configuration includes one PIC PCA. It can support from one through eight devices. For performance reasons, eight devices are seldom installed on one channel. Seven PIC PCAs could be installed on one system with an I/O Extender. However, this is not practical because there would be no room for additional memory, TICs, or Intelligent Network Processors (INP).

A typical system contains two or three PICs. The design of the PIC is similar to the General Interface Controller (GIC) in that seven device loads are built on the PCA. The HP-IB specifications state that one meter of cable can be added for each device load. This implies that a maximum of seven meters of cable can initially be added. This is not true because some devices have internal cables whose length must be included. It is best to use only the cable that is shipped with each device. You will then remain well within the specifications. If additional cable is required, it can be added, provided you do not exceed one meter per device load. Note that each PIC has its own HP-IB interface and is completely separate from other PICs. The rule of seven device loads per PIC applies to each installed PIC PCA.

When adding additional cable, do not connect two HP-IB cables together. For example, if you need a two-meter cable between two devices, use one two-meter cable. Do not connect two one-meter cables.

A "star" configuration, a "daisy chain" configuration, or a combination of the two can be configured on any PIC. Any combination is supported as long as the cable length specification is not exceeded. The "daisy chain" is the preferred configuration because it produces less noise.

If both a disc and a printer are on the same HP-IB interface, connect the disc closer to the SPU than the printer.

#### **AC Power**

The input electrical specifications of the Series 37 SPU or the I/O Extender are shown below. If an SPU and I/O Extender are installed in one system, both the current and power requirements specified below are doubled.

VOLTAGE Single phase

Nominal operating range: 100-120Vac or 220-240Vac Maximum operating range: 85-135Vac or 170-270Vac

CURRENT 4 amps maximum at 110Vac

POWER 270 watts maximum at maximum output load

FREQUENCY 45 to 66 Hz.

HOLD-UP One cycle of input AC can be dropped without causing a Power Fail condition.

without causing a rower rail condition

POWER LINE The computer will perform correctly in normal and common modes under

the following pulse conditions:

| 00 nsec |

|---------|

| 00 nsec |

| 00 nsec |

|         |

#### **RULES FOR CONFIGURING THE SERIES 37 CARD CAGE**

The card cage configuration guidelines are listed below.

- The CPU PCA must be installed in slot 5 of the SPU.

- The first TIC PCA must be installed in slot 1 of the SPU with an RS-232 connector assembly.

- The first 512k byte memory PCA must be installed in slot 2 of the SPU. If a second memory PCA is installed, it must be installed in slot 3.

- No memory can be installed in the I/O Extender.

- A maximum of four TIC PCAs can be installed in the system.

- There must be at least one slot between TICs or any other assembly that has a connector on the right side.

- A TIC cannot be installed in slot 5 of either the SPU or the I/O Extender.

#### **LESSON 2 QUIZ**

- 1. What AC power feature allows the HP 32449A system to be installed without site preparation?

- 2. Is it possible to install three TIC assemblies in the I/O Extender? Explain your answer.

- 3. What is the preferred HP-IB cabling configuration?

DAISG Chair

- 4. What is the general rule for installing HP-IB cables that will ensure that you do not violate the maximum cable length specifications? I weller per Device LOAD only use CABLE Shipped w/ System

- 5. What are the primary factors that make site preparation for the HP 32450A mandatory?

1. Per. Dot part of Basic 37

- 7. ABMORMAL ENVIRORMENT

Answers in Appendix C.

# **Operating the Series 37 SPU**

#### **OVERVIEW**

This lesson describes the operation of the console, the function of the keyswitch, and the function of the front panel LEDs. The Remote Operators Interface and the maintenance microcode are also described.

#### LEARNING OBJECTIVES

When you have successfully completed this lesson, you will be able to:

- Operate the Front Panel Keyswitch.

- Connect and operate the local and remote consoles.

- Execute and interpret Self Test results.

- Troubleshoot the SPU using the Display Indicator.

- Identify the hardware configuration using available tools.

#### SPU FRONT PANEL DESCRIPTION

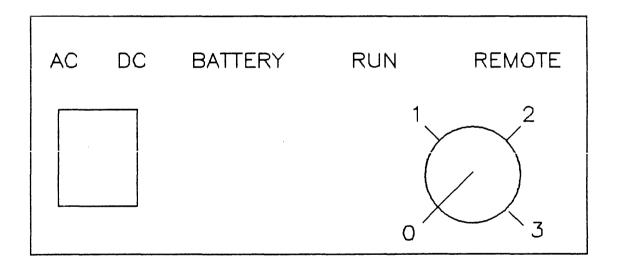

The System Processor Unit (SPU) front panel is shown in figure 3-1. The four-position key switch is used to select the control modes and power distribution of the SPU. The indicator lights show what power configuration is active and in what mode the system is running. The single digit LED display shows the status of the SPU when the self-test routines are executed. The display remains blank when the system is executing operational software.

#### Front Panel Key Switch

The front panel key switch is used to select the power configuration and the mode of operation of the SPU. You can select either the normal mode or the maintenance mode of operation. Table 3-1 shows the key switch positions, the modes of operation, and the associated actions.

#### Front Panel Status Indicators

The front panel status indicators display the state of the SPU during operation.

The AC indicator is lit if AC power is applied to the SPU. Power is applied to the battery charger. The indicator is lit in all keyswitch positions.

The DC indicator is lit if DC power is present in the SPU. It is lit if the key switch is in positions 1, 2, or 3.

The BATTERY indicator is lit if the SPU is operating on battery backup power and if AC power is not present. This condition can occur if the front panel switch is in positions 1, 2, or 3.

The RUN indicator is lit only when the Channel Program Service Request (CSRQ) signal is asserted. It is not lit if TIC or memory operations are being executed. During normal operation, it will appear to be lit continuously because channel programs are executed frequently. The indicator will flicker when TIC or memory diagnostics are run. It can be lit when the key switch is in positions 1, 2, or 3.

The REMOTE indicator is lit if the key switch is in position 3. This allows a terminal connected to port 7 via a modem to control the system.

#### Front Panel LED

The front panel LED displays a single hexadecimal error code that indicates what components are failing. The codes are displayed only when the system is in the self-test mode. There are two test modes. Self-test is run first. The normal sequence of displayed LED codes is 0, 1, 5, 1, 5, B, C, A. Self-test is then complete. If an error is detected, the error detection loop is executed.

The valid hexadecimal codes and their meaning are shown in table 3-2. The LEDs display one digit at a time. If a two-digit error code is displayed, the digits of the code flash alternately. If no error code is displayed, the SPU is executing operational software.

Figure 3-1. SPU Front Panel

Table 3-1. Key Switch Definitions

| KEY<br>SWITCH |        |                                                                                                                                                                                                |

|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POSITION      | MODE   | ASSOCIATED ACTION                                                                                                                                                                              |

| 0             | DC Off | DC power is off. Battery DC is off. AC power is applied. Power is applied to the battery charger.                                                                                              |

| 1             | Normal | The system console is on port 0, channel 1. Control B (maintenance mode) sequences can not be executed in this mode.                                                                           |

| 2             | Local  | The system console on channel 1, port 0 is active and can execute the Control B sequence.                                                                                                      |

| 3             | Remote | The terminal on channel 1, remote port (port 7) is the active console and can execute the Control B sequence. The local console on port 0 monitors and displays remote console data transfers. |

Table 3-2. Front Panel LED Codes and Descriptions

| LED CODE | DESCRIPTION                                                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | ROM code loads into WCS.                                                                                                                                                                          |

| 1        | Not used. LOAD Rom code into wes                                                                                                                                                                  |

| 2        | Not used. Vertient Checking Failer                                                                                                                                                                |

| 5        | Processor chip, WCS, RFILE tests executing.                                                                                                                                                       |

| 0        | Maintenance code entered. Multi-bit memory error occurred.                                                                                                                                        |

| В        | A steady "B" means the memory test is executing. A flashing "B" means the memory failed the test.                                                                                                 |

| С        | A steady "C" means the Console TIC in slot 1 is being tested. A flashing "C" followed by a "1" means the Console TIC failed. If only a flashing "C" occurs, speed sensing of the terminal failed. |

| D        | IOMAP not Run on PON Se                                                                                                                                                                           |

| E        | These error codes show that the TIC or PIC in the indicated extender slot has failed. The "E" and the slot number flash alternately.                                                              |

| A        | All tests passed.                                                                                                                                                                                 |

| Blank    | DUS or MPE is being loaded or had been loaded.                                                                                                                                                    |

|          |                                                                                                                                                                                                   |

S.A.B.C FAIL DIAY will Loop

#### I/O EXTENDER DESCRIPTION

The standard Series 37 SPU has a five-slot backplane, in which the four standard boards are installed (CPU, PIC, TIC, and memory). One slot remains available for either memory or I/O expansion. The I/O extender increases the total number of slots from five to ten. The five additional slots can be used only for I/O expansion. Memory is supported only in slots 2 and 3 of the SPU.

#### Comparison of Extender to SPU

The Extender is identical to the SPU, with the following exceptions:

- The CPU board and Memory board cannot be installed in the Extender.

- There is no keyswitch on the Extender. Power is controlled from the SPU by means of the interconnect cable.

- There are no RUN or REMOTE indicators on the front panel of the Extender.

- There are minor hardware differences in the card cages to allow them to be connected together.

The backplanes, power supplies, battery packs, and rear panels are identical. Both the SPU and Extender backplane slots are numbered from 1 through 5.

#### **Battery Backup**

The battery backup system is identical to that in the Series 37 SPU. However, it is used to save the contents of critical RAMs on I/O boards rather than save the contents of main memory.

#### I/O Extender Service Note

#### WARNING

Always turn off DC power first. Then remove AC power before servicing the Series 37.

DC power in the Extender is controlled by the keyswitch on the SPU. The SPU and the Extender are connected via the flat interconnect cable. If DC power is turned off and the interconnect cable is removed, DC power in the Extender will be turned on if the AC power has not been removed. This will also happen if the Display Board cable in the SPU is removed. Under these circumstances, if AC power is later removed, the battery backup will be turned on, keeping the memory voltages up.

Because of power supply loading requirements, the Extender is not supported without at least one I/O board being installed. If the Extender is unpopulated, it is not guaranteed that DC power will come up.

#### **EXTENDER FRONT PANEL DESCRIPTION**

The Extender front panel is shown in figure 3-2. The Extender front panel status indicators are a subset of the SPU status indicators.

The AC indicator is lit if AC power is applied to the Extender. The DC indicator is lit if DC power is present in the Extender.

The BATTERY indicator is lit if the Extender is operating on battery backup power and if AC power is not present.

Figure 3-2. Extender Front Panel

#### MINIMUM REQUIREMENTS FOR TERMINALS

Refer to Appendix B for the list of HP terminals that are supported on the Series 37 system. Non-HP terminals can also be used if they are compatible with the HP terminals. Some of the minimum requirements are listed below.

- The system console must be connected to port 0 on the TIC installed in slot 1 (channel 1) of the SPU. MPE and DUS expect this configuration.

- The ENQ/ACK handshake capability must be present.

- The console must operate at one or more of the following standard baud rates: 110, 300, 600, 1200, 2400, 4800, 9600, 19200.

- The console must have either 8N1 (eight data bits, no parity, one stop bit) or 701 (seven data bits, no parity, one stop bit, and the eighth bit set to zero).

- 80 character input buffer

- Full duplex

- It must be capable of issuing a Control B sequence and other supported sequences.

- It must be capable of accepting a DC1 as a line turn-around character.

#### Connecting Hardwired Terminal to Series 37

Refer to Appendix B for information on cabling a supported terminal to the RS-232-C hardwired ports.

#### Connecting Terminal to Series 37 Modem Port

Refer to Appendix B for information on cabling a supported terminal to the RS-232-C modem port. Note that the qualifications for a local terminal are the same for a terminal connected to the modem port.

#### MAINTENANCE MODE MICROCODE

#### Introduction

The maintenance mode microcode contains the code for interpreting maintenance commands and the Series 37 Self Test. Unlike earlier versions of HP 3000 computers, there is no special maintenance processor. The maintenance microcode resides on the CPU board. The Control B detection logic is located on the TIC. Only the TIC in slot 1 (channel 1) of the SPU card cage can have the Control B logic enabled. To enable the logic, the key switch must be in the Local or Remote position. Note also that only the console connected to port 0 (local) or port 7 (remote) can execute the Control B sequence.

When the Control B sequence is initiated, software execution is halted and the H for help-> prompt is displayed. The maintenance microcode then begins execution. Note that the MPE environment is protected only if you execute a Run, Help or Speed command.

If any other commands are executed, MPE is not protected.

#### Microcode Load Sequence

The ROM code is made up of executable ROM code and two types of loadable ROM code - executable code and ROM-based messages. The executable ROM code is used to load the first series of self tests from ROM into WCS upon power-up. Control is then passed to the code loaded into Writeable Control Store (WCS). WCS is RAM located on the CPU board that is used to store microcode.

This code tests the CPU chip and parts of WCS. It then loads the Code Loader and the second series of tests into Slow WCS. These tests check additional portions of the CPU chip, fast WCS, and the CPU register file. When these tests are successfully completed, the maintenance panel code is loaded into WCS and enabled. The Self Test Executive is then loaded into WCS and control is passed to it.

The Self Test Executive determines if an Auto Restart after power failure is to be performed. If a normal power-on sequence occurred, it then tests all of memory. A subset of the memory tests is run if an auto-restart is being executed. The Self Test Executive then tests all of the I/O cards installed in the system and speed senses the system console. The slot numbers of the failing cards is displayed on the LED of the SPU front panel. If the console is successfully speed sensed, the test results are displayed on the console and a prompt is issued, unless Auto Warmstart is specified. If Auto Warmstart is specified, control is passed to the Loader code and the Start device number is displayed.

#### Power-on Self Test

When power is applied to the SPU, the ROM-based Power-on Self Test is executed. Self Test loads all of the code in ROM 3 into WCS. The code in WCS is then executed.

The basic CPU chip test, a general WCS test, and a ROM code loader are in ROM 3. This code tests some of the Series 37 CPU chip functions. The last function performed by the CPU chip test is to test all of Slow WCS and to load two more CPU test modules. These modules test the remaining CPU chip functions. When these tests are complete, the Mainframe Panel module, the Control module, and the Test Executor module are loaded. Control is then passed to the Test Executor.

The Test Executor loads the memory tests, the PIC test, and the TIC tests. The memory tests are then executed. If a failure occurs, the memory tests are repeated and error code B is displayed on the LED

display. When the memory tests are successfully executed, the console TIC and all of the other boards in the SPU are tested. The results are displayed on the LED display. If the console TIC passes and the console speed senses, the pass/fail information is also displayed on the console. If the console fails to speed sense, the tests are looped and displayed on the LED display. If the failure occurs because the console was offline, putting the console online will result in the console being speed sensed. When the console has been speed sensed and the results have been displayed on the console, the Control module begins execution.

#### **Control Module Options**

The Control module initializes the TIC and displays the H for help-> prompt if the Automatic Warmstart or Power Fail Auto-restart functions are not being executed. The following functions can then be performed:

Automatic Warmstart Power Fail Auto-restart Load/Start Dump Help Run Speed Test

#### Automatic Warmstart

If MPE has been brought up and properly shut down and if the key switch is in the Normal or Remote Speek position, the power-on microcode performs an automatic warmstart to the default device. If the key Serse switch is in the Remote position and the remote console is connected by a modem, Self Test will loop until Remote the modern connection is actable to the modern connection in the Remote position and the remote console is connected by a modern, Self Test will loop until Remote to the modern connected to the modern connected to the remote console is connected by a modern. the modem connection is established. The microcode can then perform speed sensing with the remote (2<sup>NS</sup>) console. This allows Self Test to complete and Warmstart to begin. If the CPU, memory, or the system console TIC fail Self Test, it loops on the test that detected the failure. If these boards pass Self Test, Warmstart is attempted.

If the PIC or a TIC other than the system console TIC fails Self Test, information about the failure is output to the console. You can then attempt to start the system.

#### Retry Auto-Restart

A subset of the memory test is executed after the Power-on CPU test if the Auto-restart flag is set. When this test is successfully executed, all of the I/O boards are tested. Communication is established with the console. Execution is then transferred to the Auto-restart entry in the Loader module. The WCS boot code is executed with the Auto-restart flag and the Load/Restart flag set and the Start device number set in the Register file.

If Auto-restart fails because the disc is not ready, up to four retries will be made. If none of the retries are successful, the H for help-> prompt is displayed. You can type the AR (Autorestart) command to initiate five more tries. Error information is displayed on the console.

#### Load/Start

You can perform a Load or Start using the default Load and Start device numbers stored in the Time of Century Clock (TOC) RAM. You can also enter different device numbers or change the default devices. If you enter the Load/Start command, you must confirm that you want to perform the Load or Start operation. The Load or Start operation is performed by loading the Load Execution code and the WCS

boot code, and transferring control to the Load Execution code. The Load Execution code tests for valid Load or Start parameters, updates the TOC RAM, and transfers control to the WCS boot code. If a parameter error occurred or if a change in parameters is requested, control is transferred back to the Control module. If the parameters are correct and if a Load or Start operation is to be executed, control is passed to the WCS boot code. It loads the HP 3000 instruction set from the disc or tape and continues with the Load or Start operation.

Once the Load/Start command is executed, a timer is set. If the target device does not become ready in the allowed time, a time-out error (WCS boot failure) is displayed on the screen.

The format of the Load command is:

L[oad] [channel,device[,{P[erm] C[hange]}]]

The parameters in brackets are optional. The parameters in braces are also optional but you can enter only one of the parameters. If you enter "P", Load is performed from the specified device. The new channel and device numbers are stored in the TOC. If you enter "C", no Load operation is performed. The TOC is updated with the specified device number.

The format of the Start command is:

ST[art] [channel,device[,{P[erm] C[hange]}]]

The parameters in brackets are optional. The parameters in braces are also optional but you can enter only one of the parameters. If you enter "P", Start is performed from the specified device. The new channel and device numbers are stored in the TOC. If you enter "C", no Start operation is performed. The TOC is updated with the specified device number.

#### Dump

Dump loads the dump routine from the specified device. Dump uses the Start default device number stored in the TOC RAM or the device specified by the operator. The Dump command asks you to confirm that you want to perform a dump. If so, Load or Start is performed by loading the Load Execution code. Control is then transferred to the Load Execution code.

The Load Execution code tests for valid Dump parameters and transfers control to microcode in WCS. If no microcode is loaded, control is returned to the Control module. If the parameters are correct, and the microcode is loaded, control is passed to the Dump code in the instruction set. The CPU loads the Dump code from the specified device and dumps the system.

The format of the Dump command is:

D[ump] [channel,device]

The parameters in brackets are optional.

#### Help

The Help command displays the version of the CPU microcode that is loaded or ----- if no microcode is loaded. It then displays the functions of the Control mode.

There are 16 possible responses to the H for help-> prompt. They are listed in table 3-3. The channel and device for the Load, Start, and Dump commands must be specified unless the default device has been defined using the ",P" or ",C" options. The Dump command always defaults to the Start device. The ",P"

option updates the Load or Start device data in the TOC and loads or starts the system. The ",C" option updates the Load or Start data in the TOC but does not load or start the system. The valid channel numbers are 1 through 4 in the SPU and 9 through 13 in the Extender. If the system displays the H for help-> prompt after a Halt command or Control B sequence has been executed, the Run command can be used to run the system. The AR command enables you to try another restart if the system has already attempted to restart the system. The remaining Load/Start-type commands (COL, COO, DIS, NEW, RELO, TAPE, UPDA, and WAR) use the Load or Start device number stored in the TOC RAM.

Table 3-3. Control Mode Commands

|   | AR        | Retry Auto Restart.                                                       |

|---|-----------|---------------------------------------------------------------------------|

|   | COLdstart | Perform COLdload using Load device with no dialog.                        |

|   | COOlstart | Perform COOlstart using Start device with no dialog.                      |

|   | DISc      | Perform Start using Start device. Same as Start with no parameters.       |

|   | DISk      | Same as DISc.                                                             |

|   | DUmp      | Perform Dump using the indicated or Start device.                         |

|   | Help      | Display Help messages.                                                    |

|   | Load      | Perform Load from load device or specified device with dialog.            |

|   | NEWsystem | Perform Reload using Load device (only for factory MIT).                  |

|   | RELOad    | Perform Reload using Load device with no dialog.                          |

|   | RUN       | Run system after Control B halt.                                          |

|   | SPeed     | Perform speed sensing.                                                    |

|   | STart     | Perform Warm/Coolstart from Start device or specified device with dialog. |

|   | TApe      | Perform Load using Load device.                                           |

|   | TEst      | Go to Test mode.                                                          |

|   | UPDAte    | Perform Update using Load device with no dialog.                          |

|   | WARmstart | Perform Warmstart using Start device with no dialog.                      |

| l |           |                                                                           |

#### Run

Run returns execution to the software.

#### Speed

The Speed command executes under maintenance microcode. It starts a timer and allows you to change the baud rate. When you press the carriage return, the start bit is speed sensed.

#### Test

The Control mode code requests that you confirm that the Test mode is to be entered. If so, it loads the Test Executor module and transfers control to the Test entry point in the Test Executor module. If not, control is passed back to the Control module.

#### Test Mode

The Test Executor module displays the functions of the Test module and the Test-> prompt. The functions are:

All CPU Exit IOMAP Memory Channel

Help

All. This Test function executes in the following order:

CPU Memory Channel IOMAP

You can loop this test up to 9999 times. The default is 1. Upon completion, you are returned to the Test-> prompt.

CPU. This function tests all of the Bank registers, the TOC RAM locations, and ensures that the TOC and MPE timers are counting. It also displays LED codes 0 through F and tests the Watchdog timer function.

You can loop this test up to 9999 times. The default is 1. Upon completion, you are returned to the Test-> prompt.

Exit. Control is returned to the Control module. The H for help-> prompt is displayed.

IOMAP. This feature runs the memory size test portion of the memory test. It displays the size of memory, the Load, Start, and Dump devices, and then displays the types of cards installed in the system. The types of devices on the PIC are also displayed.

You can loop this test up to 9999 times. The default is 1. Upon completion, you are returned to the Test-> prompt.

Memory. The full memory test is performed and a pass/fail message is displayed on the console. The number of the failing section is displayed if a failure occurs.

You can loop this test up to 9999 times. The default is 1. Upon completion, you are returned to the Test-> prompt.

Channel. The appropriate test is run for each card installed in the SPU. If a failure occurs, the failure code is displayed next to the card description.

You can loop this test up to 9999 times. The default is 1. Upon completion, you are returned to the Test-> prompt.

The Test response to the H for help-> prompt displays the Self Test menu. You can then select from six

test options in addition to Help and Exit.

The Self Test options are shown below. Note that all of the information within the brackets is optional.

A[11] [count] A complete Power-on Self Test and several additional CPU tests

are performed. The microcoded version of IOMAP is also run.

All Self Tests are run [count] times.

C[PU] [count] The CPU Power-on Self Test and additional tests of circuitry

not tested during Power-on Self Test are performed. The CPU

Self Test is run [count] times.

E[xit] Exits the Test mode and re-enters the Control B mode.

I[OMAP] [count] The Microcoded version of IOMAP is run. It displays the

number of banks of memory and the devices in the TOC RAM. It identifies the I/O channels that are installed. IOMAP is run

[count] times.

M[emory] [count] Power-on Self Test is run on all of memory. For more

exhaustive tests and additional failure information, run the

MDIAG37 program in the Diagnostic Utility System (DUS).

CH[an] [count[,channel]] Power-on Self Test is run on a specified I/O channel or on all

channels. All channels are tested if no channel number is specified. For example, S tests all channels once. CH 2,1 runs

the tests on the TIC in slot 1. The test is executed twice.

PON [count] Run or loop the Power-on Self-Test. The key switch must be in

the Local position.

### **LESSON 3 QUIZ**

- 1. What is the function of the Local keyswitch position? How does it differ from the Normal position?

Allows CNTL-B Functions on Local Console

- 2. Under what conditions will the AC indicator on the front panel be lit?

- 3. Under what conditions will the RUN indicator on the front panel be lit?

- 4. When using the Load/Start command, what is the difference between the "P" and the "C" parameters?

P = Perm C = Change

- 5. How must the SPU be configured to receive and execute a Control B sequence?

LOCAL FOR COMPONE Remote hooked to modern For Remote Compole

- 6. What commands can be issued to obtain the device addresses of the Load, Start, and Dump devices?

- 7. List the correct command and options required to test a PIC PCA installed in slot 2 of the I/O Extender. TE, Chilip

- 8. If you execute a Load command to a non-existent device and you do not want to wait for the time-out, how can you exit the state?

- 9. Under what circumstances will the front panel LED display be blank?

- 10. How can you verify the SPU configuration?

# **CONSOLE OPERATION LAB**

The following equipment is required for this lab:

A Series 37 SPU

A supported terminal

- 1. Connect a terminal to the Series 37 SPU. Configure the terminal as a local console.

- 2. Apply AC power and turn the keyswitch to the Normal position. Record the states of the front panel LEDs. AC, DC,

- 3. Turn the keyswitch to the DC OFF position. Turn off the power to the terminal. Turn the keyswitch to the Normal position.

Record the states of the front panel LEDs and compare them with the states previously recorded.

If the above states were displayed at a customer site, what failure conditions would be indicated?

- 4. Does the LED display indicate that Selftest is looping? (True or **Ress**e)

- 5. Turn off the DC power on the Series 37 SPU. Turn on the terminal AC power. Reapply DC power by turning the keyswitch to the Remote position.

Record the states of the front panel LEDs.

- 6. Is the local console active?

- 7. Is Selftest looping?

- 8. Disconnect the terminal from the Series 37 SPU and reconnect it to the modem port. Is the console active? Verify this by typing "H" and then pressing the RETURN key.

# MAINTENANCE MICROCODE LAB

- 1. Connect the terminal to port 0. Turn the keyswitch to the Normal position. Execute a Load command and attempt to exit the hung state by issuing a Control B sequence (L 4,1).

- 2. Did the Control B sequence exit the loop?

No UNABLE to execute enti-B in Pos 1

- 3. What must be done for the Control B to work?

Pot in Posz (possib many [may wor] work) try cycle pur

- 4. From either the local or remote console, execute a Speed command and change the baud rate to 300 baud.

- 5. Now change the baud rate to 9600 baud.

- 6. Enter the Test mode and run five complete passes of all tests. List the commands required to do this.

- 7. Change the Load/Start device address in the TOC to 4,4 and 4,6 respectively.

Run IOMAP and verify the above settings.

# Removal and Replacement

### **OVERVIEW**

This lesson describes the removal and replacement of the assemblies in the SPU and the Extender. Assemblies or procedures that are unique to one unit are identified. Do not remove any of the assemblies at this time. You will remove and replace some of the assemblies when performing the lab exercise at the end of this lesson.

### LEARNING OBJECTIVES

When you have successfully completed this lesson, you will be able to:

■ Remove and replace all replaceable assemblies in the Series 37 SPU and the I/O Extender.

# WARNING

Hazardous voltages are present inside the computer and the extender. Heed all WARNING - HAZARDOUS VOLTAGE labels.

# CAUTION

The contents of memory will be lost when the main (line) and battery voltages are both off. Therefore, before proceeding, ensure that any contents of memory to be saved are stored on another medium for later retrieval.

### CAUTION

Some of the semiconductor devices used in this equipment are susceptible to damage by static discharge. Depending on the magnitude of the charge, device substrates can be punctured or destroyed by contact or mere proximity to a static charge. These charges are generated in numerous ways, such as simple contact, separation of materials, and normal motions of persons working with static sensitive devices. When handling or servicing equipment containing static sensitive devices, adequate precautions must be taken to prevent device damage or destruction. Only those who are thoroughly familiar with industry accepted techniques for handling static

### Removal and Replacement

sensitive devices should attempt to service the boards with these devices. In all instances, measures must be taken to prevent static charge buildup on work surfaces and persons handling the devices.

The following paragraphs describe how to remove and replace the various assemblies in the SPU and the Extender.

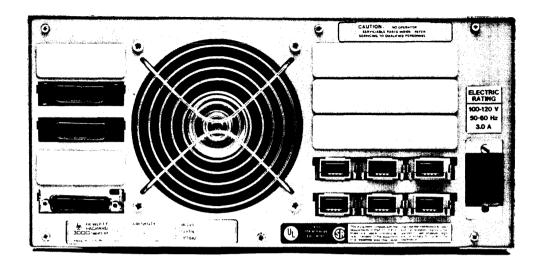

### **REAR PANEL**

### Removal

Remove the rear panel as follows:

- a. Refer to figure 4-1.

- b. Using a number 1 Pozidriv screwdriver, loosen six captive screws and remove the rear panel.

- c. Unplug the power cord from the fan on the rear panel.

# Replacement

Replace the rear panel by reversing the removal procedure.

NOTE

Ensure that the fan power cord is positioned under the board in slot 1 before replacing the rear panel.

### RS-232-C CONNECTOR ASSEMBLY.

Removal. Remove the RS-232-C connector assembly as follows:

- a. Refer to figure 4-1.

- b. Remove any attached device cables.

- c. Press the detent tabs at one side of the connectors and press the RS-232-C connector assembly back through the rear panel.

Replacement. Replace the RS-232-C connector assembly as follows:

- a. Refer to figure 4-1.

- b. Position the connector assembly in the correct slots of the rear panel.

- c. Orient the connector assembly so that the TIC PCA connector is positioned at the bottom of the assembly.

- d. Carefully press the connector assembly into the slots, applying even pressure to the RS-232-C upper and lower boards.

### RS-232-C BOARDS.

Removal. Remove each of the two RS-232-C boards as follows:

- a. Refer to figure 4-2.

- b. Using small pliers, compress the tabs on one of the I/O module clamps and separate one end of the upper RS-232-C board from the RS-232-C assembly.

- c. Using small pliers, compress the tabs on the other I/O module clamp and separate the other end of the upper RS-232-C board from the RS-232-C assembly.

- d. Using small pliers, compress the tabs on one of the I/O module clamps and separate one of the I/O module clamps from the lower RS-232-C board.

- e. Using small pliers, compress the tabs on the other I/O module clamp and separate the other I/O module clamp from the lower RS-232-C board.

Replacement. Reassemble the RS-232-C assembly as follows:

- a. Refer to figure 4-2.

- b. Press the two I/O module clamps into the lower RS-232-C board.

- c. Carefully align the board interconnect plug on the lower RS-232-C board with the board interconnect jack on the upper RS-232-C board.

- d. Press the upper RS-232-C board onto the two I/O module clamps, being careful to apply even pressure at each end of the board.

### I/O GROUND CLIPS.

Removal. Remove each of the four I/O ground clips in the RS-232-C assembly as follows:

- a. Refer to figure 4-2.

- b. Using a number 1 Pozidriv screwdriver, loosen two screws and remove the I/O ground clip.

Replacement. Replace each of the I/O ground clips be reversing the removal procedure.

Figure 4-1. SPU Rear View

Figure 4-2. RS-232 Connector Assembly

#### TUBAXIAL FAN.

Removal. Remove the tubaxial fan from the rear panel as follows:

- a. Refer to figure 4-1.

- b. Using a number 2 Pozidriv screwdriver and an open-end wrench, remove four nuts, four lock washers, four flat washers, and four bolts, and remove the tubaxial fan, fan grill, and finger guard from the rear panel.

Replacement. Replace the tubaxial fan by reversing the removal procedure.

### POWER SUPPLY

### Removal

Remove the power supply as follows:

- a. Refer to figure 4-3.

- b. Remove two Philips screws.

- c. Grasp the power supply by the handle and pull the power supply from the card cage.

# Replacement

Replace the power supply as follows:

- a. Align the top and bottom of the power supply board with the guides at the top and bottom of the card cage.

- b. Press the power supply until it is firmly mounted in the power supply connector.

### POWER SUPPLY FUSE.

Removal. Remove the power supply fuse as follows:

- a. Refer to figure 4-4.

- b. Grasp the fuse and remove it from the fuse holder.

Replacement. Replace the power supply fuse by reversing the removal procedure.

Figure 4-3. SPU Rear View, Rear Cover Removed

Figure 4-4. Power Supply Fuse and Configuration Switch

# Replacement

# Lesson 4

on the rear

removal and replacement of the assemblies in the SPU and the Extender. at are unique to one unit are identified. Do not remove any of the assemblies ove and replace some of the assemblies when performing the lab exercise at the

n the in the

### TIVES

completed this lesson, you will be able to:

te all replaceable assemblies in the Series 37 SPU and the I/O Extender.

# WARNING

Ital are present inside the computer and the extender.

NING - HAZARDOUS VOLTAGE labels.

label

· Vac

# CAUTION