# **PTSDIAG External Specifications**

# PTSDIAG External Specifications

Mon, May 7, 1984, 3:23 PM

#### 1 PRODUCT IDENTIFCATION

#### 1.1 Identification

Name:

PIC - TIC - SIMB Diagnostic

Mnemonic:

**PTSDIAG**

Product Number:

#### 1.2 Abstract

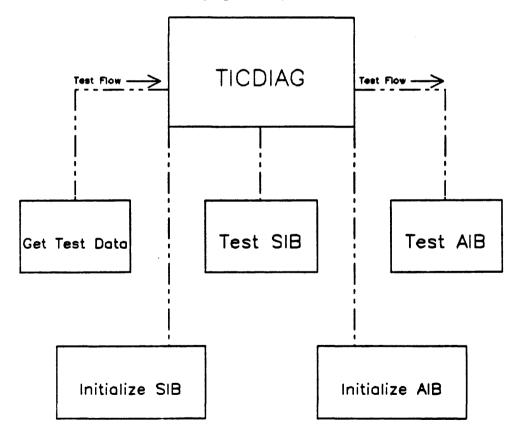

PTSDIAG is a diagnostic program which verfies the SIMB of the HP3000 Mighty Mouse System. The program is part of the Diagnostic/Utility System (DUS) for the Mighty Mouse System or Series 37. The diagnostic will use both PICs and Tics to heavily load the backplane using DMA transfers to bring out board contingencies. The diagnostic was built from sections of TICDIAG and PICDIAG.

#### 1.3 Project Personnel

Laurie Schoenbaum

#### 2 PRODUCT SPECIFICATIONS

#### 2.1 Product Overview

The PTSDIAG is written in SPL/3000. It is run under DUS (Diagnostic/Utility System).

The user is prompted for path and channel information as well as the memory size and the number of repetitions. DMA transfers are executed to load the backplane with operations. A transfer between two PICs and a transfer from a TIC using loopback completes one pass.

If data does not transfer properly or an error occurs in the transfer then an error will be displayed in a clear and understandable manner

Error messages may be suppressed or routed to the system printer.

#### 2.2 User Definition

Manufacturing and lab personnel are the primary users of PTSDIAG. Some knowledge of the Mighty Mouse system is expected to run the test and interpret the results.

The test is used to increase system reliability and detect backplane contentions.

#### 2.3 Product Environment

#### 2.3.1 Hardware Regirements and Restrictions

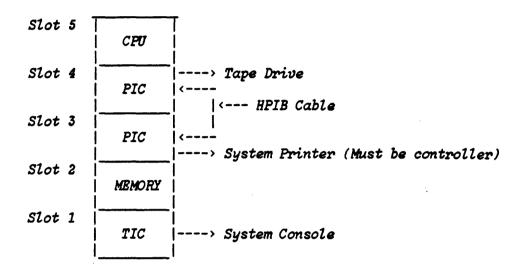

The following hardware requirements must be met to run PTSDIAG:

- 1) A minimum configuration HP3000 Mighty Mouse system

- 2) The memory board used must work well enough to initiate PSTDIAG

- 3) An HPIB tape drive and a functioning PIC as the coldload path to load DUS

- 4) At least one additional PIC

- 5) A system console and a functioning TIC in slot 1 of the main box for user interaction and operation

- 6) An HPIB cable to connect the device PIC to the controller PIC

- 7) Optional: One or two additional PICs for busy channels

#### 2.3.2 Software Regirements and Restrictions

Diagnostic/Utility System Tape

#### 2.4 User Documentation Regirements

The following documents may be used as reference for additional information:

- \* PTSDIAG source listing

- \* PICDIAG ES and source listing

- \* TICDIAG ES and source listing

- \* DMAEX37 source listing

- \* HP300 Hardware I/O Subsystem ERS

- \* HP3000 Mighty Mouse Hardware Design Document

#### 3 Detailed Functional Specifications

#### 3.1 Individual Function Desriptions

The primary function of PTSDIAG is to keep the SIMB backplane loaded with traffic from both the PIC and the TIC and to draw out problems with board interactions and timing dependencies. The test combines Step 45 of PICDIAG and the Diagnostic Loopback test of TICDIAG. A minimum test consists of two PICs, a TIC, a memory, and a CPU. One PIC is the controller PIC and the other PIC is the device PIC. The cold load device may be attached to either PIC. The system printer may only be attached to the PIC chosen as the controller. The cold load device and system printer may also be attached to the PICs chosen as busy PICs if there are more than two PICs in the system.

DUS expects the system console to be attached to channel 1, PORT 0, therefore the port numbers chosen in the test are ports 1 thru 7.

#### 3.1.1 Test Control

The operator is prompted for test configuration information, the memory size, and the number of repetitions. The diagnostic may also be reconfigured for error pause and suppression of end of program pause.

#### 3.1.2 Error Handling

Error messages may be suppressed from being displayed or routed to a printer. The printer will be configured into the system when DUS is loaded or one may be added by using the appropriate command in MANAGER.

#### 3.1.3 System Configurations

The system used in the test may be configured in different ways if there is an extender box used. With an extender box all four PICs may be used and an additional memory may be added. With only the main box, there is only one possible configuration.

The tape drive may be attached to either PIC. The system printer may only be attached to the PIC acting as the controller.

#### 3.2 User Interface

All input to PTSDIAG is done through the system console. All responses made to the diagnostic or DUS prompts should be followed by pressing the RETURN key.

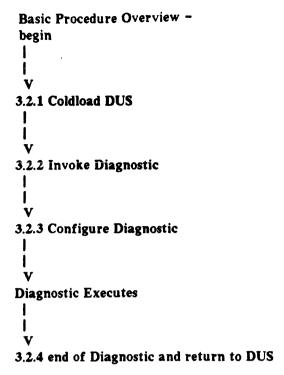

# 3.2.1 How to Coldload DUS

- a) Perform MPE shutdown to logoff every user, if applicable

- b) Run console self-test by pressing TEST on the keyboard

- c) Fully reset console by pressing RESET TERMINAL key rapidly twice

- d) Install a DUS tape on the tape coldload device

- e) Power-on the Mighty Mouse system by turning the keyswitch to the NORMAL position for the system

- f) The MM Microdiagnostics will run followed by a prompt to load DUS

Type 'H' for HELP -->

User should respond with 'L' followed by the Channel #, Device # of the Coldload device.

#### 3.2.2 Invoke Diagnostic

The Diagnostic/Utility System should respond after load with a welcome message and prompt:

DIAGNOSTIC/UTILITY SYSTEM (REVISION XX.XX)

ENTER YOUR PROGRAM NAME (TYPE HELP FOR PROGRAM INFORMATION)

Respond to the DUS prompt with:

**PTSDIAG**

PTSDIAG will load and execute displaying the following greeting:

HP3000 Mighty Mouse PIC-TIC SIMB Diagnostic - (PTSDIAG NN.NN xx/xx/xx)

#### 3.2.3 System and Diagnostic Configuration

PTSDIAG prompts the user for all information needed to run the test and to configure the diagnostic.

1) PTSDIAG prompts the user for PIC Channel information.

What is the Path # of the Controller PIC (0-2)?

What is the Channel # of the Controller PIC (1-15)?

What is the Path # of the Device PIC (0-2)? What is the Channel # of the Device PIC (1-15)?

At present, path 0 is the only path available on the HP3000 Mighty Mouse system. If the number entered is out of range or the Channel/Path combination has already been used then an error message will be displayed and the user will be prompted for the information again.

PTSDIAG will inform the user to connect the Controller PIC to the Device PIC via an HPIB cable.

2) PTSDIAG asks the user if there will be a third PIC used in the test.

Do you want a Busy PIC (Y/N)?

If 'Y' then PTSDIAG will prompt for channel information.

What is the Path # of the Busy PIC (0-2)? What is the Channel # of the Busy PIC (1-15)?

The input will be verifed and if it is invalid the user will be prompted again.

3) If 'Y' was the response for the above prompt then PTSDIAG will ask if a fourth PIC is to used in the test.

Do you want a second Busy PIC (Y/N)?

If 'Y' then PTSDIAG will prompt for channel information.

What is the Path # of the 2nd Busy PIC (0-2)?

What is the Channel # of the 2nd Busy PIC (1-15)?

The input will be verified and if it is invalid the user will be prompted again.

4) PTSDIAG next prompts for the amount of memory in the system and the number of times the test is to be repeated.

64K RAMS/1 Board -> Banks = 4

64K RAMS/2 Boards -> Banks = 8

256K RAMS/1 Board -> Banks = 16

256K RAMS/2 Boards -> Banks = 32

Input # of banks in system: (1-32)

Enter the Loop count - 0 for continuous looping (0-32767):

If the input is invalid the user is re-prompted.

5) PTSDIAG will then prompt the user for information on error handling, reporting and diagnostic control.

Pause on Error (Y/N - N=Default)?

Output results to Line-Printer (Y/N - N=Default)?

Suppress results (Y/N - N=Default)?

6) The user may select not to halt at the end of the program before exiting back to DUS. If the tape drive was removed during the test then this option should not be choosen because an error will occur in DUS if the tape drive is not attached.

Suppress End of Program Pause (Y/N - N=Default)?

7) If at any time CNTRL-Y is used to stop the program execution a prompt will be displayed:

Enter 'GO' to continue, 'RUN' to restart, or 'EXIT' to return to DUS:

8) If an end of program pause or error pause is requested a prompt is displayed:

Enter 'GO' to continue, 'RUN' to restart, or 'EXIT' to return to DUS:

When the diagnostic is restarted using 'RUN', PTSDIAG will ask the user if the PIC - TIC configuration will be changed.

Do you want to change PIC-TIC configuration (Y/N - N=Default)?

This will also allow the user to change the diagnostic control configuration. If 'Y' the user will be prompted for path/channel information. If not the diagnostic will run with the previous configuration.

When 'EXIT' is entered in response to the prompts, the diagnostic will return directly to DUS.

#### 3.2.4 End of Diagnostic and return to DUS

As PTSDIAG is executed, after every pass a 'heartbeat' message is displayed informing the user of the number of passes completed and the total number of errors. If the diagnostic is not exited early and suppress end of pause is set, then when the loop count has expired a completion message is displayed and the program returns to DUS.

PTSDIAG testing completed

#### 3.4 Compatability Specifications

The PTSDIAG is a new product and not a replacement. It takes one test from TICDIAG and one step from PICDIAG to make one complete test using both the PIC and TIC.

#### 3.5 Security Specifications

PTSDIAG runs under DUS and as such runs in priviledged mode. The system must be down to load DUS and run the diagnostic.

#### 3.6 Error Messages

If an error occurs during execution of PTSDIAG and it is not an error trapped by the PTSDIAG program, it will result in a DUS error message. This should not occur except under very unusual circumstances, ie. some part of the system other than the TIC or PIC under test failed to function properly.

Each error trapped by PTSDIAG will result in an error message.

#### 3.6.1 PIC Error Messages

The following are errors generated from the PIC DMA transfers:

a) Output Transfer failed on PICs:

EXAD=%XXXXXX X'START=%XXXXXX Y'START=%XXXXXX X'ERROR=%XXXXXXX Y'ERROR=%XXXXXXX X'DATA=%YYYYYY Y'DATA=%YYYYYYY

Where XXXXXXX = an octal address

YYYYYYY = an octal word of data

b) Input Transfer failed on PICs:

EXAD=%XXXXXX YSTART=%XXXXXX ZSTART=%XXXXXX Y'ERROR=%XXXXXX Z'ERROR=%XXXXXX Y'DATA=%YYYYYY Z'DATA=%YYYYYY

c) Controller Channel program error:

CPVA(0) = %YYYYYY

d) Device read error:

CPVA(1) = %YYYYYY

e) Device Channel program error:

CPVA(2) - %YYYYYY

f) Interrupt Status of Device incorrect:

Expected STAT1 = %YYYYYY; Expected STAT2 = %YYYYYYY STAT1 = %YYYYYYY; STAT2 = %YYYYYYY

e) Secondary Address on Device incorrect:

Expected LSA = %YYYYYY; Expected TSA = %YYYYYYY LSA = %YYYYYYY; TSA = %YYYYYYY

Where: X'START = Address of start of controller source buffer

Y'START = Address of start of controller destination buffer or device

source buffer

Z'START = Address of start of device source buffer

X'ERROR = Address of error in controller source buffer

Y'ERROR = Address of error in controller destination buffer or device source buffer

Z'ERROR = Address of error in device source buffer

EXAD = Bank address of all data buffers.

X'DATA = Data found in address with error in controller source buffer

Y'DATA = Data found in address with error in controller destination buffer or device source buffer

Z'DATA = Data found in address with error in device destination buffer

CPVA = Error conditions for the DMA transfer

STAT1 = Interrupt status from device reg. 2 for the read DMA

STAT2 = Interrupt status from device reg. 2 for the write DMA

LSA = Secondary listen address from device reg. 0

TSA = Secondary talk address from device reg. 0

#### 3.6.2 TIC Error Messages

The following are error messages generated from the TIC DMA transfers:

a) Timer expired waiting for an interrupt from the TIC:

Ports Received: X X X ... or

Ports Received: NONE!

Where  $1 \le X \le 7$

b) Wrong port number was received:

Expected Ports = 1-7; Received Port # = X X X ...

Where X is a decimal number.

c) Wrong interrupt was received:

Port # = XX; Expected interrupt = %XX; Received interrupt = %XX

d) Buffer compare error:

PORT # = XX BANK = XX

SOURCEB'START = %XXXXXXX; RECEIVEDB'START = %XXXXXXX

SOURCE'ERROR = %XXXXXXX; RECEIVED'ERROR = %XXXXXXX

SOURCE'DATA = %YYYYYYY; RECEIVED'DATA = %YYYYYYY

Where: BANK = Bank of source buffer and destination buffer

SOURCEB'START = Address of start of source buffer

RECEIVEDB'START = Address of start of destination buffer

SOURCE'ERROR = Address of source buffer error

RECEIVED'ERROR = Address of destination buffer error

SOURCE'DATA = Data from address with error in source buffer

RECEIVED'DATA = Data from address with error in destination buffer

# **SERIES 37 MEMORY**

Diagnostic Manual

PRELIMINARY

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company.

# **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

The software code printed alongside the date indicates the version level of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

| First | Edition | mon | VVVV |

|-------|---------|-----|------|

# Table of Contents

| Section 1 GENERAL INFORMATION        |                                                                                                                                    |                                 |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1. 1<br>1. 2<br>1. 3                 | Introduction.  Required Hardware.  Required Software.  Diagnostic Program Structure.  Test Limitations.                            | 1-3<br>1-3<br>1-3               |

|                                      | tion 2 ERATING INSTRUCTIONS                                                                                                        |                                 |

| 2. 1<br>2. 2<br>2. 3<br>2. 4<br>2. 5 | Introduction. Test Selection. Looping. Error Handling. Printing Messages. How To Run MDIAG37. How To Configure MDIAG37.            | 2-1<br>2-1<br>2-2<br>2-2<br>2-2 |

|                                      | cion 3<br>ST DESCRIPTIONS                                                                                                          |                                 |

| 3. 1<br>L                            | Introduction.  Test Section 1                                                                                                      | 3-1<br>3-1                      |

| 3.3<br>A<br>3.4                      | Test Section 3. Address Test. Test Section 4.                                                                                      | 3-3<br>3-3<br>3-6               |

| 3. 5<br>D<br>3. 6                    | Alternating Ones and Zeros Test.  Test Section 5.  Data Pattern Test.  Test Section 6.                                             | 3-8<br>3-8<br>3-9               |

| 3. 7<br>N<br>3. 8                    | Move Data Test.       3         Test Section 7.       3         March Ones and Zeros Test.       3         Test Section 8.       3 | 3-10<br>3-10<br>3-11            |

| 3.9                                  | Jow Memory Test.       3         Test Section 9.       3         Log Test.       3                                                 | 3-1                             |

Appendix A SYNDROME CODES

# LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the date of the most recent version of each page in the manual. To verify that your manual contains the most current information, check the dates printed at the bottom of each page with those listed below. The date on the bottom of each page reflects the edition or subsequent update in which that page was printed.

| Effective Pages |     | Date |

|-----------------|-----|------|

|                 |     |      |

| all             | Mor | YYYY |

# **GENERAL INFORMATION**

SECTION

1

#### 1.0 INTRODUCTION

This manual describes the diagnostic program for the Memory in the HP 3000 Series 37. The MDIAG37 will test all of memory and all control functions, and will force single and double-bit error detection and single-bit error correction.

This diagnostic is a tool that can be used to locate bad memory chips, verify memory control circuitry, and verify the correct operation of the Error Detection and Correction circuit (EDAC).

MDIAG37 is written in SPL and is run under the Diagnostic/Utility System (DUS).

### 1.1 REQUIRED HARDWARE

The hardware required to run MDIAG37 is the HP 3000 Series 37 minimum configuration:

Console (connected to the TIC at slot 1, port 0)

HP-IB Tape Drive

SPU (with the following board set): CPU

Memory\*

TIC

PIC\*\*

### 1.2 REQUIRED SOFTWARE

The most recent revision of the following software is required:

DUS

<sup>\*</sup>located in slot 2 of the SPU -- must work well enough to initiate MDIAG37

<sup>\*\*</sup>needed as a coldload path to load DUS

# 1.3 DIAGNOSTIC PROGRAM STRUCTURE

The MDIAG37 is composed of tests that can be run individually or in any combination that you select. The selected tests can be looped a specific number of times or until you halt them. The tests always run in ascending numerical order.

Tests 1, 8, and 9 do NOT allow error looping.

#### 1.4 TEST LIMITATIONS

This diagnostic is intended to isolate specific RAM and/or EDAC failures. The system to be tested needs to be functioning well enough to load DUS.

Multiple-bit errors will cause MDIAG37 to lose control over error reporting and the ability to recover from the interrupt, EXCEPT during Test Section 2. All other test sections will display the following message:

System Halt 6

CPU memory parity error -- multi-bit error.

The number of the test section in which the halt occurred will also be displayed.

# **OPERATING INSTRUCTIONS**

SECTION

2

#### 2.0 INTRODUCTION

This section of the manual describes how to operate the memory diagnostic (MDIAG 37).

The primary function of MDIAG37 is to test and diagnose the HP 3000 Series 37 memory. The most important feature of MDIAG37 is that you control test selection, looping, error handling, and printing messages.

#### 2.1 TEST SELECTION

MDIAG37 is divided into tests that can be run individually or in combinations. The order in which the tests run, however, is fixed. Use the TEST command to select tests.

Use the List Diagnostic. Status (LDS) command to list which tests are currently selected. A "1" under the test number indicates that test section is enabled. A "0" indicates that test section is disabled.

The standard default selects all tests. If you want to run a simple "go/no go" version of MDIAG 37, select the following test list:

- 1) Test Section 1 Low Memory/Diagnostic Compatability Test

- 2) Test Section 2 EDAC Test

- 3) Test Section 3 Address Test

- 4) Test Section 6 Move Data Test

- 5) Test Section 9 Log Test

To change the test selection, enter TEST, then enter a "-" in front of the test number(s) to be deleted, or enter a "+" in front of the test number(s) to be added. Enter TEST and a list of test numbers without using a "-" or a "+" to select only those tests that you list.

#### 2.2 LOOPING

You can select two types of looping when you configure MDIAG37.

The first type loops on the selected test list the number of times that you specify. If you do not enter a parameter, the selected tests will be looped until you halt them. Set the LOOPOFF option to discontinue looping. LOOPOFF also turns off the loop on error (LOOPERR) option. The loop count can be any number from 1 to 32,767.

The second type loops on failure. If specified, the failing test will loop continuously until you halt it with CNTRL-Y. At this point, the LOOPERR option is also turned off.

#### 2.3 ERROR HANDLING

Error messages cannot be suppressed. However, you have the option of displaying the error messages on the console (default) or of routing them to a printer (PEMP). Make certain that the printer is connected before DUS is initialized. The printer connection is not verified by MDIAG37.

You also have the option to pause on error (default) or to continue with the diagnostic (SEPS).

Only the most recent single-bit error is saved because there is only one location per memory board for error logging. Compare data errors or errors found in the EDAC test are all displayed.

#### 2.4 PRINTING MESSAGES

There are two types of messages: error and information. Error messages tell you that the memory has failed to respond properly to a test. Error messages cannot be suppressed, but can be directed to a printer instead of to the console (PEMP). Information messages can be suppressed (SNDP).

#### 2.5 HOW TO RUN MDIAG37

Input to MDIAG37 is through the system console, after Test Section 1 has run or during program pauses.

Run the memory diagnostic in the following manner:

- 1) Perform MPE shutdown to logoff all users, if applicable.

- 2) Run the console selftest.

- 3) Fully reset the console.

- 4) Install a DUS tape in the cold-load device.

- 5) If the system is off, power it on by turning the keyswitch to the LOCAL or REMOTE position. If the system is already on, verify that the keyswitch is in the LOCAL or REMOTE position. Use the appropriate load command to load DUS.

- 6) DUS displays a welcome message and a prompt:

```

DIAGNOSTIC/UTILITY SYSTEM (REVISION nn.nn)

ENTER YOUR PROGRAM NAME (TYPE HELP FOR PROGRAM INFORMATION)

```

7) Type MDIAG37 in response to the prompt.

8) The memory diagnostic loads and executes Test Section 1. The following message is then displayed:

```

HP 3000 Series 37 Memory Diagnostic - (MDIAG37 nn.nn XX/XX/XX)

Begin Section 1

Begin Step 11

If step 11 does not complete without error then there are fatal

multiple-bit errors in low memory and the diagnostic will fail

to run properly.

Step 11 completed

Begin Step 12

Step 12 completed

Begin Step 13

Detected X banks of memory on X boards using 64K RAMS

Step 13 completed

Begin Step 14

Step 14 completed

End of Section 1

Type 'GO' to Continue (HELP to list commands)

```

9) At this point, GO will execute the default tests (all tests) after Section 1. To change the test selection, enter TEST with a "-" in front of the test numbers to delete those tests, or a "+" in front of the test numbers to add those tests. Without a "-" or a "+" MDIAG37 will perform just those test sections listed.

```

Examples: TEST -5,6,7 or TEST -5/7 will delete tests 5-7

TEST +2,3,4 or TEST +2/4 will add tests 2-4

TEST 1,2,3,6,9 to run tests 1,2,3,6, and 9 (go/no go)

```

If you inadvertently select no tests by deleting test sections, MDIAG37 will select all tests (default).

10) Unless the End of Program Pause has been enabled, control is returned to DUS when the diagnostic has been executed.

# 2.6 HOW TO CONFIGURE MDIAG37

You can configure and reconfigure the diagnostic according to your needs.

MDIAG performs initialization and Section 1, followed by a prompt for an operator command. If you are going to use the default commands (indicated with an asterisk in Table 2-1), type GO in response to the prompt. If you want to reconfigure the diagnostic, you can do so at this point or after you interrupt the diagnostic. Table 2-1 provides the available commands.

Table 2-1. DIAGNOSTIC COMMANDS

| COMMAND     | NAME                            | DESCRIPTION                                                                                                                                                                                                                       |

|-------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEOPP*      | Enable End Of Program Pause     | allows end of program pause                                                                                                                                                                                                       |

| EEPS*       | Enable Error Pause              | halts after error occurs                                                                                                                                                                                                          |

| ENDP*       | Enable Non-error Display        | allows information messages                                                                                                                                                                                                       |

| EXIT        | Exits the diagnostic            | returns to DUS                                                                                                                                                                                                                    |

| GO          | resumes program at current step | allows diagnostic to continue at current step                                                                                                                                                                                     |

| HELP        | lists commands                  | lists available commands with a brief description                                                                                                                                                                                 |

| LDS         | List Diagnostic Status          | Lists the following information:                                                                                                                                                                                                  |

|             |                                 | which test sections are enabled ENDP flag: true or false EEPS flag: true or false EEOPP flag: true or false LOOPTST flag: true or false LOOPERR flag: true or false PEMP flag: true or false number of executed diagnostic passes |

| LOOPTST (n) | Loop on current Test list       | May enter a repetition factor. If a parameter is blank, the loop continues until LOOPOFF is set.                                                                                                                                  |

| LOOPERR     | Loop on test with Error         | Loops on failed test section. Halt LOOPERR with CNTRL-Y. LOOPERR is not available in test sections 1, 8, and 9.                                                                                                                   |

<sup>\*</sup> Review Copy \*

Table 2-1. DIAGNOSTIC COMMANDS

| COMMAND  | NAME                            | DESCRIPTION                                                 |

|----------|---------------------------------|-------------------------------------------------------------|

| LOOPOFF* | Do not Loop                     | overrides LOOPTST and LOOPERR                               |

| LT       | Lists Tests                     | lists available tests with a brief description              |

| PEMP     | Print Error Messages to Printer | uses printer that is defined in DUS I/O table               |

| PEMC*    | Print Error Messages to Console |                                                             |

| RUN      | restart program from section 1  | allows you to restart the diagnostic                        |

| SEOPP*   | Suppress End of Program Pause   | returns to DUS                                              |

| SEPS     | Suppress Error Pause            | does not pause after error                                  |

| SNDP     | Suppress Non-error Display      | suppresses informational messages                           |

| TEST (n) | Specify Test(s) to be executed  | allows you to select tests with a +, delete tests with a -  |

|          |                                 | NOTE: Refer to the following section for test descriptions. |

<sup>\*</sup>default configuration

# **TEST DESCRIPTIONS**

SECTION

3

## 3.0 INTRODUCTION

This section of the manual describes the test sections of the memory diagnostic (MDIAG 37).

#### 3.1 TEST SECTION 1

# Low Memory/Diagnostic Compatability Test

This section tests low memory and diagnostic compatability, reads the syndrome information, and checks memory configuration. It automatically executes when you call up MDIAG37. After completion, this test section allows the operator to change the configuration of the diagnostic.

Appendix A contains a table that decodes the syndrome codes.

NOTE

This section does NOT allow the Loop on Error option.

Step 11. Low Memory Test -- This step reads the lowest 256K bytes of memory (banks 0 and 1) to check for double-bit hardware errors. If there are any double-bit errors in bank 0 or bank 1, MDIAG37 will not run. This step does NOT have the Loop on Error option. The displayed failure indication will be a multiple-bit error system halt:

System Halt 6

CPU memory parity error -- multi-bit error.

Step 12. Diagnostic Compatability -- This step checks that the system you are testing has the correct CPU. This step does NOT have the Loop on Error option. If an incorrect CPU is detected, the following message is displayed:

This diagnostic is only for an HP 3000 Series 37 System.

Step 13. Memory Configuration -- This step determines the size of memory by reading a location in each consecutive bank until a Memory Bounds Violation occurs. This information is displayed by the following message:

Detected XX banks of memory on Y boards using ZZZK Rams.

Where: XX = 1-32 (indicating the number of banks) Y = 1/2ZZZ = 64/256

If no valid last bank number is found, the following error message is displayed:

Last Bank No. Invalid

If a Memory Bounds Violation is not detected, the following error message is displayed:

Memory Bounds Violation not detected - default ending bank = 3.

This step does NOT have the Loop on Error option.

Step 14. Clear Memory Status -- This step reads the memory status of 1 or 2 boards to clear the error syndrome code. It does NOT have the Loop on Error option.

#### 3.2 TEST SECTION 2

## **EDAC Test**

This section performs a simple pattern test on all memory boards present. It then checks the Error Detection and Correction Circuit (EDAC) to ensure that the board will function correctly with single-bit errors present.

Step 21. Simple Pattern Test -- This step does a simple pattern test before beginning the EDAC test to detect faulty RAMs. Since the EDAC facility cannot be shut off, this is the only way to ensure that the EDAC test is using locations that are free of errors.

Error message:

Single-bit error detected

Board: X

Syndrome Code: %YYY Chip Number: UZZZZ

Where: X = 0/1

YYY = Octal Syndrome Code

<sup>\*</sup> Review Copy \*

Step 22. EDAC Test -- This step verifies that single-bit error detection and correction is performed correctly. The 32 single-bit errors that can occur are generated. Proper error correction is then checked. The syndrome latch is checked for proper error logging, causing the latch to clear. Finally, a check is made to verify that the syndrome latch is cleared.

#### Error messages:

Multi-error was detected during single-bit error test;

Board: Y; Block: Y

Where: Y = 0/1

• Error in test word was not corrected; data bit XX.

Board: Y; Block: Y

Data expected: %AAAAAA; Data received: %ZZZZZZ

Where:  $0 = \langle = XX \rangle \langle = 31$  Y = 0/1AAAAAA and ZZZZZZ = octal data

• Syndrome code expected was not returned; data bit XX.

Board: Y; Block: Y

Expected: %AAA; Received: %ZZZ

Where: 0<=XX<=31 Y = 0/1 AAA and ZZZ = octal syndrome codes

Syndrome latch was not cleared after status was reported;

Board: Y

Where: Y = 0/1

Step 23. EDAC Test - Double-bit Errors -- This step will verify double-bit error detection and correction. Thirty random double-bit errors are generated and checked for proper handling. The syndrome latch is checked for proper error logging.

Error messages:

Multi-error was detected during double-bit error test.

Board: Y; Block: Y

Where: Y = 0/1

• Syndrome code expected was not returned;

Board: Y; Block: Y

Expected: %AAA; Received: %ZZZ

Where: Y = 0/1

AAA and ZZZ = octal syndrome codes

Syndrome latch was not cleared after status was reported;

Board: Y

Where: Y = 0/1

## 3.3 TEST SECTION 3

#### Address Test

Step 31. Address Test -- This step will write the "exclusive or" of the bank and address of every available location into itself. Each location is then read and verified. This procedure is repeated, using the compliment of the "exclusive or" of the bank and address of every location as data. If this test fails, the unique address capability may have failed.

The following messages will appear during test execution:

```

Begin Section 3

Begin Step 31

All of tested memory has been written

Pass 1 completed - Begin Pass 2

All of tested memory has been written

Step 31 completed

End of Section 3

```

#### Error message:

```

Expected: %XXXXXX; Received: %YYYYYY

Address = %ZZZZZZZ

Bank = W

Board = A

```

```

Where: XXXXXX = data expected in octal

YYYYYY = data received in octal

ZZZZZZ = address of error in octal 0 <= Z <= 177777

W = bank with error 0 <= W <= 31

A = 0/1

```

## 3.4 TEST SECTION 4

# **Alternating Ones and Zeros Test**

Step 41. Alternating Ones and Zeros Test -- This step writes an alternate one and zero pattern into all available memory locations in ascending address order and then reads them back. The complement pattern is then written and read back. The error latch is read after testing each pattern to check whether any single bit errors were detected.

The following message will appear during test execution:

```

Begin Section 4

Begin Step 41

All of tested memory has been written

Pass 1 completed - Begin Pass 2

All of tested memory has been written

Step 41 completed

End of Section 4

```

The following error message will be displayed only if error correction is NOT working:

The error latch information will be displayed if an error was detected during the test. Bad memory chips are identified only by the error latch information.

Error message:

Single-bit error detected

Board: X

Syndrome Code: %YYY Chip Number: UZZZZ

Where: X = 0/1

YYY = octal syndrome code

### 3.5 TEST SECTION 5

#### **Data Pattern Test**

Step 51. Data Pattern Test -- This step writes 64K data patterns into one 32-bit memory word in each block. This function attempts to access each chip on each board in order to point out any malfunctioning chips. The data patterns are generated by using the 64K possible patterns in the lower 16 bits and the one's complement of the pattern in the upper 16 bits.

The following message will be displayed during test execution:

```

Begin Section 5

Begin Step 51

Test is half way to completion

Step 51 completed

End of Section 5

```

The following error message will be displayed only if error correction is NOT working:

The error latch information is displayed if an error was detected during the test. Bad memory chips are identified only by the error latch information.

# 3.6 TEST SECTION 6

#### Move Data Test

Step 61. Move Data Test -- This step uses the lower 32K-bytes of memory as a data bank and copies it to every other 32K-byte block. The error latch is checked after each 32K-byte move operation. This step uses the Move Absolute Instruction for speed and simplicity. This step is repeated, using the 32K-bytes of each block as the data to write back into that block.

#### Error message:

Single-bit error detected

Board: X

Syndrome Code: %YYY Chip Number: UZZZZ

Where: X = 0/1

YYY = octal syndrome

## 3.7 TEST SECTION 7

### March Ones and Zeros Test

Step 71. March Ones/Zeros -- This step marches first ones and then zeros through each 32K-byte block of memory. Each 32K-byte block of memory is written to all zeros. Then each location is read for a zero and then written to all ones. When the block contains all ones, the process is repeated by reading each location for all ones and then writing a zero. The error latch is checked after each 32K-byte block of memory is completed.

The following error messsage will be displayed only is error correction is NOT working:

Expected: XXXXXX; Received: YYYYYY Address: %ZZZZZZ Bank = W Board = A Where: XXXXXX = data expected in octal

YYYYYY = data received in octal ZZZZZZ = address of error in octal 0 < = Z < = 177777 W = bank with error 0 < = W < = 31A = 0/1

The error latch information will be displayed if an error was detected during the test. Bad memory chips are identified only by the error latch information.

Single-bit error detected Board: X

Syndrome Code: %YYY

Chip Number: UZZZZ

Where: X = 0/1

YYY = octal syndrome code

### 3.8 TEST SECTION 8

# **Low Memory Test**

This section relocates the program and checks the memory area where the program was originally located (banks 0 and 1). It is then relocated back. This section will NOT respond to the Loop on Error option and does NOT provide error messages until the last step is completed. In addition, it will NOT respond to CNTRL Y or any other type of I/O.

- Step 81. Program Relocation -- This step will relocate MDIAG 37, DUS, stacks, and the Device Reference Table (DRTS) into Banks 2 and 3 in order to test the area in lower main memory, where the program was originally located.

- Step 82. Marching Ones and Zeros -- This step is identical to Step 71. These locations are written and read by the diagnostics. Any errors are recorded in the error latch. Because of limitations imposed by the relocation of the diagnostic, only the last error encountered by the marching test will be reported.

- Step 83. Program Re-Relocation -- This step relocates the program back to its original area in lower main memory. The memory status is checked and any errors that were encountered in the marching test (Step 82) are now displayed.

#### 3.9 TEST SECTION 9

# Log Test

Step 91. Log Test -- This step will check the error latch to make sure it has been cleared before the diagnostic returns control to DUS. This section will NOT respond to the Loop on Error option.

Error message:

Single-bit Error Detected Board: X

Syndrome Code: %YYY Chip Number: UZZZZ

Where: X = 0/1

YYY = octal syndrome code

# SYNDROME CODES

A

Table A-1. Single-bit Error Syndrome Codes

| OCTAL SYNDROME<br>CODE | BIT NUMBER  |

|------------------------|-------------|

| % 14                   | data bit 0  |

| % 254                  | data bit 1  |

| % 264                  | data bit 2  |

| % 324                  | data bit 3  |

| % 24                   | data bit 4  |

| % 344                  | data bit 5  |

| % 44                   | data bit 6  |

| % 104                  | data bit 7  |

| % 72                   | data bit 8  |

| % 132                  | data bit 9  |

| <b>% 232</b>           | data bit 10 |

| <b>x</b> 152           | data bit 11 |

| <b>%</b> 252           | data bit 12 |

| <b>%</b> 312           | data bit 13 |

| % 162                  | data bit 14 |

| % 322                  | data bit 15 |

| % 216                  | data bit 16 |

| <b>%</b> 56            | data bit 17 |

| <b>%</b> 66            | data bit 18 |

| % 126                  | data bit 19 |

| % 226                  | data bit 20 |

Table A-1. Single-bit Error Syndrome Codes

| OCTAL SYNDROME<br>CODE | BIT NUMBER  |

|------------------------|-------------|

| % 146                  | data bit 21 |

| % 246                  | data bit 22 |

| % 306                  | data bit 23 |

| % 270                  | data bit 24 |

| % 330                  | data bit 25 |

| % 30                   | data bit 26 |

| % 350                  | data bit 27 |

| % 50                   | data bit 28 |

| % 110                  | data bit 29 |

| % 360                  | data bit 30 |

| % 120                  | data bit 31 |

| <b>%</b> 176           | check bit 0 |

| <b>%</b> 276           | check bit 1 |

| <b>x</b> 336           | check bit 2 |

| <b>%</b> 356           | check bit 3 |

| <b>x</b> 366           | check bit 4 |

| <b>%</b> 372           | check bit 5 |

| <b>%</b> 374           | check bit 6 |

NOTE: (1) There is a decimal/octal/hexidecimal conversion chart at the beginning of this diagnostic manual set.

(2) The syndrome codes in this table are transposed and then shifted one bit to the left from those listed in the manufacturer's data sheet for the EDAC chip. This octal syndrome code is the same for block 0 and block 1.

# Self-test Diagnostics

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company.

## PRINTING HISTORY

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

The software code printed alongside the date indicates the version level of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

| First Edition Sep 1984 Sep 1984 | First | $Edition \$ |  |  | p 1984 |  |  |

|---------------------------------|-------|-------------|--|--|--------|--|--|

|---------------------------------|-------|-------------|--|--|--------|--|--|

## LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the date of the most recent version of each page in the manual. To verify that your manual contains the most current information, check the dates printed at the bottom of each page with those listed below. The date on the bottom of each page reflects the edition or subsequent update in which that page was printed.

| Effective Pages |     | Date |

|-----------------|-----|------|

| all             | Sep | 1984 |

**PRELIMINARY**

#### Table of Contents

# PRELIMINARY

| Section? |      |     |      |

|----------|------|-----|------|

| GENERAL. | INFO | RMA | TION |

|                      |                            | _                 |

|----------------------|----------------------------|-------------------|

|                      | Introduction               |                   |

|                      | Required Hardware          |                   |

|                      | Self Test ROM Code         |                   |

|                      | Self Test Executive        |                   |

|                      | Power-on Self Test         |                   |

|                      | Maintenance Mode Microcode | -                 |

|                      | Control B Mode             |                   |

| 1.7                  | Test Limitations           | ?-3               |

|                      |                            |                   |

|                      |                            |                   |

| Secti                | · · ·                      |                   |

| OPT                  | RATING INSTRUCTIONS        |                   |

|                      |                            |                   |

|                      | duction                    |                   |

|                      | Execution                  |                   |

|                      | rol B Mode                 |                   |

|                      | Test                       |                   |

| Remo                 | ote Operator Interface     | ?-3               |

|                      | •                          |                   |

|                      |                            |                   |

| Section              |                            |                   |

| TES?                 | T DESCRIPTIONS             |                   |

|                      |                            |                   |

|                      | ntroduction                |                   |

|                      | Power On Test Execution    |                   |

| 3. 2 C               | Control B Mode Commands    | ?-1               |

| Αι                   | uto Restart                | ?-2               |

|                      | oldload                    |                   |

|                      | polstart                   |                   |

|                      | sc                         |                   |

| Dı                   | ump                        | ?-3               |

|                      | elp                        |                   |

|                      | vad                        |                   |

|                      | ewsystem                   |                   |

|                      | eload                      |                   |

|                      | in.                        |                   |

|                      | eed                        |                   |

| _                    | art                        |                   |

|                      | ipe                        |                   |

|                      | est.                       |                   |

|                      | pdate                      |                   |

|                      | armstart                   |                   |

|                      | Test Mode                  |                   |

|                      | l                          |                   |

|                      |                            |                   |

|                      |                            | _ ! !             |

| Cł                   | nannel?                    |                   |

| Cł<br>Cł             | PU?                        | -11               |

| Cl<br>Cl<br>Ex       | PU?<br>xit?                | -11<br>-12        |

| Cl<br>Cl<br>Ex<br>He | PU?                        | -11<br>-12<br>-13 |

#### Table of Contents

| Memory                     |             | ?-14 |

|----------------------------|-------------|------|

| Self Test PON              |             | ?-15 |

| Appendix ? Error Codes     | PRELIMINARY |      |

| Control B Mode Error Codes |             | 2-1  |

## GENERAL INFORMATION

SECTION

?

## PRELIMINARY

#### 1.0 INTRODUCTION

This manual describes the Self Test for the HP 3000 Series 37 in both power-on (PON) mode and maintenance mode.

The Self Test is the primary turn-on test. It tests for a functioning CPU, Memory, TIC, PIC, and Synchronous Intermodule Bus (SIMB). Self Test will also verify the cold load path.

Self Test executes when any of the following happens:

- power-on via the keyswitch

- maintenance mode initiated via the system console (Control B)

- restart after power failure

- system crash

#### 1.1 REQUIRED HARDWARE

The hardware required to run Self Test is the HP 3000 Series 37:

CPU Memory TIC PIC

Console (connected to TIC channel 1/port 0) a supported cold load device

The power-on self test sequence is CPU, Memory, TIC, and PIC. If a required peripheral is not connected, tests performed before that peripheral is required are valid.

#### 1.2 SELF TEST ROM CODE

The ROM code is made up of three subsets: executable ROM code and two types of loadable ROM code executable code and ROM-based messages.

The executable ROM code loads the first series of self tests from loadable ROM code into Writable Control Store (WCS) upon power-on. Control is then passed to the code loaded into WCS.

This code tests the CPU chip and slow WCS. It then loads the Code Loader and the second series of tests into Slow WCS.

The second series of tests check additional portions of the CPU chip, fast WCS, and the CPU register file.

When these tests are successfully completed, the maintenance panel code is loaded into WCS and enabled. Then the Self Test Executive is loaded into WCS and control is passed to it.

#### 1.3 SELF TEST EXECUTIVE

The Self Test Executive determines if an Auto Restart after power failure is to be performed. Auto Restart tests a subset of the memory tests.

If a normal power-on sequence occurred, the Self Test Executive tests all of memory.

The Self Test Executive then tests all of the I/O cards installed in the system and speed senses the system console. The slot numbers of any failing cards are displayed on the console. A prompt is issued, unless Auto Warmstart is specified. If Auto Warmstart is specified, control is passed to the Loader Code and the start device number is displayed.

#### 1.4 POWER-ON SELF TEST

When power is applied to the SPU, the ROM-based Power-on Self Test is executed. Self Test loads all of the code in ROM 3 into WCS. The code in WCS is then executed.

The basic CPU chip test, a general WCS test, and a ROM code loader are in ROM 3. This code tests some of the Series 37 CPU chip functions. The last CPU chip function tested is all of Slow WCS and then CPU test modules are loaded. These modules test the remaining CPU chip functions. When these tests are complete, the Mainframe Panel module, the Control module, and the Test Executor module are loaded. Control is then passed to the Test Executor.

The Test Executor loads the memory tests, the TIC test, and the PIC test. The memory tests are then executed. If a failure occurs, the memory tests are successfully executed, the console TIC and all of the other boards in the SPU are tested. The results are displayed on the LED display.

The Control module initializes the TIC and displays the H for help-> prompt.

#### 1.5 MAINTENANCE MODE MICROCODE

The maintenance mode microcode contains the code for Control B sequences and the Series 37 Self Test. Unlike earlier versions of HP 3000 computers, there is no special maintenance processor. The maintenance microcode resides on the CPU board. The Control B detection logic is enabled on the TIC that is in slot 1 channel 1 of the SPU card cage. Only the console connected to Port 0 or the remote console can execute the Control B sequence.

#### 1.6 CONTROL B MODE

The Control B sequence can be issued and executed only from the system console. When you initiate the Control B sequence, software execution halts. The Control B maintenance microcode then begins

execution. Note that the MPE environment is protected only if you execute a Run, Help, or Dump command. If any other commands are executed, MPE is not protected.

#### 1.7 TEST LIMITATIONS

## **OPERATING INSTRUCTIONS**

SECTION

?

## PRELIMINARY

#### INTRODUCTION

This section describes how to operate both the Power On Self Test and the Maintenance Mode Microcode.

The primary function of the Power On Self Test is to verify the correct operation of the logic necessary to load the system.

The maintenance mode microcode contains the code for interpreting maintenance commands and the Series 37 Self Test. Since the Series 37 does not have a special maintenance processor, the maintenance microcode resides on the CPU borad. The Control B detection logic is on the TIC. Only the TIC in slot 1 (channel 1) can have the the Control B logic enabled. To enable the logic, the keyswitch must be in either the Local or Remote position. Note also that only the console connected to port 0 (local) or port 7 (remote) can execute the Control B sequence.

#### PON EXECUTION

Immediately upon powering on the CPU, the LED display will flash "0", "1", and "2" (the "1" may not be visible) as the first Series of tests are loaded into the WCS. Then a "5", indicating card 5 of the CPU, is displayed as the CPU tests are executed. Upon successful completion of the CPU tests, a "B" will be displayed as the memory tests are executed. Upon successful completion of the memory test, a "C" will be displayed as all of the I/O cards in the system are tested and the console is speed sensed. If any of the tests fail, the failing assembly will be indicated in the LEDs as well as on the console if the console path is operational.

A Flashing "B" indicates that the memory test failed, a flashing "C" or "1" indicates that the console failed to speed sense or that the console TIC is bad. A steady or flashing "5" indicates that the CPU card failed. All other failing I/O cards are indicated by the slot number of the failing card. If the failing card is in the Extender an "E" preceeds the the slot number.

If all the tests were passed successfully, the results will be displayed on the console and a prompt will be sent to the console unless Auto Warmstart is indicated. If the Auto Warmstart was indicated control will be passed to the loader code with the START Device indicated.

If Power On looping was specified from the test mode, the Power On Self Test will be looped until the loop count reaches 0. When all tests have been successfully completed Control B mode is entered and the following prompt is displayed:

H for help->

#### CONTROL B MODE

Control B Mode allows the operator to perform a number of functions. The major functions which can be performed are the LOAD/START/DUMP and Self Test functions. LOAD and START load MPE from tape or disc respectively, and the DUMP command loads the dump software from from the indicated device. The Self Test function allows the operator to run the Power On Self Tests with failures displayed on the console. The Self Test Mode also allows a limited looping feature. Tests can be looped with the count parameter. Count must be an integer between 1 and 9999, with 1 being the default.

There are 13 responses to the "H for help->" prompt. The LOAD START, and DUMP commands require a channel and device specification. unless the default device has been set up by the ", P" and ", C" options. The DUMP command always defaults to the START device. The ", P" option updates the LOAD or START device data in the TOC and initiates the LOAD or START. The TOC LOAD or START data can also be updated with the ", C" option but the LOAD or START is not performed. The valid channels are 1-4 for main and 9-13 for the extender. Run attempts to "run" the system if it arrived in the H for help-> mode via a Halt or Control B. The "AR" command allows the operator to try another Autorestart if the system has given up (5 tries of approximately 90 seconds each). The other LOAD/START type commands (COO, COL, DIS, NEW, RELO, TAPE, UPDA, and WAR) use the LOAD or START deivce as stored in the TOC. The following lists the valid Control-B Mode Commands:

| Command   | DESCRIPTION                                   |  |  |  |

|-----------|-----------------------------------------------|--|--|--|

| AR        | Retry Auto Restart.                           |  |  |  |

| COLDLOAD  | Perform COLDLOAD using LOAD device.           |  |  |  |

| COOLSTART | Perform COOLSTART using START device.         |  |  |  |

| DISC      | Perform START using START device.             |  |  |  |

| DUMP      | Perform DUMP using indicated or START device. |  |  |  |

| HELP      | Display HELP messages.                        |  |  |  |

| LOAD      | Perform LOAD (has options).                   |  |  |  |

| NEWSYSTEM | Perform RELOAD using LOAD device.             |  |  |  |

| RELOAD    | Perform RELOAD using LOAD device.             |  |  |  |

| RUN       | RUN system after Control B halt.              |  |  |  |

| SPEED     | Allow operator to change console speed.       |  |  |  |

| START     | Perform START (has options).                  |  |  |  |

| TAPE      | Perform LOAD using LOAD device.               |  |  |  |

| TEST      | Go to Self Test mode.                         |  |  |  |

| UPDATÉ    | Perform UPDATE using LOAD device.             |  |  |  |

| WARMSTART | Perform WARMSTART using START device.         |  |  |  |

#### SELF TEST

The Self Test function allows the operator to run the Power On Self Test tests with failures displayed on the console. The Self Test mode also allows a limited looping feature.

The Control B mode TEST command accesses the Self Test mode. There are 8 commands available in Self Test mode; these are:

| Command                | Description                                                             |

|------------------------|-------------------------------------------------------------------------|

| A[11] [,count]         | Run all self tests 1-9999 times                                         |

| CH[an] [,count[,chan]] | Loop Test of channel 1-9999 times. The default <i>chan</i> is all chann |

C[pu] [,count] Loop CPU test 1-9999 times

e[xit] Return to Control mode

I[omap] [,count] Loop IOMAP 1-9999 times

M[emory] [,count] Loop memory test 1-9999 times

PON [count] Run (or loop) Power On Selftest (keyswitch must be in local)

#### REMOTE OPERATOR INTERFACE

The remote operator interface is enabled if all of the following conditions are met:

- The modem is connected to Port 7 of TIC in Slot 1

- The keyswitch is in Remote (or Local after having been in Remote, but not switched through Normal) mode.

- The console speed is 300 or 1200 baud

## **TEST DESCRIPTIONS**

SECTION

?

#### 3.1 INTRODUCTION

This section provides descriptions of each section of the Series 37 Self Test code. Included here are definitions of the two test modes, Control B and Self Test, and their associated commands. Also included are examples of the commands with their output and returns.

Examples of error messages can be found in Appendix A.

#### 3.2 POWER ON TEST EXECUTION

Immediately upon powering on the CPU, the LED display will flash "0", "1", and "2" as the first series of CPU tests are loaded into WCS. Then a "5" will be displayed as the CPU tests are executed. Upon successful completion of the CPU tests, a "B" will be displayed as the memory test is executed. When the memory test successfully completes, a "C" will be displayed as all of the I/O cards in the system are tested and the console is speed sensed. If any of the tests fail, the failing assembly will indicated by the LED. If the console path is s operational, the number of the failing assembly will be displayed on the console.

A flashing "B" on the console indicates that the memory test failed, a flashing "C" and "1" indicates that the console failed to speed sense or that the console TIC is bad. A steady flashing "5" indicates that the CPU card failed. All other failing I/O cards are indicated with a flashing numeral indicating the card slot of the failing card. If the failing card is in the Extender, an "E" preceeds the slot number. If the LED is blank, then the console is operational and any failure messages will appear on the system console. After successful completion of the Power On Self Test, Control B mode is entered.

#### 3.2 CONTROL B MODE COMMANDS

Control B mode is indicated by the "H for help->" prompt. Control B mode initializes the TIC for communication with the operator and allows the following test commands:

| AR (Retry AutoRestart) | Reload    |

|------------------------|-----------|

| Coldload               | Run       |

| Coolstart              | Speed     |

| Disc                   | Start     |

| Dump                   | Tape      |

| Help                   | Test      |

| LOAD                   | Update    |

| Newsystem              | Warmstart |

#### **Auto Restart**

The AUTO RESTART (AR) command allows the operator to retry the Power Fail Auto Restart capability if the Auto Restart was not successful because a disc was down or broken. To initiate an AR, the cause for the Auto Restart failure must be corrected, and then the operator may attempt an Auto Restart. Auto Restart should be successful as long as the memory has been powered, the Auto Restart flag in memory location 0.0358 (hex) is AAAA (hex), and the data in memory on the disc is uncorrupted.

The following illustrates the use of the AR command:

H for help->AR

Following the Power On CPU test, an abbreviated version of the memory test is executed to find the size of memory if the Auto Restart flag at \$0.0358 is set to \$AAAA. Upon successful execution of this test, all of the I/O cards are tested and communication is established with the console. When these steps have completed, execution is transferred to the Auto Restart entry \$5001 in the Loader code module and the WCS boot code is executed with the Auto Restart flag and LOAD/Start flags set with the start device set into register file location \$EF.

If the Auto Restart should fail because the disc was not ready, up to 4 retries will be made. If none of the retries are successful, return will be to the Control B mode "H for help->" prompt. The operator may type up to 5 tries when the disc is made ready.

#### Coldload

The COLDLOAD command loads the system microcode and software from the default tape unit and allows the operator to perform COLDLOAD, RELOAD, or UPDATE operations for MPE or run DUS. Auto coldload can be run without operator intervention.

COLDLOAD differs from LOAD in the following ways:

- No channel or device parameters are allowed.

- The default LOAD device always used.

- A code "1" in TOC location \$0D to indicate COLDLOAD.

- Auto Coldload can be run without any operator interaction.

The following illustrates the use of the COLDLOAD command:

H for help->COL[dload]

#### Coolstart

COOLSTART loads the system microcode and software from the default disc unit and allows the operator to perform COOLSTART?? or WARMSTART operations for MPE or run DUS.

COOLSTART differs from START in the following ways:

- No channel or device parameters are allowed.

- The default START device is always used.

- A code "2" is placed in TOC location \$0D to indicate COOLSTART.

- Auto Coolstart can be run without any operator interaction.

The following illustrates the use of the COOLSTART command:

```

H for help->COO[lstart]

```

???put return and output examples here????????????????

#### Disc

DISC loads the system microcode and software from the default disc unit and allows the operator to perform COOLSTART or???? WARMSTART operations for MPE or run DUS.

- No channel or Device parameters are allowed.

- The default Start device is always used.

- A code "3" is placed in TOC location \$0D to indicate COOLSTART.

- START can be executed with all normal operator interaction except for the date and time.

The following illustrates the use of the DISC command:

H for help->DIS[

$$\{c\}\{k\}$$

]

???place output and return examples here?????????????????

#### Dump

Dump loads the Dump software from the indicated device and transfers execution to the dump software. The DUMP command allows optional *channel* and *device* parameters to indicate the location of the dump software if no parameters are supplied, the dump software is loaded from the default START device. The DUMP command puts a "4" in TOC register D.

Test Description

The following illustrates the DUMP command:

```

H for help->D[ump] [chan,dev]

```

????? place output and return examples here?????????

DUMP uses the START default device number stored in the TOC RAM, or the operator may specify a different deivce. The DUMP command always asks the operator to confirm that a DUMP is to be performed. Upon confirmation, the LOAD or Start is initiated by loading and transferring control to the load execution code.

The load execution code test for valid Dump parameters and transfers control to \$5FFF if microcode resides in WCS. If no microcode is loaded, control is passed back to the Control B mode.

#### Help

The HELP command lists all of the commands along with their parameters. Specific details on the commands must be in the manuals set for the system.

Note that the optional parameters change and update allow the operator to just alter the LOAD or START channel and device (change) or alter the LOAD or START and execute a LOAD or START (update). The DUMP command puts a "7" in TOC register D.

HELP displays the version code of the currently loaded microcode or '----' if no microcode is loaded and then displays all of the capabilities of the control mode.

1-NORMAL H for help->h

Microcode Version ----- AR - Re-attempt Auto Restart COL[dload] COO[lstart] DI[sk] - Start from Disk DU[mp] [chan, dev] L[oad] [chan, dev[,{P[erm] C[hange]}]] NEW[system] RUN SP[eed] ST[art] [chan, dev[,{P[erm] C[hange]}]] REL[oad] TA[pe] - Load from Tape TE[st] UPD[ate] WAR[mstart]

1-NORMAL H for help->

#### Load

The OAD command loads the system microcode and software from the indicated or default tape unit and allows the operator to perform COLDLOAD, RELOAD, or UPDATE operations for MPE or to run DUS.

If channel and device are specified, LOAD uses these parameters as the channel and device for the LOAD. The default LOAD channel and device are also updated in the TOC register C if the optional change or update parameters are specified. The LOAD command puts a code "7" in TOC register D.

The following illustrates the use of the LOAD command:

```

H for help->LOAD ]chan,device][{C[hange},{U[pdate]}]

```

<sup>\*</sup> Review Copy \*

????place examples of output and return here???????????????

The LOAD capability allows the operator to perform a LOAD or START using the default LOAD and Start device numbers stored in the TOC RAM, specify different devices, or just change the default devices. The LOAD commands always ask the operator to confirm that the LOAD is to be performed. Upon confirmation, the LOAD is performed by loading the load execution code, the WCS boot code, and transferring control to the load execution code.

The load execution code tests for the valid LOAD or START parameters and updates the TOC RAM if requested. Control is then transferred to the to the WCS boot code. If a parameter error occurred or if only a change to parameters was requested, control is passed back to the Control B mode.

If the parameters are valid and if a LOAD or START is to be done, control is passed to the WCS boot code which loads the HP3000 instruction set from the disc or tape and proceeds with the LOAD or START.

#### Newsystem

The NEWSYSTEM command operates like the LOAD command with the following exceptions:

- No channel or device parameters are allowed.

- The default LOAD device is always used.

- A code "8" is written in TOC location \$0D to indicate RELOAD.

- A RELOAD can be executed with all normal operator interaction except date and time.

The following illustrates the use of the NEWSYSTEM command:

H for help->NEW[system]

????place examples of output and return here?????

#### Reload

The RELOAD command operates exactly like the LOAD command with the following exceptions:

- No channel or device parameters are allowed.

- The default LOAD device is always used.

- A code "B" is written in TOC location \$0D to indicate RELOAD.

- The update is executed with all normal operator interraction except date and time.

The following illustrates the use of the RELOAD command:

#### Test Description

```

H for help->RELO[ad]

```

????place examples output and return here ?????

#### Run

The RUN command returns execution to MPE or DUS if the Control B mode was entered via Control B or Halt and MPE/DUS is executable, i.e., if the RUN flag is nonzero. The LOAD command puts a code "A" TOC register D.

The following illustrates the use of the RUN command:

```

H for help->RUN

```

???place examples of output and return here ?????

The RUN capability is not implemented.

#### Speed

The SPEED command allows the operator to change the console speed simply by changing the baud rate; no other interaction is required.

The following illustrates the use of the SPEED command:

```

H for help->SPEED

Change speed now ... Change the console baud rate now

p

Failed speed senses

H for help-> Prompt now at new speed

```

To abort the speed command, type any character except Control F with the console baud rate unaltered. The LOAD command puts a code "5" in TOC register D.

When changing speeds at low baud rates, it may take up to a minute to get a prompt.

#### Start

The START command loads the system microcode and software from the indicated, or default, disc unit and allows the operator to perform the coolstart or warmstart operations for MPE or run DUS.

If the START channel and device are specified, the START command uses these parameters as the channel and device for the START. The default START channel and device are also updated in the TOC register B if the optional change or update parameters are specified. The START command puts a code "C" in TOC register D. The following illustrates the use of the START command:

```

* Review Copy *

```

H for help->Start [chan,device][{C[hange},{U[pdate]}]

????place examples of output and return here????

The START capability allows the operator to perform a START using the default START device numbers stored in the TOC RAM, specify different devices, or just change the default devices. START always asks the operator to confirm that the start is to be performed. Upon confirmation, the START is performed by loading the load execution code, the WCS boot code, and transferring control to the load execution code.

The load execution code tests for the valid START parameters and updates the TOC RAM if requested. Control is then transferred to the to the WCS boot code. If a parameter error occurred or if only a change to parameters was requested, control is passed back to the Control B mode.

If the parameters are valid and if a LOAD or START is to be done, control is passed to the WCS boot code which loads the HP3000 instruction set from the disc or tape and proceeds with the LOAD or START.

#### Tape

The TAPE command operates exactly like the LOAD command with the following exceptions:

- •" No channel or device parameters are allowed.

- •" The default LOAD device is always used.

- •" A code "D" is written in TOC location \$0D to indicate COOLSTART.

- •" An Auto Coolstart can be run without any operator intervention.

The following illustrates the use of the TAPE command:

H for help->TAPE

Your momma!

Welcome to Maintenance Mode

2-LOCAL (from Normal) H for help->tape

Do you want to abort the system (Y/N)? yu

Diagnostic/Utility System Revision 03.00 Enter Your Program Name (type HELP for program information)

#### Test

The TEST command transfers control to the Self Test Executive which displays all of the Self Test capabilities and the Self Test prompt. The TEST command puts a code "E" in TOC register D.

The Control B mode code requests confirmation that test mode is to be entered. If confirmed, the Test Executor module is loaded and control is transferred to the Self test entry point in the Test Executor module. If not confirmed, control is transferred back to Control B mode.

The Self Test entry point in the Test Executor module Displays the capabilities of the Self Test mode and the "Self Test ->" prompt. The following commands are allowed in Selt Test mode:

```

1-NORMAL

H for help->TE

ROM Versions: 1. 2418 2. 2418 3. 2418 4. 2418

Selftest Menu:

AL[1] [ count ]

CH[an] [ count [ ,chan ] ]

CP[u] [ count ]

E[xit]

I[omap] [ count ]

M[emory] [ count ]

PON [ count ]

```

These commands are discussed in detail in section 3.3 Selftest Mode

#### **Update**

Self Test ->

The UPDATE command operates exactly like the LOAD command with the following exceptions:

- •" No channel or device parameters are allowed.

- •" The default LOAD device always used.

- •" A code "F" is written in TOC location \$0D to indicate UPDATE.

- •" An UPDATE can be exectuted with all normal operator interaction except for date and time.

The following illustrates the use of the UPDATE:

```

H for help->UPDA[te]

```

```

* Review Copy *?-8

```

???place examples of output and return here.?????

#### Warmstart

The WARMSTART command operates exactly like the START command with the following exceptions:

- •" No channel or device parameters are allowed.

- •" The default START device is always used.

- •" A code "0" is written in TOC location \$0D to indicate WARMSTART.

- "An Auto Coolstart can be run without any operator interaction.

The following illustrates the use of the WARMSTART command:

H for help->War[mstart]

???place examples of output and return here?????

This command enables the Automatic Warmstart feature which does a WARMSTART without any operator interaction upon powering on the system. Software may be written to enable this feature by simply writing a "0" to TOC location \$0D.

## SELF TEST MODE PRELIMINARY

Self Test mode is entered with the Control B mode TEST command. The Self Test mode allows all of the Self Test steps to be manually directed. The following Self Test commands will be discussed in greater detail:

All Channel CPU Exit Help IOMAP

TOMAP

MEMORY

PON