## **HP 3000 Computer Systems**

# HP 3000 SERIES 44 AND HP 3000 SERIES 40 COMPUTER SYSTEMS

## Reference/Training Manual

COMPUTER SYSTEMS DIVISION, 19447 PRUNERIDGE AVE., CUPERTINO, CALIFORNIA 95014

| N | O | TI | C | E |

|---|---|----|---|---|

|   |   |    |   |   |

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

#### **LIST OF EFFECTIVE PAGES**

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. Changes are marked with a vertical bar in the margin. If an update is incorporated when an edition is reprinted, these bars are removed but the dates remain. No information is incorporated into a reprinting unless it appears as a prior update.

| Title       | EPT 1981 |

|-------------|----------|

| ii          | riginal  |

| iii thru xv |          |

| 10-1/10-25  | EPT 1981 |

#### **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover of the manual changes only when a new edition is published. When an edition is reprinted, all the prior updates to the edition are incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

The software product part number printed alongside the date indicates the version and update level of the software product at the time the manual edition or update was issued. Many product updates and fixes do not require manual changes, and conversely, manual corrections may be done without accompanying  $\rho$ roduct changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

| First EditionJUN  | 1981 |

|-------------------|------|

| Update 1SEPT      | 1981 |

| Updat 1 IncorpMar | 1986 |

This manual contains hardware information for the HP 3000 Series 44 and HP 3000 Series 40 Computer Systems. Specifically, this manual contains perequisite reading material for all personnel that attend Hewlett-Packard training courses related to these systems. Since the information contained in this manual is approximately the same as that presented during classroom lectures, this manual should be retained for classroom reference, review, and note-taking purposes.

The HP 3000 Series 44 and HP 3000 Series 40 Computer Systems are functionally the same, differing only in physical characteristics and power supplies. Since both systems utilize the same hardware and operating system, and can be operated identically, this manual is divided into two parts. Part 1 consists of detailed information for HP 3000 Series 44 and that which is common to both systems. Part 2 contains information that applies only to the HP 3000 Series 40. References are made from Part 2 to Part 1 for information common to both systems.

Additional Hewlett-Packard documents that may be used during the training course and for on-site references are:

- HP 3000 Series 40 Installation Manual, P/N 30090-90002

- HP 3000 Series 40 System Block Diagram, P/N 30090-90003

- HP 3000 Series 40 U Code Listing, P/N 30090-90004

- HP 3000 Series 40 CMP Self Test Manual, P/N 30090-90005

- HP 3000 Series 40 CMP Remote Maintenance Manual, P/N 30090-90006

- HP 3000 Series 40 CMP Maintenance Mode Manual, P/N 30090-90007

- HP 3000 Series 40 Pronto Memory Diagnostic Manual, P/N30090-90001

SEPT 1981 v

### **PREFACE** (continued)

HP 3000 Series 40 Upgrade Installation Manual, P/N 30090-90008

HP 3000 Series 40 Engineering Diagram Set, P/N 30090-90009

HP 3000 Series40 Memory Add-On Installation Manual, P/N30090-90002

HP 3000 Series 40 30087A Upgrade Kit Installation Guide, m85 P/N 30079A-90002

HP 3000 Series 40 300079A Add-On Installation Manual, P/N 30079A-90002

HP 3000 Series 44 Installation Manual, P/N 30170-90002

## CONTENTS

| PART 1                                                                                                                                                                                          |                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| HP 3000 Series 44 Computer System                                                                                                                                                               |                                                 |

| SECTION I - GENERAL SPECIFICATIONS                                                                                                                                                              |                                                 |

| Paragraph                                                                                                                                                                                       | Page                                            |

| PHYSICAL DIMENSIONS  POWER REQUIREMENTS  ENVIRONMENTAL  PROCESSOR  MEMORY  INPUT/OUTPUT STRUCTURE                                                                                               | 1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7          |

| SECTION II - SYSTEM CONTROL PANEL/CONSOLE                                                                                                                                                       |                                                 |

| Paragraph                                                                                                                                                                                       | Page                                            |

| INTRODUCTION  SYSTEM CONTROL PANEL  Switch Functions  Indicator Lights  SYSTEM CONSOLE  Console Control Functions                                                                               | 2-2<br>2-2<br>2-3<br>2-5<br>2-5<br>2-6          |

| SECTION III - SYSTEM OVERVIEW                                                                                                                                                                   |                                                 |

| Paragraph                                                                                                                                                                                       | Page                                            |

| INTRODUCTION BUS SYSTEM Intermodule Bus HP-IB RS-232-C Data Communication Line PROCESSOR ELEMENTS I/O ELEMENTS General I/O Channel Asynchronous Data Communication Channel MAIN MEMORY ELEMENTS | 3-2<br>3-2<br>3-8<br>3-9<br>3-9<br>3-16<br>3-16 |

| SECTION III - SYSTEM OVERVIEW (Continued)                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                            |

| MAINTENANCE/CONTROL ELEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-11<br>3-12<br>3-12<br>3-12                                                                                                    |

| SECTION IV - CENTRAL PROCESSOR UNIT                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                                                            |

| INTRODUCTION FUNCTIONAL DESCRIPTION Instruction Execution Microinstructions DATA PATHS General Operand Sources MICROINSTRUCTION SEQUENCING OPTIONS Jumps Skips Repeats Next MACROINSTRUCTION SEQUENCING Operation Single Macroinstructions IMB INTERFACE CPU Memory Read Operation Other Operations Processor Freezes Error Conditions COMPONENT DESCRIPTION Next Instruction Register (NIR) Current Instruction Register (CIR) Look Up Table (LUT) | 4-2<br>4-2<br>4-3<br>4-4<br>4-8<br>4-10<br>4-10<br>4-11<br>4-11<br>4-11<br>4-12<br>4-12<br>4-13<br>4-14<br>4-14<br>4-14<br>4-14 |

| Multiplexers 1, 2, and 3 (MUX1, MUX2, MUX3) Incrementer (INC) Condition Branch Logic ROM                                                                                                                                                                                                                                                                                                                                                            | 4-15<br>4-15<br>4-16                                                                                                            |

| Microinstruction Register                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-16<br>4-16                                                                                                                    |

| SECTION V - CENTRAL PROCESSOR UNIT (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                         |

| A-File and B-File Register Store Logic                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-16<br>4-16<br>4-16<br>4-17<br>4-17                                         |

| SECTION V - CONTROL AND MAINTENANCE PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page                                                                         |

| INTRODUCTION  GENERAL  CMP HARDWARE FUNCTIONAL DESCRIPTION  RS-232 Interfaces  CPU Interface  IMB Interface  System Control Panel Interface  CMP LED Indicators  CMP Cabling  CMP Power Supply Requirements  CMP FIRMWARE FUNCTIONAL DESCRIPTION  Console Interface  Remote Console Interface  ADCC-System Interface  ADCC-System Interface  System Control Panel Functions  Overtemp Shutdown  Security Specifications  Installations and Configuration Specifications | 5-2<br>5-2<br>5-2<br>5-6<br>5-6<br>5-7<br>5-8<br>5-8<br>5-13<br>5-14<br>5-14 |

| SECTION VI - MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                   |

| INTRODUCTION  GENERAL  Memory Control and Logging Semiconductor Memory Arrays Data Word Address Word MEMORY OPERATIONS Read and Write Memory Status and Command Refresh ERROR DETECTION AND CORRECTION ERROR LOGGING CONFIGURATION GUIDE Switch Settings Test Lights MEMORY ERROR LOGGING FACILITY Memory Error Logging System Process (MEMLOGP) Memory Error Logging Internal Update Program (MEMTIMER) MEMORY ERROR LOG Analysis Program (MEMLOGAN)  SECTION VII - I/O SYSTEM | 6-2<br>6-3<br>6-4<br>6-6<br>6-6<br>6-7<br>6-10<br>6-14<br>6-15<br>6-19<br>6-21<br>6-22 |

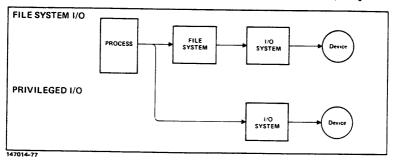

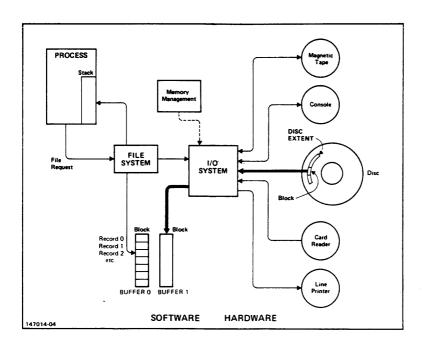

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                   |

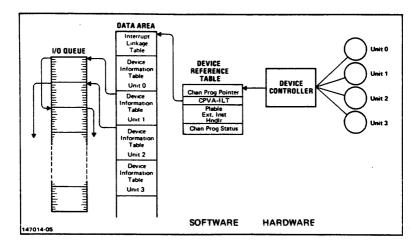

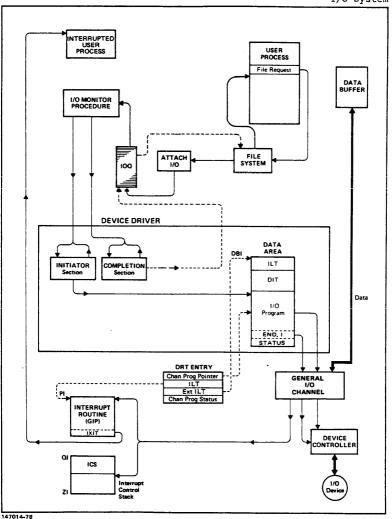

| I/O SYSTEM OVERVIEW  FILE SYSTEM OPERATION  FUNDAMENTAL ELEMENTS OF THE I/O SYSTEM  GENERAL I/O OPERATION  I/O RELATED MEMORY STRUCTURE  Word 0 of the DRT Entry  Word 1 of the DRT Entry  Word 2 of the DRT Entry  Word 3 of the DRT Entry  SOFTWARE I/O  I/O INSTRUCTION SET  ADDRESSED I/O INSTRUCTIONS  Initialize Channel (INIT)  Start I/O Program (SIOP)  Halt I/O Program (HIOP)                                                                                        | 7-3 7-4 7-7 7-16 7-16 7-16 7-16 7-16 7-16 7-16                                         |

7-13

#### SECTION VII - I/O SYSTEM (Continued)

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

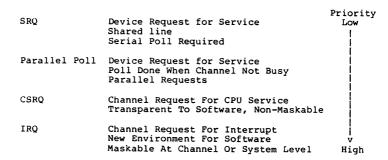

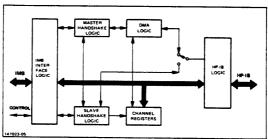

| Read I/O Channel (RIOC) Write I/O Channel (WIOC) CHANNEL PROGRAM CHARACTERISTICS CHANNEL PROGRAM INTERPRETATION CHANNEL PROGRAM MANAGEMENT CHANNEL INSTRUCTION SET I/O REQUESTS AND INTERRUPTS Request Facilities PRIORITY IMB Request Priority Channel Priority GENERAL I/O CHANNEL INTRODUCTION GIC BLOCK DIAGRAM OVERVIEW Command Decoding and Execution Logic (CDEL) Data-Not-Valid Logic (DNV) Master Handshake Slave Handshake Processor-to-HP-IB Interface Direct Memory Access (DMA) State Machine Left and Right Byte Out Registers (LBOR, RBOR) Left and Right Byte In Registers (LBIR, RBIR) CSRQ Logic Interrupt Request Logic Timeout Logic GIC Registers PHYSICAL CHARACTERISTICS | 7-13 7-14 7-14 7-14 7-15 7-17 7-18 7-21 7-21 7-21 7-23 7-23 7-24 7-25 7-27 7-28 7-28 7-29 7-35 |

| SECTION VIII - ASYNCHRONOUS DATA COMMUNICATION CHANNEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                           |

| INTRODUCTION BLOCK DIAGRAM OVERVIEW IMB Handshake Control IMB Register Decoding Device Address Latches Identify Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-2<br>8-2<br>8-2<br>8-3<br>8-3                                                                |

| SECTION VIII - ASYNCHRONOUS DATA COMMUNICATION CHANNEL                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                             |

| Channel Program Status Registers Channel Service Request Logic Device Specified Jump Logic Global Response Logic Interrupt Logic Universal Asynchronous Receiver/Transmitter Special Character Detection Modem Controls Modem Status Break Detection Logic PHYSICAL CHARACTERISTICS SYSTEM CONFIGURATION                                                                                                                                                                                       | 8-4<br>8-4<br>8-5<br>8-5<br>8-5<br>8-6<br>8-6<br>8-7<br>8-7                                      |

| SECTION IX - POWER DISTRIBUTION Paragraph                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                             |

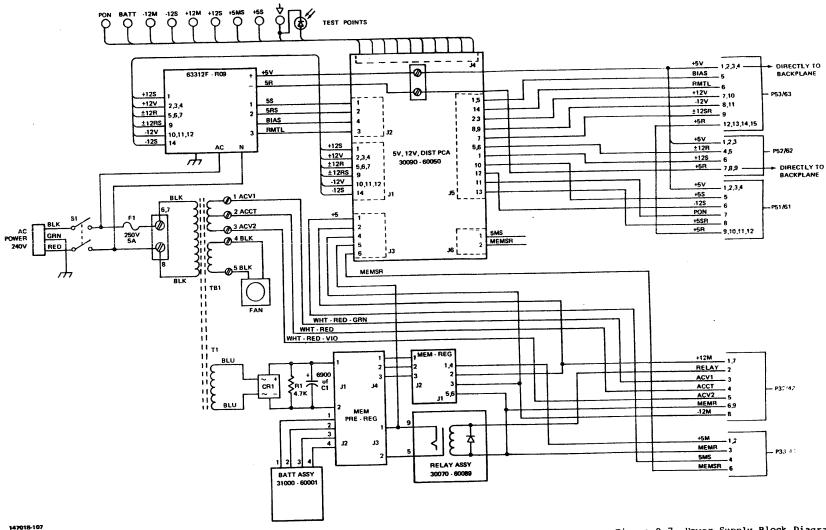

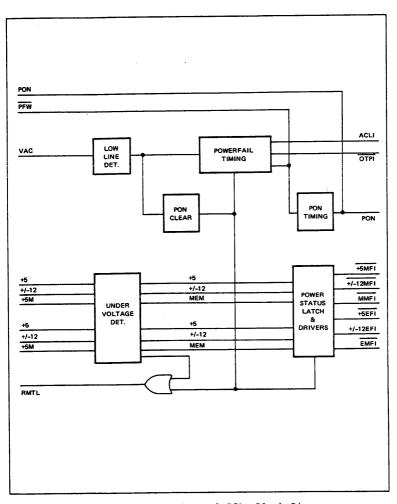

| INTRODUCTION AC POWER DISTRIBUTION Power Control Module AC Isolation Transformer DC POWER DISTRIBUTION DC Indicators and Test Points SYSTEM POWER SUPPLY UNIT Main Power Supply PCA Power Consumption Memory Power Supply POWER CONTROL General Description Operation Power Distribution PCA's POWER SUPPLY SERVICE INFORMATION Preventive Maintenance Voltage Checks Memory Power Supply Adjustments Main Power Supply Adjustments Main Power Supply Adjustments Battery Test Troubleshooting | 9-2<br>9-2<br>9-3<br>9-9<br>9-14<br>9-15<br>9-15<br>9-15<br>9-24<br>9-25<br>9-27<br>9-31<br>9-31 |

### PART 2

Section X - HP 3000 Series 40 Supplement

| Paragraph                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| INTRODUCTION GENERAL SPECIFICATIONS Processor Specifications Memory Specifications I/O SPECIFICATIONS I/O SPECIFICATIONS SYSTEM CONTROL PANEL Panel Controls Panel Indicators Security Switch SYSTEM OVERVIEW CENTRAL PROCESSOR UNIT CONTROL AND MAINTENANCE MEMORY SUBSYSTEM I/O SYSTEM ASYNCHRONOUS DATA COMMUNICATION CHANNEL CONFIGURATION INFORMATION | 10-1<br>10-1<br>10-2<br>10-2<br>10-3<br>10-3<br>10-4<br>10-5<br>10-6<br>10-6<br>10-6<br>10-7<br>10-7 |

| CONFIGURATION INFORMATION  Card Cage Configuration Rules  Sample Card-Cage Configuration  INPUT AC POWER  Line Current and Power  Turn-on Inrush Current                                                                                                                                                                                                   | 10-7<br>10-7<br>10-8<br>10-9<br>10-11/                                                               |

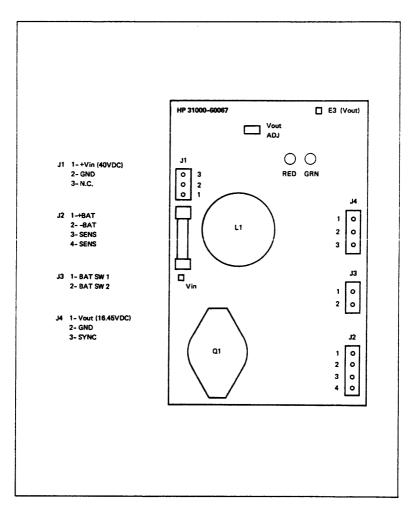

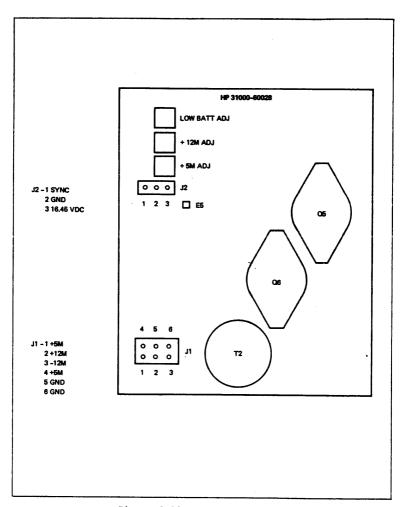

| POWER SUPPLY UNIT Main Power Supply Protection Features Voltage Adjustments MEMORY SUPPLY Memory Preregulator Battery Pack Memory Regulator Memory Power Supply Voltage Sequencing Memory Power Supply Switch POWER CONTROL                                                                                                                                | 10-12<br>10-15<br>10-15<br>10-15<br>10-16<br>10-16<br>10-16<br>10-17<br>10-17<br>10-18               |

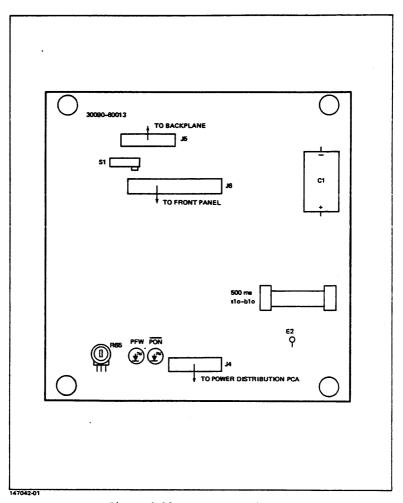

| General Description Operation PROTECTION CIRCUITRY AND SWITCH RESETS Replaceable Fuses Protection Circuitry SERVICE Test Lights Self-Test ADJUSTMENTS                                                                                                                                                                                                      | 10-26<br>10-26<br>10-27                                                                              |

xiii

## **ILLUSTRATIONS**

PART 1

| HP 3000 Series 44 Computer System                                                                                  |                          |

|--------------------------------------------------------------------------------------------------------------------|--------------------------|

| Title                                                                                                              |                          |

| System Control Panel                                                                                               | 2-3<br>3-3<br>4-5<br>4-6 |

| CTL PCAALU PCA                                                                                                     | 4-18<br>4-19             |

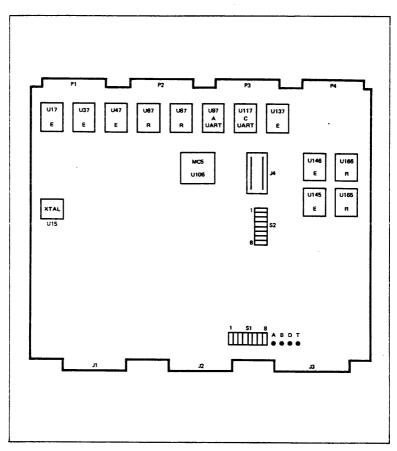

| PCS PCA CMP Interconnect Diagram CMP PCA                                                                           | 4-20<br>5-3<br>5-16      |

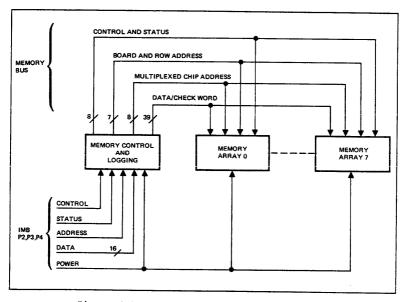

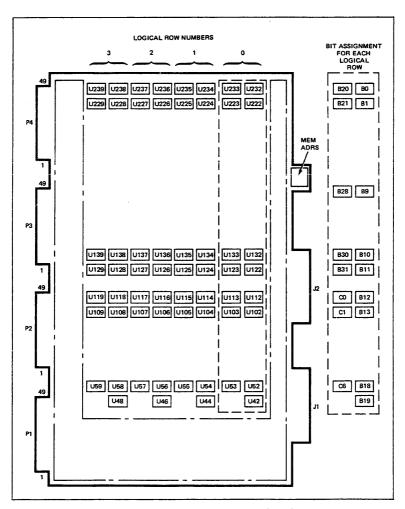

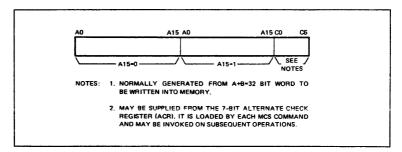

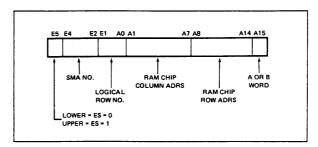

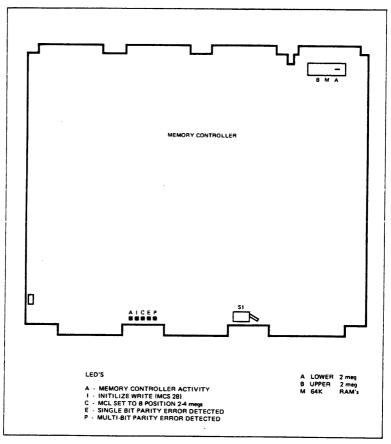

| Memory Subsystem Block Diagram                                                                                     | 6-3<br>6-5<br>6-6        |

| Address Word Format                                                                                                | 6-7<br>6-11<br>6-12      |

| Altered Status Command Bits                                                                                        | 6-13<br>6-16<br>6-20     |

| Error Printout Format                                                                                              | 6-26<br>7-3              |

| File System Basic Operation                                                                                        | 7-5<br>7-6<br>7-9        |

| General I/O Channel, Simplified Block Diagram                                                                      | 7-22<br>7-36<br>8-8      |

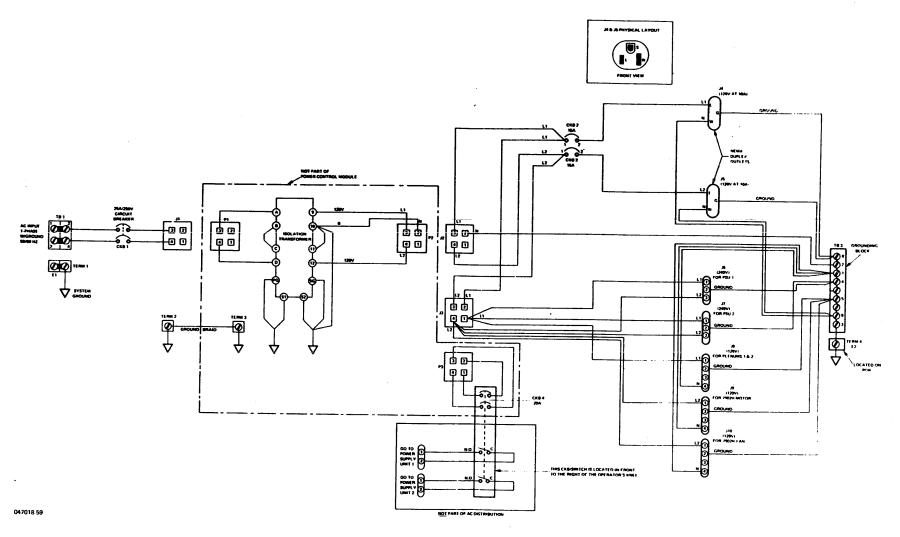

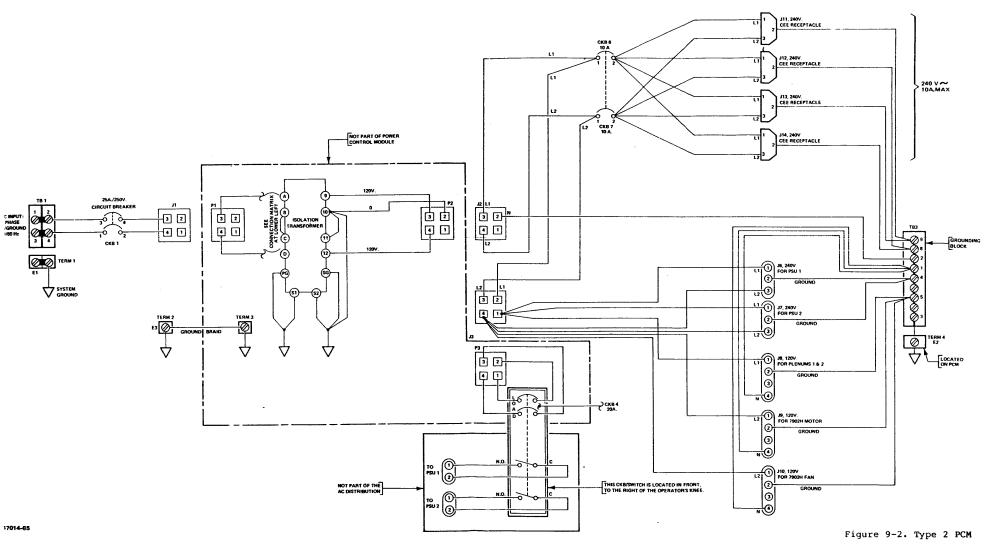

| ADCC Extender PCA Type 1 PCM Type 2 PCM                                                                            | 8-9<br>9-5<br>9-7        |

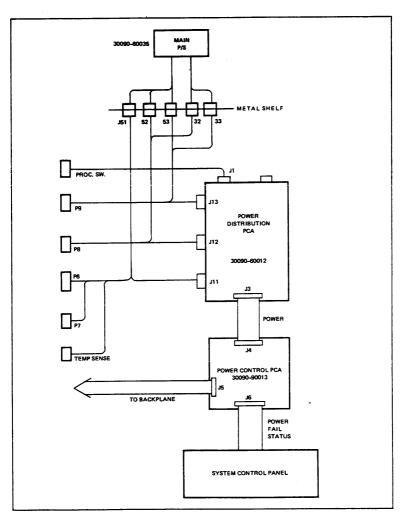

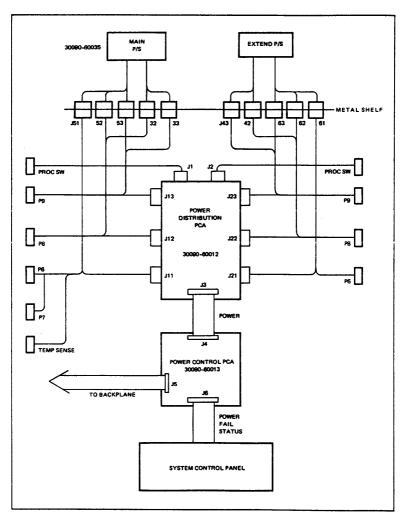

| DC Power Distribution (Single Power Supply)  DC Power Distribution (Dual Power Supplies)  Power Supply, Front View | 9-11<br>9-12<br>9-13     |

| Card Cage Backplane                                                                                                | 9-14<br>9-17             |

| Power Control Block Diagram                                                                                        | 9-21<br>9-23<br>9-28     |

| Memory Regulator PCAPower Control PCA                                                                              | 9-30<br>9-32             |

## ILLUSTRATIONS (continued)

| HP 3000 Series 40 Computer System               |                |

|-------------------------------------------------|----------------|

| Title                                           |                |

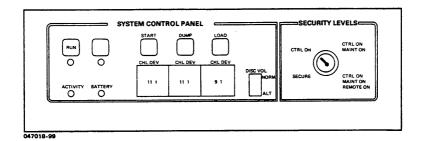

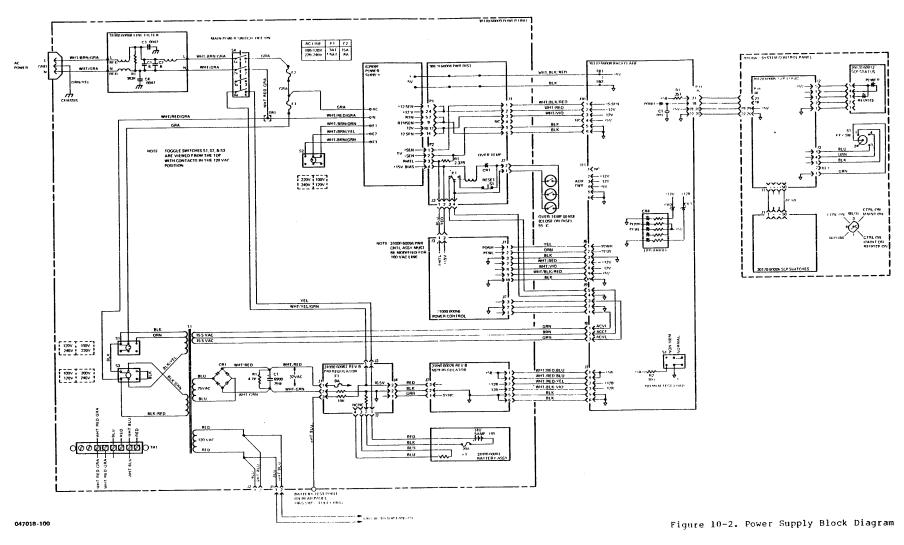

| System Control Panel Power Supply Block Diagram | 10-13          |

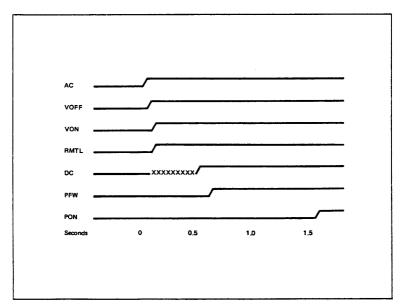

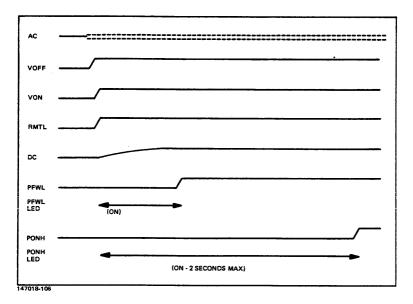

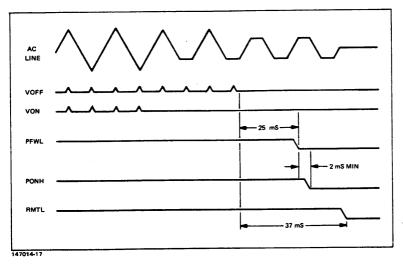

| Power and System Turn-on Sequence               | 10-19<br>10-21 |

PART 2

## **TABLES**

| Part 1                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| HP 3000 Series 44 Computer System                                                                                                                                                                                                                                                                                                               |                                                                                           |

| Title ·                                                                                                                                                                                                                                                                                                                                         |                                                                                           |

| Error Conditions and Actions Octal Syndrome Error Codes GIC Registers GIC Register Formats GIC Connector Pin Assignments Switch Functions Connectors P2 through P4 Pin Assignments Connector J1 Interconnect Wiring Connector J2 Pin Assignments AC Input Specifications Isolation Transformer Jumpers PCA Power Consumption DC Output Voltages | 6-9<br>6-17<br>7-29<br>7-30<br>7-37<br>8-10<br>8-12<br>8-14<br>9-2<br>9-9<br>9-15<br>9-27 |

| Part 2                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| HP 3000 Series 40 Computer System                                                                                                                                                                                                                                                                                                               |                                                                                           |

| Security Switch Functions                                                                                                                                                                                                                                                                                                                       | 10-6<br>10-23                                                                             |

|                                                                                                                                                                                                                                                                                                                                                 |                                                                                           |

## **GENERAL SPECIFICATIONS**

SECTION

SECTION I

HP 3000 SERIES 44

GENERAL SPECIFICATIONS

#### General Specifications

#### 1-1. PHYSICAL DIMENSIONS

| Height            | 28.5 in. (72.4 cm)    |

|-------------------|-----------------------|

| Depth             | 31.25 in. (79.4 cm)   |

| Width             | 72.25 in. (183.5 cm)) |

| Weight (uncrated) | 240 lbs (109 kg)      |

| Weight (shipping) | 310 lbs (141 kg)g)    |

#### 1-2. POWER REQUIREMENTS

Voltages 200 to 240 VAC in

10 volt steps (+4%, -10%)

Frequency 60 and 50 Hz (+/- 0.5 Hz)

Current (at full load)

8.3A at 208 VAC for 60 Hz, 8.1A at 220 VAC for 50 Hz Single Card Cage:

Dual Card Cage: 13.1A at 208 VAC for 60 Hz 12.4A at 220 VAC for 50 Hz

Power (at full load)

Single Card Cage: 1280 watts at 60 Hz, 1400 watts

at 50 Hz

Dual Card Cage: 2160 watts at 60 Hz, 2220 watts

at 50 Hz

Circuit Breaker Rating 24A

Power Connection Power cord supplied with 60 Hz

models. No power cord supplied

with 50 Hz models.

#### General Specifications

#### 1-3. ENVIRONMENTAL

Temperature

Operating

System (recommended): 68 to 78 deg F

(20 to 25.5 deg C) (maximum, 48 hrs): 86 deg F (30 deg C) (minimum, 48 hrs): 55 deg F (15 deg C)

Non-operating (maximum): 167 deg F (75 deg C)

(minimum): -40 deg F (-40 deg C)

Rate of Change 10 deg F/hr

(4.5 deg C/hr)

Relative Humidity

Recommended operating: 40 to 60 percent

(no condensation)

Non-operating 5 to 80 percent

Altitude

Operating Sea level to 4600m (15,000 ft)

Non-operating Sea level to 15,300m

(50,000 ft)

#### 1-4. PROCESSOR

| Word Length                 | 16 bits                    |

|-----------------------------|----------------------------|

| Number of instructions      | 195                        |

| Minor clock cycle time      | 26.3 ns                    |

| Microinstruction Cycle Time | 105 ns (four minor clocks) |

| Physical Address Space      | 18 Mbytes                  |

| Maximum Code Segment Size   | 16 Kwords                  |

| Maximum Data Segment Size   | 32 Kwords                  |

| Maximum Number of User      |                            |

| Code Segments               | 63                         |

| Maximum Number of User      |                            |

| Data Segments               | 256                        |

| Decimal Precision           | 28 digits                  |

| Major Clock Cycle Time      | 100 ns                     |

| Minor Clock Cycle Time      | 25 ns                      |

| Real-Time Clock Resolution  | l ms                       |

Note: The microinstructions require four major clock cycles, however, each microinstruction overlaps so that a new one starts every major clock cycle.

#### General Specifications

#### 1-5. MEMORY

Semiconducor memory with single-bit error correction and double-bit error detection.

| ta o | -4 | Length |

|------|----|--------|

| wo   | ra | Length |

Error Detection Error Correction Memory Module Size

Maximum Memory Size per card cage Per System Maximum Modules per Controller Read Access Time Battery Backup Time 39 bits (32 + 7 for error correction/detection)

2 bits per 32-bit word

1 bit per 32-bit word

256 kbyte (using 16k RAMS)

1 Mbyte (using 64k RAMS)

2 Mbyte (using 16K RAMS) 8 Mbyte (using 64k RAMS) 8

300 ns (worst case ADO to DDN)

15 minutes

#### 1-6. INPUT/OUTPUT STRUCTURE

Common asynchronous bus structure with individual data channels.

| Maximum Number of Data Channels Channel Types:                                               | 15                                                                                 |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| General I/O Channel (for HP-IB compatible devices)                                           | 5 per system, maximum                                                              |

| Maximum number of devices<br>Maximum transfer rate<br>Maximum total cable length             | 8 per channel<br>980 kbytes/s<br>13m (50 ft)                                       |

| Asynchronous Data Communication<br>Channel (for asynchronous<br>RS-232-C compatible devices) | 16 maximum                                                                         |

| Maximum number of ports per system                                                           | 60                                                                                 |

| Number of ports per channel                                                                  | 8 (4 on Main and 4 on Extender)                                                    |

| Data rates                                                                                   | 50, 75, 110, 134.5,<br>150, 200, 300, 600,<br>1200, 1800, 2400,<br>4800, 9600 Baud |

| Maximum data cable length                                                                    | 30.5m (100 ft)                                                                     |

## SYSTEM CONTROL PANEL/CONSOLE

SECTION

## SECTION II SYSTEM CONTROL PANEL AND SYSTEM CONSOLE FUNCTIONAL DESCRIPTION

#### Control Panel/Console

#### 2-1. INTRODUCTION

This section describes the system control panel and the system console keys that relate to the control panel functions.

#### 2-2. SYSTEM CONTROL PANEL

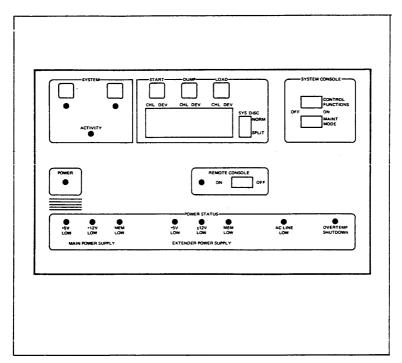

The system control panel (figure 2-1) is a module that contains the necessary circuits on two PCAs to perform the control and monitoring functions of the HP 3000/44 Computer System. The module is located behind the front door, which is normally locked. A beveled slot in the front door exposes two indicators, the POWER indicator and the REMOTE CONSOLE indicator.

The system control panel contains hardware-related and software-related controls. Also, indicators monitor the status of the system and power supplies. The two hardware-related controls are RUN and HALT. While the system is running, the CPU will respond only to the HALT control. The software-related controls are START (warmstart), DUMP (memory dump), and LOAD (cold-load). Up to eight channels and eight devices on each channel can be addressed for a cold-load, warmstart, or memory dump. The channel and device addresses are set by the thumbwheel switches located directly under the START, DUMP, and LOAD switches. The addresses are gated out when the respective momentary switch is pressed.

The system control panel includes four other switches. These switches are used to configure the system disc, enable or disable maintenance mode on the system console, enable or disable the remote console capability, and enable or disable the system console functions that duplicate the control functions on the system control panel.

Figure 2-1. System Control Panel

#### 2-3. Switch Functions

#### HALT Switch

This is a momentary switch that causes the CPU to halt if it is in the run state. There is no response if the CPU is halted.

#### Control Panel/Console

#### RUN Switch

This is a momentary switch that causes the CPU to go from the halt state to the rin state. There is no response if the CPU is in the run state.

#### LOAD, START, and DUMP Switches

Each function has one momentary switch and two associated thumbwheel switches. The thumbwheel switches select the channel and device addresses, and the momentary switch gates the selected address out on the channel and device lines to the CPU. Each channel switch wheel is marked 4 through 11. The corresponding BCD outputs sent to the CPU will be 0 through 7. The CPU adds 4 to the channel number so that the result will be the same as the switch marking. This numbering scheme is used so that channels 0 through 3 can be reserved for terminal use. The device number switches are marked 0 through 7 and the corresponding BCD outputs are also 0 through 7.

#### SYS DISC Switch

This is a two-position switch that configures either a fixed disc or removable discs as the warmstart devices of the system disc. For example, with the switch set to NORMAL the warmstart microcode will address head zero of the system disc drive. When the switch is set to SPLIT, the microcode addresses head two of the system disc drive.

#### CONTROL FUNCTIONS Switch

This is a two-position switch that, when set to ON, enables the console functions. These functions include the system control panel functions, such as START, DUMP, LOAD, RUN, and HALT. When set to OFF, the console functions are disabled.

#### MAINT MODE Switch

The output of this switch is sent to the Control and Maintenance Processor to enable the system console maintenance mode.

#### REMOTE CONSOLE Switch

This switch enables the remote console capability.

#### 2-4. Indicator Lights

Three SYSTEM indicators display system status. The RUN indicator is a yellow LED that is lit when the CPU is operating. The ACTIV-ITY indicator is also a yellow LED that provides a visual indication of IMB activity. The HALT indicator is a red LED that lights when the CPU is in the halt state.

The POWER and REMOTE CONSOLE indicators are visible through the front panel door window when lit. The POWER indicator is a yellow LED and represents DC power integrity. The REMOTE CONSOLE indicator is a red LED that is lit when the remote console facility is enabled.

Two warning indicators are included on the front panel. The AC LOW indicator is a red LED that lights when the system switches to battery backup power. The OVERTEMP indicator lights red when the temperature exceeds the threshold (135 degrees F/57.3 degrees C) of any temperature transducer in either card cage. The LED is reset by momentarily turning off then on the AC circuit breaker.

Two groups of power supply LEDs provide status of the power supplies for the main card cage and the extender card cage. The LEDs are off during normal operation. If a failure occurs in a particular power supply, the corresponding LED lights.

#### 2-5. SYSTEM CONSOLE

The system console may be any of the 264X or 262X terminals, or an HP hard copy terminal such as the HP 2635 printing terminal. The system console appears to the operating system as a standard system console and displays normal MPE console information. The console can also be used as a session device. In addition, system status is displayed, and the console keys can be used for duplicating certain control panel functions.

The console control functions that include the system control panel functions are implemented by entering CNTL B, waiting for a prompt "->", then entering the command. The commands are entered fully spelled out. When the system is halted, the prompt is automatically displayed.

Console operator commands, session modes, and system manager operations are the same as that for all previous HP 3000 computer system operations.

#### Control Panel/Console

#### 2-6. Console Control Functions

The console control functions are listed as follows:

- HELP This command prints a list of control and maintenance processor (CMP) commands.

- HALT This causes the CPU run/hat flip-flop to be set to HALT. This function duplicates the halt function on the system control panel.

- RUN This causes the CPU run/halt flip-flop to be set to RUN. This function duplicates the the run function on the system control panel.

- DUMP This initiates the dump command, loading the softdump facility from the device specified by the thumbwheel switch. When the command is entered and the system is in the run mode, the following message will be displayed:

#### "IS IT OK TO ABORT THE OPERATING SYSTEM?"

The user must respond "YES" to perform the dump. This command duplicates the same command on the system control panel.

• LOAD This causes the cold load function to be performed from the channel and device thumbwheel switches. When this command is entered and the system is in the run mode, the following message will be displayed:

#### "IS IT OK TO ABORT THE OPERATING SYSTEM?"

The user must enter "YES" to perform the load. This command duplicates the same command on the system control panel.

#### START

This causes the warmstart function to be performed from the device specified by the thumbwheel switches. When this command is entered and the system is in the run mode, the following message will be displayed:

"IS IT OK TO ABORT THE OPERATING SYSTEM?"

The user must enter "YES" to perform the warmstart. This command duplicates the same command on the system control panel.

#### SELFTEST

This command initiates the system selftest function. When this command is entered and the system is in the run mode, the following message will be displayed:

"IS IT OK TO ABORT THE OPERATING SYSTEM?"

The user must enter "YES" to perform the system selftest.

LOG

This command displays a log of actions performed or detected by the CMP. These events are:

Display On

Dump

Halt

Halt Command

Iomap

Load

Power On

Power Fail/Reset

Run

Selftest OK Selftest Failed Shuttest

Shuttest Failed

Start

DISPLAY command entered DUMP command entered CPU went to halt The HALT command was used IOMAP command entered LOAD command entered Power-on reset to CMP

when battery power was lost A power fail occurred or the PON signal went low without loss of memory backup power

CPU wne to run

System selftest passed System selftest failed Power shutown test

performed

Power shuttdown test failed START command entered

#### Control Panel/Console

These events are listed with the elapsed time (excluding power off duration) since the event occurred. The last 63 events are displayed. An example is:

|      | Eve | ent Log |                   |

|------|-----|---------|-------------------|

| Days | Hrs | Min     | Since Event       |

| 2    | 23  | 05      | Power On          |

|      | 3   | 20      | Overtemp Shutdown |

|      |     | 20      | Power Fail/Reset  |

|      | 2   | 25      | Halt              |

|      |     | 20      | Start Failed      |

|      |     | 05      | Halt              |

|      | 2   | 03      | Load Failed       |

|      | 1   | 51      | Halt              |

|      | 1   | 50      | Cold Load         |

|      | 1   | 50      | Selftest Failed   |

|      |     | 03      | Cold Load         |

|      |     | 02      | Load              |

- DISPLAY This command causes the maintenance display to appear on the screen.

- SPEED This command allows the user to change the baud rates when MPE is not running. The receive and transmit are specified in the command as follows:

#### SPEED <RATE>, <RATE>

- SPEED This command is identical to the SPEED command but allows the CMP and MPE to be set to the same speed simultaneously. This command is used when MPE is running.

- SHUTTEST This command test the power fail and overtemp shutdown circuitry on the CMP and power supply. When the command is entered, the message "Cycle Power to Restart System" is displayed. This shuts down all power except memory power. To bring the system up after this test cycle the main power breaker on system. If the test fails, the message "Test Failed" will appear on the screen.

- DCTEST This commands performs testing of the RS232 signals on the CMP. A special test adapter must be installed between J3 on the CMP and the standard CMP cable. The CMP cannot be in the remote mode while performing this test.

#### Control Panel/Console

IOMAP This command printsd the current system configuration. The memory size, control panel switches, and all channels and devices in the system are identified.

Invalid command names will cause the message "INVALID COMMAND, USE HELP FOR INFO" to be displayed.

## SYSTEM OVERVIEW

SECTION

SECTION III

HP 3000 SERIES 44

SYSTEM OVERVIEW

System Overview

#### 3-1. INTRODUCTION

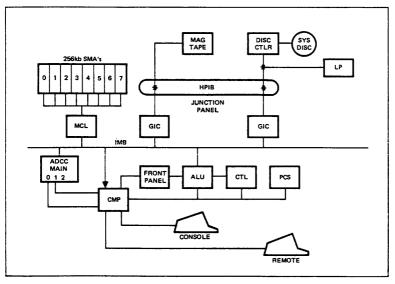

This section describes the HP 3000 Series 44 Computer System (figure 3-1). An overall system hardware description is provided with a description of the bus system and the I/O elements included. Bus control and command structure are also described.

The HP 3000/44 is designed around independent elements that are organized together through a communication network. The elements of the system consist of a central processor, memory arrays with a memory controller, I/O channels, and a bus system that enables communications between the elements. Also, the system includes a system console, system control panel, and a control and maintenance facility. Peripheral elements attach to the system through the I/O channels.

#### 3-2. BUS SYSTEM

The elements that make up the bus system include the intermodule bus (IMB), the Hewlett-Packard Interface Bus (HP-IB), and the RS-232-C Data Communication Line.

#### 3-3. Intermodule Bus

3-4. Bus Control. Communication between the CPU, Memory and I/O modules is carried over the IMB. Because the CPU generates greater than 90 percent of the Bus activity, it is given continuous access to the bus and relinquishes control to the I/O channels only on request.

The IMB has separate address and data paths each with handshake controls that operate in a master/slave mode to transfer data between modules. The CPU talks to memory and to the I/O system and always functions as a master. The GIC channels function as masters to memory but become slaves when talking with the CPU. To access memory, the I/O channels must request the bus through a priority structure. Any channel request will cause the CPU to reliquish control of the IMB so that the request can be serviced.

3-4. Bus Control. The bus control signals control access to the IMB and include the bus handshake signals. The lines that control bus access are BRQ (bus request), BACK (bus acknowledge), PRO (priority out), PRI (priority in), and PRCY (priority carry), the latter three of which are the priority tree signals for bus access. The handshake signals are discussed in later sections.

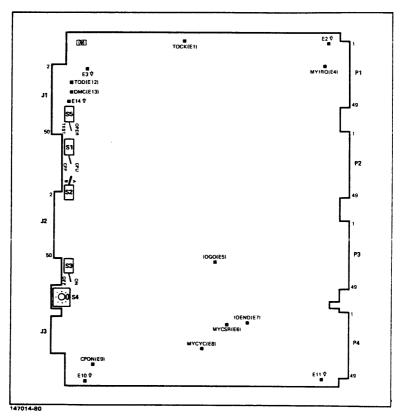

Figure 3-1. HP 3000 Series 44 Simplified Block Diagram

# System Overview

BRQ (Bus Request) Low True Open Collector

This is an OR-tieable line asserted by any channel to request access to the bus from the CPU. A true PRI input priority and BRQ high are required to assert a bus request.

BACK (Bus Acknowledge)

This is a unidirectional line that is driven by the CPU to acknowledge release of the bus to the channel asserting BRQ. The CPU releases BACK at the termination of the BRQ signal. Simultaneous bus requests are resolved by delaying the response to BRQ to allow for propogation through the priority chain for disabling the lower priority module.

PRI (Priority In) High True

The PRI's are input signals to the I/O channel and the AND of all ten must be true to be given access to the bus for memory service. On the channel card each PRI is pulled high to +5 volts through a 10K pull up resister. A tree structure is built into the backplane to establish priority as a function of physical location on the bus.

PRO (Priority Out) High True

This a normally true output signal from a module indicating lack of interest in the bus. This signal becomes one of the ten input PRI's to lower priority modules. By pulling PRO low, a channel requesting the bus can prevent access to the bus by lower priority channels.

PRCY (Priority Carry) High True

This is an output signal representing the AND of PRO of that module and the ten input PRI'S to the module. This signal is used on the backplane to restart the priority tree when the input PRI number reaches ten.

3-5. IMB I/O Commands. Interpretation of a channel instruction generally results in several transactions with a channel. It is necessary to specify IMB I/O commands in order to communicate the desired action to the channel. When the IMB operation is related to I/O (rather than memory), the sixteen low order IMB address lines assume a fixed format which is interpreted by the channel. (Refer to tables 3-1 and 3-2.)

The Addressing Mode indicates whether the command is addressed to a single channel or whether it is global and affects all channels. If bit 0 is a one the command is global. Commands that share code values are discerned by the three Bus Operation Code lines of the IMB, which specifies whether the operation is an I/O Read or an I/O Write.

The bus operation code lines are multiple source three-bit bus that carries the operation to be executed by the slave. The operations and their opcodes are as follows:

| Operation                  | Opcode |  |  |

|----------------------------|--------|--|--|

|                            |        |  |  |

| Memory read word           | 000    |  |  |

| Memory read/write 1's      | 001    |  |  |

| Memory write word          | 010    |  |  |

| Memory control/read status | 101    |  |  |

| I/O read                   | 100    |  |  |

| I/O write                  | 110    |  |  |

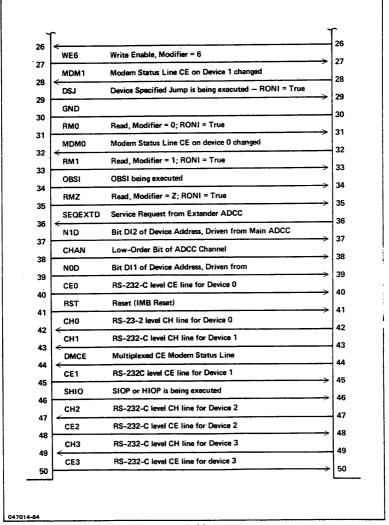

Table 3-1. IMB I/O Commands

| IMB Command           | Mnemonic | IMB Operation | Opcode |

|-----------------------|----------|---------------|--------|

| Read Data             | RIOC     | read          | 0000   |

| Obtain Interrupt Info | OBII     | read          | 0010   |

| Obtain Service Info   | OBSI     | read          | 0100   |

| Service Poll 1        | SPOLL1   | read          | 1100   |

| Write Data            | WIOC     | write         | . 0000 |

| Initialize Channel    | INIT     | write         | 0010   |

| Start I/O Program     | SIOP     | write         | 0100   |

| Halt I/O Program      | HIOP     | write         | 0110   |

| I/O Clear             | IOCL     | write         | 1010   |

# System Overview

Table 3-2. IMB Command Code Format

| )               | 3 , | 4               | 7 8 | 9              | 12 | 13 | 14 | 15 |

|-----------------|-----|-----------------|-----|----------------|----|----|----|----|

| Command<br>Code |     | Register<br>No. | x   | Channel<br>No. |    | x  | х  | ,  |

Read Data (RIOC) and Write Data (WIOC)

The RIOC and WIOC commands are associated with several machine instructions as well as assorted tasks such as serial polling of devices on the GIC. These commands transport the information on the the IMB data lines from or to a particular channel. The commands are also used to select the source or destination (Register Number) of the data at the channel controller.

# Interrupt Poll and Obtain Interrupt Information (OBII)

Interrupt Poll and OBII commands are issued by the CPU interrupt processing microcode to determine the number of the device whose interrupt request will be serviced. Interrupt Poll is issued in response to the IMB IRQ line being asserted. This IMB global command causes each channel to assert a logical 1 on its assigned IMB data line if it is asserting IRQ, and to assert logical 0 on that line otherwise. The interrupt processing microcode determines the highest priority requesting channel, then issues OBII to the channel. The channel returns the number of the highest priority device which had an interrupt pending and its channel number. The returned word will be used to vector through the DRT entry for the device to the device software driver.

# Initialize Channel

Initialize Channel causes a particular channel's hardware to be reset to a known state. I/O Clear causes a similar resetting action to all channels simultaneously. The specific actions which results from these commands are dependent upon the channel hardware.

# Start I/O Program (SIOP) and Halt I/O Program (HIOP)

The SIOP and HIOP commands I/O Program provide the link between software control of channel programs and the execution of those programs. When software causes a change in the running status of a device channel program, the channel will request service by asserting CSRQ. The CPU microcode will subsequently perform the

tasks required to inititate or terminate execution of the channel program.

During a SIOP or a HIOP, the IMB data lines contain the status change information which enables the channel to request service because of a change in running status. However, certain instances occur during the execution of channel programs which require the interpreting microcode to change the running status of a program without also causing a channel service request. If the proper bit is set, the Status Change condition is cleared and no service request results from the SIOP or HIOP command.

- 3-7. IMB Access. Bus access is achieved on a priority basis. There are three priority structures: slot, channel, and device. Each I/O PCA that can access the IMB must request bus access either using the slot or channel priority. Devices are serviced in the order of device priority. The CPU has the lowest priority, and is responsible for controlling IMB access. Different I/O PCA's may request control of the IMB for different reasons and one may retain control by continuing to request after having been granted access.

- 3-8. Slot Priority. Slot priority is used only for the General I/O Channels (GIC) during DMA transfer. The highest priority in this structure is assigned to the GIC that is physically closest to the CPU.

- 3-9. Channel Priority. Any combination of channels may be asserting IRQ, or CSRQ at one time. When the channels are polled, the lowest channel number has the highest request priority on each request line.

- 3-10. Device Priority. Within the highest priority requesting channel device priorities are:

- IRQ: If several device interrupt bits are set the lowest numbered device will be serviced first.

- CSRQ-parallel poll: If CSRQ is due to an affirmative poll response or a change in channel program status, then the device on the highest DIO line (lowest device number) has the highest priority.

- CSRQ-serial poll: If a serial poll must be conducted to determine which device is serviced, then the device priority is determined by the poll table. The first device polled has highest priority, and polling stops at the first device requiring channel program service.

# System Overview

# 3-11. HP4B

The HP-IB is the standard interface bus between a GIC and devices on a channel. The bus consists of eight data lines and eight control lines. One end connects to the side or rear junction panels and the other end employs multiple connectors to attach to devices.

- 3-12. Commands. The HP-IB protocol specifies the command structure which can be used for device control. Before a device can accept data over the HP-IB, it must receive an Address-To-Listen command containing its device number. Likewise, data cannot be acquired from a device that has not received an Address-ToTalk command. The HP-IB channel instructions invoke these commands for all write and read operations, with the device number derived from the polling sequence. Enabling a device to talk or listen is generally insufficient. A listener must be told whether the forthcoming information is data or control; a talker must be told to output either data or status information. While several methods of sending this modifying information are available, the channel instructions utilize the HP-IB message, My Secondary Address. The secondary address is sent to the device in a command cycle immediately following the primary message My-Talk-Address or My-Listen-Address. The data is then transmitted and is inter-preted as either data or control information. The final action resulting from HP-IB channel instructions is the unaddressing of the device, so the HP-IB is left in a well defined state.

- 3-13. Device Service Requests. The Parallel Poll function allows up to eight devices to assert separate lines on the HP-IB for service request. In this case, the bus controller (GIC) periodically puts the HP-IB into a parallel poll mode, and each device then uses one of the eight data lines to indicate its need for service. Since one device is assigned to each line, the controller can immediately determine which devices are requesting service.

- 3-14. Additional Talker Function. The HP 3000/44 utilizes devices that can identify themselves so that the system drivers may be configured without user inputs. However, if the user has attached a device which cannot identify itself it would return random data when addressed in the normal manner. To resolve this problem, the identification process will assume that the devices recognize another talker address (31) in addition to the one normally used for data transfers.

3-15. HP-IB Protocol. An attachment which obeys the HP-IB protocol is called an HP-IB device and has the following properties:

- a. It recognizes the Identify directive through implementation of an extra extended talker (TE) function.

- b. It accepts command information through MY-Secondary-Address messages.

- c. It utilizes a parallel poll line uniquely determined by the device address on the HP-IB; asserts a low voltage on this line to request service; and is the sole user of this line Since there are eight data lines HP-IB device addresses are numbered from 0 through 7.

# 3-16. RS-232-C Data Communication Line

This bus specifies 25 dedicated lines as the standard interface in data communication. Pin assignments are set aside for ground, data, control, and timing circuits. Transmission over this bus is bit-serial and is reserved for terminal operation.

# 3-17. PROCESSOR ELEMENTS

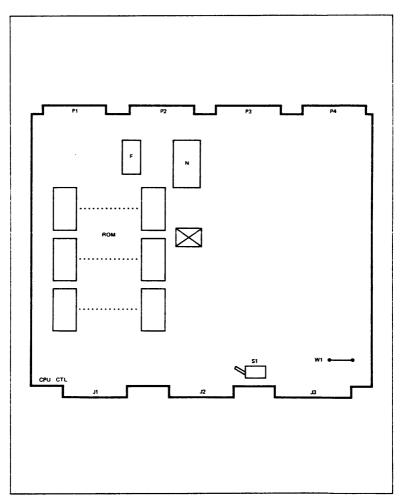

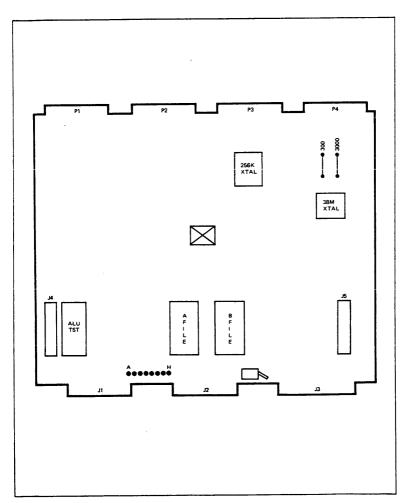

The processor elements determine the basic characteristics of the computer system hardware and consist of the ALU, CTL, and PCS PCA's. The CPU interfaces with other elements in the system through the IMB.

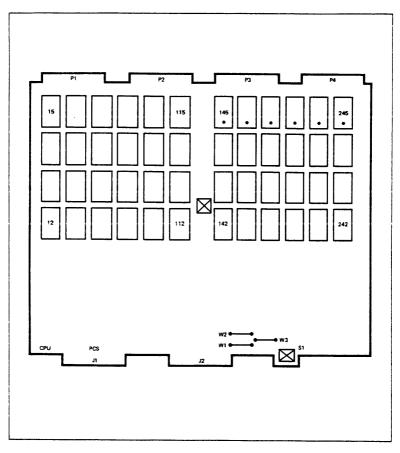

The ALU contains the arithmetic logic unit, data registers, IMB interface, clock circuitry, and shift logic. The CTL PCA contains four kilowords of microcode instruction decoding circuitry and program control entry. The PCS PCA provides ROM storage for the main microcode, decimal, 64-bit floating point, and COBOL. The three PCA's operate together to translate received instruction words into microprogram starting addresses, decode microprograms into fixed control signal sequences, and execute various arithmetic functions. The processor is microprogrammable and has a 64-bit wide control store, a 16-bit wide arithmetic path, and a 16-bit wide memory address path (7 bits are used for check bits).

# 3-18, I/O ELEMENTS

The I/O elements for the HP 3000/44 consist of two channels, the General I/O Channel (GIC) and the Asynchronous Data Communication Channel (ADCC). The GIC is the hardware I/O channel which provides the electrical interface between the computer system via the IMB and peripheral devices connected to the HP-IB. The ADCC provides a bit-serial data interface between the computer system

# System Overview

and peripheral devices. The two channels operate in a similar manner, however, the GIC has a DMA facility to permit high-speed transfer of large blocks of data and the ADCC can transfer data only one character at a time.

# 3-19. General I/O Channel

The GIC is a controller of the HP-IB and translates I/O commands from the CPU into the proper HP-IB protocol. Nearly all transactions with I/O devices are accomplished without software interrupts, since I/O is achieved with channel programs. Software is responsible for setting up a channel program, but the execution of this program is performed by the CPU channel microcode. The CPU channel microcode is devoted to I/O tasks and implements the necessary algorithms for decoding the channel instructions and effecting the required I/O operations. Once the channel program is running, device control and data flow are normally carried to completion with no software intervention and without altering the system environment. If special situations arise, software may alter the program or even halt execution.

Several devices may simultaneously need service, and the CPU must decide which one will receive attention. First, all channels are polled, and the highest priority GIC with a device request pending is chosen. The CPU then obtains from that channel the number of the highest priority device needing service. Once the device number is determined, execution of the channel program will begin. The CPU fetches each channel instruction and breaks them down into several IMB commands addressed to the proper GIC. The GIC interprets these commands and directs them onto the HP-IB device.

The GIC contains DMA (Direct Memory Access) hardware which allows large records of data to be transfered at the maximum speed of the HP-IB. The channel microcode enables the device and then initializes the DMA hardware on the GIC. On a read operation the DMA hardware will read the bytes, pack them into words and place them directly into memory, all without assistance from the CPU. The CPU is free to service other devices while DMA is in progress.

# 3-20. Asynchronous Data Communication Channel

The Asynchronous Data Communication Channel (ADCC) is the second channel type used in the system. This channel performs essentially the same functions as the GIC but not in the same manner. Data is transfered from memory to an ADCC device (terminal) in parallel form, then converted to a serial bit stream for trans-

mission over the RS-233-C lines. Information being read from a device is in serial form and is converted to eight-bit bytes for transfer to memory.

Two ADCC boards may be used, the Main ADCC and the Extender ADCC. Each board contains four ports for connection to devices through RS-232C data communication lines. The Main ADCC is used when four or less devices are connected to a channel. The Extender ADCC extends the device capability of channel to eight. All circuitry except data handling circuits are on the Main ADCC. For this reason, the Extender ADCC connects to the Main ADCC to control signal information.

When more than eight devices are to be attached to ADCC channels, additional Main ADCC's are required, since each ADCC can accommodate only one Extender.

Unlike the GIC, the ADCC does not have a DMA facility and therefore cannot be a master of the IMB or memory. As a result, the ADCC is always a slave and must be directly controlled by the CPU through the use of channel programs. Circuitry on the ADCC decodes address information relating to channel and devices and select the correct device for operation.

The ports on the ADCC (Main and Extender) may be either hardwired to devices or to modems. Currently, the only modems to be considered are the Bell Models 103 and 202.

# 3-21. MAIN MEMORY ELEMENTS

The memory is a high speed, high density memory system that is compatible with IMB protocol. Memory arrays are 256 kbyte or one Mbyte, using 16k or 64k RAM's, respectively. The maximum memory configuration is 4 Mbytes. The minimum memory configuration consists of one MCL and one SMA. One MCL controls up to eight controls up to eight SMA's; however, the system can operate with two MCL's. This means that each MCL will then provide for two Mbytes of memory using 16k RAM's.

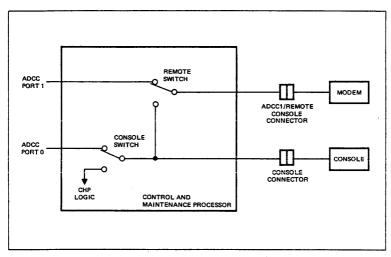

# 3-22. MAINTENANCE/CONTROL ELEMENTS

The control and maintenance processor (CMP) is a single PCA that provides control functions to perform warmstarts, cold loads, and memory dumps and aids in system maintenance by including a system selftest and a maintenance display. These functions allow the system to have a consistent and friendly user interface. When the operating system or the CPU fails, the user can use commands from the system console to bring the system up if a software error occurred, or to help diagnose hardware problems. The CMP also has a HELP feature to assist untrained operators in bringing the

# System Overview

system up. In addition, the CMP provides the capability for remote maintenance which allows diagnosis of software and hardware problems from a remote location.

### 3-23. System Console

The system console is a terminal that is the main interface between the operator and the system. The console displays normal MPE console information and can also be used as a session device. In addition, it is the front panel for the system and contains controls for operation. Various types of diagnostics can be initiated from the system console. The system console can be any of the 264%, 262% or printing terminals.

# 3-24. System Control Panel

The system front panel allows the system operator to perform the control and monitoring functions of the system. Control functions on the system front panel enable direct access to major functions through the use of the system console, activate the maintenance mode, enable hardware-related functions such as RUN and HALT, and software-related functions such as warm start, memory dump, and cold load. Also, since the system console utilizes the same control functions for hardware, the system front panel can be used as a backup panel if the console is down.

# 3-25. PERIPHERAL ELEMENTS

The peripheral elements used with the HP 3000/44 are connected primarily to GIC's while the ADCC is reserved solely for terminals. Peripherals attached to GICs through the HP-IB include disc drives, line printers and magnetic tape drives. The GIC's are used for all peripherals, except terminals. For a listing of the supported peripherals used in the HP 3000/44, refer to the current Price/Configuration Guide.

# **CENTRAL PROCESSOR UNIT**

SECTION

SECTION IV

CENTRAL PROCESSOR UNIT

### 4-1. INTRODUCTION

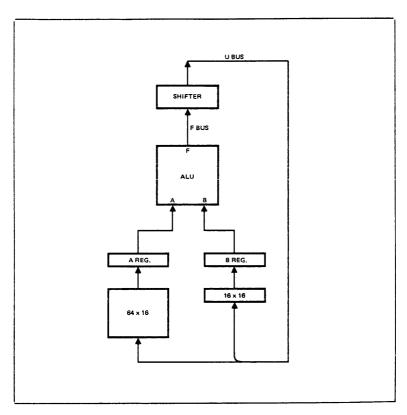

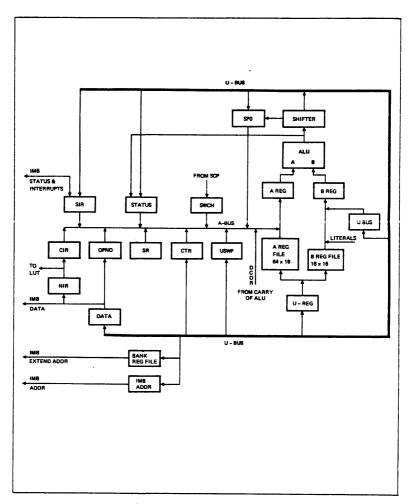

This section describes the Central Processor Unit (CPU), which includes a functional description, system component description (registers, etc.), and the CPU implementation of hardware. (See the HP 3000 Series 44 Block Diagram, part no. 30090-90003, for for component and functional references.)

The Series 44 CPU is a microprogrammed pipeline processor that executes the current 3000 instruction set through the use of microinstructions. The processor consists of three PCA's, the CTL, ALU, and the PCS. The CTL PCA contains 4 kilowords of microcode, instruction decoding circuitry and program control entry. The CTL provides control for the ALU, sequences the Control Store Address Register (CSAR), and controls test functions. The microcode consists of the channel program processor (CPP) code and selftest.

The ALU contains the Arithmetic Logic Unit, data registers, IMB interface, clock circuitry, and shift logic. The PCS provides an additional 8k X 48 bits of ROM storage. The microcode in the ROM storage consists of the main microcode, decimal, 64-bit floating point, and COBOL.

The processor is a fully synchronous machine, operating with a major clock cycle of 105 nanoseconds.

## 4-2. FUNCTIONAL DESCRIPTION

# 4-3. Instruction Execution

The processor indirectly executes instructions. Each macroinstruction causes a microprogram, which resides in ROM on the CTL and PCS PCA's, to be executed. The 16-bit macroinstructions are obtained from memory over the IMB and loaded into the Next Instruction Register (NIR). When the CPU completes current microprograms and is ready to execute the next instruction, the instruction is loaded from the NIR into the Current Instruction Register (CIR) and the Look-Up Table (LUT), which maps the instruction into a microprogram starting address to implement that instruction.

Once the starting address is dertermined, the control store presents a 48-bit microinstruction which is latched in the Microinstruction Register (MIR). This is where the various instruction fetch and execute fields are inputted and decoded. This decoded information is then passed to the ALU PCA which properly fetches registers and then executes the given function.

After executing the function, the results are stored into registers specified by the CTL PCA. The CTL circuitry then executes the next microinstruction or performs the necessary microprogram jumps, which store the address in either the Subroutine Return Register (SRR) or Slow Jump Register (SJR). When the microprogram is finished, the last microinstruction will have the NEXT instruction in the Special field. This informs the CTL PCA that it is ready to load the next macroinstruction from the NIR into the CIR and repeat the process.