## HP 3000 Series II/III Computer System

## **System Reference Manual**

## HP 3000 Series II/III Computer Systems

# System Reference Manual

5303 STEVENS CREEK BLVD., SANTA CLARA, CALIFORNIA 95050

Part No. 30000-90020 Printed in U.S.A. 7/78

#### **NOTICE**

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

### LIST OF EFFECTIVE PAGES

The List of Effective Pages gives the date of the current edition and of any pages changed in updates to that edition. Within the manual, any page changed since the last edition is indicated by printing the date the changes were made on the bottom of the page. Changes are marked with a vertical bar in the margin. If an update is incorporated when an edition is reprinted, these bars are removed but the dates remain. No information is incorporated into a reprinting unless it appears as a prior update.

| Page        | Date |

|-------------|------|

| i to ii     | 7/78 |

| iii to iv   | 1/79 |

| v to ix     | 7/78 |

| 1-1         | 7/78 |

| 1-2 to 1-3  | 1/79 |

| 2-1 to 2-10 | 7/78 |

| 3-1 to 3-66 | 7/78 |

| 4-1 to 4-32 |      |

| 5-1 to 5-20 | 7/78 |

| 6-1 to 6-24 | 7/78 |

| 7-1 to 7-40 | 7/78 |

| I-1 to I-8  |      |

#### **PRINTING HISTORY**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The date on the title page and back cover of the manual changes only when a new edition is published. When an edition is reprinted, all the prior updates to the edition are incorporated. No information is incorporated into a reprinting unless it appears as a prior update. The edition does not change.

The software product part number printed alongside the date indicates the version and update level of the software product at the time the manual edition or update was issued. Many product updates and fixes do not require manual changes, and conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one to one correspondence between product updates and manual updates.

## CONTENTS

| Section I Page                            | P RegisterPL Register        | 3-15<br>3-15 |

|-------------------------------------------|------------------------------|--------------|

| INTRODUCTION D. G.M. and 1-1              | Data Segment Registers       | 3-15         |

| Purpose of Manual                         | DL Register                  | 3-15         |

| System Descriptions1-1                    | DB Register                  | 3-15         |

| Section II Page                           | DB-Bank Register             | 3-15         |

| Section II Page SYSTEM FEATURES           | Q Register                   | 3-15         |

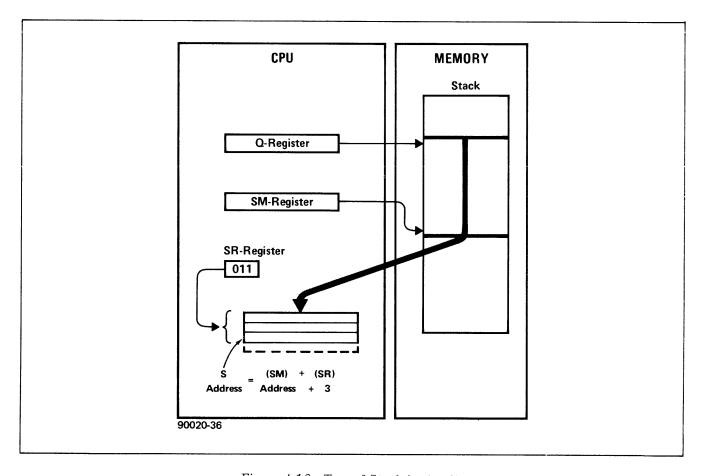

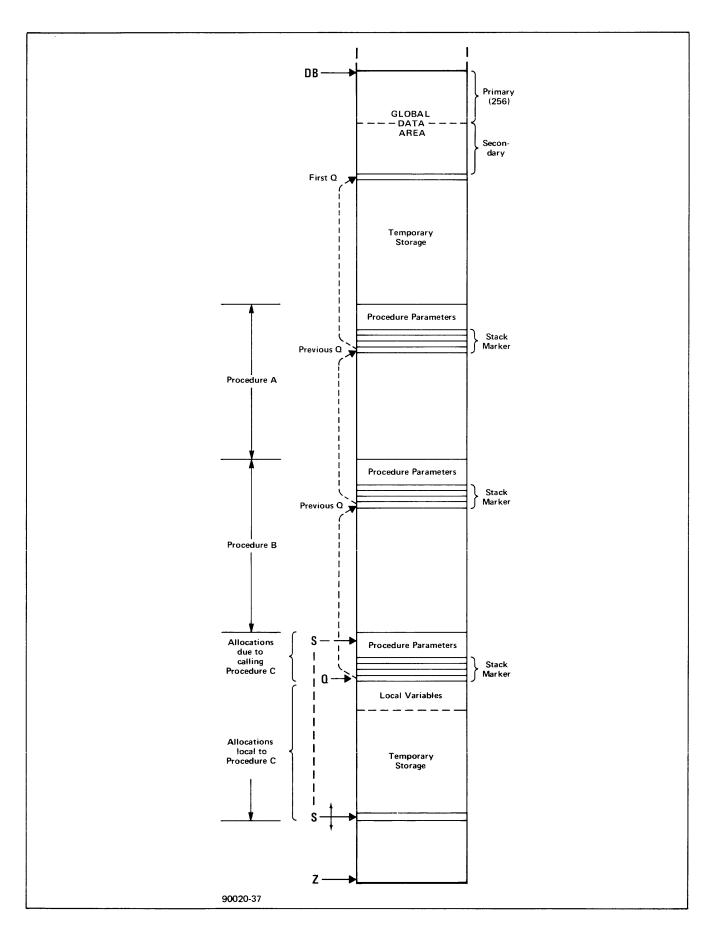

| Central Processing Unit (CPU)2-2          | SM Register                  | 3-17         |

| Separate Code and Data                    | SR Register                  | 3-17         |

| Data Stacks                               | S Pointer                    | 3-17         |

| Variable-Length Segmentation              | Z Register                   | 3-17         |

| Registers2-5                              | Stack Bank Register          | 3-17         |

| Instructions                              | Other CPU Registers          | 3-17         |

| Microcode                                 | Index Register               | 3-17         |

| Main Memory                               | Status Register              | 3-17         |

| Input/Output2-7                           | Privileged Mode              | 3-18         |

| Direct I/O (DIO)                          | Addressing Conventions       | 3-18         |

| Programmed I/O (SIO)                      | Memory Addressing            | 3-18         |

| Multiplexer Channel2-8                    | Indirect Addressing          | 3-20         |

| Selector Channel2-8                       | Code Indirect                | 3-20         |

| Device Reference Table (DRT) 2-8          | Data Indirect                | 3-21         |

| Data Service and Interrupt Priorities 2-8 | Indexing                     | 3-21         |

| Interrupt System                          | Code Indexing                | 3-21         |

| Peripherals                               | Data Indexing                | 3-21         |

| 1 et ipitet als                           | Byte Addressing              | 3-24         |

| Section III Page                          | Direct                       | 3-25         |

| THEORY OF OPERATION                       | Direct, Indexed              | 3-25         |

| Introduction                              | Indirect                     | 3-25         |

| System-Level Description                  | Indirect, Indexed            | 3-25         |

| CPU General Information                   | Double-Word Indexing         | 3-25         |

| Pipeline                                  | Bounds Checking              | 3-25         |

| Data Formats                              | Program Transfer             | 3-25         |

| Byte Format                               | Program References           | 3-26         |

| Logical Format                            | Data References              | 3-26         |

| Single-Word, Fixed-Point Format           | Stack Overflow               | 3-26         |

| Doùble-Word, Fixed-Point Format           | Stack Underflow              | 3-26         |

| Floating-Point Format                     | Access to DB- Area           | .3-28        |

| Long Floating-Point Format                | Word Addressing              | 3-28         |

| Instruction Formats                       | Byte Addressing              | 3-28         |

| General Format3-9                         | Block-Level Description      | 3-29         |

| Stack Op                                  | Bus System                   | 3-29         |

| Shift                                     | Central Data Bus             | 3-31         |

| Branch                                    | IOP Bus                      | 3-31         |

| Bit Test                                  | Selector Channel Bus         |              |

| Move                                      | Multiplexer Channel Bus      | 3-31         |

| Special                                   | Power Bus                    | . 3-3]       |

| Immediate                                 | Overview                     | . 3-3]       |

| Field                                     | Unconditional Jump           | . 3-32       |

| Register Control 3-11                     | Conditional Jump             | . 3-32       |

| Program Control                           | Central Processor Unit       |              |

| I/O and Interrupt                         | Next Instruction Register    | 3-33         |

| Loop Control3-11                          | Current Instruction Register | . 3-33       |

| Memory Address3-11                        | CMUX and CMUX Control        | . 3-3        |

| Status Word Format3-12                    | Mapper and Mapper Control    | . კ-კ        |

| CPU Registers                             | Look Up Table ROM            | . კ-კ        |

| Code Segment Registers                    | V-Bus MUX and V-Bus Control  |              |

| PB Register                               | ROM Address Register         |              |

| PR-Bank Register                          | Save Register                | . ა-ა        |

## **CONTENTS** (continued)

| Read-Only Memory3-35          | Basic Table Structures           | 4-7  |

|-------------------------------|----------------------------------|------|

| ROM Output Registers3-35      | Code Segment Table and Extension |      |

| Microcode Jumps3-35           | Data Segment Table               |      |

| S-Bus Field Decoder 3-36      | Code Segment Linkage             |      |

| Store Field Decoder           | Stack Operation                  |      |

| Function Field Decoder 3-36   | Examples of Stack Usage          |      |

| Skip Field Decoder3-36        | Basic Arithmetic                 |      |

| Shift Field Decoder           | Procedure Calls                  |      |

| Special Field Decoder         | Recursion                        |      |

| MCU Option Field Decoder      | Main Program Call                |      |

| R-Bus Field Decoder           | Test for Zero                    |      |

| Processor Registers           | First Recursive Call             |      |

| Renamer 3-61                  | Successive Recursions            |      |

| Top-of-Stack Registers 3-62   | First Exit                       |      |

| Index Register 3-62           | First Recursive Exit             |      |

| Stack Limit Register          | Successive Exits                 |      |

|                               | Successive Exits                 | 4-02 |

| Program Limit Register        | Section V                        | Domo |

| Scratch Pad 0 Register        | Section V                        | Page |

| Scratch Pad 1 Register        | INPUT/OUTPUT SYSTEM              | F 1  |

| Stack Register                | Introduction                     |      |

| Program Base Register         | File System Operation            |      |

| Data Limit Register           | Definition of Terms              |      |

| Stack Memory Register 3-63    | I/O Instructions                 |      |

| Data Base Register            | General I/O Operation            |      |

| Q Register                    | Direct I/O Operation             |      |

| Scratch Pad 2 Register        | Direct Read                      |      |

| Scratch Pad 3 Register        | Direct Write                     |      |

| Process Clock Register        | Blocked/Unblocked I/O            |      |

| Program Counter Register 3-63 | Blocked I/O                      |      |

| Operand Register              | Unblocked I/O                    |      |

| Status Register               | Hardware I/O System              |      |

| Counter Register              | Hardware Elements                |      |

| Overflow                      | I/O Processor                    | 5-14 |

| Carry 3-65                    | Multiplexer Channel              |      |

| Condition Code Logic          | Selector Channel                 |      |

| Pre-Adder                     | Device Controller                | 5-16 |

| R-Bus Register                | Peripheral Device                | 5-16 |

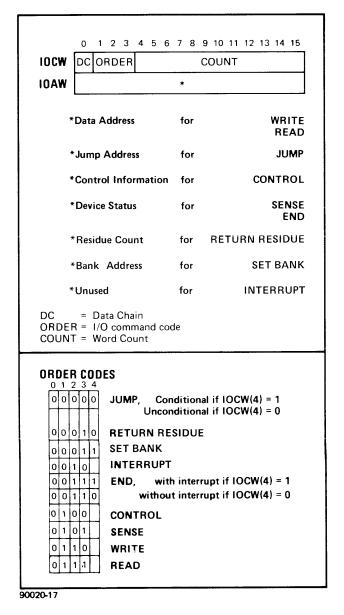

| S-Bus Register 3-65           | I/O Programming                  | 5-16 |

| Arithmetic Logic Unit3-65     | I/O Program Word                 | 5-16 |

| Shifter                       | Typical I/O Program Operation    | 5-18 |

| Decimal Corrector 3-65        |                                  |      |

| ACOR 3-66                     | Section VI                       | Page |

| DCOR 3-66                     | INTERRUPT SYSTEM                 |      |

| CPX1 Register 3-66            | Interrupt System Overview        | 6-1  |

| CPX2 Register                 | Interrupt Control Stack (ICS)    |      |

| <b>U</b>                      | Interrupt Types                  |      |

|                               | External Interrupts              |      |

| Section IV Page               | ICS Internal Interrupts          |      |

| MEMORY SEGMENTATION           | Non-ICS Internal Interrupts      |      |

| Introduction                  | External Interrupt Processing    |      |

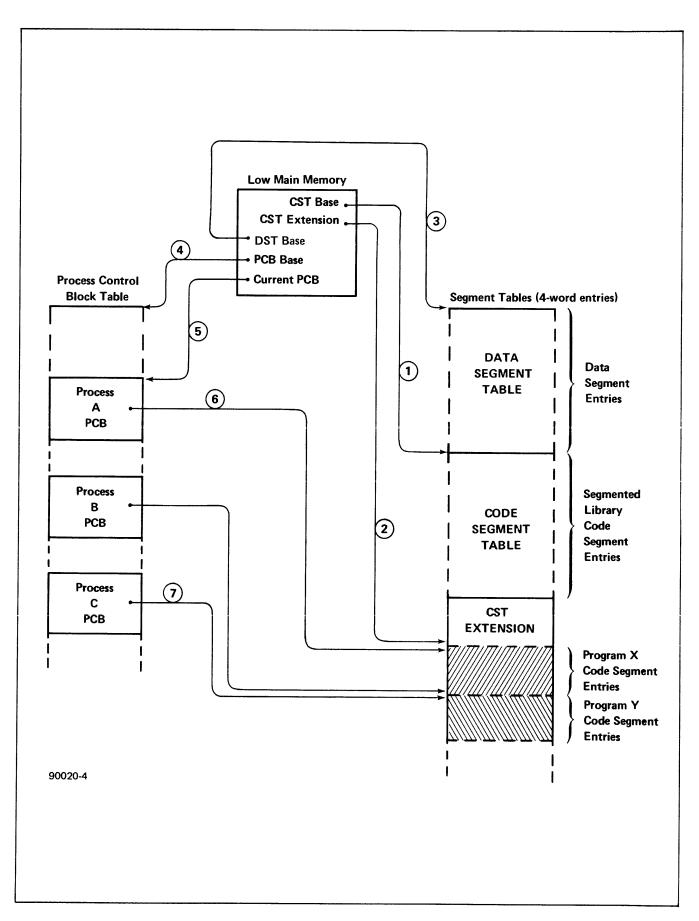

| Virtual Memory4-1             | Interrupt Program Pointer        |      |

| Processes                     | Sequence of Operations           |      |

| Procedures 4-3                | Internal Interrupt Processing    |      |

| System Library4-3             | General Descriptions             |      |

| Memory Management4-3          | Bounds Violation                 |      |

| Code Segmentation 4-3         | Illegal Memory Address           |      |

|                               | Non-Responding Module            |      |

| Data Segmentation             | Mon-responding Module            | 0-13 |

| Main Memory Organization 4-6  |                                  |      |

## **CONTENTS** (continued)

| System Parity Error 6-13                       | Store an Operand              | . 7-7  |

|------------------------------------------------|-------------------------------|--------|

| Address Parity Error 6-13                      | CPU Address Transmit          | . 7-7  |

| Data Parity Error 6-13                         | Memory Receive                | . 7-7  |

| Module Interrupt 6-14                          | CPU Data Transmit             | . 7-7  |

| Power Fail                                     | Memory Receive                | . 7-8  |

| Unimplemented Instruction 6-14                 | Command a Module              | . 7-8  |

| STT Violation                                  | I/O System                    | . 7-9  |

| CST Violation 6-14                             | I/O Priorities                |        |

| DST Violation 6-14                             | I/O Data Routes               |        |

| Stack Underflow 6-14                           | Multiplexer Channel Device    | 7-10   |

| Privileged Mode Violation 6-14                 | Selector Channel Device       |        |

| Stack Overflow                                 | Transfer Modes                |        |

| Integer Overflow 6-14                          | Multiplexer Channel           | 7-11   |

| Floating-Point Overflow 6-15                   | Selector Channel              | 7-11   |

| Floating-Point Underflow 6-15                  | I/O Processor                 |        |

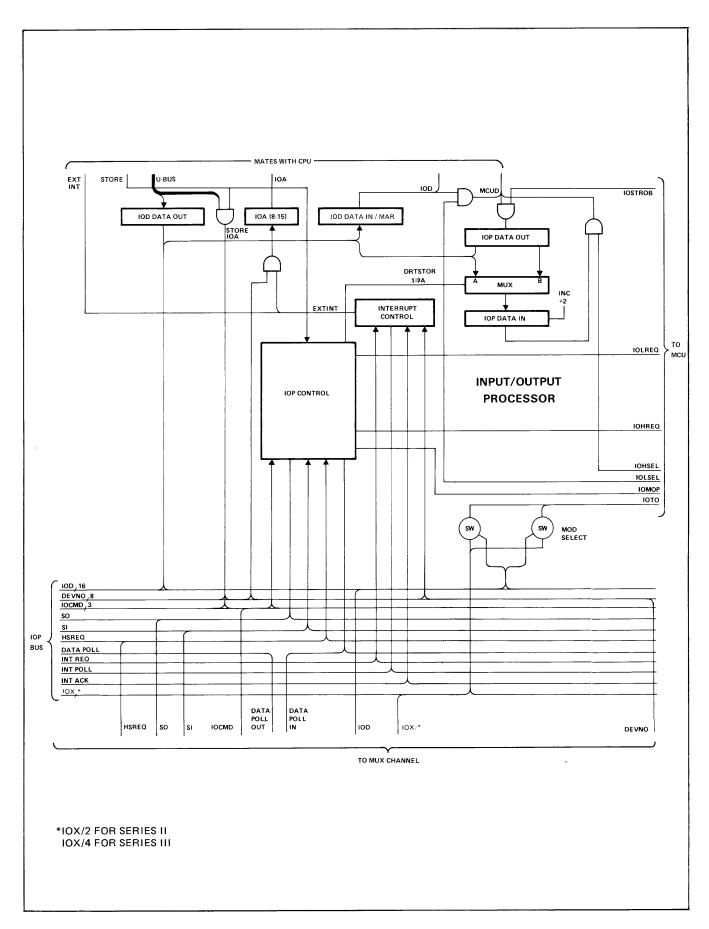

| Integer Divide by Zero 6-15                    | IOP Logic                     | 7-12   |

| Floating-Point Divide by Zero 6-15             | I/O Command                   | 7-12   |

| Extended Precision Floating-Point              | IOP Control                   | 7-12   |

| Overflow                                       | Interrupt Control             |        |

| Extended Precision Floating-Point              | INT DEVNO                     | 7-12   |

| Underflow                                      | Data Output Registers         |        |

| Extended Precision Floating-Point              | Data Input Registers          | 7-13   |

| Divide by Zero                                 | IOP Module Control Unit       | 7-13   |

| Decimal Overflow                               | Initialize                    | 7-13   |

| Invalid ASCII Digit                            | DRT Fetch                     |        |

| Invalid Decimal Digit                          | I/O Program Word Transfers    |        |

| Invalid Word Count                             | IOCW Fetch                    | 7-15   |

| Result Word Count Overflow                     | IOAW Fetch                    | 7-16   |

| Decimal Divide by Zero                         | IOAW Store                    |        |

| Absent Code Segment                            | Next Operation                | 7-17   |

| Trace                                          | Data Transfers                | 7-17   |

| STT Entry Uncallable                           | Address Transfer              | 7-17   |

| Absent Data Segment                            | Output Transfer               |        |

| Power On                                       | Input Transfer                | 7-18   |

| Cold Load 6-16                                 | End of Transfer by Word Count | 7-18   |

| Sequence for ICS Type Internal Interrupts 6-17 | End of Transfer by Device     | 7-18   |

| Sequence for Non-ICS Type Interrupts 6-19      | Interrupts                    | 7-18   |

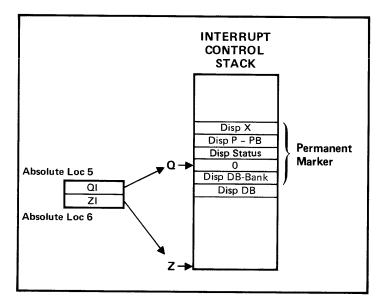

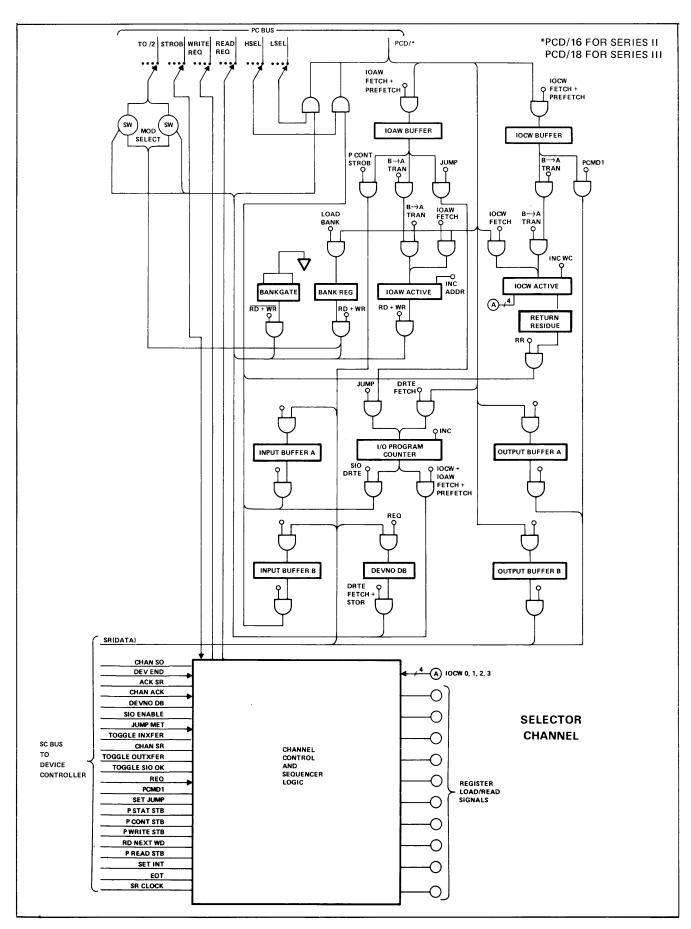

| Interrupt Handler                              | Selector Channel              | 7-19   |

| DISP Instruction                               | Port Controller               | 7-19   |

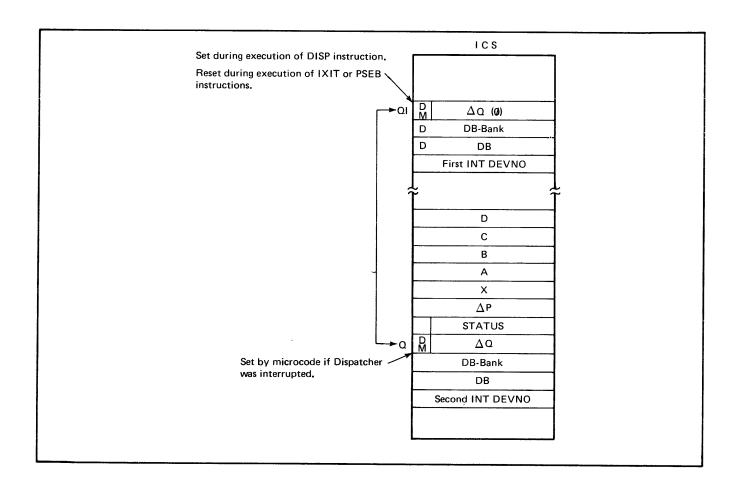

| Pseudo Enabling/Disabling the Dispatcher 6-23  | Initiator Sequence            |        |

| IXIT Instruction                               | Fetch Sequence                | 7-21   |

|                                                | Execute Sequences             | 7-22   |

| Section VII Page                               | Sense                         | 7-22   |

| FUNCTIONAL OPERATION                           | Interrupt                     | 7-22   |

| Introduction                                   | Jump                          | 7-22   |

| Central Processor Unit                         | Control                       | . 7-23 |

| Module Control Unit                            | Set Bank                      | 7-23   |

| Central Data Bus Transmissions                 | Read                          | 7-23   |

| Fetch Next Instruction                         | Return Residue                | . 7-24 |

| CPU Address Transmit                           | Write                         |        |

| Memory Receive and Transmit                    | End                           | . 7-25 |

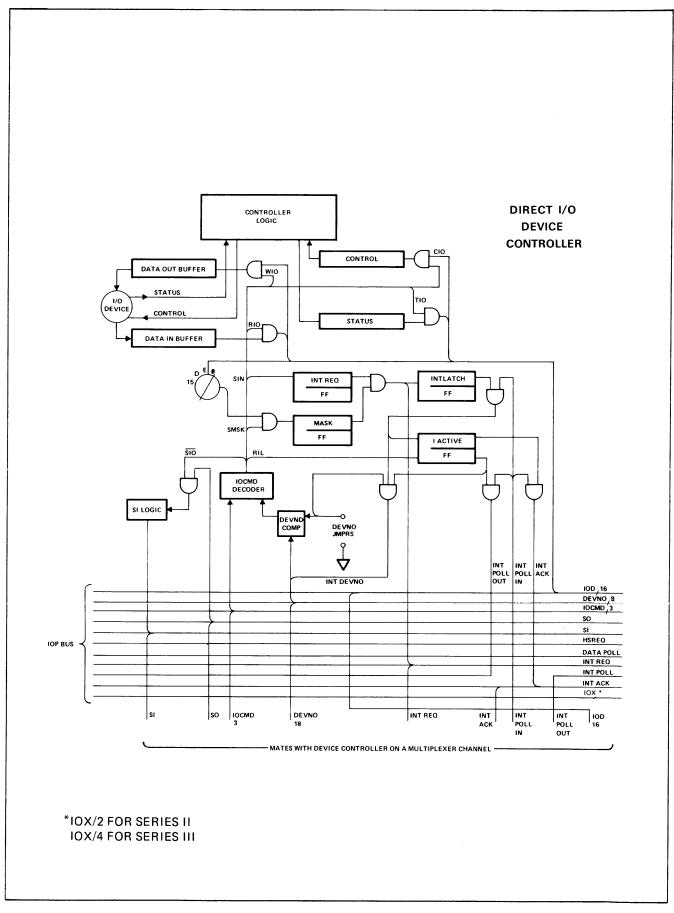

| CPU Receive                                    | Direct I/O Operation          |        |

| Fetch an Operand                               | TIO                           | . 7-25 |

| CPU Address Transmit                           | RIO                           | . 7-26 |

| Memory Receive and Transmit7-7                 | CIO                           | . 7-26 |

| CPII Receive                                   | WIO                           | . 7-26 |

## **ILLUSTRATIONS**

| Title Page                                            | Title Page                                      |

|-------------------------------------------------------|-------------------------------------------------|

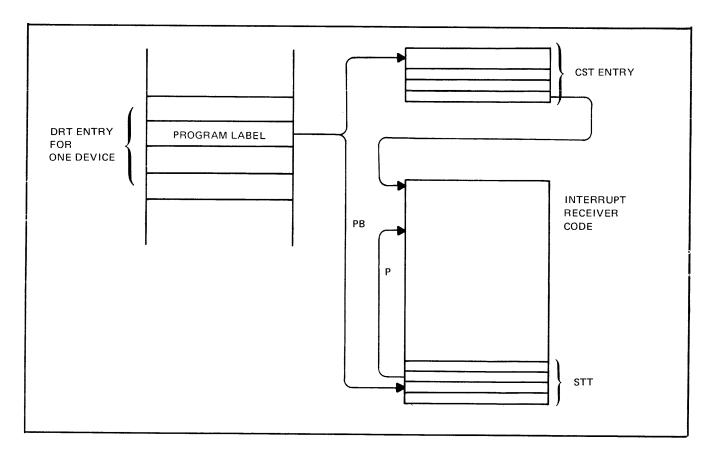

| 2-Bay Computer System                                 | Device Reference Table                          |

| 3-Bay Computer System                                 | I/O System Overview                             |

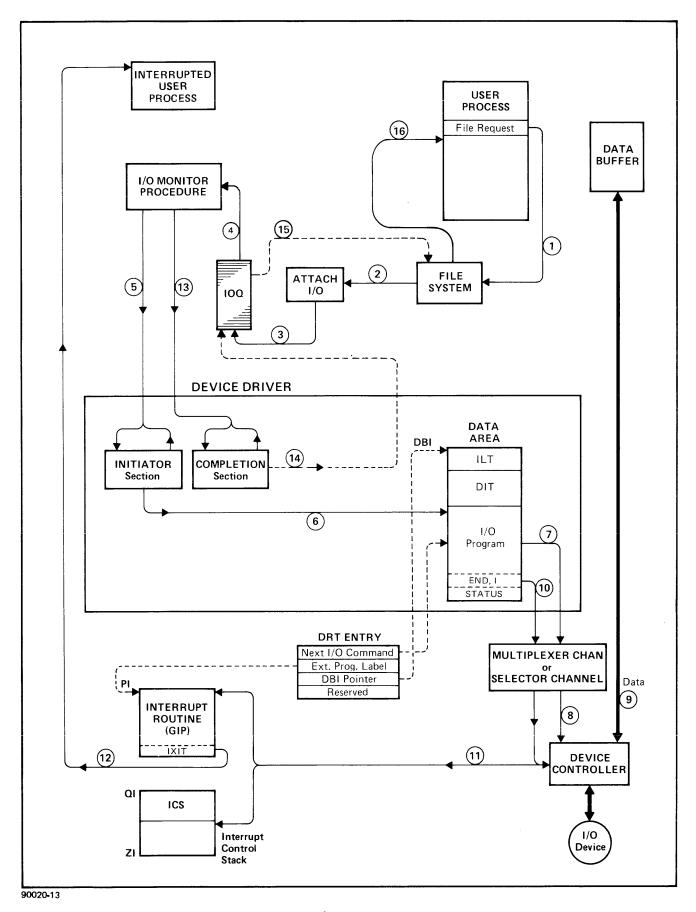

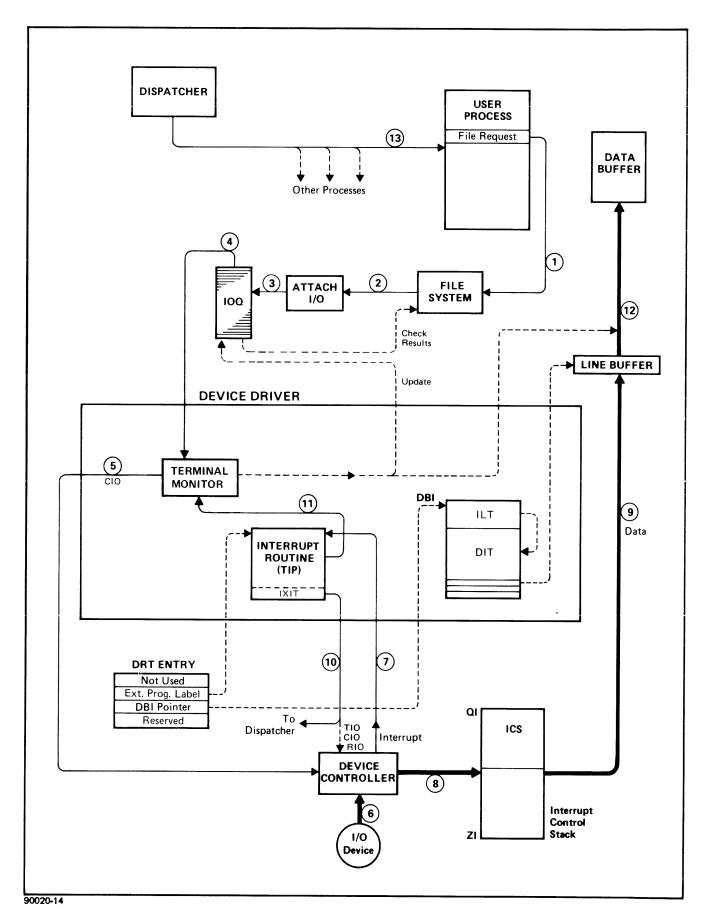

| Series III (23435A) 1- and 2-Bay Computer Systems 1-3 | Direct Read for Terminal Devices 5-10           |

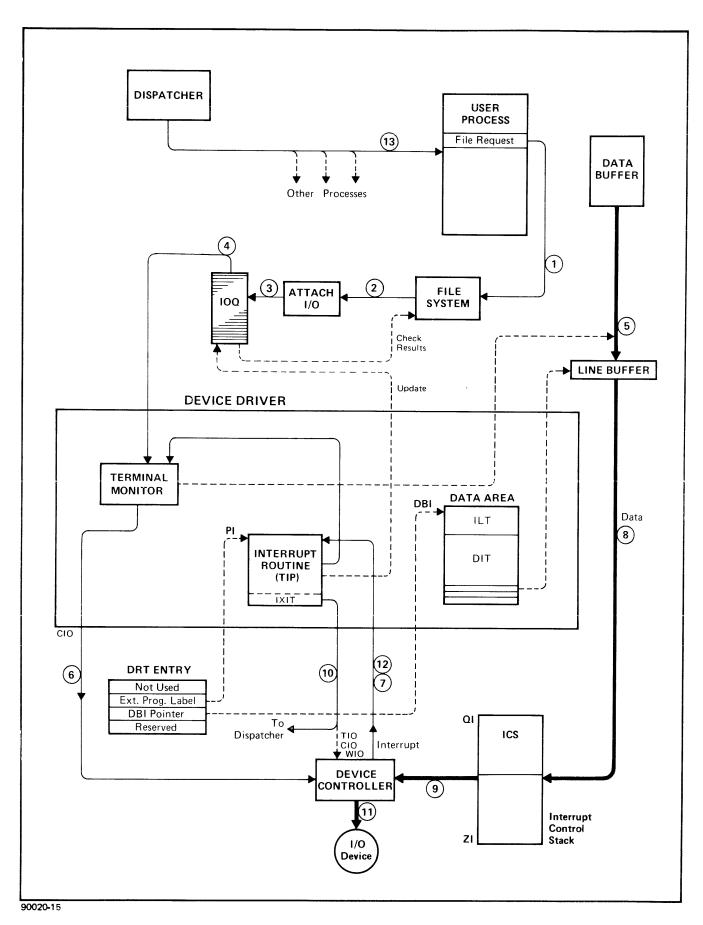

| HP 3000 Series II and III Hardware Organization 2-1   | Direct Write for Terminal Devices5-12           |

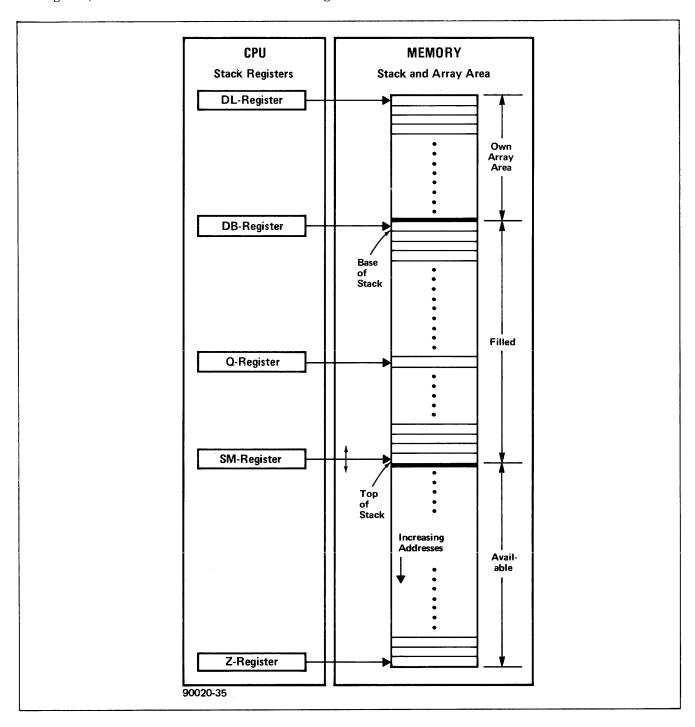

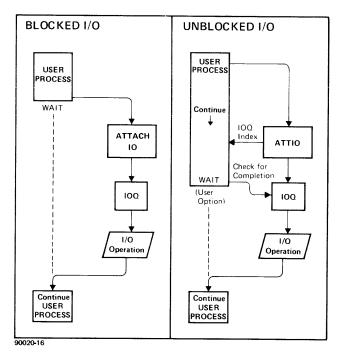

| Subprogram's View of the Data Stack2-4                | Blocked and Unblocked I/O 5-14                  |

| Typical Computer System                               | Hardware I/O Elements5-15                       |

| Data Formats                                          | I/O Program Word Format 5-17                    |

| Floating-Point Data Representation 3-8                | I/O Program Operation 5-18                      |

| Instruction Groups                                    | Dispatcher Marker on ICS 6-3                    |

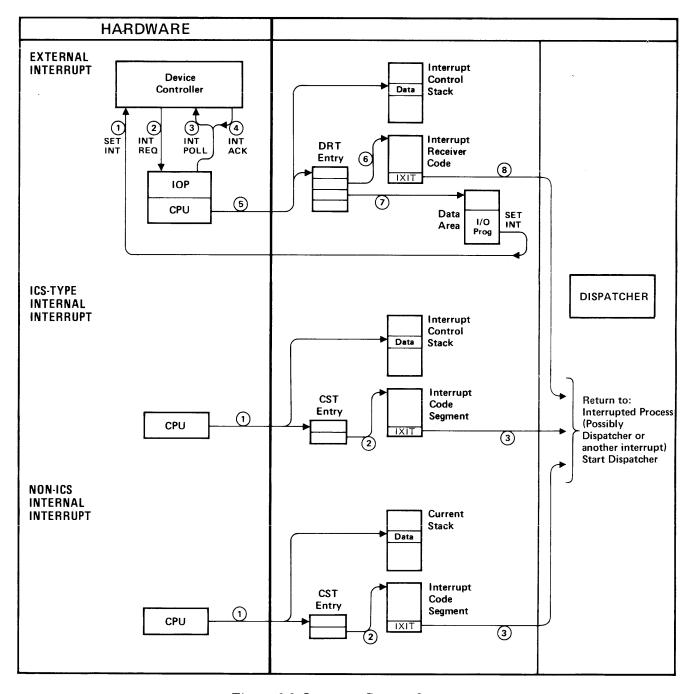

| Status Word Format                                    | Interrupt System Overview6-5                    |

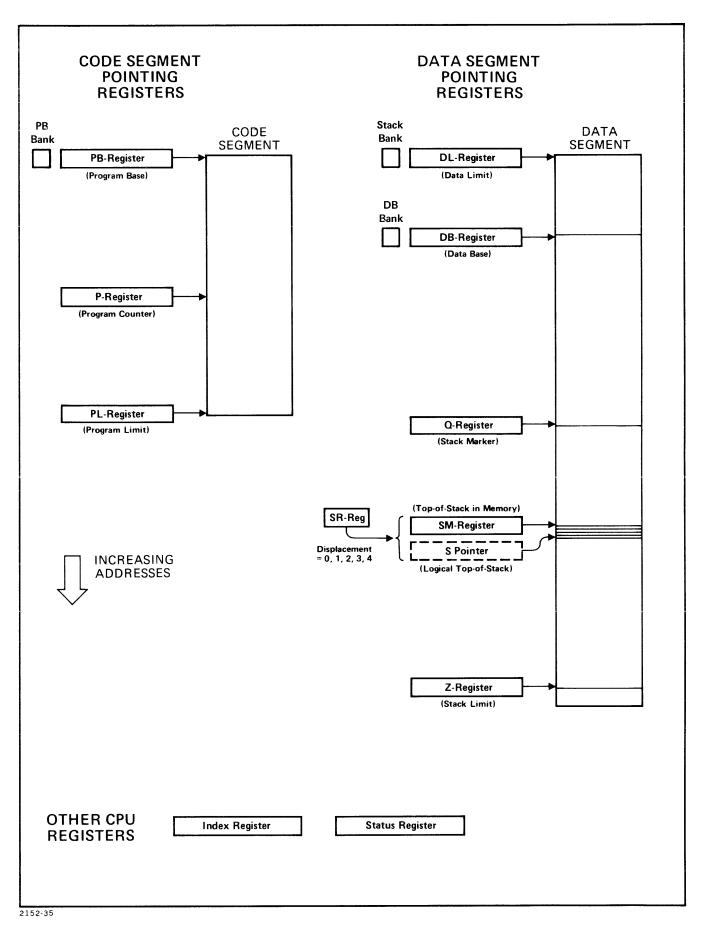

| CPU Registers                                         | Device Controller 6-8                           |

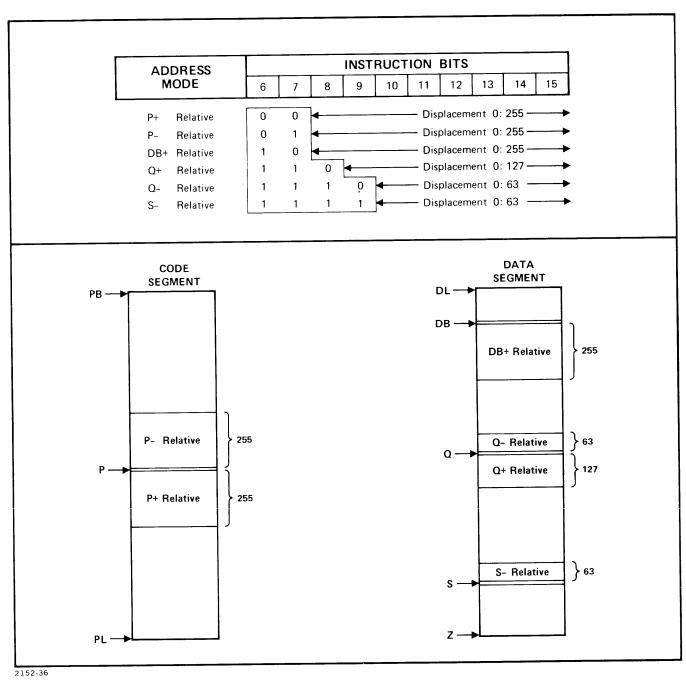

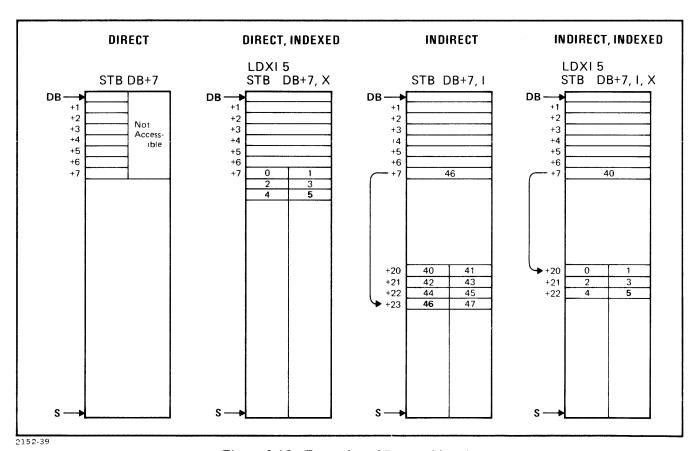

| Memory Addressing Modes                               | First Level External Interrupt 6-9              |

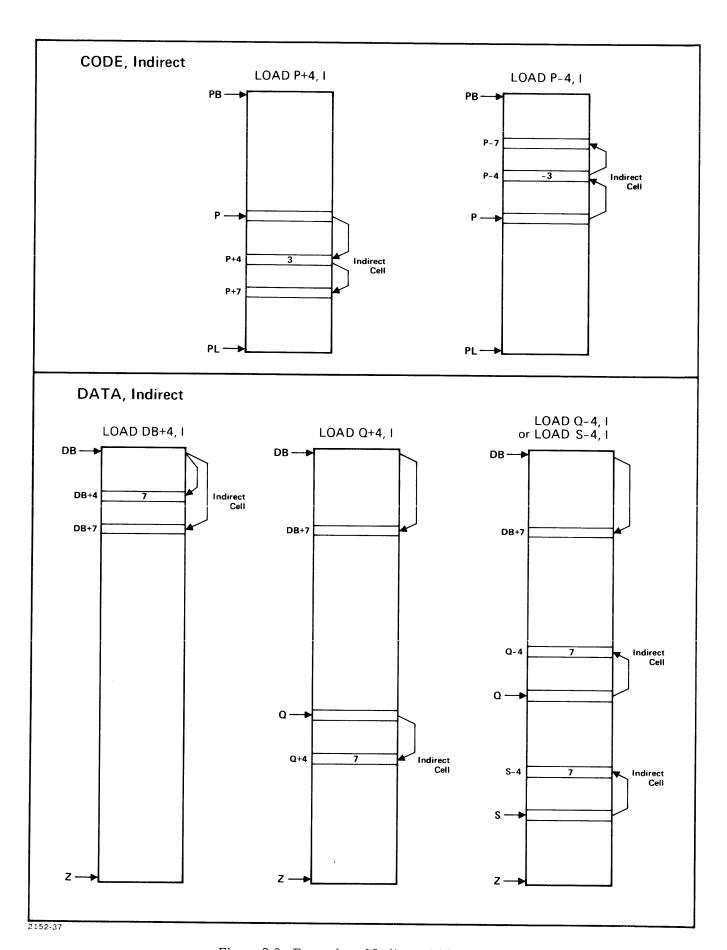

| Examples of Indirect Addressing 3-22                  | Second Level Interrupt 6-10                     |

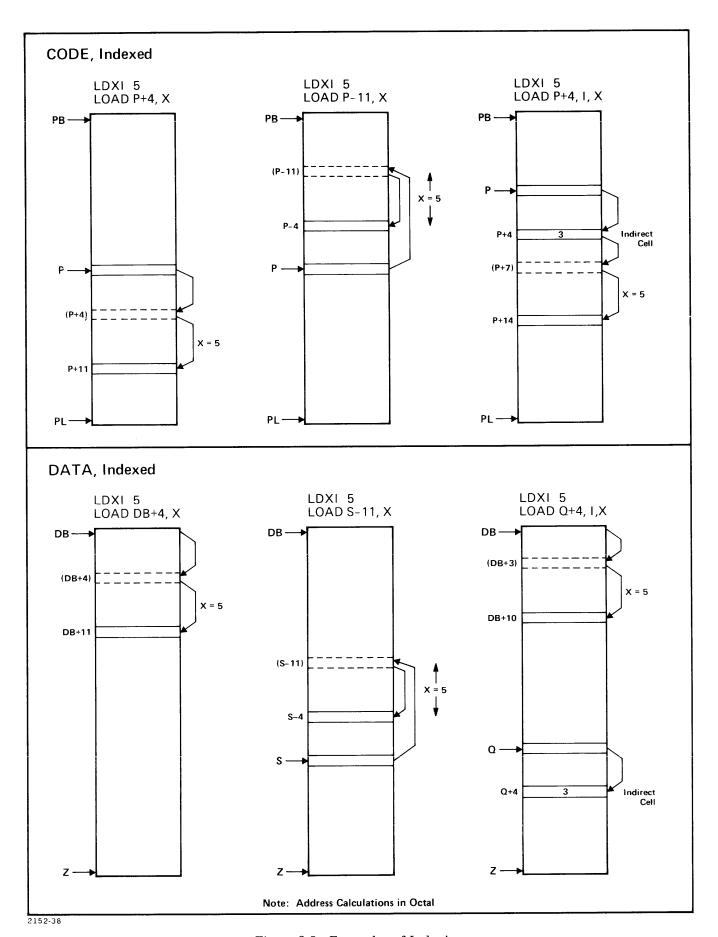

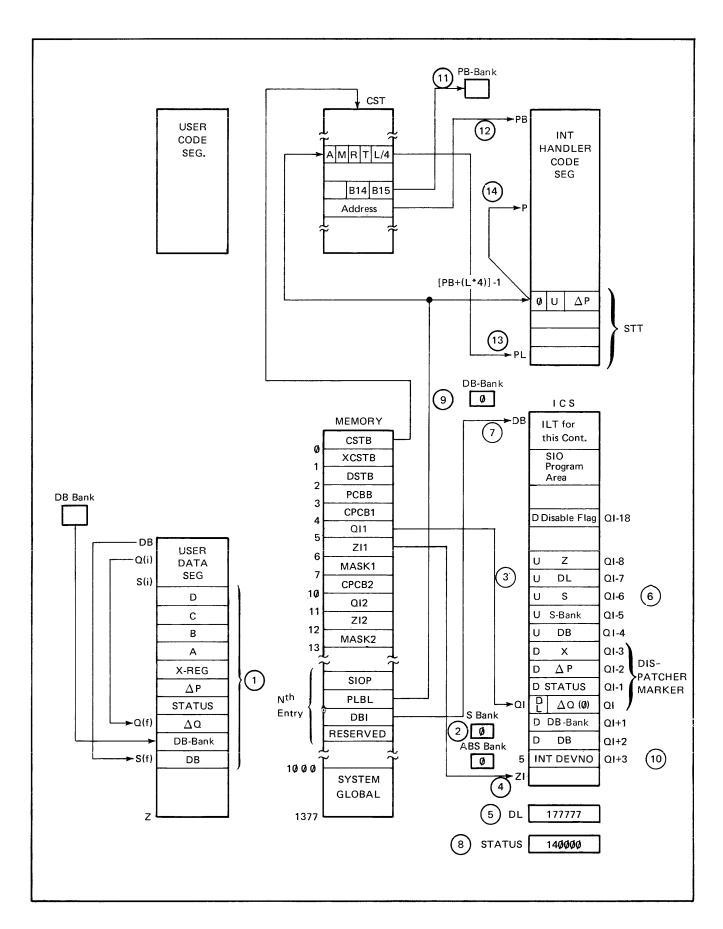

| Examples of Indexing                                  | ICS Internal Interrupt Operations 6-18          |

| Examples of Byte Addressing 3-24                      | Non-ICS Internal Interrupt Operations 6-20      |

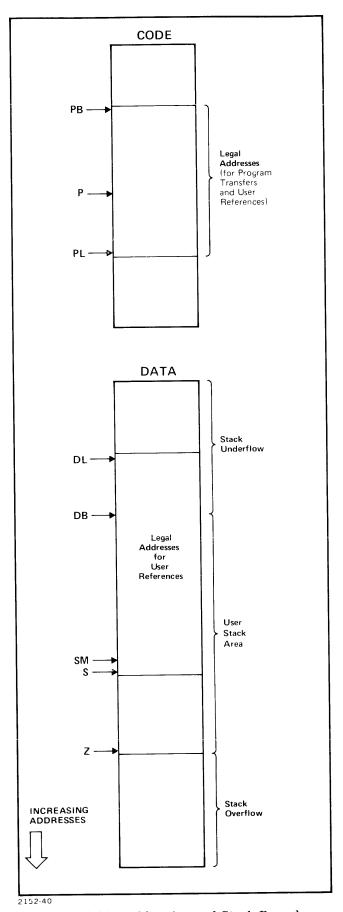

| Addressing and Stack Bounds                           | Interrupt Handler 6-21                          |

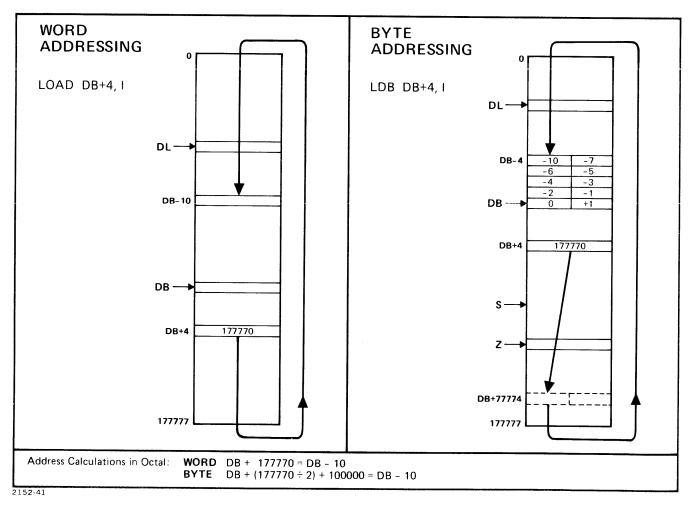

| Access to DB- Area                                    | IXIT Instruction                                |

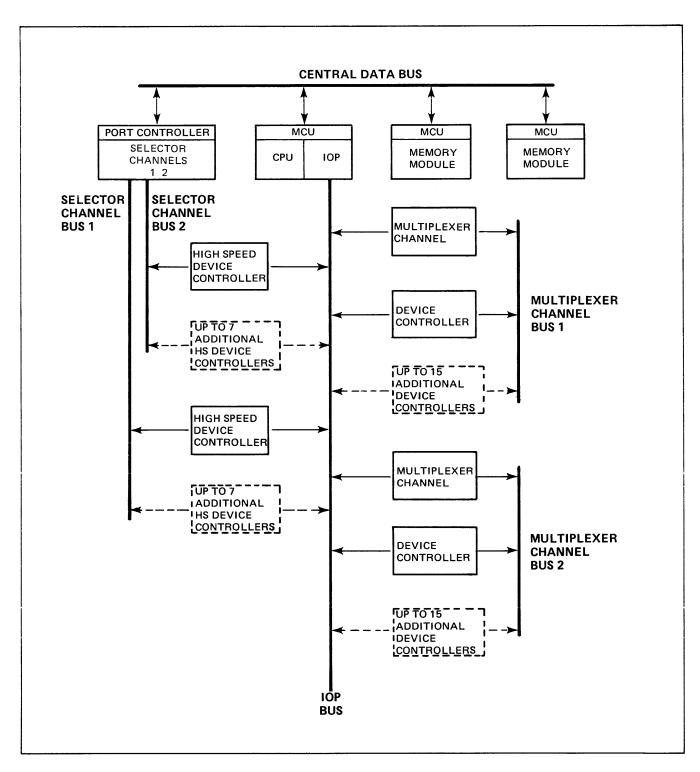

| Bus System Block Diagram                              | Simplified Logic Diagram, Plan View             |

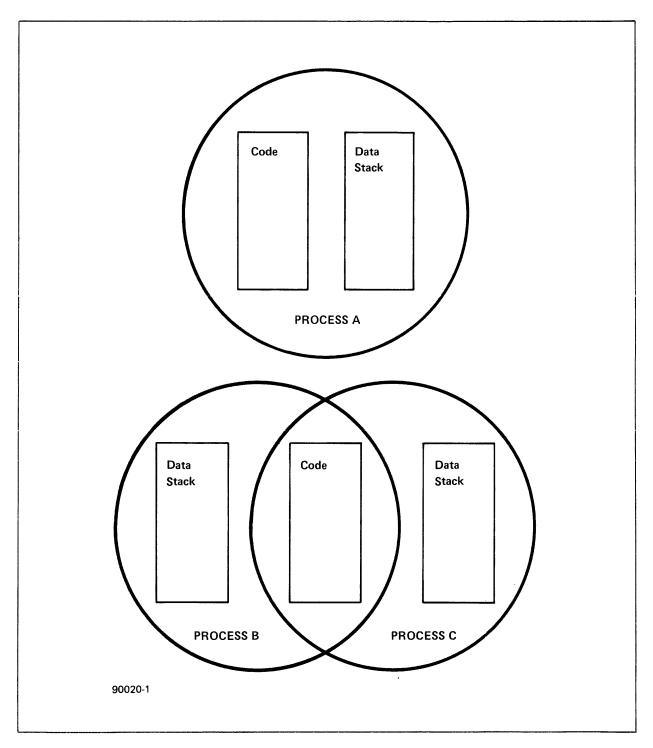

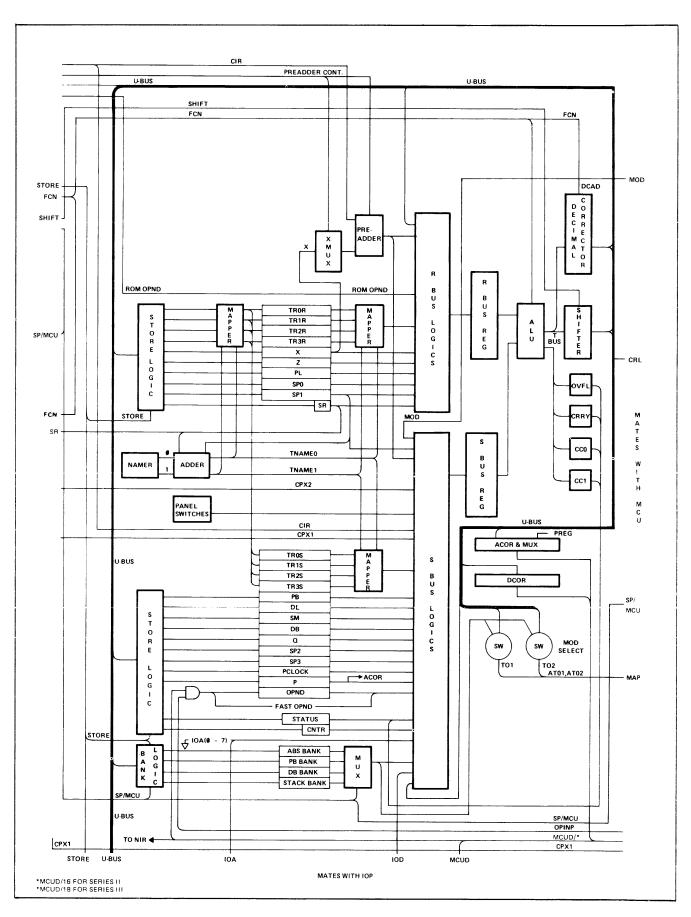

| Code Sharing and Data Privacy 4-2                     | Central Processor Unit (CPU) Simplified         |

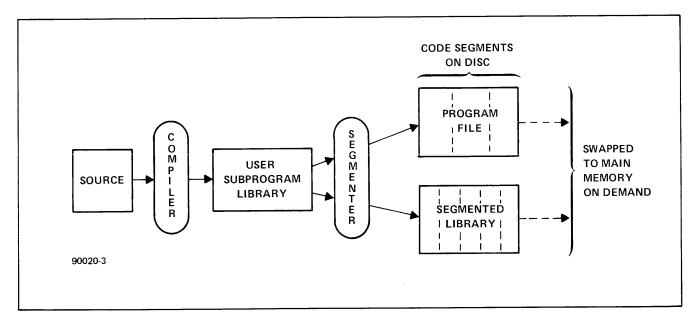

| Segmented Memory Management4-4                        | Logic Diagram                                   |

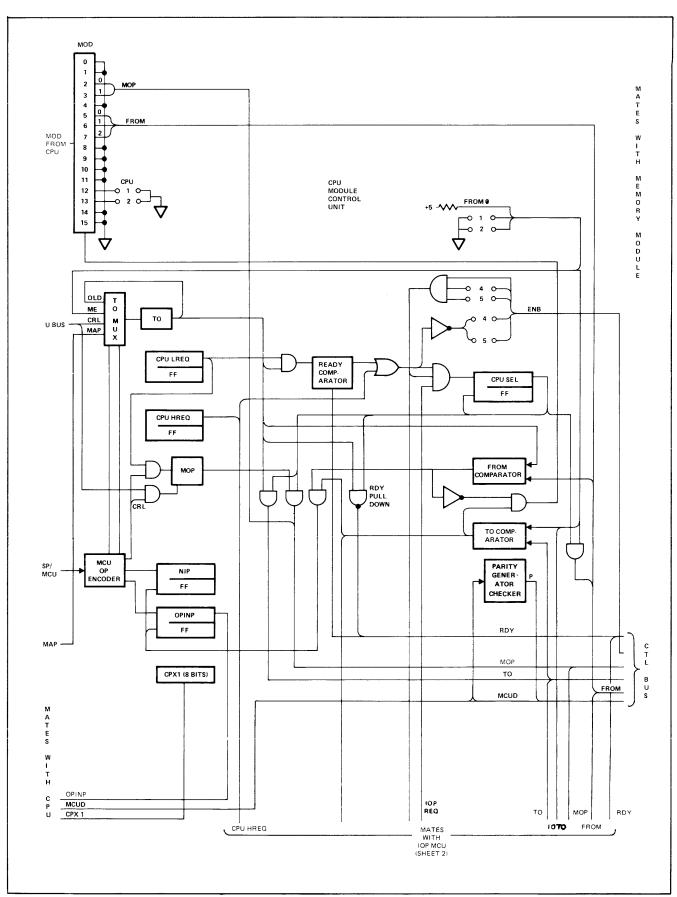

| Code Segment Evolution4-5                             | Model Control Unit (MCU) Simiplified            |

| Basic Data Structures                                 | Logic Diagram                                   |

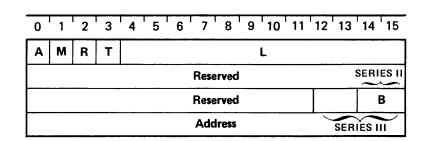

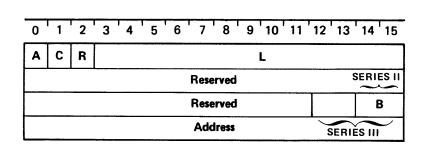

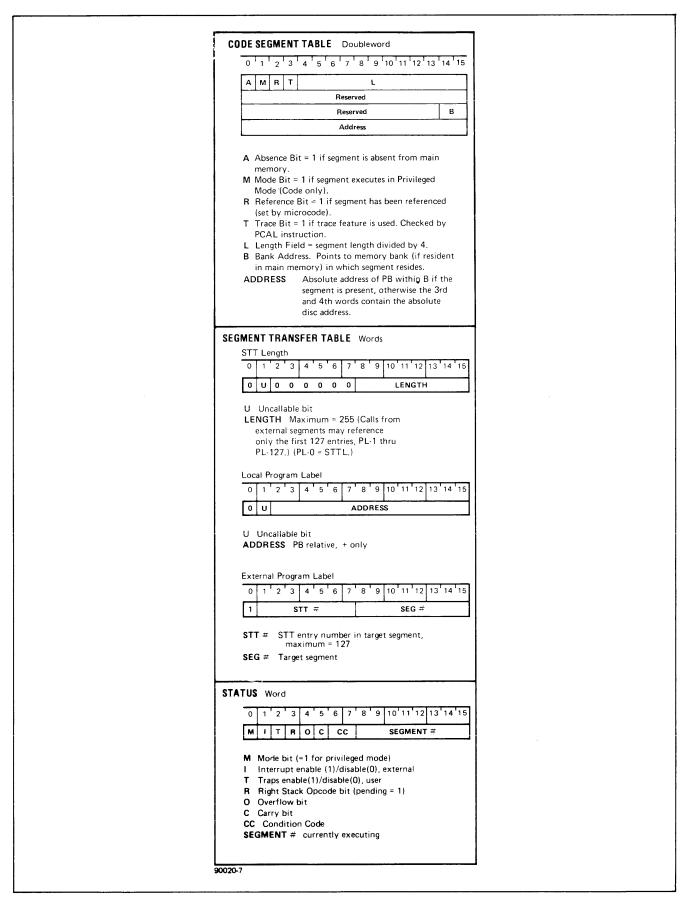

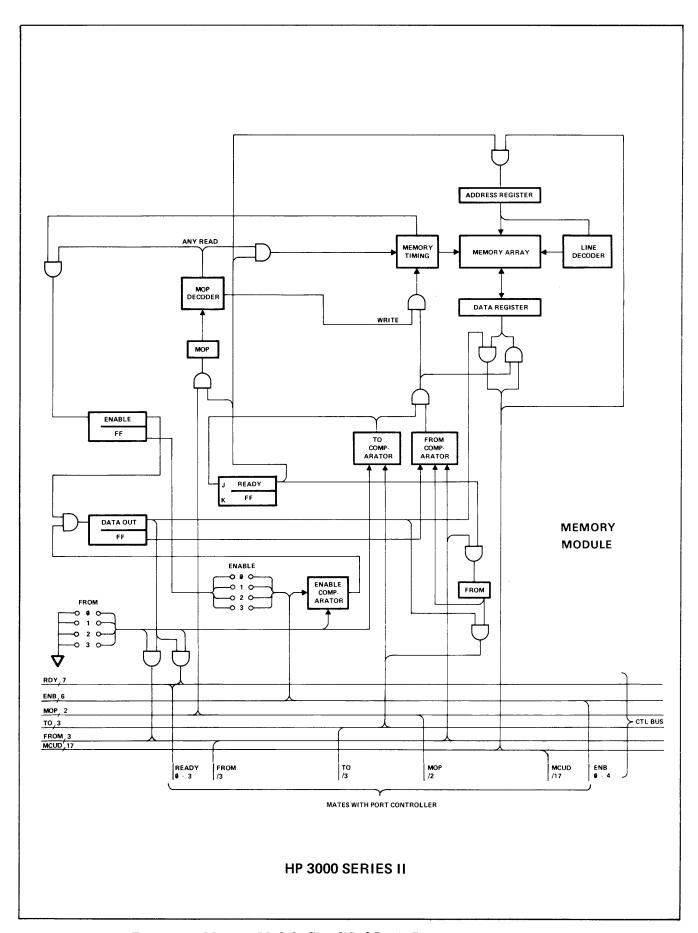

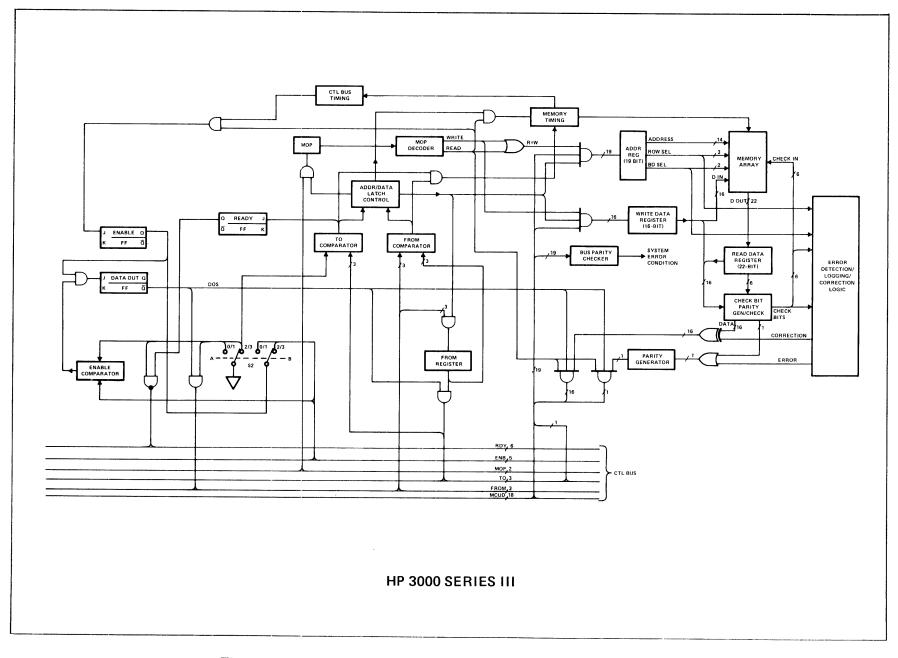

| Code Segment Table Entry Format 4-9                   | Memory Module Simplified Logic Diagram 7-29     |

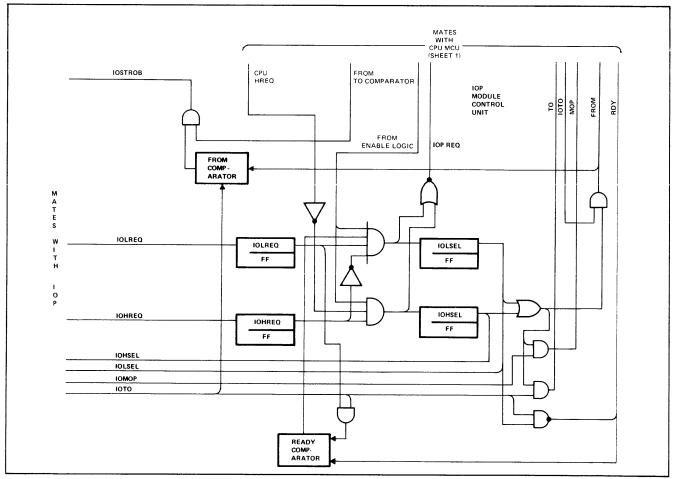

| Data Segment Table Entry Format 4-10                  | Input/Output Processor (IOP) Simplified         |

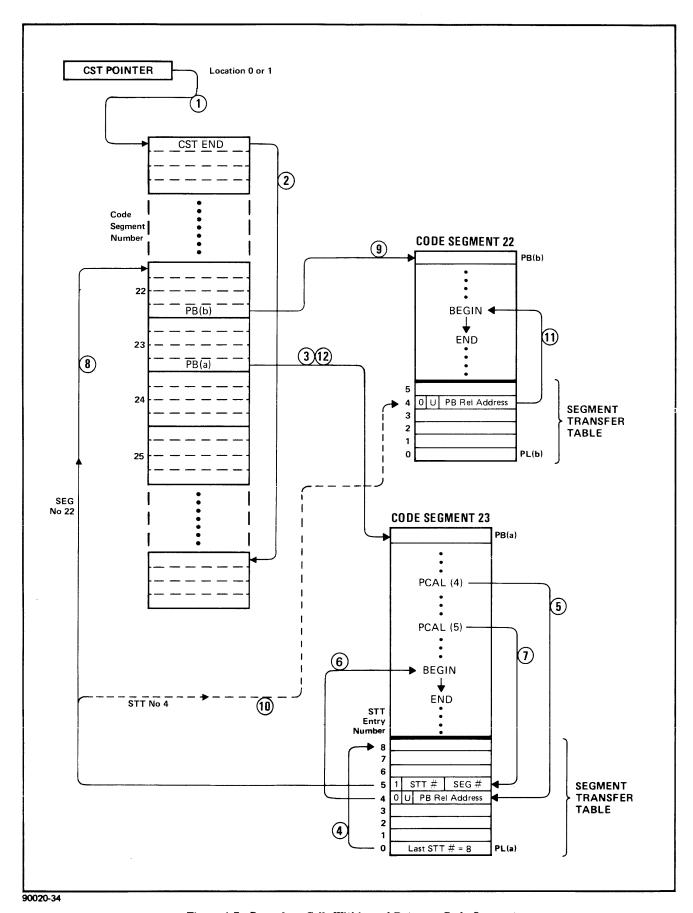

| Procedure Calls Within and Between                    | Logic Diagram                                   |

| Code Segments                                         | Interrupt Poll and Data Poll                    |

| Formats Associated with Code Segments 4-13            | Input/Output Data Routes                        |

| Stack Registers and One Stack 4-15                    | Basic Comparison of Multiplexer and             |

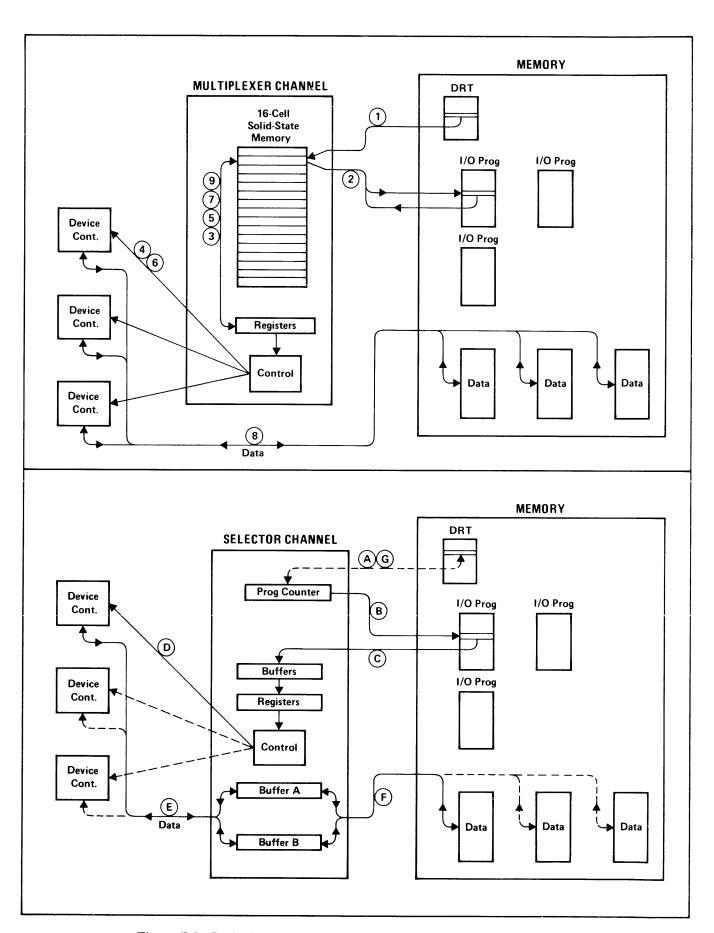

| Top of Stack in the CPU4-16                           | Selector Channels                               |

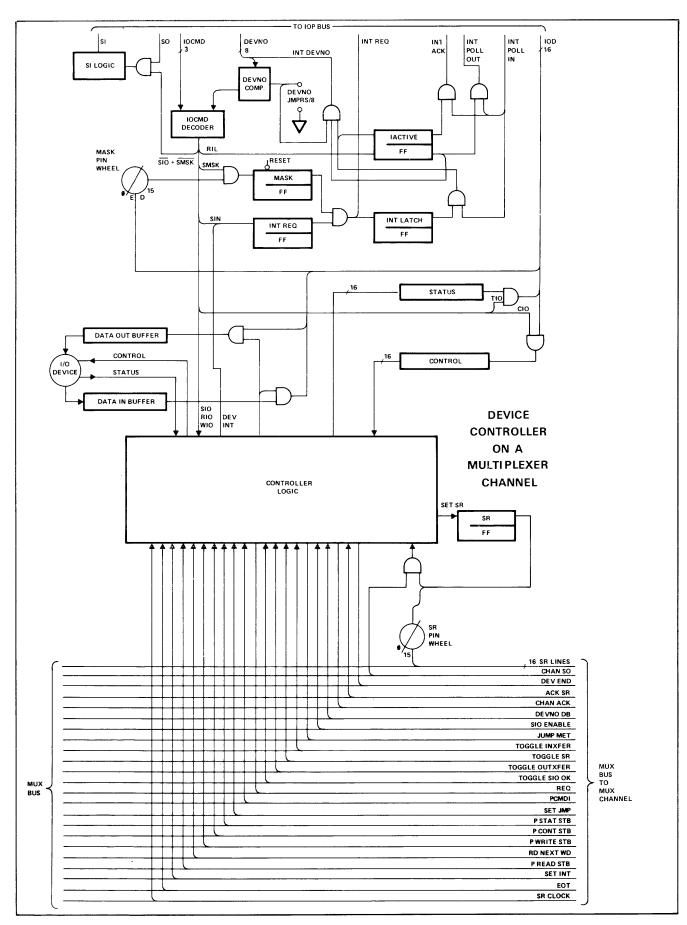

| Stack Mark Chain 4-17                                 | Multiplexer Channel and Device Controler        |

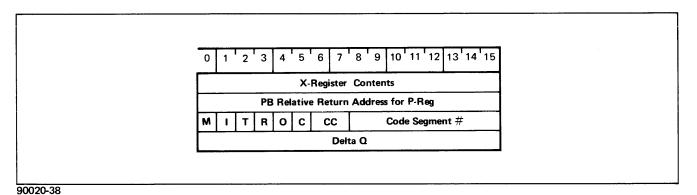

| Standard 4-Word Stack Marker Format 4-19              | Simplified Logic Diagram                        |

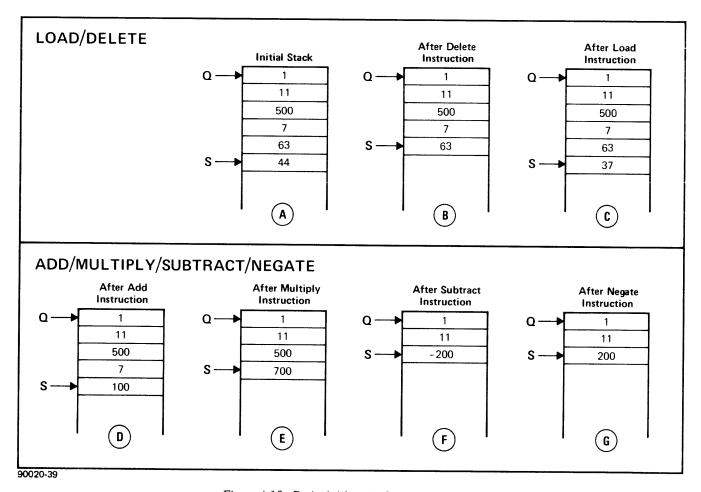

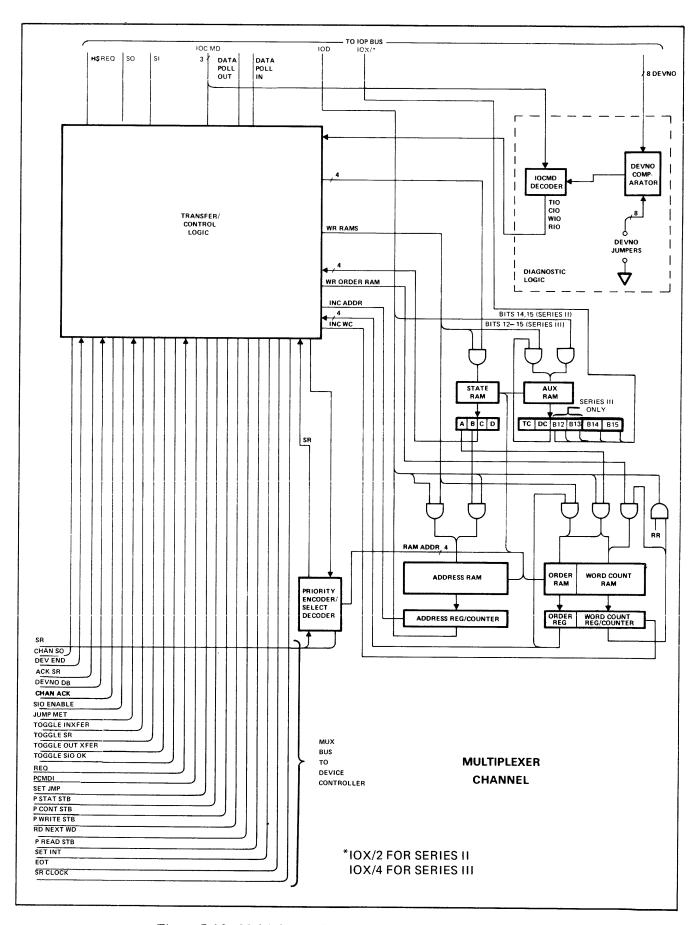

| Basic Arithmetic Stack Operations 4-20                | Multiplexer Channel Simplified Logic            |

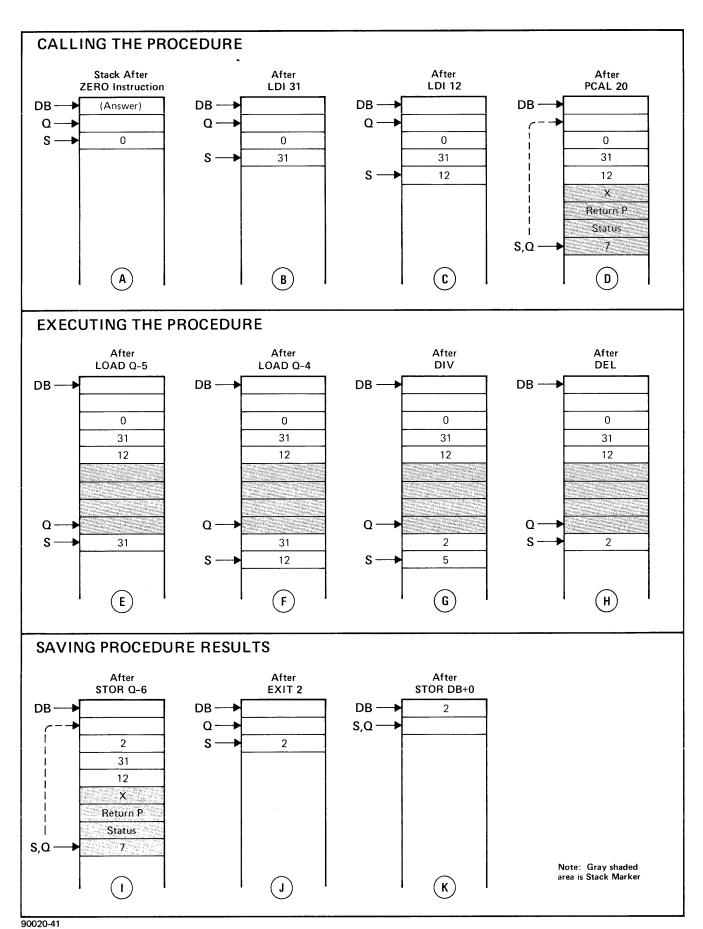

| Declaring and Calling a Procedure 4-22                | Diagram 7-36                                    |

| Executing a Simple Procedure 4-23                     | Port Controller Simiplified Logic Diagram 7-37  |

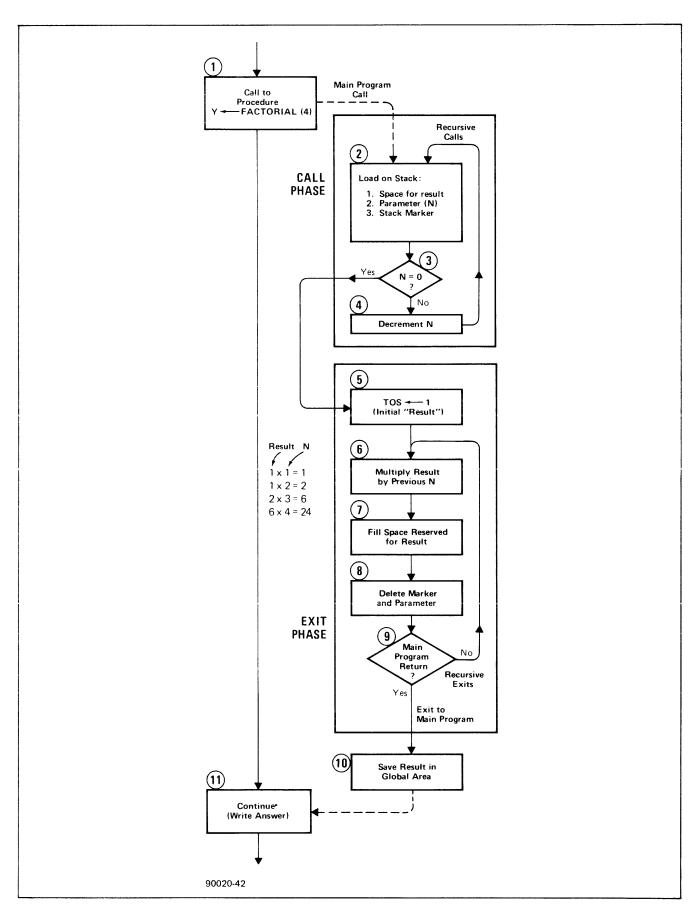

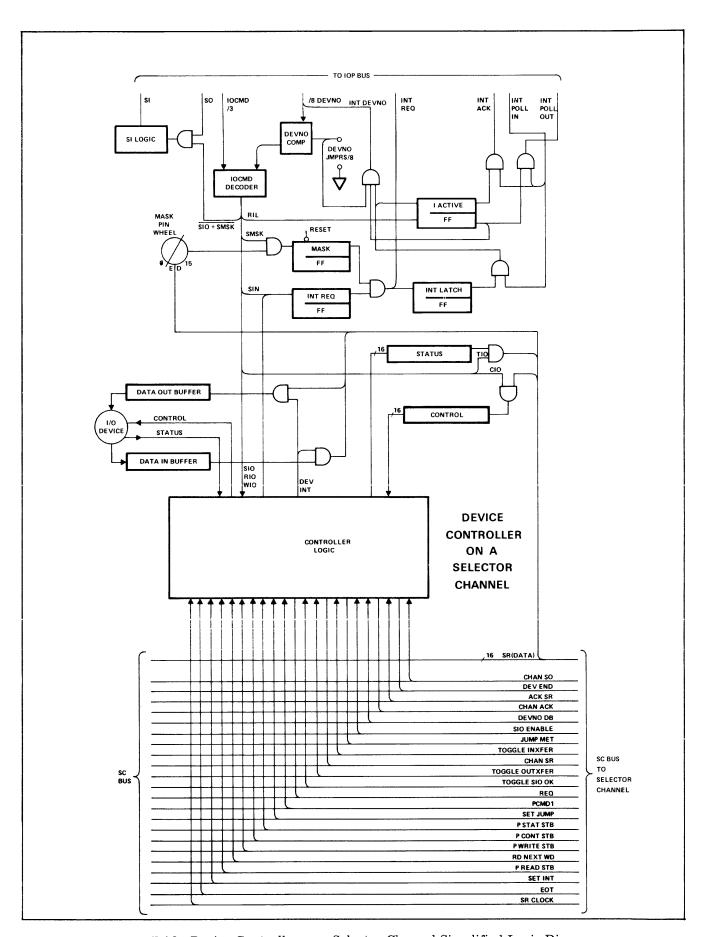

| Example of Recursive Procedure 4-28                   | Device Controller on a Selector Channel         |

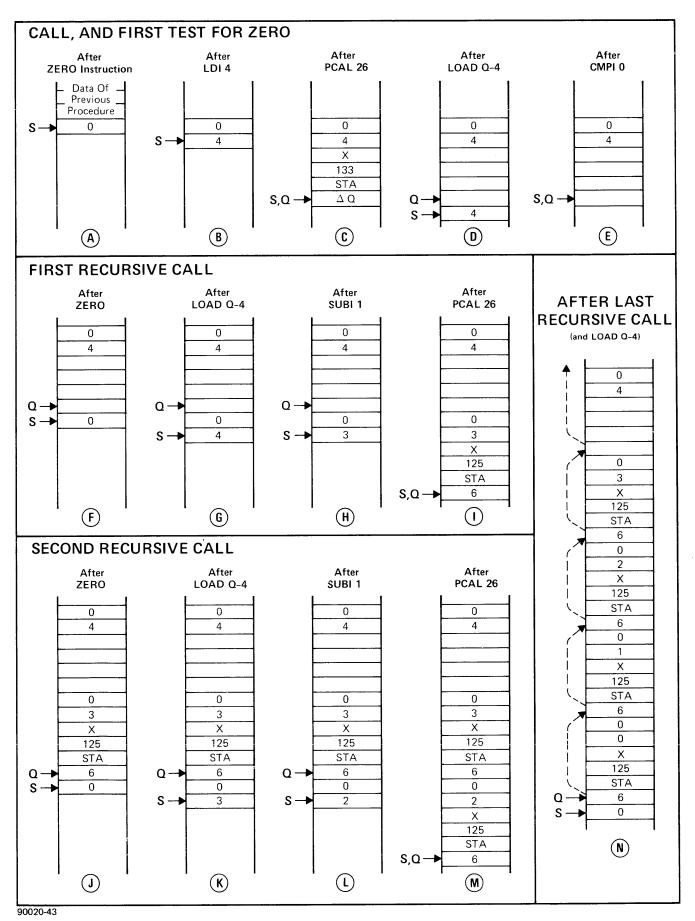

| Recursive Calls                                       | Simplified Logic Diagram                        |

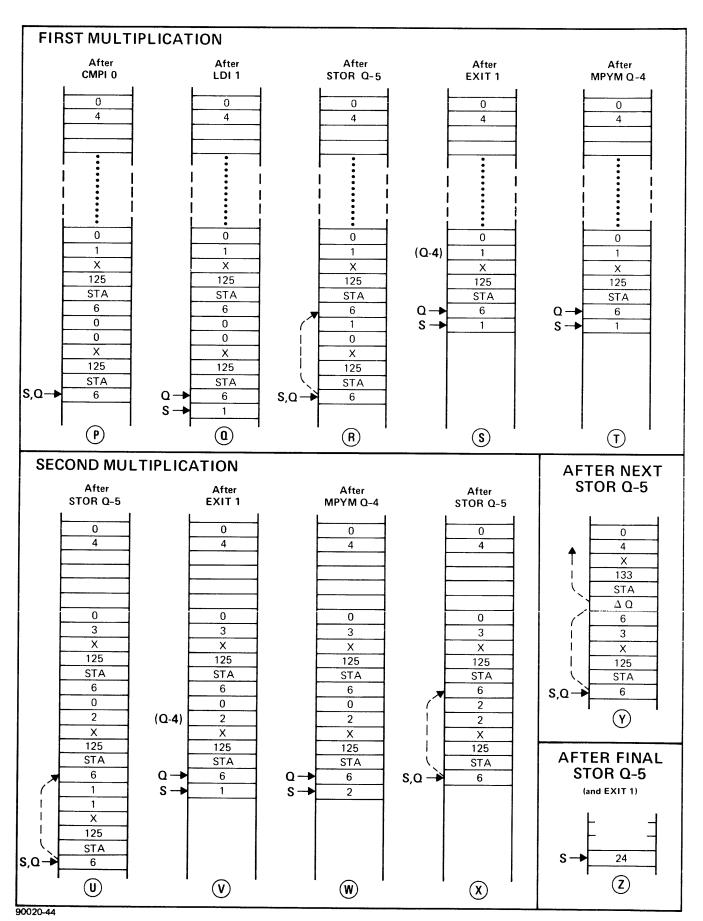

| Recursive Exits                                       | Selector Channel Simiplified Logic Diagram 7-39 |

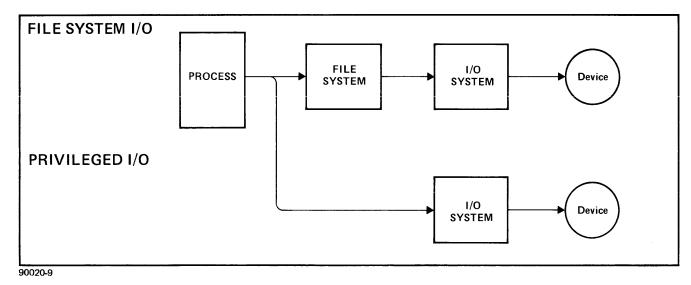

| Basic I/O Access Methods                              | Direct I/O Device Controller Simplified         |

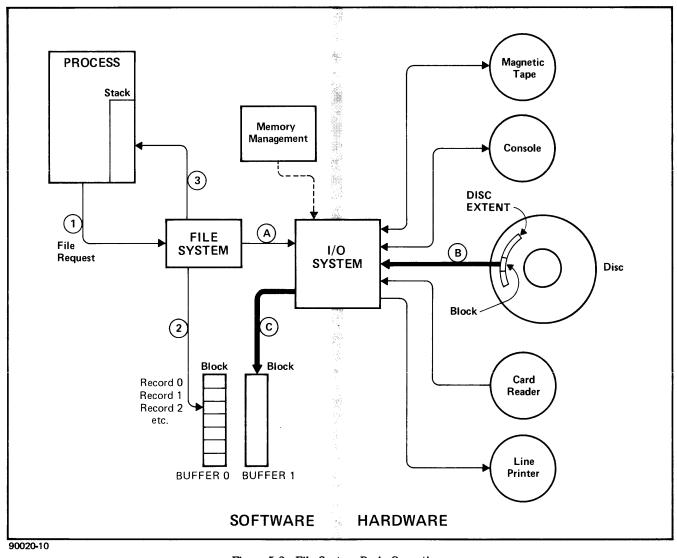

| File System Basic Operation 5-3                       | Logic Diagram                                   |

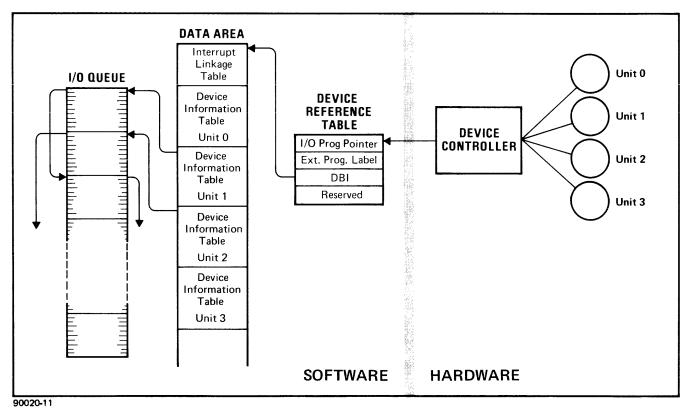

| Fundamental Elements of I/O System 5-4                |                                                 |

viii

## **TABLES**

| Title                           | Page | Title                                 | Page |

|---------------------------------|------|---------------------------------------|------|

| CPU Features                    | 2-3  | Shift Field Code Definitions          | 3-53 |

| Machine Registers               | 2-5  | Special Field Code Definitions        | 3-54 |

| Main Memory Features            |      | MCU Option Field Code Definitions     | 3-57 |

| Condition Codes                 |      | R-Bus Field Code Definitions          | 3-59 |

| Bounds Checks                   | 3-26 | Top-of-Stack Namer Relationships      | 3-61 |

| S-Bus Field Code Definitions    | 3-37 | Low Main Memory Location Reservations | 4-7  |

| Store Field Code Definitions    |      | Recursive Program                     | 4-27 |

| Function Field Code Definitions |      | Interrupt Types                       | 6-1  |

| Skip Field Code Definitions     |      | • • •                                 |      |

### INTRODUCTION

SECTION

#### 1-1. PURPOSE OF MANUAL

This manual is the reference document for the Hewlett-Packard HP 3000 Series II and III Computer Systems. Except where specified, the content of this manual applies equally to the Series II and Series III Computer Systems. The sections of this manual are arranged in a building block sequence for the reader who is unfamiliar with the computer systems. Specifically, this manual contains seven sections arranged as follows:

- Section I Provides an introduction to the HP 3000 Series II and Series III Computer Systems.

- Section II Describes the prominent features of the systems.

- Section III Provides a system-level description of the principles of operation for complete systems and a detailed block-level theory of operation description of the central processor units.

- Section IV Describes the memory segmentation schemes used in the HP 3000 Series II and III, including an in-depth description of the stack and stack operations.

- Section V Describes the I/O system as accessed via the file system.

- Section VI Describes system interrupts and trap processing.

- Section VII Provides a functional operation description of the systems.

#### 1-2. SYSTEM DESCRIPTIONS

The HP 3000 Series II and Series III Computer Systems are general purpose computers with true multiprogramming and multilingual capabilities. They can simultaneously handle many interactive and batch operations; each in any of several programming languages. The systems feature a hardware stack architecture, variable-length code segmentation in a hardware-assisted virtual memory scheme, user protection, dynamic storage allocation, and integrated hardware/software design. The hardware and software work together in an interrelated manner with the hardware performing many operations conventionally performed by software. The computer systems use a common Multiprogramming Executive (MPE) operating system. MPE is a general purpose, disc-based software system that supervises the processing of user programs. MPE relieves the user of many program control, input/output, and other housekeeping responsibilities by monitoring and controlling the compilation, run preparation, loading, execution, and output of user programs. MPE also controls the order in which programs are executed and allocates the hardware and software resources they require.

The computer systems are configured with semiconductor memory. Series II memory sizes range from 64K words to 256K words (K=1024). Series III memory sizes range from 128K words to 1024K words.

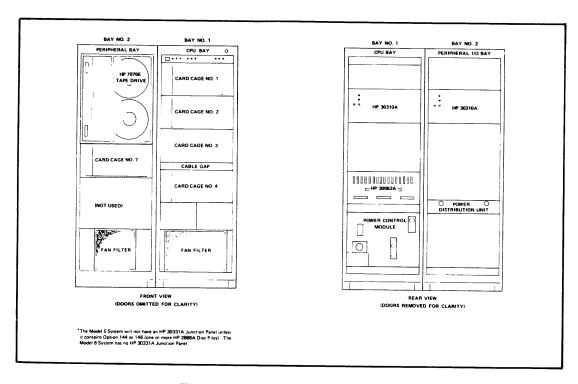

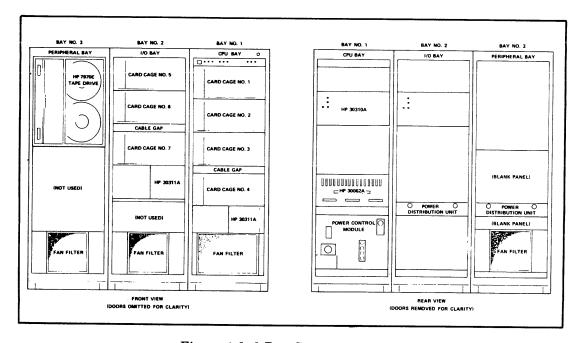

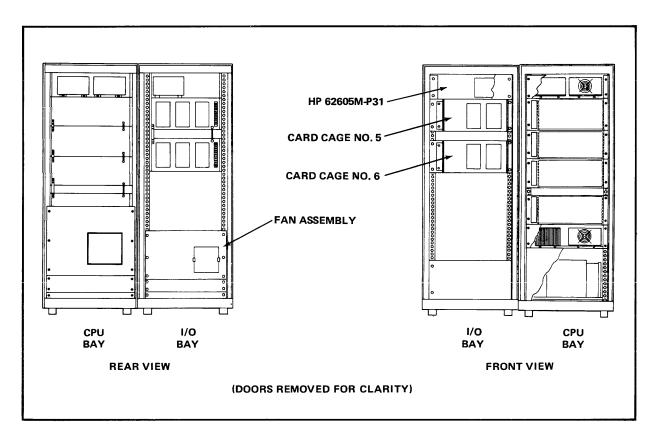

The Series II Computer System is available in two hardware configurations; a two-bay system (Model 6) and a three-bay system (Model 8). The Series III Computer System is offered in two product models, 32421A and 23435A, each of which is available in two hardware configurations. The Series III Computer System, product number 32421A, is available in the standard two-bay system and an optional three-bay (Option 200) system. Rack layouts for the two- and three-bay systems are shown in figures 1-1 and 1-2, respectively. The Series III Computer System, product number 23435A, is also available in two hardware configurations, a standard one-bay system and an optional two-bay (Option 200) system. The rack layouts for this product are shown in figure 1-3.

Figure 1-1. 2-Bay Computer System

Figure 1-2. 3-Bay Computer System

Figure 1-3. Series III (23435A) 1-Bay and 2-Bay Computer Systems

## SYSTEM FEATURES

SECTION

This section summarizes the architectural features of the HP 3000 Series II and III Computer Systems. The design of the hardware provides an efficient and powerful foundation upon which the software is built.

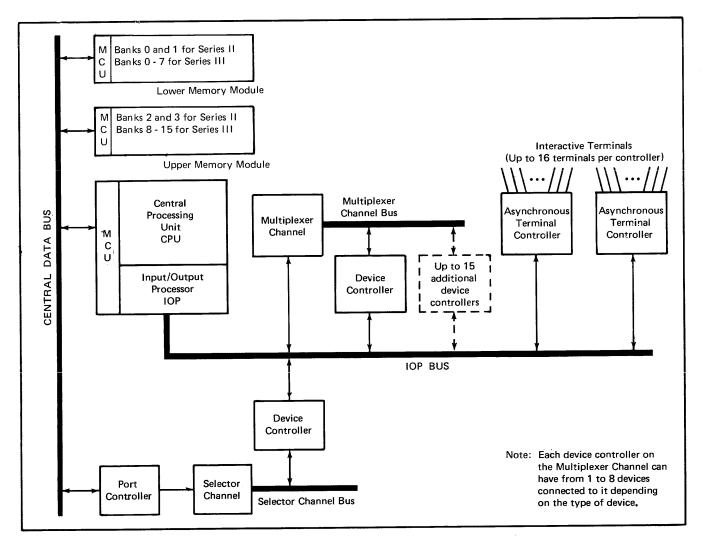

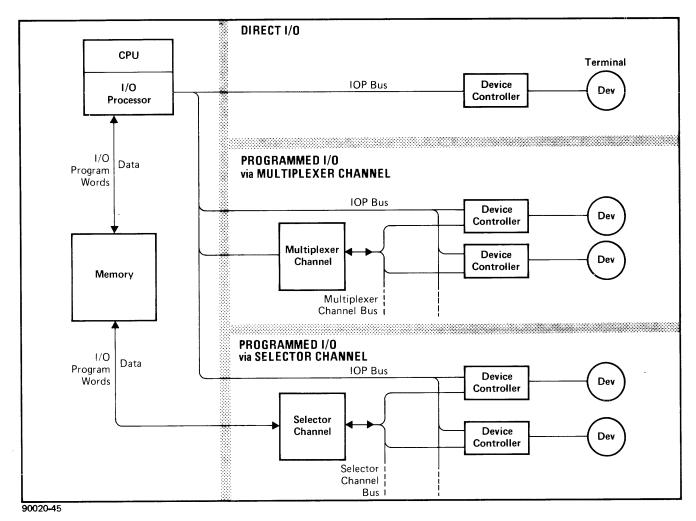

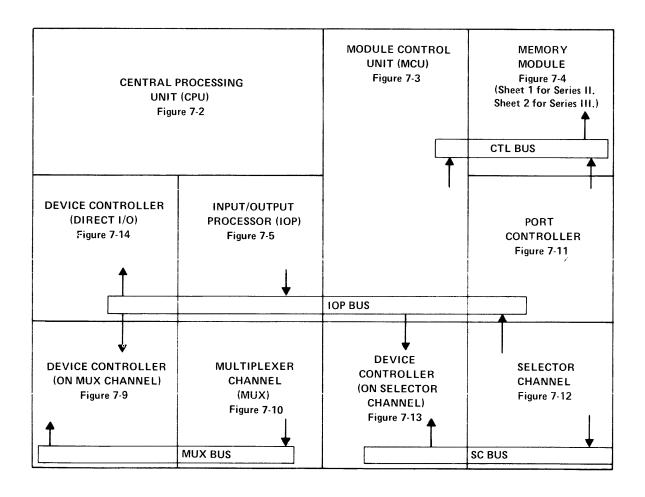

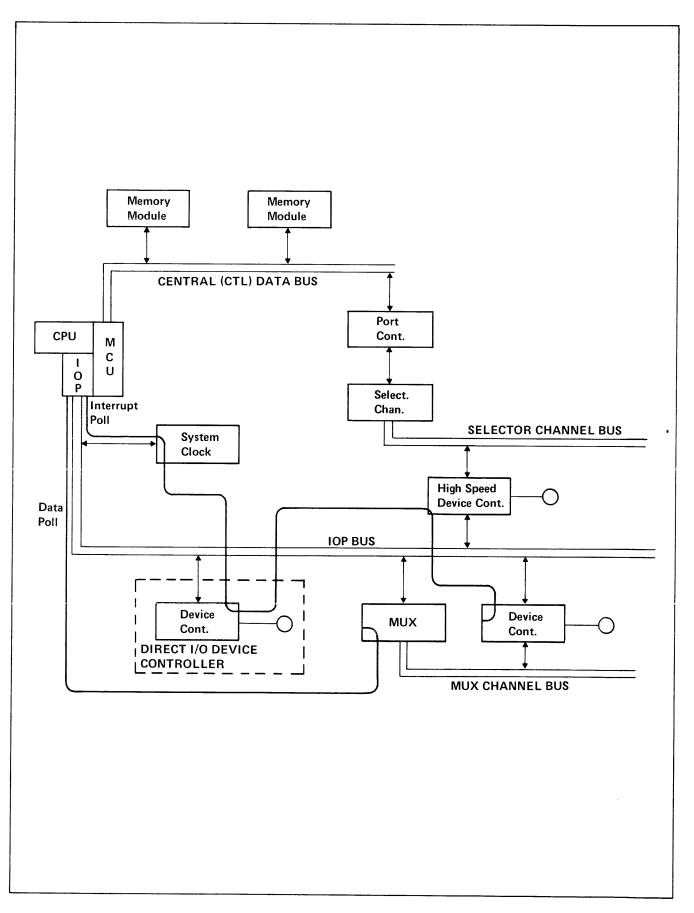

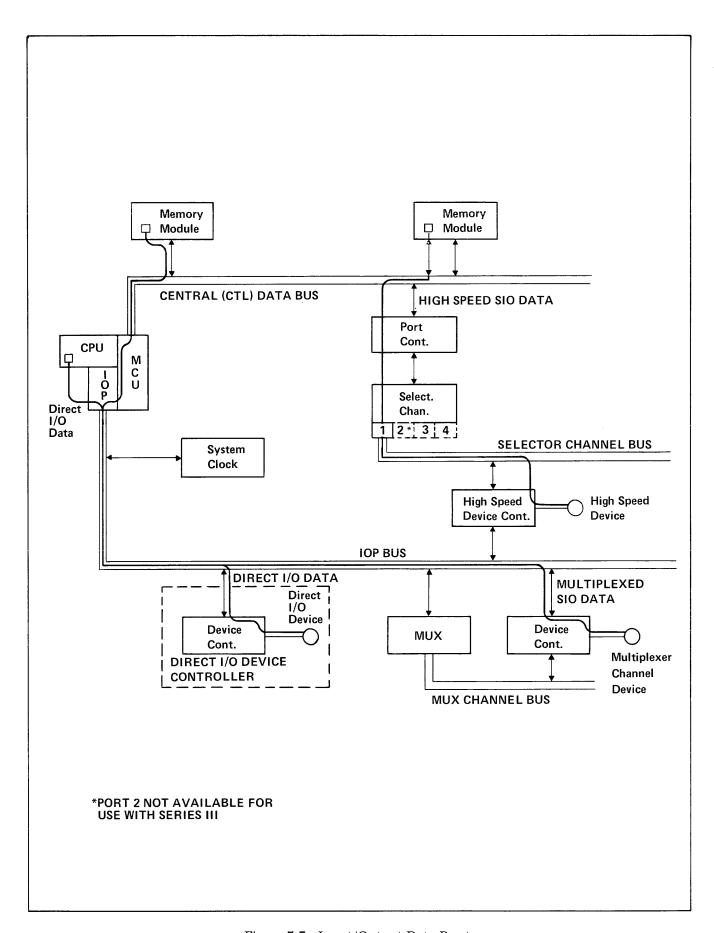

The hardware elements of the computer systems are organized as illustrated in figure 2-1. Communication between modules occurs over the Central Data Bus. The Central Processing Unit (CPU) and the Input/Output Processor (IOP), although independent of one another, share a common module address. This is resolved by giving the IOP a higher priority in the case where both processors concurrently request use of the bus. The CPU is controlled by a specially designed microprocessor to allow a great deal of flexibility in the machine instruction set. The computer systems also employ high-speed, semiconductor memory modules which use automatic fault detection and correction with no loss in performance.

Figure 2-1. HP 3000 Series II and III Hardware Organization

The basic structure of independent modules organized around a Central Data Bus permits high-speed internal data rates. When not communicating over the bus, each module can run independently at its own speed. New equipment can also be added without having to go through a major hardware reconfiguration.

The presence of a separate IOP Bus which is totally dedicated to input/output data transfers means that the computer systems can always respond immediately to the needs of I/O devices regardless of what transfers are currently in progress between the various system modules. It also means that many I/O operations can be handled concurrently with CPU, main memory, and high-speed Selector Chanel operations.

Data may be transferred directly between main memory and high-speed peripheral devices in block mode by way of high-speed Selector Channels connected to the Central Data Bus. For lower speed devices, data may be multiplexed on a word-by-word basis by way of the IOP and a Multiplexer Channel. In both cases the I/O channels execute in parallel with CPU operations. Direct control of devices attached to the IOP bus is also possible through the use of the CPU's direct I/O instructions.

The configuration of hardware modules and peripheral devices is easily changed to accommodate system expansion.

#### 2-1. CENTRAL PROCESSING UNIT (CPU)

The significant features of the CPU are listed in table 2-1.

#### 2-2. SEPARATE CODE AND DATA

Code consists of the executable instructions and unchanging constants of a program or subprogram. As the code executes, the manipulated values are referred to as data. Code and data are maintained in strictly separate domains by the compilers and the system and cannot be intermixed (with the exception, however, that program constants may be present in code segments). This fact, plus the fact that code is non-modifiable while active in the system, permits code to be sharable and re-entrant. This means that main memory can be used with optimum efficiency since one copy of heavily used programs is shared by many users concurrently. Re-entrancy and stack-structured data (discussed in the next paragraph) together make possible subprogram recursion (a subprogram calling itself), which is essential for efficient compilers and system software. Also, since code is non-modifiable, exact copies of all active code are always retained on disc, thus allowing code to be overlayed without having to first write it back out to the disc.

#### 2-3. DATA STACKS

The data for each user is organized into a data stack. In general, a stack is a storage area where the last item stored in is usually the first item taken out. In actual use, however, programs have direct access to all elements in the stack by specifying addresses relative to several CPU registers (the DB, S, and Q registers). The stack structure provides an efficient mechanism for parameter passing, dynamic allocation of temporary storage, efficient evaluation of arithmetic expressions, and recursive subprogram calls. In addition, it enables rapid context switching to establish a new environment on subprogram calls and interrupts. All features of the stack (including the automatic transferring of data to and from the CPU registers and checking for stack overflow and stack underflow) are implemented in the hardware.

#### **ARCHITECTURE**

- Hardware-implemented stack

- Separation of code and data

- Non-modifiable, re-entrant code

- Variable-length code segmentation

- Virtual memory for code

- Dynamic relocatability of programs

#### **IMPLEMENTATION**

- Microprogrammed CPU

- 175 nanosecond microinstruction time

- Automatic restart after power failure

- Central Data Bus

- Bus parity checking

- Concurrent CPU and I/O operations

#### INSTRUCTIONS

- 209 powerful instructions

- All instructions except stack operations are 16 bits in length (stack operations may be packed two per word)

- 16- and 32-bit integer arithmetic

- 32- and 64-bit floating point arithmetic

- 28-digit packed decimal arithmetic

- Special instructions that optimize the efficiency of the operating system

When programming in a high-level language such as COBOL or RPG, all manipulation of the stack is done for the user automatically by the language processor. The user can, however, manipulate the stack directly by writing subprograms in SPL (Systems Programming Language for the HP 3000).

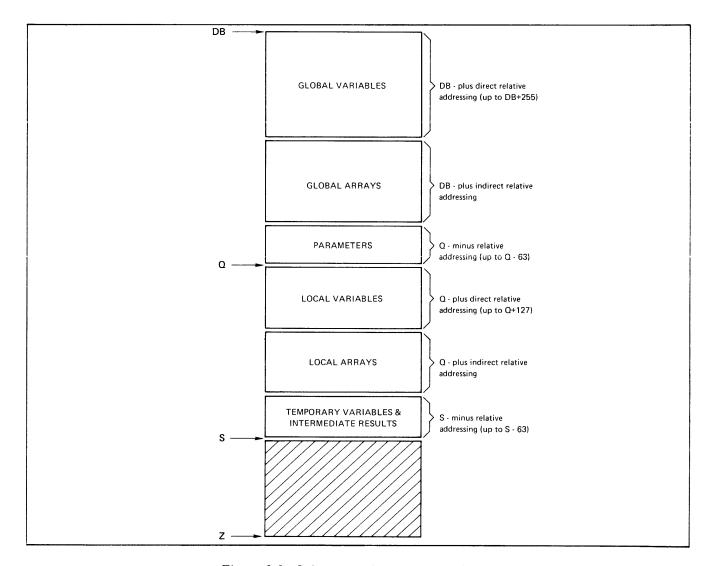

Figure 2-2 illustrates the general structure of a data stack as viewed from a subprogram. The white area represents filled locations, all containing valid data, while the shaded area represents available unfilled locations. The stack area is delimited by the locations defined as DB (Data Base) and S (Stack pointer). The addresses DB and S are retained in dedicated CPU registers. The Q-minus relative addressing area contains the parameters passed by the calling program. The area between Q and S contains the subprogram's local and temporary variables and intermediate results.

The data in the DB location is the *oldest* element on the stack. The data in the S location is the *most current* element. The location S is also referred to as the *Top of Stack* or TOS. Conventionally, the *top* is shown in diagrams *downward* from DB; this corresponds to the normal progression of writing software programs where the most recently written statement is farther down the page than previous (older) ones.

The area from S+1 to Z (the shaded area) is available for adding more elements to the stack. When a data word is added to the stack, it is stored in the next available location and the S pointer is automatically incremented by one to reflect the new TOS. This process is said to *push* a word onto the stack. To *delete* a word from the stack, the S pointer is simply decremented by one, thus putting the word in the undefined area.

To refer to recently stacked elements of data, S-minus relative addressing is used. Under this convention, S-1 is the second element on the stack, S-2 is the third, and so on. S-minus relative addressing is one of the standard addressing conventions. The others are DB-plus relative addressing and Q-minus and Q-plus relative addressing (the Q-register separates the data of a calling program or subprogram from the data of a called subprogram).

Since the top four elements of the stack are the most frequently used, there are four CPU registers (RA, RB, RC, and RD) which may at various times contain up to four of the topmost stack elements. The use of CPU registers in this way increases the execution speed of stack operations by reducing the number of memory references needed when manipulating data at or near the top of the stack. These registers are implicitly accessed by many of the machine instructions and whenever the stack locations S, S-1, S-2, or S-3 are specifically referenced. Data stacks are expanded automatically by the operating system during execution up to a maximum size of 64K bytes.

#### 2-4. VARIABLE-LENGTH SEGMENTATION

Variable-length segmentation of code and data is used to facilitate multiprogramming. This method, in comparison with paging schemes, minimizes "checkerboard" waste of memory resources due to

Figure 2-2. Subprogram's View of the Stack

internal fragmentation. It also makes it possible for the operating system to deal with logical instead of physical entities. This means, for example, that a particular subprogram can always be contained within one segment rather than arbitrarily divided between two physical pages, thus minimizing the amount of swapping that need be done while executing that subprogram. The location and size of all executing code segments is maintained in a *Code Segment Table* while the location and size of all associated data segments is maintained in a *Data Segment Table*. These tables are known to both hardware and software. Software uses them for dynamic memory management by the operating system. Hardware uses them to perform references and transfers between segments and to make sure that all segments required for current execution are present in main memory. Code segments may be up to 32,760 bytes in length. Data segments may be up to 65,528 bytes in length.

Segments are stored on disc and are brought into main memory only when needed. This design results in a virtual memory environment which appears to be many times larger than the maximum size of the physical main memory.

#### 2-5. REGISTERS

The architecture of the computer systems employs a set of 38 special purpose registers rather than a smaller set of general purpose registers. Each register is included in the system to efficiently perform a specific function.

All addressing of code and data is done relative to hardware address registers. Thus, by simply changing the base addresses in these registers, segments are dynamically relocatable in memory. The few instances where absolute addresses are required are privileged operations handled by the operating system. The registers are summarized in table 2-2.

Table 2-2. Machine Registers

| REGISTER                  | FUNCTION                                                  | REGISTER                   | FUNCTION                                  |

|---------------------------|-----------------------------------------------------------|----------------------------|-------------------------------------------|

| PB<br>P<br>PL             | Code Segment Pointers                                     | SWCH<br>PCLK               | Switch Register<br>Program Clock Register |

| PB-Bank<br>CIR<br>NIR     | Current Instruction Register<br>Next Instruction Register | SP0<br>SP1<br>SP2<br>SP3   | Scratch Pad, Flag, and                    |

| DL<br>DB<br>Q<br>SM<br>SR | Stack Pointers                                            | CTR ABS-Bank CPX1 CPX2 MOD | Interrupt Registers                       |

| Z<br>DB-Bank<br>S-Bank    |                                                           | IOA<br>IOD                 | ⊮O Registers                              |

| RA<br>RB<br>RC<br>RD      | Top of Stack Registers                                    | ACOR<br>DCOR<br>OPND       | Memory Address and Data<br>Registers      |

| X<br>STA                  | Index Register<br>Status Register                         | RAR<br>SAVE                | Firmware Address Registers                |

#### 2-6. INSTRUCTIONS

There are 209 unique instructions for the computer systems, including instructions for performing 4-word extended precision floating point and 28-digit packed decimal arithmetic. Many of these instructions have multiple actions, several addressing modes (DB-plus, S-minus, Q-plus, Q-minus, P-plus, and P-minus), indirect addressing, and/or indexing which give a high complexity-to-instruction ratio. Code compression is achieved through the use of no-address (stack) instructions which implicitly use the content of the stack registers as operands. All instructions except the 63 stack operations are in 16-bit format; the stack operations may be packed two per 16-bit word to further enhance the code density.

A complete set of arithmetic instructions provides integer (16-bit two's complement), double integer (32-bit two's complement), logical (16-bit positive integer), 28-digit packed decimal (BCD coded digits packed two per byte), floating-point (32 bits including a 23-bit precision mantissa), and extended precision floating-point (64 bits including a 55-bit precision mantissa) arithmetic.

Other instructions are designed to facilitate string processing, subprogram linkage, and loop control.

Certain special instructions are designated as *privileged*, meaning that they were designed specifically for use by the operating system. They may, however, be used by programs which the installation permits to run in privileged mode. Some of these special instructions, such as the DISP instruction for entry to the MPE Dispatcher, instructions for enabling/disabling process switching, and instructions for data transfers between data segments, contribute greatly to the efficiency of the operating system.

#### WARNING

The normal checks and limitations that apply to the standard users in MPE are bypassed in privileged mode. It is possible for a privileged mode program to destroy file integrity, including the MPE operating system software itself. Hewlett-Packard cannot be responsible for system integrity when programs written by users operate in the privileged mode.

#### 2-7. MICROCODE

The entire instruction set of the computer systems is in the form of microcoded operations in read-only memory. This microcode is executed by a microprocessor in response to machine instructions fetched into the CPU. By allowing microprogrammed hardware to execute certain repetitive functions, such as subprogram linkage, string processing, and buffer transfers (traditionally software-implemented), the amount of code and execution times are greatly reduced. In addition to the instruction set, other system functions have been microprogrammed, including the interrupt handler, a cold-start loader, the saving of critical environment information on power failure, automatic restart upon restoration of power, and a set of microdiagnostics that can be invoked from the front panel of the systems. All of these features are standard in the HP 3000 Series II and III.

The microprogrammed instructions routinely check for addressing bounds violations during execution and automatically interrupt to error handling routines if violations occur. These memory protection checks are usually overlapped with the operand fetch and therefore do not slow execution.

#### 2-8. MAIN MEMORY

The significant features of main memory are listed in table 2-3.

Table 2-3. Main Memory Features

- High-speed, semiconductor, random access memory

- Automatic fault detection and single bit fault correction

- Seven memory sizes ranging from 64K words to 256K words for Series II

and six memory sizes ranging from 128K words to 1024K words for

Series III

- Rechargeable battery packs to maintain memory data for a minimum of 40 minutes during power failure

The computer systems use high-speed, semiconductor, random access memory which provides single-bit fault correction and some double-bit fault detection. The parity system is retained with this feature, thus maintaining integrity over the various busses. Series II main memory is available in 64K, 96K, 128K, 160K, 192K, 224K, and 256K word configurations (K=1024). Series III main memory is available in 128K, 256K, 384K, 512K, 768K, and 1024K word configurations. Due to the modular design, any system can be easily expanded from one memory size to another. When there are more than 128K words of memory in the Series II system, the memory is divided into two modules; 128K words in the first module and the remainder in the second. When there are more than 512K words of memory in the Series III system, the memory is divided into two modules; 512K words in the first module and the remainder in the second. These modules can operate concurrently, which improves execution time. The word length transmitted over the bus is 17 bits — 16 bits of data (one word or two bytes), and one parity bit. For Series II memory modules, the word length is expanded to 21 bits — 16 bits of data and five bits for automatic fault detection and correction. For Series III memory modules, the word length is expanded to 22 bits — 16 bits of data and six check bits.

Operating power for the memory modules is supplied by rechargeable battery packs in the semiconductor memory power supplies. When the power supply input voltage is removed, battery power is available for a minimum of 40 minutes to maintain memory data.

The memory modules interface with other system modules by way of the Central Data Bus. The other system modules may request transfers of data to or from the memory modules on that bus. Communication between the various modules on the Central Data Bus is controlled by Module Control Units (MCU's), one for each module.

#### 2-9. INPUT/OUTPUT

All user access to input/output devices is by way of the device-independent MPE file system. All location of data, buffering, data transfers, and deblocking are handled automatically by MPE. When you ask to read a named file, you are only implicitly specifying the actual device and/or disc address of the file; the file system determines the explicit device and/or address for you and performs the read. At another level, when you ask the file system for a certain type of device by specifying a device class name (e.g., magnetic tape, line printer, etc.), the file system takes care of allocating an actual device for you. Users who must have actual contact with specific devices may address them directly. Below this simple, flexible interface is a powerful and carefully balanced hardware/software input/output system.

All devices can be operated concurrently (within system bandwidth). Peripherals that fail are taken off-line from the operating system by operator command.

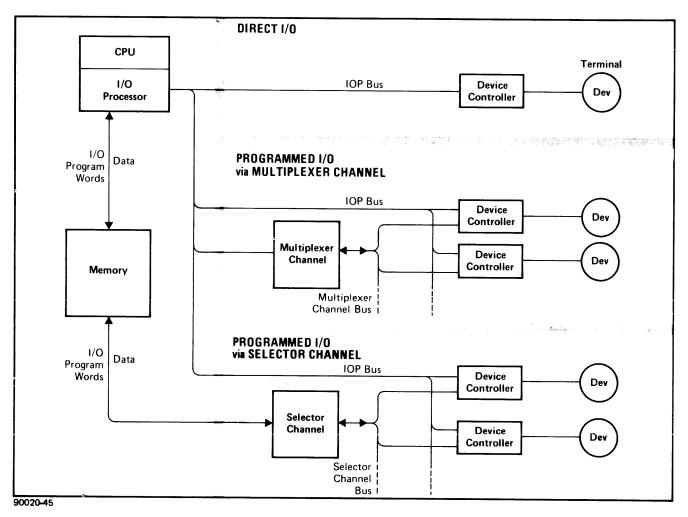

There are two distinct means of implementing I/O: direct I/O (DIO) and programmed I/O (SIO).

#### 2-10. **DIRECT I/O (DIO)**

Direct I/O allows for single-word transfers of data, status, or control information between a device connected to the IOP bus and the top of the user's data stack.

#### 2-11. PROGRAMMED I/O (SIO)

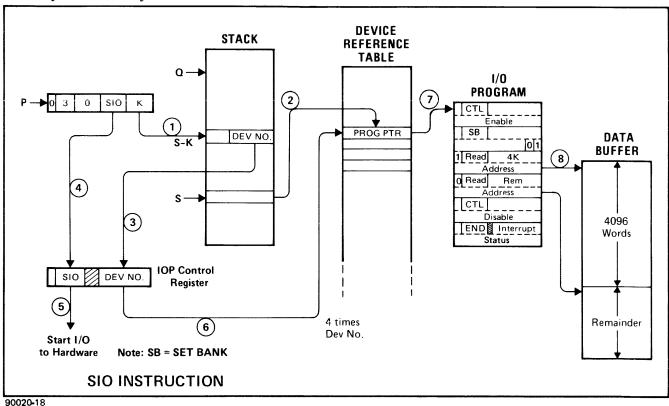

Programmed I/O can be used with devices on either the Selector Channel (high-speed devices) or the Multiplexer Channel (medium- to low-speed devices). With programmed I/O, the CPU simply issues a Start I/O (SIO) instruction to the Device Controller. The Device Controller, in turn, initiates the SIO program for the particular device which then runs under the control of the Selector Channel or under the control of the Multiplexer Channel and the IOP. The SIO program uses a unique set of commands (optimized for I/O operations) to transfer information between main memory and the external device. Both the Selector Channel and the Multiplexer Channel (via the IOP) have direct access to main memory. The SIO program and CPU processing run concurrently until the appropriate I/O command terminates the device transfer (this I/O command can also cause an interrupt signal to be sent to the CPU, thus informing the CPU that the I/O task is complete).

- **2-12. MULTIPLEXER CHANNEL.** Each Multiplexer Channel handles up to 16 Device Controllers. The Multiplexer Channel, in conjunction with the IOP, allows the Device Controllers connected to it to run concurrently, interleaving their transfers on a word-by-word basis. By multiplexing, cumulative data rates of up to 1,038,000 bytes per second (inbound) and 952,000 bytes per second (outbound) are possible. Data from the Multiplexer Channel is supplied directly to the IOP for transfer to main memory via the Central Data Bus.

- **2-13. SELECTOR CHANNEL.** Selector Channel data transfers bypass the IOP completely to provide transfer rates of up to 1.9 million bytes per second for a single device. All Selector Channel data transfers are performed in block mode and the data is supplied directly to main memory via the Central Data Bus.

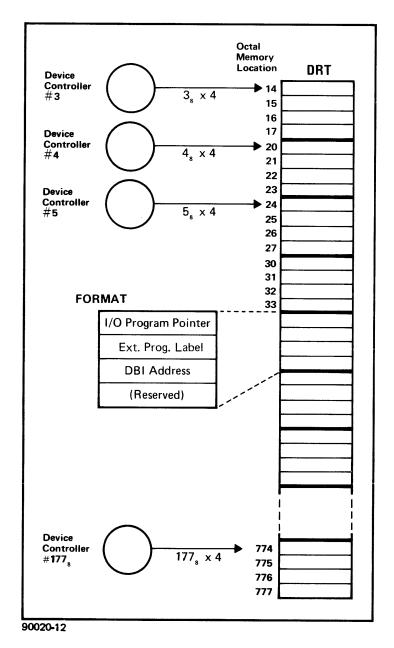

#### 2-14. DEVICE REFERENCE TABLE (DRT)

Device Controllers are identified by a device number which is used to access the Device Reference Table (DRT). The DRT is a table known to both hardware and software and it contains, among other things, a pointer to the start of the SIO program for each Device Controller. Since there can be a maximum of 125 entries in this table, the HP 3000 Series II may have up to 125 Device Controllers in its I/O system (the actual limitation is the 7-bit I/O address bus). Certain Device Controllers may control several devices. In such cases, each device attached to the controller is addressed separately using a unit number assigned when the device is installed.

#### 2-15. DATA SERVICE AND INTERRUPT PRIORITIES

In addition to a device number, there are two other characteristic numbers associated with each device. These are: data service priority and interrupt priority. Each of these values is completely independent of the others, and none is related to the physical location of devices or controllers. This mutual independence of characteristics provides the following advantages:

1. Device numbers can be assigned consecutively, starting at number 3 and proceeding up to the last assigned device in the system. When a new Device Controller is added, it is merely assigned the next higher available number (or any vacant number).

- 2. A new device added to the system may have its controller connected anywhere in the interrupt or data service priority chains, independent of physical location within the cabinet.

- 3. Since data service priority and interrupt priority are independent of each other, a device which requires a high data transfer rate but interrupts infrequently (such as a disc) may be assigned a high data service priority but a low interrupt priority. Conversely, a device which has a low data rate but has an important interrupt significance (such as an alarm condition) may be configured to a high interrupt priority but a low data service priority.

#### 2-16. INTERRUPT SYSTEM

The interrupt system provides for up to 125 external interrupt levels. When interrupts occur, the microprogrammed interrupt handler identifies each interrupt and grants control to the highest priority interrupt. Current operational status is saved by the microprogram, which then sets up the interrupt processing environment and transfers control to the interrupt routine.

External interrupt routines operate on a common stack (*Interrupt Control Stack*) which is known to both hardware and software. This feature permits nesting of interrupt routines in the case of multiple interrupts, thus allowing higher priority devices to interrupt lower priority devices.

The interrupt system also provides for 17 internal interrupts and traps including various user errors, system violations, hardware faults, power fail/restart, arithmetic errors and illegal use of instructions.

#### 2-17. PERIPHERALS

Mass storage devices consist of moving-head disc drives. These units provide storage capacities from 15 to 120 million bytes and data transfers of nearly one megabyte per second. On-line storage can be greatly expanded by adding additional disc drives to the system.

Low cost magnetic tape units are available in 9-channel models with recording densities of 800 or 1600 bpi.

Card readers are available that operate at 200 or 600 cards per minute.

An HP 2640B CRT Console is supplied as standard equipment for the system console.

Line printers are available with operating speeds of 165, 200, 240, 300, 436, 600, 925, or 1800 lines per minute. The various line printers provide 132-column print lines, using 64, 96, or 128 characters.

High-speed punched tape equipment is available that reads at 500 characters per second. Punched tape output is available as a separate unit operating at 75 characters per second. Paper, plastic, or mylar tape may be used with all units.

An interface is available which allows connection of a CalComp Series 500, 600, or 700 (excluding models 745 and 748) Plotter to the system.

Also available are an Asynchronous Terminal Controller and synchronous interfaces for data communications. There may be up to two Asynchronous Terminal Controllers connected to the system, each controlling up to 16 asynchronous terminals.

Hewlett-Packard furnishes available peripherals as complete I/O subsystems (including the device, interface, cables, etc.) to facilitate system expansion.

## THEORY OF OPERATION

#### 3-1. INTRODUCTION

This section contains a system-level description of the principles of operation for the HP 3000 Series II and III Computer Systems, a block-level and a functional theory of operation for the central processor unit (CPU), and additional CPU information such as architecture, data formats, and instruction formats. Since I/O and interrupts are extensive subjects, they are treated in separate sections. Brief descriptions of the following units are provided:

- Bus system

- Central Processor Unit (CPU)

- Module Control Unit (MCU)

- Typical memory module

- Input/Output Processor (IOP)

- Multiplexer (MUX) Channel

- Selector Channel

In addition, sequences of operations for CPU transfers to and from memory are given.

#### 3-2. SYSTEM-LEVEL DESCRIPTION

A block diagram of a computer system is shown in figure 3-1. The diagram does not show a complete system but a typical system containing a Multiplexer Channel and I/O interface and device (I/O subsystem). Direct I/O devices are not shown on the diagram, nor are additional Multiplexer Channels and their associated I/O subsystems. The following components, therefore, comprise the typical system as depicted:

- Memory subsystem.

- Central processor unit (CPU).

- Input/output processor (IOP).

- Multiplexer channel.

- I/O subsystem (interface PCA and I/O device), such as line printer or card reader.

The memory subsystem contains the I/O drivers that are executed by the CPU, I/O programs that are transferred by the IOP to the Multiplexer Channel, and the Device Reference Tables (DRT). The I/O drivers contain I/O instructions such as Read I/O (RIO), Write I/O (WIO), Start I/O (SIO), Test I/O (TIO), and Control I/O (CIO). The DRT begins in memory location octal 14 and contains a maximum of 125 four-word entries. Each table entry corresponds to a unique I/O device number. The first word of each entry contains the address of the next I/O program instruction for the device.

When the CPU executes an I/O instruction (TIO, CIO RIO, WIO, or SIO), direct commands are sent through the IOP and IOP bus to the addressed I/O subsystem. When the I/O subsystem accepts a direct command, it returns an acknowledge signal and executes the command.

If the CPU executes an SIO instruction, the IOP, in conjunction with the Multiplexer Channel, assumes control of the I/O subsystem and the CPU is free to continue processing other functions. The IOP transfers an I/O program, one instruction at a time, from the memory to the Multiplexer Channel. The Multiplexer Channel then controls the operation of the I/O subsystem.

Figure 3-1. Typical Computer System

#### 3-3. CPU GENERAL INFORMATION

#### 3-4. PIPELINE

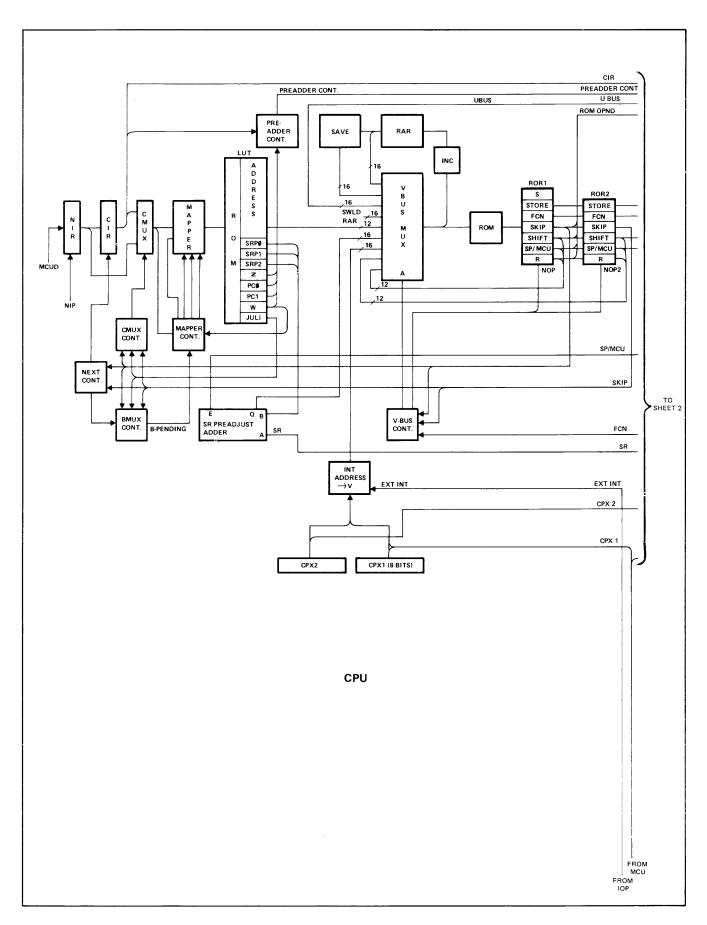

There are two pipelines in the CPU, the data pipeline and the microcode pipeline. The microcode pipeline consists of the V-Bus Mux, ROM, ROR1, and ROR2. The data pipeline consists of the store logic, registers, R- and S-Bus logic, arithmetic logic unit (ALU), shifter, and decimal corrector. Because the data pipeline is controlled by the microcode pipeline they will be discussed together.

The general operation of the data circuitry is to pick up two operands from two registers and input them to the ALU where a mathematical calculation can be accomplished. The result is then output on the T-Bus where the result can either be shifted (shift left 1, shift right 1, or swap bytes with or without clearing either byte) or decimal arithmetic corrected. This final result is then put on the U-Bus and stored in any one of the registers or input to the ALU a second time for further calculations. This entire operation is specified by one microcode instruction which, in effect, takes 175 nanoseconds to execute. To achieve this time, the computer systems use a data and microcode pipeline which have the end effect of one data calculation (stated another way, one microcode instruction) completed every clock cycle (175 nanoseconds).

Consider, for the moment, microcode instructions from consecutive ROM addresses being executed (no microcode jumps or interrupts). To give the data time to propagate through the entire data circuitry, the data is stepped through in two steps. The first step is to read the operands from the two source registers to the input lines for the R- and S-Bus Registers. The logic is given one clock cycle (175 nanoseconds) to accomplish this. The second step is for the data to go through the ALU, shifter or decimal corrector, and store logic and be on the input to the selected store register. The logic is given a second clock cycle to complete this operation.

To cause this to happen the microcode instruction must be executed in two steps. During the first step the instruction is held in ROR1 and effectively the only two fields being decoded during this clock cycle are the R- and S-Bus fields. These two fields cause the R- and S-Bus logic to select the correct registers for the two operands and gate the operations to the input of the R- and S-Bus registers.

The same clock pulse edge that clocks the operands into the R- and S-Bus registers also:

- Clocks the microcode instruction into ROR2

- Clocks the next microcode instruction into ROR1

- Clocks the final result of the previous microcode instruction into the register specified by its store field.

During the clock cycle period that the microcode instruction is held in ROR2, the *function* field of that instruction is specifying what calculation is to be accomplished by the ALU. The *shift* field of the instruction is specifying what the shifter/decimal corrector circuitry (depending on which of these two circuits is specified by the function field) is to be accomplishing. The *store* field is specifying to the store logic which register to select to gate the final result appearing on the U-Bus. On the next clock edge the now completed microcode instruction will be discarded by loading the next microcode instruction in ROR2. The final result of the instruction that was executed is clocked into the register specified by the store field of that instruction.

During the clock cycle, the instruction that progressed through the microcode pipeline is in ROR2. The R- and S-Bus fields of ROR (which contain the next instruction to be executed) are being decoded and the clock edge that moves this next instruction from ROR1 to ROR2 also clocks the new operands into the R- and S-Bus registers. Thus, it can be seen that on the leading edge of each clock the following operations occur simultaneously:

- A new microcode instruction is clocked into ROR1

- The instruction in ROR1 is clocked into ROR2

- The operands specified by the R- and S-Bus fields of the instruction that has been in ROR1 are clocked into the R- and S-Bus registers.

• The final result of the operands specified by the instruction that has been in ROR2 is clocked into the destination register specified by the store field of that instruction.

This gives the net result of one microcode instruction being executed per clock cycle and thus, one arithmetic calculation accomplished each clock cycle.

Two fields of the microcode instruction that have not been discussed are the *skip* and *special* fields. The *special* field controls the hardware to accomplish such operations as setting condition codes, popping the stack and incrementing and decrementing the SR register. For a full list of operations specified by this field and the results of these operations, refer to the *Microprogram Listings Manual*.

The *skip* field specifies a test condition such as the status of internal flags; the contents of the SR register as compared to zero, two, three, or four; and operand results that appear on the T-Bus as compared to zero, non-zero, odd, and even. For a complete list of test conditions that can be specified by this field refer to the Microprogram Listings Manual. When the condition being tested is true, the microcode instruction at the next ROM address is not executed. If the current instruction is a microcode jump instruction, however, the jump will be executed only if the condition being tested is true. In the case where the next microcode instruction is not to be executed, the skip condition is tested while the microcode instruction is in ROR2. This means that the instruction to be skipped is in ROR1. The clock pulse edge that moves the instruction to be skipped from ROR1 to ROR2 also sets the NOP2 flip-flop. This tells the decode circuitry to cause the ALU to add, the shift field will be forced to a pass function, and the store field will not be decoded. However, the operands specified by the R- and S-Bus fields of the instruction to be skipped were clocked into the R- and S-Bus registers so that the contents of the U-Bus at the end of the NOP clock cycle will be the sum of the contents of the source registers.

#### 3-5. DATA FORMATS

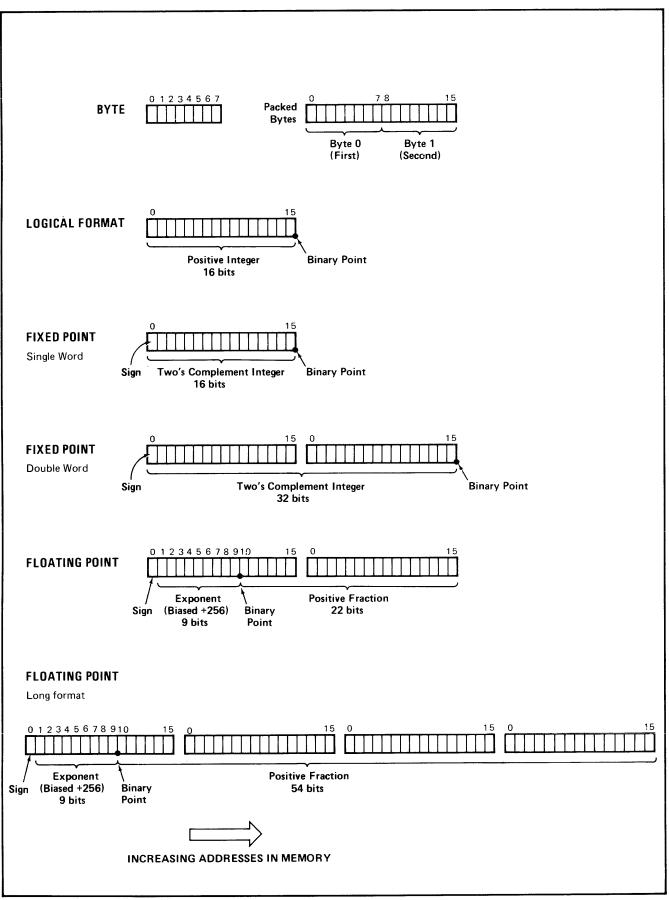

There are six different data formats (see figure 3-2) that are processable by the computer system's instruction set:

- Byte format

- Logical format

- Single-word, fixed-point format

- Double-word, fixed-point format

- Floating-point format

- Long floating-point format

#### NOTE

Definitions of the machine instructions referenced in the following paragraphs are contained in the *Machine Instruction Set Reference Manual*.

2152-31

Figure 3-2. Data Formats

- **3-6. BYTE FORMAT.** Bytes are processed by five of the move instructions (CMPB, MVB, MVBW, SCU, SCW), by two memory reference instructions (LDB and STB), and by the byte test instruction, BTST. Figure 3-2 shows the basic byte format, and the format for packing two bytes into a memory word. When bytes are processed by machine instructions, the bytes are individually addressed, fetched, and stored as though memory consisted of a number of eight-bit locations. (See paragraph 3-48, "Addressing Conventions".) When consecutive bytes are addressed in memory with ascending addresses, the high order byte (bits 0 through 7) of a packed word is accessed first and the low order byte (bits 8 though 15) second.

- 3-7. LOGICAL FORMAT. In logical arithmetic, a 16-bit data word is taken as a positive integer, with an assumed binary point to the right of bit 15 and an assumed + sign to the left of bit 0. The range of possible integers is from 0 through +65,535, decimal. The instruction set provides six instructions for logical arithmetic: LCMP, LADD, LSUB, LMPY, LDIV, and NOT. In logical addition and subtraction (LADD, LSUB), the only difference from integer adds and subtracts is that logical adds and subtracts do not set the Overflow indicator. All other respects are the same. For addition, the Carry bit is set if a carry out of the most significant bit occurs; if the carry out does not occur, the Carry bit is cleared. For subtraction (which is accomplished by two's complementing the subtraction and adding), Carry is set by a computation of A-B if B is less than A. Carry is cleared if B is greater than A. Thus if the Carry bit is set by LADD, the sum has exceeded + 65,535, and if the Carry bit fails to be set by LSUB, the difference is less than zero. In either case the result is modulo 217. For multiplication (LMPY), overflow cannot occur and the Carry bit has a special meaning (see the definition of the LMPY instruction in the Machine Instruction Set Reference Manual). For division (LDIV), the Overflow (instead of Carry) bit is used, and indicates that the quotient is too large to be represented in 16 bits. The quotient in this case will be modulo 216. When the Condition Code is set by a logical operator, it is set as if the result were a signed quantity. For example, CCL is set if bit 0 is a "1" (negative quantity).

- 3-8. SINGLE-WORD, FIXED-POINT FORMAT. The single-word, fixed-point format permits two's complement representation of both positive and negative integers. Bit 0 is a sign bit, and the remaining 15 bits define the quantity. The range of possible integers is 32,768 through + 32,767. Bit 0 is a "0" for positive numbers and a "1" for negative numbers. The binary point is assumed to be to the right of bit 15. The instruction set provides 24 instructions for single-length integer arithmetic. These include various modes of addition, subtraction, incrementing and decrementing. In addition and subtraction (ADD, SUB), conventional two's complement arithmetic is used. Both Overflow and Carry indicators are provided. Overflow indicates that the computation result required more than 15 bits for the quantity and consequently overflowed into bit 0, the sign bit. For multiplication and division, Carry is not used; Overflow indicates that the result cannot be contained in 15 bits plus sign.

- 3-9. **DOUBLE-WORD, FIXED-POINT FORMAT.** The double-word, fixed-point format is the same as the single-word format described in the preceding paragraph except that two words are linked together to form a 32-bit double-word quantity. Bit 0 of the most significant word is the sign bit. The range of possible integers is approximately 2 billion to + 2 billion. The instruction set provides eight instructions for double-word integer arithmetic: DCMP, DADD, DSUB, DMUL, DDIV, DNEG, MPYL, and DIVL. For multiplication with MPYL, overflow cannot occur and the Overflow bit is always cleared; Carry is used for a special purpose (see the definition of the multiply long instruction in the *Machine Instruction Set Reference Manual*). The operands for MPYL and the divisor and quotient for DIVL are single-word.

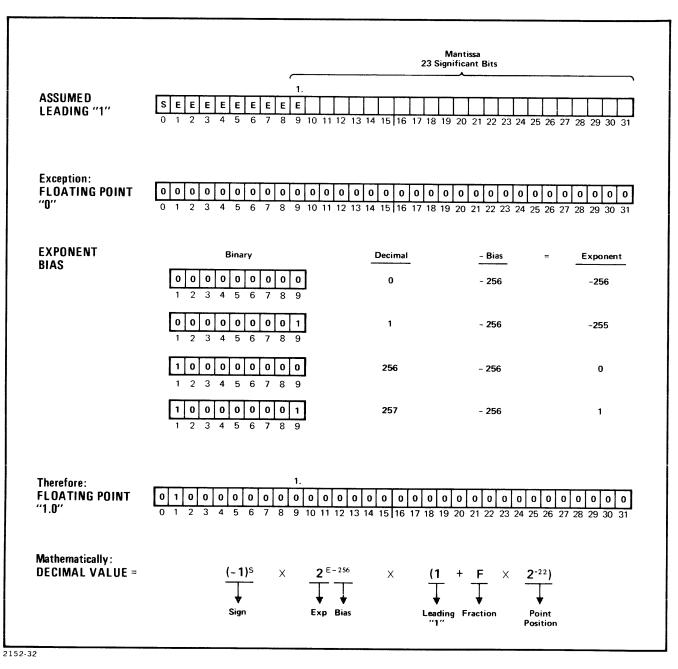

- 3-10. FLOATING-POINT FORMAT. In this format, bit 0 of the most significant word is the sign bit, bits 1 through 9 are used to express the exponent, and the remaining bits represent the fraction. The binary point is assumed to be to the left of bit 10.

The floating-point format used by the computer system has some special features which are illustrated separately in figure 3-3. The important distinction is the use of "sign with + magnitude" representation. In this type of representation, the fraction is always positive, with the sign bit indicating the sign of the number. There is an assumed "1" to the left of the binary point. Thus all floating-point numbers, by definition, exist in normalized form and the mantissa effectively has 23 bits. However, no bit is wasted on the leading "1", and all fraction bits are significant.

The exception to this convention is that zero is a word containing all "0"s. For this to be true, the assumed leading "1" is disregarded.

The exponent for floating-point numbers is biased by +256. Since the nine exponent bits give a range of 0 through 511, subtracting the bias yields an exponent range of -256 through +255. Figure 3-3 shows four examples of exponent calculation. Note that if bit 1 is a "0", exponents are negative; if bit 1 is a "1", exponents are positive or zero.

Thus the floating-point representation of 1.0 is a "1" in bit 1 and "0"s in all other bits. This indicates  $1 \times 2^{0}$ .

Figure 3-3 also shows the mathematical equation for computing the value of a floating-point number represented by the above conventions. (The exception: zero is defined as: S = E = F = 0.)

The instruction set provides ten floating-point instructions: FCMP, FADD, FSUB, FMPY, FDIV, FNEG, FLT, DFLT, FIXT, FIXR. Overflow indication is provided by the mathematical operations (FADD, FSUB, FMPY, FDIV), and by the fix instructions (FIXT, FIXR). The Carry indication is not used, except for a special purpose by the FIXT and FIXR instructions (see the definitions of these instructions in the *Machine Instruction Set Reference Manual*).

3-11. LONG FLOATING-POINT FORMAT. The long floating-point format is the same as the standard format described above except that 32 fraction bits are added to the right of the second word. With only this change, the information given in figure 3-3 is also valid for this format. (Note that the "point position" modifier in the equation becomes  $2^{-58}$  instead of  $2^{-22}$ .)

#### NOTE

In all cases where more than one word is used to represent a single unit of data, the words are stored in memory such that the least significant word is stored in the higher address location. For example, when pushing a double-word or triple-word quantity onto the stack, the least significant word will be on the TOS.

Figure 3-3. Floating Point Data Representation

#### 3-12. INSTRUCTION FORMATS

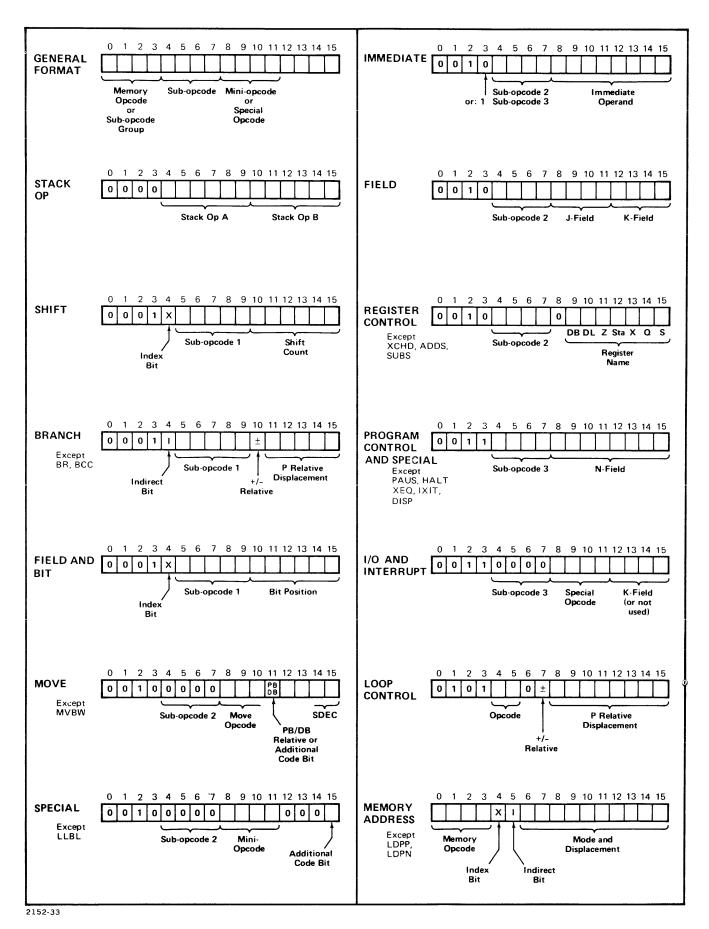

The instruction set has been designed for maximum efficiency of bit usage in the instruction word. Therefore, the instruction formats do not necessarily fall neatly into rigid field boundaries. There are 23 distinct formats used by the instruction set. Refer to the *Machine Instruction Reference Set Manual* for additional information.

In addition to the instruction formats, there are 13 instruction groups (see figure 3-4), as follows:

- Stack Op Format

- Shift Format

- Branch Format

- Bit Test Format

- Move Format

- Special Format

- Immediate Format

- Field Format

- Register Control Format

- Program Control Format

- I/O and Interrupt Format

- Loop Control Format

- Memory Address Format

- **3-13. GENERAL FORMAT.** The first format in figure 3-4 shows the general scheme for dividing the instruction word into code fields. Only the first field is rigidly adhered to. This field, bits 0 through 3, either defines a specific instruction code in the memory address group (or the "loop control" group), or else defines one of the sub-opcode groups. There are four sub-opcode groups: 1, 2, 3, and "stack ops". The field for sub-opcodes varies. For sub-opcodes 2 and 3, bits 4, 5, 6, and 7 are used, as shown. For sub-opcode group 1 codes, bits 5 through 9 are used, and for stack ops the remainder of the word is used. In some cases the sub-opcode will enable a third field, called a mini-opcode or a special opcode, in bits 8, 9, 10, and 11. The remainder of the word has a variety of special uses, and commonly is part of an "argument field".

- **3-14. STACK OP.** The stack op format is defined by four "0"s in the first four bits. The remaining 12 bits are divided into two fields; stack op A and stack op B. Either or both of these fields may contain any of the 63 stack op instruction codes. Execution sequence is from left to right (A first, then B). Interrupts may occur between the execution of A and B. Also note that indicators (Carry, Overflow, and Condition Code) are set by the last executed stack op. If using only one of the two stack op fields, it is more efficient to use stack op A since the hardware always looks ahead to see if stack op B is a NOP; this permits the hardware to ignore the second field, resulting in a time saving.

- **3-15. SHIFT.** The shift instruction group uses about half of the sub-opcode 1 group of codes. Sub-opcode group 1 is defined by 0001 in the first four bits. If bit 4, the Index bit, is a "1", the content of the index register is added to the shift count in bits 10 through 15 to specify the number of places each data bit is shifted. Bits 5 through 9 encode the specific shift instruction.

- 3-16. BRANCH. The branch instructions account for 11 of the sub-opcode 1 group of codes. In the branch instruction format, bit 4 is used as an indirect bit (indirect if bit 4 = "1"). Bits 5 though 9 encode the specific branch instruction. Bits 11 through 15 give a P-relative displacement (0 through 31), and bit 10 specifies whether the displacement is + or relative to P("0" = +, "1" = -).

Figure 3-4. Instruction Groups

- **3-17. B**racter TEST. The bit test instructions, also in sub-opcode group 1, use bits 5 through 9 to specify the instruction. Bits 10 through 15 specify a bit position in the TOS word for testing. The specified bit position is modified by the addition of the index register contents if the Index bit is set (bit 4 = "1").

- **3-18. MOVE.** The move group of instructions accounts for twelve of the codes specified by the sub-opcode 2 code 0000. Sub-opcode group 2 is defined by 0010 in the first four bits. Bits 8, 9, and 10 of the move instruction format encode the specific instruction. Bit 11 is used for some instructions to specify whether the source of the moved data is PB-relative (bit 11 = "0") or DB-relative (bit 11 = "1"). Bit 11 is also used in some cases as an additional code bit for specifying the instruction. Bits 12 and 13 are not used. Bits 14 and 15 are used to specify an S-decrement value to delete, if desired, the move parameters from the top of the stack.

- **3-19. SPECIAL.** The special group uses four mini-opcodes. The mini-opcode group is, like the moves, specified by the sub-opcode 2 code 0000. Bits 8 through 11, plus bit 15, encode the instruction. Bits 12, 13, and 14 are not used.

- **3-20. IMMEDIATE.** The immediate instruction group uses codes in both sub-opcode group 2 (coded 0010) and sub-opcode group 3 (coded 0011). Bits 4 through 7 encode the instruction and bits 8 through 15 are used for the immediate operand.

- **3-21. FIELD.** The format for field deposit and extract instructions is specified by two of the sub-opcode 2 group of codes. Bits 4 through 7 specify the instruction and the remaining eight bits are divided into a *J-field* and a *K-field*. The *J-field* specifies the starting bit number and the *K-field* specifies the number of bits.

- **3-22. REGISTER CONTROL.** The format for the register control instructions uses bits 9 through 15 to name a register and bits 4 through 7 in sub-opcode group 2 to specify the operation.

- **3-23. PROGRAM CONTROL.** The program control instructions account for four of the sub-opcode 3 codes. Sub-opcode 3 is specified by 0011 in the first four bits. The instruction is encoded by bits 4 through 7, and the *N-field* in bits 8 through 15 is used either for a PL- displacement (PCAL and SCAL) or to specify a number of parameters to be deleted on return from a procedure or subroutine (EXIT and SXIT).

- **3-24.** I/O AND INTERRUPT. The I/O and interrupt instructions use 11 of the special opcodes (bits 8 through 11) defined by the sub-opcode 3 code of 0000. The K-field, bits 12 through 15, is used by some of the instructions for an S-displacement to locate a device number given in the stack.

- **3-25. LOOP CONTROL.** The loop control instructions are defined by a special coding of bits 4, 5, and 6 for memory opcode 05 (which is otherwise defined as the STOR instruction). Bits 8 through 15 give a P-relative displacement for a branch address, and bit 7 specifies whether the displacement is + (= "0") or (= "1") relative to P.

- **3-26. MEMORY ADDRESS.** The memory address instruction format uses bits 0, 1, 2, and 3 to encode specific instructions. Bits 6 through 15 give both an addressing mode and a displacement. (Refer to paragraph 3-48, "Addressing Conventions".) Bit 5 is used to specify indirect addressing (= "1"), if desired, and bit 4 is used to specify indexing (= "1"), if desired. If both indirect addressing and indexing are specified, post-indexing will occur.

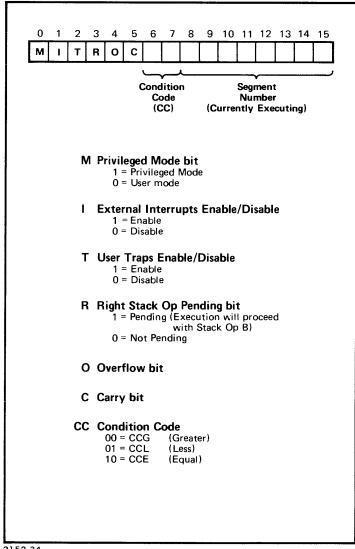

# 3-27. STATUS WORD FORMAT

There is a Status word for each code segment in the system. At all times, the Status word associated with a given process indicates the machine status following the execution of the most recent instruction in that segment. The status for the currently executing segment is resident in the status register, and is constantly being updated as each instruction is executed. For segments that are not current (suspended by either an interrupt or a procedure call), the Status word exists in a stack marker in a data stack. (See figure 4-11 in Section IV.)

Figure 3-5 shows the format for the Status word. Note that bits 8 through 15 indicate the segment number of the currently executing code segment (when the particular Status word is resident in the status register). Thus, when a Status word is pushed into a stack marker by an interrupt or procedure call, these bits identify the segment that is to be returned to when execution is resumed later.

The following descriptions of Status bits will assume that the Status word under discussion is resident in the status register. All references to "current" conditions can also be inferred as "then current" conditions in the case of suspended segments or procedures.

Bit 0, the Privileged Mode bit, indicates that the current segment is running either in privileged mode (if a "1") or user mode (if a "0"). The state of this bit cannot be changed by machine instructions while resident in the status register (except in privileged mode), and the PCAL, IXIT, and EXIT instructions include checks to prevent illegal mode changes by altering the non-current Status mode bits.

Bit 1 is used to enable or disable external interrupts. This bit also cannot be changed in user mode while current, and the EXIT instruction invokes a trap if a non-privileged user illegally altered the bit while non-current. The state of bit 1 may be changed only in privileged mode.

Bit 2 is used to enable or disable user traps. The state of this bit may be changed in any mode while current (SETR instruction) or non-current (state not affected by EXIT).

Bit 3 is normally used only by the hardware. The computer hardware will set this bit to a "1" if the right stack opcode (bits 10 through 15) contains a valid instruction other than NOP. The hardware requires this information in case an interrupt occurs between the execution of the left and right stack ops. The state of bit 3 cannot be changed in user mode while current.