# Logic MODEL 64600S Timing/Hardware Analyzer

**TECHNICAL DATA 1 SEP 83**

## Description

Model 64600S Logic Timing Analyzer subsystem offers powerful, highresolution, asynchronous analysis with extensive postprocessing capabilities in the HP 64000 Logic Development System. The 64600S, consisting of a control card (64601A) and acquisition card (64602A) with a probe, provides eight input channels; option 010 adds a second acquisition card and probe for a total of 16 channels. Many triggering modes allow precise positioning of the display window to locate timing margin and interaction problems. The analyzer's resources can be allocated to provide wide, fast, glitch, or dual-threshold measurements. Postprocessing adds another dimension to timing analysis with the ability to perform operations on acquired data, such as statistical analysis of raw timing data.

# **Features**

- Modular architecture allows optimum system configuration for each application environment.

- Sample rates from 2 Hz to 400 MHz for excellent resolution.

- Memory depth of 4060 samples in wide sample mode and 8140 samples in fast sample mode for long, time measurement windows.

- Glitch capture and trigger for glitches as narrow as 3 ns to quickly locate problem-causing transients.

- Dual-threshold mode provides threestate analysis for checking transition times, loading problems, and noise margins.

- Low interchannel skew, less than 1.5 ns within an 8-channel pod and less than 3.0 ns between pods, minimizing errors in timing measurements.

- Extensive selection of powerful triggering specifications allows fast and precise definition of pertinent timing measurements.

- Patterns that exceed or fall short of specified time duration

- Transition into, or out of, specified state

- Glitch

- Boolean NOT condition

- Intermediate signals between logic 1 and logic 0 voltages

- Combined level and transition or sequence triggering with the 16channel analyzer option

- Friendly user interface and symbolic triggering decrease learning time and increase convenience and simplicity of use

- Powerful interactive analysis when state/timing analyzers are installed streamlines integrating hardware and software

- Trigger the emulation subsystem from timing triggers for powerful interactive measurement techniques

- Postprocessing of collected data for correlation and off-line analysis frees analyzer for use in other measurements

- Compensated probing with convenient connection alternatives for quicker setup and reliable measurements

### Architecture

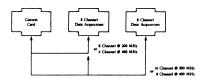

A 64000 development station with two available card slots can be configured, with Model 64600S, as an 8-channel timing analyzer (figure 1). Model 64600S Option 010 uses a third card slot to add a second data acquisition card to increase the subsystem input to 16 channels. Depending on measurement needs, and available card slots, timing analysis subsystems can be added to create a multiple analysis system in a single development station.

Figure 1. Timing Analysis subsystem combines a control card and a single data acquisition card for 8-channel input or a control card and two data acquisition cards for 16-channel input.

### Measurement Modes

Measurements with the Timing Analyzer are made in four different modes: wide sample, fast sample, glitch capture, or dual threshold. Each mode offers a different view into the system under test. Selection of the desired mode is under software control and is made using the softkeys.

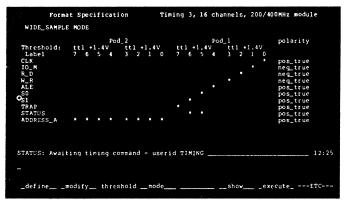

Figure 2. Wide Sample mode measurements are used for sampling rates from 2 Hz to 200 MHz.

Wide Sample Mode (figure 2) is used to gather 4060 bits of data from each of eight inputs on each probe pod at sample rates from 2Hz to 200 MHz (0.5 s to 5 ns periods). Depending on the analyzer configuration, there can be one or two probe pods with the ability to monitor 8 or 16 test points. Measurement resolution is 6.5 ns including 1.5 ns of skew and memory depth is 4060 samples.

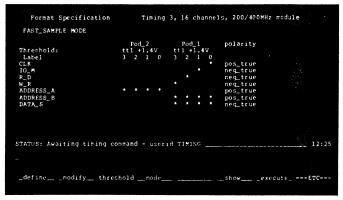

**Figure 3.** Fast Sample mode is used for sampling rates up to 400 MHz. Memory depth is 8140 samples.

Fast Sample Mode (figure 3) increases the time resolution by using a 2.5 ns sample period (400 MHz). This increase in resolution is accomplished by allocating two samplers to each input with a 2.5 ns time separation between the samplers. Memory depth is increased to 8140 samples. The number of inputs to each probe that can be sampled is reduced by half (four or eight channels). However, this fast sample rate is generally only needed to compare data on a small number of channels. Measurement resolution between channels within a single pod (one clock period plus skew) is 4 ns.

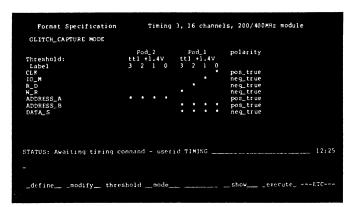

Figure 4. Glitches as narrow as 3 ns are detected and displayed with the Glitch Capture measurement mode.

Glitch Capture Mode (figure 4) captures and displays glitches as narrow as 3 ns on 4 or 8 channels, depending on the system configuration. The glitch capture mode monitors edges on incoming data while sampling data over a 2 Hz to 100 MHz range. When more than one edge occurs between two adjacent sample times, the event is recorded in a separate memory as a glitch. Since separate circuits and memory are used for detection and recording, glitches do not distort normal edge locations and glitches that are close to or on edges are captured and displayed separately.

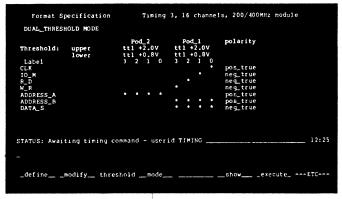

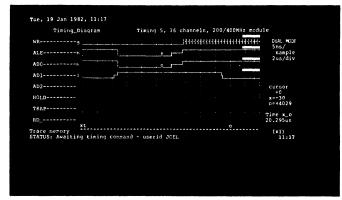

Figure 5. For Dual Threshold measurements, upper and lower thresholds are specified. This mode is valuable in analyzing tristating and rise and fall times.

Dual Threshold Mode (figure 5) offers more voltage resolution than is available with a basic timing analyzer measurement. This mode allows the specification of upper and lower thresholds for the signals being tested. Signals are displayed as the transition across the defined thresholds in three-level waveforms. By setting thresholds at a minimum acceptable high and maximum acceptable low, you can isolate marginal signal levels caused by excessive fan-out, defective components, weak pulldowns, etc.

In the dual threshold mode, marginal conditions are detected at sample rates from 2 Hz to 200 MHz. As with the preceding two modes, one-half of the available channels (4 or 8) can be monitored because twice the information is stored in memory for each input channel.

## Format Specification

Softkeys and symbolic triggering greatly simplify timing analysis by allowing the definition of measurement commands, specifications, displays, and recorded data in terms of signal names. Basic set-up is accomplished in the Format Specification where labels and names are assigned individual bits, input channels, or groups of channels. These assigned names are stored in a table and become part of the softkey command structure for building trace specifications.

The desired format display is called using softkeys (figures 2 through 5) which list the current data acquisition modes and the number of channels available. For example, the format specification in figure 3 is for a fast sample mode with a 16-channel system. Because system resources may be assigned as needed, the sampling rate is doubled to 400 MHz by halving the number of input channels. Therefore, the display shows eight channels, four for each of the two pods. Thresholds are defined on sets of four channels and displayed above the related channels. Logic polarity can be set for individual channels or labels. Labels, up to nine characters long, may be assigned to channels or group of channels (figure 5). In the Format Specification, labels may overlap: i.e., two or more labels may be assigned to the same input channel, allowing you to define labels for several different measurements.

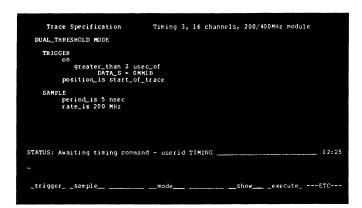

### Trace Specification

Sophisticated triggering allows you to take full advantage of the hardware analyzer's powerful measurement modes. These advanced triggering functions let you position the measurement window exactly where it is needed to solve difficult timing margin and system interaction problems. Complex measurements are set up easily using the softkeys with directed syntax.

There are five types of pattern triggering to qualify data capture in ways not possible with a simple occurrence trigger.

- Trigger upon entering a pattern

- Trigger upon leaving a pattern

- Trigger on greater than a specified duration of a pattern (including a middle level in the dual threshold mode)

- Trigger on less than a specified duration of a pattern (including a middle level in a dual threshold mode)

- Trigger on combinations of patterns and glitches.

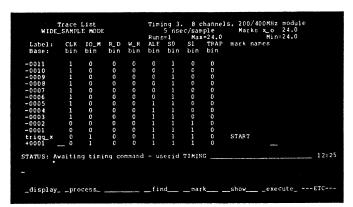

Pattern Triggering is used in all measurement modes; an example trace specification of a wide sample mode is shown in figure 6. A trigger pattern (which may be entered in binary, octal, decimal or hexadecimal) is specified for the selected label and the occurrence of that pattern triggers the analyzer to collect a trace. The pattern may also include "don't care" entries where information on that line is captured in relation to selected points on other input lines. The Boolean NOT condition of a pattern may also be used as a trigger.

Transition Triggering sets a trigger on the condition of a set of signals (or single signal) "entering" or "leaving" a defined pattern (figure 7).

Time Interval Triggering (figure 8) can be used in two ways: a trigger can be specified for a pattern that persists too long or a pattern that does not persist long enough to meet a specification.

Glitch Triggering on one or more channels can be specified as trigger points. The occurrence of a glitch may be ANDed with a pattern, transition, or time duration specification to allow isolation of a glitch in proximity to a critical operation.

Additional cross-pod triggering in a 16-channel subsystem allows conditional OR triggering, conditional duration triggering, and sequential triggering.

For example, it is possible to trigger on a pattern detected on one probe pod with its associated time

Figure 6. Pattern triggers can be specified for any of the four measurement modes. The patterns may be defined in binary, octal, decimal, or hexadecimal, and assigned to input lines or to a label.

Figure 7. Trigger conditions may be set for one or more signals entering or leaving a defined state in transition triggering.

duration specification followed by the pattern and a second time specification on the second probe. Another example is to set the first pod in a level-trigger mode (pattern plus duration), and the second pod in a transition-trigger mode where the trigger occurs when both conditions are met.

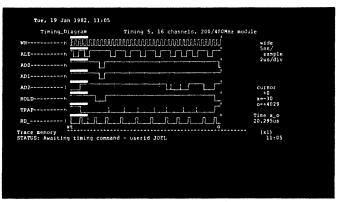

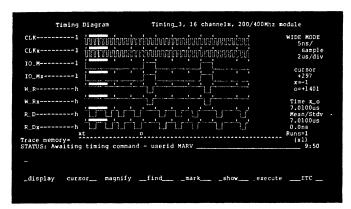

Measurement data can be displayed in the form of either a timing diagram or a trace list. The timing diagram presents up to sixteen channels of measurement data. Channel ordering and spacing can be set by entering labels or default channel numbers. By selecting appropriate labels, data can be presented in a form that gives a clear display of what has been measured (figure 9).

Magnification, time cursors, and memory indicators are important features for study of the timing diagram. Magnification along the time axis allows the fine detail of a portion of the timing diagram to be expanded. Expansion ranges are X1, X10, and X100. An intensified region that can be positioned over areas of interest defines the expansion window for the next higher magnification factor.

Figure 8. Time Interval trigger may be specified for a defined pattern that persists too long, or too short a time to meet specification.

Figure 9. An eight-channel display of a glitch capture mode. Displayed channels are arranged in order of interest for easy interpretation. Glitches are clearly displayed as dashed vertical lines and timing information is displayed directly on screen.

Multiple time cursors (x, o in figures 9 and 10) are available to measure durations of events or intervals between events. Graticules and time-per-division information provide another reference to the amount of time being displayed.

For easy identification, glitches are displayed as dashed vertical lines (figure 9). Note that glitches are also displayed when they occur on transitions. Measurements in the dual threshold mode are displayed as three-level waveforms where the midlevel is for the sample periods during which the signal level is between the defined maximum and minimum threshold levels (figure 10).

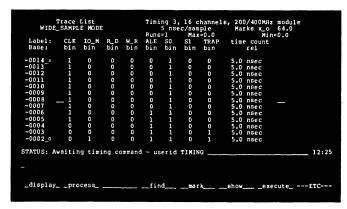

Captured timing information can be displayed in trace list form (figure 11). You can scroll through the 4060 word memory, or by using the "find" softkey, go directly to areas of interest. When the Glitch Capture mode is used, the state listing indicates where a glitch occured with a "g" adjacent to the line. An "m" in the state listing defines the middle threshold condition when using the dual threshold mode. The x and o indicate where the time measurement markers are positioned.

Figure 10. The three-level display for the Dual Threshold mode adds very powerful measurement capability to the 64600S for analyzing problems such as contention, loading, and transition time.

Figure 11. The x and o on the word listing of a timing trace indicate the start and stop points, respectively, for time measurement markers.

### **Interactive Measurements**

Simultaneous, interactive timing and state measurements are powerful techniques for logic analysis in a microprocessor system. These measurements are made with an HP 64000 station configured with both a Timing Analyzer (Model 64600S) and Logic State/Software Analyzer (Model 64620S) connected by an Intermodule Bus (IMB). Either subsystem can enable or trigger the other subsystem in several functional combinations:

State triggers state and timing.

Timing triggers state and timing.

State enables timing, timing triggers both.

Timing enables state, state enables timing.

State triggers state, state enables timing.

Timing triggers timing, timing enables state.

Feedback-restart loops, where state trigger enables state trace and simultaneously enables timing:

Timing then:

finds timing trigger and runs.

State then finds another condition, causing either

- (1) timing to retain data, or,

- (2) timing to reset and rerun, initiating a new trigger search.

Figure 12 is an example of enabling the timing analyzer by another subsystem in the station; i.e., "enable received" is the first condition for the trigger specification.

The IMB is not restricted to software analyzer/timing analyzer interfaces. It can be used to connect two or more timing analyzers, or two or more software analyzers, or analyzer and emulator analyzer subsystems. The emulator/analyzer combination is of particular value for developing multiprocessor-based systems.

One line of the IMB is a delay clock that can be used to define triggering and arming conditions in combination with delays. The display in figure 13 shows an "enable received" from another module; the timing module drives the trigger line 40 delay clocks after the specified trigger is satisfied.

Other forms of interactive measurements with external instruments are driven by the timing analyzer through a BNC connector on the rear panel of a 64000 station. Commonly, this mode can be used to trigger an oscilloscope, trigger a serial data analyzer, or provide a stimulus to user system hardware.

Figure 12. The statement "enable received" shows that this trace specification is to be initiated after another analysis subsystem sends a signal on the Intermodule Bus (IMB).

Figure 13. After a signal from another subsystem in the station is received via IMB, delay is added to the trace specifications of the Timing Analyzer.

Figure 14. Recalled data from a file named "Test 1" reformatted and displayed in trace list form can be analyzed at your convenience.

Figure 15. Automatic search through deep memory for a particular bit pattern simplifies analysis. The cursor "o" identifies the location in memory of the bit pattern of interest. If the pattern exists more than once in memory, it can be located again by executing the same command.

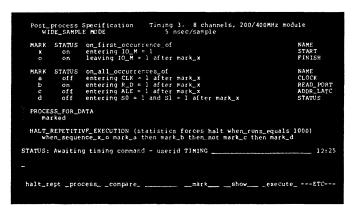

Figure 16. The postprocess specification displays the conditions that have been identified and marked along with other processing specifications. These specifications are displayed even when the conditions were setup in other specifications.

### **Postprocessing**

An extensive software package offers sophisticated, onboard, postprocessing capabilities of timing information. Postprocessing offers detailed analytical manipulation and statistical analysis of captured data without using external computers. There are seven major postprocessing functions:

- Storing and retrieving measurements

- Finding specific timing conditions

- Marking timing events

- Statistics on marked timing events

- Extended triggering conditions

- Processing asynchronous input as state listings

- Comparing stored and current measurements

## Storing and Retrieving Measurements

Measurement results can be stored on disc and recalled for display and analysis at a later, more convenient time. Recalled data can be operated on as though it were just acquired, which allows sequential measurements to be acquired and detailed analysis accomplished with the analyzer off-line of the target system. The ability to store measurements on flexible disc means that analysis can be accomplished on other 64000 stations that did not initially acquire the data. An example of a recalled measurement displayed in trace list form is in figure 14.

### Finding Specified Timing Conditions

Timing analyzers store data asynchronously without storage qualification, which means that a deep memory is important. With a memory depth of 4k bits, or 8k bits in fast sample mode, searching for a particular bit pattern 16-lines wide is not a trivial task. The postprocessing capability will automatically locate a particular machine state, each time that state occurred. The analyzer can also be directed to collect the occurrences of a bit pattern only when it exists longer or shorter than defined or, on entering or leaving a specified pattern. For example, figure 15 contains a trace list that was defined to locate a bit pattern upon entering CLK=1, IOM=0, etc. A cursor is placed at the desired location in either the trace list or timing diagram.

### **Marking Timing Events**

Timing events can be marked using x and o markers along with four other markers labeled a, b, c, and d. The x and o markers are used to set start and end points of interest. In all cases, the markers can be set using specifications rather than manual positioning (figure 16).

| WIDE_                       | SARPL       | E MUDE |       |                                         | Dung | Time x_o 3.0000 usec<br>00 usec Min=1.4950 usec |       |   |            |

|-----------------------------|-------------|--------|-------|-----------------------------------------|------|-------------------------------------------------|-------|---|------------|

| t abol -                    | CIV         | TO M   | p n   | w D                                     |      |                                                 |       |   | mark names |

| Base:                       | bin         |        |       | bin                                     |      |                                                 |       |   | mark names |

|                             |             |        |       |                                         |      |                                                 |       |   |            |

| -0011                       | 1 1 1 1 1 1 | 0      | 0     | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1    | 1                                               | 0     |   |            |

| -0010                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0009                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0008                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0007                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0006                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0005                       | î<br>1<br>1 | 0      | 0     | 1                                       | 1    | 1                                               | 0     | 1 |            |

| -0004                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 1     | 1 |            |

| -0003                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 1     | 1 |            |

| -0002                       | 1           | 0      | 0     | 1                                       | 1    | 1                                               | 1     | 0 |            |

| -0002<br>-0001_x<br>trigger | 1           | 1      | 0     | 1                                       | 1    | 1                                               | 1     | 0 | START      |

| trigger                     | 1           | 1      | 0     | 1                                       | 1    | 1                                               | 1     | 0 |            |

| +0001                       | _ 1         | 1      | 0     | 1                                       | 1    | 1                                               | 1     | 0 | arter      |

|                             |             |        |       |                                         |      |                                                 |       |   |            |

| TATUS: AV                   | aitin       | g timi | ng co | mmand                                   | - us | erid                                            | TIMIN | G | 12:        |

|                             |             |        |       |                                         |      |                                                 |       |   |            |

|                             |             |        |       |                                         |      |                                                 |       |   |            |

|                             |             |        |       |                                         |      |                                                 |       |   |            |

Figure 17. Status information for statistical measurements, number of runs, maximum and minimum times, etc., is displayed in the upper right of the display.

|     |                    |       | Timing 3. 8 channels, 200/400MHz module 5 nsec/sample Runs=10 Max=4.0 Min=4.0 |         |       |       |       |       |      |                                       |

|-----|--------------------|-------|-------------------------------------------------------------------------------|---------|-------|-------|-------|-------|------|---------------------------------------|

|     | WIDE               | SAMPL | E MODE                                                                        |         |       |       | 5 nse | c/sam |      |                                       |

| - 1 | Processe           | d     |                                                                               |         |       | Runs  | =10   | Max   | =4.0 | Min=4.0                               |

|     | Label:             | CLK   | IO M                                                                          | R D     | WR    | AL E  | 50    | Sl    | TRAP | mark names                            |

| -   | Base:              | bin   |                                                                               | bin     |       |       |       | bin   |      |                                       |

|     |                    |       |                                                                               |         |       |       |       |       |      |                                       |

|     | triqq_x            | 0     | 111111111111111111111111111111111111111                                       | 0       | 0     | 1     | 1     | 1     | 0    | START                                 |

|     | +0101_b            | _ 0   | 1                                                                             | 1       | 0     | 0     | 1     | 1     | C    | READ_PORT                             |

| -   | +0501_b            |       | 1                                                                             | 1       | 0     | 0     | 0     | 1     | 0    | READ_PORT                             |

|     | +0801 b            | 0     | 1                                                                             | 1       | 0     | 0     | 0     | 1     | 0    | READ_PORT                             |

| - 1 | +0801_b<br>+1101_b | ō     | ī                                                                             | í       | c     | 0     | 1     | ī     | 0    | READ_PORT                             |

|     | +1500_b            | Ó     | 1                                                                             | 1       | 0     | 0 0 0 | 6     | 1     | 0    | READ_PORT                             |

| 1   | +1800_b            | 0     | ī                                                                             | 1       | 0     | ò     | 0     | 1     | 0    | READ_PORT                             |

|     | +2100 b            | ō     | ī                                                                             | ī       | ō     | Ó     | 1     | 1     | 0    | READ_PORT                             |

|     | +2500_b            | 0     | 1                                                                             | 1       | 0     | ō     | 0     | 1     | 0    | READ_PORT                             |

|     | +2800_b            | Ó     | 1                                                                             | 1       | 0     | 0     | U     |       |      | READ_PORT                             |

|     | +3100 b            | 0     | i                                                                             | 1       | 0     | 0     | 1     | ī     | ٥    | READ_PORT                             |

| - 1 | +3500_b            |       | 1                                                                             | 1 1 1 1 | 0     | 0     | 0     | 1     | 0    | READ_PORT                             |

| 1   | +3800_b            | 8     | 1                                                                             | 1       | 0     | 0     | 0     | 1     | 0    | READ_PORT                             |

|     |                    |       |                                                                               |         |       |       |       |       |      |                                       |

| - 1 | STATUS: AV         | aitin | g timi                                                                        | ng co   | mmand | - us  | erid  | TIMIN | G    | 12:25                                 |

|     |                    |       |                                                                               |         |       |       |       |       |      |                                       |

| 1   | -                  |       |                                                                               |         |       |       |       |       |      |                                       |

| 1   |                    |       |                                                                               |         |       |       |       |       |      |                                       |

| 1   |                    |       |                                                                               |         |       |       |       |       |      |                                       |

| 1   | _display_          | _pro  | cess_                                                                         |         |       | fin   | d     | mar   | k    | _showexecuteETC                       |

|     |                    |       |                                                                               |         |       |       |       |       |      |                                       |

|     |                    |       | _                                                                             |         |       |       |       |       |      | ··· · · · · · · · · · · · · · · · · · |

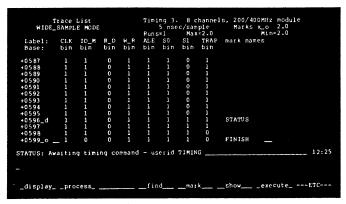

Figure 18. The number of times a particular bit pattern occurred, mark b, between the marks x<sub>o</sub> can be selected for display with extraneous information omitted. This makes it easier to characterize system operation under known conditions.

One example of the a, b, c, and d markers could be to indicate the bit pattern that identifies service interrupts. By marking the interrupt with an "a", it is much easier to locate the interrupts in a trace than searching for the handshake that defines the interrupt.

# Statistics on Marked Timing Events

The ability to define specific boundaries and parameters allows statistical measurements on those conditions. Statistical measurements can be run on time intervals or event counts by setting the analyzer for repetitive runs with the measurement made and accumulated on each run. A display of the maximum time, minimum time, mean time, standard deviation, and number of runs is updated with each run (figure 17). This measurement can be executed up to 1000 times to get a time interval measurement population for a circuit under test.

In addition to the time interval statistical measurements, the occurrences of other marked conditions within a defined time interval (x and o) can be counted. For

Figure 19. The mean and standard deviation can be automatically calculated and displayed to aid in system characterization.

Figure 20. A post processing specification can be set up to identify conditions that occur more times than expected by directing the system to perform repetitive measurements.

Figure 21. A repetitive measurement may be directed to halt execution when the time between two particular patterns in a program is too long. The captured data can then be analyzed to determine why the defined time span was exceeded.

example, to determine the number times an I/O port is read, that condition can be identified as mark "b" (figure 16). The specification is then set to display the number of times mark "b" occurred between the time interval (x and o) on each run, including the maximum

Figure 22. A repetitive measurement may be directed to halt repetitive execution when a defined sequence does not occur. The data acquired at that time can then be analyzed to determine what caused the program to change its sequence.

|   | WIDE SAMPLE MODE |             |                                         |       |         |      | Timing 3. 8 channels, 200/400MHz module<br>5 nsec/sample<br>Runs=15 Mean=3.9 Stdv=0.3 |             |   |                 |  |  |

|---|------------------|-------------|-----------------------------------------|-------|---------|------|---------------------------------------------------------------------------------------|-------------|---|-----------------|--|--|

|   |                  |             |                                         |       |         |      |                                                                                       |             |   | time count      |  |  |

|   | Base:            |             |                                         |       |         |      |                                                                                       |             |   | rel             |  |  |

|   |                  |             |                                         |       |         |      |                                                                                       |             |   | • •             |  |  |

|   | +0046            | _ 0         | 1                                       | 0     | 0       | ĭ    | 1                                                                                     | į.          |   | 0.0 nsec        |  |  |

|   | +0100 _          | _ 0         | ī                                       | 0     | 0       | Ü    | Ţ                                                                                     | 1           | Ü | 270.0 nsec      |  |  |

|   | +0446            | 1           | 1                                       | 0     | 0       | 1    | 0                                                                                     |             |   | 1.7300 usec     |  |  |

|   | +0499            | 0           | 1                                       | 0     | 0       | 0    | 0                                                                                     | 1           | 0 | 265.0 nsec      |  |  |

|   | +0746            | 1           | 1                                       | 0     | 0       | 1    | C                                                                                     | 1           | 0 |                 |  |  |

|   | +0799            | 0           | 1                                       | 0     | 0       |      | 0                                                                                     | 1           | 0 | 265.0 nsec      |  |  |

|   | +1045            | 1<br>0<br>1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0     | 0       | 1    | 1                                                                                     | 1           | 0 | 1.2300 usec     |  |  |

|   | +1099            | 0           | 1                                       | 0     | 0       | 0    | 1                                                                                     | 1           | 0 | 270.0 nsec      |  |  |

|   | +1445            | 1           | 1                                       | 0     | 0       | 1    | 0                                                                                     | 1           | C | 1.7300 usec     |  |  |

|   | +1499            | 0           | 1                                       | 0     | 0       | 0    | 0                                                                                     | 1           | 0 | 270.0 nsec      |  |  |

|   | +1745            | ī           | ī                                       | ō     | ō       | 1    | 0                                                                                     | 1           | 0 | 1.2300 usec     |  |  |

|   | +1799            | ō           | i                                       | ō     | Ó       | 0    | 0                                                                                     | 1           | 0 | 270.0 nsec      |  |  |

|   | +2045            | ī           | ī                                       | ō     | 0       | 1    |                                                                                       | 1 1 1 1     | 0 | 1.2300 usec     |  |  |

|   | Thereto has      | -: -: -     |                                         |       |         |      |                                                                                       | TT 14 1 1 1 | ~ | 12:             |  |  |

| • | IAIUS: AW        | a1 C1 II    | g timi                                  | ng co | нашанте | - us | erio                                                                                  | TIMIN       |   | 12:             |  |  |

|   |                  |             |                                         |       |         |      |                                                                                       |             |   |                 |  |  |

|   |                  |             |                                         |       |         |      |                                                                                       |             |   |                 |  |  |

|   |                  |             |                                         |       |         |      |                                                                                       |             |   |                 |  |  |

|   |                  |             |                                         |       |         |      |                                                                                       |             |   | showexecuteETC- |  |  |

Figure 23. Stored information can be postprocessed to display only the data that existed longer than a defined time period. This automatically provides only the information of interest by removing transition and duplicate states.

| WIDE      |        |                                         | Timing 3. 8 channels, 200/400MHz module 5 nsec/sample |          |             |       |          |          |               |     |

|-----------|--------|-----------------------------------------|-------------------------------------------------------|----------|-------------|-------|----------|----------|---------------|-----|

| Process   |        |                                         | Dune                                                  | -15      | Mos         | D-3 0 | Stdv=0.3 | C+du=0 3 |               |     |

|           |        | IO_M                                    |                                                       |          |             |       |          |          | time count    |     |

| Label:    |        |                                         |                                                       |          |             |       |          |          |               |     |

| Base:     | bin    | bin                                     | bin                                                   | bin      | bin         | 51 N  | bin      | bin      | rel           |     |

| -0003     | 1      | 0                                       | 0                                                     | 0        | 1           | 1     | 0        | 0        | 0.0 nsec      |     |

| +0045     | ō      |                                         | o                                                     | 0        | 1           | 1     | 1        | 0        | 240.0 nsec    |     |

| +0097     |        | ī                                       | 0                                                     | 0        | 0           | 1     | 1        | 0        | 260.0 nsec    |     |

| +0145     | ñ      | ī                                       | 1                                                     | 0        | G           | ī     | 1        | 0        | 240.0 nsec    |     |

| +0197     | 0      | ĭ                                       | ī                                                     | ō        | 0           | ī     | ī        | ō        | 260.0 nsec    |     |

| +0245     | ô      | 111111111111111111111111111111111111111 | 1<br>1<br>1                                           | ŏ        | ō           | ī     | ī        | ŏ        | 240.0 nsec    |     |

| +0297     | ~ i    | ī                                       | ō                                                     | ō        |             | ī     | ī        | 0        | 260.0 nsec    |     |

| +0345     | õ      | î                                       | ŏ                                                     | ō        | 0<br>1<br>1 | 1     | ī        | ō        | 240.0 nsec    |     |

| +0397     | ĭ      | ī                                       | ŏ                                                     | ŏ        | ī           | ī     | ī        | ŏ        | 260.0 nsec    |     |

| +0445     | ō      | ī                                       | ŏ                                                     | ō        | ī           | ō     |          | ō        | 240.0 nsec    |     |

| +0497     | ĭ      | i                                       | ŏ                                                     | ŏ        | ō           | Ö     | ī        | ō        | 260.0 nsec    |     |

| +0545     | ō      | î                                       | ĭ                                                     | ō        | ō           | ō     |          |          | 240.0 nsec    |     |

| +0597     | 1      | ī                                       | ī                                                     | ŏ        |             | ŏ     | ĩ        |          | 260.0 nsec    |     |

| TATIC. A  |        | a timi                                  | na co                                                 | mmand    | - 446       | orid  | TIMIN    | c        | 1             | ٠.  |

| 31A103. A | TED CY | 9 11111                                 | ing co                                                | mana inc | 0.5         | erra  |          |          |               | 'n, |

|           |        |                                         |                                                       |          |             |       |          |          |               |     |

|           |        |                                         |                                                       |          |             |       |          |          |               |     |

|           |        |                                         |                                                       |          |             |       |          |          |               |     |

| display   | DIO    | CRSS                                    |                                                       |          | 110         | C     | mar      | K        | showexecuteET | 35  |

Figure 24. Data can be processed relative to another signal which provides information synchronous to that signal. At a 200 MHz sample rate, this effectively gives you 66 MHz synchronous analysis.

and minimum port accesses (figure 18). In addition to the maximum and minimum occurrences, the mean and standard deviation of the marks for the defined number of runs can also be displayed (figure 19).

| WIDE_SAMPLE MODE<br>Processed                                                                                                    |        |        |       |       |      |      |                                         |   | Stdv=0.3                    |  |

|----------------------------------------------------------------------------------------------------------------------------------|--------|--------|-------|-------|------|------|-----------------------------------------|---|-----------------------------|--|

|                                                                                                                                  |        |        |       |       |      |      |                                         |   | mark names                  |  |

| Base:                                                                                                                            | bin    | bin    | bin   | bin   |      |      |                                         |   |                             |  |

| trigg_x<br>+0046_a<br>+0101_b<br>+0146_a<br>+0246_a<br>+0346_a<br>+0396_c<br>+0446_a<br>+0500_b<br>+0546_a<br>+0646_a<br>+0646_a | 0      | 1      | 0     |       | 1    | 1    | 1                                       | 0 | START<br>CLOCK<br>READ_PORT |  |

| +0046_a                                                                                                                          | 1      | 1      | 0     |       | 1    | 1    | 1                                       | 0 | CLOCK                       |  |

| +0101_b                                                                                                                          | О      | 1      | 1     |       | 0    |      | 1                                       | 0 | READ. PORT                  |  |

| +0146_a                                                                                                                          | 1      | 1      | 1     | 0     | 0    | 1    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0 | CLOCK                       |  |

| +0246_a                                                                                                                          |        | 1      | 1     | 0     | 0    | 1    | 1                                       | 0 | CLOCK                       |  |

| +0346_a                                                                                                                          |        | 1      | 0     |       | 0    | 1    | 1                                       | 0 | CFOCK                       |  |

| +0396_c                                                                                                                          | 1      | 1      | 0     | 0     | 0    | 1    | 1                                       | 0 | ADDR_LATC                   |  |

| +0446_a                                                                                                                          | _ 1    | 1      | 0     | 0     | 1    | 0    | 1                                       | 0 | CLOCK                       |  |

| +0500_b                                                                                                                          | 0      | 1      | 1     |       | 0    | 0    | 1                                       | 0 | READ_PORT                   |  |

| +0546_a                                                                                                                          | 1      | 1      | 1     |       | 0    | О    |                                         | 0 | CLOCK                       |  |

| +0646_a                                                                                                                          | 1      | 1      | 1     | 0     | 0    | 0    | 1                                       | 0 | CLOCK                       |  |

| +0696_c                                                                                                                          | 1      | 1      | 0     |       |      | 0    | 1                                       | 0 | ADDR_LATC                   |  |

| +0746_a                                                                                                                          | 1      | 1      | 0     |       |      | 0    | 1                                       | 0 | CLOCK                       |  |

| STATUS: AN                                                                                                                       | vaitin | g timi | ng co | rmand | - us | erid | TIMIN                                   | G | 12:                         |  |

Figure 25. Data in memory can be processed so that only the marked conditions (a,b,c) are displayed to eliminate long searches through memory.

### Extended Triggering

Extended triggering adds another capability to the analyzer. The analyzer can be directed to make repetitive measurements until the number of marks exceed a given amount and then stop the measurement (figure 20). This capability allows the analyzer to capture the data present when there are more mark conditions than expected.

The analyzer can also be directed to trigger when the time interval from point x to point o exceeds a specified time duration (figure 21). This makes it very easy to monitor system operation over many runs and captures any timing violations.

Another powerful aspect of extended triggering is the ability to define sequences as part of a trigger. Up to five marks can be used in a trigger sequence. The mark sequence is set up in the Post\_process Specification (figure 22) and when the sequence is detected during a run, it triggers the analyzer to hold the captured information.

# Processing Timing Display for State Listing

The ability to translate a timing display to a state listing allows additional measurements to be performed on stored information. Data may be processed for conditions or patterns lasting longer than a specified time, removing transition or duplicate states not needed for analysis (figure 23). Additionally, stored data can be processed in relation to a sampled signal that can be defined as a clock with the data synchronized and displayed in relation to the clock (figure 24).

Data can also be processed for all marked conditions. This allows the study of only the areas of interest without extraneous information (figure 25).

Figure 26. Stored timing diagrams can be recalled for comparison to current measurements. The stored waveforms are labeled with an x for easy differentiation from the current waveform.

### Comparing Stored and Current Measurements

There are times when it is useful to visually compare stored and current timing waveforms. The postprocessing specification allows designation of a compare file where a timing waveform can be stored, another measurement executed, and then both displayed simulataneously (figure 26). Displayed waveforms are differentiated by labeling the compare file waveform with an x.

# **Probes**

The timing probe consists of a cable connected to the acquisition board in the station, a detachable probe pod (figure 27) containing a hybrid circuit with an active comparator, and eight detachable coaxial probe inputs. The probe leads are similar to HP 10017A miniature oscilloscope probes which allows all the accessories (tips, clips, etc.) to be used with the timing probe. A Model 10211A dual-in-line package clip, supplied with the timing probe, allows easy connection to most 0.3, 0.4, 0.6, and 0.9-inch wide IC packages. The 10211A clip is also stackable, end-to-end, to allow probing all pins on 40 of 60-lead packages.

Probe inputs are compensated to provide the comparator in the pod a high fidelity reproduction of the signal at the probe tip, avoiding the ringing and resulting uncertainty associated with opern-wire probes and fast edges. The input impedance at the tip is  $100k\Omega$  in parallel with 6 pF capacitance.

Figure 27. A variety of probe tips and clips simplify connection of the timing analyzer to your system. The miniprobe tip on the timing probe can be used with a variety of accessories including pincer tips, ground leads, and IC test clips.

The probe has two comparison thresholds, one for channels 0 through 3 and one for channels 4 through 7. The thresholds are set by software from -10 V to +10 V in 0.1 V steps. The dynamic range of the probe is specified as  $\pm 10 \text{ V}$ . Exceeding this value, as might happen with CMOS circuits using 15 V supplies, causes less than 1 ns of additional skew as the input clamps are activated, and essentially no change in loading.

# Hard Copy Output

Printouts of timing displays for records are available by adding a Model 64050A Graphics Output Card. HP-)B compatible printers can be used directly without the need for an additional external interface. The graphics output card transmits both text and graphics.

Graphics information is transmitted using raster graphics consisting of 720 dots scanned left to right in 90 8-bit bytes. Model 2631G Option 200 Graphics Printer and Model 2673A Intelligent Graphics Printer are compatible with the 64050A graphics output card. For more information about the compatibility of other BP graphics printers, please consult with your local HP Instrumentation Field Engineer.

# **Specifications**

### RESOLUTION

Total Skew from Probe Tip: within pod,  $\pm 1.5$  ns; pod to pod:  $\pm 3.0$  ns. These specifications are true for input signal, VH=-1.0 V, VL=-1.6 V, VTH at 1.3 V, slew rate 0.25 V/ns; for skew specifications under other conditions, refer to the Operating Manual.

Sample Rate Accuracy: approx ±0.002%, rate adjustable from 2 Hz to 400 MHz (in fast-sample modes) in a 1, 2, 4 sequence.

### MEMORY DEPTH

Wide Sample, Glitch, and Dual Threshold Modes: 4k. Fast Sample Mode: 8k.

### PROBE CHARACTERISTICS

Input Z:  $100k\Omega \pm 2\%$  shunted by <6 pF.

Dynamic Range: ±10 V. Maximum Input: ±40 V.

Threshold Accuracy:  $\pm 50$  mV or  $\pm 2\%$ , whichever

is greater.

Hysteresis: approx 50 mV.

Drive Requirements

Minimum input amplitude: 600 mV, P-P. Minimum input overdrive: 200 mV or 25% of input amplitude, whichever is greater Minimum pulse width: 3 ns at threshold.

### Glitch Mode

Maximum Sample Rate: 100 MHz. Minimum Width: 3 ns at threshold. Maximum Width: sample period less 4 ns.

### TRIGGERING

Time Duration Accuracy: ±(20% + 2ns). Minimum Width for "Narrower than"

Trigger: approx 6 ns.

Minimum Width for Transition Trigger: approx 6 ns.

Displayed Position Accuracy: ±4 samples; ±8 samples in Fast Sample mode.

Delay from Input to External BNC Drive: approx 60 ns.

Delay from Input to Internal IMB Drive: approx 55 ns.

Dead Time for Restart Measurement Reset: approx 50 ns + the time required to fill the memory with the selected amount of pretrigger information.

Time Duration Restart: for accurate restarts, pattern must go false for at least 1.5 times the selected time duration.

### **BNC DRIVE**

**Output Signal Swing in Transition**

Trigger Mode

Amplitude: approx 2.0 V with 50Ωload.

Width at 50%: approx 10 ns.

Output Signal Swing in "Width Greater than" Trigger Mode

Amplitude: approx 2.5 V.

Width: input trigger width less selected duration.

Output Signal Swing in "Width Less-than"

Trigger Mode

Amplitude: same as in transition trigger mode. Width: same as in transition trigger mode.

Position: occurs when trigger pattern

disappears before selected duration times out.

#### Power Requirements

Current Required for Timing Analysis Subsystem Components

Note: Refer to the HP 64000 Logic Development System Selection and Configuration Guide for power requirements. The chapter on Configuration Requirements contains data for calculating current required for subsystems to be installed, and currents available in development stations. Model 64100A Development Station, serial number prefix 2136 and below, can be retrofitted to accommodate new subsystems if required. Please contact your Hewlett-Packard Logic Systems Field Engineer or System Engineer for further information.

### DEVELOPMENT STATION

SUPPLY +5V +12V +17V -3.25V -5.2V

TIMING MODILLE

Timing Control 1.4A - - 1.5A 1.7A

Timing Acquisition 3.6A - - 2.5A 0.8A

Timing Probe 0.04A - - - 0.24A

# **ENVIRONMENTAL**

Conforms to environmental specifications of Model 64100A or 64110A Development Station

#### **ACCESSORIES SUPPLIED**

Model 64600S: one Model 64601A Control Card, one Model 64602A Data Acquisition Card, one Model 64604A Timing Probe, one 2-position 8-channel Timing Bus Cable (P/N 8120-4094), two coaxial cables (P/N 64600-61601), one Timing Cable (P/N 64604-61601), Operating Software on flexible disc, and Operating and Service Manuals.

Model 64600S Opt 010: one Model 64601A control card, two Model 64602A Data Acquisition Cards, two Model 64604A Timing Probes, one 3-position 16-channel Timing Bus Cable (P/N 8120-4093), four coaxial cables (P/N 64600-61601), two Timing Cables (P/N 64604-61601), Operating Software on flexible disc, and Operating and Service Manuals.

The following accessories are supplied with each Model 64604A Timing Probe: eight ground leads (P/N10006-61301), eight probe holders (P/N 10017-62302), eight IC probe tip adapters (P/N 10017-69501), eight timing probe leads (P/N 64604-62101), eight split rings (P/N 64604-23201), one Model 10211A 20-pin dual in-line package clip with one interconnecting ground wire (P/N 10211-61601) and two insulated circuit interface pins and one Model 10024A IC Test Clip with four insulated circuit interface pins.

# ORDERING INFORMATION

Model 64600\$ 8-channel Timing Analyzer

with one timing probe

Model 64600S Opt 010: 16-channel Timing Analyzer

with two timing probes

### COMPONENTS

Note: Order replacement items from the following listing.

Model 64601A timing analysis control card

Model 64602A 8-channel timing card

Model 64604A 8-channel timing probe

Model 64963A 2-position timing bus cable

Model 64963A Opt 010: 3-position timing bus cable

Model 64050A Graphics Output Card

Note: When expanding an existing station to include another measurement system, IMB cables must be ordered separately. IMB cables are supplied on initial order of a complete development station with two or more subsystems.

Model 64964A 2-position IMB cable

Model 64964A Opt 001: 4-position IMB cable Model 64964A Opt 002: 6-position IMB cable

Model 64964A Opt 003: 8-position IMB cable