HP64000 Logic Development System

### CERTIFICATION

Hewlett-Packard Company certifies that this product met its published specifications at the time of shipment from the factory. Hewlett-Packard further certifies that its calibration measurements are traceable to the United States National Bureau of Standards, to the extent allowed by the Bureau's calibration facility, and to the calibration facilities of other International Standards Organization members.

### WARRANTY

This Hewlett-Packard system product is warranted against defects in materials and workmanship for a period of 90 days from date of installation. During the warranty period, HP will, at its options, either repair or replace products which prove to be defective.

Warranty service of this product will be performed at Buyer's facility at no charge within HP service travel areas. Outside HP service travel areas, warranty service will be performed at Buyer's facility only upon HP's prior agreement and Buyer shall pay HP's round trip travel expenses. In all other cases, products must be returned to a service facility designated by HP.

For products returned to HP for warranty service. Buyer shall prepay shipping charges to HP and HP shall pay shipping charges to return the product to Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to HP from another country.

HP warrants that its software and firmware designated by HP for use with an instrument will execute its programming instructions when properly installed on that instrument. HP does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. HP SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. HP SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

### **ASSISTANCE**

Product maintenance agreements and other customer assistance agreements are available for Hewlett-Packard products.

For any assistance, contact your nearest Hewlett-Packard Sales and Service Office.

BUSINESS REPLY CARD

FIRST CLASS PERMIT NO. 1303 COLORADO SPRINGS, COLORADO

POSTAGE WILL BE PAID BY ADDRESSEE

## **HEWLETT-PACKARD**

**Logic Product Support Dept.** Attn: Technical Publications Manager Centennial Annex - D2 P.O. Box 617 Colorado Springs, Colorado 80901-0617

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

FOLD HERE

Your cooperation in completing and returning this form will be greatly appreciated. Thank you.

## **READER COMMENT SHEET**

Operating Manual, Model 64650A General Purpose Preprocessor 64650-90902, October 1983

Your comments are important to us. Please answer this questionaire and return it to us. Circle the number that best describes your answer in questions 1 through 7. Thank you.

| 1.                                                  | The information in this book is complete:      |   |   |   |   |   |                         |  |  |  |

|-----------------------------------------------------|------------------------------------------------|---|---|---|---|---|-------------------------|--|--|--|

|                                                     | Doesn't cover enough (what more do you need?)  | 1 | 2 | 3 | 4 | 5 | Covers everything       |  |  |  |

| 2.                                                  | The information in this book is accurate:      |   |   |   |   |   |                         |  |  |  |

|                                                     | Too many errors                                | 1 | 2 | 3 | 4 | 5 | Exactly right           |  |  |  |

| 3.                                                  | The information in this book is easy to find:  |   |   |   |   |   |                         |  |  |  |

|                                                     | I can't find things I need                     | 1 | 2 | 3 | 4 | 5 | I can find info quickly |  |  |  |

| 4.                                                  | 4. The Index and Table of Contents are useful: |   |   |   |   |   |                         |  |  |  |

|                                                     | Helpful                                        | 1 | 2 | 3 | 4 | 5 | Missing or inadequate   |  |  |  |

| 5. What about the "how-to" procedures and examples: |                                                |   |   |   |   |   |                         |  |  |  |

|                                                     | No help                                        | 1 | 2 | 3 | 4 | 5 | Very helpful            |  |  |  |

|                                                     | Too many now                                   | 1 | 2 | 3 | 4 | 5 | I'd like more           |  |  |  |

| 6.                                                  | What about the writing style:                  |   |   |   |   |   |                         |  |  |  |

|                                                     | Confusing                                      | 1 | 2 | 3 | 4 | 5 | Clear                   |  |  |  |

| 7.                                                  | What about organization of the book:           |   |   |   |   |   |                         |  |  |  |

|                                                     | Poor order                                     | 1 | 2 | 3 | 4 | 5 | Good order              |  |  |  |

| 8.                                                  | What about the size of the book:               |   |   |   |   |   |                         |  |  |  |

|                                                     | too big/small                                  | 1 | 2 | 3 | 4 | 5 | Right size              |  |  |  |

| С                                                   | omments:                                       |   |   |   |   |   |                         |  |  |  |

|                                                     |                                                |   |   |   |   |   |                         |  |  |  |

| _                                                   |                                                |   |   |   |   |   |                         |  |  |  |

| Pa                                                  | articular pages with errors?                   |   |   |   |   |   |                         |  |  |  |

| Jo                                                  | ame (optional):bb title:                       |   |   |   | - |   |                         |  |  |  |

| Company:Address:                                    |                                                |   |   |   |   |   |                         |  |  |  |

Note: If mailed outside U.S.A., place card in envelope. Use address shown on other side of this card.

## General Purpose Preprocessor

© HEWLETT-PACKARD COMPANY 1982 LOGIC SYSTEMS DIVISION COLORADO SPRINGS, COLORADO, U. S. A.

ALL RIGHTS RESERVED

## **Printing History**

Each new edition of this manual incorporates all material updated since the previous edition. Manual change sheets are issued between editions, allowing you to correct or insert information in the current edition.

The part number on the back cover changes only when each new edition is published. Minor corrections or additions may be made as the manual is reprinted between editions.

First Printing......February 1982 (P/N 64650-90902) Reprinted.....October, 1983

## TABLE OF CONTENTS

| Chapter 1                          |

|------------------------------------|

| General Information1-1             |

| Chapter 2                          |

| Installation2-1                    |

| Chapter 3                          |

| Interface Module3-1                |

| Chapter 4                          |

| Preprocessor Operation3-1          |

| LIST OF ILLUSTRATIONS              |

| LIST OF ILLUSTRATIONS              |

| 4-1. Preprocessor Block Diagram4-2 |

## **General Information**

The HP 64650A General Purpose Preprocessor is a versatile probe for the HP 64620S Logic State/Software Analyzer. The preprocessor is designed to operate with a variety of processor specific interface modules, providing a flexible and convenient probing capability.

By utilizing the appropriate interface module and control and data acquisition circuit boards, state/software analysis can be performed on both 8-bit and 16-bit microprocessor target systems and target system buses.

As many as 60 data channels are available for use in target system analysis. Channels not used for target system analysis are available for general purpose probing of the target system.

The components needed within the station mainframe for state/software analysis are:

- a. 64621A Logic State Analyzer Control circuit board.

- b. 64622A 40 Channel data acquisition circuit board.

- c. 64623A 20 Channel data acquisition circuit board.

### Installation

Connection of the preprocessor to the state/software analyzer is made through 50-conductor cables. The cables are plugged into the top cover of the preprocessor.

One of the cables is dedicated to transferring clock signals, and the remaining cables transfer address, data, and status signals. One clock cable and two data cables (40 data channels) are used for 8-bit target system analysis; one clock cable and three data cables (60 data channels) are used for 16-bit target system analysis.

Initializing the system is accomplished by loading software, normally provided on a mini-floppy disc, into the system.

In order to accommodate the specific target system to the state/software analyzer, an interface module must be installed in the preprocessor pod. The interface module must match the target system microprocessor.

If the analysis system is to be user defined, a special interface module must be installed in the preprocessor. The interface module must be designed and configured by the user. Software, including format specification, status mapping, and machine code inverse assembly, must also be user generated.

For additional information refer to the "Software Updating Procedure" found in the 64000 System Software Reference Manual.

### Interface Module

The interface module consists of microprocessor specific software and hardware.

The software includes a configuration file, composed of the trace specification (usually of a default type), the format specification and symbol maps, and an inverse assembler that will display trace information in the target system mnemonics.

The interface module has circuitry in it that provides the connection to the target system, and typically consists of buffers to reduce the loading of the target system. Some interface modules have circuitry to generate additional status, to dequeue instruction flow, or have other functions unique to that microprocessor. In addition, microprocessors that have multiplexed buses are demultiplexed so that all information about a bus cycle is contained in one analysis state.

Connection of the interface module to the target system is accomplished by removing the target system microprocessor, plugging the cable socket into the target system socket, and then installing the microprocessor into the cable socket.

## **Preprocessor Operation**

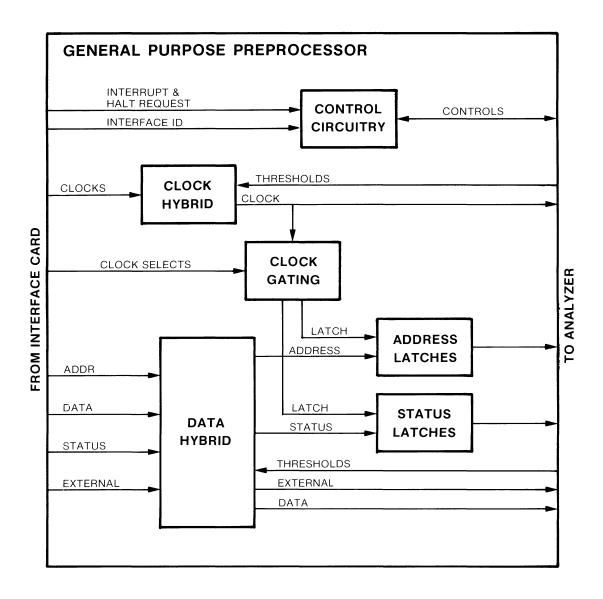

The preprocessor can accommodate 68 channels of information. These 68 channels are divided into five groups. There are 24 channels in the address group, 16 channels in the data group, 12 channels in the user definable group, 8 channels in the status group, and 8 channels in the clock group. The address and status groups are latched and can be sampled at any clock time; the user-definable and data groups are not latched and must be sampled at master clock time. Clocks 2 & 3 capture the address group, clocks 4 & 5 capture the status group, and the remaining clocks, 0, 1, 6, and 7, are connected directly to the analyzer. See Figure 4-1 for the preprocessor block diagram.

The interface module determines how the four clocks (two clocks for the status group, two clocks for the address group) latch target system information. The active polarity of each clock is selectable, or the clock may be disabled. The two clocks for each group are OR'ed. All of these options are defined when a using a microprocessor specific interface module.

The preprocessor and interface module identify themselves to the state/software analyzer so that proper configuration and inverse assembly software will be used.

Data collected from the target system is processed and displayed on the station CRT at the operators request. Control of data collection and mode of display is exercised through state/software analyzer softkey commands.

The preprocessor performs in a manner that is transparent to the target system unless a stimulus or halt signal is utilized. These signals are controlled in the state/software analyzer trace specification.

The STIMULUS line can be defined to become active at trigger, window, or sequencer events. The HALT line can be activated at trace point or at measurement complete. The trigger, window, or sequencer events can be assigned to drive BNC Port 1 with the STIMULUS line; the trace point or measurement complete can be assigned to drive BNC Port 2 with the HALT line. The signals at the BNC ports are not, however, controlled by the preprocessor.

The method by which the preprocessor utilizes the STIMULUS line is defined by the preprocessor-specification. The way in which it is connected to the target system is dependent upon the interface module being used.

Figure 4-1. Preprocessor Block Diagram

The following sequence will cause the HALT line to exercise control of the target system after trace completion:

- a. The desired trace must be correctly defined in the trace specification.

- b. The HALT line must be defined active, in the trace\_specification, at measurement complete. The syntax is:

assert halt line on measurement complete

The HALT line is then connected to the target system through the interface module, and the target system will be halted at measurement\_complete. The HALT line will remain active until the start of a new trace. The HALT line is an active low open collector output.

The STIMULUS line can be controlled with several variations in the preprocessor specification. The choices are as follows:

- a. Disabled.

- b. Enabled.

- 1. single mode.

- a) pulse mode (5 microsecond pulse).

- b) handshake mode (remains active once asserted).

- 2. repetitive mode.

- a) pulse mode (5 microsecond pulse).

- b) handshake mode (remains active until acknowledged).

The preprocessor will block the signal if STIMULUS is disabled in the preprocessor\_specification even though the STIMULUS line is defined in the trace specification and becomes active during a trace.

The STIMULUS line, when enabled in the single mode, will be asserted only once during a trace, even if the conditions on which it is asserted become true more than once during the trace. The STIMULUS line, when enabled in the repetitive mode, will be asserted at each occurrence during the trace. The STIMULUS signal at the BNC port will in either case, single or repetitive, be asserted at each occurrence during the trace.

A choice of signal type, either pulsed or handshake, can be made for single or repetitive mode. The pulsed type is a signal approximately five microseconds in duration. The signal, in handshake mode, will remain asserted until acknowledged by the target system through the ACK line in the interface module. The ACK line is an active low input; the STIMULUS line is an active low open collector output.

There are nine INPUT/OUTPUT wires that can be plugged into the preprocessor endcap. (These wires and grabbers are supplied with the 64650A Preprocessor.) These lines are routed to the interface circuit board through connector J5 and are available at the wire wrap pins labeled INPUT/OUTPUT. The label on the preprocessor endcap can be written on with a standard lead pencil to identify the wires.