HP 13255

PROCESSOR (8008-1) MODULE

Manual Part No. 13255-91008

PRINTED

AUG-01-76

# DATA TERMINAL TECHNICAL INFORMATION

## 1.0 INTRODUCTION.

This module uses the Intel 8008-1 microprocessor as the central controlling element in the terminal. The processor fetches and executes instructions which are stored in the terminal's memory modules.

#### 2.0 OPERATING PARAMETERS.

A summary of operating parameters for the Processor (8008-1) Module is contained in tables 1.0 through 5.1.

Table 1.0 Physical Parameters

| Part   Number | Nomenclature                | Size (L x W x D)  <br>  +/-0.100 Inches | (Pounds) |

|---------------|-----------------------------|-----------------------------------------|----------|

| 02640-60008   | Processor (8008-1) PCA      | 1 12.5 x 4.0 x 0.5                      | 6.31     |

|               |                             |                                         |          |

| <br>          |                             | <br>                                    |          |

|               | Number of Backplane Slots R | Reguired: 1                             |          |

HP 13255

PROCESSOR (8008-1) MODULE

Manual Part No. 13255-91008

PRINTED

AUG-01-76

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

Copyright c 1976 by HEWLETT-PACKARD COMPANY

NOTE: This document is part of the 264XX DATA TERMINAL product series Technical Information Package (HP 13255).

#### 1.0 INTRODUCTION.

This module uses the Intel 8008-1 microprocessor as the central controlling element in the terminal. The processor fetches and executes instructions which are stored in the terminal's memory modules.

## 2.0 OPERATING PARAMETERS.

A summary of operating parameters for the Processor (8008-1) Module is contained in tables 1.0 through 5.1.

Table 1.0 Physical Parameters

| Part  <br>  Number                   | Nomenclature              | Size (L x W x D)<br>  +/-0.100 Inches | (Pounds)        |

|--------------------------------------|---------------------------|---------------------------------------|-----------------|

| 02640-60008                          | Processor (8008-1) PCA    | 12.5 x 4.0 x 0.5                      | 6.31            |

| !<br>!                               |                           |                                       | †.   1<br>†   1 |

| † !<br>• !                           |                           | -  <br>                               | ! !<br>! !      |

| ==================================== | Number of Backplane Slots | Reguired: 1                           |                 |

Table 2.0 Reliability and Environmental Information

| Restrictions: Type tested at product level   | ==<br>!<br>!<br>! | Environmental: | (      | X ) F          | IP Class | в (                                    | ) Other: | ************* | :======<br> <br> <br> <br> |

|----------------------------------------------|-------------------|----------------|--------|----------------|----------|----------------------------------------|----------|---------------|----------------------------|

| <br> -==================================     | <br> <br> <br>    | Restrictions:  | Type   | tested         | lat pro  | duct level                             |          |               | 1<br> <br> <br> <br> <br>  |

| (dilute nace: 1.005 (percent per 1000 hours) | <br>  =<br> <br>  |                | ailure | =====<br>Rate: | 1.00     | ====================================== | per 1000 | hours)        | <br> -=====:<br> <br>      |

Table 3.0 Power Supply and Clock Requirements - Measured (At +/-5% Unless Otherwise Specified)

| +5 Volt Supply                        | +12 Volt Supply  | -12 Volt Supply      | -42 Volt Supply |

|---------------------------------------|------------------|----------------------|-----------------|

| e 400 mA                              | @ 005 mA         | @ 075 mA             | e mA            |

|                                       |                  | <b>,</b> 2, 2, 1,,,, |                 |

| i i                                   | 1                |                      | NOT APPLICABLE  |

| = = = = = = = = = = = = = = = = = = = |                  |                      |                 |

| 1 115 vol                             | ts ac            | 220 vc               | olts ac         |

| 9                                     | A                | ę.                   | A               |

| NOT APPL                              | TCABLE           | NOT APE              | PLICABLE        |

| ===================================== |                  |                      |                 |

| )<br>                                 | Clock Frequency: | 4.915 MHz +/- 0.1    | !               |

|                                       |                  |                      |                 |

Table 4.0 Connector Information

| Table 4.0 Connector Information          |                                         |                                         |  |  |  |  |

|------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|

| Connector                                | Signal                                  | Signal                                  |  |  |  |  |

| l and Pin No.                            |                                         | Description                             |  |  |  |  |

| lessessessessessessessessessessessessess | 1====================================== | bescription                             |  |  |  |  |

| P1, Pin 1                                | +5V                                     | +5 Volt Power Supply                    |  |  |  |  |

| 1 F1, F111 1                             | 1 +34                                   | to voit tower amphity                   |  |  |  |  |

| -2                                       | GND                                     | Ground Common Return (Power and Signal) |  |  |  |  |

| -3                                       | SYS CLK                                 | 4.915 MHz System Clock                  |  |  |  |  |

| -4                                       | -12V                                    | -12 Volt Power Supply                   |  |  |  |  |

| -5                                       | ADDR0                                   | Negative True, Address Bit 0            |  |  |  |  |

| -6                                       | ADDR1                                   | Negative True, Address Bit 1            |  |  |  |  |

| -7                                       | ADDR2                                   | Negative True, Address Bit 2            |  |  |  |  |

| -8                                       | ADDR3                                   | Negative True, Address Bit 3            |  |  |  |  |

| -9                                       | ADDR4                                   | Negative True, Address Bit 4            |  |  |  |  |

| -10                                      | ADDR5                                   | Negative True, Address Bit 5            |  |  |  |  |

| -11                                      | ADDR6                                   | Negative True, Address Bit 6            |  |  |  |  |

| -12                                      | ADDR7                                   | Negative True, Address Bit 7            |  |  |  |  |

| -13                                      | ADDR8                                   | Negative True, Address Bit 8            |  |  |  |  |

| -14                                      | ADDR9                                   | Negative True, Address Bit 9            |  |  |  |  |

| -15                                      | ADDR10                                  | Negative True, Address Bit 10           |  |  |  |  |

| -16                                      | ADDR11                                  | Negative True, Address Bit 11           |  |  |  |  |

| -17                                      | ADDR12                                  | Negative True, Address Bit 12           |  |  |  |  |

| -18                                      | ADDR13                                  | Negative True, Address Bit 13           |  |  |  |  |

| -19                                      | ¥<br>4                                  | l} Not                                  |  |  |  |  |

| -20                                      |                                         | I) Used                                 |  |  |  |  |

| -20                                      | 1                                       | 1                                       |  |  |  |  |

| -21                                      | 1/0                                     | Negative True, Input Output/Memory      |  |  |  |  |

| -22                                      | GND                                     | Ground Common Return (Power and Signal) |  |  |  |  |

|                                          |                                         | •                                       |  |  |  |  |

Table 4.0 Connector Information (Cont'd.)

|             | Table 4.0 ( | Connector Information (Cont'd.)                   |

|-------------|-------------|---------------------------------------------------|

| Connector   | Signal      | Signal                                            |

| and Pin No. |             | Description                                       |

| P1, Pin A   | GND         | Ground Common Return (Power and Signal)           |

| -B          |             | <br> } Not                                        |

| 1<br>1 -D   | PWR ON      | System Power On                                   |

| -E          | BUS0        | Negative True, Data Bus Bit 0                     |

| -F          | BUS1        | Negative True, Data Bus Bit 1                     |

| ,<br>1 -н   | BUS2        | Negative True, Data Bus Bit 2                     |

| -J          | BUS3        | Negative True, Data Bus Bit 3                     |

| Н           | BUS4        | Negative True, Data Bus Bit 4                     |

| i -t        | BUS5        | Negative True, Data Bus Bit 5                     |

| IM          | RUS6        | Negative True, Data Bus Bit 6                     |

| ! -N        | BUS7        | Negative True, Data Bus Bit 7                     |

| -P          | WRITE<br>I  | Negative True, Write/Read Type Cycle              |

| -R<br>  -S  | <br>        | } Not<br> } Used                                  |

| -т          | PRIOR IN    | Bus Controller Priority In                        |

| -U          | PRTOR OUT   | Bus Controller Priority Out                       |

| -v          | PROC ACTVE  | Negative True, Processor Active (Controlling Bus) |

| -W          | BUSY        | Negative True, Bus Currently Busy (Not Available) |

| X           | RUN         | Allow Processor to Access Bus                     |

| Y           | REO         | Negative True, Reguest (Bus Data Currently Valid) |

| -z          |             | Negative True, Data Comm Interrupt Request        |

Table 5.0 Module Bus Pin Functions for Input Instructions

|                                                    | 1          | l Bus         |

|----------------------------------------------------|------------|---------------|

| Module Address: $(ADDR 11,10,9,4) = (M2,M1,M0,A4)$ | Value      | Signal        |

|                                                    |            |               |

| During an input instruction the upper byte of      | 0          | ADDR 15       |

| the address register is loaded with the input      | i ŏ        | I ADDR 14     |

| instruction and the lower byte, with the contents  | iŏ         | ADDR 13       |

| of the accumulator just prior to the execution     | iö         | ADDR 12       |

| of the input instruction. ADDR4 is controlled      | 1 M2       | ADDR 12       |

| by bit 4 of the accumulator. The other seven       | I M1       | ADDR 10       |

|                                                    | I MO       |               |

| bits may be used by the IO module for strobes.     |            | ADDR 9        |

|                                                    | 1 1        | I ADDR 8      |

|                                                    | I A7       | I ADDR 7      |

|                                                    | I A6       | I ADDR 6      |

|                                                    | I A5       | ADDR 5        |

|                                                    | I A4       | I ADDR 4      |

|                                                    | 1 A3       | I ADDR 3      |

|                                                    | 1 A2       | I ADDR 2      |

|                                                    | I A1       | I ADDR 1      |

|                                                    | I AO       | ADDR 0        |

| M2 M1 M0 = Module address from input               | ======     | ========      |

| instruction (TNP)                                  | 1 B7       | I BUS 7       |

|                                                    | I 86       | BUS 6         |

| A4 = Controlled by program; set by contents of     | l B5       | I BUS 5       |

| bit 4 in accumulator before input                  | 1 B4       | I BUS 4       |

| instruction is executed                            | 1 B3       | BUS 3         |

|                                                    | 1 B2       | BUS 2         |

| A4 = 1 Modules 1,3,5,7,11,13,15,17 (octal)         | 1 B1       | BUS 1         |

|                                                    | I B0       | BUS 0         |

| A4 = 0 Modules 0,2,4,6,10,12,14,16 (octal)         | =======    |               |

| At - V Rougles Vyly Pyry Pyriy to Coccary          | I 1=T.ogic | al 1=Bus Low  |

|                                                    |            | al 0=Bus High |

|                                                    | IX=Don't   |               |

| Data Bus Bit Interpretation:                       |            |               |

| pala bus bit interpretation:                       |            |               |

|                                                    |            |               |

| B7 - B0 Data from terminal bus is loaded           |            |               |

| into accumulator (A-register)                      |            |               |

| •                                                  |            |               |

| of microprocessor.                                 |            |               |

|                                                    |            |               |

|                                                    |            |               |

|                                                    |            |               |

|                                                    |            |               |

| ,                                                  |            |               |

|                                                    |            |               |

|                                                    |            |               |

Table 5.1 Module Bus Pin Functions for Output Instructions

|                                                    | ========= | :==========                             |

|----------------------------------------------------|-----------|-----------------------------------------|

| 1                                                  | 1 .       | Bus I                                   |

| Module Address: $(ADDR 11,10,9,4) = (M2,M1,M0,R1)$ | Value     | Signal                                  |

|                                                    | ======    | ======================================= |

| During an output instruction, the instruction      | 1 0       | ADDR 15 I                               |

| I itself is loaded into the upper and lower bytes  | 1 0       | ADDR 14                                 |

| of the address register. The format of the         | 1 R2      | ADDR 13 I                               |

| output instruction determines which module is      | R1        | ADDR 12                                 |

| l addressed.                                       | I M2      | ADDR 11 I                               |

| 1                                                  | M1        | ADDR 10 I                               |

|                                                    | I MO      | ADDR 9 I                                |

|                                                    | 1 1       | ADDR 8 1                                |

|                                                    | 1 0       | ADDR 7 I                                |

|                                                    | 1 1       | ADDR 6 I                                |

| M2 M1 M0 = Module address from output              | I R2      | ADDR 5 I                                |

| instruction (OUT)                                  | I R1      | ADDR 4 I                                |

|                                                    | M2        | ADDR 3 I                                |

|                                                    | I M1      | ADDR 2 I                                |

| R2 R1 - 01 ADDR4 = 1 Modules $1,3,5,7,11,13$ ,     | I MO      | ADDR 1                                  |

| 11) 15,17 (octal)                                  | 1 1       | ADDR 0 I                                |

|                                                    | ======    | ========                                |

|                                                    | B7        | BUS 7                                   |

| R2 R1 - 10) ADDR4 = 0 Modules $0,2,4,6,10,12$ ,    | 1 B6      | BUS 6                                   |

| 14,16 (octal)                                      | B5        | BUS 5                                   |

|                                                    | 1 B4      | BUS 4 I                                 |

|                                                    | 1 B3      | BUS 3                                   |

| R2 R1 - 00) Cannot be generated from processor     | 1 B2      | BUS 2                                   |

|                                                    | 1 B1      | BUS 1                                   |

|                                                    | 1 во      | I BUS O I                               |

|                                                    | •         |                                         |

| A make a mile make a shaddana                      |           | 1 1=Bus Low                             |

| Data Bus Bit Interpretation:                       |           | 1 0=Bus High!                           |

|                                                    | IX=Don't  |                                         |

| t page 20 decharts of commutation (lungations)     | =======   |                                         |

| B7 - 80 Contents of accumulator (A-register)       |           | Į.                                      |

| are gated to the terminal bus.                     |           | į                                       |

|                                                    |           | •                                       |

|                                                    |           | !                                       |

|                                                    |           | 1                                       |

|                                                    |           | !                                       |

|                                                    |           | <br>                                    |

| # T & Y & Y & Y & Y & Y & Y & Y & Y & Y &          |           |                                         |

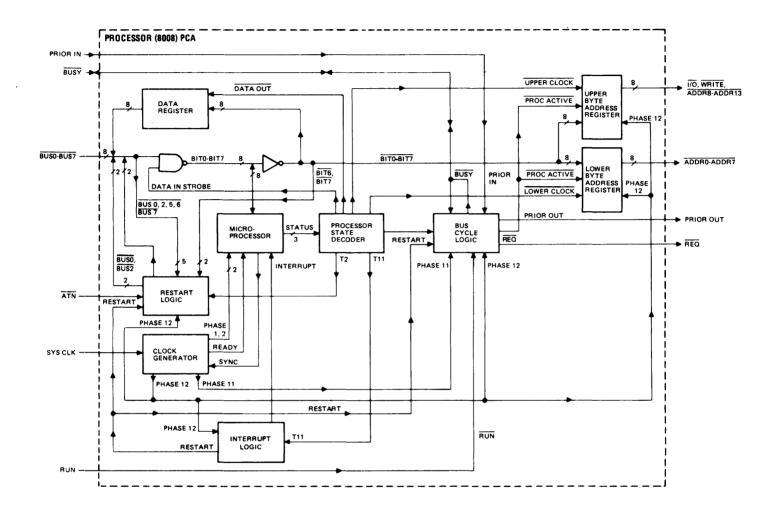

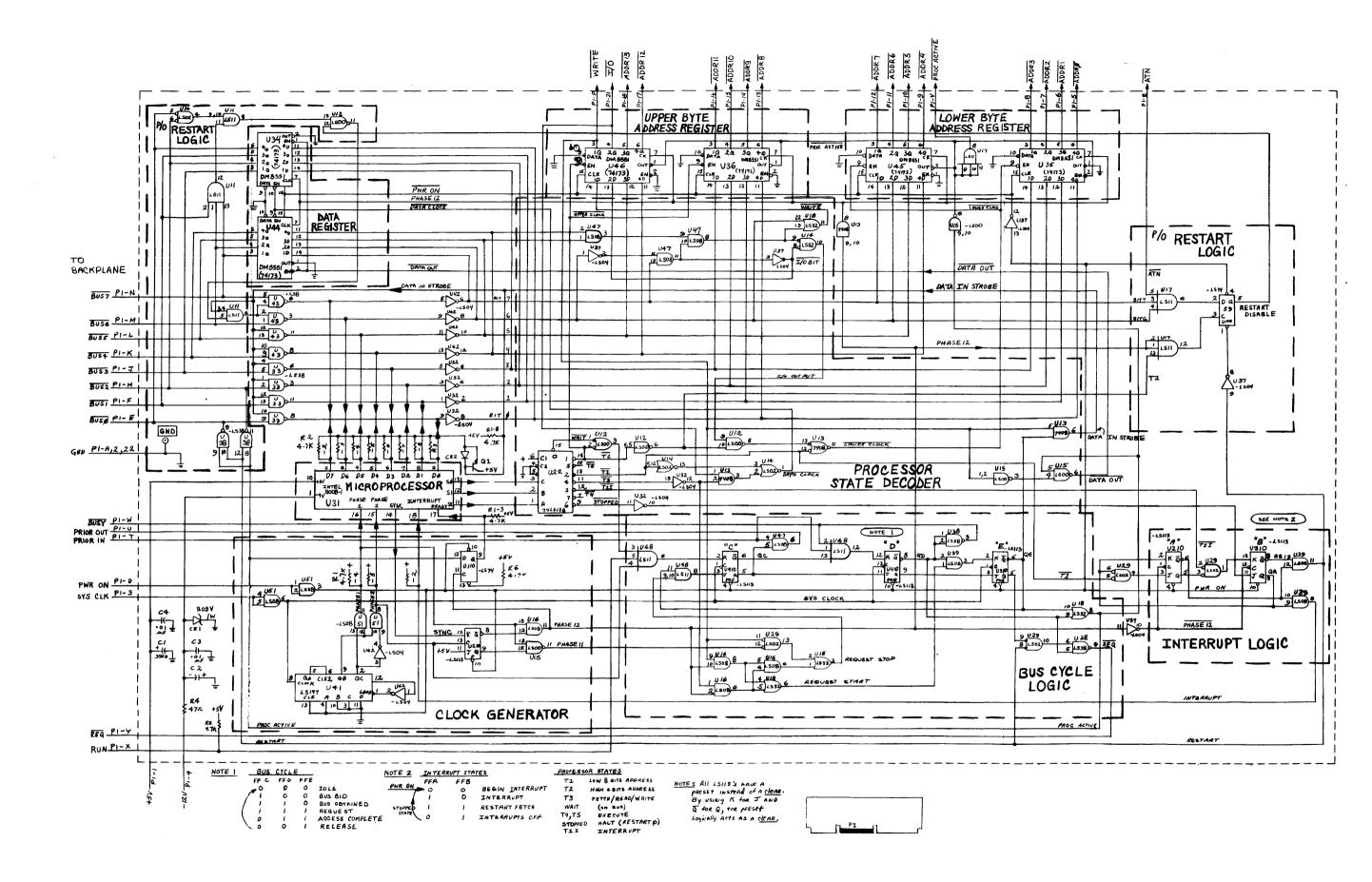

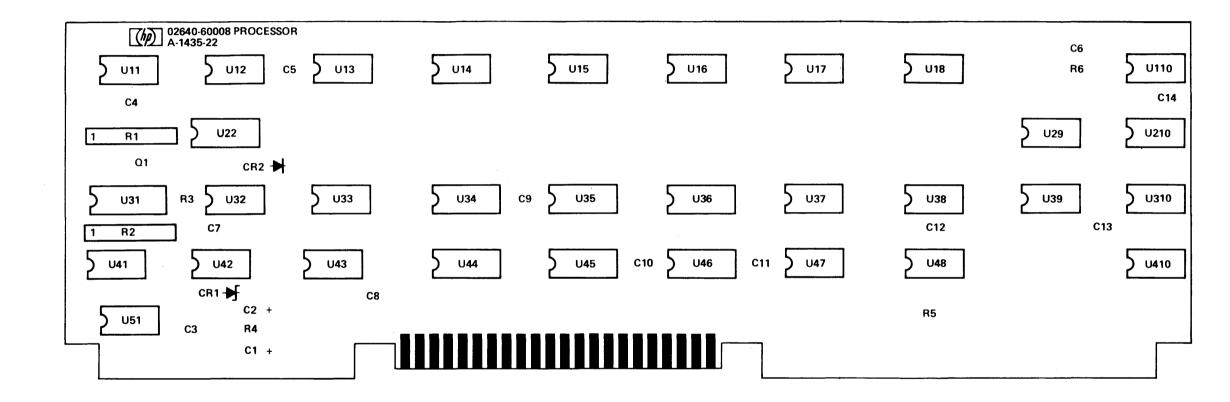

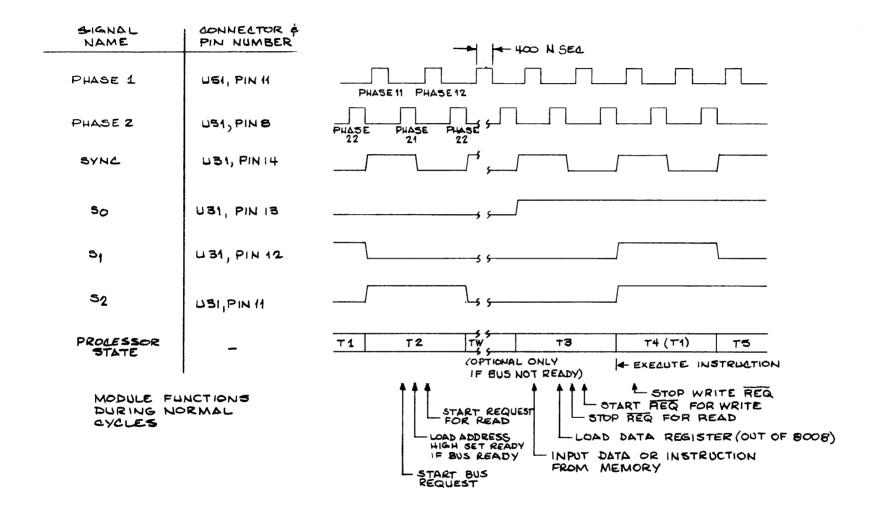

FUNCTIONAL DESCRIPTION. Refer to the block diagram (figure 1), schematic diagram (figure 2), timing diagrams (figures 3 and 4), component location diagram (figure 5), and parts list (02640-60008) located in the appendix.

The Processor (8008-1) Module consists of the following functional groups: microprocessor, clock generator, processor state decoder logic, bus cycle logic, data register, upper and lower byte address registers, interrupt logic, and restart logic.

- 3.1 MICROPROCESSOR.

- 3.1.1 The 8008-1 microprocessor is an 8-bit central processing unit which is implemented on a single LSI integrated circuit. The microprocessor chip has a basic 8-bit architecture internally with an accumulator, six registers, a program counter, and a subroutine return address stack (allowing seven levels of subroutines).

- 3.1.2 The microprocessor (U31) has 48 different instruction types of one, two, or three bytes per instruction. It has only one 8-bit input/out-put bus which is multiplexed between data and address information by the state outputs. The chip requires two phase clocks and has a basic cycle time of 2.8 microseconds (two periods of the phase clocks). The microprocessor has an addressing range of 16,384 bytes (14 bits).

- 3.1.2.1 Processor signals. The microprocessor has eighteen pins including two for power, +5 volts (Pin 1%) and -9 volts (Pin 1). Eight pins comprise the bidirectional bus (Pins 2 through 9) which is used for data and address output and data input. Three output signals S2 (Pin 11), S1 (Pin 12), and S0 (Pin 13) encode processor state information which is used to control the other logic elements of the Processor (8008-1) Module. Two inputs (Pins 15 and 16) are used for the two phase clocks. The microprocessor provides an output called SYNC (Pin 18) which is used with the clocks to define a basic microprocessor cycle (T-cycle). The remaining signals are inputs READY (Pin 17) and INTERRUPT (Pin 18). READY is used to synchronize the microprocessor with the terminal bus and INTERRUPT is used to start the microprocessor during a power on or reset sequence.

- 3.1.2.2 Processor bus. The microprocessor bus is multiplexed, under control of the state outputs, for lower and upper address byte out, instruction fetch, and data in or out of the processor. The direction of data flow is determined by control information available when the upper address byte is output during microprocessor state T2.

Open-collector inverting buffers (U33 and U43) gate information from the terminal bus when DATA IN STROBE (U13, Pin 6) is high. Inverters (U32 and U42) buffer the data output from the microprocessor, since the output drive is limited. The pull-up resistor network (R2) and transistor (Q1) provide input drive current for the buffers (U33 and U43) and are disabled during output operations (decreasing the input current).

Processor states. The state outputs S2, S1, and S0 encode eight microprocessor states as illustrated below. These states are one T-cycle (or 2.8 microseconds) and indicate to the module processor state decoder logic what the processor is doing. States T1 and T2 are used to output lower and upper address bytes. State T3 is instruction fetch or data in or out and states T4 and T5 are used to execute instructions. Wait is a special state entered when the READY line is not high in time for the microprocessor to enter the T3 state. This allows the Processor Module to synchronize with the terminal bus and perform single step operations during program development. State T1I is a special Interrupt state which is entered only when a halt instruction is executed. Stopped is the processor state entered after a halt instruction and is used to force the module into a power on sequence to prevent the microprocessor from dying unexpectedly. (Refer to figure 3 for processor state timing information.)

8008-1 PROCESSOR STATES

| s2   | <b>S</b> 1 | so   | NAME    | COMMENTS                       |

|------|------------|------|---------|--------------------------------|

| ==== | ====       | ==== |         |                                |

| 0    | 1          | 0    | T 1     | Lower eight bits of address    |

|      |            |      |         | out of processor               |

| 0    | 0          | 1    | Т2      | Upper six bits of address      |

| · ·  | v          | •    | 12      | and two control bits           |

|      | •          |      | ·       | and two control bits           |

| 0    | 0          | 0    | Wait    | If bus not ready processor     |

|      |            |      |         | will stay in this state        |

|      |            |      |         |                                |

| 1    | 0          | 0    | т3      | Instruction or data in or      |

| •    | •          | •    | 13      | out of the processor           |

|      |            |      |         | out of the processor           |

| 1    | 1          | 1    | Т4      | Instruction execution          |

|      | •          | •    | 4 3     | institution excedition         |

| 1    | 0          | 1    | Т5      | Instruction execution          |

| •    | J          | 1.   | 13      | institution execution          |

| 0    | 1          | 0    | T1 I    | Interrupt state, used to       |

|      | •          | •    | ***     | start processor                |

|      |            |      |         | searc brocessor                |

| 1    | 1          | 0    | Stopped | Entered after halt instruction |

| -    | •          | •    |         | causes power on sequence       |

|      |            |      |         | causes power on sequence       |

- Instruction set. The microprocessor has 48 different instruction codes which can be one, two, or three bytes long. Each instruction begins with a memory read to fetch the first byte. If the instruction decoded is one byte only, it is executed in states T4 and T5. If more bytes are needed to complete the instruction, they are read during succeeding memory cycles. Instructions can be from 3 to 11 microprocessor states (each 2.8 microseconds) plus any additional wait states. Several instruction codes (restart, input/output, and halt) require special handling. The halt instruction should not be used because it will cause a power on sequence to occur, thus causing the microprocessor to begin executing instructions at memory location zero.

- 3.1.2.5 Input/output instructions. (See tables 5.0 and 5.1) The input and output instructions are special cases in that the upper and lower byte address registers hold different information than when a memory read or write is performed. When an output instruction is executed, the upper byte address register (U36 and U46) and lower byte address register (U35 and U45) both contain the output instruction when the address information is gated to the bus. During an input instruction, the upper address byte contains the input instruction and the lower byte contains the contents of the accumulator just prior to the input instruction fetch. Address information for input/output is then decoded by the modules on the bus and output data from the processor's accumulator register is received by the addressed module or data from an addressed module is loaded into the processor's accumulator register.

- 3.1.2.6 Restart instruction. The special use of the restart instruction is described in section 3.9. The microprocessor executes a subroutine call

when it receives a restart instruction and the bus signal ATN is low causing a subroutine call to one of eight predefined locations as encoded in the Restart instruction.

- 3.2 CLOCK GENERATOR.

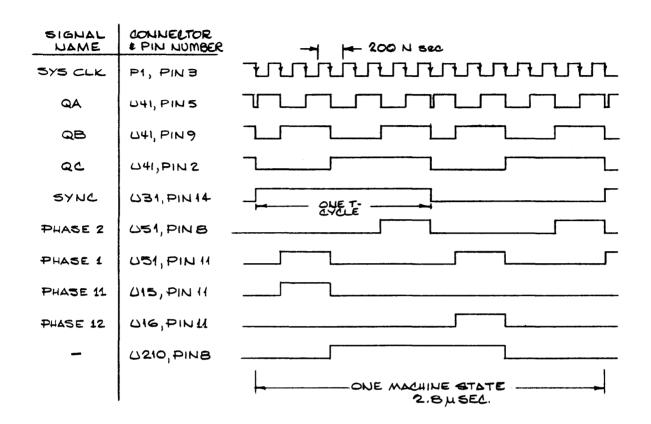

- 3.2.1 The clock generator provides the required two phase clocks to the 8008-1 microprocessor. The two phase clocks are derived from the terminal bus system clock by dividing the system clock down with a counter. Additional timing information is generated using the SYNC output (U31, Pin 18).

- 3.2.2 The basic microprocessor timing cycle is two periods of the phase clocks (each 1.4 microseconds) for a machine state of 2.8 microseconds. Each phase of the clocks will occur during a T-cycle. Each instruction is made up of three or more machine states, which determines the time that a particular instruction will take. The microprocessor clock and processor state decoder outputs determine the control and timing necessary for the various module functions.

- 3.2.2.1 Counter. The basic clock timing period is produced by a 4-bit counter (U41) which counts seven periods and then is preset at Pin 1 to redo the sequence (1, 2, 3, 4, 5, 6, 7, with state 8 causing a preset). Two AND gates (U51, Pins 11 and 8) decode the counter states and produce microprocessor clock PHASE 1 and PHASE 2.

- 3.2.2.2 SYNC flip-flop. The microprocessor SYNC output signal (Pin 14) goes high at the beginning of a processor T-cycle and goes low at the mid-point of the cycle, as shown in the clock generator timing diagram in figure 4. Flip-flop U210 at Pin 8 latches SYNC on the PHASE 2 fall edge. The SYNC flip-flop outputs generate two additional signals, PHASE 11 (U15, Pin 11) and PHASE 12 (U16, Pin 11). These signals provide timing information to the rest of the Processor (8008-1) Module.

- 3.2.2.3 READY. The READY line at Pin 17 is used to synchronize the microprocessor with the terminal bus. Flip-flop U110 at Pin 9 holds this information. If READY is not high by PHASE 12 of state T2, then the microprocessor will enter the Wait state until READY does go high again, thus allowing the microprocessor to enter state T3.

- 3.3 PROCESSOR STATE DECODER.

- 3.3.1 The processor state decoder controls the Processor (8008-1) Module by decoding microprocessor states. The state decoder controls address and data, in and out of the microprocessor.

- 3.3.2 The processor state decoder receives three outputs from the microprocessor which have state information encoded. This state information tells what the 8-bit bus is being used for (data in or out, or address upper or lower out) or if the microprocessor is in a special state such as Wait or Stopped. The outputs of the processor state decoder logic control other module functions.

- 3.3.2.1 State decoder. The microprocessor has three encoded state outputs (U31, Pins 13, 12, and 11) which are decoded by a one-of-eight decoder (U22). The three inputs encode the eight microprocessor states, which decode as eight outputs (U22, Pins 7, and 9 through 15). The outputs of the decoder indicate when the microprocessor is in a particular state (low output). The only states not used in controlling Processor (8008) Module functions are states T4 and T5 which are instruction execution cycles.

- 3.3.2.2 Address register clocks. The processor state decoder logic uses the outputs of the decoder and the PHASE 12 clock to strobe data into the upper (U46 and U36) and lower (U45 and U35) byte address registers. The registers have clock and data enable inputs (Pins 7 and 9) which control the address inputs. The upper byte address registers have

WRITE (Pin 14), I/O (Pin 13), and address inputs clocked in during state T2 and on the rising edge of PHASE 12. The lower byte address

register has address inputs clocked in (LOWER CLOCK) at U13, Pin 11 during state T1 of all except output instructions and during state T2 of output instructions. The four registers all have PHASE 12 at Pin 7 as the input clock which is buffered by a gate at U13, Pin 8. The upper byte address register receives two control bits which represent

WRITE and I/O on the bus. I/O is derived by decoding BIT7 and BIT6 of

the upper address byte out of the processor during state T2. WRITE is derived by decoding an input instruction or a write command from the two control bits of processor state T2.

3.3.2.3 Data register clocking. The processor state decoder logic also controls the data register (U34 and U44). Data from the microprocessor is clocked into the data register on the rising edge of PHASE 12 Clock (U34 and U44, Pin 7) during state T3 of all (except I/O instructions) and during state T1 of an output instruction. Data is gated onto the

bus during write cycles when DATA OUT (U15, Pin 6) is low. Another signal, DATA IN STROBE (U13, Pin 6) is provided by the processor state decoder logic to enable data from the terminal bus during read or input instructions. DATA IN STROBE controls the direction of data on the 8-bit processor bus and enables the current switch (Q1) so that resistor R2 can act as a pull-up to buffers U43 and U44.

3.4 BUS CYCLE LOGIC.

3.4.1 The bus cycle logic controls the microprocessor's access to the terminal bus, controls gating of data and address onto the bus, and controls

REO and PROC ACTIVE signals for the module. The RUN signal from the bus determines if the bus cycle will be allowed to begin, which enables halting the processor temporarily or single stepping during development of programs.

- 3.4.2 A bus access is begun during processor state T2 and ended during state T3 for (reads or inputs) and (during write or output). If the terminal bus is not obtained and ready before state T3, the processor will enter a Wait state by following its READY input (U31, Pin 17).

- 3.4.2.1 Bus cycle states. The three J-K flip-flops labled "C" (U410, Pin 6), "D" (U410, Pin 8), and "E" (U310, Pin 6) implement a 6-state counter which times the terminal bus access. The six bus cycle states are summarized below. The Tdle state is in effect when no bus cycle is needed. Bus Bid is the state which begins a bus cycle. Bus Obtained is the state where the Processor (8008-1) Module gains control of the

bus, makes BUSY low, and gates data and address to the terminal bus. The Request state actually performs the data transfer on the bus and Access Complete is the state which begins the last three states. The Release State is followed by Idle and the Processor (8008-1) Module has then completed the terminal bus cycle.

#### BUS CYCLE LOGIC

| FF C | FF D | FF E | NAME                                    | COMMENTS                                                    |  |  |

|------|------|------|-----------------------------------------|-------------------------------------------------------------|--|--|

| ==== | ==== | ==== | ======================================= |                                                             |  |  |

| n    | 0    | 0    | Idle                                    | Processor does not require terminal bus                     |  |  |

| 1    | 0    | 0    | Bus Bid                                 | Regin terminal bus access (during T2 and RUN is high)       |  |  |

| 1    | 1    | 0    | Bus Obtained                            | Processor (8008-1) Module has control of terminal bus       |  |  |

| 1    | 1    | 1    | Request                                 | REO made true (data & address gate out during Bus Obtained) |  |  |

| O    | 1    | 1    | Access Complete                         | Begin process of releasing<br>bus, REO off                  |  |  |

| 0    | 0    | 1    | Release                                 | Processor (8008-1) Module gives up bus and goes to Idle     |  |  |

- 3.4.2.2 Bus cycle start. A bus cycle is begun when the T2 state is entered (or Wait if bus is not ready) and the RUN line is high. This sets flip-flop "C" which makes the state counter go from Idle to Bus Bid. The PRIOR OUT signal is disabled at U47, Pin 6 and then waits until the PRIOR IN signal is high and the bus is not available. Flip-flop "D" is set at U48, Pin 12 putting the module in the Bus Obtained state, and making the bus busy by making BUSY at U38, Pin 3 low.

- 3.4.2.3 When the module is in the Bus Obtained state it gates address and data

to the bus and makes PROC ACTIVE true. The bus cycle logic stays in the Bus Obtained state until PEOUEST START at U18, Pin 6 goes high. This will set flip-flop "E" and put the state counter in the Pequest

state. The module then makes REQ (U38, Pin 6) low which will begin the bus operation. The state counter will stay in the Request state until flip-flop "C" is reset by the REQUEST STOP signal at U18, Pin 3.

3.4.2.4 Bus cycle end. The bus cycle state counter enters the Access Complete state when flip-flop "C" is reset by REQUEST STOP and flip-flop "E" being set (Request state). REQUEST STOP is high when a write is in progress at PHASE 11 and when a read is in progress at PHASE 12 of processor state T3 (Refer again to figure 3 for processor state timing information). After flip-flop "C" is reset, the bus cycle logic goes

to the Release state (REQ is brought high) and then to the Idle state with flip-flops "D" and "E" being reset on the next two clocks. The state counter is in the Idle state and the bus has been released.

- 3.5 DATA REGISTER.

- 3.5.1 The data register holds data from the microprocessor during writes to memory or during output instructions. The data comes out of the microprocessor on the 8-bit microprocessor bus and is clocked into the data register. The data register is a 3-state latch and is gated onto the terminal data bus by the processor state decoder logic during a write or output.

- 3.5.2 The data registers (U34 and U44) hold the 8-bit output from the micro-processor bus which is buffered by inverters (U32 and U42). Data is clocked into the registers on the rising edge of PHASE 12 during processor state T3 of all writes (except I/0) and during state T1 for

output instructions. The data registers are normally in the off condition and the data registers are not enabled. During data write or output, however, the data registers are enabled and drive the bus. The

DATA OUT, signal at U15, Pin 6 enables data out when U15, Pin 3 and U18, Pin 8 are true.

- 3.6 UPPER BYTE ADDRESS REGISTER.

- 3.6.1 Two 3-state latches (U46 and U36) make up the upper byte address register and receive address inputs from the microprocessor bus during processor state T2.

- 3.6.2 For a memory read or write, the register will hold the most significant

six bits (ADDR13 thru ADDR8) and two bits of control (wRITE and I/O). The two control bits are encoded from the processor bus BIT7 and BIT6 and are loaded into the upper byte address register (U46) at Pins 13 and 14. During an I/O instruction, the instruction itself, is loaded into the upper byte address register and is used to address I/O modules. The clock and enable signals for the registers are provided by the processor state decoder logic. Address information from the regis-

ters is gated to the terminal bus when PROC ACTIVE is high.

- 3.7 LOWER BYTE ADDRESS REGISTER.

- 3.7.1 Two 3-state latches (U45 and U35) make up the lower byte address register and receive address inputs from the microprocessor bus during processor state T1 (for memory access or an input instruction) and during state T2 (for an output instruction).

- 3.7.2 The lower byte address register will contain the least significant eight bits of a memory address for a read or write. During an input instruction, the registers will hold the contents of the microprocessor accumulator (A-register) prior to fetching the input instruction. During an output instruction, the register will hold the output instruction itself, which is sent out from the microprocessor during state T2 of the instruction execution. The registers receive clock and enable signals (U45 and U35, Pins 7 and 9) from the processor state decoder logic. Address information in the registers is gated to the terminal

bus when PROC ACTIVE is true.

- 3.8 INTERRUPT LOGIC.

- 3.8.1 The interrupt logic ensures that the microprocessor initializes correctly during power on or reset. This logic also detects the microprocessor Stopped state and performs a reset function to ensure that the microprocessor does not remain halted. The start-up function is performed by forcing a special 1-byte instruction into the microprocessor which causes the processor to begin executing instructions at location zero. This special instruction is called a restart.

- 3.8.2 The interrupt logic consists of two J-K flip-flops, flip-flop "A" (U210, Pin 6) and flip-flop "B" (U310, Pin 8) which implement a counter. The following is a summary of the states and their meanings.

| FF A | FF B | State Name      | Comments                                                        |

|------|------|-----------------|-----------------------------------------------------------------|

| ==== | ==== |                 |                                                                 |

| 0    | 0    | Begin Interrupt | Either power on, reset or halt                                  |

| 1    | 0    | Interrupt       | Cause processor to enter T1I                                    |

| 1    | 1    | Restart Fetch   | Gate Restart to microprocessor                                  |

| 0    | 1    | Interrupts Off  | Sequence complete - go to Begin<br>Interrupt if halted or reset |

- 3.8.2.1 The interrupt logic state counter starts when PWR ON at U210, Pin 4 and U310, Pin 10 resets the two flip-flops which puts the state counter in the Begin Interrupt state. The state counter will go to the Interrupt state on the next PHASE 12 clock and make the microprocessor INTERRUPT signal (U39, Pin 8) true. When the microprocessor enters the Til state, the interrupt logic goes to the Restart Fetch state at U39, Pin 11 and causes the input buffers (U33 and U34) to force a restart instruction into the microprocessor. Two bus drivers (U38, Pins 8 and

- 11) are enabled by RESTART and PROC ACTIVE and cause BUS2 and BUS0 to be changed to "1's" during the fetch. During the fetch of the restart

instruction REQ is not enabled, so the RESTART 0 pattern is present on the terminal bus. On the next processor T1 state, the counter will advance to the Interrupts Off state.

- 3.8.2.2 Both power on and reset cause the interrupt logic to start an interrupt sequence. This is done by making PWR ON low. The state counter will advance through the states described in section 3.8.2 until the microprocessor has executed a restart instruction and has begun execution of terminal programs at location zero of the memory range.

- 3.8.2.3 When the microprocessor executes a halt instruction, it will enter the Stopped state. This is decoded by the processor state decoder logic at U22, Pin 9. The interrupt logic state counter will be in the Interrupts Off state and will go to the Begin Interrupt state when flip-flop "B" is reset at U310, Pin 11. The state counter advances through the sequence described in section 3.8.2.1 and the microprocessor goes out of the Stopped state and begins executing instructions at location zero.

- 3.9 RESTART LOGIC.

- 3.9.1 The restart logic block implements a special hardware/software interrupt feature for the microprocessor. During program execution restart instructions will be placed in the program when a data comm interrupt is allowed. The Restart will be changed to an alternate 8008-1 instruction code if no data comm interrupt exists, otherwise a normal restart instruction will be performed.

- 3.9.2 The restart instruction is a 1-byte subroutine call and is conditionally executed based on the terminal bus ATN signal. If the ATN line is high, all restart instructions encountered will be modified to an al-

ternate 8008-1 instruction code (see summary below). If ATN is low, the restart instruction will not be modified and a subroutine will be executed to service the interrupt condition. This allows the program

to control when it can be interrupted so that the modified instruction codes do not make unexpected changes to the microprocessor registers.

#### RESTART INSTRUCTIONS

| INSTRUCTION ADDRESS                     | ATN = HIGH | ATN = LOW | SUBROUTINE START |

|-----------------------------------------|------------|-----------|------------------|

| ======================================= | ========   | ========  |                  |

| RST 0                                   | LAH        | RST 0     | 0                |

| RST 1                                   | LBH        | RST 1     | 8 (10 OCTAL)     |

| RST 2                                   | LCH        | RST 2     | 16 (20 OCTAL)    |

| RST 3                                   | T/DH       | RST 3     | 24 (30 OCTAL)    |

| RST 4                                   | LEH        | RST 4     | 32 (40 DCTAL)    |

| RST 5                                   | LHH        | RST 5     | 40 (50 OCTAL)    |

| PST 6                                   | LLH        | RST 6     | 48 (60 OCTAL)    |

| RST 7                                   | LMH        | RST 7     | 56 (70 OCTAL)    |

The restart logic makes a check during processor state T2 of an in-

struction fetch at U17, Pin 6 and 12 to see if ATN is low. If ATN is low or if it is not an instruction fetch, the Restart Disable flip-flop is reset at U59, Pin 5, which disables the restart instruction decoding

and allows data to pass unmodified. If ATN is high (no interrupt), the restart instruction decoding at U11, Pin 8 will modify all restart instructions according to the restart instruction summary above. This modifying is done by disabling the buffers (U43, Pin 6 and 3) which change BIT7 and BIT6 of the instruction from "0" to "1".

Figure 2

Processor (8008-1) PCA Schematic Diagram

AUG-01-76

13255-91008

Figure 3

Processor State Timing Diagram

AUG-01-76

13255-91008

# Replaceable Parts

| Reference<br>Designation          | HP Part<br>Number                                             | Qty              | Description                                                                                                                                                                                                                 | Mfr<br>Code                               | Mfr Part Number                                                           |

|-----------------------------------|---------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------|

|                                   | 02 <b>640</b> –60008                                          | 1                | PROCESSOR (8008-1) ASSEMBLY DATE CODE: A-1435-22                                                                                                                                                                            | 28480                                     | 02640-60008                                                               |

| 61<br>62<br>63<br>64              | 0160-0393<br>0160-1746<br>0160-2055<br>0160-2055<br>0160-2055 | 1<br>1<br>12     | REVISION CODE: 04-15-76  CAPACITOR-FXD 39UF+-10% 10VDC TA  CAPACITOR-FXD 15UF+-10% 20VDC TA  CAPACITOR-FXD .01UF +80-20% 100WVDC CER  CAPACITOR-FXD .01UF +80-20% 100WVDC CER  CAPACITOR-FXD .01UF +80-20% 100WVDC CER      | 56289<br>56289<br>28480<br>28480<br>28480 | 1500396 X901082<br>1500156 X902082<br>0160-2055<br>0160-2055<br>0160-2055 |

| C6<br>C7<br>C8<br>C9<br>C10       | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055 |                  | CAPACITOR-FXC .01UF +80-20% 100WVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100WVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100WVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100WVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100WVDC CER         | 28480<br>28480<br>28480<br>28480<br>28480 | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055<br>0160-2055             |

| C11<br>C12<br>C13<br>C14          | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055              |                  | CAPACITOR-FXD .01UF +80-20% 100HVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100HVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100HVDC CER<br>CAPACITOR-FXD .01UF +80-20% 100HVDC CER                                                    | 28480<br>28480<br>28480<br>28480          | 0160-2055<br>0160-2055<br>0160-2055<br>0160-2055                          |

| CRI<br>CRZ                        | 1902-0651<br>1901-0040                                        | 1                | DIODE-ZNR 9.09V 5% DO-15 PD=1W TC=+.057%<br>DIODE-SWITCHING 30V 50MA 2NS DO-35                                                                                                                                              | 28480<br>28480                            | 1902-0651<br>1901-0040                                                    |

| £1                                | 0360-0124                                                     | 1                | TERMINAL-STUD SGL-PIN PRESS-MTG                                                                                                                                                                                             | 28480                                     | 0360-0124                                                                 |

| Q1                                | 1854-0467                                                     | 1                | TRANSISTOR NPN 2N4401 SI TU-92 PD=310MW                                                                                                                                                                                     | 04713                                     | 2N4401                                                                    |

| R1<br>K2<br>K3<br>K4<br>K5        | 1810-0125<br>1810-0125<br>0683-4725<br>0683-4705<br>0683-4725 | 2<br>3<br>1      | METHORK-RES 8-PIN-SIP .125-PIN-SPCG NETHORK-RES 8-PIN-SIP .125-PIN-SPCG RESISTOR 4.7K 5% 2.25M FC TC=-400/+700 RESISTOR 47 5% .25M FC TC=-400/+700 RESISTOR 4.7K 5% .25M FC TC=-400/+700                                    | 11236<br>11236<br>01121<br>01121<br>01121 | 750<br>750<br>CB4725<br>CB4705<br>CB4725                                  |

| K6                                | 0683-4725                                                     |                  | RESISTOR 4.7% 5% .25W FC TC=-400/+700                                                                                                                                                                                       | 01121                                     | C84725                                                                    |

| 011<br>012<br>013<br>014<br>015   | 1820-1203<br>1820-1197<br>1820-0511<br>1820-1144<br>1820-1197 | 3<br>2<br>1<br>2 | IC-DIGITAL SN74LSIIN TTL LS TPL 3 AND IC-DIGITAL SN74LSOON TTL LS QUAD 2 NAND IC-DIGITAL SN744SO8N TTL QUAD 2 AND IC-DIGITAL SN74LSO2N TTL LS QUAD 2 NOR IC-DIGITAL SN74LSOON TTL LS QUAD 2 NAND                            | 01295<br>01295<br>01295<br>01295<br>01295 | SN74L S11N<br>SN74L S00N<br>SN7408N<br>SN74L S02N<br>SN74L S00N           |

| U16<br>U17<br>U18<br>U22<br>U29   | 1820-1201<br>1820-1203<br>1820-1208<br>1820-1216<br>1820-1144 | 1 1              | IC-DIGITAL SN74LSORN TTL LS QUAD 2 AND IC-DIGITAL SN74LS11N TTL LS IPL 3 AND IC-DIGITAL SN74LS32N TTL LS QUAD 2 OR IC-DIGITAL SN74LS13RN TTL LS 3 IC-DIGITAL SN74LS13RN TTL LS QUAD 2 NOR                                   | 01295<br>01295<br>01295<br>01295<br>01295 | SN74L SO8N<br>SN74L S1 IN<br>SN74L S32N<br>SN74L S138N<br>SN74L S02N      |

| U31<br>U32<br>U33<br>U34<br>U39   | 1820-1221<br>1820-1199<br>1820-1209<br>1820-0574<br>1820-0574 | 1<br>3<br>3<br>6 | IC-DIGITAL C#008-1 MOS IC-DIGITAL SN74LS04N TTL LS HEX 1 IC-DIGITAL SN74LS38N TTL LS QUAD 2 NAND IC-DIGITAL DM8551N TTL QUAD D-TYPE IC-DIGITAL DM8551N TTL QUAD D-TYPE                                                      | 34649<br>01295<br>01295<br>27014<br>27014 | C8008-1<br>SN74LS04N<br>SN74LS38N<br>DM8551N<br>DM8551N                   |

| U30<br>U37<br>U38<br>U39<br>U41   | 1820-0574<br>1820-1199<br>1820-1209<br>1820-1201<br>1820-1193 | 1                | IC-DIGITAL DM8551N TTL QUAD D-TYPE IC-DIGITAL SN74LS04N TTL LS HEX 1 IC-DIGITAL SN74LS38N TTL LS QUAD 2 NAND IC-DIGITAL SN74LSC8N TTL LS QUAD 2 AND IC-DIGITAL SN74LS18N TTL LS QUAD 2 AND IC-DIGITAL SN74LS197N TTL LS BIN | 27014<br>01295<br>01295<br>01295<br>01295 | DM8551N<br>SN74LS04N<br>SN74LS38N<br>SN74LS08N<br>SN74LS197N              |

| U42<br>U43<br>U44<br>U45<br>U46   | 1820-1199<br>1820-1209<br>1820-0574<br>1820-0574<br>1820-0574 |                  | IC-DIGITAL SN74LSO4N TTL LS HEX 1 IC-DIGITAL SN74LS38N TTL LS QUAD 2 NAND IC-DIGITAL DM855IN TTL QUAD D-TYPE IC-DIGITAL DM855IN TTL QUAD D-TYPE IC-DIGITAL DM855IN TTL QUAD D-TYPE                                          | 01295<br>01295<br>27014<br>27014<br>27014 | SN74L SO 4N<br>SN74L S38N<br>DM8551N<br>DM8551N<br>DM8551N                |

| U47<br>U48<br>U51<br>U110<br>U210 | 1820-1201<br>1820-1203<br>1820-1201<br>1820-1112<br>1820-1213 | 3                | IC-DIGITAL SN74LSCON TTL LS QUAD 2 AND IC-DIGITAL SN74LSIAN TTL LS TPL 3 AND IC-DIGITAL SN74LSCON ITL LS QUAD 2 AND IC-DIGITAL SN74LS74N TTL LS DUAL IC-DIGITAL SN74LS113N TTL LS DUAL                                      | 01295<br>01295<br>01295<br>01295<br>01295 | SN74L SO8N<br>SN74L S1 1N<br>SN74L SO8N<br>SN74L S74N<br>SN74L S1 13N     |

| U310<br>U410                      | 1820-1213<br>1820-1213                                        |                  | IC-DIGITAL SN74LS113N TTL LS DUAL<br>IC-DIGITAL SN74LS113N TTL LS DUAL                                                                                                                                                      | 01295<br>01295                            | SN74L S1 13N<br>SN74L S1 13N                                              |

| XA3T                              | 1200-0539                                                     | 1                | SOCKET-IC 18-CONT DIP-SLDR                                                                                                                                                                                                  | 28480                                     | 1200-0539                                                                 |

|                                   |                                                               |                  |                                                                                                                                                                                                                             |                                           |                                                                           |

|                                   |                                                               |                  |                                                                                                                                                                                                                             |                                           |                                                                           |