# 1401 DATA PROCESSING SYSTEM BULLETIN

1401 DATA FLOW

New, more efficient programming techniques for the IBM 1401 Data Processing System are being developed as the programming knowledge and the experience level on the system increases. This manual presents a semi-detailed data flow explanation of every 1401 operation. This approach should assist both the new, and the more experienced, programmer with his 1401 programming effort.

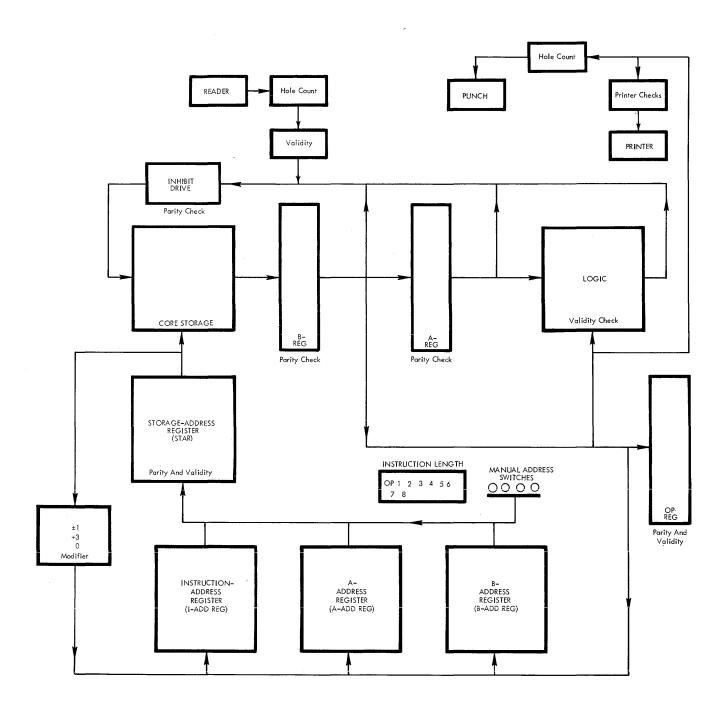

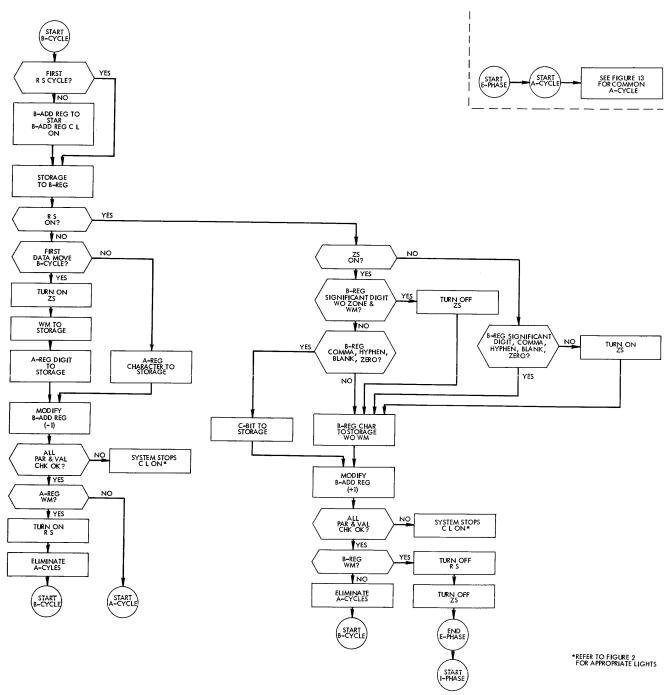

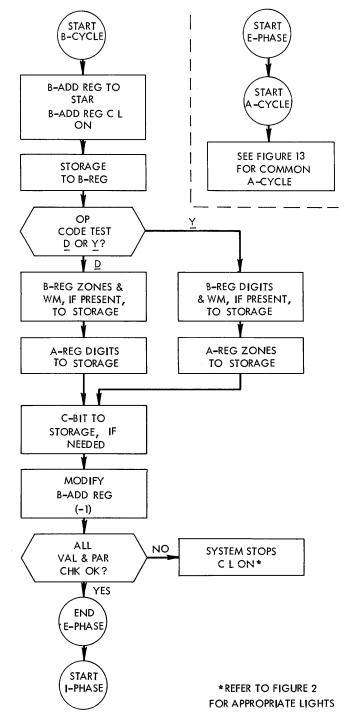

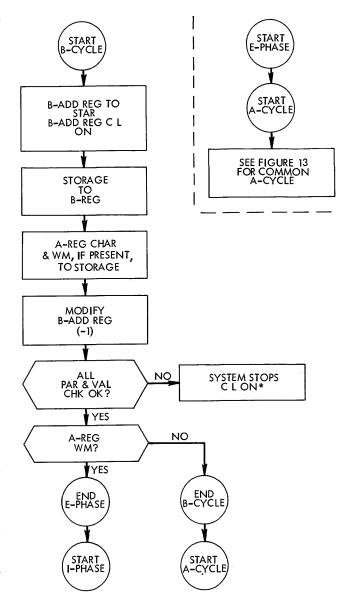

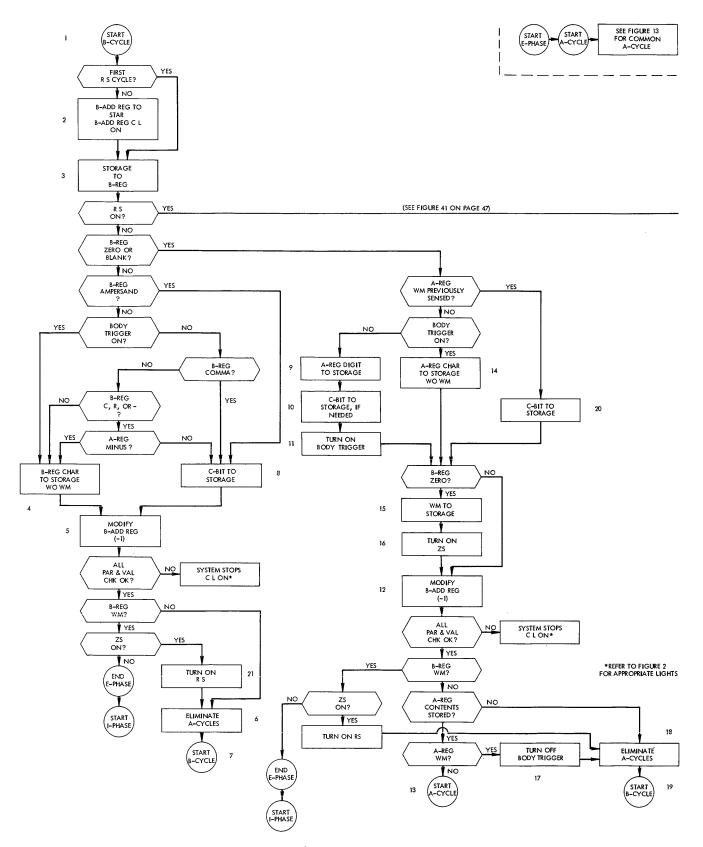

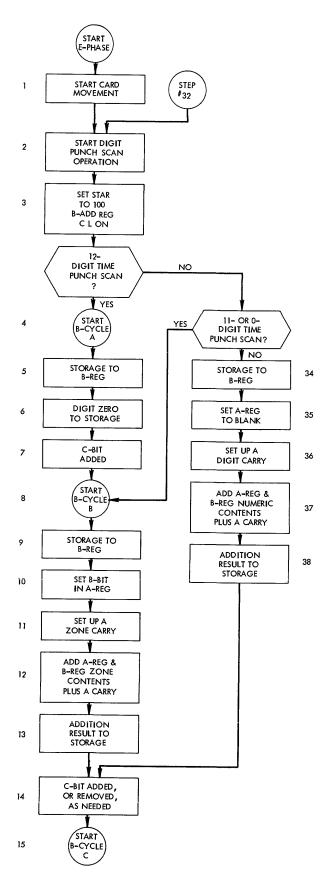

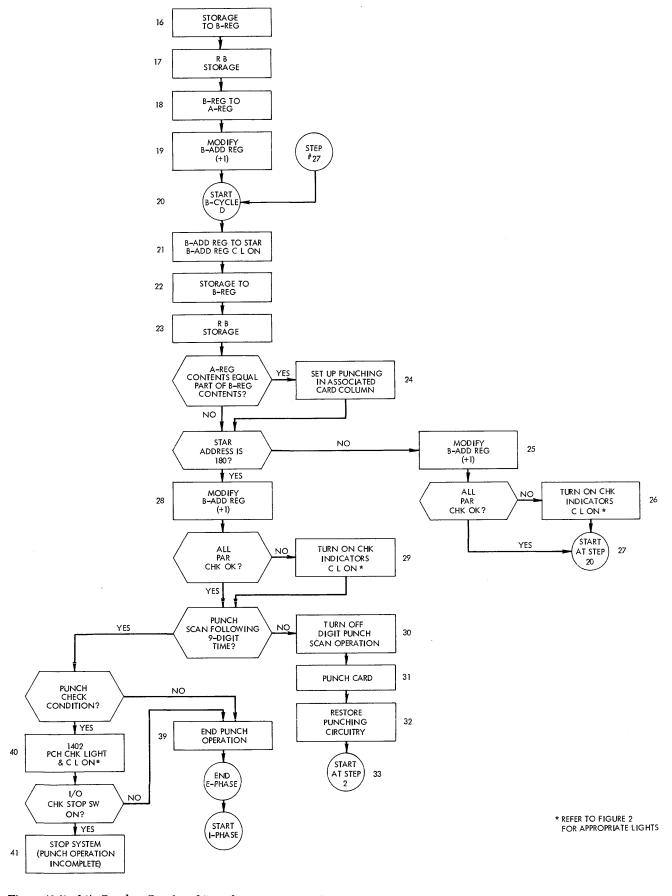

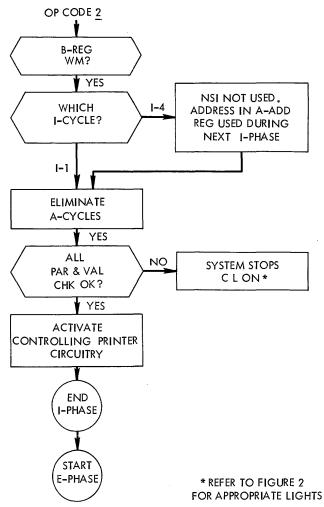

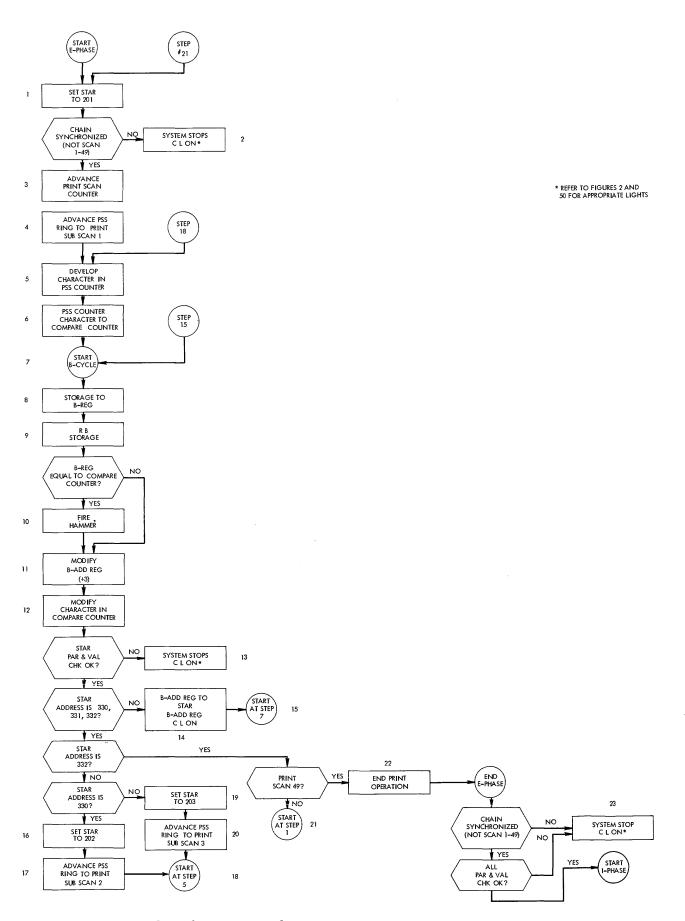

Each operation is presented in the form of a dataflow diagram. The path that the data takes during an operation is graphically presented along with a written explanation of the steps involved. The internal-parity and validity-checking operations are also presented, along with a list of the console lights that will be on in the event of a parity or validity check condition.

#### **Data Flow**

The data flow of an IBM 1401 Data Processing System is schematically shown in Figure 1. The flow paths used are initially specified by the stored program instructions. These instructions tell the system what areas to read out of, and what areas to read into. The internal circuitry of the system then carries out the specified data movement. The various component areas of the system are:

#### CORE STORAGE

The IBM 1401 Data Processing System uses magnetic-core storage for storing instructions and data. All the data in core storage is readily available, and the design of the core-storage area makes each position individually *addressable*. All data received from input units is stored in the core storage, and all data sent to the output units is sent from core storage.

Information is always read out of core storage during the early half of a cycle. The read-out is actually accomplished by setting all the cores, at the specified location, to zero. A core originally set at *one* will, when flipped from one to zero during read-out, induce a volt-

age on one of the wires running through the center of the core. This voltage is recognized as a bit.

Information is always read into core storage during the late half of a cycle. If the information that was read out of a storage location is to be retained in the same location, it is read back into that location from one of the registers during the late half of the read-out cycle. The 1401 system also makes use of this core-storage operation to perform the system's arithmetic operations. Two areas are alternately read out a position at a time, added together, and the sum stored in the last position read out. This is called add-to-storage logic, and it eliminates the need for special-purpose accumulators or counters. Because any group of storage positions can be used as an accumulating field, the capacity for arithmetic functions is not limited by a predetermined number of counter positions.

# DATA LINES AND INHIBIT DRIVE

The data-flow paths shown in Figure 1 as single lines are actually eight lines (4 digit, 2 zone, 1 word mark, and 1 check). The lines leading to the inhibit drive are called inhibit lines because they inhibit, or prevent, the setting of cores unless *activated* by the presence of a bit of information. Information being sent into core storage goes through the inhibit-drive area, while information being sent from core storage goes through the B-register.

#### **B-REGISTER**

Each character leaving 1401 core storage enters the B-register and is stored in an 8-bit code (BCD code, word mark, check bit). The register is reset and filled with a character from core storage during the read-out portion of every storage cycle. The character can be entered back into core storage from the output of the B-register during the storage read-in portion of a storage cycle. This is necessary when an instruction is being read and will be needed another time, because the cores of a position are all set to zero when that position is read out.

Figure 1. Data Flow and Checking Features

#### A-REGISTER

The A-register is reset and filled with the character from the B-register during each cycle that involves an A-address, and during all instruction cycles, except the first and last cycle of each instruction. The character is stored in an 8-bit code. The character can be entered back into core storage from the output of the A-register during the storage read-in portion of a storage cycle.

#### OP-REGISTER

The Op- (operation) register is reset and filled with a 7-bit character output from the B-register (word mark is dropped), whenever the character is an operation-code character. The Op-register stores the operation code of the instruction in process for the duration of the operation.

#### LOGIC AREA

The logic area is made up of the circuitry that executes the adding, subtracting, and comparing of the A- and B-register outputs. Depending on the operation, the resultant logic-area output may be entered back into storage and/or may indicate the next step to be taken.

#### I-ADDRESS REGISTER

The I-(Instruction) address register (I-Add. Reg.) is a 3-position register, and always contains the core storage location of the next instruction character to be read out. (This 3-digit core-storage location is converted to its 4-or 5-digit number when it is displayed in the storage-address register.) The location number is increased by one as the instruction is read out of core storage, lower-order core-storage position to higher-order core-storage position.

# A-ADDRESS REGISTER

The A-address register (A-Add. Reg.) is a 3-position register, and normally contains the core-storage location specified in the A-address portion of an instruction. (This 3-digit core-storage location is converted to its 4or 5-digit number when it is displayed in the storageaddress register.) Normally, this core-storage location is the units position of the A-field. As the instruction is executed, the number in this register is decreased by one during each storage cycle that involves the A-address. During several operations, the A-Add. Reg. operation differs. These differences are discussed as they are encountered. Note: If the A-address portion of the instruction does not contain a 1401 storage address (%Ux, for example), the numeric portion of the A-Add. Reg. contents is not disturbed as the instruction is executed.

# B-ADDRESS REGISTER

The B-address register (B-Add. Reg.) is a 3-position

register, and normally contains the core-storage location specified in the B-address portion of an instruction. (This 3-digit core-storage location is converted to its 4-or 5-digit number when it is displayed in the storage-address register.) Normally, this core-storage location is the units position of the B-field. As the instruction is executed, the number in this register is decreased by one during each storage cycle that involves the B-address. During several operations, the B-Add. Reg. operation differs. These differences are discussed as they are encountered.

#### STORAGE-ADDRESS REGISTER

The storage-address register (STAR) is a 3-position register, and contains the address of the core-storage location that is being read out and/or read into on any particular storage cycle. (This 3-digit core-storage location is converted to its 4- or 5-digit number when it is displayed.) This address is received from one of the address registers. As the STAR addresses core storage, the address is also modified and read back into the appropriate address register.

#### ADDRESS-MODIFICATION AREA

Because each character in core storage has a different address, the circuitry that specifies the address must be constantly changing. Instructions are placed in storage with the Op code occupying the lowest-numbered location and the rest of the instruction occupying the adjacent higher-numbered locations. To read out the Op code and then the rest of the instruction, in sequence, the lowest-numbered location must be addressed first, and then each succeeding location must be addressed. Therefore, during the read out of instructions, the address must be modified +1 each time so that the adjacent higher-numbered location is read out.

The data fields, however, are placed in core storage the opposite way. The units position of the field occupies the highest-numbered core-storage location, and the rest of the field occupies the adjacent lower-numbered core-storage locations. To perform the arithmetic functions correctly, the units digit of a field must be worked on first, followed by the tens digit, etc. Therefore, the address must now be modified by -1 each time so that the adjacent lower-numbered location is read out.

Operations involving the printer require that the address must be increased by three each storage cycle, and still other operations require no address modification.

#### INSTRUCTION-LENGTH LIGHTS

These lights indicate which position of an instruction is being read out of core storage.

#### MANUAL-ADDRESS SWITCHES

The four manual-address switches select the address entered in the storage-address register. These switches are effective only with these selected positions of the *mode switch*:

- 1. Character display

- 2. Alter

- 3. Address stop

- 4. Storage print-out

- 5. Storage scan.

#### INPUT-OUTPUT UNITS

The various input units send data into the 1401 system where each character is converted to its BCD form and then stored in a specified core-storage location. Core

storage supplies each character for the various output units that can be attached to a 1401 system. The character is converted from its BCD form to a form that is acceptable by the output unit.

#### PARITY AND VALIDITY CHECKING

The internal self-checking features within the process unit consist of parity and validity checking. Each character is checked, at various locations in the process unit, to be sure it has an odd number of bits, and that it is a valid 1401 character. An even number of bits initiates a parity-check condition, and an incorrect bit configuration initiates a validity-check condition. Refer to Figure 2 for a list of the process-unit check conditions.

Additional checking of the input-output units is done. Refer to the appropriate sections for more detail.

| UNIT                            | TYPE OF<br>CHECK          | MACHINE STOPS<br>CHECK STOP SWITCH<br>ON CE PANEL ON | STORAGE-ADDRESS<br>REGISTER (STAR)<br>CONTAINS                                                 | LIGHTS ON<br>WHEN STOPPED                 | RESET BY           | REMARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------|---------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A-REG                           | PARITY                    | END OF NEXT<br>CYCLE                                 |                                                                                                | PROCESS<br>A-REGISTER<br>CHECK RESET      | CHECK RESET<br>KEY | A-register contents in error still<br>on display ordinarily                                                                                                                                                                                                                                                                                                                                                                                                                |

| B-REG                           | PARITY                    | END OF CYCLE IN<br>WHICH CHECK IS<br>DETECTED        | ADDRESS LOCATION<br>THAT WAS READ<br>INTO THE B-REGISTER                                       | PROCESS<br>B-REGISTER<br>CHECK RESET      | CHECK RESET<br>KEY | B-REGISTER CONTENTS IN ERROR STILL<br>ON DISPLAY IN B-REGISTER                                                                                                                                                                                                                                                                                                                                                                                                             |

| LOGIC                           | VALIDITY                  | END OF FOLLOWING<br>CYCLE                            | NEXT A-ADDRESS                                                                                 | PROCESS<br>LOGIC<br>CHECK RESET           | CHECK RESET<br>KEY | B-ADDRESS REGISTER INDICATES ONE LESS THAN THE LOCATION THAT THE RESULT READ INTO EXCEPT:  1. WHEN THE CHECK IS DETECTED IN THE LAST CYCLE OF THE FIRST FORWARD SCAN DURING A RECOM- PLEMENT OPERATION. INDICATED LOCATION IS THE ERROR LOCATION  2. DURING A REVERSE SCAN OPERATION INDICATED LOCATION IS ONE MORE THAN THE LOCATION THAT THE RESULT READ INTO  THE BIT COMBINATION THAT CAUSES THE CHECK IS IN THE STORAGE UNIT AND IS NOT ON DISPLAY IN THE LOGIC AREA. |

| INHIBIT<br>DRIVE                | PARITY                    | END OF FOLLOWING                                     | DEPENDS UPON THE<br>OPERATION BEING<br>PERFORMED AND<br>THE PHASE (I OR E)<br>THE SYSTEM IS IN | PROCESS<br>STORAGE<br>CHECK RESET         | CHECK RESET<br>KEY | A CHECK INDICATES THAT AN EVEN-BIT<br>COMBINATION WAS READ INTO STORAGE                                                                                                                                                                                                                                                                                                                                                                                                    |

| OP-<br>REGISTER                 | PARITY<br>AND<br>VALIDITY | END OF CYCLE<br>IN WHICH CHECK<br>IS DETECTED        | DEPENDS UPON THE<br>OPERATION BEING<br>PERFORMED AND<br>THE PHASE (I OR E)<br>THE SYSTEM IS IN | PROCESS<br>OP REG<br>CHECK RESET          | CHECK RESET<br>KEY | CHECK WILL NOT BE DETECTED<br>DURING AN I-OP CYCLE                                                                                                                                                                                                                                                                                                                                                                                                                         |

| STORAGE-<br>ADDRESS<br>REGISTER | PARITY<br>AND<br>VALIDITY | END OF CYCLE IN WHICH CHECK IS DETECTED              | BIT COMBINATION<br>THAT CAUSED THE<br>ERROR                                                    | PROCESS<br>STORAGE-ADDRESS<br>CHECK RESET | CHECK RESET<br>KEY | THE CHECK IS MADE AFTER THE FULL<br>ADDRESS HAS BEEN ENTERED                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                 | WRAP-<br>AROUND           |                                                      | DEPENDS UPON THE<br>OPERATION BEING<br>PERFORMED AND<br>THE MODIFICATION                       | PROCESS<br>STORAGE-ADDRESS<br>CHECK RESET | CHECK RESET<br>KEY | CAN BE MODIFIED BY +1 OR BY -1                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 |                           |                                                      |                                                                                                |                                           |                    | NOTE: IF ANY OF THE ABOVE CHECKS OCCUR DURING AN INPUT-OUTPUT OPERATION, THAT OPERATION IS COMPLETED BEFORE THE SYSTEM STOPS.                                                                                                                                                                                                                                                                                                                                              |

Figure 2. Process Unit Check Conditions

# **Data Flow Diagrams**

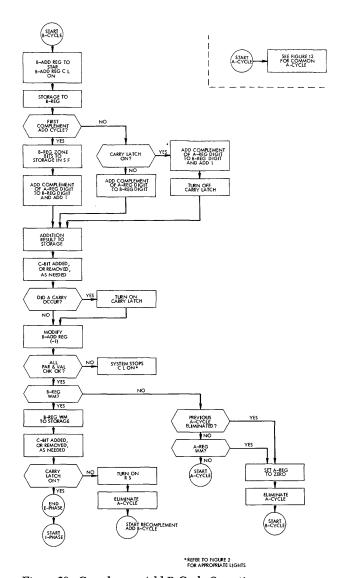

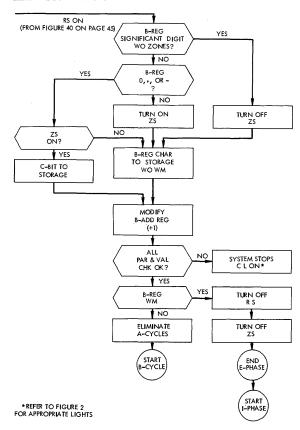

The positive logic approach is used in the data-flow diagrams. For example, all register modification is shown. If register modification is bypassed for any reason, it will not be shown (rather than show it as not happening). If a latch or trigger is shown turned on, it remains on until shown turned off or until it is automatically reset on during the next I-Op cycle. For example, if all A-cycles are eliminated, it will remain that way until the next I-Op cycle, or until the system is instructed to start an A-cycle.

# **Abbreviations and Symbols**

The abbreviations and symbols used in the data-flow diagrams are shown in Figure 3.

| A-REG     | A-register                                                                          |

|-----------|-------------------------------------------------------------------------------------|

| A-ADD REG | A-address register                                                                  |

| B-REG     | B-register                                                                          |

| B-ADD REG | B-address register                                                                  |

| СВ        | Circuit breaker(s)                                                                  |

| CHAR      | Character; all bits, including zone bits, digit bits, word mark bit, and check bit. |

| СНК       | Check                                                                               |

| CL      | Console Light(s)                                       |

|---------|--------------------------------------------------------|

| DIGIT   | The 1, 2, 4, and 8 bits and C-bit as required.         |

| E-PHASE | The machine cycles required to execute an instruction. |

HUND Hundred

I-ADD REG Instruction-address register

I-OP The portion of the I-phase when the operation code is handled by the system.

I-PHASE The machine cycles required to read out an instruction from core storage.

NSI Next Sequential Instruction

PAR Parity

POS Position

RS

R B Read back into core storage from the Bregister. The entire character is placed

in the core storage location specified by

the Storage Address Register. This is the

location it was originally read out of.

Reverse Scan. Data is read out of core storage starting at the high-order position (lower address) and ending at the low-order position (higher address). This is the reverse of a forward scan operation where data is read out of core storage starting at the low-order position and ending at the high-order position. When a reverse scan is initiated after a forward scan, the high-order position is readdressed by keeping the previous core storage location in the Storage Address

Register.

STAR Storage Address Register

S F Standard Form -- applies to sign indication. Any field is considered plus if it

has any zone bit combination other than a B-bit alone. Standard form for a plus sign is an A- and a B-bit combination.

THOU Thousand

TRIG Trigger

VAL Validity

WM Word Mark

WO Without

Z S Zero Suppress

Figure 3. Abbreviations and Symbols

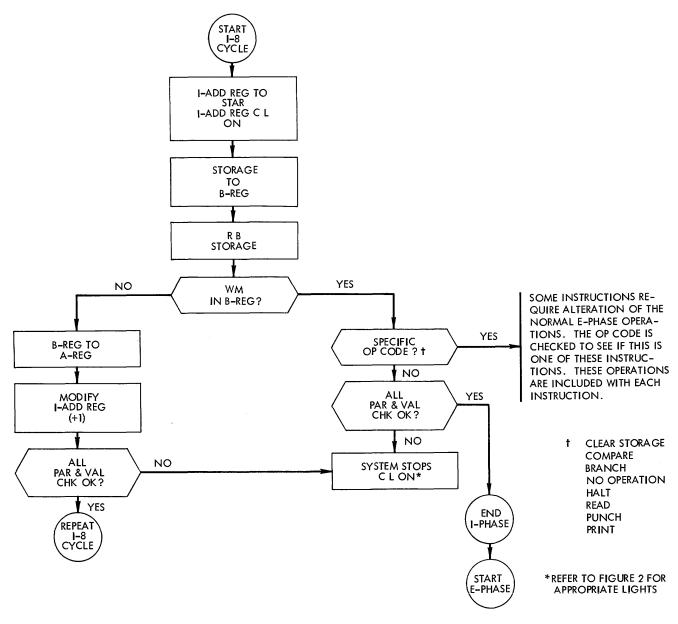

# Instruction Reading (I-Phase)

All operations executed by an IBM 1401 Data Processing System are initiated by a stored-program instruction.

The instruction is read first, and then the operation specified by the instruction is executed. The system operating time used to read one complete instruction from core storage is called the instruction (I) phase of the instruction. The time used to execute the specified operation is called the execute (E) phase.

#### I-Phase

The I-phase is divided into 11.5  $\mu$ s storage cycles, called I-cycles. A total of nine I-cycles (I-Op, I-1, through I-8) is indicated, but the exact number of I-cycles taken during any I-phase depends on the instruction length. Each instruction character reads out of storage on a separate I-cycle. An additional I-cycle is needed to recognize the end of the instruction (the first word mark encountered after an I-Op cycle).

Two exceptions to this rule are the SET WORD MARK (two addresses) and the unconditional branch instructions. The I-phase portion of the operation is automatically ended after the I-7 cycle on the SET WORD MARK operation and after the I-4 cycle on the unconditional branch operation.

As each character is read out of core storage and placed in its proper register, it is also transferred back into core storage for later use.

#### **Active Components**

There are four components that both receive and transmit data during an I-phase. These components are the I-address register, the storage-address register, the core-storage area, and the B-register.

#### I-ADDRESS REGISTER

During I-phase, the I-address register (I-Add. Reg.) specifies the core-storage position that is read out next, with one exception. This is during branch operations when the A-Add. Reg. specifies the core-storage position that reads out next. This address is transferred to the storage-address register, which does the actual corestorage addressing. The address in the I-Add. Reg. is modified by +1 so that another instruction character can be read out on the following storage cycle.

#### STORAGE-ADDRESS REGISTER

The storage-address register (STAR) sets up the corestorage selection circuitry so that the requested corestorage position contents read out to the B-register.

#### CORE STORAGE

The core-storage area reads out the contents of the specified core-storage position to the B-register.

# B-REGISTER

The B-register accepts the core-storage read-out and, depending on the I-cycle involved, transmits it to other

registers. It also sends the instruction character back into core storage where it is stored in the same position from which it came.

There are other registers that receive certain instruction-word characters. For the most part, however, these are stored in the registers for use during the E-phase. These registers and their contents are pointed out when they receive the data.

The various I-cycle operations are shown as they appear during a single-cycle operation.

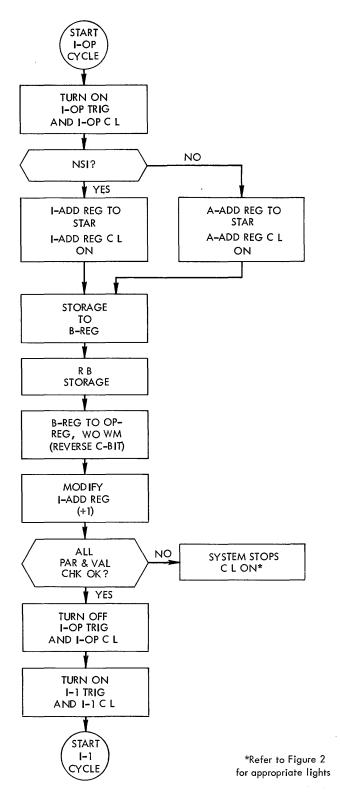

# I-Op Cycle (Figure 4)

The I-phase is started when the last execute cycle completion signals the system to end the E-phase and start the I-phase. The first I-phase trigger (I-Op) is turned on and the op instruction-length light on the 1401 console panel turns on.

The controlling circuitry now determines the starting address of the instruction that will be read out of core storage during this I-phase. If the next sequential instruction (NSI) in the stored program is used, the I-Add. Reg. already contains the core-storage address of its first character. This address was established during the previous I-phase. The address in the I-Add. Reg. is transferred to the STAR and the I-Add. Reg. keylight on the 1401 console panel turns on. The STAR lights on the console panel display the core-storage position being addressed (in BCD bit form).

NOTE: If the previous instruction was a branch instruction, and a branch was initiated, the core-storage address in the A-Add. Reg. is used. The A-Add. Reg. obtained this address (the I-address of a branch instruction) during the previous I-phase when the branch instruction was read out of core storage.

The STAR activates the lines that cause the specified core-storage position to read out to the B-register where the contents of that position are displayed in BCD form. This core-storage position contains the operation code of the instruction. From the B-register, the Opcode character:

- 1. is transferred back into core storage where it is stored in the same position it came from

- 2. is transferred into the Op-register. During the transfer, the character is stripped of the word mark, and a C-bit is added or deleted (depends on original bit configuration) for parity purposes.

The core-storage position specified in the I-Add. Reg. is changed by adding one to it. This is accomplished by reading out the contents of the STAR and adding one to it before reading it back into the I-Add. Reg. The I-Add. Reg. now contains the address of the character that follows the Op-code character.

The parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. (An Op-register par-

Figure 4. I-Op Cycle

ity or validity check will not show up during an I-Op cycle, however.)

If no check condition occurs, the I-Op trigger is turned off. This turns off the op instruction length light on the console panel and turns on the I-1 trigger. The

I-1 instruction length light on the console panel is then turned on.

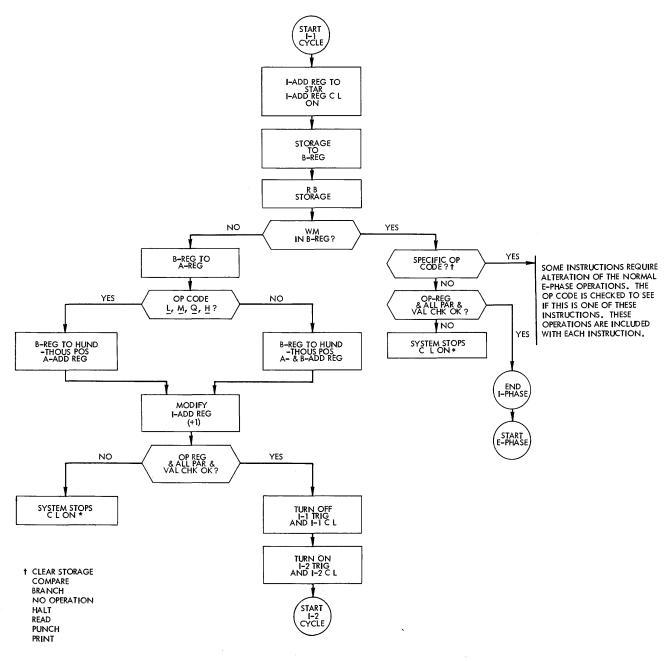

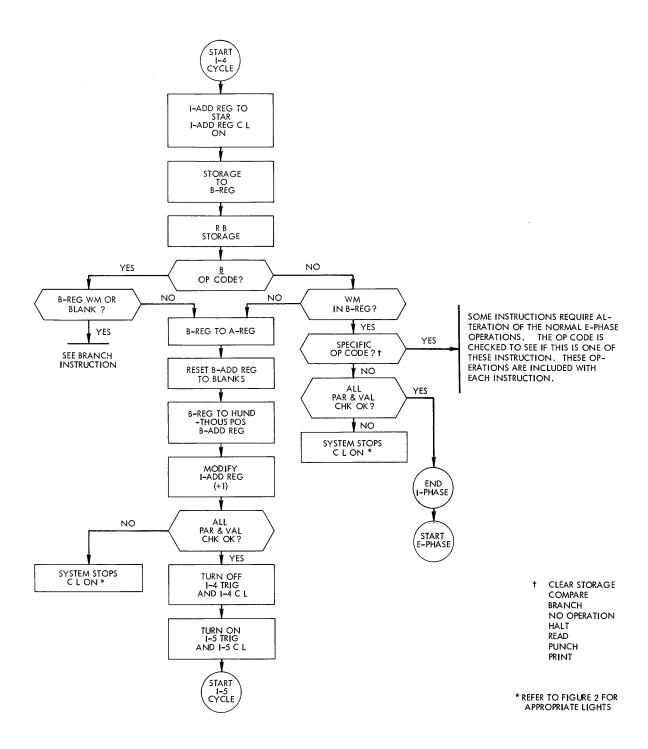

# I-1 Cycle (Figure 5)

The I-1 trigger and its associated I-1 instruction-length light turn on when the I-Op trigger turns off. The I-Add. Reg. already contains the core-storage location of the second instruction character. (Actually, the STAR already contains the core-storage location of the second instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage, and is also checked to see if the character has a word mark associated with it (signifying another Op code).

#### 1-CHARACTER INSTRUCTION

Normally, the second character of an instruction is the hundreds-thousands position of an A-field address. If the character does have a word mark, it means that this character is the Op code for the next instruction. Only one character has been read out of core storage (Op code) so the previous addresses in the A- and B-address registers will be used in the execution of this instruction if this is a *chaining* type of operation.

The previous Op code (read out during the I-Op cycle) is checked to see if it is one of the Op codes that has to set up the alteration of some of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the Op-register and all other appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins.

# 2-CHARACTER INSTRUCTION

If this second character does not have a word mark, it means that the instruction is at least two characters long. It may be only two characters long, but this cannot be established until I-2 cycle time. Because of this possibility, the character is transferred from the B-register to the A-register. The A-register normally stores the operation modifier character and, in a 2-character instruction, the second character would be the modifier.

#### OTHER LENGTH INSTRUCTION

Because this might be a longer-length instruction, the character must be stored in the hundreds-thousands position of the A- and B-Add. Reg. However, for certain operations, the character should be placed in the hundreds-thousands position of the A-Add. Reg. only.

\*REFER TO FIGURE 2 FOR APPROPRIATE LIGHTS

Figure 5. I-1 Cycle

The Op code is checked, and if it is an <u>L</u>, <u>M</u>, <u>Q</u>, or <u>H</u> Op code, the character enters the A-Add. Reg. only. If it is not one of these codes, it is placed in the hundreds-thousands position of the A-Add. Reg. and B-Add. Reg.

The address in the I-Add. Reg. is increased by one, and the Op-register and all other appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-1 trigger and its associated console light are

turned off. This turns on the I-2 trigger and its associated console light.

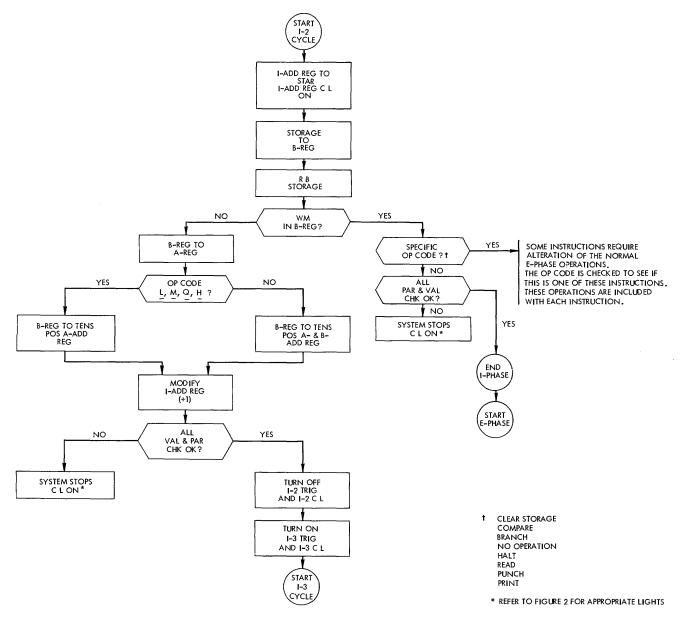

# I-2 Cycle (Figure 6)

The I-2 trigger and its associated instruction-length light are turned on when the I-1 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the third instruction character. (Actually, the STAR already contains the core-storage location of the third instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part

Figure 6. I-2 Cycle

of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage and is also checked to see if the character has a word mark associated with it (signifying another Op code).

# 2-CHARACTER INSTRUCTION

Normally, the third character of an instruction is the tens-position character of an A-field address. If the character does have a word mark, it means that this character is the Op code for the next instruction. The two characters read out of core storage make up the complete instruction.

The previous Op code (read out during the I-Op cycle) is checked to see if it is one of the Op codes that has to set up the alteration of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins.

#### OTHER LENGTH INSTRUCTION

If this third character does not have a word mark, it means that the instruction is at least four characters long (Op code plus one 3-character address). It may be longer, but this cannot be established now.

The character is transferred from the B-register to the A-register, where it replaces the character that was stored there during the I-1 cycle. This character could not be an operation modifier character, but it is still stored in the A-register.

Also, the character must be stored in the tens position of the A- and B-Add. Reg. However, for certain operations, the character should be placed in the tens position of the A-Add. Reg. only. The Op code is checked, and if it is an <u>L</u>, <u>M</u>, <u>Q</u>, or <u>H</u> Op code, the character enters the A-Add. Reg. only. If it is not one of these codes, it is placed in the tens position of the A-Add. Reg. and B-Add. Reg.

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-2 trigger and its associated console light are turned off. This turns on the I-3 trigger and its associated console light.

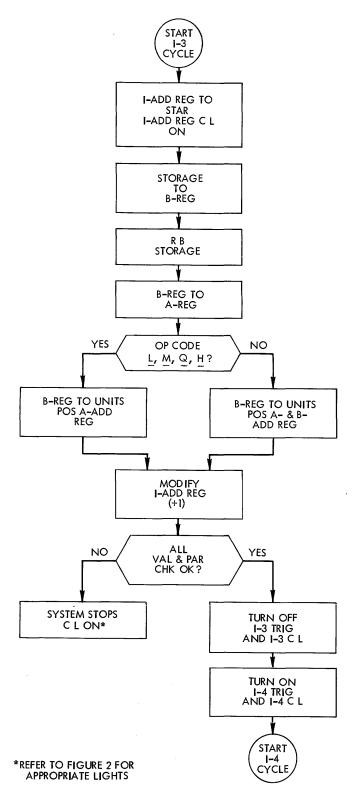

# I-3 Cycle (Figure 7)

The I-3 trigger and its associated instruction-length light are turned on when the I-2 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the fourth instruction character. (Actually, the STAR already contains the core-storage location of the fourth instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage and read into the A-register.

It is possible that this may be the last character of the instruction, but this cannot be established before the next I-cycle. Regardless of the final length, this fourth character must be stored in the units position of the A-Add. Reg. and B-Add. Reg. However, the same conditions present during the I-1 and I-2 cycles are still valid here. The Op code is checked, and if it is an <u>L</u>, <u>M</u>, <u>Q</u>, or <u>H</u> Op code, the character enters the units position of the A-Add. Reg. only. If it is not one of these Op codes, it is placed in the units position of the A-Add. Reg. and B-Add. Reg.

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-3 trigger and its associated console light are turned off. This turns on the I-4 trigger and its associated console light.

Figure 7. I-3 Cycle

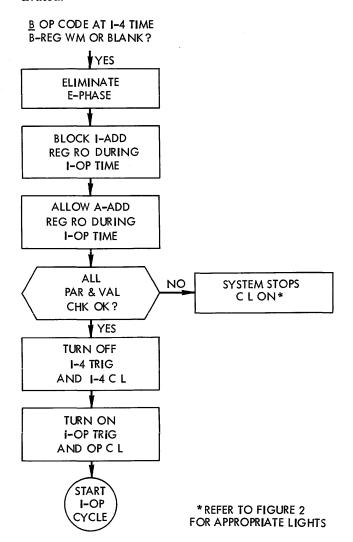

#### I-4 Cycle (Figure 8)

The I-4 trigger and its associated instruction-length light are turned on when the I-3 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the fifth instruction character. (Actually, the

Figure 8. I-4 Cycle

STAR already contains the core-storage location of the fifth instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage.

# BRANCH INSTRUCTION

The Op code stored in the Op-register is checked to see if it is a <u>B</u>. If it is a <u>B</u>, then the B-register contents are checked to see if it is a blank character (C-bit only), or whether the character has a word mark associated with it. If either of these conditions are present, it signifies a branch instruction (unconditional). Refer to the Branch instruction for the remainder of the operation.

If it is still a B Op code, but the B-register contains

something else, it signifies a BRANCH IF INDICATOR ON instruction or a BRANCH IF CHARACTER EQUAL instruction. The B-register then sends this fifth instruction character (the operation-modifier character) to the A-register and the hundreds-thousands position of the B-Add. Reg. (B-Add. Reg. previously reset to blanks).

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system, and turns on the appropriate check lights on the console panel.

If no check condition occurs, the I-4 trigger and its associated console light are turned off. This turns on the I-5 trigger and its associated console light.

#### OTHER INSTRUCTION

If the Op code stored in the Op-register is not a <u>B</u>, then the character in the B-register is checked for an associated word mark. If there is no word mark, then the B-register contents are sent to the A-register and the hundreds-thousands position of the B-Add. Reg. (B-

Figure 9. I-5 Cycle

Add. Reg. previously reset to blanks). The I-Add. Reg. modification, the parity and validity checking, and the I-cycle progression previously described now occur.

If there is a word mark in the B-register (signifying a new Op code), then the Op code read out during the I-Op cycle is checked to see if it is one of the Op codes that has to set up the alteration of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins.

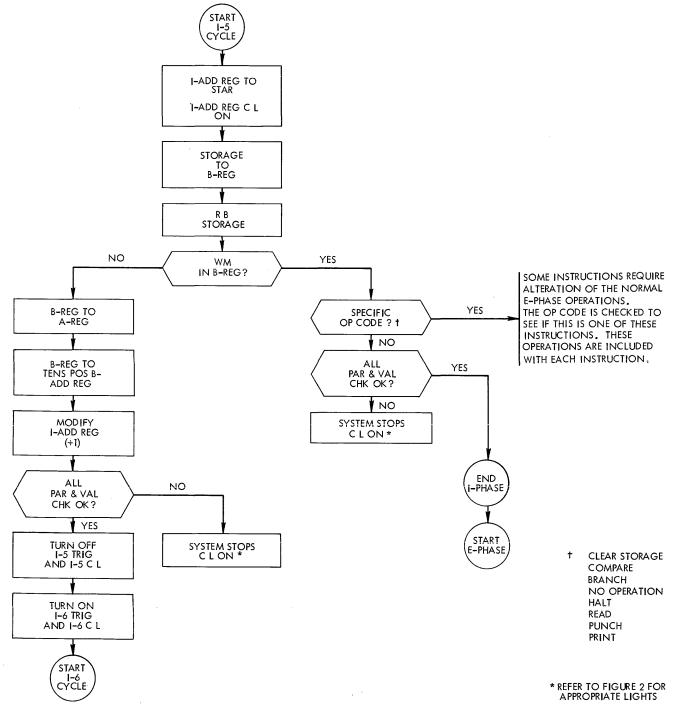

# I-5 Cycle (Figure 9)

The I-5 trigger and its associated instruction-length light are turned on when the I-4 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the sixth instruction character. (Actually, the STAR already contains the core-storage location of the sixth instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage, and the character is also checked to see if it has a word mark associated with it (signifying another Op code).

#### 5-CHARACTER INSTRUCTION

If the character has a word mark associated with it, then the five preceding characters constitute a complete instruction (Op code, a 3-character address, and an operation-modifier character). The Op code read out during the I-Op cycle is checked to see if it is one of the Op codes that has to set up the alteration of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins.

# OTHER INSTRUCTION

If the character does not have a word mark associated with it, then the B-register contents are sent to the A-register and the tens position of the B-Add. Reg.

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-5 trigger and its associated console light are turned off. This turns on the I-6 trigger and its associated console light.

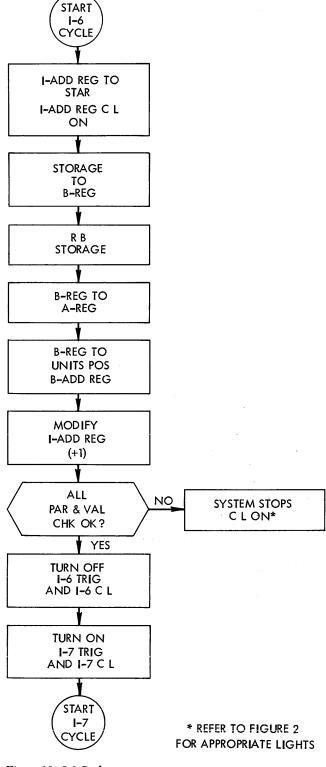

# I-6 Cycle (Figure 10)

The I-6 trigger and its associated instruction-length light are turned on when the I-5 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the seventh instruction character. (Actually, the STAR already contains the core-storage location of

Figure 10. I-6 Cycle

the seventh instruction character. This address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage, and read into the A-register, and read into the

units position of the B-Add. Reg.

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-6 trigger and its associated console light are turned off. This turns on the I-7 trigger and its associated console light.

Figure 11. I-7 Cycle

\*REFER TO FIGURE 2 FOR APPROPRIATE LIGHTS

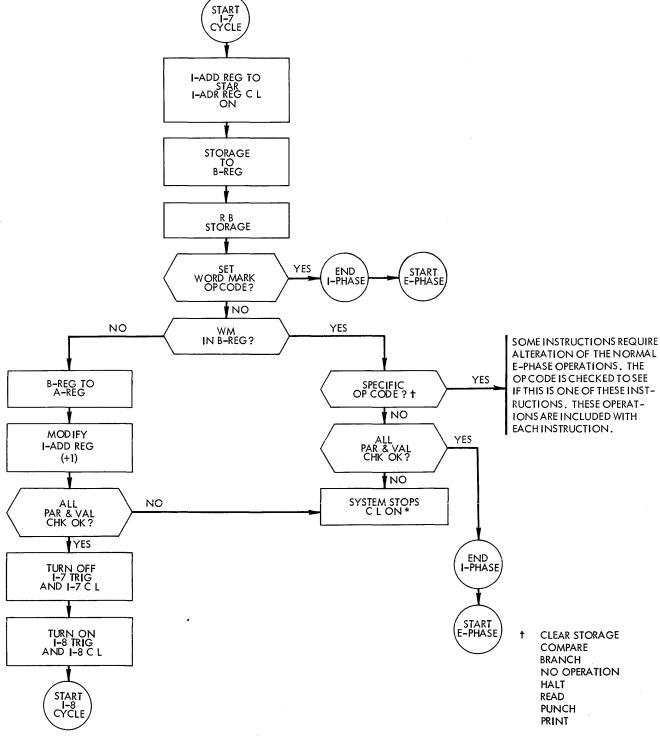

# I-7 Cycle (Figure 11)

The I-7 trigger and its associated instruction-length light are turned on when the I-6 trigger is turned off. The I-Add. Reg. already contains the core-storage location of the eighth instruction character. (Actually, the STAR already contains the core-storage location of the eighth instruction character. The address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage.

#### SET WORD MARK INSTRUCTION

The Op code stored in the Op-register is checked to see if it is a *set word mark* Op code. If it is, the I-phase ends and the E-phase begins. This is done so that word marks can be set in specified core-storage locations during the program-loading routine.

If the Op code stored in the Op-register is not a *set* word mark Op code, then the B-register character is checked to see if it has a word mark associated with it (signifying another Op code).

#### 7-CHARACTER INSTRUCTION

If the character has a word mark associated with it, then the seven preceding characters constitute a complete instruction (Op code and two 3-character addresses). The Op code read out during the I-Op cycle is checked to see if it is one of the Op codes that has to set up alteration of some of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check conditions occur, the I-phase ends and the E-phase begins.

# OTHER INSTRUCTION

If the character does not have a word mark associated with it, then the character must be an operation-modifier character, and the B-register contents are sent to the A-register.

The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-7 trigger and its associated console light are turned off. This turns on the I-8 trigger and its associated console light.

# I-8 Cycle (Figure 12)

The I-8 trigger and its associated instruction-length light are turned on when the I-7 trigger is turned off.

The I-Add. Reg. already contains the core-storage location of the next character, which should be the Op-code character of the next instruction. (Actually, the STAR already contains this core-storage location. The address was transferred from the I-Add. Reg. to the STAR in the last part of the previous I-cycle, but this is not evident during a single-cycle operation.) This address is transferred to the STAR, which then addresses core storage. The character is read out of storage and into the B-register. From the B-register it is read back into core storage. The character is also checked to see if it has a word mark associated with it (signifying another Op code).

#### 8-CHARACTER INSTRUCTION

If the character has a word mark associated with it, then the eight preceding characters institute a complete instruction (Op code, two 3-character addresses, and an operation-modifier character). The Op code read out during the I-Op cycle is checked to see if it is one of the Op codes that has to set up alteration of some of the normal E-phase operations before the actual instruction execution begins. If E-phase alteration is not needed, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check conditions occur, the I-phase ends and the E-phase begins.

# PROGRAMMING ERROR

If the character does not have a word mark associated with it, then the B-register contents are sent to the A-register. The address in the I-Add. Reg. is increased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, then the I-8 cycle is repeated until a character with a word mark is read out of core storage. This condition signifies poor programming technique because the program has gaps between sequential instructions.

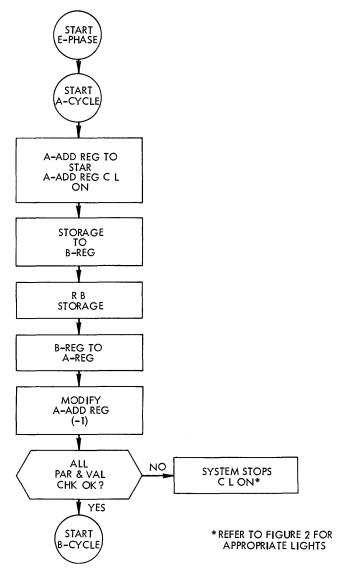

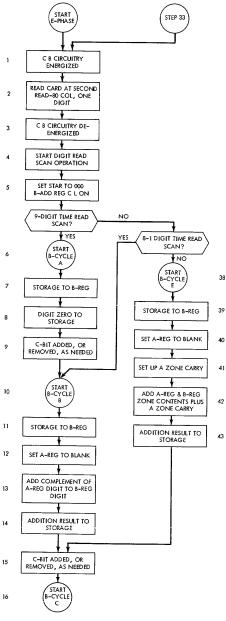

# Instruction Execution (E-Phase)

Normally, the word mark associated with the Op code of the next instruction signals the end of the I-phase. Ending the I-phase automatically starts the E-(execute) phase.

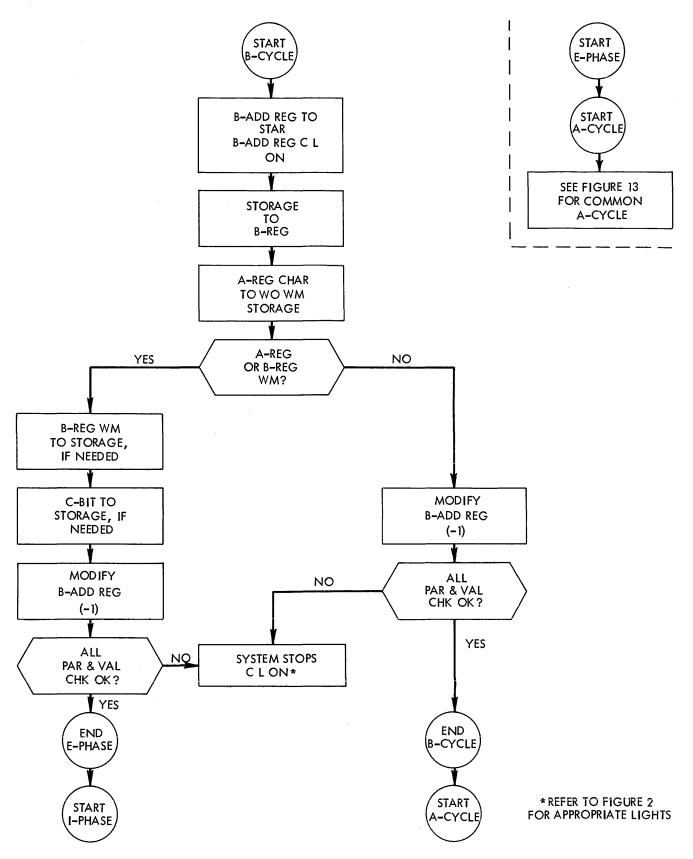

The E-phase is the system operating time necessary to perform the operation specified by the instruction read out during I-phase. The E-phase is made up of A-cycles and/or B-cycles. During an A-cycle, one position of data from the previously-specified A-field is read out of core storage. During a B-cycle, one position of data from the previously-specified B-field is read out of core storage.

Figure 12. I-8 Cycle

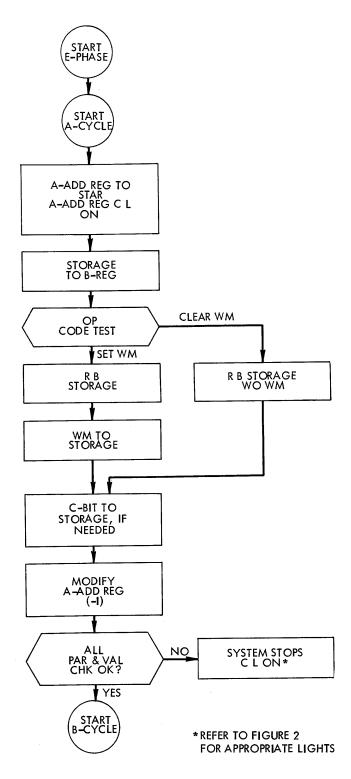

# A-Cycle (Figure 13)

The first cycle during any E-phase is usually an A-cycle (some instructions have no A-cycles). The A-cycle illustrated in Figure 13 is an A-cycle operation that is common to many 1401 instructions. When discussing instructions that use the common A-cycle, reference is made to Figure 13. A-cycles that are different are covered in that instruction writeup.

The A-Add. Reg. contains the core-storage location specified in the A-address portion of the previously-read instruction. This core-storage location is, normally, the units position of the A-field. The address in the A-Add. Reg. is transferred to the STAR, and the A-Add. Reg. key-light on the 1401 console panel is turned on. The STAR lights on the console panel display the core-

storage position being addressed (in BCD bit form).

The STAR activates the lines that cause the specified core-storage position to read out to the B-register where the contents of that position are displayed in BCD form. From the B-register, it is normally read back into the core-storage position it came from, and it is also transferred to the A-register where it is displayed in BCD form.

The core-storage position specified in the A-Add. Reg. is changed by subtracting one from it. This is done because the units position of a data field occupies the highest-numbered core-storage location and the rest of the field occupies the adjacent lower-numbered corestorage locations. To perform the arithmetic functions correctly, the units digit of a field must be worked on

Figure 13. A-Cycle

first, followed by the tens digit, etc. Therefore, the address in the A-Add. Reg. must be modified by -1 each time so that the adjacent lower-numbered location is read out. This -1 modification is accomplished by reading out the contents of the STAR and subtracting one from it before reading it back into the A-Add. Reg.

The parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel.

If no check condition occurs, the A-cycle ends and the B-cycle begins (the STORE ADDRESS REGISTER instructions are exceptions).

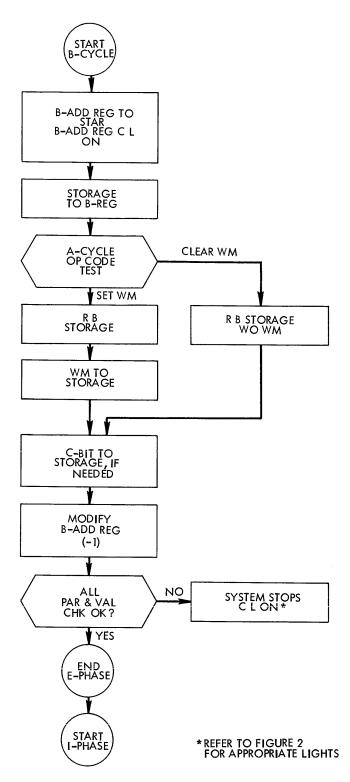

# **B-Cycle**

It is during the B-cycle that the instruction execution usually takes place. In an add operation, for instance, the actual addition of the A- and B-field characters takes place during the B-cycle and the result is stored in the B-field position. Therefore, all instructions discussed in this publication normally show the system's method of operation during a B-cycle. However, when the A-cycles differ from the common A-cycle, this difference is discussed along with any other forms of instruction execution that may be used.

#### **E-Phase Termination**

The E-phase portion of an instruction is usually ended when a word mark is sensed in the B-register. The word mark signifies that the end of that word in core storage has been reached. However, there are operations that stop only when an A-field word mark is sensed. Other operations stop only when a B-field word mark is sensed, and still other operations stop when either an A-field or a B-field word mark is sensed. These different conditions are all included in the system's internal circuitry and the actual operation termination is done automatically.

# **Logic Operations**

# Branch (<u>B</u> III)

The Branch (unconditional) instruction (<u>B</u> III) always causes the program to branch to the specified I-address. This address contains the Op code of some instruction. This branch operation is used to interrupt normal program sequence, and to continue the program at some other desired point, without testing for any specific conditions.

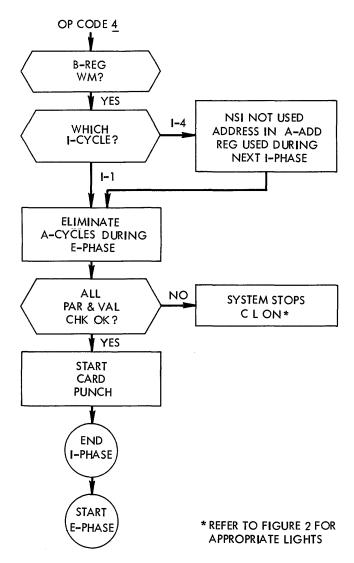

# I-Phase Operation (Figures 8 and 14)

During I-4 time of an I-phase, the Op-register is checked to see if it contains a B Op code. When a B Op code is established, the B-register is checked to see if it contains a blank character or a word mark (the Op-code position of the next sequential instruction). When one of these two conditions is established, the circuitry to eliminate the E-phase portion of this instruction is activated.

Figure 14. Branch Instruction I-Phase Operation

Also, circuitry is activated that blocks the I-Add. Reg. read-out, and allows the A-Add. Reg. read-out during the next I-Op cycle. (The A-Add. Reg. contains the I-address as specified by the instruction.)

The appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-4 trigger and its associated console light are turned off. This turns on the I-Op trigger and its associated console light. During the I-Op cycle, the core-storage position specified by the I-address (in the A-Add. Reg.) is read out of core storage, followed by a normal I-phase operation.

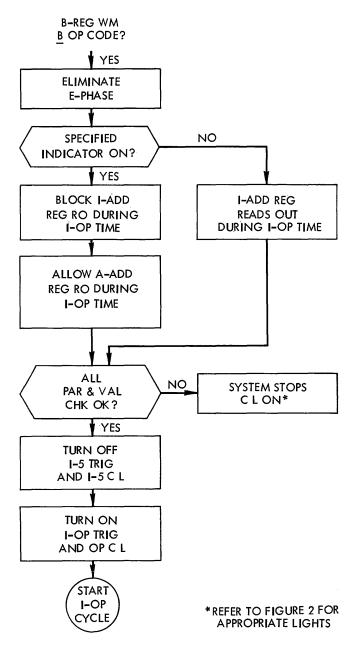

# Branch if Indicator On (B III d)

The Branch if indicator on instruction ( $\underline{B}$  III d) causes the program to branch to the specified I-address if the specified indicator, when tested, is on. If the indicator is off, the next sequential instruction is read.

#### I-Phase Operation (Figures 9 and 15)

During I-5 time of an I-phase, the B-register is checked to see if it contains a word mark. If the B-register does contain a word mark (the Op-code position of the next sequential instruction), the Op-register is checked to see if it contains a B.

When the presence of a  $\underline{B}$  Op code is established, the circuitry to eliminate the E-phase portion of this instruction is activated.

The indicator specified by the operation-modifier character (d-character) is tested to see if it is on. If the indicator is on, circuitry is activated that blocks the I-Add. Reg. read-out, and allows the A-Add. Reg. read-out during the next I-Op cycle. (The A-Add. Reg. contains the I-address as specified by the instruction.) If the indicator is not on, the normal I-Add. Reg. read-out is active during the next I-cycle.

The appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-4 trigger and its associated console light are turned off. This turns on the I-Op trigger and its associated console light. During the I-Op cycle, the core-storage position specified by either the I-address (in the A-Add. Reg.) or the I-Add. Reg. is read out of core storage.

Figure 15. Branch if Indicator On Instruction: I-Phase Operation

# Branch if Character Equal (<u>B</u> III BBB d) Branch if Word Mark and/or Zone (<u>V</u> III BBB d)

Both the Branch if character equal instruction (B III BBB d) and the branch if word mark and/or zone instruction (V III BBB d) cause the program to branch to the specified I-address if the condition specified by the operation-modifier character (d-character) is met by the character located in the specified B-address. The branch if character equal instruction tests the character at the B-address for the same bit configuration as the d-character, and branches if the bit configuration is

| Condition                        |  |

|----------------------------------|--|

| Word mark                        |  |

| No zone (No-A, No-B-bit)         |  |

| 12-zone (AB-bits)                |  |

| 11-zone (B, No-A-bit)            |  |

| Zero-zone (A, No-B-bit)          |  |

| Either a word mark, or no zone   |  |

| Either a word mark, or 12-zone   |  |

| Either a word mark, or 11-zone   |  |

| Either a word mark, or zero-zone |  |

|                                  |  |

Figure 16. Branch if Word Mark and/or Zone d-Characters and Conditions

the same. The Branch IF Word Mark and/or zone instruction tests the character at the B-address for the condition specified by the d-character, and branches if the condition is met. The d-characters and the conditions they represent are shown in Figure 16.

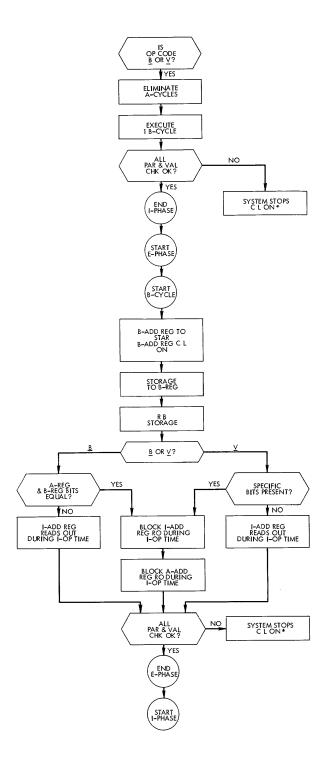

### I-Phase Set-Up Operations (Figure 17)

Some instructions require alterations of the normal E-phase operations for correct execution of the instruction. These alterations are set up before the I-phase ends. During certain I-cycles the Op code is checked to see if it is one of the Op codes that has to set up the alteration of the normal E-phase operations before the actual instruction execution begins. As soon as the word mark is sensed in the B-register, either a B or V Op code sets up the circuitry to eliminate A-cycles and execute one B-cycle. The appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins.

# Single B-Cycle (Figure 17)

The core-storage position containing the character that is checked by the d-character during this single B-cycle was previously specified by the instruction, and the address was placed in the B-Add. Reg. during I-phase. The address in the B-Add. Reg. is transferred to the STAR and the B-Add. Reg. key-light on the console panel is turned on. The STAR lights on the console panel display the core-storage position being addressed (in BCD form).

The STAR activates the lines that cause the specified core-storage position to read out to the B-register, where the contents of that position are displayed in BCD form.

The character in the B-register is read back into the core-storage position it came from. The Op code is then checked to see if it is a B or a V Op code.

#### B OP CODE

If it is a <u>B</u> Op code, then the A-register contents (the d-character) are compared against the B-register con-

\* REFER TO FIGURE 2 FOR APPROPRIATE LIGHTS

Figure 17. Branch if Character Equal and Branch if Word Mark and/or Zone Instructions: I- and E-Phase Operations

tents (the B-field character). If the bit configurations are the same, the branch to the specified I-address occurs. The circuitry is activated that blocks the I-Add. Reg. read-out, and allows the A-Add. Reg. read-out during the next I-Op cycle. (The A-Add. Reg. contains the I-address as specified by the instruction.) If the bit

configurations are not the same, the normal I-Add. Reg. read-out is active during the next I-Op cycle.

#### **Y** OP CODE

If the Op code is a <u>V</u> Op code, then the B-register contents (the B-field character) is checked to see if the bits specified by the A-register contents (the d-character) are present. If the specified bits are present, the branch to the specified I-address occurs. The circuitry is activated that blocks the I-Add. Reg. read-out, and allows the A-Add. Reg. read-out during the next I-Op cycle. (The A-Add. Reg. contains the I-address as specified by the instruction.)

If the specified bits are not present, the normal I-Add. Reg. read-out is active during the next I-Op cycle.

The appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the E-phase ends and I-phase begins.

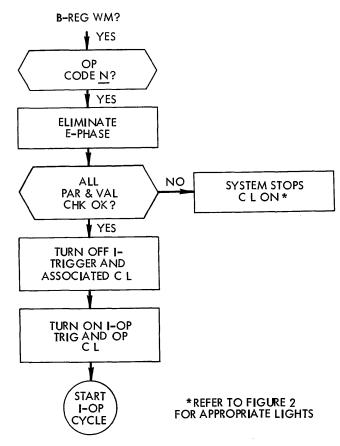

# No Operation (N)

An instruction with an  $\underline{N}$  Op code performs no operation. It can be substituted for the operation code of any instruction to make that instruction ineffective. It is commonly used in program modification to cause the program to skip over a specific instruction. This instruction skipping is accomplished by eliminating the E-phase. The instruction reading continues until the word mark of the next instruction is sensed. If characters without word marks follow an  $\underline{N}$  Op code, these characters enter the A- and B-address registers.

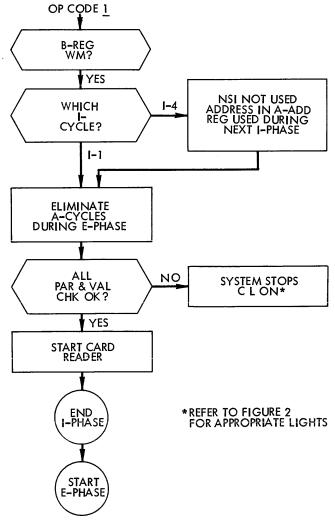

### I-Phase Operation (Figure 18)

During I-phase, a word mark in the B-register signals the end of I-phase and the beginning of E-phase. During certain I-cycles, the Op code is checked to see if any special operations must be performed before Iphase ends.

If the Op code is an N, circuitry is set up to eliminate the E-phase portion of the operations. Then the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-trigger and the associated console light that are on are turned off. The I-Op trigger and its associated console light are turned on and an I-Op cycle begins.

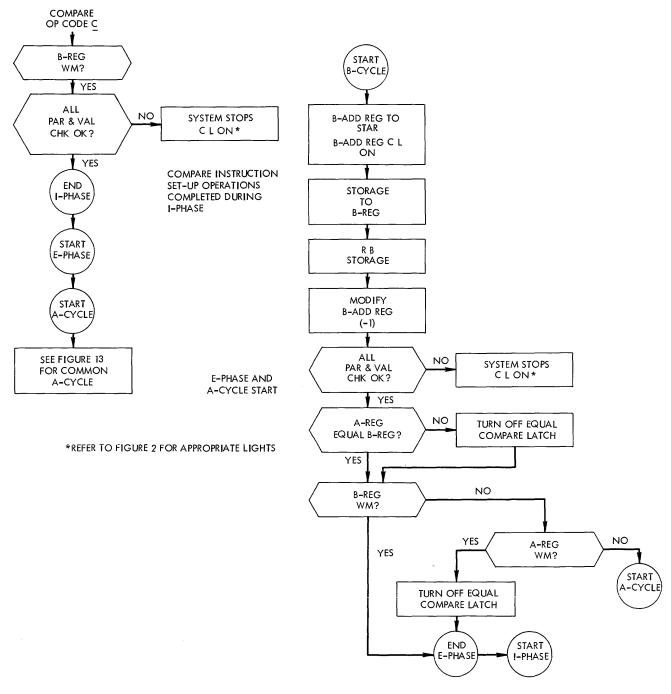

# Compare (C AAA BBB)

The COMPARE instruction compares the data in the A-field to an equal number of characters in the B-field.

Figure 18. No Operation Instruction: I-Phase Operation

The bit configuration of each character in the two fields is compared and the comparison lets the equal-compare latch stay on, or it turns the latch off. The latch setting can be tested by a BRANCH IF INDICATOR ON instruction. This latch is initially set on during I-2 time (not shown in Figure 6).

#### I-Phase Set-Up Operations (Figure 19)

Some instructions require alterations of the normal Ephase operations for correct execution of the instruction. These alterations are set up before the I-phase ends. During certain I-cycles the Op code is checked to see if it is one of the Op codes that has to set up the alteration of the normal E-phase operations before the actual instruction execution begins. As soon as a word mark is sensed in the B-register, the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the I-phase ends and the E-phase begins. The first cycle executed during the E-phase is an A-cycle. The common A-cycle previously described (see Figure 13 and the accompanying text) is used during the A-cycle portion of the E-phase. As soon as the A-cycle is successfully completed, the B-cycle begins.

# **B-Cycle (Figure 19)**

The core-storage position containing the B-field character compared by the A-field character during this B-cycle was previously specified by the instruction, and the address was placed in the B-Add. Reg. during I-phase. The address in the B-Add. Reg. is transferred to the STAR and the B-Add. Reg. key-light on the console panel is turned on. The STAR lights on the console panel display the core-storage position being addressed (in BCD form).

The STAR activates the lines that cause the specified core-storage position to read out to the B-register, where the contents of that position are displayed in BCD form.

The character in the B-register is read back into the core-storage position from which it came. The address in the B-Add. Reg. is decreased by one, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the A-field character bit configuration is compared against the B-field character bit configuration.

If the character comparison results in an unequal condition, the equal-compare latch, which was turned on during the I-phase, is turned off. The latch remains on if the characters are equal.

The B-register is then checked to see if it contains a word mark. If a word mark is present, the E-phase ends and the I-phase for the next instruction begins.

If no word mark is present in the B-register, then the A-register is checked to see if it contains a word mark. If no word mark is present in the A-register, then the compare operation is continued and another A-cycle is started. If a word mark is present in the A-register, it signifies the presence of a B-field that is longer than the A-field and it results in an unequal condition. The equal-compare latch is turned off, followed by the ending of the E-phase and the starting of the I-phase for the next instruction.

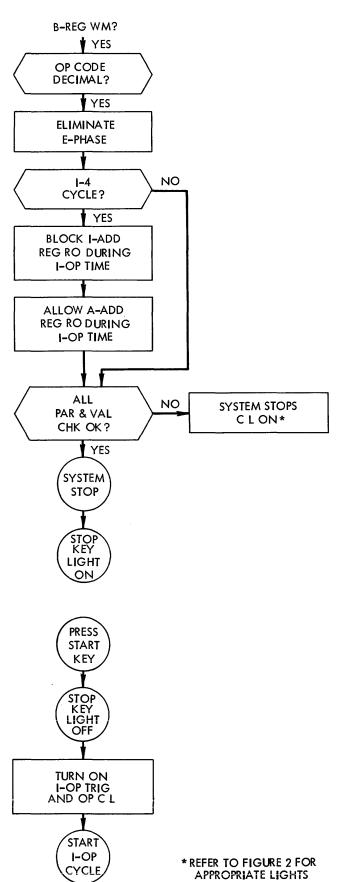

# Halt (<u>●</u>) Halt and Branch (<u>●</u>III)

Both the HALT instruction (•) and the HALT AND BRANCH instruction (• III) cause a system stop, and turn on the stop key-light on the 1401 console panel.

If the instruction is a HALT instruction only, operating the start key causes the program to start at the next instruction in sequence.

If the instruction is a HALT AND BRANCH instruction, operating the start key causes the program to start at the specified I-address.

Figure 19. Compare Instruction: I- and E-Phase Operation

# I-Phase Operation (Figure 20)

During the I-phase cycle that has a word mark in the B-register, the Op-register is checked to see if it contains a decimal. When the presence of a decimal Op code is established, the circuitry that eliminates the E-phase portion of this instruction is activated.

The present I-phase cycle must be determined. If the I-phase cycle is I-4, circuitry is activated that blocks the I-Add. Reg. read-out, and allows the A-Add. Reg. read-out during the next I-Op cycle. (The A-Add. Reg. contains the I-address as specified by the instruction.)

If the I-phase cycle is not I-4, the normal I-Add. Reg. read-out is active during the next I-cycle.

The appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the circuitry that stops the system is activated and the stop key-light on the 1401 console panel turns on.

Operating the start key on the console panel turns off the stop key-light and turns on the I-Op trigger and its associated console light. Depending on the operation,

Figure 20. Halt and Halt and Branch Instructions: I-Phase Operation

the core-storage position specified by either the I-address (in the A-Add. Reg.), or the I-Add. Reg. will be read out of core storage during this I-Op cycle.

# **Arithmetic Operations**

The add, subtract, zero and add, and zero and subtract operation codes are used to perform the system's arithmetic operations. The use of add-to-storage logic in the IBM 1401 eliminates the need for special-purpose accumulators or counters in the system. Because any group of storage positions can be used as an accumulating field, the capacity for arithmetic functions is not limited by a predetermined number of counter positions.

| SIGN  | BCD CODE BIT<br>CONFIGURATION | CARD CODE<br>CONFIGURATION |

|-------|-------------------------------|----------------------------|

| Plus  | No A– or B–bit                | No-Zone                    |

| Plus  | A– and B–bits                 | 12-Zone                    |

| Minus | B–bit only                    | 11-Zone                    |

| Plus  | A–bit only                    | 0-Zone                     |

Figure 21. Sign Bit Equivalents

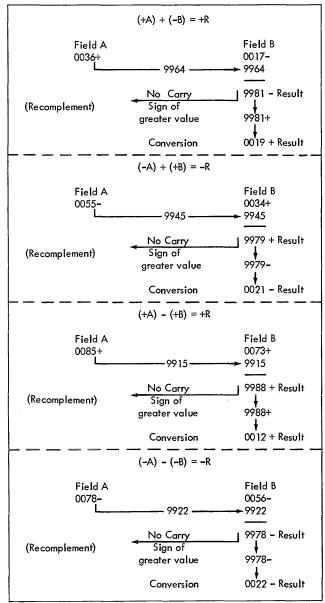

All arithmetic operations are performed under complete algebraic sign control. Figure 21 shows the four possible combinations of zone bits and the values of the signs they represent. When the system signs a field, it is done in the standard form. A positive factor is indicated with an A- and a B-bit, and a negative factor is indicated with a B-bit. The sign of the resultant field is determined by the type of operation and the signs and values of the data fields as shown in Figure 22.

| TYPE<br>OF<br>OPER. | A-FLD.<br>SIGN | B-FLD.<br>SIGN | TYPE OF ADD<br>CYCLE | SIGN OF<br>RESULT                           |

|---------------------|----------------|----------------|----------------------|---------------------------------------------|

|                     | +              | ÷              | True add             | +                                           |

| A<br>D+             |                | -              | Compl. add           | Sign of greater<br>value<br>(Standard Form) |

| D                   | -              | +              | Compl. add           |                                             |

| }                   |                | -              | True add             | -                                           |

| S<br>U              | +              | -              | True add             | -                                           |

| B<br>T              |                | +              | Compl. add           | Sign of greater                             |

| BT -                | -              | -              | Compl. add           | (Standard Form)                             |

| Ť                   |                | +              | True add             | +                                           |

Figure 22. Types of Add Cycles and Sign of Result for Add and Subtract Operation

# Add (A AAA BBB) and Subtract (S AAA BBB)

The add and subtract operations in the IBM 1401 Data Processing System are performed by using one of the two types of add operations incorporated in the system:

- 1. true add

- 2. complement add

The type of add operation that will be taken is determined during the first E-phase B-cycle.

# First A-Cycle

The first cycle during any E-phase is always an A-cycle. The A-Add. Reg. contains the core-storage location specified in the A-address portion of the previously-read instruction. In this instance, it is the units position of the A-field. The address in the A-Add. Reg. is transferred to the STAR, and the A-Add. Reg. key-light on the 1401 console panel turns on. The STAR lights on the console panel display the core-storage position being addressed (in BCD form).

The STAR activates the lines that cause the specified core-storage position to read out to the B-register, where the contents of that position are displayed in BCD form. The B-register contents are then read back into the core-storage position they came from, and are also transferred to the A-register. The address in the STAR is transferred back into the A-Add. Reg. without modification. The A-cycle ends and the B-cycle begins.

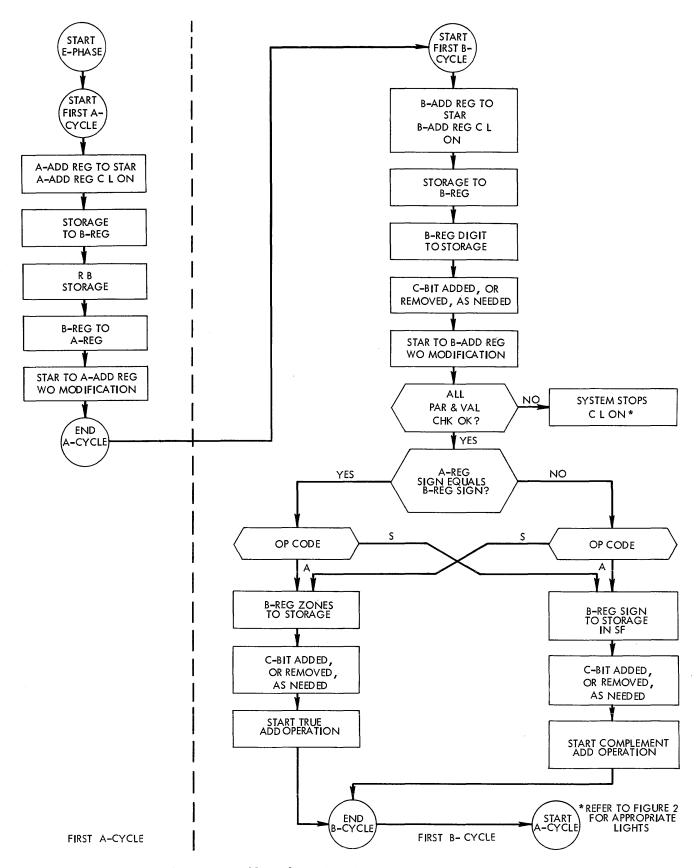

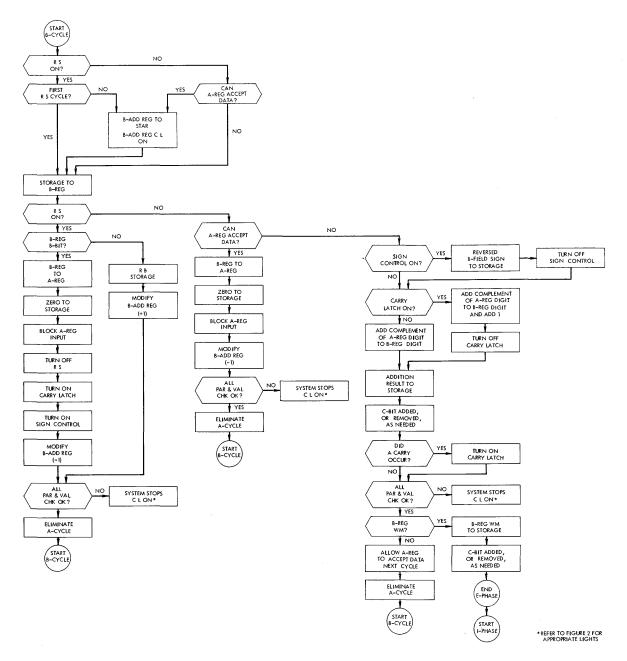

# First B-Cycle (Figure 23)

The core-storage position that is the units position of the B-field was previously specified by the instruction, and the address was placed in the B-Add. Reg. during I-phase. The address in the B-Add. Reg. is transferred to the STAR and the B-Add. Reg. key-light on the console panel is turned on. The STAR lights on the console panel display the core-storage position being addressed (in BCD form).

The STAR activates the lines that cause the specified core-storage position to read out to the B-register, where the contents of that position are displayed in BCD form.

The digit portion of the B-register contents is read back into the core-storage position from which it came. Also, a C-bit is added or removed to maintain odd-bit parity. The address in the STAR is transferred back into the B-Add. Reg. without modification, and the appropriate parity and validity checks are made. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs the A-register sign is compared against the B-register sign. The result of this comparison, in conjunction with the specified operation, determines the type of add operation performed, and determines the initial sign of the result field.

#### EOUAL SIGNS

If the A-register sign is equal to the B-register sign, and the Op Code is  $\underline{A}$  (add), then the B-register zone bits are read back into the core-storage position they came from, and a C-bit is added or removed to main-

Figure 23. First A- and B-Cycle During an Add or Subtract Operation

tain odd-bit parity. In this instance, the sign returned to storage is the sign of the resultant B-field (refer to Figure 22). The circuitry used to execute true-add operations is also activated, and the first A-cycle of the true-add operation starts when the B-cycle ends.

If the A-register sign is equal to the B-register sign, and the Op code is  $\underline{S}$  (subtract), then the B-register sign is read back in standard form into the core-storage position it came from and a C-bit is added or removed to maintain odd-bit parity. Depending on the value of the fields involved, this sign may, or may not, be the sign of the resultant B-field (refer to Figure 22). The circuitry used for executing complement-add operations is also activated, and the first A-cycle of the complement-add operation starts when the B-cycle ends.

#### UNEQUAL SIGNS

If the A-register sign is not equal to the B-register sign, and the Op code is  $\underline{S}$  (subtract), then the B-register zone bits are read back into the core-storage position they came from, and a C-bit is added or removed to maintain odd-bit parity. In this instance, the sign returned to storage is the sign of the resultant B-field (refer to Figure 22). The circuitry used for executing true-add operations is also activated and the first A-cycle of the true-add operation starts when the B-cycle ends.

If the A-register sign is not equal to the B-register sign, and the Op code is  $\underline{A}$  (add), then the B-register sign is read back in standard form into the core-storage position it came from and a C-bit is added or removed to maintain odd-bit parity. Depending on the value of the fields involved, this sign may, or may not, be the sign of the resultant B-field (refer to Figure 22). The circuitry used to execute complement-add operations is also activated, and the first A-cycle of the complement-add operation starts when the B-cycle ends.

No addition takes place during the first A- and B-cycles of an add operation (true or complement). These cycles are used to determine the type of add operation performed, and to activate the necessary circuitry.

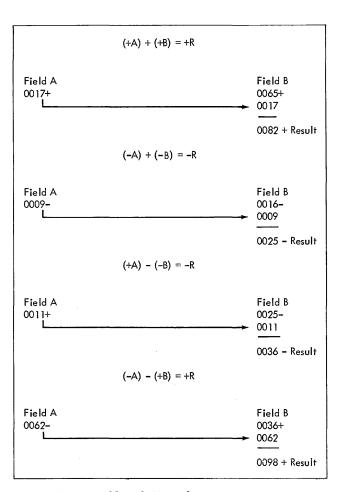

# **True-Add Operation**

The decision to execute a true-add operation is arrived at in the system by an A- and B-register sign comparison in conjunction with the specific operation (addition or subtraction) to be performed. This decision is made during the first B-cycle of an add or subtract operation. The various groups of conditions that can result in a true-add operation are shown in Figure 24. Notice that the original sign of the B-field is always the sign of the resultant B-field.

Figure 24. True-Add Cycle Examples

#### A-CYCLE

The common A-cycle previously described (see Figure 13 and the accompanying text) is used during the A-cycle portion of all true-add operations. As soon as the A-cycle is successfully completed, the B-cycle begins.

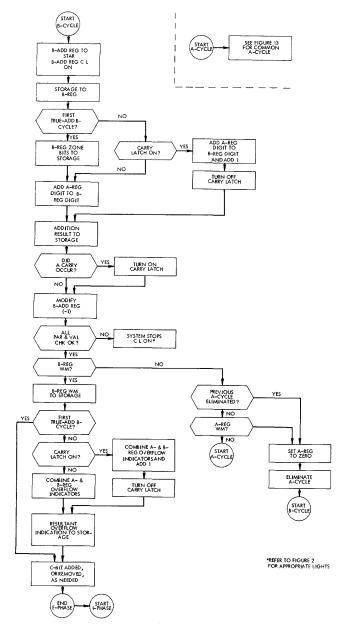

# **B-CYCLE** (FIGURE 25)

The core-storage position that receives the result of the A- and B-field digit addition during the B-cycle was previously specified by the instruction, and the address was placed in the B-Add. Reg. during I-phase. This is the units position of the B-field, and is the same position previously read out during the first B-cycle when the type of add operation was decided. During that B-cycle, there was no B-Add. Reg. modification so the B-Add. Reg. still contains the original address (see Figure 23). (This was also true for the A-Add. Reg. during its first cycle.) The address in the B-Add. Reg. is transferred to the STAR, and the B-Add. Reg. key-light on the 1401 console panel turns on. The STAR lights on the console panel display the core-storage position being addressed (in BCD form).

The operation is checked to see if this B-cycle is the first true-add B-cycle. If it is the first true-add B-cycle,

Figure 25. True-Add B-Cycle Operation

the zone portion of the B-register is read back into the core-storage position from which it came. The digit portion of the A-register is added to the digit portion of the B-register next, and then the addition result is read back into the specified core-storage location (in this case, the units position of the B-field).

If this B-cycle is not the first true-add B-cycle, then the carry latch is checked to see if it was turned on during the previous B-cycle. If the carry latch is not on, then the digit portion of the A-register is added to the digit portion of the B-register, and the addition result is read back into the specified core-storage location. If the carry latch is on, then the digit portion of the A-register is added to the digit portion of the B-register and this result is increased by one (the carry). The carry

latch is turned off, and the addition result is then read back into the specified core-storage location.

A check is made to see if a carry resulted from this addition. If no carry occurred, the address in the B-Add. Reg. is decreased by one. If a carry occurred, then the carry latch is turned on and the B-Add. Reg. is decreased by one.

The appropriate parity and validity checks are made next. Any check condition stops the system and turns on the appropriate check lights on the console panel. If no check condition occurs, the B-register is checked to see if it contains a word mark.

If the B-register contains a word mark, it is transferred to the specified core-storage position. A check is made to see if this B-cycle is the first true-add B-cycle. If it is the first true-add B-cycle, then a C-bit is added or removed to maintain odd-bit parity in that core-storage position. Then, the E-phase ends and the I-phase of the next instruction begins. If this B-cycle is not the first true-add B-cycle, then the carry latch is checked to see if it is on. If the carry is not on, the overflow indications (zone bits) in the A-register are added to the overflow indications (zone bits) in the B-register. The resultant addition of overflow indications are transferred into the specified core-storage location, and a C-bit is added or removed to maintain odd-bit parity in that core-storage position. (Refer to Figure 26 for zone-bit configurations of overflow indications.) The E-phase ends and the I-phase of the next instruction begins.

| OVERFLOW<br>INDICATION                                     | ZONE-BIT<br>CONFIGURATION |  |

|------------------------------------------------------------|---------------------------|--|

| First overflow                                             | A-bit                     |  |

| Second overflow                                            | B-bit                     |  |

| Third overflow                                             | A- and B-bits             |  |

| Fourth overflow                                            | No A- or B-bits           |  |

| Overflow Indications 1–4 Repeated for Subsequent Overflows |                           |  |

Figure 26. Zone-Bit Configuration of Overflow Indications

If the carry latch is on, the overflow indications in the A-register are added to the overflow indications in the B-register, and this result is increased by one (the carry). The carry latch is turned off and the resultant addition of overflow indications are transferred into the specified core-storage location. A C-bit is added or removed to maintain odd-bit parity in that core-storage position. The E-phase ends and the I-phase of the next instruction begins.

If the B-register does not contain a word mark, then a check is made to see if the previous A-cycle was eliminated. The A-cycle would have been eliminated if an A-field word mark had been encountered before a B-field word mark. (If the A-field is the same length as the B-field, an A-field word mark is not needed.) If the pre-

vious A-cycle was eliminated, then a zero is generated and transferred into the A-register. Then, the circuitry is set up to eliminate the next A-cycle and another Bcycle starts.

If the previous A-cycle was not eliminated, then the A-register is checked to see if it contains a word mark. If the A-register does not contain a word mark, then the next A-cycle begins. If the A-register does contain a word mark, it signifies that the end of the A-field has been reached before the end of the B-field. A zero is generated and transferred into the A-register. Then, the circuitry is set up to eliminate the next A-cycle and another B-cycle starts.

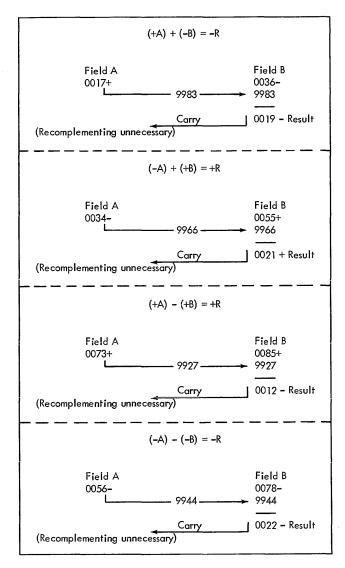

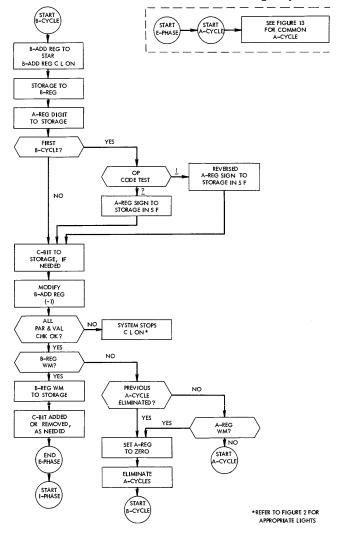

# **Complement-Add Operation**

The decision to execute a complement-add operation is arrived at in the system by an A- and B-register sign comparison in conjunction with the specific operation (addition or subtraction) to be performed. This decision

Figure 27. Complement-Add Cycle Examples

is made during the first B-cycle of an add or subtract operation. The various groups of conditions that can result in a complement-add operation are shown in Figures 27 and 28.

The system converts the A-field factor to its nines complement figure and adds it to the B-field factor (plus one initial carry). When the addition is over, the system initiates a carry test to determine whether a carry occurred from the high-order position of the B-field. The presence of a carry indicates that the result in the B-field is a true figure (Figure 27). The original sign of the B-field is the sign of the result (in standard form).