Reference Manual IBM 1620 Data Processing System

## MAJOR REVISION (July 1961)

This edition, A26-4500-2, renders obsolete A26-4500-1. Because significant changes have been made throughout the manual, this new edition should be reviewed in its entirety. Information has been added on the following new subjects:

| Subject Pa                               | ıge |

|------------------------------------------|-----|

| Transfer Numerical Strip                 | 2   |

| Transfer Numerical Fill                  |     |

| Move Flag 3                              | 0   |

| Tape Splicing 3                          | _   |

| Manual Adjustments to Typewriter 3       |     |

| Appendix E: Storage Register Functions 7 | 1   |

| Appendix F: 1620 Operating Modes 7       | 1   |

Address comments regarding this publication to: IBM, Product Publications Department, San Jose, California

# Contents

| Page                                                                                   | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Introduction 5                                                                         | Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Data Representation                                                                    | Keys, Indicator Displays, and Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Modes of Operation10                                                                   | Console Operating Procedures58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Computer Instructions                                                                  | Program Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Instruction Characteristics                                                            | Program Languages68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Arithmetic Instructions                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Internal Data Transmission Instructions       21         Compare Instructions       23 | Annendix A. Evecution Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Branch Instructions 23 Branch Instructions 24                                          | Appendix A — Execution Times70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input/Output Instructions                                                              | A 10 B. A.L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Program Control Instructions                                                           | Appendix B — Add Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

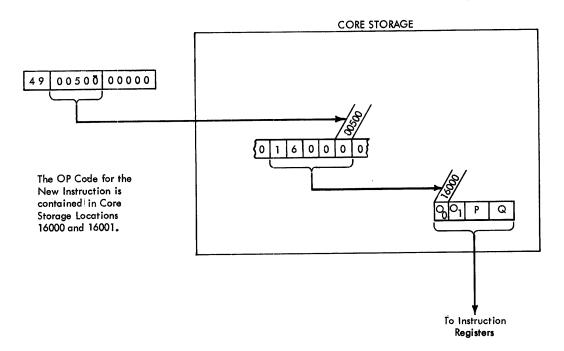

| Indirect Addressing – Special Feature                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                        | Appendix C — Multiply Table70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Components35                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Typewriter                                                                             | Appendix D — 1620 Character Coding71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Paper Tape and Paper Tape Code                                                         | The state of the s |

| 1624 Tape Punch                                                                        | Appendix E — 1620 Storage Register Functions $\dots 71$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1621 Paper Tape Reader       38         1622 Card Read-Punch Unit       42             | 1020 Sidiuge Register Functions71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1623 Core Storage Unit                                                                 | Assess II II 1400 o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2020 Otto Brotage Offic                                                                | Appendix F — 1620 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

IBM 1620 Data Processing System

The IBM 1620 Data Processing System is an electronic computer system designed for scientific and technological applications. The use of solid-state circuit components and the availability of from 20,000 to 60,000 positions of core storage provide the 1620 system with the capacity, reliability, and speed to solve problems that in the past have required the use of larger and more expensive data processing systems.

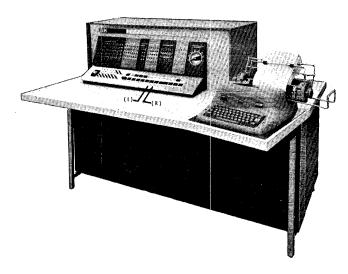

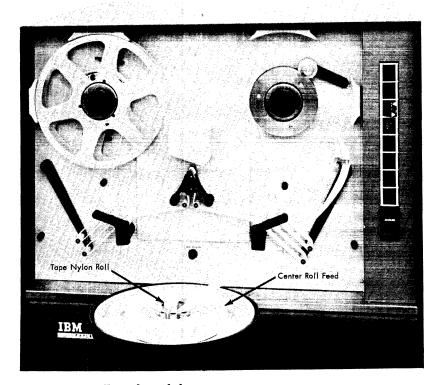

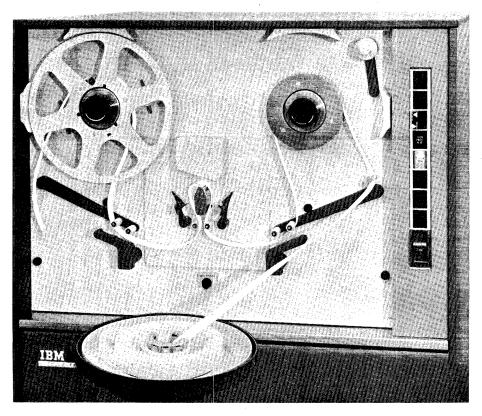

Four units (see Frontispiece) are available with the IBM 1620 Data Processing System.

The IBM 1620 Central Processing Unit contains the computer, 20,000 positions of core storage, a console panel, and an input/output (I/O) typewriter. Paper tape I/O operations are permitted by the IBM 1621 Paper Tape Reader unit, which also includes the paper tape controls and the IBM 1624 Tape Punch.

The IBM 1622 Card Read-Punch is available for card I/O operations. The IBM 1623 Storage Unit expands the 20,000 core storage positions in the Central Processing Unit of the 1620 to 40,000 or 60,000 positions. The 1623 Model 1 contains 20,000 additional positions and the 1623 Model 2 contains 40,000 additional positions. Except where otherwise specifically noted, this manual is concerned with the standard 20,000-position 1620.

Data and instructions entered into the system are placed in core storage as decimal digits. Each position of core storage can be addressed individually and can store one digit of information by the use of a six-bit binary-coded decimal (BCD) code. The addressing system provides for the selection of any digit, or group of digits, in core storage. As a standard feature, the 1620 computer processes alphabetic and special characters.

The arithmetic and logic section of the computer is directed by the stored program. The computer performs 39 different operations, using a 2-address instruction format. The format is explained under instruction characteristics. Each 12-digit instruction includes a 2-digit operation code and two 5-digit addresses. Use of the 2-address format and automatic sequential execution of the programmed instructions simplify programming and reduce the number of instructions required to solve a problem. The sequence of operations may be altered at any point in the program by unconditional or conditional branch instructions. Conditional branch instructions provide logical decisions through tests performed on a system of indicators and switches set by the computer or by the operator.

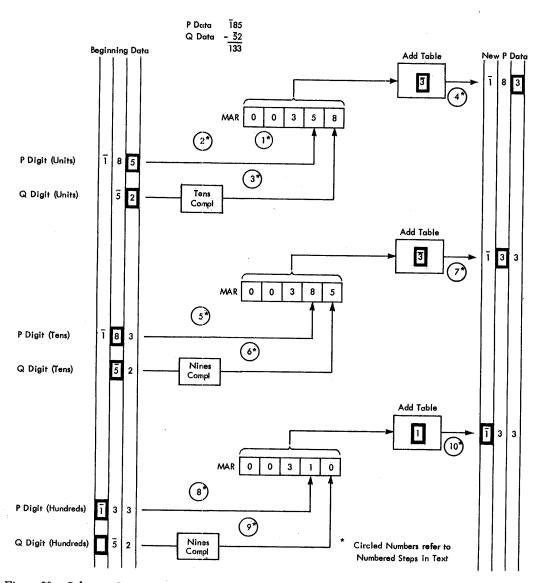

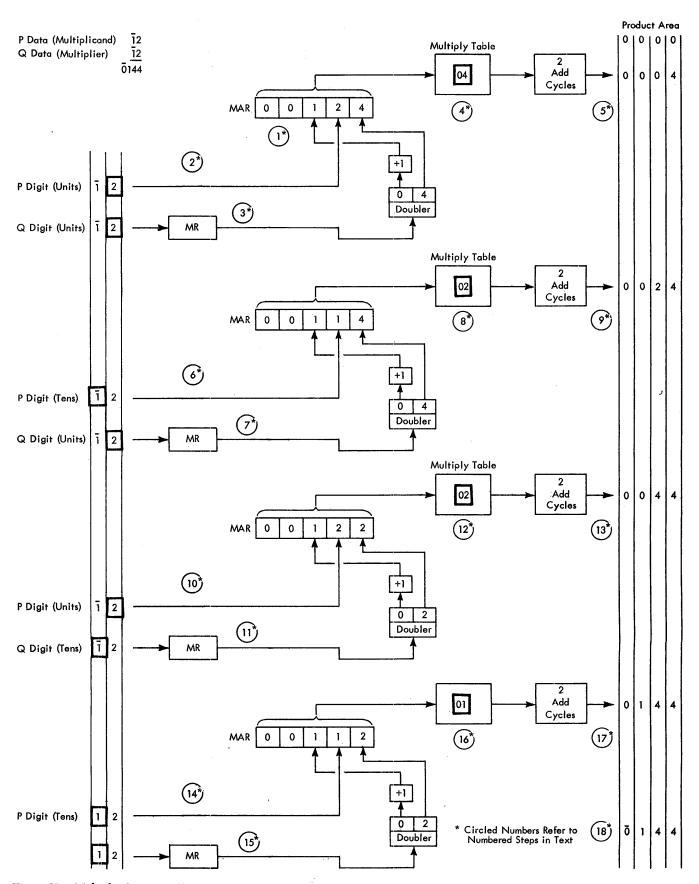

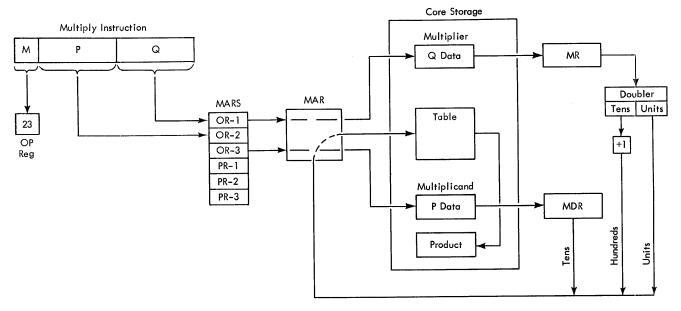

Addition, subtraction, and multiplication operations

are accomplished by a table lookup method, in which Add and Multiply tables located in specified areas of core storage are referred to automatically when arithmetic operations are being performed. Division is accomplished by a division subroutine or by the automatic divide feature.

The IBM 1620 is a variable field length computer. The shortest admissible field is two digits (a field is a unit of information composed of related consecutively addressed digits); the longest field can be any number of digits within the capacity of available core storage positions. Not only can data fields be stored in core storage in varying sizes, but these same variable fields can also serve as factors in all arithmetic operations without being edited for size or position. Accuracy of results is ensured by automatic validity checking which operates when the data enters, exits, or is processed inside the system.

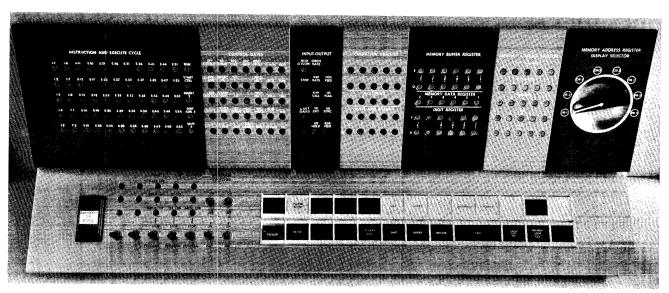

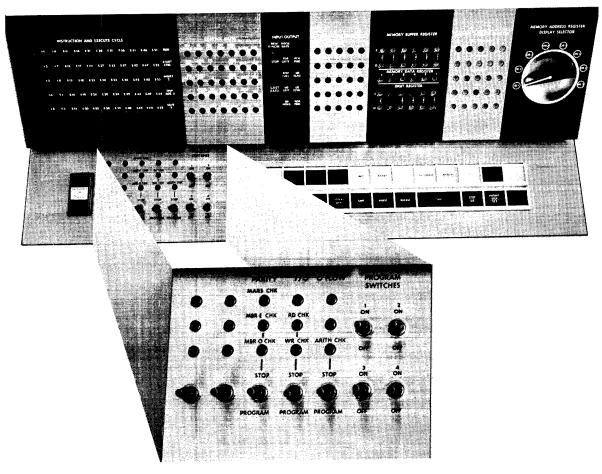

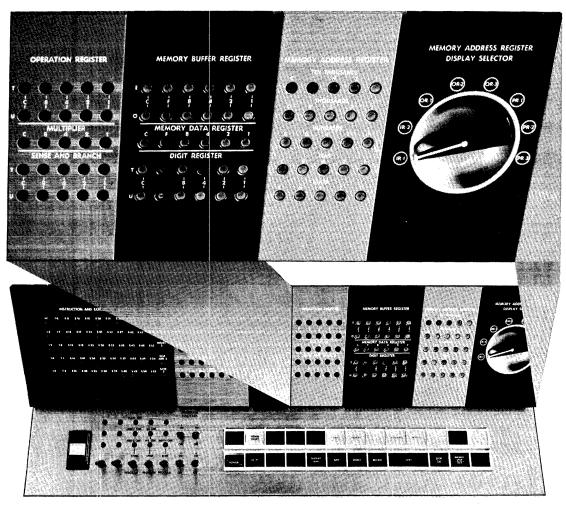

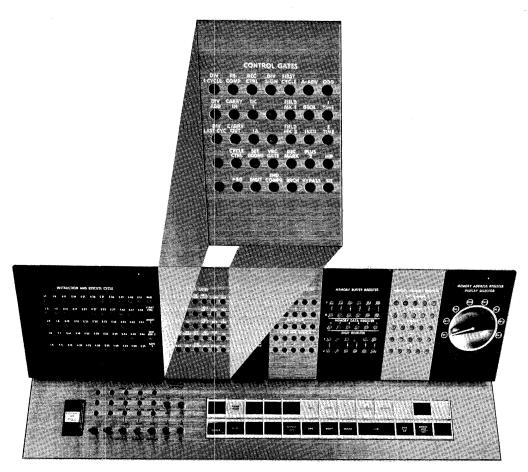

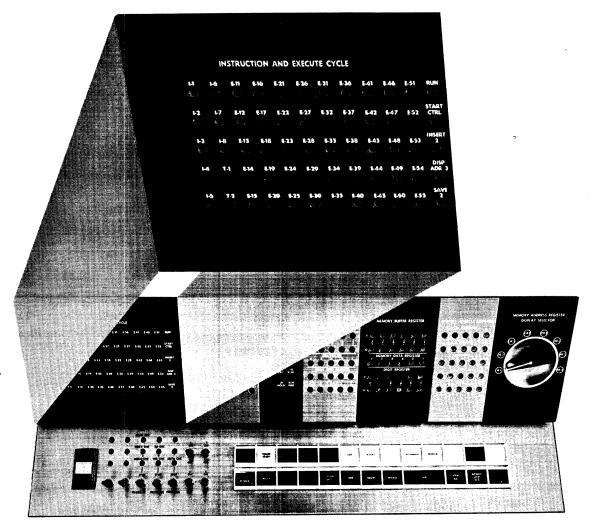

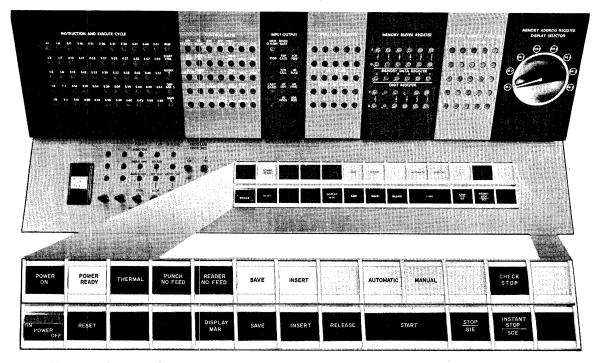

As shown in the Frontispiece, the console of the 1620 contains control keys, switches, an indicator panel, and a typewriter. The control keys and switches are used for manual or automatic operation of the system. The console panel provides visual indication of the status of various registers, indicators, and I/O conditions. The typewriter provides direct entry of data and instructions into core storage; it also provides a permanent log of the operator's intervention during the execution of a program.

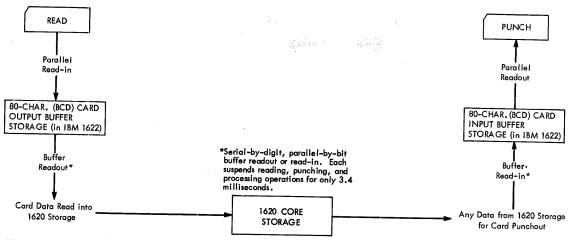

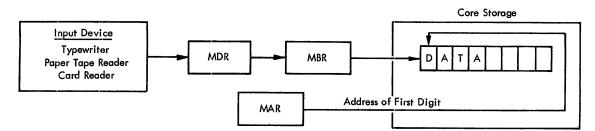

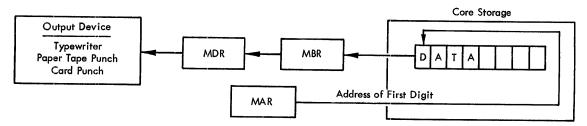

Information is entered into the system by input devices: namely, the IBM 1621 Paper Tape Reader, the IBM 1622 Card Read-Punch, and the typewriter. The 1622 reads 80-column cards at a maximum rate of 250 cards per minute. The 1621 reads an 8-track paper tape at the rate of 150 characters per second. The operator's typing speed determines the rate of entry of information through the typewriter.

Output devices, the IBM 1622 Card Read-Punch, the 1624 Tape Punch, and a typewriter, record processed data. The typewriter prints at a maximum rate of 10 characters per second; the card punch and tape punch operate at the rate of 125 cards per minute and 15 characters per second, respectively.

Preparation of programs for the 1620 is simplified by IBM advanced programming systems and the IBM library of utility routines. These programs are similar to those used with the IBM 650, 1401, 704, 705, 709, 7070, and 7090 Data Processing Systems. The Symbolic Programming System (sps) simplifies programming by reducing

the clerical work involved. sps assembles a program written in mnemonic and symbolic notation by converting the symbols to machine language and assigning locations in core storage for both data and instructions. FORTRAN (FORmula TRANslation) is the term applied to another IBM programming system that translates a problem, expressed as a series of algebraic statements, into a complete machine language program, generating the step-by-step instructions necessary to solve the problem. A program written for the 1620 in FORTRAN can, with minor changes, also be compiled and executed on the IBM 7070, 704, 709, and 7090 Data Processing Systems. The library of utility routines provides a series of thoroughly tested programs that perform most of the more standardized computations and routine tasks occurring in many computer problems.

#### **Stored Program Concept**

The 1620 is a stored program computer; that is, it stores and executes its instructions internally. The computer can perform distinct operations such as adding, subtracting, multiplying, comparing, branching, and so on. It is directed to perform a specific operation by an instruction placed in core storage. To solve a problem or to process data, the programmer selects from various computer operations those necessary to do the desired work. A group of instructions representing the operations to be performed is called a program.

Once the program is placed in core storage, the computer can be directed to execute automatically the instructions composing the program. The program normally is executed in a sequential manner, that is, the computer starts with the first instruction and progresses serially through the program, interpreting and executing each instruction. However, this sequence of operations can be altered by the use of instructions that may direct the computer to an instruction located at other than the next sequential position.

## **System Configuration**

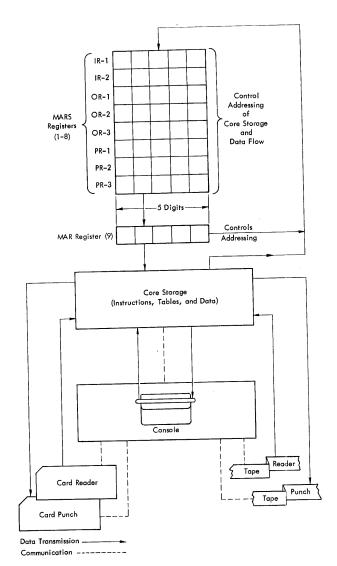

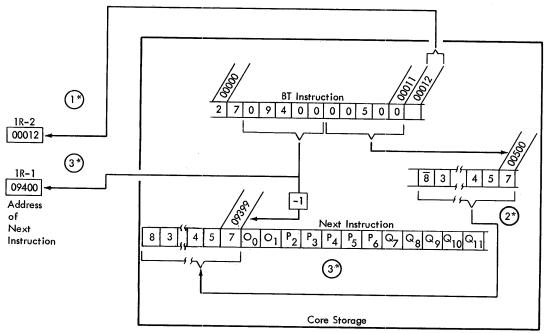

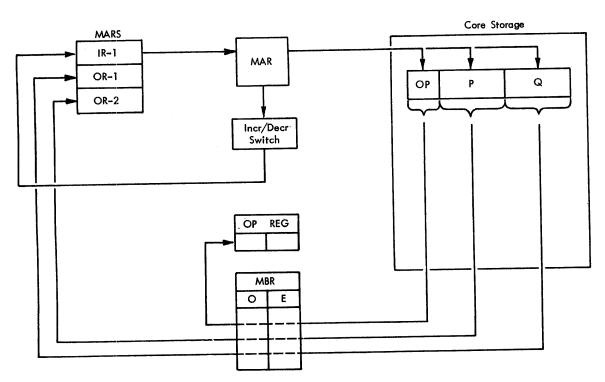

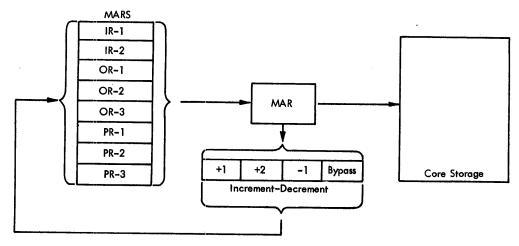

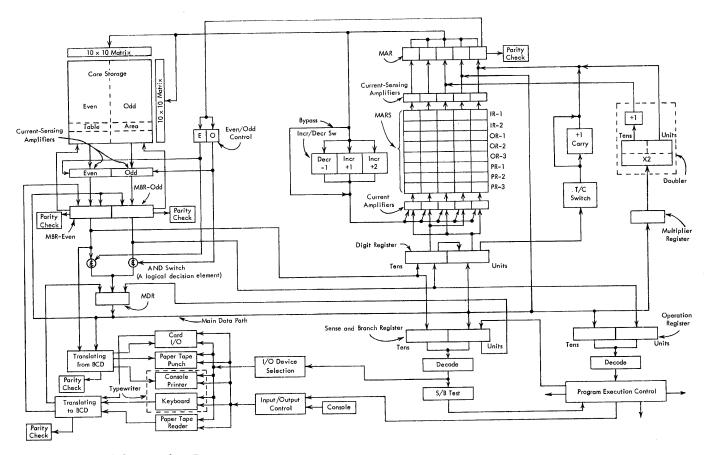

As shown in Figure 1, all input enters core storage and all output is from core storage. Eight MARS (Memory Address Register Storage) registers (see Appendix E), comprising nonaddressable core storage, control the addressing of core storage locations and the flow of data during processing. These eight 5-digit registers are:

- 1. IR-1: Instruction Address Register 1

- 2. IR-2: Instruction Address Register 2

- 3. OR-1: Operand Address Register 1

- 4. OR-2: Operand Address Register 2

- 5. OR-3: Operand Address Register 3

- 6. PR-1: Product Address Register 1

Figure 1. Diagram of 1620 System

- 7. PR-2: Product Address Register 2

- 8. PR-3: Product Address Register 3

In the basic 1620 System, these eight registers can contain 5-digit addresses from 00000 to 19999. The MARS registers address core storage through an additional 5-digit Memory Address Register (MAR), which also comprises nonaddressable cores. All addressing of core storage (for both instructions and data) is done through MAR. The operation code of the instruction determines the functions to be performed by the eight registers and the particular registers to be used.

The console is a connecting link between the computer and the I/O devices; it provides the operator with two-way communication to and from the 1620 System.

### **Data Representation**

Data can be classified as digits, fields, or records, depending upon the operation in which the data is addressed. A field is composed of related digits (distance, time, etc.) treated as a unit of information. A record consists of related fields. Additional details can be found under FIELD and RECORD.

#### **Digits**

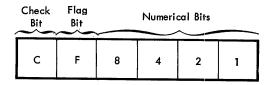

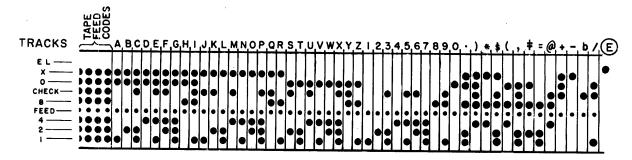

#### BCD BIT ARRAY

Each core storage position is addressable and can store one digit of information in binary-coded decimal (BCD) form (C, F, 8, 4, 2, and 1). The bit positions of each digit consist of four numerical bits, one flag (F) bit, and one check (C) bit.

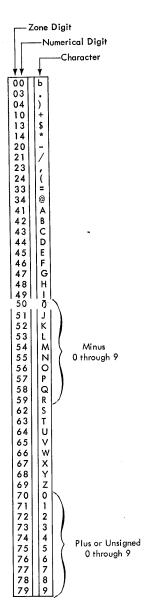

The value of a decimal digit is the sum represented by the bits present in the 8, 4, 2, and 1 numerical bit positions. Only bit combinations whose sum is nine or less are used. A minus numerical expression has a sign flag in the units position of its field. Considering only the numerical bit positions, the decimal 6 is represented as 0110, the decimal 7 as 0111, etc., as shown in Figure 2, which gives configurations for both plus (without sign) and minus (with sign) numerals.

In Figure 2, it can be seen that the C and F bit configurations for each minus numeral are opposite to those for each plus numeral, while the 8, 4, 2, and 1 configurations are the same for both. This results from the fact that an odd-bit character is required for character validity (see also CHECK BIT).

## CHECK BIT (C)

Each digit position within the computer must contain an odd number of coded bits, including a flag bit, if there is one, for correct parity. To create this odd-bit number, a C-bit is automatically added to each digit position when data enters core storage. Thereafter, during processing, a digit position with an even number of bits causes the machine to signal a parity error. A C-bit alone represents a plus zero.

#### FLAG BIT (F)

The flag bit is used in five ways, depending upon its location and the operation performed.

| D                           | igit | С | F | 8 | 4 | 2 | 1 |

|-----------------------------|------|---|---|---|---|---|---|

|                             | 0    | 1 | 0 | 0 | 0 | 0 | 0 |

| No Field Definition or Sign | 1    | 0 | 0 | 0 | 0 | 0 | 1 |

| ö                           | 2    | 0 | 0 | 0 | 0 | 1 | 0 |

| E                           | 3    | 1 | 0 | 0 | 0 | 1 | 1 |

| ini                         | 4    | 0 | 0 | 0 | 1 | 0 | 0 |

| Pe                          | 5    | 1 | 0 | 0 | 1 | 0 | 1 |

| 무                           | 6    | 1 | 0 | 0 | 1 | 1 | 0 |

| Ë                           | 7    | 0 | 0 | 0 | 1 | 1 | 1 |

| ž                           | 8    | 0 | 0 | 1 | 0 | 0 | 0 |

|                             | 9    | 1 | 0 | 1 | 0 | 0 | 1 |

| <u> </u>                    | 0    | 0 | 1 | 0 | 0 | 0 | 0 |

| N 2                         |      | 1 | 1 | 0 | 0 | 0 | 1 |

|                             |      | 1 | 1 | 0 | 0 | 1 | 0 |

| <u> </u>                    | 3    | 0 | 1 | 0 | 0 | 1 | 1 |

| Sig                         | 4    | 1 | 1 | 0 | 1 | 0 | 0 |

| ō                           | 5    | 0 | 1 | 0 | 1 | 0 | 1 |

| <u>ĕ</u>                    | 6    | 0 | 1 | 0 | 1 | 1 | 0 |

| Def                         | 7    | 1 | 1 | 0 | 1 | 1 | 1 |

| 를 [                         | 8    | 1 | 1 | 1 | 0 | 0 | 0 |

| ī,                          | 9    | 0 | 1 | 1 | 0 | 0 | 1 |

Figure 2. Bit Configuration for Decimal Digits 0 through 9

### 1. Sign Control

A numerical data field is minus if the units digit contains a flag bit, and plus if the units digit does not contain a flag bit. Minus five is shown as 5; plus five is shown as 5. The BCD representations for minus and plus five are F-4-1 and C-4-1, respectively.

A flag bit as a field mark defines the leftmost (highorder) digit of a numerical data field. A field is shown as XXXX, where the dash over the highorder digit is the field mark.

### 3. Carries

Flag bits present in certain digits of the add table are interpreted in arithmetic operations as carries. For example, an eight with a carry is shown as 8. Flag bits are contained in table storage and transferred automatically, as required.

## 4. Minus Zero

The F bit alone represents a minus zero.

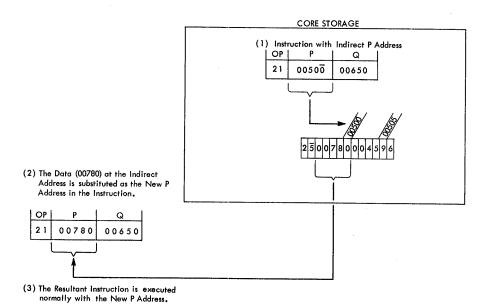

Indirect Addressing (Special Feature)

A flag bit over the units position of an instruction address (P or Q) indicates an indirect address, as explained in INDIRECT ADDRESSING.

#### RECORD MARK (‡)

The record mark is a nondecimal machine digit coded C-8-2. It is used primarily in input/output operations and in record transmission within the 1620 System; it cannot be used as a significant digit in an arithmetic or compare operation.

#### NUMERICAL BLANK

The numerical blank (coded C-8-4) is used for format control of blank columns when card punching, and cannot be used in arithmetic or compare operations. Read Numerically and Write Numerically, under INPUT/OUTPUT INSTRUCTIONS, give further details concerning the numerical blank.

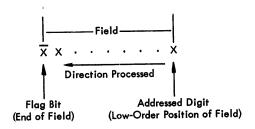

#### Field

A field consists of a number of consecutively addressed digits related to arithmetic operations and internal field transmission. A field is addressed by its rightmost (low-order) digit which occupies the *highest-numbered* core storage position of the field. Fields are processed from *right to left* into successively *lower-numbered* core storage positions until a digit with a flag bit is sensed. The shortest admissible field consists of two digits: the addressed digit and the digit containing the flag bit or field mark.

Minus numerical fields are signed by a flag bit in the addressed low-order digit. The absence of a flag bit in the addressed digit is unconditionally interpreted as a plus field.

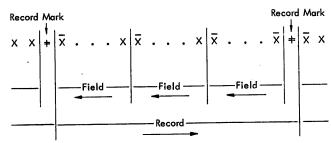

### Record

A record consists of a field or fields of related data normally grouped for input/output operations and internal record transmission. A record is addressed at the *leftmost* (high-order) digit, which occupies the *lowest-numbered* core storage position of the record. Records are processed serially from left to right into successively higher-numbered core storage positions.

Output and internal record transmission are terminated when a record mark is sensed, except for card output which is terminated only after 80 columns are transferred to 1622 buffer storage. Buffer storage data transfer is described under IBM 1622 CARD READ-PUNCH UNIT.

A record is entered into core storage, starting at the addressed digit and continuing from left to right into successively higher-numbered core storage positions until terminated by an end-of-record signal from the input unit. The end-of-record signal from paper tape

causes a record mark to be placed in core storage as the rightmost digit of the record. When input is from the typewriter, the Record Mark key must be depressed to place a record mark in core storage. When input is from punched cards, a record mark is automatically placed in core storage only when 0, 8, 2 are punched in a card column.

Arrows Indicate Direction of Processing

## **Magnetic Core Storage**

The standard 1620 contains 20,000 addressable positions of magnetic core storage. Data stored in these cores is not affected by the manual turning on or off of power if care is taken to ensure that the 1620 System is in the manual mode when power is manually turned off. (A programmed "halt" automatically places the 1620 in the manual mode. See Appendix F for information on manual mode of operation.)

Additional storage is available in the IBM 1623, Models 1 and 2, to bring the total core storage capacity of the 1620 to 40,000 or 60,000 positions.

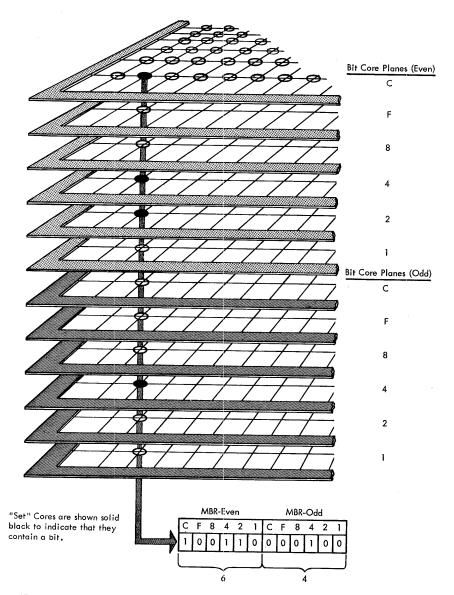

#### **Core Array**

Core storage in the 1620 is made up of 12 core planes as shown in Figure 3. Each core plane contains all cores for a specific value. The core planes are labeled C, F, 8, 4, 2, and 1. The even-address planes are the top six planes, and the odd-address planes are the bottom six planes. An even address has an even number as its units digit, while an odd address has an odd-numbered units digit.

The magnetic condition of the cores at any address determines which digit is stored at that address. A magnetic core is either in the magnetic "set" or "on" condition, or in the "reset" or "off" condition. If "set," the core contains a bit; if not, it is said to be "reset."

Readout from the 1620 core storage does not alter the "set" or "reset" condition of any core read out. Unless blocked by an immediate read-in of new data, a "data regeneration" occurs with each readout, leaving the cores in their "before readout" state. Thus read-in, but not readout, normally changes the data in the cores.

Figure 3. 1620 Core Array

### **Two-Character Transfer**

During a core storage readout cycle, which takes 20 microseconds, all cores shown by the vertical line (one core in each bit plane, Figure 3) are read out at the same time. However, only "set" cores are read out to the 2-digit MBR (Memory Buffer Register) as bits.

The function of the MBR is to receive digits entering or leaving core storage. Digits leaving storage are "regenerated" through the MBR. In effect, the MBR is subdivided into two 1-digit registers: MBR-even and MBR-odd (abbreviated as MBR-E and MBR-O). From core storage, the even-address digits flow through MBR-E, while the odd-address digits flow through MBR-O. Digits entering core storage are handled similarly, under control of the units position of the associated MAR address.

For example, an even digit in the units position of the MAR address causes data selection from MBR-E. Figure 3 shows that the C, 4, and 2 cores are "set" in the evendigit planes. The 4 core is "set" in the odd-digit planes. Thus, MBR-even and MBR-odd contain 64, the two-digit code for "U."

Because all 12 core planes are affected, any single core storage address affects two adjacent storage positions; one with an odd-numbered address and one with an even-numbered address. Even-numbered addresses affect the next higher position. For example, if the digit at address 00500 (even) is addressed and programmed to be read from core storage, the digit at address 00501 is also read. Odd-numbered addresses affect the next lower position. For example, address 00501 (odd) also

Figure 4. Alphameric Codes

affects address 00500. The selection of the digit to be used is determined by the operation to be performed. The digit actually addressed is moved to the 1-digit Memory Data Register (MDR).

Data transfer is illustrated under DATA FLOW in the Program Testing section of this manual.

#### Sequential Addressing

Core storage positions are addressed sequentially from 00000 to the highest-numbered address of the core storage positions installed: 19999, 39999, or 59999. The 1620 core storage has "wrap-around" storage: address 00000 follows the highest-numbered address when incrementing; the highest-numbered address follows 00000 when decrementing.

## **Modes of Operation**

The 1620 System can either be in the numerical or the alphameric mode when reading or writing data. The input/output instruction determines the mode used. For given data, an output instruction should place the 1620 in the same mode as did the input instruction. All 1620 modes of operation are summarized in Appendix F.

#### **Numerical Mode**

One decimal digit is required in core storage to represent a numerical character. No alphabetic or special characters, except the record mark and numerical blank, can be represented in the numerical mode.

#### **Alphameric Mode**

Two decimal digits are required in core storage to represent an alphameric character, i.e., an alphabetic character, a special character, or a numerical character. A two-digit alphameric representation of numerical characters is provided to permit reading of mixed alphabetic, special, and numerical characters without changing from an alphameric to a numerical instruction. Figure 4 shows the zone and numerical digits that have been assigned to represent all the alphameric characters used in the 1620. Complete representations of all characters for all I/O devices are given in Appendix D. These two alphameric digits must be at adjacent core storage positions, and the zone digit must occupy the even address. The 1620 accomplishes this automatically during I/O operations by addressing the numerical digit to the odd address. Figure 3 shows the bit configuration for a "U" if the 1620 is in the alphameric mode. All 1620 instructions fall into one of five general categories, according to function:

- 1. Arithmetic

- 2. Internal data transmission

- 3. Logic (compare and branch)

- 4. Input/output

- 5. Program control

During normal operation, program instructions are performed sequentially. Beginning at 00600, for example, the instructions located at 00612, 00624, and so on, are executed in order. However, this order can be changed if an instruction causes a branch to any but the next sequential instruction. This aspect of machine operation is covered under COMPARE INSTRUCTIONS and BRANCH INSTRUCTIONS.

In addition to the programming information given in this section, many programming suggestions are contained in the *IBM 1620 Data Processing System Bulletin*, *Program Writing and Testing* (Form [26-5547).

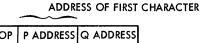

#### Instruction Characteristics

### **Instruction Format**

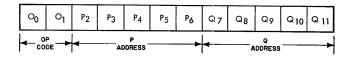

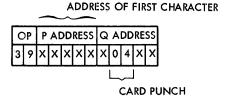

The IBM 1620 uses a 12-digit machine language instruction divided into three parts: a 2-digit operation (OP) code, a 5-digit "P" address, and a 5-digit "Q" address. Figure 5 represents the format of an instruction as it appears in core storage. The O, P, and Q subscripted numbers are used throughout the manual.

In contrast to a data field, which is addressed at its rightmost (low-order) digit and read from right to left, instructions are addressed at O<sub>0</sub>, the leftmost (high-order) digit, and read from left to right.

#### OP CODE

Upon initiation of an instruction, the OP code is placed in a 2-digit OP register and is analyzed to determine the operation to be performed. The address of an instruction must always be even, i.e., the  $O_0$  digit of an operation code must be stored in an even-num-

Figure 5. Instruction Format

bered address so that the OP register can receive both digits. Figure 6 lists the 1620 instructions, with their OP codes and associated mnemonics.

#### P ADDRESS

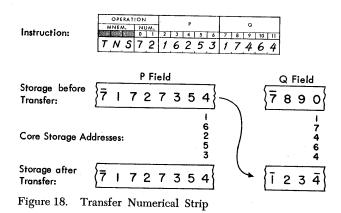

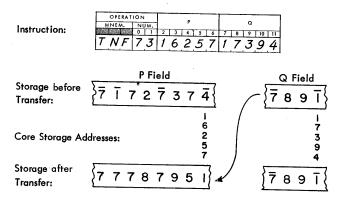

The P address specifies: (1) location to which data is transmitted, (2) location to which the program branches, (3) location from which data is transmitted (output instructions), or (4) location of the alphameric field in the Transfer Numerical Strip and Transfer Numerical Fill instructions.

| Arithmetic Instructions: | MNEMONIC | CODE |

|--------------------------|----------|------|

| Add                      | Α        | 21   |

| Add Immediate            | AM       | 11   |

| Subtract                 | S        | 22   |

| Subtract Immediate       | SM       | 12   |

| Multiply                 | M        | 23   |

| Multiply Immediate       | MM       | 13   |

| Load Dividend *          | LD       | 28   |

| Load Dividend Immediate  | * LDM    | 18   |

| Divide *                 | D        | 29   |

| Divide Immediate *       | DM       | 19   |

### Internal Data Transmission Instructions:

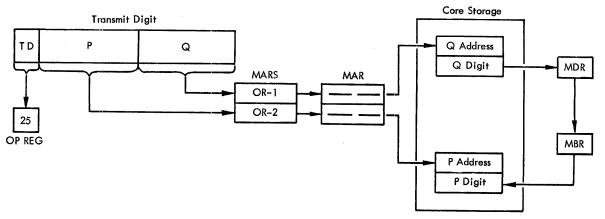

| Transmit Digit             | TD  | 25 |

|----------------------------|-----|----|

| Transmit Digit Immediate   | TDM | 15 |

| Transmit Field             | TF  | 26 |

| Transmit Field Immediate   | TFM | 16 |

| Transmit Record            | TR  | 31 |

| Transfer Numerical Strip * | TNS | 72 |

| Transfer Numerical Fill *  | TNF | 73 |

## Logic Instructions (Compare and Branch):

| Compare                       | С   | 24 |

|-------------------------------|-----|----|

| Compare Immediate             | CM  | 14 |

| Branch                        | В   | 49 |

| Branch No Flag                | BNF | 44 |

| Branch No Record Mark         | BNR | 45 |

| Branch On Digit               | BD  | 43 |

| Branch Indicator              | BI  | 46 |

| Branch No Indicator           | BNI | 47 |

| Branch and Transmit           | BT  | 27 |

| Branch and Transmit Immediate | BTM | 17 |

| Branch Back                   | BB  | 42 |

#### Input-Output Instructions:

| Read Numerically     | RN | 36 |

|----------------------|----|----|

| Write Numerically    | WN | 38 |

| Dump Numerically     | DN | 35 |

| Read Alphamerically  | RA | 37 |

| Write Alphamerically | WA | 39 |

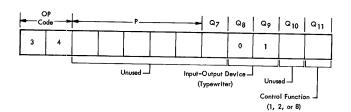

| Control              | K  | 34 |

### Program Control Instructions:

| Set Flag     | SF  | 32 |

|--------------|-----|----|

| Clear Flag   | CF  | 33 |

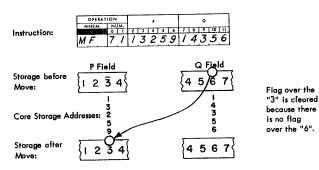

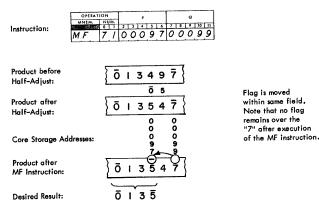

| Move Flag *  | MF  | 71 |

| Halt         | Н   | 48 |

| No Operation | NOP | 41 |

\* Special Feature

Figure 6. 1620 Instructions

#### **Q ADDRESS**

The Q address specifies: (1) location from which data is transmitted, (2) which indicator is interrogated, (3) which input/output device is used, or (4) location of the numerical field in the Transfer Numerical Strip and Transfer Numerical Fill instructions. The OP code determines how the Q address is used in an instruction.

### **Immediate Instructions**

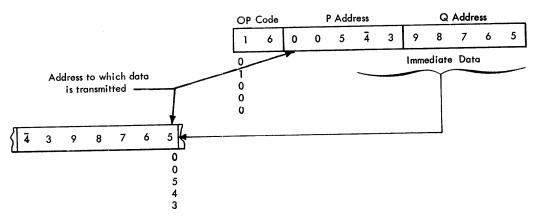

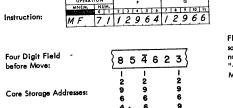

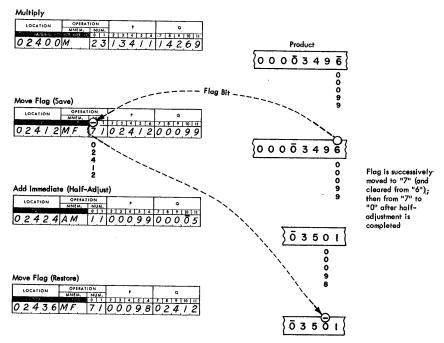

Certain arithmetic, internal data transmission, and logic instructions are labeled "immediate." In immediate instructions, the Q part represents the data used rather than the address where the data is stored. The address of the units position  $(Q_{11})$  is used for this data, and is always 11 higher than the address of the immediate instruction. The Q part of an instruction usually refers to the five digit positions Q7, Q8, Q9, Q10, and Q11. However, when the Q field is used as data in an immediate instruction, the data is not restricted to five digits; the operation continues until a flag bit (field mark) is sensed. If more than five digits of data are required, the digits in excess of five must be valid data and must also be all or part of a valid P address (and of a valid, useful OP code if more than ten data digits are required). An example in which seven digits of data are used is given in Figure 7 for a TFM instruction. The Q data is transmitted to the field beginning at the P address. Transmission continues until terminated by the flag in the P part of the instruction.

CAUTION: Because a flag in the P<sub>6</sub> position indicates an indirect address, the use of six digits of data is not advisable with a 1620 containing Indirect Addressing (covered in a later section).

#### **Operation Cycles**

Each instruction or operation performed by the computer is divided into two parts: I (Instruction) cycle and E (Execution) cycle.

#### INSTRUCTION CYCLE

During the I-cycle, an instruction is read from core storage and analyzed to establish the type of operation that is to be performed. This analysis always takes eight 20-microsecond machine cycles,  $I_1$  through  $I_8$ , for a total of 160 microseconds, and is displayed on the 1620 console during a Single Cycle Execute operation (explained elsewhere in this manual).

#### EXECUTION CYCLE

The operation specified by the instruction is carried out during the E-cycle. The number of machine cycles necessary to execute an instruction depends on the operation, the size of the data fields, and the signs of the fields (in arithmetic operations).

The last machine cycle of E-time is followed by the first machine cycle (of I-time) of the next instruction.

#### **Execution Time**

The formula for computing execution time follows the description of each instruction. Execution times for all instructions are summarized in Appendix A. The symbols used in the formulas are defined as follows:

- $D_P$ =Number of digits, including high-order zeros, in the field at the P address.

- $D_Q$ =Number of digits, including high-order zeros, in the field at the Q address.

- $D_{Q'}$ =Number of digits, including high-order zeros, in the data field of an immediate instruction.

- $D_z$ =Number of positions compared prior to the detection of a digit other than zero.

- T=Time, in microseconds (one microsecond = one millionth of a second).

Additional symbols used only in LD, LDM, D, and DM instructions are defined under EXECUTION TIME, following the explanation of the Divide instruction.

Figure 7. Transmit Field Immediate

#### **Arithmetic Instructions**

Characteristics that are similar in all 1620 arithmetic instructions are described in this section.

#### Description

Data flow, field length definition, sign indication, and indicator control are similar in all 1620 arithmetic instructions.

## DATA FLOW AND FIELD LENGTH DEFINITION

Data is read serially from right to left (low-order to high) until terminated by a flag bit defining the high-order position of the field. Where the data in a field is shown as  $\overline{285}$ , for example, the dash (flag bit) over the high-order digit indicates a field mark.

The minimum length of both the P and Q fields is two digits. The units digit contains the sign; at least one higher-order digit is needed for field definition (flag bit).

#### SIGN INDICATION

The algebraic sign of the factors and result is indicated by the presence (negative) or absence (positive) of a flag bit in the units position.

## ARITHMETIC INDICATORS

Three arithmetic indicators and their associated console lights are controlled by arithmetic instructions and turned off by the Reset key on the 1620 Console. Functions of this key are explained under RESET KEY.

High/Positive (H/P). The high/positive indicator is turned on at the beginning of each arithmetic instruction and remains on if the result is positive and not zero. It is turned off if the result is negative or zero.

Equal/Zero (E/Z). The equal/zero indicator is turned on at the beginning of each arithmetic instruction and remains on if the result is zero. It is turned off if the result is not zero.

Overflow (O'flow). The overflow indicator is turned on during the execution of add, subtract, and compare instructions, if either of the following conditions exists:

- 1. The number of digits in the Q data exceeds the number of digits in the P data. Only the number of digits in the Q data that equal the number of digits in the P data are used in developing the result.

- 2. The result causes a carry beyond the high-order position of the initial field at P. The carry is lost.

This indicator is also turned on during a divide operation if more than nine successful subtractions occur, indicating mispositioning of the divisor.

The overflow indicator is turned off by the execution of a Branch Indicator or Branch No Indicator instruction, or by manual depression of the reset key. It is not turned on automatically at the beginning of each arithmetic instruction.

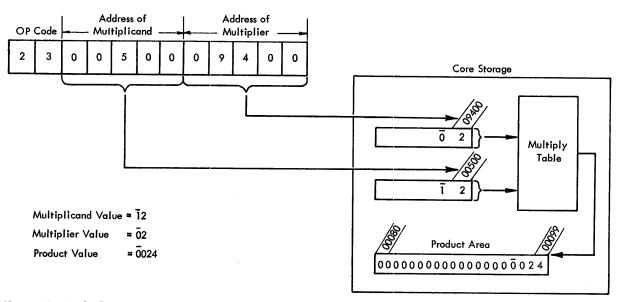

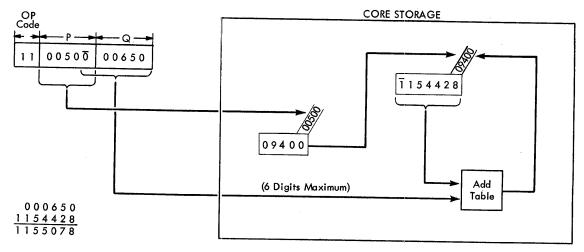

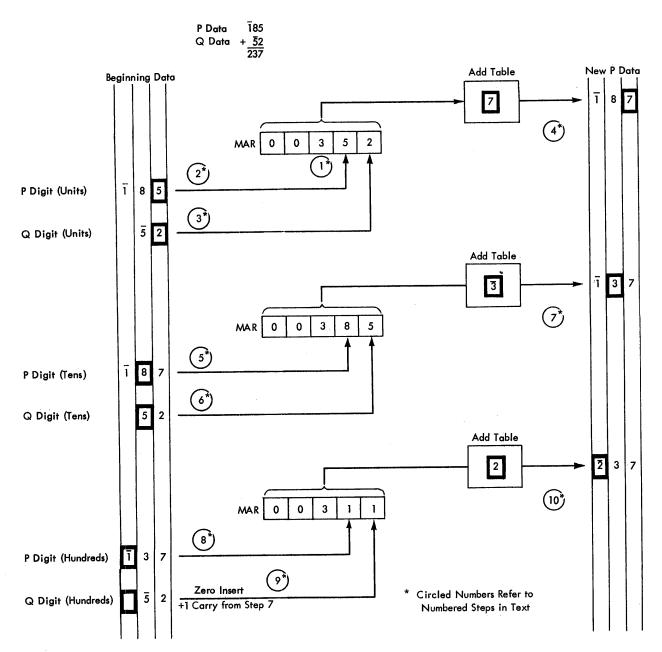

#### TABLE LOOKUP

A unique method of doing arithmetic calculations is used in the 1620. Two tables (Multiply and Add) stored in the "table area" of core storage are automatically referred to by the computer during arithmetic operations. The positions of core storage containing the table data are addressable but must not be altered; altering can cause incorrect arithmetic operations to result.

Three hundred positions of core storage have been assigned to the table area. Two hundred positions, 00100 through 00299, are assigned to the storage of the Multiply table. One hundred positions, 00300 through 00399, are assigned to the storage of the Add table used in all arithmetic operations (see Appendixes B and C). A digit with a flag bit in the table indicates that a carry is associated with that digit.

In addition, twenty positions, 00080 through 00099, are used to receive the product or partial product in multiply operations.

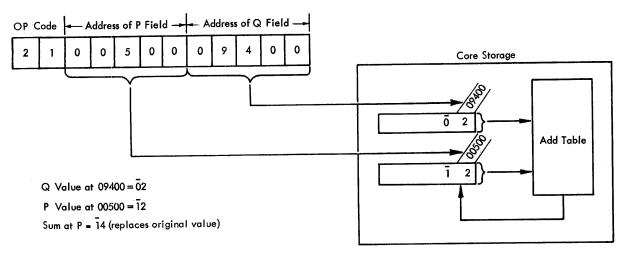

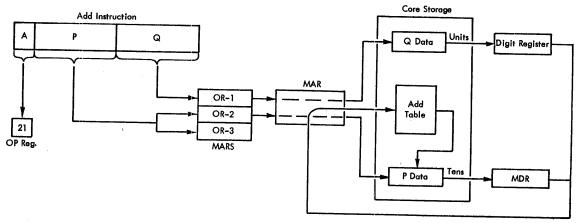

#### Add (A-21)

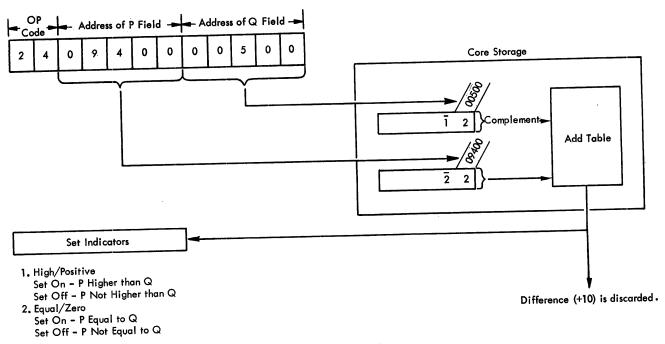

Description. The data in the field at the Q address is added to the data in the field at the P address and the sum replaces the P field data. The Q field data remains unchanged.

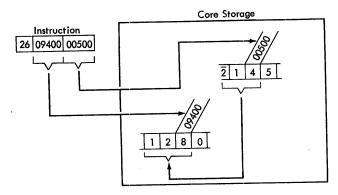

In Figure 8, the sum (14) is "looked up" in the add table and replaces the 12 at 00500 (P address). The field mark remains at the high-order position. When the sum is zero, the sign of the P field is retained. For sums other than zero, the sign of the larger value field is retained. High-order zeros are supplied if the number of significant digits in the Q field is less than the number of significant digits in the initial field at P.

The high/positive indicator is on if the sum is positive and not zero; the equal/zero indicator is on if the sum is zero. Neither indicator is on if the sum is negative.

Execution Time. Execution time varies according to the number of digits (high-order zeros included) in the field at P and according to whether recomplementing is necessary. Recomplement time must be added to the basic time when the signs of the fields at the Q and P addresses are different initially and the absolute numerical value of the Q field is greater than the absolute numerical value of the P field.

Basic Execution Time:  $T=160+80 D_P$ Recomplement time:  $T=80 D_P$

### Add Immediate (AM-11)

Description. The description is the same as that for Add (A-21) except that the data in the Q part of the instruction is used as the Q data. For example, if the OP

Figure 8. Add Operation

code were 11 in Figure 8, the Q data would be  $\overline{0}9400$  and the result would be 12,  $(00+\overline{0}2)$ . The three high-order positions of the Q data  $(\overline{0}94)$  are not used, because the P data flag bit (over the one in  $\overline{1}2$ ) stops the add operation. The overflow indicator is turned on because the Q data field  $(\overline{0}9400)$  exceeds the two digits of data  $(\overline{1}2)$  contained in the field defined by the P address (00500).

Execution Time. Same as Add (A-21).

## Subtract (S-22)

Description. The data in the field at the Q address is subtracted from the data in the field at the P address and the difference replaces the data in the field at the P address. The data in the field at the Q address remains unchanged.

The data in the field at the Q address is complemented if it has the same sign as the data in the field at the P address. The sign control chart in Figure 9

shows the conditions under which the result (stored at the P address) is recomplemented.

A zero result retains the sign of the field at the P address. The sign of a result, other than zero, is determined by algebraic analysis of the P and Q fields. Highorder zeros are supplied if the number of significant digits in the Q field is less than the number of significant digits in the initial field at the P address.

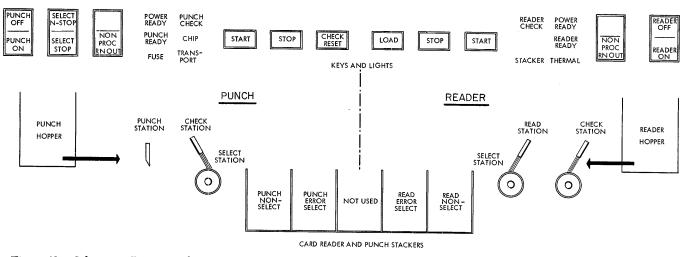

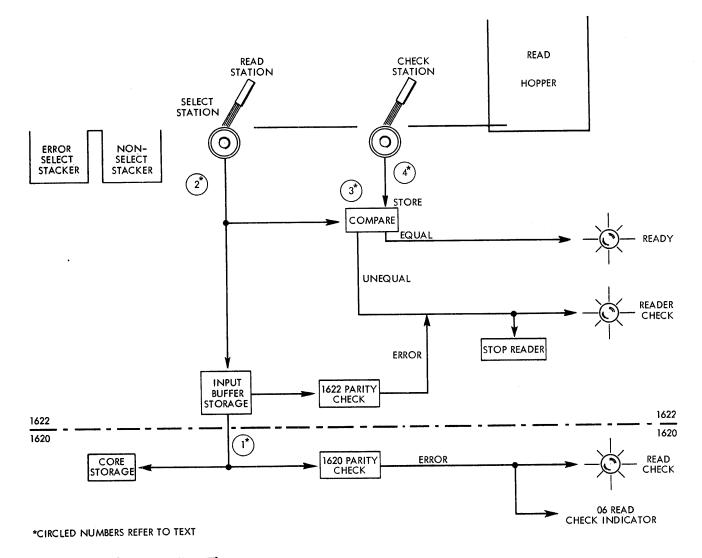

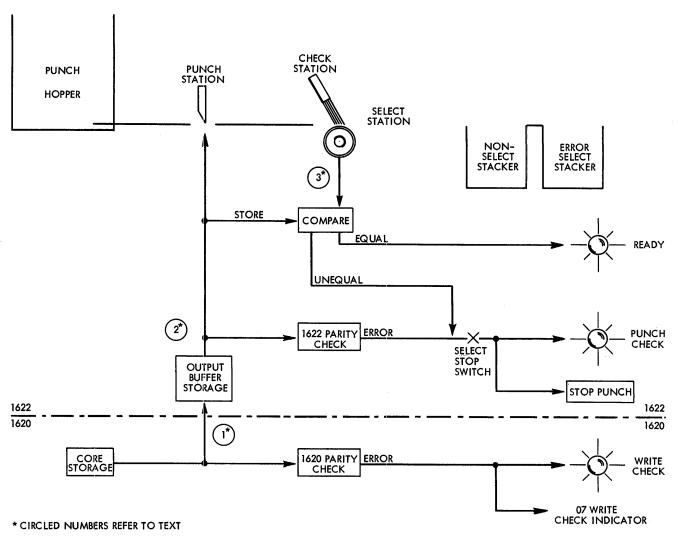

The high/positive indicator is on if the difference is positive and not zero; the equal/zero indicator is on if the difference is zero. Neither indicator is on if the difference is negative.