# Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

2250 Display Unit Model 1

## PREFACE

This manual provides the customer engineer (CE) with information useful for preventive and corrective maintenance of the IBM 2250 Display Unit, Model 1. This edition updates the former edition (Form Y27-2045-0) and incorporates the graphic design feature FE supplement (Form Z27-2572).

Text in this maintenance manual is supported by references to diagrams located in the FE Diagram Manual (Form Y27-2044). The following are related manuals and reference material that may be used in conjunction with this manual:

2250-1 FE Theory of Operation (FETOM), Form Y27-2043 2250-1 FE Diagram Manual (FEDM), Form Y27-2044 2250-1 FE Installation Manual (FEIM), Form 226-2022 2250-1 Illustrated Parts Catalog (IPC), Form 123-0442

IBM. System/360 I/O Interface - Channel to Control OEMI, Form A22-6843

SLT Component Circuits Manual, Form Z22-2798 (IBM Confidential, for release only to authorized persons)

SLT Common Power Supply Manual, Form 223-2799

SLT Packaging Manual, Form Z22-2800 (IBM Confidential, for release only to authorized persons)

It is assumed that the CE who services the 2250-1 has had experience and/or training on the unit and is familiar with the following:

- 1. 2250-1 Diagnostic Programs

- 2. Use of oscilloscope and related tools

- 3. CRT Safety precautions and protective equipment

This manual has been prepared by the IBM Systems Development Division Product Publications, Dept. 520, CPO Box 120, Kingston, N.Y., 12401. Address comments concerning the manual to this address.

# CONTENTS

| CHAPTER 1 | REFERENCE DATA AND SERVICE AIDS             |   | 1-1  | 2.6.2     | Display Generation                            | 2-10       |

|-----------|---------------------------------------------|---|------|-----------|-----------------------------------------------|------------|

|           |                                             |   |      | 2.7       | Marginal Checking                             | 2-11       |

| SECTION 1 | REFERENCE DATA                              | • | 1-1  |           |                                               |            |

| SECTION 2 | DIAGNOSTIC TECHNIQUES                       |   | 1-5  | CHAPTER 3 | PREVENTIVE MAINTENANCE                        | 3-1        |

| 1.1       | Maintenance Philosophy                      |   | 1-5  |           |                                               |            |

| 1.1.1     | Error Detection                             |   | 1-5  | CHAPTER 4 | CHECKS, REMOVALS, AND ADJUSTMENTS             | 4-1        |

| 1.1.2     | On-Line Localization                        |   | 1-5  | 4.1       | CRT Removal/Replacement Procedures            | 4-1        |

| 1.1.3     | Isolation and Repair                        |   | 1-5  | 4.2       | Analog Alignment Procedures                   | 4-2        |

| 1.1.4     | On-Line/Off-Line - Power ON/OFF Switching . |   |      | 4.2.1     | 2250-1 CRT Image Specifications               | 4-3        |

| 1.1.4.1   | On-Line to Off-Line Switching               |   |      | 4.2.2     | Alignment                                     | 4-3        |

| 1.1.4.2   | Off-Line to On-Line Switching               |   |      | 4.2.3     | De-Skew Adjustment                            | 4-5        |

| 1.1.4.3   | On-Line Power ON/OFF Switching              |   |      | 4.2.4     | Asynchronous Adjustment (for Machines Without | 4-3        |

| 1.1.5     |                                             |   |      | 4.2.4     | · · · · · · · · · · · · · · · · · · ·         | 4-5        |

| 1.1.5     | Repair of Field-Replaceable Assemblies      |   |      | 4.2.5     | Absolute Vector Graphics)                     | 4-3<br>4-6 |

|           | Diagnostic Programs                         |   |      | · ·       | Character Generator Alignment                 | _          |

| 1.2.1     | Without Buffer                              |   |      | 4.2.6     | Character Overdrive Adjustment                | 4-6        |

| 1.2.1.1   | Automatic Program                           |   |      | 4.2.7     | Line or Vector Contrast                       | 4-6        |

| 1.2.1.2   | Manual Program                              |   |      | 4.2.8     | Light Pen Gain                                | 4-6        |

| 1.2.1.3   | Timing Program                              |   |      | 4.2.9     | Absolute Vector Graphics Alignment            | 4-6        |

| 1.2.2     | With Buffer                                 |   | 1-6A | 4.2.10    | Asynchronous Adjustment (With Absolute Vector |            |

| 1.2.2.1   | Automatic Program                           |   | 1-6A |           | Graphics Feature)                             | 4-8        |

| 1.2.2.2   | Manual Program                              |   | 1-6A | 4.2.11    | Absolute Vector Generator Maintenance         | 4-8        |

| 1.2.2.3   | Timing Program                              |   | 1-6A | 4.2.12    | Phasing of Fans                               | 4-17       |

| 1.3       | Pattern Failures Identified                 |   | 1-6A | 4.2.13    | Visual Effects of Controls on Analog Circuits | 4-17       |

| 1.4       | Diagnostic Flow Charts                      |   | 1-7  | 4.2.13.1  | Character Pre-Intensity Time Delays           | 4-17       |

| 1.5       | Catastrophic Troubleshooting Procedure      |   | 1-7  | 4.2.13.2  | Character De-Intensify Time Delay             | 4-17       |

| 1.5.1     | De-Skew Check                               |   | 1-33 | 4.2.13.3  | Vector Pre-Intensify SS                       | 4-17       |

| 1.5.2     | Character Generator Check                   |   | 1-34 | 4.2.13.4  | Point Plot SS                                 | 4-30       |

| 1.5.3     | Light Pen Check with GDF                    |   | 1-35 | 4.2.13.5  | Character Position Overdrive SS               | 4-30       |

| 1.5.4     | Light Pen Check Without GDF                 |   | 1-35 | 4.2.13.6  | Position Change Time, Standard Characters     | 4-30       |

| 1.5.5     | AVG Check                                   |   |      | 4.2.13.7  | Position Change Time, Expanded Characters .   | 4-30       |

| 1.5.6     | Program 1, Full Square                      |   |      | 4.2.13.8  | Minimum Position Time SS                      | 4-30       |

| 1.5.7     | Program 2, "A" Characters                   |   |      | 4.2.13.9  | De-Skew SS                                    | 4-30       |

|           |                                             | ٠ |      | 4.2.14    | CRT Arc-Protection Check                      | 4-31       |

| SECTION 3 | SYMPTOM INDEX                               |   | 1-38 | 4.3       | Single-Shots, Timing, and Adjustment          | 4-31       |

|           |                                             |   |      | 4,4       | Delay Line Adjustments                        | 4-31       |

| SECTION 4 | SERVICE AIDS                                | ٠ | 1-38 | 4.5       | M-8 Storage Adjustments                       | 4-31       |

|           |                                             |   |      | 4.6       |                                               | 4-31       |

| CHAPTER 2 | MAINTENANCE FEATURES                        |   | 2-1  | 4.7       | Power Pack Removal                            |            |

| 2.1       | Operator Controls                           |   | 2-1  |           | SLT Power Supply Removal                      | 4-34       |

| 2.2       | Power Supply Panel                          |   | 2-1  | 4.8       | High-Voltage Power Supply Removal             | 4-34       |

| 2.3       | CE Panel Controls and Indicators            |   | 2-1  | 4.9       | Primary Power Assembly Removal                | 4-36       |

| 2.3.1     | Controls                                    |   | 2-1  | 4.10      | 24V Power Supply Removal                      | 4-37       |

| 2.3.2     | Indicators                                  |   | 2-2  | 4.11      | Logic Gate Blower Removal                     | 4-37       |

| 2.4       | Analog Potentiometer Panel Controls         |   | 2-5  | 4.12      | SLT Power Supply Blower Removal               | 4-37       |

| 2.4.1     | Switches                                    |   | 2-5  | 4.13      | High-Voltage Power Supply Blower Removal      | 4-37       |

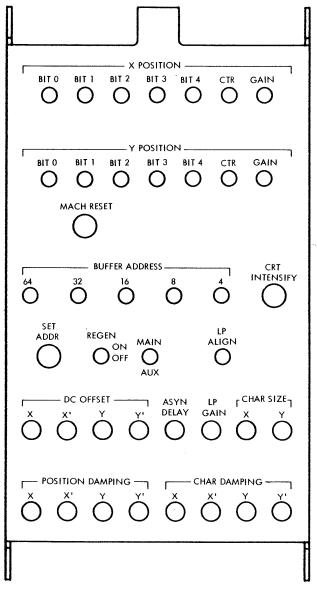

| 2,4.2     | Potentiometers                              |   | 2-6  | 4.14      | Relay Panel Removal                           | 4-37       |

| 2.5       | Program Monitoring                          |   | 2-6  | 4.15      | Optic Light Pen Adjustments                   | 4-37       |

| 2.5.1     | Sense and Status Bytes                      |   |      | 4.15.1    | Optic Focusing                                | 4-37       |

| 2.5.2     | Read XY Position Register Command           |   |      | 4.15.2    | Switch Adjustment                             | 4-38       |

| 2.6       | CE Operating Procedures                     |   | 2-7  | 4.16      | Intensity Alignment Procedure                 | 4-38       |

| 2.6.1     | Command Performance                         |   |      |           |                                               |            |

| 2.6.1.1   | Prepare Unit for Manual Control             |   | 2-7  | CHAPTER 5 | POWER SUPPLIES                                | 5-1        |

| 2.6.1.2   | Initial Selection Sequence                  |   |      | 5.1       | General                                       | 5-1        |

| 2.6.1.3   | Set BAC and Stop                            |   |      | 5.2       | Power Supply Protection                       | 5-1        |

| 2.6.1.4   | Write Buffer                                |   | 2-7  | 5.3       | ** *                                          |            |

| 2.6.1.4   |                                             |   |      |           | Power Cooling                                 | 5-1        |

|           | Read Buffer                                 |   | 2-8  | 5.4       | Thermal Reset                                 | 5-1        |

| 2.6.1.6   | Sense                                       |   | 2-9  | 5.5       | Voltage Checks and Adjustments (SLT Supplies) | 5-2        |

| 2.6.1.7   | Ending Sequence                             |   |      | 5.6       | Power Supply Failures                         |            |

| 2.6.1.8   | Initial Selection with Bad Parity           |   | 2-9  | 5.6.1     | Loss of Power                                 | 5-2        |

# Form Y27-2045-1 FES Y27-2178

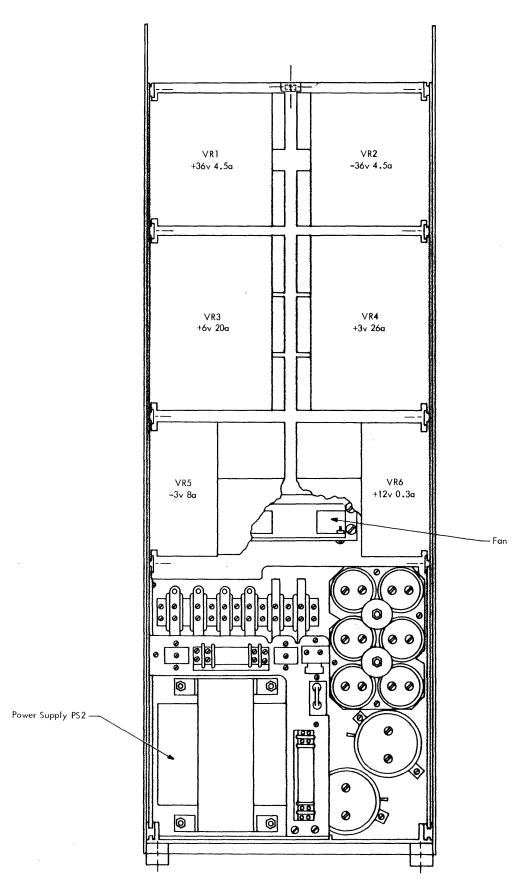

| 5.6.1.1   | Inability to Restore Power Following CB Trip       | . 5-2 | -2 | CHAPTER 6  | LOCATIONS                                          | 6 | 5-1        |

|-----------|----------------------------------------------------|-------|----|------------|----------------------------------------------------|---|------------|

| 5.6.1.2   | Ability to Restore Power Following CB Trip         | . 5-2 | 2  |            |                                                    |   |            |

| 5.6.1.3   | Causes of Power Loss                               | . 5-2 | 2  | APPENDIX A | TOOLS, TEST EQUIPMENT, AND SAFETY                  |   |            |

| 5.6.2     | Display Raster Changing Size                       |       | _  |            | EQUIPMENT                                          | F | <b>\-1</b> |

| 5.6.3     | Loss of Display/ Distorted Image                   |       |    | A.1        | Tools                                              | A | <b>\-1</b> |

| 5.6.4     | Machine Hangup/Error Conditions in Status Byte     |       | -  | A.2        | Test Equipment                                     | A | <b>A-1</b> |

| 5.7       | SLT Power Supply Repair                            |       |    | A.3        | Safety Equipment                                   | F | A-1        |

| 5.8       | High-Voltage Supply Output                         |       |    |            |                                                    |   |            |

| 5.9       | High-Voltage Power Supply Repair                   |       | 2  |            |                                                    |   |            |

| 5.10      | Power Distribution                                 |       |    | APPENDIX B | 2250-1 CHARACTERISTICS                             | Ŀ | 3-1        |

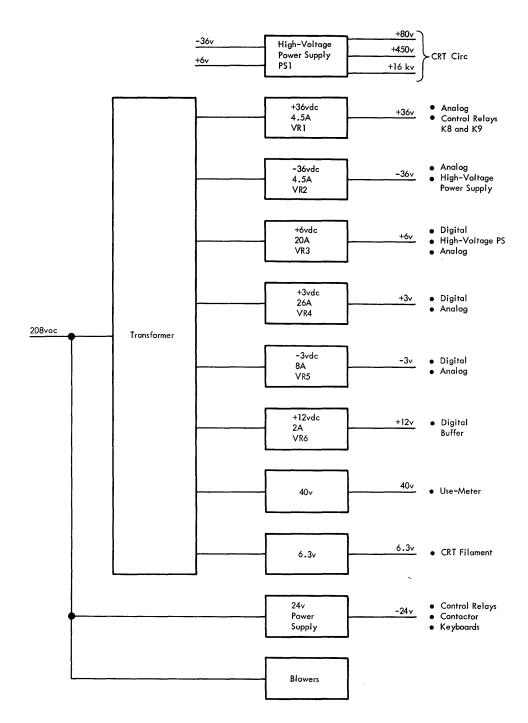

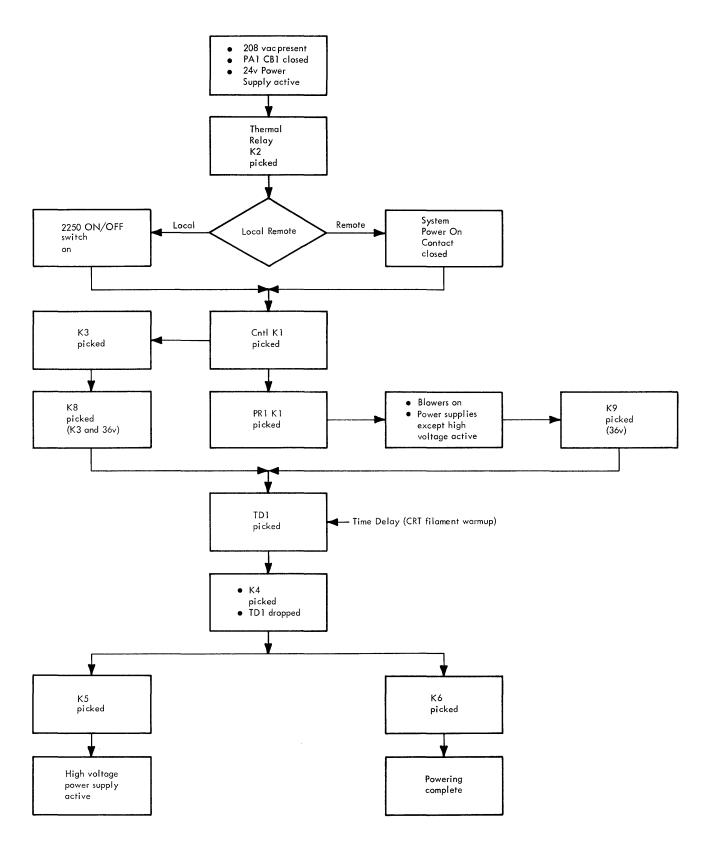

| 5.11      | Power-On Sequence                                  |       |    |            |                                                    |   |            |

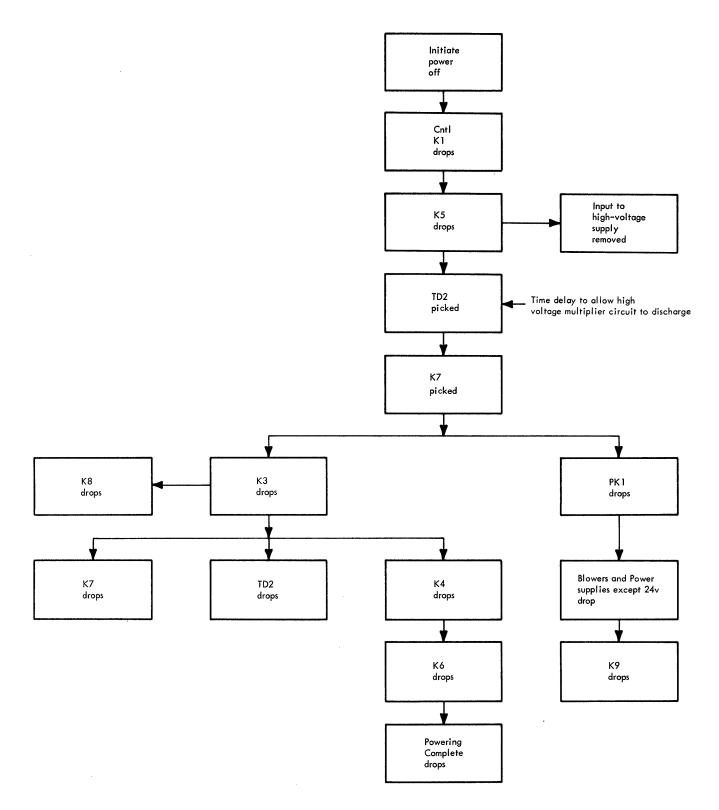

| 5.12      | Power-Off Sequence                                 |       | -  | APPENDIX C | DECIMAL-HEXADECIMAL CONVERSION                     | c | 3-1        |

| 5.13      | +36V <sub>3</sub> -36V Minibus Routing             |       |    | C.1        | Four-Byte Absolute Vector Conversion               |   | C-1        |

| 5.14      | Power Control and Distribution Wiring Diagram .    |       |    | C.2        | Two-Byte Relative Vector Conversion                |   |            |

|           |                                                    |       |    |            |                                                    |   |            |

| ILLUSTRAT | TIONS                                              |       |    |            |                                                    |   |            |

| 1-1       | Display Unit Commands                              | . 1-1 | 1  | 4-3        | Absolute Vector Graphics Alignment Pattern         | 4 | 4-7        |

| 1-2       | Display Unit Orders                                |       | 2  | 4-4        | Absolute Vector Graphics Malfunctions (7 Sheets)   |   | 4-10       |

| 1.3       | Character Display Characteristics                  | . 1-2 | 2  | 4-5        | Analog Patterns (12 Sheets)                        |   | 4-18       |

| 1-4       | Formats                                            |       |    | 4-6        | Single-Shots (3 Sheets)                            |   | 1-32       |

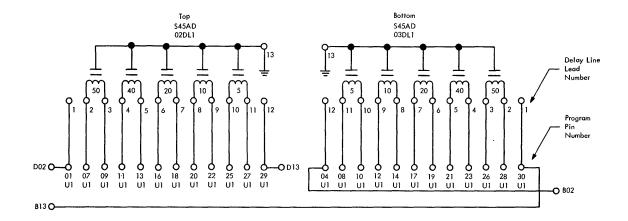

| 1-5       | Character Set and Code Assignment                  |       | 4  | 4-7        | Delay Lines                                        |   | 4-35       |

| 1-6       | Diagnostic Programs                                | . 1-6 | 6  | 4-8        | Adjustable Delay Lines                             |   | 4-36       |

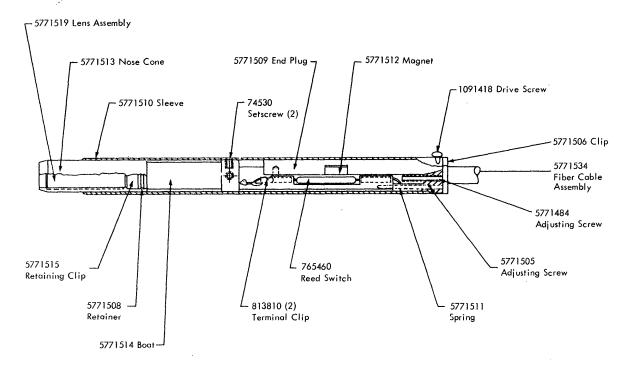

| 1-7       | Pattern Explanation                                | . 1-7 | 7  | 4-9        | Optic Light Pen Assembly                           | 4 | 1-38       |

| 1-8       | Visible Pattern Malfunctions (22 Sheets)           |       | 9  | 4-10       | 01BA2J6 Card Output Levels                         | 4 | 4-39       |

| 1-9       | DC Intensity I CRT Output                          | . 1-3 | 30 | 5-1        | Possible Causes of Thermal Conditions              | 4 | 5-1        |

| 1-10      | Blank-Unblank II CRT Output                        | . 1-3 | 31 | 5-2        | Input Voltages to SLT Supplies                     |   | 5-2        |

| 1-11      | Yoke Waveforms, Bits 5 through 9 Active            | . 1-3 | 31 | 5-3        | Causes of Power Loss                               | 4 | 5-3        |

| 1-12      | Position Isolation Output                          | . 1-3 | 31 | 5-4        | AC/DC Voltage Distribution                         | 4 | 5-4        |

| 1-13      | Yoke Waveforms, Bit 0, and Bits 5 through 9 Active | . 1-3 | 32 | 5-5        | Power-On Sequence                                  |   | 5-5        |

| 1-14      | Position Isolation Output, Yoke Clamped            | . 1-3 | 32 | 5-6        | Power-Off Sequence                                 |   | 5-6        |

| 1-15      | Asynchronous Delay Waveforms                       | . 1-3 | 32 | 5-7        | +36V, -36V Minibus Routing (3 Sheets)              |   | 5-7        |

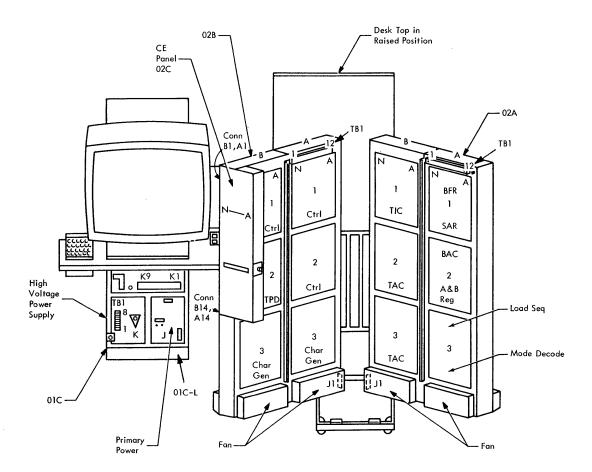

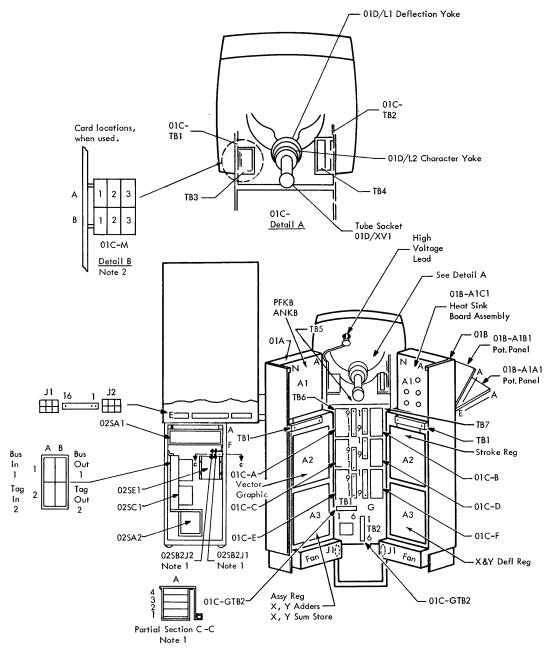

| 1-16      | Blank-Unblank Waveforms                            | . 1-3 | 33 | 6-1        | Component Location, Operational                    | 6 | 5-2        |

| 1-17      | DC Offset Outputs                                  | . 1-3 | 33 | 6-2        | Component Location, Front View                     | 6 | 5-3        |

| 1-18      | Position System Dynamic Intensity II Output        |       |    | 6-3        | Component Location, Rear View                      |   | 5-4        |

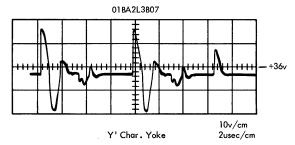

| 1-19      | Character Yoke Waveforms                           |       | 34 | 6-4        | Detail 01C, Front View                             |   | 5-5        |

| 1-20      | Character System Dynamic Intensity II Output       |       |    | 6-5        | Detail 01C, Rear View                              |   | 5-6        |

| 1-21      | AVG Waveforms                                      |       |    | C-1        | Decimal-Hexadecimal Conversion Chart for Four-Byte |   |            |

| 2-1       | Analog Potentiometer Panel                         |       |    |            | Absolute Vectors                                   | ( | C-2        |

| 3-1       | Preventive Maintenance Chart                       |       |    | C-2        | Decimal-Hexadecimal Conversion Chart for Two-Byte  |   |            |

| 4-1       | Analog Alignment Controls                          |       |    |            | Relative Vectors                                   | ( | C-4        |

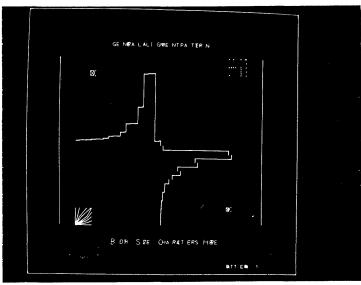

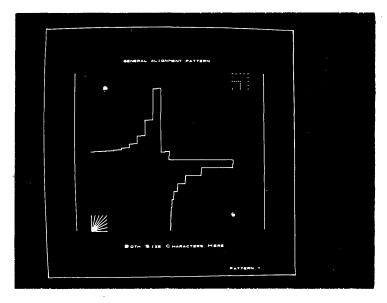

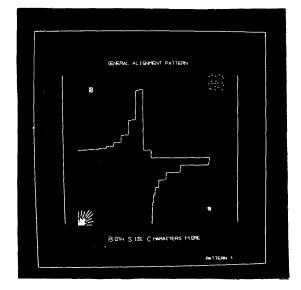

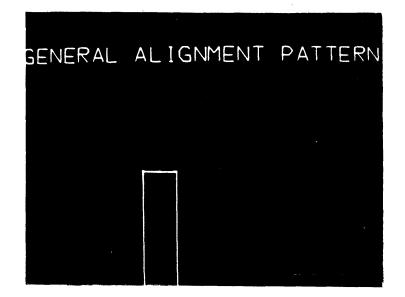

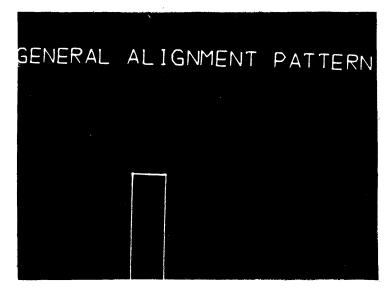

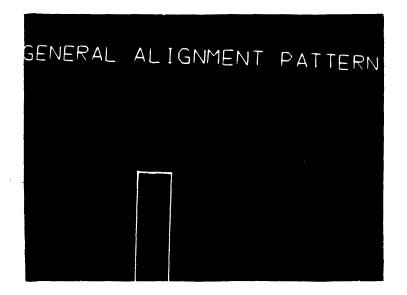

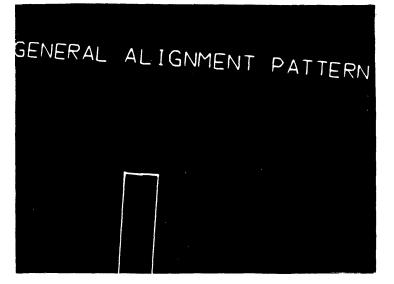

| 4-2       | General Alignment Pattern                          |       |    |            |                                                    |   |            |

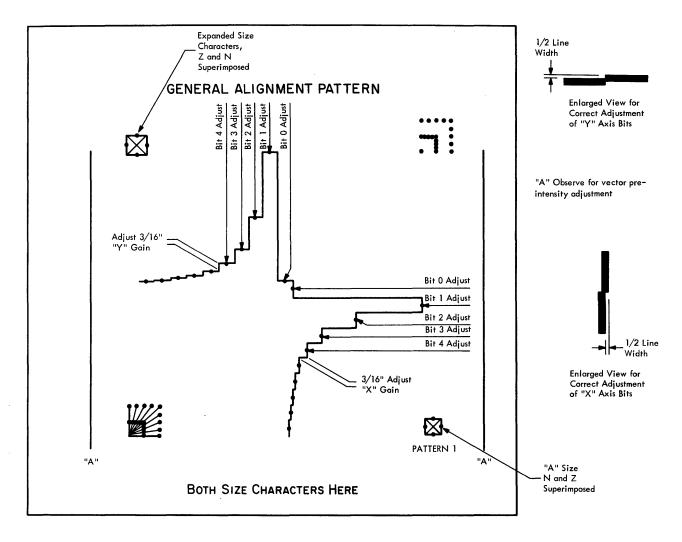

General Alignment Pattern . . . . . . . . . . . . 4-4

To ensure personal safety and the safety of coworkers, each CE should make it a practice to observe safety precautions at all times.

The CE must be especially aware of the dangerous voltages present in a 2250-1 and of the potential hazard presented by an unprotected cathode-ray tube (CRT). Thus, the following DANGER notices appear here.

#### DANGER

Voltages of 16,000 and 450 are used in the 2250-1. Exercise extreme caution when working in the area of the high-voltage power supply and CRT's. Do not remove the high-voltage lead from the CRT following power-off until the power-off sequence has been completed. Field repair of the high-voltage power supply is limited to replacement of pluggable cards.

#### DANGER

Cathode-ray tubes are subject to implosion. Protective gear must be worn by persons working with or in the area of an unprotected CRT.

All CE's should become familiar with the general safety practices and procedures for performing artificial respiration that are outlined in CE Safety Practices (Form 229-1264).

# CATHODE-RAY TUBES - SAFE HANDLING

Cathode-ray tubes contain a high vacuum and are subject to implosion. Such as implosion can propel flying glass, thus presenting a source of personal injury. Therefore, when handling CRT's, exercise extreme caution.

# TRANSPORTATION - HANDLING

Cathode-ray tubes must be enclosed when received, transported, or moved from area to area. If they are shipped in a carton, they must be in the original carton or one of equivalent strength, securely sealed to prevent accidental opening. Also, original or equivalent packing materials and/or forms must be placed inside the carton to properly support and protect the tube. If tubes are transported in a unit or piece of equipment, the equipment must be able to contain the glass fragments if an implosion occurs.

- 2. Each CRT carton must be identified with a "Danger Cathode Ray Tube-Implosion Hazard" label.

- 3. All persons handling tubes or in the vicinity of exposed CRT's under vacuum must wear protective gear.

#### STORAGE

- Tubes must be kept in the carton or unit except when exposure is required for inspection or test.

- 2. Adequate storage area must be provided for all CRT's. Tubes should be stacked in such a manner that they cannot easily be tipped over and will not be difficult to handle when removed from stack. It is recommended that the storage area be away from the normal flow of internal trucking and pedestrian traffic.

# TESTING

Personnel involved in testing CRT's must be instructed in the hazards involved and precautions to be observed.

# PROTECTIVE EQUIPMENT

Persons handling or working with or near unprotected CRT's must wear:

- 1. Full-face shield

- 2. Apron, synthetic rubber

- 3. Gloves, welder's

- 4. Cape, welder's rawhide

# DEFECTIVE-CRT DISPOSITION

No attempt should be made to repair defective CRT's in the field. A defective CRT should be properly packed and disposed of in accordance with the CRT-disposition procedures.

This chapter contains general reference data, diagnostic techniques, and service aids to assist the CE in effecting quick diagnosis and/or repair.

# SECTION 1. REFERENCE DATA

This section contains miscellaneous information that may be helpful to the CE in troubleshooting and maintaining the equipment. Most of the information summarized in Figures 1-1 through 1-5 is covered in detail in the 2250-1 Theory of Operation manual.

| Class   | Command Designation             | Mnemonic | Hex. Code | Feature(s) Required |

|---------|---------------------------------|----------|-----------|---------------------|

|         | No Operation                    | NOOP     | 03        | None                |

|         | Set Audible Alarm               | ALRM     | OB        | None                |

| 1       | Set Buffer Address and Stop     | SBÁ      | 07        | Buffer              |

| Control | Set Buffer Address and Start    | SBAS     | 27        | Buffer              |

|         | Insert Cursor                   | CSRI     | 0F        | Buffer Char.        |

| -       |                                 |          |           | Gen A/N kbd         |

|         | Remove Cursor                   | CSRR     | 1F        | Buffer Char         |

|         |                                 |          |           | Gen A/N Kbd         |

|         | Set Program Function Indicators | SPFI     | 18        | Prog Funct Kbd      |

|         | Write Direct                    | WRT      | 01        | None                |

| Write   | Write Buffer                    | WBFR     | 01        | Buffer              |

|         | Read Buffer                     | RBFR     | 02        | Buffer              |

| Read    | Read Cursor                     | RCSR     | 06        | Buffer Char.        |

|         |                                 |          |           | Gen A/N Kbd         |

|         | Read Manual Inputs              | RMAN     | 0E        | A/N Kbd and/or      |

|         | '                               | ·        |           | Prog Funct Kbd      |

|         | Read X-Y Position Registers     | RXY      | 12        | None                |

|         | Basic Sense                     | SNS      | 04        | None                |

| Sense   | Test I/O                        |          | 00        | None                |

Figure 1-1. Display Unit Commands

| Mode      | Order Designation                         | SM Byte<br>Hex. Code | MC Byte<br>Hex. Code | Mnemonic             | Remarks      |

|-----------|-------------------------------------------|----------------------|----------------------|----------------------|--------------|

|           | Enter 2-Byte No Op                        | 2A                   | 80                   | GNOP2                |              |

|           | End Order Sequence                        | 2A                   | 81                   | GEOS                 | 2-Byte Class |

| Control   | Start Regeneration Timer                  | 2A                   | 82                   | GSRT                 |              |

|           | Enter 4-Byte No Op                        | 2A                   | C0                   | GNOP4                | 4-Byte Class |

|           | Transfer Unconditional                    | 2A                   | FF                   | GTRU                 | 4 byte Ciass |

|           | Enter Graphic Mode<br>Point Plot          | 2A                   | 00                   | GEPM                 |              |

|           | Enter Graphic Mode<br>Line/Vector         | 2A                   | 02                   | GEVM                 |              |

| Graphic   | Enter Point Plot<br>Incremental*          | 2A                   | 04                   | GEPI2                | 2-Byte Class |

|           | Enter Point Plot                          | 05                   | GEVI2                |                      |              |

|           | Enter Fixed Space<br>Size A – Unprotected | 2A                   | 40<br>50<br>52       | GECF<br>GECV<br>GECV |              |

|           | Enter Fixed Space<br>Size B — Unprotected | 2A                   | 41<br>51             | GECF<br>GEVC         |              |

| Character | Enter Fixed Space<br>Size A – Protected   | 2A                   | 44                   | GECP                 | 2-Byte Class |

|           | Enter Fixed Space<br>Size B – Protected   | 2A                   | 45                   | GECP                 |              |

|           | Enable Switch Detect*                     | 2A                   | 84                   | GESD                 |              |

| Light Pen | Disable Light Pen Detects*                | 2A                   | 85                   | GDPD                 |              |

|           | Enable No Switch Detects*                 | 2A                   | 86                   | GENSD                |              |

|           | Transfer on No Detect*                    | 2A                   | FD                   | GIND                 | 4-Byte Class |

<sup>\*</sup>Operational only when Graphic Design feature is installed.

Figure 1-2. Display Unit Orders

| Characteristics                                                                                     | Character Size |          |  |

|-----------------------------------------------------------------------------------------------------|----------------|----------|--|

|                                                                                                     | Basic          | Large    |  |

| Chacters per line (max.)                                                                            | 74             | 49       |  |

| Lines per display (max.)                                                                            | 52             | 35       |  |

| Number of characters on display (max.)                                                              | 3848           | 1715     |  |

| Displayed character time* (in-<br>cludes average character time<br>and adjacent character spacing). | 9.2usec        | 11.2usec |  |

| Blank character time* (includes adjacent character spacing).                                        | 5.4usec        | 7.4usec  |  |

| Character spacing (raster units)                                                                    | 14             | 21       |  |

| Line spacing (raster units)                                                                         | 20             | 30       |  |

<sup>\*</sup>Approximate time is indicated. The display character time is for a six-stroke character. (The number of strokes for a character is variable from one to nine, but six is average.) Flyback time is not included.

Figure 1-3. Character Display Characteristics

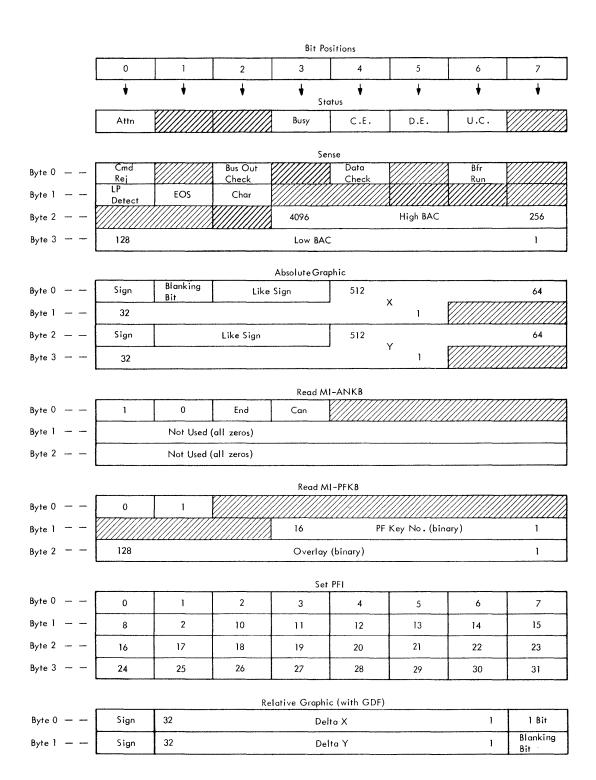

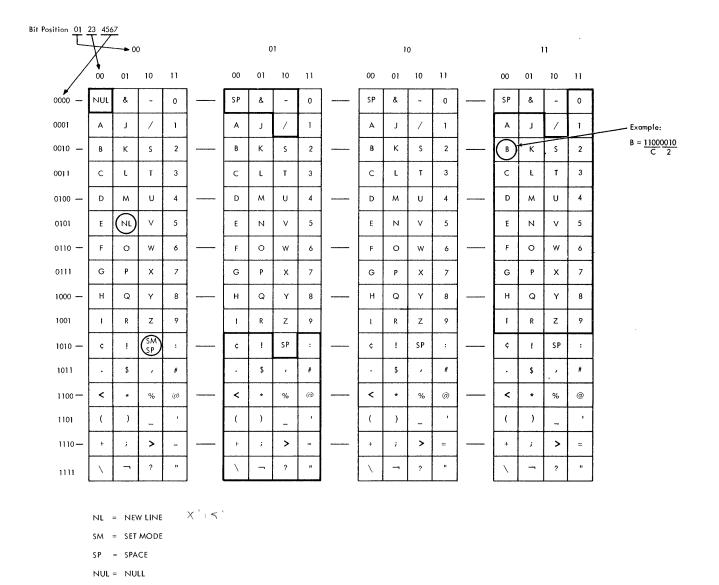

Figure 1-4. Formats

Figure 1-5. Character Set and Code Assignment

#### SECTION 2. DIAGNOSTIC TECHNIQUES

This section contains diagnostic information and material that will aid in the diagnosis and correction of 2250-1 malfunctions. Included are maintenance philosophy, diagnostic programs, pattern analysis techniques, diagnostic flow charts, and a catastrophic troubleshooting procedure.

## 1.1 MAINTENANCE PHILOSOPHY

In general, the 2250-1 maintenance philosophy is as follows:

- 1. On-line failure detection.

- On-line localization of failures to a functional area through the use of diagnostic programs and techniques.

- 3. Off-line isolation and correction of failure.

- 4. On-line verification of repair.

# 1.1.1 Error Detection

The occurrence of a machine-detectable error sets the Unit Check bit (bit 6) in the 2250-1 status byte and an error-indicating bit (indicating type of error) in the 2250-1 sense byte.

The status byte is presented to the channel at the beginning of an operation to indicate acceptance or rejection of a command. The byte is also presented to the channel at the end of an operation to indicate success or failure of the operation.

The transfer of the status byte to the channel occurs as an integral part of the initial and ending sequences, whereas the sense byte is transferred only in response to a Sense command.

If the status byte contains a Unit Check, it indicates only that an error has been detected by the 2250-1. If more details regarding the error are required (as defined by the program), the Sense command is issued, and the sense byte is transferred to the channel for program interrogation. Subsequent action is determined by the program.

Error conditions that are not machine-detectable become apparent through image loss, image distortion, or the inability to perform manual intervention.

# 1.1.2 On-Line Localization

While the unit is on-line, appropriate diagnostic routines should be used to localize failures that cannot otherwise be readily diagnosed to a functional area (digital, analog, etc.).

#### 1.1.3 Isolation and Repair

The method used to isolate a failure depends on the feature makeup of the machine. On a 2250-1 that is not equipped with the buffer feature, off-line failure isolation can be performed only when the CRT does not require a test pattern. If test patterns are required, the 2250-1 without the buffer feature must be placed in the On Line mode and must receive test patterns from the CPU.

On a 2250-1 equipped with the buffer feature, most failure isolation can be performed in the Off Line mode. By loading the buffer with appropriate diagnostic routines or test patterns (while on-line), off-line diagnosis can be performed without interfering with the CPU or the channel.

# 1.1.4 On-Line/Off-Line - Power On/Off Switching

Units without the Isolation feature require the processor to be placed in the STOP or WAIT state before power is switched or the unit is enabled or disabled. These same conditions must exist to switch from on-line to off-line or off-line to on-line.

Units with the Isolation feature must be switched as outlined in the following paragraphs.

# 1.1.4.1 On-Line to Off-Line Switching

- 1. Place ENABLE/DISABLE switch (located under the left side of CRT housing, adjacent to the usage meters) in down (disabled) position.

- 2. Wait for I/O INTF DSBLD indicator (green indicator on Ace panel) to light.

- Place I/O INTF DEGATE switch on CE panel in up position.

The unit is now off-line and can be used for off-line troubleshooting procedures.

# 1.1.4.2 Off-Line to On-Line Switching

- Place I/O INTF DEGATE switch in down position.

- 2. Place ENABLE/DISABLE switch in up position (enable). The green I/O INTF DSBLD indicator should go out.

When the channel drops the Clock Out signal, the unit will be on-line.

#### 1.1.4.3 On-Line Power On/Off Switching

- Place ENABLE/DISABLE switch in down (disable) position.

- 2. Wait for I/O INTF DSBLD indicator to light.

- 3. Depress POWER OFF pushbutton.

To bring power up, depress the POWER ON pushbutton. The unit will automatically sequence itself to power on, on-line, but disabled (I/O INTF DSBLD indicator lit). To enable the machine:

- Place ENABLE/DISABLE switch in up position (enabled).

- Wait for I/O INTF DSBLD indicator to extinguish and the channel to drop the Clock Out signal.

The unit is now enabled.

#### 1.1.5 Repair of Field-Replaceable Assemblies

Assemblies replaced in the field should be handled as follows:

- Analog cards should be returned to IBM Kingston for repair.

- 2. Power supplies should be returned to IBM Kingston for repair if not field-repairable.

- 3. Digital cards should be returned to SLT Repair Center for repair.

- 4. CRT's should be disposed of locally in accordance with General Safety CEM No. 45 (or any FE procedure replacing it).

- Fan assemblies should be returned to Kingston for repair.

- 6. Buffer arrays should be returned to Kingston for repair.

- 7. Light pen assemblies should be returned to Kingston for repair.

#### 1.2 DIAGNOSTIC PROGRAMS

The diagnostic programs for the 2250 Model 1 are available in two packages: one for the 2250-1 without the buffer feature and one for the 2250-1 with the buffer feature. Each diagnostic program package consists of three programs: Automatic, Manual, and Timing. Each program is further divided into independent program sections, each requiring 4,000 positions of CPU storage. The independent sections of the diagnostic programs are given in Figure 1-6. The programs can operate on any System/360 from the 8K Model 30 to the Model 92.

All sections of the diagnostic programs operate under control of the Diagnostic Monitor (DM) programs, and all standard DM options are available.

| Program Number |                 |                                    | A - Automatic<br>M - Manual |

|----------------|-----------------|------------------------------------|-----------------------------|

| With Buffer    | Without Buffer* | Program Title                      | T - Timing                  |

| F760           | F750            | Interface Commands                 | Α                           |

| F761           |                 | Buffer Storage                     | Α                           |

| F762           | F751            | Regeneration Order                 | Α                           |

| F763           | F752            | Data Sequencing                    | A                           |

| F764           | F753            | Data Registers                     | A                           |

| F766           | F756            | Graphic Display                    | М                           |

| F767           | F757            | Absolute Vector Graphic<br>Display | М                           |

| F768           | F758            | Character Generation               | м                           |

| F769           | F759            | A/N Keyboard                       | м                           |

| F76A           | F75A            | PF Keyboard                        | м                           |

| F76B           | F75B            | Light Pen Detection                | м                           |

| F76C           |                 | A/N Keyboard (Cursor)              | м                           |

| F76E           | F75E            | XCPU Tests                         | Т                           |

<sup>\*</sup>A buffer is now mandatory in all 2250-1 Display Units. However, several earlier machines did not have a buffer; these require F75X diagnostic series programs.

Figure 1-6. Diagnostic Programs

# 1.2.1 Without Buffer

# 1.2.1.1 Automatic Program

The Automatic program consists of four sections (Figure 1-6) and operates without manual intervention or visual checks. The various sections are designed to detect equipment failures associated with the 2250-1 channel-interface commands, the regeneration control orders, and the data registers. These sections use functional commands, status bits, sense bytes, and X and Y register feedback to detect and diagnose failures. This program does not include tests of the keyboards, light pen, character generator, or analog circuits; however, portions of the associated control logic are tested.

#### 1.2.1.2 Manual Program

The Manual program consists of five sections (Figure 1-6) and operates with manual testing and/or visual failure-detection. The various sections are designed to functionally exercise and test the equipment not covered in the Automatic program. The sections include test patterns to visually check the graphic display and character generation logic and manual tests of the program function keyboard, alphameric keyboard, and light pen. Diagnosis of

failures is performed by combined program, manual, and visual means. Analog circuit alignment may be checked and corrected with the Manual program.

#### 1.2.1.3 Timing Program

The Timing program consists of one section (Figure 1-6) and performs timing and time-dependent tests in the Exclusive CPU mode of the Diagnostic Monitor programs. This section operates without requiring manual intervention or visual checks.

#### 1.2.2 With Buffer

#### 1.2.2.1 Automatic Program

The Automatic program consists of five sections (Figure 1-6) and operates without manual intervention or visual checks. The various sections are designed to detect equipment failures associated with the 2250-1 channel-interface commands, the 4K or 8K buffer storage, the regeneration control orders, the data registers, and the cursor and light pen control logic. These sections use functional commands, status bits, sense bytes, and X and Y register feedback to detect failures. Though the program does not include tests of the keyboards,

light pen, character generator, or analog circuits, portions of the associated control logic are tested.

#### 1.2.2.2 Manual Program

The Manual program with the buffer feature is as described in paragraph 1.2.1.2. However, the alignment procedures can be, and should be, performed off-line.

#### 1.2.2.3 Timing Program

The Timing program has one section (Figure 1-6) which operates in the Exclusive CPU mode of the Diagnostic Monitor programs. This program performs timing and time-dependent tests of the interface and of buffer regeneration.

#### 1.3 PATTERN FAILURES IDENTIFIED

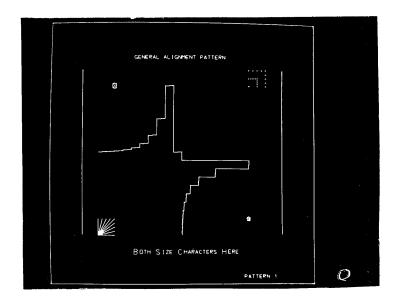

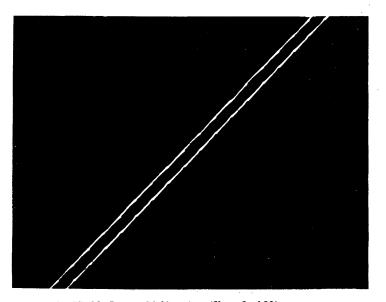

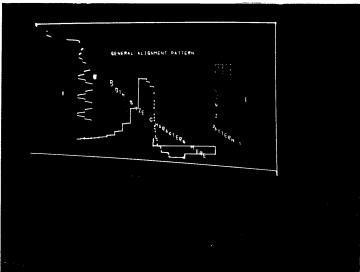

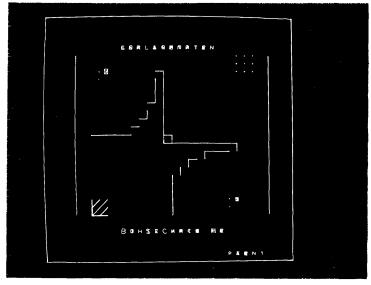

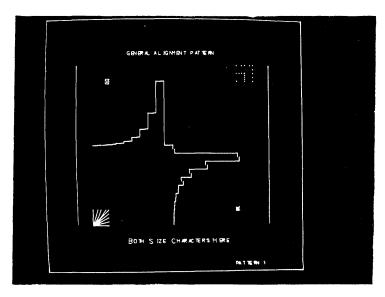

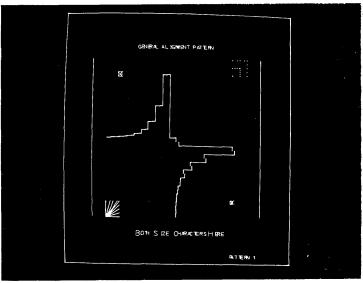

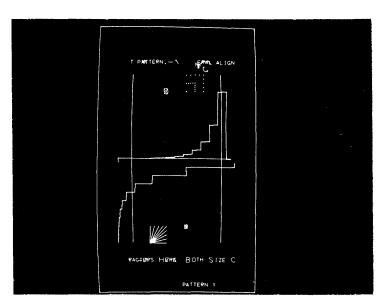

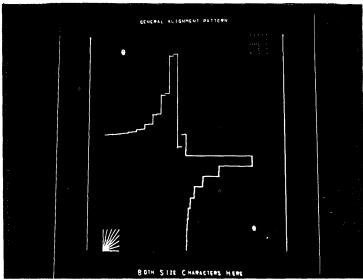

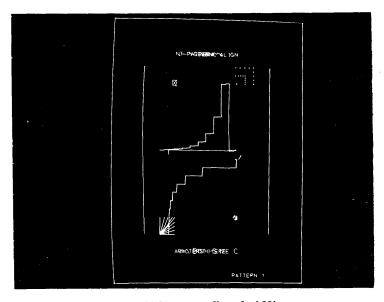

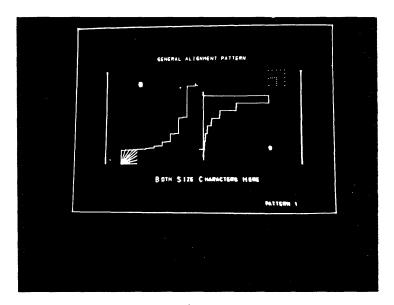

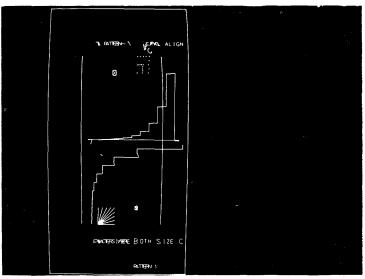

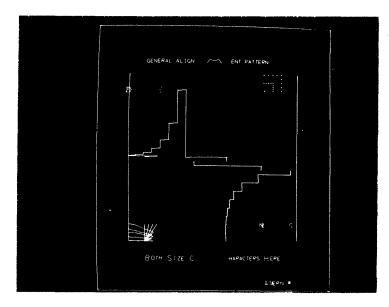

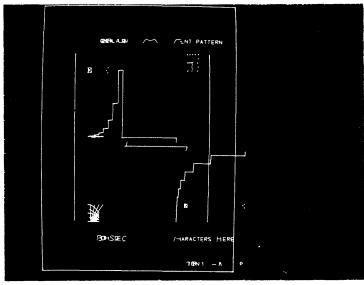

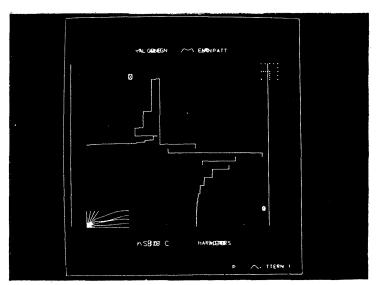

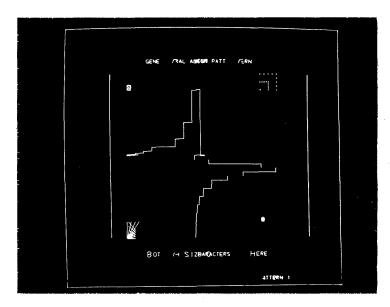

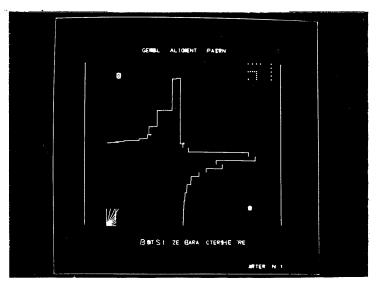

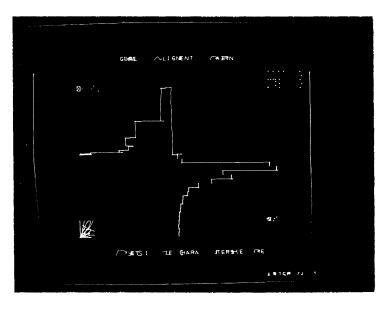

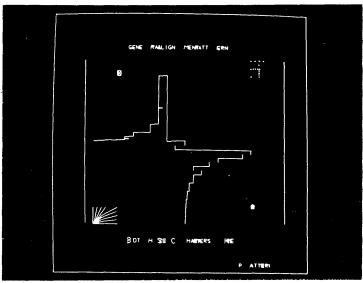

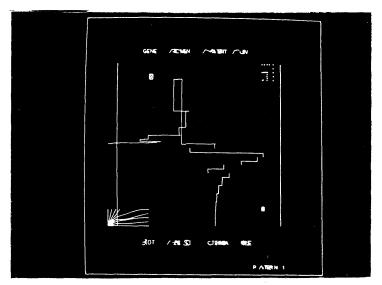

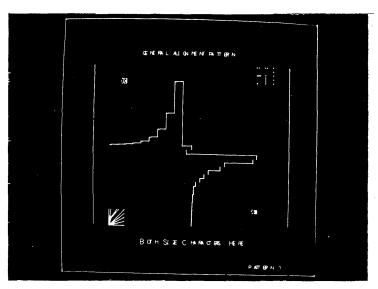

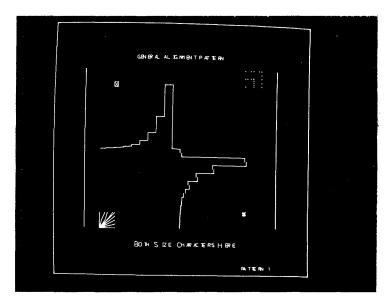

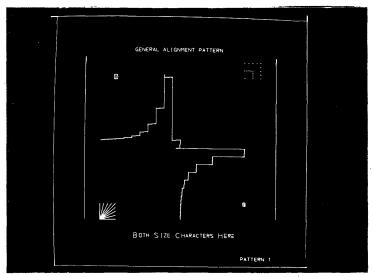

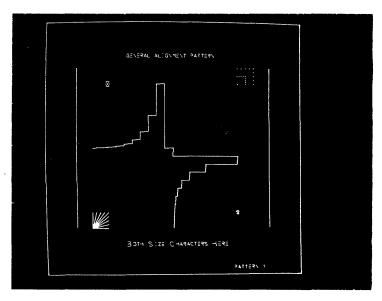

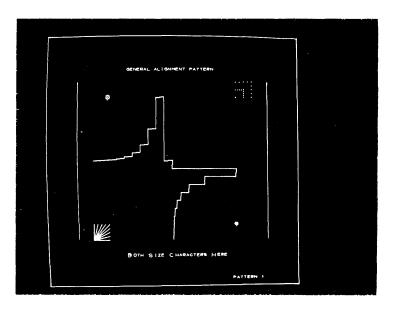

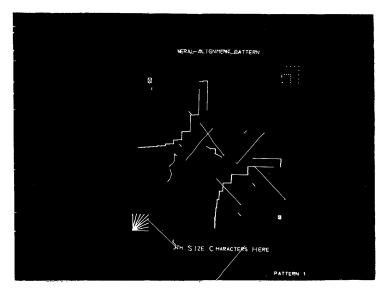

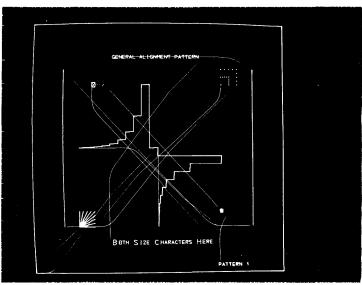

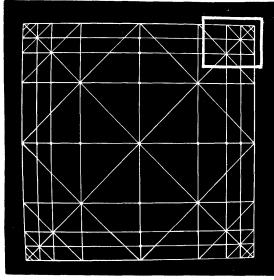

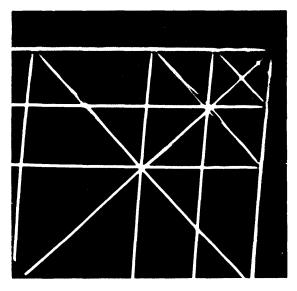

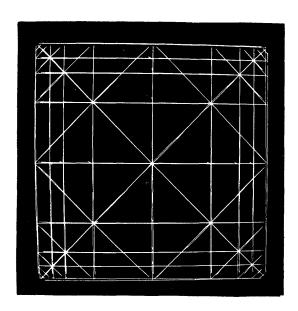

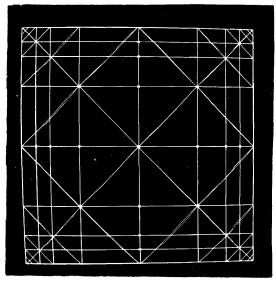

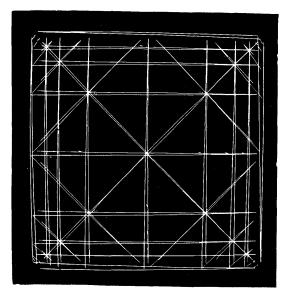

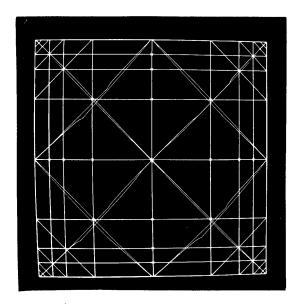

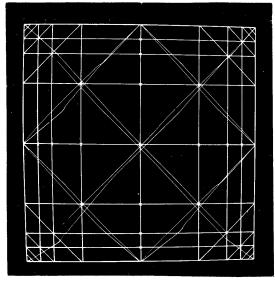

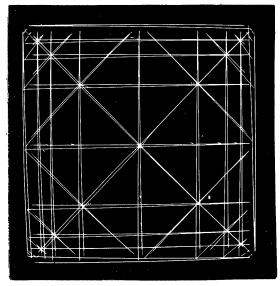

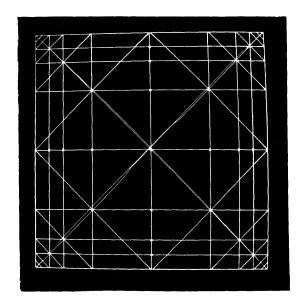

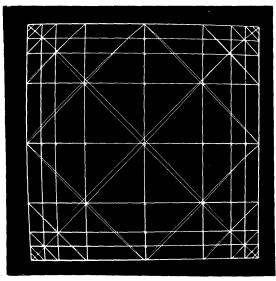

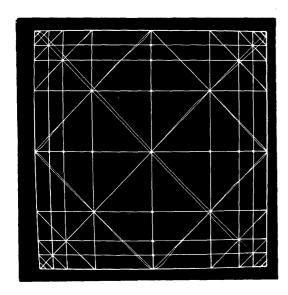

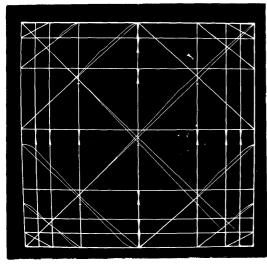

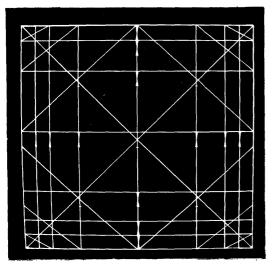

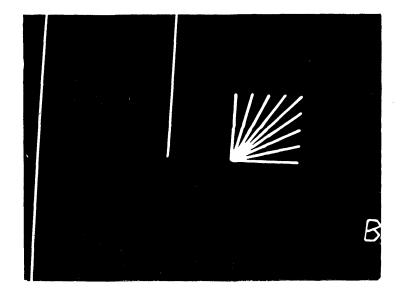

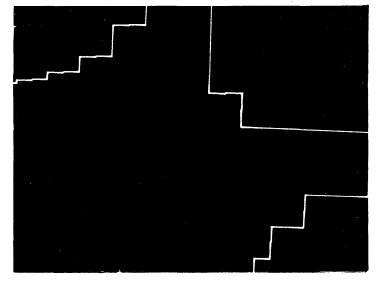

An explanation of the various portions of the general alignment pattern is shown in Figure 1-7. If a display on the CRT appears to be misaligned, the failing area can possibly be determined by displaying the general alignment pattern and observing the various portions of the display as indicated in Figure 1-7.

When there is a high probability that trouble has developed in the analog section of the 2250, pattern

| Portion of Display    | Area under Observation                                                                                                                                                                                    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overall Display       | Blank-unblank circuitry                                                                                                                                                                                   |

| Full-Size Square      | Overall display size; affords rough check on high-voltage status; vector dynamic intensity early blank operating; minimum position change time SS set for approximately 7.25usec; +11v clamp; +60v clamp. |

| X and Y Bit Staircase | Switching of bits<br>Weight of bits<br>Gain control status                                                                                                                                                |

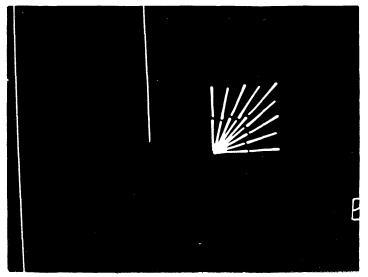

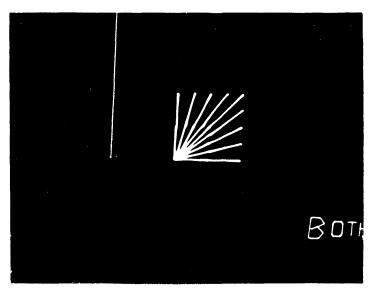

| Vector Fan            | Damping<br>Vector intensity<br>Yoke time constant                                                                                                                                                         |

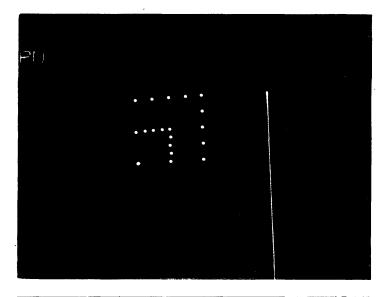

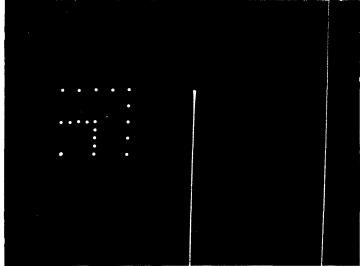

| Point Plot Fan        | Damping<br>Point plot intensity<br>Minimum position time<br>SS approximately correct                                                                                                                      |

| Character Information | Character generator bit status Character damping Character size Dynamic intensity; character Preintensification and de- intensification time delays; character overdrive                                  |

| Vertical Vectors      | Vector preintensification<br>Early blank<br>Dynamic intensity, position<br>system                                                                                                                         |

Figure 1-7. Pattern Explanation

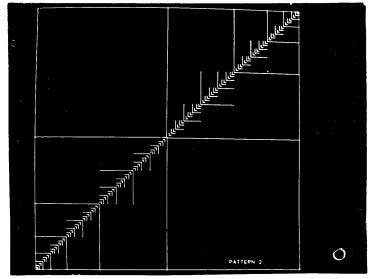

analysis techniques (comparing patterns with known standards) can be used to locate defective cards. Figure 1-8 (sheets 1 and 2) shows six photographs with patterns in alignment. Sheets 3 through 22 of the figure show photographs of patterns that are misaligned; the failing areas are identified.

Note that these photographs represent failures in the indicated component and location only. Component failures similar to those identified can also be determined when a display appears similarly misaligned but displayed at a different location on the CRT. For example, the "X'Bit 0 Switch" with a collector to emitter shorted looks similar to an "X Bit 0 Switch" similarly shorted, but the display would appear on the right side of the CRT. If the failure cannot be determined by this pattern analysis technique, proceed to paragraph 1.4.

#### 1.4 DIAGNOSTIC FLOW CHARTS

The General Alignment program displays visual information for all operating modes. If appropriate portions of the display are viewed in conjunction

with the use of the analog flow charts (FEDM Figures 6031 through 6038), troubleshooting time should be minimized.

Figure 1-7 provides a pattern explanation to aid in understanding visual defects; however, the flow chart priority should be observed.

# 1.5 CATASTROPHIC TROUBLESHOOTING PROCEDURE

The following troubleshooting procedure is recommended for analog failures involving multiple troubles that prevent the normal analog diagnostic programs from being loaded and displayed. The procedure should be used as a last resort and only if the analog diagnostic flow charts (paragraph 1.4) have failed to help isolate the problem.

The two programs indicated by this procedure are described in paragraphs 1.5.5 and 1.5.6. The scope sync point for the Full Square program is 02BB1J2B04; for the Character program, the sync point is 02BB1C5B03.

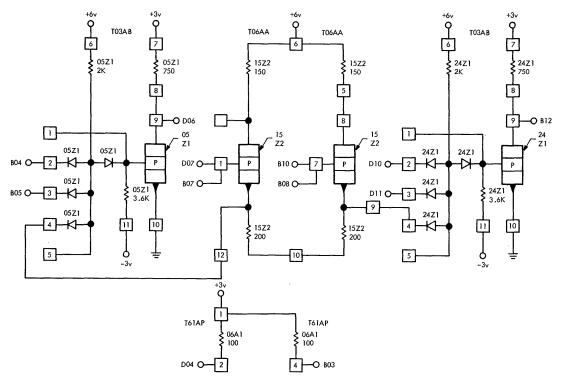

For this procedure, assume that the 2250-1 has every feature. On machines lacking certain features, ignore the procedural steps that apply to those features. In addition, two 2250-1 logic pages, AN101 (PN 5704665) and AN102 (PN 5704676), should be used as reference when performing this procedure.

- 1. Turn dc power off.

- Remove the following analog cards on 01BA2, 01BA3, and 01AA2. Also remove the light pen amplifier card (PN 5807078) at location 01EA1 if the graphic design feature is installed.

# CAUTION

Power must be turned off before inserting or removing any analog cards.

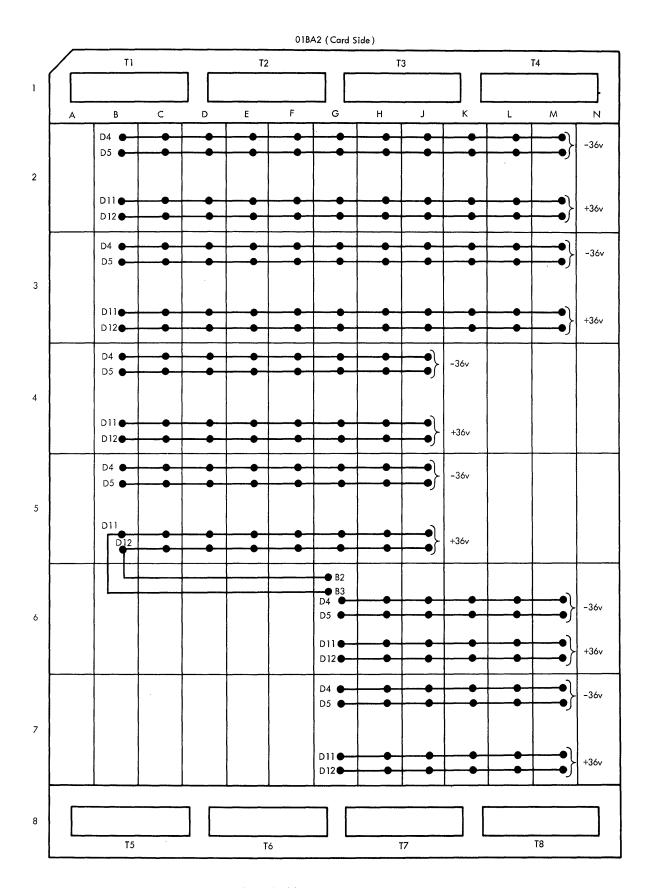

#### Board 01BA2

| Card No. | Location | <u>Function</u>            |

|----------|----------|----------------------------|

| 5804248  | J2/J3    | X, X' Character Driver     |

| 5804247  | K2/K3    | X, X' Character Buffer     |

| 5804247  | L2/L3    | Y, Y' Character Buffer     |

| 5804249  | M2/M3    | Y, Y' Character Driver     |

| 5804246  | J4/J5    | Character Ref V            |

| 5804732  | H2/H3    | Char. Isolation            |

| 5804733  | H6/H7    | Char. Dynamic Intensity II |

| 5800450  | В6       | Light Pen Verification     |

| 5801306  | B4/B5    | Light Pen Amplifier*       |

| 5801307  | G6/G7    | Blank-Unblank I            |

| 5801308  | J6/J7    | Blank-Unblank II           |

| 5800827  | G3       | Async Delay III            |

\*Not used when GDF is installed.

#### Board 01BA2

| Card No. | Location | Function                    |

|----------|----------|-----------------------------|

| 5800825  | G4/G5    | Async Delay II              |

| 5800826  | F4/F5    | Async Delay I               |

| 5800828  | H4/H5    | Deskew Ref                  |

| 5801305  | M6/M7    | Deskew Switch               |

| 5804732  | L6/L7    | Position Isolation          |

| 5804733  | K6/K7    | Vector Dynamic Intensity II |

| 5804731  | B2/B3    | X, X' DC Offset II          |

| 5804731  | C2/C3    | Y, Y' DC Offset II          |

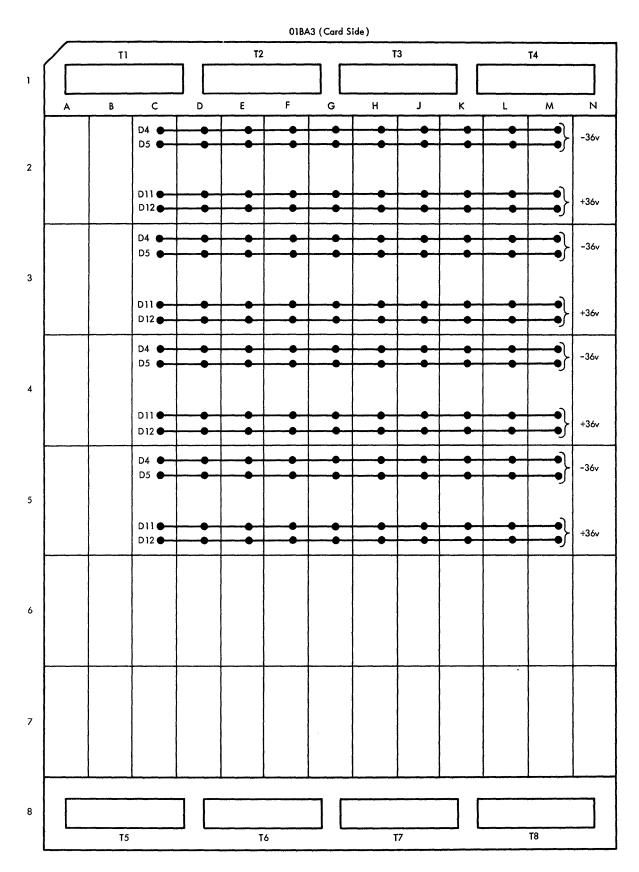

#### Board 01BA3

| Card No. | Location | <u>Function</u>      |

|----------|----------|----------------------|

| 5800831  | F2/F3    | X Centering and Gain |

| 5800831  | H2/H3    | Y Centering and Gain |

| 5800832  | C4/C5    | X Bit O              |

| 5800832  | H4/H5    | Y Bit 0              |

| 5800829  | D4/D5    | X Bits 1 and 4       |

| 5800829  | J4/J5    | Y Bits 1 and 4       |

| 5801304  | E4/E5    | X Bits 2 and 3       |

| 5801304  | K4/K5    | Y Bits 2 and 3       |

| 5801303  | F4/F5    | X' Bits 5 through 9  |

| 5801303  | G4/G5    | X Bits 5 through 9   |

| 5801303  | L4/L5    | Y Bits 5 through 9   |

| 5801303  | M4/M5    | Y' Bits 5 through 9  |

| 5800833  | G2/G3    | Reference Voltage    |

| 5800830  | E3       | Deflection Overdrive |

| 5801309  | D2/D3    | X, X' DC Offset I    |

| 5801309  | K2/K3    | Y, Y' DC Offset I    |

| 5807042  | E2       | X DC Offset          |

| 5807042  | J2       | Y DC Offset          |

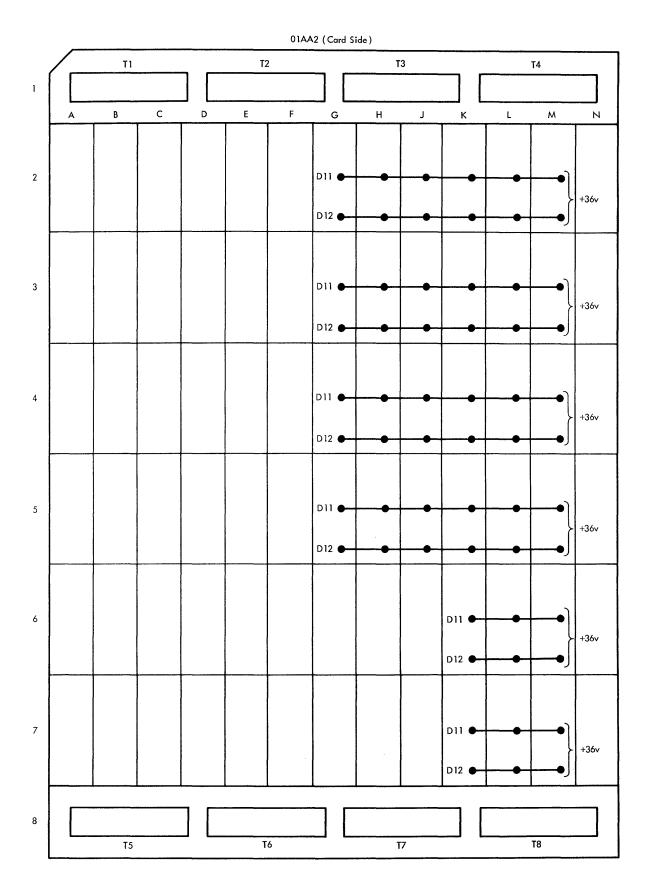

# Board 01AA2 (AVG)

| Card No. | Location | Function          |

|----------|----------|-------------------|

| 5801685  | G4/G5    | Bit 4             |

| 5801686  | H4/H5    | Bit 3             |

| 5801684  | J4/J5    | Bit 2             |

| 5801687  | K4/K5    | Bit 1             |

| 5801687  | L4/L5    | 1/2 Bit OB        |

| 5801687  | M4/M5    | 1/2 Bit <b>0A</b> |

| 5801690  | H2/H3    | 042 Transistor    |

| 5801689  | K2/K3    | Zener Diodes      |

| 5801688  | M2/M3    | Reference Voltage |

- 3. Turn dc power on and measure voltage at following locations:

- a. -36v at laminar bus in 01B.

- b. +36v at laminar bus in 01B.

- c. -36v delayed at laminar bus in 01B.

- d. +3v at laminar bus in 01B.

- e. -3v at laminar bus in 01B.

- f. +6v at laminar bus in 01B.

- 4. Measure yoke clamp voltages at:

- a.  $9v \pm 2v$  at 01BA1C1TB3A20.

- b.  $+61v \pm 5v$  at 01BA1C1TB3A21.

#### DANGER

Perform the following steps with extreme caution because of the magnitude of the voltage involved.

- 5. Turn operator's brightness control and the brightness limiting potentiometer at 01E/ A1R4 fully counterclockwise. Remove dc power and then remove CRT socket from neck of tube. Turn dc power on, and measure the voltages between the following points:

- a. Pins 1 and 12 6.8 vac  $\pm 10\%$

- b. Pin 6 and ground  $+450v \pm 5\%$

- c. Pin 10 and ground  $+450v \pm 5\%$

- d. Pin 2 and ground  $-36v \pm 4\%$

- e. Measure voltage between pin 11 of the CRT socket and ground. Simultaneously, vary brightness control and brightness limiting potentiometer from minimum to maximum. Voltage should vary from approximately +80v to approximately +20v.

- f. Set both controls fully counterclockwise (meter should read approximately +80v). Remove dc power, and replace CRT socket on neck of tube.

- 6. Turn dc power on. Depress CRT INTENSITY switch, located on 01BA1A1 potentiometer panel, and turn brightness controls slowly in clockwise direction. A spot should be visible within 0.75 inch of center of CRT. Release the switch, turn off power, and insert analog cards as described in the steps that follow.

#### CAUTION

Power must be turned off before inserting or removing any analog cards.

- 7. Insert DC offset cards (PN 5804731) in locations 01BA2B2/B3 and 01BA2C2/C3.

- 8. Turn on dc power, and check voltage at card (PN 5804732) location 01BA2L6/L7, pins L6B02, L7B09, and L7B10 with Simpson 270 meter or equivalent. Voltages at these points should be +35v to +36v (ground reference). Also, scope pin L6B03 to determine that online noise does not exceed ±2%.

- 9. Remove dc power, and insert X and Y centering and gain control cards (PN 5800831). These cards are packaged with the centering and gain functions on the same card. The X card location is 01BA3F2/F3; the Y card location, 01BA3H2/H3. It should be possible to move the CRT spot approximately 1-1/2 inches in the X-axis and approximately 1-1/2

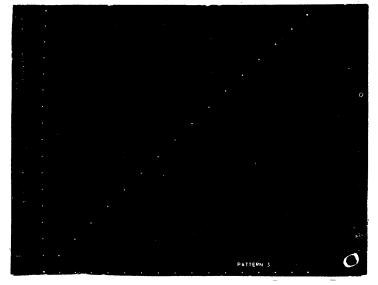

1. Pattern 1 in alignment.

2. Pattern 2 in alignment.

3. Pattern 3 in alignment.

Figure 1-8. Visible Pattern Malfunctions (Sheet 1 of 22)

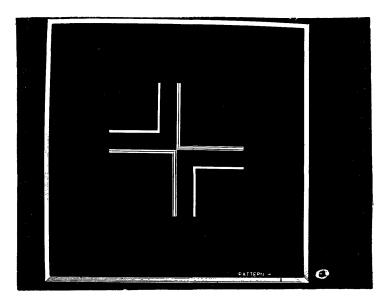

4. Pattern 4 in alignment.

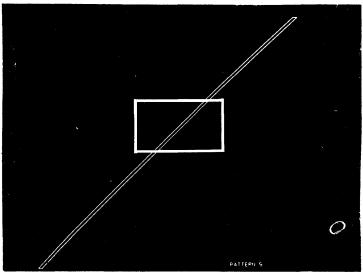

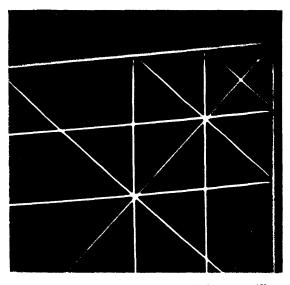

5. Pattern 5 in alignment. Section marked is shown expanded in pictures numbered 5a, 5b, 5c, and 5d.

5a. Expanded pattern 5 in alignment.

Figure 1-8. Visible Pattern Malfunctions (Sheet 2 of 22)

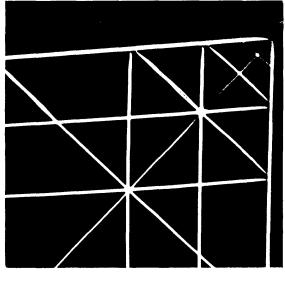

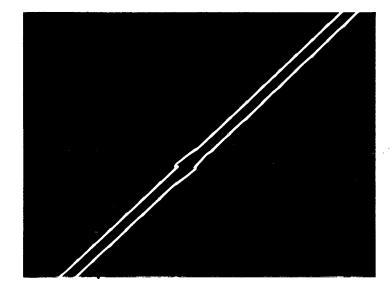

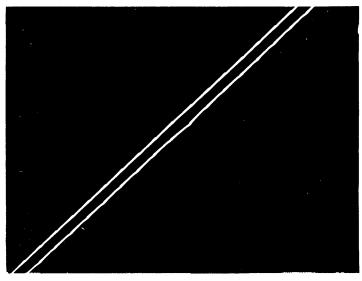

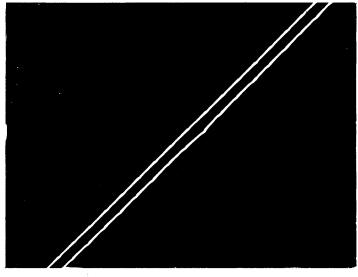

5b. Expanded pattern 5. De-skew reference – loss of voltage. Check 01BA2 H04, H05.

5c. Expanded pattern 5. De-skew reference – shorted transistor on card. Check 01BA2 H04, H05.

•Figure 1-8. Visible Pattern Malfunctions (Sheet 3 of 22)

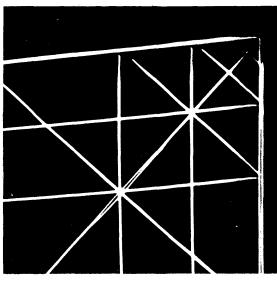

5d. Expanded pattern 5. De-skew switch - open 138 transistor. Check 01BA2 M06, M07.

6. Position isolation - Shorted input diode - L7B09 input. Check 01BA2 L06, L07. X axis input.

7. Position isolation – Shorted input diode – L7B02 input. Check 01BA2 L06, L07. Y axis input.

Figure 1-8. Visible Pattern Malfunctions (Sheet 4 of 22)

8. De-skew switch - shorted 138 transistor. Check 01BA2 M06, M07.

De-skew switch - shorted diode across X yoke. Check 01BA2 M06, M07.

10. De-skew switch - shorted diode across Y yoke. Check 01BA2 M06, M07.

Figure 1-8. Visible Pattern Malfunctions (Sheet 5 of 22)

11. Loss of reference voltage inverter. Check 01BA3 G02, G03.

12. Reference voltage inverter; open 026 transistor. Check 01BA3 G02, G03.

13. Open output transistor gain control (189 transistor). Check 01BA3 F02, F03. X axis.

X axis.

open. Check 01BA3 C04, C05.

14. Bit 0 constant current source

Figure 1-8. Visible Pattern Malfunctions (Sheet 6 of 22)

15. Bit 0 constant current source open. Check 01BA3 H04, H05. Y axis.

16. Bit 0 constant current source shorted, collector to emitter. Check 01BA3 C04, C05. X axis.

shorted, collector to emitter. Check 01BA3 H04, H05. Y axis.

Bit 0 constant current source

17.

Figure 1-8. Visible Pattern Malfunctions (Sheet 7 of 22)

18. Bit 0 constant current source shorted, base to collector. Check 01BA3 C04, C05. X axis.

19. Bit 0 constant current source shorted, base to collector. Check 01BA3 H04, H05. Y axis.

Check 01BA3 C04, C05. X axis.

20.

Bit 0 switch open - B03 input.

Figure 1-8. Visible Pattern Malfunctions (Sheet 8 of 22)

21. Bit 0 switch open - B03 input. Check 01BA3 H04, H05. Y axis.

22. Bit 0 switch shorted collector to emitter - B03 input. Check 01BA3 C04, C05. X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 9 of 22)

23. Bit 0 switch shorted collector to emitter - B03 input. Check 01BA3 H04, H05. Y axis.

24. Bit 1 constant current source open. Check 01BA3 D04, D05. X axis.

25. Bit 1 constant current source shorted, collector to emitter. Check 01BA3 D04, D05. X axis.

Bit 1 constant current source shorted, base to collector. Check 01BA3 D04, D05. X

axis.

26.

Figure 1-8. Visible Pattern Malfunctions (Sheet 10 of 22)

27. Switch 1 open - D10 input. Check 01BA3 D04, D05. X axis.

28. Switch 1 shorted, collector to emitter – D10 input. Check 01BA3 D04, D05. X axis.

29. Bit 2 constant current source open. Check 01BA3 E04, E05. X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 11 of 22)

30. Bit 2 constant current source shorted, collector to emitter. Check 01BA3 E04, E05. X axis.

31. Bit 2 constant current source shorted, base to collector. Check 01BA3 E04, E05. X axis.

Check 01BA3 E04, E05. X axis.

32. Bit 2 switch open - D09 input.

Figure 1-8. Visible Pattern Malfunctions (Sheet 12 of 22)

33. Bit 2 switch shorted, collector to emitter – D09 input. Check 01BA3 E04, E05. X axis.

34. Bit 3 constant current source open. Check 01BA3 E04, E05. X axis.

35. Bit 3 constant current source shorted, collector to emitter. Check 01BA3 E04, E05. X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 13 of 22)

36. Bit 3 constant current source shorted, base to collector.

Check 01BA3 E04, E05.

X axis.

37. Bit 3 switch open - J10 input. Check 01BA3 E04, E05. X axis.

38. Bit 3 switch shorted – J10 input. Check 01BA3 E04, E05. X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 14 of 22)

39. Bit 4 constant current source open. Check 01BA3 D04, D05. X axis.

40. Bit 4 constant current source shorted, collector to emitter. Check 01BA3 D04, D05, X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 15 of 22)

41. Bit 4 constant current source shorted, base to collector. Check 01BA3 D04, D05. X axis.

42. Bit 4 switch open - B02 input. Check 01BA3 D04, D05. X axis.

43. Bit 4 switch shorted, collector to emitter. B02 input. Check 01BA3 D04, D05. X axis.

44. Low – order bits open (card removed F4F5). Check 01BA3 F04, F05. X axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 16 of 22)

45. Low - order bit input diode shorted. Check 01BA3 F04, F05. X axis.

46. Low - order bit; 2 input diodes shorted. Check 01BA3 F04, F05. X axis.

Check circuit located at 01BA1C1 and 01BA1D1.

Loss of +11v clamp.

47.

Figure 1-8. Visible Pattern Malfunctions (Sheet 17 of 22)

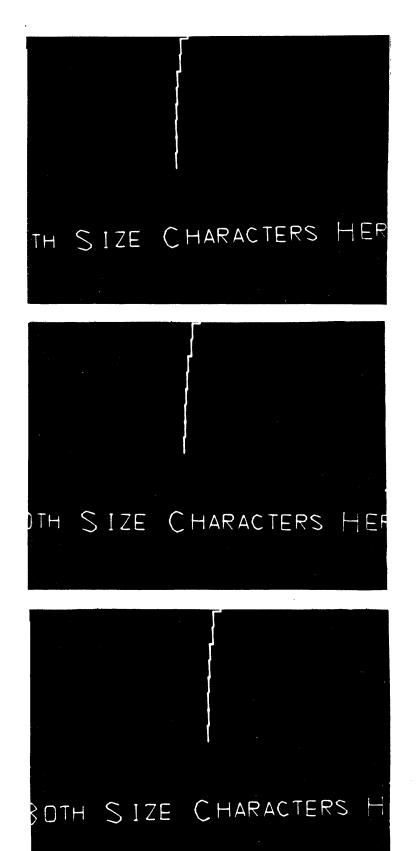

48. Character isolation; open input diode. Check 01BA2 H02, H03. (Also see 48a and 48b.) Y axis.

48a. Character isolation; open input diode. Check 01BA2 H02, H03. Regular-size characters shown. Y axis.

48b. Character isolation; open input diode. Check 01BA2 H02, H03. Large-size characters shown. Y axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 18 of 22)

49. Character isolation-shorted input diode. Check 01BA2 H02, H03. (Also see 49a and 49b.) Y axis.

49a. Character isolation-shorted input diode. Check 01BA2 H02, H03. Effect on regular-size characters shown. Y axis.

49b. Character isolation—shorted input diode. Check 01BA2 H02, H03. Effect on large—size characters shown. Y axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 19 of 22)

50. Character generator – shorted bit 4 collector to emitter. Check 01BA2 M02, M03. (Also see 50a and 50b.) Y axis.

50a. Character generator – shorted bit 4 collector to emitter. Check 01BA2 M02, M03. Effect on regular-size characters shown. Y axis.

50b. Character generator – shorted bit 4 collector to emitter. Check 01BA2 M02, M03. Effect on large-size characters shown. Y axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 20 of 22)

51. Open character buffer. Check 01BA2 L02, L03. (Also see 51a and 51b.) Y axis.

51a. Open character buffer. Check 01BA2 L02, L03. Effect on regular-size characters shown. Y axis.

51b. Open character buffer. Check 01BA2 L02, L03. Effect on large-size characters shown. Y axis.

Figure 1-8. Visible Pattern Malfunctions (Sheet 21 of 22)

52. Analog deflection complete line plus all the time. Check 01BA2 G04, G05.

53. Maladjusted blank-unblank card mounted potentiometer (simulates poor adjustment or partial switching of unblank transistor). Readjust 01BA2 J06, J07.

Figure 1-8. Visible Pattern Malfunctions (Sheet 22 of 22)

- inches in the Y-axis by use of the centering controls. Return the spot to approximate center of CRT.

- 10. Turn on dc power, and check voltage variations on the outputs of the X gain control at 01BA3F3D06 by turning X GAIN potentiometer. Voltage should vary from 0v to approximately -12v. Set voltage at -5v.

- 11. Check for voltage variation in the Y gain control output at 01BA3H3D06. Voltage should vary between 0v and approximately -12v. Set voltage at -5v.

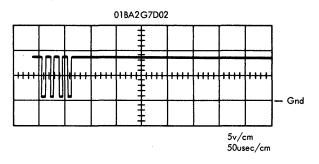

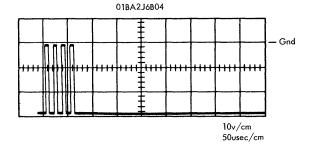

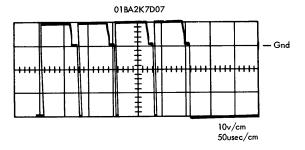

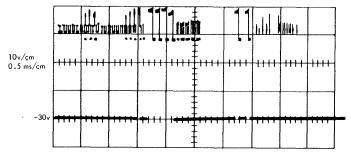

- 12. Remove dc power, and insert blank-unblank I card (PN 5801307) in location 01BA2G6/G7. Turn on dc power, and load the Full Square program (program #1) from CE panel as directed. Scope for voltage swing from

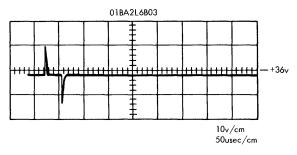

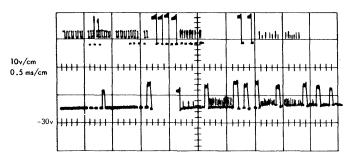

- ground to approximately +8v at 01BA2G7D02. See Figure 1-9.

- 13. Remove dc power, and insert blank-unblank II card (PN 5801308) in location 01BA2J6/J7.

Figure 1-9. DC Intensity I CRT Output

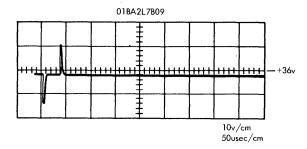

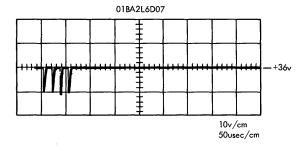

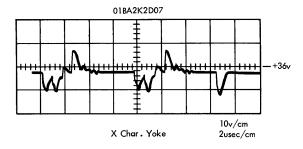

Turn on dc power, and scope for a voltage swing of -30v to ground at 01BA2J6B04. If necessary, adjust card-mounted potentiometer until -30v level slowly goes positive. Then, reverse direction of control until -30v level is again solid, and rotate control approximately two more turns. With potentiometer adjusted, a spot should appear in the middle of the CRT. See Figure 1-10. (CRT INTENSIFY pushbutton should not be used now.)

Figure 1-10. Blank-Unblank II CRT Output

- 14. Remove dc power, and install reference voltage inverter driver card (PN 5800833) in location 01BA3G2/G3.

- 15. Turn on dc power, and check the voltage for X output at 01BA3G2D09 and Y output at 01BA3G3D09. Voltage should vary between ground and at least -12v when associated gain control potentiometer is adjusted from minimum to maximum. Set potentiometers for -4v output.

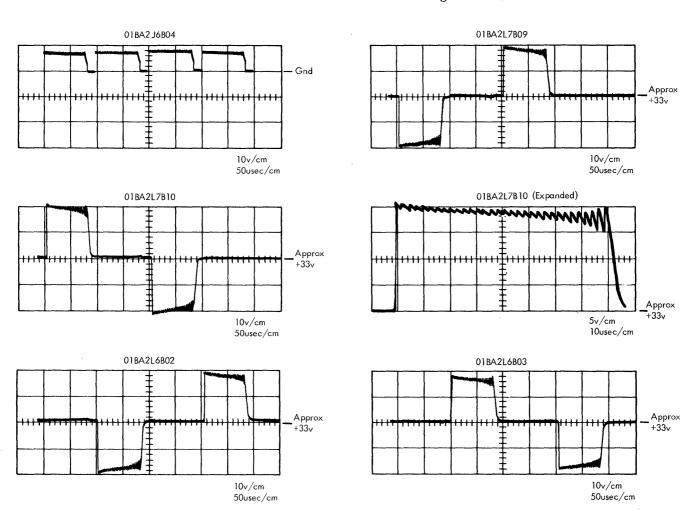

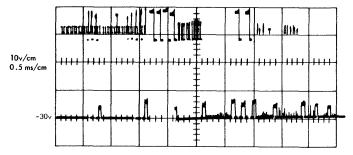

- 16. Remove dc power, and install bits 5 through 9 for both the X- and Y-axes, which comprises a total of four cards (PN 5801303). The X card locations are 01BA3F4/F5 and 01BA3G4/G5; the Y card locations, 01BA3L4/L5 and 01BA3M4/M5.

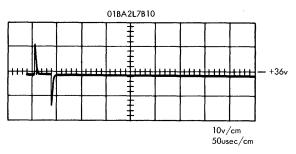

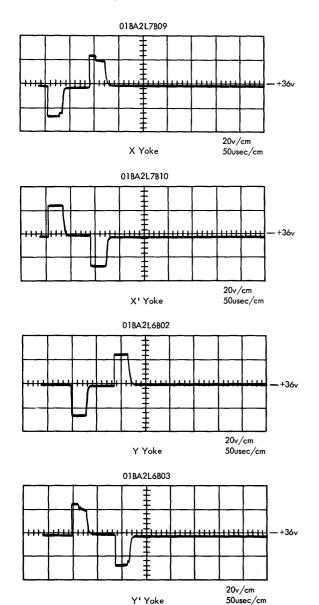

- 17. Turn on dc power. Using the Full Square program, observe bit-switching on the CRT. The display should be a square of approximately 3/8 inch. If the corners are overshooting, it may be necessary to adjust position damping. Observe the yoke waveforms at the points indicated in Figure 1-11.

ı

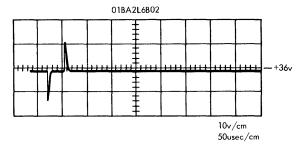

- 18. Remove dc power, and insert position isolation card (PN 5804732) in location 01BA2L6/L7. Turn on power, and scope the output at 01BA2L6D07 for signal swing of +36v to approximately +20v. See Figure 1-12.

- 19. Turn off power, and insert asynchronous delay card PN 5800825 in position 01BA2G4/G5, PN 5800826 in 01BA2F4/F5, and PN 5800827 in 01BA2G3. Turn on power, and ensure that full-square pattern is still present and undistorted.

Figure 1-11. Yoke Waveforms, Bits 5 Through 9 Active

Figure 1-12. Position Isolation Output

- 20. Turn off power, and insert X and Y bit 0 cards (PN 5800832) in 01BA3C4/C5 and 01BA3H4/H5.

- 21. Turn on power, and check CRT for approximately a 6-inch square. Observe yoke waveforms at points indicated in Figure 1-13.

Figure 1-13. Yoke Waveforms, Bit 0, and Bits 5 Through 9 Active

- 22. Observe change in waveform at 01BA2L6D07 as shown in Figures 1-12 and 1-14.

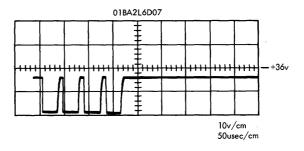

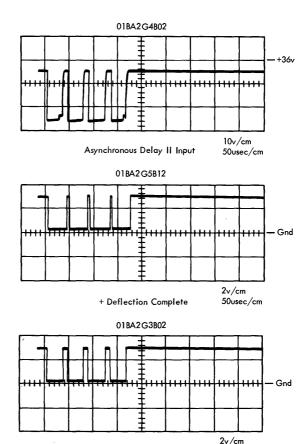

- 23. Observe asynchronous delay waveforms at 01BA2G4B02, 01BA2G5B12, and 01BA2G3B02. They should be as shown in Figure 1-15.

Figure 1-14. Position Isolation Output, Yoke Clamped

Figure 1-15. Asynchronous Delay Waveforms

+ Early Deflection Complete

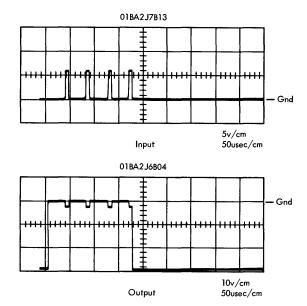

- 24. Observe blank-unblank waveforms at 01BA2J7B13 and 01BA2J6B04. They should be as shown in Figure 1-16.

- 25. Turn off power, and install X and Y bits 1 and 4, card PN 5800829, in locations 01BA3J4/J5 and 01BA3D4/D5.

50usec/cm

26. Turn on power, and check CRT for approximately a 9-1/2-inch square. (Waveforms will be essentially the same. The only difference will be longer times because of longer deflection distances.)

Figure 1-16. Blank-Unblank Waveforms

- 27. Turn off power, and install bits 2 and 3, card PN 5801304, in locations 01BA3E4/E5 and 01BA3K4/K5.

- 28. Turn on power, and check CRT for approximately a 12-inch square. (Waveforms will be essentially the same. The only difference will be longer times because of longer deflection distances.)

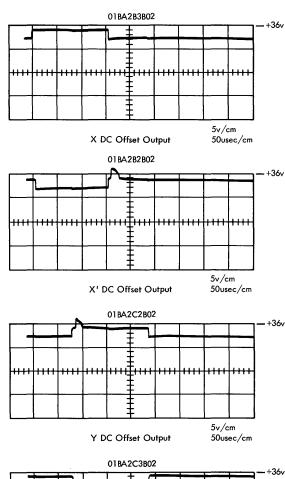

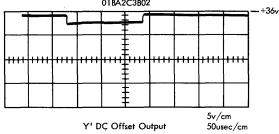

- 29. Insert DC offset cards (PN 5801309) in 01BA3D2/D3 and 01BA3K2/K3. Install low-order DC offset card (PN 5807042) in 01BA3E2 and 01BA3J2. Scope at points indicated in Figure 1-17.

- 30. At this point, the analog deflection system is operating correctly and should be capable of being aligned. Display normal analog alignment program (#766 pattern 1), and align as prescribed in paragraph 4.2. That is, adjust size, centering, dc offset, damping, bit weights, and brightness controls.

- 31. Turn off power, and insert dynamic intensity II, card PN 5804733, in location 01BA2K6/K7. With power on, but before starting program, measure voltage at 01BA2L6D07. Adjust card-mounted potentiometer in location 01BA2L6/L7 for a 0.5v negative level with respect to +36v. Using Full Square program, scope at 01BA2K7D07 (maximum positive amplitude depends on vector contrast control setting). See Figure 1-18.

# 1.5.1 De-Skew Check

- 1. Turn off dc power.

- 2. Insert de-skew card (PN 5801305) in

Figure 1-17. DC Offset Outputs

- 01BA2M6/M7 and card PN 5800828 in 01BA2H4/H5.

- 3. Turn on power.

- 4. Using normal De-Skew Alignment program (pattern 5 of program F756 or F766), adjust single-shot in 02BB1F2D02 for a negative pulse whose trailing edge occurs 100ns before the positive transition of TP6 at 02BB1H6B09. (Refer to Note 13 of Figure 4-6 for SS adjustment.) Adjust single-shot in 02BB1E2D13 (middle) to minimize any irregularities on CRT.

Figure 1-18. Position System Dynamic Intensity II Output

# 1.5.2 Character Generator Check

- 1. Turn off power.

- 2. Insert character reference voltage card (PN 5804246) in location 01BA2J4/J5.

- 3. Turn on power.

- 4. Check voltage at 01BA2J4D09 with Simpson 270 (or equivalent) meter while rotating the X CHAR SIZE potentiometer. This voltage should vary approximately 1v somewhere in the range of +4.0v to +6.3v.

- 5. Check 01BA2J4B04, and rotate Y CHAR SIZE potentiometer. This voltage should vary approximately 1v somewhere in the range of 4.0v to 6.3v.

- Turn off dc power, and insert the following character cards:

- X buffer 5804247 in location 01BA2K2/K3.

- Y buffer 5804247 in location 01BA2L2/L3.

- X driver 5804248 in location 01BA2J2/J3.

- Y driver 5804249 in location 01BA2M2/M3.

- Turn on dc power. Load the character program (program #2), and, if required, perform the following operations while observing the CRT:

- a. While observing the character "A", adjust X, X', Y, Y' CHAR DAMPING potentiometers for the best straight lines and so that the end points are not dropped.

- b. Adjust X and Y CHAR SIZE controls. The character size should be adjusted for Y displacement of approximately 0.160 inch and X displacement of approximately 0.120 inch. (Character overdrive is still out; therefore, spacing for the second "A" may not be correct.)

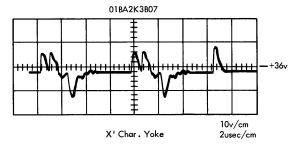

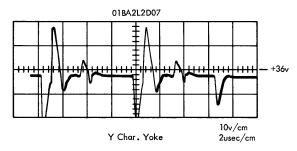

The character yoke waveforms should be as shown at the indicated points in Figure 1-19.

- 8. Turn off dc power, and insert character overdrive card (PN 5800830) in location 01BA3E3.

- 9. Turn on dc power.

- 10. Check to ensure that single-shot located in 02BB1F3B02 is set for approximately 2.75usec

Figure 1-19. Character Yoke Waveforms

and that single-shot located in 02BB1G2B02 is set for approximately 3. Ousec (for B-size characters). (See Note 13 of Figure 4-6 for method of adjusting SS.)

- 11. Use character program #2, and adjust single-shot located in 01BA3M6B02 until characters become distorted. Reverse adjustment slightly until characters are normal. Spacing between the characters should now be corrected.

- 12. Remove dc power, and insert character isolation card (PN 5804732) in 01BA2H2/H3. Insert dynamic intensity II card (PN 5804733) in 01BA2H6/H7. Turn on dc power, but, before starting program, measure voltage at

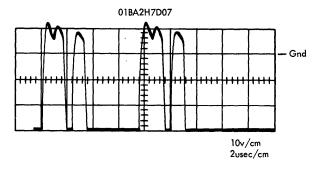

01BA2H2D07. Adjust card-mounted potentiometer in location 01BA2H2/H3 for 0.5v negative level with respect to +36v. Using the Character program, scope at 01BA2H7D07 (maximum positive amplitude dependent on setting of character contrast control). See Figure 1-20.

Figure 1-20. Character System Dynamic Intensity II Output

# 1.5.3 Light Pen Check With GDF

Use program F76B for this check. If the proper intensity alignment procedure has been followed as specified in paragraph 4.2.2, step 1, correct light pen alignment and operation will be obtained if the operator's brightness control is set fully clockwise (maximum brightness).

Perform light pen check as follows:

- Remove dc power, and insert light pen verification card in 01B-A2B6. Turn on dc power, run program, and check display for intensity distortion (broken vectors or noise on CRT).

- 2. If no intensity distortion is present, remove dc power, and install light pen amplifier card (PN 5807078) in 01E-A1.

NOTE: Do not operate the Light Pen Detect switch during alignment.

- 3. Turn on dc power and run program. Place LP ALIGN switch (potentiometer panel) in ON position. This will affect targets as follows:

- a. Distortion to a character.

- b. A partial blanking of a vector near the pen.

- c. A small unblanked vector will appear displaced down and to the left from a detected point.

- 4. Place LP ALIGN switch in OFF position.

# 1.5.4 Light Pen Check Without GDF

Use program F784 for this check. If the proper intensity alignment procedure has been followed as specified in paragraph 4.2.2, step 1, correct light pen alignment and operation will be obtained if the operator's brightness control is set fully clockwise (maximum brightness).

Perform light pen check as follows:

- 1. Remove dc power, and insert light pen verification card in 01B-A2B6. Turn on dc power, run program, and check display for intensity distortion (broken vectors or noise on CRT).

- 2. If no intensity distortion is present, remove dc power, and ensure that light pen paddle card is in 01BA2A5.

- 3. Insert light pen amplifier card (PN 5801306) in 01BA2B4/B5.

- 4. Turn on dc power, and measure level at 01BA2B5B07. Voltage should be  $+10v \pm 1v$ .

- 5. Measure dc level at 01BA2B5B13. Voltage should be  $+33y \pm 0.5y$ .

- Align light pen as described in paragraph

4.2.8.

## 1.5.5 AVG Check

- 1. Turn off power, and insert 30v reference supply cards in the following locations:

- a. Heat sink and 042 transistor, PN 5801690; install in 01AA2H2/H3.

- b. Heat sink and Zener diode, PN 5801689; install in 01AA2K2/K3.

- c. Reference voltage amplifier, PN 5801688; install in 01AA2M2/M3.

- 2. Apply power, and (using Simpson 270 meter or equivalent) measure the voltage from pin locations 01AA2H2B08 and 01AA2H2B09 to ground as the REF VOLTS potentiometer on the 01AA1 potentiometer panel is varied from maximum clockwise to maximum counterclockwise. Voltage at the pins should vary from at least +28vdc to +32vdc. Adjust this voltage to +29vdc ±0.1v.

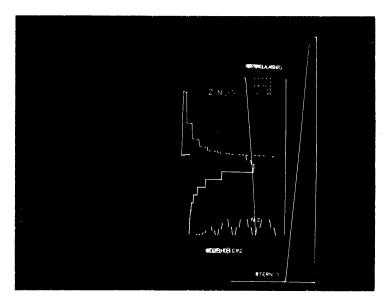

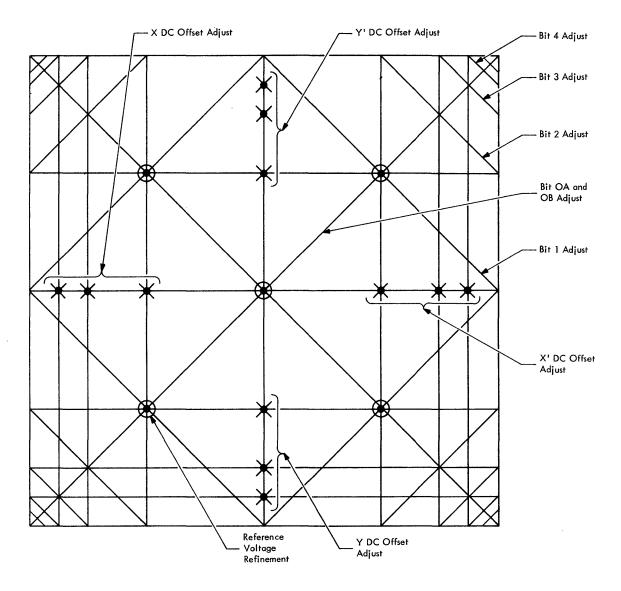

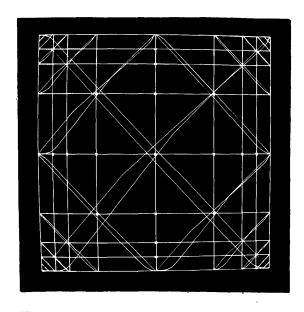

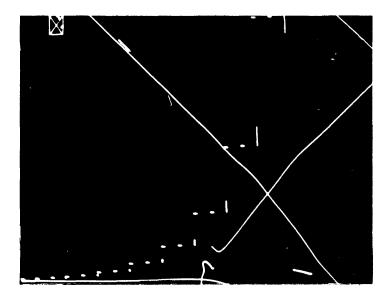

- 3. With power off, insert card PN 5801685 in location 01AA2G4/G5. Apply power, and display the vector graphic alignment pattern (Program Set 767/757).

- 4. Scope 01AA2G4B03 (sync at 02BB1J2B04), and ascertain that square wave is 2.5usec ±1 percent in width for both positive and negative transitions. (The delay line is located at 01AA2G6.)

- 5. Scope 02BB1K2D12, and (using upper potentiometer) adjust the negative pulse for 200ns ±5 percent.

- 6. Scope 02BB1M6D12, and (using upper potentiometer) adjust the negative pulse for 250ns ±10 percent.

- 7. Ensure that BIT 4 control on 01AA1 potentioneter panel can vary the second set of 45-degree double-traced lines at the four corners of the display. Adjust for minimum spacing between lines.

- 8. Remove power, and insert card PN 5801686 in location 01AA2H4/H5. Apply power, and ensure that BIT 3 control on 01AA1 potentiometer panel can vary the third set of 45-degree double-traced lines at the four corners of the display. Adjust for minimum spacing between the lines.

- 9. Remove power, and insert card PN 5801684 in location 01AA2J4/J5. Apply power, and ensure that BIT 2 control on 01AA1 potentiometer panel can vary the fourth set of 45-degree double-traced lines at the four corners of the display. Adjust for minimum spacing between the lines.

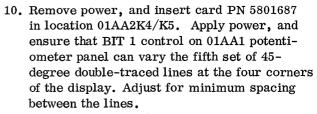

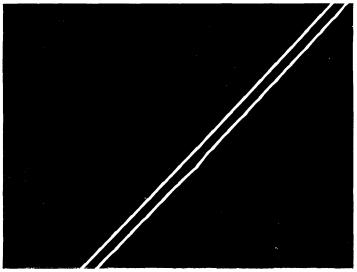

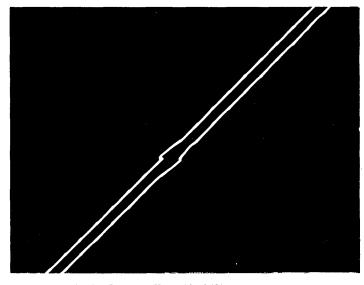

- 11. Remove power, and insert two PN 5801687 cards in locations 01AA2L4/L5 and 01AA2M4/M5. Apply power, and ensure that BIT 0 controls on 01AA1 potentiometer panel can vary the diagonals on the 12-inch by 12-inch display. Adjust for minimum spacing between the lines.

- 12. Normal AVG alignment should now be made as prescribed in paragraph 4.2.9.

- 13. With the exception of the waveforms in Figure 1-21, the previously shown waveforms should not be altered (except a longer time base) as a result of the absolute vector graphic feature. Use the Full Square program, sync at 02BB1J2B04, and scope at points called out in Figure 1-21.

Figure 1-21. AVG Waveforms

# 1.5.6 Program 1, Full Square

The following procedure results in a 12-inch by 12-inch full square display. The program is loaded from the CE panel as follows:

- 1. Set LOAD SELECT switch to BUFFER position, and place REGENERATE switch in the off (down) position.

- 2. Depress MACHINE RESET.

- 3. Place switches in the order listed below, and depress ENTER switch after each setting:

- a. 2A

- ъ. 82

- c. 2A

- d. 02

- e. OF

- FC.

- 00

- 00

- f. OF

- FC

- OF

- FC g. 00

- 00

- 0F

- FC h. 00

- 00

- 00

- 00

- i. 2A j. FF

- k. 00

- 1. 00

- 4. Depress MACHINE RESET.

- 5. Start regeneration.

# 1.5.7 Program 2, "A" Characters

The following procedure results in a display of two "A" characters on the left center of the CRT. The program is loaded from the CE panel as follows:

- 1. Set LOAD SELECT switch to BUFFER position, and place REGENERATE switch in the off (down) position.

- 2. Depress MACHINE RESET.

- 3. Set switches in the order listed below, and depress ENTER switch after each setting:

- a. 2A

- ь. 82

- c. 2A

- d. 02

- e. 40

- f. 00

- g. 08

- h. 00 i. 2A

- j. 40

- k. C1

- 1. C1

- m. 2A

- n. FF

- o. 00

- p. 00

- 4. Depress MACHINE RESET.

- 5. Start regeneration.

# SECTION 3. SYMPTOM INDEX

Field Engineering generates and distributes the Symptom Index. Insert this index following this page.

# SECTION 4. SERVICE AIDS

Field Engineering generates and distributes Service Aids. Insert these service aids following the Symptom Index.

# CHAPTER 2. MAINTENANCE FEATURES

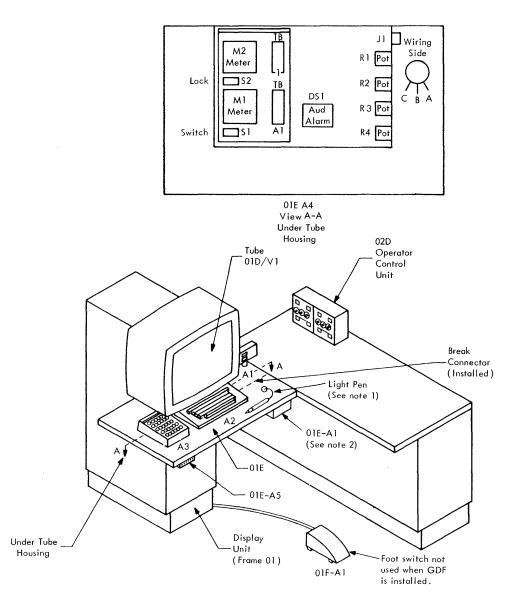

This chapter outlines and briefly describes the features of the 2250-1 that are provided to aid the CE during scheduled and corrective maintenance. The feature include the operator, power, and manual controls and indicators (CE panel and analog potentiometer panel) and the program-monitoring capabilities provided by the sense and status bytes and the Read XY Position command.

#### 2.1 OPERATOR CONTROLS

The operator controls, located along the right side of the tube housing, are briefly described as follows:

BRIGHTNESS

LIMITING

POTENTIOMETER:

BRIGHTNESS:

Limits CRT intensity. Adjusts CRT intensity.

LINE/VECTOR

CONTRAST:

Adjusts line and vector contrast.

CHARACTER

CONTRAST: POWER ON:

Adjusts character contrast. Initiates power-on sequence if

REMOTE/LOCAL switch is set

to LOCAL position.

POWER OFF:

Drops power if REMOTE/LOCAL

switch is in LOCAL position.

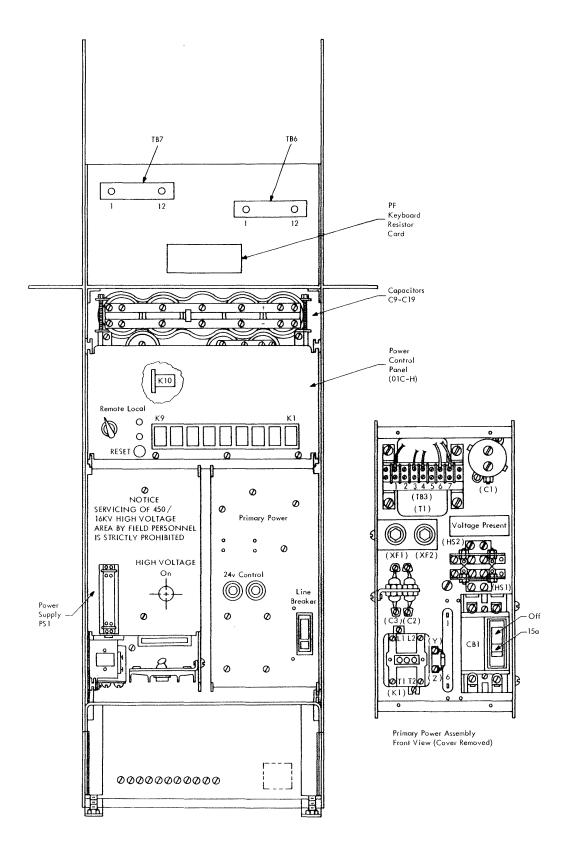

# 2.2 POWER SUPPLY PANEL

The power supply panel is located under the console station.

REMOTE/LOCAL:

The power-on/-off sequences are controlled by the system power contacts when REMOTE/LOCAL switch is in REMOTE position. The power-on/-off sequences are controlled by POWER ON and POWER OFF console switches when REMOTE/LOCAL switch is in

LOCAL position.

THERM RESET:

Restores power after a thermal condition when the thermal condition has cooled and no power control switches have been operated. If one of the power control switches has been operated, THERM RESET

is ineffective.

LINE BREAKER:

Removes power from entire power system when primary power input

is overloaded.

HIGH VOLTAGE

ON:

When lit, indicates that the 16kv supply is on.

CB ALARM: Indicates that one of the CB's has

tripped.

THERM ALARM: Indicates that operating tempera-

tures have exceeded a safe level. Indicates a fuse blown in the 24v

#### 2.3 CE PANEL CONTROLS AND INDICATORS

#### 2.3.1 Controls

24V CONTROL:

All CE panel controls except IND TEST, MACHINE RESET, and the FEATURE ENABLE switch are inoperative unless the machine is logically disabled and the CE Key switch is in the CE position. (See FEDM Figure 9006.) In the following list, if a feature is required to activate a control, the feature is identified:

IND TEST: Checks all operational indicators

when depressed.

MACHINE RESET: Resets all registers and controls

when depressed.

INTERFACE OUT: Seven switches that simulate the

> interface control signals from the channel. In the down position, they simulate the 2250 response to

the control signals.

BUS OUT: Nine switches that simulate bus out

data from the channel.

LOAD SELECT: Four-position switches that select

> areas to be loaded with data from Bus Out switches. The four posi-

tions are:

1. BAC HIGH - Enters data into the high-order positions of the

BAC.

2. BAC LOW - Enters data into the low-order positions of the

3. BUFFER - Permits data entry into the 2250-1 buffer.

4. REG B - Permits data entry into

registers A and B.

ENTER: Transfers contents of BUS OUT

switches to area selected by LOAD

SELECT switch.

CURSR: This switch removes (REMV) or

> inserts (INS) a Cursor bit when LOAD SELECT is in BUFFER or REG B position and ENTER switch

is depressed.

TPD MODE: A two-position switch that selects

> mode of TPD operation as follows: 1. AUTO NORM - TPD operates

at machine speed.

2250-1 FEMM (1/68) 2-1

|                 | <ol> <li>SINGLE STEP - TPD generates<br/>one pulse for each depression of<br/>SINGLE STEP pushbutton.</li> </ol>                                                                                               |                                                                                                                                                                                                                                                                              | Assignment of switch positions is described in paragraph 2.3.2 under "Switched Indicators." |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| SINGLE STEP:    | Causes TPD to generate a single pulse when TPD MODE switch is in SINGLE STEP position.                                                                                                                         | 2.3.2 <u>Indicators</u>                                                                                                                                                                                                                                                      |                                                                                             |  |

| READ BUFFER:    | Depressing this switch causes contents of buffer address to be read into register B. Releasing the switch writes the information back into the buffer and steps BAC to next-higher address. Repeated operation | All indicators are mounted on the CE panel (FEDM Figure 9006) except sense byte 0, which is located to the left of the CRT under the table top. In the list that follows, the feature that is required to activate the indicator is identified.  Sense Byte 0 (4 indicators) |                                                                                             |  |

|                 | sequentially steps through any por-<br>tion of the buffer. (Buffer feature                                                                                                                                     | Command Reject (bit 0):                                                                                                                                                                                                                                                      | Indicates an invalid modifier bit in the command or an in-                                  |  |

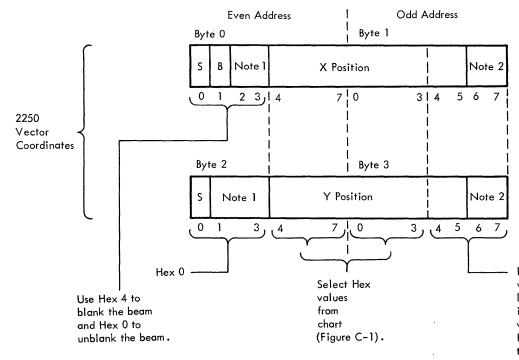

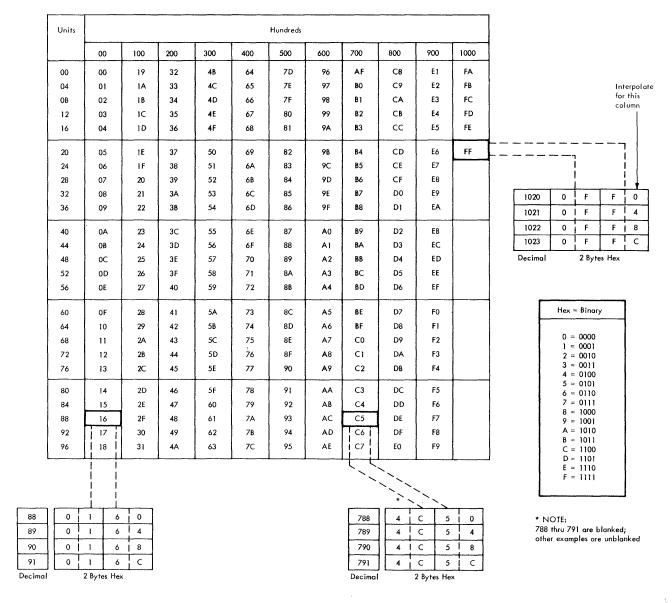

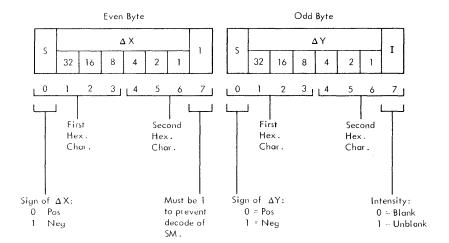

|                 | required.)                                                                                                                                                                                                     | n 0 . 01 1 1 1 . 01                                                                                                                                                                                                                                                          | valid command sequence.                                                                     |  |