## Systems Reference Library

# IBM System/360 Basic Programming Support

Basic Assembler

Program Logic Manual

This publication provides detailed information on the internal logic of the IBM System/360 Basic Programming Support Basic Assembler. It is intended for technical personnel who are responsible for analyzing program operation, diagnosing malfunctions, and/or adapting the program to special usage.

This manual is designed to give the reader a thorough understanding of the functioning of the Basic Programming Support Basic Assembler Program.

Effective use of this publication is based on an understanding of the IBM System/360 machine operations and the System/360 Basic Programming Support Basic Assembler Language. This information can be found in the following IBM System/360 publications:

IBM System/360 Principles of Operation,

Form A22-6821

IBM System/360 Basic Programming Support Basic Assembler Language, Form C28-6503

The first section of this manual presents the overall purpose and description of the Basic Programming Support Basic Assembler program. A breakdown of the Basic Programming Support Basic Assembler into its major components is also provided in this first section. The remainder of the manual is devoted to more detailed descriptions and flowcharts of the major components, down to the function block level. If more detail is needed than that provided by the function block description, the reader is referred to the Basic Programming Support Basic Assembler Program listing.

MAJOR REVISION (June, 1965)

This publication is a major revision of the previous edition, Form C28-6555-0, which is now obsolete. Significant changes have been made throughout this publication. The new edition should be reviewed in its entirety.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

Copies  $\,$  of this and other IBM publications can be obtained through IBM Branch Offices.

A form for readers' comments appears at the back of this publication. It may be mailed directly to IBM. Address any additional comments concerning this publication to the IBM Corporation, Program Logic Documentation, Department D89, PO Box 390, Poughkeepsie, N.Y. 12602

© 1965 by International Business Machines Corporation

| GENERAL INTRODUCTION 7                  | CNOP Translation - Chart AC            |

|-----------------------------------------|----------------------------------------|

| 7. V                                    | (Blocks 01-09)                         |

| Purpose of Program                      | DS Translation - Chart AD              |

|                                         | (Blocks 10-20)                         |

| Program Organization                    | DROP Translation - Chart AD            |

|                                         | (Blocks 12-15)                         |

| Overall Operation of Program 7          | EJECT Translation - Chart AD           |

| Phase I (Chart 01) 7                    | (Blocks 01-02) 34                      |

| Phase II (Chart 02) 8                   | END Translation - Chart AD             |

|                                         | (Blocks 08-11) 34                      |

| Storage Allocation 9                    | ENTRY Translation - Chart AD           |

|                                         | (Blocks 03-07)                         |

| I/O Flow 9                              | EQU Translation - Chart AE             |

|                                         | (Blocks 01-08)                         |

| PHASE I                                 | EXTRN Translation - Chart AE           |

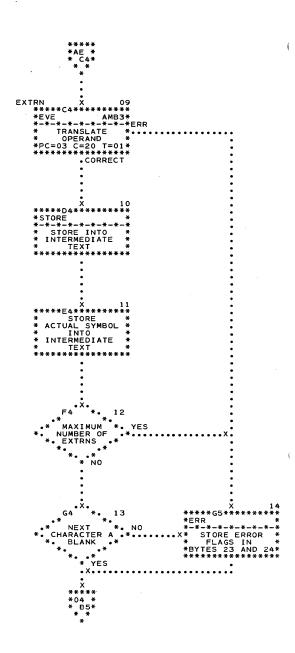

|                                         | (Blocks 09-14) 37                      |

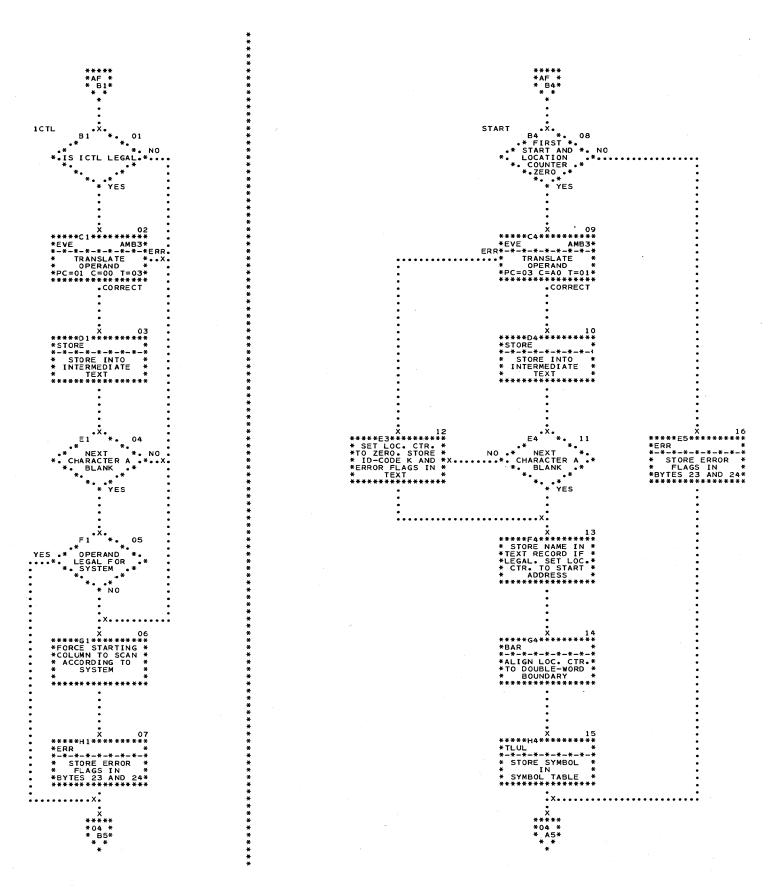

| Section 1: Introduction                 | ICTL Translation - Chart AF            |

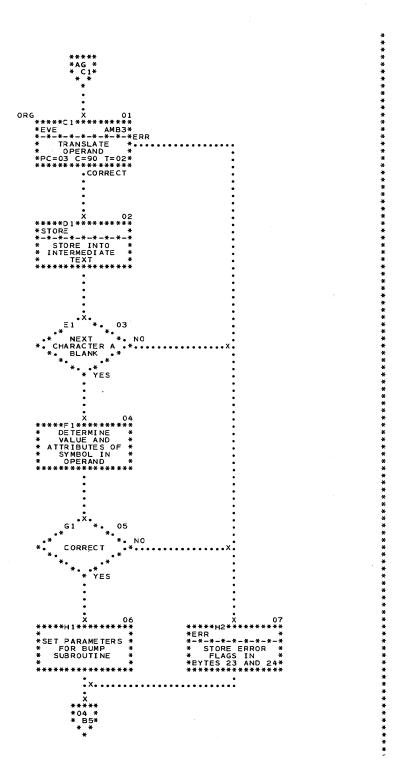

| Replace the Symbolic Operation          | (Blocks 01-07)                         |

| Code with Its Machine Language          | ORG Translation - Chart AG             |

| Equivalent                              | (Blocks 01-07)                         |

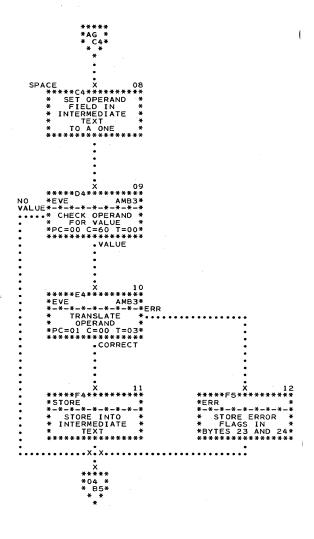

| Translate Symbolic Operands into        | SPACE Translation - Chart AG           |

| Intermediate Text 15                    | (Blocks 08-12)                         |

| Allocate Storage for                    | START Translation - Chart AF           |

| Intermediate Text                       |                                        |

| intermediate fext                       | (Blocks 08-16)                         |

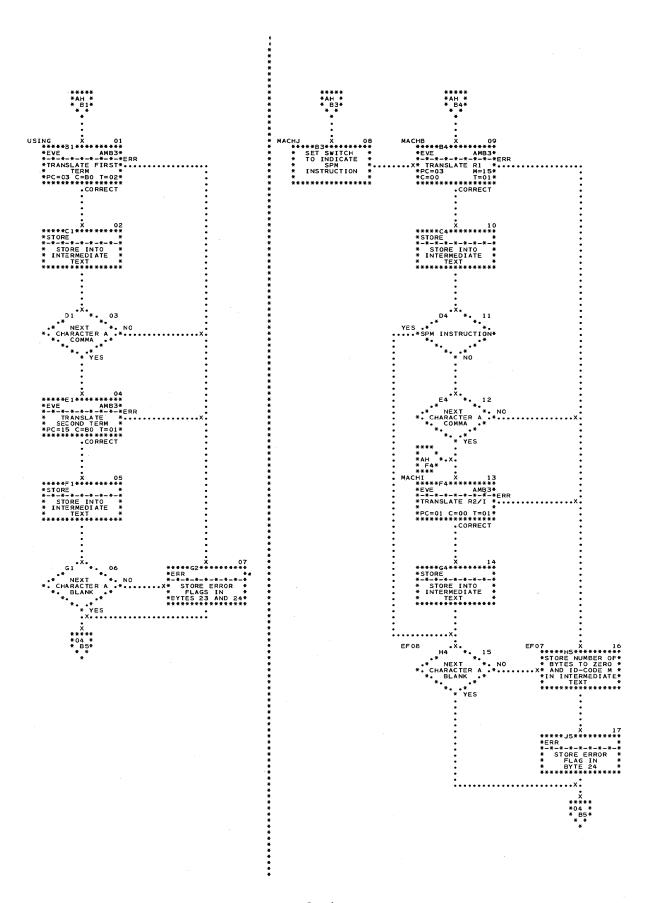

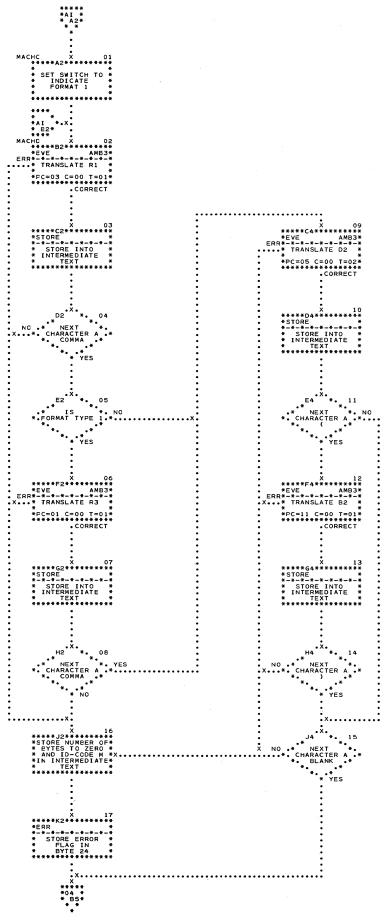

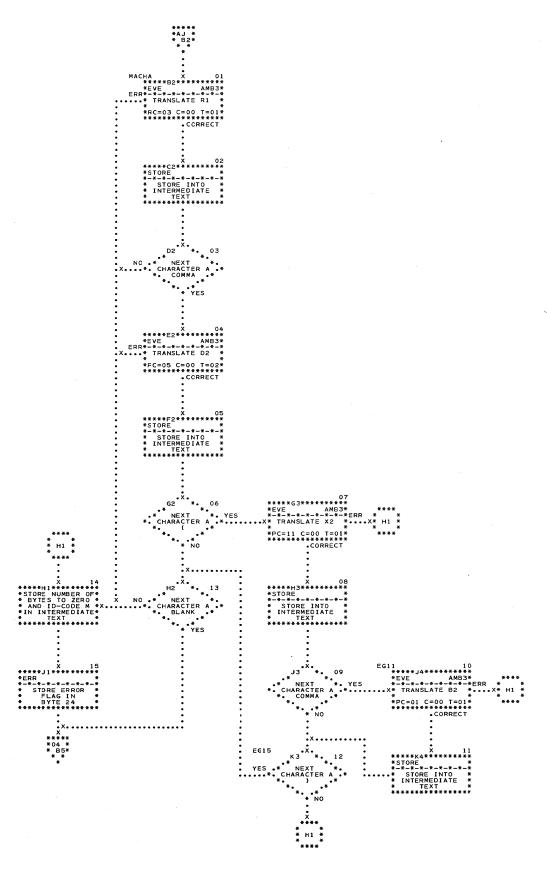

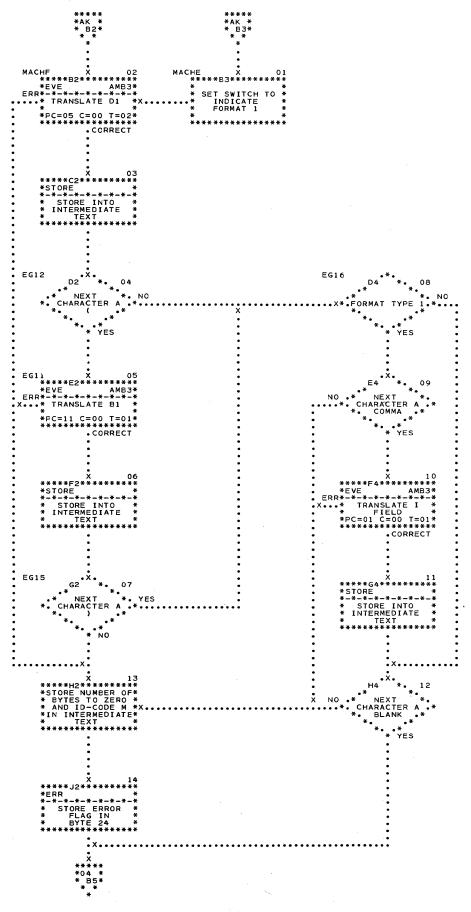

| 0 13 0 million 46                       | USING Translation - Chart AH           |

| Section 2: Tables                       | (Blocks 01-07)                         |

| Intermediate Text 16                    | Machine Instruction Statements 42      |

| Byte 1 - ID-Code 16                     | RR Format Translation - Chart AH       |

| Byte 2 - Operation Code 16              | (Blocks 08-17) 42                      |

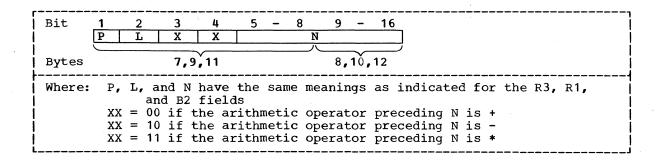

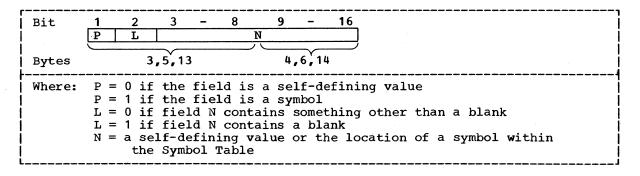

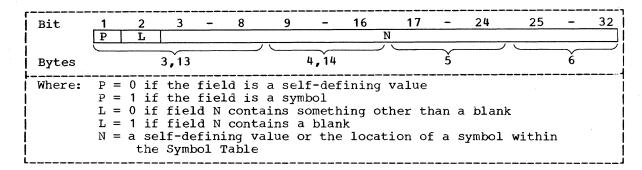

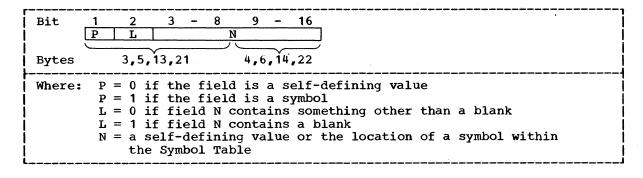

| Bytes 3-22 - Operand Field 16           | RS Format Translation - Chart AI . 43  |

| Bytes 21-24 - Error Flags 16            | RX Format Translation - Chart AJ . 45  |

| Operation Code Table 16                 | SI Format Translation - Chart AK . 46  |

| Symbol Table                            | SS Format Translation - Chart AL . 47  |

| Location                                |                                        |

| Length                                  | PHASE II 71                            |

| Relocatability 18                       | •                                      |

| Defined Bit 18                          | Section 1: Introduction 71             |

|                                         | Translate Intermediate Text into       |

| Section 3: Subroutine Description 20    | Machine Language 71                    |

| EVE - Evaluation Routine                | Produce Output Cards 71                |

| (Charts AM and AN) 20                   | Produce Object Program Listing 74      |

| ERR - Store Error Flags 21              |                                        |

| BAR - Boundary Alignment Routine . 21   | Section 2: Tables                      |

| STORE - Store into Intermediate         | Register Table                         |

| Text                                    | Relocation List Dictionary (RLD)       |

| BUMP - Increment Location               | Table                                  |

| Counter                                 | Table                                  |

| TLUN/TLUS - Symbol Table                | Section 3: Subroutine Description 76   |

|                                         |                                        |

| Procedures 23                           | SER - Simple Expression                |

| INOUT - Input/Output Subroutine         | Translation Routine 76                 |

| (CHARTS AO and AP) 24                   | EER - Compound Expression              |

|                                         | Translation Routine                    |

| Section 4: Phase I Processing Flow 26   | PRTA - Print Subroutine 78             |

| Initialization - Chart 03 26            | PCHA - Store into Punch Buffer         |

| Control Routine - Chart 04 26           | Routine                                |

| Control Routine - Chart 05 27           | Punch RLD and END Cards Routine 79     |

|                                         | DOUT - Punch TXT Cards Routine 79      |

| SECTION 5: Operand Field Translation 29 | FERR - Store Error Flags Routine . 79  |

| Assembler Instruction Statements 29     | INOUT - Input/Output Subroutine 79     |

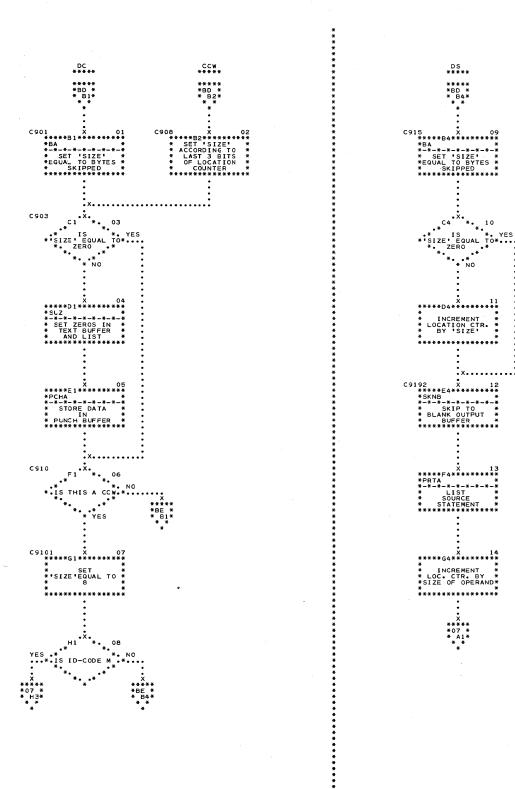

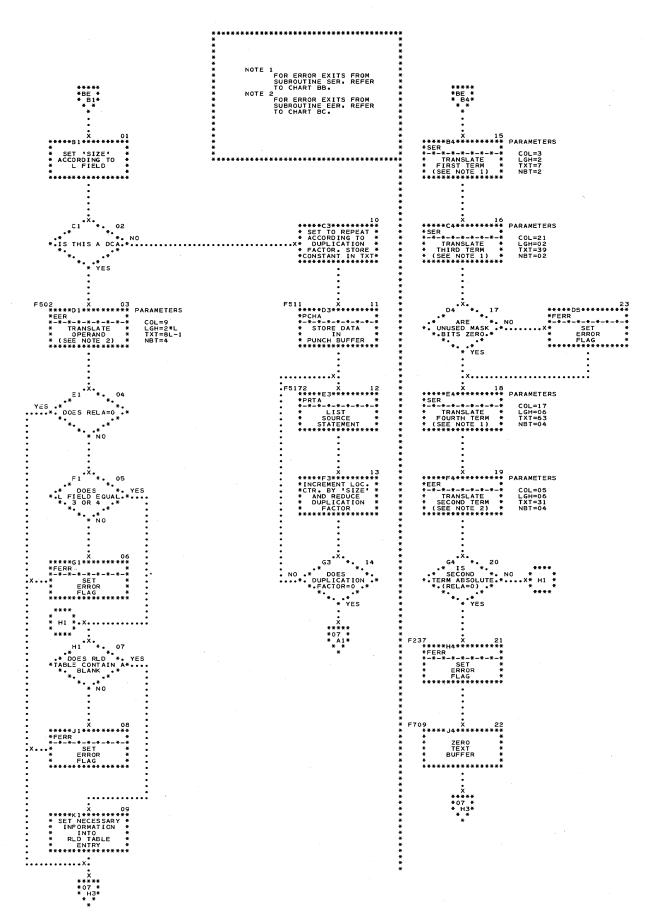

| CCW Translation - Chart AA 29           |                                        |

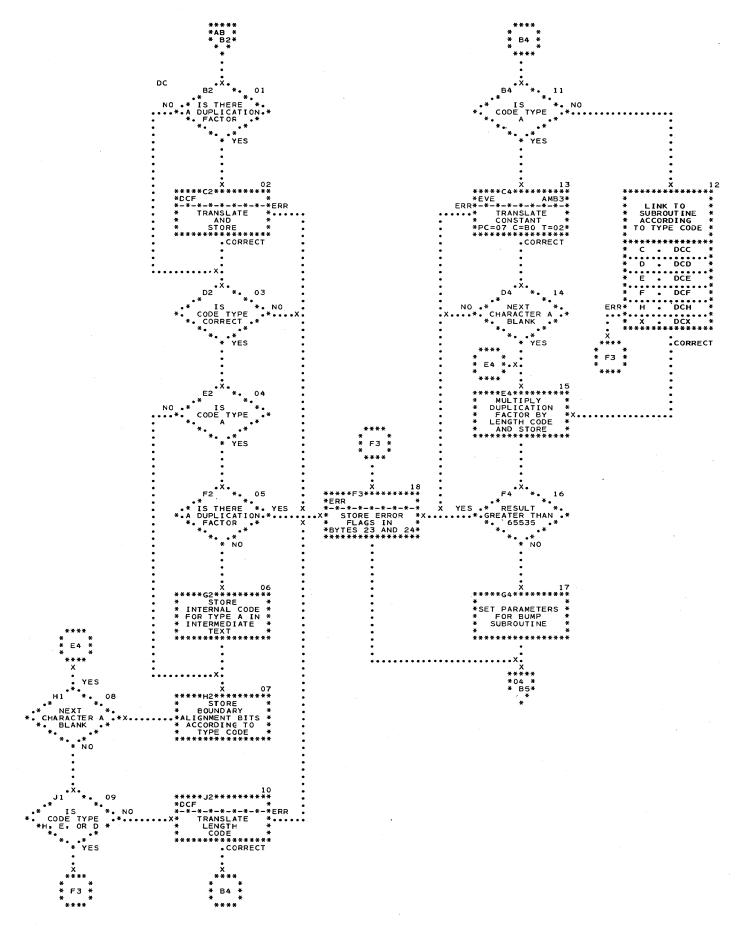

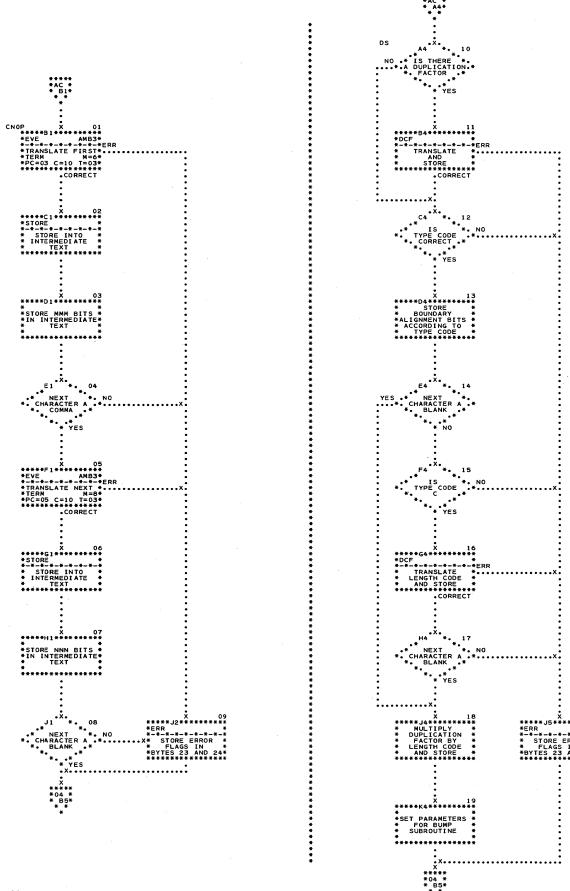

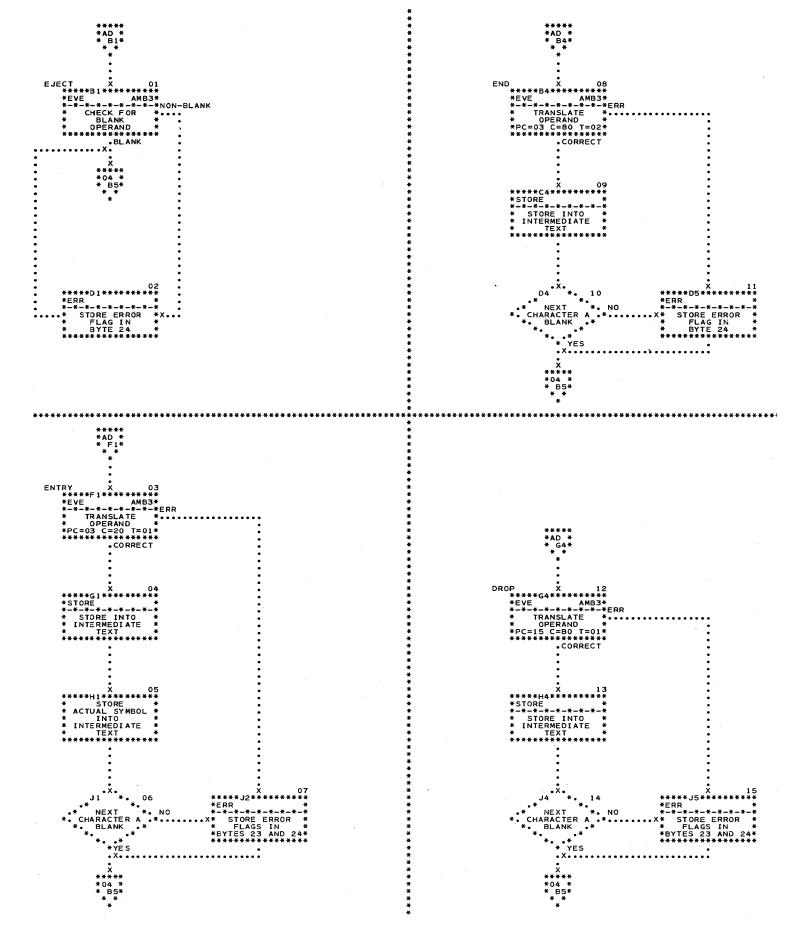

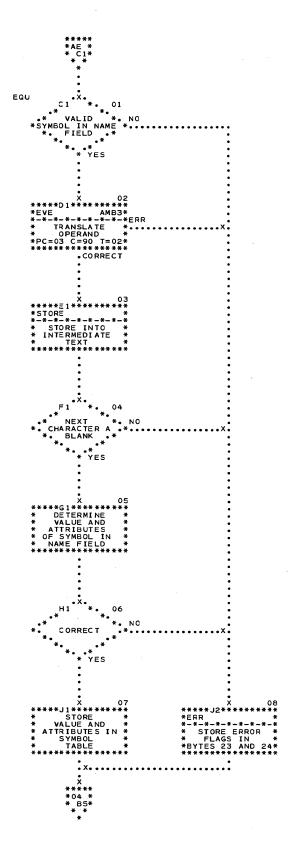

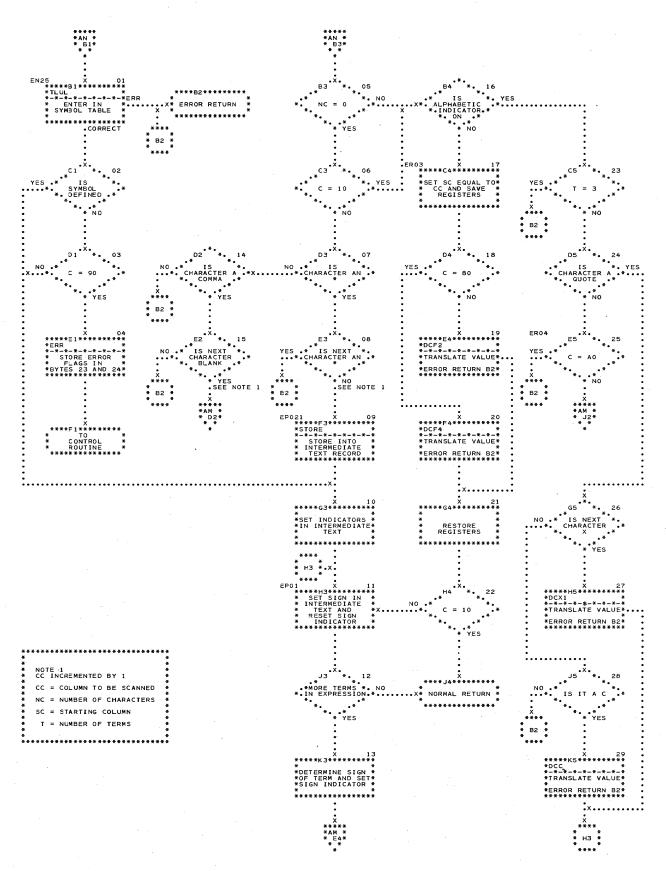

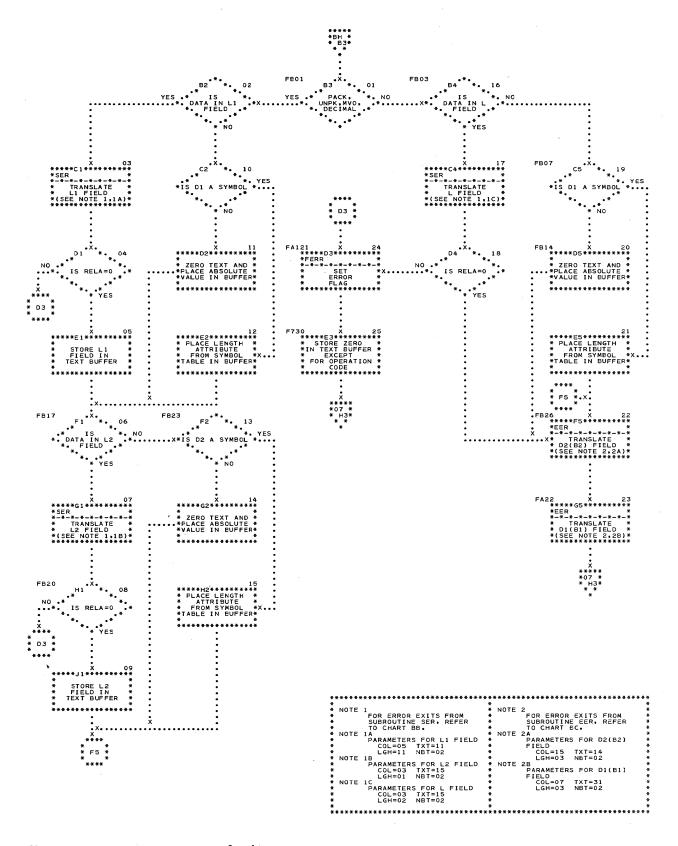

| DC Translation - Chart AB 30            | Section 4: Phase II Processing Flow 80 |

|                                         | Initialization - Chart 06              |

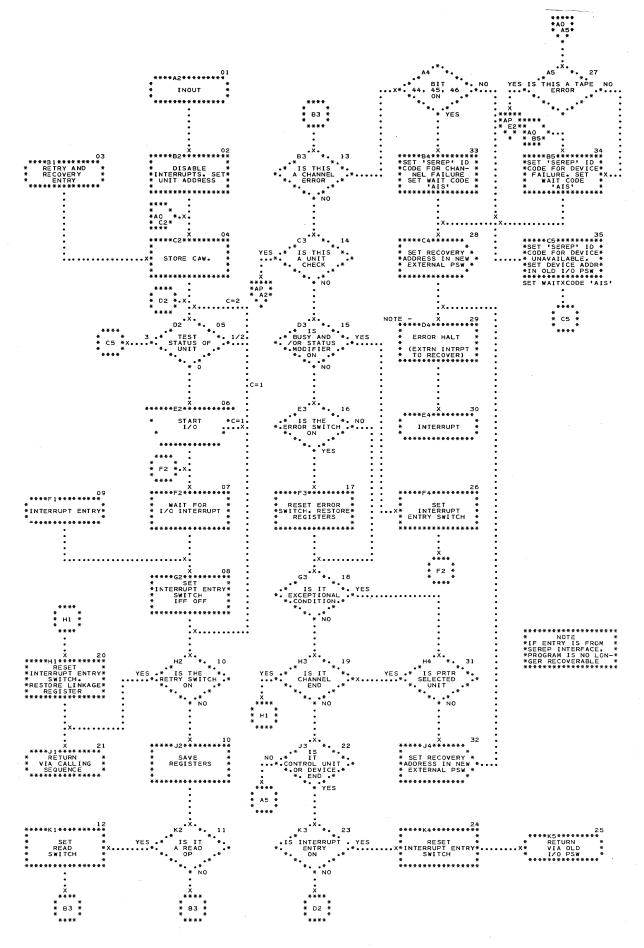

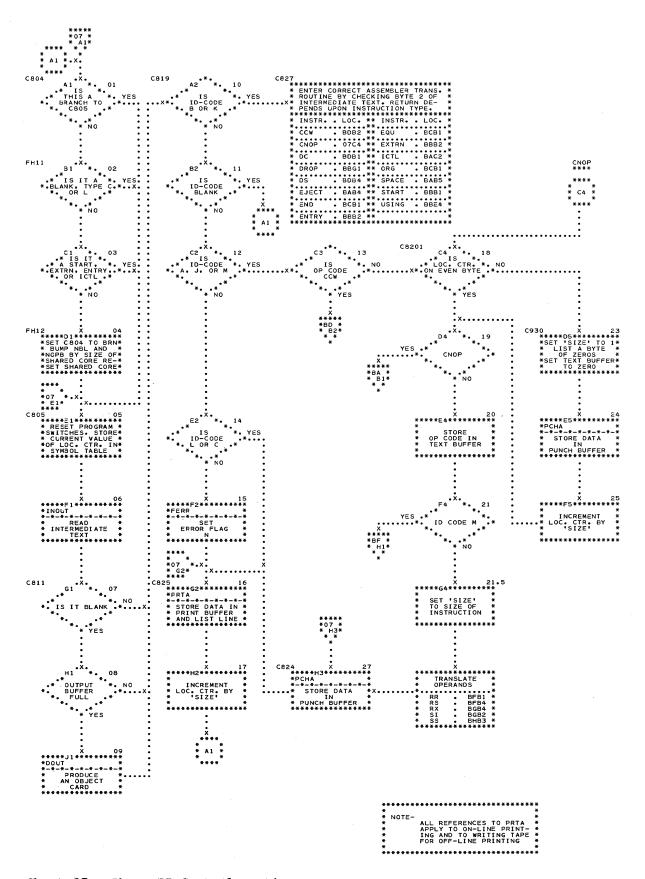

| Control Routine - Chart 07 80     | CCW Translation - Chart BD              |

|-----------------------------------|-----------------------------------------|

| General 80                        | (Blocks 02-08) and Chart BE             |

| Common 81                         | (Blocks 15-22) 85                       |

| Machine Instruction Processing 81 | DC Translation - Chart BD               |

|                                   | (Blocks 01, 03-06) and Chart BE         |

| SECTION 5: Intermediate Text      | (Blocks 01-14) 85                       |

| Translation 83                    | Machine Instructions                    |

| ASSEMBLER INSTRUCTIONS 83         | RR Format Translation - Chart           |

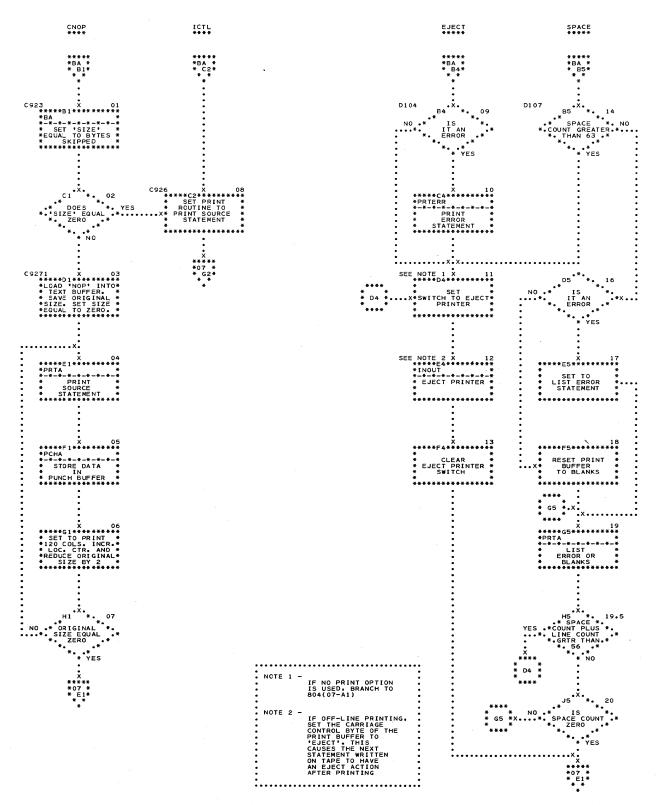

| CNOP Translation - Chart BA       | BF (Blocks 01-08) 85                    |

| (Blocks 01-07) 83                 |                                         |

| ICTL Translation - Chart BA       | BF (Blocks 09-15) 86                    |

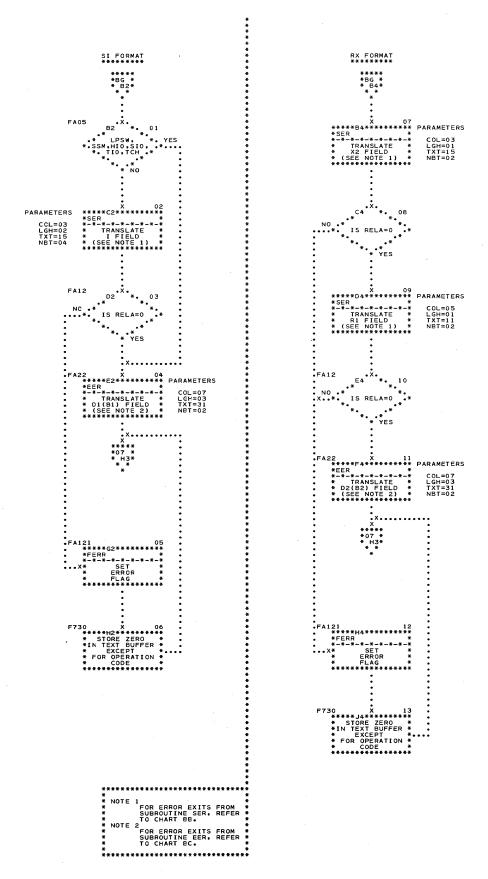

| (Block 08) 83                     | RX Format Translation - Chart           |

| EJECT Translation - Chart BA      | BG (Blocks 07-13) 86                    |

| (Blocks 09-13) 83                 | SI Format Translation - Chart           |

| SPACE Translation - Chart BA      | BG (Blocks 01-06) 86                    |

| (Blocks 14-20) 83                 | SS Format Translation - Chart BH . 86   |

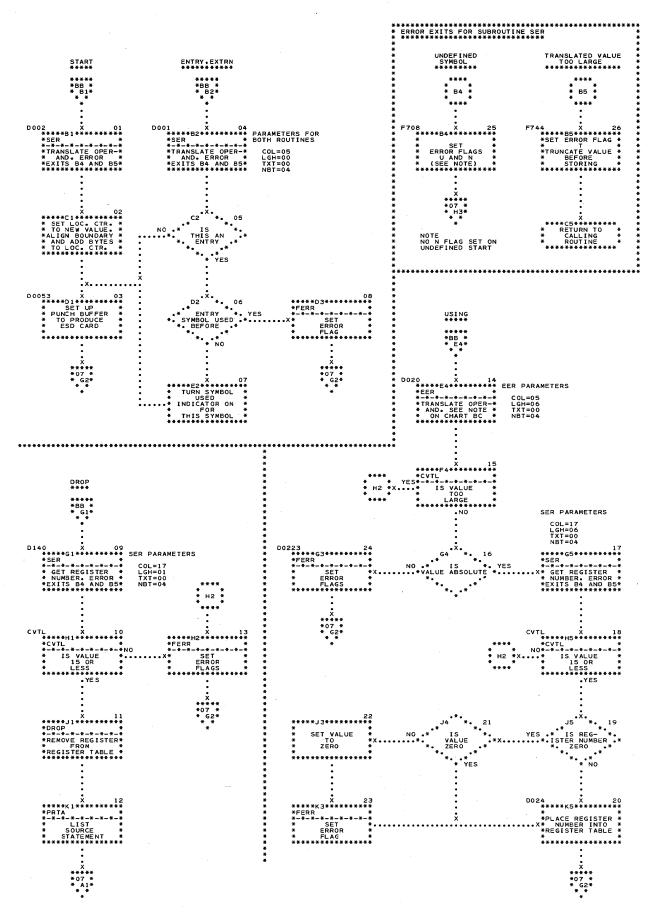

| START Translation - Chart BB      |                                         |

| (Blocks 01-03)83                  | APPENDIX A: AUTOCHART CROSS-REFERENCE   |

| ENTRY and EXTRN Translation -     | TABLES                                  |

| Chart BB (Blocks 04-08) 83        |                                         |

| DROP Translation - Chart BB       | Table I: Labels 97                      |

| (Blocks 09-13) 84                 |                                         |

| USING Translation - Chart BB      | Table II: Entry Connector References 99 |

| (Blocks 14-24) 84                 | •                                       |

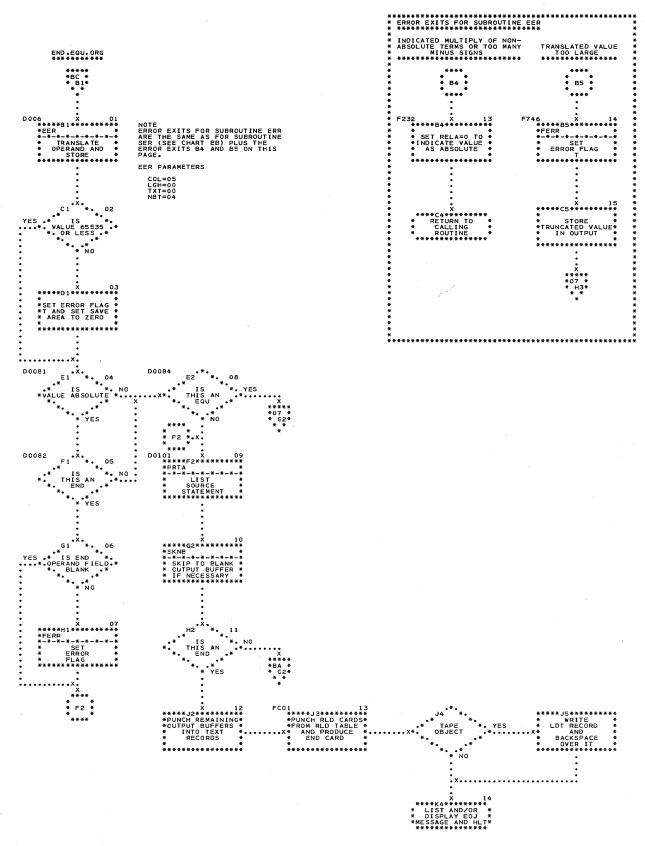

| END, EQU, and ORG Translation -   | Table III Subroutine Usage              |

| Chart BC 84                       | •                                       |

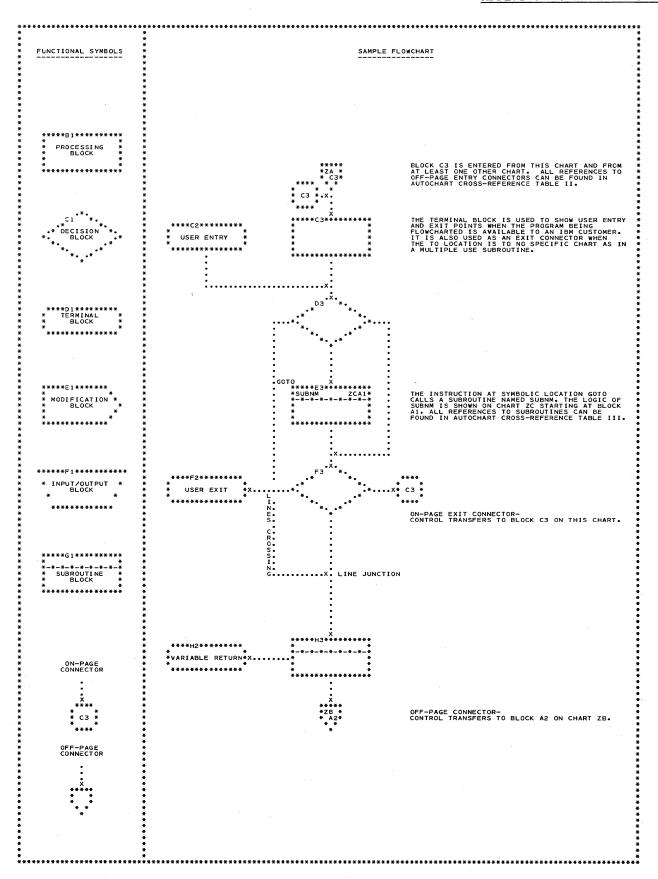

| DS Translation - Chart BD         | APPENDIX B: AUTOCHART SYMBOLS           |

| (Blocks 09-14)                    |                                         |

|                                   | GLOSSARY                                |

|                                   |                                         |

|                                   | INDEX                                   |

## ILLUSTRATIONS

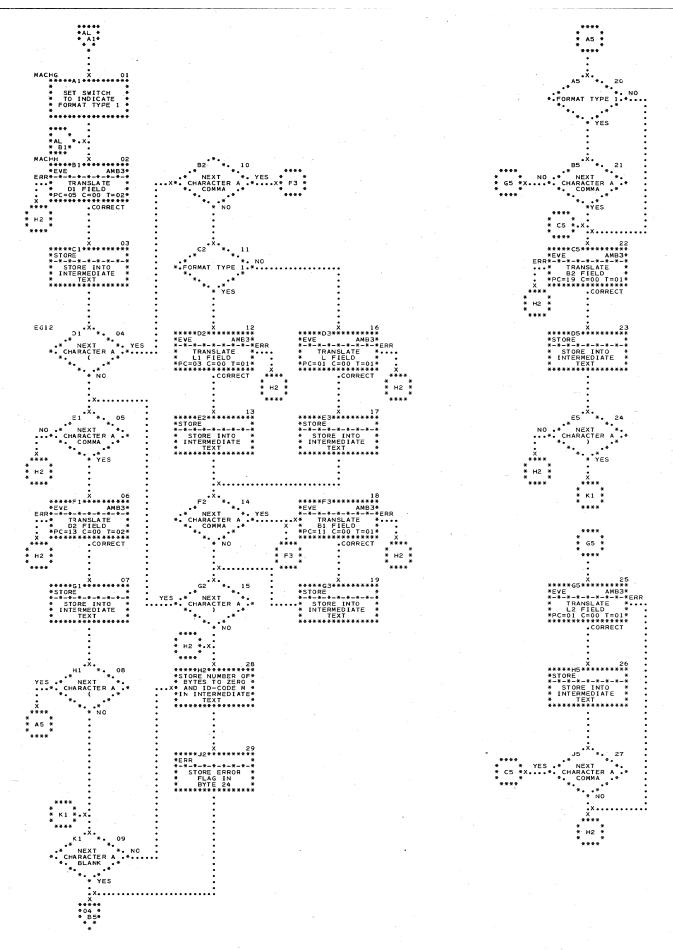

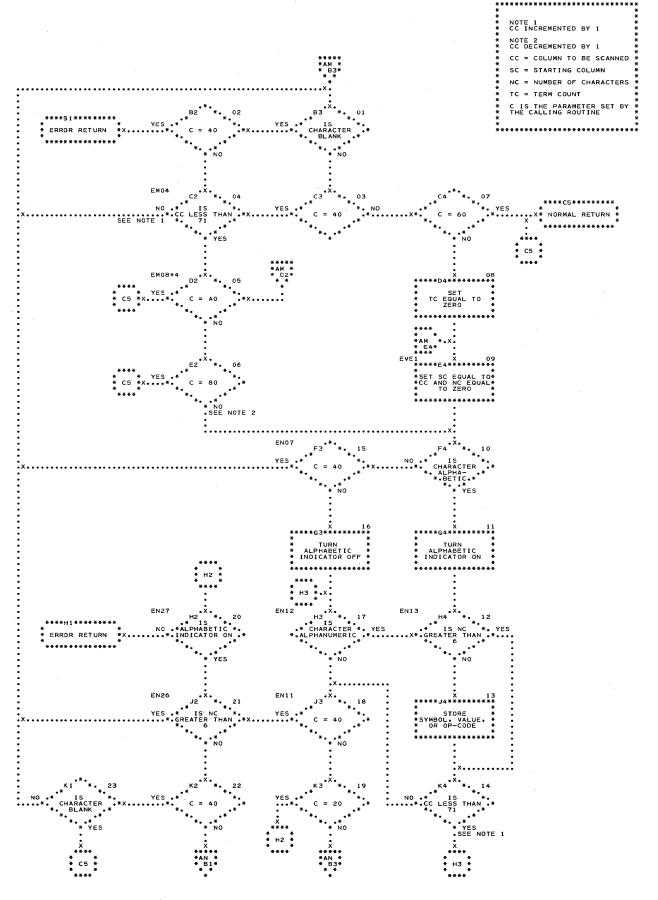

| Chart 01. Phase I                           | Chart AN. EVE Subroutine (continued) 67 |

|---------------------------------------------|-----------------------------------------|

| Chart 03. Phase I Initialization 51         | Chart AO. Input/Output Subroutine 68    |

| Chart 04. Phase I Control Routine 52        | Chart AP. Tape Read/Write Retry         |

| Chart 05. Phase I Control Routine           | Procedures 69                           |

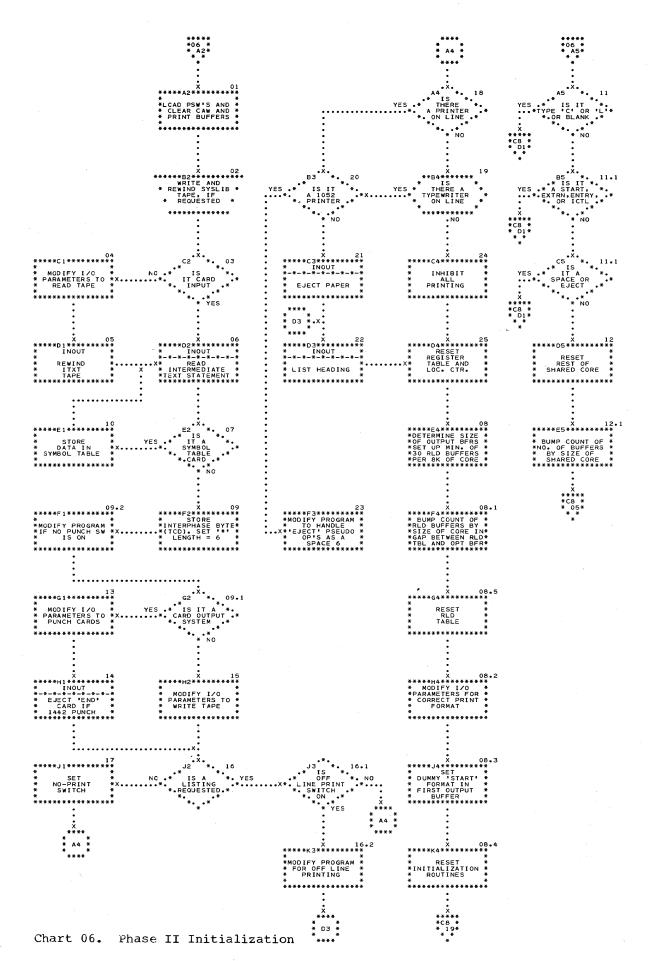

| (continued) 53                              | Chart 06. Phase II Initialization 87    |

| Chart AA. CCW Translation 54                | Chart 07. Phase II Control Routine 88   |

| Chart AB. DC Translation 55                 | Chart BA. SPACE, EJECT, CNOP, and ICTL  |

| Chart AC. CNOP and DS Translation 56        | Translation 89                          |

| Chart AD. DROP, EJECT, END, and             | Chart BB. DROP, ENTRY, EXTRN, START,    |

| ENTRY Translation 57                        | and USING Translation 90                |

| Chart AE. EQU and EXTRN                     | Chart BC. END, EQU, and ORG             |

| Translation 58                              | Translation 91                          |

| Chart AF. ICTL and START                    | Chart BD. CCW, DC, and DS               |

| Translation 59                              | Translation 92                          |

| Chart AG. ORG and SPACE                     | Chart BE. CCW and DC Translation        |

| Translation 60                              | (continued)                             |

| Chart AH. USING and RR Format               | Chart BF. RR and RS Format              |

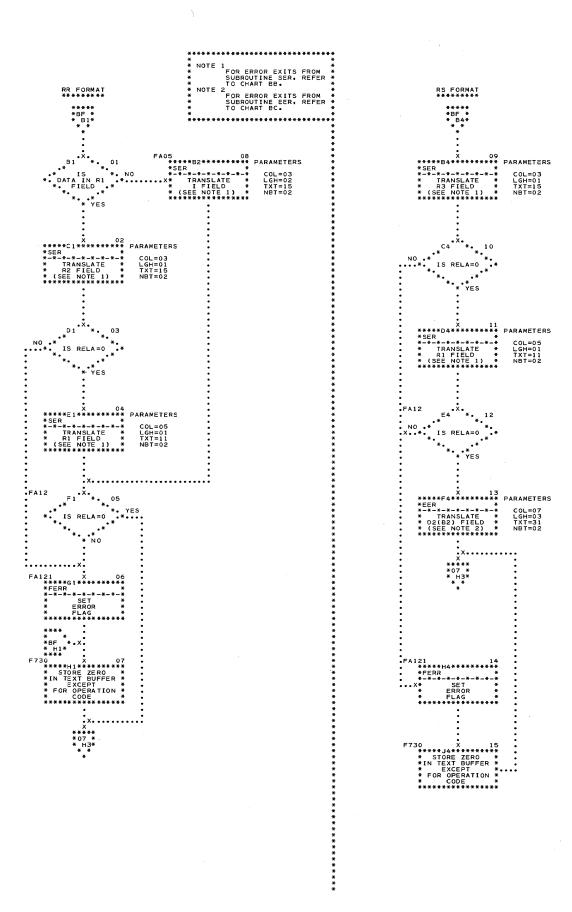

| Translation 61                              | Translation 94                          |

| Chart AI. RS Format Translation 62          | Chart BG. RX and SI Format              |

| Chart AJ. RX Format Translation 63          | Translation 95                          |

| Chart AK. SI Format Translation 64          | Chart BH. SS Format Translation 96      |

| Chart AL. SS Format Translation 65          |                                         |

| •                                           |                                         |

| •                                           |                                         |

|                                             |                                         |

|                                             |                                         |

|                                             |                                         |

|                                             | FIGURES                                 |

|                                             |                                         |

|                                             |                                         |

| Time 1 Characa 211 and in 0                 | Figure 7. Error Flags 21                |

| Figure 1. Storage Allocation 9              | Figure 8. Error Summary                 |

| Figure 2. I/O Flow 10                       | Figure 9. Increment Values              |

| Figure 3. Buffer Areas for Card Option      | Figure 10. Output Formats               |

| Figure 4. Buffer Areas for Tape Option . 11 | Figure 11. Object Program Listing       |

| Figure 5. Intermediate Text Summary 17      | Example                                 |

| Figure 6. Symbol Table Card Format 19       | Figure 12. Print Control Switch (SWPT)  |

| righte of plumor rapite card rormac 13      | rigure 12. Filite control switch (Swit) |

## PURPOSE OF PROGRAM

The Basic Programming Support Basic Assembler Program is designed to translate a source program written in symbolic language into an object program in machine language. Each phase of the program must be assembled on an IBM System/360 with main storage of greater than 8,192 bytes.

## PROGRAM ORGANIZATION

The assembler is a two-phase program, i.e., two-storage-load program. Phase I is the first storage load, and Phase II is the second storage load. Only the phase currently being executed occupies an area in main storage. The program is designed in this manner so that the maximum amount of main storage is available as working area for each phase (main storage not occupied by the assembler, tables, etc.).

The Basic Programming Support Basic Assembler Program has the same functions as any assembly program. It accomplishes the following:

- Replaces each symbolic operation code with its machine-language equivalent,

- Replaces each symbolic operand with an actual address,

- Reserves an area of main storage for each instruction and data area.

Phase I accomplishes the following major functions:

- 1. Replaces the symbolic operation code of each source statement with its machine language equivalent through the use of the Operation Code Table. (See "Phase I," Section 2, "Tables.") This information is placed in a buffer, the Intermediate Text Buffer, to be translated by Phase II. (See "Phase I," Section 2, "Tables.")

2. Builds a table of all symbolic oper-

- 2. Builds a table of all symbolic operands in the source statements. This table is called the Symbol Table. (See "Phase I," Section 2, "Tables.") The location of the symbolic operand within the Symbol Table, along with all self-defining operands, is also placed in the Intermediate Text.

- 3. Allocates storage to source statements and to data areas with an internal counter called the location counter.

Phase II of the Assembler Program accomplishes the following major functions:

- Translates the Intermediate Text into machine language. During this translation the symbolic operands are replaced with the actual addresses of symbols from the Symbol Table.

- 2. Produces the object program.

- 3. Produces a program listing.

The tables, cards, records, and the translation required to accomplish the functions listed above are described in detail in the discussion of each phase.

## OVERALL OPERATION OF PROGRAM

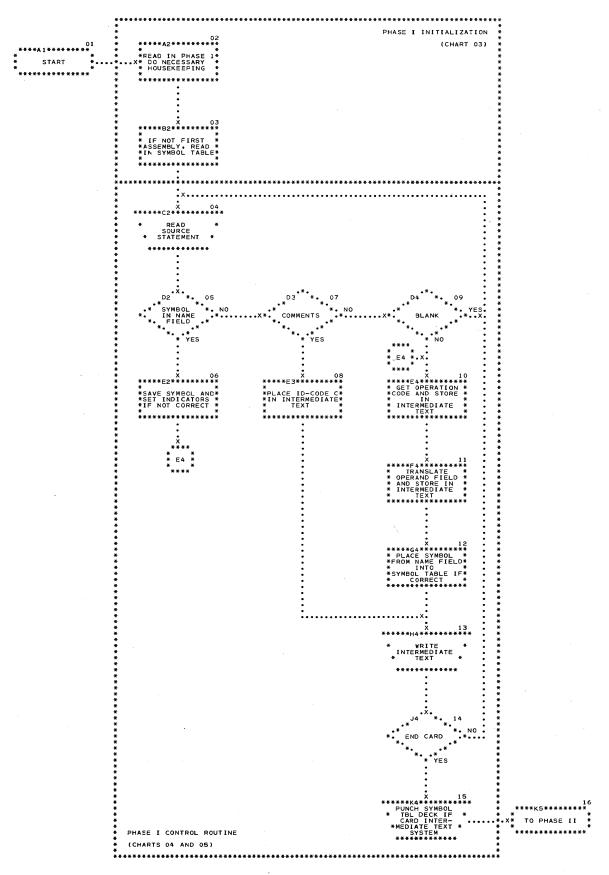

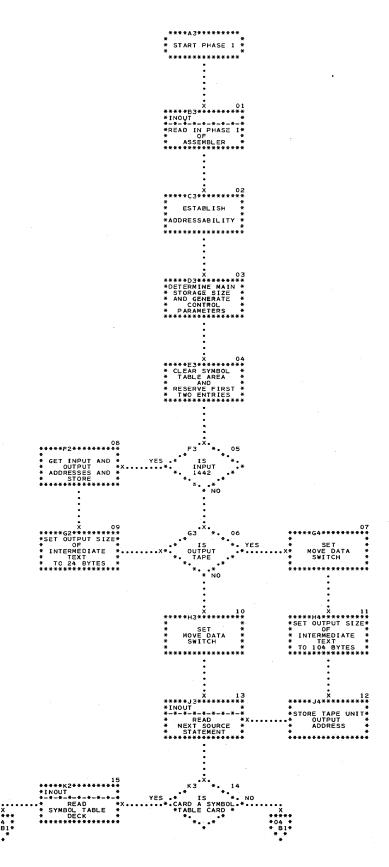

A generalized logic flow of the twophase assembly program is shown on Charts 01 and 02. A detailed description of each phase is given in the "Phase I" and "Phase II" sections of this publication. In the following text, the flowchart block numbers being described are indicated in parentheses.

## Phase I (Chart 01)

At the start of the assembly, the Phase I assembly deck or tape is loaded into lower main storage (02).

If the source program is on cards and is being reassembled, the symbol table that was constructed and punched into cards from a previous assembly is read into main storage (03).

The symbolic language source program, on cards or in the form of card images on tape, follows Phase I of the assembly program and the symbol table (if present). Each source statement from card or tape is read and processed, and the necessary information is punched into the same card, or written onto tape, or punched into a new card before the next source statement is read. If this is a reassembly, the new information is compared to the old information before any action occurs. The type of input depends upon the system configuration.

The first test performed on a source statement is to check for a symbol in the name field (05). If the statement has a symbol in the name field, it is noted (06). The symbol is not placed in the Symbol Table at this time because the correct processing of the symbol will be determined by the operation code of the statement. Symbols in the name field of some Assembler instructions will not be used by the assembler and, therefore, will not be placed in the Symbol Table.

If the name field does not contain a symbol, but the statement begins with an asterisk (07), indicating a comments statement, the only action taken is to indicate this in the Intermediate Text (08).

If the statement is blank (09), it is ignored, and the next source statement is read in (04). If it is not blank, the Operation Code Table that was loaded into main storage as part of the assembler deck is searched for the corresponding machine language operation code (10). The machine language operation code is then stored in the Intermediate Text. If the operation code is not found, or if other errors in any part of the source program statement are found by the assembler, the necessary error flag(s) is placed in the Intermediate

The operand field of the source statement is scanned next (11). Formats are checked, and the expressions in the operand field are translated according to format and placed in the Intermediate Text. (See "Phase I," Section 5, "Operand Field Translation.")

All the information concerning the source statement that can be determined by Phase I is stored in the Intermediate Text, and the Intermediate Text is then punched into a card or written on tape, depending upon the system configuration (13).

The next source statement is then read and processed. Source statements are read and processed until the END statement is encountered (14). When the END statement is encountered, the Symbol Table is punched into blank cards for a card system (15), the value (attribute) section of the Symbol Table is relocated to upper main storage, and the message 1EA is printed. The assembly program is then ready to read Phase II into main storage. However, if the assembler was loaded from tape, the message 1EA is not printed, and Phase II is loaded immediately.

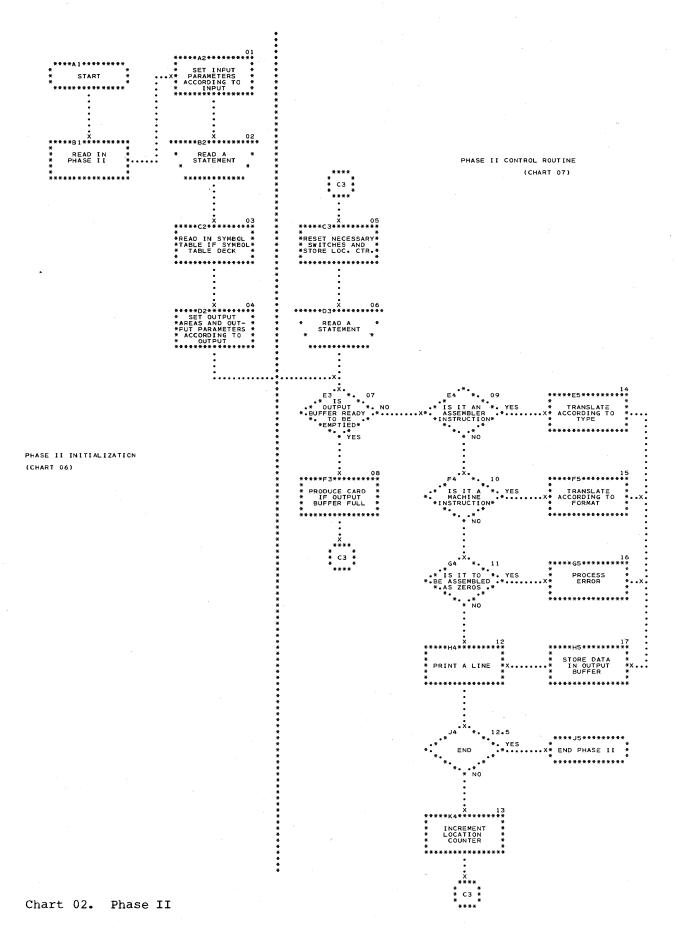

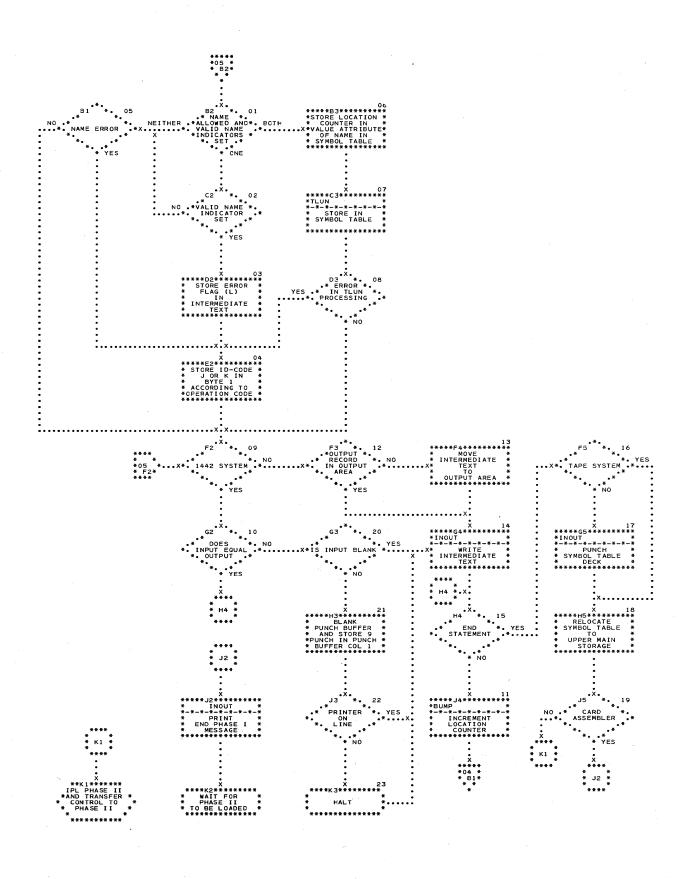

## Phase II (Chart 02)

Phase II of the Assembler Program is read into main storage. If the Symbol Table deck is in the card reader, it is read into the area of main storage reserved for the Symbol Table (03).

first statement containing the Intermediate Text is then read and checked. The output buffer area is checked to determine if enough information has been translated to produce an object program card (07). If enough information has been translated, an object program card is produced (08) before the next statement is read (05).

The Intermediate Text is translated according to the type and format of the input source statement.

An Assembler instruction (09) is transaccording to type (14). instruction has different requirements and requires a different routine to translate it. (See "Phase II," Section "Intermediate Text Translation.")

A machine instruction (10) must translated according to format (15) since there are five different formats (RR, RX, RS, SI, SS) for machine instructions. (See "Phase II," Section 5, "Intermediate Text Translation.")

If an error was encountered during Phase I requiring that the instruction be assembled as zeros (11), zeros are stored in the output buffer (16).

A statement that contains comments, or an error that will not allow the instruction to be translated, will cause only the source statement to be printed in the object program listing (12).

The Intermediate Text is read and translated until the END statement is encountered (12.5). When the END statement is encountered, the following conditions occur:

- The remaining information in the output area is produced in object program form.

- 2.

- RLD cards, if any, are produced.

If object code is being written on tape, a LDT record is written immediately after the END record and the tape is backspaced. If it is stacked output, only the final LDT record remains, the others being overlaid by the first record of each succeeding job.

- The message 2EA is printed and the program stops.

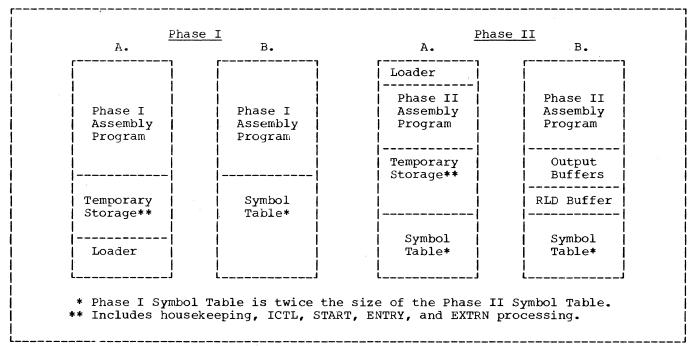

Figure 1. Storage Allocation

#### STORAGE ALLOCATION

Figure 1 illustrates the relative locations in main storage of Phase I and Phase II of the Assembler Program. Figure 1, part A, shows the allocation at load time, and Figure 1, part B, shows the allocation after the housekeeping and the ICTL, START, ENTRY, and EXTRN processing are completed.

## I/O FLOW

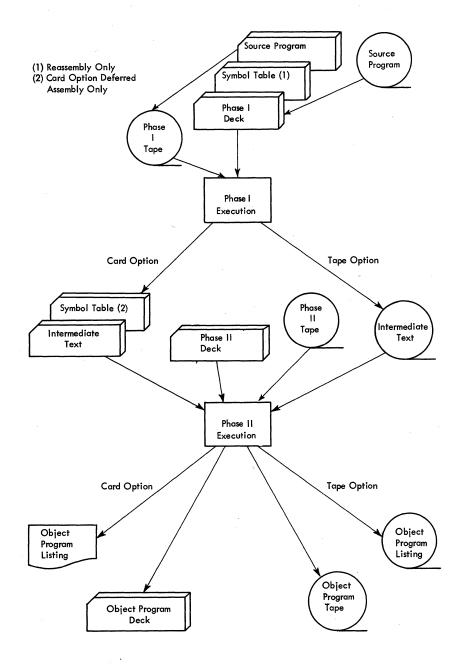

Figure 2 illustrates the I/O flow of the Assembler Program.

The Phase I deck is read from the card reader or input tape unit. The Symbol Table deck will then precede the source deck if this is a reassembly procedure as described in the publication, IBM System/360 Basic Programming Support Basic Assembler Language, Form C28-6503.

After the Phase I Assembler deck is read into main storage, and the Symbol Table deck if present, each Statement of the source program is read and partially translated. The partially translated source statement (Intermediate Text) is punched into the source statement card (1442), punched into a new card along with the source statement (2540), or placed on tape (1442 or 2540 with tape).

The Phase II deck is then read from the card reader or tape unit. The Symbol Table deck will then be read into main storage if this is a deferred assembly, as described in the publication, <a href="IBM System/360">IBM System/360</a> Basic Programming Support Basic Assembler Language, Form C28-6503.

The Intermediate Text developed by Phase I is then read one card or record at a time and translated, the object program is punched into cards or placed on tape, and the object program listing is produced.

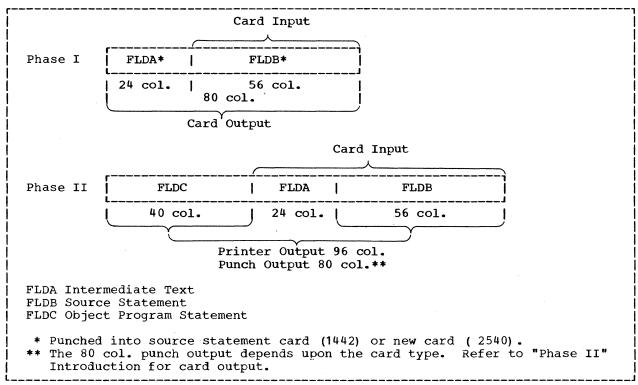

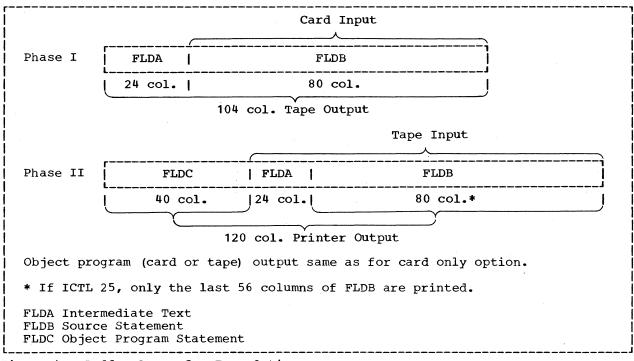

Figure 3 shows the buffer areas for the card-only option and Figure 4 shows the buffer areas for the tape option.

Figure 2. I/O Flow

Figure 3. Buffer Areas for Card Option

Figure 4. Buffer Areas for Tape Option

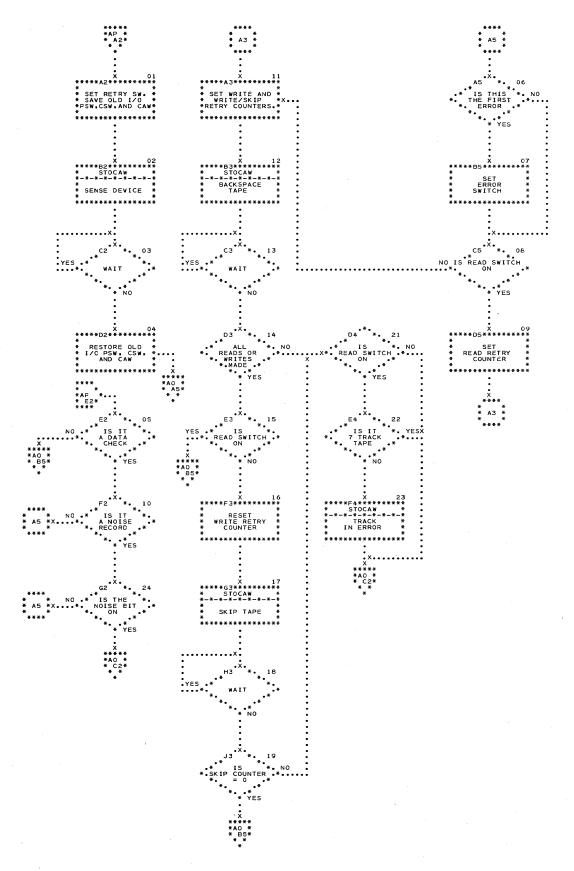

Chart 01. Phase I

#### SECTION 1: INTRODUCTION

The major functions of Phase I of the Assembler Program are as follows:

# Replace the Symbolic Operation Code with Its Machine Language Equivalent

The symbolic operation code of each assembler language source statement is replaced with its machine language equivalent through the use of a table called the Operation Code Table. This table contains each assembler language symbolic operation code and its equivalent machine language operation code. The Operation Code Table is discussed in detail in Section 2, "Tables."

The Assembler Program reads the symbolic operation code in each source program statement, looks it up in this table, and picks up the corresponding machine operation code. The machine operation code and other pertinent information concerning the source statement are stored in a buffer called an Intermediate Text buffer. The Intermediate Text is discussed in detail in Section 2, "Tables."

# <u>Translate Symbolic Operands into Intermediate Text</u>

The symbolic operands of each assembler language source statement are partially translated by Phase I and placed into the Intermediate Text. The symbolic operands of statements refer to the symbolic names of data fields, or symbolic names of other source statements. In order to determine the actual address for a symbolic operand, the actual address of all symbols must first be determined. This is why the final translation of the source statement is accomplished by Phase II.

The actual address of all symbols is determined by building a table during the

execution of Phase I. This table, called the Symbol Table, consists of each symbolic name and its associated actual address, and other pertinent data. The Symbol Table is discussed in detail in Section 2, "Tables." The Symbol Table is punched into cards at the completion of Phase I when the card intermediate text system is being used. The Symbol Table remains in main storage when intermediate text is on tape.

If Phase II of the Assembler Program is not executed immediately following Phase I, the Symbol Table cards must be placed in front of the source deck when Phase II is to be executed. When a tape system is being used, Phase II must immediately follow Phase I. If Phase II is executed immediately following Phase I, the Symbol Table remains in main storage, and the Symbol Table cards do not have to be loaded.

During the execution of Phase II, the Symbol Table entry corresponding to the symbolic operand is found, and the value of that symbol is used to generate the object program statement.

## Allocate Storage for Intermediate Text

A counter internal to the program is used to allocate storage for the intermediate text compiled from the source statements. This counter, called the location counter, is initialized with the machine address at which the program is to begin by using the START Assembler instruction.

When the length of a translated source statement has been determined, the counter is incremented by this length (after boundary alignment, if necessary), and the next instruction or data area will begin at the new location specified by the location counter.

When a statement is encountered that specifies that an area of storage must be reserved for data, the location counter is incremented by the number of storage bytes specified for that area.

#### SECTION 2: TABLES

#### INTERMEDIATE TEXT

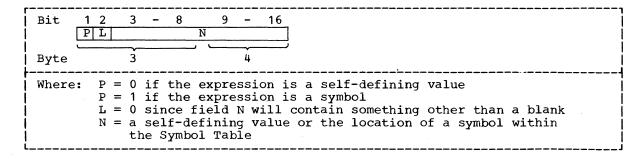

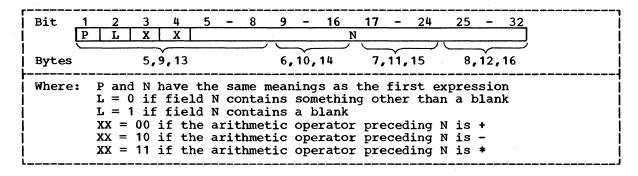

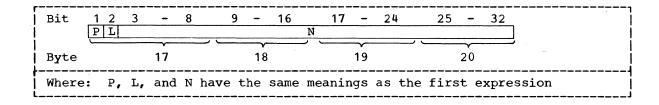

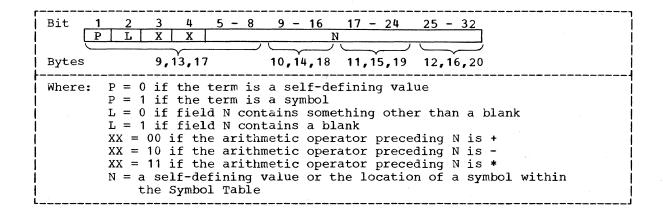

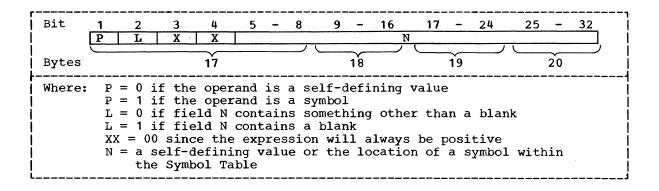

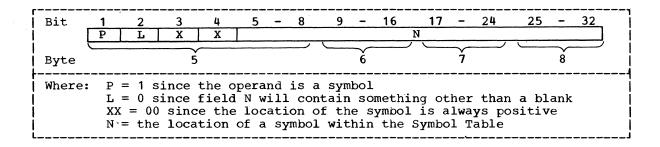

The Intermediate Text associated with each statement contains a total of 24 bytes of information. The specific meaning of the 24 bytes of information and the bit patterns associated with the bytes are shown in a figure accompanying the description of each instruction type in Section 5, "Operand Field Translation." A general discussion of the bytes in the Intermediate Text is given in this section.

Figure 5 is a summary of the Intermediate Text associated with each instruction type.

The breakdown of the Intermediate Text is as follows:

#### Byte 1 - ID-Code

This field is one byte in length and contains an ID-Code which indicates whether the source statement is a machine instruction or an Assembler instruction, whether the instruction contains an error, and whether or not the statement requires further processing by Phase II. The possible ID-Codes and their meanings are as follows:

| Code | Meaning                                                      |  |  |  |

|------|--------------------------------------------------------------|--|--|--|

| Α    | Machine instruction, no errors                               |  |  |  |

| В    | Assembler instruction, no errors                             |  |  |  |

| C-   | Comments*                                                    |  |  |  |

| J    | Error in a machine instruction statement                     |  |  |  |

| K    | Error in an Assembler instruction statement                  |  |  |  |

| L    | Error, statement not assembled*                              |  |  |  |

| М    | Error, operand field assembled as zeros                      |  |  |  |

| •    | * Error flags printed but no further translation by Phase II |  |  |  |

After it is determined whether the operation code is a machine instruction, an

Assembler instruction, or a comments statement, an ID-Code of A, B, or C, respectively, is placed into byte 1 of the Intermediate Text. If an error is encountered later during the translation of the source statement, these ID-Codes will be replaced with the appropriate error ID-Code (i.e., J,K,L, or M).

### Byte 2 - Operation Code

The machine-language operation code is placed in this field after the search of the Operation Code Table. This field will be blank if the source statement contains an illegal operation code.

## Bytes 3-22 - Operand Field

These bytes contain the text compiled from the operand field of the instruction. Since these bytes will contain different information for each instruction type, they are explained in detail in the discussion of each instruction in Section 5, "Operand Field Translation." Bytes 21 and 22 may contain error flags if the error ID-Code is L or M.

## Bytes 21-24 - Error Flags

These bytes will contain error flags to indicate the type of error encountered during the translation of the instruction. If no error is encountered, the bytes will be blank. The error flags and their meanings are shown in Phase I, Section 3, "Subroutine Description," under the discussion of subroutine ERR.

## OPERATION CODE TABLE

The Operation Code Table is divided into five sections, each section containing all the symbolic codes of the same length (e.g., all one-character symbolic codes in one section, all two-character symbolic codes in another section, etc.) plus the equivalent machine-language code. All symbolic codes within each section are also grouped according to the operand field format (e.g., all machine instructions in the SI Format, SS Format, etc.)

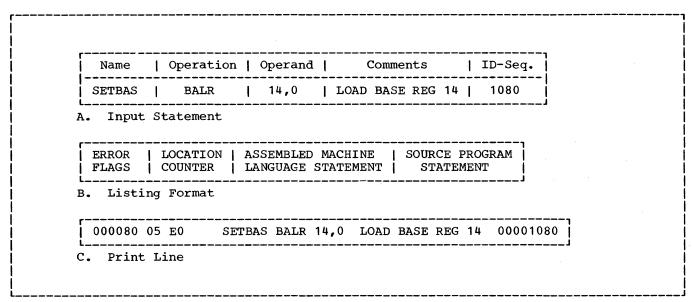

| Byte                                                               | 1 2                  | 3 4      | 5               | 6              | 7  8                                 | 9 10                       | 11 12           | <br> -1    | 3   14                       | 15              | 16     | <br>                 | 18   19       | 9 20      |                   | 1 22              | 23 24 |

|--------------------------------------------------------------------|----------------------|----------|-----------------|----------------|--------------------------------------|----------------------------|-----------------|------------|------------------------------|-----------------|--------|----------------------|---------------|-----------|-------------------|-------------------|-------|

| RR                                                                 | A OP                 | <br>     | <br>R1          |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| RX                                                                 | A OP <br> <br>  A OP |          | R 1             |                |                                      | D2                         |                 |            | <br>В2                       |                 |        |                      |               |           |                   |                   |       |

| RS                                                                 | A OP                 |          | R1              |                |                                      | D2<br>D2                   |                 |            | B2<br>B2                     | . <u>-</u>      |        |                      |               |           |                   |                   |       |

|                                                                    | A OP                 | I        |                 |                |                                      | D2<br><br>D1               |                 |            | в <b>2</b><br><br>В <b>1</b> | . <u>-</u>      |        |                      |               |           |                   |                   |       |

| S1<br>                                                             | <del> </del>         | L2/L     | <br>т.1         |                |                                      | D1                         |                 |            | Б1<br>В1                     | · <del></del> - |        |                      |               |           | E                 |                   |       |

| CNOP                                                               | B E3                 | ba       |                 | - <u>-</u> '-  | d2                                   |                            |                 | <u>-</u> - |                              |                 |        |                      |               |           |                   |                   |       |

| <br> ICTL                                                          | B E5 <br> <br>  B ED | d        | - <del></del> - |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| <br>                                                               | <del> </del>         |          |                 |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| ·                                                                  | B EB <br>            |          | ·<br>           |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| SPACE<br>                                                          | B E7 <br>            | - a      |                 |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| ORG                                                                | B E8 <br>            |          |                 |                |                                      | ry                         |                 |            |                              |                 |        | <del> </del>         |               |           |                   |                   |       |

| END<br>                                                            | B EF                 | <u>-</u> |                 |                |                                      |                            | blank<br>       |            |                              |                 |        | !<br>                |               |           |                   |                   |       |

| EQU<br>                                                            | B E5 <br>            | <u> </u> |                 |                |                                      | ax or<br>                  |                 |            |                              |                 |        | !<br>                |               |           |                   |                   |       |

| USING<br>                                                          | B E6 <br>            | !        |                 |                |                                      | rx<br>                     | ·               |            |                              |                 |        | <u></u>              | sx<br>        |           |                   |                   |       |

| DROP<br>                                                           | B EC <br>            |          |                 |                |                                      |                            | ·               |            | <del></del> -                |                 |        | <u> </u>             | sx<br>        |           |                   |                   |       |

| EXTRN<br>                                                          | B E9 <br>            | 1        |                 | rs<br>         |                                      |                            | as<br>          |            |                              | <u> </u>        |        |                      |               |           |                   |                   |       |

| ENTRY<br>                                                          | B EA <br>            |          |                 | rs             | 1                                    |                            | as<br>          |            |                              | <u> </u>        |        |                      |               |           |                   |                   |       |

| START                                                              | B EE                 | ba       |                 | aa<br>         |                                      |                            | as              |            |                              | 1               |        |                      |               |           |                   |                   |       |

| CCW                                                                | B E4                 | sx       |                 |                |                                      | rx                         |                 |            |                              |                 |        | <u> </u>             | sx            |           | s                 | х                 | l<br> |

| DS                                                                 | B E0                 | 1 ba     | đ               | 1.             |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| DC (C,D,E,F,H,X)                                                   | B E1                 | 1 ba     | m               | ĺ              |                                      |                            |                 |            | d<br>                        | lc              |        |                      |               |           |                   |                   |       |

| DC (A)                                                             | B E2                 | 1 ba     | m               | 1              | 1                                    |                            |                 |            | ax c                         | r r             | ٤,     |                      |               |           | 1                 |                   |       |

| COMMENTS                                                           | Cl                   |          |                 |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   |       |

| Err.Mach.Instr.                                                    | J OP                 |          | ,               |                |                                      | sa                         | me as           |            | ype                          | A               | ٠,     |                      |               |           |                   | ,                 | e.f.  |

| Err.Assem.Inst.                                                    | •                    |          |                 |                |                                      | sa                         | me as           |            |                              | В               |        |                      |               |           |                   |                   | le.f. |

| ERR (1)                                                            | L                    |          |                 |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   | flags |

| ERR (2)                                                            | MOP                  | n        |                 |                |                                      |                            |                 |            |                              |                 |        |                      |               |           |                   |                   | flags |

| aa = assembled<br>as = actual sy<br>ax = absolute<br>ba = boundary | ymbol<br>express     | sion     | ts              | dc<br>e.f<br>l | = dec:<br>= def:<br>• = e:<br>= leng | ined o<br>rror f<br>gth of | ntege<br>consta | nt<br>ta   | nt                           | rs<br>rx        | =<br>= | zero<br>relo<br>relo | s to<br>catal | be<br>ble | ass<br>sym<br>exp | emb<br>bol<br>res | led   |

| (1) sta                                                            | atement              | not as   | ssem            | ble            | d<br>                                |                            | (2) 0           | pe         | rand                         | l ass           | sem    | bled                 | as 2          | zero      | s                 |                   |       |

Figure 5. Intermediate Text Summary

The organization of this table allows a faster assembly because it is not necessary to search the entire table to find the equivalent machine-language code. Only the section of the table containing the same number of characters as the symbolic code is searched. In addition, the table provides the Assembler Program with the operand field format and the address of the subroutine necessary to translate that format.

The machine-language operation code obtained from the table is placed into the Intermediate Text.

The Operation Code Table is loaded into main storage as part of Phase I.

#### SYMBOL TABLE

The Symbol Table is divided into two sections. The first section contains the compressed symbols from the source statements; the second section contains the attributes (values) associated with each symbol. Only the attributes are passed on to Phase II because there is no further need of the symbol itself once it has been replaced with the address of the location within the Symbol Table that contains the symbol attributes.

The first two entries in the Symbol Table refer to the location counter. The first entry contains the current setting of the location counter. This entry is necessary because the current setting of the location counter can be referred to within the symbolic program with an asterisk. For example, the expression (\*+12) in the operand field of a symbolic statement refers to the current location plus 12 bytes. Therefore, when an asterisk is encountered as a symbol, the Assembler Program replaces the asterisk with the address contained in the first entry of the Symbol Table.

The second entry contains the highest value the location counter reached during Phase I. This location is needed for the producing of an External Symbol Dictionary (ESD) START card, which is used by the relocatable loader. This is a function of Phase II and is discussed in detail in the introduction to Phase II.

The format of the Symbol Table Cards produced by Phase I is shown in Figure 6.

The attributes assigned to a symbol when the symbol is defined in the Symbol Table are as follows:

#### Location

This is a two-byte field containing the machine address of the symbol.

#### Length

This is a one-byte field containing the number of storage bytes associated with the symbol. This number will always be one less than the actual number due to programming considerations. For example, if the symbol DATA is the name of the DS instruction that defines a data area of 16 bytes, DATA would have a length of 15 assigned to it in the Symbol Table. When a length is not indicated, the Assembler Program assumes a length of one byte.

If the symbol is defined by a compound expression, the length is the same as the implied length of the leftmost simple expression in the compound expression. If the leftmost expression is a self-defining value, the length attribute is one.

### Relocatability

This four-bit (1/2 byte) field contains a 1 - 15 if the symbol is relocatable and a zero if the symbol is not relocatable (i.e., is assigned an absolute address).

If the symbol is a linkage symbol that has been defined in the operand field of an EXTRN instruction, the relocatability field will contain a value from 2 to 15, depending upon which EXTRN instruction in the source program defines the symbol. For example, if the symbol was defined by the first EXTRN instruction, the relocatability value would be 2. If it was defined by the second EXTRN instruction, the relocatability value would be 3, etc. If the symbol is defined in the same program and not in the operand field of an EXTRN instruction, the relocatability attribute will be one.

## Defined Bit

Each Symbol Table entry also contains one bit to indicate whether or not the symbol was ever defined.

| 1 2 3 4 1                        | 5-16 | 17-28 | 1 29 | -40 | 41-52 | 53-64 | 65-76 | 77 - 80     |

|----------------------------------|------|-------|------|-----|-------|-------|-------|-------------|

| 12 Address of  <br>9 first loc.  | *    | *     |      | *   | *     | *     | *     | <br>  Blank |

| 4 of Phase II  <br> Symbol Table |      | İ     | Ì    |     |       |       | İ     | İ           |

\* Each of these 12 bytes contains the symbol name, value, and attributes as follows:

| <u>Byte</u> | Contents                                          |

|-------------|---------------------------------------------------|

| 1-2         | Pointer to symbol position in table               |

| 3-4         | Not used                                          |

| 5-8         | Symbol in compressed form                         |

| 9-10        | Symbol value                                      |

| 11          | Symbol length                                     |

| 12          | Symbol attributes                                 |

|             | bits 0-3 relocatability                           |

|             | bit 4 defined bit                                 |

|             | 1 = defined                                       |

|             | 0 = undefined                                     |

|             | bit 5 1 = entry used                              |

|             | <pre>0 = not an entry or entry not defined.</pre> |

|             |                                                   |

Figure 6. Symbol Table Card Format

#### SECTION 3: SUBROUTINE DESCRIPTION

This section describes the subroutines of the Assembler Program that are used during Phase I processing.

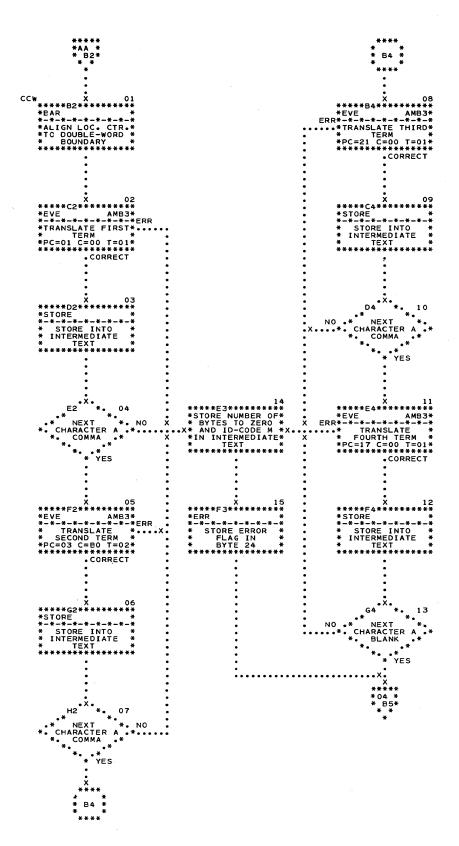

#### EVE - Evaluation Routine (Charts AM and AN)

This subroutine is used during Phase I of the Assembler Program to accomplish the following:

- 1. Scan the Name Field

- 2. Scan for non-blank character

- 3. Scan the Operation Code Field

- 4. Translate the Operand Field

The first three items mentioned above are discussed in detail in Section 4, "Phase I Processing Flow," under "Control Routine." Only the translation of the operand field will be discussed here. However, the parameters necessary for each of the above procedures are shown at the end of this discussion.

This subroutine is shown in detail in Charts AM and AN.

Subroutine EVE will scan the operand field until the first character of the operand field expression is located. Subroutine EVE then translates the first term of the operand field expression and compares the translation to the parameters described below. The translated results, if correct, are placed into the relevant bytes of the Intermediate Text bý subroutine STORE.

If the translation is not correct, control exits from this subroutine via the error exit set up by the calling routine.

After the translated term is placed into the Intermediate Text, control exits to the calling routine. The calling routine then determines if the character following the term is correct. If it is correct, and more terms of the operand field need translation, new parameters are set up and subroutine EVE is entered again.

The parameters used by subroutine EVE, which describe the next term of the expression in the operand field to be translated, are as follows:

T is set according to the type of term to be translated as follows:

- 0 = operand should be blank

- 1 = a simple term

- 2 = a compound term

- 3 = an integer (decimal value)

- L indicates the number of bytes of intermediate text the term being translated will occupy.

- M indicates the maximum value allowed for any self-defining value within the expression being translated.

- PC indicates the starting column minus 2 (due to programming considerations) of the Intermediate Text into which the translated term of the expression will be placed.

- C indicates the operation code of the statement being translated or the operation to be performed by subroutine EVE, as follows:

- 10 = CNOP

- 20 = EXTRN

- 20 = ENTRY

- 40 = Name Field or Operation Code scan

- 60 = DS or DC (type C,D,E,F,H,X), EJECT, SPACE, or scan until nonblank character

- 80 = END

- 90 = ORG or EQU

- A0 = START

- B0 = DC (type A), USING, DROP, or CCW (2nd term)

- 00 = all other operation codes

The other subroutines used by subroutine  ${\tt EVE}$  are:

DCC - Define Character Constant:

routine is used when a character constant

appears in the operand field of a source

statement. It translates the character

constant and checks its validity.

DCF - Define Full-Word Constant: This subroutine is used when a full-word constant appears in the operand field of a source statement. It converts a decimal integer to its binary representation and checks its validity.

<u>DCX - Define Hexadecimal Constant:</u> This subroutine is used when a hexadecimal constant appears in the operand field of a source statement. It translates the hexadecimal constant and checks its validity.

TLUS - Symbol Table Look-up: This subroutine is used when a symbol appears in the operand field of a source statement. It looks up the symbol in the Symbol Table and indicates its value (if known), its location in the Symbol Table, its length and relocatability attributes, and the bit

indicating whether or not the symbol is defined.

STORE - Store into Intermediate Text: This subroutine stores the translated terms of the expression in the operand field into the Intermediate Text.

#### ERR - Store Error Flags

The ERR subroutine places the necessary error flags into the Intermediate Text. If the error is such that the statement can not be assembled by Phase II, ID-Code L is also placed into the Intermediate Text. This subroutine is entered from the calling routine at location ERR if it is necessary to place the ID-Code into the Intermediate Text along with the error flags. If only the error flags are to be placed into the Intermediate Text, this subroutine is entered at location ERR1. The error flags are dependent upon the error conditions and are set by the calling routine.

The error flags that may be placed into the Intermediate Text by Phase I are shown in Figure 7.

Figure 8 shows what action is taken in Phase I of the Assembler Program when errors are encountered in the source statement.

## BAR - Boundary Alignment Routine

The BAR subroutine is used to align the location counter to the proper word boundary, if necessary.

This subroutine will interrogate the boundary alignment bits of the Intermediate Text (byte 4) and, if necessary, add to the location counter the number of bytes that will align it to the proper word boundary.

After the location counter is incremented, it is tested to see if it exceeds the maximum allowable value of 65,535. If it does, the location counter is truncated and an error flag is placed into the Intermediate Text.

| F. | lag | Meaning                                                                      |

|----|-----|------------------------------------------------------------------------------|

| *  | Α   | Expression not simply relocatable                                            |

|    | В   | START, EXTRN, ENTRY, or ICTL out of order                                    |

|    | Ċ   | Location counter overflow                                                    |

|    | E   | More than 14 EXTRNs or more than 100 ENTRIES                                 |

|    | F   | Operand field format error or self-defining value in operand field too large |

|    | G   | DC D or E range error                                                        |

|    | J   | Symbol Table full                                                            |

|    | L   | Name field error                                                             |

|    | M   | Multiple defined symbol                                                      |

| *  | N   | Statement not used                                                           |

|    | 0   | Invalid operation code                                                       |

| *  | R   | Expression not absolute                                                      |

| *  | S   | Specification error                                                          |

| *  | T   | Value too large                                                              |

|    | V   | ORG or EQU symbol not previously defined                                     |

| *  | Y   | Negative expression                                                          |

|    | Z   | Column 72 not blank                                                          |

| *  | May | also be set by Phase II.                                                     |

Figure 7. Error Flags

## STORE - Store into Intermediate Text

The STORE subroutine is used to store the translated expressions of the operand field into the Intermediate Text.

This subroutine will store, one byte at a time, the translated terms of the expression in the operand field into the correct bytes of the Intermediate Text. The correct byte is determined by adding the value of the input parameter PC, which is set to the starting byte (minus 2) into which the translated term is to be placed, to the length of the translated term.

Therefore, the translated term is placed into the Intermediate Text beginning with the low-order byte of the field of the Intermediate Text associated with the term.

| r                             |                                      |                                                                                              |

|-------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|

| INSTRUCTION                   | NAME FIELD ERROR<br>(Error Flag      | OPERAND FIELD ERROR Set For All Instructions)                                                |

| All Machine  <br>Instructions | Symbol stored in Symbol Table        | Indicate how many bytes of zeros<br>are to be assembled by Phase II<br>for the operand field |

| CCW                           | Symbol not stored<br>in Symbol Table | Indicate how many bytes of zeros<br>are to be assembled by Phase II<br>for the operand field |

| CNOP                          | Symbol ignored                       | Statement ignored                                                                            |

| DC                            | Symbol not stored in Symbol Table    | Statement ignored Undefined symbol in type A will set operand field to zero                  |

| DROP                          | Symbol ignored                       | Statement ignored                                                                            |

| DS                            | Symbol not stored<br>in Symbol Table | Statement ignored                                                                            |

| EJECT                         | Symbol ignored                       | Symbol ignored                                                                               |

| END                           | Symbol ignored                       | No ENTRY point to this program will be defined                                               |

| ENTRY                         | Symbol ignored                       | Statement ignored                                                                            |

| EQU                           | Statement ignored                    | Statement ignored                                                                            |

| EXTRN                         | Symbol ignored                       | Statement ignored                                                                            |

| ICTL                          | Symbol ignored                       | Operand set to a 1 in a tape system and to 25 in a card system                               |

| ORG                           | Symbol ignored                       | Statement ignored                                                                            |

| SPACE                         | Symbol ignored                       | If not a decimal value, statement ignored                                                    |

| START                         | Symbol not stored<br>in Symbol Table | Location counter set to zero                                                                 |

| USING                         | Symbol ignored                       | Statement ignored                                                                            |

Figure 8. Error Summary

## BUMP - Increment Location Counter

The BUMP subroutine is used to increment the location counter by the required number of bytes and to indicate if the location counter exceeds the maximum allowable value of 65,535.

After the source statement is translated and placed into the Intermediate Text, the location counter is incremented by the number of bytes determined by the operation code of the statement. The location counter is incremented (after boundary alignment) as shown in Figure 9.

This subroutine is entered with the parameter VALUE indicating the amount the location counter is to be incremented by or reset to. It is entered with parameter ADJUST BIT set to a zero if the location counter is to be incremented; parameter ADJUST BIT set to a one if the location counter is to be reset.

After the location counter is incremented or reset, it is tested to see if it exceeds the maximum allowable value. If it does, the location counter is truncated and an error flag is placed into the Intermediate Text.

The BUMP subroutine also places the highest value the location counter reached during Phase I of the assembly into the second entry of the Symbol Table.

| Instruction<br>Type | Location Counter<br>Incremented by                                                                   |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| RR Format           | 2 bytes                                                                                              |  |  |  |

| RX,RS,SI<br>Format  | 4 bytes                                                                                              |  |  |  |

| SS Format           | 6 bytes                                                                                              |  |  |  |

| ORG                 | Reset to the value of the translated operand field                                                   |  |  |  |

| START               | Translated operand field expression after alignment to a double-word boundary                        |  |  |  |

| CCW                 | 8 bytes                                                                                              |  |  |  |

| CNOP                | Depends upon the current setting of the location counter and the translated operand field expression |  |  |  |

| DS                  | Translated operand field expression                                                                  |  |  |  |

| DC                  | Length of the constant mul-<br>tiplied by the duplication<br>factor                                  |  |  |  |

Figure 9. Increment Values

## TLUN/TLUS - Symbol Table Procedures

This subroutine is used during Phase I to build the Symbol Table and enter the attributes of each symbol into the Symbol Table. The subroutine has two entry points as follows:

- TLUN used when a symbol is encountered in the name field

- TLUS used when a symbol is encountered in the operand field

The symbol entry point in the Symbol Table is determined by dividing the compressed symbol by the length of the Symbol Table. The remainder is added to the starting location of the Symbol Table, and this sum is used as the entry point within the Symbol Table.

Thus, it can be seen that it is possible for more than one symbol to have the same entry point. A different symbol, therefore, may already have been entered into

the Symbol Table at this entry point. When this mismatch occurs, the Symbol Table is searched (from the entry point down) until a match occurs or until the next empty location is found.

The symbol name is reduced from 48 to 32 bits as follows:

- The first two bits of each character (always ones) are disregarded;

- 2. The next two bits of each character are saved, as the first 12 bits of the 32-bit reduced symbol name;

- 3. The remaining four bits of each character are converted to decimal and then, as a six-digit decimal number, this group is converted to binary and stored as the remaining 20 bits of the 32-bit reduced symbol name.

TLUN: The symbol entry point within the Symbol Table is checked. If the symbol has already been entered into the Symbol Table at this location, a check is made to determine if the symbol is defined. If the defined bit is a one, the symbol has been previously defined and error flag M is placed in byte 24 of the Intermediate Text.

If the defined bit is zero, the symbol has not been previously defined, and the attributes associated with the symbol are entered into the Symbol Table at this location. The defined bit is then set to a one.

If the symbol is not in the table at this location, and the location is empty, the symbol and its attributes are entered into this location. The defined bit is then set to a one.

If the symbol is not in the table at this location, and the location is not empty, a search of the Symbol Table is made to determine if the symbol was previously entered or to locate the next empty location within the table. If the symbol was previously entered at a different location, and the defined bit is not a one, the attributes associated with the symbol are entered into that location and the defined bit is set to a one. If the defined bit is a one, the symbol has been previously defined, and error flag M is placed into the Intermediate Text. If the symbol has not been previously entered into the Symbol Table, the symbol and its associated attributes are entered into the next empty location in the Symbol Table, and the defined bit is set to a one.

If the Symbol Table is completely scanned before the symbol or an empty location is found, error flag J is placed in byte 24 of the Intermediate Text to indicate that the Symbol Table is full.

This symbol, and any other symbol following that is not already entered into the Symbol Table, will remain undefined.

TLUS: The symbol entry point within the Symbol Table is checked. If the symbol has already been entered into the Symbol Table at this location, a pointer to this location is placed into the relevant bytes of the Intermediate Text.

If the symbol is not in the table at this location, and the location is empty, the symbol is entered into this location. Since the symbol is from the operand field, none of the symbol attributes are known at this time. Therefore, the remainder of the table entry for this symbol remains blank. The attributes for the symbol will be placed into the Symbol Table when the symbol is encountered in the name field of a source statement. A pointer to this location is then placed into the relevant bytes of the Intermediate Text.

If the symbol is not in the table at this location, and the location is not empty, a search of the Symbol Table is made to determine if the symbol was previously entered or to locate the next empty location within the Symbol Table. If the symbol was previously entered at a different location, a pointer to that location is placed into the relevant bytes of the Intermediate Text. If the symbol has not been previously entered into the Symbol Table, the symbol is entered into the next empty location in the Symbol Table, and a pointer to that location is placed into the relevant bytes of the Intermediate Text.

If the Symbol Table is completely scanned before the symbol or an empty location is found, error flag J is placed in byte 24 of the Intermediate Text.

# INOUT - Input/Output Subroutine (CHARTS AO and AP)

This subroutine is the same for both Phase I and Phase II. It controls all the I/O operations for the Assembler Program.

The subroutine is entered at location INOUT from the calling routine. The interrupts are disabled and the CAW and device address are stored (02-04).

The I/O device is then tested for the following conditions (05):

Device unavailable. This is an error condition and an error halt occurs. The SEREP ID code for the unavailable device is set and the device address is stored in the old IOPSW (bytes 2 and 3).

- 2. Device busy. The program goes into an internal loop until the device is ready. When the device is ready, a test is made to determine if the CSW is stored.

- CSW stored. Control is transferred to the interrupt routine.

The condition codes and their meanings are as follows:

| Condition | on code | Meaning             |               |

|-----------|---------|---------------------|---------------|

| (         | )       | Available           | <u> </u>      |

| •         | 1       | CSW store operation | ed (Immediate |

| 2         | 2       | Busy                |               |

| 3         | 3       | Unavailak           | ole           |

When the device is available and ready, an attempt is made to start the I/O operation. Two procedures are possible as follows:

- 1. The device is started and the data transfer initiated. Interrupts are enabled, and the program enters a wait state until an interrupt occurs (06-07). When an interrupt occurs, either as a result of the current SIO or from a previous SIO, the interrupt procedure is initiated. The interrupt entry switch is set (except when a busy condition was cleared by a TIO operation), and a Retry switch is tested (09-10).

- The device is started for an immediate operation (rewind, skip), the interrupt procedure is initiated, and the Retry switch is tested.

The Retry switch is tested and if this a tape-positioning operation (backspace, skip) or sensing operation resulting from the error correction procedure, control is transferred to the error correction procedure.

If the Retry switch is not on, the read switch is set if this is a read operation, and the error conditions are checked (11-12). If it is a channel error, the SEREP ID code and the recovery address in the external New PSW are set and the program enters a wait state with AIS in the location counter (13-33-28). If it is a unit error and the unit is not tape, the SEREP ID code for device failure is set, the recovery address is set in the external New PSW, and the program enters a wait state with AIS in the location counter (14-34-28). If there is a unit error, and

the unit is tape, control is transferred to the error correction procedure (AP-A2).

If there are no errors, the busy indicator is checked (15). If the busy indicator is on, control is transferred to the interrupt procedure to check the Retry switch.

If the error switch was set on this pass, it is cleared and the registers restored before EOF and other exceptional conditions are checked.

If there are no exceptional conditions, control is returned to the calling routine. If an exceptional condition is caused by the printer, it is ignored, and control is returned to the calling routine; otherwise the error halt occurs and the recovery address is placed in the external New PSW (32).

Error Recovery Procedure: This procedure is entered for a tape error only. The

Retry switch is set and the I/O Old PSW, CSW, and CAW are saved (01). The sense bytes are requested and the original conditions are restored (02-04).

If the sense information is a unit check, a test is made to determine if it is a first read error (05-06). If it is, the error switch is turned on. If it is not a first error, the read switch is checked and 10 read retries are made. If the read attempt is still not successful, an error halt occurs and a standard device failure message is produced.

If it is a write failure, three rewrite and skip operations occur three times before an error halt occurs and a standard device failure message is produced.

Note: The error recovery procedure described above does not conform to IBM standards; i.e., no priority checking or tape cleaning is implemented.

This section uses three charts to describe the overall processing flow of Phase I of the Assembler Program. Chart 03 illustrates the initialization procedures, and Charts 04 and 05 illustrate the Control Routine. The numbers in parentheses within the text describing each chart indicate the block on the chart being explained.

## INITIALIZATION - CHART 03

Phase I of the Assembler Program is read into main storage (01). The addressability and main storage size, as determined by the Phase I Configuration Card, are set up, and the necessary control parameters to be used by the subroutines of Phase I are generated and stored (02-03).

The Configuration Card is discussed in detail in the publication, <u>IBM System/360</u>

Basic Programming Support Operating Guide for Basic Assembler and Utilities, Form C28-6557.

The area reserved for the Symbol Table, determined by the size of main storage, is cleared, and the first two entries are reserved for the uses indicated in Section 2, "Tables" (04).

The input/output addresses are determined and set up for the read and write routines. These addresses are determined by the intermediate text device being used (card or tape). The size of the Intermediate Text to be written or punched as output (24 bytes for a card intermediate text system, 104 bytes for a tape intermediate text system) is stored into the necessary locations of the write routine (05-12). The first source statement is then read in (13).

In a card intermediate text system, if column 1 of the first card indicates it is a Symbol Table card (14), the Symbol Table deck is read into the area of main storage reserved for the Symbol Table (15). The use of the Symbol Table deck is discussed in detail in the publication, IBM System/360 Basic Programming Support Basic Assembler Language, Form C28-6503.

After the last card of the Symbol Table deck is read into main storage, or when the Symbol Table deck is not present, control exits to the Phase I Control Routine (Chart 04).

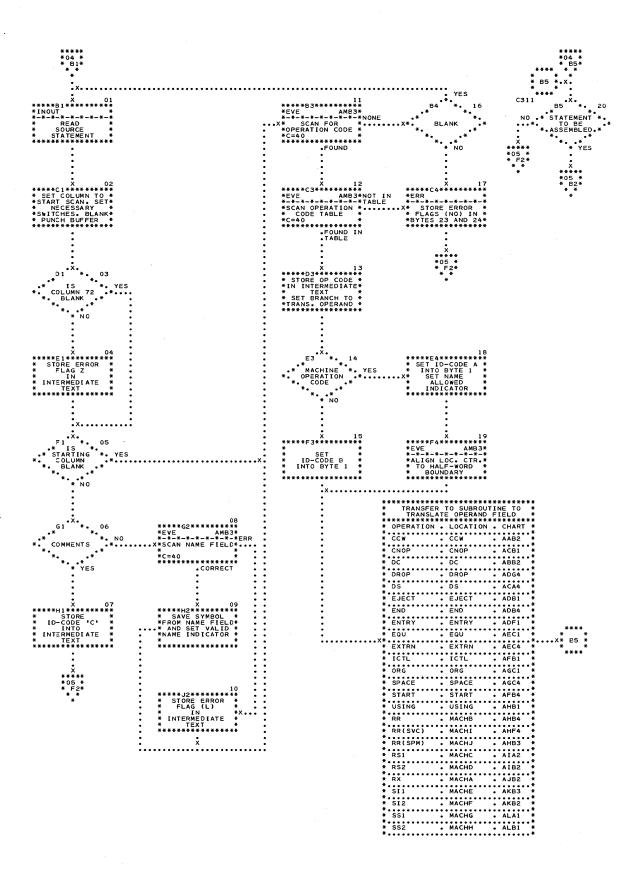

The first statement of the source program is read in (01). The first column of the card to be scanned by the EVE subroutine (determined by the SYSCON control byte of the Phase I Configuration Card) is set, the control switches are set, and the punch buffer output area is cleared (02).

Column 72 of the source program statement, which must be blank, is tested (03). If it does not contain a blank, error flag Z is placed in byte 22 of the relevant Intermediate Text (04). Any information contained in column 72 is ignored when the source statement is processed, but column 72 is printed as part of the source statement in the program listing.

The first column of the source statement is tested for an asterisk or a blank (05-06). If the source statement begins with a blank, the operation code is then checked (11). If the column contains an asterisk, ID-Code C, indicating the source card is a comments card, is placed in byte 1 of the Intermediate Text. No further translation of the source statement is performed during the assembly process. A comments card is only reproduced in the object program listing.

If the statement begins with neither an asterisk nor a blank, it indicates that the source statement begins with a symbol in the name field. The symbol in the name field is scanned by subroutine EVE to If the determine if it is valid (08). symbol is valid (i.e., begins with an alphabetic character and contains no more than six characters), the valid-symbol indicator is set. However, the symbol is not placed into the Symbol Table at this time. A symbol in the name field of the source statement being translated may not be allowed. Until this can be determined, the symbol is only temporarily stored (09). If the symbol is not valid, error flag L is placed in byte 24 of the Intermediate Text The operation code is then checked (10). (11).

If the operation code field of the source statement is blank (the remainder of the source statement is blank) ID-Code L, indicating the statement is not to be assembled as part of the object program, and error flags NO are placed in bytes 1, 23, and 24, respectively, of the Intermediate Text (17). If the remainder of the source statement is not blank, but the operation code has been omitted, the first characters of the operand field or comments field will be treated as the operation code. Control then exits to produce the Intermediate Text (Chart 05, block F2).

If the operation code field contains an operation code, the Operation Code Table is searched to determine if the operation code is valid (12). If the operation code is not valid, ID-Code L, indicating the statement is not to be assembled as part of the object program, and error flags N and O are placed in bytes 1, 23, and 24, respectively, of the Intermediate Text (17). The next source program statement is then read in (01).

If the operation code contained in the source statement is found during the search of the Operation Code Table, it is checked for type (14). If it is a machine operation code, ID-Code A is placed in byte 1 of the Intermediate Text, and the location counter is aligned to a half-word boundary (18-19). Control then exits to the subroutine necessary to translate the operand field as determined by the operation code.

If the operation code indicates an Assembler Instruction, ID-Code B is placed in byte 1 of the Intermediate Text and control exits to the subroutine necessary to translate the operand field as determined by the operation code. (See Section 5, "Operand Field Translation.")

Subroutine EVE is used to translate the operand field of each statement. The translation of each operand field by subroutine EVE is basically the same regardless of the type of statement. This subroutine is, however, entered with different parameters for each statement type. These parameters are shown in the description of subroutine EVE in Section 3, "Subroutine Description."

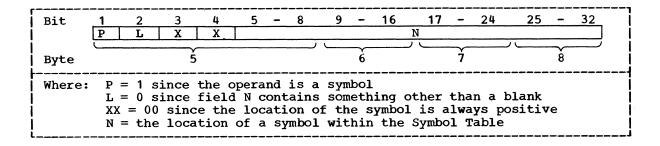

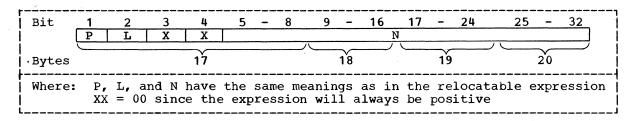

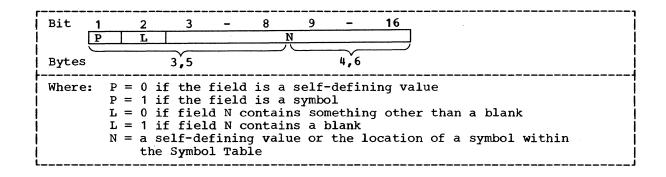

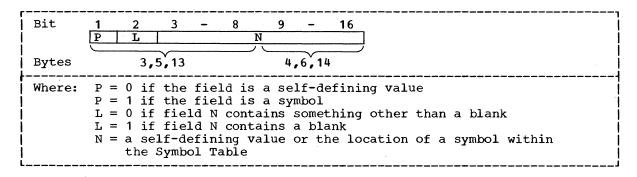

Each expression within the operand field is translated separately and placed in the relevant bytes of the Intermediate Text for that statement.