# Field Engineering Theory of Operation

# Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

2025 Processing Unit

RESTRICTED DISTRIBUTION: This publication is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

# First Edition (October 1968)

Significant changes or additions to the specifications contained in this publication are continually being made. Any such changes will be reported in subsequent revisions or FE Supplements.

This publication has been prepared by the IBM Systems Development Division, Product Publications, Dept. 171, P.O. Box 6, Endicott, N.Y. 13760. A form has been provided at the back of this publication for readers' comments. If the form has been removed, comments may be addressed the same as above.

# BACKGROUND AND LEVEL OF READER

This manual is intended for use by IBM personnel who have a knowledge of System/360 operation.

# PREREQUISITE MANUALS

- The reader should be familiar with the following SRL publications.

- IBM System/360 Principles of Operation, Form A22-6821

- IBM System/360 Model 25 Functional Characteristics, Form A24-3510

- IBM System/360 Model 25, 1401/1460 and 1440 Compatibility Features, Form A24-3512.

#### COMPANION MANUAL

The following companion manual is necessary to study the IBM 2025.

• IBM 2025 Processing Unit, FE Maintenance Diagrams Manual, Form Y24-3529.

Diagrams in the FE Maintenance Diagrams Manual are referenced using the initials MDM followed by the diagram number; e.g., MDM x-xx.

# SYSTEM MANUALS

The following manuals are necessary for overall study of the Model 25 System.

- IBM 2025 Processing Unit, System/360 Channels FETOM, Form Y24-3531.

- IBM 2025 Processing Unit, Integrated 2540 Attachment FETOM, Form Y24-3532.

- IBM 2025 Processing Unit, Integrated 1403 Attachment FETOM, Form Y24-3533.

- IBM 2025 Processing Unit, Integrated 2311 Attachment FETOM, Form Y24-3534.

- IBM 2025 Processing Unit, FE Maintenance Manual, Form Y24-3528.

#### FEATURES OF MANUAL

Material is arranged in the order of learning.

# Contents

Lists the major headings of the manual.

# Abbreviations

Alphabetic list of abbreviations, acronyms, and symbols used in the manual.

# Introduction

High-level presentation of the major points needed to understand the system.

#### Functional Units

Describes parts of the machine that always act in much the same manner.

# Principles of Operation

Contains the concepts and information needed to understand the microlistings.

#### Features

Describes special features, including 1400 Compatibility.

# Power Supplies and Controls

Describes power sequencing, power distribution, etc.

#### Console and Maintenance Features

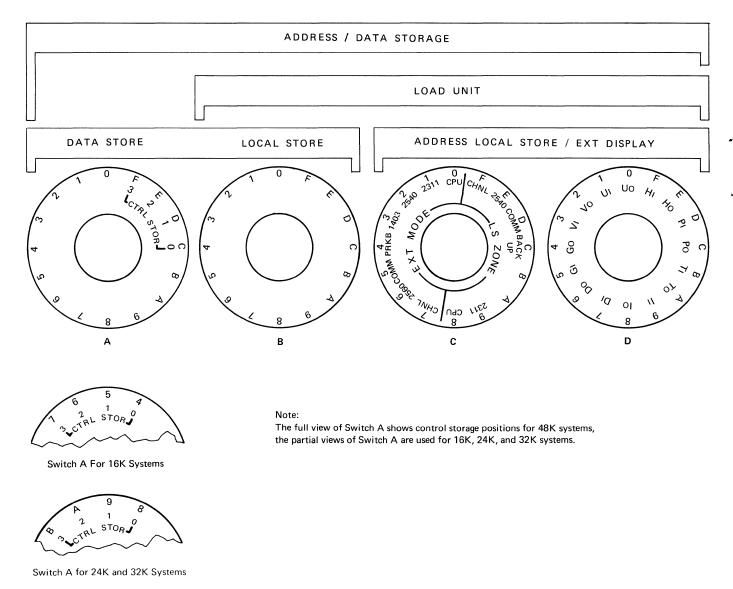

Describes all console keys, lights, and switches. The theory of operation for the Console Printer-Keyboard is included in this section, as well as the alter/display and logout facilities.

# Appendixes

List speed and capacity of system units. Provide World Trade information.

#### Index

Detailed, cross-referenced, alphabetic listing of headings, key words, phrases, operations, etc.

| •            |

|--------------|

| •            |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

|              |

| <b>V</b>     |

| ,            |

| · (          |

| • 3          |

|              |

| 4            |

| 4            |

| 4            |

| <del>Q</del> |

# CONTENTS

| PREFACE                                | . iii          | Traps                                                           |       |

|----------------------------------------|----------------|-----------------------------------------------------------------|-------|

| Background and Level of Reader         | .iii           | Priority 2-1                                                    | L2    |

| Prerequisite Manuals                   | 111            | External Facilities                                             |       |

| rierequisite manuais                   | • +++          |                                                                 |       |

| Common ton Monney 1                    |                | MMSK Register                                                   |       |

| Companion Manual                       | .111           | S-Register                                                      |       |

| System Manuals                         | .iii           | BC - External Facility 2-2 Dynamic Condition (DYN) Register 2-2 |       |

| Features of Manual                     | .iii           | Control Register                                                | 21    |

| CONTENTS                               | . v            | Arithmetic and Logical Control                                  | 2 2   |

| ABBREVIATIONS                          | .ix            | Circuits                                                        | 23    |

| CHAPTER 1. IBM SYSTEM/360 MODEL 25     | .1-1           | A-Register                                                      | 23    |

|                                        |                | ALU                                                             |       |

| System Control                         | .1-1           | A-Register Gating 2-2                                           | 24    |

|                                        |                | B-Register Gating 2-2                                           | 24    |

| Data Flow                              | .1-1           | True/Complement Controls 2-2                                    |       |

| Main Storage                           |                | Adder                                                           |       |

| Program Storage                        |                | ALU Controls                                                    |       |

| Control Storage                        |                | Carry Insert                                                    |       |

| Auxiliary Storage                      |                | Decimal Corrector                                               |       |

| M-Register and M-Register Assembler    |                | ALU Check                                                       |       |

| Storage Address Assembler              |                | ALU Modifier                                                    |       |

| W-Register                             |                | ALU MOUTITET                                                    | 20    |

|                                        |                | Togal Charage (Figure 2-15)                                     |       |

| C-Register                             |                | Local Storage (Figure 2-15)2-2                                  |       |

| Local Storage                          |                | Zone 0                                                          | 30    |

| Local-Storage Data Assembler           |                | Zone 1                                                          |       |

| Local-Storage Address Assembler.       |                | Zone 4 2-3                                                      | 30    |

| A/B Register Assembler                 | • 1 <b>-</b> 6 | Zone 5 2-3                                                      |       |

| Arithmetic and Logical Control         |                | Zone $\frac{6}{2}$                                              | 31    |

| Circuits                               |                | Zone 7 2-3                                                      | 31    |

| Integrated I/O and Channels            | -1-6           | Local Storage Address Assembler 2-3                             | 31    |

| External Facilities                    | .1-6           | Local Storage Data Assembler 2-3                                | 32    |

| CHAPTER 2. FUNCTIONAL UNITS            | .2-1           | CPU Checks                                                      | 33    |

|                                        |                | Hard-Stop Latch 2-3                                             | 3 4   |

| CPU Clock                              | .2-1           | Machine-Check Latch 2-3                                         | 34    |

| Clock Control                          |                |                                                                 |       |

|                                        |                | CHAPTER 3. THEORY OF OPERATION 3-1                              | L     |

| Core Storage                           | . 2-1          |                                                                 |       |

| Core Array (8K Halfwords)              | · 2-3          | Microprogram Concepts                                           |       |

| Common Sense/Inhibit                   | . 2-5          | Definitions                                                     | L     |

| Storage Clocks                         |                | Microprogram Functions 3-3                                      | 3     |

| Storage Addressing                     |                | Microlistings 3-3                                               | 3     |

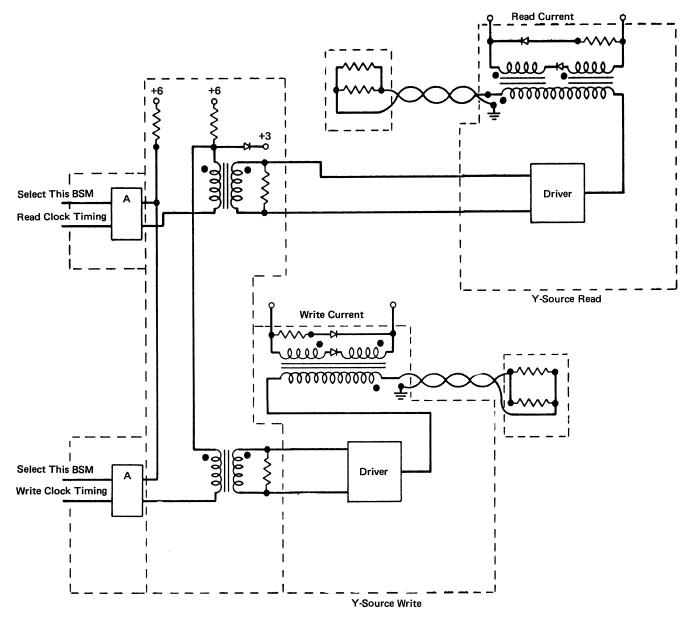

| Current Sources                        | .2-7           | Microprogram, Machine Language                                  |       |

| X- and $Y-$ Drive Gate and Selection . | -2-8           | Tie-In                                                          | 3     |

| X-Decode Drive                         |                | Control Storage Load (CSL) 3-5                                  | 5     |

| Y-Decode Drive (Main Storage)          | .2-8           | CSL Using Integrated 2540 3-5                                   |       |

| XY-Decode Drive (Auxiliary             |                | CSL Using a Reader on the                                       | •     |

| Storage)                               | . 2-9          | Standard Interface 3-5                                          | 5     |

| Storage Data Assembler and Register    |                | CSL Using Integrated 2560 3-5                                   | Ś     |

| Power Supply and Temperature           | · • ·          | Set/Reset Word                                                  |       |

| Compensation                           | 2-9            | Bit Significance Fields (Figure                                 | ,     |

| M-Register Assembler                   |                | 3-2)                                                            | =     |

| M-Register                             |                |                                                                 |       |

| W-Register                             | 2 11           | Description                                                     | 2     |

|                                        |                | Examples                                                        | )<br> |

| Address Match Circuits                 |                | Arithmetic Constant Word 3-1                                    | r 2   |

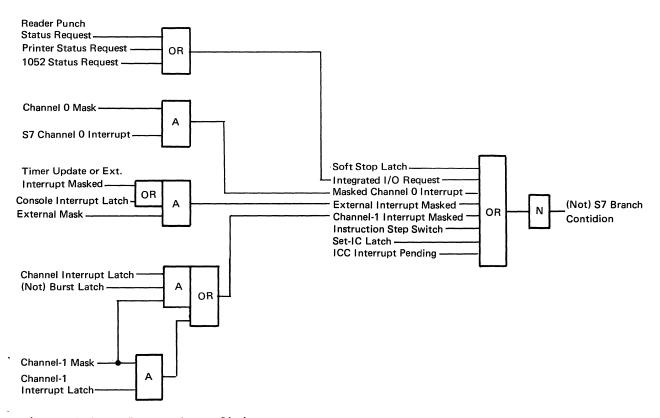

| Traps and Priority                     | • 2-12         |                                                                 |       |

|                                           | 4 35                                  |

|-------------------------------------------|---------------------------------------|

| Bit Significance Fields (Figure           | I-Cycles                              |

| 3-6)                                      | I-Cycles Objectives                   |

|                                           | I8 Objectives                         |

| Examples                                  | 10 Objectives                         |

| Storage Word                              | I7 Objectives 4-16                    |

| Bit Significance Fields (Figure           | I5 Objectives                         |

| 3-7),                                     | I4 Objectives                         |

| Decembration                              | TO Objectives 4-17                    |

| Description 3-20                          | I2 Objectives                         |

| Examples                                  | I1 Objectives                         |

| Move/Arithmetic Word                      | Indexing                              |

| Bit Significance Fields (Figure           |                                       |

|                                           | 7.00                                  |

| 3-8)                                      | I/O Operations                        |

| Examples                                  | 1402 Read Operations 4-18             |

| Branch Unconditional Word 3-24            | Microroutine Objectives 4-19          |

| Bit Significance Fields (Figure           | 1402 Punch Operations                 |

|                                           | 1402 Punch Operations                 |

| 3-9)                                      | Microroutine Objectives 4-19          |

| Description3-25                           | 1403 Printer Operations 4-20          |

| Examples                                  | Microroutine Objectives 4-21          |

| Dranch on Mack Hord                       | 1442 Drinter Operations 4-21          |

| Branch on Mask Word 3-26                  | 1443 Printer Operations               |

| Bit Significant Fields (Figure            | Microroutine Objectives 4-21          |

| 3-10)                                     | 1442 Card Read-Punch Operations 4-22  |

| Description3-26                           | Microroutine Objectives; Read         |

|                                           | Omenations 4-22                       |

| Examples                                  | Operations                            |

| Branch on Condition Word 3-30             | Microroutine Objectives, Punch        |

| Bit Significance Fields (Figure           | Operations                            |

| 3-12)                                     | Disk Compatibility Operation 4-23     |

|                                           | Formats                               |

| Description3-33                           | rolliats                              |

| Examples                                  | File Circuitry 4-24                   |

|                                           | Operational Objective 4-25            |

| CHAPTER 4. FEATURES 4-1                   | Seek Command 4-25                     |

| CHALLER 4. LEWICKED                       | Dood (Write Operations With           |

|                                           | Read/Write Operations With            |

| System/360 Model 25 1401/1460 and 1440    | Indelible Address 4-25                |

| Compatibility Features 4-1                | Wordmarks and Zone Bits in            |

|                                           | Control Fields 4-26                   |

| - 1 · · · · · · · · · · · · · · · · · ·   | De 1 (Tail L. Ou and Laure Control    |

| Implementation 4-1                        | Read/Write Operations, Sector         |

|                                           | Mode                                  |

| Compatibility Initialization 4-2          | Alternate Track Operation 4-28        |

|                                           | Magnetic Tape Operations 4-28         |

| On Code Convenies and Descentition        | Microroutine Objectives 4-29          |

| Op-Code Conversion and Recognition 4-2    | Microroacine Objectives 4 29          |

|                                           |                                       |

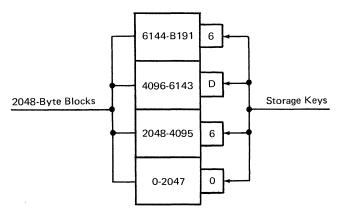

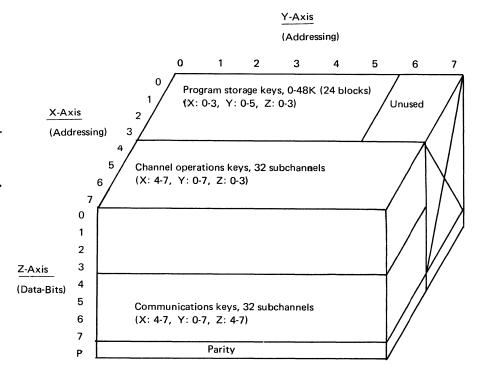

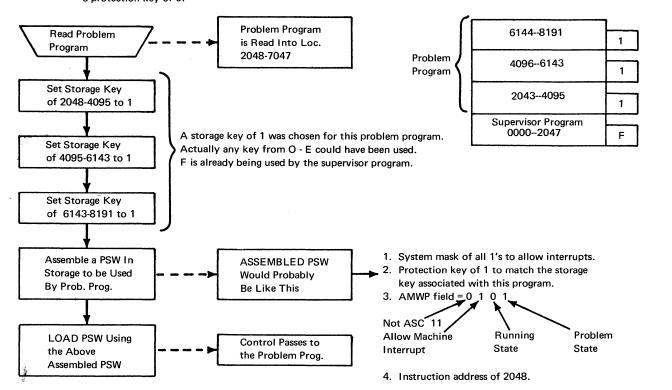

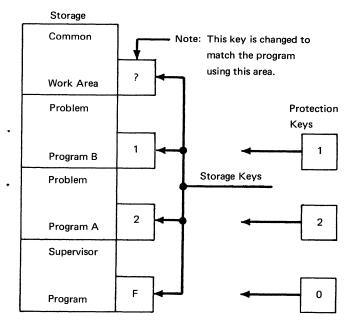

| Character Configuration 4-4               | Storage Protection                    |

|                                           | Storage Key                           |

| 1401/1460 and 1440 Program Addressing4-4  | Protection Key                        |

| 140171400 and 1440 llogram nadlesbing 4-4 | Dretection Execution 4-34             |

|                                           | Protection Exception                  |

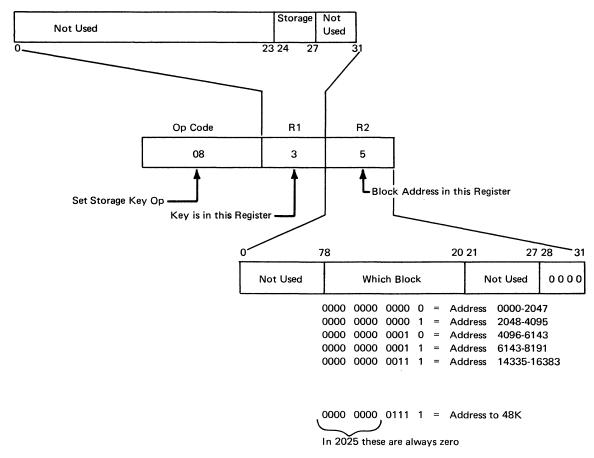

| Address Conversion 4-5                    | Setting Up Storage Protection 4-35    |

| Address Error Detection                   | Set Storage Key (Machine              |

| · · · · · · · · · · · · · · · · · · ·     | Language Instruction) 4-37            |

| Aurilianu Chorago                         | Ingort Storage Voy (Maghine           |

| Auxiliary Storage 4-7                     | Insert Storage Key (Machine           |

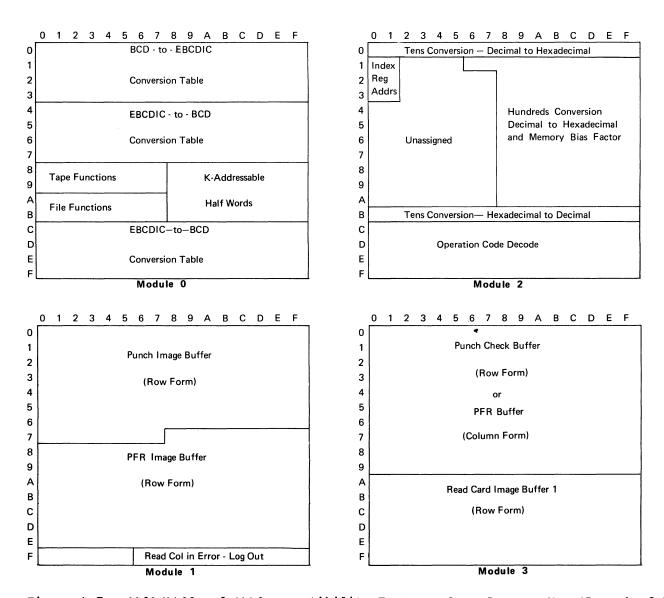

| Auxiliary Storage Module $04_{-10}$       | Language Instruction) 4-37            |

| Auxiliary Storage Module 1 4-12           | Displaying A Storage Protect Key4-37  |

| Auxiliary Storage Module 2 4-12           |                                       |

| Auxiliany Characa Madula 2                | Functional Unite (Bofor to Figure     |

| Auxiliary Storage Module 3 4-13           | Functional Units (Refer to Figure     |

| Auxiliary Storage Module 4 4-13           | 4-13)                                 |

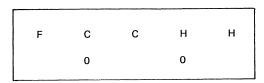

| Auxiliary Storage Module 5 4-13           | STP1 Map                              |

| Auxiliary Storage Module 6 (Module        | -                                     |

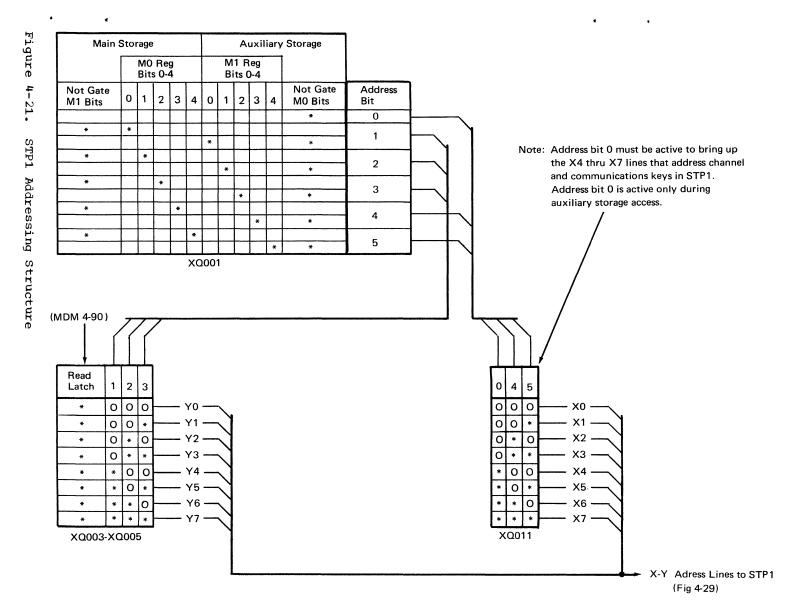

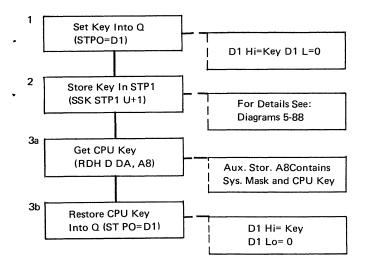

| 8 in 24K Systems)4-13                     | Theory of Operation (MDM 4-90) 4-38   |

| The line Character Martin 7 (Martin 2)    | CMD1 Addressed to Characters (Dimens  |

| Auxiliary Storage Module 7 (Module        | STP1 Addressing Structure (Figure     |

| 9 in 24K Systems) 4-13                    | 4-21)                                 |

|                                           | Loading STP14-38                      |

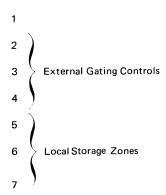

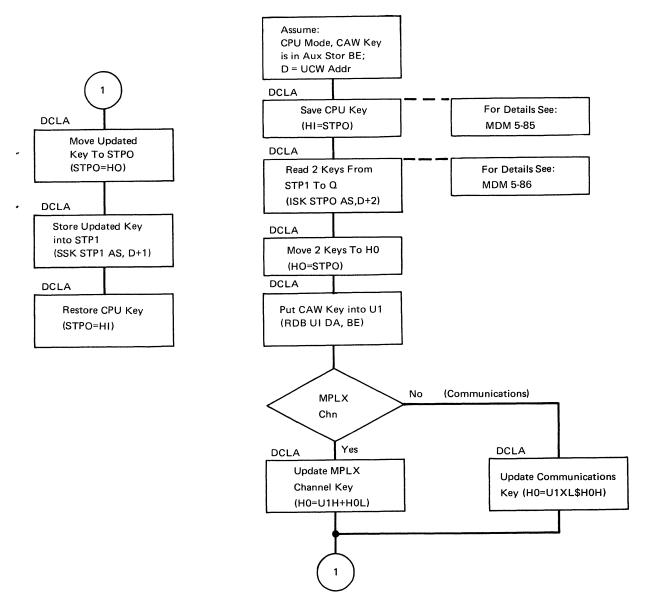

| Local Storage 4-13                        | Set Storage Key Microword Cycle       |

| 7000 0                                    | (Figure 4-24)                         |

| Zone 0                                    | (rigure 4-247                         |

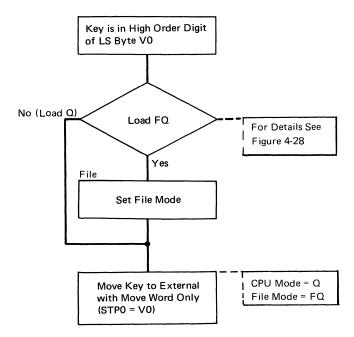

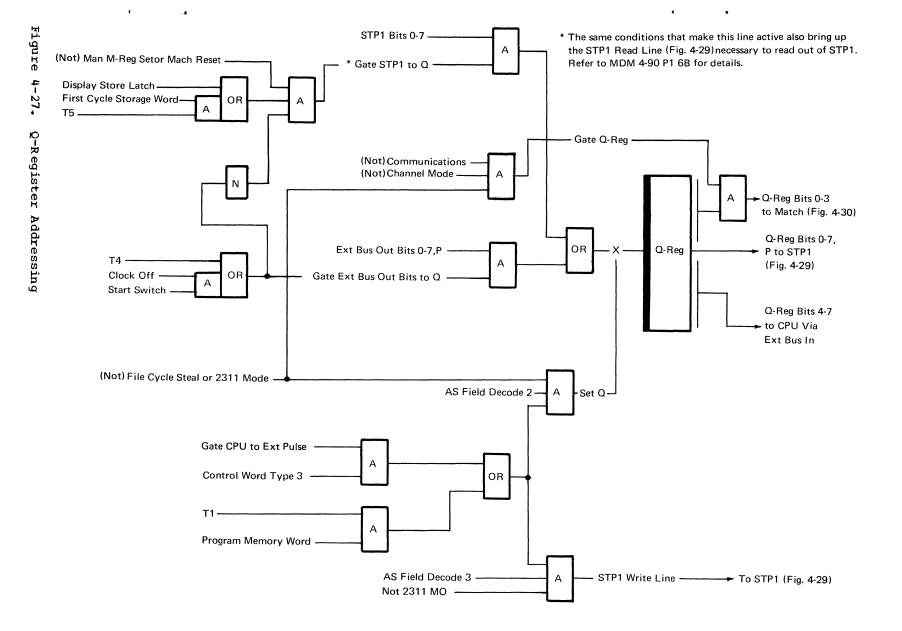

| Zone 1                                    | Loading Q- and FQ-Registers 4-43      |

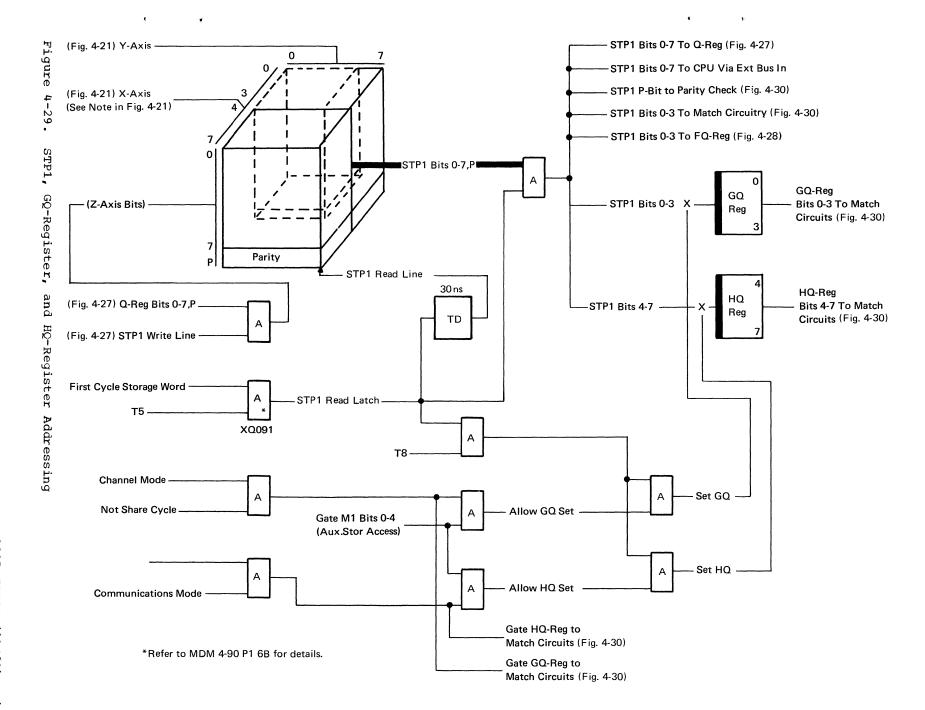

| Zone 4 4-14                               | Loading GQ- and HQ-Registers          |

| Zone 6                                    | (Figure 4-29)                         |

| Zone 7                                    | Main Storage Access (Figure 4-29)4-44 |

|                                           | Zero Test (Protection Key 0) 4-44     |

| 0                                         |                                       |

| Operation                                 | Parity Check (Figure 4-30) 4-44       |

|                                           | Match Circuitry (STP0=STP1)4-44       |

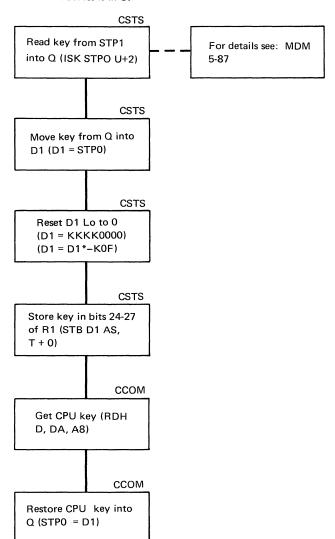

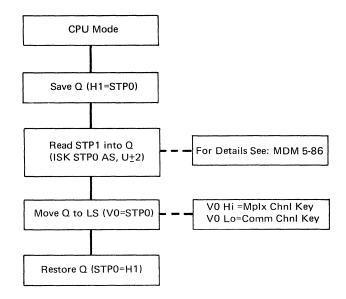

| CPU Operations 4-15                       | Insert Storage Key (CSTS Routine)4-49 |

|                                           | - <u>-</u>                            |

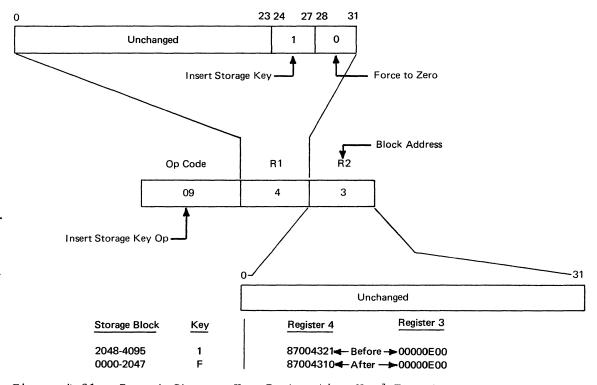

| Insert Storage Key (Microword             |                        | Manual Store Operation (Core        |                 |

|-------------------------------------------|------------------------|-------------------------------------|-----------------|

| Statement)                                | 4 40                   | Storage)                            | 6_12            |

| Statement)                                | . 4-49                 |                                     |                 |

|                                           |                        | Alter/Display Local Storage         |                 |

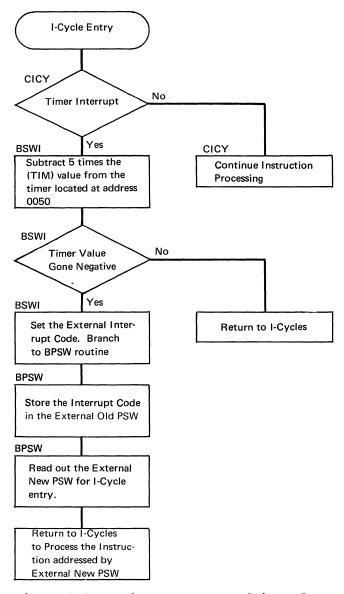

| Interval Timer                            |                        | ALU/External Display                | . 6-13          |

| 60-Cycle Operation                        |                        |                                     |                 |

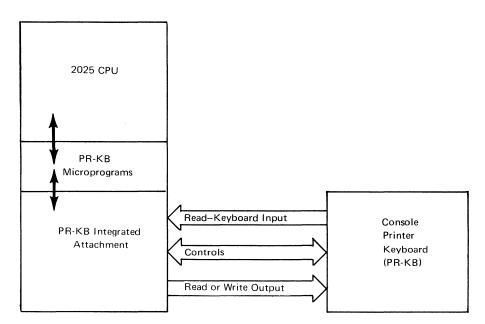

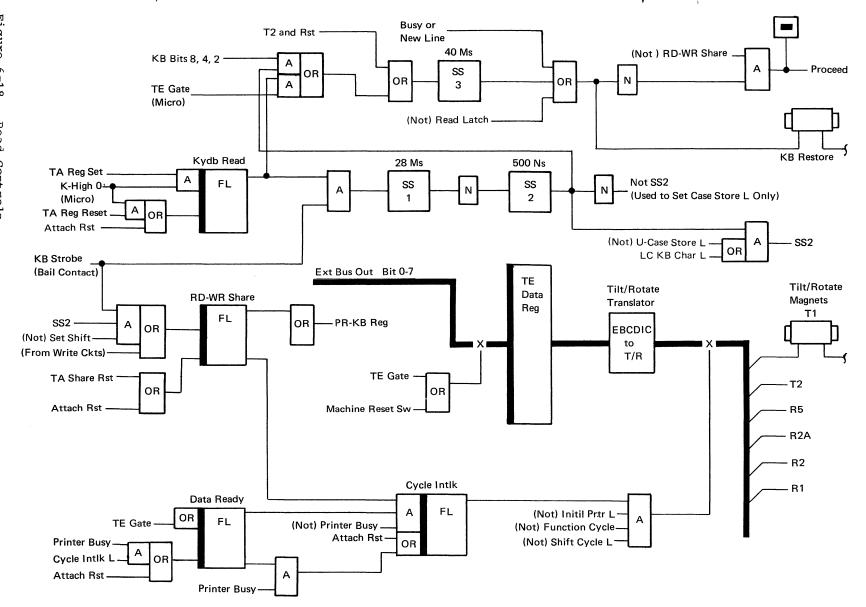

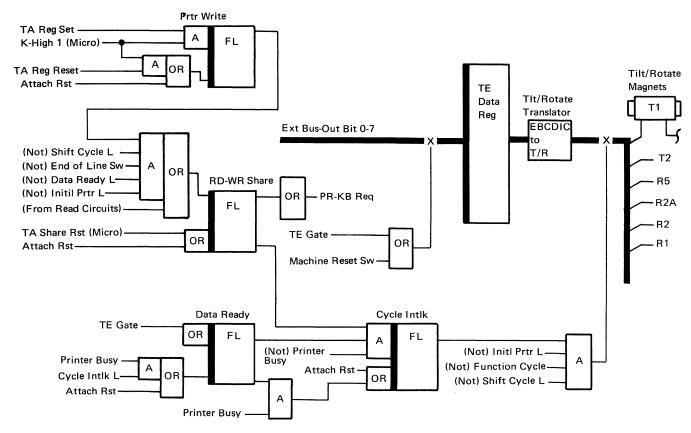

| 50-Cycle Operation                        | . 4-52                 | Console Printer-Keyboard            | .6-13           |

|                                           |                        |                                     |                 |

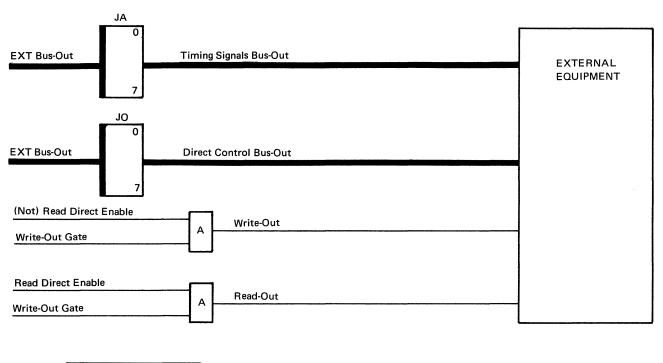

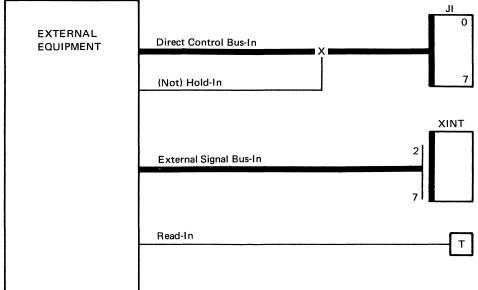

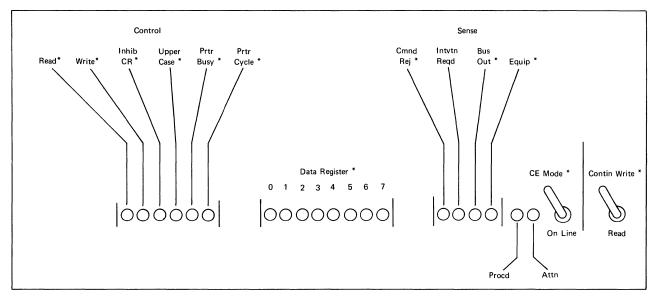

| Direct Control Feature                    | <ul><li>4-52</li></ul> | Comprehensive Introduction          | .6-13           |

| Direct Control Bus-Out                    | . 4-52                 | Input Data Code                     |                 |

| Timing Signal Bus-Out                     |                        | Output Data CodeEBCDIC              | 6-14            |

| Direct Control Bus-In                     |                        | Tilt/Rotate Printing Code           |                 |

|                                           |                        |                                     |                 |

| External Signal Bus-In                    |                        | Data Flow                           | . 0-10          |

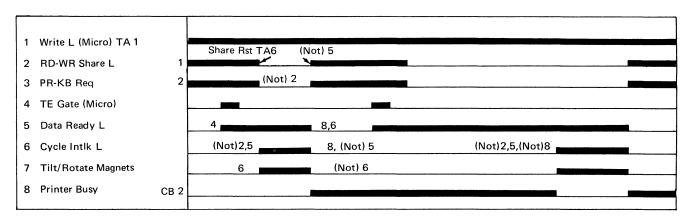

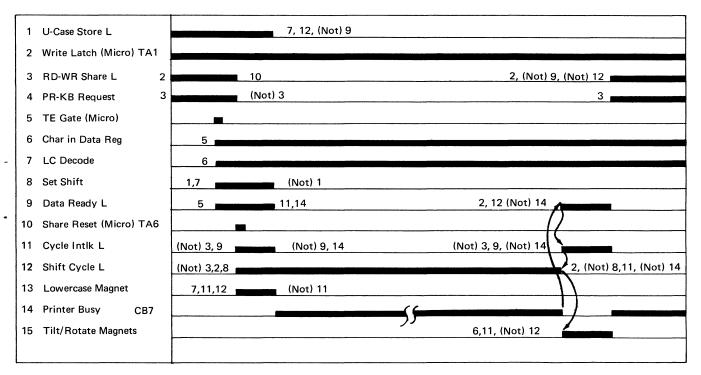

| Writeout                                  |                        | Controls-Out (TA)                   | . 6-18          |

| Readout                                   |                        | Controls-In (TU and TT)             |                 |

| Hold-In                                   |                        | Diagnostic Registers (TR and TD)    |                 |

| Read-In                                   | <ul><li>4-54</li></ul> | Input Data (TI)                     |                 |

| Application                               | · 4-54                 | Output Data (TE)                    | .6-18           |

| Situation A                               | • 4-55                 | Share Request Control               |                 |

| Situation B                               |                        | •                                   |                 |

|                                           | • 4-33                 | Functional Units                    | 6-18            |

| Esternal Interrupt                        | 4 55                   | Printer Keyboard                    |                 |

| External Interrupt                        | • 4-55                 | Printer Reyboard                    | • 0-10          |

| THE DEED S. DOLLED GUIDDI THE AND COMMENT |                        | PR-KB Auxiliary Storage Areas       | • 6-19          |

| CHAPTER 5. POWER SUPPLIES AND CONTROL.    | • 5 <b>-</b> 1         | Alter/Display Message Area          |                 |

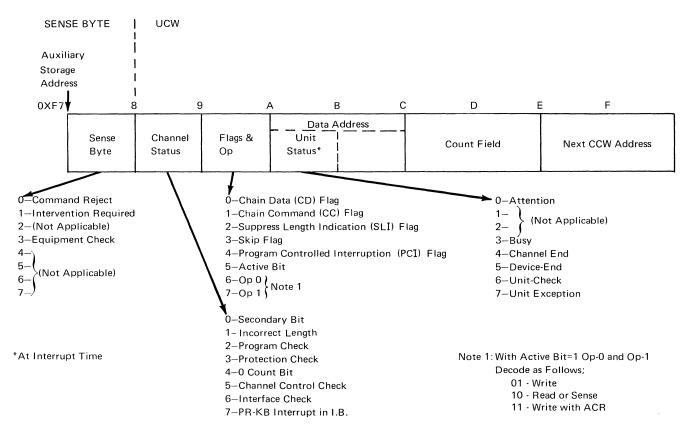

|                                           |                        | Sense Byte (PR-KB)                  | • 6 <b>-</b> 19 |

| Power-On Sequence                         | • 5-2                  | PR-KB Unit Control Word (UCW)       |                 |

|                                           |                        | Flags/Op Byte                       | • 6-19          |

| Power-Off Sequence                        | • 5-2                  | Channel Status Byte                 |                 |

| Power-Off Key                             |                        | Unit Status Byte                    |                 |

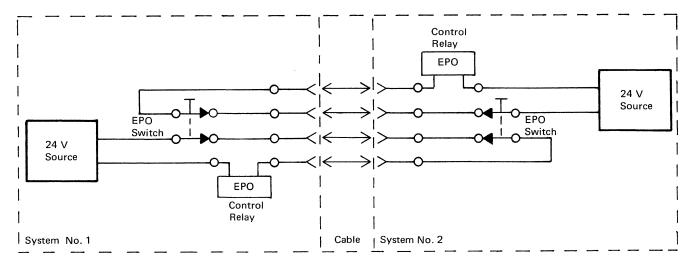

| Emergency Power Off (EPO)                 | 5-3                    | PR-KB Translate Table (Keyboard     |                 |

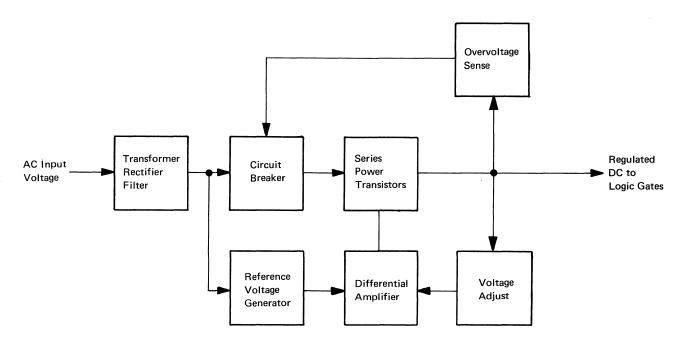

| Cvercurrent, Overvoltage Detection.       | - 5 1                  | Code to EBCDIC)                     | 6-22            |

| Voltage Sensing System                    |                        | Translate Subroutine (Keyboard Code |                 |

|                                           |                        |                                     |                 |

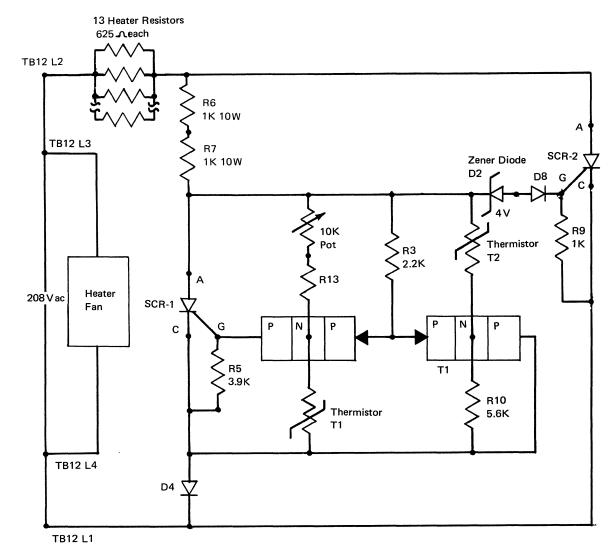

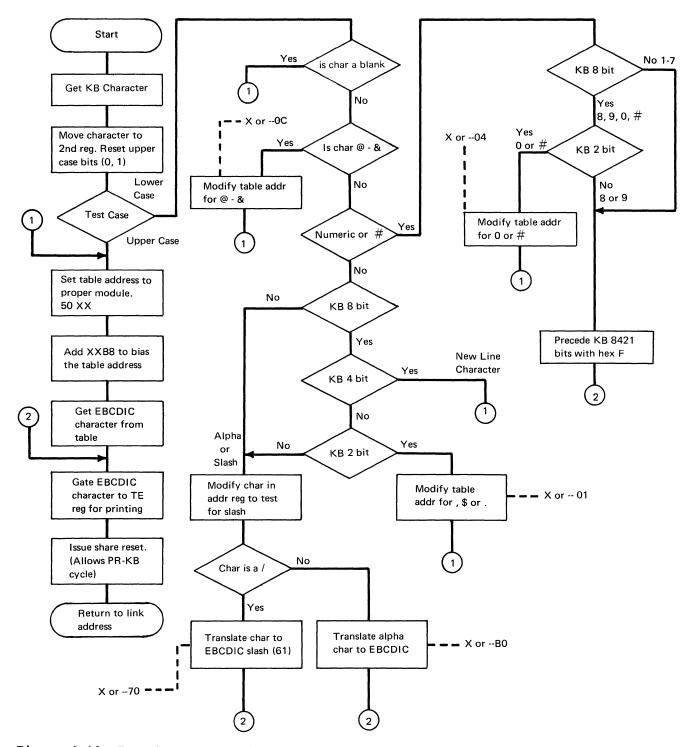

| Thermal Sensing                           | • 5-5                  | to EBCDIC)                          | . 6-22          |

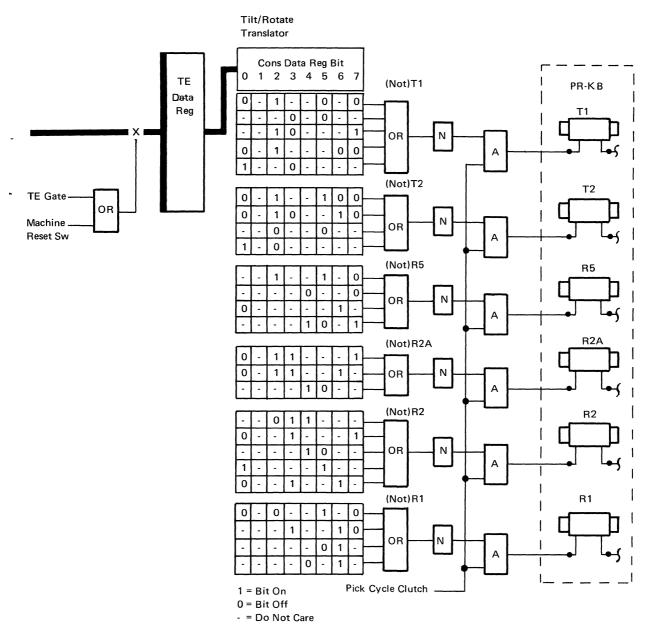

|                                           |                        | Tilt/Rotate Translator              |                 |

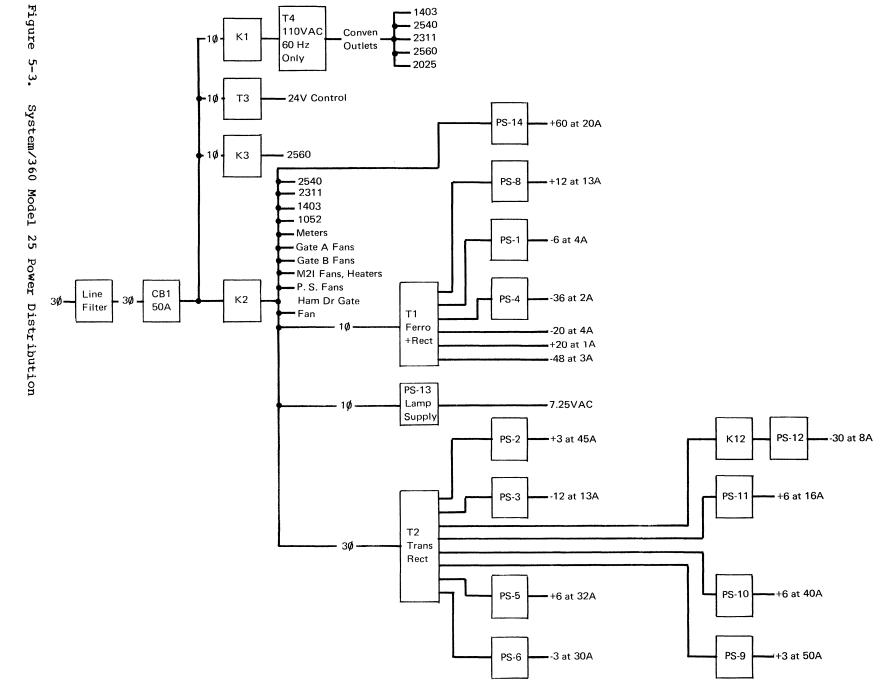

| Power Distribution                        | • 5 <b>-</b> 5         | External FieldsCPU to PR-KB         | . 6-25          |

|                                           |                        | TAControls Out                      | • 6-25          |

| Marginal Checking                         | • 5 <b>-</b> 5         | TEData Out                          | · 6-26          |

|                                           |                        | External FieldsPR-KB to CPU         | • 6-26          |

| CHAPTER 6. CONSOLE AND MAINTENANCE        |                        | TIData In                           |                 |

| FEATURES                                  | - 6-1                  | TUBranch Conditions                 |                 |

|                                           | - 0-1                  | TT Branch Conditions                |                 |

| System Control Panel                      | <i>c</i> 1             | TRTilt/Rotate Diagnostic            | • 0 20          |

| System Control Panel                      | • 6-T                  |                                     | ( ) (           |

| To 34 and some on Disculation             |                        | Register                            | • 0-20          |

| Indicators or Displays                    | - 6-1                  | TD PR-KB Diagnostic Register        |                 |

| Byte-0 and Byte-1 Indicators              | • 6-1                  | (Figure 6-16)                       | . 6-29          |

| CPU Status Indicators                     | • 6 <b>-</b> 1         |                                     |                 |

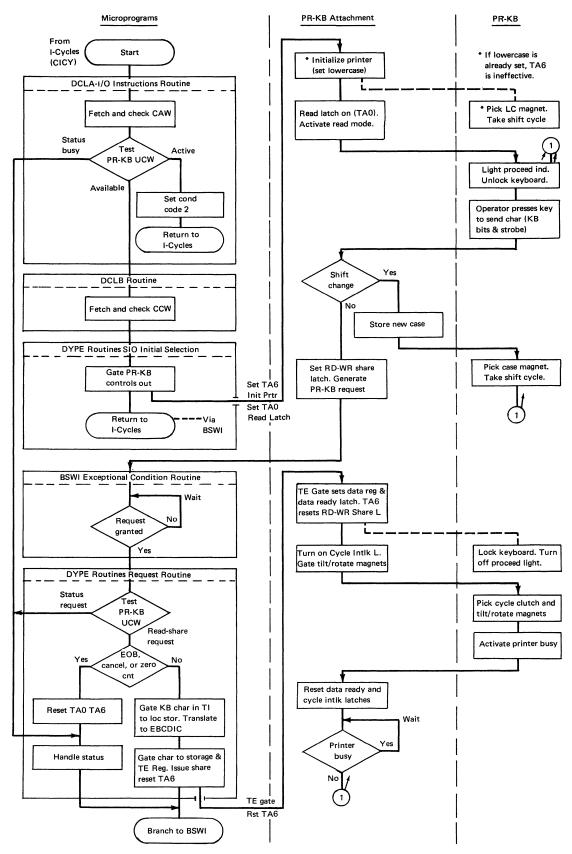

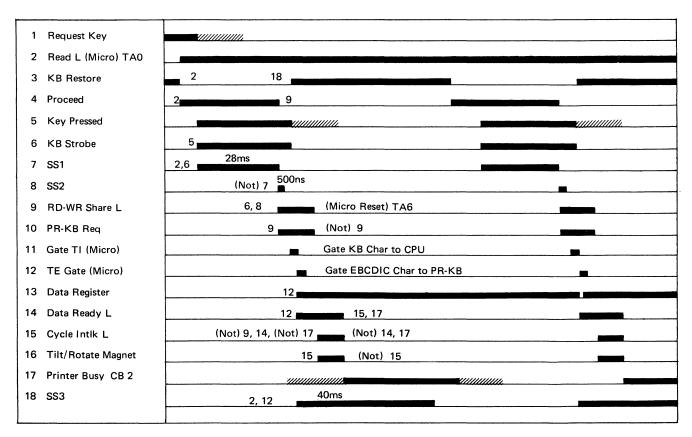

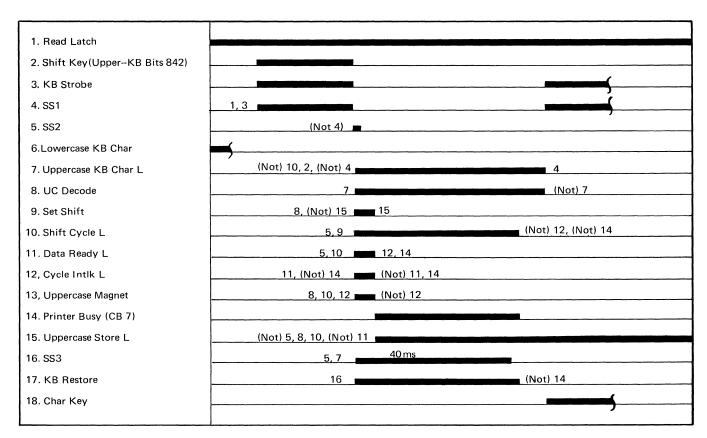

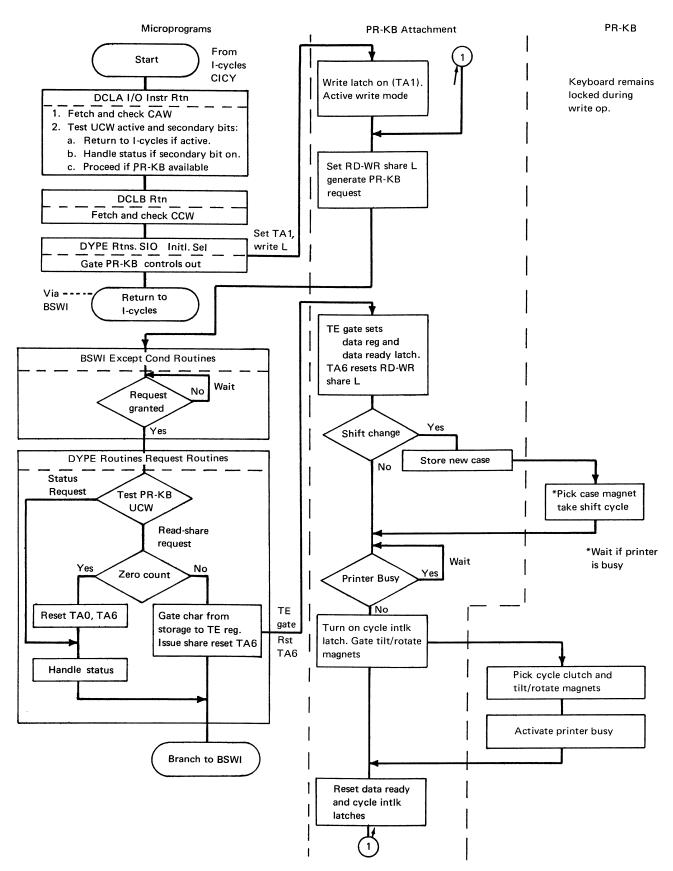

| System Checks                             | • 6 <b>-</b> 3         | Console Printer-Keyboard Theory of  |                 |

| CPU Checks                                | - 6-4                  | Operation                           |                 |

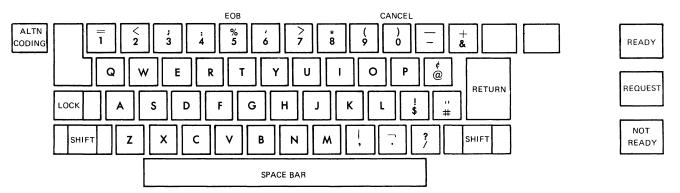

|                                           |                        | Request KeyAttention Status         | • 6-29          |

| Operator Control Section                  | • 6-5                  | I/O Instructions Routine            | • 6-30          |

| Switches and Keys                         | • 6-5                  | Start I/O with Prior Status to      |                 |

| Indicators                                |                        | Clear                               | - 6-30          |

| Indicacols                                | • 6-6                  | Start I/OPrinter Keyboard Not       | • 0-30          |

| Operator Intervention Section             |                        |                                     | c 20            |

| Operator Intervention Section             | • 6-6                  | Busy                                | • 6-30          |

|                                           |                        | Sense Command                       | • 6-31          |

| Customer Engineering Controls             | • 6 <b>-</b> 8         | Intervention Required               |                 |

| Mode Switch                               | • 6 <b>-</b> 8         | No-Operation Command                | • 6-31          |

| Operating Mode Positions (MDM             |                        | Read Command                        |                 |

| 4-4)                                      | -6-8                   | Initial SelectionRead Command.      | • 6 <b>-</b> 34 |

| Single-Cycle Mode Positions               | • 6-9                  | Keyboard Shift                      | • 6-35          |

| Alter/Display Functions                   |                        | Write Command                       |                 |

| Check Control Switch                      |                        | Initial SelectionWrite Command      |                 |

| Diagnostic Control Switch (Figure         | - 0-IO                 | and Write with ACR Command          |                 |

| 6-1)                                      | 6 10                   | PR-KB Request Routine               |                 |

| Coom and Tood Desiliens                   | • 0-TO                 |                                     | • 0-35          |

| Scan and Load Positions                   |                        | Active Bit = 0, Secondary Bit =     |                 |

| Metering Switch                           | • 6 <b>-</b> 11        | 0                                   | • 6-39          |

| Console Procedures                        |                        | Active Bit = 0, Secondary Bit =     |                 |

| Manual Display of Core Storage .          | <b>-6−1</b> 2          | 1                                   | • 6-39          |

| Active Bit = 1, Secondary Bit =                                                                                                    | Ready 6-47                              |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1 6-40                                                                                                                             | Not Ready 6-47                          |

| Active Bit = 1, Secondary Bit =                                                                                                    | Alternate Coding (AITN CODING) 6-47     |

| 0 6-40                                                                                                                             | End-of-Block (EOB) 6-47                 |

| Read Share Request 6-40                                                                                                            | Cancel 6-47                             |

| Read Operation Ending Procedure6-41                                                                                                | PR-KB Alter/Display (on CPU             |

| CR/LF Ending Routine 6-41                                                                                                          | Console)6-47                            |

| Function Cycle $\dots \dots \dots$ |                                         |

| Write Share Request 6-42                                                                                                           | PR-KB Alter/Display Facility 6-47       |

| Write Operation Ending Procedure .6-42                                                                                             | ·                                       |

| Case Shift During Write                                                                                                            | Description and Operation 6-47          |

| Operation 6-42                                                                                                                     | Setup 6-47                              |

| Common Interrupt Routine 6-43                                                                                                      | Addressing 6-48                         |

| Test I/O Command (PR-KB)6-44                                                                                                       | Execution of Alter and Display 6-48     |

| Active Bit = 1, Secondary Bit =                                                                                                    | End Operation 6-48                      |

| 0 6-44                                                                                                                             | Message Formats 6-49                    |

| Active Bit = 1, Secondary Bit =                                                                                                    | Alter Storage 6-49                      |

| 1 6-44                                                                                                                             | Display Storage 6-49                    |

| Active Bit = 0, Secondary Bit =                                                                                                    | Errors 6-49                             |

| 1 6-44                                                                                                                             |                                         |

| Active Bit = 0, Secondary Bit =                                                                                                    | PR-KB Alter/Display Microprogram        |

| 0 6-44                                                                                                                             | Routine 6-50                            |

| Halt I/O Command (PR-KE) $6-45$                                                                                                    |                                         |

| Active Bit = 0, Secondary Bit =                                                                                                    | Logout 6-50                             |

| 0 6-45                                                                                                                             |                                         |

| Active Bit = 1, Secondary Bit =                                                                                                    | Machine Check Logout 6-50               |

| 0 6-45                                                                                                                             | ,                                       |

| Secondary Bit = 1, CC Flag = $1 \cdot .6-45$                                                                                       | Channel Control Check Logout 6-50       |

| Secondary Bit = 1, CC Flag = 0,                                                                                                    | •                                       |

| Active Bit = $0. \dots 6-45$                                                                                                       | Interface Control Check Logout 6-50     |

| Secondary Bit = 1, CC Flag = 0,                                                                                                    | GS Channel External Conditions6-51      |

| Active Bit = 1 6-45                                                                                                                | GT Channel External Conditions6-51      |

| 0 13                                                                                                                               | GD Channel External Conditions6-51      |

| Keys and Indicators (PR-KB)6-45                                                                                                    | Code Byte 6-51                          |

| Indicators (Figure 6-25)6-45                                                                                                       |                                         |

| Intervention Required (INTVTN                                                                                                      | APPENDIX A. MACHINE CHARACTERISTICS A-1 |

| REQD) 6-45                                                                                                                         | Power and Cooling Requirements A-1      |

| Proceed (PROCD)6-45                                                                                                                | Overall Dimensions and Weights A-1      |

| Attention (ATTN) 6-46                                                                                                              | •                                       |

| Alter/Display Indicator on CPU                                                                                                     | APPENDIX B. SPECIAL CIRCUITS B-1        |

| Console (ALTER DPLY)6-46                                                                                                           |                                         |

| Keys (Figure 6-25)6-47                                                                                                             | APPENDIX C. WORLD TRADE                 |

| Request 6-47                                                                                                                       |                                         |

| - 0-47                                                                                                                             | TNDEX                                   |

|   | microprogram<br>defined in t | list does not include mming mnemonics, which are the sections on microprogramming or in the section where they | LCW<br>LS    | Line Control Word<br>Local Storage |

|---|------------------------------|----------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|

|   | are used.                    | _                                                                                                              | Man          | Ma nua l                           |

|   |                              |                                                                                                                | MAS          | Microprogram Automation System     |

|   | ACR                          | Automatic Carrier Return                                                                                       | MDM          | Maintenance Diagram Manual         |

| • | Addr, Adr                    | Address                                                                                                        | Mem          | Memory                             |

|   | ALU                          |                                                                                                                |              | Modifier                           |

|   |                              | Arithmetic and Logic Unit                                                                                      | Mod          |                                    |

|   | AS                           | Auxiliary Storage                                                                                              | Mplx, MPX    | Multiplexer                        |

| - | Asm, Assm                    | Assembler                                                                                                      | MS           | Main Storage                       |

|   | Attn                         | Attention                                                                                                      | ms           | millisecond                        |

|   | Aux                          | Auxiliary                                                                                                      |              |                                    |

|   |                              |                                                                                                                | No-Op        | No Operation                       |

|   | BCD                          | Binary Coded Decimal                                                                                           | ns           | nanosecond                         |

|   | bpi                          | bits per inch                                                                                                  |              |                                    |

|   | BSM                          | Basic Storage Module                                                                                           | Op           | Operation                          |

|   |                              |                                                                                                                | - 1          | F                                  |

|   | CAW                          | Channel Address Word                                                                                           | Pch          | Punch                              |

|   | CC                           | Command Chain                                                                                                  | PCI          | Program Controlled Interrupt       |

|   | CCW                          | Channel Command Word                                                                                           | PFR          | Punch Feed Read                    |

|   | CD                           | Chain Data                                                                                                     | PLB          | Print Line Buffer                  |

|   | Chan                         | Channel                                                                                                        | PLBAR        | Print Line Buffer Address          |

|   |                              |                                                                                                                | PLDAR        |                                    |

|   | Char                         | Character                                                                                                      | _            | Register                           |

|   | Chk                          | Check                                                                                                          | Prgm         | Program                            |

|   | Chnl                         | Channel                                                                                                        | PR-KB        | Printer-Keyboard                   |

|   | CKD                          | Count, Key, and Data                                                                                           | Procd        | Proceed                            |

|   | Comm                         | Communications                                                                                                 | Prot         | Protect                            |

|   | CPU                          | Central Processing Unit                                                                                        | Prt          | Printer                            |

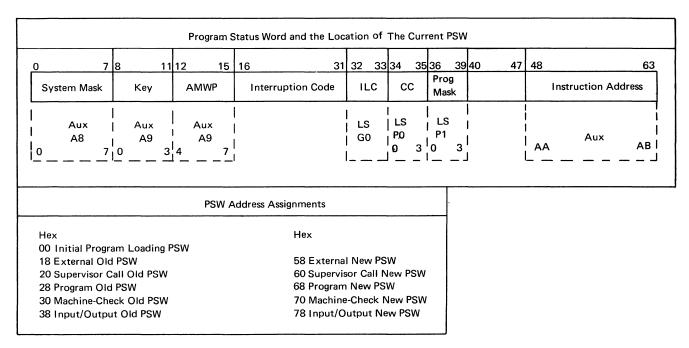

|   | CR/LF                        | Carriage Return/Line Feed                                                                                      | PSW          | Program Status Word                |

|   | CSL                          | Control Storage Load                                                                                           | Pwr          | Power                              |

|   | CSW                          | Channel Status Word                                                                                            |              |                                    |

|   | Ctr                          | Counter                                                                                                        | RBC          | Read Back Check                    |

|   | Ctrl                         | Control                                                                                                        | Rdr          | Reader                             |

|   |                              |                                                                                                                | Reg          | Register                           |

|   | DAC                          | Disk Attachment Control                                                                                        | Reqd         | Required                           |

|   | DCF                          | Disk Control Field                                                                                             | Rst          | Reset                              |

|   | Diag                         | Diagnostic                                                                                                     | RTH          | Return to Home                     |

|   | Dply, Dsply                  | -                                                                                                              | Rtn          | Return, Routine                    |

|   | DF-1, DOF-1                  | 2 1                                                                                                            | 1.0          | noculity noucline                  |

|   | EBCDIC                       | Extended Binary-Coded-Decimal                                                                                  | SAR          | Storage Address Register           |

|   |                              | Interchange Code                                                                                               | SCR          | Silicon Controlled Rectifier       |

|   | EOB                          | End of Block                                                                                                   | SDB          | Storage Data Bus                   |

|   | EPO                          | Emergency Power Off                                                                                            | SDBO         | Storage Data Bus-Out               |

|   | Ext                          | External                                                                                                       | Seq          | Sequential                         |

|   | EAC                          | EXCELIMI                                                                                                       | Ser <b>v</b> | Service                            |

|   | Нех                          | Hexadecimal                                                                                                    | SLI          | Suppress Length Indication         |

|   | пех                          | nexadecimal                                                                                                    | SLT          |                                    |

|   | I/A                          | Indelible Address                                                                                              |              | Solid Logic Technology             |

| _ |                              | Interrupt Buffer                                                                                               | SRP          | Serial Reader Punch                |

|   | I.B.                         | <b>L</b>                                                                                                       | Stor         | Storage                            |

|   | IC                           | Instruction Counter                                                                                            | STP          | Storage Protect                    |

|   | IL                           | Incorrect Length                                                                                               | Str          | Straight                           |

| _ | I/O                          | Input/Output                                                                                                   | S <b>w</b>   | Switch                             |

|   | IPL                          | Initial Program Load                                                                                           | S <b>y</b> s | System                             |

|   | Insn                         | Instruction                                                                                                    |              |                                    |

|   | Int                          | Interrupt                                                                                                      | Temp         | Temperature                        |

|   | Intlk                        | Interlock                                                                                                      | <b>T∕</b> R  | Tilt/Rotate                        |

|   | Intvtn                       | Intervention                                                                                                   |              |                                    |

|   |                              |                                                                                                                | UC           | Uppercase                          |

|   | KB                           | Keyboard                                                                                                       | UCW          | Unit Control Word                  |

|   |                              |                                                                                                                |              |                                    |

|   | IC                           | Lowercase                                                                                                      | WLR          | Wrong Length Record                |

|   |                              |                                                                                                                |              |                                    |

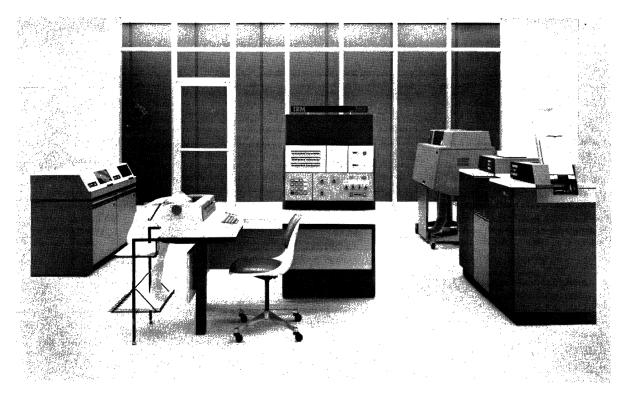

Figure 1-1. System/360 Model 25

The Model 25 (Figure 1-1) is a solid-state medium-speed data processing system. It includes the integrated attachment of a console printer-keyboard as a required feature, as well as the 2540 reader/punch, the 1403 printer (Model 2 or 7) and the 2311 disk drive. Two channel options also are available using the System/360 standard interface to attach additional I/O equipment.

The 2025 processing unit uses a core storage unit for program, control, and auxiliary storage and a 64-byte monolithic storage unit for local storage. The remaining major sections of the processor are the arithmetic and logic unit (ALU) and the clock and control circuits. Each of these units is discussed in detail under Data Flow and in Chapter 2.

# SYSTEM CONTROL

- System control is provided by circuitry that decodes and interprets control words.

- The control words are contained in the control storage area of main storage.

Cverall control of the Mcdel 25 system is by microprogram routines. The microprogram routines used for system control are a series of steps referred to as control words. How these control-word routines are constructed and placed into control storage is explained in Chapter 3.

The microprogram routines, however, provide the control words necessary for the system to perform its basic functions. These functions include:

- Entering machine-language instructions and information into the system through an input device.

- Processing the information.

- Formatting the information on an output device to produce a meaningful record.

Further control of these basic functions must be provided for the processing to result in useful information. This is achieved through the interaction of the microprograms and the machine language instructions. The machine language instructions define the operations to be performed while the microprograms actually perform the operation. For example, a simple machine language program function might be to read a card, add field 1 to

field 2, and print the results. These three instructions to the processing unit are executed by a series of microprogram steps (control words).

In this example, several different areas of the system are involved:

- The card reader that puts the data into the system

- The storage areas that hold the data and the instructions during execution

- 3. The ALU, where the fields are added

- The printer that performs the output functions.

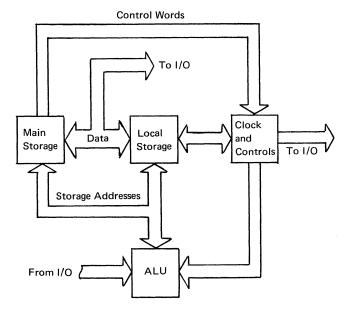

Figure 1-2 shows how some of these areas are tied together to form a system.

#### DATA FLOW

Control word decode determines actual data flow.

Actual data flow in the Model 25, for any given operation, is determined by the bit configuration of the control word being executed. A single control word is decoded to provide the gating and control necessary to perform a specific function. This could be a program storage access, an arithmetic operation, a movement of data to or from local storage, or in some cases, a combination of these.

Figure 1-2. System Data Flow

.

---

.

Control words in the 2025 are one halfword in length (16 information bits and 2 parity bits). The words are arranged in sequence to form a microprogram routine. The routines are assembled from symbolic input statements written by a microprogrammer, and are loaded into the control-storage area of main storage prior to the execution of any machine language instruction. This control-storage load is ordinarily done when the system is installed, or when changing modes of operation (between System/360 and 1400 emulator modes, for example). A breakdown of the control words and a description of the control-storage load routine can be found in Chapter 3.

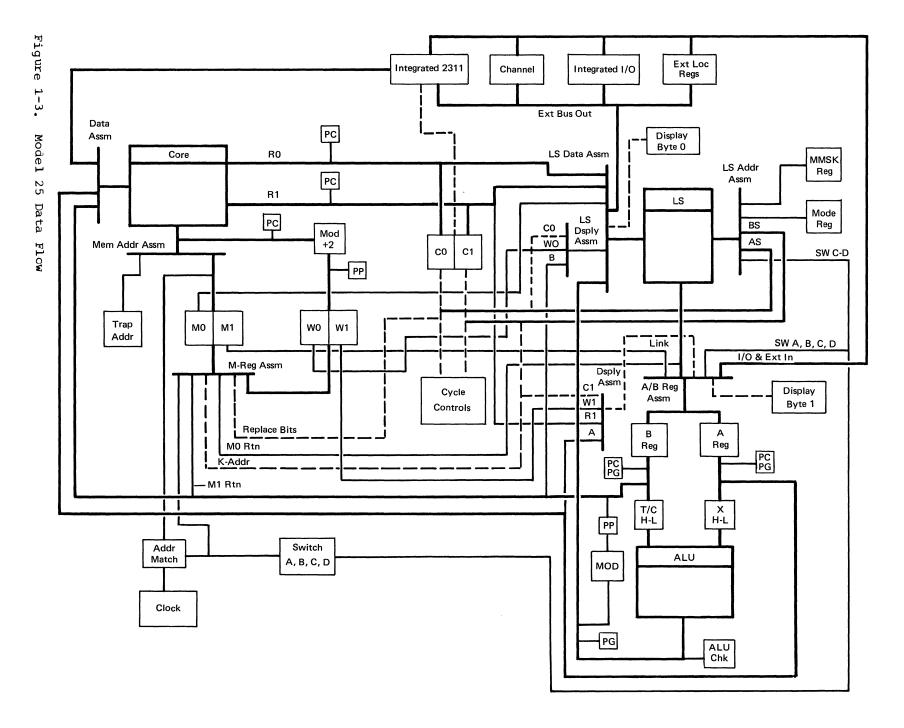

Figure 1-3 is a simplified data-flow diagram for the Model 25. The description of the functions performed by elements in the data flow is of a general nature because of the dependency on the control word decode for actual data paths.

#### MAIN STORAGE

- Mcdel 25 uses an 18-bit 900-ns storage unit.

- Storage sizes are 16K, 24K, 32K, and 48K.

The main-storage array used by the Model 25 for program, control, and auxiliary

storage is the 18-bit 900-ns M2-I. Three array sizes (16K, 24K, and 32K) are used in combination to provide the total main storage requirements of the system (Figure 1-4).

Main storage is divided into three distinct areas:

Program storage

Control storage

Auxiliary storage

#### Program Storage

This area of main storage contains the user's programs and is used for storing machine language instructions and data. Certain locations in program storage (hex addresses 0000 through 0087) are permanently assigned to ensure program compatibility within System/360, as described in the IBM System/360 Principles of Operation, Form A22-6821. The remaining locations of program storage can be used as desired.

#### Control Storage

This main storage area contains the microprogram routines necessary for control of system operations. Model 25 has 16,384 bytes of control storage. These locations are always the highest 16K block of byte addresses of the installed array(s).

| System<br>Size | Array Size                                                                   | Program Storage |                              | Control Storage |                              | Auxiliary Storage |                          |

|----------------|------------------------------------------------------------------------------|-----------------|------------------------------|-----------------|------------------------------|-------------------|--------------------------|

|                |                                                                              | Bytes           | Address Range<br>Decimal/Hex | Bytes           | Address Range<br>Decimal/Hex | Bytes             | Address Range<br>Hex     |

| 16K            | One 32K Composite Array<br>(Note 1)                                          | 16,384          | 0-16,383<br>0000-3FFF        | 16,384          | 16,384-32,767<br>4000-7FFF   | 2,048             | 0X00-7XFF                |

| 24K            | One 24K Array for<br>Program Storage<br>One 16K Array for<br>Control Storage | 24,576          | 0-24,575<br>0000-5FFF        | 16,384          | 32,768-49,151<br>8000-BFFF   | 2,560             | 0X00-5XFF &<br>8X00-BXFF |

| 32K            | One 32K Array for<br>Program Storage<br>One 16K Array for<br>Control Storage | 32,768          | 0-32,767<br>0000-7FFF        | 16,384          | 32,768-49,151<br>8000-BFFF   | 3,072             | 0X00-BXFF                |

| 48K            | One 32K Array for<br>Program Storage<br>One 32K Composite Array<br>(Note 1)  | 49,152          | 0-49,151<br>0000-BFFF        | 16,384          | 49,152-65,535<br>C000-FFFF   | 4,096             | 0X00-BXFF                |

Notes: 1. Program storage is always located in the low-order area of the composite core-storage array(s). For example, program storage for the 48K system is all of the low order 32K unit plus the low-order 16K bytes of the high-order 32K unit.

2. Control storage is always the high-order 16K bytes of the composite core-storage array(s).

Figure 1-4. Model 25 Core-Storage Allocations and Addressing Scheme

#### Auxiliary Storage

There are 1,024 bytes of auxiliary storage associated with each main storage array of 16K byte locations. (256 bytes are associated with each 1000 hexadecimal addresses.) Model 25 has a maximum of 4096 bytes in a 48K system (Figure 1-4).

This storage area is used for the sixteen general purpose registers, four floating-point registers, multiplexer channel UCW storage, I/O translation tables, multiply and divide tables, and other microprogramming requirements.

As with other System/360 models, only limited areas of auxiliary storage (general and floating-point registers) are normally accessed by the user's program. Other defined locations are used only by the microprogram routines. Undefined areas are available for expanding microprogram functions.

Information read from main storage is placed on the storage data-out lines (via the storage data register) and enters the LS data assembler or the control register (C-register). Control words are entered into the C-register and decoded at its output to bring up the gating and branching

lines necessary to perform the functions indicated by the control word.

Data and information from main storage is sent to the LS data assembler. Entry into local storage or an external facility from the assembler is controlled by the decode of the control word being executed.

#### M-REGISTER AND M-REGISTER ASSEMBLER

Main storage is addressed from the M-register, a 16-bit register in the processing unit. The M-register is composed of two single-byte registers, MO and M1, which are fed from the M-register assembler where the actual addresses are constructed.

Control-storage addresses require a slight change in the addressing scheme because of the location of control storage for the different program storage sizes. Regardless of storage size, control storage is the upper 16K block of byte addresses.

For branch unconditional, branch and link, and return control words, the two high-order bits of MO are forced to a specific pattern, corresponding to the

total storage size, to address control storage.

Auxiliary storage addressing is similar to program storage addressing except that an additional signal (USE AUX STORE) is generated. Control-word bit structure is used to generate this signal.

#### STORAGE ADDRESS ASSEMBLER

The output of the M-register feeds the storage address assembler. This assembler, in turn, feeds the main storage addressing circuits. The assembled address is modified and then placed in the W-register. The updated address in the W-register provides a means of stepping to the address of the next sequential control word.

The storage address assembler is used also for address substitution in case of a trap (a forced address to execute a control-word routine other than the next sequential word). The contents of the assembler are replaced with the starting address of the trap routine, and the M-register is left unchanged. This allows the next control-word address to be saved. The trap routine stores the contents of the M-register so that the correct control-word sequence can be resumed when the trap routine is completed.

The forced trap address is modified +2 and placed into the W-register from the assembler. Normal control-word stepping occurs during execution of the trap routine.

## W-REGISTER

The W-register is a 16-position register that holds an updated (+2) address of the control word presently being executed. It retains this address during program or auxiliary storage access cycles.

The output of the storage address assembler and M1 register bit 7 are presented to a modifier circuit for address modification of +2 and stored in the W-register. The modified output is then presented to the M-register assembler as the address of the next sequential control word, if the next sequential word is to be executed. In some branching cases (see Chapter 3), only part of the W-register output is gated to the M-register.

# C-REGISTER

The C-register is a 16-bit register that is fed from the main storage data-out lines. It is used to hold the control word being

executed. The C-register output decode circuitry interprets the control-word bits and conditions the gates, lines, and data paths that determine the operation of the CPU as required for that particular control word.

<u>Cycle Controls:</u> These circuits include the system clock, elements that decode the control words to direct the flow of information through the system, and elements that provide data paths for the information.

#### LOCAL STORAGE

- Local storage is provided by the Model B150 high-speed (180-nanosecond) monolithic stack.

- The unit contains sixty-four 1-byte locations on a single SIT card.

- Readout is non-destructive.

Local storage as used in the Model 25 is separated from main storage, and is composed of sixty-four 9-bit (including parity) bytes. (A tenth bit for each byte is available but not used.) These locations are used for intermediate storage for factors to be operated on by the Arithmetic and Logical Unit (ALU): the operation bytes, instruction counter, register operand, program mask, backup locations, data addresses for the channel and integrated I/O devices, and work areas.

Local-storage locations are loaded by control words so that required storage addresses and problem or microprogram factors are made available without readdressing main storage.

Data stored in local storage is used by control words to perform some problem-program function.

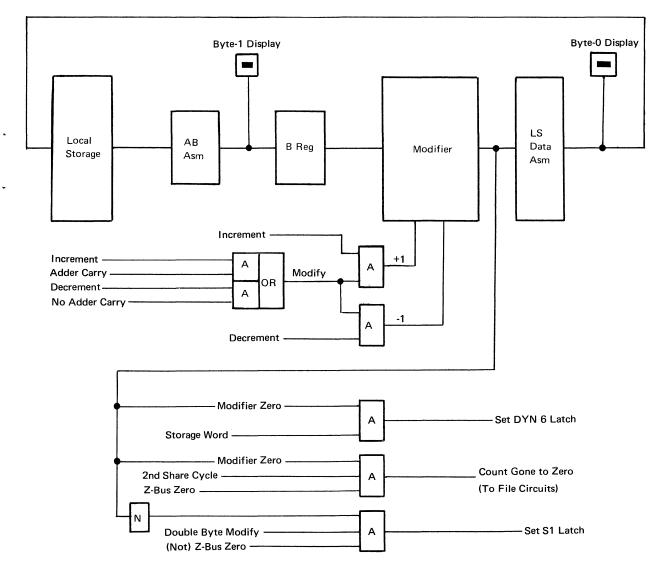

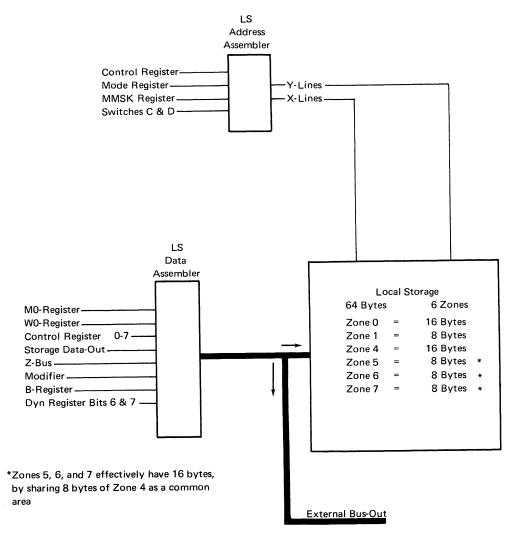

Data enters local storage from the LS data assembler and exits on the LS bus-out lines. Output is to the A/B register assembler or the M-register assembler, depending upon the control word being executed.

During the execution of microprogram (control program) steps, local storage can accept or read out a byte of information as many as four times within the primary system cycle of 900 nanoseconds.

#### Local-Storage Data Assembler

The LS data assembler is a group of gating circuits that can receive a byte of data from several sources. Among the sources are the storage data bus lines, the

MO-register, the ALU modifier, the WO-register, the B-register, and the Z-bus. The control word being executed determines which of these is used. (W or B inputs are used for manual display purposes.)

The output of the LS data assembler is presented to local storage or to external facilities.

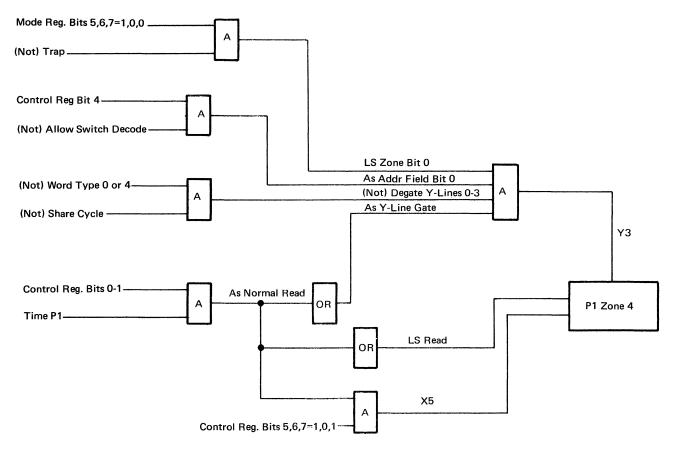

#### Local-Storage Address Assembler

Local storage is addressed through the LS address assembler. The outputs of this assembler are the X- and Y-drive lines for local storage. Local-storage addresses are usually made up from the outputs of the C-register, combined with the MODE register. However, when a trap occurs, the MMSK register overrides the MODE register and combines with the AS- or BS-field to form the LS address. The switches on the console also can be used to address local storage.

#### A/B REGISTER ASSEMBLER

The A/B register assembler is a group of gating circuits that can receive data bytes from local storage, external facilities, and a number of other sources. Data selection and gating for the assembler is determined by the control word decode or the function being performed. The output of the assembler is to the A-register and B-register.

# ARITHMETIC AND LOGICAL CONTROL CIRCUITS

All arithmetic and logical data manipulations are performed by these circuits. The A-register and B-register provide the input to the ALU; however, the control word decode determines the manner in which the data is presented and the operation performed.

Refer to <u>Chapters 2 and 3</u> for further information concerning ALU operation for the various control words.

#### INTEGRATED I/O AND CHANNELS

The integrated attachments for the Model 25 are:

IBM 1052 Model 7 Console Printer-Keyboard

(PR-KB)

IBM 1403 Printer Model 2 or 7

IBM 2311 Disk Storage Drive Model 1 (up to four)

IBM 2540 Card Read-Punch Model 1.

These units, together with the 2025 processing unit, make up a compact and versatile data processing system.

The PR-KB, 1403, and 2540 are permanently assigned to channel 0. The 2311s are permanently assigned to channel 1. In addition, the Model 25 can have a System/360 standard interface optional feature that may be either a byte-mode (multiplexer) channel assigned as channel 0 or a burst-mode (selector) channel assigned as channel 1. Circuitry for these I/O attachments and the channel feature is contained in the central processing unit.

## EXTERNAL FACILITIES

The external facilities (registers and lines) are source and destination locations that are not within local storage. That includes all locations external to local storage that can be addressed by a control word. This does not include the A, B, C, M, or W registers, or any main storage location.

Some of the more prominent externals are the S-register, MMSK register, BC-Facility, DYN register, and the MODE register. Each of these is discussed in detail in <a href="Chapter">Chapter</a> 2.

#### CPU CLCCK

- The basic timing pulses for the IBM 2025 (except core storage) are generated by the CPU clock.

- A crystal oscillator drives a five-stage latch ring.

Five latches are connected to form an overlapped latch ring for creating the basic clock pulses (MDM 4-11). A free-running crystal oscillator provides the pulses that drive the latch ring circuit.

The latch ring is reset with the clock-5 latch on. For the clock to be started, the clock-start latch must be turned on. This allows clock-1 latch to turn on with the next oscillator pulse. The following (not) oscillator pulse ANDed with clock 1 turns clock-5 latch off. The next oscillator pulse ANDed with clock 1 and (not) clock 5 turns clock 2 on. This sequence continues through the latch ring. The result is five overlapping clock pulses that develop ten overlapping (TO through T9) timing pulses (MDN 4-11). The complete clock cycle takes 900 nanoseconds.

The 180-nanosecond T0-through-T9 pulses are used to develop 90-nanosecond P-pulses (P1, P3 through P8). The P pulses are developed near the logic area that uses the actual pulse; this minimizes ringing and noise.

#### CLOCK CONTROL

- The clock operates as long as the clock-start latch is on or the inhibit clock stop line is active.

- The clock always stops with only clock-5 latch on.

For the clock to be started, the start interlock latch must be turned on (MDM 4-11). Once the start interlock latch turns on, the next (not) oscillator pulse turns the clock start latch on. This conditions the clock-1 latch to turn on with the following oscillator pulse. Once the clock start latch is set, the clock operates until the clock start latch is reset.

The clock start latch is reset by:

1. the machine reset switch line being active

- 2. the hard stop latch being on

- 3. the clock-stop pulse line being active.

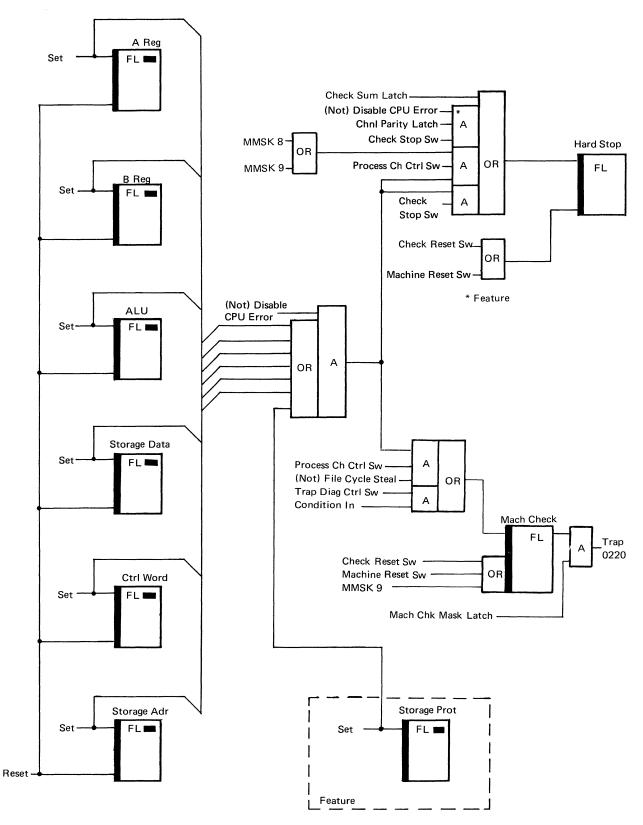

The machine reset switch line is active during the power-on sequence or when the system reset, load, or control storage load key is pressed. The hard-stop latch is set by check control switch at the check-stop position and any error occurring, or by an incorrect checksum being recognized. The clock-stop pulse is activated by several conditions as shown on MDM 4-11.

When the machine reset switch line is active, the entire clock and the control latches are reset immediately. This turns the clock-5 latch and the clock-off latch on.

The clock-off latch is turned off the first time the clock-1 latch is turned on after the clock-start latch is set. When the clock is conditioned to stop at the end of a cycle, the clock-off latch turns on. This blocks the T8 and T9 lines from being active with the clock stopped (clock-5 latch on). Also the line clock-off is activated, which conditions many of the manual operations.

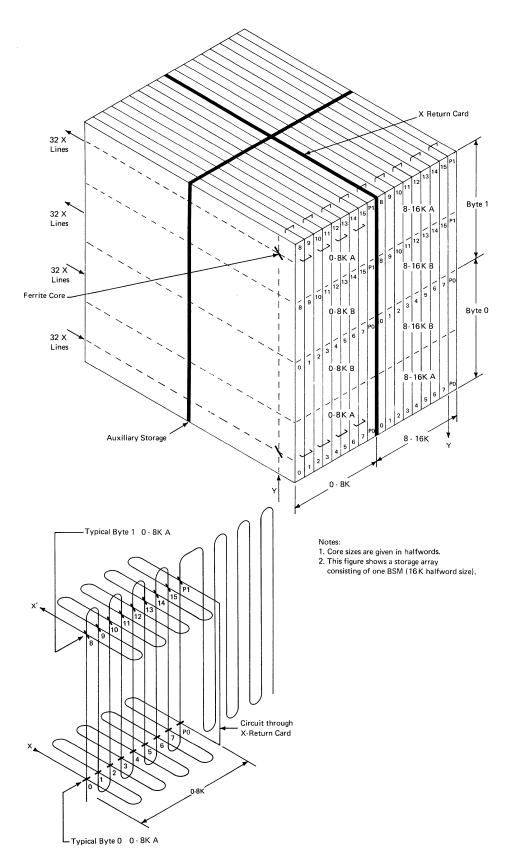

# CORE STORAGE

The M2I Basic Storage Module (BSM) operating at 900 nanoseconds is used in the 2025. Depending on the amount of core storage installed, one or two BSMs are used. The BSM(s) is a separate unit installed within the 2025 and connected to the 2025 control and data lines via a core storage interface cable. The BSM is available in three sizes: 8K, 12K, or 16K halfwords. (The size of the BSM also depends on total storage capacity of the system.)

Note: In this publication, the 16K BSM is used to describe the storage theory, and all references to BSM are for 16K.

Unless otherwise indicated, all reference to core size is by addressable halfwords, both in this description and in the ALDs. Whenever core storage is read out, two bytes (18 bits: 16 data plus 2 parity) are read out and two bytes are written back. A read call cycle is divided into two portions: read and write. A write always occurs after a read in the 2025. Refer to MDM 3-3 for the overall data flow of the core storage unit and the associated 2025 functional units.

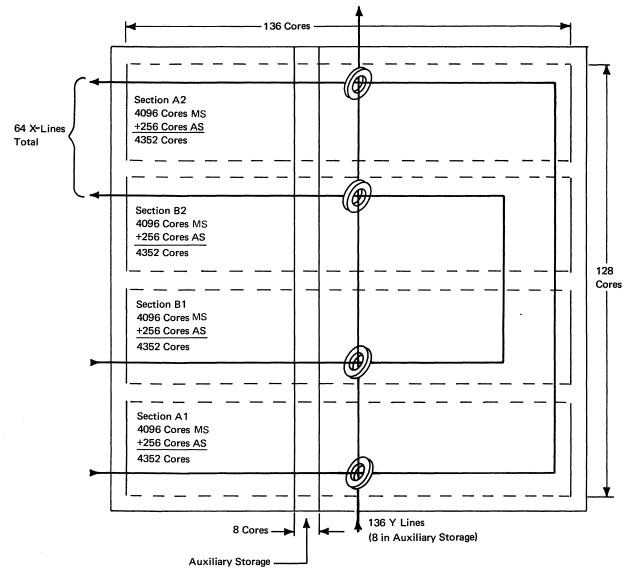

Figure 2-1. Storage Array

Figure 2-2. Core Plane

# CORE ARRAY (8K HALFWORDS)

- An 8K core array consists of nine discrete core planes.

- Two 8K core arrays make up one 16K BSM.

- Three wires pass through each core.

The arrangement of one BSM is shown in Figure 2-1. An 8K array is composed of nine core planes (one-half of a 16K BSM). Each plane is constructed of a plastic frame approximately 6-1/2 inches square. The frame is crossed horizontally by 128 X-lines and vertically by 136 Y-lines, with a ferrite core located at each intersection

of the lines. Of the 17,408 cores in each plane, 16,384 are used for main storage (control and program) and 1,024 for auxiliary storage. Each core plane consists of four sections A1, B1, B2, A2 (Figure 2-2).

Each X-line winding travels through one section of nine planes before crossing to another section of the same nine planes via an X-return card at the end of the array. The X-return card contains printed lines that carry current from the X-line winding in one section of the array to the X-line winding in another section. The winding pattern of the array is such that alternate X-line winding current is driven from

opposite ends of the core plane. An example of this can be seen in MDM 4-27, Part 4.

The Y-line winding starts at either the top (side C) or the bottom (side A) of the array and winds through each plane as shown in Figure 2-1 or Part 4 of MDM 4-27. Therefore, each Y-line winding crosses any X-line winding at 18 points: two points on any one plane. This provides a selection of 18 bits for any address.

A combined sense/inhibit line winding in each section of one plane is wound parallel to the X-line winding and passes through each core in that section.

Two 8K arrays are used to form one 16K BSM. Two, three, or four 8K arrays are possible, depending on the amount of core storage installed. In one 16K BSM, the two

8K arrays share a common set of Y-line windings. Each winding passes through all 18 planes. The 16K BSM uses two sets of X-line windings: one for the 0-8K halfword addressable array and the other for the 8-16K halfword addressable array (Figure 2-1 or MDM 4-27 Part 4).

In each 8K array the X-line windings are divided into two groups, each group containing 32 lines. Thirty-two of these lines pass through section A1 and A2, while the remaining 32 pass through sections B1 and B2. A core in section A1 or B1 is a byte-0 bit, while a core in section A2 or B2 is a byte-1 bit.

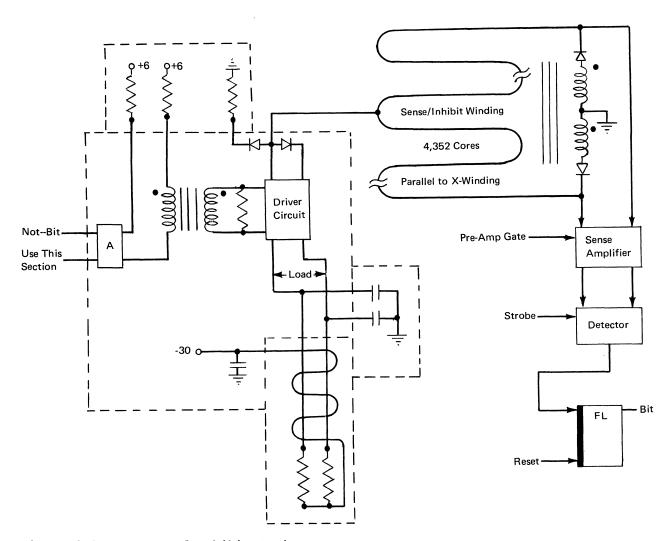

Figure 2-3. Sense and Inhibit Logic

#### COMMON SENSE/INHIBIT

- Use combination sense/inhibit winding.

- Each sense/inhibit winding goes through 4352 cores, parallel to X-line winding.

- The sense/inhibit windings sense pulses caused by cores changing status during the read portion of the cycle.

- The sense/inhibit windings are used to prevent cores from changing 0 status during the write portion of the cycle.

One 16K BSM contains eight sections of nine planes each, providing a total of 72 combined sense/inhibit windings. A sense/ inhibit winding is parallel to the X-line winding, going through 4,352 cores in a single core plane. There are four sense/inhibit windings in each core plane. During the read portion of a storage cycle, a core that switches status (logical 1 to logical 0) induces a pulse onto the sense/inhibit winding. This pulse is amplified by a sense amplifier (Figure 2-3). If a core does not switch status (remains at a logical 0), no pulse is induced onto the sense/inhibit winding. A differential amplifier senses the change or difference in current on the sense/inhibit winding.

To prevent unwanted noise from being amplified in other storage sections, only the sense/inhibit windings output for the two sections of the BSM being addressed is gated to the sense amplifiers. If the byte being sensed (one section) is to be regenerated during the write portion of the storage cycle, a strobe pulse (generated from the storage clock) gates the sense amplifier output to the storage data register (MDM 4-27 Part 5). Sensing a logical 1 in a core causes the data-bit latch for that position to set, while a logical 0 does not set the data-bit latch.

During the write portion of the cycle, if a bit is to be stored in a core, the core is switched by the effect of the coincident X- and Y-line winding currents. Inhibit current is allowed for a bit when the corresponding data-bit latch in the storage data register is not set.

Because inhibit current flows in the opposite direction of the X-line winding write current, that position does not switch (stays a logical 0).

SAR bits 1 and 14 are used to select the group of sense/inhibit windings to be gated to the storage data register. SAR bits 1 and 14 also gate the inhibit drivers to the same sensed inhibit windings during the write portion of the storage cycle.

#### STORAGE CLOCKS

- Each BSM has a separate clock.

- The clock consists of two delay lines.

- Both clocks are started by a read call.

Each BSM in the 2025 has a separate clock, allowing the storage unit to operate independently of the 2025 once a read call starts a storage cycle (MDM 4-27 Part 1). Each clock is composed of two 250-nanosecond delay lines tied together. The delay lines are tapped at 25-nanosecond intervals. These outputs are ANDed and ORed together to form the necessary signals to read out and write into the core storage array.

If core-storage size requires two BSMs, both core storage clocks run at the same time. Only one BSM is allowed to read out or write in on any one storage cycle. This is accomplished by allowing only the current drivers in the selected BSM to drive the storage array. The desired BSM is selected by the high-order bit of the addressing network (storage address lines), which also blocks the control lines for the other BSM.

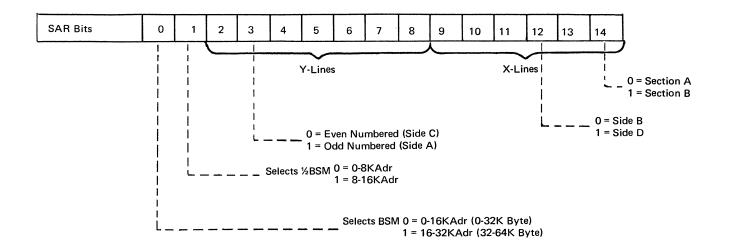

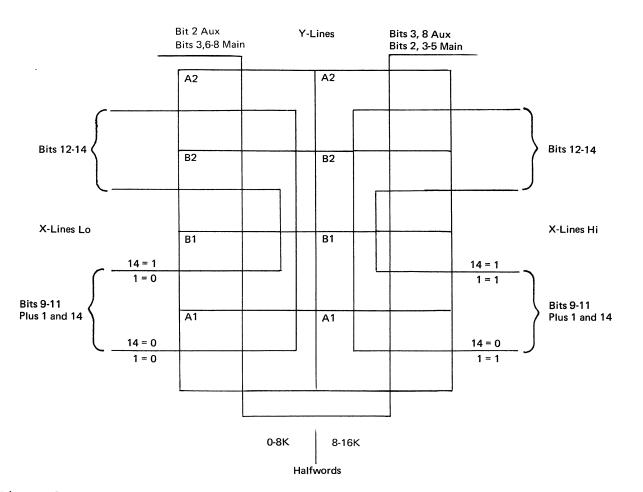

### STORAGE ADDRESSING

- Fifteen address lines are decoded to select the desired address.

- Two bytes are read out for each address.

Fifteen storage address (SAR) lines are routed from the 2025 to each BSM. These lines are decoded to select the corrected BSM and the correct X- and Y-lines to read out and write into the cores selected for a given address (Figure 2-4). The SAR lines are set at P4 time of a 2025 clock cycle, and the 'read call' latch is set at T5 time (MDM 4-27 Part 1). This allows the address lines to be valid by 10 nanoseconds after 'read call' initiates a storage clock cycle.

The decode of the SAR lines for the X-and Y-lines is shown on MDM 4-27 Parts 2 and 3. The actual line selected for any given address is shown on MDM 4-27 Part 4.

If auxiliary storage is selected, the 'main aux control' latch (MDM 4-27 Part 2) is turned off. Normal X-line decode is done while the Y-line decode is limited to SAR bits 2, 3, and 8, as shown on MDM 4-27 Parts 3 and 4. SAR bit 0 selects the BSM to be used.

Figure 2-4. SAR Lines

Figure 2-5. Current Sources

# CURRENT SCURCES

- Current sources supply drive current to the X- and Y-line windings.

- The drive current comes from the secondary winding of a transformer.

- The primary windings of the source transformer are driven by transistors.

- Selection of current source allows current to flow only in the selected BSM.

Each current source consists of a transformer secondary winding (Figure 2-5). The primary winding of each transformer is