| 952-5497-2  | IBM NO                                                      | 66-584-002           |                                       |

|-------------|-------------------------------------------------------------|----------------------|---------------------------------------|

|             |                                                             |                      | · · · · · · · · · · · · · · · · · · · |

| SYSTEM/4 PI | ORIGINATING                                                 | GROUP Department 584 |                                       |

| ENGINEERING | CONTENT APP                                                 | ROVED BY             |                                       |

| DESCRIPTION |                                                             | J Beth               |                                       |

| MODEL EP    | hadridinala ik saaltaassinininkota saaninalain sori-Garandi | f j ow               |                                       |

|             | CONTRACT NO                                                 |                      |                                       |

|             | DATE                                                        | November 7, 1966     |                                       |

|             |                                                             | A. Company           |                                       |

|             |                                                             |                      |                                       |

## IBM CONFIDENTIAL

This document contains information of a proprietary nature. ALL INFORMATION CONTAINED HEREIN SHALL BE KEPT IN CONFIDENCE. None of this information shall be divulged to persons other than: IBM employees authorized by the nature of their duties to receive such information, or individuals or organizations authorized by the Federal Systems Division in accordance with existing policy regarding release of company information.

#### PREFACE

This Engineering Description has been prepared for applications engineers and Model EP users. It provides a broad based introduction to the Model EP architecture, support software and to the concepts of microprogramming. The technologies used in Model EP and the logical design of the CPU and Multiplex Channel are described. Much of the information in this document is merely descriptives of design and implementation techniques and does not constitute a commitment to deliver equipment or services in exact conformance to that described.

A companion document, <u>Model EP Function Specification</u>, #66-584-001, describes the functions and features of System/4 Pi Model EP and particularizes them in relation to System/360.

These documents supersede and replace the previous Model EP,

Product Description (3-001-56). In addition to an expansion of the information provided, these documents include numerous revisions. Most of these are changes in detail rather than in concept but they are too numerous to identify individually.

This document has been issued in preliminary form. It is incomplete and may contain some errors of detail. It will be completely revised and reissued early in 1967.

# Table of Contents

| . • |       |                                                                                                                                                                                                                                                                      | Page |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.0 | Intro | duction                                                                                                                                                                                                                                                              | 1    |

|     | 1.1   | System/360 Compatibility                                                                                                                                                                                                                                             | 1    |

|     | 1.2   | Microprogramming                                                                                                                                                                                                                                                     | 2    |

|     | 1.3   | Features                                                                                                                                                                                                                                                             | 2    |

| 2.0 | Arch  | itecture                                                                                                                                                                                                                                                             | 4    |

|     | 2.1   | General Concepts                                                                                                                                                                                                                                                     | 4    |

|     | 2.2   | System/360 Compatibility                                                                                                                                                                                                                                             | 4    |

|     | 2.3   | System Structure                                                                                                                                                                                                                                                     | 6    |

|     |       | 2.3.1 Main Storage 2.3.2 Central Processing Unit 2.3.3 Arithmetic and Logical Unit 2.3.4 Program Execution 2.3.5 Protection Features 2.3.6 Timer Feature 2.3.7 Direct Control Feature 2.3.8 Multisystem Operation 2.3.9 Input and Output 2.3.10 System Control Panel |      |

|     | 2.4   | Instruction Sets                                                                                                                                                                                                                                                     | 32   |

| 3.0 | Softw | are                                                                                                                                                                                                                                                                  | 33   |

|     | 3.1   | Language Translators                                                                                                                                                                                                                                                 | 33   |

|     | 3.2   | Program Checkout System (Simulator)                                                                                                                                                                                                                                  | 34   |

|     | 3.3   | Service Programs                                                                                                                                                                                                                                                     | 35   |

|     | 3.4   | Control System                                                                                                                                                                                                                                                       | 36   |

| 4.0 | Micro | oprogramming Concepts and Techniques                                                                                                                                                                                                                                 | 38   |

| 5 <b>.</b> 0 | Detai    | led Descr | intion                        | Page<br>39 |

|--------------|----------|-----------|-------------------------------|------------|

| 3.0          | 20001    |           |                               | 3,         |

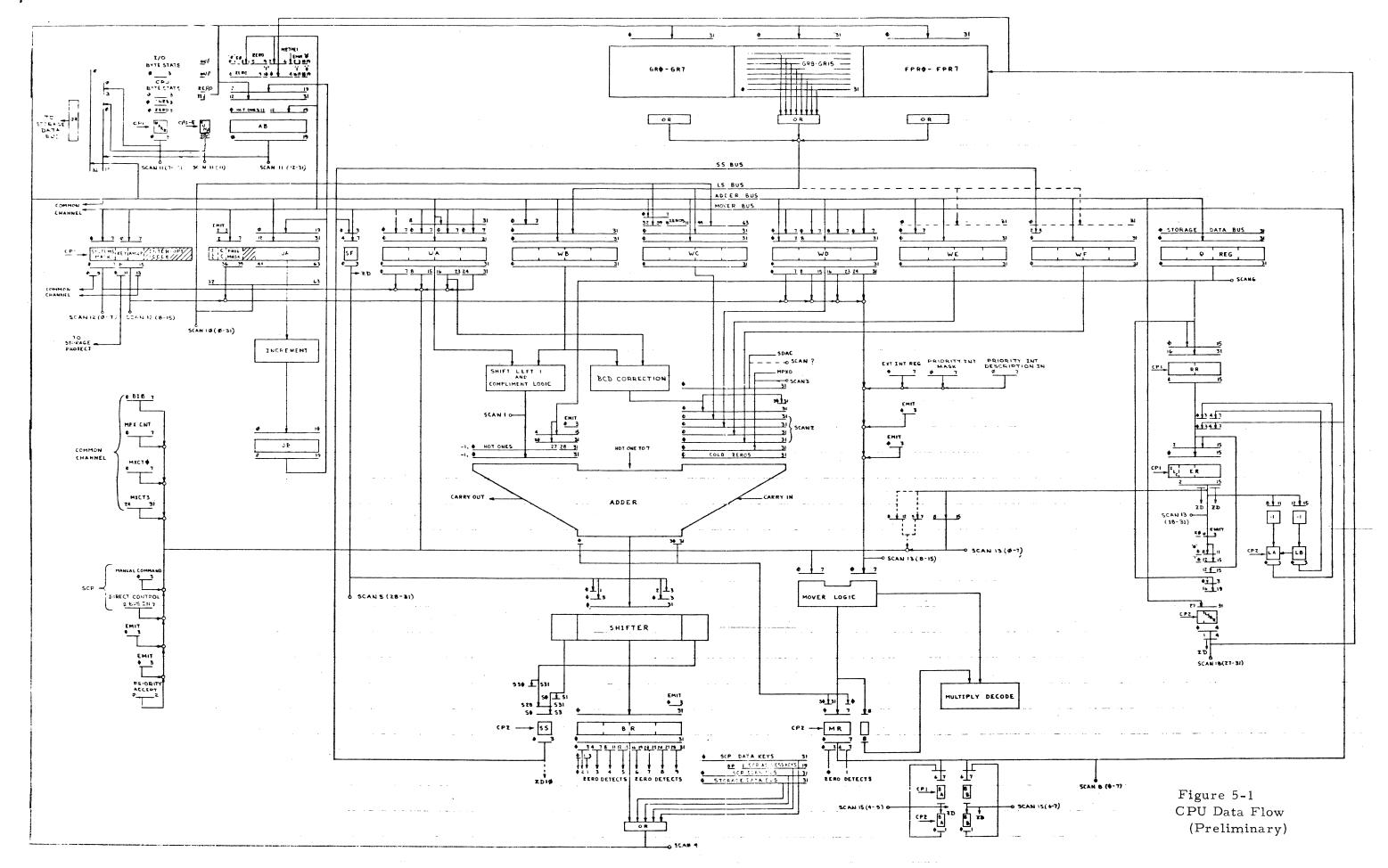

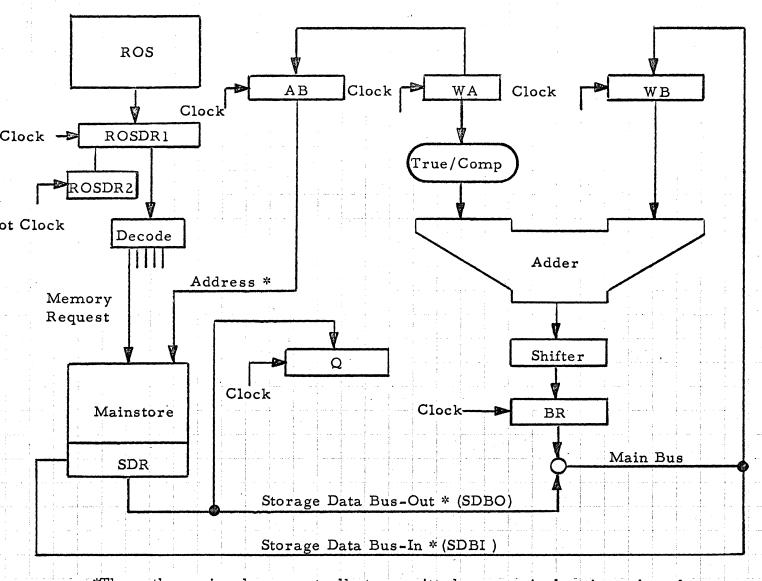

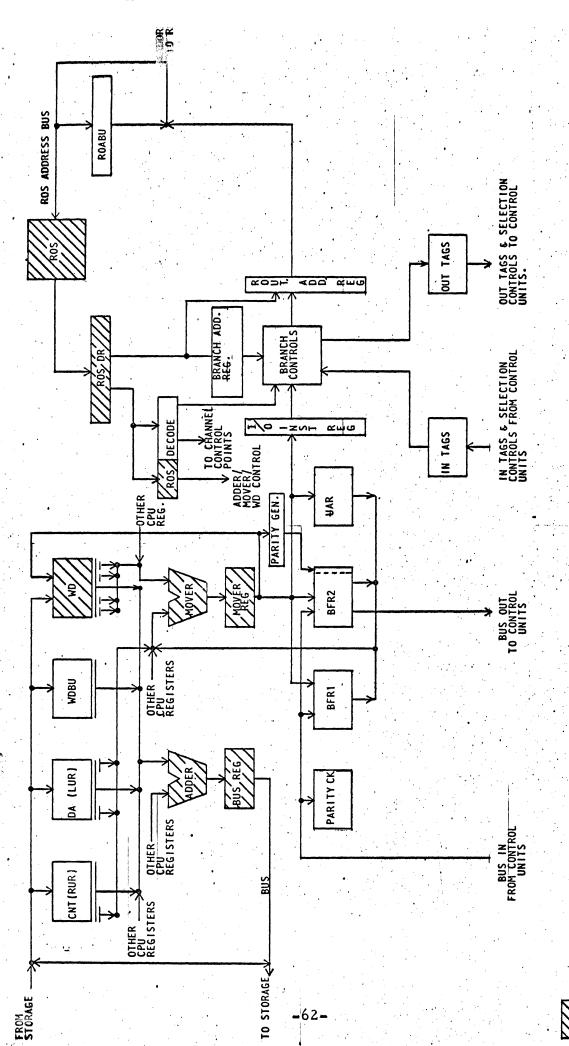

|              | 5.1      | CPU Da    | ta Flow                       | 39         |

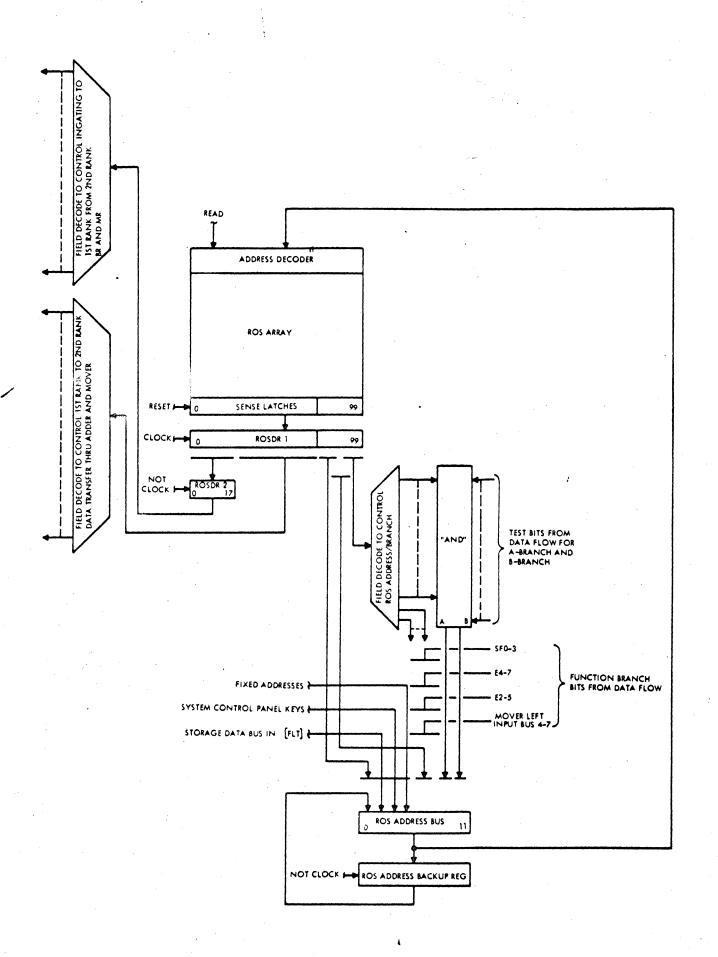

|              | 5.2      | Microp    | rogramming Control            | 43         |

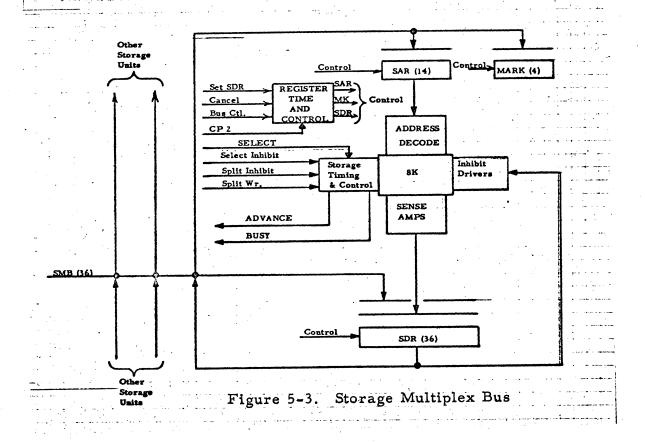

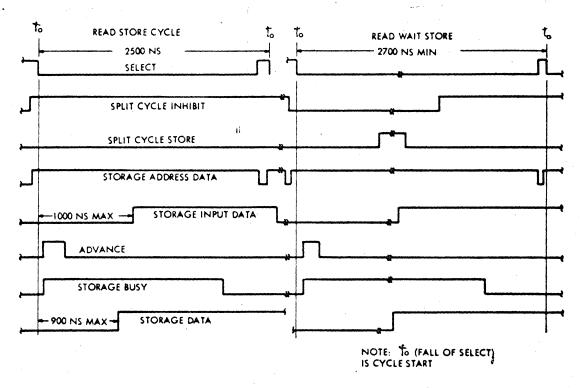

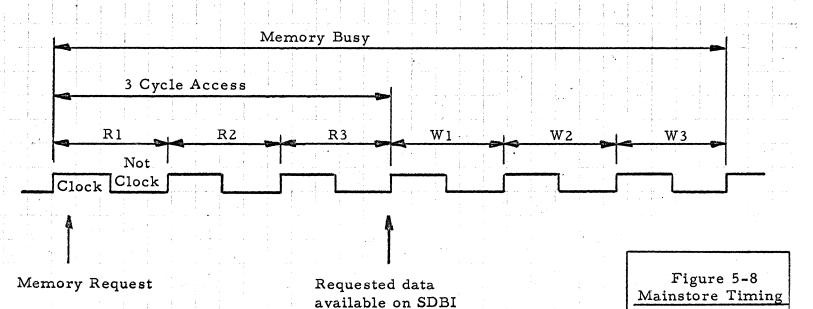

|              | 5.3      | Main St   | orage                         | 49         |

|              | 5.4      | Timing    | System                        | 51         |

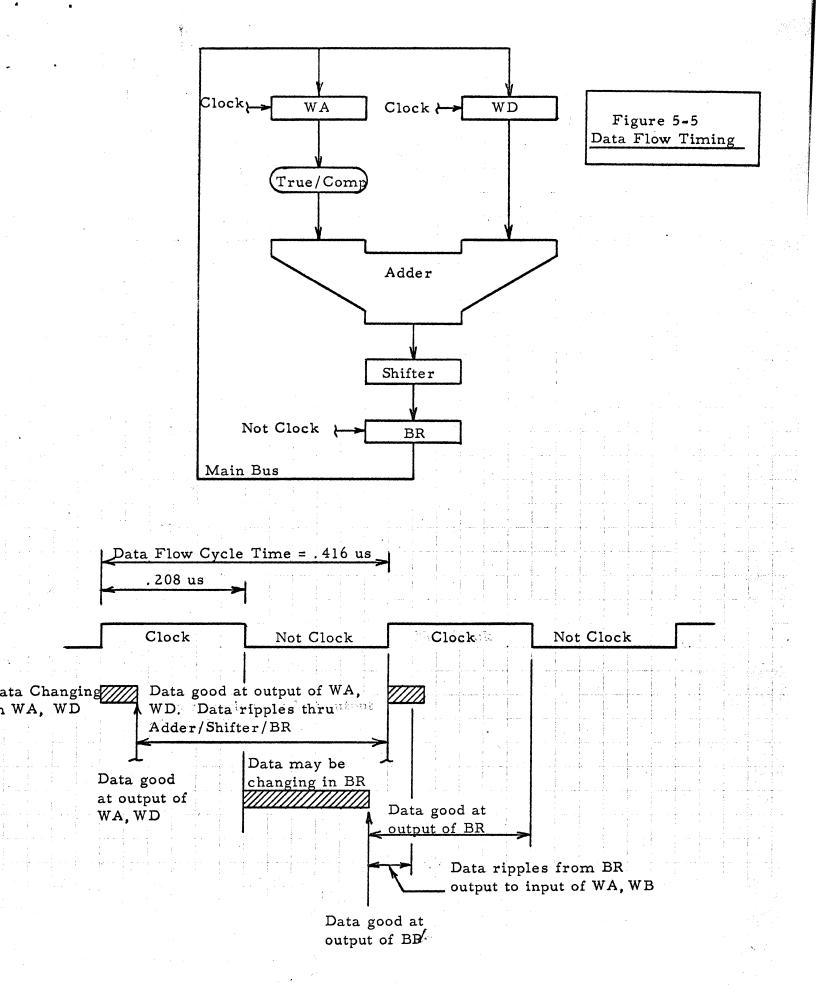

|              |          | 5.4.1     | Data Flow Timing              |            |

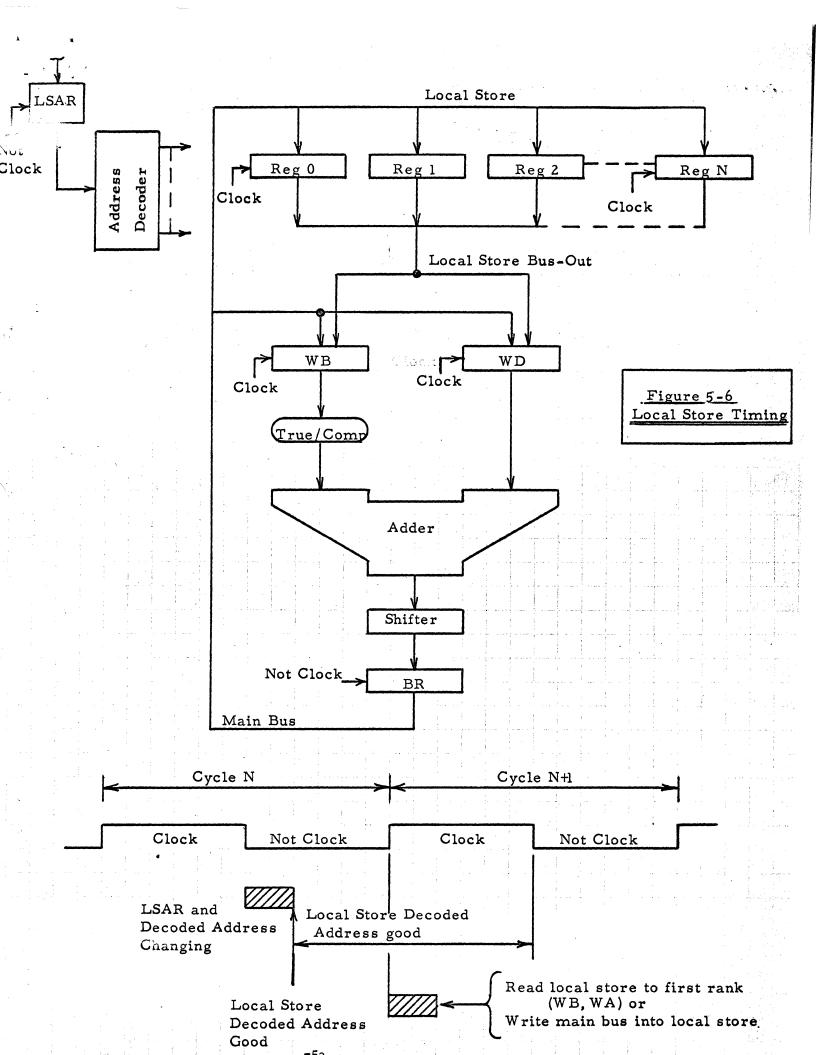

|              |          | 5.4.2     | Local Storage Timing          |            |

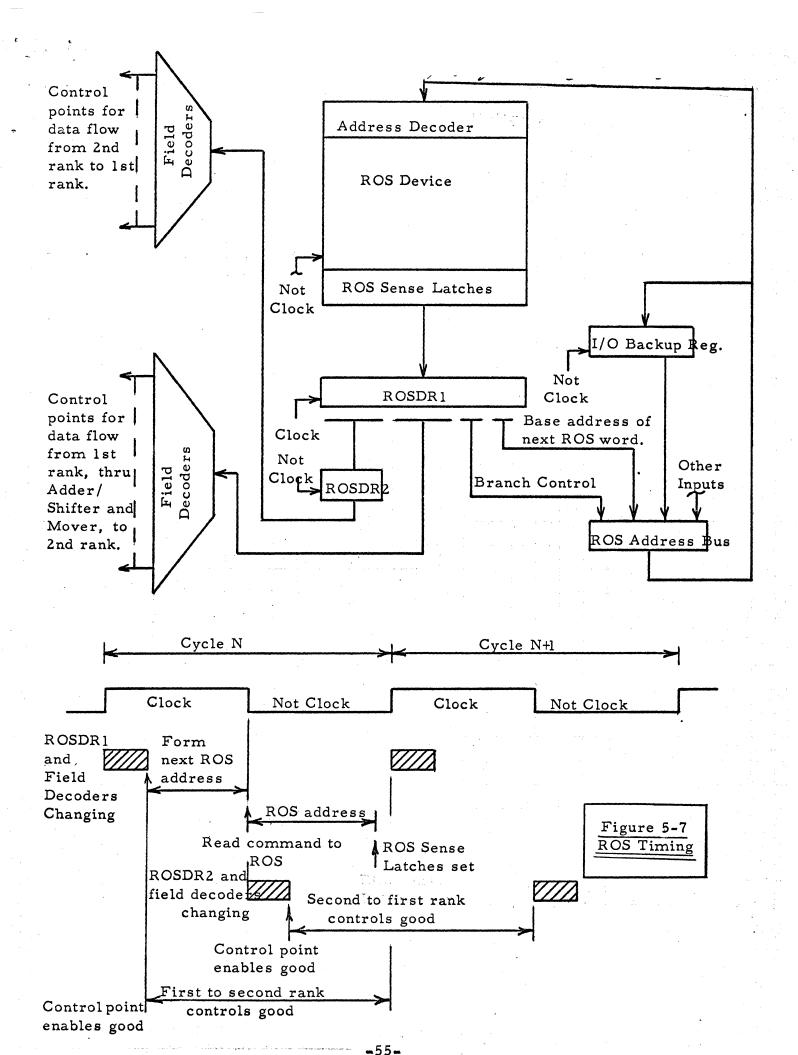

|              |          | 5.4.3     | ROS Timing                    |            |

|              |          | 5.4.4     | Main Storage - ROS            |            |

| 6.0          | Multi    | plex Chan | nel Design                    | 58         |

|              | 6.1      | Introduc  | etion                         | 58         |

|              | 6.2      | Channel   | - Control Unit Interface      | 59         |

|              | 6.3      | The Mu    | ltiplexor Channel Data Flow   | 61         |

|              | 6.4      | Multiple  | exor Channel Control          | 63         |

|              |          | 6.4.1     | Micro-Control                 |            |

|              |          | 6.4.2     | Hardwired Control             |            |

|              | ·. · · · | 6.4.3     | Break-In                      |            |

|              |          | 6.4.4     | Break-Out                     |            |

|              | 6.5      | Start In  | put/Output                    | 65         |

|              |          | 6.5.1     | Forming a Subchannel          | •          |

|              |          | 6.5.2     | Device Selection              |            |

|              |          | 6.5.3     | Interface Signaling Sequences |            |

|              | 6.6      | Data Tr   | ansfer                        | 70         |

|              |          | 6.6.1     | Multiplex Mode                |            |

|              |          | 6.6.2     | Burst Mode                    |            |

|              |          | 6.6.3     | Lockout Mode                  |            |

|              | * ,      |           |                               |            |

|              | 6.7      | I/O Inte  | rrupts                        | 72         |

|              |          | 6.7.1     | Interrupts From a Device      |            |

|              |          | 6.7.2     | Program Controlled Interrupts |            |

| •   | 6.8   | Chaining                                   | Page<br>74 |

|-----|-------|--------------------------------------------|------------|

|     |       | 6.8.1 Data Chaining 6.8.2 Command Chaining |            |

|     | 6.9   | Other I/O Instructions                     | 75         |

|     | 6.10  | Direct Input/Output                        | 76         |

|     | 6.11  | Resets                                     | 77         |

|     | 6.12  | Multiplexor Channel Performance            | 78         |

| 7.0 | Techn | ologies                                    | 79         |

|     | 7.1   | Logic Circuits                             | 79         |

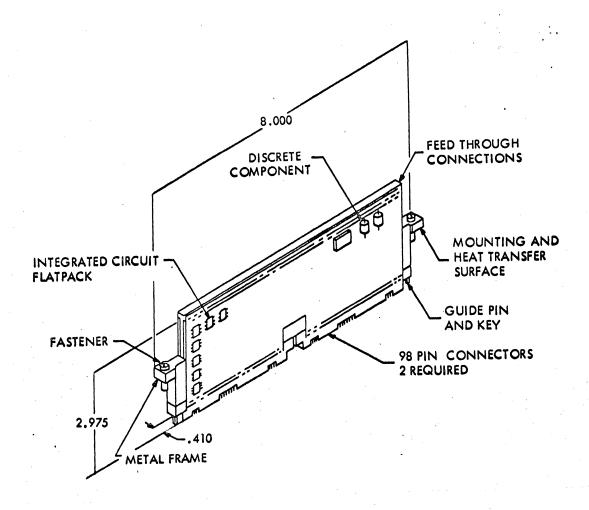

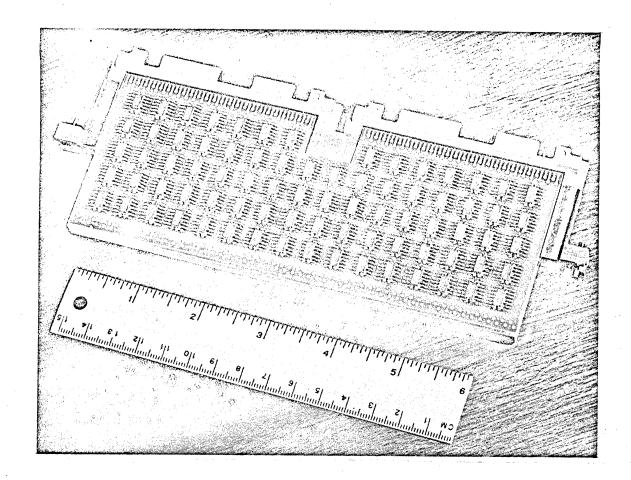

|     | 7.2   | Page and Back Panel Assembly               | 83         |

|     | 7.3   | Interface Circuits and Interconnections    | 86         |

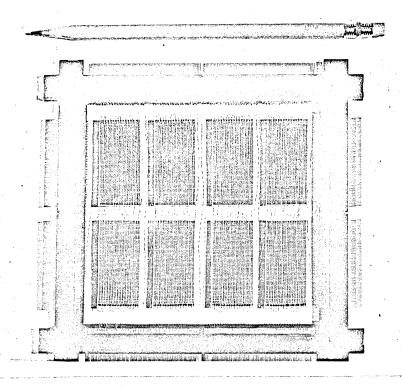

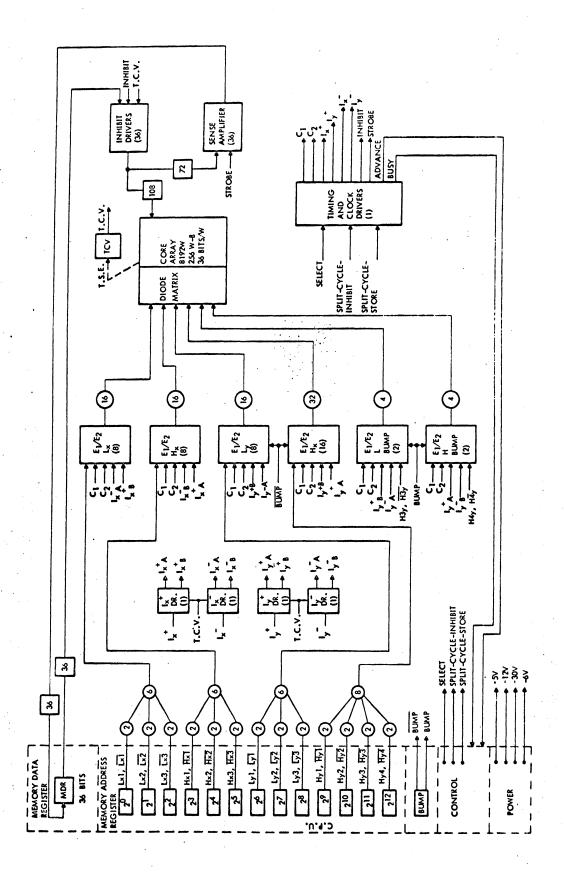

|     | 7.4   | Mainstore                                  | 87         |

| •   | 7.5   | Read-Only Store (ROS)                      | 92         |

|     | 7.6   | Power Supplies and Distribution            | 97         |

|     | 7.7   | Structural Design                          | 97         |

#### 1.0 INTRODUCTION

Model EP provides the power and facilities of a large scale general purpose processor for use in the aerospace and mobile environment. Three basic characteristics contribute toward the unique capabilities which it offers:

- o Architectural compatibility with System/360 reduces the effort and expense required to write and verify operational programs.

- o Microprogramming capability permits the incorporation of problem oriented instructions and procedures thereby providing the throughput of a special purpose processor within the context of a general purpose machine.

- o A number of special features are offered which enhance the system operation in a real-time environment and which provide for flexible multisystem operation.

The compatibility with System/360, the computational power obtained through microprogramming and the versatility offered through the many features, have produced a processor system which introduces a previously unavailable level of performance to the hardened environment.

# 1.1 System/360 Compatibility

System/4 Pi Model EP is based upon System/360 and its primary instruction sets, status sequencing, interruption handling and input/output system are fully compatible with System/360 thereby permitting bi-directional compatibility with ground-based computers. Provided that equivalent facilities are available and that programs are not time-dependent, programs written for Model EP may be run on any System/360 processor and identical results will be obtained. Conversely, programs available for System/360 (including certain software aids) may be used in Model EP.

Bi-directional compatibility offers the opportunity for efficient program development and for exact program verification in a host machine. It provides the ability to make use of a large repertory of existing programs and to call upon a large pool of experienced programmers.

Many features and options such as storage sharing, fall within the architectural concepts of System/360. Some of the features and options such as the use of special macroinstructions, are not ordinarily available in System/360 and require that specialized software be utilized. Such software will be offered in a standard, modular package which will provide effective support for the Model EP processor.

# 1.2 Microprogramming

The Model EP is a microprogrammed processor. The exact details of performance of each instruction are stored in a read-only memory (ROS) and new or modified instructions may be added merely by changing the contents of this memory. The concepts of microprogramming and an introduction of its techniques are provided in section 4.

In real-time applications, the microprogramming facility permits the processor to be "tuned" to the application such that problem solution times can be drastically reduced for specific requirements. One class of special instructions that can be added is mathematical routines such as square root, tangent, arc tangent, matrix multiply, etc. For example, if many trigometric operations are required, such as in Euler angle conversion, the use of sine and cosine instructions simplifies programming and will decrease problem solution time.

In some applications, it is necessary to perform complex and unusual routines repetitively. Examples are searching for a specific field in a bank of words to find if there is a match between any of the words searched and a specific key. Another example would be computation of radar steering angles: It is often possible to create highly specialized instructions to perform such applications dependent operations. Through microprogramming, the entire response of Model EP to a specific problem may be modified such that the processor will operate like a special purpose machine for unique parts of a problem and will continue to be a powerful, general purpose processor for the remainder of the application requirements.

## 1.3 Features

Model EP offers a large number of options and features in order that each installation may be systematically optimized. The <u>Functional Specification</u>, #66-584-001, provides detail concerning the functions which are available and their application. Briefly, the CPU may be equipped with a variety of standard instruction sets as well as with special instructions as mentioned above. The computational speed of the CPU may be varied by means of choosing general registers stored in mainstore or a hardware implementation of those registers.

The storage system may be modularly expanded in units of 8K words to a maximum of 131K words. Memory systems from several processors may be interconnected to form a "storage pool" with each processor having full access to the entire pool or with each processor having its isolated part and each processor having access to a limited pool. The storage protection feature may be utilized to protect specific blocks of information for prevention of illegal storage in the block or for both store and fetch protection.

The input/output system is designed to allow a wide span of performance for System/360 compatible channels and to permit the effective design of special purpose channel facilities. In particular, the ability of the storage system to accommodate multiple buses permits simultaneous and asynchronous loading of mainstore through stand-alone channels.

Processors are equipped with a System/360 compatible interruption system. In addition, real-time operations may be enhanced by use of a 32 level priority interrupt system which provides programmed masking, automatic priority resolution and automatic nesting of interrupts. Special power supply designs are offered to accommodate widely varying power sources and to provide automatic shutdown and restart in the event of transient power losses.

Multisystem operations may be achieved through the use of shared mainstore systems, shared input/output devices and direct communication between processors. Multisystem operation may be controlled by means of special instructions (Test and Set, Direct Read and Direct Write), by special features (Multisystem Signalling, and Direct Control) and by exchanging control signals through shared I/O devices or channel-to-channel adapters.

#### 2.0 ARCHITECTURE

## 2.1 General Concepts

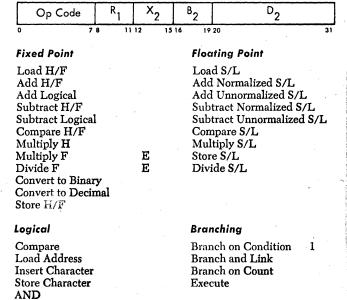

Model EP introduces the broad base capability of large scale processors into the aerospace and mobile environment. Model EP is a general purpose system that can readily accommodate scientific, control and communications applications. A Basic instruction set provides a fixed point and logical capability. A Standard instruction set provides the addition of logical manipulations of variable field length. A Floating Point feature may be added to either the Basic or Standard set. Other instructions are related to a variety of special features which are used to enhance real-time operations or provide for multisystem operations. Special purpose instructions may be incorporated in Model EP to optimize performance for specific applications.

Interplay of equipment and program is an essential consideration in System/4 Pi. The system is designed to operate with a supervisory program that coordinates and executes all I/O instructions, handles exceptional conditions, and supervises scheduling and execution of multiple programs. System/4 Pi provides for efficient switching from one program to another, as well as for the relocation of programs in storage. To the problem programmer, the supervisory program and the equipment are indistinguishable.

IBM can provide System/4 Pi programs that control and schedule the use of CPU facilities, main storage, input/output devices, etc. These programs are designed to control all system resources, including programs supplied by the user.

# 2.2 System/360 Compatibility

The Model EP is based on System/360 and the architecture is substantially identical to System/360 with the exception that:

- (1) Model EP may be supplied with an instruction set which is smaller than the System/360 Standard set. The System/4 Pi Basic Set is the System/360 Standard Set less the 12 Variable Field Length (VFL) instructions and the 2 Convert instructions.

- (2) Model EP may be supplied with instructions not available in System/360. Such instructions may be associated with:

- a. features not generally available in System/360 such as Priority Interrupt.

- b. special mathematical microinstructions such as Square Root, Sine/Cosine, Arc Tangent, etc.

- c. special application-oriented microinstructions such as Compute Radar Angle, etc.

Based on the compatibility with System/360, the documents describing that system may be used as valid descriptions of the Model EP. The Model EP Functional Specification, #66-584-001, particularizes Model EP within the context of System/360 and provides additional information about system application, feature availability and processor operation under exceptional conditions.

System/4 Pi is compatible with System/360; that is, any program gives identical results on Model EP or on any System/360 model. This rule is subject to the following limitations:

- 1. The systems facilities used by a program should be the same in each case. For example, the optional CPU features and the storage capacity, as well as the quantity, type, and priority of I/O equipment, should be equivalent. System facilities are understood to include instruction set availability such that each machine has at least the set of instructions used in the program.

- 2. The program should be independent of the relation of instruction execution times and of I/O data rates, access times, and command execution times.

- 3. The compatibility rule does not apply to detail functions for which neither frequency of occurrence nor usefulness of result warrants identical action in all models. These functions, all explicitly identified in 360 PO, are concerned with the handling of invalid programs and machine malfunctions.

- 4. Certain special features such as Priority Interrupt and Power Loss Protection/Recovery are transparent to 360 architecture but their operation usually may not be replicated on a System/360 processor.

## 2.3 System Structure

The material in this section has been prepared as an introduction to those aspects of system structure which are common to both System/360 and System/4 Pi. This material is largely extracted from System/360 Principles of Operation. Changes have been incorporated to delete unavailable features, to shift emphasis, to enhance clarity and to mention priority interrupt and special purpose input/output channels. The material in this section is introductory in nature. The reader is referred to System/360 Principles of Operation for an extensive description of the architecture and to System/4 Pi Functional Specification for a detailed description of features available in Model EP.

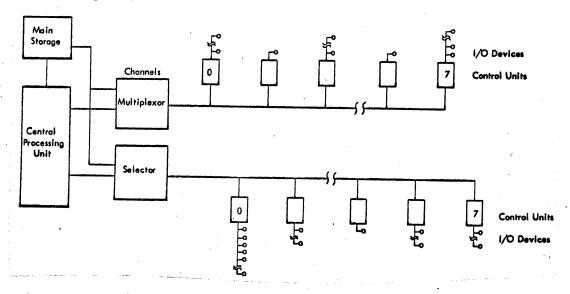

The basic structure of a System/4 Pi consists of main storage, a central processing unit (CPU), the input/output channels, and the input/output devices attached to the channels through control units. It is possible for systems to communicate with each other by means of shared I/O devices, a channel, or shared storage. Figure 1 shows the basic organization of a single system.

Figure 1. IBM System/4 Pi Basic Logical Structure

#### 2.3.1 Main Storage

Storage units may be either physically integrated with the CPU or constructed as stand-alone units. The storage cycle speed is not directly related to the internal cycling of the CPU.

Main storage may be shared by CPU's. Fetching and storing of data by the CPU are not affected by any concurrent I/O data transfer or by reference to the same storage location by another CPU. If a CPU and a channel concurrently refer to the same storage location, the accesses normally are granted in a sequence that assigns higher priority to references by channels. If the first reference changes the contents of the location, any subsequent storage fetches obtain the new contents.

Information Formats - The system transmits information between main storage and the CPU in four units, of eight bits at a time. Each eight-bit unit of information is called a byte, the basic building block of all formats. A ninth bit, the parity or check bit, is transmitted with each byte and carries odd parity on the byte. The parity bit cannot be affected by the program; its only purpose is to cause an interruption when a parity error is detected. Reference in this manual to the size of data fields and registers exclude the mention of the associated parity bits.

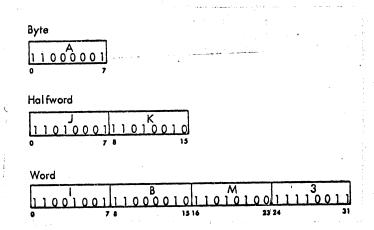

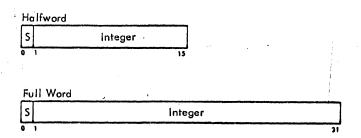

Bytes may be handled separately or grouped together in fields. A halfword is a group of two consecutive bytes and is the basic building block of instructions. A word is a group of four consecutive bytes; a double word is a field consisting of two words (Figure 2). The location of any field or group of bytes is specified by the address of its leftmost byte.

Figure 2. Sample Information Formats

The length of fields is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length, which can be either one, two, four, or eight bytes.

When the length of a field is not implied by the operation code, but is stated explicitly, the information is said to have variable field length. Variable-length operands are variable in length by increments of one byte.

Within any program format or any fixed-length operand format, the bits making up the format are consecutively numbered from left to right starting with the number 0.

Addressing - Byte locations in storage are consecutively numbered starting with 0; each number is considered the address of the corresponding byte. A group of bytes in storage is addressed by the leftmost byte of the group. The number of bytes in the group is either implied or explicitly defined by the operation. The addressing arrangement uses a 24-bit binary address to accommodate a maximum of 16,777,216 byte addresses. This set of main-storage addresses includes some locations reserved for special purposes.

When only a part of the maximum storage capacity is available in a given installation, the available storage is normally contiguously addressable, starting at address 0. An addressing exception is recognized when any part of an operand is located beyond the maximum available capacity of an installation.

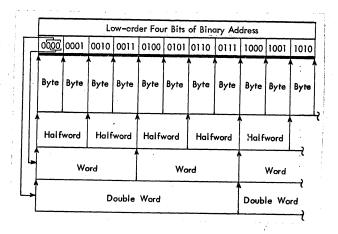

Information Positioning - Fixed-length fields, such as halfwords and double words, must be located in main storage on an integral boundary for that unit of information. A boundary is called integral for a unit of information when its storage address is a multiple of the length of the unit in bytes. For example, words (four bytes) must be located in storage so that their address is a multiple of the number 4. A halfword (two bytes) must have an address that is a multiple of the number 2, and double words (eight bytes) must have an address that is a multiple of the number 8.

Storage addresses are expressed in binary form. In binary, integral boundaries for halfwords, words, and double words can be specified only by the binary addresses in which one, two, or three of the low-order bits, respectively, are zero. (Figure 3). For example, the integral boundary for a word is a binary address in which the two low-order positions are zero.

Variable-length fields are not limited to integral boundaries, and may start on any byte location.

Figure 3. Integral Boundaries for Halfwords, Words and Double Words

## 2.3.2 Central Processing Unit

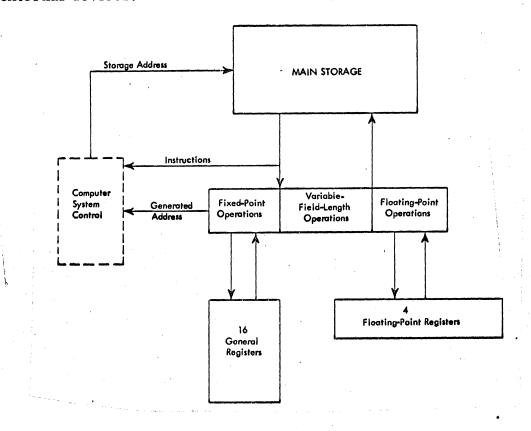

The central processing unit (Figure 4) contains the facilities for addressing main storage, for fetching or storing information, for arithmetic and logical processing of data, for sequencing instructions in the desired order, and for initiating the communication between storage and external devices.

Figure 4. Basic Concept of Central Processing

Unit Functions

The system control section provides the normal CPU control that guides the CPU through the functions necessary to execute the instructions.

The CPU provides 16 general registers for fixed-point operands and four floating-point registers for floating-point operands. Implementation of these registers may be in special circuitry or in a separate area of main storage. In either case, the address and functions of these registers are identical.

General Registers - The CPU can address information in 16 general registers. The general registers can be used as index registers, in address arithmetic and indexing, and as accumulators in fixed-point arithmetic and logical operations. The registers have a capacity of one word (32 bits). The general registers are identified by numbers 0-15 and are specified by a four-bit R field in an instruction (Figure 5). Some instructions provide for addressing multiple general registers by having several R fields.

| R Field | Reg No. | General Registers | Floating-Point Registers |

|---------|---------|-------------------|--------------------------|

| 0000    | 0       | SE-32 Bits        | 64 Bits                  |

| 0001    | 1       |                   |                          |

| 0010    | 2       |                   |                          |

| 0011    | 3       |                   |                          |

| 0100    | 4       |                   |                          |

| 0101    | 5       |                   |                          |

| 0110    | 6       |                   |                          |

| 0111    | 7       |                   |                          |

| 1000    | 8       |                   |                          |

| 1001    | 9       |                   |                          |

| 1010    | 10      |                   |                          |

| 1011    | 11      |                   |                          |

| 1100    | 12      |                   |                          |

| 1101    | 13      |                   |                          |

| 1110    | 14      |                   |                          |

| 1111    | 15      |                   |                          |

Figure 5. General and Floating-Point Registers

For some operations, two adjacent general registers are coupled together, providing a two-word capacity. In these operations, the addressed register contains the high order operand bits and must have an even address, and the implied register, containing the low-order operand bits, has the next higher address.

Floating-Point Registers - Four floating-point registers are available for floating-point operations. They are identified by the numbers 0, 2, 4, and 6 (Figure 5). These floating-point registers are two words (64 bits) in length and can contain either a short (one word) or a long (two words) floating-point operand. A short operand occupies the high-order bits of a floating-point register. The low-order portion of the register is ignored and remains unchanged in short-precision arithmetic. The instruction operand code determines which type of register (general or floating-point) is to be used in an operation.

## 2.3.3 Arithmetic and Logical Unit

The arithmetic and logical unit can process binary integers and floating-point fractions of fixed length, and logical information of either fixed or variable length. Processing is done in parallel using a 32 bit wide adder-shifter path and an 8 bit wide mover path which can operate simultaneously.

Arithmetic and logical operations performed by the CPU fall into three classes: fixed-point arithmetic, floating-point arithmetic, and logical operations. These classes differ in the data formats used, the registers involved, the operations provided, and the way the field length is stated.

Fixed-Point Arithmetic - The basic arithmetic operand is the 32-bit fixed-point binary word. Sixteen-bit halfword operands may be specified in most operations for improved performance or storage utilization. See Figure 6. To preserve precision, some products and all dividends are 64 bits long.

Figure 6. Fixed-Point Number Formats

Because the 32-bit word size readily accommodates a 24-bit address, fixed-point arithmetic can be used both for integer operand arithmetic and for address arithmetic. This combined usage provides economy and permits the entire fixed-point instruction set and several logical operations to be used in address computation. Thus, multiplication, shifting, and logical manipulation of address components are possible.

The absence of the need for recomplementation and the ease of extension and truncation make two's-complement notation desirable for address components and fixed-point operands. Since integer and addressing algorisms often require repeated reference to operands or intermediate results, the use of multiple registers is advantageous in arithmetic sequences and address calculations.

Additions, subtractions, multiplications, divisions, and comparisons are performed upon one operand in a register and another operand either in a register or from storage. Multiple-precision operation is made convenient by the two's-complement notation and by recognition of the carry from one word to another. A word in one register or a double word in a pair of adjacent registers may be shifted left or right. A pair of conversion instructions - CONVERT TO BINARY and CONVERT TO DECIMAL - provides transition between decimal and binary radix (number base) without the use of tables. Multiple-register loading and storing instructions facilitate subroutine switching.

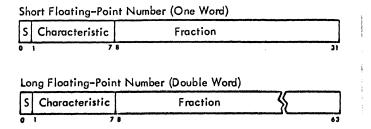

Floating-Point Arithmetic - Floating-point numbers occur in either of two fixed-length formats -- short or long. These formats differ only in the length of the fractions (Figure 7.)

Figure 7. Short and Long Floating-Point Number Formats

Floating-point operands are either 32 or 64 bits long. The short length, equivalent to seven decimal places of precision, permits a maximum number of operands to be placed in storage and gives the shortest execution times. The long length, used when higher precision is desired, gives up to 17 decimal places of precision, thus eliminating most requirements for double-precision arithmetic.

The operand lengths, being powers of two, permit maximum efficiency in the use of binary addressing and in matching the physical word sizes of the different models. Floating-point arithmetic is designed to allow easy transition between the two formats.

The fraction of a floating-point number is expressed in hexadecimal (base 16) digits, each consisting of four binary bits and having the values 0-15. In the short format, the fraction consists of six hexadecimal digits occupying bits 8-31. In the long format the fraction has 14 hexadecimal digits occupying bits 8-63.

The radix point of the fraction is assumed to be immediately to the left of the high-order fraction digit. To provide the proper magnitude for the floating-point number, the fraction is considered to be multiplied by a power of 16. The characteristic portion, bits 1-7 of both formats, is used to indicate this power. The characteristic is treated as an excess 64 number with a range from -64 through +63, and permits representation of decimal numbers with magnitudes in the range of 10-78 to 10<sup>75</sup>.

Bit position 0 in either format is the sign (S) of the fraction. The fraction of negative numbers is carried in true form.

Four 64-bit floating-point registers are provided. Arithmetic operations are performed with one operand in a register and another either in a register or from storage. The result, developed in a register, is generally of the same length as the operands. The availability of several floating-point registers eliminates much storing and loading of intermediate results.

Logical Operations - Logical information is handled as fixedor variable-length data. It is subject to such operations as comparison, translation, editing, bit testing, and bit setting.

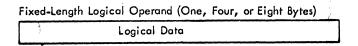

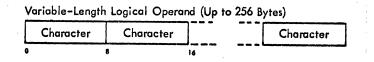

When used as a fixed-length operand, logical information can consist of either one, four, or eight bytes and is processed in the general registers (Figure 8).

Figure 8. Fixed-Length Logical Information

A large portion of logical information consists of alphabetic or numeric character codes, called alphametic data, and is used for communication with character-set sensitive I/O devices. This information has the variable-field length format and can consist of up to 256 bytes (Figure 9). It is processed storage to storage, left to right, an eight-bit byte at a time.

Figure 9. Variable-Length Logical Information

## 2.3.4 Program Execution

The CPU program consists of instructions, index words, and control words specifying the operations to be performed. This information resides in main storage and general registers, and may be operated upon as data.

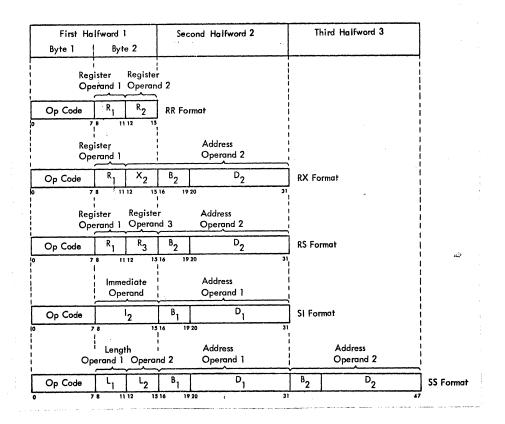

Instruction Format - The length of an instruction format can be one, two, or three halfwords. It is related to the number of storage addresses necessary for the operation. An instruction consisting of only one halfword causes no reference to main storage. A two-halfword instruction provides one storage-address specification; a three-halfword instruction provides two storage-address specifications. All instructions must be located in storage on integral boundaries for halfwords. Figure 10 shows five basic instruction formats.

Figure 10. Five Basic Instruction Formats

The five basic instruction formats are denoted by the format codes RR, RX, RS, SI, and SS. The format codes express, in general terms, the operation to be performed, RR denotes a register-to-register operation; RX, a register-and-indexed-storage operation; RS, a register-and-storage operation; SI, a storage and immediate-operand operation; and SS, a storage-to-storage operation. An immediate operand is one contained within the instruction.

For purposes of describing the execution of instructions, operands are designated as first and second operands and, in the case of branch-on-index instructions, third operands. These names refer to the manner in which the operands participate. The operand to which a field in an instruction format applies is generally denoted by the number following the code name of the field, for example  $R_1$ ,  $B_1$ ,  $L_2$ ,  $D_2$ .

In each format, the first instruction halfword consists of two parts. The first byte contains the operation code (op code). The length and format of an instruction are specified by the first two bits of the operation code.

## Instruction Length Recording

| Bit Positions (0-1) | Instruction<br>Length | Instruction<br>Format |

|---------------------|-----------------------|-----------------------|

| 00                  | One halfword          | RR                    |

| 01                  | Two halfwords         | RX                    |

| ` <b>10</b>         | Two halfwords         | RX or SI              |

| 11                  | Three halfwords       | SS                    |

The second byte is used either as two 4-bit fields or as a single eight-bit field. This byte can contain the following information:

Four-bit operand register specification (R1, R2, or R3)

Four-bit index register specification  $(X_2)$

Four-bit mask (M1)

Four-bit operand length specification  $(L_1 \text{ or } L_2)$

Eight-bit operand length specification (L)

Eight-bit byte of immediate data (I<sub>2</sub>)

In some instructions a four-bit field or the whole second byte of the first halfword is ignored.

The second and third halfwords always have the same format:

Four-bit base register designator ( $B_1$  or  $B_2$ ), followed by a 12-bit displacement ( $D_1$  or  $D_2$ ).

Address Generation - For addressing purposes, operands can be grouped in three classes: explicitly addressed operands in main storage, immediate operands placed as part of the instruction stream in main storage, and operands located in the general or floating-point registers.

To permit the ready relocation of program segments and to provide for the flexible specifications of input, output, and working areas, all instructions referring to main storage have been given the capacity of employing a full address.

The address used to refer to main storage is generated from the following three binary numbers:

Base Address (B) is a 24-bit number contained in a general register specified by the program in the B field of the instruction. The B field is included in every address specification. The base address can be used as a means of static relocation of programs and data. In array-type calculations, it can specify the location of any array and, in record-type processing, it can identify the record. The base address provides for addressing the entire main storage. The base address may also be used for indexing purposes.

Index (X) is a 24-bit number contained in a general register specified by the program in the X field of the instruction. It is included only in the address specified by the RX instruction format. The RX format instructions permit double indexing; i.e., the index can be used to provide the address of an element within an array.

Displacement (D) is a 12-bit number contained in the instruction format. It is included in every address computation. The displacement provides for relative addressing up to 4095 bytes beyond the element or base address. In array-type calculations the displacement can be used to specify one of many items associated with an element. In the processing of records, the displacement can be used to identify items within a record.

In forming the address, the base address and index are treated as unsigned 24-bit positive binary integers. The displacement is similarly treated as a 12-bit positive binary integer. The three are added as 24-bit binary numbers, ignoring overflow. Since every address includes a base, the sum is always 24 bits long. The address bits are numbered 8-31 corresponding to the numbering of the base address and index bits in the general register.

The program may have zeros in the base address, index, or displacement fields. A zero is used to indicate the absence of the corresponding address component. A base or index of zero implies that a zero quantity is to be used in forming the address, regardless of the contents of general register 0. A displacement of zero has no special significance. Initialization, modification, and testing of base addresses and indexes can be carried out by fixed-point instructions, or by BRANCH AND LINK, BRANCH ON COUNT, or BRANCH-ON-INDEX instructions.

As an aid in describing the logic of the instruction format, examples of two instructions and their related instruction formats follow.

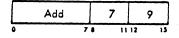

#### RR FORMAT

Execution of the ADD instruction adds the contents of general register 9 to the contents of general register 7 and the sum of the addition is placed in general register 7.

#### RX FORMAT

Execution of the STORE instruction stores the contents of general register 3 at a main-storage location addressed by the sum of 300 and the low-order 24 bits of general register 14 and 10.

Sequantial Instruction Execution - Normally, the operation of the CPU is controlled by the instructions taken in sequence. An instruction is fetched from a location specified by the instruction address in the current PSW. The instruction address is then increased by the number of bytes in the instruction fetched to address the next instruction in sequence. The instruction is then executed and the same steps are repeated using the new value of the instruction address.

Conceptually, all halfwords of an instruction are fetched from storage after the preceding operation is completed and before execution of the current operation, even though physical storage word size and overlap of instruction execution with storage access may cause actual instruction fetching to be different. Thus, it is possible to modify an instruction in storage by the immediately preceding instruction.

A change from sequential operation may be caused by branching, status switching, interruptions or manual intervention.

Branching - The normal sequential execution of instructions is changed when reference is made to a subroutine, when a two-way choice is encountered, or when a segment of coding, such as a loop, is to be repeated. All these tasks can be accomplished with branching instructions. Provision is made for subroutine linkage, permitting not only the introduction of a new instruction address but also the preservation of the return address and associated information.

Decision-making is generally and symmetrically provided by the BRANCH ON CONDITION instruction. This instruction inspects a two-bit condition code that reflects the result of a majority of the arithmetic, logical, and I/O operations. Each of these operations can set the code in any one of four states, and the conditional branch can specify any selection of these four states as the criterion for branching. For example, the condition code reflects such conditions as nonzero, first operand high, equal, overflow, channel busy, zero, etc. Once set, the condition code remains unchanged until modified by an instruction that reflects a different condition code.

The two bits of the condition code provide for four possible condition code settings: 0, 1, 2, and 3. The specific meaning of any setting is significant only to the operation setting the condition code.

Loop control can be performed by the conditional branch when it tests the outcome of address arithmetic and counting operations. For some particularly frequent combinations of arithmetic and tests, the instructions BRANCH ON COUNT and BRANCH ON INDEX are provided. These branches, being specialized, provide increased performance for these tasks.

Program Status Word - A double word, the program status (PSW), contains the information required for proper program execution. The PSW includes the instruction address, condition code, and other fields to be discussed. In general, the PSW is used to control instruction sequencing and to hold and indicate the status of the system in relation to the program currently being executed. The active or controlling PSW is called the "current PSW." By storing the current PSW during an interruption, the status of the CPU can be preserved for subsequent inspection. By loading a new PSW or part of a PSW, the state of the CPU can be initialized or changed. Figure 11 shows the PSW format.

| Syst    | em Mask   | Key       | AMWP  | Ínte             | ruption Code                  |

|---------|-----------|-----------|-------|------------------|-------------------------------|

| 0       | 7         | 8 11      | 12 15 | 16               | 31                            |

| ILC     | CC Prog   | ram<br>sk |       | Instructio       | n Address                     |

| 32 33 3 | 4 35 36   | 39        | 40    |                  | 63                            |

|         | _         |           | 1     |                  |                               |

| 0-7     | System m  |           |       |                  | Wait state (W)                |

| 0       | Channel   |           |       | 15               | Problem state (P)             |

| 1       | Channel   | 1 mask    |       | 16-31            | Interruption code             |

| 2       | Channel   | 2 mask    |       | 32-33            | Instruction Length code (ILC) |

| 3       | Channel   | 3 mask    |       |                  | Condition code (CC)           |

| . 4     | Channel   | 4 mask    |       |                  | Program mask                  |

| 5       | Channel   | 5 mask    |       | 36               |                               |

| 6       | Channel   | 6 mask    |       | . 37             | Decimal overflow mask         |

| 7       | External  | mask      |       | 38               | Exponent underflow mask       |

| -11     | Protectio | kev       |       | 39               | Significance mask             |

| 12      | ASCII-8   |           | 3     |                  | Instruction address           |

| 13      | Machine   |           |       | <del>-0-00</del> | man octron address            |

Figure 11. Program Status Word Format

Interruption - The interruption system permits the CPU to change state as a result of conditions external to the system, in input/output (I/O) units or in the CPU itself. Five classes of interruption conditions are possible: I/O, program, supervisor call, external, and machine check.

Each class has two related PSW's called "old" and "new" in unique main-storage locations (Figure 12). In all classes, an interruption involves merely storing the current PSW in its "old" position and making the PSW at the "new" position the current PSW. The "old" PSW holds all necessary status information of the system existing at the time of the interruption. If, at the conclusion of the interruption routine, there is an instruction to make the old PSW the current PSW, the system is restored to the state prior to the interruption and the interrupted routine continues.

Interruptions are taken only when the CPU is interruptable for the interruption source. The system mask, program mask, and machine check mask bits in the PSW may be used to mask certain interruptions. When masked off, an interruption either remains pending or is ignored. The system mask may keep I/O and external interruptions pending, the program mask may cause four of the 15 program interruptions to be ignored, and the machine-check mask may cause machine-check interruptions to be ignored. Other interruptions cannot be masked off.

|     | Address   | Length      | Purpose                      |

|-----|-----------|-------------|------------------------------|

| 0   | 0000 0000 | double word | Initial program loading PSW  |

| 8   | 0000 1000 | double word | Initial program loading CCW1 |

| 16  | 0001 0000 | double word | Initial program loading CCW2 |

| 24  | 0001 1000 | double word | External old PSW             |

| 32  | 0010 0000 | double word | Supervisor call old PSW      |

| 40  | 0010 1000 | double word | Program old PSW              |

| 48  | 0001 0000 | double word | Machine check old PSW        |

| 56  | 0011 1000 | double word | Input/output old PSW         |

| 64  | 0100 0000 | double word | Channel status word          |

| 72  | 0100 1000 | word        | Channel address word         |

| 76  | 0100 1100 | word        | Unused                       |

| 80  | 0101 0000 | word        | Timer                        |

| 84  | 0101 0100 | word        | Unused                       |

| 88  | 0101 1000 | double word | External new PSW             |

| 96  | 0110 0000 | double word | Supervisor call new PSW      |

| 104 | 0110 1000 | double word | Program new PSW              |

| 112 | 0111 0000 | double word | Machine check new PSW        |

| 120 | 0111 1000 | double word | Input/output new PSW         |

| 128 | 1000 0000 |             | Diagnostic scan-out area *   |

|     |           |             |                              |

<sup>\*</sup> The size of the diagnostic scan-out area depends upon the particular system's CPU and I/O channels.

Figure 12. Permanent Storage Assignments

An interruption always takes place after one instruction execution is finished and before a new instruction execution is started. However, the occurrence of an interruption may affect the execution of the current instruction. To permit proper programmed action following an interruption, the cause of the interruption is identified and provision is made to locate the last executed instruction.

Input/Output Interruption - An I/O interruption provides a means by which the CPU responds to conditions in the channels and I/O units.

An I/O interruption can occur only when the mask bit associated with the channel is set to one. The address of the channel and I/O unit involved are recorded in bits 16-31 of the old PSW. Further information concerning the I/O action is preserved in the channel status word (CSW) that is stored during the interruption.

Program Interruption - Unusual conditions encountered in a program create program interruptions. These conditions include incorrect operands and operand specifications, as well as exceptional results. The interruption code identifies the interruption cause. Figure 13 shows the different causes that may occur.

| Int | erruption | Program Interruption  |

|-----|-----------|-----------------------|

|     | Code      | Cause                 |

| . 1 | 00000001  | Operation             |

| 2   | 00000010  | Privileged operation  |

| 3   | 00000011  | Execute               |

| 4   | 00000100  | Protection            |

| 5   | 00000101  | Addressing            |

| 6   | 00000110  | Specification         |

| 7   | 00000111  | Data                  |

| 8   | 00001000  | Fixed-point overflow  |

| 9   | 00001001  | Fixed-point divide    |

| 10  | 00001010  | Decimal overflow      |

| 11  | 00001011  | Decimal divide        |

| 12  | 00001100  | Exponent overflow     |

| 13  | 00001101  | Exponent underflow    |

| 14  | 00001110  | Significance          |

| 15  | 00001111  | Floating-point divide |

Figure 13. Interruption Code for Program Interruption

Supervisor-Call Interruption - This interruption occurs as a result of execution of the instruction SUPERVISOR CALL. Eight bits from the instruction format are placed in the interruption code of the old PSW, permitting an identification to be associated with the interruptions. A major use for the instruction SUPERVISOR CALL is to switch from the problemstate to the supervisor state. This interruption may also be used for other modes of status-switching.

External Interruption - The external interruption provides the means by which the CPU responds to signals from the interruption key on the system control panel, the timer, and the external signals of the direct control feature.

An external interruption can occur only when system mask bit 7 in the PSW is one.

The source of the interruption is identified by the interruption code in bits 24-31 of the PSW (Figure 14). Bits 16-23 of the interruption code are made zero.

| Interruption  Code Bit | External Interruption Cause | Mask Bi  |

|------------------------|-----------------------------|----------|

| 24                     | Timer .                     | . 7      |

| 25                     | Interrupt key               | . ,      |

| 26                     | External signal 2           | 7        |

| 27                     | External signal 3           | - ',     |

| 28                     | External signal 4           | <u>'</u> |

| 29                     | External signal 5           |          |

| 30                     | External signal 6           |          |

| 31                     | External signal 7           | 7        |

Figure 14. Interruption Code for External Interruption

Priority Interruption - In real time applications, the computing power of the CPU needs to be coupled with the ability to respond quickly to external events, and to distinguish between many different external situations with a minimum of programming. These abilities can be provided with a special feature called Priority Interrupt. The 32 levels of priority interrupt feature are supplemental to the single level, 6 line external interrupt feature described above. The two systems are logically and physically independent.

The priority interrupt feature permits individual masking and hardware nesting of up to 32 levels of priority. Information transmitted from the interrupting source may be expanded to allow as many as 256 external conditions at each level of priority.

When the priority interrupt is requested and enabled at the same time that one of the basic System/4 Pi interrupts is requested and enabled, resolution of priority may be controlled by the programmer to permit the priority interruption to be serviced first.

Machine-Check Interruption - The occurrence of a machine check (if not masked off) terminates the current instruction, initiates a diagnostic procedure, and subsequently causes the machine-check interruption. A machine check cannot be caused by invalid data or instructions. The diagnostic scan is performed into the scan area starting at location 128. Proper execution of these steps depends on the nature of the machine check.

Priority of Interruptions - During execution of an instruction, several interruption requests may occur. Simultaneous interruption requests are honored in the following predetermined order:

Machine Check

Program or Supervisor Call

External

Input/Output

The program and supervisor-call interruptions are mutually exclusive and cannot occur at the same time.

When more than one interruption cause requests service, the action consists of storing the old PSW and fetching the new PSW belonging to the interruption which is taken first. This new PSW subsequently is stored without any instruction execution and the next interruption PSW is fetched. This process continues until no more interruptions are to be serviced. When the last interruption request has been serviced, instruction execution is resumed using the PSW last fetched. The order of execution of the interruption subroutines is, therefore, the reverse of the order in which the PSW's are fetched.

Thus, the most important interruptions - I/O, external, program or supervisor call - are actually serviced first. Machine check, when it occurs, does not allow any other interruptions to be taken.

Program States - Over-all CPU status is determined by four types of program-state alternatives, each of which can be changed independently to its opposite and most of which are indicated by a bit or bits in the PSW. The program-state alternatives are named stopped or operating, running or waiting, masked or interruptible, and supervisor or problem state. These states differ in the way they affect the CPU functions and the manner in which their status is indicated and switched. All program states are independent of each other in their functions, indication, and status-switching.

Stopped or Operating States: The stopped state is entered and left by manual procedure. Instructions are not executed, interruptions are not accepted, and the timer is not updated. In the operating state, the CPU is capable of executing instructions and being interrupted. Running or Waiting State: In the running state, instruction fetching and execution proceed in the normal manner. The wait state is normally entered by the program to await an interruption, for example, an I/O interruption or operator intervention from the console. In the wait state, no instructions are processed, the timer is updated, and I/O and external interruptions are accepted, unless masked. Running or waiting state is determined by the setting of bit 14 in the PSW.

Masked or Interruptible State: The CPU may be interruptible or masked for the system, program, and machine interruptions. When the CPU is interruptible for a class of interruptions, these interruptions are accepted. When the CPU is masked, the system interruptions remain pending, while the program and machine-check interruptions are ignored. The interruptible states of the CPU are changed by changing the mask bits of the PSW.

Supervisor or Problem State: In the problem state, all I/O instructions and a group of control instructions are invalid. In the supervisor state, all instructions are valid. The choice of problem or supervisor state is determined by bit 15 of the PSW.

#### 2.3.5 Protection Features

Two protection features are available. These features make it possible to protect the contents of main storage from destruction or misuse. When the store-protection feature is installed, attempts to modify storage are monitored. The addition of the fetch-protection feature to the store-protection feature provide for monitoring of all accesses to storage.

Protection is achieved by dividing main storage into blocks of 2,048 bytes, and by associating a five-bit key with each block. Two instructions - SET STORAGE KEY and INSERT STORAGE KEY - are provided for assigning and inspecting the code in a key. The same code may be used in many keys.

A user's right of access to storage is identified by a four-bit protection key. For references caused by the CPU, the protection key in the current PSW is used; accesses by channels are controlled by the protection key assigned to the associated I/O operation.

When protection applies to a main-storage reference, the key in storage is compared with the protection key associated with the reference. Access to the location, for both operands and instructions, is granted only when the two keys match. The keys are said to match when the four high-order bits of the key in storage are equal to the protection key or when the protection key is zero. When store-and-fetch protection is installed, the low-order bit of the key in storage is used to specify whether or not fetching is to be monitored.

When a protection mismatch is detected, the content of the protected main-storage location remains unaltered. A protection violation due to a CPU reference causes the instruction to be suppressed or terminated and program execution to be altered by an interruption. A violation due to an I/O operation causes the I/O operation to be terminated, with the protection mismatch indicated in the channel status word stored at the end of an I/O operation.

#### 2.3.6 Timer Feature

The timer consists of a full word in main-storage location 80. The timer word is counted down at a rate determined by an external pulse source. The timer word is treated as a signal integer following the rules of fixed-point arithmetic. An external interruption condition is signalled when the value of the timer word goes from positive to negative.

An updated timer value is available at the end of each instruction execution but is not updated in the stopped state. The timer is changed by addressing storage location 80. As an interval timer, the timer is used to measure elapsed time over relatively short intervals. It can be set to any value at any time.

## 2.3.7 Direct Control Feature

The direct control feature provides two instructions, READ DIRECT and WRITE DIRECT, and six external interruption lines. The read and write instructions provide for the transfer of a single byte of information between an external device and the main storage of the system. It is usually most desirable to use the data channels of the system to handle the transfer of any volume of information and use the direct data control feature to pass controlling and synchronizing information between the CPU and special external devices.

Each of the six external signal lines, when pulsed, sets up the conditions for an external interruption.

## 2.3.8 Multisystem Operation

The design of System/360 permits communication between individual CPU's at several transmission rates. The communication is possible through shared control units, through a channel-to-channel adapter, and through shared storage. Interconnection of CPU's is further enhanced by the direct control feature (described in the previous section), which can be used to signal from one CPU to another, and by facilities for direct address relocation, malfunction indication, and external CPU initialization.

The relocation procedure applies to the first 4,096 bytes of storage. This area contains all permanent storage assignments and, generally, has special significance to supervisory programs. The relocation is accomplished by inserting a 12-bit prefix in each address which has the high-order 12 bits set to zero and hence, pertains to location 0-4095. Two manually set prefixes are available to permit the use of an alternative area when storage malfunction occurs. The choice between the prefixes is determined by a prefix trigger set during initial program loading.

To alert one CPU to the possible malfunction of another CPU, a machine check-out signal is provided, which can serve as an external interruption to another CPU.

Finally, provision is made for starting one CPU by a signal from another CPU.

# 2.3.9 Input and Output

The following information is introductory in nature. For thorough definition of the input/output system, see System/360 Principles of Operation.

Input/Output Devices and Control Units - Input/output operations involve the transfer of information to or from main storage and an I/O device. Input/output devices include such equipment as card read punches, magnetic tape units, disk storage, drum storage, typewriter-keyboard devices, printers, teleprocessing devices, and process control equipment.

Many I/O devices function with an external document, such as a punched card or a reel of magnetic tape. Some I/O devices handle only electrical signals, such as those found in process-control networks. In either case, I/O device operation is regulated by a control unit. The control-unit function may be housed with the I/O device, as is the case with a printer, or a separate control unit may be used. In all cases, the control-unit function provides the logical and buffering capabilities necessary to operate the associated I/O device. From the programming point of view, most control-unit functions merge with I/O device functions.

Each control unit functions only with the I/O device for which it is designed, but each control unit has standard-signal connections with regard to the channel to which it is attached.

Input/Output Interface - So that the CPU may control a wide variety of I/O devices, all control units are designed to respond to a standard set of signals from the channel. This control-unit-to-channel connection is called I/O interface. It enables the CPU to handle all I/O operations with only four instructions.

Special Purpose Channels - In order to effectively integrate Model EP into existing systems and to accommodate unusual data transfer situations such as those arising from radar inputs, special purpose channels may be designed and attached to a Model EP. These channels may operate as special purpose transfer paths under control of a standard channel or they may be entities with unique control instructions and architecture. Such channels may be used in addition to or in place of standard channels described below.

Channels - Standard channels connect with the CPU and main storage and, via the I/O interface, with control units. Channels control transfer of data between I/O devices and main storage. The CPU program is free to resume processing data after initiating channel control of I/O operations, including concurrent operation of several I/O devices on a single channel, as well as concurrent operation of several other channels.

A channel may be an independent unit, complete with necessary logical and storage capabilities, or it may time-share CPU facilities and be physically integrated with the CPU. In either case, channel functions are identical. Channels may be implemented, however, to have different maximum data transfer capabilities.

The System/360 has two types of channels: multiplexor and selector. The channel facility necessary to sustain an operation with an I/O device is called a subchannel. The selector channel has one subchannel; the multiplexor channel has multiple subchannels.

Channels have two modes of operation: burst and multiplex.

In the burst mode, all channel facilities are monopolized for the duration of data transfer to or from a particular I/O device. The selector channel functions only in the burst mode.

The multiplexor channel functions in either the burst mode or in the multiplex mode. In the multiplex mode, the multiplexor channel can sustain concurrent I/O operations on several subchannels. Bytes of data are interleaved together and routed to or from the selected I/O devices and to or from the desired locations in the main storage. In the multiplex mode, the multiplexor channel's single data path is time-shared by the concurrently operating I/O devices, each of which uses a subchannel.

In burst mode, the multiplexor channel's data path is pre-empted by a burst-mode device; other devices attached to the channel cannot transfer data or communicate with the CPU until the burst-mode device releases the data path.

Some I/O devices can operate only in burst mode. Other I/O devices have a manual switch in the control unit that may be set to a burst-mode or to a multiplex-mode position, when attached to a multiplexor channel. When attached to a selector channel, an I/O device can operate only in burst mode.

Input/Output Instructions - The System/360 uses only four I/O instructions:

START I/O TEST I/O HALT I/O TEST CHANNEL

Input/output instructions can be executed only while the CPU is in the supervisor state.

Start I/O - The START I/O instruction is used to initiate an I/O operation. The address part of the instruction specifies the channel and I/O device.

Test I/O - Execution of the TEST I/O instruction sets the condition code in the PSW to indicate the state of the addressed channel, subchannel, and I/O device, and may cause a CSW to be stored. The instruction may be used to clear I/O interruption conditions, selectively by device.

Halt I/O - The HALT I/O instruction terminates a channel operation.

Test Channel - Execution of the TEST CHANNEL instruction sets the condition code in the PSW to indicate the state of the channel addressed by the instruction. The resulting condition code indicates one of the following: channel available, interruption condition in channel, channel working, or channel not operational.

Input/Output Operation Initiation - An I/O operation is initiated by a START I/O instruction. If the necessary channel and device facilities are available, START I/O is accepted and the CPU continues its program. The channel independently governs the I/O device specified by the instruction.

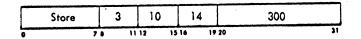

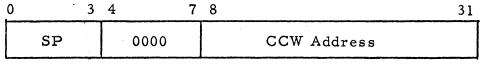

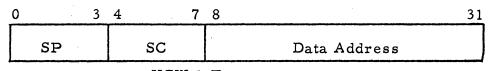

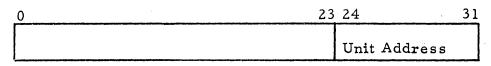

Channel Address Word - Successful execution of START I/O causes the channel to fetch a channel address word (CAW) from the main-storage location 72. The CAW specifies the byte location in main storage where the channel program begins.

Figure 15 shows the format for the CAW. Bits 0-3 specify the storage-protection key that will govern the I/O operation. Bits 4-7 must contain zeros. Bits 8-31 specify the location of the first channel command word (CCW).

Figure 15. Channel Address Word Format

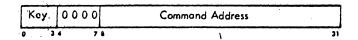

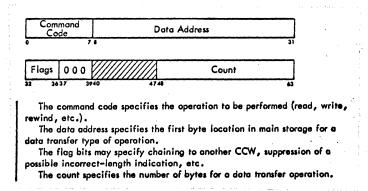

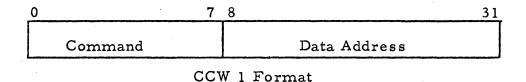

Channel Command Word - The byte location specified by the CAW is the first of eight bytes of information that the channel fetches from main storage. These 64 bits of information are called a channel command word (CCW). Only the START I/O instruction may cause the channel to fetch CCW's.

One or more CCW's make up the channel program that directs channel operations.

A channel command word can specify one of six commands:

Read

Write

Read Backward

Control

Sense

Transfer In Channel

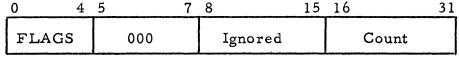

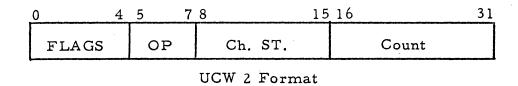

If more than one CCW is to be fetched, the CCW's are to be fetched sequentially, except when transfer in channel is encountered. Figure 16 shows the format for CCW's.

Figure 16. Channel Command Word Format

## Input/Output Commands

Read - The read command causes data to be read from the selected I/O device and defines the area of main storage to be used.

Write - The write command causes a write operation on the selected I/O device and defines the data in main storage to be written.

Read Backward - The read-backward command causes a read operation in which the characters are read from the external document in reverse order by the I/O device. Bytes read backward are placed in descending main storage locations.

Control - The control command contains information used to control the selected I/O device. This control information is called an order. Order information may be entirely contained in the command code, or the control command may provide a data address and byte count for additional order information in main storage such as the address of a particular disk storage track.

Orders are peculiar to the particular I/O device in use; orders can specify such functions as rewinding a tape unit, loading a tape cartridge, or line skipping on a printer. A control command may cause mechanical motion by an I/O device, or it may specify a function altogether electronic in nature, such as setting the recording density for a tape unit operation.

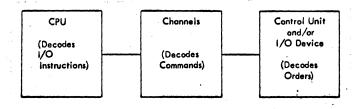

The general relationship of I/O instructions, commands, and orders is shown in Figure 17.

Figure 17. Relationship of I/O Instructions, Commands, and Orders

Sense - The sense command specifies the beginning main storage location to which sense information is transferred from the selected control unit. One or more bytes of sense data may be specified, depending upon the type of I/O device. The sense data provides detailed information concerning the selected I/O device, such as a stacker-full condition of a card reader or a file-protected condition of a reel of magnetic tape on a tape unit. Sense data have significance peculiar to the type of I/O device involved.

Transfer in Channel - The transfer-in-channel (TIC) command specifies the location of the next CCW to be fetched and used by the channel. The TIC command is used whenever the programmer wants to specify a CCW that is not located at the next higher double word location in main storage. The TIC command permits a programmer to cause execution of any CCW, including a CCW immediately preceding a TIC command, except that the channel will not permit a TIC command to specify execution of another TIC command. Also, the CAW may not address a TIC command.

Input/Output Termination - Input/output operations terminate with the device and channel signalling end of operation and a request for an I/O interruption.

A command can be rejected during an attempt to execute a START I/O, however, by a busy condition, by a channel programming error, etc. The condition code set in the PSW by an unsuccessful START I/O instruction will indicate one of the following: that a channel status word (CSW) has been stored to detail the conditions that precluded initiation of the I/O operation, that the equipment is busy, or that the addressed equipment is not operational.

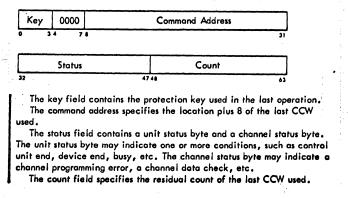

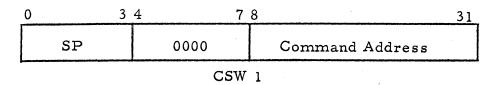

Channel Status Word - The channel status word (CSW) provides information about the termination of an I/O operation. It can be formed or reformed by START I/O, TEST I/O, HALT I/O or by an I/O interruption. The instruction TEST CHANNEL does not affect the CSW. Figure 18 shows the CSW format.

Figure 18. Channel Status Word Format

Input/Output Interruptions - Input/output interruptions are caused by termination of an I/O operation or by operator intervention at the I/O device. An I/O interruption stores the current PSW in the I/O old PSW location, and places the I/O new PSW in control of the system. The I/O new PSW, when made current by an I/O interruption, may cause CPU interrogation of the channel status word, or take whatever action is considered appropriate by the programmer.

An I/O interruption request may be initiated by an I/O interruption condition in a device, a control unit, or a channel. When a channel has multiple I/O interruption requests pending, it establishes a priority sequence for them before initiating an I/O interruption request to the CPU. Conditions responsible for I/O interruption requests remain pending in the I/O devices or channels until they are accepted by the CPU.

# 2.3.10 System Control Panel

The system control panel provides the switches, keys, and lights necessary to operate and control the system. The need for operator manipulation of manual controls is held to a minimum by the system design and the governing supervisory program. The result is fewer and less serious operator errors.

System Control Panel Functions - The main functions provided by the system control panel are the ability to: reset the system; store and display information in main storage, in registers, and in the PSW; and load initial program information.

System Reset - The system-reset function resets the CPU, the channels, and on-line control units and I/O devices. In general, the system is placed in such a state that processing can be initiated without the occurrence of machine checks, except those caused by subsequent machine malfunction.

Store and Display - The store-and-display function permits manual intervention in the progress of a program. The function may be provided by a supervisory program in conjunction with proper I/O equipment and the interrupt key. Or, the system-control-panel facilities may be used to place the CPU in the stopped state, and then to store and display information in main storage, in general and floating-point registers, and in the instruction-address portion of the PSW.

Initial Program Loading - The initial-program-loading (IPL) procedure is used to begin or renew system operation. The load key is pressed after an input device is selected with the load-unit switches. This causes a read operation at the selected input device. Six words of information are read into main storage and may be used for reading more information into any part of main storage. Upon completion of the IPL read operation, the double word from location 0 is made the current PSW for subsequent control of the system.

The system controls are divided into three sections: operator control, operator intervention, and customer engineering control.

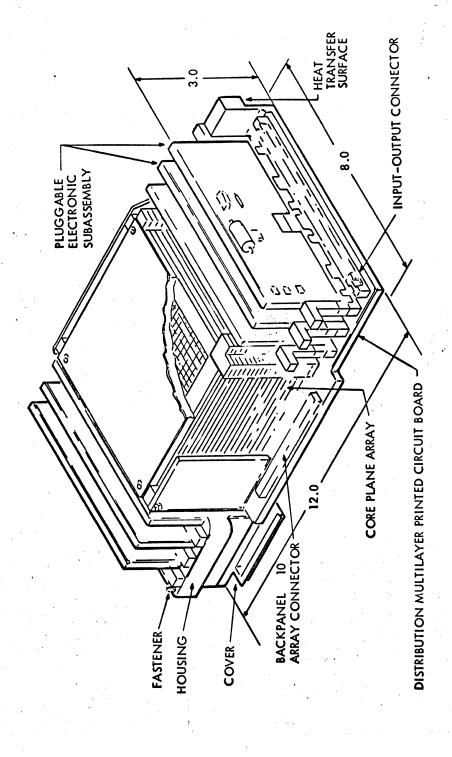

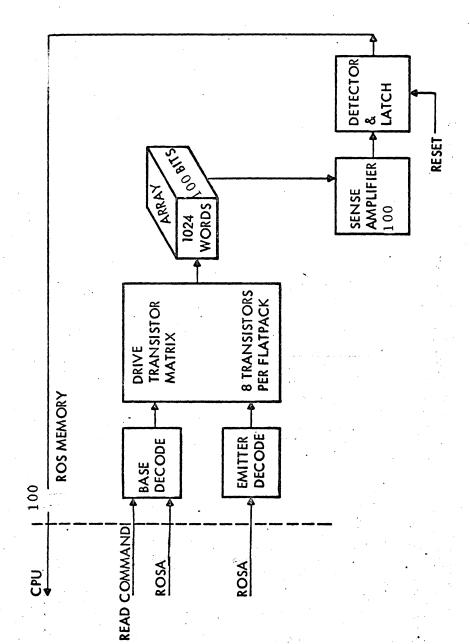

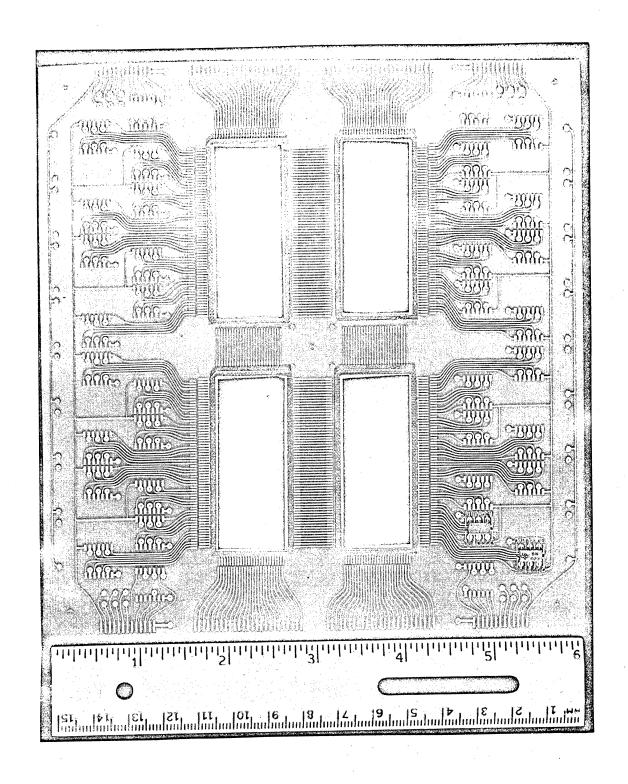

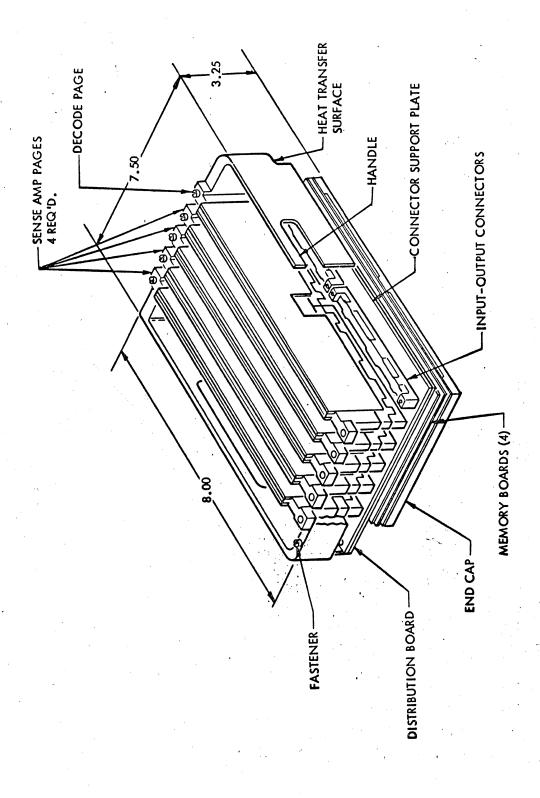

Operator Control Section - This section of the system control panel contains the operator controls required when the CPU is operating under supervisory program control.