Reference Manual

704-709-7090 Programming Package

for the IBM 7030 Data Processing System

Reference Manual

704-709-7090 Programming Package for the IBM 7030 Data Processing System The program descriptions in this manual are considered preliminary and subject to future revision. Revisions will reflect changes in the programs and correction and clarification of details.

Strap-1 was produced by the Los Alamos Scientific Laboratory. The chapter describing Strap-1 was prepared by IBM, but includes many descriptions and examples supplied by Los Alamos personnel. The Simulator programs and write-up were produced by IBM.

Neither IBM nor Los Alamos guarantee the accuracy of the Strap-1 and Simulator programs. Furthermore, neither IBM nor Los Alamos assume any responsibility for errors resulting from the use of these programs.

# CONTENTS

| STRAP-1                                                             |       |       |      |      |       |     |     |     |   |   | 5  |

|---------------------------------------------------------------------|-------|-------|------|------|-------|-----|-----|-----|---|---|----|

| STRAP CODING FORM                                                   |       |       |      |      |       |     |     |     |   |   | 5  |

| EXPRESSION OF MACHINE INS                                           | TRU   | CTI   | ONS  |      |       |     |     |     |   |   | 6  |

| Symbolic Instruction Formats .                                      |       |       |      |      |       |     |     |     |   |   | 6  |

| Data Description (dds)                                              |       |       |      |      | •     |     |     |     |   |   | 8  |

|                                                                     |       |       |      |      |       |     |     |     |   |   | 9  |

| Mnemonics                                                           |       |       |      |      |       |     |     |     |   |   | 9  |

| Arithmetic Expressions                                              |       |       |      |      |       |     |     |     |   |   | 11 |

| System Symbols                                                      |       |       |      |      |       |     |     |     |   |   | 14 |

| Variable-in-Number Field Form                                       | nat . |       |      |      |       |     |     |     |   |   | 16 |

|                                                                     |       |       |      |      |       |     |     |     |   |   |    |

| PSEUDO-OPERATIONS                                                   |       |       |      |      |       |     |     |     |   |   | 17 |

| Pseudo-Operations that Create S                                     | Stora | age : | Elen | ents | 3     |     |     |     |   |   | 17 |

| Entry Mode in Data Definition St                                    | ater  | nent  | s    |      |       |     |     |     |   |   | 19 |

| Entry Mode in Data Definition St<br>The Form of D in a Data Definit | ion S | State | men  | ıt   |       |     |     |     |   |   | 23 |

| Pseudo-Operations that Define S                                     | ymb   | ols   |      |      |       |     |     |     |   |   | 30 |

| Pseudo-Operations that Give Dir                                     |       |       |      |      |       |     |     |     |   |   | 32 |

|                                                                     |       |       |      |      | •     |     |     |     |   |   |    |

| IBM 7030 SIMULATION SYSTEM                                          | Ι.    | •     |      |      |       |     | •   | •   |   |   | 38 |

| PROGRAMMER'S NOTES .                                                |       |       |      |      |       |     |     |     |   |   | 38 |

| Setting Up Input for Strap-1 .                                      |       |       |      |      |       |     |     |     |   |   | 39 |

| Strap-1 Binary Output                                               |       |       |      |      |       |     |     |     |   |   | 39 |

| Card Formats Accepted by the S                                      | imu.  | lato  | r Lo | ader |       |     |     |     |   |   | 41 |

| Preparing a Binary Deck for the                                     |       |       |      |      |       |     |     |     |   |   | 42 |

| Input-Output Usage                                                  |       |       |      |      |       |     |     |     |   |   | 43 |

|                                                                     |       |       |      |      |       |     |     |     |   |   | 44 |

|                                                                     |       |       | •    | •    |       | •   |     | •   |   |   |    |

| OPERATOR'S NOTES                                                    |       | _     |      |      |       |     |     |     |   |   | 47 |

| Copying Tape with the System Ta                                     |       |       |      |      |       |     |     | :   |   | • | 47 |

| Assembly Using Strap-1                                              |       |       |      |      |       |     |     | :   |   | • | 48 |

| Simulating a 7030 Program .                                         | •     |       |      | •    | :     |     |     |     | • | • | 49 |

| Summary of Sense Switch Setting                                     |       |       |      |      |       |     | :   |     | • | • | 53 |

| Summary of Stops                                                    |       |       | •    |      |       |     | •   | •   | • | • | 54 |

| building of beops                                                   | •     | •     | •    | •    | •     | •   | •   | •   | • | • | 94 |

| APPENDIX A; Strap-1 Mnemon                                          | ics . |       |      |      |       |     |     |     |   |   | 56 |

| APPENDIX B; Strap-1 Pseudo-                                         | Opei  | ratio | ns   |      |       |     |     |     |   |   | 59 |

| APPENDIX C; Symbolic Descrip                                        | ptior | ıs aı | nd M | nem  | onics | for | IBM | 703 | 0 |   | 60 |

| APPENDIX D: Error Marks                                             | -     |       |      |      |       |     |     |     | - | • | 60 |

STRAP-1 is a symbolic programming system for the IBM 7030 which utilizes a 704 with 32,768 word capacity for assembly. It is a planned predecessor of Strap-2, a more elaborate programming system for the 7030 which is to use the 7030 instead of the 704 for assembly. Because Strap-1 is a planned subset of Strap-2, the specifications defined here are applicable to both Strap-1 and Strap-2.

Strap-1 specifications are divided into three categories: Category 1 pertains to the Strap coding form. In this category a form is defined that conveniently allows for the expression of both machine instructions and pseudo-instructions that direct the assembler itself. Category 2 pertains to the expression of symbolic machine instructions. In this category, definitions are made covering symbolic instruction formats, the fields which make them up, and the various mnemonics, classes of symbols, and numbers that may be used in fields. Category 3 pertains to the expression of the compiler's pseudo-instructions. In this category pseudo-instruction mnemonics, formats, and addresses are defined.

### STRAP CODING FORM

The coding form is directly related to the instruction card form. Both have 80 columns and are divided into 4 fields. These four fields and their respective positions are:

| l<br>CLASS | 2<br>NAME | 9 | 10 72<br>STATEMENT | 73 80 IDENTIFICATION |

|------------|-----------|---|--------------------|----------------------|

|            |           |   |                    | ·                    |

|            |           |   |                    |                      |

|            |           |   |                    |                      |

|            |           |   |                    |                      |

|            |           |   |                    |                      |

### STRAP CODING FORM

The purpose of each field is:

- 1. Class (1 column): to identify the card format (binary, decimal, symbolic, etc.).

- 2. Name (8 columns): to identify the statement.

- 3. Statement (63 columns): to express a machine instruction or a pseudo-instruction.

- 4. Identification (8 columns): to identify the card.

Card identification (columns 73-80) is reproduced on the listing, but does not contribute any information to the assembly program for translating instructions.

# EXPRESSION OF MACHINE INSTRUCTIONS

Machine instructions are written symbolically on the coding form described previously. They are usually entered one per line, according to a prescribed format that varies with the type of instruction operation. The instructions are written with fixed mnemonic operation codes.

Symbolic instructions are divided into fields (operation, address, offset, etc.) by commas. These fields may be stated within the general symbolic forms of the system, and, when so stated, constitute symbolic expressions. The order and manner in which such symbolic expressions are written in specifying the elements of any particular instruction are dictated by the symbolic instruction format; that is, a general type that provides for the expression of a whole class of particular machine instructions. Major fields may be further divided into subfields or modified by expressions contained in parentheses, such as index register specifications, secondary operations in progressive indexing, and so on.

- 1. A 11-0 double punch (;) is used to imply the end of a statement, so that multiple statements may be written per line. The number of instructions that may be written on one line is limited only by the number of columns available in the statement field of the card. The symbol in the name field of a card having more than one instruction in the statement field is associated with the first instruction only. The remaining instructions are treated as if they appeared on separate cards having blank name fields.

- 2. A single instruction cannot be continued from one card to another.

- 3. A comment may follow any instruction. A comment is initiated by the symbol ' (an 8-4 double punch) and is terminated either by the end of the card or by a;. Thus, the character; may never be used in a comment. A' in the name field causes the whole card to be treated as a comment; it will be printed on the listing but will not otherwise affect the assembly.

#### SYMBOLIC INSTRUCTION FORMATS

Symbolic instructions are entered in the statement field. Within this field, variable length operation codes and address expressions are separated by commas and form subfields. A variable length modifier to either an operation or an address is enclosed in parentheses and attached to the modified subfield. Blanks have no meaning in any field except to indicate the spacing desired on the printed output listing. Blank cards are ignored. The twelve symbolic instruction formats for Strap-1 are:

|    | Format Type                                        | Operation                                |

|----|----------------------------------------------------|------------------------------------------|

| 1. | OP(dds), A <sub>18</sub> (I)                       | Floating point                           |

| 2. | OP, A <sub>19</sub> (I)                            | Miscellaneous, unconditional branch, SIC |

| 3. | $OP, J, A_{19}(I) \underline{or} OP, J, A_{18}(I)$ | Direct index arithmetic                  |

| 4. | OP, J, A <sub>19</sub> or OP, J, A <sub>18</sub>   | Immediate index arithmetic               |

| 5. | OP, J, B <sub>19</sub> (K)                         | Count and branch                         |

| 6. | OP, B <sub>19</sub> (K)                            | Indicator branch                         |

| 7. | $OP(dds)$ , $A_{24}(I)$ , $OF_{7}(I')$             | VFL arithmetic, connect, convert         |

| 8. | $OP_1(OP_2)(dds), A_{24}(I), OF_7(I')$             | Progressive indexing                     |

| Format Type                                          | Operation                 |

|------------------------------------------------------|---------------------------|

| 9. OP, J, A <sub>18</sub> (I), A' <sub>18</sub> (I') | Swap, transmit full words |

| 10. OP, A <sub>24</sub> (I), B <sub>19</sub> (K)     | Branch on bit             |

| 11. $OP_1(OP_2), A_7(I), CW_{18}(I')$                | Input-output              |

| 12. LVS, J, A, A', A'', A''',                        | Load value with sum       |

Definitions of the above format symbols are:

| 1.  | OP and OP <sub>1</sub> | Primary instruction operation.                                   |  |  |

|-----|------------------------|------------------------------------------------------------------|--|--|

|     | $oP_2$                 | A secondary operation permitted only in progressive indexing     |  |  |

|     | ~                      | and input-output.                                                |  |  |

| 3.  | $A_n$                  | An "n" -bit data address.                                        |  |  |

| 4.  | B <sub>19</sub>        | A 19 -bit branch address.                                        |  |  |

| 5.  |                        | A 4-bit index address where (0) signifies no indexing and (1.)   |  |  |

|     |                        | to (15.) signifies indexing by the corresponding index register. |  |  |

| 6.  | K                      | A 1-bit index address where no modification (0) or modifica-     |  |  |

|     |                        | tion by index register 1 (1.) are the only possibilities.        |  |  |

| 7.  | $OF_7$                 | A 7-bit offset field.                                            |  |  |

| 8.  | dds                    | Data description (see "Data Description").                       |  |  |

| 9.  | J                      | A 4-bit index address that refers to an index register as an     |  |  |

|     |                        | operand. Here (0) refers to index register 0, word 16.           |  |  |

| 10. | A7                     | A 7-bit input-output channel address.                            |  |  |

| 11. | CW <sub>18</sub>       | An 18-bit control word address.                                  |  |  |

|     | LVS                    | Refers to one specific operation: Load Value with Sum            |  |  |

| 13. | primes                 | Used to distinguish otherwise identical fields in a format.      |  |  |

|     |                        |                                                                  |  |  |

There is a general right-to-left drop-out order for all fields separated by commas. For example, a VFL instruction (format 7 above), for which the offset and its index modifier are zero, is written:

The comma is the major separator for the symbolic instruction types. If there are less than the maximum number of major symbolic fields in a given instruction expression (as indicated by the comma count), the instruction is compiled as if the missing fields contained zeros and had been added at the end of the statement. Such fields, whose contents are implied in a standard way by the omission of any explicit specification, are called null fields. A null field is always compiled as a zero, with the exception (indicated under "Data Description") of those subfields of a data description which express mode and byte size. Within a major field, a parenthesized subfield may be made null by omission. Thus, in the VFL example above, if the main index designation were to be zero but the offset and its index modifier (which in the hardware also modifies field length and byte size) were both to be one, the instruction could be written:

A major field may be null, even though other non-null fields follow it. Such is the case if nothing but the comma denoting the field termination is written. Thus, in the example just shown, if the offset and its modifier were both to be one but the principal address and its modifier were both to be zero, the instruction could be written:

# DATA DESCRIPTION (dds)

The small letters "dds" enclosed in parentheses in the special instruction formats stand for the data description field. This field is established by specifying:

- 1. M use mode

- 2. L field length, and

- 3. BS byte size

These three entries appear in the above order within parentheses and are separated by commas, thus: (M, L, BS).

A data description given with any of the four data entry or data reservation pseudo-operations (DD, DDI, SYN, and DR) is attached to the symbol in the name field, and is automatically invoked whenever that symbol appears in the principal address field of an instruction. When a string of symbols is added in an address field, the <u>last</u> symbol written is the one whose data properties control those of the instructions. When the data description is specified explicitly as a modifier to the operation code in the two machine instruction formats where it applies (VFL and floating point), it overrules any other data description derived from a symbolic address. Thus, in straightforward coding, it is unnecessary to write a data description in machine operations.

A description of the method by which a data description may be attached to the symbol that names a piece of data is given under "Data Definition."

There are seven fixed use mode designators:

- 1. N Normalized Floating Point

- 2. U Unnormalized Floating Point

- 3. B Binary

- 4. BU Binary Unsigned

- 5. D Decimal

- 6. DU Decimal Unsigned

- 7. P Properties Mode

The mnemonic "P" in the mode field of a data description has the following meaning:

# (P, RIVER)

implies in an instruction that the data description associated with the symbol RIVER is to be invoked as if it had been written out explicitly. Thus, in an instruction, the dds of RIVER overrules anything implied by the symbol in the major address field. The P mode can be used only with legal machine instructions, never with a pseudo-operation.

Within a data description field, the usual right-to-left drop-out order and null field conventions hold (except, as indicated, that the mode field may not be null), so that a data description may appear in any of the following four forms:

(M) Field length and byte size are null

(M, L) Byte size is null

(M, BS) Field length is null

(M, L, BS)

If the field length is null, a field length of 0 (effectively 64, except in the case of immediate VFL operations, where it is 24) is compiled. If the byte size is null, the compiled byte size is a function of the mode:

| Mode_   | Standard Byte Size                    |

|---------|---------------------------------------|

| D or DU | 4                                     |

| В       | 1                                     |

| BU      | 8                                     |

| N or U  | Fixed format of 64 bits; field length |

|         | and byte size not appropriate.        |

Cases can arise from programmer errors in which a data description and an operation are not mutually consistent. In this case, the operation overrules. If there is no way to obtain a data description from either the symbolic address or an explicit data description field, three cases arise:

- 1. The operation symbol can stand for either floating point or VFL operations (+,-,\*,/). The operation is assembled as a VFL operation with data description (BU, 64, 8).

- 2. The operation symbol can stand for a VFL operation only (M+1). It is assigned a data description (BU, 64, 8). If VFL immediate, (BU, 24, 8) is assigned.

- 3. The operation can stand for a floating point operation only (-A, \*NA). The operation is assembled as normalized floating point, except for E+1 and its modified forms, which are made unnormalized unless overruled.

An error mark will be printed on the listing in any of these cases. (See description of error flag ''M'' in Appendix D.)

# MNEMONICS

A complete list of all machine mnemonics is included in Appendix A. Both operation codes and system symbols are included in the list.

A complete list of Strap-1 pseudo-operation mnemonics is given in Appendix B.

# NUMBERS AND SYMBOLS

Two different number systems, in general, run through the Strap-1 language: the ordinary system of real numbers, and a bit-address numbering system. The ordinary real numbers are restricted in all non-data fields to being integers. Real numbers that are not integers may be entered as data, but they may not take part in arithmetic expressions nor may they be symbolized, so that the general forms of the language are actually limited to integers and bit addresses.

A bit address is a style of writing a machine address; it consists of a pair of integers separated by a period. The integer to the left of the period specifies a word address, and the integer to the right of the period specifies a bit address. Thus, 6.32 is the decimal equivalent of either a 19- or 24-bit binary address specifying bit 32 of storage location 6--the bit preceded by exactly six and one-half storage words. (Note that only the presence of the period distinguishes a bit address from an integer.)

Example: 505.17 = 500.337 = 0.32337

As the name "bit address" implies, the two integers are converted to and carried as 24-bit binary integers, such as are appropriate to the address fields of VFL instructions. When used in the address field of an instruction for which a shorter address is appropriate, a bit address is truncated to the correct length and inserted. The location counter contains a bit address. There is no limit on the size of the pair of integers in a bit address except that  $64 \times 10^{-24}$  x word address portion + bit address portion =  $10^{-24}$ .

Thus, the address designation A(I) has two possible meanings:

- 1. If I is a bit address, then it designates an index word and is compiled in the so-called I field.

- 2. If I is an integer, then an address equal to A plus I times the field length of A is compiled.

A symbol is any sequence of six or fewer alphabetic and numeric characters conforming to the following conditions:

- 1. It contains only alphameric characters.

- 2. Its first character is specifically alphabetic.

- 3. It appears in the name field of an instruction, by virtue of which it is "defined" and is assigned a value that is either a 24-bit binary address or an integer, or occasionally both.

A given symbol may appear in the name field only once. The name of an ordinary machine instruction or data entry pseudo-operation is set equal to the value of the assembly program location counter at the point of its appearance in the code.

Symbols that identify storage elements in the object program are automatically assigned bit addresses that locate these storage elements. A symbol may, however, be given the value of an integer through the use of a "synonym" pseudo-operation. Thus, in general, both bit addresses and integers may be symbolized. The term "integer" is used to denote either an integral number or a symbol that takes on an integral value.

Symbols that name instructions themselves are automatically assigned data descriptions. Specifically, instruction-naming symbols are given field lengths equal to the lengths of the particular instructions named (either 32 or 64), and are defined as unsigned binary with byte size 8.

A programmer symbolized field is a field that may contain programmer symbols and/or system symbols. Of the fields shown in the instruction formats, all may contain programmer symbols except the operation field and the mode field of a data description.

Integers in programmer symbolized fields are always converted to binary. They are limited in length to the length of the field in which they are to be inserted. An integer larger than 24 bits cannot be symbolized.

Bit addresses and symbols for bit addresses are intended primarily for use in address fields of machine instructions. Integers and symbols for integers are intended primarily for use in fields for which they seem more appropriate: counts, shifts, field length, byte size, and so on.

#### ARITHMETIC EXPRESSIONS

Arithmetic expressions in Strap-1 may be composed of addition and/or subtraction of any combination of symbols, integers, and bit addresses. Although integers and bit addresses are generally used in different fields, algebraic addition of the two types of numbers is defined; the result is a function of the type of field into which the sum is to be inserted.

Integers add into all fields as integers; that is, the units digit adds into the low-order position of the <u>field</u>. Symbols for both bit addresses and integers are signed numbers. The number of additive operands in an arithmetic expression is limited only by the space available on the card.

Example: SAM-JOE+FRED-72.386+5,

This example, where SAM and JOE are defined as bit addresses and FRED is an integer, is, in general, a legal address. The data description of the <u>final</u> symbol, FRED, applies to the whole combination.

If the field for which the address is intended is signed (for example, the value field of XW or VF), the sign will be placed in the correct bit and the true value will be compiled.

If the final result is negative and the n-bit field for which it is intended is unsigned, a 2's complement is formed and inserted, except in the case of EXT (L, L') where |L| and |L'| are used. For example, in the case of the 7-bit offset field of a symbolic instruction, negative numbers may be used to describe the low-order position of the data field in relation to the left rather than the right end of the accumulator. Thus, the 128 bits of the accumulator, proceding from left to right, bear the offset addresses "127, 126,....1,0" or, alternatively, of "-1, -2,....-127, -128." The programmer is reminded that a 2's complement must be used with care on the 7030 in order not to cause the address invalid indicator to be turned on.

A positive result is inserted as a true value.

Either an integer or a bit address, or a combination of the two, may appear in any programmer symbolized field with five restrictions:

- 1. The "I" or "K" index field must contain at least one bit address term.

- 2. The entries in an array specification must not contain any bit address terms. In EXT (L, L'),(L, L') is not considered an array specification (See "Pseudooperations that Direct the Compiler" for a discussion of DR and the specifications of arrays).

- 3. A period may not appear in the field of a parenthetical integer entry. A bit address appearing in such a field is treated as a 24-bit integer. For example, V+I, (.18) 4.32 is not allowed, but V+I, (.18)9 is.

- 4. No arithmetic may appear in the name field, which is reserved entirely for the definition of symbols. Only one symbol per statement may be defined in this manner.

- 5. Arithmetic expressions may not appear in the operation code part of the operation field, the mode subfield of the data description field or any entry mode field. These exceptions are reserved for designations whose meanings to the compiler are absolute and may not be symbolized.

# Rules for Combining Integers and Bit Addresses

The following rules describe the method by which bit addresses and integers are truncated and added:

- 1. The numbers are shifted with respect to each other by the proper amount. See the following diagram.

- 2. The numbers are assumed to be signed 24-bit integers before the operation. Addition is algebraic.

- 3. The result is complemented if necessary.

- 4. The result is truncated if necessary.

- 5. The result is inserted into the correct position in the operation word.

Although the diagrams show the final sum truncated to the appropriate length, the bits are not actually discarded unless they fall outside the address field of the instruction. Some operations do not use all of the space available in their address fields (transmit, input-output select), and in these cases bits may be placed in the unused portions.

An error indication is given if non-zero bits are discarded when truncation occurs (see explanation of "V" error flag in Appendix D), except in the case of index fields where a "1" bit in the fifth position from the right(in the "16" position) is discarded without error indication.

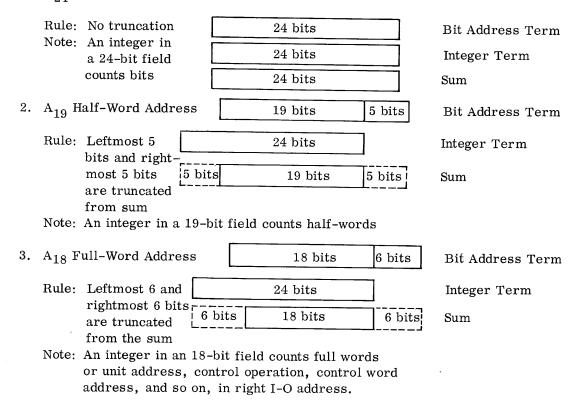

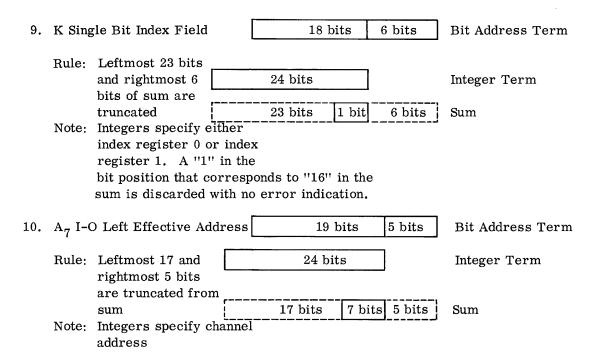

Truncation occurs for particular fields in the following manner:

# 1. A<sub>24</sub> Bit Address

| 4. | $A_{11\pm}$ Signed 11-Bit Address                                                                                                                                                                                                | 24 bits                       | Bit Address Term    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|

|    | Rule: Leftmost 13 bits                                                                                                                                                                                                           | 24 bits                       | Integer Term        |

|    | are truncated from the sum. Rightmost 11 bits plus sign are placed in leftmost 12 bits of address field of shift and Add Immedi to Exponent instructions Note: Integer counts number number of bits to be ad floating point word | s<br>of bits in shift or      | Sum                 |

| 5. | OF <sub>7</sub> Offset                                                                                                                                                                                                           | 24 bits                       | Bit Address Term    |

|    | Rule: Leftmost 17 bits of sum are truncated                                                                                                                                                                                      | 24 bits  17 bits 7 bits       | Integer Term Sum    |

|    | Note: Integers count number<br>of bits of offset<br>Bit address 1.32 = .96 = integ                                                                                                                                               |                               |                     |

| 6. | FL <sub>6</sub> Field Length                                                                                                                                                                                                     | 24 bits                       | Bit Address Term    |

|    | Rule: Leftmost 18 bits of sum are truncated Note: Integers count length                                                                                                                                                          | 24 bits 18 bits 6 bits        | Integer Term<br>Sum |

|    | of field in bits Bit address 1.0 = .64 = 0 not                                                                                                                                                                                   | error marked                  |                     |

| 7. | BS <sub>3</sub> Byte Size                                                                                                                                                                                                        | 24 bits                       | Bit Address Term    |

|    | Rule: Leftmost 21 bits of sum are truncated                                                                                                                                                                                      | 24 bits                       | Integer Term        |

|    | Note: Integers count byte size in bits                                                                                                                                                                                           | 21 bits 3 bits                | Sum                 |

|    | .8 = 8 = 0 not error marked                                                                                                                                                                                                      |                               |                     |

| 8. | I, J 4-Bit Index Fields                                                                                                                                                                                                          | 18 bits 6 bits                | Bit Address Term    |

|    | Rule: Leftmost 20 bits and rightmost 6 bits of sum are truncated                                                                                                                                                                 | 24 bits 20 bits 4 bits 6 bits | Integer Term        |

|    | Note: Integers represent index register number.  A "1" in the bit positio immediately to the left of the final sum field is discarded with no erro indication.                                                                   | n<br>:                        | 7                   |

#### SYSTEM SYMBOLS

System symbols are symbols whose values are fixed in the compiler. They are identified in programmer symbolized fields by the appearance of the special prefix character \$ (which, as one of the non-alphameric characters, can never appear in a programmer symbol), followed by five or fewer alphabetic or numeric characters. System symbols may appear in arithmetic expressions in programmer symbolized fields where, in cases where restrictions apply, they can be considered the same as numeric entries because their values are immediately available to the compiler.

All system symbols that represent the addresses of special registers in storage (\$AOC, the All Ones Counter) or special bits in storage (\$LC, the Lost Carry indicator) are bit addresses. All others are integers or real numbers.

The appearance of the \$ character alone makes for a special system symbol that provides a standardized substitute in place of a name for the current statement. That is, the character \$ is a bit address which, in any particular statement where it appears, functions as if it had been defined by being written in the name field of that statement. Because it represents the value of the location counter when the instruction is encountered by the compiler (if the instruction actually compiles space in the program), the appearance of the \$ as follows:

B, \$-2.

means "Branch to the instruction which begins two full words before this branch instruction." In another illustration:

B, \$+.32

the meaning is "Branch to the next instruction.", effectively a "no operation."

Another special use of the \$ character is to prefix any operation code in this manner: \$OP. This directs the compiler to suppress any error indications that arise in connection with the compilation of this statement.

The system symbols are:

# 1. Index Registers

\$0 through \$15, identical to \$X0 through \$X15, represent index registers 0 through 15, addresses 16.0 through 31.0 in storage. For example, \$5 (or \$X5) will be correctly replaced by the index field 5 if it appears in an I or J field, or by the address 21.0 if it appears in an address field.

# 2. Special Registers

The mnemonics for the system symbols that stand for special registers in the 7030 are listed below with the bit address and name for each.

| Bit Address | Mnemonic | Name                      |

|-------------|----------|---------------------------|

| 0.0         | \$Z      | Word number zero          |

| 1.0         | T        | Interval timer            |

| 1.28        | \$TC     | Time clock                |

| 2.0         | \$IA     | Interruption address      |

| 3.0         | \$UB     | Upper boundary            |

| 3.32        | \$LB     | Lower boundary            |

| 3.57        | \$BC     | Boundary control          |

| 4.32        | MB       | Maintenance bits          |

| 5.12        | \$CA     | Channel address           |

| 6.0         | \$CPU    | Other CPU                 |

| 7.17        | \$LZC    | Left zeros count          |

| 7.44        | \$AOC    | All ones count            |

| 8.0         | \$L      | Left half of accumulator  |

| 9.0         | \$R      | Right half of accumulator |

| 10.0        | \$SB     | Sign byte                 |

| 11.0        | \$IND    | Indicator register        |

| 12.20       | \$MASK   | Mask                      |

| 13.0        | \$RM     | Remainder register        |

| 14.0        | FT       | Factor register           |

| 15.0        | \$TR     | Transit register          |

#### 3. Indicator Bits

The symbol for any indicator bit may be prefixed with a dollar sign and placed in a programmer symbolized field, where it will represent the correct bit address in word 11. Note that when the indicator symbols are inserted in the "branch on indicator" instructions, the dollar sign prefix is omitted. System symbols for indicator bits are listed in Appendix A.

# 4. Input-Output Addresses

Since the actual numeric addresses which are to identify particular I-O units and channels may be chosen arbitrarily, system symbols that represent integers are provided for use in addressing I-O equipment. The numeric values of members of this set of system symbols, unlike the values of all other system symbols, may vary from

one installation to another in order that RDR, for example, may represent the card reader channel address independently of what that address, in any particular installation, may be. I-O system symbols are:

| Symbol          | Meaning                                     |  |  |

|-----------------|---------------------------------------------|--|--|

| \$PCH           | Punch (Channel Address)                     |  |  |

| \$PRT           | Printer (Channel Address)                   |  |  |

| \$RDR           | Reader (Channel Address)                    |  |  |

| \$DISK          | Disk Unit (Channel Address)                 |  |  |

|                 | Note: The arcs of a disk may be addressed   |  |  |

|                 | by any legal symbolic integer expression    |  |  |

|                 | evaluated modulo $2^{12}$ to assure a valid |  |  |

|                 | arc address.                                |  |  |

| \$CNSL          | Console (Channel or Unit Address)           |  |  |

| \$TC1,TC2,\$TCK | Tape Channels 0, 1,,K                       |  |  |

If more than one punch, printer, console or any other input-output unit is attached to the machine, the same numbering system used in channel and tape addresses is adopted, where \$CONSL=\$CONSL0, and so on. Thus, one may have \$PRT0, \$PRT1, \$PRT2, etc.

At each installation's option, some system symbols representing equipment not included in the particular system at hand may elicit error flags in the listings.

# 5. Mathematical Constants

Four mathematical constants, useful in many scientific and engineering problems, can be represented by system symbols. The four system symbols and their real number values are:

| Mathematical Constant |

|-----------------------|

| е                     |

| $\log_{10}$ e         |

| $\log_{\mathbf{e}^2}$ |

| <b>₽</b>              |

|                       |

These four symbols can be used only in the data field of a DD statement using normalized floating-point mode. All of the system symbols in classes 1, 2, and 3 are bit addresses and are assigned standard data descriptions with mode binary unsigned, byte size 8, and a field length equal to the length of the register (or bit, in which case BS=1).

# VARIABLE-IN-NUMBER FIELD FORMAT

The Load Value with Sum (LVS) instruction may be written with a variable number of address fields, each of which actually picks out a single bit position within the LVS address field itself. For an LVS order, each address field may specify one of index registers 0 through 15. These fields are evaluated exactly as if they were regular index designator fields, so that index addresses may be specified in terms of either bit addresses or integers in the usual manner.

#### PSEUDO-OPERATIONS

In this section are itemized a number of operation codes provided for purposes of defining data and controlling and directing the assembly process itself. Because these codes do not directly produce machine instructions in the object program, the functions which they do trigger are referred to as "pseudo-operations."

The pseudo-operations are grouped according to class. There are two main classes of pseudo-operations:

- 1. Those that create storage elements.

- 2. Those that control the assembly process.

- a. Those that define symbols by assigning values that appear in the variable fields.

- b. Those that give directions to the compiler.

The name field of all pseudo-operations that neither create storage elements nor define symbols is ignored, with the exception of CNOP (see "Pseudo-Operations that Direct the Compiler").

# PSEUDO-OPERATIONS THAT CREATE STORAGE ELEMENTS

The following provide the basic means for defining and entering generalized data in the Strap-1 language:

| Mnemonic | Name                                      | Usage                                  |

|----------|-------------------------------------------|----------------------------------------|

| 1. DD    | $"DA\overline{TA} \overline{DE}FINITION"$ | (EM) DD (dds), D, D', D'',             |

|          |                                           | Where the bracketed dds is a           |

|          |                                           | data description prescribing the       |

|          |                                           | meaning of all succeeding numbers (D). |

|          |                                           | The numbers D are compiled in          |

|          |                                           | consecutive fields and any symbol      |

|          |                                           | appearing in the name field of the     |

|          |                                           | DD statement applies to the first      |

|          |                                           | such field                             |

The use of the pseudo-operation DD enables the programmer to enter data into a program in a variety of forms. Among the possibilities that exist are:

- a. Decimal to floating binary conversion, either normalized or unnormalized.

- b. Conversion of decimal fraction to binary fraction in fixed point.

- c. Integer to integer conversion from any of the radices 2 through 10 and 16 to a radix of either 2 or 10.

- d. Conversion of alphabetic information to binary coded form.

In the general form illustrated above, the field symbolized by (EM) represents the entry mode, a field which supplies information about the form in which data appear on the card (see "Entry Mode in Data Definition Statements").

The data description (dds) is identical in form and content to that described under "Data Description;" that is, to the data description that may be used when writing an individual instruction (except that the "P" mode is not permitted in this or any other pseudo-operation). Thus, a data description may be given with a number at the point of definition of the number itself, or may be given at the point of reference as part of an

instruction referring to the number. The relationship between these two different points of possible definition is as follows:

When the data description is given by a DD statement (or other data defining operation), the description is invoked whenever the symbol appearing in the name field of the DD statement is used in the principal address field of an instruction. The instruction mode and—in the case of a VFL order—the field length and byte size are supplied by this data description, which is logically affixed to the name of the DD statement.

Such a description set down at the point of symbol definition is overruled by a description appearing in an instruction referring to the symbol. Whenever an overruling description appears in the data description field of an instruction, the entire description which was given at the point of definition of the address symbol is overruled. Thus, the statement:

OP (BU), JOE

causes the binary and unsigned modifiers to be compiled along with an implicitly defined field length of 64 and a byte size of 8, regardless of the description occurring in the statement in which JOE appeared in the name field. Overruling is strictly local and applies only to the instruction at hand.

If symbols are used in defining either the field length or byte size subfields of a DD statement's data description, the symbols must be fully defined when the compiler encounters the DD statement on the second pass. This requirement is not imposed on the data description of an instruction because, in that instance, no assignment of storage space is dependent on the contents of the subfields.

The address fields, D, D', D'', etc. are all equivalent to each other. They are compiled sequentially as separate pieces of data, each having the data description specified, but the name specified in the name field is attached only to the first piece of data. The effect produced is exactly the same as if the entry mode, operation, and data description were repeated on separate cards with only one D field per card and blank name fields. If one wishes to name the separate entries D, D', D'', etc., it is necessary to punch each one on a separate card with its own name.

Programmer symbols may not appear in the main body of a D field; various letters in the main body of a D field have fixed meanings not subject to programmer control.

2. XW "INDEX WORD" XW, VALUE, COUNT, REFILL, FLAG

The location counter is rounded to the next full word. The contents of the four symbolic fields following the operation are converted and compiled in an index word format. FLAG denotes the machine field comprised of bits 25, 26, and 27. An expression in the flag field of an XW statement is therefore evaluated modulo  $2^3$ . The octal integer 4 written in the flag field turns on the index flag in the index word being compiled.

NOTE: Bit 24 of the word format is taken to be the VALUE sign position. A negative sign is interpreted in two's complement form in the usual way for all other fields.

# 3. VF "VALUE FIELD" VF, VALUE

The location counter is rounded to the next half word. The contents of VALUE are compiled as a 24-bit plus sign quantity in positions 0-24 of the next half word. The location counter stands at bit 25 at the end of the operation.

# 4. CF "COUNT FIELD" CF, COUNT

The location counter is rounded to the next <u>half</u> word. The contents of the count field are compiled as an 18-bit integer in positions 0-17. The location counter stands at bit 18 at the end of the operation.

5. RF "REFILL FIELD" RF, REFILL

This pseudo-operation is the same as CF, except Refill is substituted for Count.

NOTE: The last four operations (the index word pseudo-operations) defined above are given data descriptions by the compiler, as though they had been defined by DD statements. Specifically, the index elements created by these orders have had the following data descriptions affixed automatically, and cannot be overruled in the pseudo-operation statement:

| Operation     | Data Description |

|---------------|------------------|

| XW            | (BU)             |

| $\mathbf{VF}$ | (B, 25)          |

| CF or RF      | (BU, 18)         |

|               |                  |

6. CW "CONTROL WORD" CW(OP), ADDRESS, COUNT, CHAIN ADDRESS

The pseudo-operation CW employs a special symbolic format as illustrated above and defined initially under "Symbolic Instruction Formats." A set of secondary operations is provided—whose members are expressed as parenthesized secondary operations in the manner of (OP) above—for the purpose of providing mnemonics for control word functions:

|                                  | Multiple Bit | Chain Bit | Skip Flag |

|----------------------------------|--------------|-----------|-----------|

| CR "Count Within Record"         | 0            | 0         | 0         |

| CCR "Chain Counts Within Record" | 0            | 1         | 0         |

| CD "Count Disregarding Record"   | 1            | 0         | 0         |

| CDSC "Count Disregarding Record, |              |           | Ner       |

| Skip, and Chain'                 | 1            | 1         | 0         |

| SCR "Skip, Count Within Record"  | 0            | 0         | 1         |

| SCCR "Skip, Chain Counts Within  |              |           |           |

| Record''                         | 0            | 1         | 1         |

| SCD "Skip, Count, Disregarding   |              |           |           |

| Record''                         | 1            | 0         | 1         |

| SCDSC "Skip, Count, Disregarding |              |           |           |

| Record, Skip and Chain"          | 1            | 1         | 1         |

The location counter is rounded up to insure that the control word compiled will begin at a full word address. CW is assigned a data description of (BU, 64, 8).

# ENTRY MODE IN DATA DEFINITION STATEMENTS

The data description field represents a kind of generalized use mode for the data, in that properties specified in this field are translated into bits and numbers that are compiled into machine instructions referring to the data. A corresponding field called

the entry mode is available to specify properties which describe the source language information and its form, but which are not themselves compiled into the object program.

The entry mode may be employed in one of three ways.

Statement Entry Mode

(EM) DD (dds), D, D', D'', ...

An entry mode may be used to specify the properties of all data in a DD or DDI statement. When used in this fashion, it is enclosed in parentheses and appears before the DD or DDI operation code in the operation field. The mode is more general in form in its usage in connection with the data of a DD or DDI statement, as it may in this instance—but only in this instance—designate that alphabetic information is to be compiled. The two entry modes that may only appear as statement entry modes—that is, immediately before the operation code (of a DD or DDI statement)—are:

(Ax) Alphabetic Conversion

(AQ) DD (BU, 60, 6), DO NOT PANIC Q

The card code characters beginning with the one after the comma which terminates the operation field are converted to IBM tape BCD until the character "x" is reached. The end-of-statement character is not itself compiled. (Note that tape BCD is different from internal 704 BCD.) Blanks occurring within the field to be converted are retained and stored correctly. The characters are counted by Strap-1 and the location counter is properly advanced.

The byte size of converted characters may range from 1 through 12 in a DD statement, or 4 through 12 in a DDI statement, and is specified by the dds. Leading zeros are inserted for each byte where BS > 6; leading bits are truncated from each byte where BS < 6. The byte size compiled in an operation referring to the data is set to either the specified byte size or 8, whichever is smaller.

The statement terminating character "x" may be any legal card code character except:

) ' (8-4) ; (11-0) blank

Only one D field is allowed per statement.

(IQSx) Inquiry Station Conversion

The IQS entry mode operates in exactly the same fashion as the alphabetic entry mode, except that card code characters are converted to the 7-bit inquiry station code. Therefore, leading zeros are inserted where BS  $\gt$  7, and leading bits are truncated where BS  $\lt$  7.

Although the IQS code includes a large number of special characters, Strap-1 is limited to those which can be entered by means of IBM off-line card and tape equipment.

# Statement or Field Entry Modes

Some entry modes may be used either to specify the properties of all fields of a statement or to specify the properties of a specific field or fields in a statement. Statement entry modes and field entry modes may both appear in the same statement. When contradictory properties (for instance, two different radices) are implied by the statement and field entry modes, the field entry mode overrules for the case of the particular field on hand. Entry modes may not appear in a manner that causes parentheses within parentheses.

(Fn): The entry mode (Fn) implies that the data which follow are written in the decimal radix, are to be converted to binary, and may include a decimal fraction portion that is to be converted to a binary fraction of length n bits.

The "n" symbolizes a decimal integer that specifies the number of fractional bits desired to the right of the binary point when the number or numbers which follow are converted. (Fn) appears in DD or DDI binary mode statements only.

Radix Specifications: In any programmer symbolized field not enclosed by parentheses, numerical integers and bit addresses may be written in any radix from 2 through 10, or 16. The radix is specified by enclosing the appropriate integer, written in decimal, in parentheses at some appropriate point in the subfield. (Usually, but not always, the radix specifier is the first item to appear in the subfield.) The radix applies to the entire subfield unless it is reset before reaching the end. If no radix is specified, the base 10 is assumed. If used as a statement entry mode, the radix specified applies to the entire statement unless individual fields contain their own radix specifier, in which case the field entry mode overrules the statement entry mode for that field only.

In the case of data entry, the radix specifier can be used with integers only; a decimal point or floating point notation implies a radix of 10. The entry mode radix specifies the radix in which an integer is written on the card, but says nothing about the one to which it is converted.

Some examples of the use of the radix specifier are:

- 1. (8)573 34+50 (all numbers are in octal)

- 2. (2) 11011011100011.111100 (bit address written in binary)

- 3. (5) SAM 342 (the symbol SAM is not affected by the radix, having been previously converted to binary. The integer 342 is written in the number system of the base 5.)

- 4. (8)7436.(10)60+9 (the full word portion of this bit address is written in octal, whereas the bit address portion and the integer 9 are written in decimal.)

- 5. (2)DD(B, 16, 8), (10)-972, 111011110 (the first D field is written in decimal, the second one is in binary)

Field Entry Mode--Parenthetical Integer Entry

One entry mode in Strap-1 may never appear as a statement entry mode. By means of the parenthetical integer entry, any integer or pattern of bits may be stored in any position of an instruction or data entry field. The general format for this entry mode is:

(.n)  $A_{n+1}$

The symbol .n represents the bit address of the rightmost bit of the field into which the integer is to be entered. The integer  $A_{n+1}$  is formed as an unsigned n+1-bit field and added into the addressed instruction or data field by means of a logical OR into the leftmost n+1 bits.

The parenthetical integer entry is made by means of a logical OR so that it may be combined with other fields of the statement or other parenthetical OR fields. The first bit of the statement is counted as bit 0. Although the parenthetical field may cross field lines within a statement, it may not cross statement lines. Thus, if the bit address is specified as ".n", the parenthetical expression has a field length of n+1 and is evaluated modulo  $2^{n+1}$ . All parenthetical fields are regarded as unsigned, so that a negative number is compiled as the complement, re  $2^{n+1}$ , of the magnitude of the number.

This entry mode cannot be used in pseudo-operations that give instructions to the compiler (SLC, END). This mode must appear in a statement that compiles space in storage. It is a modification that may be appended to any D field or to any programmer symbolized field (or in place of such a field) which is not enclosed in parentheses. Thus, FL and BS may not contain a parenthetical entry.

In the case of an instruction, the position of the entry is determined by counting the bits of the whole instruction field, no matter in which subfield the integer entry may be appended. For example, in a VFL instruction so modified, OP,  $A_{24}(I)(.n)A_{n+1}$ , OF7 is exactly the equivalent of OP,  $A_{24}(I)$ , OF7(.n) $A_{n+1}$ . In the case of a DD pseudo-operation, the position of the parenthetical field is determined by counting bits of the D field in which it appears; i.e., from the previous comma forward. In any case, the integer entry must follow all other information in the field or subfield in which it appears, except for another parenthetical entry.

Although one entry could be made to serve in any single instruction, it is more convenient to write several different integer entry specifications when one wishes to place numbers in various positions in an instruction. Therefore, no limit is set on the number of consecutive entries which can be written together, except as imposed by the length of the statement field on the card.

Because the parenthetical entry is not permitted to cross statement lines, ".n" must be less than or equal to 31 in a half word instruction, and less than or equal to 63 in a full word instruction.

Example: E+I, (.8) 41 The integer 41 will be converted to binary and OR'ed into the leftmost 9 bits of the E+I instruction.

Radix designators are permitted in parenthetical OR fields, separated by commas from the bit address designation, and the two may be in any order. Thus, (.32,8) or (8, .32) signifies an octal field to be terminated at bit 32.

Parenthetical expressions may contain anything that goes in a normal address field (except periods), but may not have other information such as real numbers or alphabetic characters which are permitted in a DD or DDI statement. A data description associated with a symbol appearing in a parenthetical field has no effect in this usage of the symbol. All numbers appearing in a parenthetical field are converted to an internal binary format, never to decimal or floating point.

Example:

- 1. (.50,8)17 JOE + (10)4203(4, .22) 33303(.60)1030

- 2. (7)(.30)1265(.20)(10)138 (6)43(.10)553

Note that the radix does not have to be specified with the .n. If no radix is specified, the current operative radix is continued; it is not reset to 10. It is understood to be 10 if no radix has been previously specified in the field to which the general parenthetical integer entry is appended.

The radices which apply in the above examples are:

| Example | Number | Radix          |

|---------|--------|----------------|

| 1       | 17     | 8              |

| 1       | JOE    | does not apply |

| 1       | 4203   | 10             |

| 1       | 33303  | 4              |

| 1       | 1030   | 4              |

| 2       | 1265   | 7              |

| 2       | 138    | 10             |

| 2       | 43     | 6              |

| 2       | 553    | 6              |

|         |        |                |

All numbers that appear within parentheses are interpreted as decimal numbers.

# THE FORM OF D IN A DATA DEFINITION STATEMENT

All data fall under the category of one of the six use modes of the data description field: N, U, B, BU, D, DU. The numbers D, D', D'',... are expressed in the general form:

Decimal numbers are a special case; they may be written in fixed or floating point form, with or without a decimal point. The general form is:

$$\pm XX...X.X...XE \pm YYY$$

In this form E means that the number which precedes it is multiplied by 10 raised to the power which follows it. That is, 572.34E-57 means  $572.34\times10^{-57}$ . Overlapping facilities for specifying an exponent "Ei" are provided in the sense that the decimal point in the number itself also indicates a decimal exponent. If no decimal point is written, the number is assumed to be an integer. Thus, parts of the general form that are not necessary for writing a number may be omitted.

| a. | ±XXX              | integer                            |

|----|-------------------|------------------------------------|

| b. | ±XXX,XX           | decimal fraction                   |

| c. | $\pm XXXE\pm YYY$ | integer times power of 10          |

| d. | ±XXX. XXE±YYY     | decimal fraction times power of 10 |

A plus sign is understood if no sign is specified. The decimal point may be in any position in the number. The portion of the number above symbolized by X is limited in length to 15 digits; that symbolized by Y is restricted to a length of 3 digits (recall that floating point numbers in the 7030 are limited to a range of  $10^{308}$  to  $10^{-308}$ ).

Data entries may have other quantities following them which are identified and separated from the main number by declension characters. The declension characters, which are used for the insertion of specific fields, are:

# 1. Sign Byte Entry--Si

The letter S is used to enter information into the sign byte of data. The letter i represents an octal integer which is evaluated and OR'ed in with any sign byte previously calculated. Thus, if either the sign of the main number or i implies a negative sign bit in the sign byte, the sign byte sign position is made negative.

The sign byte generated depends on the byte size in accordance with the following table:

| Byte Size | Sign Byte |              |

|-----------|-----------|--------------|

| 1         | S         |              |

| <b>2</b>  | ST        |              |

| 3         | STU       | Z = zone bit |

| 4         | STUV      | S = sign bit |

| 5         | ZSTUV     | T)           |

| 6         | ZZSTUV    | U flag bits  |

| 7         | ZZZSTUV   | v J          |

| 8         | ZZZZSTUV  |              |

In a data definition statement where byte size 1 is specified, using sign byte entry S1 yields a negative sign, whereas if byte size 4 had been specified, S10 would yield a negative sign with zero flag bits.

# 2. Exponent Entry--Xi

The letter "X" may be used to enter any arbitrary information into the exponent of a floating point word. The decimal integer i is compiled as the machine exponent of a floating point number. It overrules and replaces the computed exponent, which is completely eradicated by the replacement process.

# Rules for Entering Data

The legal formats for entering data can be classified according to the use mode written in the data description field of the DD statement. In general, an element listed in the general format may be omitted if it is not needed to specify the data.

The data entries in a DD statement are restricted to real numbers. Bit addresses are not permitted. Integers are allowed as a special case of real numbers, but they may not be symbolized.

Floating point data are always compiled in addressable full-words; the location counter is rounded up, if necessary, to the next full-word address in order to accomplish this. This is an example of a general Strap-1 principle: a machine format that ordinarily depends in use on the fact that the 24-bit address of the lead bit ends in a string of zeros of some definite length causes the compiler to round the location counter appropriately. Thus:

- 1. Instructions always start at either half- or full-word bit addresses.

- 2. Indexing full- and half-word storage formats are forced to begin at full- and half-word addresses, respectively.

3. A floating point data block being reserved through use of a DR operation code (defined in "Pseudo-Operations That Direct the Compiler") is forced to begin at a full-word address. Moreover, when a field from an instruction format requires the truncation of the rightmost bits before compilation, a warning indication is given if significant bits are truncated (which can occur if an instruction addresses a format other than its natural one; e.g., if a floating point instruction addresses a VFL data element).

# Normalized Floating Point

Format: Name | DD(N), ±xx'''xx.x'''xxE±yyySn

The decimal number is converted to a normalized floating binary number consisting of an 11-bit signed exponent, a 48-bit fraction, and a 4-bit sign byte. If no sign byte has been entered by means of an S, the sign preceding the number is used with the flag bits set to zero. If a different binary exponent is desired, it can be entered following an X, as follows:

Format: Name DD(N), ±xx'''xx.x'''xxE±yyySnXzzz

### Examples:

a. DD(N), 54.73 E 4

$54.73 \times 10^4$  is converted to floating binary. The sign bit is zero (= plus), and the flag bits are zero (i, e., entire sign byte is zero).

b. DD(N), -54.73 E 4, or DD(N), 54.73 E 4 S 10

In this case the sign bit is set to one (negative) and the flag bits are zero.

c. DD(N), -54.73 E 4 S 5

The sign bit is one, since the number is negative, and flag bits T and V are one. U is zero.

d. DD(N), 1, 3E-5, -45.7, 12 S 17

This example illustrates the multiple entry feature. This single DD statement compiles four 64-bit floating point words and advances the location counter accordingly.

In normalized floating point a special feature is available for use in any D field, making the entry of rational fractions and certain irrational numbers much easier. Arithmetic involving several numbers may be written using the standard Fortran symbols. Strap-1 will perform the arithmetic and compile a single normalized constant. The operations available are: addition (+), subtraction (-), multiplication (\*), and division (/); only relatively simple expressions are allowed—that is, they must contain no parentheses. Multiplications and divisions are performed first (in a series of multiplications and divisions they are done in order from left to right), and then the additions and subtractions. The arithmetic is done among absolute constants, and a sign byte may be used at the end. It will be OR'ed in with the final result.

#### Examples:

a. DD(N), 1/3, 472\*351, 4-7\*5/21 S 4

Note: Sign byte entered in last D field.

b. DD(N),

$$27.9/31.4/12/14 {E}$$

5,  $4+3*7/5*6$

The number produced in the first case is:

$$\frac{27.9}{31.4 \times 12 \times 14 \times 10^5}$$

in the second:  $4 + \frac{3 \times 7 \times 6}{5}$ .

c. DD(N),

$$1/7 - 3/11 + 1.4321 E - 2$$

,  $.12 + 1/144$

As an extra convenience, certain system symbols are defined by which constants involving irrational numbers can be entered. They are:

Thus, one can enter a number such as  $4\pi \times 10^{-7}$  by writing:

$$DD(N)$$

, 4 \* \$PI \* 1E - 7.

Note that in Strap-1 this arithmetic feature is available with the normalized floating point mode only.

Unnormalized Floating Point

Format: Name (Fn)DD(U),

$$\pm xx^{\cdots}x.x^{\cdots}xE\pm yyySn X\pm n$$

or DD(U), (Fn)  $\pm xx^{\cdots}xx.x^{\cdots}xE\pm yyySnX\pm n$ , (Fn) $\pm xx^{\cdots}etc$ .

The number is converted to binary with the correct number of binary fractional places as specified by the (Fn) entry mode, and a correct exponent is computed and entered. This exponent is overruled and replaced by that following the X if X is used (necessary only if, for some reason, the programmer desires an incorrect exponent). The entry mode (Fn) can come before the DD, in which case it applies to all D fields of the statement, or it may form the first element of a D field, in which case it overrules one given before the DD. Either the X or the S or both may be omitted or their order may be interchanged. Omitting S has the same effect here as in the normalized case. Omitting X simply allows the correct exponent to remain as computed. Leaving out the sign, decimal point, or E is permitted as in normalized numbers.

# Examples:

a. DD(U), (F21) - 343.7, (F10) 432

Two numbers are compiled. In the first, 343 is converted as an integer and .7 is converted to a 21-bit fraction. They are joined and placed in the rightmost bits of the fraction portion of the floating point word, and the correct exponent (in this case 27) and sign are supplied. In the second D field, 432 is converted to a binary integer. Because ten fractional bits are specified, but no decimal fraction is written, the ten rightmost bits of the fraction field are set to zero and the number is entered with its rightmost bit in position 50.

b. (F15)DD(U), 767.52, 767.52 X-12 S11

The (F15) applies to both D fields

The (F15) applies to both D fields. In the second, the computed exponent is overruled by the specified one and the number is made negative by means of the specified sign byte.

c. (F15)DD(U), 767.52, (F20) 767.52 S11 X-12, 398

This example is identical to example b except that in the second field the operation entry mode (F15) is overruled by a field entry mode (F20), and the order of S and X is interchanged, which makes no difference. (F15) still applies to 398, however.

If the entry mode is omitted, two cases arise:

- 1) If the number entered is an integer, (F0) is understood.

- 2) If the number entered is a decimal fraction, it is converted to a normalized floating point number, but will be used as though unnormalized.

### Examples:

a. DD(U), 17, 17X-35

In the first case 17 is converted to binary and placed in the fraction with its rightmost bit in position 60 and an exponent of 48 supplied. In the second field the same thing is done except that the exponent is set to -35.

b. DD(U), 17.5

In this example 17.5 is converted to normalized floating binary and stored as such. However, instructions whose normalization bits depend on the symbol in the name field of this pseudo-operation will have them set to unnormalized.

Note: 17 E 5 is an integer and will be recognized as such.

17 E-5 is a decimal fraction and will be normalized.

17.5 E 5 is an integer but will be treated as a fraction and normalized. Thus, a normalized integer can be assigned use mode "unnormalized."

An integer greater than  $2^{48}$  is stored as a normalized number.

Binary Signed VFL

```

Formats: (Fn)DD(B, FL, BS), ± xx···x.x···xE±yy Sn DD(B, FL, BS), (Fn) ±xx···x.x···xE±yy Sn (R)DD(B, FL, BS), ±xx···xx Sn DD(B, FL, BS), (R) ±xx xx Sn

```

A data definition of binary signed data may have either (Fn) or (R) entry modes, but not both at the same time. (Fn) implies that the data following it are written in a decimal radix, whereas (R) implies that the number following it is an integer. An integer subject to a radix entry mode must be written without the aid of E because E is not defined for a radix other than 10. A decimal fraction must have a controlling (Fn) entry mode. There is no obvious way to convert to a fixed point number without specifying the binary scaling. In the data description either the field length or byte size or both may be omitted. The implied field length in this case is 64; the implied byte size is 1. The sign byte need not be specified unless the programmer desires to have flag or zone bits different from zero. Note that the sign bit position changes for a byte size less than 4. To make a number negative, specify the sign byte as:

BS = 1, S1 BS = 2, S2 BS = 3, S4 BS = 4, S10 If a number has no entry mode at all, it must be a decimal integer, but may in this case be written with the aid of the E notation.

# Examples:

- a. (F7)DD(B,,4), .005E3S13, -17, 143.2S11, (8) 77760, 777

Implied field length is 64. Octal specification in the fourth D field overrules (F7) written before DD, but (F7) still applies to 777.

- b. (2)DD(B, 16, 8) 110101S377, (10) -972, 11101110S201 Binary entry, overruled in only the second D field.

- c. (F12)DD(B, 24), 1.324E3, -72.1E-4, 3.4E-4S1 Implied byte size is 1.

- d. DD(B), 1489, -1272, 1491, (F13) -972.16, 13948S1, 12E5

Decimal integers, except where a field entry mode is written.

# Binary Unsigned VFL

```

Formats: (Fn)DD(BU, FL, BS), xx · · · x · · · x E±yy

DD(BU, FL, BS), (Fn) xx · · · x · · · x E±yy

(R)DD(BU, FL, BS), xx · · · xx

DD(BU, FL, BS), (R) xx · · · xx

(Az)DD(BU, FL, BS), alphabetic information to ''z''

(IQSz)DD(BU, FL, BS), alphabetic information to ''z''

```

Numerical entry is exactly the same as in binary signed data except that no sign byte is formed, and if the byte size is left out of the dds, it is set to 8. Any sign or sign byte (with S) written with mode BU is ignored. The two alphabetic modes are permitted here; they are explained under "Entry Modes." Note that the alphabetic entry mode must precede the DD, that there can be only one D field per statement, and that if the field length is omitted, it is set equal to the byte size.

#### Examples:

- a. (F13)DD(BU, 30), 17.2, 183, (8) 70707

- b. (A\*)DD(BU, 48, 6), GLORIOUS FRIDAY, THE 13TH.\*

The mode and field length have no effect on the conversion and storage; they are used in compiling instructions that refer to the name of this statement. Field length 48 indicates that the programmer wants to process these characters in groups of 8.

- c. (IQSS)DD(BU, 32, 8) DOG EAT DOG S

# Decimal Signed VFL

```

Formats: (R)DD(D, FL, BS), \pm xx \cdots xxx Sn DD(D, FL, BS), \pm (R) xx \cdots xx Sn DD(D, FL, BS), \pm xx \cdots xxEyy Sn (Fn) has no meaning for mode = D or DU.

```

The two decimal modes in DD and DDI statements represent the only cases in which Strap-1 converts numbers to an internal decimal radix. This conversion is limited to being available only from integers to integers. The radix entry mode indicates the radix in which the numbers are written on the card. Thus, it is possible to write an integer in binary or octal and have it converted to decimal for machine use. If no entry mode is given, decimal to decimal is implied and the E notation can be used to

multiply an integer by positive powers of 10. If either the field length or byte size is omitted, the implied values are FL = 64, and BS = 4.

# Examples:

a. DD(D), -9534812, +173E5, 18E10S13

Field length = 64; byte size = 4. A 4-bit sign byte is formed. Decimal-to-decimal conversion.

b. (2)DD(D, 20), 111010001101S7

Byte size = 4. Binary-to-decimal conversion.

c. DD(D, , 8), 432E3

Field length = 64. Decimal-to-decimal conversion. Four binary zeros are inserted in the zone positions of each byte.

### Decimal Unsigned VFL

Formats: (R)DD(DU, FL, BS), xx···xx

DD(DU, FL, BS), (R) xx···xx

DD(DU, FL, BS), xx···xxxEyyy

(Az)DD(DU, FL, BS), alphabetic information to "z"

(IQSz)DD(DU, FL, BS), alphabetic information to "z"

The numerical conversion is just as in decimal signed mode except for the omission of the sign byte. Alphabetic conversion is exactly as in the binary unsigned mode, except that instructions referring to these data are compiled as decimal operations. For alphabetic entry, implied field length is equal to byte size.

### Examples:

a. DD(DU), 8430051, (8) 77241, 82E10

Field length = 64; byte size = 4.

An octal-to-decimal conversion is inserted between two decimal-to-decimal conversions.

b. (IQS3)DD(DU, , 8), PUSH PANIC BUTTON 3 Field length = 8.

# Summary of Rules for DD Statements

| Entry Mode | Appropriate Use Modes |

|------------|-----------------------|

| Fn         | U, B, BU              |

| R          | B, BU, D, DU          |

| A          | BU, DU                |

| IQS        | BU, DU                |

Note: Use mode N should have no entry mode.

| Special Field Entry | Appropriate Use Modes |

|---------------------|-----------------------|

| S                   | N, U, B, D            |

| X                   | N. U                  |

The floating decimal notation, using E to designate multiplication by powers of 10, is appropriate to all modes although it is always restricted to a decimal radix, and in the decimal use modes, is restricted to increasing the magnitude of decimal integers.

If the field length is omitted from the dds, it will be assigned a value of 64, except in the case of alphabetic entry where it is set equal to the byte size. The maximum permissible field length for a DD statement is 64.

The following examples illustrate the use of general parenthetical integer entry with DD:

- a. DD(N), 572(.59)1, 347.89E12(.63, 2)1011

- In the second case the sign byte is specified by means of (.n) entry.

- b. DD(B), (F9) -35.7(.24) SAM + 4

- The address SAM + 4 is placed in the first part of the 64-bit field, followed by the converted number -35.7.

- c. (8)DD(BU), 4762(.10)707(10, .20)34 707 is written in octal, 34 in decimal.

# PSEUDO-OPERATIONS THAT DEFINE SYMBOLS