| Сору    | No. |  |

|---------|-----|--|

| - · · · |     |  |

REVISED MANUAL HARVEST SYSTEM

November 13, 1957

## Company Confidential

This document contains information of a proprietary nature. ALL INFORMATION CONTAINED HEREIN SHALL BE KEPT IN CONFIDENCE. No information shall be divulged to persons other than IBM employees authorized by the nature of their duties to receive such information, or individuals or organizations who are authorized by IBM Research or its appointee to receive such information.

IBM Research Laboratory Poughkeepsie, N. Y.

#### TABLE OF CONTENTS

```

Hl.

Stream Indexing

Control Parameters and Control Bits

H1.1

Stream Indexing Setup

H1.2

H1.3

Operation

Nested Indexing

H1.3.1

Control Bits

H1.3.1.1

Triangular Indexing

H1.3.2

H1.3.2.1

Control Bits

Sequential Indexing

H1.3.3

H1.3.3.1

Control Bits

Special Values of Indexing Parameters

H1.4

Automatic Adjustment of Index Level

H1.5

H1.5.1

Repeat Byte in P (Q)

Repeat Byte in R

H1.5.2

Skip Byte in P (Q)

H1.5.3

Runout First Level in P (Q)

H1.5.4

Runout Second Level in P (Q)

H1.5.5

Runout Higher Level in P (Q)

H1.5.6

Runout Field in P (Q)

H1.5.7

Runout Sequence in P (Q)

H1.5.8

Reset First Level in P (Q, R)

H1.5.9

Reset Second Level in P (Q, R)

H1.5.10

Reset Higher Level in P (Q, R)

H1.5.11

Advance Second Level in P (Q, R)

H1.5.12

Advance Higher Level in P (Q, R)

H1.5.13

H1.6

Examples

Nested Mode

H1.6.1

Sequential Mode

H1.6.2

Triangular Mode

H1.6.3

The Streaming Mode

H2.

General Operation

H2.1

Stream Units P and Q

H2.1.1

Stream Unit R

H2.1.2

Stream Unit T, the Table Address Assembler (TAA)

H2.1.3

Stream Unit U, the Table Extract Unit (TEU)

H2.1.4

Statistical Accumulator (SACC) and Threshold Register (THR)

H2.1.5

Statistical Counter (SCTR)

H2.1.6

Logic Unit (LU)

H2.1.7

H2.1.8

Group Signal (G)

H2.1.9

Byte Masks (BM)

H2.1.10

Match Units (W, X, Y, and Z)

```

H2.1.11

## TABLE OF CONTENTS

```

H2.2 Harvest Setup

H2.2.1 The Setup Words

Initial and Developed Values of Parameters

H2.2.2

SKIP and SKAM

H2.2.3

SBBB - The Stream Byte-by-Byte Instruction

Data Gating

H2.3.1

Gate #0

H2.3.1.1

Gates #1, #2, #3, #4, #5, and #6

H2.3.1.2

H2.3.1.3

Gate #7

H2.3.1.4 Gate #8

H2.3.1.5 Gates #9, #10, and #11

Gates #12 and #13

H2.3.1.6

GS - Group Size

H2.3.2

H2.3.3

The STOP Code

RC - R Control

H2.3.4

The Action of the Logic Unit in Byte-by-Byte Streaming

H2.4

The Byte-by-Byte Operations

H2.4.1

E, F, and G

H2.4.2

The Functioning of T and U in Byte-by-Byte Streaming

T

H2.5.1

H2.5.2

U

The Match Units (W, X, Y, Z)

The Statistical Accumulator and Statistical Counter (SACC and

H2.7

SCTR)

H2.7.1

SACC

H2.7.2

SCTR

Other quantities in the SACC and SCTR setup words

H2.7.3

Automatic Adjustments

H2.8

Stream Indicator Bits

H2.9

H2.10 The Hybrid Instructions

SUBR - STREAM UNCONDITIONAL BRANCH

H2.10.1

SCBR - STREAM CONDITIONAL BRANCH

H2.10.2

(Not Yet Specified)

H2.10.3

SMOV - STREAM MOVE

H2.10.4

SCSI - STREAM COUNT AND SET INDICATOR

H2.10.5

SCAD - STREAM CONDITIONAL ADJUST

H2.10.6

SCLM - STREAM CLEAR MEMORY

H2.10.7

SSTC - STREAM STORE AND CLEAR

H2.10.8

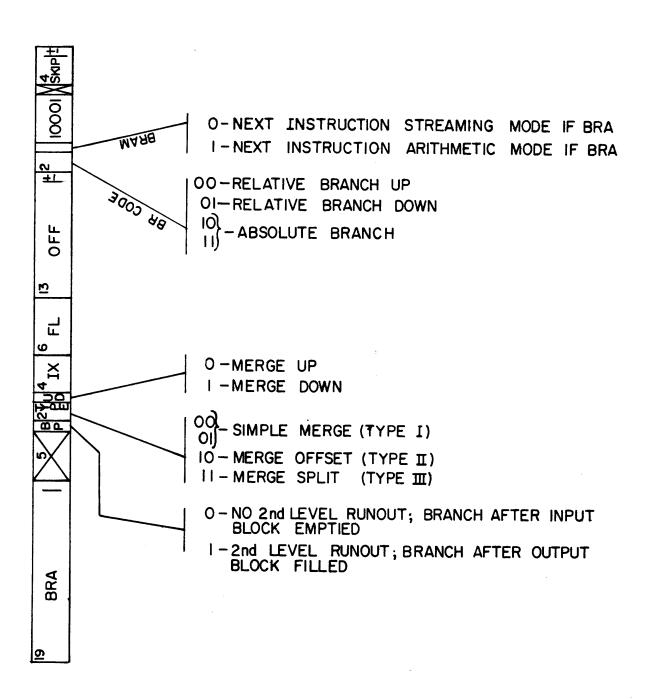

SMER - STREAM MERGE

H2.10.9

H2.10.9.1 Index Control Parameters

H2.10.9.2 Type I - SIMPLE MERGE UP (DOWN)

H2.10.9.3 Type II - MERGE OFFSET UP (DOWN)

H2.10.9.4 Type III - MERGE SPLIT UP (DOWN)

H2.10.9.5 Merging Files of Unequal Length

```

#### TABLE OF CONTENTS

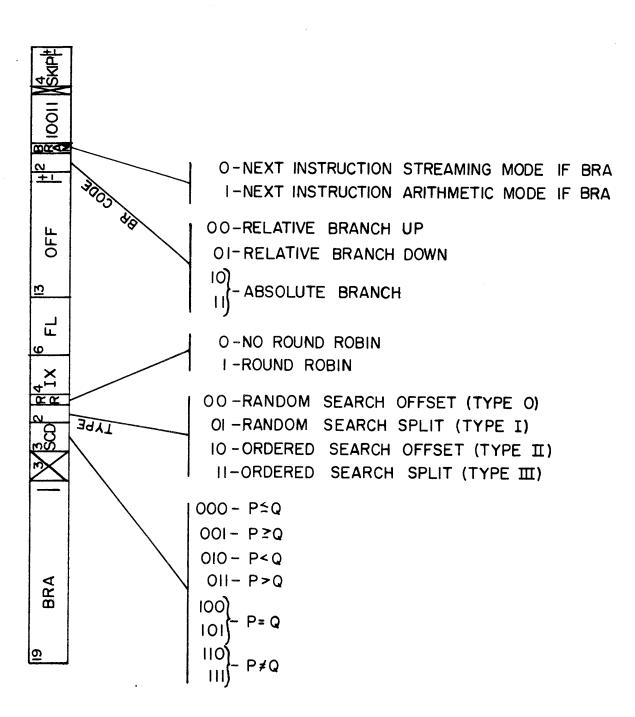

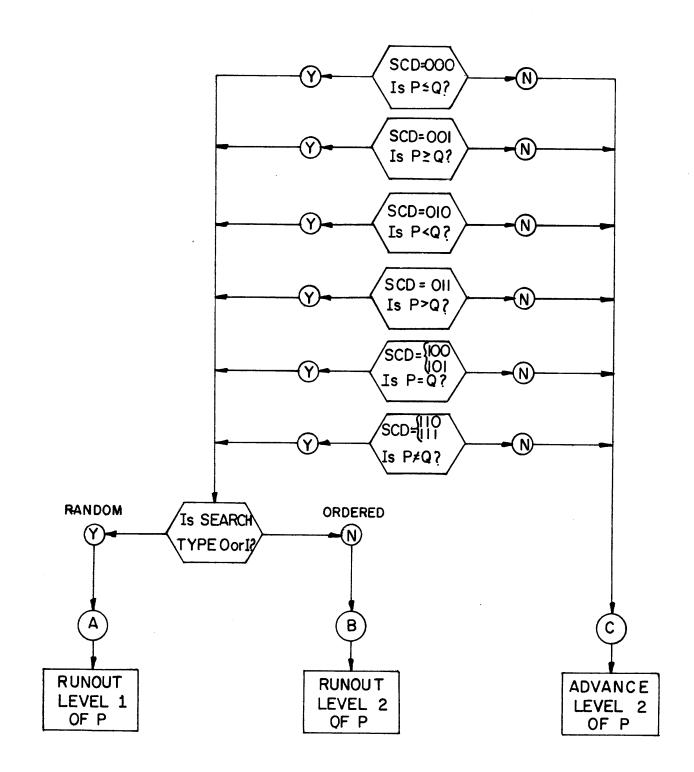

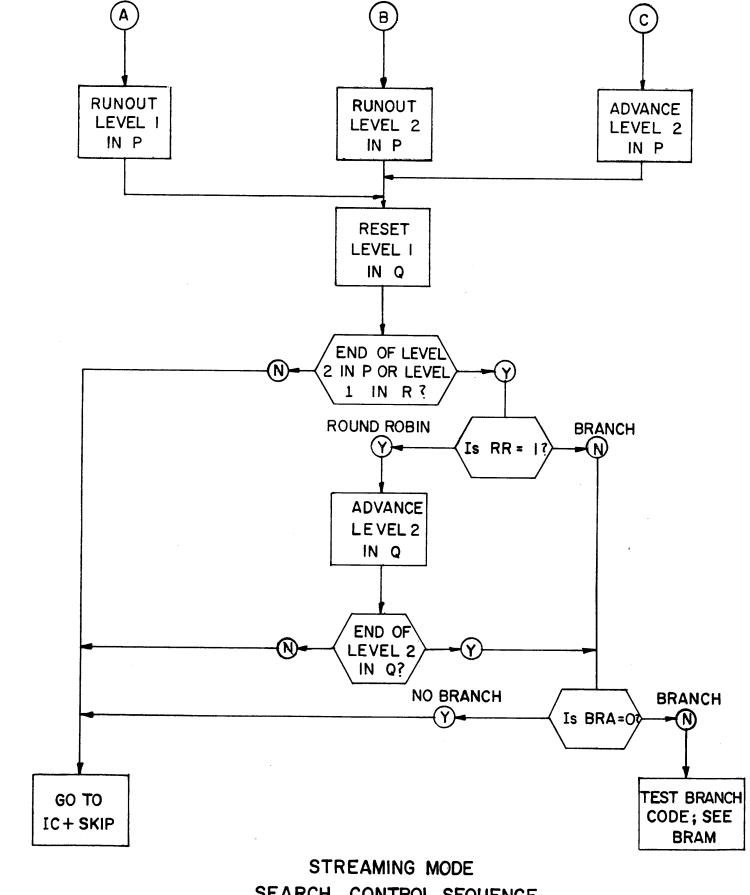

- H2.10.10 SSER STREAM SEARCH

- H2.10.10.1 Index Control Parameters

- H2.10.10.2 Type 0 RANDOM SEARCH OFFSET

- H2.10.10.3 Type I RANDOM SEARCH SPLIT

- H2.10.10.4 Type II ORDERED SEARCH OFFSET and Type III ORDERED SEARCH SPLIT

- H2.10.11 SADD STREAM ADD

- H2.10.12 SMPY STREAM MULTIPLY

- H2.10.13 SMLU STREAM MULTIPLE LOOKUP

- H2.10.14 SILS STREAM INDIRECT LOAD AND STORE

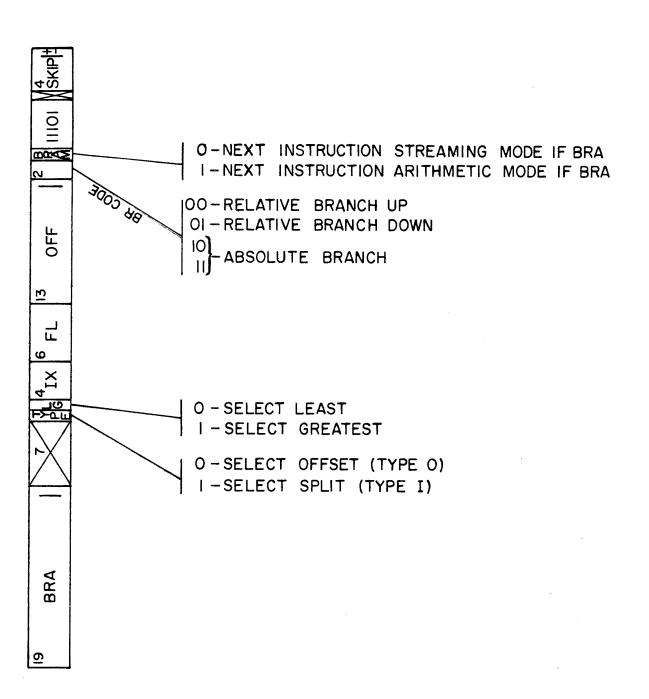

- H2.10.15 SSEL STREAM SELECT

- H2.10.15.1 Index Control Parameters

- H2.10.15.2 Type 0 SELECT OFFSET LEAST (GREATEST)

- H2.10.15.3 Type I SELECT SPLIT LEAST (GREATEST)

- H2.10.16 (Not Assigned As Yet)

# Harvest Abbreviations

| A, B, C, D | BASIC registers             | MOD         | Modulus                     |

|------------|-----------------------------|-------------|-----------------------------|

| ADJ        | Adjustment                  | MS          | Match station               |

| ADV        | Advance                     | MU          | Match unit                  |

| BAR        | Byte address register       | N           | Total count                 |

| BM         | Byte mask                   | OFF         | Offset                      |

| BP         | Branch point                | P, Q, R     | Harvest registers or SU's   |

| BRA        | Branch address              | PAR         | Parity                      |

| BRAM       | Branch to arith. mode       | PB          | Parity Bit                  |

| CL         | Clear                       | PRI         | Priority                    |

|            | Connection                  | RA.         | Relative-absolute           |

| CPU        | Central Processing Unit     | RC          | R store control             |

| E          | "or" of k and/or 1 and/or n | $\alpha$ RR | Round robin                 |

| EC         | End of chain                | RS          | Return to stream indicator  |

| EU         | Equal-unequal               | RST         | Reset                       |

| F          | One bit memory for E        | S           | Effective address           |

| FL         | Field length                | SACC        | Statistical accumulator     |

| G          | Group                       | SAM         | SACC mode                   |

| GS         | Group size                  | SBC         | Six bit counter             |

| Н          | Higher levels address       | SCD         | Search condition            |

| HL         | Higher level                | SCTR        | Statistical counter         |

| I          | Increment                   | SGN         | Sign modifier               |

| IC.        | Instruction Counter         | SKAM        | Skip to arithmetic mode     |

| IM         | Index mode                  | SM          | Switch matrix               |

| IX         | Index address               | SP          | Span                        |

| J          | Accumulated increment       | su          | Stream unit                 |

| k          | One bit signal from LU      | SUP         | Supplemental signal         |

| K          | Cell size in TAA            | sw          | Swallow - non swallow       |

| KK         | Cell size for TAA in SILS   | T, TAA      | Table Address assembler     |

| 1717       | instruction                 | TAM         | TAA mode                    |

| 1          | One bit signal from LU      | TB          | Test bit                    |

| L          | Byte output from LU         | TEU, U      | Table extract unit          |

| LG         | Least-Greater bit           | TG          | One bit memory device       |

| LS         | Large-small; load-store     | THR         | Threshold register          |

| LU         | Logic unit                  | TR          | Triangular indexing         |

|            | One bit signal from LU      | U, TEU      |                             |

| m<br>M     | Partial count               | UD          | Up - down                   |

| M<br>MD    | Memory distributor          | UL          | Upper - lower               |

| *          | Memory distributor mode     | v           | Start point for TAA address |

| MDM        | Match - non match           |             | Z Match units or characters |

| MN         | TATCHOOTI TTO TT TTTCO.     |             |                             |

H1.1 10/15/57

#### H1. Stream Indexing

Generally speaking, the Harvest Computer obtains data from one or two places in memory, performs some arithmetic or logical operation on the data, and stores the result in memory. The addresses of the source (or sources) and destination of the data are independent of each other, and are modified by independent indexing units. Thus one or two streams of input data (input streams) are processed and an output stream is stored in memory.

The pattern of address modification associated with any data stream is determined by a number of parameters at each of several levels of index control. The control levels are chained together so that there are a first level, a second level, ..., and a highest level of control. There is no practical limit to the number of control levels that can be chained to one stream unit. The values of the parameters for each control level are arbitrary, and are set by the programmer when he sets up the indexing chain prior to executing a stream instruction.

The manner in which the various levels react with one another also is determined by the programmer and specified in the various control levels. Three modes of indexing are available to the programmer; he may choose nested, sequential, or triangular indexing (these are discussed below) by setting control bits at the various levels. Some interplay between the three modes is possible (under the programmer's control).

## H1.1 Control Parameters and Control Bits

Each control level in the index chain consists of two words. For every level, each pair of words contains the following parameters and control bits:

| N,  | Total Count;                           |

|-----|----------------------------------------|

| M,  | Current Count;                         |

| I,  | Increment:                             |

| J,  | Accumulated Increment, or Field Offset |

|     | (depending on index mode);             |

| IM, | Index Mode Control Bit;                |

| TR, | Triangular Indexing Control Bit;       |

| UL, | Upper-Lower Control Bit;               |

| EC, | End of Chain Control Bit.              |

In addition, all levels higher than the second contain

HL, Higher-Level Control Bit

H1.1 10/15/57

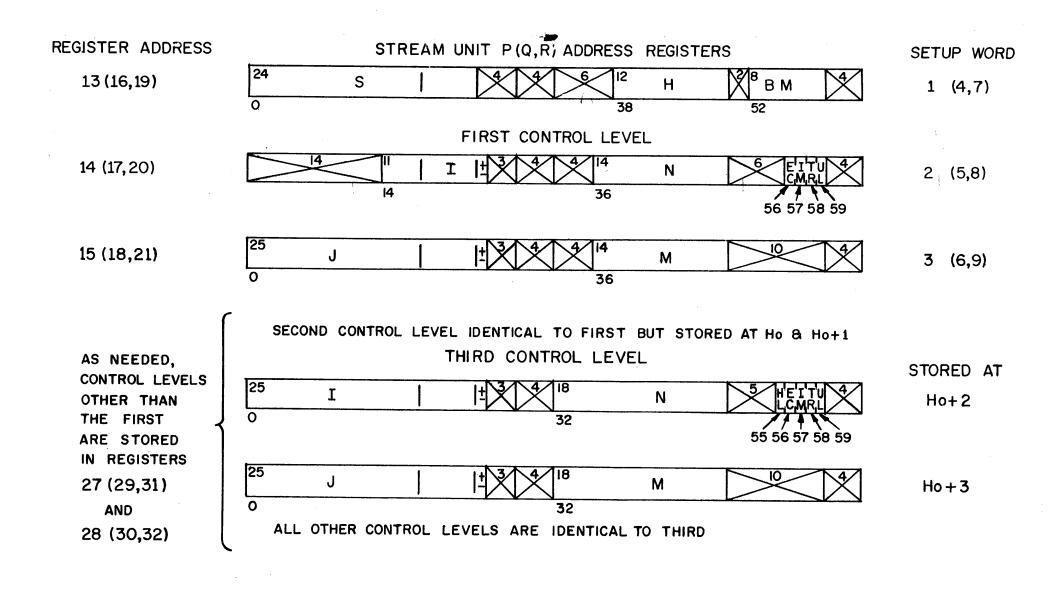

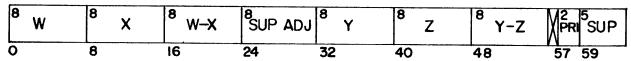

During stream indexing the first level control parameters and bits for each stream unit are stored in fixed, addressable registers associated with the particular stream units. These addresses are summarized in Figures H1. la and H1. lb. The location of the control bits and parameter fields, and the sizes of these fields are shown in Figure H1. la.

Two additional parameters are kept in addressable Stream Address Registers associated with each stream unit. They are:

S, Effective Address;

H, Higher Levels Address.

Their addresses are indicated in Figure H1.1a.

Finally, the parameter

BM, Byte Mask,

is kept in the Stream Address Registers associated with each stream unit. This will be discussed in Chapter H2.

H1. 2 10/15/57

### H1.2 Stream Indexing Setup

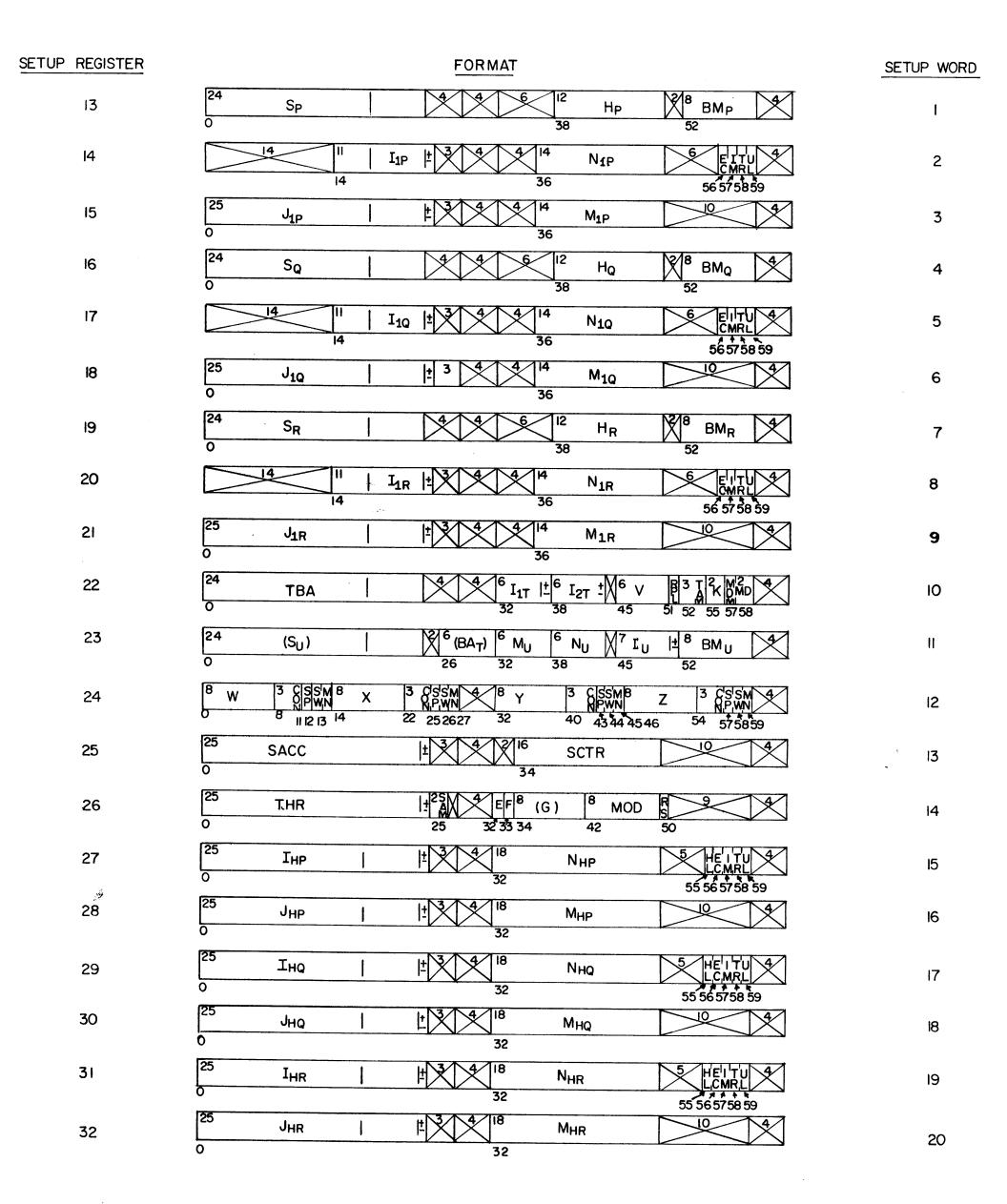

In order to prepare the Harvest Computer to execute a stream instruction, the programmer must "set up" a number of parameters and controls. To accomplish this, he may TRANSMIT a set of 20 consecutive "setup" words from somewhere in memory to fixed registers whose addresses are the 20 consecutive word addresses 13 through 32. In particular, the nine setup words 1 through 9 are transmitted to registers having the nine word addresses 13 through 21 (Figure H1.1a). The contents of those setup word fields that are indicated as not used have no effect on Harvest, as the corresponding register positions do not exist.

The first three of these nine setup words contain the parameters (S, H) (I, N, Control Bits) and (J, M) that are stored in the three registers that are associated with SU-P. The second three words contain the corresponding parameters that are stored in the three registers of SU-Q. The last three contain parameters for SU-R. Parameters for all control levels higher than the first are stored in consecutive pairs of words starting at the arbitrary addresses  $H_0$  (P),  $H_0$  (Q), and  $H_0$  (R) corresponding to the index chains for SU-P, SU-Q, and SU-R. Within each control level, the first word must contain (I, N, Control Bits) while the second must contain (J, M).  $H_0$  must be a full word address and all index control words must lie in memory whose address is less than  $2^{12}$ . These words are not transmitted to registers at setup time, but are brought into registers automatically as needed.

At the time of the initial setup for a particular stream operation, S contains the starting address,  $S_0$ , for the particular stream unit involved, H contains the second control level address,  $H_0$ . Generally speaking, J and M are initially zero in the nested and triangular indexing modes. In these cases, the second word of the appropriate control level is entirely zero.

The entire Harvest setup (including index and all other information) is summarized in Figure H2.2. Any parameter (bit or field) may be loaded into or stored from the Harvest setup register by the use of VFL instructions.

## H1.3 Operation

The Harvest stream unit indexing controls have been designed to facilitate the control of nested loops, since the read out pattern of most streams can be described in terms of nested loops. Triangular indexing is a special case of nested indexing in which the number of times a program executes a given loop within a loop of the next higher order changes with every execution of the higher order loop. Sequential indexing is also a special case of nested indexing. Since the nested mode of operation is basic to the triangular and sequential modes, it will be described first.

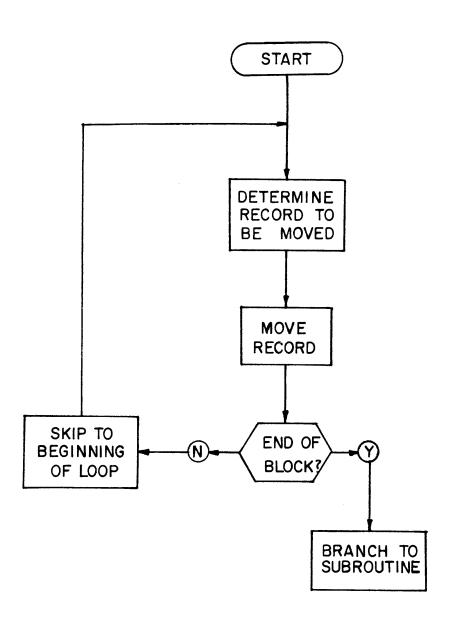

The description of stream indexing that follows is summed up in the flow chart, Figure H1.3.

### H1.3.1 Nested Indexing

In this indexing mode the first indexing level controls the byte read out of the stream unit concerned.  $N_1$  bytes at a distance of  $I_1$  bits from each other, having the addresses  $S_0$ ,  $S_0 + I_1$ ,  $S_0 + 2I_1$ , ...,  $S_0 + M_1 I_1$ , ...,  $S_0 + (N_1-1) I_1$  are read out of memory via the stream register onto some data path specified in the stream instruction (see Chapter H2). As each new address is formed it is stored in the effective address register,  $S_0$ , while the value of the current count,  $M_1$ , in the M register is increased by  $I_1$  and the partial accumulated increment  $I_1 = M_1 I_1$  in the  $I_1$  register is incremented by  $I_1$ . This is known as a first level advance. Each time  $I_1$  and  $I_2$  are updated,  $I_2$  and  $I_3$  is compared with  $I_3$ . If  $I_4$  is decremented by  $I_4$  then another byte is read out; if  $I_4$  and  $I_4$  are reset to zero. This is the end of the first level and is also the end of the first iteration at the second level.  $I_4$  and  $I_4$  are now incremented by  $I_4$ , while  $I_4$  is incremented by  $I_4$  and compared to  $I_4$ . This is a second level advance.

Assume  $M_2 \neq N_2$ . then the  $N_1$  bytes  $S_0 + I_2$ ,  $S_0 + I_1 + I_2$ , ...,  $S_0 + M_1 I_1 + I_2$ , ...,  $S_0 + (N_1 - 1) I_1 + I_2$ , are read out. Again,  $S + I_1$  replaces  $S_1$ , and  $M_1 + I$  replaces  $M_1$ . Now  $M_1 = N_1$  again,  $S_1 - J_1$  replaces  $S_1$ , and  $S_1 - J_1$  and  $S_1 - J_1$  replaces  $S_1 - J_1$  and  $S_1 - J_1$  are reset to zero. This is again the end of first level and is also the end of the second iteration at the second level.  $S_1 - J_1$  are again incremented by  $S_1 - J_1$  while  $S_1 - J_1$  is incremented by  $S_1 - J_1$  and compared to  $S_1 - J_1$  (another second level advance). The effective address is now  $S_1 - J_1$ .

Eventually, during the  $N_2$ -th iteration at the second level, S becomes  $S_0 + (N_1 - 1) I_1 + (N_2 - 1) I_2$ . After  $S + I_1$  replaces S,  $J_1 + I_1$  replaces  $J_1$ , and  $M_1 + 1$  replaces  $M_1$ , then  $M_1 = N_1$ . Now  $S - J_1 = S_0 + (N_2 - 1) I_2$  replaces S, and  $J_1$  and  $M_1$  are again reset to zero. Next S and  $J_2$  are incremented by  $I_2$  and  $I_3$  is incremented by  $I_4$ . At this point  $I_3$  is compared

10/15/57

to  $N_2$  and  $M_2 = N_2$ , so the second level must be reset.  $S - J_2$  replaces  $S_1$ , and  $J_2$  and  $M_2$  are reset to zero. This is the end of second level and is also the end of the first iteration at the third level

In general, given a k-level chain, an end of (j+1)-th level occurs only immediately after an end of j-th level  $(j=1,2,\ldots,k-1)$ . After S is decremented by  $J_j$ , and  $J_j$  and  $M_j$  are reset to zero, the effective address is  $S = S_0 + M_j + 1$   $I_j + 1$   $M_j + 2$   $I_j + 2$   $+ \ldots + M_k$   $I_k$ . After an end of j-th level, the next byte is read from  $S + I_j + 1$  unless this address results in an end of (j+1)-th level.

#### H1.3.1.1 Control Bits

- (1) EC Given a k-level chain, the End of Chain Control Bit, EC<sub>j</sub>, must be zero for all levels j < k. If EC<sub>k</sub> has the value 1, then after S,  $J_k$ , and  $M_k$  are reset the indexing mechanism will halt. Moreover, the End of Chain P, Q, or R indicator bit (see Chapter H2.9) will turn on according as EC<sub>k</sub> is in the P, Q, or R index chain. EC<sub>k</sub> also activates a Stop signal which the programmer may use to advance the computer to the next instruction.

- (2) HL

The Higher-Level Control Bit, HL, is used to mark a level higher than the second for purposes of Adjustment. This will be described in Chapter H1.5.

- (3) IM, TR

The Index Mode Control Bit, IM, and the Triangular Indexing Control

Bit, TR, must be zero in all control levels in the nested mode.

- (4) UL

The value of the Upper-Lower Control Bit, UL, is immaterial in the nested mode.

## H1.3.2 Triangular Indexing

This mode is identical to the nested mode except that on the control level designated as triangular, after S, J, and M are reset, N is decremented or incremented by 1 depending on the value of UL.

The programmer must note that although in the nested mode all parameters are reset to their initial values if indexing is terminated by EC being 1 for some level, this is not true in the triangular mode. In this mode

the final value of  $N_j$  is not equal to the initial value of  $N_j$ . The program must reset this parameter before using this particular setup for another data pass.

## H1.3.2.1 Control Bits

- (1) EC, HL

These bits are used as in the nested mode.

- (2) IM

This bit must be zero.

- (3) TR

The Triangular Indexing Control Bit must have the value 1 on each level at which it is desired to change N automatically.

- (4) UL

To increment N, set the Upper-Lower Control bit to 1; to decrement N, set UL to zero.

# H1.3.3 Sequential Indexing

In the sequential mode, several consecutive control levels beginning with the first control the byte read out of the stream unit concerned.

After each byte is read on any control level designated as sequential, S is incremented by I, M by I, but J is unchanged. Moreover, at the end of any such level, S is incremented by J, J is unchanged, and only M is reset to zero.

Thus each sequential level defines and causes to be read out a field of N bytes at intervals I from each other while J defines the distance in bits (field Offset) between the end of this field and the beginning of the next. In particular, the value of J for the last level in the sequence may be the algebraic distance in bits between the end of the last field and the beginning of the first field in the sequence. The entire sequence then must be nested in the next higher control level.

H1.3

#### H1.3.3.1 Control Bits

- (1) HL

This bit is used as in the nested mode.

- (2) EC

This bit is immaterial in the sequential levels, but has its regular meaning in all levels of order higher than the sequential levels.

- (3) IM

This bit must have the value 1 in the sequential levels and must have the value zero in the first non-sequential level. It is immaterial in all others.

- (4) TR, UL

These bits are immaterial in the sequential levels but have their usual meaning in all others.

H1.4

# H1.4 Special Values of Indexing Parameters

The parameters M and N are always unsigned, while I and J may be positive or negative (see Figure H1. la).

In the nested and triangular modes, if I is zero then J is always zero. In the sequential mode, J is independent of I.

N may be zero. But since M (which is non-negative) is always incremented before being compared with N, if N is zero then indexing cannot advance to a higher level and cannot be terminated by any EC bit until 2<sup>14</sup> iterations (if this is the first level) or 2<sup>18</sup> iterations (if this is a higher level) have been performed. (M resides in a 14 or 18 bit counter.)

H may be zero. If it is, all parameter and control bits for the second level will be loaded into the stream indexing mechanism as zero, and H will remain unchanged. Under these circumstances M<sub>2</sub> will always equal 1 and N<sub>2</sub> will always equal zero when they are compared. Thus the second level will continue to iterate indefinitely, and indexing must be terminated by some signal that originates outside of the stream indexing mechanism involved.

# H1.5 Automatic Adjustment of Index Level

As part of certain streaming mode instructions a number of Adjustment operations are available. Those that adjust stream indexing controls are the subject of this section; the rest are discussed in Chapter H2.8.

# H1.5.1 Repeat Byte in P (Q)

The last byte read out of stream register P (Q) is read out again, after which indexing proceeds normally. This is defined for all indexing modes.

# H1.5.2 Repeat Byte in R

The next byte read into stream register R is read in over the last byte after which indexing proceeds normally. This is defined for all indexing modes.

# H1.5.3 Skip Byte in P (Q)

Suppress the read out of the next byte in P (Q) and then proceed normally. This is defined for all indexing modes.

# H1.5.4 Runout First Level in P (Q)

The remaining bytes in P (Q) are read out and bypass the LU, TAA, TEU, and all MS's. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.5 Runout Second Level in P (Q)

All bytes read out of P (Q) bypass the LU, TAA, TEU, and all MS's until the end of second level is reached. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.6 Runout Higher Level in P (Q)

All bytes read out of P (Q) bypass the LU, TAA, TEU, and all MS's until the end of the higher level whose HL bit has the value 1 is reached. Indexing then proceeds normally. This is defined for all indexing modes; but in the sequential mode HL may only have the value 1 in a nested level.

# H1.5.7 Runout Field in P (Q)

The remaining bytes in the present <u>sequential</u> level in P (Q) are read out and bypass the LU, TAA, TEU, and all MS's. Indexing then proceeds normally. This is defined only for the sequential mode.

# H1.5.8 Runout Sequence in P (Q)

All bytes in the remaining sequential levels in P (Q) are read out and bypass the LU, TAA, TEU, and all MS's. Indexing then proceeds normally. This is defined only for the sequential mode.

# H1.5.9 Reset First Level in P (Q, R)

The effective address, S, in P (Q, R) is decremented by  $J_1$ , and  $J_1$  and  $M_1$  are reset to zero. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.10 Reset Second Level in P (Q, R)

S in P (Q, R) is decremented by  $J_1$  and  $J_2$ , and  $J_1$ ,  $J_2$ ,  $M_1$ , and  $M_2$  are reset to zero. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.11 Reset Higher Level in P (Q, R)

S in P (Q, R) is decremented by  $J_1$ ,  $J_2$ , ...,  $J_h$ , and these J's and  $M_1$ ,  $M_2$ , ...,  $M_h$  are reset to zero. Here h is that level whose HL bit has the value 1. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.12 Advance Second Level in P (Q, R)

S in P (Q, R) is decremented by  $J_1$ ;  $J_1$  and  $M_1$  are reset to zero; S and  $J_2$  are incremented by  $I_2$ ; and  $M_2$  is incremented by 1. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

# H1.5.13 Advance Higher Level in P (Q, R)

S in P (Q, R) is decremented by  $J_1$ ,  $J_2$ , ...,  $J_{h-1}$ ; these J's and  $M_1$ ,  $M_2$ , ...,  $M_{h-1}$  are reset to zero; S and  $J_h$  are incremented by  $I_h$ ; and  $M_h$  is incremented by 1. Here h is defined as in H1.5.11. Indexing then proceeds normally. This is defined for the nested and triangular modes only.

10/16/57

#### H1.6 Examples

The flow of bytes selected from memory by each stream indexing mechanism and presented to the Harvest data buses fits a well defined pattern which may be simple or complex. Examples are given here which illustrate patterns one could expect in the three indexing modes.

## H1.6.1 Nested Mode

A stream might consist of one thousand consecutive six-bit bytes beginning at a particular address. This is a simple stream that requires only one index control level. The values of the parameters for this level are:

A more complex stream may be described as follows (see Figure H1.6.1 for first two levels): read out three overlapping eight-bit bytes (each byte overlaps the last half of the preceding byte) and then skip six bits; repeat this three times, each time moving the effective starting point 22 bits, thus giving a six-bit skip; repeat this entire process five times using the original starting point; finally each time all previously described steps have been completed repeat them at a new starting point one-hundred bits from the original starting point, continuing such repetition until a total of ten cycles have been completed. This complex stream requires four levels of index control, whose parameters have the following initial values:

| Level | 1   | N  | J | M | $\mathbf{IM}$ | TR | UL | EC | HL |

|-------|-----|----|---|---|---------------|----|----|----|----|

| 1     | 4   | 3  | 0 | 0 | 0             | 0  | 0  | 0  | 0  |

| 2     | 22  | 3  | 0 | 0 | 0             | 0  | 0  | 0  | 0  |

| . 2   | -0  | 5  | 0 | 0 | 0             | 0  | 0  | 0  | 0  |

| 4     | 100 | 10 | 0 | 0 | 0             | 0  | 0  | 1  | 0  |

# H1.6.2 Sequential Mode

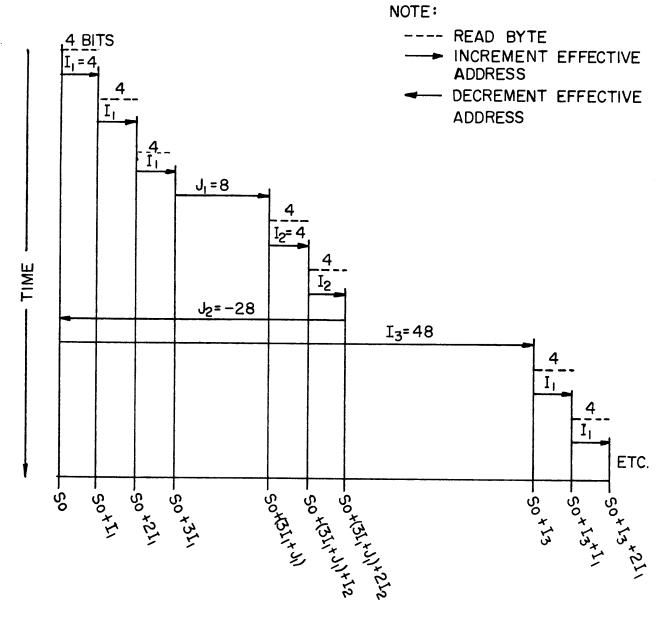

A pattern of the simpler sequential type is characterized by the following example (see Figure H1.6.2). A record consists of twelve 4-bit decimal digits. It is desired to read out three digits at the beginning of the record, skip two, read out two, and then go to the next record. Three levels of control are used to produce this pattern. Their parameters have the following initial values:

| Level | I  | N | J   | M | IM | TR | UL | EC | HL |

|-------|----|---|-----|---|----|----|----|----|----|

| 1     |    |   |     |   |    |    | 0  |    | 0  |

| 2     | 4  | 2 | -28 | 0 | 1  | 0  | 0  | 0  | 0  |

| 3     | 48 | _ | 0   | 0 | 0  | 0  | 0  | -  | 0  |

### H1.6.3 Triangular Mode

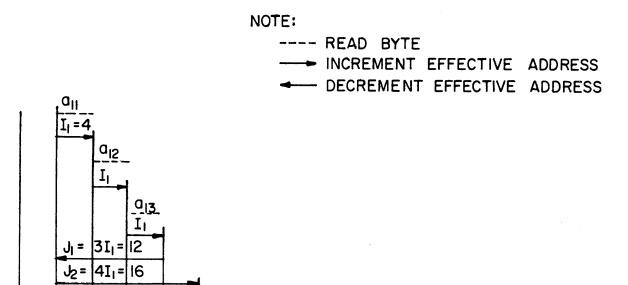

Consider the following array of data:

the numbers  $a_{11}$ ,  $a_{12}$ ,  $a_{13}$ ,  $a_{21}$ ,  $a_{22}$ ,  $a_{23}$ ,  $a_{31}$ ,  $a_{32}$ , and  $a_{33}$  are

arranged consecutively in memory. These numbers represent the elements

of three rows of a third order matrix. It is desired to read all elements of

the first row, then the last two elements of the second row and finally the

last element of the third row. Such a readout is illustrated in Figure

H1.6.3a. Such an array of data is called an Upper Right matrix triangle.

In order to read out such a pattern, it is necessary only to be able to change

the value of the total count, N, on that level of indexing that reads a row of

the matrix. For example, if each element of the matrix is a six-bit byte,

then the first level of indexing controls the readout of a row of the matrix.

In this fourth indexing example, the total count for the first level is initially

3. After reading the first row, the total count is decremented by one. Thus

the total count is now 2. After the elements of the second row are read out

the total count is again decremented 1 and the count is now 1.

In addition to this it is necessary to increment at the second level by four times the byte length, that is, a multiple of the byte size that is one more than the number of elements in the first row. The size of the increment on the second level remains constant throughout the pattern of indexing. Since there are three rows to be read, the value of the total count for the second level is 3. The initial setup is as follows:

| Level | I  | N | J | M | IM | TR | ÜL | EC | HL |

|-------|----|---|---|---|----|----|----|----|----|

| 1     | 6  | 3 | 0 | 0 | 0  | 1  | 0  | 0  | 0  |

| 2     | 24 | 3 | 0 | 0 | 0  | 0  | 0  | 1  | 0  |

There are four triangles in every matrix. They are designated Upper Left, Upper Right, Lower Left and Lower Right. If it were desired to read the Upper Left triangle from the matrix described above, the output would be as follows:

The corresponding Lower Right triangle consists of the elements

the Lower Left triangle is

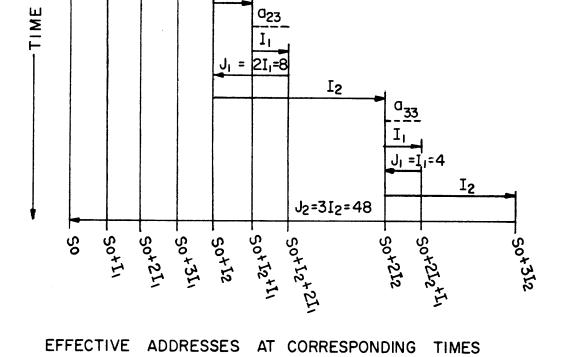

An analogous pattern of indexing may be applied to vectors. Thus, if a vector consists of the three elements  $a_1$ ,  $a_2$ ,  $a_3$ , and it is desired to read these elements out in the order  $a_3$ ,  $a_2$ ,  $a_3$ ,  $a_1$ ,  $a_2$ ,  $a_3$ , then we can say that we are applying Triangular Indexing to the vector. Figure H1.6.3b illustrates precisely this Lower Right vector. Once again there are four triangles, Upper Left, Upper Right, Lower Left and Lower Right. The analogous Upper Left vector triangle produces an array as follows:

the Upper Right vector triangle is

finally the Lower Left vector triangle is

The following table indicates the values of the control bits and the parameters for indexing in this fashion:

| Triangle    | $\mathtt{TR}_{\mathbf{x}}$ | $\mathtt{UL}_{\mathbf{x}}$ |                   | Value of I <sub>x+1</sub> |                       | Value of $N_{x+1}$ |        |

|-------------|----------------------------|----------------------------|-------------------|---------------------------|-----------------------|--------------------|--------|

|             |                            |                            | of N <sub>x</sub> | Vector                    | Matrix                | Vector             | Matrix |

| Upper Left  | 1                          | 0                          | n                 | 0                         | $^{ m nI}_{ m x}$     | n                  | n      |

| Upper Right | 1                          | 0                          | n                 | $\mathbf{I_x}$            | $(n+1)I_{\mathbf{x}}$ | n                  | n      |

| Lower Left  | 1                          | 1                          | 1                 | O                         | $^{ m nI}_{f x}$      | n                  | n      |

| Lower Right | 1                          | 1                          | 1                 | -I <sub>x</sub>           | (n-1)I <sub>x</sub>   | n                  | n      |

n is the order of the matrix, or the dimension of the vector. In all cases  $I_x>0$ .

H2. 10/21/57

### H2. The Streaming Mode

Harvest is designed to operate upon a sequence of bytes in an extremely rapid and automatic manner. This speed is attained by the simultaneous functioning of several independent indexing and addressing mechanisms (described in Chapter H1) and by the sequential processing of bytes by units working in an assembly-line fashion. In addition to the various processing units a counter and an accumulator have been provided for calculating pertinent statistics during the course of byte processing.

In one respect the functioning of Harvest in the streaming mode may be compared to that of a plug board computer. That is, the operation to be performed and all the relevant parameters are specified before any action takes place; then the execution of a single streaming instruction may cause the logical or arithmetic manipulation of many thousands of data bytes. Of course the big difference is that the "plugging" in Harvest is all done under program control and can be changed completely in a number of microseconds. Moreover the arithmetic and logical facilities of a general-purpose computer are always at hand to resolve difficulties that cannot easily be resolved in the streaming mode.

To a large extent the streaming mode is conceptually separate from the arithmetic mode. The arithmetic section contains the instruction "BRANCH TO Y AND ENTER STREAMING MODE". Upon this command the complexion of Harvest changes; the manifold processing units are activated, and the philosophy of information handling and processing changes. One of the basic differences between the arithmetic mode and the streaming mode of operation is that in the streaming mode the programmer has the responsibility of designating how the Instruction Counter must change from instruction to instruction, while in the arithmetic mode this is, in general, automatic. When a streaming instruction indicates a shift to the arithmetic mode, the normal arithmetic functioning of the Basic computer is resumed.

In order to diminish the necessity for frequent alternations between the streaming and arithmetic modes and to gain speed and flexibility in some vital manipulative operations, the streaming mode is equipped to perform automatically many kinds of "adjustments" upon the stream of data and the operation applied to it. In addition to the automatic adjustments the streaming mode has a small repertoire of "hybrid" instructions which perform basic arithmetic and logical functions but which utilize the various independent indexing and addressing facilities of Harvest to gain speed and generality. Lastly, a few streaming conditions are represented in the indicator register and may stimulate action there upon completion of the streaming instruction.

H2. 1 10/21/57

## H2.1 General Operation

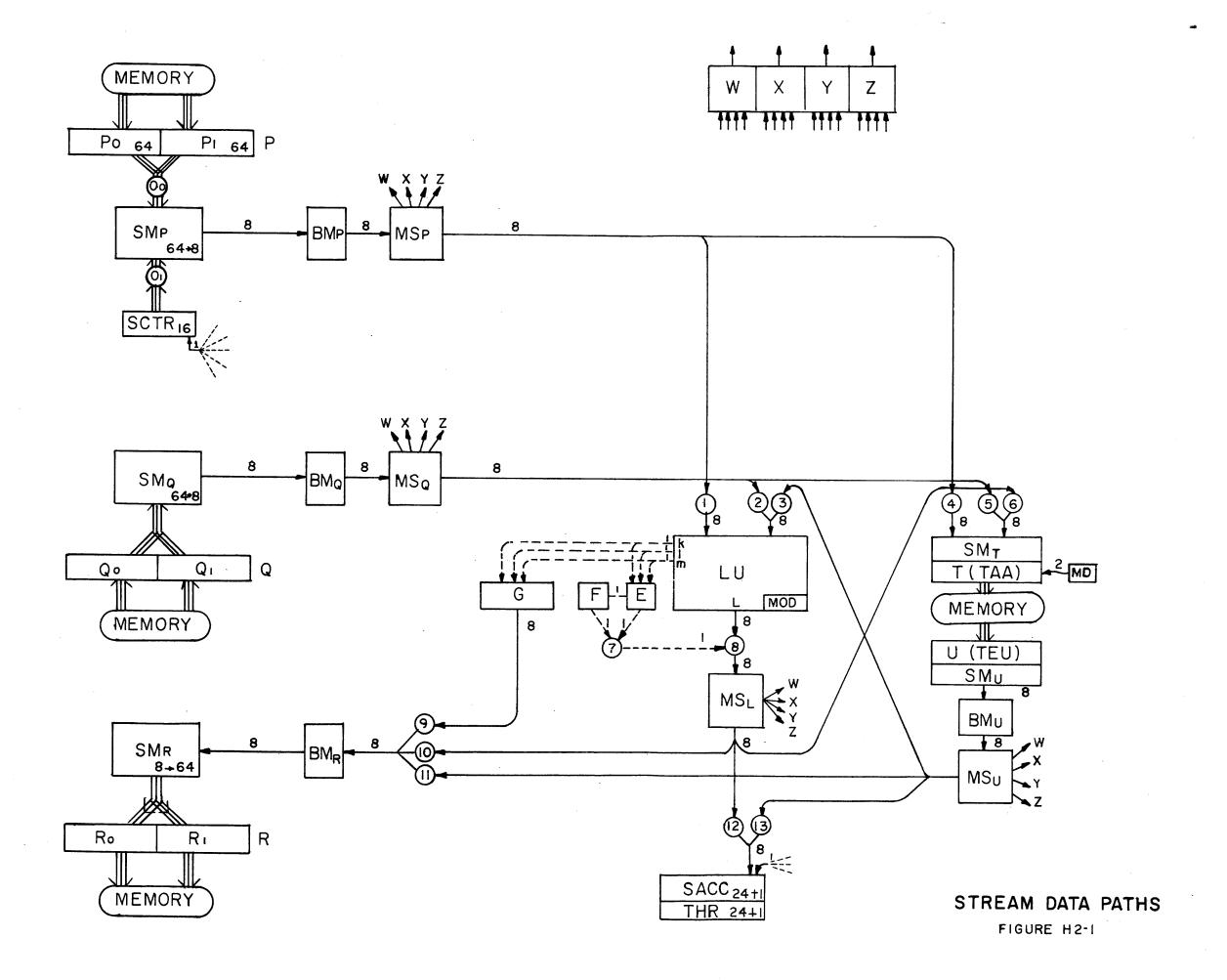

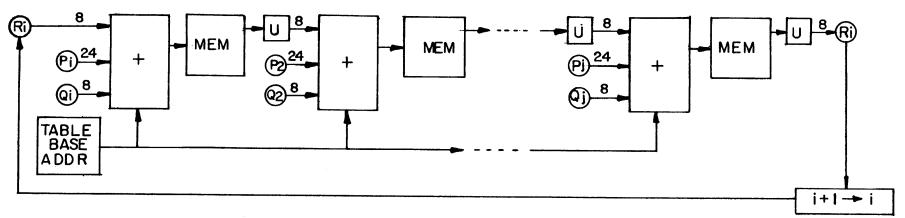

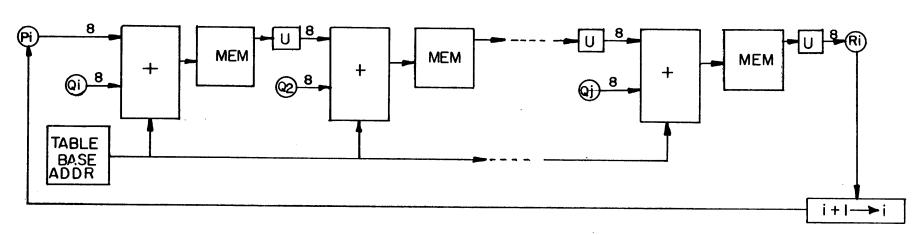

Figure H2. 1 shows the various functional units of the Harvest CPU and the data paths and gates that connect them. The general operation of these units is described in the sections that follow.

#### H2. 1. 1 Stream Units P and Q

These units control the input data streams. Each consists of a double length (128-bit) register ( $P_0$ - $P_1$  or  $Q_0$ - $Q_1$ ), an associated switch matrix ( $SM_P$  or  $SM_Q$ ), and a built-in indexing unit (see Chapter H1). The SU built-in controls permit automatic loading of the registers with 64-bit words from memory, normally without any interruption in the stream of bytes being generated. The streams consist of 8-bit bytes that are read from the registers and switched to the byte buses for processing.

#### H2.1.2 Stream Unit R

This unit (consisting of a double length register,  $R_0$ - $R_1$ , the switch matrix  $SM_R$ , and a built-in indexing unit) is used primarily to store a data stream in memory. It switches 8-bit bytes from the byte bus to the proper positions in its double length register. The contents of these registers are then normally stored automatically as full 64-bit words in memory.

#### H2. 1. 3 Stream Unit T, the Table Address Assembler (TAA)

The Table Address Assembler provides a means of assembling bytes from one or more SU's together with the contents of a register and a program-controlled counter, the Memory Distributor (MD), to form addresses for table lookup, counting in memory, and other similar memory reference functions.

The word referenced in memory may have a 1 added or or-ed to it in a designated position. Moreover, the original, unchanged word referenced may be sent to the Table Extract Unit (TEU).

The TAA consists of a 24-bit register, T, an associated switch matrix,  $\mathrm{SM}_{\mathrm{T}}$ , a base address register, the memory distributor, MD, and a simplified built-in indexing unit.

## H2.1.4 Stream Unit U, the Table Extract Unit (TEU)

The Table Extract Unit is a data storage register similar in design to the Stream Units. Its primary function is to receive data words from memory as addressed by the Table Address Assembler and to select from them the appropriate bytes for transfer to other units in the computer.

A single length register, U, a switch matrix,  $\mathrm{SM}_{\mathrm{U}}$ , and a single-level built-in indexing unit make up the TEU.

#### H2. 1. 5 Statistical Accumulator (SACC) and Threshold Register (THR)

The SACC accumulates input bytes that come from the Logic Unit, LU, or from the TEU. It may also be stepped by any one of several 1-bit signals from various parts of the CPU. Associated with the SACC is a special Threshold register, THR, which may be loaded as a part of the setup operation. Whenever the value in SACC reaches or exceeds the value in THR, a special 1-bit signal is produced. This signal may cause special action to take place in the CPU.

#### H2. 1. 6 Statistical Counter (SCTR)

The SCTR may be stepped by practically any 1-bit signal from the Harvest CPU. Its contents may be gated onto the byte bus to SU-R by Adjustment operations. The SCTR may be reset automatically. It also may be connected to SMp and have its current contents continuously available for logical operations.

#### H2. 1. 7 Logic Unit (LU)

The LU performs a variety of arithmetic and logical operations on the successive bytes or pairs of bytes presented to it. It provides an 8-bit output, L, and three 1-bit outputs, k, 1, and m. L may be gated onto the byte bus. A selected set of the 1-bit signals, k, 1, and m are or-ed together to produce a 1-bit signal, E. This signal may also be put on the byte bus, or be used to cause Adjustments.

H2. 1 10/21/57

#### H2.1.8 F

F is a small memory device used primarily to record the changes in E. It may be gated to the byte bus or may automatically adjust the flow of data in the CPU.

## H2.1.9 Group Signal (G)

G is a memory device used to record the status of groups of bytes that pass through the LU. The size of the group is specified in the particular stream instruction being used. The status recorded is a function of the three 1-bit signals, k, 1, and m. The output of G is an 8-bit byte that may be gated to R, or be used to cause Adjustment.

## H2. 1. 10 Byte Masks (BM)

In order to provide a ready means of operating upon any size byte from 1 through 8 bits and on any subset of bits within a byte the four byte masks BMp, BMQ, BMR, and BMU are provided in association with the corresponding SU's. In particular, BMR indicates which bits are to be stored in a memory word and which are not. The mask format is specified as a part of the streaming setup (see Section H1.1 and Figure H1.1a).

# H2.1.11 Match Units (W, X, Y, and Z)

During the streaming mode of operation it is possible to monitor input and output streams for the occurrance of prespecified bytes. The four units W, X, Y, and Z provide a capacity for specifying four different special bytes at any one time. Automatic adjustment of the data flow may be initiated upon recognition of a prespecified byte.

### H2.2 Harvest Setup

In order to execute a Harvest stream instruction, the programmer must initialize, or set up, the Harvest CPU. He accomplishes this by loading various memory positions — i. e., set up registers — with the proper values of a number of parameters and control bits while in the arithmetic mode of operation.

Figure H2.2 shows the array of twenty consecutive words (forty consecutive half words) that comprise the complete Harvest setup. The setup registers are loaded, just as any memory position is loaded, by STORE, TRANSMIT, SWAP, etc., instructions. For example, if the twenty word setup array is stored in memory beginning at location x + 1, then the parameters contained in the third setup word (righthand column of numbers, Figure H2.2) may be loaded in to the appropriate setup register by TRANSMIT two half words from x + 3 to 15 (lefthand column of numbers, Figure H2.2). By TRANSMIT forty half words from x + 1 to 13, all the setup parameters and control bits would be loaded in the appropriate setup registers. VFL instructions may be used to load or store any particular parameter or control bit. In Figure H2.2, the number directly under a field is its bit address; the number in the field is its field length (one-bit field lengths are not designated).

#### H2.2.1 The Setup Words

Setup words 1 through 9 and 15 through 20 have been described in Section H1.2. They contain the stream index control parameters and control bits.

Setup word 10 contains the parameters for the TAA and the MD. Setup word 11 contains the parameters for the TEU. The use of these parameters and control bits is described in Section H2.5.

Setup word 12 contains the parameters for all four MU's. Their use is discussed in Section H2.6.

Word 13 contains the parameters for the SACC and SCTR, while word 14 contains the THR. These parameters are described in Section H2.7.

Setup word 14 also contains E, F, G (discussed in Section H2.4.2), MOD (Section H2.4.1), and RS (Section H2.9).

H2. 2 10/25/57

## H2. 2. 2 Initial and Developed Values of Parameters

The values of most of the parameters and control bits must be designated by the programmer in the setup before streaming begins. However, certain parameters and control bits have values that are developed during the streaming mode of operation of Harvest, S<sub>U</sub>, BA<sub>T</sub>, E, F, G, RS. The programmer is concerned with the values of these parameters only if streaming has been interrupted; he is not concerned with their initial values. The abbreviations for these fields are in parentheses in Figure H2.2.

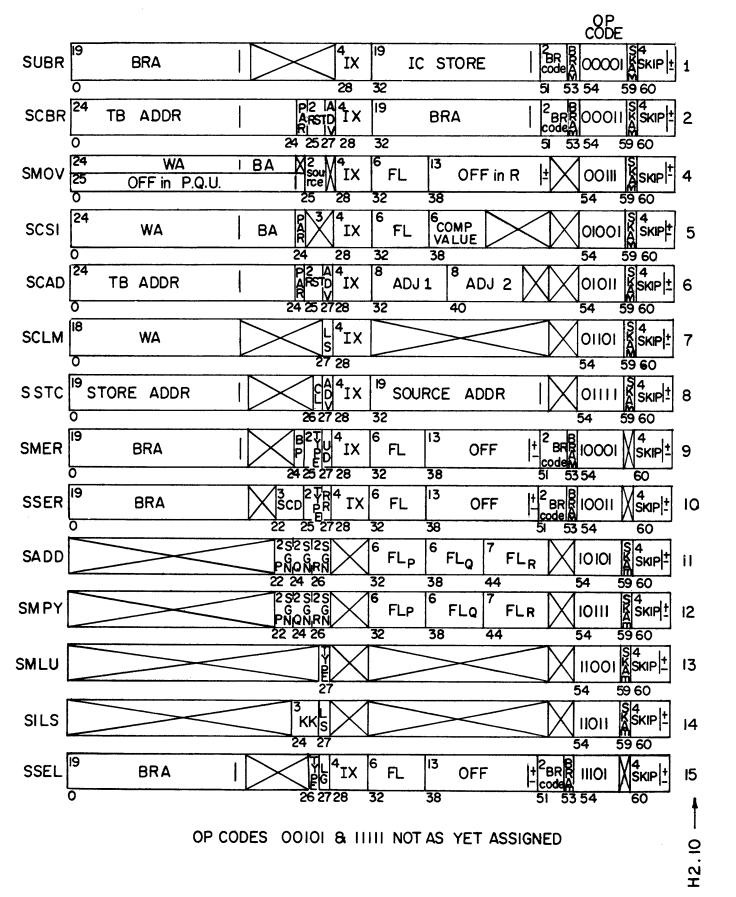

## H2. 2. 3 SKIP and SKAM

As was indicated in Section H2, while Harvest is in the streaming mode the programmer has the responsibility of designating how the Instruction Counter, IC, must change from instruction to instruction. In order to accomplish this, the programmer uses a four bit (three bits plus sign) SKIP field (Figure H2.10) in every stream instruction (whether byte-by-byte or hybrid). The value of this field is added algebraically to the current value of the IC at the end of execution of the stream instruction, giving IC + SKIP as the location of the next instruction to be executed.

The programmer also must indicate whether or not the next instruction is in the arithmetic mode. If the control bit SKAM (skip to arithmetic mode) has the value 1, then the next instruction is in the arithmetic mode; if the value is zero, then the computer remains in the streaming mode.

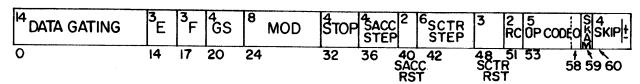

# H2. 3 SBBB - The Stream Byte-by-Byte Instruction

Byte-by-byte operations require additional parameters not specified in the setup words. These parameters are presented in the Stream Byte-by-Byte Instruction itself. They include:

- a) Data Gating the interconnection of the various processing units (H2.3.1)

- b) Op Code the operation to be performed in the Logic Unit (H2.4.1)

- c) MOD the modulus in modular operations; an extra available 8-bit byte in others (H2.4.1)

- d) F Mode the behavior of F (H2.4.2)

- e) GS the group size (H2.3.2)

- f) STOP the criterion for passing to the next instruction (H2.3.3)

- g) RC the control of R storage (H2. 3. 4)

- h) SKIP and SKAM the progression to the next instruction (H2.2.3)

#### H2. 3. 1 Data Gating

The data paths that are to be used in a byte-by-byte stream operation are specified by the first fourteen bits of the instruction. Each of these fourteen bits refers to a particular gate in the network of data paths (see Figure H2.1). Some of the gates act merely as switches: i. e., they select between two possible sources. Most act as true gates: i. e., they permit or prevent the passage of data. The specific actions of and restrictions on each gate are described in paragraphs H2.3.1.1 - H2.3.1.6. These restrictions insure that the expected result of an operation is actually obtained. Other combinations are at the user's risk.

#### H2. 3. 1. 1 Gate #0

- $0 = Data from Register P enters SM_P$

- 1 = Data from SCTR enters SMp

This gate is used to put the current contents of SCTR on the byte buses for further processing.

In addition to specifying that Gate #0 is set at 1 one must also set up Register P indexing to specify what exactly is read out of SCTR. For this purpose the SCTR acts as a register whose bits 34-49 are the current value of the SCTR, the other 48 bits all being 0. Only the bit portion of the addresses generated by P indexing are used when Gate #0 is set at 1.

#### H2. 3. 1. 2 Gates #1, 2, 3, 4, 5, and 6

These gates control the paths:

- 1: P -- LU

- 2:  $Q \rightarrow LU$

- 3: U → LU

- 4: P ——T

- 5: Q → T

- 6: LU → T

For all these gates:

0 = closed; no data passes

1 = open; data passes

Gates #2 and #3 cannot be open simultaneously. They both refer to one input to the LU.

Gates #5 and #6 cannot be open simultaneously. They both refer to one input to T.

Gates #3 and #6 cannot be open simultaneously. This "Figure 8" path has been dis-allowed because of the extreme difficulty in controlling it satisfactorily.

Gate #6 cannot be open if Gate #2 is closed. The second level of indexing of T is controlled by Q when Gate #6 is used.

At least one of Gates #1, #2, #4, and #5 must be open. Some input is needed.

Gate #3 cannot be open if both Gates #4 and #5 are closed. There must be an input to T if something is to emerge from U.

Thus there are altogether 25 allowable combinations for these six gates:

any xx0xx0 except 000000 x011x0 x01010 x10x01

For combinations 101100, 101110, and 110101:  $N_1P$  must be 1. For combination 110110:  $N_1P$  and  $N_1Q$  must both be 1.

H2. 3. 1. 3 Gate #7

0 = E → Gate #8 1 = F → Gate #8

H2. 3. 1. 4 Gate #8

$0 = L \longrightarrow MS_L$   $1 = \text{Output of Gate } #7 \longrightarrow MS_L$

If the output of Gate #7 is put on the byte bus to  $MS_L$ , the significant bit is put on the leftmost of the eight lines. The righthand seven bits are made 0.

H2. 3. 1. 5 Gates #9, #10, and #11

000 = no readin to R

$001 = U \longrightarrow R$

$010 = \text{output of } MS_L \rightarrow R$

011 = not allowed

$100 = G \longrightarrow R$  at end of group

101 = not allowed

110 = not allowed

$111 = G \longrightarrow R$  at every byte

H2. 3. 1. 6 Gates #12 and #13

00 = no input to SACC

$01 = U \longrightarrow SACC$

10 = output of  $MS_L \longrightarrow SACC$

11 = not allowed

#### H2. 3. 2 GS - Group Size

The GS field defines a group length in terms of the indexing parameters of the Stream Units. This length is used for control of G and assorted adjustment operations. The field is 4 bits long. The first two bits identify the level of indexing:

```

00 = end of byte

01 = end of first level

10 = end of second level

11 = end of higher level (defined by HL control bit - see H1.1)

```

The second two bits identify the controlling unit:

```

00 = SU-P

01 = SU-Q

10 = SU-R

11 = SU-U

```

Thus 0110 defines the group size as the second level of R. Codes 1011 and 1111 are defined to say that no group size is specified.

#### H2. 3. 3 The STOP Code

The STOP Code specifies when to terminate this byte-by-byte instruction and progress to the next instruction. If the instruction is stopped in some other way before this point is reached, this field naturally does not apply. The first two bits specify the end-of-level signal which controls the STOP:

```

00 = end of byte

01 = end of first level

10 = end of second level

11 = end of chain (defined by EC control bit - see H1.1)

```

The second two bits identify the controlling unit:

```

00 = SU-P

01 = SU-Q

10 = SU-R

11 = SU-U

```

Thus 0100 specifies STOP at the end of the first level in P. Codes 1011 and 1111 are defined as NO STOP. Some other means of getting to the next instruction must then be arranged.

#### H2.3.4 RC - R Control

The first bit of this two-bit field designates how R is to store information during byte-by-byte operations:

- 0 = The data formed in R is to be sent to memory, totally obliterating any previous data in that memory word. Any bits not specified will be made 0's.

- 1 = The data formed in R will replace the corresponding bits in memory but not affect adjacent bits. This is generally slower than option 0, but more selective.

In option 0 the R register is then initially all 0's. In option 1 the R register initially contains the contents of the memory word in which the data will be stored. As each byte enters, the bits opposite 1's in  $BM_R$  will replace the bits already in R; the bits opposite 0's in  $BM_R$  will have no effect.

The second bit designates how R is to behave at the conclusion of a byte-by-byte operation:

- 0 = R is to be stored before proceeding. (This insures that results which do not occupy a full word will still be stored.)

- 1 = R is not to be stored. (Storage is to be avoided in some types of instruction loops.)

H2. 4 10/23/57

### H2. 4 The Action of the Logic Unit in Byte-by-Byte Streaming

During streaming one may obtain any possible function of a set of bytes by means of the table lookup facility. Nevertheless a separate Logic Unit is provided. There are several reasons: many functions are extremely simple and regular; table lookup slows down when references to memory occur in a random order; large tables can often be reduced in size by first performing a simple function on the operands; if a table is to be used, it must first be read into memory while built-in functions in the LU are always immediately available.

The LU accepts an input byte from either or both of two sources and produces one output byte. In a streaming operation the LU performs the same function upon each set of sequentially presented inputs. The function, routing of the bytes, and other details of the stream operation are specified in advance by means of a series of setup instructions and by the stream instruction itself. The setup remains fixed until specifically altered.

The eight lines from registers P and Q or U lead directly to the eight positions of the LU. The lowest-numbered bit (the leftmost or high-order bit) of an input register goes to the leftmost position of the LU.

The 8-bit outputs of the LU correspond bit by bit to the inputs. All eight bits may travel to each of three possible recipients: R, T, and SACC.

In addition to the byte output the LU produces three primary 1-bit signals -k, 1, and m - which are combined in units E, F, and G. These are described in Section H2.4.2.

#### H2. 4. 1 The Byte-by-Byte Operations

In the definitions of the operations P represents the input from P. Q represents the input from Q or U, depending on the data gating. If a function requires two operands — and most do — and only one gate to the LU is open, the missing operand is automatically taken to be all 0's.

For logical operations bytes are regarded merely as an ordered set of bits. For comparison and modular arithmetic bytes are regarded as unsigned positive numbers in binary form.

To obtain the expected answer in modular arithmetic P, Q, and MOD must all have the same byte size - just sufficient for representation of MOD - and be positioned as far to the left as possible. P and Q must already have been reduced to a value between 0 and MOD-1, inclusive. When MOD is specified in the setup (see Figure H2.4) the pertinent bits are to the left; empties on the right are filled with 0's. BMp and BMQ must have 1's in those positions corresponding to the proper byte size with 0's in the other (righthand) positions. For example; proper use of a modulus of 22 requires:

$BM_P = BM_O = 11111000$

MOD = 10110000

bytes from P, Q = xxxxx---

(A MOD of 10110000 is used not only for 22, but also for 44, 88, and 176. Which it acts as is determined by the placement and size of P and Q.)

The 32 Byte-by-Byte logical operations are specified by five bits of the op code of the stream instruction. See Figure H2.4 (the sixth bit says that the instruction is a byte-by-byte instruction rather than a hybrid instruction). They are defined as follows:

| OP Code | <u>L =</u> | Byte Output  | k        | = 1       | 1 = 1      | m = l      |

|---------|------------|--------------|----------|-----------|------------|------------|

| 0       | Logical    | Connection C | Connect  | ion all 0 | Connection | Connection |

|         |            |              |          |           | of even    | of odd     |

|         |            |              |          |           | parity but | parity     |

|         |            |              |          |           | not all 0  |            |

| 1       |            | '' 1         |          |           | 11         | 11         |

| 2       | ,          | " 2          | 1        | 11        | 11         | 11         |

| 3       |            | 11 3         | }        | it .      | 11         | 11         |

| 4       |            | 11 4         | <u> </u> | 11        | 11         | 11         |

| 5       |            | '' 5         | <b>;</b> |           | 11         | 11         |

| 6       |            | " 6          | )        | 11        | ft .       | 11         |

| 7       |            | " 7          | ,        | 1 #       | TT         | 11         |

| 8       |            | " 8          | }        | 11        | 11         | 11         |

| 9       |            | 11 9         | ,        | it.       | 11         | 11         |

| 10      |            | " 1          | .0       | 11        | 11         | 11         |

| 11      |            | " 1          | 1        | 11        | 11         | 11         |

| 12      |            | 711          | .2       | 11        | 11         | tf         |

| 13      |            | " 1          | .3       | 11        | t t        | tt .       |

| 14      |            |              |          | H.        | f f        | 11         |

| 15      |            |              |          | 11        | 11         | 11         |

|         |            |              |          |           |            |            |

| OP C | Code L = Byte Output                | k = 1     | 1 = 1     | m = 1             |

|------|-------------------------------------|-----------|-----------|-------------------|

| 16   | Max (P, Q)                          | P > Q     | P=Q       | P <q< td=""></q<> |

| 17   | Min (P, Q)                          | tt        | . 11      | 11                |

| 18   | P if P = Q, otherwise all 0         | 11        | . 11      | 11                |

| 19   | P  if  P = Q, otherwise no byte     |           |           |                   |

|      | output                              | 11        | 11        | 5.1               |

| 20   | P if $P \neq Q$ , otherwise all 0   | 11        | 11        | 11                |

| 21   | P if P # Q, otherwise no byte       |           |           |                   |

|      | output                              | 11        | 11        | 11                |

| 22   | Q if P # Q, otherwise all 0         | 11        | 11        | 11                |

| 23   | Q if $P \neq Q$ , otherwise no byte |           |           |                   |

|      | output                              | 11        | tŤ        | 11                |

| 24   | P - Q if P≥Q, otherwise all 0       | 11        | 11        | 11                |

| 25   | P - Q if P≥Q, otherwise no          |           |           |                   |

|      | byte output                         | 11        | .11       | 11                |

| 26   | Q - P if Q≥P, otherwise all 0       | 11        | 11        | 11                |

| 27   | Q - P if Q≥P, otherwise no          |           |           |                   |

|      | byte output                         | 11        | 11        | 11                |

| 28   | P - Q modulo MOD (MOD ≤255)         | 11        | 11        | 11                |

| 29   | Q - P modulo MOD "                  | 11        | 11        | 11                |

| 30   | P + Q modulo MOD "                  | 11        | 11,       | 11                |

| 31   | P + Q modulo MOD "                  | P + Q > M | P + Q = M | P + Q < M         |

The 16 Logical Connections referred to above are:

| Code | Logical Connection                           |    |     | PQ |    |

|------|----------------------------------------------|----|-----|----|----|

|      | ,                                            | 00 | 01. | 10 | 11 |

| 0    | 0                                            | Ō  | 0   | 0  | 0  |

| 1    | P·Q                                          | 0  | 0   | 0  | 1  |

| 2    | $\mathtt{P} \boldsymbol{\cdot} \overline{Q}$ | 0  | 0   | 1  | 0  |

| 3    | P                                            | 0  | 0   | 1  | 1  |

| 4    | $\overline{\mathbf{P}} \cdot \mathbf{Q}$     | 0  | 1   | 0  | 0  |

| 5    | Q                                            | 0  | 1   | 0  | 1  |

| 6    | P ₩ Q                                        | 0  | 1   | 1  | 0  |

| 7    | P v Q                                        | 0  | 1   | 1  | 1  |

| 8    | ₽·Q                                          | 1  | 0   | 0  | 0  |

| 9    | P ≡ Q                                        | 1  | 0   | 0  | 1  |

| 10   | $\overline{Q}$                               | 1  | 0   | 1  | 0  |

| 11   | ΡνQ̄                                         | 1  | . 0 | 1  | 1  |

| 12   | $oldsymbol{ar{P}}$                           | 1  | 1   | 0  | 0  |

| 13   | $\overline{\mathtt{P}}$ v Q                  | 1  | 1   | 0  | 1  |

| 14   | $\overline{P} \vee \overline{Q}$             | 1  | 1   | 1  | 0  |

| 15   | 1 · · · · · · · · · · · · · · · · · · ·      | 1  | 1   | 1  | 1  |

#### H2.4.2 E, F, and G

The three primary 1-bit signals of the LU-k, 1, and m-are manipulated in the units E, F, and G to produce other signals which enter into the streaming operations. These signals are all calculated at the same time as the byte L. Since they occur in the first segment of the byte path – from input register to LU-they are available for controlling the indexing of the registers feeding the LU.

E is the final one-bit output of the Logic Unit. It may be put on the byte bus, cause SCTR to step, or cause an adjustment. It is calculated by specifying in a 3-bit field in the byte-by-byte instruction which of the bits k, l, and m are to be or-ed together. The three bits correspond to k, l, and m in that order. Thus an E field of 101 in the instruction means that E consists of the "or" of k and m.

F is a small memory device used to record changes in E. It takes its input from E and changes state according to a 3-bit F field in the byte-by-byte instruction. The coding there means:

| 000 | Stay on 1 after the first | one has be  | een received | i             |

|-----|---------------------------|-------------|--------------|---------------|

| 001 | Change state on 1         |             | ¥            |               |

| 010 | Set to 1 if the previous  | bit was 0,  | the current  | bit 0         |

| 011 | 11                        | Ο,          | 11           | 1             |

| 100 | 11                        | 1,          | 11           | 0             |

| 101 | 11                        | 1,          | 11           | 1             |

| 110 | Set to 1 if the previous  | bit and the | current bit  | are the same  |

| 111 | - 11                      |             |              | are different |

F is set to 0 at the beginning of this byte-by-byte instruction and at every end-of-group signal occurring during the instruction. The output of F may be put on the byte bus, cause SCTR to stop, or cause an adjustment.

G is a memory device used to infer and record the status of groups from analysis of the bytes within the groups. It is fed directly by k, l, and m from the Logic Unit. G may stimulate the SCTR or cause an adjustment. Its output may go to R through Gate 9.

This output is an 8-bit byte:

a) For logic operations 0-15:

```

Bits 0 and 1: 00 = (does not arise)

01 = Group connection all 0

10 = Group connection of even parity but not all 0

11 = Group connection of odd parity

```

H2.4 10/23/57

Bit 2 = 1 if group connection all 0, 0 if not all 0

Bit 3 = 1 if group connection of even parity, 0 if of odd parity

Bit 4 = 1 if group connection of even parity but not all 0, 0 if of odd parity or all 0

Bit 5 = 1 if group connection not all 0, 1 if all 0

Bit 6 = 1 if group connection of odd parity, 0 if of even parity

Bit 7 = 1 if group connection of odd parity or all 0, 0 if of even parity but not all 0

b) For operations 16-31:

```

Bits 0 and 1: 00 = (does not arise)

01 = Group P > Group Q

10 = Group P = Group Q

11 = Group P < Group Q

```

```

Bit 2 = 1 if Group P>Group Q, 0 if Group P≤Group Q

, 0 if

2

Bit 3 = 1

, 0 if

11

11

Bit 4 = 1

<

11

11

11

11

Bit 5 = 1

0 if

≥

11

Bit 6 = 1

11

11

0 if

11

11

*

0 if

11

Bit 7 = 1

```

- c) The output outlined in (b) above does not really have a straightforward interpretation for operation 31. However it is put in this category because of the similarity of its k, 1, and m outputs to those of operations 16-30.

- d) Selection of the bits for storage thru R is made by BMR and the R indexing.

H2.5 10/25/57

### H2. 5 The Functioning of T and U in Byte-by-Byte Streaming

The Table Address Assembler (T) and the Table Extract Unit (U) are provided to facilitate the referencing and altering of tabular quantities stored in memory. T forms table addresses from a Base Address and one or more bytes, while U converts the extracted word into bytes for further processing.

The word referenced by T may be extracted. If the word lies in the 2-microsecond memory it may also have a 1 or-ed in the addressed bit after extraction takes place. If the word lies in the 1/2-microsecond memory the same or-ing can take place. Alternatively, in the 1/2-microsecond memory only, the 1 may be added in a selected position after the extraction. These three functions are referred to as "extraction", "or-ing in memory", and "counting in memory".

For extraction, the address formed by the TAA refers to the left-hand bit of the first byte that is extracted by the TEU. For or-ing in memory, the address formed by the TAA refers to the bit in memory to which a 1 is or-ed. For counting in memory, the address formed by the TAA - after a modification - refers to the bit in memory to which a 1 is added. For a combined action e.g., extract and count - the formed address may serve two different functions.

#### H2.5.1 T

The TAA may accept bytes from two sources. The first is the output of MSp through Gate #4, that is, either P or SCTR. The second is either the output of  $MS_Q$  or the output of  $MS_L$ , depending on whether Gate #5 or Gate #6 is open. How the bytes enter and are positioned in the address is determined both by the parameters given in the T setup word (#10) and by end-of-level signals coming from P and Q.

The sequence of steps performed in forming the table address are:

- 1) TBA (the Base Address, specified in the setup word) enters the cleared address accumulator.

- 2) If Gate #4 is set at 1, a set of bytes from the first source enters the address accumulator via the T Switch Matrix and is added to the Base Address. The number of bytes entered is N<sub>1</sub>p. The first byte is positioned so that its leftmost bit is at the start point V (specified in the setup). (The positions in the table address are labelled 0-23, as are the other addresses.) The next byte is positioned so its leftmost bit is at the point V + I<sub>1</sub>T. The next, at V + 2I<sub>1</sub>T. At the

H2.5 10/25/57

end-of-first-level-in-P signal, readin from the first source is discontinued. The position of entry of the last byte from this source now has another  $I_{1\,T}$  added to it.

If Gate #4 is set at 0, there is no read-in from the first source. V is not incremented.

- 3) a) If Gate #4 was set at 1, the start point for the second source is V + N<sub>1</sub>P I<sub>1</sub>T. If Gate #4 was set at 0, the start point for the second source is V.

- b) If either Gate #5 or #6 is set at 1 but not both, a set of bytes from the second source enters the address accumulator via the T Switch Matrix and is added to the current contents. The number of bytes entered is N<sub>1Q</sub>. If Gate #5 is open the bytes come directly from Q. If Gate #6 is open the bytes come from the Logic Unit. However in this latter case Gate #2 must also be open the actual entry can be 0, if necessary. Then the end-of-level signal from Q will flow along with the bytes to the TAA and govern the end of the readin. The first byte is positioned as in (3a) above. The next byte is at that position plus I<sub>2</sub>, etc., until all have been read in.

- c) If neither Gate #5 or Gate #6 was set at 1, nothing enters from source two, and the assembling of bytes is complete at the end of the readin from source one.

- 4) If during the readin of bytes from either source the input byte "hangs over" the right edge of the address mechanism, the excess bits are disregarded. If the positioning address of the input byte is negative the entire byte is disregarded.

- If the Memory Distributor Mode Bit (MDM) is 0 the assembling of the table address is now complete. If MDM is 1, this further operation takes place: Bits 0-17 of the assembled address are each shifted two places left. (This destroys Bits 0 and 1.) The two bits from the Memory Distributor field (MD) are put in the vacated positions 16 and 17. The MD then is increased by 1 modulo 4 and will insert this increased value into the next assembled table address. It keeps counting modulo 4 on every subsequent address and thus cycles the addresses through the four interleaved memory units.

6) If extraction is to be performed, the bit portion of the assembled address is sent to the TEU. If or-ing in memory is to take place, the bit portion of the address designates where in the memory word the 1 is to be or-ed. If counting in memory is to take place, the bit portion of the address is further modified to determine where in the memory word the 1 is to be added. See below.

A 3-bit field in the T setup word specifies the TAA mode (TAM). The bits refer, respectively, to counting in memory, or-ing in memory, and extraction, and a 1 means that the function takes place. More precisely:

TAM: 000 = No memory reference is made. The 24-bit table address is sent directly to the first 24 bits (#0-23) of U.

001 = The referenced word is extracted from memory and sent to U.

010 = A 1 is or-ed to the referenced word in memory at the position designated by the bit portion of the address.

011 = The successive performance of operations 001 and 010.

100 = (1/2-microsecond memory only) A 1 is added to the last position of the cell in memory containing the addressed bit. (See below for explanation of cell size.)

101 = (1/2-microsecond memory only) The successive performance of operations 001 and 100.

Not defined.

Counting in memory may take place in cells of size 8, 16, or 32. A counting cell resides entirely within a single memory word and a word is completely filled with cells of one size. For the three possible sizes of cells, one memory word contains either 8, 4, or 2 cells respectively. The one is added to the righthand bit of the cell. If a cell should attempt to overflow, the entry in the cell will become all 0's, but the attempted carry will not propagate to the next cell. Moreover the Memory Counter Overflow Indicator (Bit #43) will go on so that one may check at the end of the counting operation to see if any cell did overflow. (A more current check may be managed for 8-bit cells by monitoring the output of U in MSU. However the necessary Match Unit is not always available.)

The cell size is determined by the 2-bit K field in the setup word:

8 = 00

01 = 16

10 = 32

The coding sets up the overflow control. To determine where the 1 is to be added to the memory word, the K field is or-ed to bits 19 and 20 of the assembled table address. In addition, the number 111 is or-ed to bits 21, 22, and 23 of the assembled address. Thus the 1 can be added to the memory word only in every 8th position – i. e., at bit positions 7, 15, ..., 63.

Bit #50 of the T setup word is the Replace Bit (RPL). If it is 0, everything procedes as described above. If it is 1, everything procedes as described for the formation of the first table address. However then the initial base address is replaced by the just-formed first address. And on every subsequent address formation the base address used is the table address formed just previously.

#### H2.5.2 U

The address of the word entering the Table Extract Unit is placed in the word portion of  $S_U$ . The bit address has already come from the TAA and has been put both in the bit portion of  $S_U$  and in the  $BA_T$  field. The left bit of the first byte to be read out is specified by this bit address. After the first byte has been read out, the bit portion of  $S_U$  is increased by  $I_U$ ; this gives the location of the second byte, etc. The number of bytes read out is  $N_U$ . The only index reset available in U is to the beginning of the reference. In this case  $BA_T$  replaces the bit portion of  $S_U$ , and  $M_U$  is set to 0.

If the bit address of the byte to be extracted is so close to the right edge of the word that fewer than eight bits can be obtained from U, the overhanging ones are automatically made 0. If the bit address goes higher than 63 the carry to the word portion of the address is suppressed. Thus there is cyclic readout in a slightly degraded sense.

$S_U$  and  $BA_T$  are not set up. They always get their information from T. If the operation stops at any time  $S_U$  indicates the address of the last byte read out. BMU specifies Byte Mask U.

## H2.6 The Match Units (W, X, Y, Z)

Four Match Units are provided to monitor the information passing on the byte buses. The Match Units may be connected to the buses at any of four Match Stations (MS's) within the computer. MSp monitors the output of P; MSQ, the output of Q; MSL, the output of the Logic Unit and its associated signals; and MSU, the output of U. Several Match Units may be connected to the same Match Station, but no unit may be connected to more than one Match Station.

The Match Units normally look at every byte. Some automatic adjustments may specifically disable them for one or more bytes. The RUNOUT indexing level adjustments also disable them.

The operation of the Match Units is specified in one setup word. For each unit there are 14 bits, and the same format applies to all:

First 8 bits:

The Match Character (W, X, Y, Z)

Next 3 bits:

The point of connection (CON)

0xx: No connection

100: MS<sub>P</sub> 101: MS<sub>Q</sub> 110: MS<sub>L</sub> 111: MS<sub>II</sub>

Next bit:

The Span Bit (SP)

- 0: The Match Unit compares all 8 bits of the passing bytes with all 8 bits of the Match Character.

- 1: The Match Unit compares only the rightmost bit of the passing bytes with the rightmost bit of the Match Character.

Next bit:

The Swallow Bit (SW)

- 0: Regardless of whether or not a match occurs, the bytes pass the Match Station without alteration.

- 1: If a byte is matched (regardless of SP or MN setting) the entire byte is suppressed taken off the bus and the next byte from that sending unit is automatically called for.

Last bit:

The "Match or No-match" Bit (MN)

- 0: An adjustment is performed on a match.

- 1: An adjustment is performed on a no-match.

Note: Swallowing takes place only on matches; adjustment, on either matches or no-matches.

The Match Units may send counting pulses to the SCTR or the SACC - this is determined by the SCTR and SACC setup in the byte-by-byte stream instruction. However their main function is to signal automatic adjustments. The word following the byte-by-byte instruction specifies what these adjustments are to be. See H2.8.

In the specification of adjustments the "simultaneous observation of W and X or of Y and Z" is referred to. The pair W and X are defined to signal adjustment simultaneously only when their specified recognition conditions have arisen and they are connected to the two byte buses entering the Logic Unit (one to each bus). If P and Q supply the entries, one of W or X must be connected to MSp, the other to MSQ. If P and U supply the two entries, one of W or X must be connected to MSp, the other to MSQ.

If W or X signal simultaneously in this sense, the W-X adjustment field is first consulted. If this says "sum of actions", the W adjustment is first performed, then the X adjustment. If it says anything else, this W-X adjustment is performed and the individual W and X adjustments are disregarded.

Y and Z simultaneity is defined similarly.

Because of the timing involved in an assembly-line processing of data, the Match Units are not free to perform unrestricted adjustments. The restrictions that insure meaningful results are detailed in H2.8.

H2. 7 10/28/57:

H2.7 The Statistical Accumulator and Statistical Counter (SACC and SCTR)

#### H2. 7. 1 SACC

The basic function of SACC is to accumulate bytes from either the Logic Unit or the Table Extract Unit. The input from the Logic Unit is usually either E or F signals or the data itself from P or Q. The input from U is generally more important in that two frequently-used statistical functions can be calculated during a table addressing operation. a) During a count in memory the function

$$\frac{1}{2} \sum_{i=1}^{n} f_{i} (f_{i} - 1) = \sum_{i=1}^{n} \frac{f_{i} - 1}{x = 0} x$$

can automatically be accumulated. b) By using ordinary extraction the function  $\sum_{i=1}^{n} f_i$   $W_i$  can be accumulated. An initial value of SACC may be set up, and everything is then added to this.

Bytes entering SACC may be unsigned or signed. The bits in SACC are numbered 0-24, with #24 being its sign. Unsigned bytes enter bits 16-23. With signed bytes the lefthand 7 bits enter bits 16-22 while the rightmost bit of the byte interacts with the sign bit of SACC. In addition there is the option of having SACC automatically reset to 0 when its value becomes negative. The first bit of the SACC mode field (SAM) says:

0 = unsigned bytes

1 = signed bytes.

The second bit of SAM says:

0 = normal accumulation

1 = reset negative values.

Associated with SACC is a Threshold Register (THR) which is set up in advance. When the SACC value equals or exceeds the THR value a signal is generated which sets a bit in the Indicator Register and which may also cause a count or automatic adjustment.

Whether or not the SACC is being used as an accumulator it may also have one-bit counts entered into it or be automatically reset to zero, as governed by the SACC STEP and SACC RST fields in the stream byte-by-byte instruction. The counts are entered into Bit 22; this is equivalent to counting by 2's. The reset is always to 0, not to the initial value.

The coding for SACC STEP gives the source of the counting pulse:

```

0000 = no count

0001 = E = 0

0010 = E = 1

0011 = F = 0

0100 = F = 1

0101 = G = 01 at end-of-group

0110 = G = 10 at end-of-group

0111 = G = 11 at end-of-group

1000 = match in W

1001 = match in X

1010 = match in Y

1011 = match in Z

1100 = operation in LU

1101 = byte enters R

1110 = end-of-group

1111 = STOP.

```

The coding for SACC RST gives the source of the resetting pulse:

```

00 = no reset

01 = match in Z

10 = end-of-group

11 = STOP.

```

Care must be used in specifying SACC counting and resetting as some asynchrony with the byte stream may be involved. Counts are entered in addition to any bytes being entered. If the same stimulus should be specified for both counting and resetting, the reset will take place and not the count.

SACC overflow and underflow are also represented in the Indicator Register.

#### H2. 7. 2 SCTR

SCTR is a counter which can count practically any kind of signal arising in the Harvest processing units. Its current contents may also be put onto the byte buses by means of Gate #0. (See H2.3.1.)