# N. Rochester

This is the best available form of the 8106 manual. We should have it entirely rewritten within six weeks time. Regards.

J. W. Franklin Dept 251 Bldg 965 Systems Planning THE IBM 8106 DATA PROCESSING SYSTEM (Preliminary Operating Manual)

IBM CONFIDENTIAL

# Chapter l

# THE IBM 8106 DATA PROCESSING SYSTEM

# Contents

|                                      | Section | Page  |

|--------------------------------------|---------|-------|

| Introduction                         | 1.1     | 1.1   |

| System Organization                  | 1.2     | 1.3   |

| Storage Units                        | 1.2.1   | 1.3   |

| Core Storage                         |         | 1.4   |

| Shared Core Storage                  |         | 1.4   |

| Core Storage With Fast Channels      |         | 1.4   |

| Input-Output                         | 1.2.2   | 1.5   |

| Central Processor                    | 1.2.3   | 1.6   |

| System Operation                     | 1.3     | 1.8   |

| Instruction Sequencing               | 1.3.1   | 1.8   |

| Operand Addressing                   | 1.3.2   | 1.9   |

| Arithmetic and Logical Processing    | 1.3.3   | 1.10  |

| Floating-Point Arithmetic            |         | 1.10  |

| Fixed-Point Arithmetic               |         | 1.11  |

| Logical Processing                   |         | 1. 12 |

| Control-Word and Decision Operations | 1.3.4   | 1.13  |

| Data Transmission                    | 1.3.5   | 1. 15 |

| Maintenance                          | 1.3.6   | 1. 16 |

|                                      |         |       |

|                                      |         |       |

| Table - Features of the system       |         | 1.2   |

| Figure 1.1 - System organization     |         | 1.3   |

| Figure 1.2 - Data paths              |         | 1.7   |

#### IBM CONFIDENTIAL

This document contains information of a proprietary nature, ALL INFOR-MATION CONTAINED HEREIN SHALL BE KEPT IN CONFIDENCE. No information shall be divulged to persons other than IBM employees authorized by the nature of their duties to receive such information, or individuals or organizations who are authorized by IBM Product Development Laboratory or its appointee to receive such information.

OK

#### Chapter 1

#### THE IBM 8106 DATA PROCESSING SYSTEM

#### 1. 1 INTRODUCTION

The IBM 8106 Data Processing System is designed to satisfy a wide range of applications. These applications may require a disk- or tape-oriented system; a system with great data-manipulation facility or a system for technical computation; a system for conventional daily operation or one with around-the-clock availability; a system for batch or in-line processing; a system for scheduled or short-notice processing; a system operating virtually unattended or requiring extensive man-machine communication.

To meet these diverse and often conflicting requirements at an efficient cost-to-performance ratio, two principles have been used in the systems design.

The first principle is modularity of systems components. A universal interconnection is provided between the central processor and input-output to provide maximum freedom in the selection of input-output units. The choice between a disk- or tape-oriented system, or any intermediate solution, no longer affects the equipment within the central processor. Similar remarks apply to other system alternatives. The modular principle also applies to the size and characteristics of storage units, and furthermore, extends to the number and characteristics of central processing units which may be part of a system. Thus, two or more central processors may communicate with each other and with input-output units in such a manner that continuous systems availability is insured. The central processors within a system need not be identical. For instance, increased technical computing performance may be achieved by incorporating one or more IBM 8112 processors within the system.

The second principle applied in the 8106 system design is integration of a large number of basic features which enable the system to satisfy different application requirements. It is expected that each of these features will be used to some degree in all installations. However, the particular emphasis which a given feature receives will determine the operating capability of the system.

#### FEATURES OF THE SYSTEM

Direct and indirect addressing Indexing of floating-point operands Data specification by control words Chained control words Program and data relocation Multiple simultaneous input-output operation Independent instruction streams for input-output channels Multiplexed processors Rapid program switching Address protection Program interrupt Maskable indicators Interval timer Time clock Instruction count Program and data monitoring Variable precision floating point Noisy mode for floating-point significance test Floating-point extremum handling Binary and decimal fixed-point arithmetic Signed and unsigned arithmetic Arithmetic with single or multiple operands Processing on fields or streams of data Data flags Code translation Logical connectives Compressed four-bit numeric data Extended eight-bit alphanumeric characters Processing till match, clash or count Decisions on bits or bytes Error scan

The individual cost of each of these features has been reduced greatly by using a highly integrated design. Registers are shared by input-output control words, data control words, and operands. Input-output channel controls are shared by interrupt functions. Buses serve for serial, parallel, input-output, diagnostic, and initializing information flow. A fast-responding priority circuit permits simultaneous data flow through several input-output channels, flexibility in operand designation, immediate response to system alerts, and accurate fault location.

Automated fault location

#### 1.2 SYSTEM ORGANIZATION

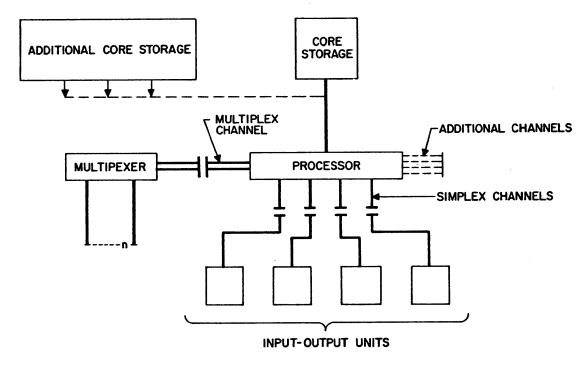

A basic system is composed of a central processor, core storage, and input-output. Information moves between input-output devices and core storage via channels which are part of the central-processing unit. The central-processing unit further consists of registers, arithmetic devices, and control circuits necessary for performing operations upon data taken from core storage. The central processor is controlled by a succession of instructions which themselves come from core storage. Registers and controls are shared in performing the tasks of channel operations, data manipulation, and instruction modification.

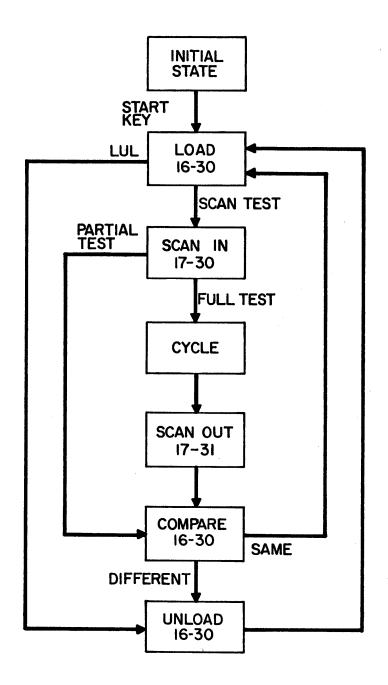

Figure 1.1 - System organization

### 1.2.1 Storage Units

The computing system uses core storage units with a read-write cycle time of two microseconds. A word consists of 64 information bits and eight nonaddressable redundancy bits. The redundancy bits are provided for error detection by the central processor and the input-output units.

The address space in instructions provides for processing directly on any operation any of 65,536 (2<sup>16</sup>) word locations numbered 0 to 65,535 consecutively. Some of the low-order addresses are reserved for special purposes.

#### 1.2.1.1 Core Storage

Storage units contain 4096, 8192, or 16,384 words. A system may contain several units of 16,384 words operating as one logical unit. Only one storage reference is in process at the same time. These units also have a two-microsecond read-write cycle time.

# 1.2.1.2 Shared Core Storage

The computing system permits the use of additional core-storage units which have two storage bus connections, but which are otherwise identical to the core-storage units mentioned above. They permit communication between two central-processing units. These processors may operate simultaneously, each with their own input-output units, and if desired, each with additional core storage connected to its own storage bus. The shared core-storage unit provides a link between the two storage bus systems. Messages can be exchanged between processors by placing them in the shared core-storage unit. In particular, the systems can be organized in such a fashion that, in the case of routine maintenance or malfunction of one processor, the other processor can keep the system in satisfactory operating condition. The use of several shared storage units permit more than two processors to be part of a system.

Shared core storage units contain 4096 or 16,384 words.

# 1.2.1.3 Core Storage With Fast Channels

Two types of input-output channels are provided, the types differing only in individual and in total rate of transmission through the channels. When high-performance channels are provided in the central-processing unit, one core-storage unit with fast channels must be employed in the system. This type of core-storage unit is identical with the unit mentioned under Storage Units, except that equipment is provided to permit assembling or disassembling of input-output data at a high data rate. The presence of the fast channels also serves to reduce the number of storage cycles required by a channel while transmitting data.

Core-storage units with fast channels contain 4096 or 16,384 words exclusive of the fast-channel equipment. A maximum of eight channels can be provided.

#### 1.2.2 Input-Output

Input to the system passes from the input devices to storage through the channels of the central processor. These channels assemble complete 64-bit words from the flow of input information and store the assembled words in core storage locations. The central processor specifies the starting location and the number of input words to be read. While the central processor proceeds with computation, the channel completes the input operation and signals the central processor when transmission is finished.

The same channels operate similarly for output, fetching core-storage words and disassembling them for the output devices independent of computations in the central processor. External storage devices, such as tapes and disks, may be operated via a channel as if they were input and output units.

The basic central-processing unit has five channels which can operate independently. Four of these basic channels -- the simplex channels--can be replaced by up to eight fast channels when a core-storage unit with fast channels is provided in the system. The simplex channels can accommodate the data rate of an IBM 729IV tape unit. A maximum of four units with this data rate can run simultaneously. The fast channels can run units with a data rate up to 300 kc. The fifth basic channel -- the multiplex channel -- can function either as a single channel or as a connection to a multiplexing device. When a multiplexing device is connected, the channel is logically and operationally equivalent to as many as 112 channels. These channels share a major portion of the channel equipment, and they accommodate the aggregate data rates required by communication equipment.

A wide variety of input-output units can be attached to the channels-card readers, printers, magnetic tape units, disk units, communication equipment, displays, and operators' consoles. Some control units permit only one input-output device to be attached to a channel. Others, such as the magnetic tape-control unit or the disk-control unit, are designed to allow several units to be attached to a single channel. When this is done, only one of these units can be operated at a time. Control units designed for attachment to the multiplex channel accommodate many units simultaneously.

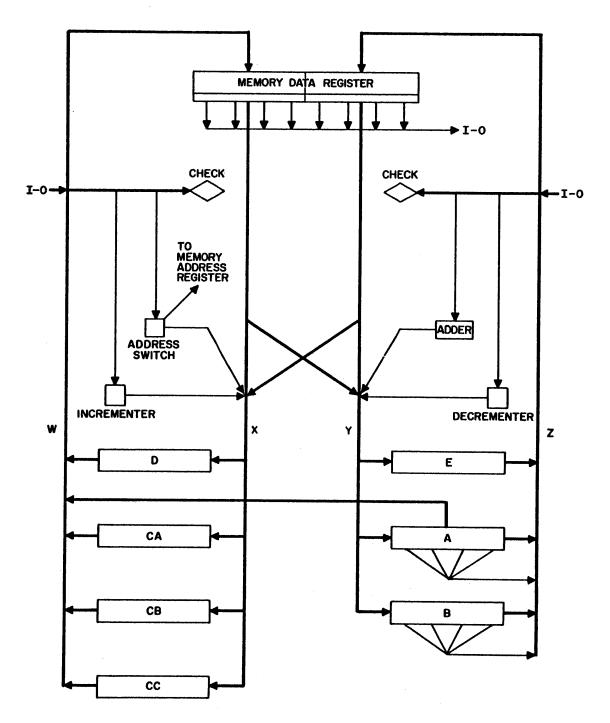

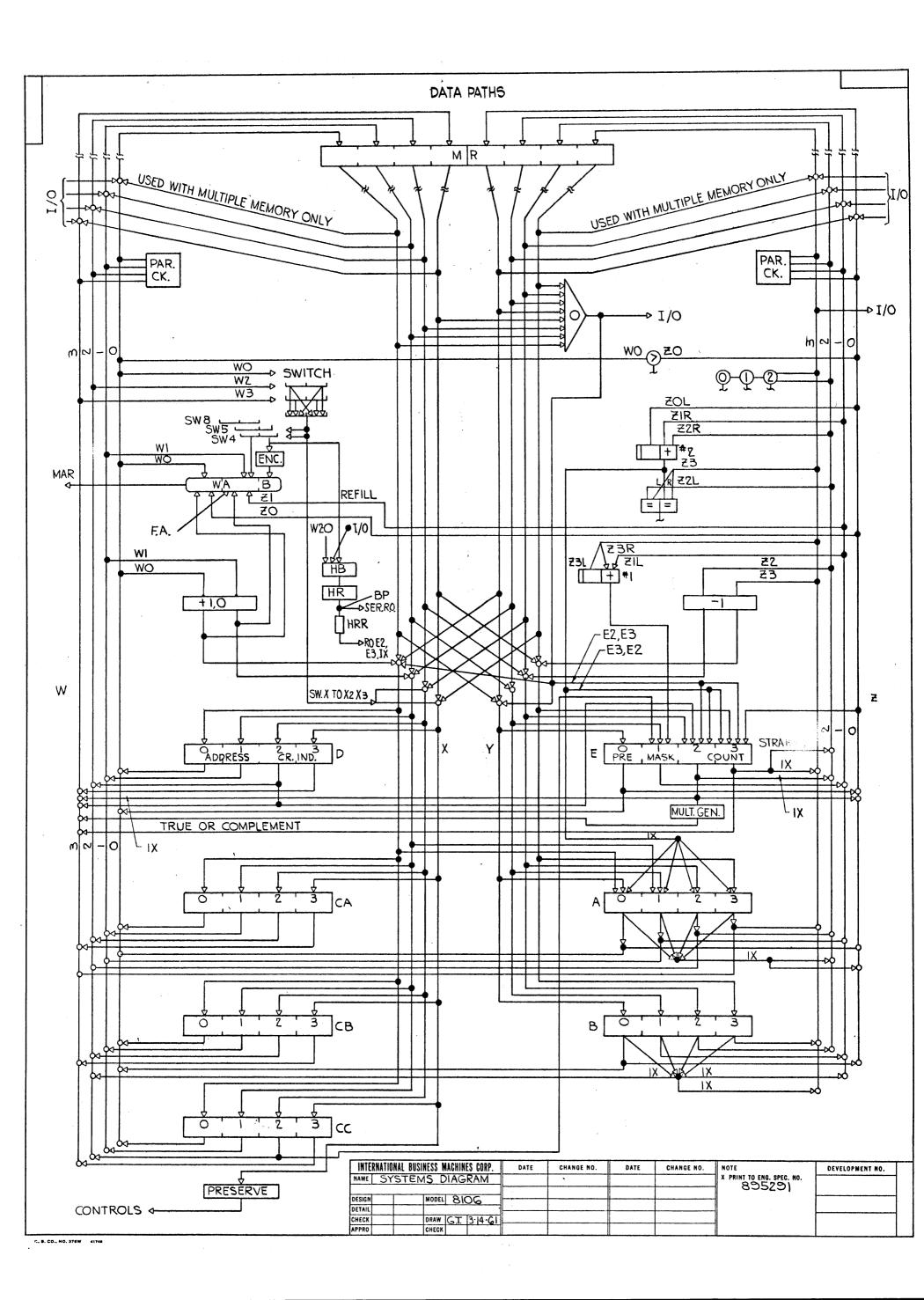

## 1.2.3 Central Processor

The central processor performs the basic tasks of instruction sequencing, operand addressing, and arithmetic or logical processing. A diagram of the central processor is shown in Figure 1.2. Operations are specified one at a time by instructions taken from storage. The operands specified by the instruction are also obtained from storage. The arithmetic or logical process specified by the instruction is performed subsequently and the result returned to storage. The internal registers and data paths of the central processor permit parallel access to storage. Hence, the fetching of instructions and data, and the storing of results are performed in parallel. The high speed of storage permits rapid parallel operation. The actual processing operation, which requires great flexibility in the selection of successive digits or characters to be processed and in the various modes of processing, is performed serially: a digit or a character at a time. The combination of parallel data transmission and serial data processing allows for speed and flexibility in over-all operation.

Figure 1.2 - Data paths

### 1.3 SYSTEM OPERATION

# 1.3.1 Instruction Sequencing

Instructions have a length of one, two, or three 32-bit half-words with each instruction half-word containing an address. Therefore, one-, two-, or three-address instructions are available. Instructions of any length can be intermixed without regard to word boundaries.

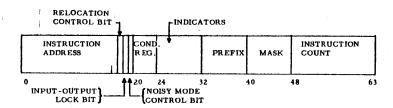

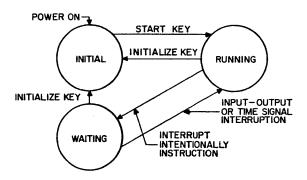

Instructions are taken in succession as specified by an instruction address. Alteration of the succession of instructions is possible by branching operations which can be controlled by several conditions. Automatic interruption of the normal sequence of instructions will occur under control of certain system alerts. Part of these alerts are caused by the program in execution and are identified by indicator bits. The programmer can selectively permit or prevent interruption caused by the program alerts by means of a set of mask bits. The condition bits, the indicator bits, and the mask bits identify the condition under which the program is currently executed. These bits form part of a program control word which contains the essential information which defines the state of the processor as it executes a given program. The instruction address, mentioned above, is also part of the program control word. The program control word further contains mode bits, a prefix address, and an instruction count.

The prefix address is a reference address for the program being executed. Some information belonging to this program, such as the floating-point accumulator, is stored relative to the prefix address. The prefix address also serves as a boundary address in the address-protecting procedure.

The instruction count is a tool for program diagnosis. The count is reduced by one for each instruction executed until zero is reached. When zero is reached, a program interruption is initiated.

The program control word permits rapid program switching. All information vital to the current program can be preserved by storing the program control word. When the program is to be resumed, the program control word need only be loaded into internal working registers to restore the processing unit to the state belonging to this program. Since the prefix address is part of the program control word, a change in prefix address can be part of a switch in program control words. This avoids dumping and loading of vital registers as part of the change from one program to another.

A program interruption is executed as a switch between the current program and the auxiliary program which belongs to the interruption. As an interruption occurs, the processor is placed in the disabled state and further interruptions are delayed. Any subsequent interruptions are stacked in storage and will occur in turn when the processor is placed again in the enabled state.

Interruptions may be caused by input-output units, by various program monitoring functions and by exceptional arithmetic results. The input-output interruptions indicate normal or special termination of a channel operation. The monitoring functions include an interval timer, the instruction count, and checks on valid data, addresses and operation codes. The exceptional arithmetic results include various types of overflows and are individually maskable by the programmer.

## 1.3.2 Operand Addressing

Operands are specified by the address parts of the instruction being executed. In floating-point and a few related operations, an accumulator is used and only one additional operand is specified. All other operations specify all operand and result locations, and do not use an accumulator. Fixed-point arithmetic and logical-processing operations, therefore, are two- or three-address operations.

The address specified by the instruction may further be modified by indirect addressing, and in the case of floating-point operands, by indexing.

Several operand formats can be used. The floating-point format occupies a full word. The operands of arithmetic or logical processes occupy fields up to 64 bits in length. Fields of different length may be assigned to adjacent locations in core storage, even if this means that a field lies partly in one word and partly in the next. Each field may be addressed directly by specifying its start and end in the instruction. The computer selects the words required and alters only the desired information. Since the field length is explicitly stated in each instruction rather than being implied by the data, there is no restriction on the coding of variable field-length data. In logical operations, long fields which do not have the restriction of a maximum length of 64 bits may be specified. Thus, editing operations may be performed upon records rather than individual fields. In arithmetic instructions, multiple fields may be specified and the arithmetic process is repeated for each field specified by the given instruction.

Individual characters in a field may occupy four or eight bits. Thus, a decimal digit may be compactly represented by a binary code of four bits, or it may be expanded to eight bits when intermixed with alphabetic information.

Operand addressing is subject to an address-monitoring system. All addresses below the prefix address of the current program are protected from store operations. This permits protection of a supervisory program against programming mistakes in a subject program. Because it is often very difficult to predict all the addresses which might be generated by indexing, indirect addressing or other address modification, the built-in address-monitoring facilities give far better protection than is possible by screening the program before execution. This is particularly true when the program is not yet error-free.

Systems required to process a wide variety of data in many different ways and on short notice may be arranged to store programs and files on external media. Because of overlapped processing and input-output operation, it is impossible to assign in advance the storage areas required for programs and data. In order to avoid time-consuming and logically complex address alterations, the relocation mode can be used. This mode has the additional advantage of isolating, and therefore protecting from each other, the instruction and data areas belonging to the different programs which may appear simultaneously in storage.

When programs are run in the relocated mode, all data and instruction addresses are translated prior to addressing storage. A translation table associated with the program allows individual relocation of several data areas and instruction areas. Relocation takes place in blocks of 256 words. The translation process permits continuous addressing of noncontiguous data areas. Relocation may be performed with all types of operands and every mode of address modification.

## 1.3.3 Arithmetic and Logical Processing

The instruction set includes elementary operations, such as ADD (A), MULTIPLY (M), and DIVIDE (D), which are altered by modifier bits. Thus, the operations "subtract" or "add absolute" are obtained by use of sign modifiers with an ADD (A) instruction, and are not provided as separate operations. The same modifiers permit controlling the sign of a number to be multiplied or divided.

#### 1.3.3.1 Floating-Point Arithmetic

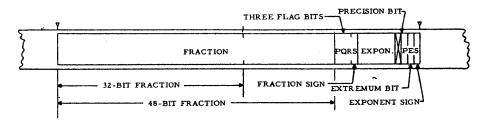

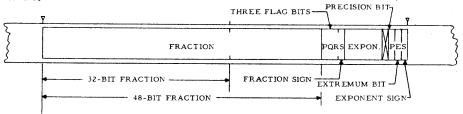

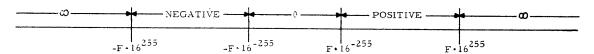

Floating-point arithmetic makes use of a specialized data format wherein numbers are represented as a signed exponent and a signed fraction which, together, occupy a full 64-bit word.

Floating-point instructions contain sign modifiers which permit any desired combination of operand signs. They also contain a normalization modifier which specifies the choice between normalized and unnormalized operation. Normalization shifts take place four bits at a time. Consequently, the operating radix for floating point is said to be hexadecimal, rather than binary. The exponent of the floating-point word is a hexadecimal number and denotes the power of 16 by which the fraction should be multiplied.

The fraction length may be either 32 or 48 bits as specified by the precision bit of the floating-point word. The 32-bit fraction length gives the fastest operating speed. The 48-bit fraction length makes it possible to compute in single-precision mode for a number of problems which would have to be done in double-precision otherwise. The two fraction lengths may be intermixed within one computation.

In order to simplify significance studies, a mode of operation called "noisy mode" is provided in which results are altered in a specified fashion. Consecutive runs of the same problem in standard and noisy mode permit an estimate of the significance of the results to be obtained.

Floating-point numbers cover a range between the positive and negative value of the fraction having the maximum exponent. Since the exponent range is finite, a discontinuity exists between positive and negative values of fractions having minimum exponent. Included in this range is the number zero. An extremum flag bit has been incorporated in the floating-point word format to provide a straightforward control of data exceeding the exponent range or falling within the range of discontinuity.

#### 1.3.3.2 Fixed-Point Arithmetic

The class of fixed-point arithmetic operations is designed to facilitate arithmetic on other than the specialized floating-point numbers. The emphasis here is on versatility and economy of storage. Data may be signed or unsigned. For unsigned data, the sign is simply omitted in storage, thus saving space and avoiding the task of assigning signs where there are none. Unsigned numbers are treated as if they were positive.

All integer operations are available in either decimal or hexadecimal form by setting the radix modifier bit. Again, the term "hexadecimal" is used in preference to "binary" to indicate that addressing and processing proceed four bits at a time.

A radix-conversion operation is provided to facilitate the use of decimal input and output while retaining the advantages of hexadecimal operation within the machine. In this operation, the operand is an integer and may be converted either from hexadecimal to decimal or from decimal to hexadecimal.

## 1.3.3.3 Logical Processing

The logical-processing operations are divided into three groups: connective, translation, and alphameric-comparison operations.

Connective operations provide a simple and orderly fashion for performing operations which logically combine bits by "and," "or," and "exclusive or," as well as many other nonarithmetic data-handling operations. Each connective operation specifies two or three storage fields as in integer arithmetic. Two operand fields are logically combined bit for bit and placed in the result field. The result is tested for the all-zero condition. The instruction CONNECT FOR TEST (CT) allows fields to be tested without altering the contents of storage.

There are sixteen possible ways to combine or connect two bits, each of these can be specified with the connective operations. Besides the connectives "and," "or," and "exclusive or," there are connectives to invert, to replace, and to set bits to zero or one. While the term "logical connectives" suggests evaluation of elaborate expressions in Boolean algebra, the connective instructions have important every-day applications, such as assembling and testing input-output data. Their power lies in the ability to specify fields of any length and in any position in storage.

Several modifications, which may be combined in any desired way, are provided with the connective operations. One modification, the choice between storing the result or only testing the result, has been mentioned already. Another modification is the ability to connect a field with a single four- or eight-bit character. This single character is connected over and over with the successive characters of the field. A third modification is the match or clash option. In this option, the result characters are compared with a four- or eight-bit comparison character. An equality is called a match; an inequality, a clash. The operation is terminated either on the first match or on the first clash. This operation has the characteristics of a search operation.

Translation operations also proceed a character at a time. Either a four- or eight-bit character is selected from the operand field as the argument for the table from which the result character is obtained. The result character is four or eight bits independent of the size of the argument character. Successive argument characters are used to obtain a stream of result characters, which are placed in the result field.

The translation operations have direct application in code conversion operations. A second application is character-size alteration by translation from four- to eight-bit size, or vice versa. A third less obvious application is character reordering. Here, an operand stream of control characters is used to select, from a translation table containing the subject data, the result characters in a prescribed order. This reordering function has application in such editing functions as punctuation insertion.

A fourth application of the translation operations is logical manipulation. Two additional translation instructions, TRANSLATE WITH LEFT CARRY (TLL) and TRANSLATE WITH RIGHT CARRY (TLR) are provided to increase the logical power for this class of operations. In these operations, part of the result character is used as argument for the next character translation. The two operations differ in the direction of processing. These translation operations are also used in editing operations, and provide means for zero suppression and similar functions.

Alphameric-comparison operation differs from the numeric comparison operation (provided as part of the arithmetic operations) in the direction of processing, and in that the field length is unrestricted. Alphameric high-low comparisons are made from right to left by simple binary subtraction of successive characters. There is no fixed character code built into the computer. The only requirement is that the binary numbers representing each character fall into the comparing sequence desired for the application. If the code used for input or output does not conform to this comparing requirement, the translate instructions may be used to perform the desired conversion.

#### 1.3.4 Control-Word and Decision Operations

Every instruction may have its address portions modified by indirect addressing, or substitutionary indexing. In the case of floating-point operations, additive indexing is provided as well. The information referred to in indirect addressing and in indexing is the value field of a control word. Normally, the instruction and the control word remain unchanged. To alter the control words is the function of control-word operations.

Each control word contains a count to keep track of the number of times a program loop has been traversed, or in the case of long fields, the number of times a word boundary has been passed. A third field in each control word specifies a refill address from which another control word may be loaded automatically.

$\gamma$

Together, these three fields provide a very convenient indexing technique. At each traversal of a program loop, an increment is added to the control-word value and the count is stepped down by one. When the count reaches zero, the control word is reset by refilling it from the storage location containing the original value and count. All this may be done with one instruction at the appropriate point in the loop.

The instruction set permits many other control-word techniques. An important one is the use of the refill address to indicate the next control word in succession in a chain of control words. Such chains permit the computation to progress through a series of items which are not stored in the order in which they are to be used. Chaining can greatly simplify insertion, deletion, and sorting of items by not requiring rearrangement of data in storage.

In logical-processing operations, control words are used to specify operands which have a length greater than 64 bits. The refill address is used to chain together successive data fields. Thus, the control words permit entire records or groups of records to participate in a single operation.

The instruction set includes operations for incrementing the value field, decrementing the count field, and chaining. Several of these functions may be combined in one operation. The counting function may also be combined with fixed-point arithmetic in a set of very flexible control-word modification operations.

While control-word instructions are provided to change control words explicitly, it is also possible to take advantage of an implicit control-word modification mode. This mode is provided by the fact that control words which are used in processing operations are always stored back into a fixed storage location at the end of the operation. These so-called "final control words" are carefully updated to reflect correctly the point reached in processing the operand. The final control words can be used in subsequent operations involving the same record. This mode of operation may be applied to advantage in stepping along a string of data of various lengths without requiring a separate incrementing instruction at each step.

The branching operations alter the instruction counter so as to change the course of a program. The number of operations is not large, but modifiers are available to provide a great deal of flexibility. The branch instruction refers to the four-bit condition register which reflects the result of the instruction last executed. By means of four select bits, the branch decision may be based on the state of some or all of the condition bits. The various options include an unconditional branch and a NO OPERATION (NOP) instruction. Branch instructions may be coupled with an operation to store the program control word at any desired location before branching. This simplifies re-entry to a program from a subprogram.

The condition register may be loaded prior to a branch operation from any four-bit location in storage.

## 1.3.5 Data Transmission

The transmission operation provides the facilities to move a block of data from one set of addresses to another. The operation may be terminated by a control-word count, or by a match or clash. The match or clash condition is obtained by comparing one character in each word transmitted with a comparison character. Additional operations are provided to interchange the contents of storage locations and to move half-words.

There are two basic instructions for controlling input-output and external storage units: START CHANNEL (SRT) and RELEASE CHANNEL (RLS). Each instruction specifies the unit desired and the storage area involved in the data transmission.

The storage area is specified by a control word which contains the first address in storage and a count of the number of words to be transferred. The control word also specifies the operation to be performed by the channel. The control word contains a refill address which can specify the address of another control word. Control words can thus be chained together to define storage areas and channel operations to be executed with these storage areas. This makes it possible to proceed with a series of operations on a given channel without further attention by the main program.

Input-output control words have the same format as control words used in indexing and indirect addressing. This important feature greatly simplifies the processing and sorting of large files.

All instructions for operating external units are executed independently of the computer program. A number of data transfers can thus take place simultaneously, all sharing access to storage. Signalling functions inform the program when an external process is completed.

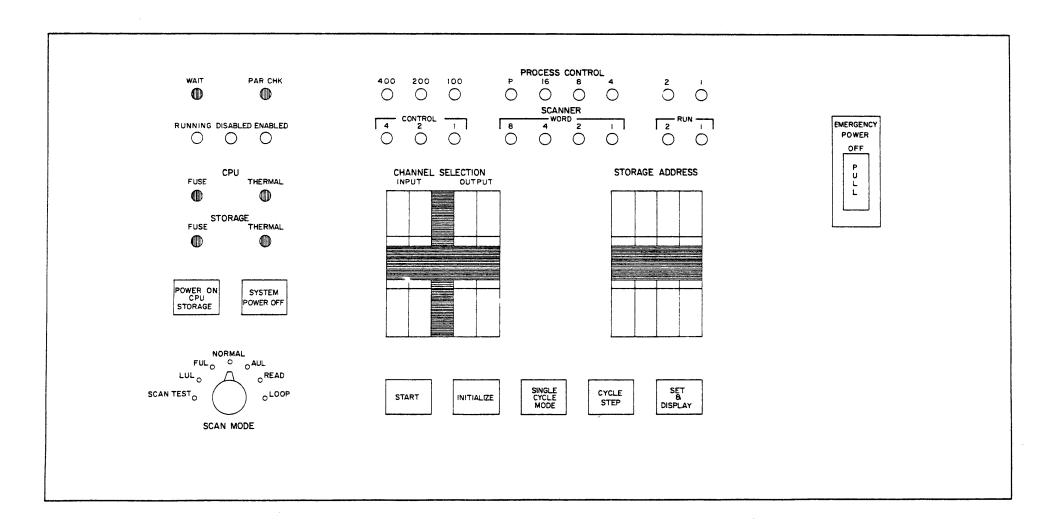

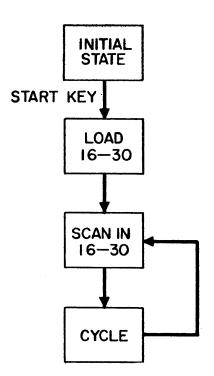

### 1.3.6 Maintenance

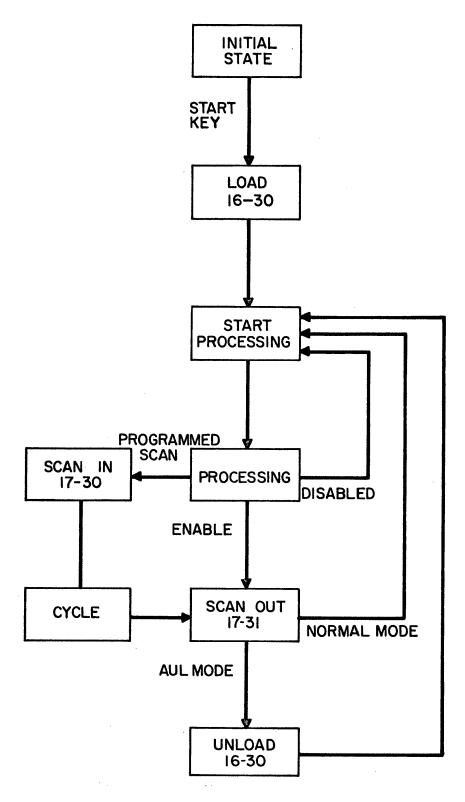

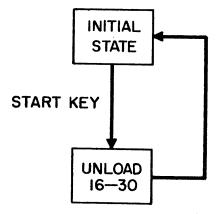

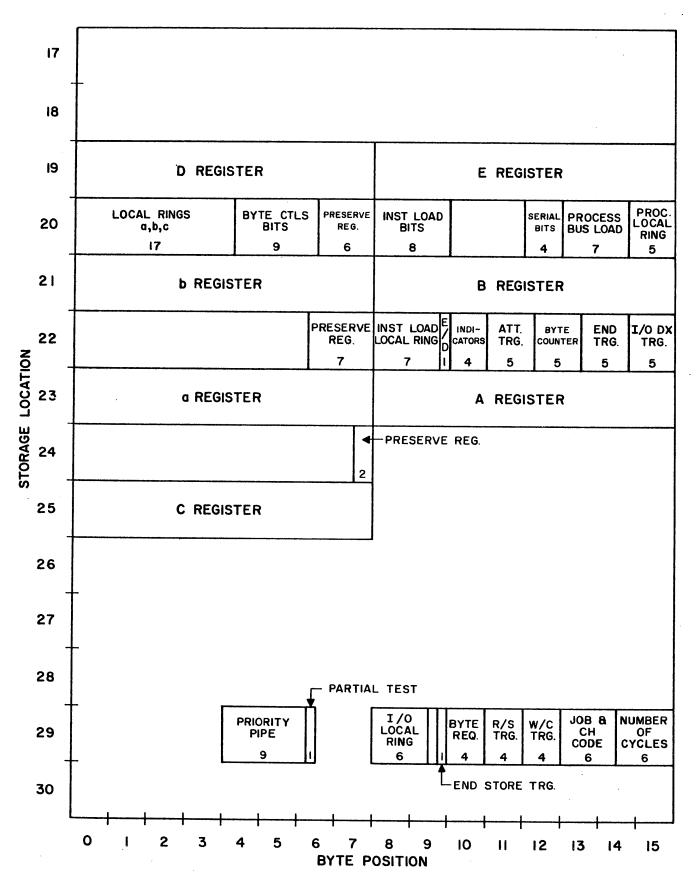

Throughout the processor, a high degree of checking is used for data and controls. The internal organization of the processor makes it possible to halt machine operation when an error is detected. The state of the internal registers therefore is preserved, and may be used to determine the type of error and the location of the fault which caused the error. To facilitate diagnosis, the contents of the machine registers are automatically scanned and placed in storage when an error is detected. If desired, the scanned information may be dumped on an output medium, thus producing an external record of all error counts which occur. This procedure aids in diagnosing intermittent errors.

When a permanent fault is known to exist in the processor, a scan-in, as well as a scan-out, may be employed -- internal registers of the processor are set according to data which resides in storage. Following this scan-in, a predetermined number of machine cycles is taken, followed by a scan-out. The scan-in information may be obtained from an input device; the scan-out information may be dumped on an output device, and a large number of scans may be taken in succession. Thus, an exhaustive equipment test may be performed in a short time.

Machine-scans may also be initiated by program control as an aid to diagnostic programs.

# Chapter 2

# OPERAND DESIGNATION

# Contents

|                                             | Section    | Page |

|---------------------------------------------|------------|------|

| General Description                         | 2.1        | 2.1  |

| Format                                      | 2.2        | 2.3  |

| Data                                        | 2.2.1      | 2.5  |

| Program                                     | 2.2.2      | 2.6  |

| Instruction                                 |            | 2.8  |

| Control Word                                |            | 2.8  |

| Indirect Addressing                         | 2.3        | 2.11 |

| Indexing                                    | 2.4        | 2.13 |

| Operand Addressing                          | 2.5        | 2.14 |

| Byte                                        | 2.5.1      | 2.14 |

| Word                                        | 2.5.2      | 2.15 |

| Half-Word                                   | 2.5.3      | 2.15 |

| Field                                       | 2.5.4      | 2.15 |

| Record                                      | 2.5.5      | 2.15 |

| Multiple Field                              | 2.5.6      | 2.16 |

| Multiple Word                               | 2.5.7      | 2.17 |

| Address Translation                         | 2.6        | 2.19 |

| Relocation Table                            | 2.6.1      | 2.19 |

| Block Boundaries                            | 2.6.2      | 2.20 |

| Addresses Translated                        | 2.6.3      | 2.20 |

| Address Monitoring                          | 2.7        | 2.22 |

| Definition of Monitoring Area               | 2.7.1      | 2.22 |

| Action of Address Monitoring                | 2.7.2      | 2.22 |

| Addresses Monitored                         | 2.7.3      | 2.23 |

| Control-Word Operations                     | 2.8        | 2.25 |

| Conditions                                  | 2.8.1      | 2.26 |

| Indicators                                  | 2.8.2      | 2.26 |

| Operations                                  | 2.8.3      | 2.26 |

| Increment Address (IA)                      |            | 2.26 |

| Diminish Count (DC)                         |            | 2.26 |

| Increment Address and Diminish Count (IDC)  |            | 2.26 |

| Increment Address and Refill (IR);          |            |      |

| Diminish Count and Refill (DCR);            |            |      |

| Increment Address, Diminish Count, and Ref. | ill (IDCR) | 2.27 |

| Refill (R)                                  |            | 2.27 |

| Refill from Address (RA)                    |            | 2.27 |

# Contents Chapter 2 (continued)

|                                       | Section   | Page |

|---------------------------------------|-----------|------|

| Accumulator Operations                | 2.9       | 2.28 |

| Conditions                            | 2.9.1     | 2.28 |

| Indicators                            | 2.9.2     | 2.28 |

| Operations                            | 2.9.3     | 2.28 |

| Load Accumulator (LA)                 |           | 2.28 |

| Store Accumulator (SA)                |           | 2.29 |

| Store Effective Address, First (SEAF) |           | 2.29 |

| Store Effective Address, Last (SEAL)  |           | 2.29 |

| Data Transmission                     | 2.10      | 2.30 |

| Multiple-Word Transmission            | 2.10.1    | 2.31 |

| Match or Clash                        | 2.10.2    | 2.31 |

| Conditions                            | 2.10.3    | 2.32 |

| Match or Clash                        |           | 2.32 |

| First Count Zero                      |           | 2.32 |

| Last Count Zero                       |           | 2.32 |

| Indicators                            | 2.10.4    | 2.32 |

| Operations                            | 2.10.5    | 2.32 |

| Swap Half-Word (SWH)                  |           | 2.32 |

| Swap (SW)                             |           | 2.32 |

| Transmit Half-Word (TMH)              |           | 2.33 |

| Transmit (TM)                         |           | 2.33 |

| Transmit Till Match (TMM); and        |           |      |

| Transmit Till Clash (TMK)             |           | 2.33 |

| Storage Assignment                    | 2.11      | 2.34 |

| Relocation Table                      | 2.11.1    | 2.34 |

| Final Data Description                | 2.11.2    | 2.35 |

| Accumulator                           | 2.11.3    | 2.35 |

| Timer                                 | 2.11.4    | 2.35 |

| Time Clock                            |           | 2.36 |

| Interval Timer                        |           | 2.36 |

| Interruption Control Words            | 2.11.5    | 2.37 |

| Store Interruption Control Word       |           | 2.37 |

| Fetch Interruption Control Word       | _         | 2.37 |

| Backup Locations                      | 2.11.6    | 2.37 |

| Scan Area                             | 2.11.7    | 2.37 |

| Program Control Word                  | 2.11.8    | 2.38 |

| Arithmetic Tables                     | 2.11.9    | 2.38 |

| Input-Output Area                     | 2.11.10   | 2.39 |

| Data-Buffer Locations                 |           | 2.39 |

| Control-Word Locations                | _         | 2.39 |

| Index Words                           | 2.11.11   | 2.39 |

| Main Core Storage                     | 2. 11. 12 | 2.40 |

# Contents Chapter 2 (continued)

|                                                   | Page |

|---------------------------------------------------|------|

| Table - Storage assignments                       | 2.41 |

| Figure 2.1 - Example of data formats              | 2.4  |

| Figure 2.2 - Possible numeric fields              | 2.4  |

| Figure 2.3 - Floating-point format                | 2.4  |

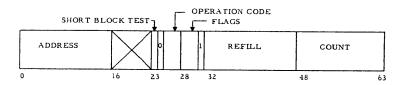

| Figure 2.4 - Instruction and control-word formats | 2.7  |

| Programming note - Indirect addressing            | 2.12 |

| Programming note - Refilling                      | 2.17 |

| Programming note - Crossing word boundaries       | 2.20 |

| Programming note - Relocating                     | 2.24 |

| Programming note - Fixed-point operations         | 2.27 |

| Programming note - The match byte                 | 2.31 |

| Programming note - The time clock                 | 2.36 |

### Chapter 2

#### OPERAND DESIGNATION

### 2.1 GENERAL DESCRIPTION

The central processor is capable of addressing 65,536 (2<sup>16</sup>) words of storage, each containing 64 bits of information. Most of these locations contain general-purpose information, but some locations have been assigned for a special purpose. The information obtained from core storage may be used as data or as program.

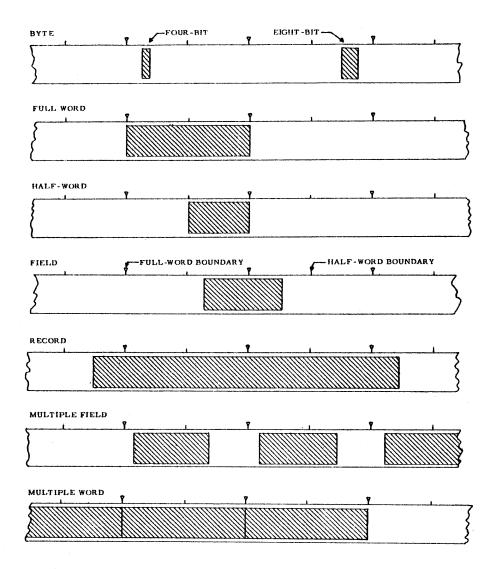

Data may be alphameric or numeric. Depending upon the type of processing to be performed, the data format may be a full word or a half-word, a field or a record. A field has variable length, and may start within one word and continue through that word into the next higher addressed storage location. The length of a field is limited to 64 bits. A record also has variable length, but it is not limited to 64 bits. Thus, records and fields can cross word boundaries, and may be placed side by side in storage.

Processing of data proceeds four or eight bits at a time. Alphameric data consist of characters which are processed in a uniform manner. Numeric data consist of digits and, where needed, a sign. Floating-point data consist of a signed fraction and a signed exponent. Floating-point arithmetic operations make use of an accumulator. All other operations place their results in general-purpose storage.

Data may be moved internally by a set of data-transmission operations. To transmit data to and from the accumulator, LOAD ACCUMULATOR and STORE ACCUMULATOR operations are provided.

The program specifies computer operation by means of instructions and control words. Instructions are executed sequentially -- control words are consulted and updated in any desired sequence.

The program specifies processor operation by means of instruca variable-length instruction format is used. Instruction addresses may be modified by indexing or indirect addressing.

The index quantity or operand specification required for this address modification is placed in control words. Control words are also used to specify the addresses of the data which take part in input-output operations. A third use of control words is the specification of the details of instruction sequencing and interruption.

The contents of control words follow a standard pattern. A set of control-word modification operations is provided to change the various parts of control words.

Internal registers, in general, are not addressable and do not preserve information from one operation to the next. The only information kept in internal registers as the processor proceeds from one operation to the next is the content of the program control-word register. The program control word is fetched at the start of a program and stored at the end of a program. Among the information contained in the program control word is the prefix address. This address is used as a reference address, and specifies the location of the index registers and accumulator of a particular program. The program control word and its prefix address avoid the need for dumping and loading of registers in switching from one program to another.

Some applications require program and data to be placed at different storage locations as processing proceeds. To simplify storage allocation and address modification for these applications, a relocation mode may be used. In this mode, the addresses used in a program are considered symbolic. A translation procedure is used to change them to actual addresses each time they are used to address storage.

The programs executed by the processor often are known to contain mistakes. When these programs are executed, it is important to protect certain storage areas from erroneous store operations to preserve proper processor control. Address monitoring provides this storage protection. The extent of the monitored area is determined by the prefix address.

#### 2.2 FORMAT

The system stores information in core storage in 64-bit words. Information transmission between storage and processor is in parallel, a 64-bit full word or 32-bit half-word at a time. Information words of 64 bits are part of 72-bit machine words. The extra eight bits are single error detection check bits and are not available to the programmer. Within the central processing unit, each check bit is used as the odd-parity bit of eight consecutive information bits.

Words in storage are specified by a contiguous set of addresses numbered from 0 to 65,535 (2<sup>16</sup>-1). Words are subdivided into sixteen groups, or "bytes," of four bits each. In each word, the bytes are numbered from 0 to 15, left to right. Byte 15 of a word may be considered adjacent to byte 0 of the next higher addressed word. The four bits of a byte are numbered from 0 to 3, left to right. Numbering of bytes and bits within a byte may be combined by numbering the 64 bits of a word from 0 to 63. The parity bits are not numbered.

The set of addresses includes the addresses of core storage used for special purpose. A list of these addresses is described in the storage assignment section. There are no processor registers which need addressing, since all necessary information is placed in storage in the course of the machine operation.

In some operations, information is processed a word at a time; in others, a half-word at a time. A half-word contains eight bytes of four bits each and corresponds either to the first half (bits 0-31) or the second half (bits 32-63) of a full word. In a third group of operations, information is processed a byte at a time. The byte size may be four or eight bits. Eight-bit bytes always consist of two consecutive even and odd numbered bytes. A group of bytes which is processed serially is called a field. A field may start with any byte in a word in storage, and continue through that word and into the word in the next higher addressed storage location.

Information, whether a full word, half-word, or field, is always addressed by the leftmost byte. The rightmost byte is either implied by the operation to be performed or specifically stated as part of the instruction.

In all serial processing operations, operand data are fetched from storage a half-word at a time or an eight-bit byte at a time. Results are always stored a half-word at a time. When operand and result data fields which overlap partially are chosen, caution should be taken that results do not replace operands before the latter are fetched for processing. When operand and result fields are identical, no complications arise except where noted.

Figure 2.1 - Data formats

Figure 2.2 - Numeric fields

Figure 2.3 - Floating-point data format

## 2.2.1 Data

Seven data formats are used in the processor. These formats are closely related and may be considered variations upon the basic field format. Examples of these formats are shown in Figure 2.1. The byte, word, and half-word format correspond to the basic subdivisions of storage in bytes, words, and half-words. The field format has a length of one to sixteen 4-bit bytes, or one to eight 8-bit bytes. The field format is not restricted by word or half-word boundaries, and may start and end with any byte within a word. In a record, the number of bytes is not limited. A record therefore may continue through many words in storage. A multiple field consists of a set of fields equal in length and with their left-hand boundaries sixteen bytes apart. The fields, therefore, occupy the same groups of bytes in successive full words. Multiple fields may cross word boundaries. The multiple-word format consists of one or more adjacent full words.

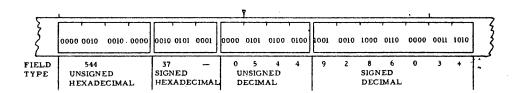

Fixed-point arithmetic operations process data four or eight bits at a time in hexadecimal or in decimal radix. In decimal arithmetic, the digits 0 through 9 are represented by the four-bit binary integers 0000 through 1001. Hexadecimal arithmetic makes use of the same four-bit size with the values 0 through 15 being represented by the binary integers 0000 through 1111. The processor uses the hexadecimal rather than binary radix, because processing proceeds four bits at a time. Therefore, the processing resolution is four bits and not one bit. Otherwise, hexadecimal processing is in all respects equal to binary processing.

Numbers may be signed or unsigned. When present, the sign of a number is specified by a single bit. A zero indicates a positive sign; a one, a negative sign.

With the sign, up to three flag bits may be used. Flag bits permit special identification of numbers and are placed to the left of the sign bit to form with this bit the four-bit sign byte.

For unsigned numbers, the sign byte is omitted and the sign is assumed to be plus. During arithmetic operations, all numbers are handled as if they were signed. When unsigned operands are obtained from storage, the implied sign is modified as specified by the instruction. Thus, an operand can be brought in without sign and the result stored with sign or vice versa.

In fixed-point arithmetic, the data fields specified have variable field length. For unsigned data, the entire field is treated as a positive integer. With signed data, the rightmost byte is interpreted as a sign byte. Figure 2.2 shows possible numeric fields.

The format for floating-point arithmetic is shown in Figure 2.3 The two portions of the floating-point word are: left, the fraction; and right, the exponent. Both fraction and exponent are signed, and have the hexadecimal radix. The fraction has 32 or 48 numeric bits. Flag bits of the fraction sign byte serve for the entire floating-point word. The exponent has two numeric bytes. The flag bits of the exponent sign byte are used for the extremum bit, which indicates a true zero or infinite quantity, and for the precision bit, which specifies fraction length. The third flag bit is ignored.

Logical-processing operations usually process information four bits at a time, but occasionally processing proceeds eight bits at a time. Input-output operations always proceed eight bits at a time. Alphameric characters normally occupy an eight-bit byte. No preferred code sets other than those implied by a binary collating sequence are assumed by these processing operations.

### 2.2.2 Program

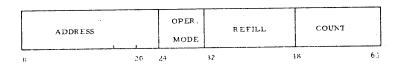

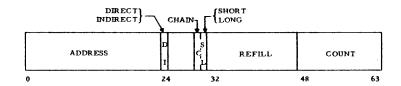

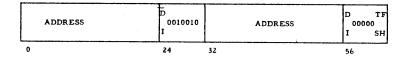

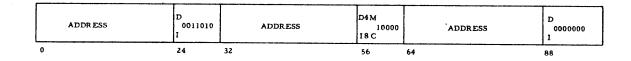

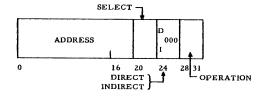

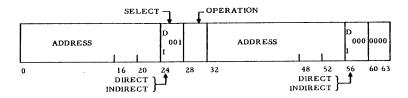

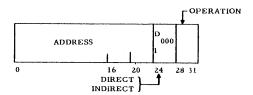

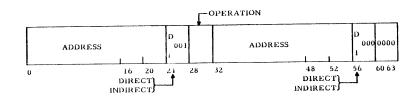

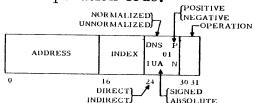

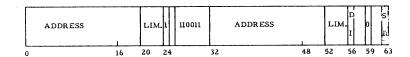

The processor program consists of instructions and control words used in the control section of the processor to specify the operation to be performed. They are stored in core storage and when desired may be operated upon as data. Instructions occupy one, two, or three half-words. They are referred to as "one-address," "two-address," and "three-address instructions." Each of these instruction types may start at bit address 0 or 32. Control words occupy a half-word or a full word and are distinguished as short or long control words. A long word always has bit address 0, while a short word may have bit address 0 or 32. The formats used for instructions and control words are shown in Figure 2.4. In this figure, the bit address of all instructions and control words is assumed to be 0. In some cases, this bit address may be 32, in which case the addresses of the individual fields in the instruction differ from those shown. For convenience of presentation, all references of bits and fields will use the numbering of Figure 2.4.

Instructions and control words follow a basic pattern upon which some variations are made. This pattern consists of four parts: the address, the operation or mode, the refill, and the count.

# ONE-ADDRESS INSTRUCTION ADDRESS (F) 16 20 TWO-ADDRESS INSTRUCTION OPER. ADDRESS (F) ADDRESS (L) OPER. 16 20 24 32 56 THREE-ADDRESS INSTRUCTION ADDRESS (F) OPER, ADDRESS (M) ADDRESS (L) OPER. 32 16 20 24 SHORT DATA DESCRIPTION ADDRESS MODE LONG DATA DESCRIPTION

Figure 2.4 - Instruction and control word formats

COUNT

REFILL

MODE

ADDRESS

The entire pattern occupies a full word and is the format of a long control word. The first two parts of the pattern occupy a half-word and can appear alone as an instruction half-word or as a short control word. Records, multiple fields, and multiple words can only be described by the long format. All other data can be described by the short format.

#### 2.2.2.1 Instruction

The total length of an instruction in half-words is directly related to the number of addresses necessary to perform the operation. The half-words are distinguished as the first (F), middle (M), and last (L) half-word. Each half-word subsection consists of two parts: the address and the operation.

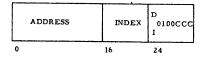

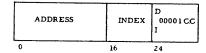

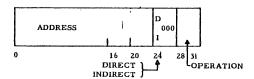

The address part consists of 24 bits and is leftmost in the instruction half-word. The first twenty bits specify the byte address, while the last four bits specify the limit of a field or in branch instructions the branching conditions. The operation part is rightmost in the instruction half-word and contains eight bits which are used as class, as code, and as modifier bits. Class bits specify type of addressing, instruction length, and operation class. Code bits specify basic operations within a class, whereas modifier bits specify modifications to these operations.

The last half-word of each instruction has bit 27 as a zero. All other instruction half-words have this bit as a one. This code bit may be used to separate an instruction stream into individual instructions. Bit 28 of the first instruction half-word is zero for two-address instructions and one for three-address instructions. The length of the instruction is determined from bits 27 and 28 of the first instruction half-word and is verified against bit 27 of the last instruction half-word. If, in the case of two- or three-address instructions, bit 27 is not found to be zero, interruption code Operation Code Invalid (OP) is given.

#### 2.2.2.2 Control Word

Control words in general describe information. When this information is used as the operand of an instruction, the control word is called a "data description." Instructions refer to data descriptions by means of indirect addressing. Data descriptions may have the short or the long format.

Control words are also used for input-output control, for instruction-sequencing control, and for interruption control. These control words all have the long format.

The leftmost 24 bits of a data description form the address part in the same way as for an instruction half-word. The next eight bits are the mode bits. Mode bits specify type of addressing and type of data description, including the distinction between a short and a long data description.

In a long data description, the right half of the full word contains the refill and the count fields, each sixteen bits in length.

Each field of a data description word is intended for a distinct The address field is used to address the operand or series of operands to which the data description refers. The address field can be changed by an increment which is either implied or explicitly specified. Implied increments normally increase the word address by one. Word address 65,535 (2<sup>16</sup>-1) is followed by word address zero. The count field registers the number of times an increment is to be applied. The contents of the count field are reduced by one whenever a count is specified. A zero count is followed by a count of 65,535  $(2^{16}-1)$ . An initial count of zero is interpreted as 65,536 (216). The refill field contains the address of a new control word that can replace the original control word. Refill can be made conditional on the count reaching zero or it can be specified to occur unconditionally. By means of this refill operation a sequence may be established between control words. Such control words are said to be "chained." Chained control words may specify chained records, multiple fields, or multiple words. The operand addressing and the instruction set take full advantage of the data description fields for the above purposes. However, a different use of data description fields is possible if desired. For instance, the address field may be compared against a limit placed in the count or refill field. Sufficient operations are available to permit flexibility in this respect.

In input-output operations, a control word is used to control data transmission to and from the external units. In these operations, some of the mode bits are further defined, as described in Chapter 7.

The uniformity of format allows a control word to be used both for input-output and for internal processing operations.

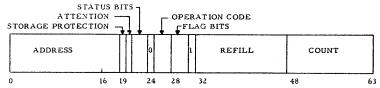

The input-output format is also used for the interruption control words and in modified form for the program control word.

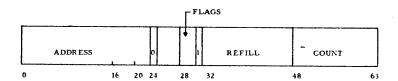

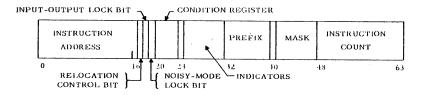

The program control word format is shown below. The address field of the program control word is shortened to seventeen bits, leaving room for mode and condition bits. The address field is used to specify the next instruction to be performed. Three mode bits are available to specify addressing, input-output, and floating-point operating modes. The condition bits refer to the final condition of the current instruction. The next two bytes are used for indicator bits. These bits record program alert situations. The refill field is used for the prefix field and the mask bits. The prefix field is a truncated full-word address. The eight low-order bits of this address, the prefix address, are omitted because they are always zero. Mask bits are used in conjunction with the indicator bits and specify which program alerts may cause an interruption. Further explanation of the purpose of these fields is found in Chapter 3.

## 2.3 INDIRECT ADDRESSING

The address part of an instruction half-word is normally used to address the data upon which the instruction operation is performed. This addressing mode is called "direct addressing." In another mode, bits 0-16 of the address can be used to address a data description which in turn contains an address part that can be used to address data. The process of using a first-level address to obtain a second-level address is called "indirect addressing." The second-level address can in turn refer to another data description of which, again, the address can be used. In this manner, it is possible to extend indirect addressing through many levels. Indirect addressing has a variety of applications as a programming tool. In addition, it should be noted that since some data formats can only be described by long data descriptions, indirect addressing is required to specify these formats.

Bit 24 of an instruction half-word or a data description indicates whether or not indirect addressing will take place. When bit 24 is zero, direct addressing takes place. When bit 24 is one, indirect addressing takes place. Indirect addressing applies only to the address which is part of the instruction half-word and may be specified for each instruction half-word independently. Indirect addressing is also independent of the operation to be performed. Conversely, the operation as specified in bits 27-31 of an instruction half-word is not altered by indirect addressing. Bits 25 and 26, when used as the byte size modifier and signed-unsigned modifier in two-or three-address instructions are replaced by the corresponding bits of the data description. Otherwise, bits 25 and 26 of the instruction half-word remain unchanged by indirect addressing.

Each time a data description is fetched in indirect addressing, bit 24 is inspected. When bit 24 is one, indirect addressing continues through another level, using bits 0-16 to address the next data description. When bit 24 of the data description is zero, a direct address is indicated. The data description is short or long accordingly as bit 31 is zero or one. A long data description is normally obtained from a full word address location. When bit 16 of the address referring to the control word is one, that is, when it refers to the right half of a full word address location, the right and left half of the control word are interchanged. The middle address (M) of a three-address operation can never refer to a long data description. For this address, bit 31 is not tested, and a short data description will always be assumed.

When a refill operation takes place, bit 24 of the new control word is again inspected, and any indirect addressing which may be specified is performed. At the end of the indirect addressing operation, bit 31 again is inspected to distinguish short and long data descriptions.

During an input-output operation, no indirect addressing takes place when a refill operation replaces an input-output control word by its successor. Bit 24 and 31 of the new control word are always ignored under these circumstances.

The last data description fetched by a refill or indirect addressing operation is retained in its entirety. The processor has enough register storage to retain the necessary instruction code and modifier bits, as well as all 64 bits of a long data description. As a result, the processor may return a long data description to storage at the end of an operation with updated address and count fields, but otherwise identical to the data description which was fetched. Storing of these final data descriptions is further described in Section 2.5.

In indirect addressing, it is possible that through a programming error the addresses refer to each other in such a way that they form a loop. As a result, the processor cannot finish its operation and no interruption is accepted. To prevent the machine from being locked in this way, an instruction will be terminated if still active after one-tenth second, and an interruption code Unending Sequence will be stored in the interruption stream.

#### PROGRAMMING NOTE

The indirect-addressing action for bits 25 and 26 makes it possible to specify byte size and signed-unsigned options as part of a data description.

#### 2.4 INDEXING

Floating-point arithmetic, accumulator and control-word instructions permit address modification by indexing. A total of 255 index words may be specified by a program.

Bits 16-23 of the instruction are used to indicate the index to be selected. When these bits are all zero, no indexing takes place, otherwise these bits are used as the index address. The index words are found at locations 1-255 following the prefix location of the program. Therefore, the address of an index word may be obtained by using the prefix field, bits 32-39 of the program control-word, as the high-order part, and the index field, bits 16-23 of the instruction as the low-order part.

Some of the index locations are special-purpose locations, such as final control-word and accumulator locations, and therefore serve a dual purpose.

Address modification is performed by adding bits 0-15 of the index word, the value field, to bits 0-15 of the instruction. Both fields are treated as unsigned hexadecimal integers and any overflow carry is ignored. Since only bits 0-15 of the index word are used in address modification, the other bits may be assigned in any desired way. In particular, when the control-word format is chosen, control-word operations may be used to change the index value.

It is permissible to specify both indexing and indirect addressing in one instruction. When both are specified, indexing takes place first, then the modified address is used in indirect addressing. Following the indirect-addressing operation, the new data description is inspected again for any additional indexing. Indexing and indirect addressing will alternate when each is specified in subsequent data descriptions. When no indexing is specified, indirect addressing takes place at once. The process terminates when no further indirect addressing is designated. The combined indexing-indirect addressing process is subject to the one-tenth of a second time limitation. When the time limit has been exceeded, the interruption code Unending Sequence (US) will be stored. When a refill operation takes place, both indexing and indirect addressing may be performed.

# 2.5 OPERAND ADDRESSING

The address part of an instruction half-word may be modified by indexing or indirect addressing, as has been described. The final address thus obtained is called the "effective address." When no address modification occurs, the address part of the instruction half-word is the effective address. An effective address always contains 24 bits, but depending upon the operation, less than 24 bits may be required. In each case, only the applicable part of the effective address is used, the nonapplicable part being ignored. When a long data description is used to address an operand, the refill and count field, as well as the effective address, are used to specify the operand.

The refill field of a long data description may be used to obtain a new data description. This new data description may be short or long and may specify indirect addressing or indexing, depending upon the state of bits 31, 24, and for indexable instructions, bits 16-23. The new data description may also introduce a new byte size and signed-unsigned modifier.

The refill field introduces the possibility of an unending chain of control words. Because of a programming error, this chain of control words may result in an unending operation. To prevent such an operation from locking the processor, the operation will be terminated after one-tenth second, at which time the interruption code Unending Sequence (US) will be stored.

The final values of long data descriptions are placed in core storage at the completion of the operation. These values are called "final data descriptions." The data description belonging to the first instruction address, called the "first final data description," is stored at the address two above the prefix address of the current program. The data description belonging to the last instruction address, called the "last final data description," is stored at the next higher word address. Short data descriptions are stored only in data-transmission operations.

The storing of final data descriptions makes it possible to use them in subsequent operations. The final data descriptions, furthermore, identify the results of match-type operations.

# 2.5.1 Byte

The operation LOAD CONDITION REGISTER addresses a single four-bit byte in memory. For this operation, the first twenty bits of the effective address are used to specify the addressed byte. In byte connect and in match-type operations, a single byte is also addressed. The addressed byte may contain four or eight bits. Accordingly, the first twenty or nineteen

bits of the operand address are used to specify the byte. The choice of byte size is indicated by the modifiers, bits 25, 57, and 89.

# 2.5.2 Word

A full-word operand is implied by floating-point operations, control-word operations, and full-word transmission operations. These operations use the first sixteen bits of the effective address.

#### 2.5.3 Half-Word

A half-word operand is implied by branch and half-word transmission operations, and whenever indirect addressing is specified. For these operations, the first seventeen bits of the effective address are used. The sixteen high-order bits address a full word; the low-order bit addresses the first or second half of the full word.

## 2.5.4 Field

Operands of fixed-point or logical-processing operations normally have the field format. To specify a field, all 24 bits of the effective address are used. The sixteen high-order bits address a full word and the next four bits address the byte in the addressed word which is the leftmost byte of the field. Bits 20-23 address the rightmost byte of the field. This byte may be part of the addressed word or of the next higher addressed word in storage. The word-address of this byte need not be given since the field length never exceeds sixteen bytes. The leftmost and the rightmost bytes of the field thus defined are part of the operand. When the byte address of these two bytes is the same, a field length of one byte is implied.

#### 2.5.5 Record

In logical-processing operations, a long data description may be used to address a record when processing from left to right. The leftmost byte of the record is addressed by bits 0-19 of the data description. The count field specifies the number of full words in which the record is placed. This number includes the words in which the leftmost and the rightmost bytes are located, although these words may not be fully occupied by the record. When no word boundaries are crossed by a record, the count is one. When a record crosses a word boundary, the count should be two. If, in this instance, a count of one instead of two is given, the processing will terminate either within the first word or at the word boundary.

The byte address of the rightmost byte of the record is specified by bits 20-23 of the data description.

Only the first and last address of an instruction may refer to a long data description and thereby specify a record. The middle address of a three-address instruction cannot specify a record.

Records may be changed by means of a refill function. After processing the last byte of a record, a new data description may be used to specify the record with which processing is to continue. The first byte of the new record follows the last byte of the current record without disruption of the logical-processing operation. The full-word location of the new data description is defined by the refill address of the current data description. Refill operation only takes place when bit 30 (the chain bit) of the current data description is one. When the chain bit is zero, no refilling takes place. As part of a refill operation, the byte size of the record may be changed.

A logical-processing operation may use both fields and records for operands and results. The operation is terminated when the first termination of a field or a record occurs. In some operations, termination may occur even earlier because of other conditions which will be discussed later.

The final data description placed in storage specifies the part of the record or records which remain to be processed; that is, the address, count, and refill field of the final data descriptions have been updated to refer correctly to these remaining record parts. If the entire record were processed, the byte beyond the rightmost byte of the record is addressed, and the final count is zero.

#### 2.5.6 Multiple Field

The multiple-field format permits arithmetic operations to be repeated with a series of operands. A long data description is used to address the multiple field. The address part of the data description is used to address a field in the same manner as is the case for the field format. When the numeric operation on the specified field is completed, the word address of this field is incremented by one and the operation repeated with the newly defined field. At the same time, the count of the data description is reduced by one. When the count reaches zero, operation is terminated unless the chain bit is one, in which case the data description is refilled. When two multiple fields are used in an operation, the multiple field which terminates first will terminate the entire operation. When one of the operands in a multiple-field operation is specified by a single field, the data in that field is used repeatedly. The middle address of a three-address instruction cannot refer to a multiple field.

Multiple-field operation may be specified in all floating-point operations and in fixed-point operations with the exception of DIVIDE.

Multiple field may also be specified in TRANSLATE WITH LEFT CARRY.

The first and last operand should both be a field or both be a multiple field in all operations except ADD, TRANSLATE WITH LEFT CARRY, and LOAD, otherwise incorrect results will occur.

The final data descriptions specify the fields which remain to be processed. If all fields are processed, one field beyond the last field is addressed and the count is zero.

#### PROGRAMMING NOTE

The refill operation introduces an entire new record description and makes it possible to change byte size, signed-unsigned modifiers, length, and relative location of subsequent fields.

### 2.5.7 Multiple Word

In full-word data transmission, a long data description may be used to address multiple words. The address part of the data description is used to address a word, as in the case of full-word addressing. The initial count specifies the total number of words to be transmitted. The word address, bits 0-15, is incremented by one each time a word is transmitted. At the same time, the count is reduced by one. When the count reaches zero, operation is terminated provided the chain bit of the data description is zero. If the chain bit is one, the control word is refilled. When data descriptions are used for both operands of a transmission operation, the data description which terminates first will terminate the operation. When a data description is used for only one operand, the effective address of the other operand is incremented until the operation is terminated by the data description.

In data-transmission operations, the final data description, including address, count, and refill fields, specifies the words which remain to be transmitted. If all words are transmitted, one word beyond the last word is addressed and the final count is zero.

Two final data descriptions are stored even if only one long description is specified. A short data description or an instruction half-word when stored will have the full-word address correctly updated, and bits 24 and 31 will both be zero, and therefore can be used in indirect addressing. The other bits of this final data description are uncertain and should not be used.

Input-output control words also address multiple words. Data transmission in input-output operations is in several ways similar to internal transmission; chaining is provided and final control words are placed in storage. Input-output data transmission and multiple-word definition are described in Chapter 7.

### 2.6 ADDRESS TRANSLATION

Address translation, provided to allow dynamic program relocation, only takes place when the relocation mode is specified in the current program control word. The relocation control bit, bit 17 of the program control word, when one, specifies the relocation mode; when zero, no address translation takes place. Input-output operations are not controlled by a program control word and therefore are never in the relocation mode.

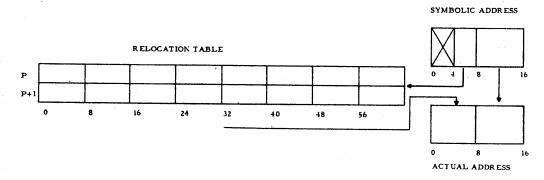

In the relocation mode, all addresses supplied by and available to the program are treated as "symbolic addresses." These symbolic addresses are changed by means of a relocation table to "actual addresses" when storage is addressed. As a result of address translation, storage is divided into 256 blocks which can be individually assigned.

# 2.6.1 Relocation Table

The relocation table is used to translate a symbolic address into an actual address. The table has sixteen 8-bit entries and is placed in the two locations at the prefix address and the next higher word address.

Bits 0-3 of the symbolic address are ignored. Bits 4-7 of the symbolic address are used to select an eight-bit entry from the relocation table. This entry replaces bits 0-7 of the symbolic address, thus forming the actual address. Bits 8-15 of the symbolic address remain unchanged in the translation process.

An all-zero entry in the relocation table is called an "empty address." When such an address is obtained in the translation process, the operation is terminated, and the program is alerted by the interruption code Empty Address (EA). If several of the symbolic addresses used by an instruction are empty, only one interruption code will be stored. Following the detection of an empty address, the instruction address may point either to the next instruction in sequence or to the second or third instruction half-word of the current instruction.

## 2.6.2 Block Boundaries

Entries in the relocation table specify the addresses of 256-word storage blocks. The translation process makes it possible to refer with a set of continuous symbolic addresses to noncontiguous storage blocks. Because each address occurring in an operation is individually translated, the data participating in the operation may belong to different blocks. However, individual fields, records, multiple fields, and multiple words should be entirely within a block. When a block boundary is crossed, operation is terminated and the interruption code, Address Invalid (AD) is stored. Similarly, the instruction address may not be incremented across a block boundary. Again, the code Address Invalid (AD) will be given if this event occurs. In order to cross block boundaries for data, the refill feature should be used. In the case of instructions extending beyond a single block, a branch instruction should be used. An Address Invalid (AD) code will also be given when the address in the data descriptions stored in a transmission operation or the address in the program control word stored in a branch and preserve operation would have crossed a block boundary, even though the operand or instruction addresses had not yet crossed that boundary. In these cases the control word is not stored.

#### PROGRAMMING NOTE

Although a record or multiple field cannot cross a block boundary, the final control word will address a new block when termination occurs at the boundary.

### 2.6.3 Addresses Translated

Addresses are translated only when they are used to address storage. All addresses placed in storage, such as the addresses in final data descriptions or program control words, are stored in their updated symbolic form.

#### Address translation includes

- all effective addresses used in fetching or storing data or instructions;

- addresses used in fetching data descriptions or control words as part of indirect addressing;

- 3) the address of the initial control word of an input-output operation, including the RELEASE CHANNEL instruction; and

4) the direct address of a channel in an input-output instruction.

### Addresses not translated are