# IBM CONFIDENTIAL

This document contains information of a proprietary nature. ALL INFORMATION CONTAINED HEREIN SHALL BE KEPT IN CONFIDENCE. None of this information shall be divulged to persons other than IBM employees authorized by the nature of their duties to receive such information, or individuals or organizations who are authorized by the Data Systems Division in accordance with existing policy regarding release of company information.

Reference Manual

7750 Programmed Transmission Control

**Preliminary Edition**

#### **PREFACE**

This manual, a preliminary edition, presents the operation and use of the IBM 7750 Programmed Transmission Control. It provides a reference and guide for those familiar with the 7750 and serves as an instructional aid in the training of operators and programmers.

The 7750 Reference Manual contains four sections: Introduction, Detailed Description, Channel Adapters, and Communication System Design.

Section I introduces the 7750. It tells what the 7750 is, the computers that it can operate with, and how it functions in a TELE-PROCESSING system.

Section II describes the 7750 functionally. This section covers in detail such areas as registers, timing, instructions, priority processing, and so on.

Section III explains the type of adapters used by the 7750 to communicate with the various terminals of a TELE-PROCESSING system. The description and operation of each type of adapter is presented.

Section IV tells the philosophy behind the design of the 7750, its flexibility, and its limitations. Tables are provides to show how various channel configurations are possible and practical.

Address comments concerning this manual to: IBM Corporation

Customer Manuals, Dept. 298

P. O. Box 390

Poughkeepsie, N. Y.

Form No. A22-6679

©1962 by International Business Machines Corporation

# CONTENTS

| INTRODUCTION                                   | ]<br>] |

|------------------------------------------------|--------|

| General Organization                           | 3      |

| Communication Terminology                      | 4      |

| Assembly of Character                          | 4      |

| Mode System of Interrupts                      | 9      |

| Methods of Processing                          | 10     |

| Information Transfer                           | 12     |

|                                                |        |

| DETAILED DESCRIPTION                           | 13     |

| Process Storage                                | 13     |

| Control Storage                                | 15     |

| Registers                                      | 17     |

| Timing                                         | 20     |

| Instructions                                   | 27     |

|                                                | 27     |

| Description of Instructions                    | 42     |

| Priority Processing                            | 42     |

| Channel Input-Output                           |        |

| Transmission Between the Computer and the 7750 | 64     |

| Loading the IBM 7750                           | 70     |

| Programming Aspects                            | 72     |

| Error Checking                                 | 74     |

| Operator's Panel                               | 76     |

| CHANNEL ADAPTERS                               | 79     |

| Type I Multiplexing Channel Adapter            | 79     |

| Detailed Description                           | 83     |

| MCA 1 Operation                                | 88     |

| Timing                                         | 90     |

| Error Checking                                 | 93     |

| Type 2 High Speed Channel Adapter              | 93     |

| Communications Line Terminator                 | 99     |

| Low Speed Operation (On Line)                  | 102    |

| High Speed Operation (On Line)                 | 102    |

| Diagnostic Operation (Off Line)                | 102    |

| COMMUNICATION SYSTEMS DESIGN                   | 104    |

| Processing Canabilisis                         | 104    |

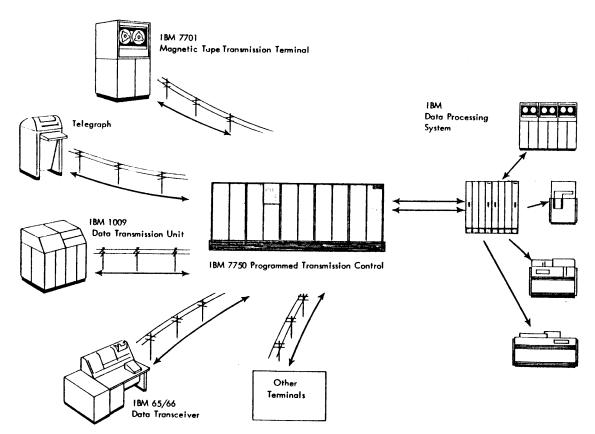

Figure 1. Communication-Based Data Processing System

#### INTRODUCTION

# GENERAL INFORMATION

The IBM 7750 Programmed Transmission Control is a TELE-PROCESSING system component that links a central computer with remote terminals. Tele-communications equipment such as telegraph terminals, IBM 65/66 Telegraph Data Transceivers, or IBM 7701 Magnetic Tape Transmission Terminals may be connected to the 7750 through appropriate channel adapters. On the other end, the 7750 is connected to an IBM Data Processing System through a data channel. The 7750 thus enables computer users to combine data processing capabilities with the transmission capacity of many telecommunication devices (Figure 1).

The 7750 is a stored program unit that serves as a buffer control device, directing and controlling the flow of information between the computer and its communication network. This communication network may have a variety of standard or specially designed terminals, each operating independently but linked directly to the system. The terminals may have different transmission speeds. The 7750 accepts electrical signals simultaneously from a number of communication lines, converts these signals into bits, then into characters, then into records and, finally, relays these records at high speed to the computer for processing.

In most uses, the prime function of the 7750 is to connect the diverse elements of the communication network to an associated computer such as the IBM 1410, 7040, 7044, 7070, 7074, 7080, 7090, or 7094. TELE-PROCESSING systems using the 7750 may be employed for airline reservations, message routing, centralized data processing, production control, or other applications. The system planner can choose the computer and be assured that the communication problem will not be a significant factor in determining his choice.

The TELE-PROCESSING system depends on the terminals used, which model of the 7750 is installed, and the traffic volumes of the customer.

Within a TELE-PROCESSING system, the 7750 performs five basic functions:

Data Assembly (and Distribution) proceed automatically with only occasional supervision from the stored program. Data assembly begins with the derivation of bits from the incoming communication circuit by the channel adapter. The process continues to the point where characters are assembled into complete data messages in the process storage section of the 7750.

<u>Information Conversion</u> from or to the form required by the computer may include changes to both the code and format of the message. Conversion is controlled by the 7750 stored program.

Editing involves omitting and adding special characters -- and, sometimes, format changes -- under program control.

Monitoring and Supervision checks incoming (or outgoing) traffic to indicate the status of terminals and oversees the data flow in a network. The stored program controls these functions.

<u>Data Transfer</u> supplies data to and accepts data from the computer, on a demand and response basis, through linkage connecting the 7750 and the computer.

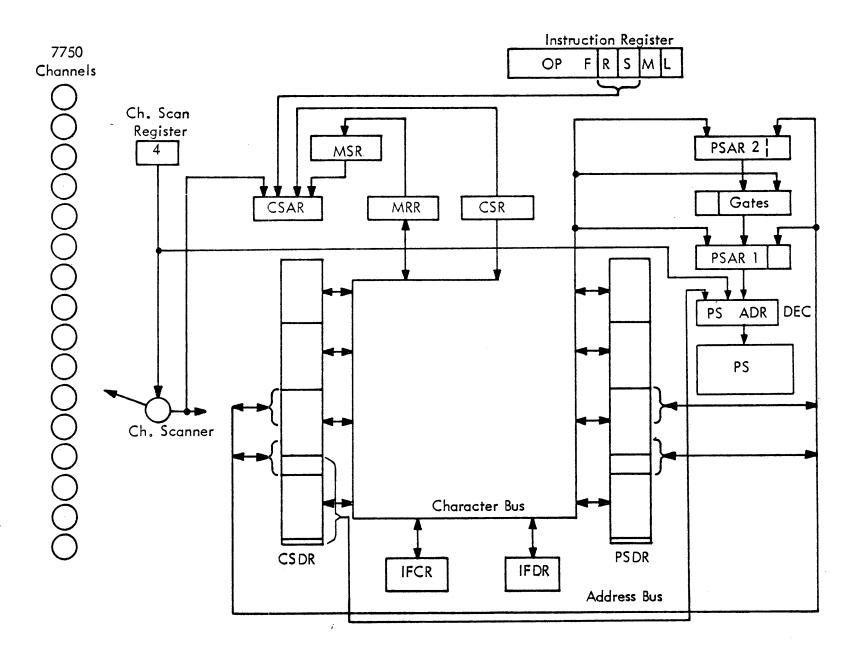

#### GENERAL ORGANIZATION

The 7750 is made of five standard IBM racks. An optional sixth rack is used for low speed relay connection to telegraph lines.

## 1. Communications Line Terminator Rack

The major function of this rack is to aid the customer in isolating troubles in his communications network. The rack contains patch panels, signal generation circuitry, and equipment to aid in the running of diagnostic programs in the 7750.

#### 2. Channel Adapter Rack

This rack is designed to hold different types of Channel Adapters, and different combinations of these types. The Channel Adapters perform a variety of functions such as time multiplexing a number of low speed communications channels into one high speed output, and recovering bit timings from synchronous data. The design of this rack is modular, to match different types of communications networks.

#### 3. Process Control Rack

This rack contains the registers and the instruction control circuitry of the 7750. All processing is controlled by this rack.

# 4. Core Storage Rack

This rack contains two magnetic core memories, called Process Storage and Control Storage. Process Storage is available in three different sizes, 4,096, 8,192, and 16,384 words at 48 bits per word. Control Storage contains 128 words, 48 bits per word. The data and address registers for these storages are in the Process Control Rack.

# 5. Power Supply Rack

The Power Supply Rack contains all the power supplies necessary to run the 7750.

The IBM 7750 is organized around two magnetic core storages. Control Storage is used to control the communications network and to assist in the execution of the programs. This memory contains 128 words, 48 bits per word of storage. Process Storage is used to hold the message queues, and the programs. Process Storage may be one of three sizes; either 16, 384 words, 48 bits per word; 8, 192 words, 48 bits per word; or 4, 096 words, 48 bits per word. The size of Process Storage is chosen to fit particular job applications. All important functions of the 7750 are performed in and around these memories.

## COMMUNICATIONS TERMINOLOGY

The following communications terms are defined to clarify the explanation of 7750 operation.

Half Duplex -- A half duplex communications channel is one in which information can be transmitted in either direction, but only one direction of transmission may be employed at any one time.

Full Duplex -- A full duplex communication channel is one in which information can be transmitted in both directions simultaneously. In actual practice, full duplex channels are often made of two half duplex channels.

Start - Stop Transmission -- In this method of transmission the data bits are preceded by a start bit, and are followed by one or more stop bits. The total number of stop bits is not necessarily an integer. The purpose of this method is to allow the receiving terminal to stay in synchronization with the transmitting terminal. The start and stop bits are the synchronizing information, and thus the receiver is resynchronized by each character. This method of transmission is used by normal telegraph machines.

Synchronous Transmission -- In this method of transmission, the receiving terminal is initially synchronized with the transmitting terminal by the receipt of special synchronizing information, (bit pattern) and then the transmission of data begins. While data is being transmitted, no special synchronizing information is needed. It is assummed that both terminals will stay in step for the duration of the transmission. At intervals, new synchronizing information will be transmitted. This may be done at the beginning of every message, or it may be done as infrequently as once a day. Synchronous transmission is generally used on high speed channels, since one of its main advantages is that it requires less bits than start-stop to transmit the same amount of information. For example, the IBM 7701 Magnetic Tape Terminal employs synchronous transmission.

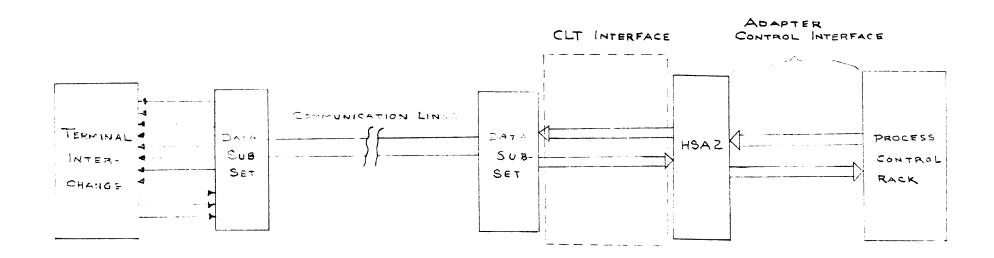

Sub-Set -- The word subset is an abbreviation for the words subscriber set. This is a modulation-demodulation device which accepts as an input binary-valued electrical signals, and gives as an output a modulated wave form, suitable for transmission over a communications channel. Conversely, the subset receives modulated wave forms from the communications channel and converts them into binary-valued electrical signal outputs.

#### ASSEMBLY OF CHARACTERS

Messages from the communications network enter the 7750 via one of several types of channel adapters. These adapters perform a variety of functions. One type, the Low Speed Group, time multiplexes a number of low speed communications adapters into one

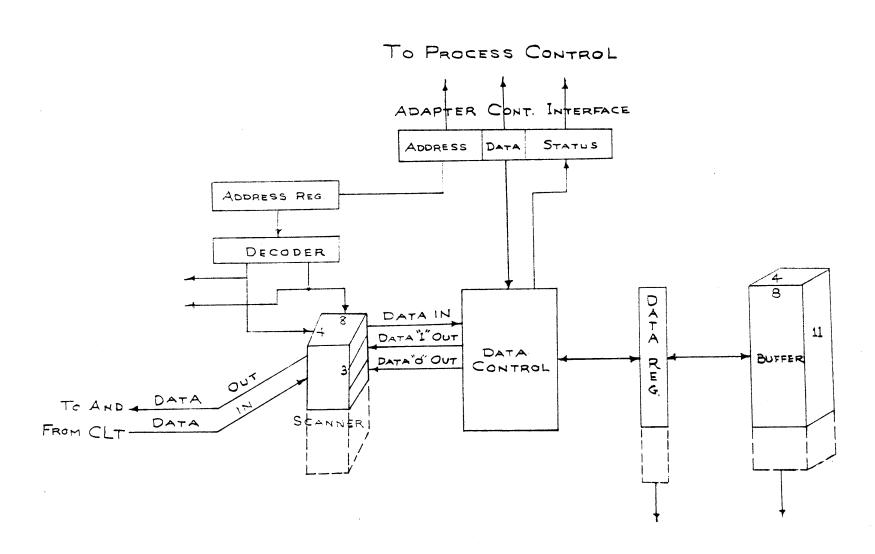

high speed information channel. It does this by a process of scanning and storing the results in a small core buffer. The high speed adapter (HSA2) receives its information from an FM subset or the 202 A or B subset. All adapters communicate with Control Storage by means of the Adapter Control Interface.

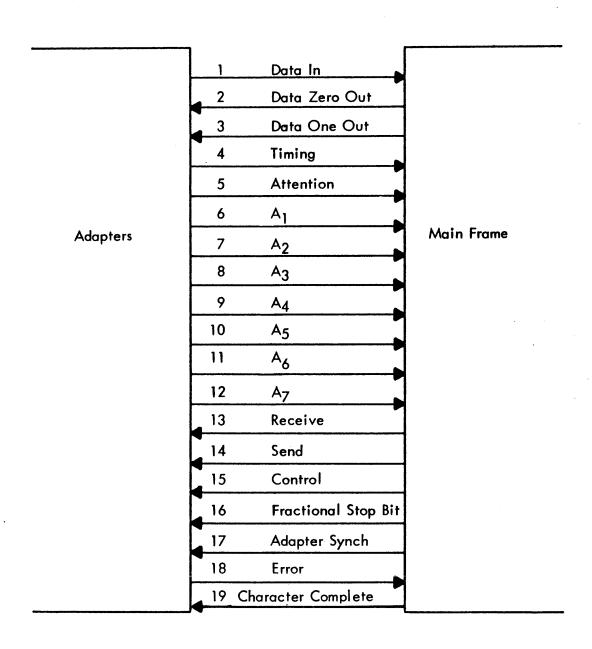

# Adapter Control Interface

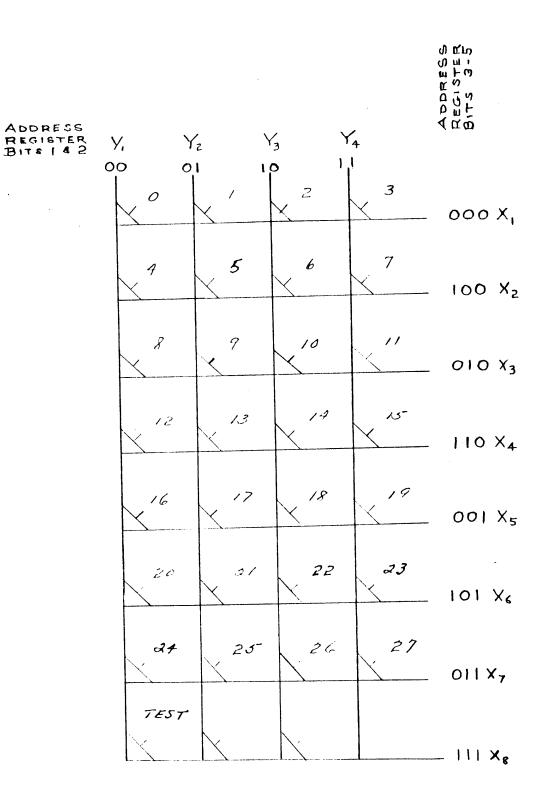

The Adapter Control Interface connects the channel adapters to the Control Storage Data register. This interface contains nineteen lines. Each adapter is connected in parallel to these nineteen lines, and a sixteen position scanner selects a particular adapter at a given time. In other words, all the adapters are on a bus system, with the scanner doing the selecting. The scanner is timed sequentially; there is no addressing of the scanner and no priority scan system employed.

Three types of information are passed across the interface. They are: data, control information, and addresses. Data is transferred serially one bit at a time. Characters are not assembled in the adapters; they only acquire bits. Therefore, data is transferred one bit at a time across this interface, together with control information telling when a new bit should be accepted. Address information is transferred from the adapters to Control Storage, each adapter having one or more Control Storage locations associated with it. The rest of the control lines perform such functions as indicating to an adapter whether it should be in sending or receive status, or indicating to Control Storage when some type of error has occurred in the adapters. All the lines in the Adapter Control Interface are controlled by a word in Control Storage, called the Channel Word.

#### Channel Word

The Control Storage operates on two different types of cycles alternately. These cycles are called Scan and Process cycles. The Process cycle is devoted to message processing and is discussed later. The Scan cycle is devoted to receiving bits from, or transmitting bits to the communications network. During Scan cycles, Channel Words are read from Control Storage. The address of this word is generated in the channel adapter selected by the sixteen position scanner in the Adapter Control Interface. There is at least one Channel Word per half-duplex communications channel connected to the 7750, and two Channel Words for each full duplex communications channel attached; one word for the receive portion of the full duplex channel, and one word for the transmit portion of the full duplex channel. These channel words completely control the action of the associated communications channel.

The Channel Word has three major functions: It serves as the assembly area in which bits are assembled into characters; it directs the assembled character into the proper queue, and it controls the communications channel.

1. The assembly of bits into characters is done in one 11 bit field of the 48 bit Channel Word. Character length may be any number of bits from one to eleven. As this

assembly field is a shift register, bits are accepted one at a time and shifted until a complete character has been received. During transmission, a complete character is put into the assembly area, and shifted out one bit at a time. Certain control fields are associated with the character assembly field. These are the Character Length and the Bit Count. The Character Length is a four bit field used to indicate the size of the character being received or transmitted over this particular communications channel. The Bit Count is a four bit field which may be used to indicate how many bits of a given character have been received or transmitted. The use of these fields differs somewhat in start-stop and synchronous transmission, and their exact usage is explained in the detailed description section. As an example, however, consider the reception of a synchronous transmission which uses six-bit characters. To do this the Character Length would be set to six by the program, and the Bit Count would advance every time a bit was received. Every time the Bit Count equalled the Character Length, a complete character had been received. Three fields, the character assembly field, the Character Length, and the Bit Count, working in conjunction with one another, allow the reception and transmission of variable character lengths, one bit at a time.

- 2. When the character has been assembled, it must be directed into the proper queue in Process Storage. Another field in the Channel Word contains a 16 bit address which refers to Process Storage. The assembled character is stored at this location in Process Storage. Note that 16 bits are sufficient to refer to 65,536 locations. Each word in Process Storage may be divided into four fields, and the address in the Channel Word is sufficient to specify any of them. When the character is complete, it is immediately put into Process Storage, regardless of what else may be going on in the machine. This process of transferring a complete character from the Channel Word to the Process Storage is called Character Interrupt, and is done automatically without program intervention. After a character has been transferred to Process Storage, the 16 bit address in the Channel Word is automatically incremented by one. When transmitting, the reverse procedure takes place. Characters are transferred from Process Storage into the character assembly field of the Channel Word, and the address in the Channel Word is incremented.

- 3. The third function of the Channel Word is to control the communications channel. A number of bits in the Channel Word are used for this purpose. These bits perform such functions as indicating whether the channel is in send or receive status, whether the start-stop or synchronous mode of transmission is being used, whether the initial synchronization pattern has been found, or whether the channel should be searching for this pattern, and whether the 7750 is waiting for a response on this channel. The use of these bits in the Channel Word are further explained in the next section.

By assigning these functions to the Channel Word, and by having at lease one Channel Word per communications channel, it is possible to have every communications channel operating in a different fashion, using different character lengths, and different methods of transmission, and yet maintain control over the channel by accessing the proper word. Only one control register is required, the Control Storage Data Register and it is time shared. Thus, the Channel Word concept provides an economical means of channel control and of character assembly.

#### Queue Formation

When characters have been assembled in Channel Words, they are automatically transferred into a queue in Process Storage. The formation and maintenance of these queues is one of the most important tasks performed by the 7750. A large portion of Process Storage may be occupied with such queues since there will be an incoming queue for every channel receiving information from a communication terminal, an outgoing queue for every channel transmitting information to a communication terminal, a queue of information for the computer, and a queue of information coming from the computer. If Process Storage is to be efficiently used, a good system for assigning queuing space must be used.

Many methods of memory space assignment are possible. For example, a fixed block of storage can be assigned to each communications channel for its queuing space. This is a relatively inflexible and inefficient method of storage location. Problems exist of overflowing the fixed amount of space, or of never using an appreciable fraction of the space. The problem is made more severe since message lengths are not restricted or in any way controlled. The 7750 assigns its memory space for queues by the process of chaining.

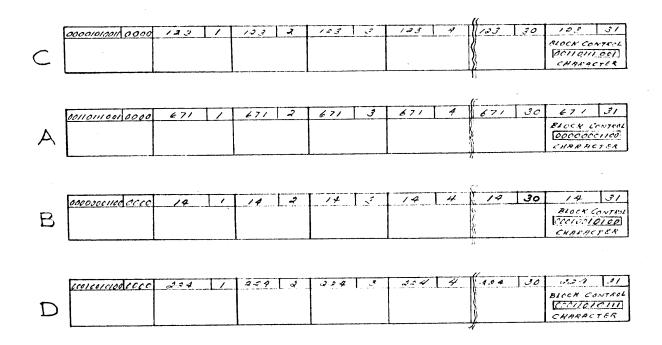

Chaining consists of associating a sufficient number of pieces of memory space so that enough storage locations are available to perform a given job. For purposes of chaining, Process Storage is broken into pieces called blocks. Each block consists of 8 words. Each word is broken into four fields of eleven bits each. Therefore, thirty-two characters may potentially be stored in each block. However, the thirty-second storage location in each block is reserved for a special character, called the Block Control Character. Each block has a starting address whose five low order bits are all ZERO'S, and since there are thirty-two characters per block, an ending address is one whose five low order bits are all ONES.

The Block Control Character is the means by which the blocks are chained together. The Block Control Character is the 11 high order bits of the starting address of the next block in the chain. For example, four blocks can be arbitrarily labeled A, B, C, and D. Figure 2 shows these blocks with their starting addresses. Figure 3 shows these blocks chained together, the order of the chain being C-A - B-D. They are chained because the Block Control Character in block C is the eleven high order bits of the starting address of block A; the Block Control Character is block A in the eleven high order bits of the starting address at block B, and so on. By means of chaining, small pieces of storage have been effectively assembled into a larger portion of storage. Note that the blocks which make up the chain are not necessarily continuous in storage. These blocks may be physically located almost anywhere within Process Storage, but they act like a continuous segment of storage due to chaining.

To make this process work, a certain amount of bookkeeping is required. One method of doing this is as follows: First, chain together all the unused blocks of memory. Then maintain as records two addresses, A1, the starting address of the first empty block in the chain, and A2, the address of the Block Control Character in the last empty

FIGURE 2 BLOCKS

FIGURE 3 CHAIN C-A-B-D

block in the chain. Suppose that a message queue has filled its chain and that another block is required. Then the eleven high order bits of the starting address of the next block are put into the Block Control Character of the last block in the message queue, and the first empty block from the chain of empty blocks is attached to the message queue. Since this block is chained to the rest of the empty blocks, its Block Control Character is the starting address, A3, of the next empty block in the chain. Now A3 should be stored in the location which formerly held A1, since A3 is now the starting address of the first block in the chain of empty blocks. Thus, the process can be repeated.

When blocks become empty they must be returned to the chain of empty blocks. Suppose that A4 is the starting address of an empty block which is to be returned to the chain of empty blocks. A4 is then written at the address specified by A2. In other words, A4 is written as the Block Control Character of the last block in the chain of empty blocks The block whose starting address is A4 is now connected to the end of the chain of empty blocks. To complete the process, A5, the address of the Block Control Character of this block, is now written in the location at which A2 was stored.

After both these operations have been completed, a block has been removed from the front of the chain of empty blocks, and a block has been added to the end of the chain of empty blocks, and the addresses A3, and A5 have been stored. These addresses are again the starting address of the first empty block in the chain of empty blocks, and the address of the Block Control Character of the last block in the chain of empty blocks.

In the 7750, the chaining process is done under program control. When a particular channel requires more storage space for its queue, the Channel Service program is automatically brought into operation. The need for this program is sensed by noting when the five low order bits of the address contained in the channel word are all Ones. This indicates that the end of a block has been reached and that Channel Service is necessary to assign a new block to the chain. Thus far, characters have been assembled, and put into queues in Process Storage. They will next be processed in some way before being sent on to the computer.

#### MODE SYSTEM OF INTERRUPTS

The 7750 works in an essentially uncontrolled environment. In many applications, the 7750 cannot dictate when messages will occur on the communications network, or what the length of these messages will be. Communications from the associated computer may take place at random intervals. For these reasons, the 7750 is equipped with a very flexible interrupt system, so that it may quickly and automatically switch from one program to another when various conditions require immediate attention.

This interrupt system has several levels. An interrupt may interrupt an interrupt, and so on. Priorities are assigned to various classes of interrupts so that the machine can decide which interrupt to execute. There are six such classes of priorities in the 7750, and these classes are called modes. These modes, listed in order of decreasing priority are:

- 1. Service

- 2. Channel Service

- 3. Copy

- 4. Out

- 5. In

- 6. Normal

At the end of every machine cycle, the mode circuitry is examined to determine what modes are requested. The machine will then go into the requested mode with the highest priority and execute the programs associated with that mode. Requests for a mode are stored in a particular register, called the Mode request Register. This register maintains the requests until they can be serviced.

For example, assume the 7750 were in Normal Mode, and that some error detection circuitry turned on the Service Mode request, and during the same cycle the request for Channel Service Mode was turned on. The 7750 would then automatically start to execute the Service Mode programs, and when it had completed this program, it would switch into Channel Service Mode, and execute the Channel Service program. Finally, if no other mode requests had occurred, the 7750 would fall back into Normal Mode, and continue to execute the normal mode program from the point of the interruption. Note that a new mode may be requested either by the program, or automatically by means of special hardware.

Changes in mode can be made without any special preparation on the part of the programmer. It is not necessary to write a number of housekeeping programs to change modes. Instead, the 7750 stores all working registers and the instruction counter at the end of every machine cycle. Instruction counters are stored in Control Storage in a special format called the Process Word, or P word. This word contains three working registers as well as the instruction counter. There is one P word for each mode. Therefore, to change modes it is only necessary to access a different P word in Control Storage. The instruction counter in this P word will then address the programs associated with the new mode.

# METHODS OF PROCESSING

The 7750 processes messages in real time, in a wide variety of formats, character sizes, and codes. Methods of processing must be extremely flexible to meet the diverse requirements. Therefore, table look-up is the fundemental processing technique.

Table look-up is used for many purposes in a typical 7750 program including Code translations. Any code of up to 11 bits per character may be readily translated into any other arbitrary code of up to 11 bits per character. All shifts are performed by using shift tables. There is no shift instruction. Arithmetic operations are performed by means of multiple table look-ups. Perhaps the most important use of this technique is to control the operation of the Normal Mode program.

As an example of how the program may be controlled by table look-up, consider a telegraph polling system in which five programs may be required. These programs are Polling, Sending Data, Answer Back, Header Processing, and Message Processing. Assume there are 20 telegraph channels connected to the 7750. Each channel will require these programs in unpredictable sequence. A technique for handling this situation requires the use of a Program Branching Table, and the assignment of a unique identification number, called a Channel Number, to each communication channel. The 7750 then uses the Channel Number to address the Program Branching Table. The Program Branching Table will then cause the program to branch to the proper one of the five programs. The last action any one of the programs performs is to update the relevent entry in the Program Branching Table so that the next time the Table is addressed by the Channel Number, the proper program will be selected.

Table look-up operations can be programmed, due to certain features of the instruction set. These features are an address modification method, and a register and size specification method. Each method is described below.

The 7750 is a single address machine. In many instructions, this address can be modified by means of information specified in the instruction. Two fields in an instruction, the M field and the L field, specify this modification. The M field specifies a particular register, and the L field specifies from zero to eleven low order bits in that register. These bits then replace the L low order bits in the address before the instruction is executed.

Consider as an example, an instruction containing the address (163245)<sub>8</sub>; with M specifying the Y register, and L equaling 5. Assume the contents of the Y register to be (3732)<sub>8</sub>. The instruction would then be executed as though the address it contained were (163272)<sub>8</sub>; that is five low order bits of the Y register have replaced the five low order bits in the instruction.

The register and size feature of the 7750 instruction set allows the results of many machine instructions to be placed in one of seven addressable registers. The particular register to be used may be selected by setting the proper bits in the R field of the instruction. The number of bits which are to be loaded into the specified register may also be varied by setting the S field of the instruction. This feature allows the programmer to have the option of loading from zero to eleven bits into the specified register.

The combined use of the register and size feature, and the address modification method allows a table look-up to be performed in one instruction, with the final result stored in a designated register.

The instruction set contains other useful features. These features include the ability to perform most instructions with an indirect address; the ability to complement the operands in an instruction and the ability to increment the address of the Process Storage word address by the instruction. Indirect addressing, complementing, and incrementing may be done individually, or they may be done in combination when executing most instructions.

The instruction set makes message processing more efficient. The program operates upon characters and messages which have been automatically stored in the Process Storage. There will be one queue of data to be processed for each receiving communications channel, and one queue of data to be processed from the computer. The program processes the contents of these queues, character by character, and places the results in other queues. Some of these queues will be transmitted back into the communications network, and one queue will be transmitted to the computer. Thus information has been acquired from the communications network, processed, and is now in the format which the associated computer requires.

#### INFORMATION TRANSFER

The 7750 connects to a host computer by a read bus, a write bus, and a number of control lines to the proper data channel. The 7750 can be connected to the IBM 1410, 7040, 7044, 7070, 7074, 7080, 7090, and 7094 data processing systems.

The 7750 operates in three modes to service the computer. These modes are In, Out, and Copy. The In mode is used to prepare the 7750 for receipt of information from the computer. The control lines are examined, and the proper responses are made. The In mode program prepares a block of storage for the incoming information and sets up the proper control word so that the 7750 can determine when all the information has been received from the computer. The Out mode is used to prepare the 7750 for the transmission of information to the computer. Its mode program sets the proper signal to inform the computer that the 7750 has information to transmit. In addition, this mode program also prepares the queue of outgoing information, and sets up a control word so that the 7750 can determine when all information has been sent to the computer.

The actual transfer of information takes place in Copy Mode, which has no program. Information is transferred one character at a time, using a demand and response system. The control words which were prepared in the In or Out modes terminate character transfer at the proper number.

#### DETAILED DESCRIPTION

#### PROCESS STORAGE

The IBM 7750 Process Storage is a magnetic core storage available in three sizes:

4,096 words

8, 192 words

16,384 words

Each word contains 48 bits, including one parity bit.

#### Process Storage Word Formats

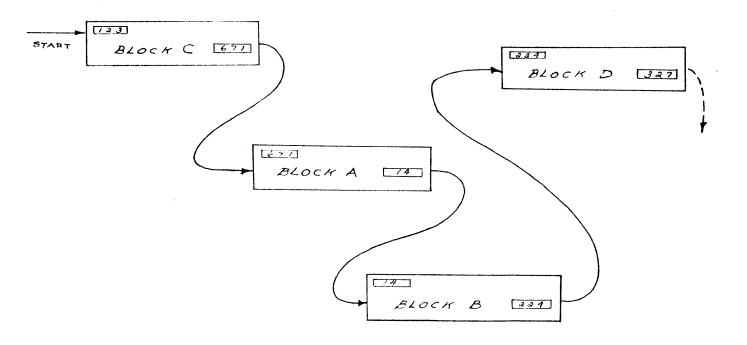

The contents of a word in Process Storage may be arranged in several ways, depending upon its intended use. Figure 4 shows the word format for Data Words, Instruction Words, and Limit Words.

#### Data Word - DWD

The Data Word is made up of four eleven-bit registers; A, occupying bit positions 47 through 37; B, occupying bit positions 33 through 23; C, occupying bit positions 22 through 12; and D, occupying bit positions 11 through 1. Bit positions 36 through 34 are not used. Bit position P is the parity bit for the entire word.

#### Instruction Word - IWD

The Instruction Word contains a ten-bit Operation Code in bit position 1 through 10, an OP code parity bit in bit position 11, a two-bit Flag field in bit positions 12 and 13, a four-bit L field in bit positions 14 through 17, a three-bit M field in bit positions 18 through 20, a four-bit S field in bit positions 23 through 26, a three-bit R field in bit positions 27 through 29, and a 16-bit Address in bit positions 32 through 47 (low order in position 32). Bit position P is a parity bit for the word, and bits 21, 22, 30, and 31 are not used.

#### Limit Word - LWD

The Limit Word, shown in Figure 4, contains a 16-bit address in the normal Address portion of the word (W). The Address occupies bit positions 32 through 47 of the word. In addition, the word contains a Limit of 16 bits which fills the C, and part of the B character fields. The five low order bits of the Limit occupy bit positions 23 through 27 in the B character field.

FIGURE 4 IBM 7750 WORD FORMATS

#### CONTROL STORAGE

The IBM 7750 Control Storage is a magnetic core storage with a capacity of 128 words. Each word has 48 bits, including one parity bit.

The Control Storage operates on alternate Scan and Process cycles of 11 microseconds and 17 microseconds, respectively. The Scan cycle contains 3 microseconds for modification of the data word between read and write, and the Process cycle contains 11 microseconds modification time. The beginning of the Control Storage Scan cycle precedes the beginning of the Process Storage Instruction cycles by 6 microseconds.

Data is entered into and out of the Control Storage by means of the Control Storage Data Register (CSDR).

#### Control Storage Data Register

The Control Storage Data Register is a 48-bit register which holds the word to be read out of, or to be written into storage. See Figure 4. The control circuits for this register provide the means to use it as:

- (1) a single 48-bit register.

- (2) four independent registers; X, Y, Z, (which are 11 bits), and an Instruction Counter (which is 14 bits).

- (3) three independent registers; Z (which is 11 bits), an Operational Address Register, and an Address of 16 bits each.

The Z register is a count down counter which may be decremented under program control.

# Control Storage Word Formats

The Control Storage Word will be arranged in three ways, depending upon its intended use. These word formats are described below. See Figure 4.

Channel Word - CWD

The Channel Word is divided into fields as indicated in the following table:

| Field                                                                                                                                                                            | CSDR Position No.                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| W - Word Address A - Character B - Last Timing C - Character Length D - Status-Micro E - Action F - Character Control G - Status-Macro H - Assembly/Distribution P - Word Parity | 47-34 33-32 31 30-27 26-23 22-20 19-15 14-12 . 11- 1 P |

| E - Action F - Character Control G - Status-Macro H - Assembly/Distribution                                                                                                      | 22-20<br>19-15<br>14-12<br>. 11- 1                     |

Process Word - PWD

or

For all modes except the Copy Mode, the Process Word will have one of the following interpretations:

| Field Name          | No. of Bits | Position |

|---------------------|-------------|----------|

| Instruction Counter | 14          | 47-34    |

| X                   | 11          | 33-23    |

| Y                   | 11          | 22-12    |

| $ar{\mathbf{z}}$    | 11          | 11- 1    |

| Word Parity         | 1           | P        |

|                     |             |          |

| Instruction Counter | 14          | 47-34    |

| Operational Address |             |          |

| Register            | 16          | 27-12    |

| Z                   | 11          | 11- 1    |

| Word Parity         | 1           | P        |

The second interpretation is used only with the Address and Limit moving instructions.

# Copy Mode Process Word

During the process cycle of the Copy Mode, the Control Storage Data Register is interpreted as follows:

| Field Name  | No. of Bits | Position |

|-------------|-------------|----------|

| Address     | 16          | 47-32    |

| Limit       | 16          | 27-12    |

| Z           | 11          | 11- 1    |

| Word Parity | 1           | P        |

#### REGISTERS

Registers are temporary storage devices. The size of a register is determined by the number of bits of information it can hold. Its use is determined by the nature of information that goes into the register. For example, a data register temporarily stores data, an address register temporarily stores an address, an instruction register temporarily stores an instruction, and so on.

From the programmer's point of view, registers may be divided into two general types: addressable and non-addressable. Addressable registers can be addressed by the stored program. That is, an addressable register may be loaded, set, or requested by the programmer.

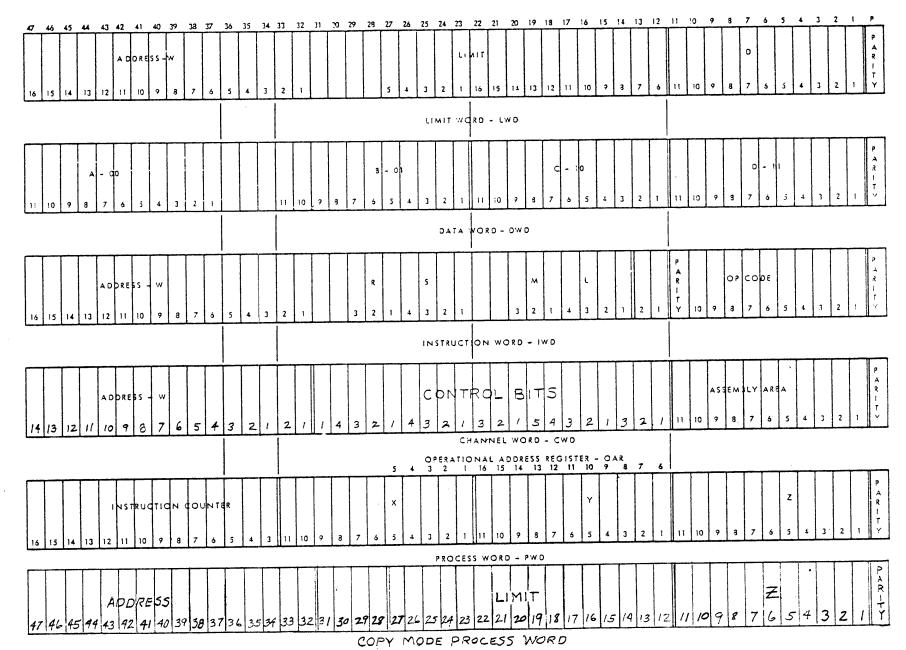

Non-addressable registers cannot be addressed by the stored program. They are set and reset automatically at the proper time. Figure 5 shows the registers of the 7750.

Non-Addressable Registers

Instruction Register

The Instruction Register is a 26-bit register which holds all of the instruction being executed, except the address. The first 10 bit positions contain the OP Code, the next two bit positions contain the Flag bits, the last 14 bits contain the R, S, M, and L fields.

Mode Status Register

The Mode Status Register is a 5-bit position register. Before the execution of each instruction, this register selects the bit associated with the highest priority mode from the priority requests contained in the Mode Request Register. At any one time, the Mode Status Register may contain only one bit (a logical One) to indicate the highest priority mode selected. If this register contains no logical One, the 7750 selects the Normal Mode.

Process Storage Address Register #1

The Process Storage Address Register #1 (PSAR #1) contains the current address for addressing the Process Storage. Address modification takes place as the address is set into this register from the Process Address Register #2 (PSAR #2). This register can hold 16 bits; fourteen bits are used to address the correct word in storage, and two bits are used to specify a particular character (0, 1, 2, or 3) within a four-character word.

Process Storage Address Register #2

The Process Storage Address Register #2 (PSAR #2) temporarily store a 16-bit address from the PSDR or CSDR. The address is transferred to the PSAR 1 when it is used to address the Process Storage.

FIGURE 5 IBM 7750 REGISTERS

## Control Storage Address Register

The Control Storage Address Register (CSAR) contains the current address for addressing a Channel Word or Process Word in Control Storage.

#### Process Storage Data Register

The Process Storage Data Register is a 48-bit register which holds the word read out from or to be written into Process Storage. This register can conform to any one of the three word formats in the Process Storage; namely, the Data Word format, the Process Word format, and the Instruction Word format.

# Control Storage Data Register

The Control Storage Data Register is a 48-bit register which holds the word read out of or to be written into the Control Storage. This register can conform to any one of the four formats of the Control Storage; namely, the Channel Word format, the two Process Word formats and the Copy Mode Process Word format.

# Addressable Registers

# Channel Service Register

The Channel Service Register enables a channel requiring assignment of new storage space to identify itself to the Channel Service Program. This register has seven bit positions to hold the channel address. When Channel Service is obtained during a Character Interrupt or a Scan Cycle, the Channel Service Register is automatically set with the channel address.

During the execution of Storage-to-Storage instructions while in the Channel Service Mode, the 7750 transfers the contents of the Channel Service Register to the Control Storage Address Register to address Control Storage. This transfer is automatically done on the Second Process Cycle of a two cycle instruction which refers to the Control Storage while the machine is in Channel Service Mode.

#### Interface Data Register

The Interface Data Register is a nine-bit position register (eight bits plus one parity bit) which enables the 7750 to communicate with a computer. This register may be automatically loaded or its content stored under program control. It may also be loaded or its content automatically stored when data is transferred to or from the associated computer.

#### Interface Control Register

The Interface Control Register, an eight-bit register (Figure 6), controls the data flow between the IBM 7750 and the associated computer. This register may be loaded, its content stored or modified under program control. Most of these bits may be set or reset automatically when the 7750 is transferring data to or from the associated computer.

# Mode Request Register

The Mode Request Register is a five-bit register which holds requests for priority program service (Figure 7). The 7750 requests a mode by setting the bit associated with that mode in the Mode Request Register to a logical One. A mode's priority depends on the position of its associated bit in the Mode Request Register. If more than one modes are requested in the Mode Request Register, the 7750 will always select the highest mode first. If no mode is requested in the Mode Request Register, the 7750 will execute the Normal Mode program.

#### TIMING

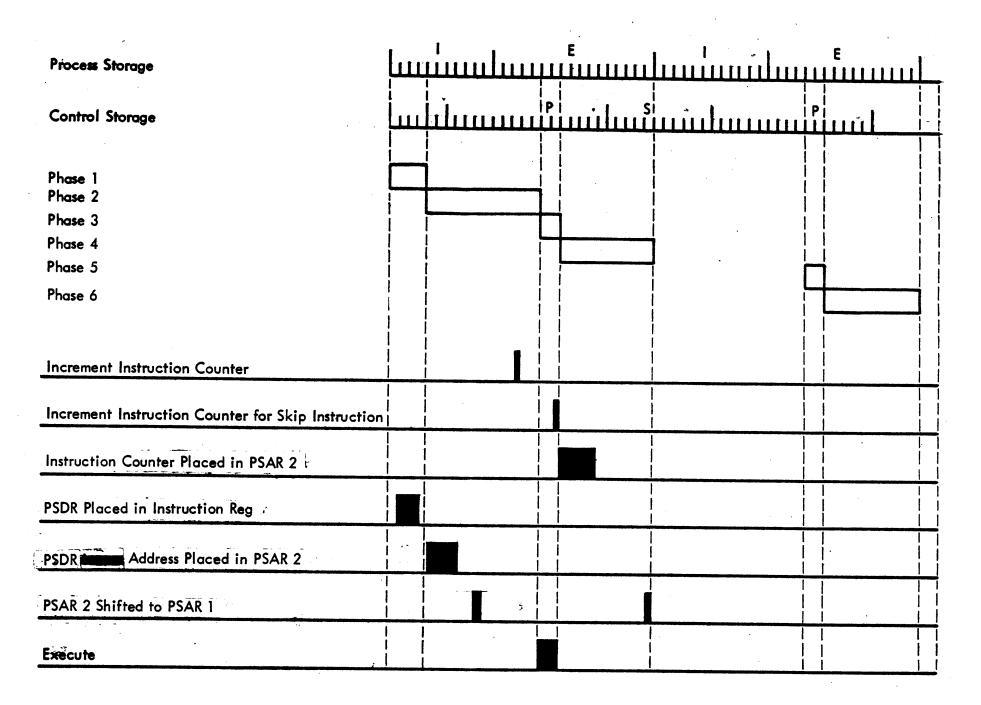

The basic machine cycle of the 7750 is 28 microseconds. Most 7750 instructions are one-cycle instructions. Two-cycle instructions, which require 56 microseconds for execution, are the instructions used for indirect addressing, with the exception of branch indirect, and storage-to-storage data manipulations.

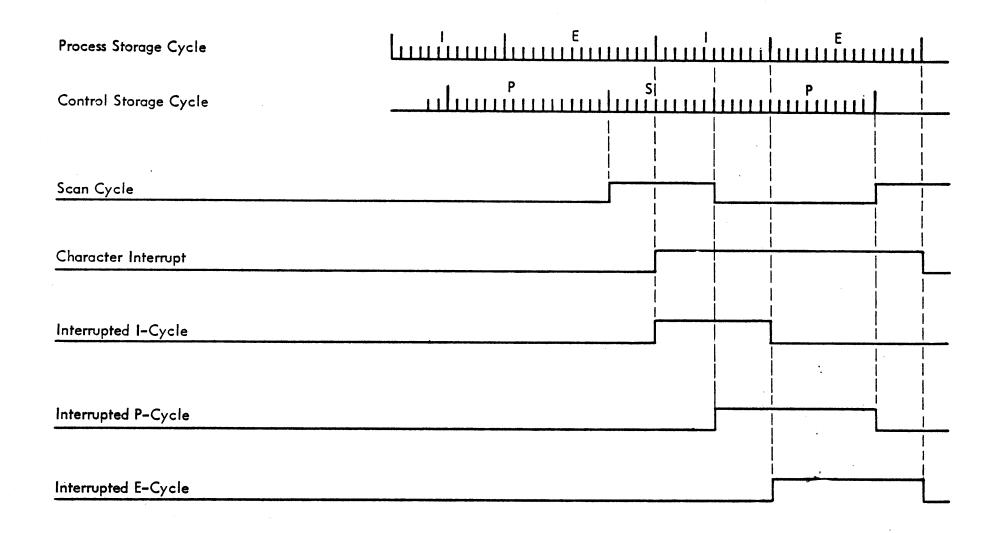

For Control Storage operations, the basic machine cycle is divided into two storage cycles, scan and process, which are 11 microseconds and 17 microseconds long, respectively. During 7750 operation, the Control Storage goes through alternate cycles during which it:

- 1. Services one of the channels, assembling bits until a character has been accumulated, or sending bits until a complete character has been sent.

- 2. Provides the operational registers for the process storage to execute the instructions.

For Process Storige operations, the basic machine cycle is also divided into two cycles. These two cycles, the Instruction cycle and the Execute cycle, alternate and are 12 and 16 microseconds long, respectively. During an Instruction cycle, the 7750 obtains an instruction; during the execute cycle, it executes the instruction.

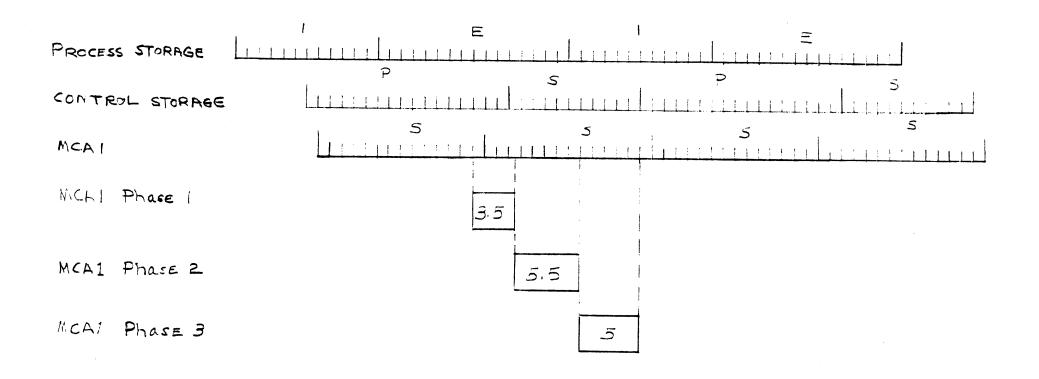

The Control Storage and the Process Storage cycles overlap, allowing the information of either cycle of either storage to influence the operation of the other. In one machine cycle the Process Storage goes through an Instruction cycle and an Execute cycle while the Control Storage goes through a Scan cycle and a Process Cycle. The Process cycle of the Control Storage, being 17 microseconds long, overlaps the Instruction and Execute cycles of the Process Storage.

| Load | Attention | Control | Sense | Stop | End | Unusual<br>End | End<br>Response |

|------|-----------|---------|-------|------|-----|----------------|-----------------|

| 8    | 7         | 6       | 5     | 4    | 3   | 2              | 1               |

# FIGURE 6 INTERFACE CONTROL REGISTER

In Out Copy Channel Service Service

**Increasing Priority**

FIGURE 7 MODE REQUEST REGISTER

#### Clock Phases

The 7750 clock is composed of a 28 stage ring driven at a one megacycle rate. The clock cycles are divided into six phases, as shown in Figure 8. Four phases are used for single cycle instructions, and all six are used for two-cycle instructions. During phase one, the 7750 brings out an instruction from Process Storage, places it in the Instruction Register, and decodes it. During phase 2, the address contained in the Instruction Word is placed in PSAR #2. Later in phase two, if there is no address modification, the address in PSAR #2 is transferred to PSAR #1 to address the Process Storage at the beginning of the Execute Cycle. If there is address modification, the eleven low order bits of the address are modified as the address is transferred from PSAR #2 to PSAR #1. The location and length of the modifier is given by the M and L fields of the Instruction Word, Modification is accomplished by replacing the L low order bits of the address with L low order bits from the register specified by the M field. The modified address is used to address the Process Storage at the beginning of the Execute cycle. During a Branch on Zero or a Branch on Ones instruction, address modification cannot take place. This is because phase 2 is used to test S low order bits of Register R for zero or ones to determine if the branch takes place rather than used for address modification. The uses of phase 3 through phase 6 are determined by the types of instruction being executed.

# One-Cycle Instructions

During phase one, the 7750 brings out an instruction from Process Storage, places this instruction in the Instruction Register and decodes it (Figure 8). At the beginning of the phase 2, the address contained in this instruction is placed in PS AR #2, then moved into PS AR #1 for addressing Process Storage. At the end of phase two, the instruction counter is incremented to address the next instruction at the beginning of the next machine cycle. If the instruction being executed is a skip type instruction, the instruction counter will be incremented again in phase 3. The use of the remainder of phase 3 and phase 4 depends on the type of one-cycle instructions to be executed.

#### **Branch Instructions**

At the beginning of phase 2 of a non-indirect branch type instruction, the Address contained in the Process Storage Data Register is not moved to PSAR #2. Therefore, the Process Storage Address is not addressed during this phase. In phase 3, this Address is placed in the Instruction Counter of the Process Word contained in the Control Storage Data Register. During phase 4, the Instruction Counter is put in PSAR #2 and later moved to PSAR #1 to address Process Storage. At some time in phase 4, the Instruction Word is read back into Process Storage and the Process Word is read back into Control Storage.

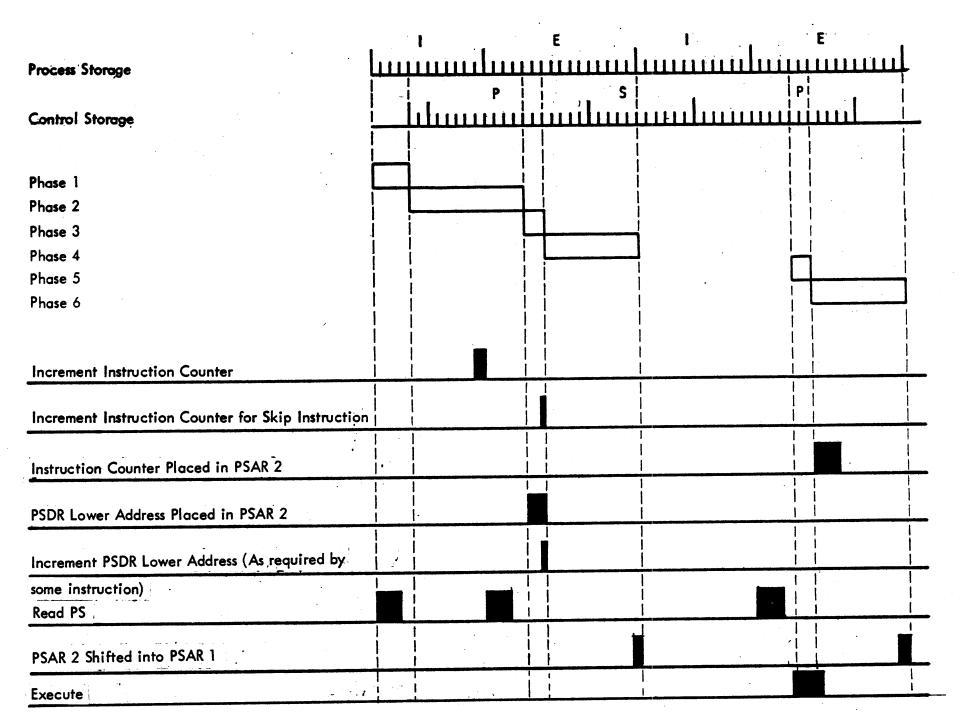

At the beginning of phase 2 (Figure 9) of an indirect branch type instruction, the address contained in the Process Storage Data Register is placed to PSAR #2. This Address is then shifted from PSAR #2 to PSAR #1. The remaining part of the cycle is used in the same manner as described above for non-indirect branch type instructions.

# Compare Address to Limit

During phase 3 of this type of instruction, the Limit of the Process Storage Data Register is compared with the address. If they are identical, the 7750 takes the next instruction in sequence. If they do not compare, the Address is incremented. During phase 4, the Instruction Counter is placed in PSAR #2 and the data registers are stored.

# Character and Address Moving Instructions

During phase 3 of a character or address moving instruction, the character or address is placed in the proper register such as the OAR or the PSDR. At the beginning of phase 4, the Instruction Counter is placed in PSAR #2 and the data registers are stored.

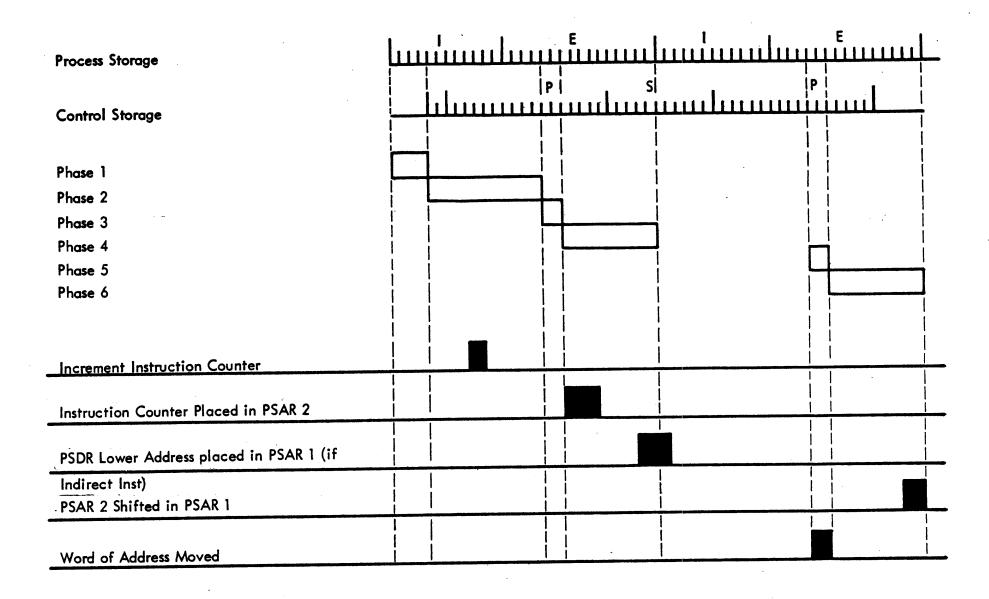

# Two-Cycle Instructions

Some instructions require more than two Process Storage cycles for execution. Phases 1 and 2 of these instructions are the same as those for one-cycle instructions and are explained in Section 4.2. Phases 3 through 6 depend on the specific instruction.

Indirect and Branch Indirect Instructions (Except Storage-to-Storage Instructions)

During phase 3 of an indirect type instruction (Figure 9), the Address in the PSDR is placed into the Process Storage Address Register 2. During phase 4, the Address is incremented, if specified in the instruction, and the content of the PSDR is read back into Process Storage. Just prior to phase 5, Process Storage is read using the indirect address. During phase 5, the instruction is executed. Phase 5 of an indirect instruction is similar to phase 3 of a non-indirect instruction. During phase 6, the Instruction Counter is placed in PSAR #2, the data registers are stored and PSAR #2 is shifted to address the next instruction.

# Storage-to-Storage Instructions

Phase 3 of a Storage-to-Storage Instruction is idle (Figure 10). The Instruction Counter is placed in PSAR #2 during phase 4, since it will not be available from the CSDR for use during phase 6. If the instruction is indirect, the Address of the Process Storage Data Register is placed in PSAR #1 at the end of phase 4. Since Process Storage has been written at this time, it is too late to increment the Address. Therefore, there can be no indirect and increment Storage-to-Storage Instructions. The appropriate\* Control Storage Word is read out for the second Process Cycle prior to phase 5. During phase 5, the address or word specified by the instruction is moved from

<sup>\*</sup>In modes other than Channel Service, the word is addressed by the 7-bit R and S field of the instruction. In Channel Service Mode, it is the word addressed by the Channel Service Register.

FIGURE / O STORAGE INSTRUCTIONS

one storage to another. During phase 6, the data registers are stored. The Instruction Counter in PSAR #2 (placed there during phase 4) is put into PSAR #1 to address the next instruction.

#### **INSTRUCTIONS**

All 7750 instructions belong to one of four types:

- 1. Character Manipulating Instructions CH

- 2. Address and Limit Moving Instructions AL

- 3. Storage-to-Storage Data Transfer Instructions SS

- 4. Control Instructions CT

# Addressing

The IBM 7750 is a single address machine. Each instruction contains one address for addressing storage. However, the addressing format of this machine includes address modification and indirect addressing.

#### Instruction Word Address - W

All 7750 instructions contain a 16-bit address (W) in bit positions 47 to 32. For direct, unmodified Character Manipulating Instructions, W is the location in Process Storage of one of the characters to be manipulated. In the execution of the other three types of direct, unmodified instructions, the 14 high order bits (47-34) address the word to be used in the execution of the instruction. The 2 low order bits of the 16-bit address are not used because these instructions deal with words in storage rather than characters. With Character Moving Instructions, however, both the word and the specific character (0, 1, 2, or 3) within the word must be specified. Therefore the complete 16-bit address must be used.

#### Address Modification

With the exception of all branch instructions other than Branch Indirect, the Address W of any instruction may be modified by specifying a non-zero value for the L field of the Instruction Word. If L is zero, no modification takes place. If L is non-zero, the M field (bits 20-18) specifies the register containing the modifier and L is a binary number specifying the number of bits of the modifier to be used, counting from the low order end of the specified register. L cannot be larger than eleven. The effective Address  $W_e$  is formed in the PSAR #1 by replacing the low order L bits of W by the low order L bits of the modifier in the register specified by M. The Address W is read back into storage as W rather than  $W_e$  because the read-back process was done before address modification. Table B-1 lists the value of M and the register each value specifies.

#### Indirect Addressing

In executing directly addressed instructions,  $W_e$  is the location of one of the operands. When an execution is executed indirectly, the operand is located at  $W^*$ , and  $W^*$  is the Address (bits 47 through 32) contained in the word addressed by  $W_e$ .

Register Addressing - R, S, and OAR

All Character Manipulating Instructions deal with two character locations, one in Process Storage specified by  $W_e$  or  $W^*$  and the other a register specified by R (bits 29-27). S (bits 26-23) is a binary number specifying the size of the character to be operated on, counting from the low order bit of the register specified by R. In Character Manipulating Instructions, S cannot be larger than eleven. Table B-1 lists the values of R and the registers each value specifies.

Address and Limit Moving Instructions must specify the 16 bit Operational Address Register as one of their operands because the other registers are too small to accommodate the Address or Limit. The OAR is composed of the Y register and 5 low order bits of the X register. When an address or limit is moved into the OAR, the 5 low order bits of the address or limit go to the 5 low order bit positions of the X register and the 11 high order bits of the address or limit go to the Y register.

#### Control Storage Addressing

Storage-to-Storage Instructions deal with two word locations: one in Process Storage, specified by We or W\*, and one in Control Storage, specified by R and S in all Modes except Channel Service. In Channel Service Mode, Storage-to-Storage instructions are executed using the contents of the Channel Service Register to address Control Storage.

TABLE B-1 - ADDRESSABLE REGISTERS

| R   | M   | Registers         |

|-----|-----|-------------------|

| 000 | 000 | No register       |

| 001 | 001 | X                 |

| 010 | 010 | $\mathbf{Y}$      |

| 011 | 011 | ${f z}$           |

| 100 | 100 | Channel Service   |

| 101 | 101 | Interface Data    |

| 110 | 110 | Interface Control |

| 111 | 111 | Mode Request      |

|     |     |                   |

# Address Incrementing

If the last alphabetic code character of an operation code mnemonic is an I,  $W^*$  will be incremented after its use. Address incrementing may occur whether or not  $W^*$  is used as an indirect address. Incrementing starts with bit 32 of the word addressed by  $W_e$  (bit 1 of  $W^*$ ).

Indirect Addressing With Incrementing - Skip

All 7750 instructions whose mnemonic codes end in I\* are skip instructions. If, after incrementing, bits 5-1 of W\* are all Ones, the IBM 7750 executes the next instruction in sequence. Ones in bit positions 5-1 mean—that the 7750 has reached the last character position of a block. To proceed any further, the 7750 must locate a new block of characters when it is receiving data or a new empty block when it is transmitting data. Therefore the next instruction in sequence is a Branch instruction which enables the 7750 to enter the subroutine for locating the next block of characters to be sent out or the next empty block to be filled.

If bits 5-1 of W\* are not all Ones after incrementing, indicating that the last (32nd) character position of the block has not been reached, the 7750 skips the Branch instruction and executes the instruction following.

#### Flags

Bits 12 and 13 of an Instruction Word are Flag bits. Any combination of these two Flag bits may be used in an instruction. If bits 12 is a One, the Z register is decremented by one between the address modification and execution times of the instruction. If bit 13 is a One, no mode change can take place between the execution of the instruction containing this Flag bit and the next instruction executed.

#### Operation Code

Bit 10 through 1 of the Instruction Word is the Operation Code. It specifies what instruction the 7750 is to do. Bit 11 is the odd parity bit for bits 10 through 1 and the Flat bits.

#### DESCRIPTION OF INSTRUCTIONS

The instruction descriptions are arranged as follows in the text:

Instruction Name:

Load Character Indirect

Example:

2 LOD\* W 1312

2

LOD\*

W

1302

Execution length in

cycles (28

Mnemonic

Op Code

\*Indirect

Direct Unmodified or Modified Octal Op Code, Not Incl. Parity

or Flags

Address

Address

NOTE: Unless stated otherwise, all instructions may be executed using  $W_e = W$  modified by M and L. In all cases where modification is allowed, any of the registers in Table B-1, including no register, may be used.

# Character Operations

None of the instructions in this group may be used to alter bits 1 through 7 of the Channel Service Register. Specifying R=4 on a Load Instruction will reset the error indicators (CSR 8-11), but will not change the test of the CSR. All instructions whose mnemonic begins with X must specify R=1, the X Register. None of the instructions whose mnemonic begins with A can specify R=5, the Interface Data Register.

#### Load Character

#### 1 LOD W 1302

All bits of register R are cleared and the lower S bits are replaced by the corresponding bits of the character addressed by  $W_{e^{\bullet}}$  The contents of storage are unchanged.

# Load Character Indirect

2 LOD\* W 1312

Same as LOD with indirect addressing.

# Load Character and Increment

1 LOI W 1322

Same as LOD with increment.

#### Load Character Indirect and Increment

2 LOI\* W 1332

Same as LOD with indirect and increment.

# Load Complemented Character

1 LDC W 1342

All bits of register R are cleared and the lower S bits are replaced by the One's complement of the corresponding bits of the character addressed by  $W_e$ . The contents of storage are unchanged.

# Load Complemented Character Indirect

2 LDC\* W 1352

Same as LDC with indirect addressing.

# Load Complemented Character and Increment

1 LCI W 1362

Same as LDC with increment.

# Load Complemented Character Indirect and Increment

2 LCI\* W 1372

Same as LDC with indirect and increment.

# **Unload Character**

1 UNL W 1202

All 11 bits of the character addressed by  $W_e$  are cleared and the S low order bits are replaced by the corresponding bits of register  $R_{\bullet}$ . The contents of R are unchanged.

# Unload Character Indirect

2 UNL\* W 1212

Same as UNL with indirect addressing.

# Unload Character Indirect and Increment

2 ULI\* W 1232

Same as UNL with indirect addressing and increment.

# Unload Complemented Character

1 ULC W 1242

All 11 bits of the character addressed by  $W_{\rm e}$  are cleared and the lower S bits are replaced by the One's complement of the corresponding bits of register R. The contents of R are unchanged.

# Unload Complemented Character Indirect

2 ULC\* W 1252

Same as ULC with indirect addressing.

# Unload Complemented Character Indirect and Increment

2 UCI\* W 1272

Same as ULC with indirect addressing and increment.

# Exclusive OR

1 X OR W 1101

The S low order bits of register X are EXCLUSIVE - OR'ed, bit by bit, with the corresponding bits of the character addressed by  $W_e$ . The results replace the S low order bits of X. The contents of storage and the 11 minus S high order bits of X are unchanged. The result of an EXCLUSIVE - OR between two bits is a One when the two bits differ (10 or 01) and a Zero when they are the same (11 or 00).

# **Exclusive OR Indirect**

2 X OR\* W 1111

Same as X OR with indirect addressing.

# **Exclusive OR and Increment**

1 XOI W 1121

Same as XOR with increment.

#### Exclusive OR Indirect and Increment

2 XOI\* W 1131

Same as XOR with indirect addressing and increment.

# **Exclusive OR Complemented**

1 XOC W 1141

The S low order bits of register X are EXCLUSIVE - OR'ed, bit by bit, with the One's complement of the corresponding bits of the character addressed by We. The results replace the S low order bits of X. The contents of storage and 11 minus S high order bits of X are unchanged.

# **Exclusive OR Complemented Indirect**

2 XOC\* W 1151

Same as XOC with indirect addressing.

# Exclusive OR Complemented and Increment

1 XCI W 1161

Same as XOC with increment.

# Exclusive OR Complemented Indirect and Increment

2 XCI\* W 1171

Same as XOC with indirect addressing and increment.

# Inclusive OR

1 IOR W 1102

The S low order bits of register R are OR'ed bit by bit with the corresponding bits of the character addressed by W<sub>e</sub>. The results replace the S low order bits of R. The contents of storage and the 11 minus S high order bits of R are unchanged. The results of an OR between two bits is a One when either or both of the bits are Ones (11, 10, 01) and a Zero when they are both Zeros (00).

#### Inclusive OR Indirect

2 IOR\* W 1112

Same as IOR with indirect addressing.

#### Inclusive OR and Increment

1 IOI W 1122

Same as IOR with increment.

# Inclusive OR Indirect and Increment

2 IOI\* W 1132

Same as IOR with indirect addressing and increment.

# Inclusive OR Complemented

1 IOC W 1142

The S low order bits of register R are OR'ed, bit bi bit, with the One's complement of the corresponding bits of the character addressed by We. The results replace the S low order bits of R. The contents of storage and the 11 minus S high order bits of R are unchanged.

# Inclusive OR Complemented Indirect

2 IOC\* W 1152

Same as IOC with indirect addressing.

# Inclusive OR Complemented and Increment

1 ICI W 1162

Same as IOC with increment.

# Inclusive OR Complemented Indirect and Increment

2 ICI\* W 1172

Same as IOC with indirect addressing and increment.

#### OR to Process Storage

1 ORP W 1002

The S low order bits of the register R are OR'ed, bit by bit, with the corresponding bits of the character addressed by  $W_e$ . The results replace the S low order bits of the character in storage. The contents of R and the 11 minus S high order bits of the character in storage are unchanged.

# OR to Process Storage Indirect

2 ORP\* W 1012

Same as ORP with indirect addressing.

## OR to Process Storage Indirect and Increment

2 ORI\* W 1032

Same as ORP with indirect addressing and increment.

## OR Complement to Process Storage

1 OCP W 1042

The One's complements of the S low order bits of the register R are OR'ed, bit by bit, with the corresponding bits of the character addressed by  $W_e$ . The results replace the S low order bits of the character in storage. The contents of R and the 11 minus S high order bits of the character in storage are unchanged.

#### OR Complement to Process Storage Indirect

2 OCP\* W 1052

Same as OCP with indirect addressing.

## OR Complement to Process Storage Indirect and Increment

2 OCI\* W 1072

Same as OCP with indirect addressing and increment.

## AND

1 AND W 1145

The S low order bits of the register R and AND'ed bit by bit with the corresponding bits of the character addressed by  $W_e$ . The results replace the S low order bits of R. The contents of storage and the 11 minus S high order bits of R are unchanged. The result of an AND between two bits is a One when both bits are One's (11) and a Zero otherwise (10, 01, 00).

#### AND Indirect

2 AND\* W 1155

Same as AND with indirect addressing.

#### AND and Increment

1 ANI W 1165

Same as AND with increment.

## AND Indirect and Increment

2 ANI\* W 1175

Same as AND with indirect addressing and increment.

## AND Complemented

1 ANC W 1105

The S low order bits of register R are AND'ed, bit by bit, with the One's complement of the corresponding bits of the character addressed by  $W_e$ . The results replace the S low order bits of R. The contents of storage and the 11 minus S high order bits of R are unchanged.

# AND Complemented Indirect

2 ANC\* W 1115

Same as AND with indirect addressing.

# AND Complemented and Increment

1 ACI W 1125

Same as ANC with increment.

# AND Complemented Indirect and Increment

2 ACI\* W 1135

Same as ANC with indirect.

Address and Limit Moving Operations

#### **Get Address**

1 GTA W 0702

The Operational Address Register (OAR) is cleared, then loaded with the Address in the word addressed by  $W_e$ . The contents of storage are unchanged as are the 2 high order bits (10 and 11) of register S. Bits 9-6 of the X register are cleared.

#### Get Address Indirect

2 GTA\* W 0712

Same as GTA with indirect addressing.

Get Limit

1 GTL W 0302

The OAR is cleared, then loaded with the Limit in the word addressed by  $W_e$ . The contents of storage are unchanged, as are the 2 high order bits of register  $X_{\bullet}$  Bits 9-6 of the X register are cleared.

#### Get Limit Indirect

2 GTL\* W 0312

Same as GTL with indirect addressing.

## Get and OR Address

1 GOA W 0502

The contents of the OAR is inclusive OR'ed into the OAR with the corresponding bits of the Address in the word addressed by  $W_e$ . The word in the Process Storage Location addressed by  $W_e$  is unchanged.

#### Get and OR Address Indirect

2 GOA\* W 0512

Same as GOA with indirect addressing.

## Get and OR Limit

1 GOL 0102

The contents of the OAR is inclusive OR'ed into the OAR with the corresponding bits of the Limit in the word addressed by  $W_e$ . The word in the Process Storage location addressed by  $W_e$  is unchanged.

# Get and OR Limit Indirect

2 GOL\* W 0112

Same as GOL with indirect addressing.

# Put Address

1 PTA W 0602

The Address field (bits 47 through 32) in the word addressed by  $W_e$  is cleared, then loaded with the contents of the OAR. The OAR is unchanged.

# Put Address Indirect

2 PTA\* W 0612

Same as PTA with indirect addressing.

#### Put Limit

1 PTL W 0202

The Limit field (bits 27 through 12) in the word addressed by  $W_{\rm e}$  is cleared, then loaded with the contents of the OAR. The OAR is unchanged.

# Put Limit Indirect

2 PTL\* W 0212

Same as PTL with indirect addressing.

Storage-to-Storage Data Moving Operations

See paragraph on Control Storage Addressing.

# Transmit Address to Process Storage

2 TAP W 0606

The Address field in the word addressed by W<sub>e</sub> is cleared, then loaded with the Address from the Control Storage word referenced. Control Storage is unchanged.

# Transmit Address to Process Storage Indirect

2 TAP\* W 0616

Same as TAP with indirect addressing.

# Transmit Address to Control Storage

2 TAC W 0706

The Address field (bits 47 through 32) of the Control Storage word referenced is cleared, then loaded with the Address in the word addressed by We. Process Storage is unchanged.

# Transmit Address to Control Storage Indirect

Same as TAC with indirect addressing.

## Transmit and OR Address to Control Storage

2 TOC W 0506

The Address field (bits 47-32) of the Control Storage Word referenced in inclusive OR'ed into itself with the Address field of the word addressed by  $W_e$ . The word in Process Storage location addressed by  $W_e$  is unchanged.

# Transmit and OR Address to Control Storage Indirect

2 TOC\* W 0516

Same as TOC with indirect addressing.

# Move Word to Process Storage

2 MWP W 0206

The word addressed by  $W_e$  is replaced by the Control Storage word referenced. Control Storage is unchanged.

#### Move Word to Process Storage Indirect

2 MWP\* W 0216

Same as MWP with indirect addressing.

# Move Word to Control Storage

2 MWC W 0306

The Control Storage word referenced is replaced by the Process Storage word addressed by  $W_{e^{\bullet}}$  Process Storage is unchanged.

# Move Word to Control Storage Indirect

2 MCW\* W 0316

Same as MWC with indirect addressing.

# Move Word and OR to Control Storage

2 MOC W 0106

The contents of the Control Storage word referenced is inclusive OR'ed into the Control Storage word referenced with the contents of the Process Storage word addressed by  $W_e$ . The word at the Process Storage location addressed by  $W_e$  is unchanged.

# Move Word and OR to Control Storage Indirect

2 MOC\* W 0116

Same as MOC with indirect addressing.

# **Control Operations**

Branch type instructions other than Branch Indirect cannot have their addresses modified by M and L.

#### Branch

1 BRA W 0707

This instruction causes the 7750 to take its next instruction from word location W and to proceed from there.

#### Branch Indirect

1 BRA\* W 0717

This instruction causes the IBM 7750 to take its next instruction from word location  $W^*$  and to proceed from there.  $W^*$  is the Address at word location  $W_e = W$  modified by M, L. See paragraph on Indirect Addressing.

# Branch on Zero

1 BRZ W 0704

If the S low order bits of register R are all Zero, the 7750 takes its next instruction from word location W and preceeds from there. Otherwise, it takes the next instruction in sequence. R is unchanged.

## Branch on Zero Indirect

1 BRZ\* W 0714

See BRA\* and BRZ.

#### Branch on Ones

1 BRO W 0744

If the S low order bits of register R are all One, the 7750 takes its next instruction from word location W and proceeds from there. Otherwise, it takes the next instruction in sequence. R is unchanged.

# Branch on Ones Indirect

2 BRO\* W 0754

See BRA\* and BRO

## Branch on Test

1 BRT 0544

The contents of positions 33 through 23 of the Instruction Word are inclusive OR'ed with the contents of the register specified by the M field of the Instruction Word. If the result is all Ones, the next instruction will be taken from the location specified in the Address field (bits 47-34) of the BRT Instruction Word. If the result is not all Ones, the 7750 executes the next instruction in sequence. The contents of the Instruction Word and of the register specified by M are unchanged.

# Compare Address to Limit

1 CAL W 0003

If the Address and Limit fields of the word addressed by  $W_e$  are identical, the 7750 takes the next instruction in sequence. If they are not identical, the 7750 skips the next instruction and proceeds from there. Storage is unchanged.

# Compare Address to Limit and Increment

1 CAI W 0023

Same as CAL with increment.

#### Sense

#### 1 SNS W 0000

The sense line as specified by the M field, (1 to 5)<sub>8</sub>, is raised for 20 microseconds. This instruction is used for diagnostic purposes only.

#### PRIORITY PROCESSING

When the IBM 7750 is executing a program, the sequence of its operation is controlled by the Instruction Counter. Since the Instruction Counter is not an actual register but is a field stored in a Control Storage Process Word, a change in the sequence of operation can be accomplished by accessing a different Process Word, and thereby a different Instruction Counter. In the 7750, priority processing is accomplished by the use of six such Process Words. Each Process Word has a preassigned priority. The choice of a specific Process Word is based on external conditions.

The 7750 is in a particular mode when its sequence of operation is under the control of the Process Word associated with that Mode. A Mode is requested by the setting of its associated trigger in the Mode Request Register, except for the Normal Mode, which is always requested although it has no trigger. In all Modes except Copy Mode, the 7750 operates as described in Section 4. The operation in Copy Mode is described in Section on Transmission Between the 7750 and the Computer. Table 1 gives the priority, MRR position and Control Storage address of each mode.

|                 | TAB      | LE 1 |                            |

|-----------------|----------|------|----------------------------|

| Mode            | Priority | MRR  | Control Storage<br>Address |

| Service         | 1        | 1    | 378                        |

| Channel Service | 2        | 2    | $77_8^{\circ}$             |

| Copy            | 3        | 3    | 1378                       |

| OUT*            | 4        | 4    | $136_8$                    |

| IN*             | 5        | 5    | 1768                       |

| Normal          | 6        | None | 1778                       |

<sup>\*</sup>The IN and OUT Modes correspond to the Write and Read operations. They refer to the data transmission relative to the IBM 7750.

#### Service Mode

The Service Mode has highest priority. In most cases, this mode is used for detecting environmental errors, and the request of this mode is automatic through channel words. In addition, the Service Mode, together with the Service Mode program, may be used to: (1) isolate or remove mistakes from a program (debugging); (2) locate a faulty

component (diagnosing); and (3) obtain a programmed output of error messages when a machine malfunction occurs. Service mode may be entered manually from the operator's panel, automatically on the occurrence of an error condition, or by program. The 7750 program must enable the machine to leave this mode.

#### Channel Service Mode

Channel Service Mode has second priority. This mode causes the execution of the program that assigns blocks to receiving and transmitting communication channels. Channel Service Request is set automatically when any communication channels need it, and turned off by the program.

#### Copy Mode

Copy Mode has third priority and is requested by the program of some other mode. When this mode is operative, data are automatically moved to or from the associated computer. Copy mode is not a program executing mode but is given a mode position because its function ranks in priority above all but Service Mode and Channel Service Mode.

#### Out Mode

Out Mode has fourth priority. Its mode program executes the necessary instructions to set up the Copy Mode process word and prepares the 7750 to transmit data to the computer. The Out mode request bit is normally turned on by the program of the associated computer and is turned off by the IBM 7750 program. This mode may also be requested by the 7750 program.

#### In Mode

In Mode has fifth priority. It is requested by action of the associated computer when the computer wants the 7750 to accept data from it. The program written for this mode locates space for the data, sets up copy mode process word to read the data into this area, and requests copy mode. The In mode request bit is normally turned on by the program of the associated computer and is turned off by the IBM 7750 program.

#### Normal Mode

Normal Mode has lowest priority. It causes the execution of the normal program which performs error checking, code translation, recognition of functional codes, monitoring, queuing, and so on. All 7750 functions not specifically delegated to other modes usually are executed by the Normal Mode program.

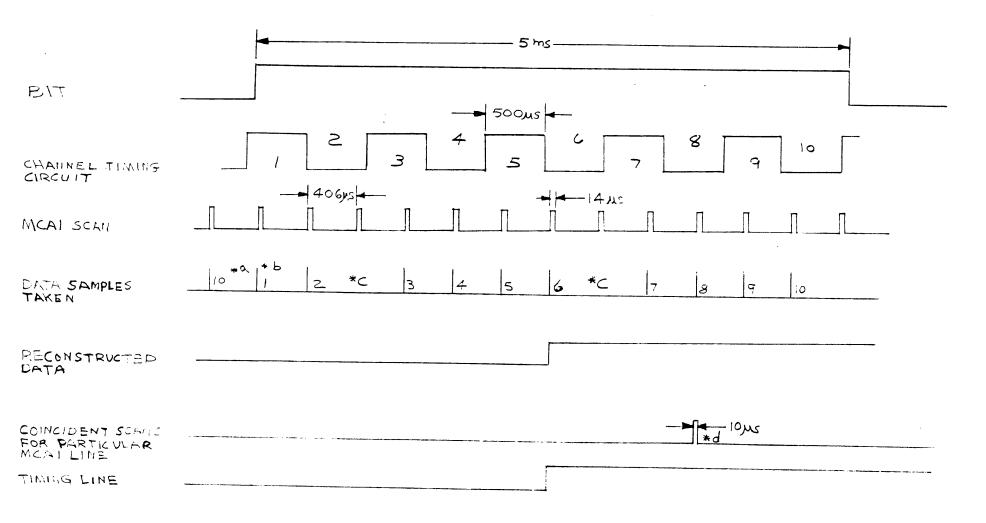

#### Mode Selector System