#### IBM CONFIDENTIAL

Memorandum to: Recipients of Advanced Future System (AFS) Proposal

Subject: Poughkeepsie AFS Proposal

Enclosed is a copy of the present draft of our proposal for AFS architecture. Though a great deal of progress has been made, this is a report on progress and not a final report. In one sense the ideal approach would have been to let the two principal authors of the conceptual work, Steve Zilles and John Sowa, proceed to the production of a complete document stating a consistent set of fundamental concepts with absolute academic purity. Then others could propose and describe practical implementations. Such an approach would have two overwhelming flaws:

- 1. The resulting proposal would suffer from a lack of contact with realities of what is required to implement a system, no matter how elegant the document.

- 2. No individual or pair of individuals is fully equipped to deal with all of the diverse disciplines that are part of the design of a full hardware-software system.

Instead, our approach has been to simultaneously develop pragmatic detail and abstract conceptual foundation. This admittedly has resulted in false starts and frequent rethinking of basic issues. The great benefit has been in the testing of concepts and of implementation against the sternest measure of all -- an orthogonal point of view. This approach has resulted in a study which is technically both broad and deep.

The process of synthesis is not yet complete. It has resulted in much change in both points of view. Only when this change has stopped will we consider the proposal complete, consistent, and final.

The two principal parts of our proposal are entitled "Fundamental Concepts and System Language" and "System Architecture". These will be referred to as the SL report and the SA report or as SL and SA. They were prepared simultaneously with related but different points of departure.

The purpose of the System Architecture study was to explore the feasibility of this approach and to discover and solve problems arising during implementation.

Creating a simple, generalized, logical foundation and finding a way to create a system language that can meet the objectives of AFS and to serve as an adequate system control and task management language and as an adequate target language for translators from high level languages was the purpose of the System Language study. The objective of producing a simple, coherent, design with a minimal number of concepts and conventions is primary.

The goal of discovering how to create a high level language that is a suitable target for translators seems within our grasp. Much supporting evidence is contained in this report in the form of definitions of functions which support fundamental language properties. Of particular importance are the functions and definitions that are aimed at supporting language facilities that have not yet been specified but will be important by the time this product reaches the market. More evidence is contained in ASP 051, "Arithmetic Operations in AFSIL".

Representing our case for feasibility is the System Architecture report. There are two aspects. On one hand, we created a simulator that dealt with all the problems associated with the critical parts of PL/I. To do this we couldn't leave any unsolved problems hidden under vague phraseology since the simulator runs. In the SA report are the solutions to problems that are glossed over or even ignored in the SL report. It may be less evident that the advanced approach in SL can be implemented with an extension of the same approach. However, close study of the two reports and discussion with the contributors will I hope convince you, in fact, what we propose can actually be done.

The second major topic of SA is efficiency. We are gratified to find that our intention of creating an efficient system appears to be quite reasonable in view of the performance being predicted through simulator usage.

Reading and understanding this report will be a sizable undertaking. To assist you, key contributors can be made available to present whatever is required.

C. J. Conti

CJC:cpl

DO NOT REPRODUCE - FOR FURTHER COPIES, PLEASE CONTACT C. J. CONTI's OFFICE - EXTENSION 3-2531

#### AFS SYSTEM ARCHITECTURE MANUAL

February 26, 1971

This document contains information of a proprietary nature. All information contained herein shall be kept in confidence. None of this information shall be divulged to persons other than: IBM employees authorized by the nature of their duties to receive such information, or individuals or organizations authorized by the Systems Development Division in accordance with existing policy regarding release of company information.

# TABLE OF CONTENTS

| Table of | Contents 2                                                                                                                                                                                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Foreword |                                                                                                                                                                                                                                                                                                                     |

| CHAPTER  | 1.1 Purpose of the System Architecture Manual (SAM)                                                                                                                                                                                                                                                                 |

|          | 1.2 Principal System Features                                                                                                                                                                                                                                                                                       |

| CHAPTER  | 2 THE LOGICAL MACHINE       12         2.1 Overview       12         2.2 The Program Tree       16         2.3 The Activation Tree       19         2.4 Dynamic Storage       22         2.5 Data Objects and Linking       26         2.6 The Interpreter       35         2.7 Building a Logical Machine       43 |

| CHAPTER  | 3 THE LOGICAL SYSTEM                                                                                                                                                                                                                                                                                                |

| CHAPTER  | 4 THE PHYSICAL SYSTEM  4.1 Control                                                                                                                                                                                                                                                                                  |

| CHAPTER  | 5 MODELING                                                                                                                                                                                                                                                                                                          |

| CHAPTER  | 6 GLOSSARY                                                                                                                                                                                                                                                                                                          |

#### FOREWORD

This document has been prepared as a manual and thus order of presentation is given in reference form. For a reader who is being exposed to the system for the first time, it may be useful to read the document in a different order. The suggested procedure is to first read the Introduction (Chapter 1); then Section 2.1, the Overview of the Logical Machine; then Chapter 3, the Logical System; then Section 4.1, the Control Description of the Physical System. With this preparation, it is hoped that the reader will be able to use the document as intended.

The authors have used several conventions to aid the reader. When a significant term or phrase is introduced for the first time it is underlined. Most terms which are capitalized can be found in the Glossary (Chapter 6).

All readers are invited to submit their commentary on the system and this document. Please contact A. Peacock, Department Bll, SDD Poughkeepsie.

#### CHAPTER 1

#### INTRODUCTION

#### Purpose of the System Architecture Manual (SAM) 1.1

SAM is one of a set of documents prepared by the Advanced Systems Group in Poughkeepsie in response to the AFS requirements and objectives which were issued jointly by Carl Conti (Manager of Advanced Systems, Poughkeepsie) and Al Magdall (Manager of Advanced Systems, Endicott) on January 19, 1971. Two other major documents in this set are the System Language Manual and a subset implementation (described in ASP memos 015, 046, and 049)\*. The relationship of these documents is simply illustrated:

Manual

System Language System Architecture Manual

Models and Design Manuals

A major purpose of SAM, then, is to provide a communication interface between the abstract, analytical, description of the system in the System Language Manual and one or more implementations. A second major purpose of SAM is as a convenient introduction to the system for skilled, but unfamiliar, readers.

It is inevitable, and even desirable, that the early versions of these three document sets are not completely compatible. Some differences, primarily in nomenclature, between the Systems Lanaguage Manual and SAM are discussed in a Glossary of terms (Chapter 6 of this Manual). More serious technical differences are, or will be, discussed in ASP memos. Ultimately, SAM will become, as these differences are resolved, an approved Reference Manual for the system.

Poughkeepsie Advanced System Proposal Department Bll SDD

IBM CONFIDENTIAL

# 1.2 Principal System Features

The novel features of this system are designed to bring about a major improvement in programmer productivity; to make the system easier to use and maintain; and to penetrate new market areas, particularly Data Base Operation.

Central to the heart of the system is the concept of <a href="Data Independence">Data Independence</a>. Specifically, the executable code references data objects by a logical name rather than physical location; the logical descriptions of data objects are maintained with the data values and not with the code; and the physical representations of data objects (both descriptions and values) are not known, implicitly or explicitly, to the executable code. Thus, the operators of the executable code are generic and may be applied to a class of data objects without regard to their current physical representation, or location.

The system has been designed to make possible the faithful support of the major high level languages; in particular COBOL, PL/1, APL, RPG, and FORTRAN. Thus a user of such a language can be provided with a logical machine that appears to him to be directly executing statements in that language. The system will detect all the errors defined in the language and report back to him in terms of his source statements. In light of these errors, he may modify his source text and, where this is meaningful, continue execution from the point of error discovery. As a natural consequence of this mode of operation, the execution unit treats a statement (i.e. a list of operators and operands) as the unit of execution rather than an individual instruction.

The system also features a new <u>System Language</u> which combines the semantic power of the best procedure oriented languages, with the operators necessary to support system programmers in their task of building and maintaining application programs, operating systems and language compilers. Since the necessary operators to build software support are directly supplied in the system language, the language controls and defines the whole system in the same manner that System/360 Principles of Operation controls the mainframe hardware of System/360.

A last important feature of the system is the clean separation of the <a href="Logical">Logical</a> (user-oriented) definition of the system from the physical (implementation-oriented) definition,

with rigorously controlled interfaces between them. makes possible a wide variety of implementations and extensions without jeopardizing the logical foundation.

#### 1.3 System Structure and Principal Components

#### 1.3.1 The Logical Machine

Every user Job is processed in a separate Logical Machine (LM). A Job is a major unit of work in the system. All Jobs are scheduled and run independently; all communication and sychronization between Jobs is the responsibility of the system users, using explicit communication mechanisms provided by the system.

An LM performs processing on behalf of the user by activating one or more Modules which are contained within the Logical Machine in a structure called The Program Tree. Both nested and parallel activation of Modules may occur within the LM, the current activation status being recorded dynamically in The Activation Tree. Connectivity to the current generations of variables used during processing is made by a set of Storage Anchors, one set being provided for each parallel activation.

The active mechanisms within a Logical Machine are called Interpreters. Every parallel activation is supported by a separate Interpreter; implicit communication (through common variables) is possible between Interpreters in the same Logical Machine. The work accomplished by a single Interpreter is called a Logical Task. Thus a Job consists of one or more Logical Tasks, the number of Tasks existing at anytime being identical to the current number of parallel

Explicit communication with the other logical components of the system (i.e. System Facilities, the Logical Machine Supervisor, and the Logical I/O System, is provided by a series of specialized communication modules accessible from the root (System Node) of the Program Tree.

Just below the System Node in the Program Tree is the External Node. The Module at this node is called the External Module and is activated (i.e. supplied with an Interpreter) when the Logical Machine starts a Job. activation includes passing a parameter to specify the source of initial commands for the machine.

THIS IS A STRICTLY PROCEDURE -ORIGINAL activities. DEN OF JOB.

BETTER WORD

#### 1.3.2 The System Facilities

Every Logical Machine has access to a number of special system functions. These capabilities are called System Facilities and include the ability to catalogue data, obey system commands, edit catalogued data, introduce procedures, etc. All of the logical objects in the system (cataloged data structures, Modules, Logical Machines, Logical I/O devices, Logical Users, etc.) are themselves AUTHORIS ATION owned by another logical object. The set of nested WOULD BE A ownership relations is reflected in the Ownership Tree which is maintained by the System Facilities. Access to objects is monitored by System Facilities (this monitoring is automatic since it is only achievable through the communication modules of the LM's) to ensure that the accessor is authorized to access the object and to provide the necessary interlocks required by the type of access (read-only, modify-exclusive, etc.). Many of the leaves and nodes of the ownership tree are themselves complex structures. This fine structure is not directly reflected in the Ownership Tree which resolves only to the detail necessary to provide unique ownership and access rights.

Any object in the Ownership Tree can be created, copied or modified by an active Logical Machine that has the appropriate authorization by using its communication modules. Thus one LM can create, copy, modify or pass messages to another LM. An active Logical Machine can in fact be thought of as a logical object in the Ownership Tree that is in the modify-exclusive state.

#### 1.3.3 The Logical Machine Supervisor

One specialized LM, called the Logical Machine Supervisor, is placed at the root of the Ownership Tree and activated at System Generation time with its External Module connected to an operators console. Other specialized LM's are provided by the systems programmers (i.e., users with the appropriate authorization) to support the normal system functions of translating (i.e. creation of a Module from a Data Object), Logical I/O, Data and Load Module editing, etc.

The principal logical task of the supervisor is to activate Logical Machines (including parametising their External Modules) and to monitor their activities in order to handle exceptional conditions such as job completion. Depending on the type of user activity this may involve providing the user with a new Logical Machine, connecting him to an existing LM or making a fresh copy for him of an existing LM.

anon,

The supervisor also has the important task of communicating with the physical control system to initiate Physical Tasks for either a Program Processing Unit or a Source-Sink Processing Unit. The communication interface between the supervisor and the physical system consists primarily of a set of tables representing the current status of work in the system. The supervisor maintains logical (user-oriented) tables representing the users' Jobs and their subdivision into Logical Tasks (parallel activations within a Logical Machine) which occur upon execution of attach operators in a Logical Machine.

These Logical Tasks are analyzed and monitored by the supervisor which breaks them into one or more Physical Tasks and places them into queue tables for Processing Units to be scheduled by the Physical Control System. A Physical Task includes in its definition the kind of processor required, any physical resource requirements, the priority of execution, and the scheduling discipline (batch, time-shared, etc.).

# 1.3.4 The Logical I/O System

The Logical I/O System is responsible for all transfer of information to and from a Logical Machine. This includes communication with a user, another LM, the System Facilities, Source/Sink devices and other systems. Logical I/O is provided by a series of specialized Modules, which are placed at the System Node of each LM's Program Tree. Thus any LM can obtain Logical I/O by a simple call or an Attach of one of these Modules.

Logical I/O does not necessarily result in the creation of a Physical Task for a Source/Sink Processing Unit. Some requests can be satisfied by the temporary incorporation of an object in the Ownership Tree into a Logical Machine's environment. Others result in copying or creating such an object which can be done as a Physical Task by a Program Processing Unit. Source/Sink Processing Units are, however, required for Source/Sink I/O, user communication, and communication with other systems.

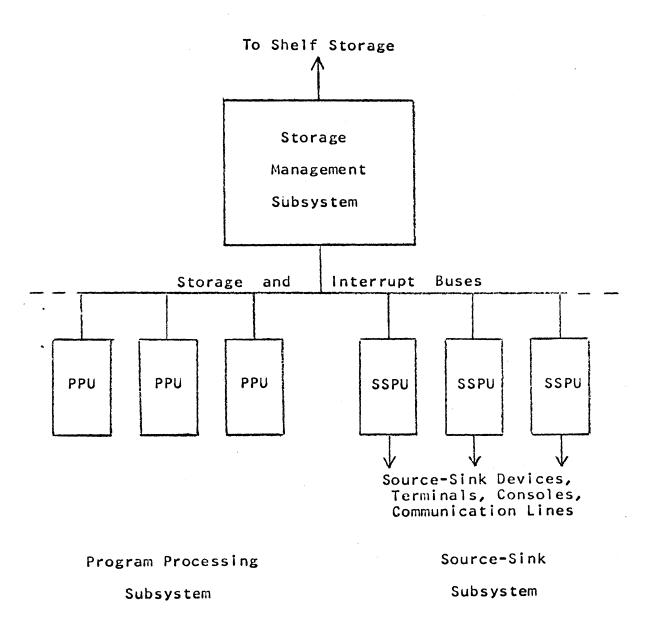

# 1.3.5 The Physical System Control

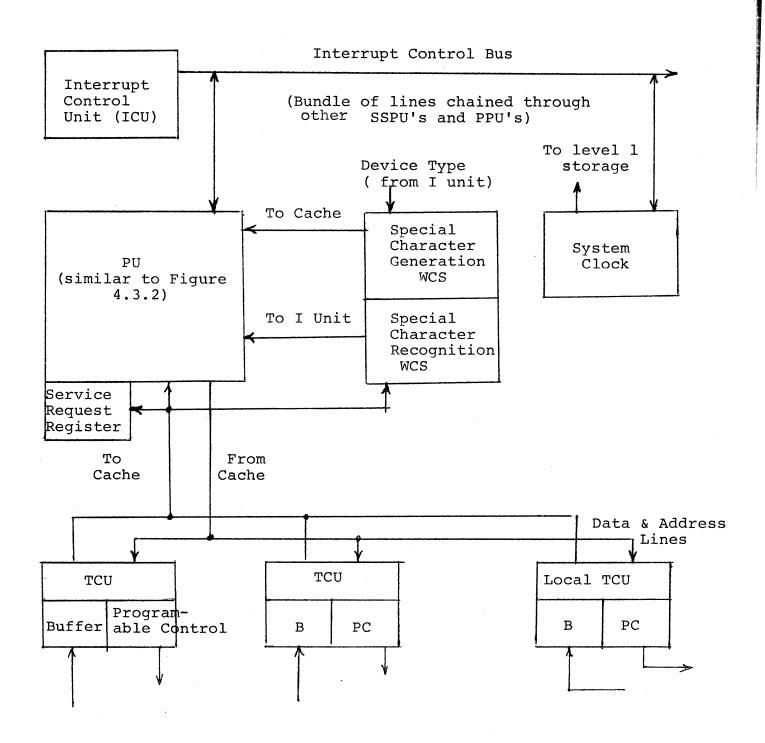

The Physical System, which supports all the structures and activities of the Logical System, consists of three major sub-systems: The Storage Management Subsystem, The Program Processing Subsystem, and The Source/Sink Processing Subsystem. The harmonious cooperation of these sub-systems and their allocation to the Physical Tasks which represent the

activities of the Logical Machines is ensured by a set of hardware and software capabilities known as Control.

Control, at the lowest level, consists of a Storage Bus which enables the Processing Sub-systems to communicate with the storage Sub-system and hence, indirectly, with each other. A minimal direct signalling capability, called the Interrupt Bus, is also provided at this level. At the next level, control consists of a number of task queues in storage (one per processor type) together with the basic operators to build, search, and control access to the queues. Thus processors have the basic ability to transfer tasks to other processors and search for tasks for themselves. At a higher level, control is a high priority Physical Task which is responsible for physical resource allocation and normal and abnormal task termination. Finally, at the highest level, control is a set of physical tasks which constitute the Logical Machine Supervisor.

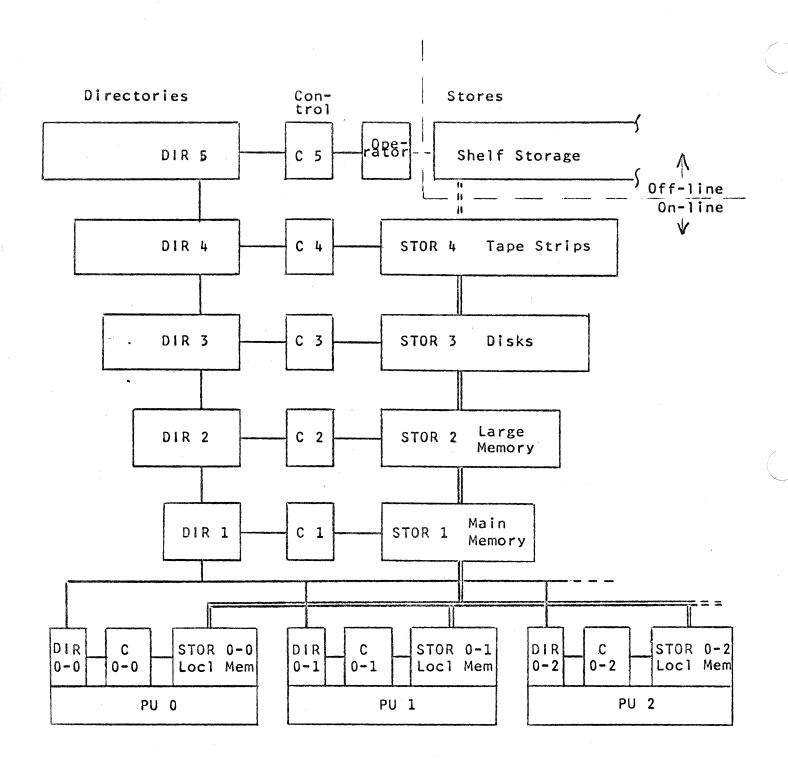

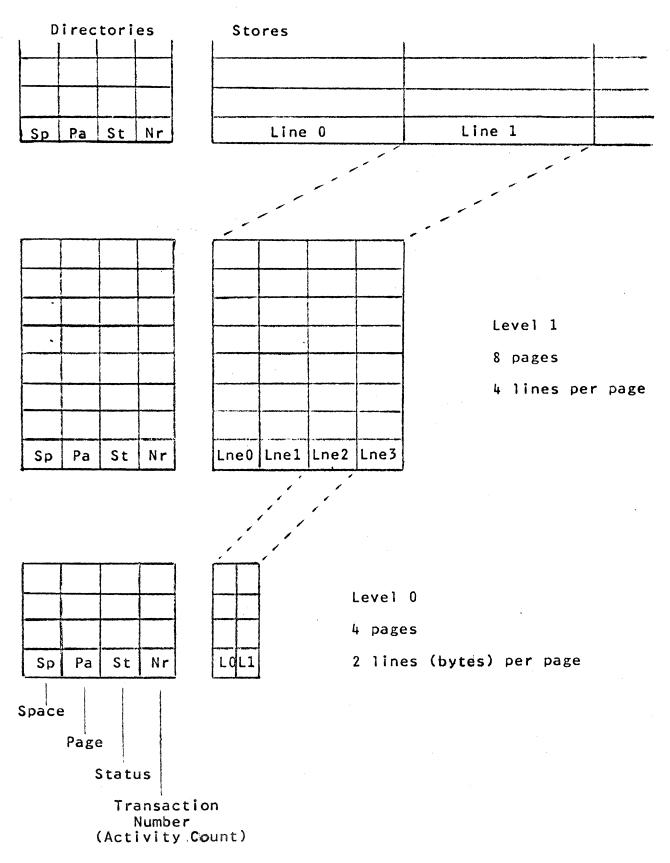

# 1.3.6 The Storage Management Sub-System

The Storage Management Sub-system is an automatic, paging hierarchy of storage devices ranging from the highest speed electronic memory to lower speed electro-mechanical devices and out through operator controlled shelf-storage. It differs from conventional 'virtual memories' in three important respects.

Firstly, rather than one, the system provides a practical infinity of independent linear spaces, each of which can grow or shrink independently. Secondly, the system only manages <u>real</u> spaces (i.e. spaces that contain data) and only to the current physical length of the space. Finally, spaces are created and grow in the page buffers of the highest speed electronic memory so that 'Get Main' is a very fast operation.

#### 1.3.7 The Program Processing Sub-System

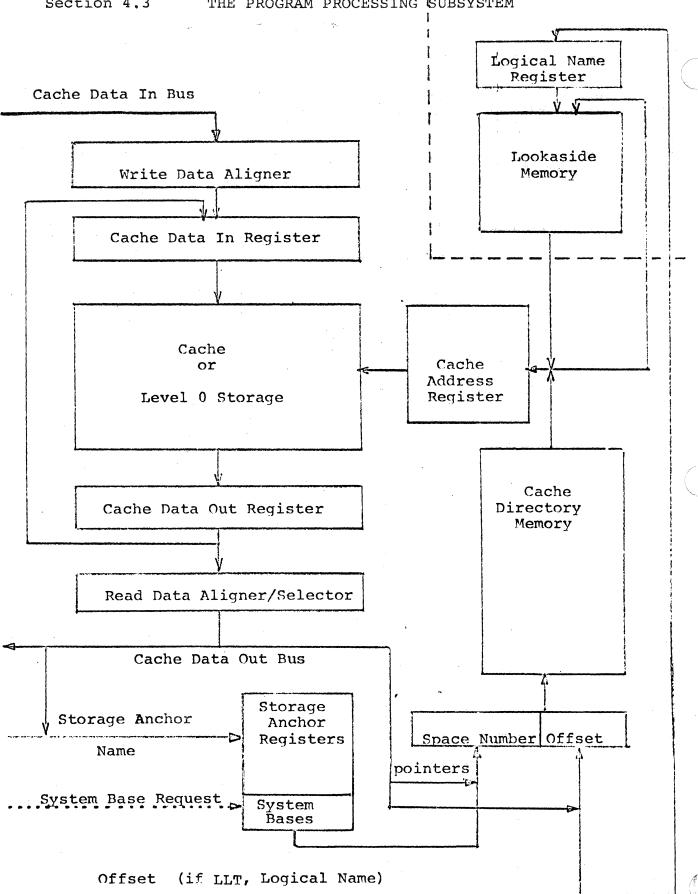

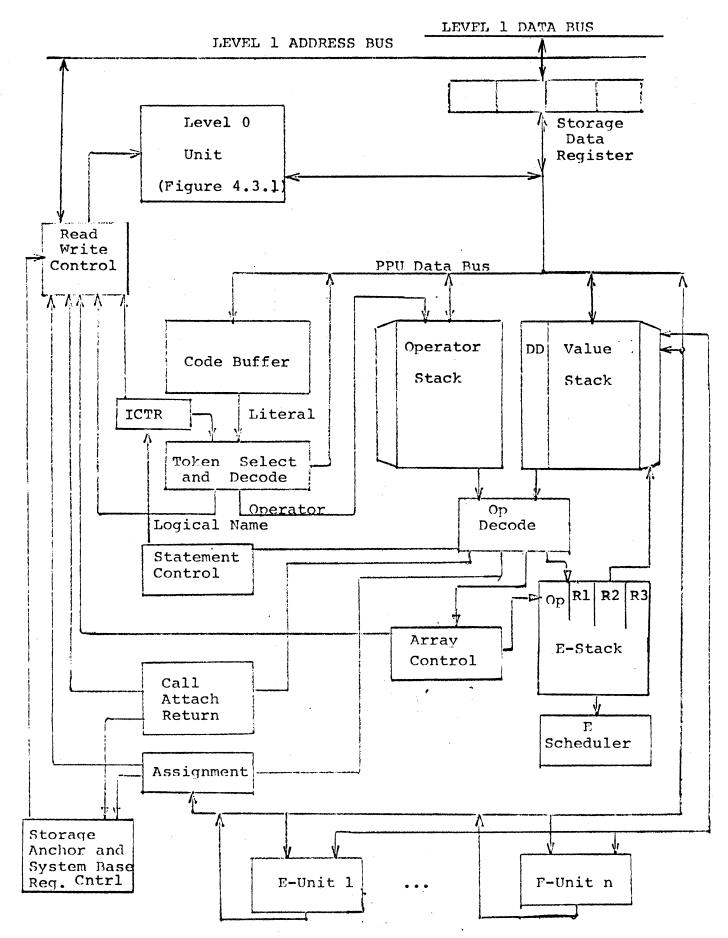

This Sub-system consists of one or more Program Processing Units (PPU) which are similar in function to a conventional CPU, but which operate at a higher level, close to a Procedure Oriented Language. They process statements rather than instructions; provide a wide range of control operators, and use described data rather than simple bytes to represent data values.

The PPU is essentially designed as a Prefix-Polish Stack Machine, extended by a set of Storage Anchor Registers which perform the function of base registers, and with built in vector and structure handling operations.

# 1.3.8 The Source-Sink Processing Sub-System

This Sub-system consists of one or more Source/Sink Processing Units (SSPU) together with the conventional source/sink devices and communication lines. The SSPU is a complete processing unit containing most of the capabilities of a PPU rather than a simple data channel. Thus it is capable of handling the complete task of data-transmission to and from storage without interrupting a PPU for intermediate processing.

The principle functions of the Source/Sink Processing Units are line control, network management, source/sink device management, control of the system clock and handling "wake-up" type interrupts to and from the PPU's. Both local and remote source/sink devices are handled by the SSPU, so that the difference is "transparent" to the casual user.

# 1.4 Using the System

The system is designed for a wide variety of users and uses, ranging from continuously running automatic jobs, through conventional application programs, to the design, debugging and operation of complex operating systems and data bases. This large skill range is provided for in several ways.

Firstly, a very powerful set of control operations is provided (obviously some of the more complex and infrequent of these are implemented in IBM supplied software or micro-code). Secondly, however, to preserve system integrity and provide high performance, many of these functions (such as Storage Management) have been built in, with rigorously controlled interfaces which do not allow for alternative approaches.

Superficially it would appear that naive users, provided with such rich capabilities, could overwhelm the entire system. A very wide degree of control is provided, however, by controlling the Node in the Ownership Tree to which a user is connected, the kind of Logical Machine that is placed at that Node, and the priority he is assigned.

Some idea of the scope of possibilities is provided by some simple examples:

# 1.4.1 Sensor-Based Applications

ENSOF.

These applications are performed on continuously active Logical Machines which are simply waiting on I/O interrupts. They have modules of code in their External Nodes which interpret commands to change parameters but do not build or modify themselves, or other Logical Machines.

# 1.4.2 Standard Batch Application Programs

These programs differ only slightly from Sensor-Based ones, in that their Logical Machine is inactive between runs. Thus, to be started, they require a sign-on and the intervention of the Logical Machine Supervisor. The addition of the sign-on capability extends the potential users of any application; however, this can be restricted to the required degree by placing the Logical Machine in the appropriate node in the Ownership Tree.

# 1.4.3 Problem-Solving and Debugging Simple Applications

The user operating in this mode signs on to a Logical Machine which initially contains merely a System Node and an External Node. The System Node contains access to the complete range of System Facilities but his capability to use them depends on the interpretive range of the External Node. In general, this node can interpret the full command language of the system but the designer of the Logical Machine may choose to restrict this capability by supplying a specialized External Node (e.g., he may only wish to supply the command language of the APL/360 system). The user once signed on to such a Logical Machine will typically be able to improve and specialize its processing capabilities by Connecting Modules below the External Node. These modules may be already in the Ownership Tree or may be introduced by him in any of the languages supported by the system (i.e., any language for which a Logical Machine that translate source text to a module exists).

# Subsystem Builders

The designer of a subsystem creates one or more Logical Machines which are to be placed into the Ownership Tree for the use of less sophisticated people. When the designer signs on for this purpose he is provided with a Logical Machine with a complete System Node and External Node. The commands which are particularly important to him are the ability to create a Logical Machine (specifying the Module to be placed in the External Node and the position in the Ownership Tree) and to call or attach one Logical Machine from another Logical Machine. Additionally, he needs to be aware of the physical system supporting a Logical Machine in order to achieve the appropriate cost performance.

#### CHAPTER 2

#### THE LOGICAL MACHINE

#### 2.1 Overview

A Logical Machine (LM) is that part of the system provided for processing each independent job. The LM's function is to execute code in the proper environment on behalf of the user. The LM, in addition to executing code, possesses the capability to communicate with the other logical components of the system (e.g. System Facilities, the Logical Machine Supervisor, and the Logical I/O System).

# Logical Machine Components

In order to execute code in the proper environment, a Logical Machine must contain the mechanisms to access the proper operands at execution time, provide the necessary operators, maintain program control, and accomplish the above while being "faithful" to the rules of the language used by the user. The mechanisms of the LM used to accomplish this are: a Program Tree to define the static connection of Modules, an Activation Tree which defines the dynamic linking of Modules, a Dynamic Storage Mechanism to provide the generation identification capability for data objects and Interpreters to execute the code.

Interpreters are the mechanisms which perform all operations required, and the Program and Activation Trees, and the Dynamic Storage Mechanism provide them the necessary information to obtain the proper results.

Each LM contains certain built in functions which are provided as special nodes in the Program Tree.

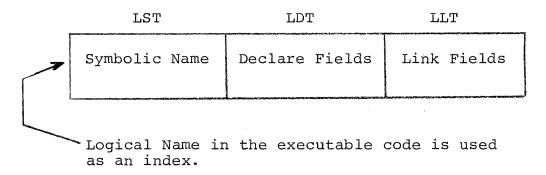

#### Program Tree

The Program Tree is the mechanism for name resolution. The nodes of the tree are modules which have been generated by Translators and grafted by the Connector. Each node contains the list of its symbols in a Local Symbol Table (LST), an accompanying Local Declare Table (LDT) describing the symbols, and a Local Link Table (LLT) for linking the symbols to their

values. Each node usually contains executable code.

# Activation Tree

Each node in the Activation Tree corresponds to an activation of a node in the Program Tree. The Activation Tree is a mechanism for maintaining the required information during Tasking, as well as Calls and Returns.

## Dynamic Storage Mechanism

The Dynamic Storage Mechanism provides a set of named Storage Anchors used as starting points for generations of variables. These point to the appropriate Reference Table for each variable. A System Storage Anchor is automatically supplied for each lexical level in the Program Tree. User Storage Anchors are supplied as required by user allocated variables.

## Interpreters

Interpreters are the logical executors of code and are the source of all functions/operations in the logical machine.

An interpreter executes on a statement basis, maintains the statement counter, and provides inter-statement control as determined by the code (e.g. IF, DO, GO TO) and intra statement control using the operand descriptor information provided (e.g. vector operations).

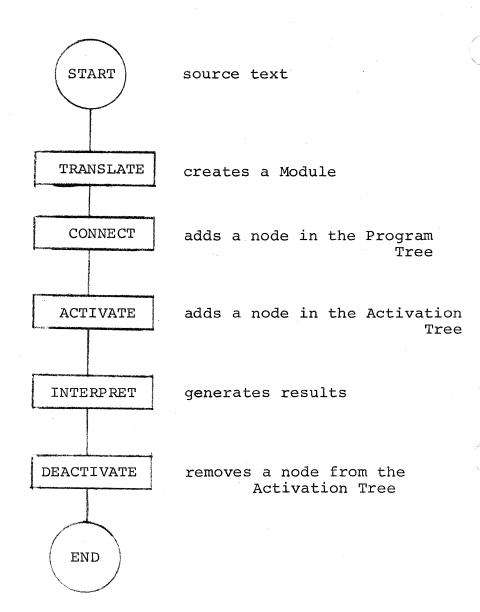

# Use of the Logical Machine

Logical Machines are activated by the Logical Machine Supervisor. This will occur when a job is created; for instance, when a user signs on the system. The LM then implements the functions required to process the user's program. A general flow of creating and executing a user's program is shown in Figure 2.1.1.

Translate takes the user's source code (APL, PL/I, FORTRAN, COBOL, RPG, etc.) and transforms it into an internal form of the System Language. The translate process accepts source code one line at a time, checks for syntax, and builds a Module. A Module consists of executable code together with information tables.

Figure 2.1.1 CREATING AND EXECUTING A PROGRAM

who con

Connect takes a Module and places it into the Program Tree which represents the static connectivity between the Modules of the program.

Activation of a module is the process of creating a node for it in the Activation Tree. The activation tree represents the dynamic structure of the program.

branks.

Names are resolved using the Program Tree. However, a name may have several generations of values associated with it. The process of determining the appropriate generation is resolved by the Dynamic Storage Mechanism which consists of a number of Storage Anchors from which the appropriate generations are chained. The result of activation is the initiation of an interpreter.

The Interpreter executes the code which is in the appropriate node of the Program Tree. Each parallel task has a separate interpreter. Interpretation is the process of executing the code in the appropriate module in the Program Tree. The result of the interpretation is the "answer" as defined in the user's code for that module.

Deactivation removes the node from the Activation Tree and removes the generation of variables associated with the activation.

# 2.2 The Program Tree

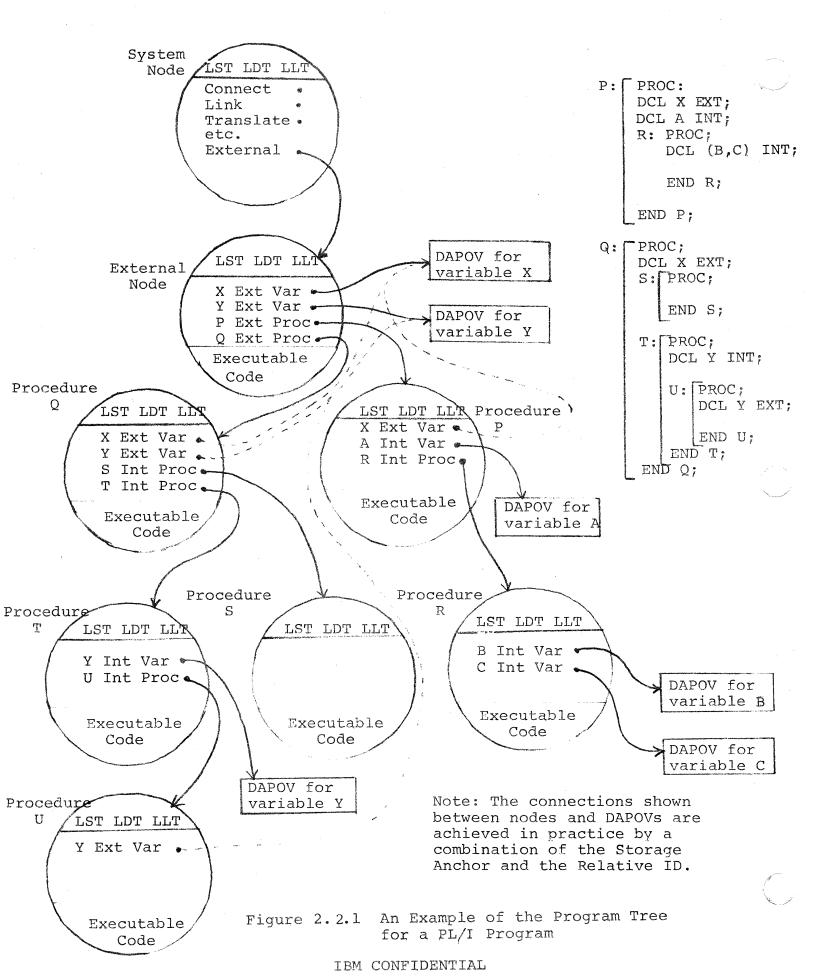

Each Logical Machine has a Program Tree. The purpose of the Program Tree is to contain the static connectivity between the Modules of the Job executing in the Logical (An example of a Program Tree is shown in Figure 2.2.1) Each node of the Program Tree represents a Module and contains the executable code for that Module, together with the Local Symbol Table containing all the Symbolic Names referenced in the Module, and the associated Local Link and Declare Tables. Each node also contains the names of, and the connectivity to, the Modules which have been connected into the Program Tree directly below that node. The Program Tree is used by the Linker in the resolution of the Symbolic Names referenced in the executable code of the Module. Further nodes can be created in the Program Tree for a particular Logical Machine by the execution of a Connect command in that Logical Machine.

There are two nodes in the Program Tree which have special properties and functions. The root node of the Program Tree is termed the System Node and contains the names of, and connectivity to, the system functions which are available to the Logical Machine. The System node also contains connectivity to the External Node. The External Node contains the Local Symbol, Link and Declare tables for all the external names of the program. The executable code of the Module represented by the External Node has the function of interpreting the Command Language. a new Logical Machine is created, it will be initiated to be executing the Module, associated with the External Node. The source of the command to be interpreted must be specified as a parameter when the Logical Machine is initiated. example, it might be an interactive terminal, or a catalogued data set.

# 2.2.1 The Use of the Program Tree for PL/I and APL

For a PL/I program there is a node in the Program Tree for each Procedure or Begin block. The Program Tree reflects directly the static block structure of the program. The External Node contains the names of, and connectivity to, every external procedure and every external name of the program. The name resolution for the symbolic Names referenced in each Procedure or Begin block is done by a search of the Program Tree. The subsequent steps required to obtain a reference to the correct generation of the variables by means of a storage anchor are discussed under Dynamic Storage Control in Section 2.4.

For an APL program there is a node in the Program Tree directly below the External node for every function. All the names referenced in the APL program appear in the External Node as user allocated external variables.

Hence, there will be a Storage Anchor name for each symbolic name in an APL program (see Section 2.4).

# 2.2.2 An Example of the Program Tree

The diagram in Figure 2.2.1 shows an example of the Program Tree for a Logical Machine which has had the PL/I program shown to the right of it connected into it.

Note: The Program Tree shown has been simplified by the omission of the nodes corresponding to the "imaginary" blocks which are said to contain the external procedures of a PL/I program. The purpose of each imaginary block is to contain the external entry names of the external procedure so that they can be seen by any reference statically contained within the procedure, but not by references statically contained within any other external procedure. The entry names, being external, will of course appear in the External Node, but the PL/I language rules say that they will only be found there by explicit declarations of the name as "external". These rules can be incorporated into the Program Tree by the inclusion of a node between the External Node and the node for each PL/I external procedure. These nodes correspond directly to the "imaginary" blocks.

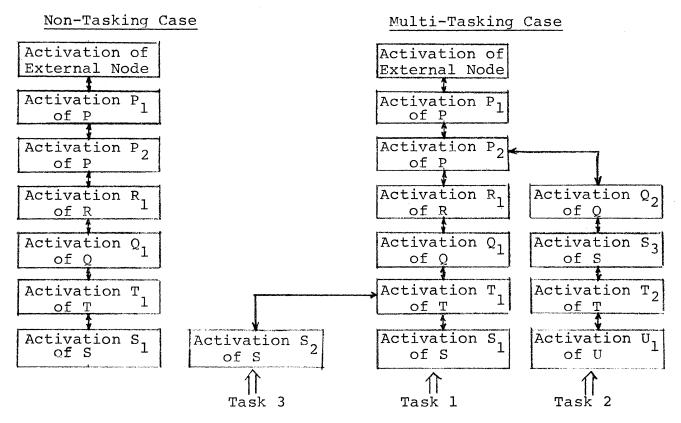

# 2.3 The Activation Tree

Each Logical Machine has an Activation Tree. The purpose of the Activation Tree is to contain information about which Modules are currently active and the order in which they called or attached each other. Each node of the Activation Tree corresponds to an activation of the Module associated with one of the nodes of the Program Tree. The root node of the Activation Tree corresponds to the activation of the Module associated with the External Node of the Program Tree. This node is activated by the creation of the Logical Machine. When there is no multitasking within the Logical Machine, the Activation Tree has only a single limb.

The following examples represent Activation Trees which could exist during the execution of the PL/I program shown in the example of the Program Tree in Section 2.2.1.

IBM CONFIDENTIAL

## 2.3.1 Invocation by Call or Function Reference

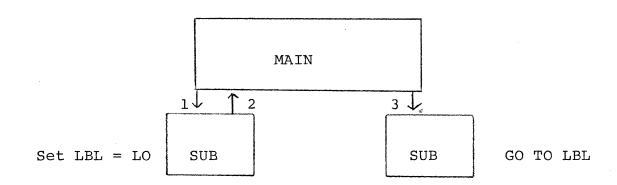

The invocation of a Module by the execution of an explicit call or of a function reference, causes a new node to be added to the branch of the Activation Tree representing the task in which the invoking operation was executed. Information is stored in the node of the activation tree to provide a link to the node of the Program Tree corresponding to the Module activated, and to enable a return to be made to the point immediately following that from which the Module was invoked.

Two types of Return are possible, these are usually termed "normal" and "abnormal" Return. Normal Return occurs when the current activation is terminated, and execution is resumed at the point remembered in the node of the Activation Tree. Abnormal Return occurs when a GO TO statement nominates a non-local label value as its operand. The current activation, and any intervening activations are terminated, and execution resumes at the label point specified in the GO TO statement.

# 2.3.2 Invocation by Attach

The invocation of a Module by the execution of an explicit Attach causes a new branch to be added to the Activation Tree. At this point the only element in this branch will represent an activation of the Module specified in the Attach. There is no return information associated with the first activation of a task. Once established, a new branch in the Activation Tree can grow and shrink in the same way as the main branch and can itself become the root of new branches.

Two types of task termination are possible. Normal task termination occurs when a Return statement or the last statement of the Module attached has been executed. The Task will be abnormally terminated if the activation which initiated its first activation itself terminates.

## 2.3.3 The Handling of Exceptional Conditions

The handling of exceptional conditions falls into three parts: the establishment of the action to be taken if an exceptional condition arises, the search to determine the action to be taken when an exceptional condition arises, and the invocation of the Module which is to perform the specified action.

Action for a PL/I condition).

Each condition name will be associated by the Linker with a stacking mechanism of the type used for user allocated variables (see Section 2.4). This stacking mechanism will be used to contain the entry value (Module, entry point, and environment) of the action which is to be taken if the

condition arises. This action may have been defined by the user (e.g., a PL/I on-unit) or by the system (e.g., Standard System

The action to be taken when the condition arises will be determined from the latest entry in the branch of the stack corresponding to the current task. The invocation of the Module giving this user or system provided action will follow exactly the protocol for the invocation of any other entry value (see Section 2.4.1).

# 2.4 Dynamic Storage

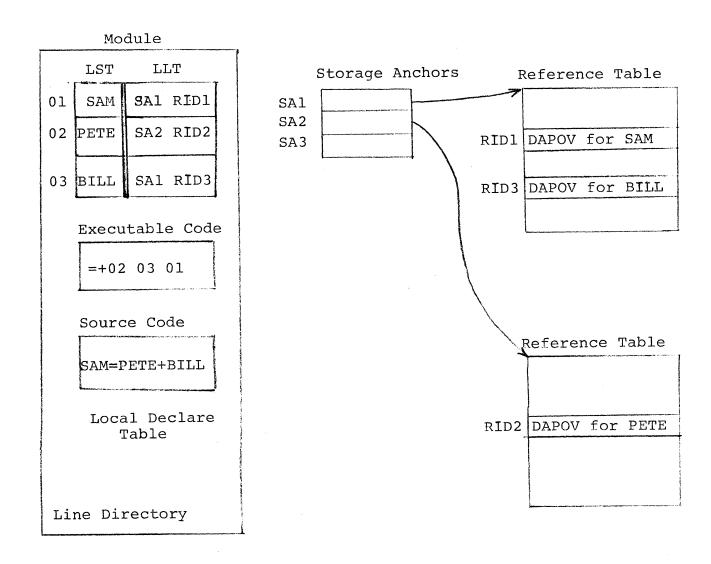

The purpose of the Dynamic Storage Mechanism is to provide storage for the Data Objects and to provide execution time addressability to the appropriate generations of the Data Objects referenced by Symbolic Names in the Modules of the program. Each generation of a Data Object consists of a Value Descriptor and value (DAPOV) as defined in Section 2.5. These DAPOV's are allocated in a Reference Table and each one can be addressed within that Reference Table by its Relative ID. Each Reference Table can contain DAPOV's for one or more variables. Addressability to each Reference Table is provided by a Storage Anchor. The total set of Storage Anchors can be divided into two parts, the set of System Storage Anchors and the Set of User Storage Anchors.

The System Storage Anchors are used to address the Reference Tables directly associated with the activations of the Modules represented by the nodes of the Program Tree. Each of these Reference Tables contains the DAPOV's for the variables which are allocated at the activation of the Module. Since only the names contained in one node at each level in the Program Tree can be referenced directly at any time, it is sufficient to have one System Storage Anchor for each level in the Program Tree. The names of the Storage Anchors to be associated with the nodes of the Program Tree will be filled in by the Connector. All the Reference Tables which use the same Storage Anchor must be chained together so that the value of the Storage Anchor can be updated as the Reference Tables are freed.

The User Storage Anchors are used to address the DAPOV's for those variables whose allocation and freeing is under the control of the user. The names of the Storage Anchors for these variables will be filled in by the Linker.

There must be a set of Storage Anchors for each Task executing in the Logical Machine, since the Reference Tables containing the current generation of the variables may be different in each task. When a Task is attached, unless there is a change of environment as described in Section 2.4.1, the only Storage Anchor to be changed is the one corresponding to the Module being activated. The rest of the Storage Anchors must be copied to provide addressability from both the Tasks to the Reference Tables associated with any Modules further up the Program Tree, and to any variables which have their own User Storage Anchors.

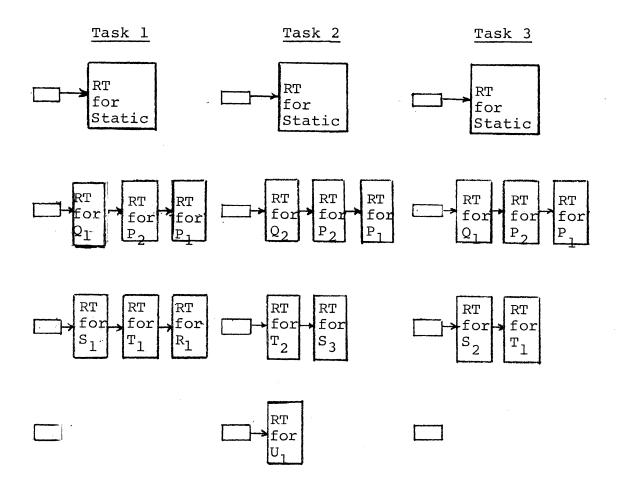

The System Storage Anchors for the multi-tasking example shown in Section 2.3 can be illustrated as follows:

Note: Although there is a Storage Anchor in each Task identifying the "RT for Static", there is only a single Reference Table for static variables; it can be addressed from any Task. The same comment applies to "RT for  $P_1$ " and the other Reference Tables which appear in the chains of a Storage Anchor in more than one Task. "RT for  $P_1$ " represents the Reference Table for activation  $P_1$  of  $P_2$ , whilst "RT for  $P_2$ " represents the Reference Table for activation  $P_2$  of  $P_3$ .

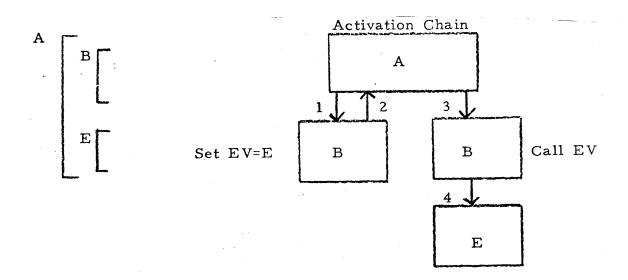

# 2.4.1 The Use of Storage Anchors for the Support of Entry Values

The environment which must be assigned with an entry value, together with the value of the entry point, can be seen

as the values of the Storage Anchors associated with each of the statically containing nodes. Again using the example of Section 2.2 and 2.3, the assignment of entry point R to a static external entry variable EV in activation  $P_1$  involves making a copy of the System Storage Anchors containing the values "External" and " $P_1$ ", and a note of to which Storage Anchors (or lexical levels) each of these values belongs.

At the call of the entry variable the values of the Storage Anchors which were copied at assignment time must be used to set the appropriate environment into the Storage Anchors, for the invocation of the entry variable. The current values of the Storage Anchors changed must of course be restored on return. In our example, assuming that the call of EV is in activation  $S_1$  of S, the value of the Storage Anchors for Task 1 before and after the activation of  $R_2$  would be as follows:

| Before the call of R | After the call of R |

|----------------------|---------------------|

| External             | External            |

| Q <sub>1</sub>       | Pη                  |

| $s_1^-$              | $R_2^-$             |

# 2.4.2 The Use of Storage Anchors for Support of Label Values

The implementation of label values with an environment component falls out as a simpler case of entry values. The difference, or simplification, is that for label values it is only necessary to switch the environment once and for all back to that which existed at the time of the assignment of the label value. All the activations which have come into existence between the time of this assignment and the branch to the label value will be wound up as part of the process of switching the environment. This approach can be used for the implementation of PL/I label variables.

# 2.4.3 The Use of User Storage Anchors for PL/I Controlled Variables

The Linker must associate a User Storage Anchor with each PL/I variable having the controlled storage class. This Storage Anchor will be used as an anchor for the Reference Tables containing the DAPOV's for the generations of the variable. The value of the Storage Anchor in each Task at any time will give direct addressability to the current generation of the variable in that Task.

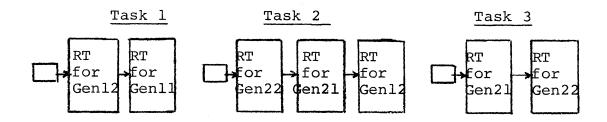

As an example, suppose that there was a controlled variable in procedure Q of the example in Section 2.2 and 2.3. At the point shown in the Activation Tree there might be two generations allocated in Task 1, two in Task 2, but none in Task 3. The relationship between the User Storage Anchor and the Reference Tables for the generations of the variable might be as shown below. (Note that the exact picture depends on the order of allocations and Task attaches.)

Note: "RT for  $\text{Gen}_{\text{ij}}$ " represents the Reference Table for the ith generation allocated in Task j.

# 2.4.4 The Use of User Storage Anchors for PL/I Based Variables

Since any remaining generations of PL/I based variables allocated in a Task must be freed at the termination of that Task, it will be useful to have a User Storage Anchor for all such generations. Thus the DAPOV's for all the generations of based variables allocated in a Task will be contained in a Reference Table addressable from this User Storage Anchor.

# 2.5 Data Objects and Linking

A <u>Data Object</u> has three components: a name, a descriptor, and a value. Included in the discussion in this section are the two forms of a name, i.e. the Symbolic Name and the Logical Name, as well as the two forms of a descriptor, i.e. the Value Descriptor and the Generic Descriptor. The Value <u>Descriptor</u> is always bound to the value, thus leading to the term <u>DAPOV</u>, meaning <u>descriptor</u> and, pointer or value, where the word pointer denotes a system supplied means of reaching a value.

# 2.5.1 Descriptors

A descriptor is stored logically with each Data Object in the system. The word "descriptor" is used in several different contexts.

- The <u>Value Descriptor</u> is stored with the value of a Data Object. It includes:

- A description of the instantaneous physical representation of the Data Object, and

- the authorization requirements for access.

- The <u>Generic Descriptor</u> is associated with the name and exists in the Local Declare Table (described fully in Section 2.5.2.3). In general, the Generic Descriptor includes:

- The set of logical declarations that are permitted for this name at varying points in time.

- The initialization expression(s) that will be used. These may be user declared. If not, defaults are supplied by the language translator and utilized if the name is not resolved at Link time to an already existing name.

This information is then sufficient to return to the Interpreter at execution time a described value when the object is read, and to permit error checking on receipt of a described value at write. The reading of an object by the Interpreter utilizes the Value Descriptor, and the writing into an object will first confirm that the described data to be stored is compatible with the Generic Descriptor.

IBM CONFIDENTIAL

Value Descriptors may be factored, such that like data elements may have a common descriptor. Access to a Data Object will be via a level in the factoring that will permit a reconstruction of the full descriptor to be returned to the Interpreter. A specific example of factoring, for example, may occur in the executable code, in which only a short, partial descriptor distinguishes Logical Names from literals or operators.

The appearance of a Data Object to the user of a Logical Machine is as if the externally presented representation (e.g. input or output to a terminal) is that contained within the machine. However, specific internal representations may be important to the skilled user, e.g.

- Structure or array stored as a vector of vectors.

- Descriptors factored

Descriptors are not directly manipulatable by the user of a Logical Machine. They are indirectly manipulated by implied descriptor changing (or creating) statements: DECLARE, ASSIGN, ....

# 2.5.1.1 Descriptors as Related to Access Machines

Descriptors are a form of access machine (as defined in the Fundamental Concepts and System Language Manual). Examples of descriptors which act as built-in access machines are a floating point number, arrays, and structures. Logically, an array is treated as a vector of vectors, although physically, a more efficient implementation may be required. Access will be made via a descriptor and will yield a described value from the representation. A descriptor also provides the capability of the "follow" mechanism of an access machine in that it may contain the value, "System Pointer", which implies that the pointer should be followed to the next DAPOV.

# 2.5.2 Names

All names have two forms, a Symbolic Name and a Logical Name. The Symbolic Name is a character string, as written by the user, used for all communication with the user. A Logical Name is the internal encoding which replaces each Symbolic Name. In the executable code of each Module, each unique Symbolic Name is replaced by a unique non-negative integer, called the Logical Name. The system may be required to supply additional Logical Names in certain special instances, for example, for unnamed BEGIN blocks or iteration

variables. A Logical Name may be used as an index to a unique position in the Local Symbol Table, the Local Link Table, or the Local Declare Table (each defined below). Once program text is encoded, it is required that the Local Symbol Table be available to reconstruct the original names.

It will not be required that an application programmer be aware of the fact that his Symbolic Names have been encoded as Logical Names, but a system programmer may need to be aware of the existence of Local Symbol Tables and their role in name resolution in the Program Tree.

The connectivity between the Logical Name in the executable code and the Symbolic Name, the Generic Descriptor, and the DAPOV are contained in a set of three tables in the Module. These are the Local Symbol Table (LST), the Local Declare Table (LDT), and the Local Link Table (LLT).

Figure 2.5.1

# 2.5.2.1 Local Symbol Table (LST)

The Local Symbol Table contains one entry for each unique (variable length) Symbolic Name, as written by the user, that is either declared or referenced within a single unit of translation. The Logical Name of any symbol can be determined by the Interpreter by searching the LST in sequence. Conversely, the Symbolic Name can be recovered by using the Logical Name as an index to the LST. (See Figure 2.5.1).

# 2.5.2.2 Local Link Table (LLT)

The Local Link Table contains one entry for each

Logical Name, in the same order as the LST. (See Figure 2.5.1). Each entry contains two fields which are filled in by the Linker. The first field will contain the Storage Anchor Name to connect each Logical Name with the Reference Table containing its execution time DAPOV. A zero in this field implies that this entry has not been linked yet. The second field will usually contain the Relative ID of the DAPOV within the Reference Table. (The Relative ID is the logical location of the DAPOV within the Reference Table.) However, a User Storage Anchor Name is contained in this field, if the first field has maximum field value.

## 2.5.2.3 Local Declare Table (LDT)

The Local Declare Table also contains one entry for each Logical Name, in the same order as the LST. (See Figure 2.5.1). Each entry contains seven fields which are filled in by the Translator. The name of each field, their possible values, and meanings follow:

| Field                      | <u>Value(s)</u> | Meaning                                                                          |  |

|----------------------------|-----------------|----------------------------------------------------------------------------------|--|

| Defined Flag               | Defined         | A declaration for this Symbolic<br>Name has been made in this module.            |  |

| Consult Node               | Undefined       | No declaration made in this module.                                              |  |

| Search Node                | Internal        | No search of Program Tree required for Linking                                   |  |

|                            | External        | Search External Node when Linking                                                |  |

|                            | System          | Search up to System Node (by-                                                    |  |

|                            |                 | passing External Node)                                                           |  |

|                            | Above           | Search one node above (see Section 2.5.2.4).                                     |  |

|                            | External +1     | Search up to one node below External Node.                                       |  |

| Storage Anchor             | Here            | Use this Module's System Storage Anchor for allocation.                          |  |

|                            | Ext SA          | Use System Storage Anchor of Ex-<br>ternal Node for allocation                   |  |

|                            | User            | Use User Storage Anchor for allocation.                                          |  |

|                            | External +2     | Use System Storage Anchor of node two below External Node.                       |  |

| Mandated<br>Storage Anchor | Yes             | Declaration requires Storage Anchor field value to be used.                      |  |

| beorage Andiron            | No              | Storage Anchor field contains default to be used only if search is unsuccessful. |  |

| Field                 | Value(s) | Meaning                                                           |

|-----------------------|----------|-------------------------------------------------------------------|

| Task FREE'd           | Yes      | Will be FREE'd by task termination if not earlier FREE'd by user. |

|                       | No       | Task FREEing not required.                                        |

| Template<br>Indicator | Real     | Symbol represents a value                                         |

|                       | Based    | Symbol represents a descriptor only.                              |

| Generic<br>Descriptor |          | (See following paragraph)                                         |

The last field in the LDT, termed the Generic Descriptor, itself contains ten subfields, some of which are variable in length. These subfields contain either the user declarations or the language defined defaults if at Link time a search is required and the name is not found in one of the containing blocks in the Program Tree. The names of these subfields, their possible values, and meanings follow:

| Subfield                        | <u>Values</u>                                                                                       | <pre>Meaning (if not self-</pre>                                                  |

|---------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Data Type                       | Any, Character, Fixed Decimal Float Binary Pointer, Offset, Label, Entry, Event, Task, or Statement |                                                                                   |

| Shape                           | Scalar, vector,<br>Array, or structure                                                              |                                                                                   |

| Con-Var                         | Constant, or<br>Variable                                                                            |                                                                                   |

| Precision<br>Scale              | Numeric value<br>Numeric value                                                                      |                                                                                   |

| Array Bounds                    | Upper expression and lower expression                                                               | Two expressions for each dimension of an array to define the limits of the array. |

| Initial<br>Locator<br>Qualifier | Expression<br>Expression                                                                            | Initial value expression Used for pointer expression declared with based variable |

| Subfield                 | Values  | Meaning                                                         |

|--------------------------|---------|-----------------------------------------------------------------|

| Parameter                | Yes     | Symbol unusable unless associated with an argument at entry.    |

|                          | No      | Symbol usable                                                   |

| Generic Desc.<br>Pointer | Pointer | For undefined symbol, pointer to Generic Descriptor of defining |

|                          |         | occurrence of symbol. Filled in by Linker.                      |

## 2.5.2.4 Entry Names

Procedure (or function) names and entry names are properly not considered to be declared within the Module that make up the statements of that procedure. Rather, they are considered as being declared as a name in the containing node of the Program Tree. Thus, to prevent the possibility of duplicate names in the LST, a second set of tables (LST, LLT, LDT) is created by the Translator which contains information relative to procedure or entry names. The search node field of the LDT contains the value "above" for these names. The Connector is responsible for merging the "above" tables of the procedure being connected with the tables of the procedure into which the connection is being made.

#### 2.5.2.5 Object Code in the LST, LLT, LDT

The object code for each source language statement will be treated as a variable. The Symbolic Name is the statement number. The line directory will contain the Logical Name of each statement number. The LLT fields will point to the start of the initialized object text for each. Fields in the LDT will be set to defined, internal, ext SA (if PL/I) or here (if APL), and will contain an initializing expression which is the encoded object text created by the Translator.

## 2.5.2.6 Treatment of APL Symbolic Names

All APL Symbolic Names will be declared by the Translator as defined, external, user. Further, for each local APL symbol in a function, the Translator will insert a user allocation statement in the entry code to initialize the DAPOV to unassigned, and a user free statement in the exit code. As with a PL/I procedure, it is only necessary to Link a function

once. The inserted statements for local symbols will create the proper visibility of symbols as required by APL.

One area requiring special mention is that a function name, when Connected, will be established as the oldest generation for that given Symbolic Name, even though there are other generations (of local variables) already in existence.

## 2.5.3 Linking

The function of the <u>Linker</u> is to resolve the static nesting of symbols so that at execution time a Logical Name will lead via the <u>fields</u> in the LLT to a DAPOV in a Reference Table. In this manner, the name of the Data Object is bound to the DAPOV of the Data Object. Linking is accomplished at first activation. In order to fill in the Relative ID, it is necessary to initialize and allocate variables while Linking.

For a name containing a value in the search node field of the Generic Descriptor of <u>internal</u>, one of three actions will be taken depending on the value of the storage anchor field of the Generic Descriptor:

- 1. Value of storage anchor field is Ext SA. The initial value is generated using the expression in the initial field of the Generic Descriptor, and the Reference Table associated with the External Node is extended to include the DAPOV. The Storage Anchor Name and Relative ID are filled into the LLT, thereby marking this name as linked. (This case is used for PL/I static internal.)

- 2. Value of storage anchor field is here. Generate the initial value and extend the RT with the DAPOV. The RT is that identified by the System Storage Anchor for this Module. The Interpreter will have already stored a newly created Space Name in this Storage Anchor. The name of this Module's System Storage Anchor and the Relative ID to the new DAPOV are filled into the LLT. (This case is used for PL/I automatic.)

- 3. Value of storage anchor field is User. Obtain the next User Storage Anchor name, and insert as its value the next available Space Name. Then extend that Space with a pointer indicating the previous generation is non-existent and a DAPOV for an unassigned value. Finally, the fields of the LLT

are filled in. It may be noted that these variables are initialized to catch a reference prior to user allocation as an error. (This case is used for PL/I controlled internal.)

For a name containing a value in the search node field of either external, system, or external +1, the Linker will extract the Symbolic Name from the LST using the Logical Name as an argument. The Symbolic Name is used as a search argument in the specified search node(s). (In the case of system or external +1, the search will start at the node above this module's node.) If found, the fields of the LLT entry where found are copied into this Module's LLT. For a defined symbol, the corresponding LDT entries are checked for consistency. For an undefined symbol, a pointer to the LDT entry of the symbol found is placed in the Generic Descriptor pointer field. If not found, one of three actions will be taken depending on the value of the storage anchor field:

- 1. Value of storage anchor field is Ext SA. ceed as in Case 1 above. Then extend and fill in the fields of the LST, LDT, and LLT of the External Node with a copy of the entry from this Module's tables. (This case is used for the first occurrence of a PL/I static external variable.)

- 2. Value of storage anchor field is User. Proceed as in Case 3 above. Then extend the fields of the LST, LDT, and LLT of the External Node with a copy of the entry from this Module's tables. (This case is used for the first occurrence of a PL/I external controlled variable or APL symbol.)

- 3. Value of storage anchor field is External +2. Two subcases apply.

- a) If this Module is at a node below external +2, initialize and allocate the DAPOV by extending the RT of the System Storage Anchor of the node two below the External Node. Fill in the LLT fields for the entry in this Module, and then copy the LST, LDT, and LLT into an extension of the tables in the external +2 node. Mark the storage anchor field in that LDT with the value, 'Here!

- b) If this Module is at the external +2 node, proceed as in Case 3a, but do not extend the LST, LDT, LLT tables, since the entry already exists there. (These cases are used for an undefined variable.)

The Link process for names with a template value of based requires that a link be established to a Storage Anchor containing all such names, so that the names may be freed by the system if the user fails to do so prior to task termination.

After Linking all the entries in the LLT, the Linker will turn on the link bit for this Module. Subsequent activations will only require allocation and initialization of those Logical Names with a storage anchor field value of Here! Procedure editing will turn the link bit for this Module off, as well as the link bit for any Logical Name affected by the editing. Additional detailing is required to state which Logical Names are affected, and the effect on Logical Names in other Modules.

# 2.6 The Interpreter

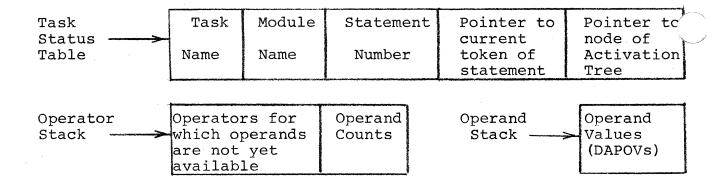

The execution of code in each active Logical Task of a Logical Machine is performed by an Interpreter. Each such Interpreter is capable of executing a set of Built-in Operators, and is provided with a separate set of mechanisms consisting of: An Operator Stack, an Operand Stack and a Task Status Table. Each interpreter also makes use of the facilities of the Logical Machine in which it is active, i.e., The Program Tree, the Activation Tree, and the Dynamic Storage Mechanism.

# 2.6.1 The Built-in Operators

The Built-in Operators which can be executed by each Interpreter can be classified as those which handle computation, those which handle the flow of control between statements of the active Module and between different Module activations, and those which provide special system functions.

The computational operators are generic with respect to the data type and aggregation of their operands and provide a combination of the logical and arithmetic operations available in APL, PL/I, FORTRAN, COBOL, and RPG. The logical operators include: ASSIGN, SUBSCRIPT, CONCATENATE, COMPARE EQUAL/NOT EQUAL/LESS THAN/ and GREATER THAN, AND, OR, NOT, SUBSTRING and single character SEARCH, TRANSLATE, SIZE and SHAPE (like APL p). The arithmetic operators include: ADD, SUBSTRACT, MULTIPLY, DIVIDE, EXPONENTIATE, LOGARITHM, ABSOLUTE VALUE, COMPARE EQUAL/NOT EQUAL/LESS THAN/ and GREATER THAN, FLOOR, CEILING, MAXIMUM, MINIMUM, ROUND and ASSIGN. Discussion of the language requirements for these operators is contained in memos ASP-045 and ASP-051. There is also a requirement for a number of operators to handle editing and conversion between different types of data.

The operators which handle the flow of control between statements of an active Module and between Module activations include: GO TO, IF-THEN-ELSE, DO, CALL, RETURN, ATTACH, and EXIT.

The operators which provide the special systems functions include: LINK, CONNECT, CREATE LM, CALL LM, ATTACH LM, ENTER/ LEAVE EDIT MODE and other Operators to support System Facilities and the Logical I/O System.

### 2.6.2 The Interpreter Mechanisms

In executing the code (which is in a prefix polish form) the Interpreter makes use of three mechanisms which are illustrated schematically below:

# The Task Status Table contains five fields:

- 1. The first field contains the name of the Logical Task being executed by the Interpreter. This provides access to the Logical Task Control Block (LTCB) and hence to the set of Storage Anchors for this task.

- 2. The second field contains the name of the Module currently being executed and provides access to the various components of this Module which are contained in the node of the Program Tree (i.e., LST, LLT, LDT, executable code and line directory).

- 3. The third field contains the number of the statement which is currently being executed, and will be updated as each statement is completed.

- 4. The fourth field identifies within the statement code the token (i.e., operator, operand, or literal which was fetched most recently).

- 5. The fifth field identifies the latest node in the branch of the Activation Tree for the task being executed, and will be used to store the information contained in the Task Status Table into the Activation Tree when the call of a new Module is executed.

The Operator Stack contains a push down list of those operators which have been fetched, but for which all the operands are not yet available, together with counts of how many operands are still needed for each operator in the stack.

The Operand Stack contains the values, in DAPOV form, of all those operands and literals which have been fetched, or computed, but which cannot be used by their operator until its other operands have been fetched or computed.

### 2.6.3 Statement Evaluation

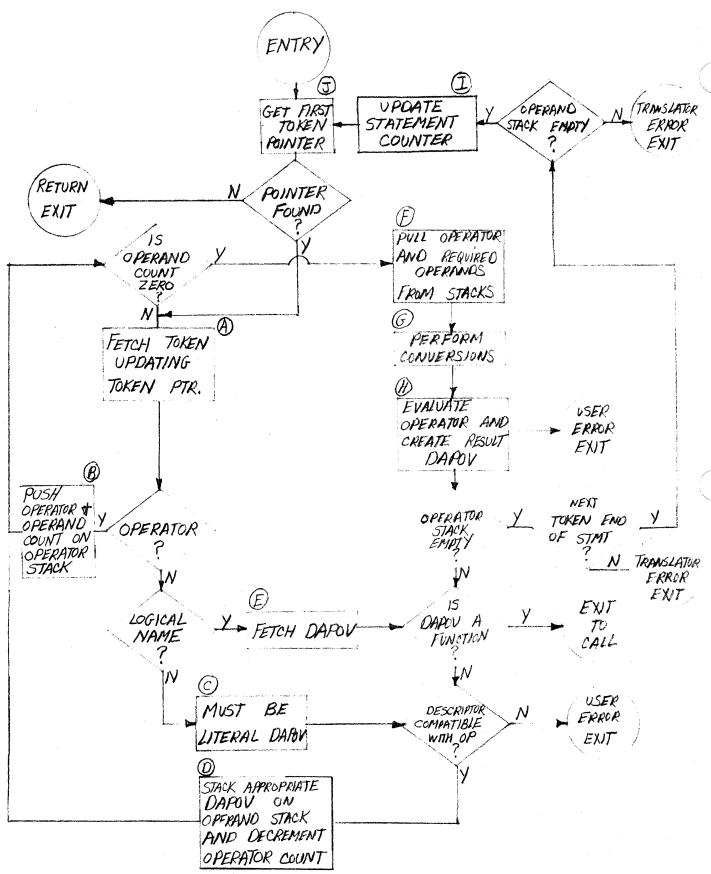

The basic protocol for statement evaluation is presented in the Figure 2.6.1. The equivalent of an instruction fetch is the token fetch loop which starts at the block labeled A and continues through block B for an operator token, or blocks C and D for a literal, or blocks E and D for a logical name. The DAPOV fetch in block E is discussed in further detail in the next section. In block D the "appropriate" DAPOV in the case of an assignment argument is a pointer to the generic descriptor in the LDT rather than the fetched value descriptor and value.

An execution cycle represented by blocks F, G and H is taken whenever the operand count of the operator on top of the operator stack is zero. Note that the evaluation of control and system operators will often result in leaving the basic evaluation loop. Simple cases of these operations are discussed in subsequent sections.

After execution a check is made to see if the Operator Stack is empty. In prefix polish notation this should be the end of the statement. To protect against a badly translated Module, an End of Statement token is required in the code and the Operand Stack must also be empty. If these conditions are met the first token pointer of the next statement is fetched by blocks I and J. This requires using the statement counter as an index to the Line Directory in the Module. If no statement is found, the Interpreter takes an automatic RETURN.

### 2.6.4 Protocol for Value Fetch from Variables

Whenever a reference type of operand is encountered during statement execution its value (DAPOV) must be fetched into the operand stack from the appropriate Reference Table. The process involved is described below and illustrated in Figure 2.6.2.

The Logical Name appearing in the code is used as an index to the LLT (contained in the node of the Program Tree) to yield a Storage Anchor name and Relative ID for the required DAPOV. The Storage Anchor name and Task name (contained in the current status table) are used to obtain the value of the

Figure 2.6.1 STATEMENT EVALUATION

Storage Anchor relevant to the current task. This Storage Anchor value identifies the required Reference Table. The Relative ID, already obtained from the LLT, is now used to access the required DAPOV from this Reference Table. If the DAPOV obtained turns out to contain an indirect reference to some other DAPOV the chain of indirection will be followed automatically to its end.

Figure 2.6.2 Access of DAPOVs

### 2.6.5 Protocol for Call

The following set of actions must be performed by the Interpreter whenever a Call operator or function reference is encountered:

- 1. Evaluate any arguments and place the values or references on the operand stack.

- 2. Update the statement number field, and save the information contained in the Task Status Table in the node of the Activation Tree identified by the fifth field of this table.

- 3. If invocation involves a switch of environment, also save the values of Storage Anchors to be modified, and set these Storage Anchors from the environment information of the entry value.

- 4. If the Module to be invoked has not previously been linked, invoke the Linker to link the Symbolic Names referenced or declared in the Module.

- 5. Create a new Reference Table for this activation, set its chain field to the value of the appropriate Storage Anchor, and set this Storage Anchor to identify the Reference Table just created.

- 6. Carry out initialization of variables allocated in this Reference Table.

- 7. Set up addressability to any parameters using the argument values contained in the operand stack.

- 8. Set the fields of the Task Status Table and start execution of the code of the invoked Module.

### 2.6.6 Protocol for Return

The following actions must be performed by the Interpreter when a Return operator is encountered:

- 1. Evaluate any return value expression and place the result in the operand stack.

- 2. Restore the appropriate Storage Anchor from the chain field of the Reference Table for the activation being terminated, and then free this Reference Table.

- 3. If the invocation had involved a switch of environment, restore the Storage Anchors switched from the values saved.

- 4. Restore the Task Status Table from the information which was saved in the Activation Tree, and remove the node of the Activation Tree associated with the activation being terminated.

- 5. Continue execution according to the information now contained in the Task Status Table.

# 2.6.7 Protocol for GO TO

There are two cases:

- a) A GO TO within the scope of the current activation:

- 1. Set the value of the statement number field of the Task Status Table to the value given by the operand, and the value of the current element pointer in the current status table to the start of this statement.

- 2. Carry on with execution of this Module.

- b) A GO TO with a destination in some suspended activation.

- 1. Search the Activation Tree to ensure that the destination activation still exists.

- 2. Terminate as many activations as necessary until the destination activation becomes the current one, freeing the Reference Tables for these activations and taking the other actions described in the protocol for Return.

- 3. Proceed with protocol for case a.

### 2.6.8 Protocol for Attach

The following actions must be performed when the Interpreter encounters an Attach operand:

- 1. Evaluate any arguments and collect the values or references in a special table.

- 2. Call upon the Logical Machine Supervisor to set

up and initiate a new Logical Task passing to the LMS the name of the attaching task (i.e., LTCB), the name of the Module to be invoked as the first activation of the new task, the values of the Storage Anchors, and the table containing the arguments to be passed to this activation. (The Logical Machine Supervisor sets up a new Logical Task which will itself be executed by an Interpreter.)

3. Activate the Module in the new task performing actions 4 through 8 of the protocol for Call.

# 2.7 <u>Building a Logical Machine</u>

Skilled users of the system may wish to modify the Logical Machine to which they are connected or to create a new Logical Machine for subsequent use. Modifying a Logical Machine requires invoking the system functions of Connect and Disconnect which add or remove Modules from the Program Tree. A separate system function is used to create a new Logical Machine.

The ability of a user to perform these functions depends upon the capability of the Logical Machine to which he is connected. The functions are always available at the System Node in the Program Tree; invoking these functions can only occur from some Module lower in the Program Tree; and recognizing commands from the user to cause this invocation is dependent on the interpretive power of the External Node in the Program Tree.

### 2.7.1 The Connect Function

The Module to be connected may either be in the Ownership Tree or supplied by the user as program statements entered through the Logical I/O System (e.g. from a keyboard).

If the user choses to enter statements from the keyboard, he must enter Edit mode. Statements entered in Edit mode are translated and, when the user is finished entering the statements, a Module is built. The statements can be written as nested procedures. If this is done the procedures will be nested into the Program Tree in the same way they were written.

Before connection into a Program Tree, a procedure exists as a Module. When the connection is initiated, information from the Module is used to construct the LLT, LST, and LDT. None of the variables of the Module are linked at this time, entry names, however, are resolved to the node of the Program Tree under which the Module is being connected.

If the Module (call it JOE) is to be nested below another Module (call it PETE), then the entry names for JOE may be found in the LST for PETE.

If they are found, PETE's corresponding LLT entries are set to identify an element of the Reference Table corresponding to JOE's entry names do not show up in PETE's LST, then they are added to PETE's LST and LLT.

The static nesting can be specified by the connect command. For example, the command sequence

Connect A

Connect B in A

Connect C in A. B

results in A being the outermost procedure with B and C nested below:

# 2.7.2 The 'Create Logical Machine' Function

The 'Create Logical Machine' function requires three parameters, a name for the Logical Machine, the position in the Ownership Tree at which the LM is to be created, and the name of a Module in the Ownership Tree which is to be placed at the External Node of the new LM.

The name of the LM will be checked in the Ownership Tree to insure uniqueness. Also, the receiving node in the Ownership Tree must authorize this kind of access. It is, of course, always possible to create a Logical Machine directly beneath the creating Logical Machine.

The choice of Module for the External Node will also be checked for authority and indeed this is one of the prime mechanisms for defining the skill level of users. Clearly at least one Module will be defined to interpret the full SL Command Language. Who is allowed access to this Module, and where they are allowed to place a Logical Machine which they create, constitute basic control mechanisms on the users of the system.

#### CHAPTER 3

### THE LOGICAL SYSTEM

# 3.1 The Logical Machine Supervisor

The Logical Machine Supervisor is an active Logical Machine at the root of the Ownership Tree with two primary functions. Firstly, it is the interface between the system users and their work, as it is processed by one or more Logical Machines. Secondly, it is the interface with the Physical Control System and loads this system with requests for physical processing as generated by the Logical Machines.

# 3.1.1 The User Session, Jobs, and Logic Tasks