# GPD technical record

IBM CONFIDENTIAL

DIGITAL COMPUTERS — LOGICAL PRINCIPLES AND OPERATION

by

George J. Saxenmeyer

#### **ABSTRACT**

A brief survey of digital computation, beginning with the origins of early computing devices — including the abacus, the suan-pan, soroban, choreb, and others — is followed by a description of the theory and operation of Babbage's Differential Analytical Machine. Typical contemporary computing system functions are reviewed, along with data flow charts, binary number systems and adders, Boolean algebra, binary-coded-decimal and bi-quinary arithmetic. Fixed-bit information codes and self-checking and self-correction codes are discussed. A comparison of codes is made, along with various storage devices — including static storage (triggers and latches) — and dynamic storage, including magnetic drum and ferrite core storage. Switch cores and core logic are briefly surveyed.

# IBM CONFIDENTIAL

This document contains information of a proprietary nature. ALL INFORMATION CONTAINED HEREIN SHALL BE KEPT IN CONFIDENCE. No information shall be divulged to persons other than IBM employees authorized by the nature of their duties to receive such information or individuals or organizations who

are authorized by the General Products Division Management in accordance with existing policy regarding the release of Company information. This document must not be photographed or otherwise reproduced in whole or in part at any time.

# TABLE OF CONTENTS

|      |                                                                     | page |

|------|---------------------------------------------------------------------|------|

| 1    | EARLY COMPUTING DEVICES EVOLUTION OF THE ABACUS                     | 1    |

|      | A. HALVING AND DOUBLING (MULTIPLICATION)                            | 1    |

| 11   | BABBAGE'S DIFFERENTIAL ANALYTICAL ENGINE                            | 2    |

|      | A. BACKGROUND OF BABBAGE'S MACHINE                                  | 4    |

|      | B. THE MATHEMATICS OF BABBAGE'S MACHINE                             | 4    |

|      | C. THEORY OF BABBAGE'S MACHINE                                      | 5    |

|      | D. DATA PROCESSING SYSTEM REQUIREMENTS                              | 6    |

| 111  | TYPICAL DATA PROCESSING MACHINE FUNCTIONS                           | 7    |

|      | A. ITERATION                                                        | 7    |

|      | B. STORAGE DEVICES                                                  | 8    |

|      | C. CONTROL LOGIC STORED PROGRAMMING                                 | 9    |

|      | D. CONTROL LOGIC WIRED PROGRAMMING                                  | 9    |

|      | E. INPUT/OUTPUT DEVICES                                             | 9    |

| IV   | FIRST-LEVEL DATA FLOW CHARTS                                        | 10   |

|      | A. IBM 604 DATA FLOW                                                | 10   |

|      | B. IBM 305 RAMAC DATA FLOW                                          | П    |

|      | C. IBM 650 DPS DATA FLOW                                            | 12   |

|      | D. IBM 7070 DPS DATA FLOW                                           | 12   |

| ٧    | THE BINARY NUMBER SYSTEM                                            | 19   |

| VI   | BOOLEAN ALGEBRA                                                     | 21   |

| VII  | THE LOGICAL BINARY ADDER                                            | 22   |

| VIII | BINARY-CODED DECIMAL ARITHMETIC                                     | 26   |

| IX   | BI-QUINARY ARITHMETIC                                               | 28   |

| X    | BI-QUINARY COMPLEMENTING AND VALIDITY CHECKING                      | 30   |

| XI - | FIXED-BIT INFORMATION CODES                                         | 33   |

| XII  | SELF-CHECKING AND SELF-CORRECTION CODES                             | 34   |

| XIII | STATISTICAL ERROR PROBABILITIES                                     | 37   |

|      | A. DEFINITIONS                                                      | 37   |

|      | B. COMPARATIVE CHECKING RELIABILITY OF THE 2 OUT OF 5 AND BCD CODES | 38   |

| XIV  | CODE TRANSLATION                                                    | 40   |

| ΧV   | COMPARISON OF CODES                                                 | 43   |

| ΧVI  | STATIC STORAGE TRIGGERS AND LATCHES                                 | 44   |

| XVII | MAGNETIC DRUM STORAGE                                               | 40   |

| XVIII   | CAPACITOR STORAGE                                                    | <b>pag</b> 54 |

|---------|----------------------------------------------------------------------|---------------|

| XIX     | FERRITE CORE STORAGE                                                 | 58            |

| XX      | SWITCH CORES AND CORE LOGIC                                          | 62            |

| XXI     | CARD READERS AND PUNCHES                                             | 66            |

|         | A. IBM 533 READER PUNCH                                              | 67            |

|         | B. IBM 537 COMPUTING PUNCH                                           | 67            |

|         | C. IBM 7070 SYSTEM                                                   | 67            |

|         | D. BASIC IBM 650 SYSTEM                                              | 68            |

| XXII    | WHEEL AND WIRE PRINTING                                              | 72            |

|         | A. IBM 407 WHEEL PRINTER                                             | 72            |

|         | B. IBM WIRE PRINTERS                                                 | 73            |

| XXIII   | CHAIN, BAR-AND-HELIX, AND STICK PRINTING                             | 82            |

|         | A. IBM CHAIN PRINTER                                                 | 82            |

|         | B. IBM BAR-AND-HELIX PRINTER                                         | 83            |

|         | C. IBM STICK PRINTER                                                 | 83            |

| XXIV    | TAPE DRIVE UNITS                                                     | 87            |

| XXV     | RANDOM ACCESS DISK FILE MEMORY                                       | 94            |

| XXVI    | CONCLUSION                                                           | 105           |

| XXVII   | BIBLIOGRAPHY                                                         | 105           |

|         | ILLUSTRATIONS                                                        |               |

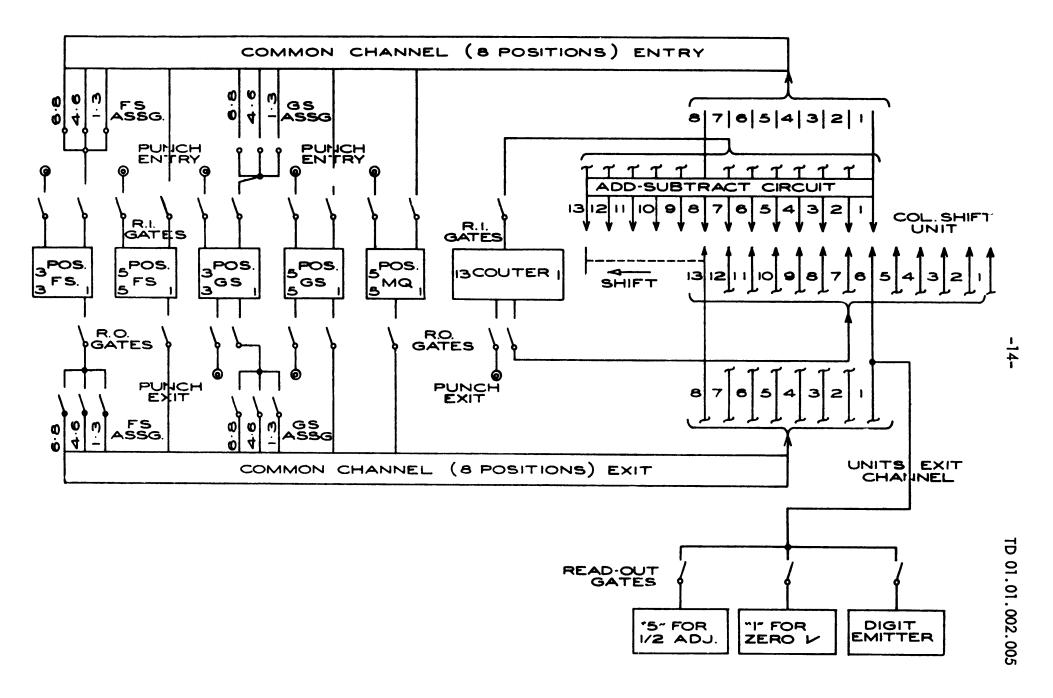

| Fig. l  | Schematic Layout of the IBM 604 Electronic Calculator                | 14            |

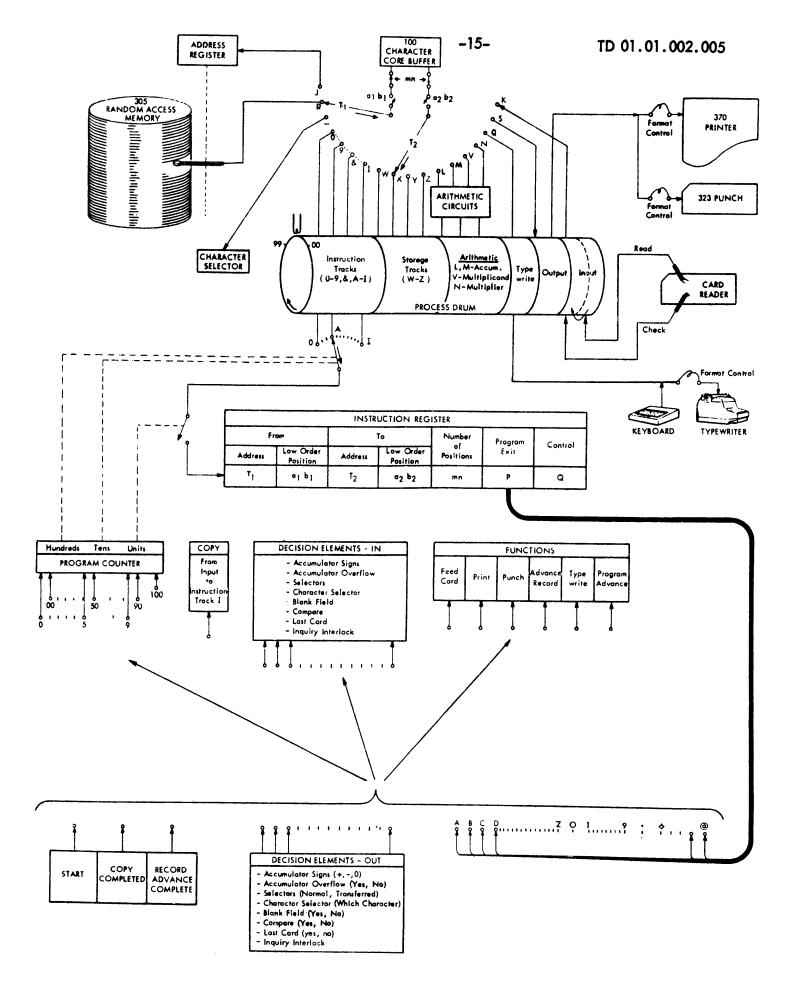

| Fig. 2  | Data Flow Chart of the IBM 305 RAMAC                                 | 15            |

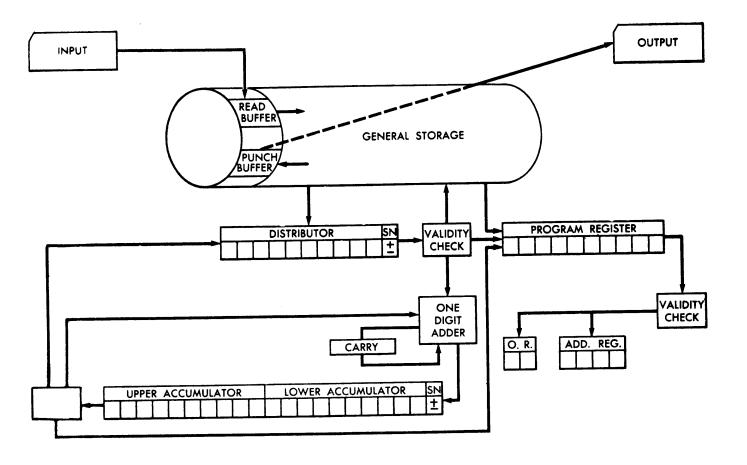

| Fig. 3  | Data Flow Chart of the IBM 650 Data Processing System                | 16            |

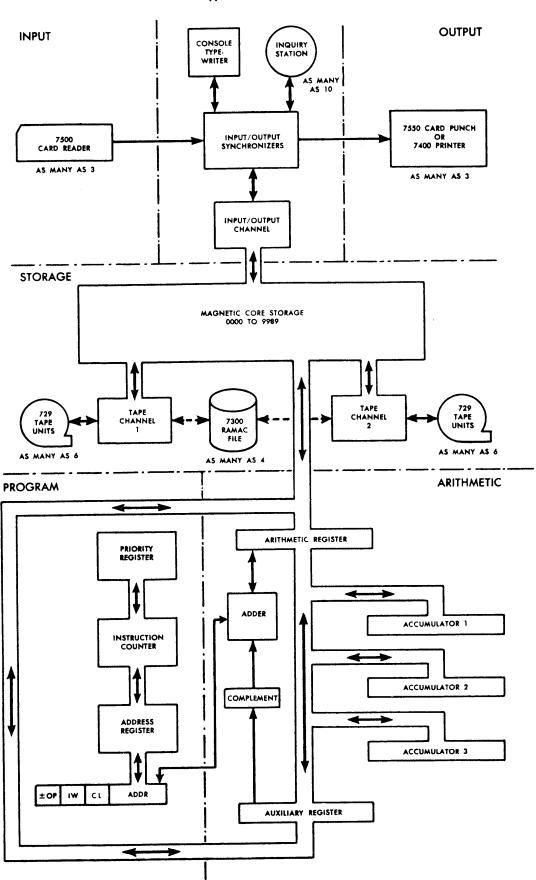

| Fig. 4  | Data Flow Chart of the IBM 7070 Data Processing System               | 17            |

| Fig. 5  | Data Flow Chart of the CPU of the IBM 705 Data Processing System     | 18            |

| Fig. 6  | Basic Binary Arithmetic Operations                                   | 20            |

| Fig. 7  | Simple Truth Tables for the Half Adder                               | 24            |

| Fig. 8  | Truth Tables for Sum and Carry for the Full Adder                    | 24            |

| Fig. 9  | Symbolic Logic for Equations 1) and 2), page 23                      | 24            |

| Fig. 10 | Two Half Adders Cascaded to Form a Full Adder in Symbolic Logic Form | 24            |

| Fig. II | Symbolic Description of BCD Adder                                    | 25            |

| Fig. 12 | Examples of Bingry-Coded Decimal (BCD) Addition                      | 26            |

|      | 10 | Allere I Clark Code                                                       | page |

|------|----|---------------------------------------------------------------------------|------|

|      |    | Addition and Subtraction in the "Excess-Three" Code                       | 27   |

| _    |    | Logic diagram of the 650 arithmetic adder                                 | 29   |

| •    |    | True complement logic used in the IBM 650                                 | 32   |

|      |    | Logical biquinary validity chech used in the IBM 650                      | 32   |

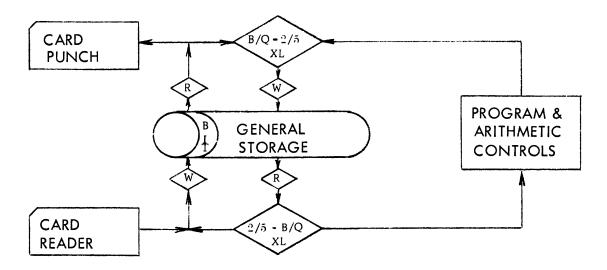

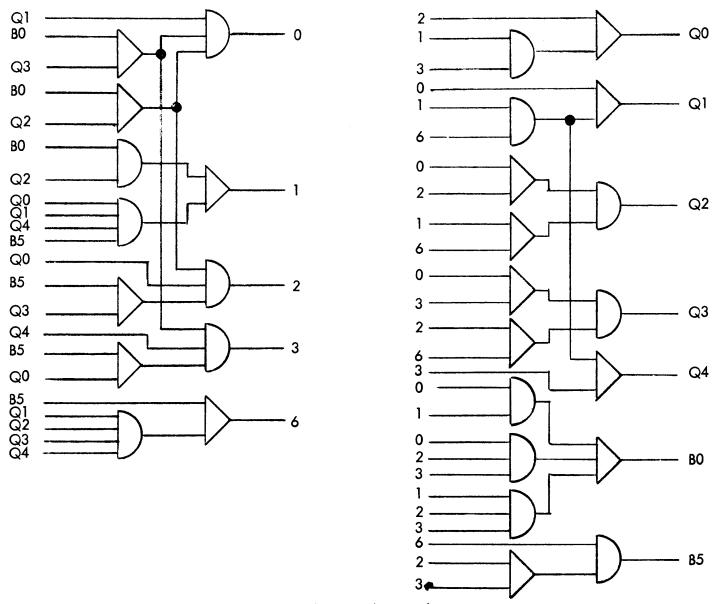

| _    |    | Data flow of B/Q- to 2/5 and 2/5-to-B/Q translators in the IBM 650        | 42   |

| Fig. |    | Symbolic Logic of B/Q-to-2/5 and $2/5$ -to-B/Q translators in the IBM 650 | 42   |

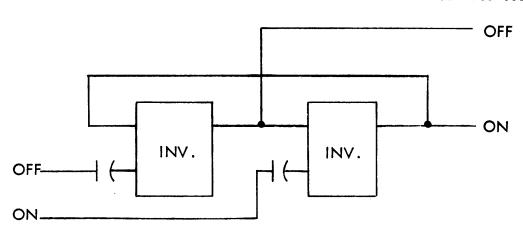

| Fig. | 19 | Trigger                                                                   | 47   |

| Fig. | 20 | Single Latch Trigger                                                      | 47   |

| Fig. | 21 | Double Latch Trigger                                                      | 47   |

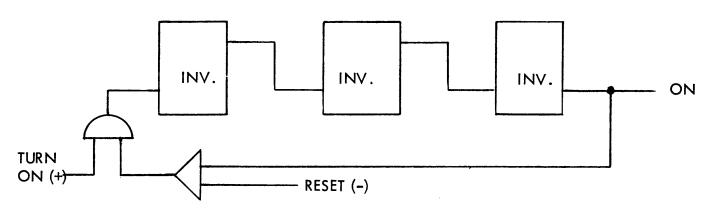

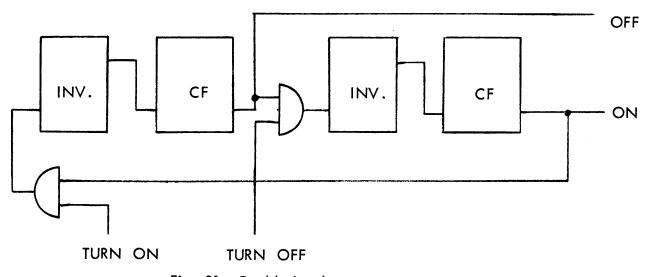

| Fig. | 22 | Overbeck Ring                                                             | 48   |

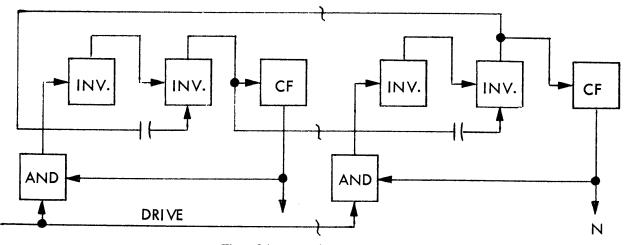

| Fig. | 23 | Inverter-coupled Ring                                                     | 48   |

| Fig. | 24 | Latch Ring                                                                | 48   |

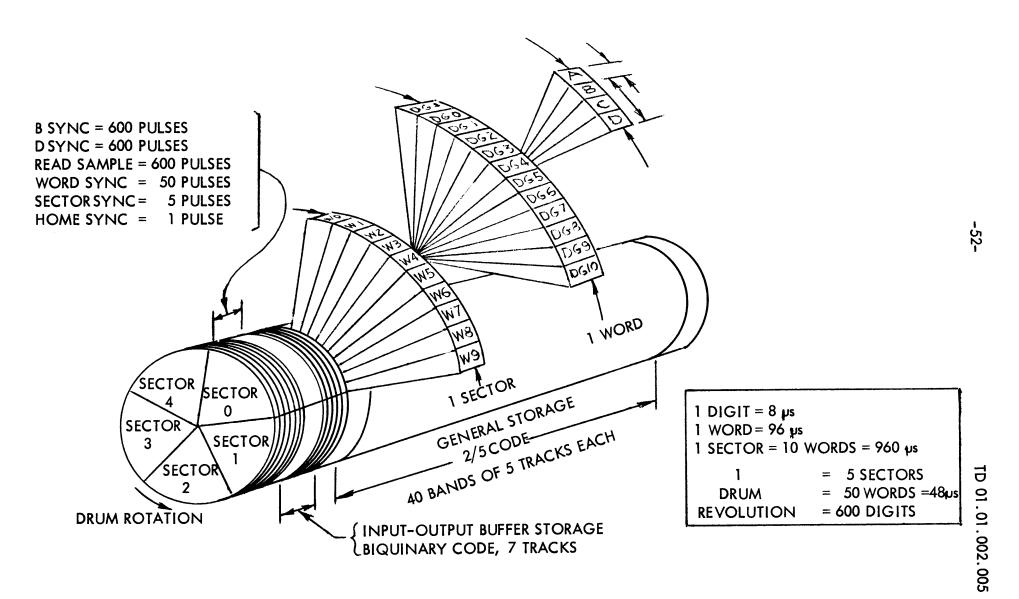

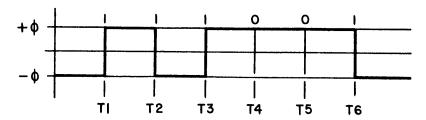

| Fig. | 25 | IBM 650 Drum Sectors and Timing                                           | 52   |

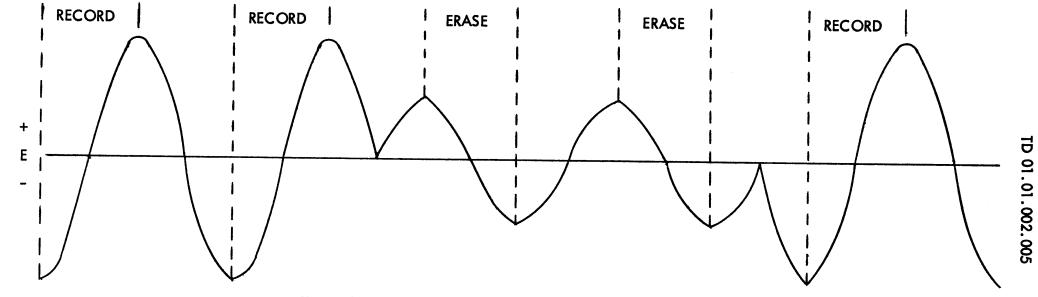

| Fig. | 26 | Residual Flux Pattern for Several Spots on Adjacent 650 Tracks            | 53   |

| Fig. | 27 | Induced Voltage Waveform of Adjacent 650 Tracks                           | 53   |

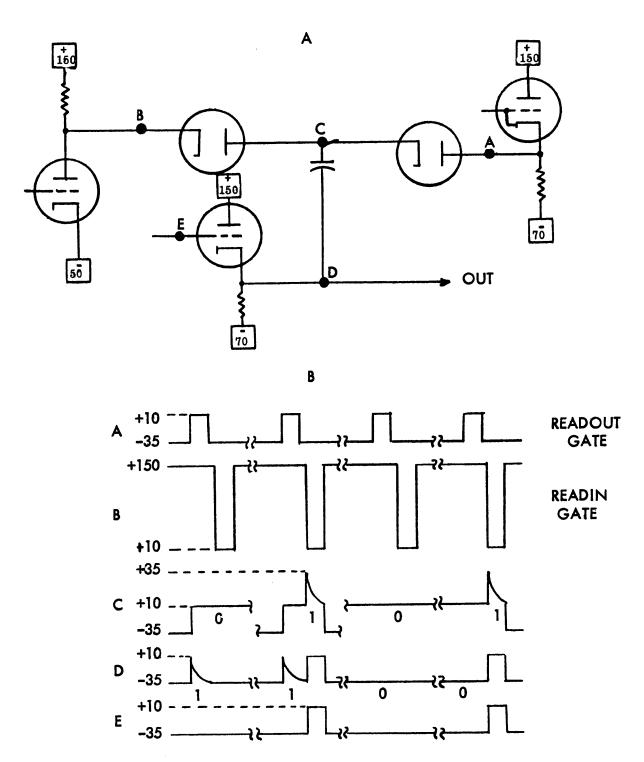

| Fig. | 28 | Capacitor Storage                                                         | 56   |

| Fig. | 29 | Capacitor Storage Cells Combined into a Matrix                            | 57   |

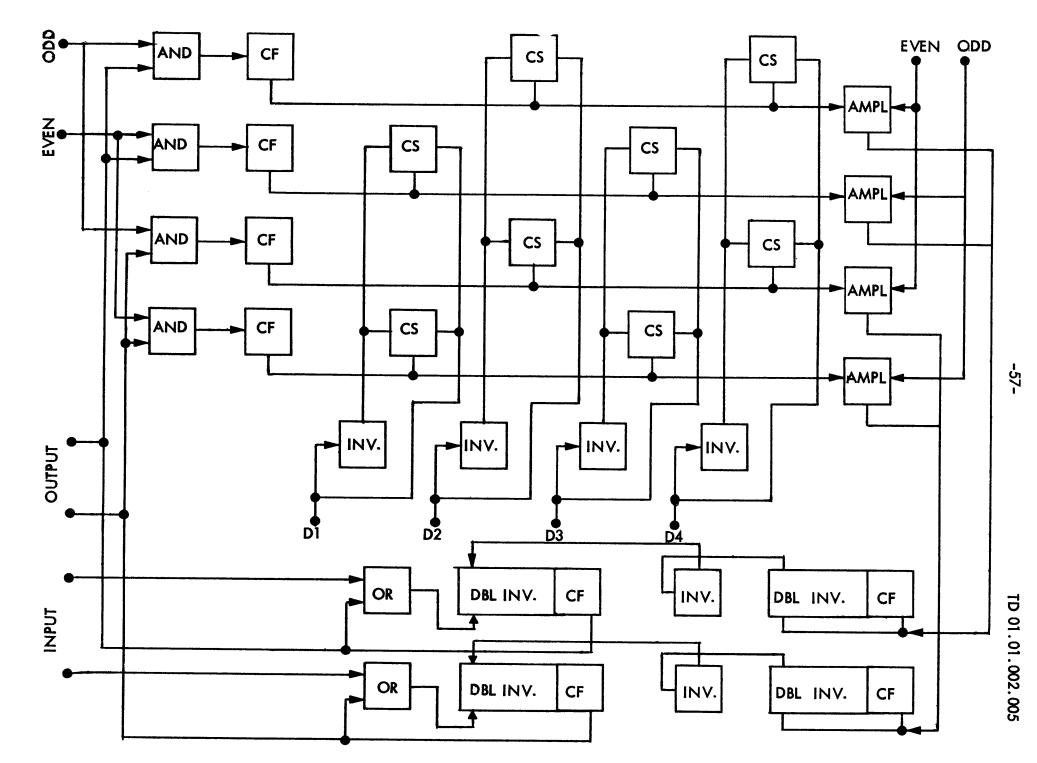

| Fig. | 30 | Ferrite hysteresis loop                                                   | 61   |

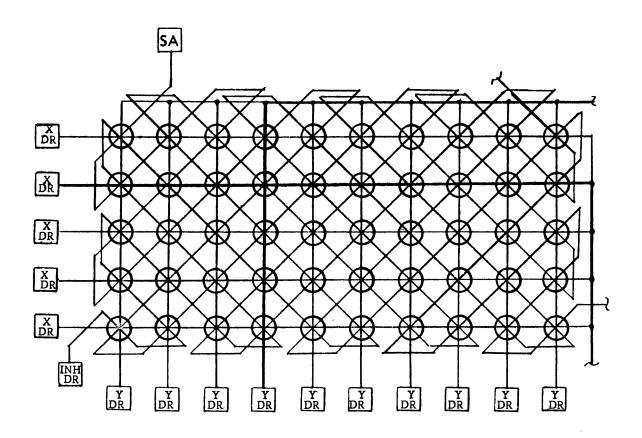

| Fig. | 31 | Ferrite memory plane                                                      | 61   |

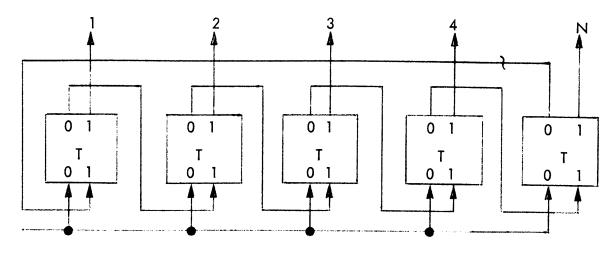

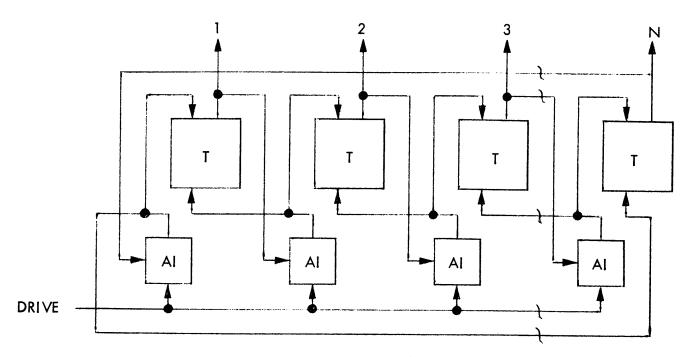

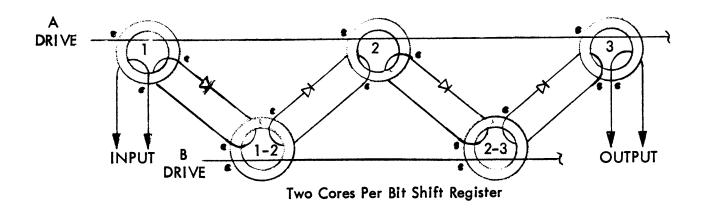

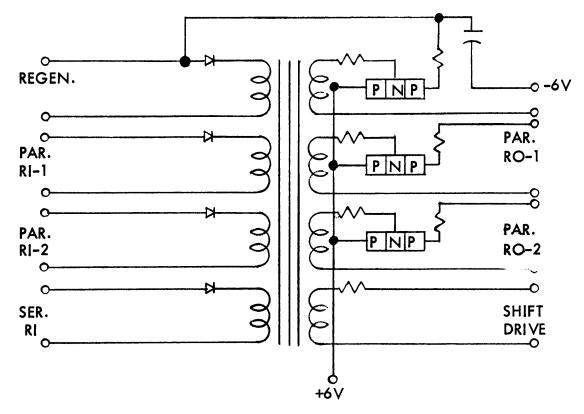

| Fig. | 32 | Basic Core Shift Register Circuits                                        | 64   |

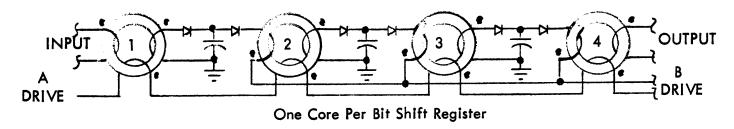

| Fig. | 33 | Circuit of One Bit in a 7070-Type Core Register                           | 64   |

| Fig. | 34 | Core Register System                                                      | 65   |

| Fig. | 35 | IBM 533 Card Reader and Punch                                             | 70   |

| Fig. | 36 | IBM 537 Computing Card Punch                                              | 70   |

| Fig. | 37 | IBM 7500 Card Reader                                                      | 70   |

| Fig. | 38 | IBM 7550 Card Punch                                                       | 71   |

| Fig. | 39 | Card input data flow for IBM 650                                          | 71   |

| Fig. | 40 | Card output data flow for IBM 650                                         | 71   |

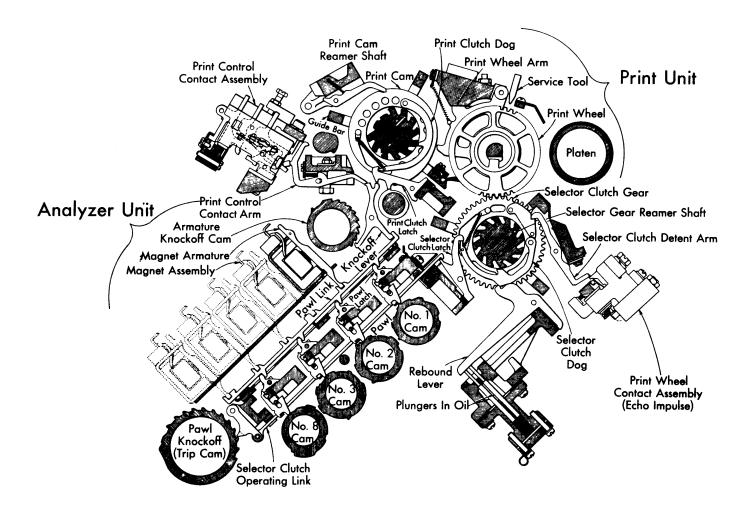

| Fig. | 41 | Printing Mechanism of the IBM 407 Accounting Machine                      | 75   |

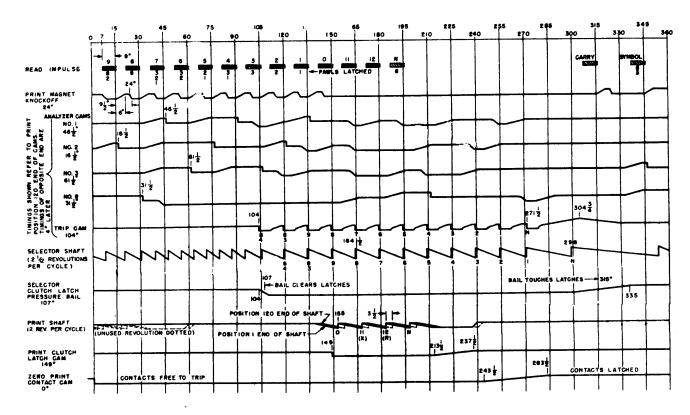

| Fig. | 42 | Mechanical timing chart for the IBM 407 Print Mechanism                   | 76   |

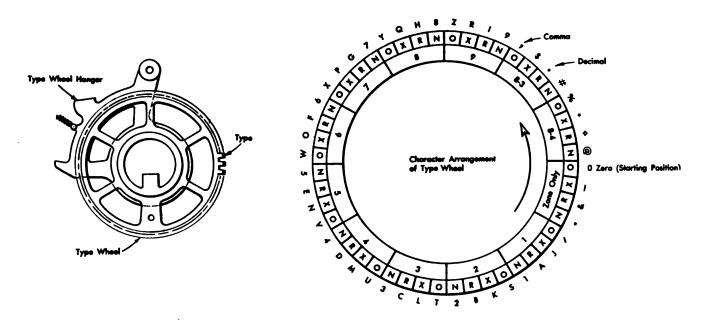

| Fig. | 43 | IBM 407 Print Mechanism typewheel                                         | 76   |

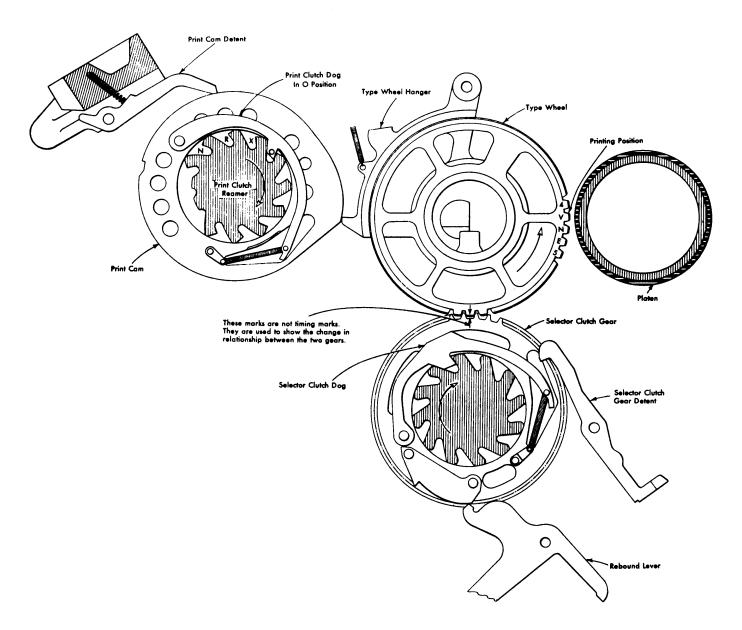

| Fig. | 44 | Print Mechanism positioned for printing V                                 | 77   |

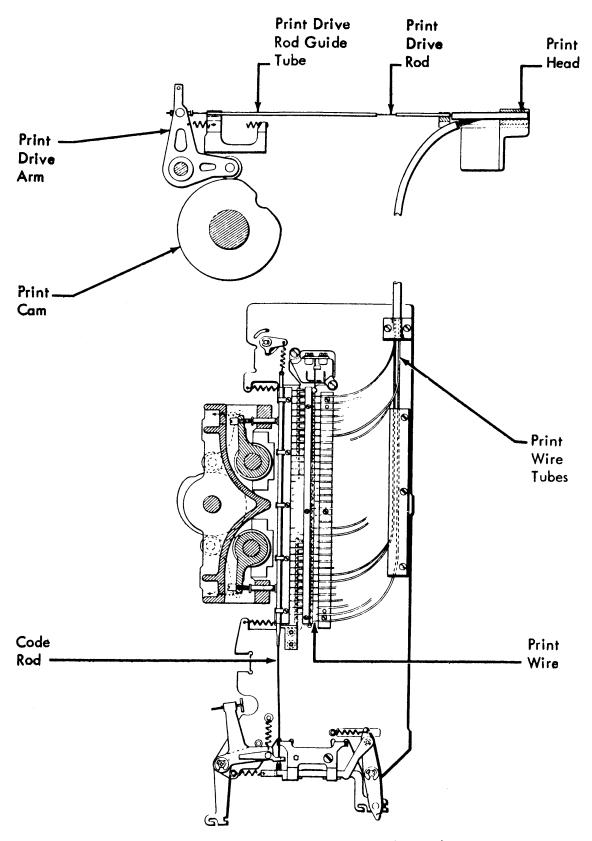

| Fig. | 45 | Print mechanism plate and mechanical drive                                | 78   |

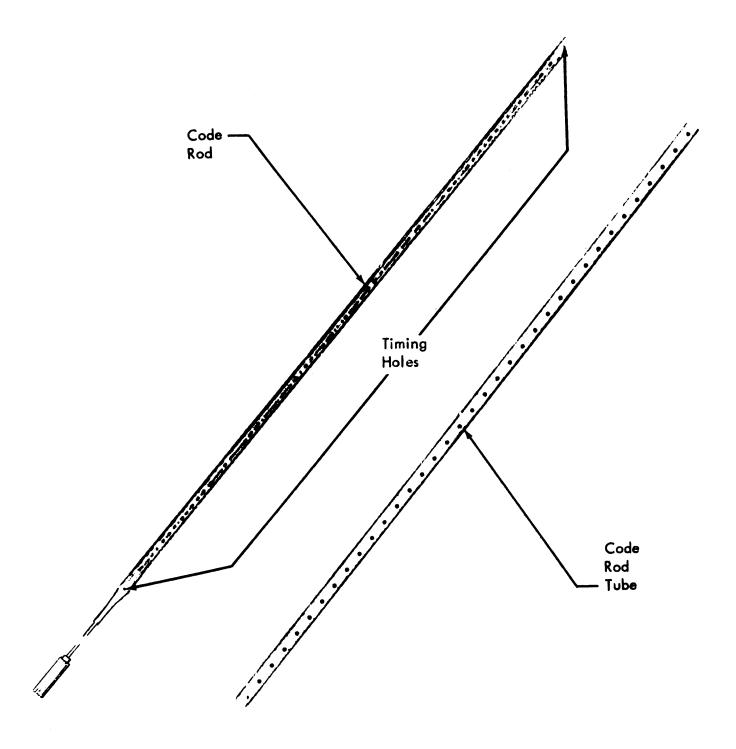

| Fia. | 46 | Code rod and tube for the IBM Wire Printer                                | 79   |

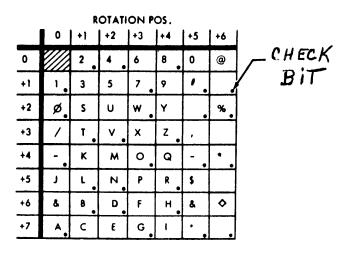

| Fig. 47 Rotational and Lateral Posi  | itions of the Code Rod   | page<br>80 |

|--------------------------------------|--------------------------|------------|

| Fig. 48 Mechanical Wedge Values      | <b>i</b>                 | 80         |

| Fig. 49 Available Character Set      |                          | 80         |

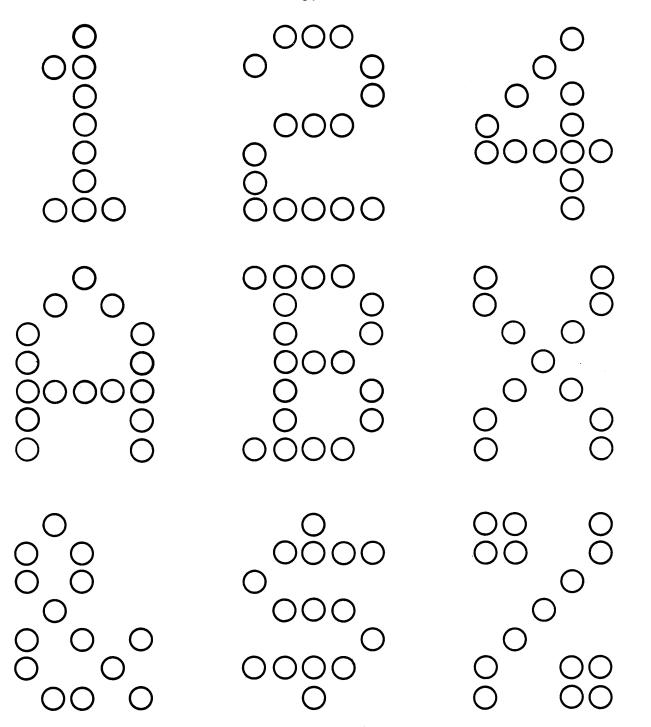

| Fig. 50 Dot Patterns Produced by a   | a Print Wire Matrix      | 81         |

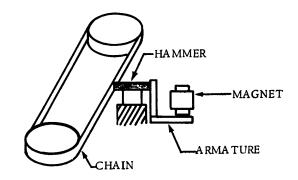

| Fig. 51 Positioning of the Print Cha | ain                      | 84         |

| Fig. 52 Descriptive Drawing of the   | Print Mechanism          | 84         |

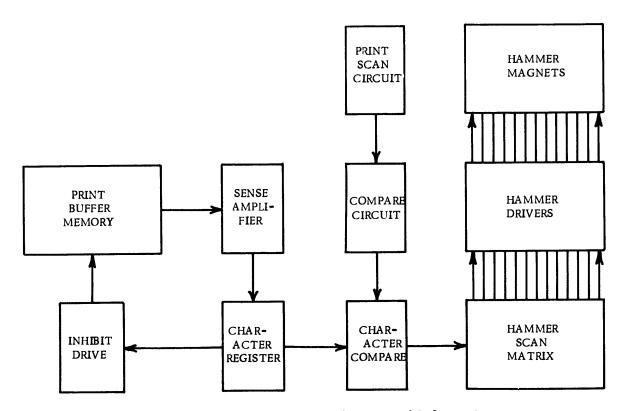

| Fig. 53 Data Flow of the Printed In  | nformation               | 84         |

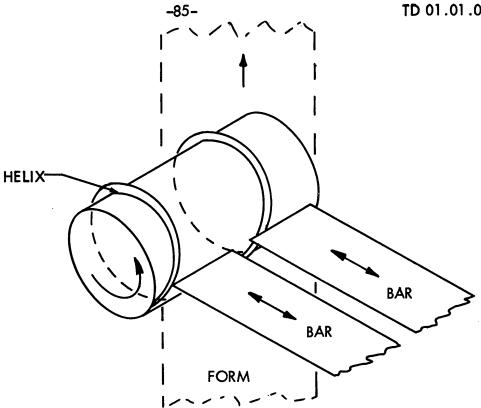

| Fig. 54 IBM Bar-And-Helix Printer    | r                        | 85         |

| Fig. 55 Formation of the Figures "   | l" and "S"               | 85         |

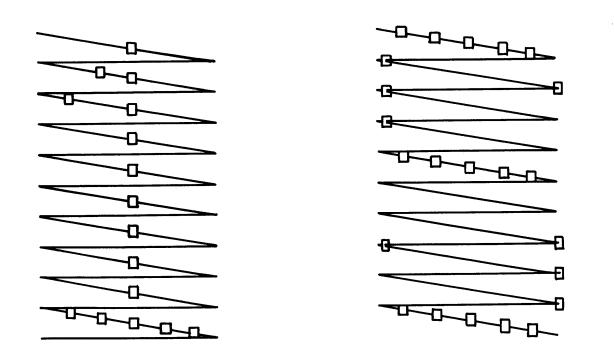

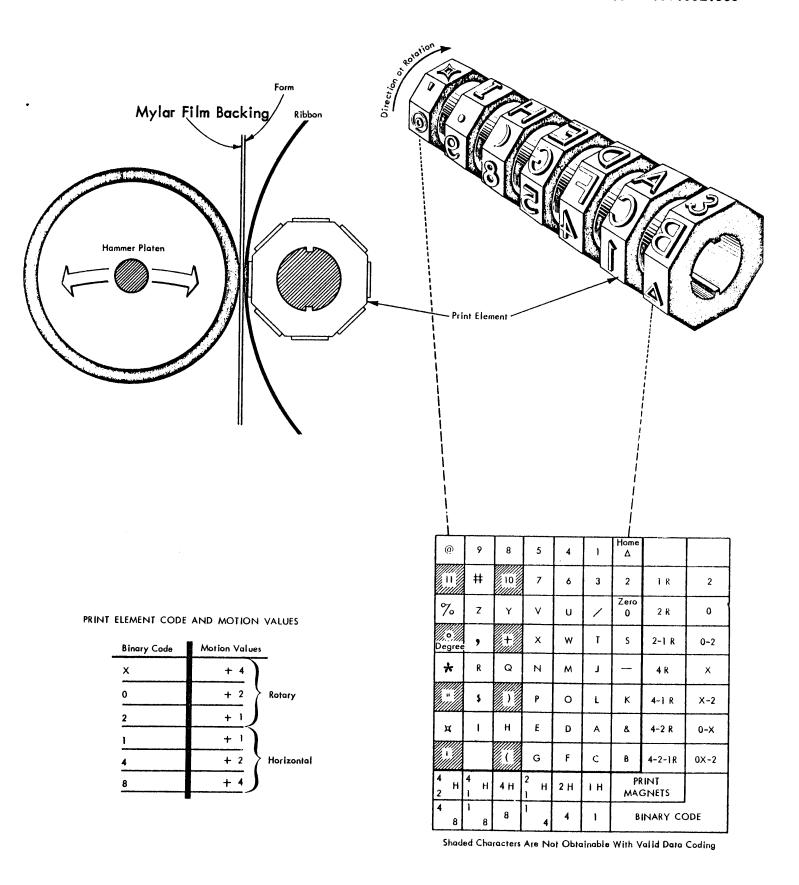

| Fig. 56 Print Element Positioning i  | n the IBM Stick Printer  | 86         |

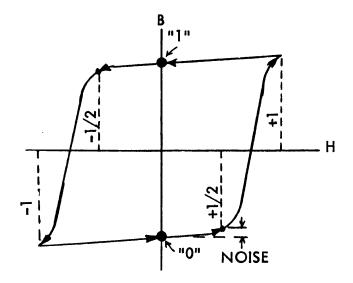

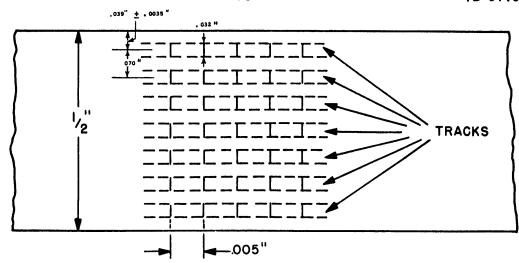

| Fig. 57 Geometry of information fl   | lux patterns on tape     | 90         |

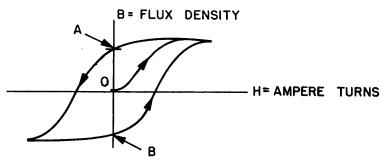

| Fig. 58 Hysteresis loop of tape cod  | ating                    | 90         |

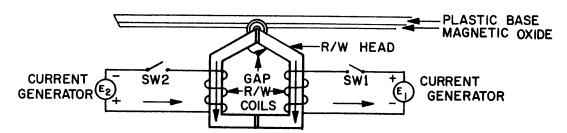

| Fig. 59a Schematic diagram of rea    | d/write head             | 90         |

| Fig. 59b Flux-pattern of typical in  | nformation sample        | 90         |

| Fig. 59c Resulting flux pattern      |                          | 90         |

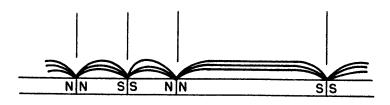

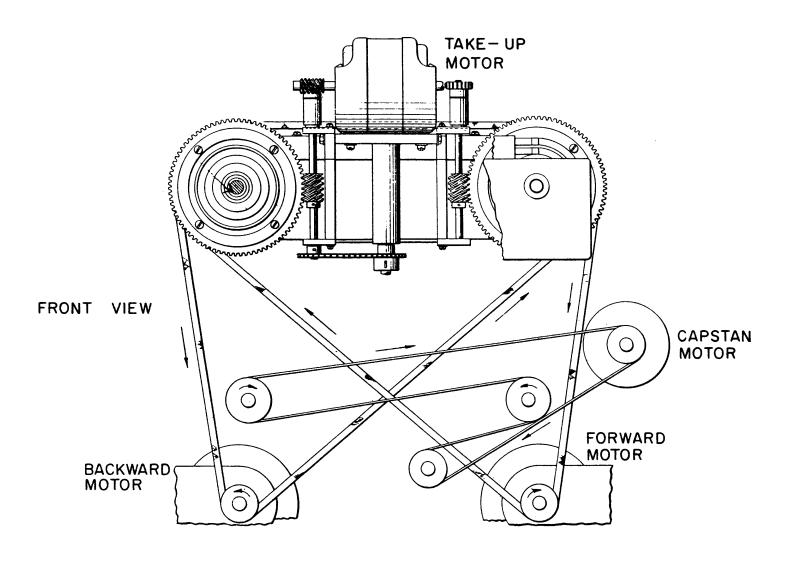

| Fig. 60 Front view of the IBM 727    | Tape Drive Unit          | 91         |

| Fig. 61 Tape Drive Unit Control Ke   | eys and Indicator Lights | 91         |

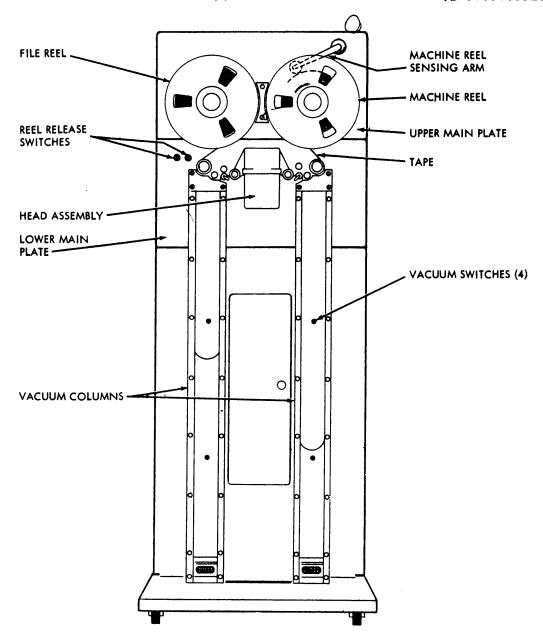

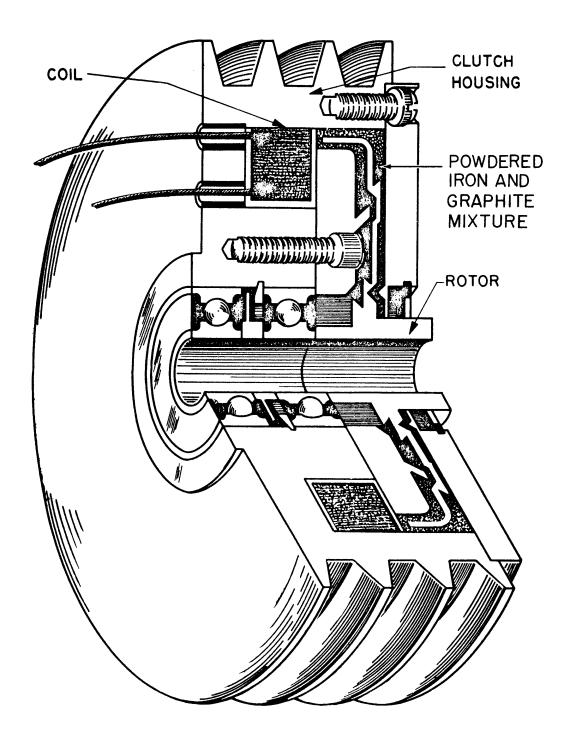

| Fig. 62 Sectional view of magnetic   | c clutch                 | 92         |

| Fig. 63 Drive motors and pulleys     |                          | 93         |

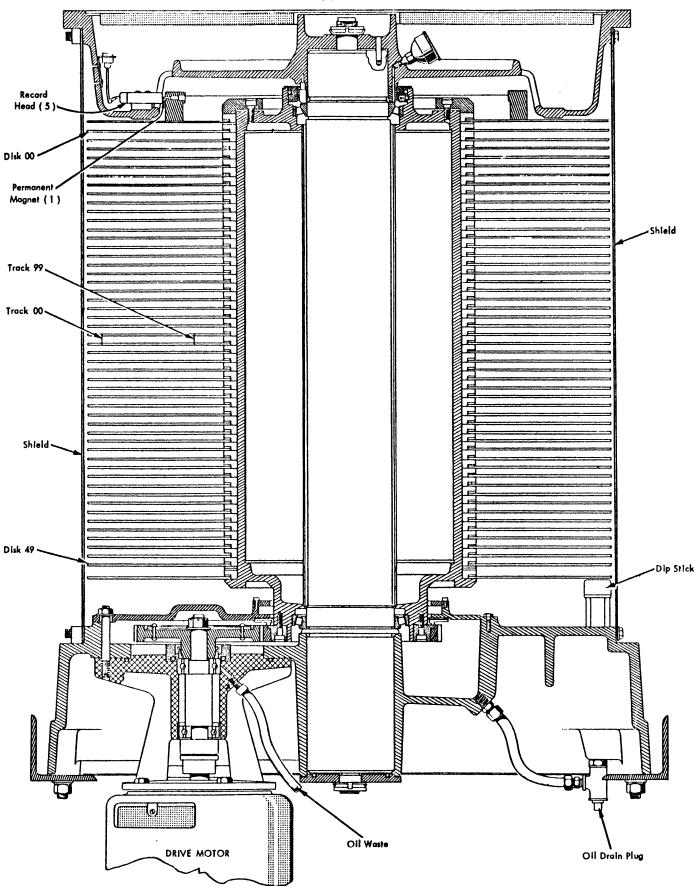

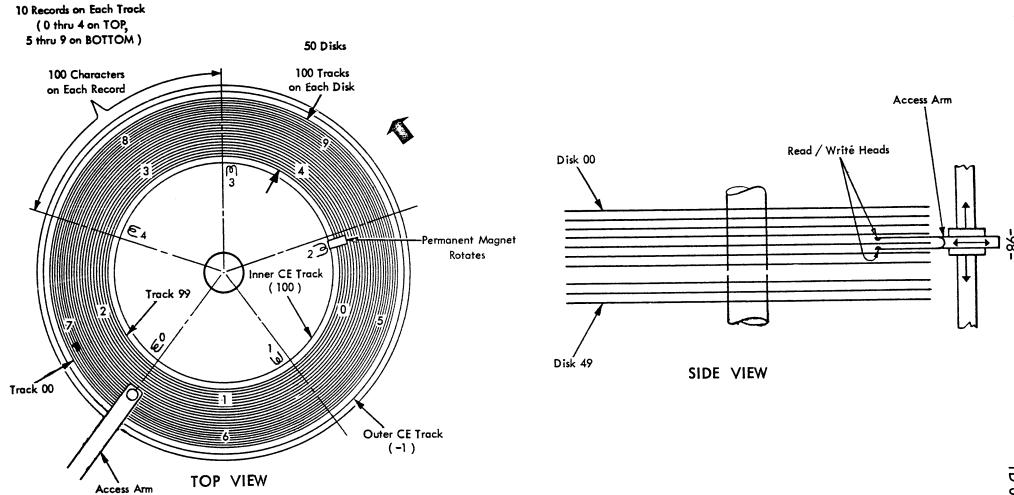

| Fig. 64 Disk Array of the RAMAC      | Disk File                | 96         |

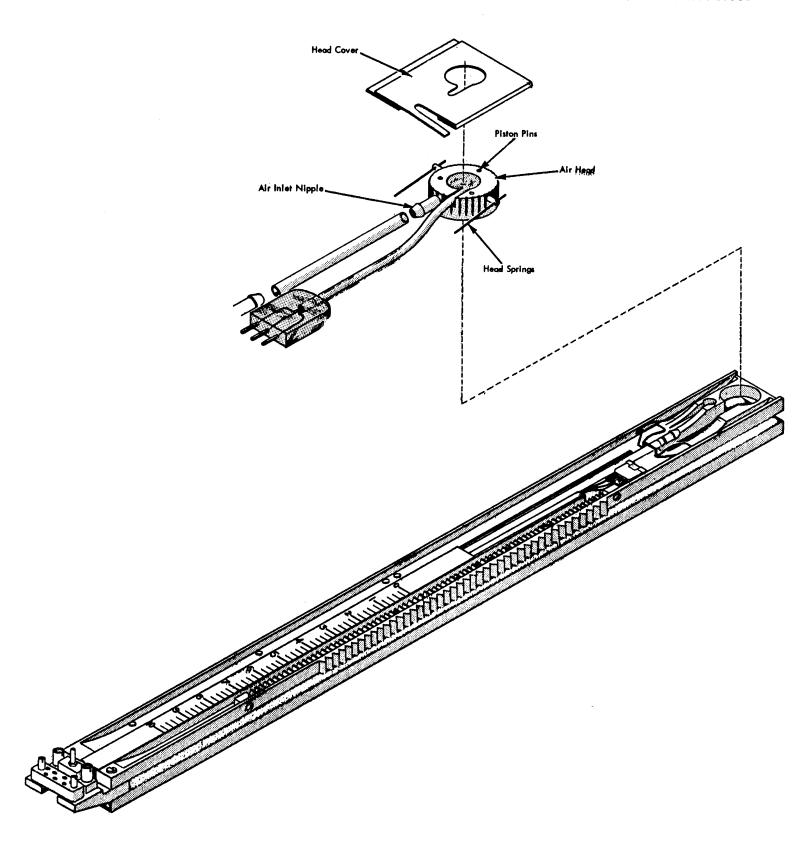

| Fig. 65 Exploded view of the RAM.    | AC Access Arm            | 65         |

| Fig. 66 Positioning of the Access A  | Arm and Disk Array       | 98         |

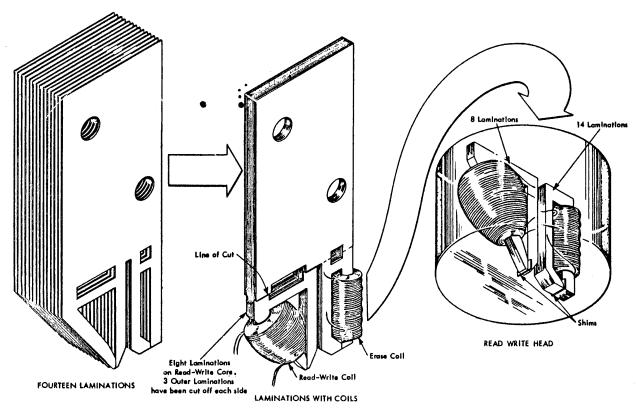

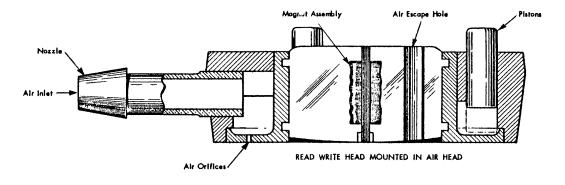

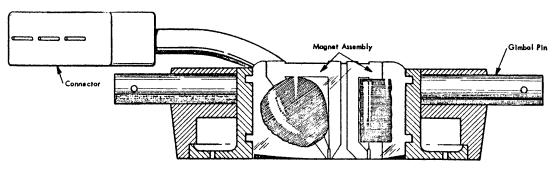

| Fig. 67 Construction details of the  | read/write head          | 99         |

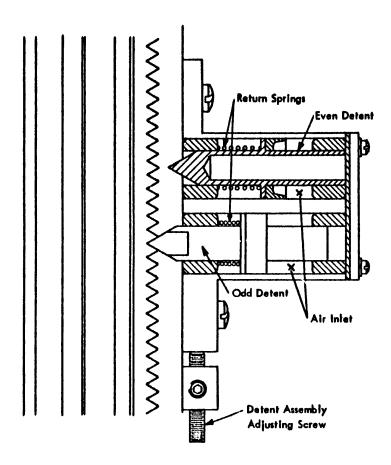

| Fig. 68 Track detent                 |                          | 100        |

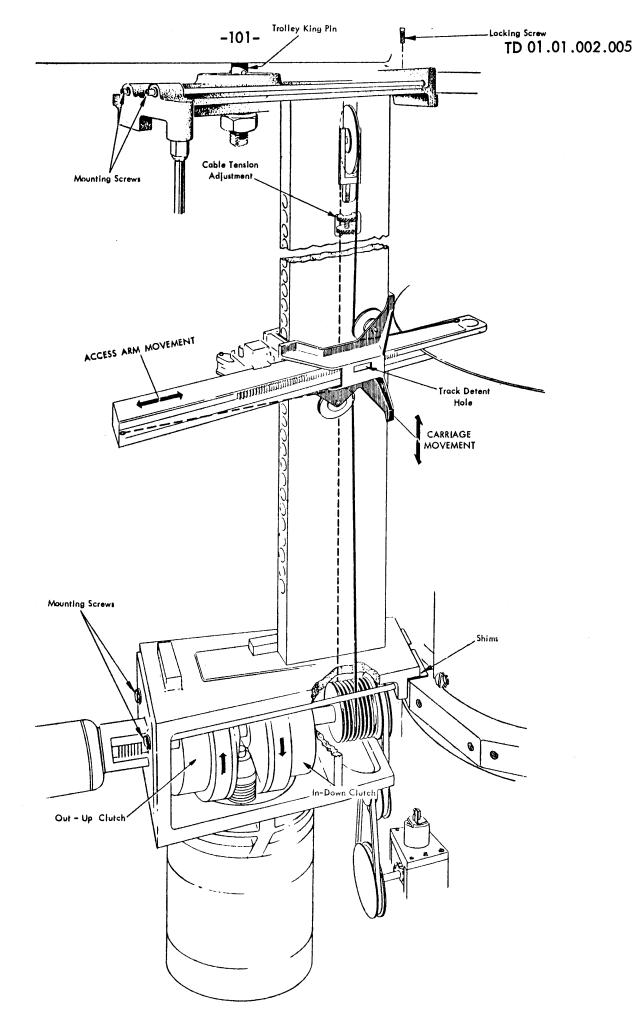

| Fig. 69 RAMAC Access Mechanism       | ı                        | 101        |

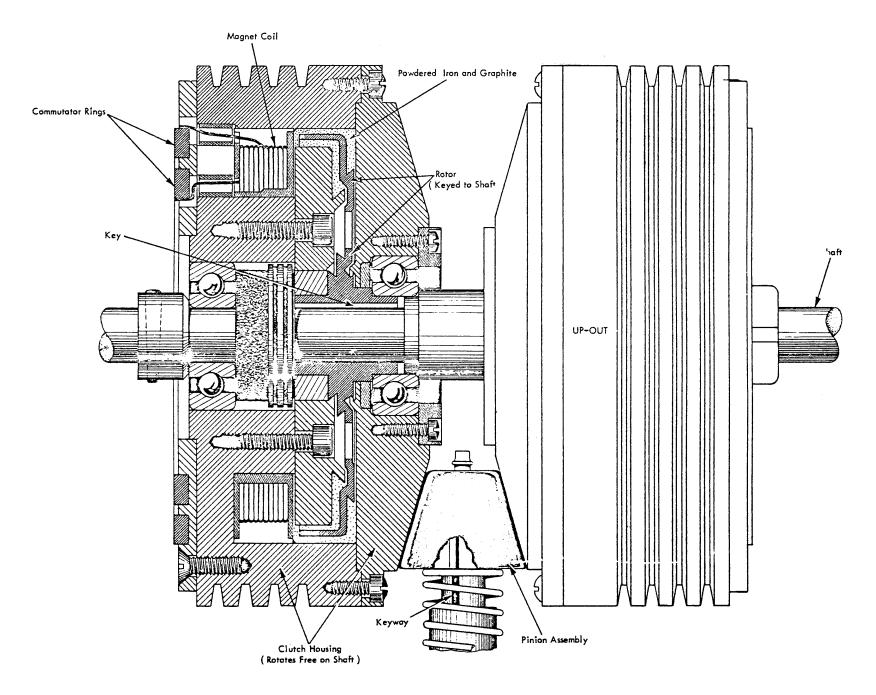

| Fig. 70 Magnetic clutch assembly     |                          | 102        |

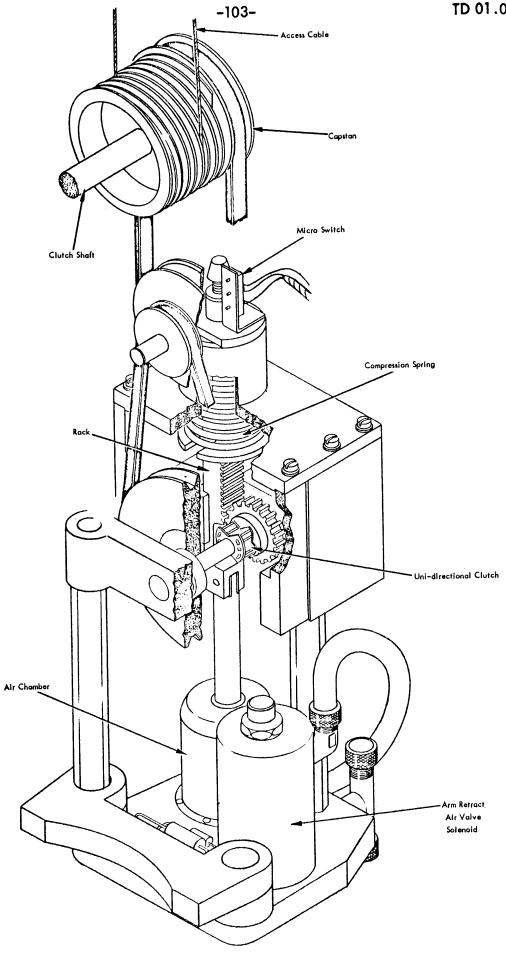

| Fig. 71 Arm retraction mechanism     |                          | 103        |

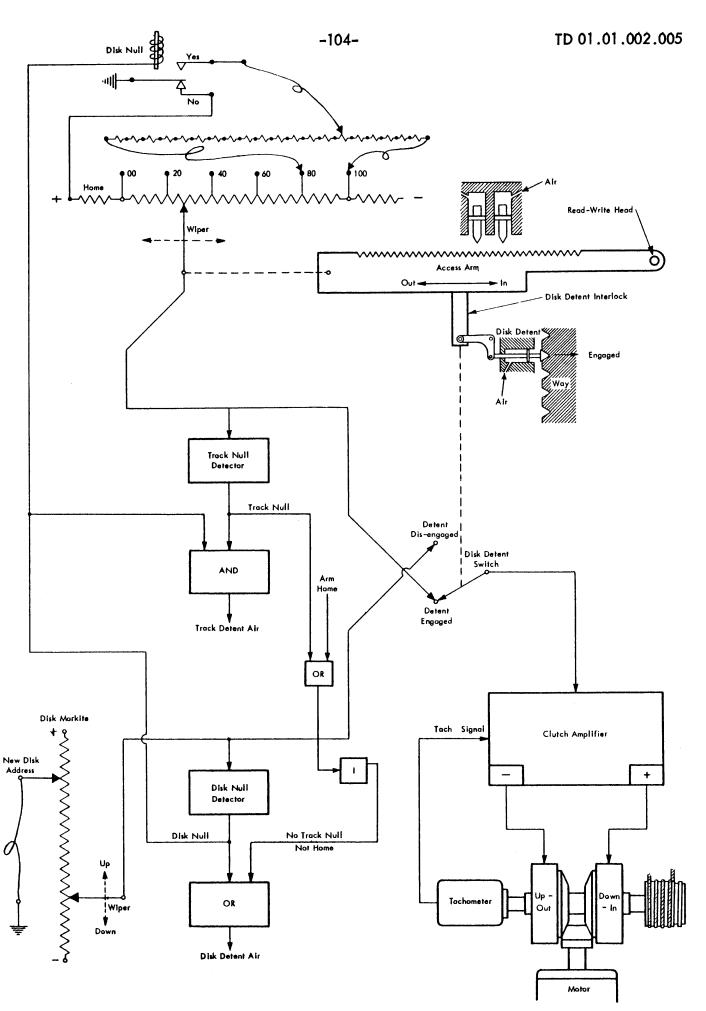

| Fig. 72 Access Control Circuit Log   | ic                       | 104        |

# **FOREWORD**

This report is a compendium of course notes used in an Engineering Training Program course presented at IBM Endicott during the latter part of 1959. The material has been compiled for distribution within IBM to serve primarily as a convenient reference source. The author hopes that this document, brief in content but comprehensive in scope, will serve the reader wishing to refresh his memory on some historical or contemporary aspect of digital computation.

#### I EARLY COMPUTING DEVICES - EVOLUTION OF THE ABACUS

The oldest known device which satisfies the basic definition of a digital computer is the abacus. Its historical origin has not yet been precisely established. In various forms and by various names it has been used since as early as the 6th century B.C. In China since the 12th century A.D. it has been called the suan-pan, with two binary and five quinary beads per position and as many as two dozen digit positions. The Japanese equivalent is the soroban dating back to the 16th century, with just one binary and four quinary beads since the other two are basically redundant.

The Russian version of the abacus is known as the e'choty and contains ten beads per position, the equivalent of two Japanese sorobans laid side-by-side as mirror-images. Available sources do not describe its method of operation. In Turkey this device is called the coulba; in Armenia, the choreb.

Devices similar in technique were the bamboo counting rods used in China until the 19th century, the counting pebbles used by the ancient Egyptians (Herodotus, 450 B.C.), and the "line abacus" used throughout Europe as late as the 18th century. The line abacus was generally a wax-covered table with ruled lines to represent the decimal denominations in bi-quinary form and "X" symbols to take the place of the beads. Modified versions also evolved for such systems as pounds, shillings, and pence.

The suan-pan and soroban are still widely used today in native shops in Asia and in American Chinatowns. An interesting story concerns an American desk calculator manufacturer, whose "queen-of-the-line" machine was decidely bested at a public exhibition in Tokyo soon after World War II. The event was intended to be a promotional stunt to publicize the advantages of the desk calculator, compared to a soroban-equipped Japanese accountant.

In addition to the popularity of the suan-pan and the soroban mental arithmetic was a highly-developed art during the preceding three or four centuries. There are dozens of outstanding "arithmetic geniuses" recorded in mathematical history whose ability to "think with numbers" is amazing even today. Most of them based their abilities on a fantastic memory for odd numerical facts, such as a list of all prime numbers up to a million. It is interesting to note that almost all of them were self-taught and that no common techniques evolved from their experiences.

# A. HALVING AND DOUBLING (MULTIPLICATION)

In another vein, a very interesting method of multiplication developed and is still widely used by some of the more primitive tribes in Africa. This method employed the system of "halving-and-doubling," in which by successive binary division of the multiplier and binary multiplication of the multiplicand produces a decimal product. The technique is so simple that with a little practice almost anyone can do it "in his head."

The following is a simple example of the basic process:

Problem:

$$13 \times 17 = ?$$

Solution:  $2 )13$

$2 )6 \text{ r. } 1 \longrightarrow 17 \longrightarrow 17$

$2 )3 34$

$2 )1 \text{ r. } 1 \longrightarrow 68 \longrightarrow 68$

$36 \longrightarrow 136 \longrightarrow 136$

$36 \longrightarrow 136 \longrightarrow 136$

$37 \longrightarrow 136 \longrightarrow 136$

$38 \longrightarrow 136 \longrightarrow 136$

$39 \longrightarrow 136 \longrightarrow 136$

## II BABBAGE'S DIFFERENTIAL ANALYTICAL ENGINE

Charles Babbage lived in England and did his most significant work during the first half of the 19th century. Like Thomas Edison, James Watt, and other inventive geniuses of that era, he was born long before his time. That is to say the dreams and goals of these people could not satisfactorily be carried out within the bounds of their contemporary technology.

To Babbage belongs the honor of originating the basic principles of calculating equipment we know today as adding machines and desk calculators. But Babbage's most significant contribution of all to the art of digital computing devices was a system concept which never reached fruition during his lifetime. In spite of never having achieved the creative satisfaction of seeing his "brain-child" constructed, Babbage's definitions, organization, and specifications for his "analytical engine" are still today an excellent generic description of what we call "stored-program digital computers." This is true in spite of, rather than because of, the rapid evolutionary progress of mechanical, electrical, and electronic technology during the next century.

Probably the personage who understood Babbage best of all in his own time was a lady mathematician of some reknown, the Countess of Lovelace. The Countess helped Babbage's personal cause to the extent of explaining his work in terms which the other mathemeticians and their patrons and government agencies with available capital to finance it could understand. As a result of this help, Babbage was finally able to achieve a working model of his "difference engine" during his later life. This model is still in operating condition and is on display in a museum. In view of the rudimentary level of technology at that time, in which every part of an assembly had to be fitted by cut-and-try methods, it was manufacturing accomplishment of the highest order.

The following is a brief description of this analytical\*engine by a contemporary, L. F. Menabrea, of Turin, Office of the Military Engineers:

"Those labours which belong to the various branches of the mathematical sciences, although on first consideration they seem to be the exclusive province of intellect, may, nevertheless, be divided into two distinct sections; one of which may be called the mechanical, because it is subjected to precise and invariable laws, that are capable of being expressed by means of the operations of matter; while the other, demanding the intervention of reasoning, belongs more specially to the domain of the understanding. This admitted, we may propose to execute, by means of machinery, the mechanical

branch of these labours, reserving for pure intellect that which depends on the reasoning faculties. Thus the rigid exactness of those laws which regulate numerical calculations must frequently have suggested the employment of material instruments, either for executing the whole of such calculations or for abridging them; and thence have arisen several inventions having this object in view, but which have in general but partially attained it. For instance, the much-admired machine of Pascal is now simply an object of curiosity, which, whilst it displays the powerful intellect of its inventor, is yet of little utility in itself. Its powers extended no further than the execution of the four first operations of arithmetic, and indeed were in reality confined to that of the two first, since multiplication and division were the result of a series of additions and subtractions. The chief drawback hitherto on most of such machines is, that they require the continual intervention of a human agent to regulate their movements, and thence arises a source of errors; so that, if their use has not become general for large numerical calculations, it is because they have not in fact resolved the double problem which the question presents, that of correctness in the results, united with economy of time.

"Struck with similar reflections, Mr. Babbage has devoted some years to the realization of a gigantic idea. He proposed to himself nothing less than the construction of a machine capable of executing not merely arithmetical calculations, but even all those of analysis, if their laws are known. The imagination is at first astounded at the idea of such an undertaking; but the more calm reflection we bestow on it, the less impossible does success appear, and it is felt that it may depend on the discovery of some principle so general, that if applied to machinery, the latter may be capable of mechanically translating the operations which may be indicated to it by algebraical notation. The illustrious inventor having been kind enough to communicate to me some of his views on this subject during a visit he made at Turin, I have, with this approbation, thrown together the impressions they have left on my mind. But the reader must not expect to find a description of Mr. Babbage's engine; the comprehension of this would entail studies of much length; and I shall endeavour merely to give an insight into the end proposed, and to develop the principles on which its attainment depends.

"I must first premise that this engine is entirely different from that of which there is a notice in the 'Treatise on the Economy of Machinery,' by the same author. But as the latter gave rise to the idea of the engine in question, I consider it will be a useful preliminary briefly to recall what were Mr. Babbage's first essays, and also the circumstances in which they originated."

#### A. BACKGROUND OF BABBAGE'S MACHINE

It is well known that in the early part of the nineteenth century the French government, wishing to promote the extension of the decimal system, had ordered the construction of logarithmical and trigonometrical tables of enormous extent. M. de Prony, who had been entrusted with the direction of this undertaking, divided it into three sections, to each of which were appointed a special class of persons. In the first section the formulae were so combined as to render them subservient to the purposes of numerical calculation. In the second section these same formulae were calculated for values of the variable, selected at certain successive distances. Under the third section, comprising about eighty individuals, who were mostly only acquainted with the two first rules of arithmetic, values which were intermediate to those calculated by the second section were interpolated by simple additions and subtractions.

#### B. THE MATHEMATICS OF BABBAGE'S MACHINE

Since a similar undertaking was begun in England, Babbage decided that the operations performed under the third section might be executed by a machine. This concept was realized by a mechanism which had been partially assembled and to which the name "Difference Engine" was applicable because of the principle upon which its construction is founded. To give some notion of this principle it will suffice to consider the series of whole square numbers, 1, 4, 9, 16, 25, 36, 49, 64, etc. By subtracting each of these from the succeeding one we obtain a new series, which can be termed the "Series of First Differences," consisting of the numbers 3, 5, 7, 9, 11, 15, etc. Subtracting from each of these the preceding one we obtain the Second Differences which are all constant and equal to 2. We may represent this succession of operations, and their results, in the following table:

|   | A<br>Column of<br>Square<br>Numbers | B<br>First<br>Differ-<br>ences | C<br>Second<br>Differ-<br>ences |

|---|-------------------------------------|--------------------------------|---------------------------------|

|   | 1                                   | 3                              |                                 |

|   | 4                                   |                                | 2b                              |

|   |                                     | 5                              | 2d                              |

| a | ۶                                   | 7                              |                                 |

| С | 16                                  |                                | 2                               |

|   | 25                                  | 9                              | 2                               |

|   | 2.5                                 | 11                             |                                 |

|   | 36                                  |                                |                                 |

Table 1 - Subtraction Chart of Whole Square Numbers

From the mode in which the two last columns B and C have been formed, it is easy to see that if, for instance, we desire to pass from the number 5 to the succeeding one 7, we must add to the former the constant difference 2. Similarly, if from the square number 9 we would pass to the following one 16, we must add to the former the difference 7, which difference is in other words the preceding difference 5, plus the constant difference 2. Or again, which arrives at the same result to obtain 16 we have only to add together the three numbers 2, 5, 9, placed obliquely in the direction ba. Similarly, we obtain the number 25 by summing up the three numbers placed in the oblique direction dc. Commencing by the addition 2 + 7, we have the first difference 9 consecutively to 7. Adding 16 to the 9 we have the square 25.

We see then that the three numbers 2, 5, 9 being given, the whole series of successive square numbers, and that of their first differences likewise, may be obtained by means of simple additions.

Now, to conceive how these operations may be reproduced by a machine, suppose the latter to have three dials, designated as A, B, C, on each of which are traced, say a thousand divisions, by way of example, over which a needle shall pass. The two dials, C, B, shall have in addition a registering hammer, which is to give a number of strokes equal to that of the divisions indicated by the needle. For each stroke of the registering hammer of the C, the needle B shall advance one division. Similarly, the needle A shall advance one division for every stroke of the registering hammer of the dial B. Such is the general disposition of the mechanism.

This being understood, let us at the beginning of the series of operations we wish to execute, place the needle C on the division 2, the needle B on the division 5, and the needle A on the division 9. Let us allow the hammer of the C to strike; it will strike twice, and at the same time the needle B will pass over two divisions. The latter will then indicate the number 7, which succeeds the number 5 in the column of first differences. If we now permit the hammer of the dial B to strike in its turn, it will strike seven times, during which the needle A will advance seven divisions; these added to the nine already marked by it, will give the number 16, which is the square number consecutive to 9. If we now recommence these operations, beginning with the needle C, which is always to be left on the division 2, we shall perceive that by repeating them indefinitely, we may successively reproduce the series of whole square numbers by means of a very simple mechanism.

### C. THEORY OF BABBAGE'S MACHINE

The theorem of the construction of the machine we have just been describing is based on a particular case of the following more general theorem: That if in any polynomial whatever, the highest power of whose variable is m, this same variable be increased by equal degrees; the corresponding values of the polynomial then calculated, and the first, second, third, etc., differences of these be taken (as for the preceding series of squares); the mth differences will all be equal to each other. So that in order to reproduce the series of values of the polynomial by means of machine analogous to the one previously described it is sufficient that there be (m + 1) dials, having the mutual relations we have indicated. As the differences may be either positive or negative, the machine will have a contrivance for either advancing or retrograding each needle, according as the number to be algebraically added may have the sign plus or minus.

A "human computer" working at a desk needs a calculating machine, reference books of tables, pen and paper with which to record the intermediate results in his calculations, and instructions as to how to proceed. But that is not all. Computing is something of an art, and the human computer will be inefficient and may not get very far unless he has some power of discrimination which enables him to interpret his instructions in the light of results which his computations have produced, and if need be, to modify his procedure accordingly. The power of discrimination of which a human operator is capable cannot be exercised automatically by any of the machines which we have discussed so far. Their potentialities are therefore limited.

Babbage clearly understood the restrictions imposed by the inability of a machine to make decisions for itself. He was able to take the next step and to suggest how to endow a machine with the minimum amount of "intelligence" which it needs. As he expressed it, he made the machine "bite its own tail." It is entirely due to these ideas of his that the modern computing machines to which we shall devote the rest of this report are so fast, so flexible, and capable of such an astonishing variety of operations.

# D. DATA PROCESSING SYSTEM REQUIREMENTS

If a data processing system is to perform the functions of a human computer, it must possess:

- 1. An arithmetic unit, capable of performing the normal operations of arithmetic. Babbage called this unit the mill.

- 2. A memory; that is to say a mechanism which will retain numbers needed in the calculation and also the instructions which will be needed to define successive stages in the computation. Babbage called this part the store. He planned to store 1,000 numbers, each of 50 decimal digits.

- 3. A built-in power of judgment, which will enable the machine to choose, according to prescribed criteria, the course which the computation has to take.

- 4. An input-output mechanism which allows the operator to feed numbers and "instructions" into the machine, and to extract from it the results of a calculation.

As we have already stated, Babbage planned to use punched cards for input. He also planned to use them for auxiliary storage; as tables of functions; further, Babbage also proposed using punched cards as one form of output. But realizing as he did the risk of error in copying tables by hand, he proposed making the machine set up its results in type where necessary. Modern machines use both tape and card for input and output and print out their results automatically as well. The sheets so prepared can then be reproduced without error by photo-lithography.

From this account it is evident that Babbage had a thorough understanding of the underlying scientific principles of modern electronic computers. He developed this understanding even though he was hampered by the primitive state of the mechanical devices and power sources of his day, by the non-existance of electronics, and by the experimental status of electromagnetism. This understanding is demonstrated by the operation of his definitions of "store, " "mill, " and "control" in virtually every modern data processing system. Today these terms are known respectively as "memory, " "execution," and "instruction" functions, no matter how such functions are implemented in any given system.

It will become increasingly more evident later in this report that Charles Babbage deserves to be called the "father of digital computers."

#### III TYPICAL DATA PROCESSING MACHINE FUNCTIONS

The typical modern digital electronic computer or data processing system generally utilizes a number of generalized logical processing functions. Since one of the basic purposes of the system is to perform arithmetic operations on input data and intermediate results some means must be provided to execute the basic arithmetic operations of addition and subtraction, as well as multiplication and division in many applications. Since all other arithmetic operations, such as square root extraction, trigonometric function generation, and the solution of simultaneous equations can be accomplished by a more or less involved series of additions, subtractions, multiplications, and divisions, it is possible within most systems to "build" these so-called "macro-operations" into the operating program of the system.

### A. ITERATION

For example, the extraction of the square root of any number can be accomplished readily by what is known as "iteration." Iteration is a repetitive which gradually "improves" a random or estimated starting value for the solution to the actual true answer to any specified degree of accuracy. Normally, an iterative calculation is terminated whenever the results of two successive iterations are equal, within the limits of the specified accuracy of the result. The following example demonstrates a popular method for iterative extraction of the square root:

General equation:

$$A_{i} + 1 = 1/2 (A_{i} + (A_{i} + \frac{N}{A_{i}})$$

Where:

A<sub>i</sub> = any given approximation (including the starting value).

N = the operand whose square root is to be developed.

An intuitive analysis shows that the actual value of the square root <u>must</u> lie between the "first guess" (A  $_0$ ), whatever value it happens to be, and the number of times that it is contained within the operand  $\left(\frac{N}{A_0}\right)$ . This truth holds for all of the

successive A<sub>i</sub>. It is evident that since the process is really one of averaging the immediate approximation and its "ghost" (which is inevitably on the other side of the true value of the square root) the next approximation will always be closer to the true value than the last one was. So as the iterations continue, the successive approximations gradually appraoch the exact square root. Finally, when the difference between successive values becomes less than the allowable error of the result, the iterations stop and the latest approximation is the answer.

Similar processes exist for all the commonly required functions. Generally these functions are generated as required by the program, since stored tables require expensive "parking space," and searching a lengthy table may require as much time as computing the desired value.

## B. STORAGE DEVICES

So far the arithmetic section of a system has been reviewed. Although the arithmetic section is certainly the heart of the system, it is by no means the most essential. Data on which it operates must be made available to the system from within. This requires what is commonly called "storage," or sometimes "memory." Since all electronically-operated information-storage devices with sufficiently high accuracy and reliability to incorporate in a computing system are binary (two-valued) devices, and because the formal symbols which humans are accustomed to (the decimal numbers, the English alphabet, and the punctuation and mathematical operation symbols count up to four or five dozen discretely different marks) it would be very inefficient to use a separate binary position for each symbol. Instead, each character is "coded" in such a form that the entire character set only requires a few binary symbols. The subject of codes will be covered in later sessions on their structure, translation, error characteristics, etc.

Storage devices are usually supplied in the form of the remanent magnetic flux which can be stored either on the surface of a rotating drum or in the toroidal flux-paths of very small metallic cores of one of the manganese ferrites. The common desirable properties of magnetic storage are high operating speed, low driving power, and high "signal-to-noise ratio." The common design factors are:

- 1. Uniformity of magnetic properties.

- 2. Addressing (singling out a specific group of positions from the whole memory).

- 3. An ever-increasing operating speed.

These factors will be reviewed later.

Memories have been built having many millions of positions of binary storage which are in use in commercial-production systems today.

### C. CONTROL LOGIC - STORED PROGRAMMING

The third basic functional element in a system is its control logic. Such logic consists of equipment necessary to accomplish the acquisition and execution of data and instructions. All large data processing systems, most intermediate-sized ones, and some small ones, now utilize what is known as "stored programming." This is usually achieved by coding instructions as if they were data, then storing them in memory with data. If instructions are coded numerically, they can be modified during the progress of the program which utilizes them. Such a method of operation provides the program with "learning" or "self-optimization" ability, as well as greatly increased flexibility for operating on ordered arrays of data or changing its own technique on a basis of intermediate results. These features account for the current popularity of stored-program machines.

#### D. CONTROL LOGIC - WIRED PROGRAMMING

The only commonly-used alternative to stored programming is "wired" programming. In such a system a "plugboard" or "control panel" is provided, containing sequentially-progressive program "exits" which are wired manually to the function "entries" to call out the desired succession of functional operations in sequential order. Usually limited means are also provided for automatic alteration of the program on a basis of intermediate results. However the overall flexibility is inevitably quite elementary compared to stored programming.

Summarizing, arithmetic functions, storage, and controls have been reviewed. These are three essential elements of any digital computer, electronic or otherwise. They date back in technological history to Babbage's "analytical engine," which contained all the logical concepts basic to any of our modern digital computing systems.

# E. INPUT/OUTPUT DEVICES

However, there is a fourth essential element which was also admitted by Babbage. This is, input/output — the "arms and legs" of the system by which it communicates bilaterally with the external human world. This is a logical necessity since a computing system is a "machine," and machines are those combinations of functional devices which do useful work. This quality of usefulness is also one of the patentability criteria. There would not really be much point in building a digital computer unless it fulfilled a useful purpose, except for the mental exercise and academic achievement involved. These in themselves seldom justify expending our best engineering and design efforts.

Input/output commonly is provided in the form of punched card readers and punches (since they are the usual vehicle for internal accounting and scientific records), magnetic tape transports (which develop much higher operating speeds, in terms of processing record volume), typewriters, punched paper tape equipment, push-buttons and switches (for manual control-input), indicator lights and audible signals (for output to the operator), and many other special-purpose devices. Most of these devices will be reviewed in detail later in this report.

We have seen how — just as an automobile needs an engine, wheels, a frame, some seats, a steering wheel, some sort of brakes, and a gas tank before it can be called "complete" — a digital computer also has some very basic functional requirements which are just as common to all of them as the essential devices are to the automobile. In the next section we will see how this combination of functions can be symbolized in logical form to permit demonstration of the features of individual systems and comparisons between them.

### IV FIRST-LEVEL DATA FLOW CHARTS

A first-level data flow chart of a computing system is a logical schematic representation of the various functional devices and units which give the system its inherent operating characteristics. The chart includes connecting lines to show the paths by which data and instructions are routed from unit to unit within the system during the execution of the program. Generally, these connecting lines are single lines which symbolize the several lines of a parallel-by-bit coded-information channel (which itself may be either serial or parallel by character). The functional units themselves are usually shown as boxes whose relative size may denote the comparative physical size of the circuitry and "hardware" they each contain.

In a previous section of this report the various essential sections of a general-purpose system were outlined and justified on a basis of the functional requirements of the system. Now the application of these devices in actual systems in current IBM production will be reviewed.

#### A. IBM 604 DATA FLOW

Figure 1 is the schematic layout of data flow in the IBM 604 Electronic Calculator. The basic machine contains 37 decimal digits of electronic (trigger) storage, plus a 13-position electronic "counter" which has an "add-subtract" accumulating function similar to the counters in an accounting machine. Factor Storage has the ability to read in from the attached card-operated Type 521 Computing Punch, and to read in or out at high speed under control of the control-panel wired program. Its 16 positions are subdivided into four units, of 3, 5, 3, and 5 positions respectively. The coupling features expand the unit capacities to a choice of 3, 5, 6, or 8 position combinations since either of the 3's may be coupled to either of the 5's, and one of the 3's may be coupled to the other. General Storage also contains 16 positions and is identical with Factor Storage except for the additional feature of the ability to read out to the 521 for punching of results into the card from which the input data was read during the previous card cycle. The Electronic Counter (13 positions) is similar to General Storage except for inability to read in from the 521.

The counter also holds multiplication products, division dividends, and the results of add and subtract operations by combining its original contents with program-selected data from the storage units. There is also a five-position M-Q (multiplier-quotient) storage unit which permits the use of a five-digit multiplier and the development of a five-digit quotient. The total count of decimal storage positions is then 50.

Since the 604 operates serial-by-bit, parallel-by-digit, there is also an eight-position column-shift unit which provides a parallel shift of the entire factor being transferred of 0-5 positions to the left. This feature permits decimal point scaling by programming and also the successive shifts required during multiplication and division.

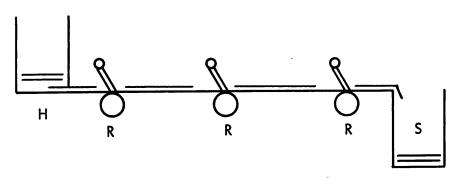

### B. IBM 305 RAMAC DATA FLOW

Figure 2 is the data flow chart of the IBM 305 RAMAC (Random Access Memory Accounting Calculator). The basic elements of the system are:

- 1. The processing drum.

- 2. The disk file.

- 3. The core buffer.

- 4. The peripheral equipment.

These elements will be discussed in that order.

Processing Drum — The processing drum contains 20 serial-by-bit tracks for instruction storage, four for data storage, four for arithmetic operations, one to buffer the console typewriter, two to buffer and check the card reader, and one for both the card punch and line printer. These 32 tracks contain 100 characters each. One character position contains eight bit-spaces for the seven bits of the character and an always-written space bit (which separates adjacent characters).

Disk File — The disk file contains fifty disks, coated on both sides with a magnetic iron oxide. There are 100 tracks on each disk-side, each divided into five 100-character sectors. The entire file then has a capacity of  $50 \times 2 \times 5 \times 100 = 100 = 5,000,000$  characters, addressable in blocks of 100, the same size as a track on the drum.

Core Buffer — The core buffer has a capacity of 100 characters and serves as intermediate storage for both the drum and the file (whose time-bases are substantially different and unsynchronized with each other) by synchronizing itself with which ever one it is communicating at the moment. This buffer consists of an array of seven planes of  $100 (10 \times 10)$  cores each, a separate plane for each of the character bits. The cores are small (.080" O.D.) "doughnuts" of a special manganese ferrite with a square hysteresis loop and low coercivity (magnetic hardness). The core buffer is connected successively to the single-character "From" and "To" block-addresses specified by the current instruction in the stored program. This produces very efficient transfer operations on approximately

punched-card-size (100 character) blocks of information between the drum, the file, and the peripheral equipment, resulting in a well-balanced card-processing system. Also shown are some of the control panel "logic" functions, which will be reviewed later.

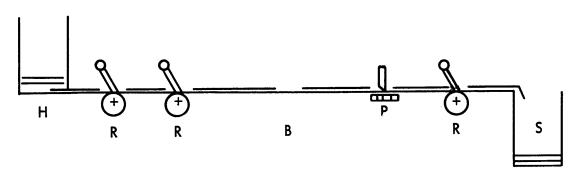

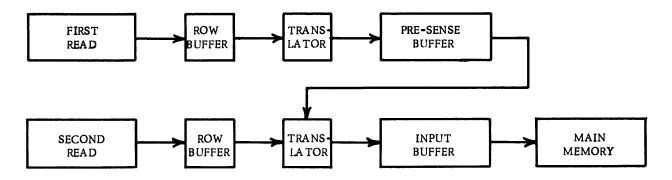

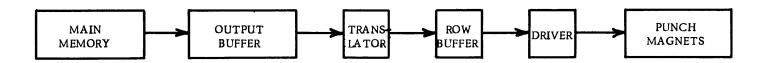

# C. IBM 650 DPS DATA FLOW

Figure 3 is the data flow chart of the IBM 650 Data Processing System. Compared to the previous charts this one is very simple even though the 650 is more complex than the 305. This comparison demonstrates the latitude of data flow charting. The general flow of data is from the read feed of the IBM 533 Reader-Punch to read buffer storage on the drum. From the drum data is block-transferred to General Storage (which is addressable by word) and also on the drum. The stored program processes information from the drum a word at a time, data words to the Distributor and instruction words to the Program Register. Results are stored in General Storage where they are punched into blank cards with the punch feed of the 533. The word size is fixed, at 10 decimal digits plus arithmetic sign.

General Storage contains 2,000 words, the read and punch buffers 10 each. The instruction format consists of a two digit Operation Code, a four digit Data Address and a four digit Instruction Address. The program advances by executing the Operation Code, using the contents of the Data Address as the operand, and then going to the Instruction Address for the next instruction. The accumulator has a capacity of two words, and contains both products and dividends (a dividend being replaced during the division by the quotient and remainder). Since the "working" storage units, the program register, distributor, and accumulator are dynamic storage devices which do not produce static outputs, the Operation and Address Registers are used for a static analysis of operation codes and addresses which are normally required for a substantial period of time during the execution of a given instruction. Validity checks are used to constantly monitor the accuracy of the information in the various dynamic registers to detect internal malfunctions as soon as they occur.

# D. IBM 7070 DPS DATA FLOW

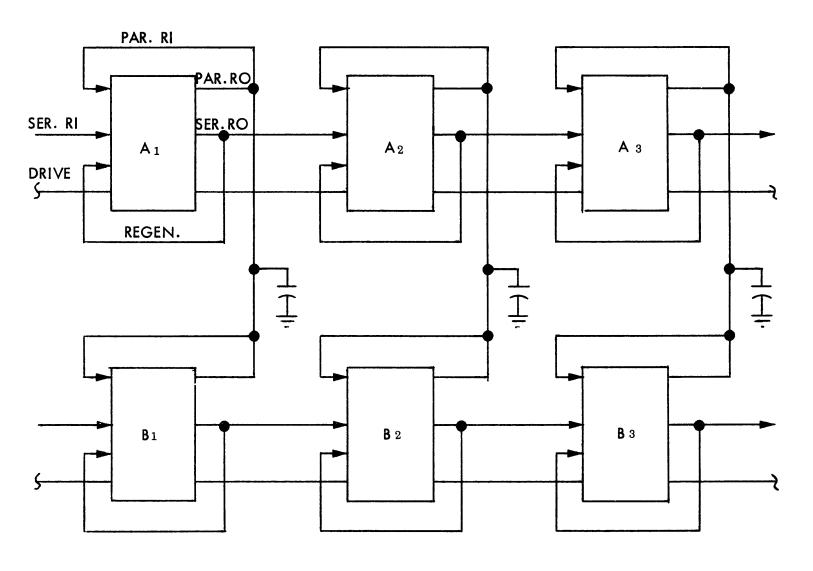

The basic data flow of the IBM 7070 Data Processing System is shown in Figure 4. Most of the data flow paths are parallel-by-bit, parallel-by-digit, handling the entire word being transferred "broadside," 53 bits wide. These parallel transfers take place in either four or six microseconds per word of 10 digits plus sign. Paralleling permits a virtual speed increase over serializing of about 10 to 1 for a given type of circuitry at a cost ratio of less than 10 since the controls need be supplied only once. The heart of the 7070 is its multiplexed 5,000-10,000 word core memory, which operates at a speed of 6 microseconds per cycle. Instructions and input data are introduced into memory via punched cards, magnetic tape, and typewriter under the control of a stored program. The word format is similar to the 650 (10 digits plus sign). The instruction format is -OP-IX-FC-DATA, two digits plus sign for the Operation Code, two digits which specify the Index Register by which the Data address will be modified, two digits which specify which segment of the operand word is to be used, and a four digit Data address normally referring to core memory.

For a typical "add" operation, the augend will already be in one of the three accumulators (specified within the operation code). The addend is in memory at the data address from where it is transferred in six microseconds to the Arithmetic Register. Simultaneously the augend is transferred from the accumulator to the Auxiliary Register. Then the arithmetic and auxiliary registers read out serially to the adder, in synchronism with each other, with the sum going back into the arithmetic register, replacing the addend digits one at a time as they are used up. A parallel transfer of the sum from the arithmetic register to the active accumulator completes the operation. "Add-to-memory" is quite similar except that the sum goes back to the operand location in memory instead of to the accumulator. The instruction path from memory to the Program Register (which is immediately to the left of the auxiliary register in the figure) has been omitted from the chart.

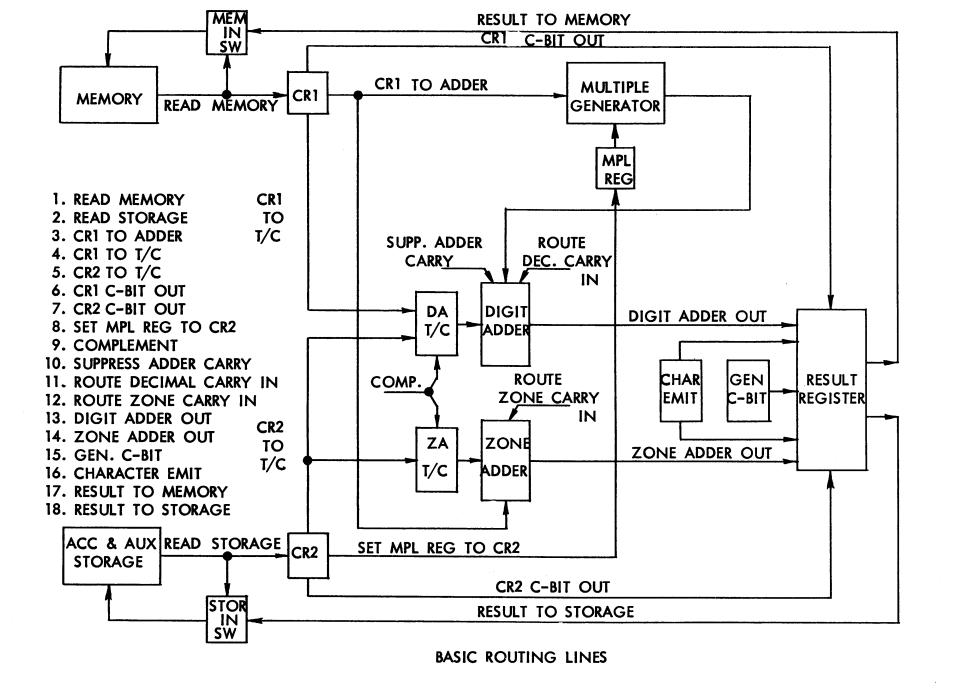

Figure 5 is the data flow chart of the CPU (Central Processing Unit) for the IBM 705 Data Processing System. The box labelled "Acc & Aux Storage" in the lower left corner corresponds to the accumulators of the 7070 and consists of a 256-digit accumulator, and fourteen 16-digit and one 32-digit storage registers. Data flow is serial-by-character using a 51-character seven bit code which will be discussed later. CR1 and CR2 are one character registers which re-time the information for the adders. There are separate adders for the coded equivalents of the Hollerith (punched card) code. Multiplication (and division) are performed by using the Multiple Generator, which develops X1, X2, X4a, X4b and X5 multiples simultaneously. The proper multiples are selected by analyzing the immediate multiplier digit, resulting in the development of the product the entire multiplicand times one multiplier digit at a time. The two T/C boxes are true-complement control circuits which develop the complement of one of the input characters or the other when required. The remaining boxes are required for system "housekeeping" functions which will become apparent later in this report.

These five systems which have been reviewed were chosen as representative primarily to demonstrate the purpose of data flow charts.

Additional information is available from the Engineering Library and Stationery Stores for anyone who desires more detailed information regarding any particular system. The information presented so far will provide sufficient background knowledge for a good understanding of the succeeding topics and is required for a broad understanding of the underlying principles of any digital computer system.

Fig. 1 - Schematic Layout of the IBM 604 Electronic Calculator

Fig. 2 - Data Flow Chart of the IBM 305 RAMAC

Fig. 3 - Data Flow Chart of the IBM 650 Data Processing System

Fig. 4 - Data Flow Chart of the IBM 7070 Data Processing System

Fig. 5 - Data Flow Chart of the CPU of t' 1BM 705 Data Processing System

### V THE BINARY NUMBER SYSTEM

The conventional decimal numbering system and its arithmetic owe their existence primarily to the fact that humans have ten fingers, which early in civilized history made convenient and readily available counters. Since ten fingers are divided on two hands, the bi-quinary numbering system of the abacus was also quite natural.

Similar reasoning shows that since many high speed electronically-operated memory devices have two well-defined "states" or "conditions," and each type of device "switches" abruptly under the control of its input signals, the most natural numbering system for use in electronic digital computers is binary (two-valued). For the moment the problem of bilateral conversion between binary numbers, and the decimal and alphabetic world we live in, can be ignored. Let us just try briefly to "think" in binary numbers.

To begin, assume that the number-symbols 2, 3, 4, 5, 6, 7, 8, and 9 do not exist. Thus, when we count (enumerate), the progression must go 0 to 1, 1 not to 2 but to 10, 10 to 11, 11 to 100, and so on. The following table correlates some common decimal numbers with their binary equivalents:

| Decimal | Binary | Decimal | Binary  | Decimal | Binary     |

|---------|--------|---------|---------|---------|------------|

| 0       | 0      | 10      | 1010    | 200     | 11001000   |

| ì       | 1      | 20      | 10100   | 300     | 100101100  |

| 2       | 10     | 30      | 11110   | 400     | 110010000  |

| 3       | 11     | 40      | 101000  | 500     | 111110100  |

| 4       | 100    | 50      | 110010  | 600     | 1001011000 |

| 5       | 101    | 60      | 111100  | 700     | 1010111100 |

| 6       | 110    | 70      | 1000110 | 800     | 1100100000 |

| 7       | 111    | 80      | 1010000 | 900     | 1110000100 |

| 8       | 1000   | 90      | 1011010 | 1000    | 1111101000 |

| 9       | 1001   | 100     | 1100100 | 1023    | 1111111111 |

Table 2 - Correlation of Some Common Decimal Numbers with Their Binary Equivalents

The following examples illustrate the basic binary arithmetic operations of addition, subtraction, multiplication, and division. Compare them with their decimal counterparts for simplicity.

| Addition: | Decimal        | Binary     |

|-----------|----------------|------------|

|           | 276            | 100010100  |

|           | +349           | +101011101 |

|           | <del>625</del> | 1001110001 |

|           |                | : ::: ; :  |

|           |                | : ::: 1    |

|           |                | : :: 16    |

|           |                | : :: -32   |

|           |                | : : -64    |

|           |                | : 512      |

|           |                | <u> </u>   |

| Subtraction:    | Decimal<br>349<br>-276<br>73                      | Binary<br>101011101<br>-100010100<br>1001001<br>: : :<br>: : 1<br>: :8<br>: 64 | 10010<br>-1011<br>111             | (18)<br>(11)<br>(7) |

|-----------------|---------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------|---------------------|

| Multiplication: | Decimal<br>23<br>×17<br>161<br>23<br>391          | Binary<br>10111<br>×10001<br>10111<br>10111000<br>110000111                    | -256<br>128<br>4<br>2<br>1<br>391 |                     |

| Division:       | Decimal<br>17<br>23 1400<br>23<br>170<br>161<br>0 | Binary<br>10001<br>10111 )110010000<br>10111<br>000100000<br>10111<br>01001    | (17)                              |                     |

Fig. 6 - Basic Binary Arithmetic Operations

Referring back to the example of multiplication by "halving and doubling," it should now be apparent that the multiplication process is actually a systematic conversion of the decimal multiplier to its binary equivalent, followed by binary multiplication of the decimal multiplicand (by selective doubling). Decimal-to-binary conversion is accomplished ordinarily in just that way, by successive division by two, the successive remainders being the binary equivalent, in reverse order. For example, consider the decimal value 349 used in the following subtraction example:

2)349(1 2)174(0 2)87(1 2)43(1 2)21(1 2)10(0 2)5(1 2)2(0 2)1(1 0 The binary value is 101011101. This is the decimal method of conversion to binary. The binary method depends on the binary "code" chosen to represent the individual decimal digits in a binary computer or calculator. The problem is too complex to deal with here. Binary-to-vecimal conversion is demonstrated in the checks of the binary arithmetic examples given above.

#### VI BOOLEAN ALGEBRA

Boolean algebra is a system which provides the symbology and operating rules for the expression and analysis of formal logic statements by the use of techniques similar to those of conventional algebra. This similarity is probably Boolean algebra's greatest difficulty since it is quite natural to lapse into conventional algebra during a Boolean algebra problem. If this potentiality is kept firmly in mind, it is possible to avoid it.

The following rules are listed to demonstrate the characteristics of Boolean algebra without resorting to the lengthy definitions used in a more formal treatment of the subject:

| <u>Function</u> | <u>Usage</u>                               | Boolean Form |

|-----------------|--------------------------------------------|--------------|

| AND (A AND B)   | Active only when both A and B are present. | Α·B          |

| OR (A OR B)     | Active if either A or B is present.        | A + B        |

| NOT (NOT A)     | Active when A is not present.              | Ā            |

Table 3 - Rules Demonstrating Boolean Algebra Characteristics

### Identities:

$$\overline{A} + \overline{B} = \overline{A} \cdot \overline{B}$$

;  $\overline{A} \cdot \overline{B} = \overline{A} + \overline{B}$ ;  $\overline{A} + \overline{B} = A \cdot B$ ;  $\overline{A} \cdot \overline{B} = \overline{A} + B$ ;  $\overline{A} \cdot \overline{A} = 0$ ;  $\overline{A} + \overline{A} = 1$ ;  $\overline{A} + B = B + A$ ;  $\overline{A} \cdot B = B \cdot A$

It is seen that the "plus sign" of conventional algebra is used to signify the OR and the multiplication symbol is used for the AND. The NOT is symbolized by a bar over the top of the function symbol(s) to which it refers. Boolean algebra will be used as a tool in the next nine sections to permit efficient coverage of the topics of information codes and their arithmetic.

#### VII THE LOGICAL BINARY ADDER

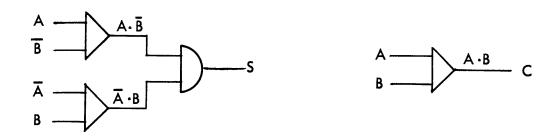

One of the more interesting devices in its various configurations is the logical binary adder which will now be analyzed in detail. The basic logical objective of the binary adder is the implementation of the simple charts of Figure 7 which are known as "truth tables." These tables provide the individual output results for the four possible combinations of inputs A and B on a basis of whether neither or either or both are present (as binary "ones").

The next step in the process of logical synthesis of the truth table is to convert the entries in the table into terms of Boolean algebra equations. The following two equations result for the "sum" and "carry" respectively:

1)

$$S = A \cdot \overline{B} + \overline{A} : B$$

(either, but not both)

2)

$$C = A \cdot B$$

(both, only)

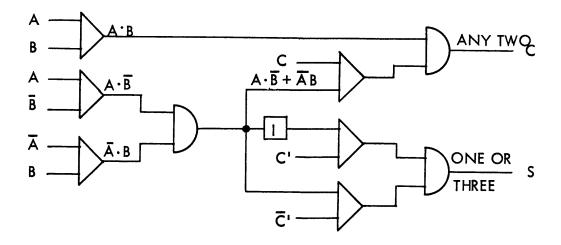

This pair of equations represents the so-called "binary half adder." The reason for the qualification "half" is that a complete or "full" adder also has the arithmetic "carry-in" as a third entry, along with A and B. This is a natural requirement for a practical binary adder which operates serially (one bit at a time, low order to high), similarly to the mental process of binary addition demonstrated in the section of this report of the binary number system. Figure 8 contains the truth tables for sum and carry for the full adder. Since there are now three binary input variables, there are  $2^3$ , or 8, entries in each table. Just as in the case of the half adder, these truth tables can be easily converted into Boolean equations:

3)

$$S = A\overline{BC} + \overline{ABC} + \overline{ABC} + ABC$$

4)

$$C' = AB\overline{C} + A\overline{B}C + \overline{A}BC + ABC$$

These equations can be modified by factorization and other Boolean operations into a number of different equivalent forms, resulting in various corresponding equivalent symbolic logic circuits. The symbolic logic for equations 1) and 2) is shown in Figure 9. Figure 10 illustrates how two half adders can be cascaded to form a full adder in symbolic logic form. This form of the full adder can also be converted to its Boolean form, for comparison with equations 3) and 4), as follows:

5)

$$S = (A\overline{B} + \overline{A}B)\overline{C'} + (A\overline{B} + \overline{A}B)C'$$

6)

$$C = (A\overline{B} + \overline{A}B) C' + AB$$

Multiplying equation 5) to eliminate the parentheses gives equation 3) directly. Equation 6) can be similarly checked against equation 4) by expanding the first term into two terms and then multiplying the other term by C' and  $\overline{C'}$  in turn (since  $C' + \overline{C'} = 1$ , this operation is valid).

Now, if we think of the symbolic circuits in terms of, say, their transistor and diode equivalents, the count for the circuit is 30 diodes and 0 transistors, while the corresponding count for the circuit of Figure 10 is 18 diodes and 1 transistor. This means that by converting to the logic of Figure 11, we have effectively "traded" 12 diodes for 1 transistor, which is a quite significant saving in "hardware," since both circuits do exactly the same thing. There are actually many different forms of binary adders possible. The choice of any specific form for a given application is usually made on a basis of the other factors involved in the choice, such as economy, reliability, speed, etc.

| SUM |     |   |   |  |  |

|-----|-----|---|---|--|--|

|     | Α   |   |   |  |  |

|     | 0 1 |   |   |  |  |

| D   | 0   | 0 | 1 |  |  |

| В   | 1   | 1 | 0 |  |  |

| CARRY |   |   |   |  |

|-------|---|---|---|--|

|       | Α |   |   |  |

|       |   | 0 | 1 |  |

| В     | 0 | 0 | 0 |  |

| Ĺ     | ] | 0 | 1 |  |

Fig. 7 - Simple Truth Tables for the Half Adder

|    | ·  | SU | JM |   |   |

|----|----|----|----|---|---|

| :  | A: | 0  | 0  | 1 | 1 |

|    | B: | 0  | 1  | 0 | 1 |

|    | 0  | 0  | 1  | 1 | 0 |

| C: | 1  | 1  | 0  | 0 | 1 |

|    |    | CARRY |   |   |   |

|----|----|-------|---|---|---|

|    | A: | 0     | 0 | 1 | 1 |

|    | B: | 0     | 1 | 0 | 1 |

| C: | 0  | 0     | 0 | 0 | 1 |

|    | 1  | 0     | 1 | 1 | 1 |

Fig. 8 - Truth Tables for Sum and Carry for the Full Adder

Fig. 9 - Symbolic Logic for Equations 1) and 2), page 23

Fig. 10 - Two Half Adders Cascaded to Form a Full Adder in Symbolic Logic Form

Fig. 11 - Symbolic Description of BCD Adder

## VIII BINARY-CODED DECIMAL ARITHMETIC

Since the binary adder and its arithmetic are relatively simple, it is a very natural evolutionary step to recode the decimal symbols into binary form and develop a set of arithmetic rules to compensate for differences between the two number systems. It requires a four-position binary number to express (that is, contain all the possible different values of) a single decimal digit. This binary number, however, is actually the binary code for a radix-16 digit, since it has that many possible values. The effect of this characteristic is shown in the following examples of binary-coded-decimal (BCD) addition:

| Example 1    |                       | Example 2        |     |                                                              |

|--------------|-----------------------|------------------|-----|--------------------------------------------------------------|

| decimal      | BCD                   | decimal          | BCD |                                                              |

| 6<br>+3<br>9 | 0110<br>+0011<br>1001 | 7<br>+5<br>(1) 2 |     | (12, base-16)<br>(carry corr.)<br>(decimal 2,<br>plus carry) |

Fig. 12 - Examples of Binary-Coded Decimal (BCD) Addition

As illustrated in the second example, if there is a decimal carry required for the result, the sum will be six too low. This situation requires that there by a logic circuit monitoring the sum (of a BCD adder) to detect a sum greater than nine and apply the required correction of +6. This is included in the logic of Figure 12, which symbolically describes the BCD adder in terms of binary full and half adders logically cascaded to accept four binary entry-pairs broadside. The intermediate sums (with primes) are the uncorrected (base-16) outputs, which then in turn feed the inputs of a second partial adder to provide the +6 correction as required, on a basis of detecting the need for correction as 8 (4 + 2) in the intermediate sum. This 8 (4 + 2) signal is also used directly to provide a "6" for the correction adder.

A variation of the above BCD code (not widely used by IBM) is known as the "excess-three" code. Its characters are respectively three units higher in binary value than their BCD counterparts, ranging in binary "weight" from 3 to 11, as shown in the following table:

| 0  | 0011 | 5 | 1000 |

|----|------|---|------|

| 1. | 0100 | 6 | 1001 |

| 2  | 0101 | 7 | 1010 |

| 3  | 0110 | 8 | 1011 |

| 4  | 0111 | 9 | 1100 |

Table 4 - Example of "Excess-Three" Code, A Variation of the BCD Code

One of the unique advantages of the "excess-three" code is that it is self-complementing, since the nines complement of a given digit value may be obtained easily by a direct bit-by-bit inversion of the original value, independent of that value itself. Since a computer must ordinarily subtract as well as add, this is a significant advantage to a low-cost system.

The examples below show the operations of addition and subtraction in this code:

Addition

| decimal      | excess-3                                                                                 | decimal       | excess-3                                                                                |

|--------------|------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------|

| 3<br>+6<br>9 | 0110<br>+1001<br>1111 (15, base-16)<br>+1101 (Correction, +10)<br>(1) 1100 (9, excess-3) | 6<br>+7<br>13 | 1001<br>+1010<br>(1) 0011 (0, excess-3)<br>+0011 (correction, +0)<br>0110 (3, excess-3) |

|              | Subtraction                                                                              |               |                                                                                         |

| decimal      | excess-3                                                                                 | decimal       | excess-3                                                                                |

| 9            | 1100                                                                                     | 4             | 0111                                                                                    |

| -3           | -0110                                                                                    | -9            | -1100                                                                                   |

| 6            | +1010 (complement)                                                                       | <del>-5</del> | +0100 (complement)                                                                      |

|              | (1) 0110 (3, excess-3)                                                                   |               | (0) 1011 (no carry)                                                                     |

|              | +0011 (0, excess-3)                                                                      |               | 0101 (recomplement)                                                                     |

|              | 1001 (6, excess-3)                                                                       | •             | +0011 (Correction, +0)                                                                  |

|              |                                                                                          |               | 1000 (5, excess-3)                                                                      |

Fig. 13 - Addition and Subtraction in the "Excess-Three" Code

It is apparent that both addition and subtraction require a correction operation in "excess-3" code, resulting in somewhat slower operation, so that the ultimate choice between the two codes for a given application will very likely depend on a compromise of the requirements, since neither code has any overriding advantages.

#### IX BI-QUINARY ARITHMETIC

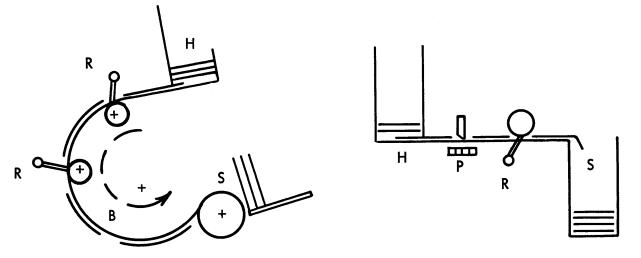

The earliest well-known use of the bi-quinary information code is the abacus. Its natural advantage in that application is that a decimal digit may be expressed in a pattern of seven beads, rather than the 10 required for true decimal representation. This code probably evolved by rationalization of the physical fact that the 10 human fingers, on which our decimal system is founded, are located five each on two hands.

The structure of the code, then, consists of a five-symbol minor quinary part and a major two-symbol binary part, one set for each decimal order of a number. Conventionally, the quinary "bits" are symbolized by their decimal arithmetic weights 0, 1, 2, 3, and 4, while the binary bits are weighted 0 and 5. Thus we have binary 0 and 5, and quinary 0 thru 4.

In arithmetic operations, "carries" are propagated similarly to the decimal system since a quinary carry (count beyond 4) advances the binary value for the same digit position to the other symbol, and a binary carry advances the quinary count for the next higher order digit by one. Thus, it is seen that the arithmetic is carried out as if the binary and quinary parts were successively alternating quinary and binary orders. It may help, to consider bi-quinary arithmetic in this fashion.

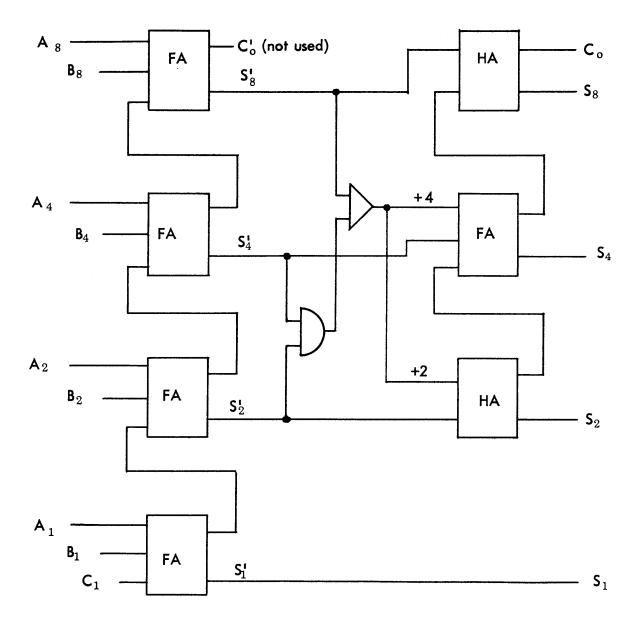

By way of historical reference, the program and arithmetic control circuits of the IBM 650 operate completely in bi-quinary code. Figure 14 is a logic diagram of the 650 arithmetic adder. The horizontal boxes are ANDs, and the vertical ones ORs. This circuit has some very interesting logic short-cuts included in it, as will be evident during an analysis of several cases of single-digit addition.

Another code which is very similar to bi-quinary is the qui-binary code used in a number of current development systems. The basic difference is that the binary and quinary parts of the code are transposed. As a result, the quinary bits have weights of 0, 2, 4, 6, and 8, and the binary bits weights of 0 and 1. The rules of arithmetic are otherwise the same as for bi-quinary. The minor advantage of this code over bi-quinary is that the translation to and from BCD is more direct, since for one thing the binary one-bit in qui-binary is the same as the one-bit of BCD. So is the quinary eight-bit the same as the BCD eight-bit, and so on. However, as is usual in such cases, there is a compensating disadvantage, which will be reviewed later in the section on "code translation."

Fig. 14 - Logic diagram of the 650 arithmetic adder

# X BI-QUINARY COMPLEMENTING AND VALIDITY CHECKING

As seen during the study of the binary adder (Section VII), subtraction by a logical adder requires the complementation of the subtrahend, and also re-complementation of the difference if the minuend were the smaller value (resulting in a change of sign from minuend to difference). This same consideration applies to the bi-quinary adder — the subtrahend must be complemented.

The bi-quinary code has the useful advantage of being "self-complementing." This means that complementation can be accomplished on a bit-by-bit basis rather than character-by-character. In this code, complementing is done very simply by a consistent transposition of bits, as seen in the following table:

| Decimal | B Tru | <u>je</u> Q | B Comple | ement Q |

|---------|-------|-------------|----------|---------|

| 0       | 0     | 0           | 5        | 4       |

| 1       | 0     | 7           | 5        | 3       |

| 2       | 0     | 2           | 5        | 2       |

| 3       | 0     | 3           | 5        | 1       |

| 4       | 0     | 4           | 5        | 0       |

| 5       | 5     | 0           | 0        | 4       |

| 6       | 5     | 1           | 0        | 3       |

| 7       | 5     | 2           | 0        | 2       |

| 8       | 5     | 3           | 0        | 1       |

| 9       | 5     | 4           | 0        | 0       |

Table 5 - Bi-Quinary Complementing by a Consistent Transposition of Bits

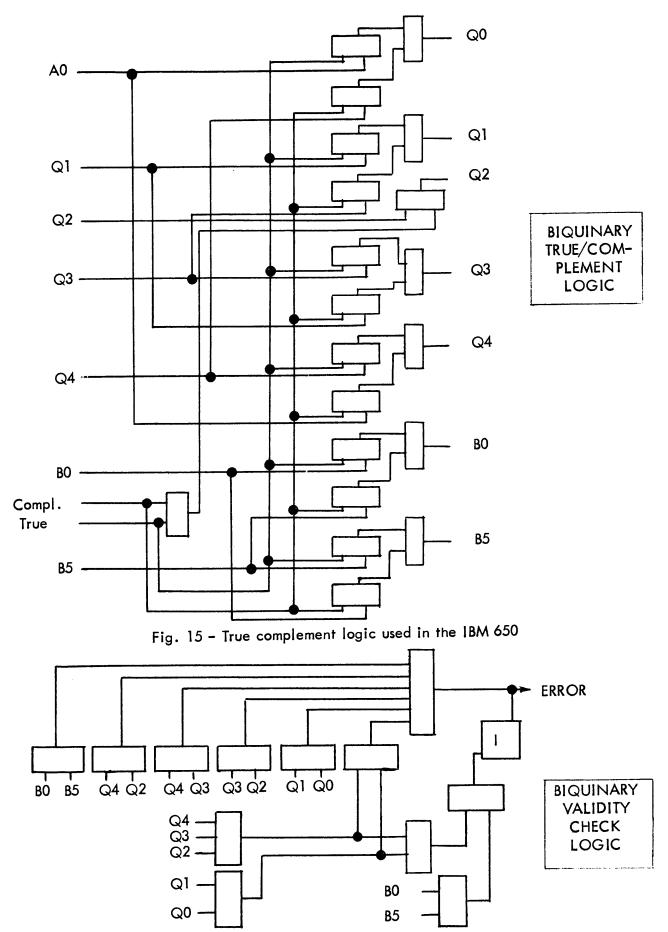

As deduced from this table, complementation requires the transposition of the binary 0 and 5 and the quinary 0 and 4 and quinary 1 and 3. The quinary 2 does not change since decimal 2 and 7 both have a Q2. The basic advantage of self-complementation is that no character analysis is required, since the same "rule" is always shared by more than one character. In addition, a valid complement can result only from a valid true value, preserving the self-checkability of the code which depends on there always being one and only one binary bit and one quinary bit. Figure 15 depicts the true complement logic used in the IBM 650.

Figure 16 shows the logical bi-quinary validity check used in the IBM 650. By way of introduction, the basic Boolean expressions for the validity check are as follows:

Quinary Error =

$$\overline{(0+1+2+3+4)} + 01 + 02 + 03 + 04 + 12 + 13 + 14 + 23 + 24 + 34$$

Binary Error = (0 + 5) + 05

Character Error = Binary Error + Quinary Error

These equations are simplified by factorization to the form corresponding to the circuit of the figure. Incidentally, this logic is also applicable as is to the qui-binary code, since the code structure is equivalent, the only difference being in the bit-weights which have no bearing on the checking rules.

Fig. 16 - Logical biquinary validity check used in the IBM 650

## XI FIXED-BIT INFORMATION CODES

Fixed-bit information codes are a class of codes having the unique property that all characters have the same bit-count (of 1's). The most commonly used of these codes is the two-out-of-five code used in general (drum) storage in the 650 and universally in the 7070. According to the permutation formula,

$$P = \frac{n!}{m! (n - m)!}$$

there are ten permutations of five elements taken two at a time. In internal form, they are: AB, AC, AD, AE, BC, BD, BE, CD, CE, and DE, where the sequence of the symbols is not significant. The 2/5 code of the 650 and 7070 assigns arithmetic weights of 0, 1, 2, 3, and 6 to the five bits transferring these weights to the literal symbols given above results in a character sequence of 01, 02, 03, 06, 12, 13, 16, 23, 26, and 36, with respective decimal values of 1, 2, 3, 6, 0, 4, 7, 5, 8, and 9. The decimal values 0 and 3 have ambiguous arithmetic weights of 3 units, since 0 + 3 = 1 + 2 = 3. Normally, however, this code is not used for arithmetic purposes, so the ambiguity is no problem. The bit weights are merely a mnemonic aid, mainly to the customer engineer maintaining the system out in the field (the logic designers, using Boolean algebra, could just as well have used the literal symbols A, B, C, D, and E).

Incidentally, of all the other possible 2/5 codes, there is only one equivalent to the 0-1-2-3-6 code which has all positive bit-weights and only the zero ambiguously weighted. It is the 0-1-2-4-7 code, whose weight for the zero is 11, the 4-7 combination.

The really powerful reliability advantage of the fixed-bit codes is their complete immunity to multiple bit-errors of a common polarity (0 to 1), which can never revalidate the affected character, as is possible in any of the parity-checked codes (which are checked by establishing the count of binary ones in the character as either even or odd). Multiple bit-errors are generally caused by polarized noise, excessive power supply regulation, or failure of one or more of the data flow control gates (which can permit whole characters to be superimposed one on the other bit-by-bit).

One larger-capacity fixed-bit code used in IBM equipment is the four-out-of-eight code of the IBM 65 Data Transceiver used to transmit the contents of punched cards to another transceiver at the remote end of a conventional land line. This particular code used 54 out of the possible 70 characters available in terms of eight elements taken four at a time  $[8!/(4!)(8-4)! = (8 \times 7 \times 6 \times 5)/(4 \times 3 \times 2 \times 1) = 70]$ . The coding chosen for the specific 54 characters of the code is based on its relatively straightforward translation to and from the Hollerith code of the punched cards that the machine processes.