NASA TM-80067

1

1 ł NASA Technical Memorandum 80067

,

NASA-TM-80067 19790013628

# INTERPRETIVE COMPUTER SIMULATOR FOR THE

NASA STANDARD SPACECRAFT COMPUTER-II (NSSC-II)

RUDEEN S. SMITH AND MARIE S. NOLAND

.

**MARCH 1979**

National Aeronautics and

Langley Research Center Hampton, Virginia 23665

Space Administration

44

LANGLEY ISLARD- CENTER LIEK-RY, 1 ISA HAMPTON, V RGINIA

| 1 Report No<br>NASA TM 80067                             | 2 Government Acces                  | sion No                                 | 3 R                       | cipient's Catalog No                                  |

|----------------------------------------------------------|-------------------------------------|-----------------------------------------|---------------------------|-------------------------------------------------------|

| 4 Title and Subtitle                                     |                                     |                                         | port Date<br>March 1979   |                                                       |

| Interpretive Computer Simu<br>Spacecraft Computer-II (NS | A Standa:                           | rd 6 Pe                                 | forming Organization Code |                                                       |

| 7 Author(s)<br>Rudeen S. S                               | Smith                               |                                         | 8 Pe                      | forming Organization Report No                        |

| Marie S. No                                              |                                     | 10 W                                    | ork Unit No               |                                                       |

| 9 Performing Organization Name and Addr                  | 'ess                                |                                         |                           |                                                       |

|                                                          | ey Research Center<br>Irginia 23665 |                                         | 11 Contract or Grant No   |                                                       |

| 12 Sponsoring Agency Name and Address                    |                                     |                                         |                           | pe of Report and Period Covered<br>chnical Memorandum |

| National Aeronautics and S<br>Washington, DC 20456       | Space Administrati                  | on                                      |                           | onsoring Agency Code                                  |

| 15 Supplementary Notes                                   |                                     | - <u></u> . <u>-</u> <u>-</u> - <u></u> |                           | · · · · · · · · · · · · · · · · · · ·                 |

|                                                          |                                     |                                         |                           |                                                       |

| 16 Abstract                                              | <u></u>                             | <u></u>                                 |                           |                                                       |

| An Interpretive Compu<br>Computer-II (NSSC-II) has       |                                     |                                         |                           |                                                       |

| Langley Research Center.                                 | The ICS is written                  | n in the                                | higher level              | language PASCAL.                                      |

| The NSSC-II is basically a and double (64-bit) precis    |                                     |                                         |                           |                                                       |

| set. The design of the IC system is implemented with     |                                     |                                         |                           |                                                       |

| registers, 64 storage prot                               | ect registers, a                    | 65K memor                               | y, a real-tin             | e clock, an                                           |

| interval timer, and a chec<br>structural design of the I |                                     |                                         |                           |                                                       |

| the instruction definition                               | s and the implement                 | ntation c                               | of the instruc            | tions. Included                                       |

| in the paper are the instr<br>to access the ICS system,  |                                     |                                         |                           |                                                       |

| output file provides, per                                | instruction, a val                  | lue race,                               | , a time histo            | ory, and the program                                  |

| status. A program listing<br>Management and Information  |                                     |                                         |                           |                                                       |

| has been used for prelimin<br>for the Annular Suspension | ary verification a                  | and testi                               | ng of NSSC-I              |                                                       |

| for the Annular Suspension                               | and formering by s                  |                                         | sy project.               |                                                       |

|                                                          |                                     |                                         |                           |                                                       |

|                                                          |                                     |                                         |                           |                                                       |

| 17 Key Words (Suggested by Authority)                    |                                     | 10. Database                            |                           |                                                       |

| 17 Key Words (Suggested by Author(s))<br>ASPS NSSC-II    |                                     | 18 Distribut                            | ion Statement             |                                                       |

| PASCAL ICS<br>CYBER                                      |                                     | Uncla                                   | assified - Un             | limited                                               |

| S/360<br>Software Verification and                       | Testing                             |                                         | Subj                      | ect Category 61                                       |

| 19 Security Classif (of this report)                     | 20 Security Classif (of this        | page)                                   | 21 No of Pages            | 22 Price*                                             |

| Unclassified                                             | Unclassified                        |                                         | 56                        | \$5.25                                                |

\* For sale by the National Technical Information Service, Springfield, Virginia 22161

TABLE OF CONTENTS

PAGE

TITLE

-

-

-

| SUMMARY                                                      | 1        |

|--------------------------------------------------------------|----------|

| INTRODUCTION                                                 | 1        |

| NSSC-II INTERPRETIVE COMPUTER<br>SIMULATOR STRUCTURAL DESIGN | 2        |

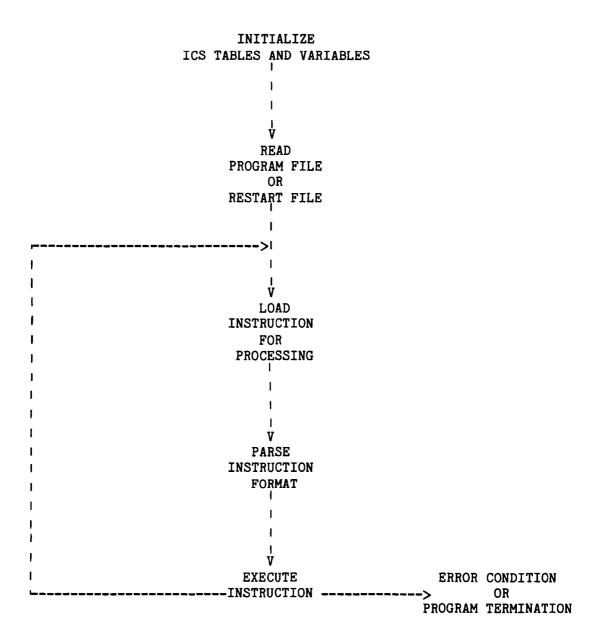

| PROGRAM FLOW DIAGRAM                                         | 8        |

| PROCEDURE DEFINITIONS                                        | 8        |

| PROCEDURE INITIALIZE                                         | 9        |

| PROCEDURE READINPUT                                          | 9        |

| PROCEDURE HEXCONV                                            | 9        |

| PROCEDURE RESTART                                            | 9        |

| PROCEDURE INSTLOAD                                           | 10       |

| PROCEDURE FORMAT                                             | 11       |

| PROCEDURE EXECUTE                                            | 11       |

| PROCEDURE ADD                                                | 12       |

| PROCEDURE ADDDBLE                                            | 12       |

| PROCEDURE ADDLOG                                             | 12       |

| PROCEDURE ADDREAL                                            | 12       |

| PROCEDURE ADDRCK                                             | 13       |

| PROCEDURE ADDSHORT                                           | 13       |

| PROCEDURE CDCREAL                                            | 13       |

| PROCEDURE CKPOINT                                            | 13       |

| PROCEDURE CKSHIFT                                            | 13       |

| PROCEDURE DIVIDERR                                           | 13       |

| PROCEDURE EXECUTEXCP                                         | 13       |

| PROCEDURE EXPONENTCK                                         | 14       |

| PROCEDURE FETCHEXCP                                          | 14<br>14 |

| PROCEDURE LOAD<br>PROCEDURE LOADBYTE                         | 14       |

|                                                              | 14       |

| PROCEDURE LOADDBLE<br>PROCEDURE LOADDREG                     | 14       |

| PROCEDURE LOADDREG                                           | 14       |

| PROCEDURE LOADREG                                            | 15       |

| PROCEDURE LOGICAL                                            | 15       |

| PROCEDURE MAXNUMD                                            | 15       |

| PROCEDURE MAXNUMF                                            | 15       |

| PROCEDURE MAXNUMS                                            | 15       |

| PROCEDURE NEGATE                                             | 15       |

| PROCEDURE NEGATEDBLE                                         | 15       |

| PROCEDURE NORMALIZE                                          | 16       |

| PROCEDURE NSSCIIREAL                                         | 16       |

| PROCEDURE ODDREGCK                                           | 16       |

| PROCEDURE ONESCOMP                                           | 16       |

| PROCEDURE ONESCOMPD                                          | 16       |

| PROCEDURE ONESCOMPS                                          | 16       |

| PROCEDURE PRENORMALIZE                                   | 16       |

|----------------------------------------------------------|----------|

| PROCEDURE PROTECTERR                                     | 17       |

| PROCEDURE PROTECTCK                                      | 17       |

| PROCEDURE REGCK                                          | 17       |

| PROCEDURE SHIFTD                                         | 17       |

| PROCEDURE SHIFTF                                         | 17       |

| PROCEDURE SHIFTL                                         | 17       |

| PROCEDURE SHIFTLD                                        | 17       |

| PROCEDURE SHIFTR                                         | 18       |

| PROCEDURE SHIFTRD                                        | 18       |

| PROCEDURE SPECCK                                         | 18       |

| PROCEDURE STORE                                          | 18       |

| PROCEDURE STOREMULT                                      | 18       |

| PROCEDURE STOREPSW                                       | 18       |

| FUNCTION TIME                                            | 18       |

| PROCEDURE TWOSCOMP                                       | 19       |

| PROCEDURE TWOSCOMPD                                      | 19       |

| PROCEDURE UNNORMALIZE                                    | 19       |

|                                                          |          |

| NSSC-II INSTRUCTION IMPLEMENTATION                       | 19       |

| ADD INSTRUCTIONS                                         | 21       |

| AND INSTRUCTIONS                                         | 22       |

| BRANCH INSTRUCTIONS                                      | 22       |

| COMPARE INSTRUCTIONS                                     | 23       |

| CONVERT INSTRUCTIONS                                     | 24       |

| DIVIDE INSTRUCTIONS                                      | 24       |

| EXCLUSIVE OR INSTRUCTIONS                                | 25       |

| EXECUTE INSTRUCTION                                      | 26       |

| INSERT CHARACTER INSTRUCTION                             | 26       |

| LOAD INSTRUCTIONS                                        | 27       |

| LOAD AND TEST INSTRUCTIONS                               | 29       |

| MULTIPLY INSTRUCTIONS                                    | 30       |

| MOVE INSTRUCTIONS                                        | 31       |

| NORMALIZE INSTRUCTION                                    | 31       |

| OR INSTRUCTION                                           | 32       |

| PACK INSTRUCTION                                         | 32       |

| SUBTRACT INSTRUCTIONS                                    | 32       |

| START I/O INSTRUCTION                                    | 34       |

| SHIFT INSTRUCTIONS                                       | 34       |

| SET MASK INSTRUCTIONS                                    | 36       |

| SET STORAGE KEY INSTRUCTION                              | 36       |

| STORE INSTRUCTIONS<br>SUPERVISOR CALL INSTRUCTION        | 37<br>37 |

|                                                          | 37<br>38 |

| TEST BITS INSTRUCTIONS                                   | 30<br>39 |

| TIMER READ AND SET INSTRUCTION<br>TRANSLATE INSTRUCTIONS | 39<br>39 |

|                                                          | 39<br>40 |

| UNPACK INSTRUCTION                                       | 40       |

-

| TITLE                                                           | PAGE     |

|-----------------------------------------------------------------|----------|

| CONCLUDING REMARKS                                              | 41       |

| APPENDIX A                                                      | 42<br>42 |

| ICS SYSTEM USAGE AND SUPPORT PROCESSORS<br>SAMPLE CONTROL CARDS | 42<br>43 |

| SAMPLE PROGRAM                                                  | 44       |

| SAMPLE DATAF                                                    | 44       |

| SAMPLE OUTPUT                                                   | 45       |

| APPENDIX B                                                      | 46       |

| NSSC-II INSTRUCTION SET TIMINGS                                 | 46       |

| STANDARD INSTRUCTION SET                                        | 46       |

| SHORT INSTRUCTION SET                                           | 49       |

| DOUBLE INSTRUCTION SET                                          | 51       |

| FLOATING POINT INSTRUCTION SET                                  | 52       |

| REFERENCES                                                      | 53       |

-

•

SUMMARY

An Interpretive Computer Simulator (ICS) for the NASA Standard Spacecraft Computer-II (NSSC-II) has been developed at Langley Research Center as a code verification and testing tool for the Annular Suspension and Pointing System (ASPS) project. The simulator is written in the higher level language PASCAL and implemented on the CDC CYBER series computer system. It is supported by a meta assembler, a linkage loader for the NSSC-II, and a utility library to meet the application requirements.

The architectural design of the NSSC-II is that of an IBM System/360 (S/360) and supports all but four instructions of the S/360 Standard Instruction Set. This paper discusses the structural design of the ICS, with emphasis on the design differences between it and the NSSC-II hardware. The program flow is diagrammed, with the function of each procedure being defined; the instruction implementation is discussed in broad terms; and the instruction timings used in the ICS are listed.

Included in the paper is an example of the steps required to process an assembly level language program on the ICS. The example illustrates the control cards necessary to assemble, load, and execute assembly language code; the sample program to be executed; the executable load module produced by the loader; and the resulting output produced by the ICS.

The ICS was designed as a verification and testing tool for the NSSC-II, but is general enough to have applications as a basic S/360 simulator.

#### INTRODUCTION

This report is to serve as the reference manual for the NSSC-II Interpretive Computer Simulator, but should be used in conjunction with the IBM Principles of Operation Manual (ref. 1) for the NSSC-II. The report provides a structural description of the ICS, a general discussion of the NSSC-II instruction set, and any variations between the ICS and the NSSC-II hardware. The IBM document should be referred to for in-depth discussions of the NSSC-II structural design and instruction definitions.

The NSSC-II architecture is basically that of an IBM System/360 and supports 83 of the 87 instructions in the S/360 Standard Instruction Set. The four unsupported S/360 instructions are discussed in the IBM manual (ref. 1). The NSSC-II hardware provides additional short and double precision instructions and a 32-bit floating-point instruction set.

# NSSC-II INTERPRETIVE COMPUTER SIMULATOR STRUCTURAL DESIGN

The NSSC-II ICS is written in PASCAL for the CDC CYBER series computers. The CYBER computer is a ones complement machine with a 60-bit word size. The NSSC-II is a twos complement machine with a 32-bit word size. As discussed below, these two incompatabilities had considerable impact on the design of the ICS.

The ones complement host machine means all arithmetic operations are performed in ones complement arithmetic. The arithmetic operands are converted from twos complement to ones complement, the operation is performed, and the ones complement result is then converted to twos complement before storing the value.

In a ones complement machine there is a positive and negative zero represented by all zeros or all ones, respectively. Negative zero in ones complement has the same representation as a minus one in twos complement. This causes a major consideration in the design of the ICS, and requires special handling in many of the arithmetic operations. These cases are discussed in the appropriate procedure definitions.

In a twos complement system there is no negative zero, thereby creating one more negative number than exists in a ones complement system. The twos complement maximum negative number (the negative number with the greatest absolute value) is not representable in ones complement. A message to this effect is given when the maximum negative number is used in an operation that requires conversion to ones complement. Generally, the operation is performed with the value still in twos complement form.

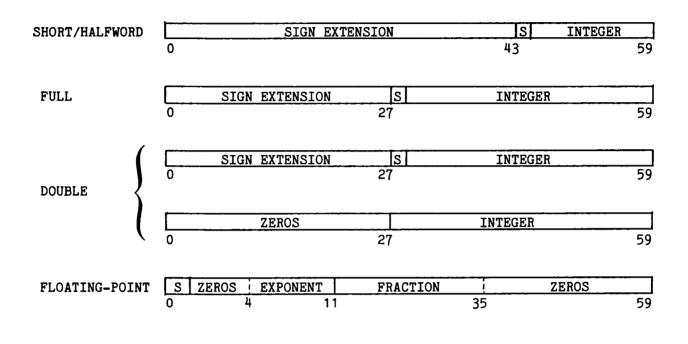

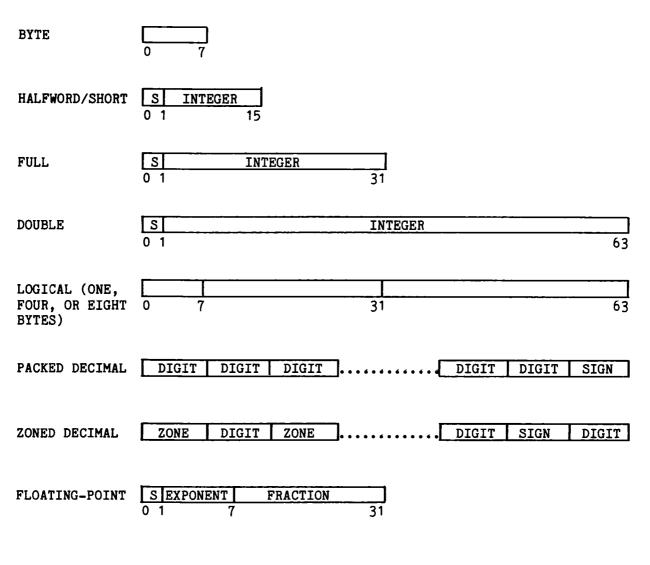

The fixed-point word size on the NSSC-II is 32 bits for full word, 16 bits for halfword, and 64 bits for double word. The 60-bit CYBER word is used to represent the fixed-point full and half words with the upper 28 and 44 bits, respectively, used for sign extension. The 64-bit double word is represented by two 60-bit words with the first word containing the sign extension in the upper 28 bits and the sign and upper 31 bits of the double word in the lower 32 bits. The second word contains the low 32 bits of the double word in the lower 32 bits; the upper 28 bits are extended with zeros. The upper 28 bits of the full and double word, and the upper 44 bits of the halfword, are ignored when storing the result but are used to record overflow.

The NSSC-II floating-point word size is 32 bits, with a sign bit, a 7-bit exponent, and a 24-bit fraction. When represented as a 60-bit CYBER word, the upper four bits of the 11-bit exponent and the lower 24 bits of the 48-bit fraction are padded with zeros.

Figure 1 shows the 60-bit CYBER representation for the NSSC-II fixed-point and floating-point data forms. Refer to figure 3 for the NSSC-II representation of these data forms.

Figure 1.

The ICS and NSSC-II differ somewhat in the handling of program interrupts. During the fetch cycle, the NSSC-II hardware suppresses instructions on some program interrupts while terminating others. The ICS suppresses instructions on all such interrupts except for the addressing exception of the Translate (TR) and Translate and Test (TRT) instructions, which are terminated. The priority of the program interrupts in the ICS are as follows: operation code, addressing, specification, storage protection, privileged, data, execute, floating-point register, fixed-point divide, fixed-point overflow, floatingpoint divide, exponent overflow, significance, and exponent underflow. An operation exception occurs when the operation code (op code) is not defined. An addressing exception occurs when an address exceeds the available storage. A specification exception occurs when proper alignment is not specified for an operand or an improper register is designated. A storage protection exception occurs when an instruction tries to store into a protected location. A privileged exception occurs when a privileged instruction is encountered in the

problem state. A data exception occurs when a sign or digit code is incorrect. An execute exception occurs when the subject instruction is an EXECUTE instruction. A floating-point register exception occurs when a register designator greater than 6 is specified. A fixed-point divide exception occurs when a quotient exceeds the register size or the divisor is zero. A fixedpoint overflow exception occurs when high-order significant bits are lost in add, subtract, and shift operations. A floating-point divide exception occurs when the divisor has a zero fraction. An exponent overflow occurs when the result exponent from an add, subtract, multiply, or divide operation exceeds 127 and the result fraction is not zero; the operation is completed and the exponent is 128 smaller than the correct exponent. A significance exception occurs when the result fraction of an add or subtract operation is zero; if PSW bit 39 is on, an interrupt occurs. An exponent underflow occurs when the result exponent from an add, subtract, multiply, halve, or divide operation is less than zero and the result fraction is not zero. If PSW bit 38 is on, an interrupt occurs; otherwise, the operation is completed and the exponent is 128 larger than the correct exponent. The NSSC-II hardware handles the privileged instructions as special cases; therefore, the program interrupts may not occur in the ICS in the same order as they do in the NSSC-II. Program interrupts are discussed further in the procedure definitions.

The program interrupt codes used in the ICS are as follows:

DOCCOM THEODILDE CALLER

| INTE | RUPT CODE | PROGRAM INTERRUPT CAUSE |

|------|-----------|-------------------------|

| 0    | 0000000   | PSW Key Not Zero        |

|      |           | -                       |

| 1    | 0000001   | Operation               |

| 2    | 00000010  | Privileged Operation    |

| 3    | 00000011  | Execute                 |

| 4    | 00000100  | Protection              |

| 5    | 00000101  | Addressing              |

| 6    | 00000110  | Specification           |

| 7    | 00000111  | Data                    |

| 8    | 00001000  | Fixed-Point Overflow    |

| 9    | 00001001  | Fixed-Point Divide      |

| 10   | 00001010  | Invalid SIO Command     |

| 11   | 00001011  | Floating-Point Register |

| 12   | 00001100  | Exponent Overflow       |

| 13   | 00001101  | Exponent Underflow      |

| 14   | 00001110  | Significance            |

| 15   | 00001111  | Floating-Point Divide   |

THTEPPHIPT CODE

Supervisor interrupts are handled through the execution of the SUPERVISOR CALL (SVC) instruction, INPUT/OUTPUT interrupts are handled through the execution of the START I/O (SIO) instruction, and external interrupts are handled through the interval timer. NSSC-II machine (hardware) check interrupts can not be detected by the ICS.

The NSSC-II interval timer and real-time clock are implemented on the ICS and accessed by the TIMER READ AND SET (TMRS) instruction. The 16-bit interval timer has a maximum time of 7.3818624 seconds (hex FFFF) and is decremented

every 112.64 microseconds. An underflow interrupt will occur if the system mask bit 7 is set; a mask of 0 leaves the interrupt pending. The timer is reset to zero to simulate the pending state until the timer mask bit is set, at which time an interrupt will occur. The 32-bit real-time clock is incremented every 112.64 microseconds and has no overflow interrupt.

The ICS is implemented with 16 32-bit general registers (numbered 0 through 15), four floating-point registers (numbered 0,2,4,6), and a memory size of 65536 bytes (64 1024-byte blocks). The memory address range is 0 to 65535 with no memory wraparound. Any memory location greater than 65535 will produce an addressing exception. Memory locations 0 through 131 are reserved for the permanent storage assignments described below:

| LOCATION | LENGTH                     | PURPOSE                               |

|----------|----------------------------|---------------------------------------|

| 0<br>8   | Double Word<br>Double Word | Initial Program Loading PSW<br>Unused |

| 16       | Double Word                | Unused                                |

| 24       | Double Word                | External Old PSW                      |

| 32       | Double Word                | Supervisor Call Old PSW               |

| 40       | Double Word                | Program Old PSW                       |

| 48       | Double Word                | Machine Check Old PSW                 |

| 56       | Double Word                | Input/Output Old PSW                  |

| 64       | Double Word                | Buffered I/O Status Word              |

| 72       | Word                       | Channel Address Word                  |

| 76       | Word                       | Unused                                |

| 80       | Word                       | Unused                                |

| 84       | Word                       | Unused                                |

| 88       | Double Word                | External New PSW                      |

| 96       | Double Word                | Supervisor Call New PSW               |

| 104      | Double Word                | Program New PSW                       |

| 112      | Double Word                | Machine Check New PSW                 |

| 120      | Double Word                | Input/Output New PSW                  |

| 128      | Word                       | Unused                                |

The general registers, floating-point registers, storage protect registers, program status word, real-time clock, total time clock, increment time clock, and memory are initialized to zero unless the Checkpoint/Restart mode is in effect. The Checkpoint/Restart status is determined by the first value of the control file CONTRLF. A zero indicates preinitialization with memory being loaded from the file DATAF and execution starting at the transfer address provided by DATAF. For anything other than zero, the registers, program status word, clocks, and memory are loaded from the file CKPTF and execution resumes at the location stored in the instruction address (bits 48-63) of the PSW. Checkpoint occurs when the clock time stored at the effective memory address is exceeded by the real-time clock value. The memory addresses for both clocks must be aligned on a full word boundary.

5

The control file CONTRLF is a text file that contains a '0' or '1' in column 1.

The file DATAF is a text file with the following format. The first column of each line is a blank.

line 1 : Program name line 2 : XXXXY------Y . . . . . line n-1 : XXXXY-----Y line n : FFFFZZZZ

> where XXXX is memory location Y-----Y is code and/or data FFFF is file terminator ZZZZ is transfer address

CKPTF is a file of integers with the current register, PSW, clock, and memory values at the time of checkpoint.

Checkpoint/Restart is activated through the Timer Read and Set (TMRS) instruction. The NSSC-II defines the first operand of the instruction for values of 0 (read real-time clock), 1 (read interval timer), 2 (read/set real-time clock), and 3 (read/set interval timer). The ICS uses the value of 4 to signal a checkpoint condition. If the first operand has a value of 4 and the real-time clock is greater than the clock time stored at the effective memory address, then a checkpoint occurs. When the program is restarted, if the value in column 1 of the control file CONTRLF is '1', execution resumes where the checkpoint occurred; otherwise, execution starts from the beginning of the program code.

The files CONTRLF, DATAF, and CKPTF must be precreated as permanent files and replaced at the termination of each program execution. The Program Status Word (PSW) is a double word (64-bits) that contains the information required for proper program execution. In general, the PSW is used to control instruction sequencing and to hold and indicate the status of the system. The PSW format is as follows:

| r<br>1<br>1   | system<br>mask         | key            | AN  | IWP    | int               | code                                                 |

|---------------|------------------------|----------------|-----|--------|-------------------|------------------------------------------------------|

| 0             | 7                      | 11             |     | 15     |                   | 31                                                   |

| г<br>, I<br>L |                        | progra<br>mask |     | unused | <b>-</b><br> <br> | instruction<br>address                               |

| <b></b><br>32 | 33                     | 35             | 39  |        | 47<br>47          | 63                                                   |

| 0<br>1-6      | System (I<br>Unused    | /0) Mask       |     | -      |                   | Instruction Length Code (ILC)<br>Condition Code (CC) |

| 7<br>5–11     | •                      | 'imer) Mask    | 2   | 36-    | -39<br>36         | Program Mask<br>Fixed-Point Overflow Mask            |

| 12<br>13      | ASCII (A)<br>Machine C | heck Mask      | (M) |        | 37<br>38          | Unused<br>Exponent Underflow Mask                    |

| 14<br>15      | Wait Stat              | e (W)          |     | 40-    | 39<br>-47         | Significance Mask<br>Unused                          |

| -31           |                        |                |     | 48-    | -63               | Instruction Address                                  |

In addition to issuing the supervisor-call interruption, the Supervisor Call (SVC) instruction may be used to terminate a program. If the I field of this instruction is a 3, the program will be terminated at that point. For any other value, the instruction will be processed normally.

The purpose of the DIAGNOSE instruction is for NSSC-II hardware testing. Since this instruction is not intended for problem or supervisor usage, it has not been implemented on the ICS.

The control sequence required to access the ICS is illustrated in appendix A with a control card setup, a sample program, and the resulting output.

Appendix B lists the timings used for the NSSC-II instruction sets.

# PROCEDURE DEFINITIONS

The procedure definitions will be ordered as they are referenced in the ICS. The definition of the primary level procedures will be preceded by a diagram showing the secondary level procedures that may be referenced from the primary level, followed by a discussion of each procedure in the diagram. The secondary level procedure names will appear in parenthesis.

### Procedure INITIALIZE

Program tables, arrays, and variables are initalized in this procedure. These include the registers, memory, the block protection array, the clocks, and, per op code, the instruction mnemonic, the instruction format, and the instruction exception conditions.

The fetch cycle exception conditions are initialized in the following order: addressing, specification, protection, privileged, data, execute, and floating-point register check. The execute cycle exceptions are divide fault and overflow/underflow checks, followed by the appropriate condition code setting.

#### Procedure READINPUT

READ CONVERT PROGRAM FILE <----> TEXT FILE TO HEX (HEXCONV)

OR

# READ RESTART FILE (RESTART)

The first character of the control file CONTRLF is read; if the character is '0' the textfile DATAF is read; if the character is '1' the integer file CKPTF is read.

READINPUT calls the procedure HEXCONV to convert the textfile to its binary equivalent before loading memory. DATAF provides the addresses for loading memory, the memory values, and the transfer address for the start of program execution. If the program is to be restarted, the procedure RESTART is called to read the restart file CKPTF and the transfer address is provided by the program status word.

#### Procedure HEXCONV

The character value is translated to its hexadecimal equivalent.

#### Procedure RESTART

The character '0' is written to CONTRLF to reset the control file for subsequent executions. The registers, memory, PSW, and clocks are loaded from the file CKPTF.

# Procedure INSTLOAD

The instruction is loaded from memory into an instruction record for processing. Addressing exception is checked and the instruction length code and instruction address of the program status word are updated.

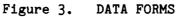

The first two bits of the instruction op code specifies the length and format of an instruction (figure 2). Some of the short instructions do not adhere to this rule and are handled as special cases in this procedure.

The five basic instruction formats are RR, denoting a register-to-register operation; RX, a register-and-indexed storage operation; RS, a register-and-storage operation; SI, a storage and immediate-operand operation; and SS, a storage-to-storage operation.

| RR FORMAT             | OP CODE         R1         R2           0         7         11         15                                                                                         |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX FORMAT             | OP CODE         R1         X2         B2         D2           0         7         11         15         19         31                                             |

| RS FORMAT             | OP CODE         R1         R3         B2         D2           0         7         11         15         19         31                                             |

| SI FORMAT             | OP CODE         I2         B1         D1           0         7         15         19         31                                                                   |

| SS FORMAT             | OP CODE         L1         L2         B1         D1         B2         D2           0         7         11         15         19         31         35         47 |

| BIT<br>Positions (0-1 | INSTRUCTION INSTRUCTION<br>I) LENGTH FORMAT                                                                                                                       |

| 00<br>01<br>10<br>11  | ONE HALFWORD RR<br>TWO HALFWORDS RX<br>TWO HALFWORDS RS or SI<br>THREE HALFWORDS SS                                                                               |

Figure 2. BASIC INSTRUCTION FORMATS

# Procedure FORMAT

An instruction is parsed into the appropriate operand fields. The effective address of the RX, RS, SI, and SS instructions are calculated and the RX flag set for the RX instructions. This flag is used in calculating the RX instruction times (refer to appendix A).

**Procedure EXECUTE**

CHECK FETCH TIME EXCEPTION CONDITIONS -----1 (FETCHEXCP) I 1 Ł T 1 t V PROCESS 1 INSTRUCTION 1 1 1 V EXECUTE TIME EXCEPTION CHECK (EXECUTEXCP) 1 L 1 V CALCULATE TIMINGS (TIME) Ł 1 V PRINT OUTPUT ł E V ł IF ERROR EXISTS I STORE OLD PSW <-----(STOREPSW) LOAD NEW PSW (LOADPSW) TERMINATE PROGRAM

The fetch time exception conditions for the instruction are checked (FETCHEXCP); if no error exists, the instruction is processed. After instruction processing is completed the execute exceptions are checked and the condition code is set (EXECUTEXCP), the timing is updated (TIME), and trace and timing information are written to the output file. If no error exists, the next instruction is loaded. If an error does exists, the current PSW is stored as the program old PSW (STOREPSW) and the program new PSW becomes the current PSW (LOADPSW); program execution is terminated.

Due to the number of procedures referenced by EXECUTE, the descriptions will be in alphabetical order rather than in the order referenced. Any procedures that are referenced within another procedure will be denoted by putting the referenced procedure name in parenthesis.

# Procedure ADD

The twos complement operands are converted to ones complement (ONESCOMP) and the addition is performed in ones complement arithmetic. If the result is a negative zero, it is converted to a twos complement positive zero before storing the results. A carry out must be tested for in ones complement arithmetic and an end around carry performed if one exists. The result is then converted to twos complement form (TWOSCOMP) and stored in the first operand register.

#### Procedure ADDDBLE

The twos complement double precision operands are converted to ones complement double precision operands (ONESCOMPD). The lower half of the operands are added, then the upper halves and any carry out of the lower halves are added. An end around carry is performed if there is a carry out of the upper halves. A negative zero result is converted to a positive zero and the carry out test for the lower and upper halves continue until no carry out exists. The double precision result is converted to twos complement form (TWOSCOMPD) and stored in the register pair designated by the first operand.

## Procedure ADDLOG

A 32-bit logical add is performed and the result is stored in the first operand register.

## Procedure ADDREAL

The two floating-point operands are converted to the CDC CYBER system floating-point format (CDCREAL). The reformatted operands are then added and the result is converted back to the NSSC-II floating-point format (NSSCIIREAL) before storing the result in the first operand register.

#### Procedure ADDRCK

The address range of an operand is checked before execution of the instruction. If any part of the operand exceeds the maximum address range, an addressing exception error occurs whether or not the data is used in the instruction.

#### Procedure ADDSHORT

The maximum negative short precision number is not representable in ones complement notation. If either operand is the short maximum negative number, a warning statement is issued, the number is not changed, and the add operation proceeds (ADD).

## Procedure CDCREAL

A floating-point operand is converted to the corresponding CDC Cyber floating-point format before a real arithmetic operation is performed.

#### Procedure CKPOINT

The control file CONTRLF is set to indicate restart mode for subsequent runs. The general registers, floating-point registers, storage block registers, memory, current PSW, real-time clock, interval timer, increment clock, and total time clock are dumped to the checkpoint file CKPTF. This file is used to restart the program at the point where the checkpoint occurred.

#### Procedure CKSHIFT

The CYBER machine has a left shift wraparound; whereas, the NSSC-II fills the vacated bits with zeros. If a shift wraparound occurs, this procedure voids the wraparound effect.

# Procedure DIVIDERR

On a fixed-point divide error an error message is written out, the error condition is set, and the interruption code is set in the PSW. A fixed-point divide error occurs for a quotient value exceeding the register size, for a division by zero, or when the result in Convert to Binary (CVB) exceeds 31 bits.

#### Procedure EXECUTEXCP

The execution time exception conditions are checked in this procedure. The exceptions consist of a fixed-point overflow check, a floating-point divide check, exponent overflow/underflow checks, a floating-point significance check, and the setting of the condition codes. Condition codes are set for the following resultant conditions: 1) =0, <0, or >0; 2) overflow; 3) carry; 4) compare equal; 5) compare logical equal; 6) 0 or not 0 compare; 7) all zeros, all ones, or mixed values; and 8) characteristic =0, <0, or >0. A fixed-point overflow will produce an interrupt only if the program mask bit 36 is set. A floating-point significance exception will cause an interrupt to occur only if the program mask bit 39 is set, and an exponent underflow will produce an interrupt only if set.

## **Procedure EXPONENTCK**

The exponent of the floating-point operand is checked for underflow (<0) and overflow (>127) conditions.

#### Procedure FETCHEXCP

The fetch time exceptions check for addressing (ADDRCK), specification (SPECCK and ODDREGCK), protection (PROTECTERR), privileged (STOREPSW and LOADPSW), data, execute, and floating-point register (REGCK) error conditions are made in this procedure. If an error exists, the instruction is suppressed and execution is terminated.

#### Procedure LOAD

Memory is loaded into a temporary register (LOADREG) and the memory location pointer is updated by the number of bytes loaded.

# Procedure LOADBYTE

A byte from memory is loaded into the lower 8 bits of a temporary register and the memory location pointer is increased by 1.

# Procedure LOADDBLE

The eight bytes of memory that make up the second double precision operand are loaded into two temporary registers (LOAD), and the first double precision operand is loaded into two temporary registers.

## Procedure LOADDREG

Both double precision operands are loaded into temporary registers.

## Procedure LOADPSW

The Program Status Word is loaded from memory.

#### Procedure LOADREG

From one to four bytes from memory are loaded into a temporary register.

## Procedure LOGICAL

The logical operations AND, OR, and XOR are performed on the operands according to the instruction being processed. The set operations operate on 59 of the 60 bits of a word. The reserved bit is used for operational purposes within PASCAL. The bit reserved on the PASCAL version in use at LRC is bit 0, but this is implementation dependent.

### Procedure MAXNUMD

In the subtraction of double precision values, if both operands are the maximum negative value, the result zero is stored in the first operand registers. For any other combination of values the second operand is negated (NEGATEDBLE) and the two operands are then added (ADDDBLE).

#### Procedure MAXNUMF

If two maximum negative numbers are subtracted, the result is zero; otherwise, the second operand is negated (NEGATE) and added to the first operand (ADD).

#### Procedure MAXNUMS

If two short maximum negative operands are subtracted, the result is zero; otherwise, the second operand is negated (NEGATE) and added to the first operand (ADDSHORT).

#### Procedure NEGATE

The twos complement of the operand is performed. Plus one, minus one, and the maximum negative number must be handled as special cases. The maximum negative number cannot be complemented and a message to this effect is given.

# Procedure NEGATEDBLE

If the operand is the maximum negative double precision number, the negating does not take place and a message is given. For any other value, the twos complement of the operand is performed. Minus one and plus one must be handled as special cases.

## Procedure NORMALIZE

The fractional part of the floating-point operand is digit normalized; that is, the uppermost digit may not be 0, but the uppermost bit may be. The exponent is corrected accordingly; for each left digit shift of the fraction, the exponent is reduced by 1.

# Procedure NSSCIIREAL

The floating-point operand is converted back to the NSSC-II floating-point format. Since the NSSC-II is a digit biased machine and the CDC machine is bit biased, the NSSC-II exponent and fraction must be corrected accordingly.

# Procedure ODDREGCK

If an odd register is specified when an even/odd register combination is required, a specification error occurs. The error condition and interruption code are set.

#### Procedure ONESCOMP

The negative twos complement operand is converted to ones complement if the operand is not the maximum negative number. If it is, a message is given and the operand remains unchanged. Minus one must be handled separately.

## Procedure ONESCOMPD

The negative twos complement double precision operand is converted to ones complement if the operand is not the maximum negative double precision number. If it is, a message is given and the value remains unchanged. Minus one must be handled separately.

#### Procedure ONESCOMPS

If the twos complement operand is the maximum negative short number, then a message is given. The operand is then converted to ones complement (ONESCOMP).

#### Procedure PRENORMALIZED

The operands of the floating-point operations multiply and divide are prenormalized before the operation is performed. The exponent of the operands is corrected according to the number of digit shifts required for the prenormalization.

## Procedure PROTECTERR

Before a memory byte is stored into, the corresponding storage block is checked for storage protection. If the block is protected, a storage protect exception occurs and the error condition and interruption code are set.

#### Procedure PROTECTCK

If the instruction terminated prematurely, a protection exception occurred. An error statement is output, the error condition is set, the interruption code is set, and the timing parameter is set to the number of bytes processed before termination.

#### Procedure REGCK

The NSSC-II has four floating-point registers, numbered 0, 2, 4, 6. An error exception occurs if the register designator is greater than 6. An error message is written and the error condition is set.

## Procedure SHIFTD

The timing parameters are evaluated according to the number of bits the double precision operand was shifted.

#### Procedure SHIFTF

The timing parameters are evaluated according to the number of bits the full precision operand was shifted.

## Procedure SHIFTL

The operand is shifted left by multiplying by the appropriate power of 2. The vacated bits are filled with zeros. A shift greater than 30 shifts all zeros into the 31-bit arithmetic operand with the sign being retained. For the logical operands, all 32 bits participate in the shift.

## Procedure SHIFTLD

For shifts less than 32, the upper half of the double precision operand is shifted left (SHIFTL) and the result is checked for any left shift wraparound effect (CKSHIFT). The lower half is then moved into the upper half according to the number of bits specified. For shifts greater than or equal to 32, the second half is shifted into and possibly out of the first half and zeros fill the vacated bits (SHIFTL and CKSHIFT). The timing parameters are set to reflect the shift that takes place.

#### Procedure SHIFTR

The operand is shifted right by dividing by the appropriate power of 2. An arithmetic shift propagates the sign through the vacated bits; a shift greater than 30 propagates the sign throughout the arithmetic operand. For the logical operand, zeros are supplied to the upper bits. Minus one and negative values must be handled as special cases.

#### Procedure SHIFTRD

For shifts less than 32, the lower half of the double precision operand is shifted out and the upper half shifted into the lower half the number of bits specified (SHIFTR). For shifts greater than or equal to 32, the lower half is shifted out entirely and the upper half is shifted into and possibly out of the lower half (SHIFTR). The timing parameters are evaluated according to the number of shifts that takes place.

# Procedure SPECCK

The boundary requirements specify that a double-word operand must be located on a 64-bit boundary, a full word must be located on a 32-bit boundary, and a halfword/short operand must be located on a 16-bit boundary. If the instruction is not on a halfword boundary or if the operand is not properly aligned, a boundary specification exception occurs, an error message is written, the error condition is set, and the interruption code is set.

## Procedure STORE

The contents of a register are stored into memory one byte at a time. Up to four bytes may be stored.

#### Procedure STOREMULT

Multiple register values are stored into memory (STORE). The memory location is checked for storage protection before the store takes place (PROTECTERR).

#### Procedure STOREPSW

The current PSW is stored into memory at the specified locations.

## Function TIME

The timing calculation is made for the current instruction. The timing parameters TFLAG, TFLAG2, and TFLAGR are evaluated during the instruction process.

#### Procedure TWOSCOMP

The negative ones complement value is converted to a twos complement value before the result is stored in the result register. Minus one must be handled as a special case.

#### Procedure TWOSCOMPD

The negative ones complement double precision value is converted to twos complement notation before the result is stored in the result register pair. Minus one must be handled as a special case.

## Procedure UNNORMALIZE

The floating-point arithmetic operations performed on the CDC machine require normalized operands. The result of the floating-point unnormalized add and subtract operations (AU, AUR, SU, SUR) must be unnormalized before storing into the result register.

# NSSC-II INSTRUCTION IMPLEMENTATION

The instructions will be discussed in groups rather than by each individual instruction. The groupings will be ordered alphabetically and not according to any operational hierarchy.

The data forms generally used in the instructions are full word, double word, halfword, short precision, and floating-point (figure 3). A full word occupies a fixed-length format consisting of a one-bit sign followed by a 31bit integer field (32-bit signed integer). Some multiply, divide, and shift operations use an operand consisting of 64 bits with a sign bit and a 63-bit integer field (64-bit signed integer). When these operands are in registers, they are located in a pair of adjacent registers and are addressed by an even address referring to the left-most register of the pair. The sign-bit position of the right-most register contains part of the integer. Likewise, the double precision data value is contained in a 64-bit signed integer field and, when in registers, occupies an even/odd register pair.

A halfword data value is a 16-bit signed integer, but most generally a halfword operand is extended to a full word operand before the instruction is processed. The extension is performed by propagating the sign-bit through the 16 high-order bit positions of the register.

Short precision numbers occupy a fixed-length format of a one-bit sign followed by a 15-bit integer field (16-bit signed integer). The short precision quantity occupies the right-most 16 bits of a register; generally, the leftmost 16 bits are neither tested nor altered. Floating-point operands contain a sign bit field, a 7-bit exponent field, and a 24-bit fraction field. The exponent is expressed in excess 64 binary notation (0-127 range); the fraction is expressed as a hexadecimal number having a radix point to the left of the high order digit. When the floatingpoint operand is contained in a register, the register must be numbered 0, 2, 4, or 6; any other designation is invalid.

For an in-depth discussion of the instructions, the IBM Principles of Operation (ref. 1) should be referenced.

# Instruction Definitions

# ADD INSTRUCTIONS .-

| Add |              | - | A,AR       |

|-----|--------------|---|------------|

| Add | Double       | - | AD, ADR    |

| Add | Halfword     | - | AH,AHI     |

| Add | Logical      | - | AL,ALR     |

| Add | Short        | - | AS,ASI,ASR |

| Add | Normalized   | - | AE,AER     |

| Add | Unnormalized | - | AU, AUR    |

The second operand is added to the first operand, and the sum is placed in the first operand location.

The halfword second operand is expanded to a full word before the addition by propagating the sign-bit.

Logical addition is performed on 32-bit operands. The occurrence of a carry out of the sign position is recorded in the condition code for the logical adds.

The normalized sum is placed in the first operand after a normalized add; the unnormalized sum is stored after an unnormalized add.

Resulting Condition Code:

|                          | 0                 | 1                 | 2              | 3                    |

|--------------------------|-------------------|-------------------|----------------|----------------------|

| Add                      | =0                | <0                | >0             | overflow             |

| Add Double               | =0                | <0                | >0             | overflow             |

| Add Halfword             | =0                | <0                | >0             | overflow             |

|                          |                   |                   |                |                      |

| Add Logical              | =0,no carry       | ≠0,no carry       | =0,carry       | ≠0,carry             |

| Add Logical<br>Add Short | =0,no carry<br>=0 | ≠0,no carry<br><0 | =0,carry<br>>0 | ≠0,carry<br>overflow |

| -                        | • •               | •                 | • •            | • •                  |

Program Interruptions:

Addressing (A,AD,AE,AH,AL,AS,AU) Specification (A,AD,ADR,AE,AER,AH,AL,AS,AU,AUR) Fixed-Point Overflow (A,AR,AD,ADR,AH,AHI,AS,ASI,ASR) Significance (AE,AER,AU,AUR) Exponent Overflow (AE,AER,AU,AUR) Exponent Underflow (AE,AER)

Procedures Referenced: LOAD (A,AH,AL,AS,AE,AU) LOADDBLE (AD) LOADREG (ADR) ADD (A,AR,AH,AHI) ADDDBLE (AD,ADR) ADDLOG (AL,ALR) ADDSHORT (AS,ASI,ASR) ADDREAL (AE,AER,AU,AUR) NORMALIZE (AE,AER) UNNORMALIZE (AU,AUR)

AND INSTRUCTIONS .-

| And |       | - | N,NC,NI,NR |

|-----|-------|---|------------|

| And | Short | - | NS,NSI,NSR |

The logical product (AND) of the bits of the first and second operand is placed in the first operand location. All bits of the fixed-length integers are treated uniformly.

Resulting Condition Code:

|           | 0  | 1          | 2 | 3 |

|-----------|----|------------|---|---|

| And       | =0 | ≠0         | - | - |

| And Short | =0 | <b>≠</b> 0 | - | - |

- Program Interruptions: Addressing (N,NC,NI,NS) Specification (N,NS) Protection (NC,NI)

- Procedures Referenced: LOAD (N,NS) LOGICAL (N,NC,NI,NR,NS,NSI,NSR) PROTECTCK (NC)

BRANCH INSTRUCTIONS .-

| Branch | and Link              | - | BAL,BALR |

|--------|-----------------------|---|----------|

| Branch | on Condition          | - | BC,BCR   |

| Branch | on Count              | - | BCT,BCTR |

| Branch | Unconditional         | - | BU,BUR   |

| Branch | on Index High         | - | BXH      |

| Branch | on Index Low or Equal | - | BXLE     |

The Branch and Link instruction stores the rightmost 32 bits of the PSW as link information in the first operand. The instruction address of the PSW is replaced by the branch address in the second operand unless this operand is register 0.

The Branch on Condition instruction replaces the updated instruction address with the branch address if the state of the condition code is as specified by the mask operand; otherwise, normal instruction sequencing proceeds.

The Branch on Count instruction reduces the first operand by one. If the result is zero, normal instruction sequencing proceeds; otherwise, the instruction address is replaced by the branch address.

The Branch Unconditional instruction replaces the instruction address with the branch address.

The Branch on Index High instruction increments the first operand; the sum is then compared algebraically with a second operand. If the sum is high, the instruction address is replaced by the branch address; otherwise, normal sequencing proceeds. The Branch on Index Low or Equal is a similar instruction except that the branch is taken when the sum is low or equal compared to a second operand.

Condition Code: The code remains unchanged.

Program Interruptions: None

Procedures Referenced: ONESCOMP (BCT, BCT, BXH, BXLE) TWOSCOMP (BCT, BCTR, BXH, BXLE)

# COMPARE INSTRUCTIONS .-

| Compare |                | - | C,CR           |

|---------|----------------|---|----------------|

| Compare | Double         | - | CD,CDR         |

| Compare | Halfword       | - | CH,CHI         |

|         | Logical        | - | CL,CLC,CLI,CLR |

| Compare | Logical Short  |   | CLS,CLSI,CLSR  |

| Compare | Short          | - | CS,CSI,CSR     |

| Compare | Floating-Point | - | CE,CER         |

The first operand is compared with the second operand, and the result determines the setting of the condition code.

The halfword second operand is expanded to a full word before the comparison by propagating the sign-bit.

The logical comparisons are binary, proceeding left to right; the other comparisons are algebraic, treating each operand as a signed integer.

The floating-point comparison is algebraic, considering the sign, fraction, and exponent of each operand.

**Resulting Condition Code:**

|                        | 0         | 1               | 2                | 3 |

|------------------------|-----------|-----------------|------------------|---|

| Compare                | Operands= | 1st Operand Low | 1st Operand High | - |

| Compare Double         | Operands= | 1st Operand Low | 1st Operand High |   |

| Compare Halfword       | Operands= | 1st Operand Low | 1st Operand High | - |

| Compare Logical        | Operands= | 1st Operand Low | 1st Operand High | - |

| Compare Logical Short  | Operands= | 1st Operand Low | 1st Operand High | - |

| Compare Short          | Operands= | 1st Operand Low | 1st Operand High | - |

| Compare Floating-Point | Operands= | 1st Operand Low | 1st Operand High | - |

Program Interruptions: Addressing (C,CD,CE,CH,CL,CLC,CLI,CLS,CS) Specification (C,CD,CDR,CE,CER,CH,CL,CLS,CS)

Procedures Referenced: LOAD (C,CD,CE,CH,CL,CLS,CS) LOADBYTE (CLC) CDCREAL (CE,CER)

CONVERT INSTRUCTIONS .-

Convert to Binary - CVB Convert to Decimal - CVD

The Convert to Binary instruction changes the radix of the second operand from decimal to binary, and the result is placed in the first operand location.

The Convert to Decimal instruction changes the radix of the first operand from binary to decimal, and the result is stored in the second operand location. The number is treated as a right-aligned signed integer before and after conversion for both instructions.

Condition Code: The code remains unchanged.

Program Interruptions: Addressing (CVB,CVD) Specification (CVB,CVD) Protection (CVD) Data (CVB) Fixed-Point Divide (CVB)

Procedures Referenced: NEGATE (CVB,CVD) DIVIDERR (CVB)

**DIVIDE INSTRUCTIONS.-**

| Divide |                | - | D,DR       |

|--------|----------------|---|------------|

| Divide | Short          | - | DS,DSI,DSR |

| Divide | Floating-Point | - | DE, DER    |

| Halve  |                | - | HER        |

The dividend (first operand) is divided by the divisor (second operand) and then replaced by the remainder and quotient for the full divide. The dividend is a 64-bit signed integer occupying an even/odd pair of registers. The 32-bit signed remainder and 32-bit signed quotient replace the even/odd registers, respectively. The dividend (first operand) is divided by the divisor (second operand) and then replaced by the quotient for the short divide. No remainder is stored. The dividend is a 32-bit signed integer and is replaced by a 16-bit signed quotient with sign extended.

The floating-point dividend (first operand) is divided by the divisor (second operand) and replaced by the quotient; the remainder is not retained. The initial operands are prenormalized to produce a normalized result. The Halve instruction divides the second operand by two, and the normalized quotient is placed in the first operand location. Exponent overflow and underflow are detected but the underflow mask bit may prohibit the underflow interrupt.

Condition Code: The code remains unchanged.

Program Interruptions: Addressing (D,DE,DS) Specification (D,DE,DER,DR,DS,HER) Fixed-Point Divide (D,DR,DS,DSI,DSR) Exponent Overflow (DE,DER) Exponent Underflow (DE,DER,HER) Floating-Point Divide (DE,DER)

Procedures Referenced: LOAD (D,DE,DS) ONESCOMP (DS,DSI,DSR) ONESCOMPS (DS,DSI,DSR) NEGATE (D,DR) NEGATEDBLE (D,DR) TWOSCOMP (DS,DSI,DSR) DIVIDERR (D,DR,DS,DSI,DSR) PRENORMALIZE (DE,DER) CDCREAL (DE,DER,HER) EXPONENTCK (DE,DER) NSSCIIREAL (DE,DER,HER) NORMALIZE (DE,DER,HER)

#### EXCLUSIVE OR INSTRUCTIONS .-

| Exclusive | 0r |       | - | X,XC,XI,XR |

|-----------|----|-------|---|------------|

| Exclusive | 0r | Short | - | XS,XSI,XSR |

The modulo-two sum (exclusive OR) of the bits of the first and second operand is placed in the first operand location. All bits of the fixed-length integers are treated uniformly.

Resulting Condition Code:

|                    | 0  | 1          | 2 | 3 |

|--------------------|----|------------|---|---|

| Exclusive Or       | =0 | <b>≠</b> 0 | - | - |

| Exclusive Or Short | =0 | ≠0         | - | - |

Program Interruptions: Addressing (X,XC,XI,XS) Specification (X,XS) Protection (XC,XI) Procedures Referenced: LOAD (X,XS) LOGICAL (X,XC,XI,XR,XS,XSI,XSR) PROTECTCK (XC)

# EXECUTE INSTRUCTION .-

Execute – EX

The single instruction at the branch address is modified by the contents of the first operand and the resulting subject instruction is executed. The modification is effective only for this execution of the instruction and does not affect the instruction in memory. Normal execution sequencing resumes following the Execute instruction unless a branch occurs while processing the subject instruction.

Condition Code: The code may be set by the subject instruction.

Program Interruptions: Addressing Specification Execute

Procedures Referenced: INSTLOAD FORMAT EXECUTE

**INSERT CHARACTER INSTRUCTION.-**

Insert Character - IC

The eight-bit character at the second operand is inserted into the lower byte of the first operand.

Condition Code: The code remains unchanged.

Program Interruptions: Addressing

Procedures Referenced: None LOAD INSTRUCTIONS .-

| Load                | - | L,LR       |

|---------------------|---|------------|

| Load Double         | - | LD,LDR     |

| Load Halfword       | - | LH,LHI,LHR |

| Load Short          | - | LS,LSI,LSR |

| Load Floating-Point | - | LE,LER     |

The second operand is placed in the first operand location. The halfword second operand is expanded to a full word before storing by propagating the sign-bit.

Condition Code: The code remains unchanged.

```

Program Interruptions:

Addressing (L,LD,LE,LH,LS)

Specification (L,LD,LDR,LE,LER,LH,LS)

```

Procedures Referenced: LOAD (L,LD,LE,LH,LS)

> Load Address - LA Load Address Short - LAS

> > Floating-Point

The address of the second operand is inserted in the low-order 24 bits of the first operand for Load Address; the upper 8 bits are made zero. For Load Address Short the address is inserted in the low-order 16 bits; the upper bits are not altered.

| Condition Code:<br>The code remains unchan                                            | ged.                      |

|---------------------------------------------------------------------------------------|---------------------------|

| Program Interruptions:<br>None                                                        |                           |

| Procedures Referenced:<br>None                                                        | ,                         |

| Load Complement<br>Load Complement Double<br>Load Complement Short<br>Load Complement | - LCR<br>- LCDR<br>- LCSR |

-

The twos complement of the second operand is placed in the first operand location.

LCER

The floating-point value in the second operand is placed in the first operand with a sign change.

| Resulting Condition Code:                                                                                               | •  |      |    | -        |

|-------------------------------------------------------------------------------------------------------------------------|----|------|----|----------|

|                                                                                                                         | 0  | 1    | 2  | 3        |

| Load Complement                                                                                                         | =0 | <0   | >0 | overflow |

| Load Complement Double                                                                                                  | =0 | <0   | >0 | overflow |

| Load Complement Short                                                                                                   | =0 | <0   | >0 | overflow |

| Load Complement                                                                                                         | -  |      |    |          |

| Floating-Point                                                                                                          | =0 | <0   | >0 | -        |

| Specification (LCDR,LCER<br>Fixed-Point Overflow (LC<br>Procedure Referenced:<br>NEGATE (LCR,LCSR)<br>NEGATEDBLE (LCDR) |    | SR)  |    |          |

| Load Negative                                                                                                           | -  | LNR  |    |          |

| Load Negative Short                                                                                                     | -  | LNSR |    |          |

| Load Negative                                                                                                           |    |      |    |          |

| Floating-Point                                                                                                          | -  | LNER |    |          |

| Load Positive                                                                                                           | -  | LPR  |    |          |

|                                                                                                                         | -  |      |    |          |

| Load Positive Short                                                                                                     | -  | LPSR |    |          |

The twos complement of the positive valued second operand is placed in the first operand location for the Load Negative and Load Negative Short instructions. Negative numbers and zero remain unchanged. The floating-point second operand is placed in the first operand location with the sign made minus (one).

-

LPER

The absolute value of the second operand is placed in the first operand location for the Load Positive and Load Positive Short instructions. Positive numbers and zero remain unchanged. The floating-point second operand is placed in the first operand location with the sign made plus (zero).

Resulting Condition Code:

Load Positive

Floating-Point

| 0  | 1                          | 2           | 3           |

|----|----------------------------|-------------|-------------|

| =0 | <0                         | -           | -           |

| =0 | <0                         | -           | -           |

|    |                            |             |             |

| =0 | <0                         | -           | -           |

| =0 | -                          | >0          | overflow    |

| =0 | -                          | >0          | overflow    |

| =0 | -                          | >0          | -           |

|    | =0<br>=0<br>=0<br>=0<br>=0 | =0       <0 | =0       <0 |

Program Interruptions: Specification (LNER,LPER) Fixed-Point Overflow (LPR,LPSR) Procedures Referenced: NEGATE (LNR,LNSR,LPR,LPSR)

| Load | oad Multiple - |    |       |  | - | LM   |

|------|----------------|----|-------|--|---|------|

| Load | Full           | to | Short |  | - | LFSR |

| Load | PSW            |    |       |  | - | LPSW |

The Load Multiple instruction loads the register range specified from the memory locations designated by the second operand address. The registers are loaded in ascending order with register 0 following register 15.

The Load Full to Short instruction loads the second operand into the first operand location.

The Load PSW instruction replaces the PSW with the double word at the location designated by the operand address.

Resulting Condition Code:

|                    | 0         | 1              | 2       | 3        |

|--------------------|-----------|----------------|---------|----------|

| Load Multiple      | The code  | remains unchan | ged.    |          |

| Load Full To Short | =0        | <0             | >0      | overflow |

| Load PSW           | The code  | is set accordi | ng to   |          |

|                    | bits 34 a | nd 35 of the n | ew PSW. |          |

Program Interruptions: Addressing (LM,LPSW) Specification (LM,LPSW) Privileged (LPSW) Fixed-Point Overflow (LFSR)

Procedures Referenced: LOAD (LM)

LOAD AND TEST INSTRUCTIONS .-

| Load and | Test |                | - | LT,LTR   |

|----------|------|----------------|---|----------|

| Load and | Test | Short          | - | LTS,LTSR |

| Load and | Test | Floating-Point | - | LTER     |

The second operand is placed in the first operand location.

Resulting Condition Code: 0 1 2 Load and Test =0 <0 >0 Load and Test Short =0 <0 >0 Load and Test Floating-Point =0 <0 >0

```

Program Interruptions:

Addressing (LT,LTS)

Specification (LT,LTER,LTS)

```

Procedures Referenced: LOAD (LT,LTS)

MULTIPLY INSTRUCTIONS .-

| Multiply |                | - | M,MR         |

|----------|----------------|---|--------------|

| Multiply | Halfword       | - | MH,MHI       |

| Multiply | Short          | - | MS, MSI, MSR |

| Multiply | Floating-Point | - | ME, MER      |

The product of the multiplier (the second operand) and the multiplicand (the first operand) replaces the multiplicand. In the full word multiply, both operands are 32-bit signed integers. The product is a 64-bit signed integer and occupies an even/odd register pair.

The halfword multiplier is expanded to a full word by propagating the sign-bit and the multiplication is processed with 32-bit signed integer operands.

The short precision operands are 16-bit signed integers and the product is a 32-bit signed integer.

The normalized product of the floating-point operands replaces the first operand. The multiply operation consists of exponent addition and fraction multiplication; the sign of the product is determined by the rules of algebra. The result is normalized by prenormalizing the initial operands and postnormalizing the intermediate product. Exponent overflow and underflow are detected but the underflow interrupt may be masked off.

```

Condition Code:

The code remains unchanged.

```

```

Program Interruptions:

Addressing (M,ME,MH,MS)

Specification (M,ME,MER,MR,MH,MS)

Exponent Overflow (ME,MER)

Exponent Underflow (ME,MER)

```

```

Procedures Referenced:

LOAD (M,ME,MH,MS)

NEGATE (M,MR)

NEGATEDBLE (M,MR)

ONESCOMP (MH,MHI)

ONESCOMPS (MH,MHI,MS,MSI,MSR)

TWOSCOMP (MH,MHI,MS,MSI,MSR)

PRENORMALIZE (ME,MER)

CDCREAL (ME,MER)

```

EXPONENTCK (ME,MER) NSSCIIREAL (ME,MER) NORMALIZE (ME,MER)

MOVE INSTRUCTIONS .-

| Move |             | - | MVC,MVI |

|------|-------------|---|---------|

| Move | With Offset | - | MVO     |

| Move | Numerics    | - | MVN     |

| Move | Zones       | - | MVZ     |

The second operand is placed in the first operand location for the Move instructions. The Move With Offset instruction places the second operand to the left of and adjacent to the low-order four bits of the first operand, and the result is placed in the first operand location. The low-order four bits of each byte in the second operand field, the numerics, are placed in the loworder bit positions of the corresponding bytes in the first operand fields for the Move Numerics instruction. The Move Zones instruction places the zones, the high-order four bits of each byte, of the second operand field in the corresponding zones of the first operand field.

Condition Code: The code remains unchanged.

Program Interruptions: Addressing (MVC,MVI,MVO,MVN,MVZ) Protection (MVC,MVI,MVO,MVN,MVZ)

Procedures Referenced: PROTECTCK (MVC,MVN,MVZ)

# NORMALIZE INSTRUCTION .-

Normalize - NRM

The 32 bits in the first operand are shifted arithmetically left until bit 0 is not equal to bit 1. The number of shifted bit positions is then placed into the second operand. A zero is considered to be normalized.

| Resulting (           | Condition Code: | :  |    |    |   |

|-----------------------|-----------------|----|----|----|---|

|                       |                 | 0  | 1  | 2  | 3 |

| Normali               | ze              | =0 | <0 | >0 | - |

| Program Int<br>None   | terruptions:    |    |    |    |   |

| Procedures<br>CKSHIFT | Referenced:     |    |    |    |   |

OR INSTRUCTIONS .-

| 0r |       | - | 0,0C,0I,IOR |

|----|-------|---|-------------|

| 0r | Short | - | OS,OSI,OSR  |

The logical sum (OR) of the bits of the first and second operand is placed in the first operand location. All bits of the fixed-length integers are treated uniformly.

-

| Resulting Condition | Code:   |            |   |   |

|---------------------|---------|------------|---|---|

|                     | 0       | 1          | 2 | 3 |

| Or                  | =0      | ≠0         | - | - |

| Or Short            | =0      | <b>≠</b> 0 | - | - |

| Program Interruptio |         |            |   |   |

| Addressing (0,0C    | ,0I,0S) |            |   |   |

| Specification (0    | ,0S)    |            |   |   |

| Protection (OC,O    | I)      |            |   |   |

| Procedure Reference | d:      |            |   |   |

LOAD (0,0S) LOGICAL (0,0C,0I,IOR,OS,OSI,OSR) PROTECTCK (0C)

### PACK INSTRUCTION .-

Pack - PACK

The format of the second operand is changed from zoned to packed, and the result is placed in the first operand location.

Condition Code: The code remains unchanged.

Program Interruptions: Addressing Protection

Procedures Referenced: None

SUBTRACT INSTRUCTIONS .-

| Subtract |              | - | S,SR       |

|----------|--------------|---|------------|

| Subtract | Double       | - | SD,SDR     |

| Subtract | Halfword     | - | SH,SHI     |

| Subtract | Logical      | - | SL,SLR     |

| Subtract | Short        | - | SS,SSI,SSR |

| Subtract | Normalized   | - | SE, SER    |

| Subtract | Unnormalized | - | SU,SUR     |

|          |              |   |            |

The second operand is subtracted from the first operand, and the difference is placed in the first operand location. Subtraction is performed by adding the twos complement of the second operand to the first operand.