# NASA STANDARD SPACECRAFT COMPUTER (NSSC-II)

# PRINCIPLES OF OPERATION

(NASA-CR-178826) NASA STANDARD SPACECRAFT COMPUTER (NSSC-2): PRINCIPLES OF OPERATION (IBM) 184 p

N90-70545

Unclas 00/60 0252763

|     | • > • | *снк | ENGRG NOTICE | LTR | DESCRIPTION     |  | DATE APPROVED              |   |

|-----|-------|------|--------------|-----|-----------------|--|----------------------------|---|

|     |       |      | ,            |     | Initial Release |  | 2/15/77<br><b>5/1</b> 5/79 |   |

| - 1 |       | •    |              | •   | Errata Sheets   |  | 3/13/79                    | ı |

The attached pages are replacements or additions to the NSSC-II Principles of Operation.

| CONTR NO. NAS8-32808 PREPARATION | INTERNATIONAL BUSINESS MACHINES CORP.  FEDERAL SYSTEMS DIVISION  GAITHERSBURG, MARYLAND |                                                                             |           |         |        |

|----------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------|---------|--------|

| DSGN CHK                         | TITLE                                                                                   | ITLE NASA Standard Spacecraft Computer II (NSSC-II) Principles of Operation |           |         |        |

| DSGN APPROVAL                    | SIZE                                                                                    | CODE                                                                        | IDENT NO. | DWG NO. | 935402 |

|                                  | SCALE                                                                                   | <u> </u>                                                                    | WT        |         | SHEET  |

|         | •         |                                 |   |          |

|---------|-----------|---------------------------------|---|----------|

| Section | Paragraph | <u>Title</u>                    |   | Page     |

|         | 7.4.4     | Branch on Index High            |   | 88       |

|         | 7.4.5     | Branch on Index Low or Equal    |   | 89       |

|         | 7.4.6     | Execute                         | • | 89       |

|         | 7.4.6.1   | Execute Exceptions              |   | 91       |

| VIII    |           | STATUS SWITCHING                |   | 92       |

|         | 8.1       | Program States .                |   | 92       |

|         | 8.1.1     | Problem State                   |   | 92       |

|         | 8.1.2     | Wait State                      |   | 93<br>94 |

|         | 8.2       | Protection                      |   | 94       |

|         | 8.2.1     | Area Identification             | • | 94       |

|         | 8.2.2     | Protection Action               |   |          |

|         | 8.3       | Program Status Word             |   | 94       |

|         | 8.4       | Instruction Format              |   | 96       |

|         | 8.5       | Instructions                    |   | 97       |

|         | 8.5.1     | Load PSW                        |   | 98       |

|         | 8.5.2     | Set Program Mask                | • | 99       |

|         | 8.5.3     | Set System Mask                 |   | 99       |

|         | 8.5.4     | Supervisor Call                 |   | 99       |

|         | 8.5.5     | Set Storage Key                 |   | 100      |

|         | 8.5.6     | Test and Set                    |   | 100      |

|         | 8.5.7     | Start Input Output              |   | 101      |

|         | 8.5.8     | Timer Read and Set              |   | 103      |

|         | 8.5.9     | Diagnose                        |   | 104      |

|         | 8.6       | Status-Switching Exceptions     |   | 104      |

| IX      | •         | INTERRUPTIONS                   |   | 106      |

|         | 9.1       | Interruption Action             |   | 106      |

|         | 9.1.1     | Instruction Execution           |   | 106A     |

| •       | 9.1.2     | Source Identification           |   | 107      |

|         | 9.1.3     | Location Determination          |   | 108      |

|         | 9.2       | Input/Output Interruption       |   | 108      |

|         | 9.3       | Program Interruption            |   | 109      |

| •       | 9.3.1     | Operation Exception             |   | 110      |

|         | 9.3.2     | Privileged-Operation Exception  |   | 110      |

|         | 9.3.3     | Execute Exception               |   | 110      |

|         | 9.3.4     | Protection Exception            |   | 110      |

|         | 9.3.5     | Addressing Exception            |   | 110      |

|         | 9.3.6     | Specification Exception         |   | 111      |

|         | 9.3.7     | Data Exception                  |   | 111      |

|         | 9.3.8     | Fixed-Point-Overflow Exception  |   | 111      |

|         | 9.3.9     | Fixed-Point-Divide Exception    |   | 111      |

|         | 9.3.10    | Exponent-Overflow Exception     |   | 111A     |

|         | 9.3.11    | Exponent-Underflow Exception    |   | 111A     |

|         | 9.3.12    | Significance Exception          |   | 111A     |

|         | 9.3.13    | Floating-Point-Divide Exception |   | 111A     |

| •       | 9.3.14    | Buffered I/O Exception          |   | 112      |

| 7       | 9.3.15    | Supervisor-Call Interruption    |   | 112 -    |

# TABLE OF CONTENTS

| Section                               | Paragraph | <u>Title</u>                      | Page |

|---------------------------------------|-----------|-----------------------------------|------|

| ĭ                                     |           | NSSC-II ARCHITECTURE              | 1    |

|                                       | 1.1       | NSSC-II Instruction Set           | 1    |

|                                       | 1.2       | Exceptions                        | 1    |

| · '.;                                 | 1.2.1     | Input/Output                      | 1    |

|                                       | 1.2.2     | Timer                             | 1    |

| ger <del>e</del>                      | 1.2.3     | Storage Protect                   | 2    |

|                                       | 1.2.4     | Execution Times                   | 2 2  |

| •                                     | 1.2.5     | Unpredictable Results             | 2    |

|                                       | 1.2.6     | Addressing Exception              | 2    |

| •                                     | 1.2.7     | Addressing                        | 2    |

| 11                                    |           | SYSTEM STRUCTURE                  | . 3  |

|                                       | 2.1       | Main Storage                      | 3    |

|                                       | 2.2       | Addressing                        | 4    |

|                                       | 2.3       | Information Processing            | 4    |

|                                       | 2.4       | Storage Protection                | 5    |

| III                                   |           | CPU                               | 6    |

|                                       | 3.1       | Central Processing Unit Functions | 6    |

|                                       | 3.2       | General Registers                 | 7    |

|                                       | 3.3       | Arithmetic and Logical Unit       | 7    |

|                                       | 3.3.1     | Fixed Point Arithmetic            | 7    |

|                                       | 3.4       | Decimal Numbers                   | 8    |

| •                                     | 3.5       | Logical Operations                | 9    |

|                                       | 3.6       | Program Execution                 | 10   |

|                                       | 3.6.1     | Instruction Format                | 10   |

|                                       | 3.6.2     | Address Generation                | 10   |

|                                       | 3.6.2.1   | Base Address (B)                  | 12   |

|                                       | 3.6.2.2   | Index (X)                         | 12   |

|                                       | 3.6.2.3   | Displacement (D)                  | 12   |

|                                       | 3.6.3     | Sequential Instruction Execution  | 13   |

|                                       | 3.6.3.1   | Branching                         | 14   |

|                                       | 3.6.4     | Program Status Word               | 14   |

|                                       | 3.6.5     | Interruption                      | 15   |

|                                       | 3.6.5.1   | External Interrupts               | 16   |

|                                       | 3.6.5.2   | Program Interrupts                | 17   |

|                                       | 3.6.5.3   | Input/Output Interruption         | 19   |

|                                       | 3.6.6     | Machine States -                  | 19   |

|                                       | 3.6.6.1   | Running or Waiting State          | 19   |

|                                       | 3.6.6.2   | Masked or Interruptible State     | 19   |

|                                       | 3.6.6.3   | Supervisor or Problem State       | 19   |

|                                       | 3.7       | System I/O                        | 19   |

|                                       | 3.7.1     | Direct I/O                        | 20   |

| e e e e e e e e e e e e e e e e e e e | 3.7.2     | Buffered I/O                      | 20   |

| <u>Section</u> | Paragraph | <u>Title</u>                      | Page |

|----------------|-----------|-----------------------------------|------|

|                | 3.7.3     | Direct Memory Access (DMA)        | 20   |

|                | 3.7.4     | Input/Output Operations           | 20   |

|                | 3.7.5     | Buffered I/O Status Word          | 22   |

| •              | 3.7.6     | Service Interrupt                 | 22   |

|                | 3.7.7     | TSE I/O Devices                   | 23   |

|                | 3.8       | Soft Stop                         | 28   |

|                | 3.9       | Test Support Equipment            | 28   |

|                | 3.9.1     | Function Code                     | 28   |

|                | 3.9.2     | System Reset                      | 30   |

| IV             |           | FIXED-POINT ARITHMETIC            | 31   |

|                | 4.1       | Data Format                       | 31   |

|                | 4.2       | Number Representation             | 32   |

|                | 4.3       | Condition Code                    | 33   |

|                | 4.4       | Instruction Format                | . 33 |

|                | 4.5       | Instructions                      | 34   |

|                | 4.5.1     | Load                              | 36   |

|                | 4.5.2     | Load Halfword                     | 36   |

|                | 4.5.3     | Load and Test                     | 37   |

|                | 4.5.4     | Load Complement                   | 37   |

| •              | 4.5.5     | Load Positive                     | 38   |

|                | 4.5.6     | Load Negative                     | 38   |

| •              | 4.5.7     | Load Multiple                     | 39   |

|                | 4.5.8     | Add                               | 39   |

|                | 4.5.9     | Add Halfword                      | 40   |

|                | 4.5.10    | Add Logical                       | 41   |

|                | 4.5.11    | Subtract                          | 42   |

|                | 4.4.12    | Subtract Halfword                 | 42   |

|                | 4.5.13    | Subtract Logical                  | 43   |

|                | 4.5.14    | Compare                           | 44   |

|                | 4.5.15    | Compare Halfword                  | 45   |

|                | 4.5.16    | Multiply                          | 45   |

|                | 4.5.17    | Multiply Halfword                 | 46   |

|                | 4.5.18    | Divide                            | 47   |

|                | 4.5.19    | Convert to Binary                 | 48   |

|                | 4.5.20    | Convert to Decimal                | 49   |

|                | 4.5.21    | Store                             | 49   |

|                | 4.5.22    | Store Halfword                    | 50   |

|                | 4.5.23    | Store Multiple                    | 50   |

|                | 4.5.24    | Shift Left Single                 | 51   |

|                | 4.5.25    | Shift Right Single                | 52   |

| •              | 4.5.26    | Shift Left Double                 | 53   |

|                | 4.5.27    | Shift Right Double                | 53   |

|                | 4.6       | Fixed-Point Arithmetic Exceptions | 54   |

| Section | Paragraph  | Title                               | Page |

|---------|------------|-------------------------------------|------|

| V       |            | DECIMAL ARITHMETIC                  | 56   |

|         | 5.1        | Data Format                         | 56   |

|         | 5.1.1      | Packed Decimal Number               | 56   |

|         | 5.1.2      | Zoned Decimal Number                | 56   |

|         | 5.2        | Number Representation               | 56   |

|         | 5.3        | Instructions                        | 57   |

|         | 5.3.1      | Pack                                | 57   |

|         | 5.3.2      | Unpack                              | 58   |

|         | 5.3.3      | Move with Offset                    | 59   |

| VI      |            | LOGICAL OPERATION                   | 60   |

|         | 6.1        | Data Format                         | 60   |

|         | 6.1.1      | Fixed-Length Logical Information    | 60   |

|         | 6.1.2      | Variable-Length Logical Information | 61   |

|         | 6.2        | Condition Code                      | 62   |

|         | 6.3        | Instruction Format                  | 62   |

|         | 6.4        | •                                   |      |

| 3.1     | 6.4.1      | Instructions                        | 64   |

|         | 6.4.2      | Move Move Numerics                  | 65   |

|         |            |                                     | 66   |

|         | 6.4.3      | Move Zones                          | 66   |

|         | 6.4.4      | Compare Logical                     | 67   |

| •       | 6.4.5      | And                                 | 68   |

|         | 6.4.6      | Or .                                | 69   |

| •       | 6.4.7      | Exclusive Or                        | 70   |

|         | 6.4.8      | Test Under Mask                     | 71   |

|         | 6.4.9      | Insert Character                    | 72   |

|         | 6.4.10     | Store Character                     | 72   |

|         | 6.4.11     | Load Address                        | 72   |

|         | 6.4.12     | Translate                           | 73   |

|         | 6.4.13     | Translate and Test                  | 74   |

|         | 6.4.14     | Shift Left Single                   | 75   |

|         | 6.4.15     | Shift Right Single                  | 75   |

|         | 6.4.16     | Shift Left Double                   | 76   |

|         | 6.4.17     | Shift Right Double                  | 76   |

|         | 6.5        | Logical Operation Exceptions        | 77   |

| VII     |            | BRANCHING                           | 79   |

|         | <b>7.1</b> | Normal Sequential Operation         | 79   |

|         | 7.1.1      | Sequential Operation Exceptions     | 80   |

|         | 7.2        | Decision-Making                     | 82   |

|         | 7.3        | Instruction Formats                 | 82   |

|         | 7.4        | Branching Instructions              | 84   |

|         | 7.4.1      | Branch on Condition                 | 84   |

|         | 7.4.2      | Branch and Link                     | 87   |

| ,       | 7.4.3      | Brench on Count                     | 07   |

| Section . | Peragraph | Title                          | Page |

|-----------|-----------|--------------------------------|------|

| •         | 7.4.4     | Branch on Index High           | 88   |

|           | 7.4.5     | Branch on Index Low or Equal   | . 89 |

|           | 7.4.6     | Execute                        | 89   |

|           | 7.4.6.1   | Execute Exceptions             | 91   |

| VIII      |           | STATUS SWITCHING               | 92   |

|           | 8.1       | Program States                 | 92   |

|           | 8.1.1     | Problem State                  | 92   |

|           | 8.1.2     | Wait State                     | 93   |

|           | 8.2       | Protection                     | 94   |

|           | 8.2.1     | Area Identification            | 94   |

|           | 8.2.2     | Protection Action              | 94   |

|           | 8.3       | Program Status Word            | 94   |

|           | 8.4       | Instruction Format             | 96   |

| * .       | 8.5       | Instructions                   | 97   |

|           | 8.5.1     | Load PSW                       | 98   |

|           | 8.5.2     | Set Program Mask               | 99   |

|           | 8.5.3     | Set System Mask                | 99   |

|           | 8.5.4     | Supervisor Call                | 99   |

|           | 8.5.5     | Set Storage Key                | 100  |

| 7         | 8.5.6     | Test and Set                   | 160  |

|           | 8.5.7     | Start Input Output             | 101  |

|           | 8.5.8     | Timer Read and Set             | 103  |

|           | 8.5.9     | Diagnose                       | 104  |

|           | 8.6       | Status-Switching Exceptions    | 104  |

| IX        |           | INTERRUPTIONS                  | 106  |

|           | 9.1       | Interruption Action            | 106  |

|           | 9.1.1     | Instruction Execution          | 106  |

|           | 9.1.2     | Source Identification          | 107  |

|           | 9.1.3     | Location Determination         | 108  |

|           | 9.2       | Input/Output Interruption      | 108  |

|           | 9.3       | Program Interruption           | 109  |

| •         | 9.3.1     | Operation Exception            | 110  |

|           | 9.3.2     | Privileged-Operation Exception | 110  |

|           | 9.3.3     | Execute Exception              | 110  |

|           | 9.3.4     | Protection Exception           | 110  |

|           | 9.3.5     | Addressing Exception           | 110  |

|           | 9.3.6     | Specification Exception        | 111  |

|           | 9.3.7     | Data Exception                 | 111  |

|           | 9.3.8     | Fixed-Point-Overflow Exception | 111  |

|           | 9.3.9     | Fixed-Point-Divide Exception   | 111  |

|           | 9.3.10    | Buffered I/O Exception         | 112  |

|           | 9.3.11    | Supervisor-Call Interruption   | 112  |

| ection | Paragraph | Title                        | Pare |

|--------|-----------|------------------------------|------|

|        | 9.4       | External Interruption        | 112  |

|        | 9.4.1     | Timer                        | 113  |

|        | 9.4.2     | Interrupt Key                | 113  |

|        | 9.4.3     | Interval Timer               | 113  |

| •      | 9.5       | Machine-Check Interruption   | 114  |

| x ·    |           | SHORT PRECISION OPTION       | 115  |

| -      | 10.1      | Data Format                  | 115  |

| •      | 10.2      | Number Representation        | 116  |

|        | 10.3      | Condition Code               | 116  |

|        | 10.4      | Instruction Format           | 117  |

|        | 10.5      | Instructions                 | 119  |

|        | 10.5.1    | ADD Halfword                 | 121  |

|        | 10.5.2    | ADD Short                    | 121  |

|        | 10.5.3    | Branch Unconditional         | 122  |

|        | 10.5.4    | Compare Halfword             | 123  |

|        | 10.5.5    | Compare Logical Short        | 124  |

|        | 10.5.6    | Compare Short                | 125  |

|        | 10.5.7    | Divide Short                 | 126  |

|        | 10.5.8    | Load Address Short           | 127  |

| •      | 10.5.9    | Load Complement Short        | 127  |

|        | 10.5.10   | Load Full to Short Register  | 128  |

|        | 10.5.11   | Load Halfword                | 129  |

|        | 10.5.12   | Load Negative Short          | 129  |

|        | 10.5.13   | Load Positive Short          | 130  |

|        | 10.5.14   | Load Short                   | 131  |

|        | 10.5.15   | Load and Test                | 131  |

|        | 10.5.16   | Load and Test Short          | 132  |

|        | 10.5.17   | Multiply Halfword            | 133  |

|        | 10.5.18   | Multiply Short               | 133  |

|        | 10.5.19   | Normalize                    | 134  |

|        | 10.5.20   | AND Short                    | 135  |

|        | 10.5.21   | OR Short                     | 136  |

|        | 10.5.22   | Shift Left Arithmetic Short  | 137  |

|        | 10.5.23   | Shift Left Logical Short     | 138  |

| * ,    | 10.5.24   | Shift Right Arithmetic Short | 139  |

|        | 10.5.25   | Shift Right Logical Short    | 140  |

|        | 10.5.26   | Subtract Halfword            | 140  |

|        | 10.5.27   | Subtract Short -             | 141  |

|        | 10.5.28   | Test Bits                    | 142  |

|        | 10.5.29   | Exclusive OR Short           | 143  |

| •      | 10.6      | Chart Dreateian Eventions    | 144  |

| Section | Paragraph | <u>Title</u>                 | Page |

|---------|-----------|------------------------------|------|

| XI      |           | DOUBLE PRECISION FIXED-POINT |      |

|         |           | ARITHMETIC OPTION            | 146  |

|         | 11.1      | Data Format                  | 146  |

|         | 11.2      | Number Representation        | 146  |

|         | 11.3      | Condition Code               | 147  |

|         | 11.4      | Instruction Format           | 148  |

|         | 11.5      | Instructions                 | 149  |

|         | 11.5.1    | Load Double                  | 149  |

|         | 11.5.2    | Load Complement Double       | 150  |

|         | 11.5.3    | Add Double                   | 150  |

|         | 11.5.4    | Subtract Double              | 151  |

|         | 11.5.5    | Compare Double               | 152  |

|         | 11.5.6    | Store Double                 | 153  |

|         | 11.6      | Double Precision Fixed-Point | 153  |

|         |           | Arithmetic Exceptions        |      |

| XII     |           | FLOATING-POINT ARITHMETIC    |      |

|         | 12.1      | Data Format                  | 155  |

|         | 12.2      | Number Representation        | 156  |

|         | 12.3      | Normalization                | 157  |

|         | 12.4      | Condition Code               | 157  |

|         | 12.5      | Instruction Formst           | 158  |

|         | 12.6      | Instructions                 | 159  |

|         | 12.6.1    | Load                         | 160  |

|         | 12.6.2    | Load and Test                | 161  |

|         | 12.6.3    | Load Complement              | 161  |

|         | 12.6.4    | Load Positive                | 162  |

|         | 12.6.5    | Load Negative                | 162  |

| •       | 12.6.6    | Add Normalized               | 163  |

| •       | 12.6.7    | Add Unnormalized             | 164  |

|         | 12.6.8    | Subtract Normalised          | 165  |

|         | 12.6.9    | Subtract Unnormalized        | 166  |

|         | 12.6.10   | Compare                      | 166  |

|         | 12.6.11   | Halve ·                      | 167  |

|         | 12.6.12   | Multiply                     | 168  |

|         | 12.6.13   | Divide                       | 169  |

|         | 12.6.14   | . Store                      | 171  |

|         | 12.7      | Floating-Point Arithmetic    | 171  |

|         |           | Exceptions                   |      |

### **PREFACE**

This document is the Machine Reference Manual for the NSSC-II. It provides a description of the system structure, the arithmetic, logical, branching, status switching, I/O operations, and the interrupt and timer systems.

The NSSC-II is a 16-bit, fixed point, microprogram controlled, general purpose computer.

The NSSC-II architecture is the same as the IBM System/360 architecture. The basic NSSC-II supports 83 of the 87 instructions in the IBM System/360 Standard Instruction Set; the basic NSSC-II also supports three unique instructions which control the timers, I/O, and storage protection. The first nine sections of this document describe the basic NSSC-II.

A short precision option is available for the NSSC-II. This option consists of 53 additional instructions which deal primarily with 16-bit operands. These instructions generally execute faster than their counterparts in the basic NSSC-II instruction set, which operate on 32-bit operands. An additional instruction format is included in this option which increases execution speed and reduces main storage requirements. The short precision option is described in Section X.

A double precision fixed point option is also available for the NSSC-II. This option consists of 10 additional instructions which operate with 64-bit fixed point operands. This option is described in Section XI.

A floating point option is also available for the NSSC-II. This option consists of 22 additional instructions which are used to perform calculations on operands with a wide range of magnitude and yield results scaled to preserve precision. This option is described in Section XII.

The following NSSC-II documents contain essentially the same information as provided in the corresponding System/360 documentation referenced herein:

NSSC-II Assembler Language, IBM Number 7935401 NSSC-II Linkage Editor, IBM Number 7935413

#### SECTION I

### NSSC-II ARCHITECTURE

### 1.1 NSSC-II INSTRUCTION SET

The NSSC-II is compatible with the IBM System/360 Problem State Standard Instruction Set. Problem programs written for the S/360 Standard Instruction Set will execute properly without change on the NSSC-II.

There are 171 valid NSSC-II instructions. Eighty-three of them are from the 87-member S/360 Standard Instruction Set. Omitted from the NSSC-II set are HIO, SIO, TCH, and TIO.

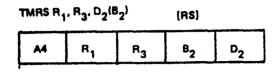

Three additional instructions, also described below, are:

|                    | Mnemonic | OP Code | Format |

|--------------------|----------|---------|--------|

| Timer Read and Set | TMRS     | A4      | RS     |

| Start I/O          | SIO      | A5      | RS     |

| Set Storage Key    | SSK      | 08      | RR     |

Note that although mnemonic SIO is used for Start I/O, and is the only NSSC-II I/O instruction, it is not the same instruction (and does not have the same op code) as the 360 SIO. Op codes A4 and A5 are unused in 360. SSK does have the same op code as 360 SSK, but performs a different function, as described below.

### 1.2 EXCEPTIONS

The NSSC-II is a Supervisor State compatible with the IBM System/360 with the following exceptions:

### 1.2.1 INPUT/OUTPUT

The I/O portion of the NSSC-II provides the means of communication between the system I/O and test support equipment (TSE) with the CPU and the main store (MS). In the 16 bit NSSC-II the I/O is implemented as a 16 bit parallel channel providing direct I/O, buffered I/O, external interrupt, and direct memory access (DMA). The 16 bit channel is SP-1 hardware compatible. There is only one I/O instruction - the SIO (Start I/O) instruction which controls direct I/O. All other I/O is device controlled.

### 1.2.2 TIMER

The NSSC-II has a real time clock and an interval timer, each containing both hardware and microprogrammed elements. Both are accessed by using the TMRS instruction. The S/360 interval timer in memory location 80 is not supported.

The interval timer (INTIMER) is 16 bits and is decremented every 112.64 microseconds. It has a maximum of 7.38 seconds. Underflow of the interval timer causes a timer external interrupt (which can be masked; see paragraph 3.6.5.1, External Interrupt.)

The real time clock (RTC) is 32 bits and is incremented every 112.64 microseconds. It has a maximum of 5 days, 14 hours, 23 minutes, and 5.116 seconds. It causes no interrupt on overflow.

### 1.2.3 STORAGE PROTECT

The size of the storage protect blocks in the NSSC-II is 1024 bytes (512 halfwords) and the operand of the SSK (Set Storage Key) instruction supports one bit for CPU and Buffered I/O protection and a second bit for DMA protection. The 4 or 5 bit protection key of S/360 is not supported. The instruction ISK (Insert Storage Key) does not exist on the NSSC-II.

### 1.2.4 EXECUTION TIMES

The instruction execution time is not the same for the NSCC-II and  $\underline{\text{any}}$  IBM 360.

# 1.2.5 UNPREDICTABLE RESULTS

These occur due to addressing errors, etc., on the IBM 360 series and will not necessarily be the same unpredictable results on the NSSC-II.

# 1.2.6 ADDRESSING EXCEPTION

Execution of most instructions residing in the last fullword of memory will yield unpredictable results, unless memory size is 64/K bytes.

### 1.2.7 ADDRESSING

All effective address computation is limited to 20 bits except for the LA (Load Address) instruction, which is 24 bits. Effective addresses larger than 65,535 will be truncated to 20 bits (modulo 1,048,575) and will not cause an addressing exception unless the modolo 1,048,575 address exceeds the available main memory. If the NSSC-II has 1,048,575 bytes of main memory, an addressing exception cannot occur.

#### SECTION II

#### SYSTEM STRUCTURE

### 2.1 MAIN STORAGE

THE RESERVE THE PROPERTY OF TH

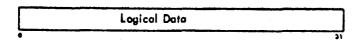

The NSSC-II has a maximum capacity of one mega-byte; however, the current capacity is 112K-bytes of Simplex memory or 80K-bytes of Fault Tolerant memory. The programmer should be aware of the size of the NSSC-II being programmed. The system transmits information between main storage and the CPU in units of eight bits, or a multiple of eight bits at a time. Each eight bit unit of information is called a byte, the basic building block of all formats.

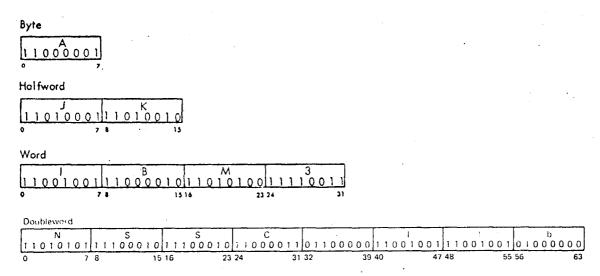

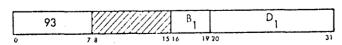

Bytes may be handled separately or grouped together in fields. A half-word is a group of two consecutive bytes and is the basic building block of instructions. A word is a group of four consecutive bytes; a double word is a field consisting of two words (Figure 1). The location of any field or group of bytes is specified by the address of its leftmost byte.

The length of fields is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length, which can be either one, two, four, or eight bytes.

When the length of a field is not implied by the operation code, but is stated explicitly, the information is said to have variable field length. This length can be varied in one-byte increments.

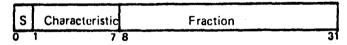

Within any program format or any fixed length operand format, the bits making up the format are consecutively numbered from left to right starting with the number 0.

Figure 1. Sample Information Formats

### 2.2 ADDRESSING

Byte locations in storage are consecutively numbered starting with 0; each number is considered the address of the corresponding byte. A group of bytes in storage is addressed by the leftmost byte of the group. The number of bytes in the group is either implied or explicitly defined by the operation. The addressing arrangement uses a 20 bit binary address. This set of main storage addresses includes some locations reserved for special purposes.

Storage addressing wraps around from the maximum byte address to address 0. Variable length operands may be located partially in the last and partially in the first location of storage, and are processed without any special indication of crossing the maximum address boundary, except, perhaps, storage protection.

When only a part of the maximum storage capacity is available in a given installation, the available storage is normally contiguously addressable, starting at address 0. An addressing exception is recognized when any part of an operand is located beyond the maximum available capacity of an installation. Except for a few instructions, the addressing exception is recognized only when the data are actually used and not when the operation is completed before using the data. The addressing exception causes a program interruption.

## 2.3 INFORMATION PROCESSING

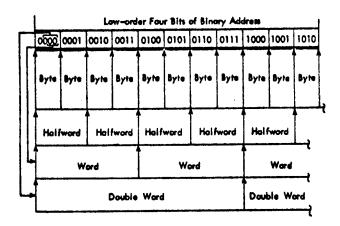

Fixed length fields, such as halfwords and double words, must be located in main storage on an integral boundary for that unit of information. A boundary is called integral for a unit of information when its storage address is a multiple of the length of the unit in bytes. For example, words (four bytes) must be located in storage so that their address is a multiple of the number 4. A halfword (two bytes) must have an address that is a multiple of the number 2, and double word (eight bytes) must have an address that is a multiple of the number 8.

Storage addresses are expressed in binary form. In binary, integral boundaries for halfwords, words, and double words can be specified only by the binary addresses in which one, two, or three of the low order bits, respectively, are zero (Figure 2). For example, the integral boundary for a word is a binary address in which the two low order positions are zero.

Variable length fields are not limited to integral boundaries, and may start on any byte location.

Figure 2. Integral Boundaries for Halfwords, Words, and Double Words

# 2.4 STORAGE PROTECTION

Memory is protected (for storing only) in blocks of 1K = 1024 bytes. There is no fetch protection. A two bit protect key is associated with each block. The first bit on protects the block against stores by the CPU; the second bit on protects the block against stores by Direct Memory Access (DMA). The key is set by the SSK instruction but cannot be read (refer to paragraph 8.5.5, SSK, and paragraph 3.7.3, DMA).

An interrupt will set the storage protect key for the first block to 01. This will allow the CPU to store in the first block and prevent DMA from storing in the first block. All other storage protect keys are unaltered by interrupts.

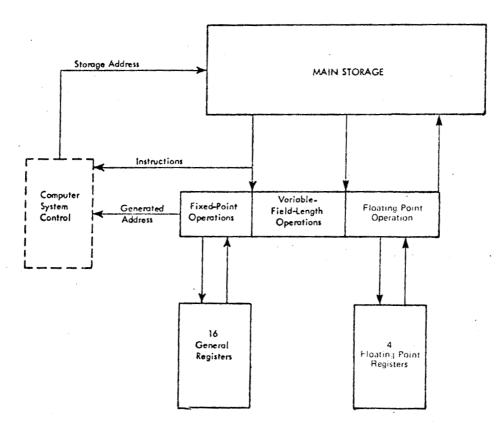

### 3.1 CENTRAL PROCESSING UNIT FUNCTIONS

The Central Processing Unit (CPU) (Figure 3) contains the facilities for addressing main storage, for fetching or storing information, for arithmetic and logical processing of data, for sequencing instructions in the desired order, and for initiating the communication between storage and external devices.

The system control section provides the normal CPU control that guides the CPU through the functions necessary to execute the instructions.

The CPU provides 16 general registers for fixed point operands and 4 floating point registers for floating point operands.

Figure 3. Basic Concept of Central Processing Unit Functions

### 3.2 REGISTERS

The CPU can address information in 16 general registers. The general registers can be used as index registers, in address arithmetic and indexing, and as accumulators in fixed point arithmetic and logical operations. The registers have a capacity of one word (32 bits). The general registers are identified by numbers 0-15 and are specified by a four bit R field in an instruction. Some instructions provide for addressing multiple general registers by having several R fields.

For some operations, two adjacent general registers are coupled together, providing a two word capacity. In these operations, the addressed register contains the high order operand bits and must have an even address; and the implied register, containing the low order operand bits, has the next higher address.

The CPU can address information in 4 floating point registers. The registers have a capacity of one word (32 bits). The floating point registers are identified by the numbers 0-2-4-6 and are specified by the four bit R field in an instruction. The floating point registers cannot be used as index registers.

# 3.3 ARITHMETIC AND LOGICAL UNIT

The arithmetic and logical unit can process binary integers of fixed length and logical information of either fixed or variable length.

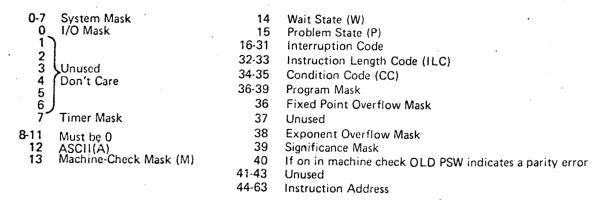

### 3.3.1 FIXED POINT ARITHMETIC

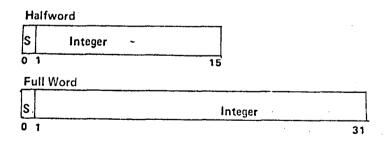

The basic arithmetic operand is the 32 bit fixed point binary word. Sixteen bit halfword operands may be specified in most operations for improved performance or storage utilization (see Figure 4). To preserve precision, some products and all dividends are 64 bits long.

Figure 4. Fixed-Point Number Formats

Because the 32 bit word size readily accommodates a 16-bit address, fixed point arithmetic can be used both for integer operand arithmetic and for address arithmetic. This combined usage provides economy and permits the entire fixed point instruction set and several logical operations to be used in address computation. Thus, multiplication, shifting, and logical manipulation of address components are possible.

Additions, subtractions, multiplications, divisions, and comparisons are performed upon one operand in a register and another operand either in a register or from storage. Multiple precision operation is made convenient by the twos-complement notation and by recognition of the carry from one word to another. A word in one register or a double word in a pair of adjacent registers may be shifted left or right. A pair of conversion instructions -- CONVERT TO BINARY and CONVERT TO DECIMAL -- provides transition between decimal and binary radix (number base) without the use of tables. Multiple register loading and storing instructions facilitate subroutine switching.

## 3.4 DECIMAL NUMBERS

Decimal numbers are represented by four bit binary coded decimal digits packed two to a byte (see Figure 5). They appear in fields of variable length and are accompanied by a sign in the right-most four bits of the low order byte. Operand fields may be located on any byte boundary.

| Digit | Code | Sign | Code |

|-------|------|------|------|

| 0     | 0000 | +    | 1010 |

| 1     | 0001 | -    | 1011 |

| 2     | 0010 | +    | 1100 |

| 3     | 0011 | _    | 1101 |

| 4     | 0100 | +    | 1110 |

| 5     | 0101 | •+   | 1111 |

| 6     | 0110 |      |      |

| 7     | 0111 |      |      |

| 8     | 1000 |      |      |

| 9     | 1001 |      |      |

Figure 5. Bit Codes for Digits and Signs

and may have a length up to 31 digits and sign. Operands participating in an operation may have different lengths. Packing of digits within a byte (Figure 6) and of variable length fields within storage results in efficient use of storage, in increased arithmetic performance, and in an improved rate of data transmission between storage and files.

|   | High-o | h-order Byte |       |  |  | Low-orde |       |       |       | er Byte | , |

|---|--------|--------------|-------|--|--|----------|-------|-------|-------|---------|---|

| ĺ | Digit  | Digit        | Digit |  |  | Digit    | Digit | Digit | Digit | Sign    |   |

Figure 6. Packed Decimal Number Format

Decimal numbers may also appear in a zoned format as a subset of the eight bit alphanumeric character set (Figure 7). This representation is required for character set sensitive I/O devices. A zoned format number carries its sign in the left-most four bits of the low order byte.

| High-order Byte |       |      |  | <br>      |      | L     | ow-ord | er Byte |

|-----------------|-------|------|--|-----------|------|-------|--------|---------|

| Zone            | Digit | Zone |  | <br>Digit | Zone | Digit | Sign   | Digit   |

Figure 7. Zoned Decimal Number Format

Instructions are provided for packing and unpacking decimal numbers so that they may be changed from the zoned to the packed format and vice versa.

# 3.5 LOGICAL OPERATIONS

Logical information is handled as fixed or variable length data. It is subject to such operations as comparison, translation, bit testing, and bit setting.

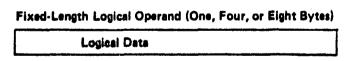

When used as a fixed length operand, logical information can consist of either one, four, or eight bytes and is processed in the general registers (Figure 8).

A large portion of logical information consists of alphabetic or numeric character codes, called alphameric data, and is used for communication with character set sensitive I/O devices. This information has the variable-field-length format and can consist of up to 256 bytes (Figure 9). It is processed storage to storage, left to right, an eight bit byte at a time.

Figure 8. Fixed-Length Logical Information

Variable-Length Logical Operand (Up to 256 Bytes)

Character Character Character

Figure 9. Variable-Length Logical Information

# 3.6 PROGRAM EXECUTION

The CPU program consists of instructions, index words, and control words specifying the operations to be performed. This information resides in main storage and general registers, and may be operated upon as data.

### 3.6.1 INSTRUCTION FORMAT

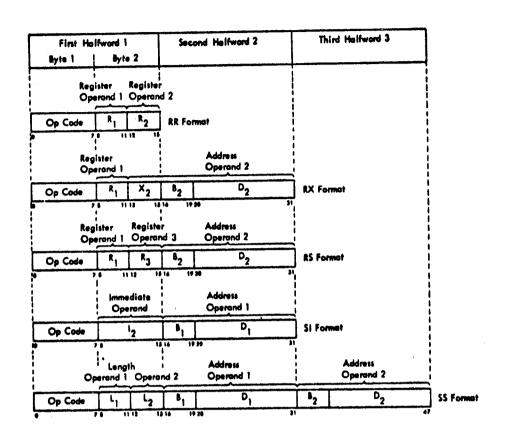

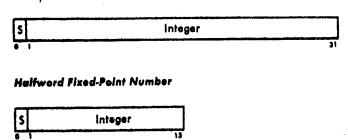

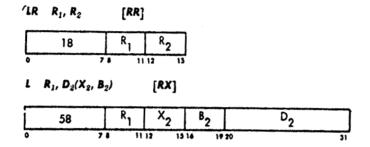

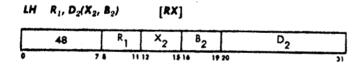

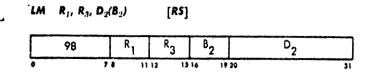

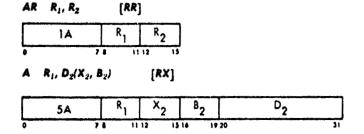

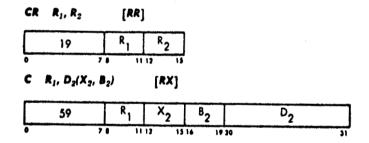

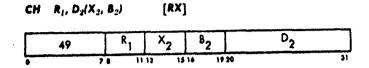

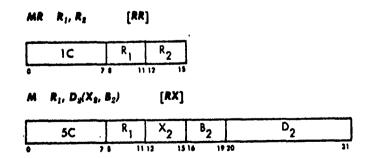

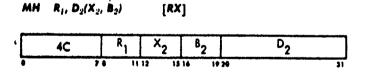

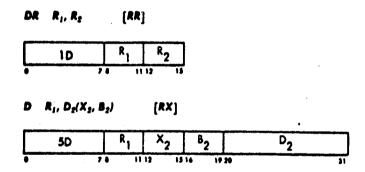

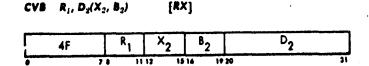

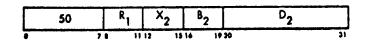

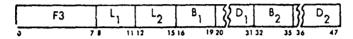

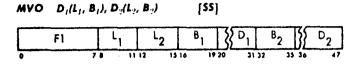

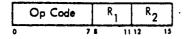

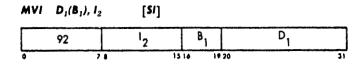

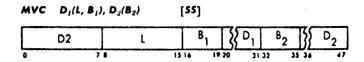

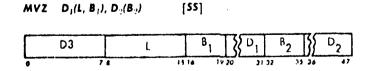

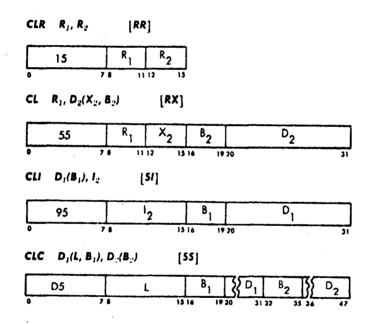

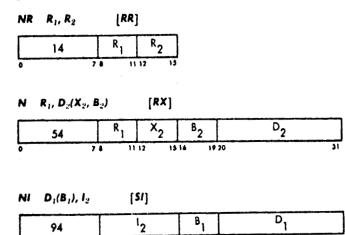

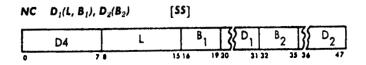

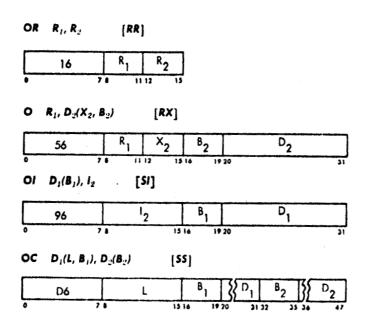

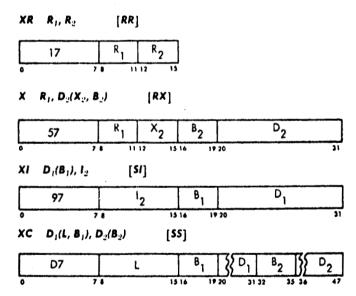

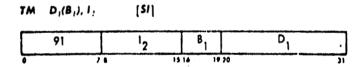

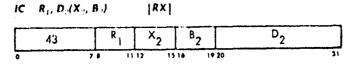

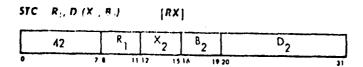

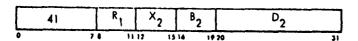

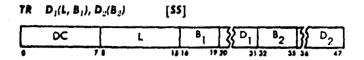

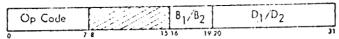

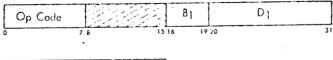

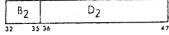

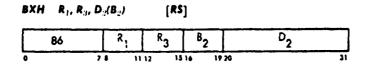

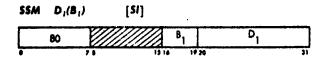

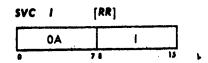

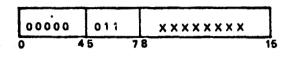

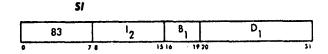

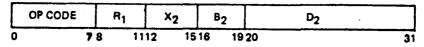

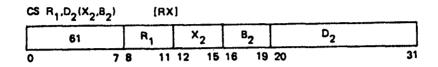

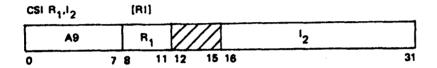

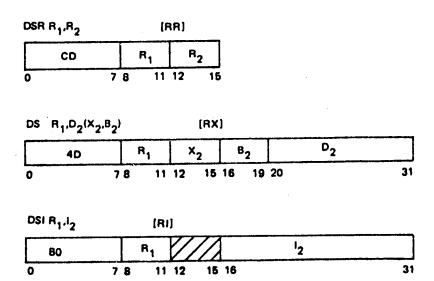

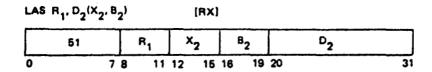

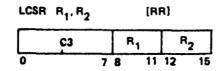

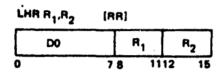

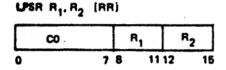

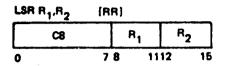

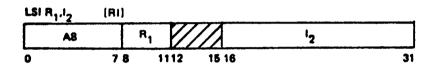

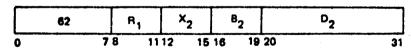

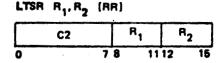

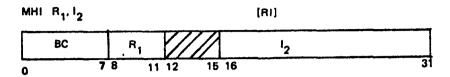

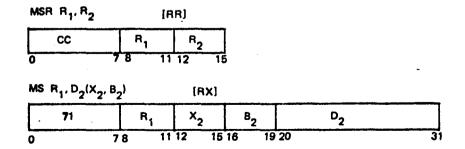

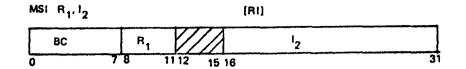

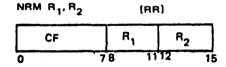

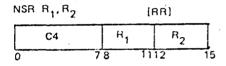

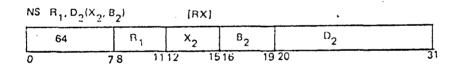

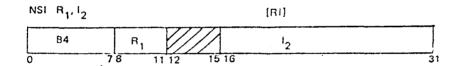

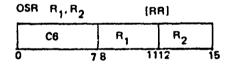

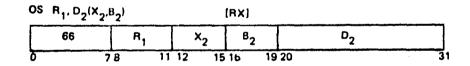

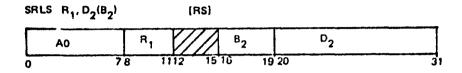

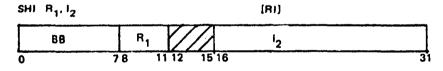

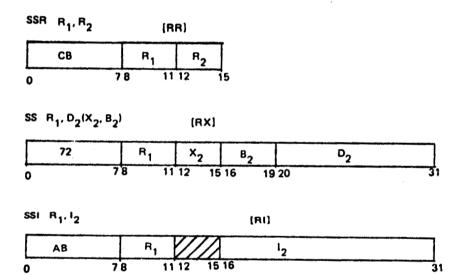

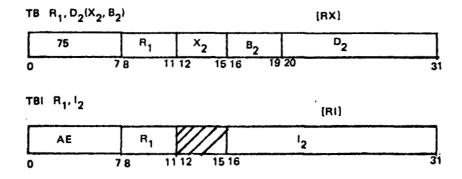

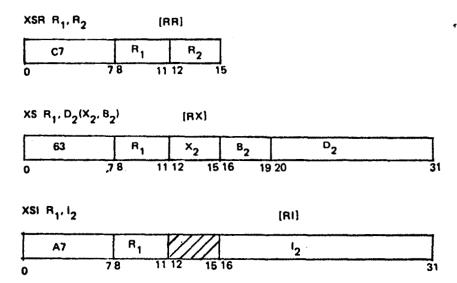

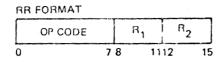

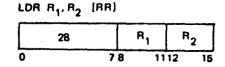

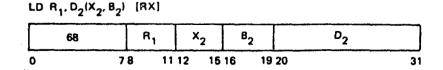

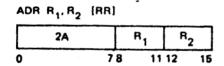

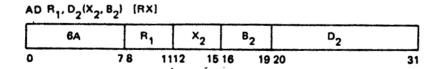

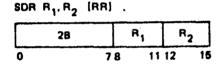

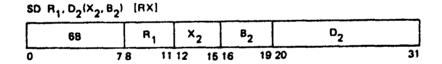

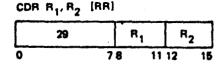

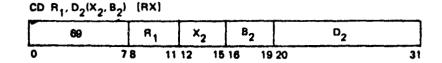

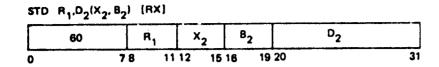

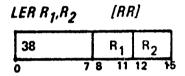

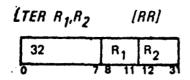

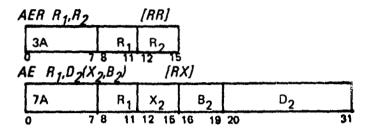

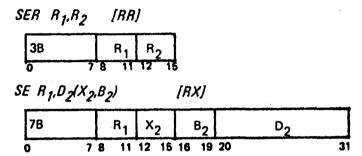

The length of an instruction format can be one, two, or three halfwords. It is related to the number of storage addresses necessary for the operation. An instruction consisting of only one halfword causes no reference to main storage. A two halfword instruction provides one storage address specification; a three halfword instruction provides two storage address specifications. All instructions must be located in storage on integral boundaries for halfwords. Figure 10 shows five basic instruction formats.

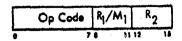

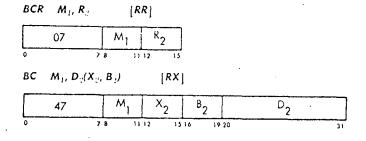

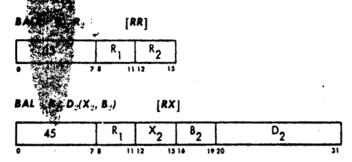

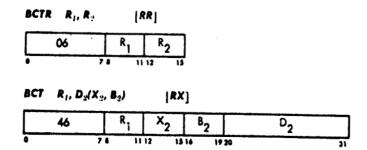

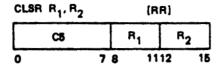

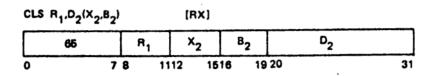

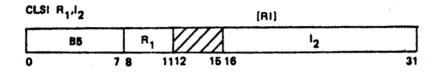

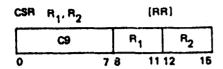

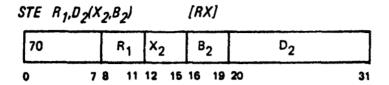

The five basic instruction formats are denoted by the format codes RR, RX, RS, SI, and SS. The format codes express, in general terms, the operation to be performed. RR denotes a register-to-register operation; RX, a register-and-indexed storage operation; RS, a register-and-storage operation; SI, a storage and immediate-operand operation; and SS, a storage-to-storage operation. An immediate operand is one contained within the instruction.

For purposes of describing the execution of instructions, operands are designated as first and second operands and, in the case of branch-on-index instructions, third operands. These names refer to the manner in which the operands participate. The operand to which a field in an instruction format applies is generally denoted by the number following the code name of the field, for example,  $R_1$ ,  $B_1$ ,  $L_2$ ,  $D_2$ .

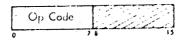

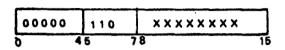

In each format, the first instruction halfword consists of two parts. The first byte contains the operation code (op code). The length and format of an instruction are specified by the first two bits of the operation code.

# 3.6.2 ADDRESS GENERATION

For addressing purposes, operands can be grouped in three classes: explicitly addressed operands in main storage; immediate operands placed as part of the instruction stream in main storage; and operands located in the general registers.

# INSTRUCTION LENGTH RECORDING

| BIT POSITIONS<br>(0-1) | INSTRUCTION<br>LENGTH | INSTRUCTION<br>FORMAT |

|------------------------|-----------------------|-----------------------|

| 00                     | One halfword          | RR                    |

| 01                     | Two halfwords         | RX                    |

| 10                     | Two halfwords         | RS or SI              |

| 11                     | Three halfwords       | 88                    |

NOTE: NSSC-II instructions above the standard System/360 set may not adhere to this instruction length format convention.

Figure 10. Five Basic Instruction Formats

To permit the ready relocation of program segments and to provide for the flexible specifications of input, output, and working areas, all instructions referring to main storage have been given the capacity of employing a full address.

The address used to refer to main storage is generated from the following three binary numbers.

## 3.6.2.1 Base Address (B)

Base Address (B) is a 20-bit number contained in a general register specified by the program in the B field of the instruction. The B field is included in every address specification. The base address can be used as a means of static relocation of programs and data. In array-type calculations, it can specify the location of an array and, in record-type processing, it can identify the record. The base address provides for addressing the entire main storage. The base address may also be used for indexing purposes.

# 3.6.2.2 Index (X)

Index (X) is a 20-bit number contained in a general register specified by the program in the X field of the instruction. It is included only in the address specified by the RX instruction format. The RX format instructions permit double indexing; i.e., the index can be used to provide the address of an element within an array.

# 3.6.2.3 Displacement (D)

Displacement (D) is a 12-bit number contained in the instruction format and is included in every address computation. The displacement provides for relative addressing up to 4095 bytes beyond the element or base address. In array type calculations the displacement can be used to specify one of many items associated with an element. In the processing of records, the displacement can be used to identify items within a record.

In forming the address, the base address and index are treated as unsigned 20-bit positive binary integers. The displacement is similarly treated as a 12-bit positive binary integer. The three are added as 20 bit binary numbers, ignoring overflow. Since every address includes a base, the sum is always 20 bits long. The address bits are numbered 12-31 corresponding to the numbering of the base address and index bits in the general register.

The program may have zeros in the base address, index, or displacement fields. A zero is used to indicate the absence of the corresponding address component. A base or index of zero implies that a zero quantity is to be used in forming the address, regardless of the contents of general register 0. A displacement of zero has no special significance. Initialization, modification, and testing of base addresses and indexes can be carried out by fixed point instructions, or by BRANCH AND LINK, BRANCH ON COUNT, or BRANCH-ON-INDEX instructions.

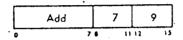

As an aid in describing the logic of the instruction format, examples of two instructions and their related instruction formats follow.

### **RR Format**

Execution of the ADD instruction adds the contents of general register 9 to the contents of general register 7 and the sum of the addition is placed in general register 7.

#### **RX Format**

Execution of the store instruction stores the contents of general register 3 at a main storage location addressed by the sum of 300 and the low order 20 bits of general registers 14 and 10.

# 3.6.3 SEQUENTIAL INSTRUCTION EXECUTION

Normally, the operation of the CPU is controlled by instructions taken in sequence. An instruction is fetched from a location specified by the instruction address in the current PSW. The instruction address is increased by the number of bytes in the instruction fetched to address the next instruction in sequence. The instruction is then executed and the same steps are repeated using the new value of the instruction address.

Conceptually, all halfwords of an instruction are fetched from storage after the preceding operation is completed and before execution of the current operation, even though physical storage word size and overlap of instruction execution with storage access may cause actual instruction fetching to be different. Thus, it is possible to modify an instruction in storage by the immediately preceding instruction. A change from sequential operation may be caused by branching, status switching, interruptions, or manual intervention.

# 3.6.3.1 Branching

The normal sequential execution of instructions is changed when reference is made to a subroutine, when a two-way choice is encountered, or when a segment of coding, such as a loop, is to be repeated. All these tasks can be accomplished with branching instructions. Provision is made for subroutine linkage, permitting not only the introduction of a new instruction address but also the preservation of the return address and associated information.

Decision making is generally and symmetrically provided by the BRANCH ON CONDITION instruction. This instruction inspects a two bit condition code that reflects the result of a majority of the arithmetic, logical, and I/O operations. Each of these operations can set the code in any one of four states, and the conditional branch can specify any selection of these four states as the criterion for branching. For example, the condition code reflects such conditions as nonzero, first operand high, equal, overflow, channel busy, zero, etc. Once set, the condition code remains unchanged until modified by an instruction that reflects a different condition code.

The two bits of the condition code provide for four possible condition code settings: 0, 1, 2, and 3. The specific meaning of any setting is significant only to the operation setting the condition code.

Loop control can be performed by the conditional branch when it tests the outcome of address arithmetic and counting operations. For some particularly frequent combinations of arithmetic and tests, the instructions BRANCH ON COUNT and BRANCH ON INDEX are provided. These specialized branches provide increased performance for these tasks.

### 3.6.4 PROGRAM STATUS WORD

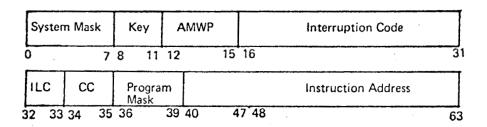

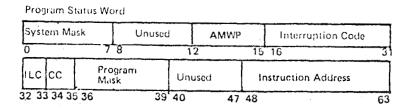

A double word, the program status word (PSW), contains the information required for proper program execution. The PSW includes the instruction address, condition code, and other fields to be discussed. In general, the PSW is used to control instruction sequencing and to hold and indicate the status of the system in relation to the program currently

being executed. The active or controlling PSW is called the "current PSW". By storing the current PSW during an interruption, the status of the CPU can be preserved for subsequent inspection. By loading a new PSW or part of a PSW, the state of the CPU can be initialized or changed. Figure 11 shows the PSW format.

Figure 11. Program Status Word Format

### 3.6.5 INTERRUPTION

The interruption system permits the CPU to change state as a result of conditions external to the system, in input/output (I/0) units, or in the CPU itself. Five classes of interruption conditions are possible: I/0, program, supervisor call, external, and machine check.

Each class has two related PSWs called "old" and "new" in unique main storage locations (Figure 12). In all classes, an interruption involves merely storing the current PSW in its "old" position and making the PSW at the "new" position the current PSW. The "old" PSW holds all necessary status information of the system existing at the time of the interruption. If, at the conclusion of the interruption routine, there is an instruction to make the old PSW the current PSW, the system is restored to the state prior to the interruption and the interrupted routine continues.

|                                                                                                       | ADDRESS                                                                                                                                                                                                                   | LENGTH                                                                                                                                                                                                                                           | PURPOSE                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>8<br>16<br>24<br>32<br>40<br>48<br>56<br>66-67<br>72<br>76<br>80<br>84<br>88<br>96<br>104<br>112 | 0000 0000<br>0000 1000<br>0001 0000<br>0001 1000<br>0010 0000<br>0011 1000<br>0011 1000<br>0100 0000<br>0100 1000<br>0101 0100<br>0101 0100<br>0101 0100<br>0101 1000<br>0101 1000<br>0111 0000<br>0111 1000<br>0111 1000 | Double Word Word Word Word Word Word Double Word | Initial Program Loading PSW Unused Unused External old PSW Supervisor call old PSW Program old PSW Machine check old PSW Input/Output old PSW Buffered I/O Status Word Channel Address Word Unused Unused Unused Unused External new PSW Supervisor call new PSW Program new PSW Machine check new PSW Input/Output new PSW |

Figure 12. Permanent Storage Assignments

Interruptions are taken only when the CPU is interruptible for the interruption source. The system mask, program mask, and machine check mask bits in the PSW may be used to mask certain interruptions. When masked off, an interruption either remains pending or is ignored. The system mask may cause I/O and timer interruptions to be ignored, and the machine-check mask may cause machine hard stops. Other interruptions cannot be masked off.

An interruption always takes place after one instruction execution is finished and before a new instruction execution is started. However, the occurrence of an interruption may affect the execution of the current instruction. To permit proper programmed action following an interruption, the cause of the interruption is identified and provision is made to locate the last executed instruction.

### 3.6.5.1 External Interrupts

External interrupts from two sources can occur: timer interrupts (when the interval timer underflows) and interrupts from the interrupt key. These interrupts are serviced between instructions.

These two types of external interrupts may be masked off. Timer interrupts are masked by bit 7 of the system mask (PSW bit 7), as usual. A 1 enables timer interrupts; a 0 masks them and the interrupt remains pending. External interrupt key interrupts are masked by system mask bit 0 (PSW bit 0) which is also used to mask I/O interrupts (refer to paragraph 3.6.5.3). If a key interrupt is disabled, it remains pending and the channel is hung. Other bits of the system mask are ignored and need not be zero upon PSW load or in the SSM instruction.

In NSSC-II, the two types of external interrupts are not presented simultaneously if they occur simultaneously or if they are enabled simultaneously. In either case, the timer interrupt is taken and the key

interrupt remains pending. The timer interrupt has interrupt code X'0080' and the external interrupt key interrupt has interrupt code X'0040'.

# 3.6.5.2 Program Interrupts

The following program exceptions are monitored in NSSC-II:

| Int | cerruption<br>Code | Program Interruption<br>Cause |

|-----|--------------------|-------------------------------|

| 1   | 00000001           | Operation                     |

| 2   | 00000010           | Privileged operation          |

| 3   | 00000011           | Execute                       |

| 4   | 00000100           | Protection                    |

| 5   | 00000101           | Addressing                    |

| 6   | 00000110           | Specification                 |

| 7   | 00000111           | Data                          |

| 8   | 00001000           | Fixed-point overflow          |

| 9   | 00001001           | Fixed-point divide            |

| 10  | 00001010           | Unused                        |

| 11  | 00001011           | Unused                        |

| 12  | 00001100           | Exponent overflow             |

| 13  | 00001101           | Exponent underflow            |

| 14  | 00001110           | Significance                  |

| 15  | 00001111           | Floating-point divide         |

More than one cause of a program interruption may occur at once, but only one program interrupt is taken. In NSSC-II, the following priorities apply when this occurs:

### Instruction Fetch:

Addressing and specification exceptions may co-occur. If the instruction address (address of the first halfword of the instruction) is out of the bounds of implemented memory, an addressing interrupt will occur. If, however, specification is bad (not on halfword boundary) and the second, third, or fourth halfword of the instruction has a bad address, a specification interrupt occurs.

### Instruction Execution:

Occurrence of an operation exception (invalid op code) rules out other interruptions. However, privileged operation, protection, addressing, and specification may co-occur. Privileged instructions are dealt with below. Barring other factors, also discussed below, the priority of these interrupts is:

Addressing Specification Storage Protection

# a) Privileged operations

There are six privileged instructions in NSSC-II. If a privileged operation exception occurs together with a memory reference exception (one of the three above) the following exception has priority and causes the interrupt:

- i) SSK privileged operation

- ii) SSM memory reference, in the above order

- iii) Diagnose privileged operation

- iv) SIO memory reference, in the above order

- v) TMRS For the interval timer, the memory reference takes priority. This is also the case for a bad RTC address. If only the second halfword of the RTC address is bad, the privileged operation exception will take precedence over the addressing exception (the RTC address need not be fullword aligned). A memory reference exception can take place even in cases of timer read only, but only for the first halfword address. (The second halfword is not read when the RTC is to be read only.)

- vi) LPSW If the new PSW address is not on a halfword boundary or is an invalid address, the addressing or specification exception will have priority over privileged operation. If the new PSW address is not on a double word boundary, the privileged operation interrupt will occur if in problem state.

- b) In the instructions D and M, a memory reference exception (for the second operand) takes precedence over a specification exception caused by improper (odd) register specification for the first operand.

- c) In SS instructions, memory reference exceptions for the second operand take precedence over those for the first operand.

Program interruptions can be masked off by the program mask in the PSW (bits 36-39). Each bit is associated with a program exception, as specified in the following table. When the mask bit is one, the exception results in an interruption. When the mask bit is zero, no interruption occurs. The significance mask bit also determines the manner in which floating-point addition and subtraction are completed.

| PROGRAM<br>MASK BIT | PROGRAM EXCEPTION    |

|---------------------|----------------------|

| 36                  | Fixed-point overflow |

| 37                  | Unused               |

| 38                  | Exponent underflow   |

| 39                  | Significance         |

|                     |                      |

# 3.6.5.3 Input/Output Interruption

An I/O interruption provides a means by which the CPU responds to conditions in the I/O units.

An I/O interruption can occur only when the mask bit associated with I/O is set to one. The status and address of the I/O unit involved are recorded in bits 16-31 of the old PSW.

#### 3.6.6 MACHINE STATES

# 3.6.6.1 Running or Waiting State

In the running state, instruction fetching and execution proceed in the normal manner. The wait state is normally entered by the program to await an interruption, for example, an I/O interruption. In the wait state, no instructions are processed; the timer is updated, and the I/O and external interruptions are accepted, unless masked. Running or waiting state is determined by the setting of bit 14 in the PSW.

# 3.6.6.2 Masked or Interruptible State

The CPU may be interruptible or masked for I/O, timer, machine-check, and some program interruptions. When the CPU is interruptible for a class of interruptions, these interruptions are accepted. When the CPU is masked, the I/O and timer interruptions remain pending, whereas program interruptions are ignored. The interruptible states of the CPU are changed by changing the mask bits of the PSW.

## 3.6.6.3 Supervisor or Problem State

In the problem state, I/O and a group of control instructions are invalid. In the supervisor state, all instructions are valid. The choice of problem or supervisor state is determined by bit 15 of the PSW.

### 3.7 **SYSTEM I/O**

Alberta Charles Care and Care

This section describes the interface of the NSSC-II with other system equipment.

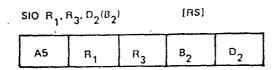

NSSC-II has a single 16-bit I/O channel providing communication between the CPU and main memory, and the I/O devices (of which there may be 16) and the test support equipment. Direct, or program-initiated, I/O is provided only through SIO instruction. All other I/O is device or TSE initiated.

The NSSC-II channel provides three types of device initiated information transfer: (1) Buffered I/O, (2) Direct Memory Access (DMA), and (3) External Interrupts. Program initiated I/O is provided by Direct I/O. A four bit device identification code permits up to 16 system devices to be attached directly to the HTC channel.

### 3.7.1 DIRECT I/O

This allows, using the SIO instruction, the transfer of a 16-bit control word to a device and the transfer of a 16-bit data (half) word to or from a device. Though this is the only program-controlled I/O, and it only allows transfer of one halfword at a time to or from memory, the programmer can, using SIO, send a control word to a device telling it to initiate I/O (see SIO).

# 3.7.2 BUFFERED I/O

This permits devices to transfer one or more 16-bit halfwords to or from a table in main memory without knowing the location of the table. Buffered I/O occurs between instructions but does not cause an interrupt (i.e., PSWs are not swapped, etc.). A device can cause an I/O interrupt to signal that buffered I/O has occurred.

# 3.7.3 DIRECT MEMORY ACCESS (DMA)

DMA allows devices to send data to or from main memory without going through the CPU. It is invisible to the programmer except when an error occurs; a device may signal DMA by causing an interrupt

### 3.7.4 INPUT/OUTPUT OPERATIONS

The NSSC-II interface provides a 16-bit parallel channel for support of two classes of I/O equipment. These are:

- 1. System I/O devices and

- 2. Test support equipment (TSE) I/O devices.

A particular I/O device is classified based on whether it is attached directly to the NSSC-II or indirectly via the TSE. Further provision has been made to allow both program and device initiated information transfer which includes I/O commands, data words, and external I/O interrupts.

This portion of the manual describes the programmed control of I/O devices by the channel and central processing unit (CPU) including formats for the various types of I/O control information. Although

certain information, formats, etc., may be applicable to both system and TSE I/O, each type is described individually for simplicity.

Buffered I/O allows a device to transfer single or multiple words of data to/from a table in main memory without knowing the location of the table. The CPU keeps track of table word count and address incrementing. When the table is full/empty the device is notified by a signal on the ZERO COUNT line. Separate input and output tables are maintained for each buffered device code (16 codes).

The Channel Address Word (CAW) at memory location 72, points to the first location of a table that consists of sixteen (16) eight (8) BYTE entries that contain the input storage address and count, and output storage address and count of each of the (possible) 16 Buffered I/O devices (see Figure 13).

The programmer controls Buffered I/O by initialization of the I/O address and word count in the Buffered I/O Control Table.

To initialize a buffer I/O sequence the programmer must:

The state of the second sec

- Set the CAW (loc 72) to the address of the start of the Buffered I/O table.

- Set the device I/O word count (in the buffered I/O table) to the number of 16 bit data words to be transferred.

- 3. Set the device I/O word address (in the Buffered I/O table) to the memory address of the beginning of the data to be written out (or to a location for the data to be written in).

- 4. Start the I/O device so it will request a buffer I/O interrupt. This is usually done by giving a direct out command to the device via a SIO instruction.

|               | INPUT             | ·                   | OUTP              | JT                  |

|---------------|-------------------|---------------------|-------------------|---------------------|

| DEVICE<br>NO. | 2 BYTES           | 2 BYTES             | 2 BYTES           | 2 BYTES             |

| •0            | I/O WORD<br>COUNT | I/O WORD<br>ADDRESS | I/O WORD<br>COUNT | I/O WORD<br>ADDRESS |

| 1<br>2<br>3   | "                 | "                   | ,, -              | "<br>"              |

| 4<br>5        | "                 | "<br>"              | "<br>"            | ** **<br>**<br>**   |

| 7 8           | "                 | <br>                | ,,<br>,,          | "                   |

| 15            | . "               | "                   | . "               | **                  |

| CAW = ADDRE   | SS OF THIS LOCA   | TION                |                   | ·                   |

Figure 13. Buffered I/O Device Table

The I/O word count is updated by one and the I/O address is updated by two in the I/O Control Table for each sixteen (16) bit [two byte] word that is transferred to or from memory by the CPU, unless the I/O word count is in TWOs complement form. If the I/O word count is in twos complement form, the I/O word count and I/O word address are not updated at the end of a Buffered I/O transfer. Therefore, the I/O address and word count start from the initial value each time the I/O device initiates a data transfer. This method of data transfer is useful for devices that send a burst of data periodically. Once a device initiates a transfer, the I/O channel is tied up until the device releases it.

If an I/O device requests a data transfer and the I/O Word Count is zero, an I/O error interrupt will be generated. The I/O Channel Code word is furnished as the interruption code in the I/O old PSW upon most I/O interrupts including error interrupt. The NSSC-II channel code word is shown in Figure 14.

It should be noted that even though the CPU hardware is interrupted to handle the buffered I/O transfers, the program is not interrupted and the time consuming save operations associated with program interrupt are not required. Buffered I/O operations are handled between instructions and do not use any register visible to the programmer.

### 3.7.5 BUFFERED I/O STATUS WORD

The Buffered I/O status word (loc 66-67) is set to the current Buffered I/O address during Buffered I/O operations and is cleared to zero when a Buffered I/O operation is completed successfully.

If an addressing exception, memory protect exception, or parity error occurs during Buffered I/O, an exception program interruption will be generated with the Buffered I/O status word set non zero; the contents will indicate the address of the Buffered I/O word in use at the time the error occurred.

### 3.7.6 SERVICE INTERRUPT

Interrupts permit a device to interrupt the normal program sequence. A single level of interrupt is provided. Programmed priorities may be implemented. In the interrupt sequence an I/O Channel Code word is sent from the device and stored as the Interruption Code in the old I/O PSW (see Figure 14).

The new I/O PSW is used as the current PSW on all I/O interrupts except Buffered I/O. A Buffered I/O interrupt is not visible to the programmer. He will never see bit 1 set in the I/O interrupt code.

A Direct Memory Access (DMA) error will cause a normal I/O interrupt, except the only bits set in the old I/O PSW interrupt code will be bits 3 or 4 indicating DMA error 1 or 2 (see Figure 14).

|               | Т | 1.0     | EX-<br>INT               | DMA<br>ERROR           | N<br>U     | CPU<br>USE | DEVI |    | FUNC |    |

|---------------|---|---------|--------------------------|------------------------|------------|------------|------|----|------|----|

| BIT           | 0 | 1       | 2                        | 3 4                    | 5          | 6 7        | 8    | 11 | 12   | 15 |

| NOTSE<br>BITS |   | USE     |                          |                        |            |            |      |    |      |    |

| 0             |   | LOGIC 1 | - I/O SERV<br>- TSE INTE | ICE<br>RRUPT           |            |            |      |    |      |    |

| 1             |   | LOGIC 1 | BUFFERI                  | ED INPUT               |            | USED OF    |      |    |      |    |

| 2             |   | LOGIC ( | · EXTERN                 | AL INTERRUPT<br>ED I/O | •          | -0         |      |    |      |    |

| 3             |   | DMA EF  | ROR NO. 1                |                        |            | •          |      |    |      |    |

| 4             |   | DMA E   | RROR NO. 2               |                        |            |            | ,    |    |      |    |

| 5             |   | UNUSE   | )                        |                        |            |            |      |    |      |    |

| 8-11          |   | TAG (D  | EVICE ADD                | RESS) OR INTE          | RRUPT CO   | DE         |      |    |      |    |

| 12-15         |   | DEVICE  | FUNCTION                 | CODE (MUST             | NOT BE ZER | RO)        |      |    |      |    |

Figure 14. I/O Interrupt Word

### 3.7.7 TSE I/O DEVICES

The TSE has a Typewriter/Paper Tape Reader or Typewriter/Magnetic Tape Reader, which are both direct I/O. All commands are sent to the TSE equipment and all data received by using the SIO instruction. The command word (see Figure 15 for TSE commands) is placed at the effective address (EA); the output data word is placed in the register designated by R1; and the data word read will be in the register designated by R3 after instruction completion. To write data to the typewriter:

- 1. Send a command to put the typewriter in the output mode.

- Send each character (byte) to the typewriter by placing it right justified in R1 and sending a write typewriter command.

- 3. Check the condition code after each SIO instruction to ensure the I/O interface was not busy and the instruction was completed successfully.

- 4. The Typewriter will give a typer cycle complete interrupt (see Figure 16) after each character is complete and it is ready to receive another command.

#### NOTE:

It is possible to preclude the typer cycle complete interrupt by immediately generating another Direct Out command to send the next character to the typewriter. The SIO instructions may be strung together in this manner and all I/O interrupts will be locked out as the typewriter will have control of the I/O channel for the whole period. Note that this type of operation will prevent the Clock and the Timer from being updated while the channel is tied up.

The typewriter input cycle is exactly the same as the output cycle except the typewriter must be placed in the input mode and each character of input is the register designated by R3 at the completion of each SIO instruction. To read from the paper tape:

- 1. Send a Start Tape command.

- When a tape character has been read and is ready to be transmitted to the CPU a Tape Data Ready I/O-TSE interrupt will be generated.

- 3. Read each character by sending a read tape command. Each character will be right justified in the register designated by R3 after the SIO instruction.

- 4. When the last desired character is read in, a stop tape command is sent to the tape reader.

#### NOTE:

It is possible to preclude the Tape Data Ready Interrupt by immediately generating another Direct In command to fetch the next character from the tape. The SIO instructions may be strung together in this manner and I/O interrupts will be locked out as the Tape Reader will have control of the I/O channel for the whole period. Note that this type of operation will prevent the Timer and Clock from being updated while the channel is tied up.

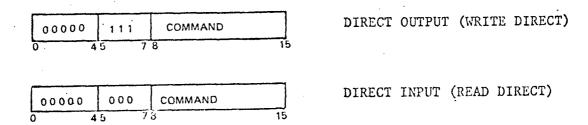

Direct I/O provides a means for the programmer to send a command or data word to an I/O device or request a data word from a device. Each Direct I/O instruction sends a 16-bit command word out on the System I/O channel and may send or request a data word to/from the addressed I/O device. Figure 17 shows the format of the command word. The channel is attached and relinquished for each Direct I/O instruction.

| 0        |   |   |        |     |     |        | 7         | 8                             | _ <del>1</del> 5                      |

|----------|---|---|--------|-----|-----|--------|-----------|-------------------------------|---------------------------------------|

| 1        | 1 | 1 | 1      | 1   | 1   | 1      | 1         | Command Code                  |                                       |

| <u> </u> |   |   |        |     |     |        |           |                               |                                       |

| 0        | 0 | 0 | 0      | 0   | 0   | 0      | 0         | Command Code                  |                                       |

| 8        |   | 9 |        |     | 11  | 12     |           |                               | 15                                    |

| 0        |   | ı | Unit A | ddr |     |        | Functi    | on Code                       |                                       |

|          | 8 | 8 | 8 9    | 8 9 | 8 9 | 8 9 11 | 8 9 11 12 | 0 0 0 0 0 0 0 0 0 0 8 9 11 12 | 0 0 0 0 0 0 0 Command Code  8 9 11 12 |

| Command                                           | Code                |

|---------------------------------------------------|---------------------|

| Typewriter Output Mode                            | 0000 0111 0000 0000 |

| Typewriter Input Mode                             | 1111 1111 0110 0010 |

| Read Typewriter                                   | 0000 0000 0110 0011 |

| Write Typewriter                                  | 1111 1111 0110 0100 |

| Start Tape                                        | 1111 1111 0100 0001 |

| Stop Tape Advance                                 | 1111 1111 0100 0010 |

| Read Tape                                         | 0000 0000 0100 0011 |

| Read 16 right-most bits of panel address register | 0000 0000 0000 0100 |

| Read 8 left-most bits of panel address register   | 0000 0000 0000 0101 |

| Read 16 left-most bits of panel data register     | 0000 0000 0000 0111 |

| Read 16 right-most bits of panel data register    | 0000 0000 0000 0110 |

| Display Registers                                 | 1111 1111 0000 1000 |

|                                                   |                     |

Figure 15. TSE Command Words

| INTERRUPT              | CODE                | CAUSE                                                                |

|------------------------|---------------------|----------------------------------------------------------------------|