# IBM RT PC Hardware Technical Reference

Volume I

# IBM RT PC Hardware Technical Reference

Volume I

#### Second Edition (September 1986)

Changes are made periodically to the information herein; these changes will be incorporated in new editions of this publication.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

International Business Machines Corporation provides this manual "as is," without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this manual at any time.

Products are not stocked at the address given below. Requests for copies of this product and for technical information about the system should be made to your authorized IBM RT PC dealer.

A reader's comment form is provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Department 997, 11400 Burnet Road, Austin, Texas 78758. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1986

#### **About This Book**

## **Purpose**

This manual describes the IBM RT Personal Computer<sup>1</sup> Product Family Hardware, the various units and components of the product family and how they interact. It provides information about the family system architecture, and about hardware and programming interfaces.

#### **Audience**

The information in this manual is for reference. It is intended for hardware and program designers, programmers, engineers, and anyone else who needs to understand the design and operation of the IBM RT¹ PC Product Family.

#### **How to Use This Book**

This manual is composed of ten sections. Section 1, System Introduction, introduces major system components in the order they are discussed in subsequent sections. It provides an initial description and understanding of the functions of key components of the product family workstations, and how the workstations are physically configured with various components.

An overview of the system architecture is included with a system block diagram which shows major partitions of the system unit elements such as the system board, processor board, memory boards, Floating-Point Accelerator board. Major system characteristics are described such as a 32-bit system unit, demand paged virtual memory system, high bandwidth interleaved memory and standard I/O.

Section 2 describes the major functions of the processor board. Section 3 provides a functional description of the system memory boards. Section 4 describes the Floating-Point Accelerator board. Section 5 contains information about the system boards, with a description of the differences between each of the boards as used with its unique system unit. Section 6 provides a complete architectural description of the I/O channel. Section 7 describes the functions provided by the system IPL ROM, including a list of the various error codes displayed by diagnostic routines. Section 8 contains information about adapters from the IBM Personal Computer Family, and their compatibility or noncompatibility with the RT PC¹family. Section 9 provides information about the

<sup>1</sup> Trademark of International Business Machines Corporation

locator, keyboard, characters, keystrokes. Section 10 describes the system unit physical dimensions, power, environmental and operating requirements. Section 11 includes detailed specification information for the system processor and memory management unit components.

Appendix A lists the instruction set by mnemonic and provides information for instruction execution time.

A glossary of terms and a bibliography of related publications is included.

An abbreviated index is included. A more complete Section Table of Contents is provided at the beginning of each section.

#### **Related Information**

IBM PC Network Technical Reference Manual

IBM RT PC Personal Computer AT Coprocessor Technical Reference

IBM RT PC Virtual Resource Manager Technical Reference

IBM Token-Ring Network RT PC Adapter Technical Reference Manual

# **Ordering Additional Copies of This Book**

To order additional copies of this publication, use either of the following sources:

- To order from your IBM representative, use Order Number SV21-8024.

- To order from your IBM dealer, use Part Number 74X9961.

A binder is included with the order.

# **Contents**

| Section 1. System Introduction                    |              |

|---------------------------------------------------|--------------|

| About this Section                                |              |

| General System Description                        |              |

| IBM 6150 System Unit                              |              |

| IBM 6151 System Unit                              | 1-0          |

| System Overview                                   | 1-           |

| System Board                                      | 1-9          |

| System Performance                                | 1-12         |

|                                                   | 1-13         |

|                                                   | 1-18         |

|                                                   | 1-19         |

| Processor Channel to I/O Address Bus Convention   | 1-20         |

| System Memory to Processor Channel Byte Positions | 1-2          |

|                                                   | 1-22         |

| IOCC to I/O Channel Alignment                     | 1-23         |

| Addressing Model                                  | 1-26         |

| Addressing From the I/O Channel                   | 1-31         |

|                                                   | 1-34         |

|                                                   | 1-36         |

| Section 2. Processor Board                        | 2-1          |

| About this Section                                |              |

| Processor Board Description                       |              |

| Processor Board Function Overview                 |              |

| Processor Channel Interface                       |              |

|                                                   | 2-16         |

|                                                   | 2-17         |

|                                                   | '            |

| Section 3. System Memory Boards                   | 3-1          |

| About this Section                                |              |

| Memory                                            | 3-4          |

| Section 4. Floating-Point Accelerator             | 4_1          |

| About this Section                                | 4-3          |

| Floating-Point Accelerator                        |              |

|                                                   | 4-13         |

|                                                   | 4-41<br>4-41 |

|                                                   | T1           |

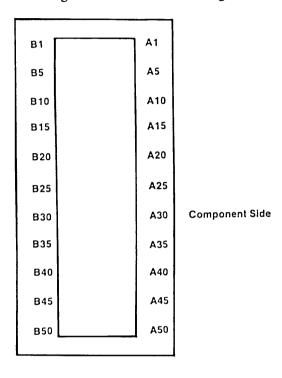

| Floating-Point Accelerator Board Pin Assignments              | 4-43  |

|---------------------------------------------------------------|-------|

| Section 5. System Boards                                      | . 5-1 |

| About this Section                                            | . 5-5 |

| IBM 6151 and IBM 6150 Common Features                         | . 5-6 |

| IBM 6150 Unique Features                                      |       |

| IBM 6151 Unique Features                                      | . 5-9 |

| System Board I/O Address Assignments                          | 5-12  |

| Addressing Modes                                              |       |

| Translation Modes                                             |       |

| Arbitration                                                   |       |

| I/O Channel Operations                                        |       |

| Interrupt Controllers                                         | 5-56  |

| Component Reset Register A (CRRA)                             | 5-59  |

| Component Reset Register B (CRRB)                             | 5-61  |

| Channel Status Register (CSR)                                 | 5-63  |

| Memory Configuration Register                                 | 5-73  |

| I/O Delay Register (IDR)                                      | 5-74  |

| I/O Subsystem Adapters                                        |       |

| Keyboard, Locator, Speaker Adapter                            |       |

| Adapter I/O Operations                                        |       |

| Adapter Commands                                              |       |

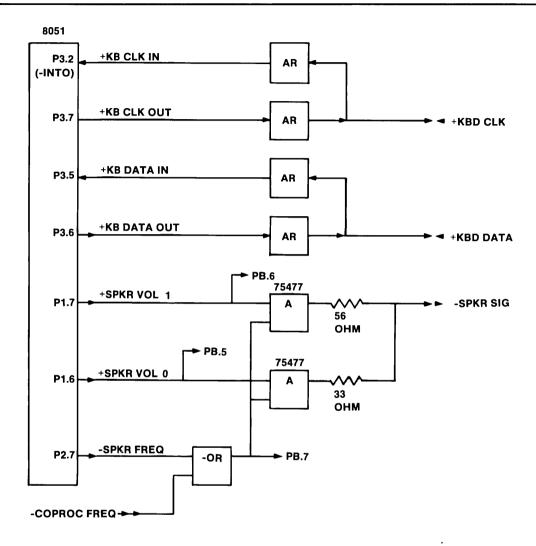

| Adapter Speaker Control                                       |       |

|                                                               | 5-123 |

| 11 mp vol 1 m m v v v v v v v v v v v v v v v v v             | 5-123 |

|                                                               | 5-130 |

|                                                               | 5-132 |

| System Board Connectors                                       | 5-144 |

| Section 6. I/O Channel                                        | . 6-1 |

| About this Section                                            | . 6-3 |

| Channel Features                                              |       |

| I/O Channel Signal Definitions                                | . 6-8 |

| I/O Channel Data Transfer                                     | 6-15  |

| Interrupts                                                    |       |

| I/O Channel Address Maps and Assignments                      | 6-48  |

| I/O Slot Uniqueness                                           | 6-54  |

| Connector/Pin Description and Electrical Characteristics      |       |

| Section 7. System IPL ROM                                     | 7 1   |

| About this Section                                            | . /-1 |

|                                                               |       |

| System IPL ROM                                                |       |

| Restrictions and Conventions for Externally Callable Routines | 7-17  |

| 1100dt timb bootion 111111111111111111111111111111111111 | -1<br>-3<br>-4 |

|----------------------------------------------------------|----------------|

| Section 9. User Input and Output Devices 9-              | -1             |

| About this Section                                       | -3             |

| Keyboard 9                                               | -4             |

| Locator                                                  | 24             |

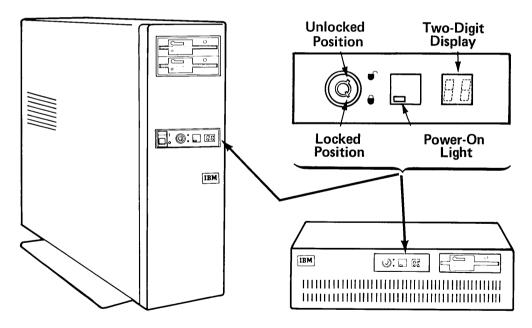

| Operator Panel 9-3                                       | 30             |

| Section 10. Power                                        | -1             |

| About this Section                                       |                |

| Input Power                                              | _              |

| Output Power                                             |                |

| •                                                        |                |

| Section 11. System Processor and MMU                     | _              |

| About this Section                                       | •              |

| System Processor                                         |                |

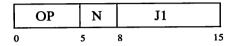

| Instruction Set                                          |                |

| Instruction Formats                                      | _              |

| Load and Store Instructions                              |                |

| Address Computation                                      |                |

| Branching                                                |                |

| Traps 11-4                                               |                |

| Moves and Inserts                                        |                |

| Arithmetic Operations                                    |                |

| Logical Operations                                       | 67             |

| Shifts                                                   | 73             |

| System Control                                           |                |

| Input/Output                                             |                |

| RAS Facilities                                           |                |

| Memory Management Unit                                   |                |

| Address Translation Hardware Operation                   |                |

| Memory Access Control                                    |                |

| Control Registers 11-13                                  |                |

| Translation Assist Functions                             |                |

| I/O Address Assignments                                  |                |

| I/O Base Address Register Initialization                 |                |

| ECC Checking                                             | 41             |

| Appendix A. Instruction Mnemonics                        |                |

| Privileged | Instructions | • • • • • |           |             | • • • • • • • |               |                                         | • • • • • • • • • • • • • • • • • • • • | A-8  |

|------------|--------------|-----------|-----------|-------------|---------------|---------------|-----------------------------------------|-----------------------------------------|------|

| Glossary   | •••••        | • • • • • | • • • • • | • • • • • • | • • • • • •   | • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | X-1  |

| Index      |              |           |           |             |               |               |                                         |                                         | X-15 |

# **Figures**

| 1-1.  | System Board Block Diagram                  | 1-8  |

|-------|---------------------------------------------|------|

| 1-2.  | Processor Channel Bit Convention            | 1-14 |

| 1-3.  | I/O Channel 8-Bit Convention                | 1-15 |

| 1-4.  | I/O Channel 16-Bit Convention               | 1-15 |

| 1-5.  | Processor Channel Byte Convention           | 1-15 |

| 1-6.  | I/O Channel Byte Convention                 | 1-16 |

| 1-7.  | System Memory Addressing Conventions        | 1-19 |

| 1-8.  | I/O Channel Address Bus Mapping             | 1-20 |

| 1-9.  | System Memory to Processor Channel Bytes    | 1-21 |

| 1-10. | Processor Channel to I/O Data Bus Mapping   | 1-22 |

| 1-11. | I/O Channel Data Bus                        | 1-22 |

| 1-12. | Data Alignment for 8- and 16-Bit Adapters   | 1-25 |

| 1-13. | System Processor Access to Address Maps     | 1-30 |

| 1-14. | Access to System Memory Maps from IOCC      | 1-33 |

| 1-15. | System Processor Address I/O Map            | 1-34 |

| 1-16. | System Processor Real Memory Address Map    | 1-35 |

| 1-17. | System Processor Virtual Memory Address Map | 1-35 |

| 1-18. | Interrupt Level Assignment                  | 1-37 |

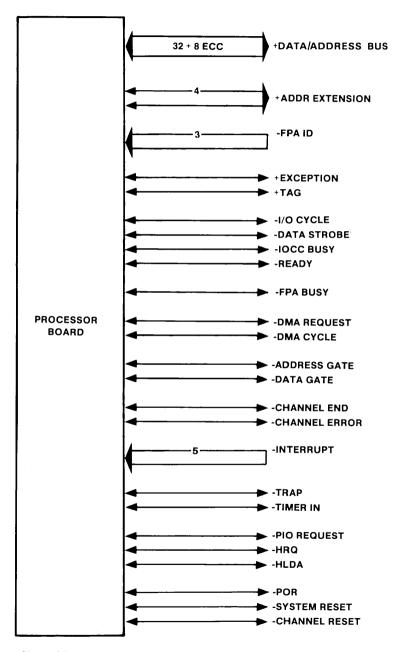

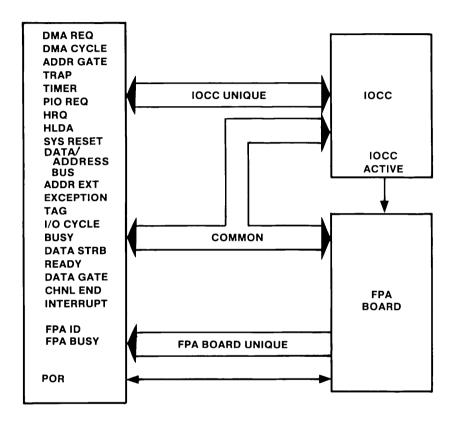

| 2-1.  | Processor Board Data Flow                   | 2-6  |

| 2-2.  | Processor Board Interfaces                  | 2-7  |

| 2-3.  | Processor Channel Interface                 | 2-9  |

| 2-4.  | Processor Channel Interconnections          | 2-10 |

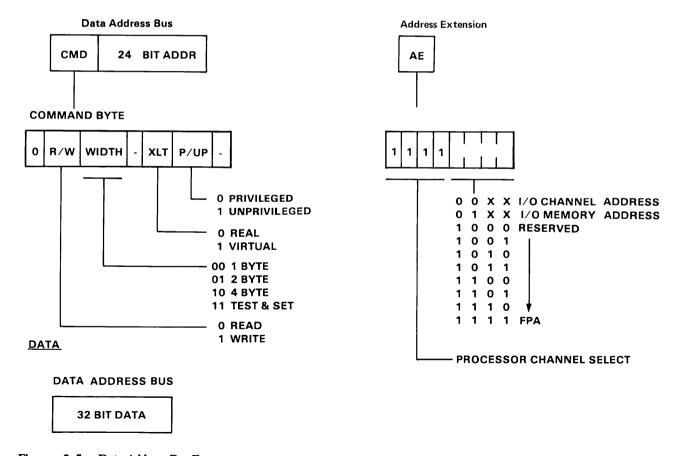

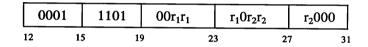

| 2-5.  | Data Address Bus Format                     | 2-11 |

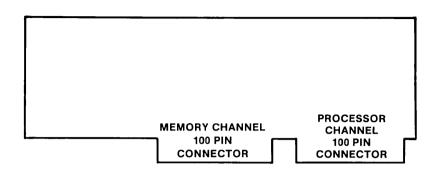

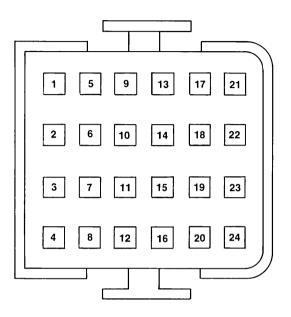

| 2-6.  | 100 Pin Processor Channel Interface Slot    | 2-17 |

| 2-7.  | Processor Channel Interface Slot (A-Side)   | 2-18 |

| 2-8.  | Processor Channel Interface Slot (B-Side)   | 2-20 |

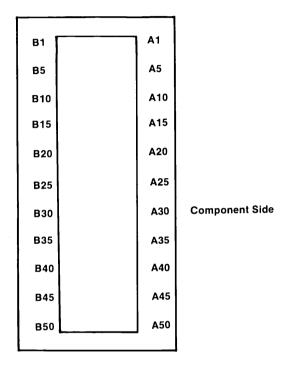

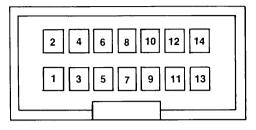

| 2-9.  | 100 Pin Memory Channel Interface Slot       | 2-22 |

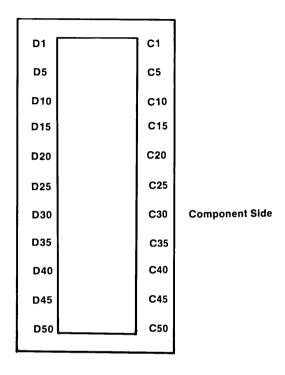

| 2-10. | Memory Channel Interface Slot (C-Side)      | 2-23 |

| 2-11. | Memory Channel Interface Slot (D-Side)      | 2-25 |

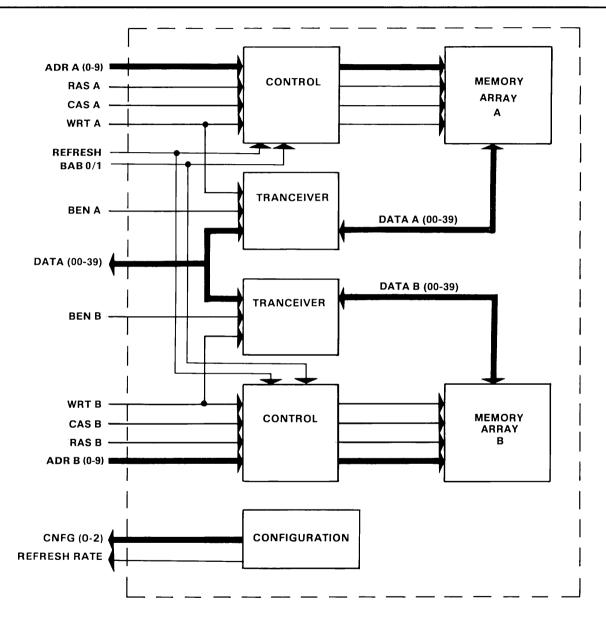

| 3-1.  | Memory Board Logical Dataflow               | 3-7  |

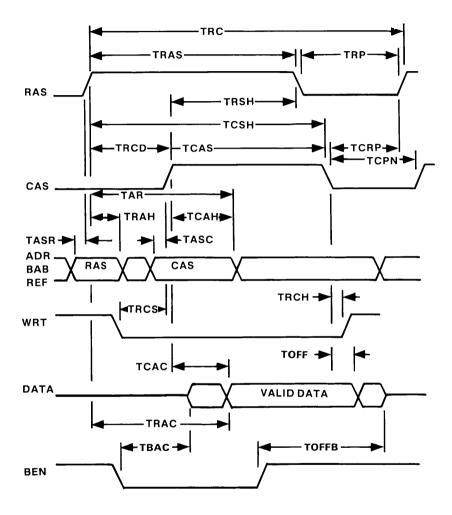

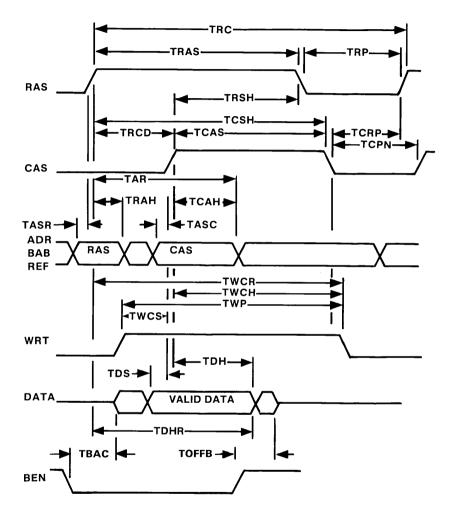

| 3-2.  | Memory Board Read Cycle Timing Waveform     | 3-18 |

| 3-3.  | Memory Board Write Cycle Timing Waveform    | 3-19 |

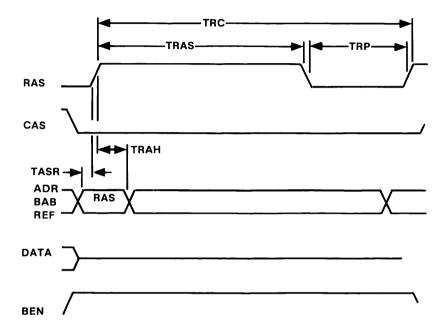

| 3-4.  | Memory Board Refresh Cycle Timing Waveform  | 3-20 |

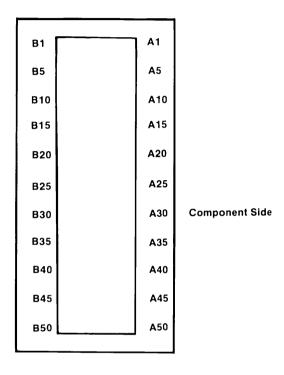

| 3-5.  | 100 Pin Memory Board Slot                   | 3-21 |

| 3-6.  | Memory Board Slot (A-Side)                  | 3-22 |

| 3-7.  | Memory Board Slot (B-Side).                 | 3-24 |

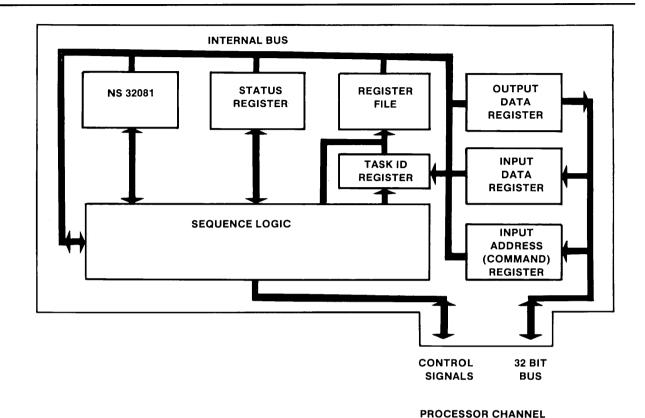

| 4-1.  | Floating-Point Accelerator Block Diagram    |      |

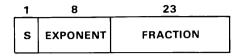

| 4-2.  | Single Precision Format                     |      |

|       |                                             |      |

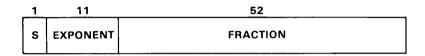

| 4-3.         | Double Precision Format                                              |      |

|--------------|----------------------------------------------------------------------|------|

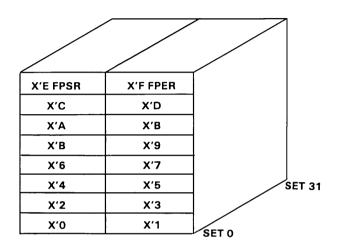

| 4-4.         | Floating Point Registers                                             |      |

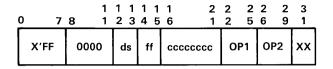

| 4-5.         | FPA Command Format                                                   |      |

| 4-6.         | Floating Point Status Registers                                      | 4-9  |

| 4-7.         | 100 Pin FPA Board Slot                                               | 4-43 |

| 4-8.         | Floating-Point Accelerator Slot (A-Side)                             | 4-44 |

| 4-9.         | Floating-Point Accelerator Slot (B-Side)                             | 4-46 |

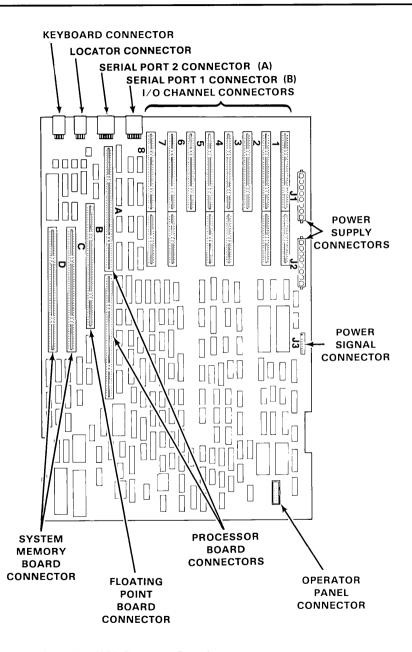

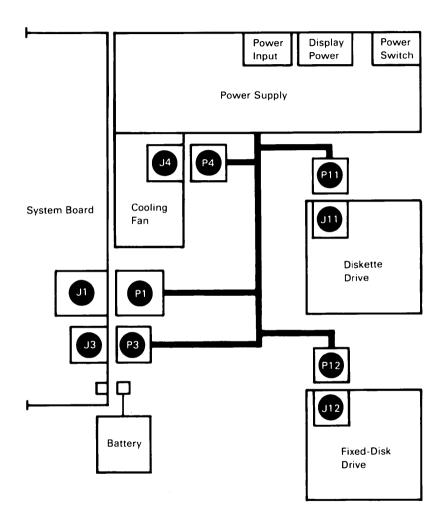

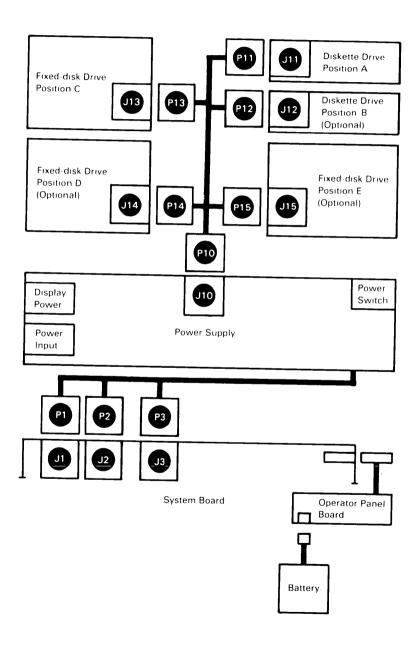

| 5-1.         | IBM 6150 Connector Locations                                         |      |

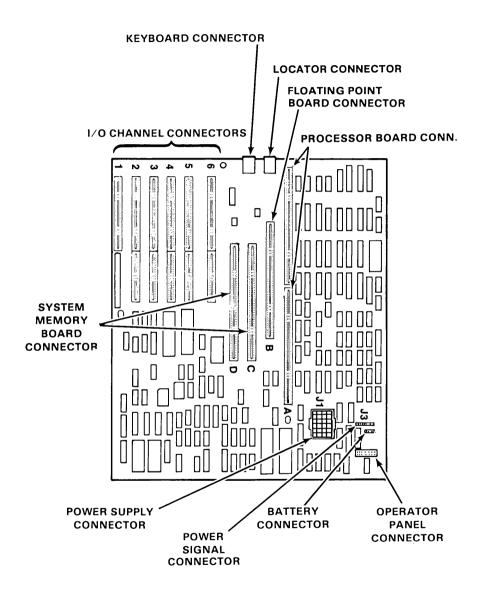

| 5-2.         | IBM 6151 Connector Locations                                         |      |

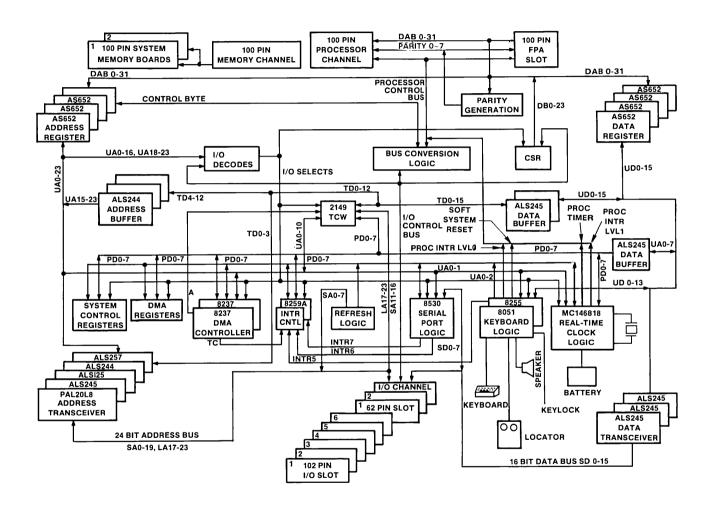

| 5-3.         | RT PC Address/Data Flow Diagram                                      |      |

| 5-4.         | System Board I/O Address Map                                         | 5-12 |

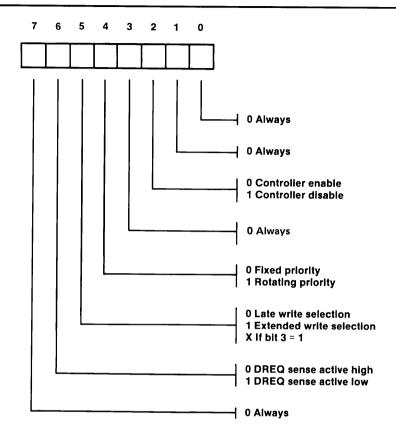

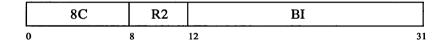

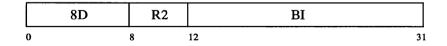

| 5-5.         | Channel Control Register (Address X'008C20')                         | 5-15 |

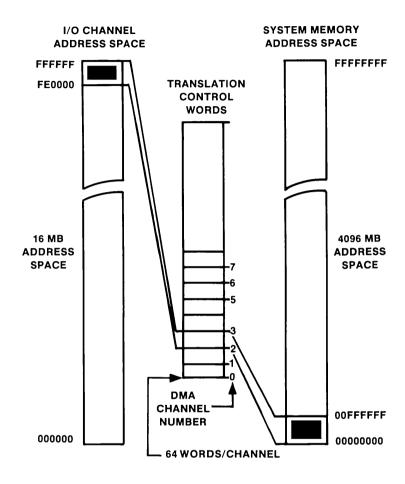

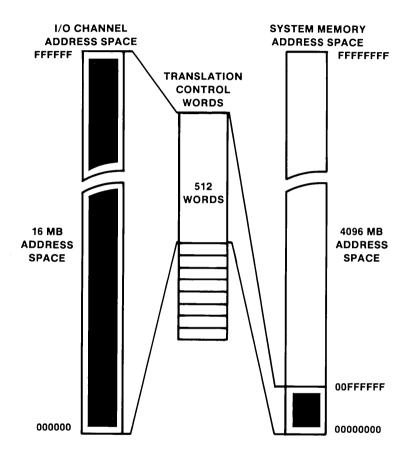

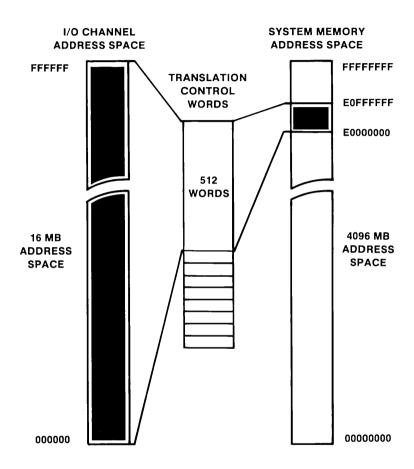

| 5-6.         | DMA Addressing Mode Combinations                                     |      |

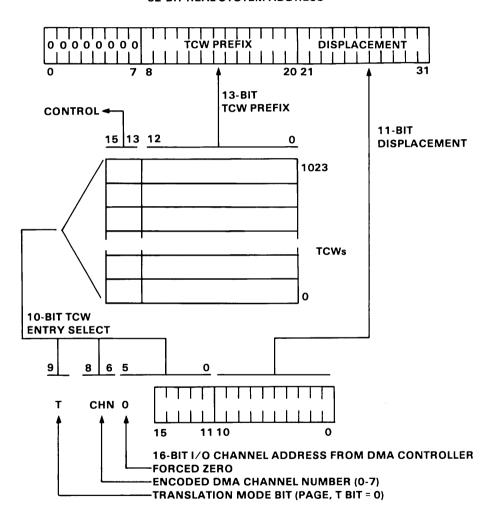

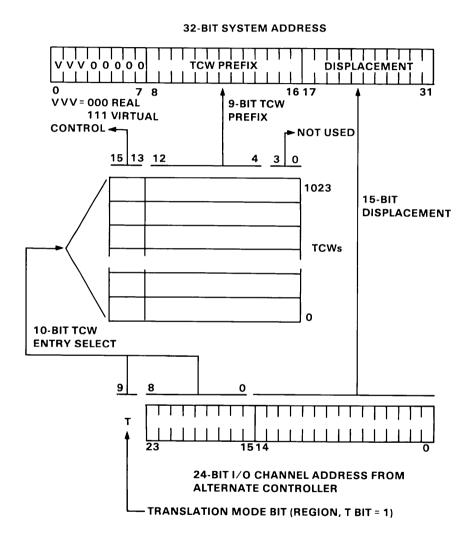

| 5-7.         | Address Translation (Page Mode) Real Address Format                  | 5-18 |

| 5-8.         | Address Translation (Region Mode) Real Address Format                | 5-19 |

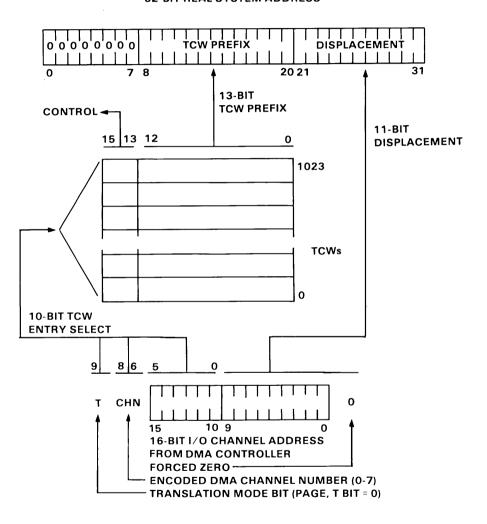

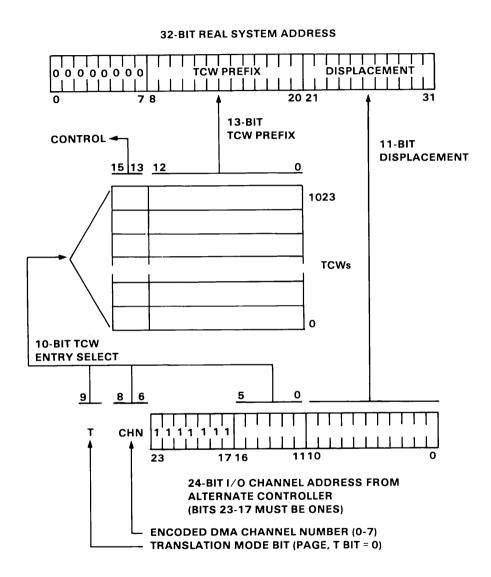

| 5-9.         | Address Translation (Region Mode) Virtual Address Format             | 5-20 |

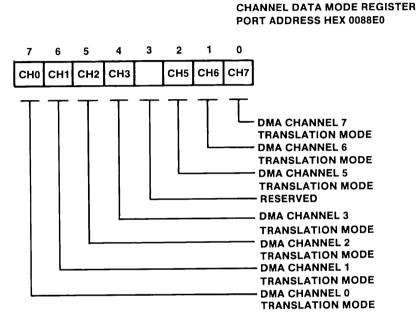

| 5-10.        | DMA Mode Register (System Address X'F00088E0')                       | 5-21 |

| 5-11.        | System DMA - Page Mode (8-Bit Channel) Translated Address Formation  | 5-23 |

| 5-12.        | System DMA - Page Mode (16-Bit Channel) Translated Address Formation | 5-24 |

| 5-13.        | Alternate Controller - Page Mode Translated Address Formation        | 5-25 |

| 5-14.        | Alternate Controller-Region Mode Translated Address Formation        | 5-26 |

| 5-15.        |                                                                      | 5-27 |

| 5-16.        | Translation Control Word (TCW) Binary Port Address                   | 5-28 |

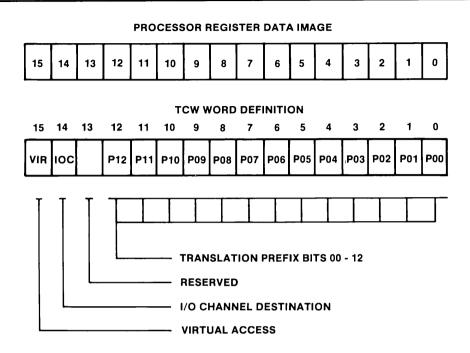

| 5-17.        | TCW Format                                                           | 5-29 |

| 5-18.        | Virtual Access and I/O Channel Destination Bits                      |      |

| 5-19.        | Channel Control Register (Address X'008C20')                         | 5-31 |

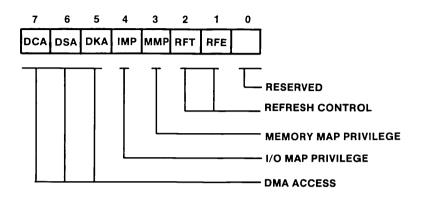

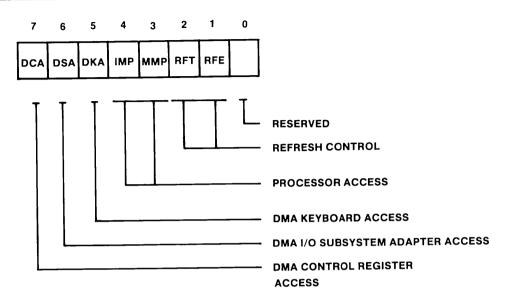

| 5-20.        | DMA Access Bits                                                      | 5-32 |

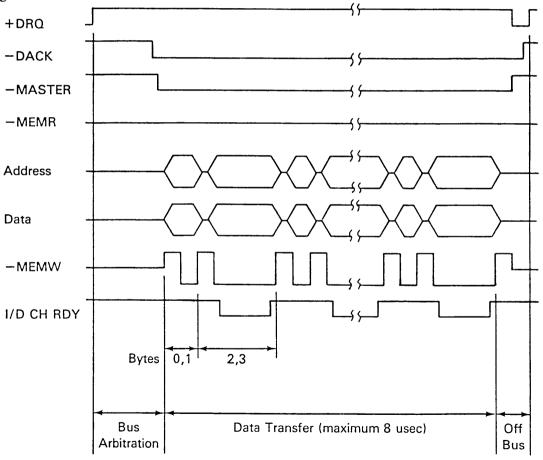

| 5-21.        | Buffered and Burst DMA Write to System Memory Timings                | 5-36 |

| 5-22.        | Processor Board to System Board Data Interface                       | 5-37 |

| 5-23.        | Single Cycle Operation Data Placement                                | 5-38 |

| 5-24.        | Multicycle Operation to 16-Bit Device                                | 5-38 |

| 5-25.        | Multicycle Operation to 8-Bit Device                                 | 5-39 |

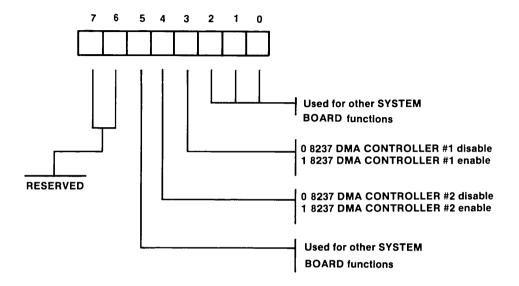

| 5-26.        | Component Reset Register B (Address X'F0008C60')                     | 5-40 |

| 5-27.        | 8237 DMA Controller #1 Control Register Addresses                    | 5-41 |

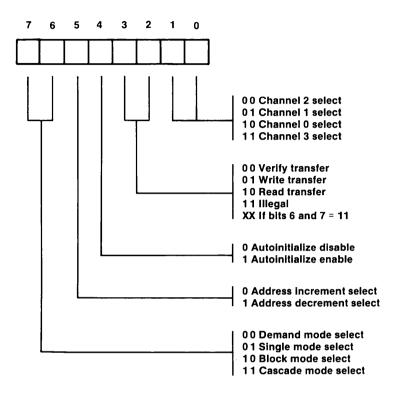

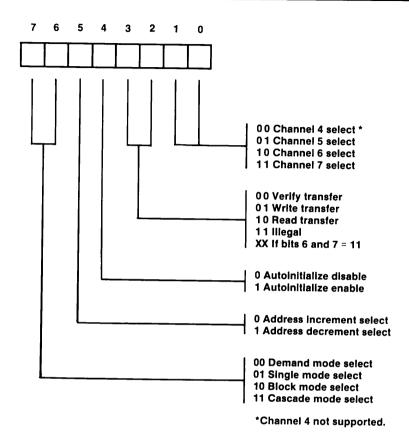

| 5-28.        | 8237 DMA Controller 1 Write Mode Register (Address X'00884B')        | 5-42 |

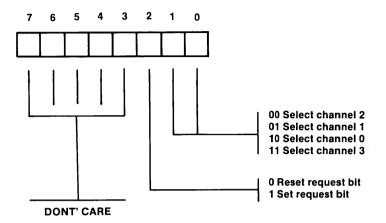

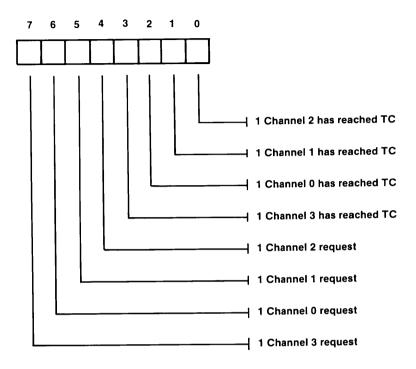

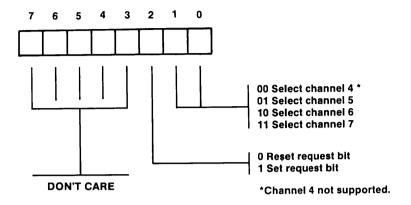

| 5-29.        | 8237 DMA Controller 1 Write Request Register(Address X'008849')      | 5-43 |

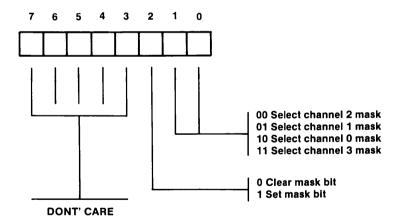

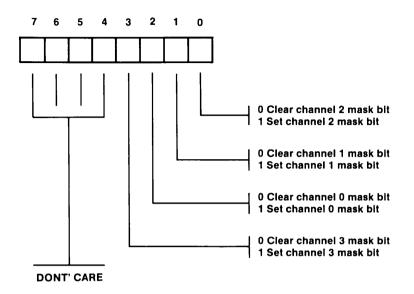

| 5-30.        | 8237 DMA Controller 1 Write Mask Register 1 (Address X'00884A')      | 5-43 |

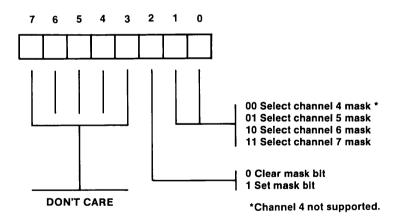

| 5-31.        | 8237 DMA Controller 1 Write Mask Register 2 (Address X'00884F')      | 5-44 |

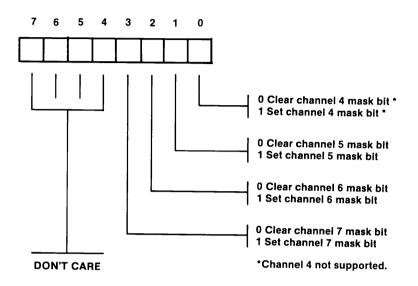

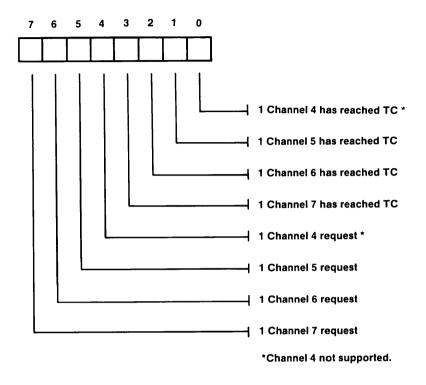

| 5-32.        | 8237 DMA Controller 1 Status Register (Address X'008848')            | 5-45 |

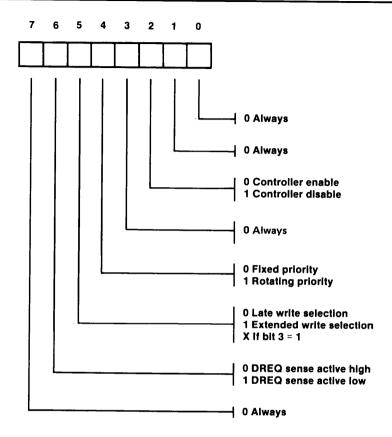

| 5-33.        | 8237 DMA Controller 1 Command Register (Address X'008848')           | 5-46 |

| 5-34.        | 8237 DMA Controller 2 Control Register Addresses                     | 5-47 |

| 5-35.        | 8237 DMA Controller 2 Write Mode Register (Address X'008876')        | 5-48 |

| 5-36.        | 8237 DMA Controller 2 Write Request Register (Address X'008872')     | 5-49 |

| 5-37.        | 8237 DMA Controller 2 Write Mask Register 1 (Address X'008874')      | 5-49 |

| 5-3 <b>8</b> | 8237 DMA Controller 2 Write Mask Register 2 (Address X'00887E')      | 2-20 |

| 5-39.          | 8237 DMA Controller 2 Status Register (Address X'008870')                                      | 5-51         |

|----------------|------------------------------------------------------------------------------------------------|--------------|

| 5-39.<br>5-40. | 8237 DMA Controller 2 Status Register (Address X 008870)                                       | 5-51<br>5-52 |

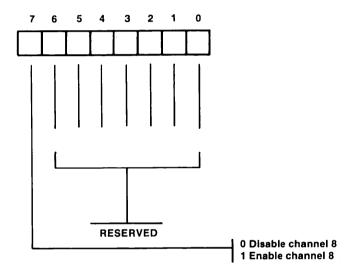

| 5-41.          | Channel 8 Enable Register (Address X'008C00')                                                  |              |

| 5-42.          | Channel Control Register (Address X'008C20')                                                   | 5-54         |

| 5-43.          | Buffer Register (Address X'0088C0')                                                            | 5-55         |

| 5-44.          | 8259 #1                                                                                        | 5-57         |

| 5-45.          | 8259 #2                                                                                        |              |

| 5-46.          | Diagnostic Interrupt Activate Register (Address X'008CA0')                                     | 5-58         |

| 5-47.          | Component Reset Register A (Address X'008C40')                                                 |              |

| 5-47.<br>5-48. | Component Reset Register B (Address X'008C60')  Component Reset Register B (Address X'008C60') |              |

| 5-49.          | CSR - Channel Status Register Address (X'010800')                                              | 5-63         |

| 5-49.<br>5-50. | Memory Configuration Register                                                                  |              |

| 5-50.<br>5-51. |                                                                                                |              |

| 5-51.<br>5-52. | Real Time Clock Address Map                                                                    |              |

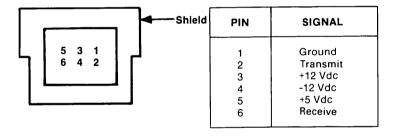

| 5-52.<br>5-53. | Serial Port Address Map                                                                        |              |

|                | Write Register 11                                                                              |              |

| 5-54.          | External Register A                                                                            |              |

| 5-55.          | External Register B                                                                            |              |

| 5-56.          | Serial Port Connectors                                                                         |              |

| 5-57.          | Adapter Logic and System Interface                                                             | 5-133        |

| 5-58.          | Adapter-to-Keyboard Connector Interface                                                        | 5-134        |

| 5-59.          | Adapter-to-Locator Connector Interface                                                         | 5-135        |

| 5-60.          | Keyboard Connector                                                                             | 5-144        |

| 5-61.          | Locator Connector                                                                              | 5-145        |

| 5-62.          | IBM 6150 Power Supply Connector (J1)                                                           | 5-146        |

| 5-63.          | IBM 6150 Power Supply Connector (J2)                                                           | 5-147        |

| 5-64.          | IBM 6150 Power Supply Signal Connector (J3)                                                    | 5-148        |

| 5-65.          | IBM 6150 Operator Panel Connector                                                              | 5-149        |

| 5-66.          | IBM 6150 Serial Port Connectors                                                                | 5-150        |

| 5-67.          | IBM 6151 Power Supply Connector (J1)                                                           | 5-151        |

| 5-68.          | IBM 6151 Power Supply Signal Connector (J3)                                                    | 5-152        |

| 5-69.          | IBM 6151 Operator Panel Connector                                                              | 5-153        |

| 5-70.          | IBM 6151 Battery Connector                                                                     | 5-154        |

| 6-1.           | 62-Pin PC Adapters                                                                             | . 6-6        |

| 6-2.           | 98 and 102 Pin PC-AT or RT PC Adapters                                                         |              |

| 6-3.           | Data Transfer Table                                                                            | 6-10         |

| 6-4.           | Protocol Functional Block Diagram                                                              | 6-21         |

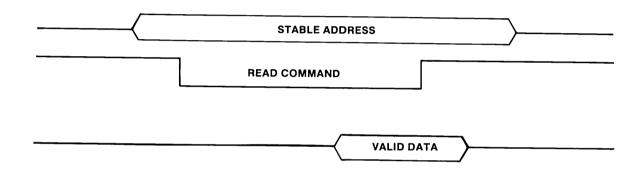

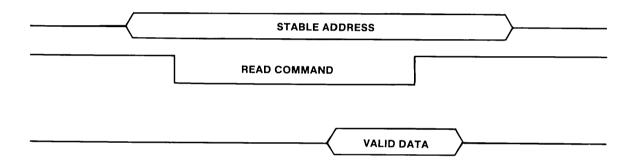

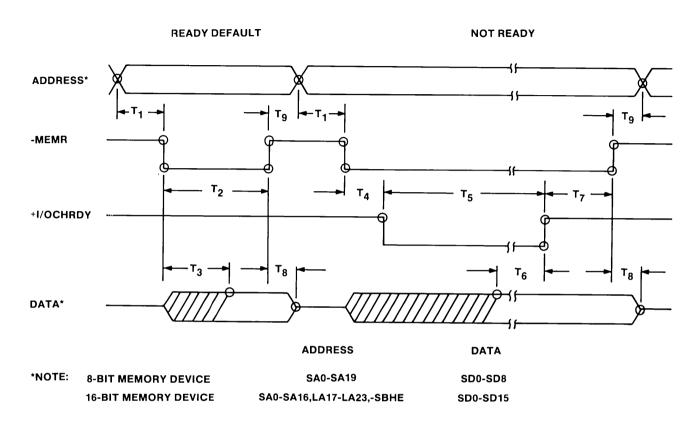

| 6-5.           | Memory Read Operation Sequence                                                                 | 6-22         |

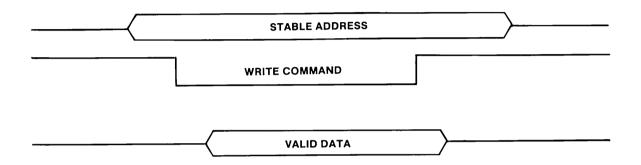

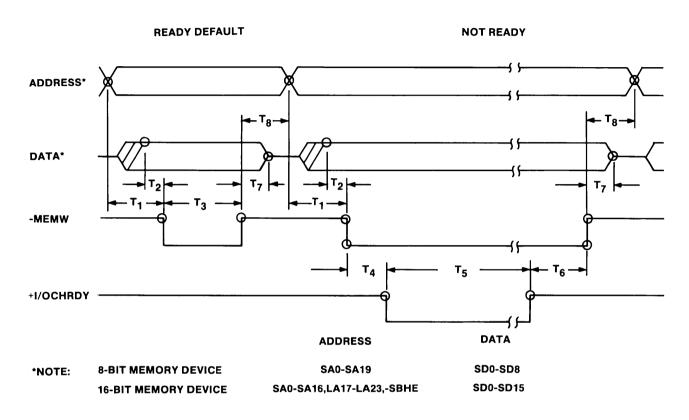

| 6-6.           | Memory Write Operation Sequence                                                                |              |

| 6-7.           | I/O Read Operation Sequence                                                                    | 6-24         |

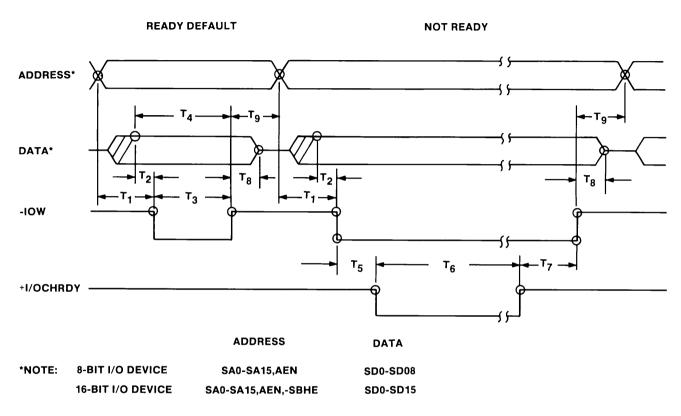

| 6-8.           | I/O Write Operation Sequence                                                                   | 6-25         |

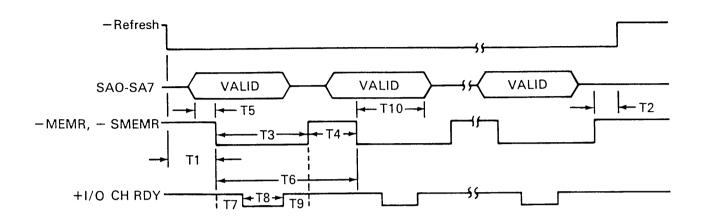

| 6-9.           | Refresh Timing                                                                                 | 6-27         |

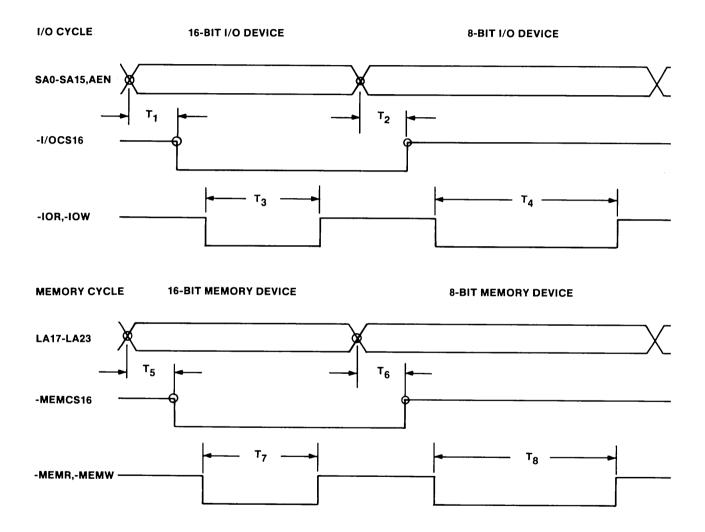

| 6-10.          | I/O And Memory Default Cycle Timing                                                            |              |

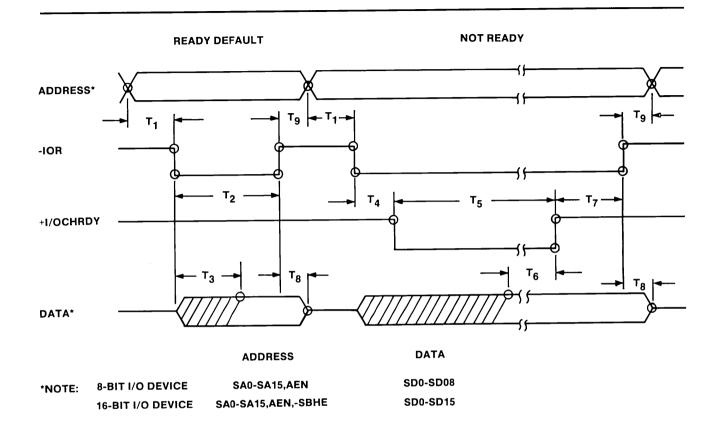

| 6-11.          | I/O Read Operation                                                                             |              |

| 6-12.          | I/O Write Operation                                                                            |              |

| 6-13.          | Memory Read Operation                                                                          | 6-34         |

| 6-14. | Memory Write Operation                                         | 6-36  |

|-------|----------------------------------------------------------------|-------|

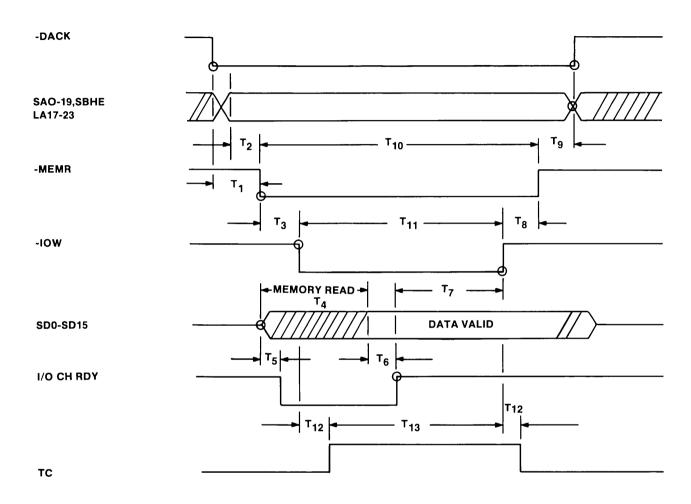

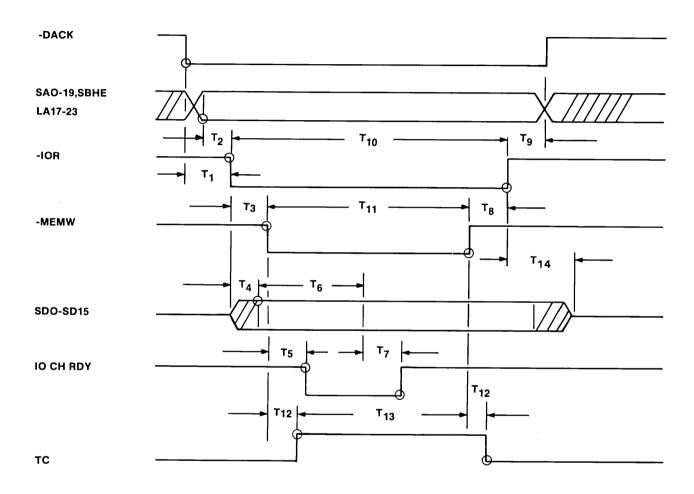

| 6-15. | DMA Read Operations                                            | 6-38  |

| 6-16. | DMA Write Operations                                           | 6-40  |

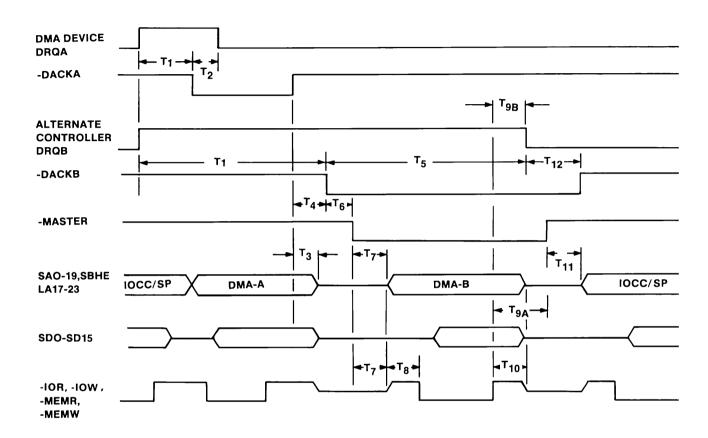

| 6-17. | Bus Arbitration                                                | 6-42  |

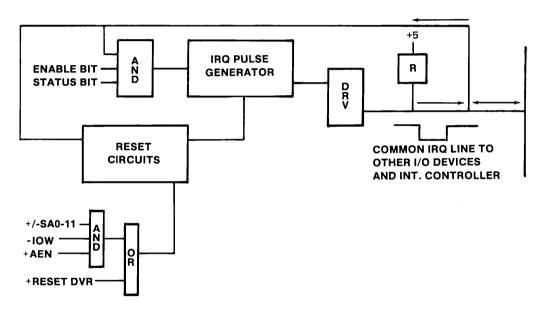

| 6-18. | Block Diagram For IRQ Line                                     | 6-46  |

| 6-19. | Memory Address Map                                             | 6-48  |

| 6-20. | I/O Address Map                                                | 6-50  |

| 6-21. | DMA Channels                                                   | 6-52  |

| 6-22. | Interrupt Levels                                               | 6-53  |

| 6-23. | IBM 6150 System Boards                                         | 6-54  |

| 6-24. | IBM 6151 System Board                                          | 6-55  |

| 6-25. | Unique Pin Assignments                                         | 6-55  |

| 6-26. | 62-Pin Connector Side A                                        | 6-58  |

| 6-27. | 62-Pin Connector Side B                                        | 6-60  |

| 6-28. | 40-Pin Connector Side C                                        | 6-61  |

| 6-29. | 40-Pin Connector Side D                                        | 6-62  |

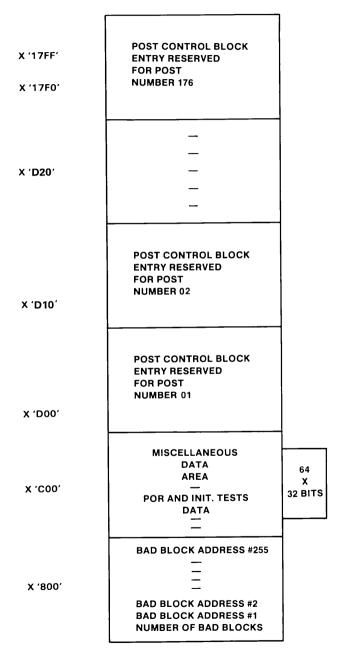

| 7-1.  | Layout of Post Control Block                                   | . 7-5 |

| 7-2.  | Layout of the Post Control Block Section Dedicated to One Post | . 7-6 |

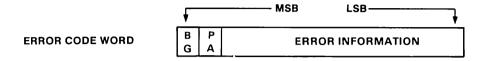

| 7-3.  | Error Code Word                                                |       |

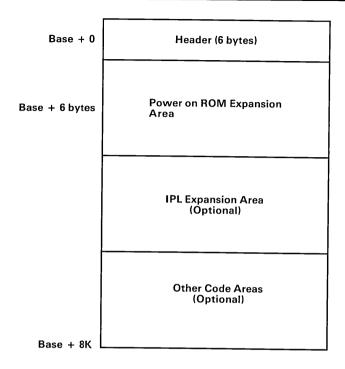

| 7-4.  | ROM Expansion View                                             | 7-12  |

| 7-5.  | RAM and ROM layout during ROM IPL                              | 7-19  |

| 7-6.  | Layout of Offsets in the ROM Entry Table                       | 7-21  |

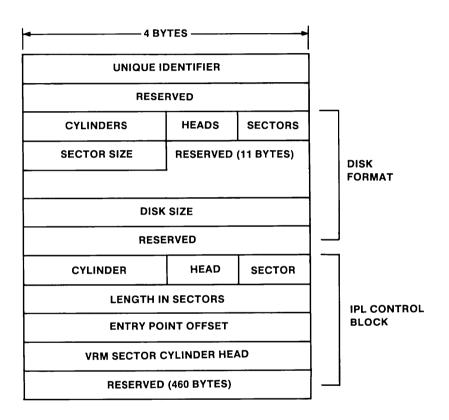

| 7-7.  | IPL ROM Boot Record Format                                     | 7-32  |

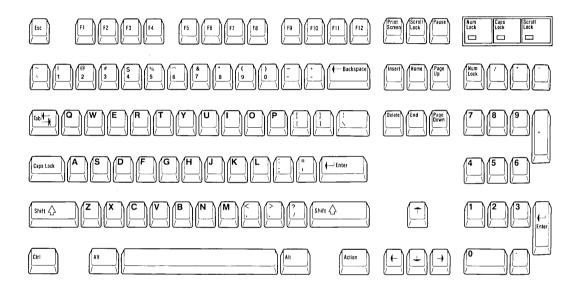

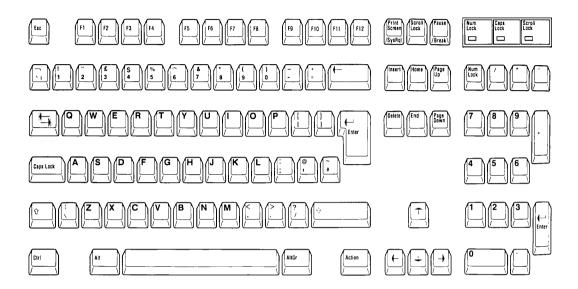

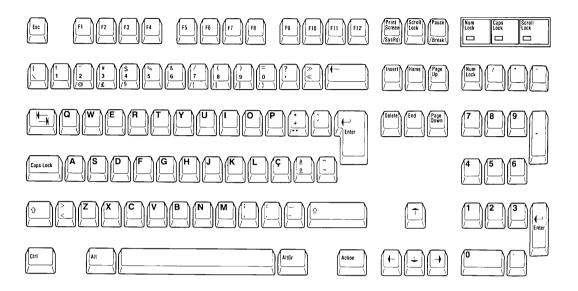

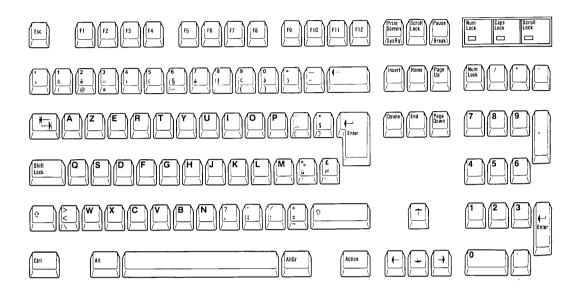

| 9-1.  | US Keyboard                                                    | . 9-7 |

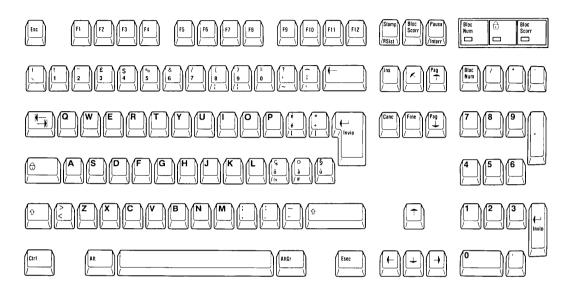

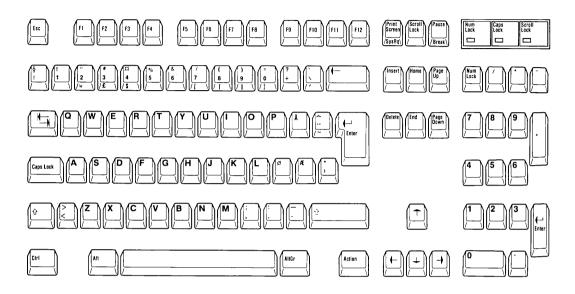

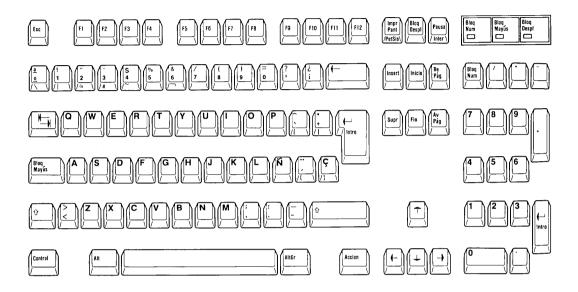

| 9-2.  | Italy Keyboard                                                 |       |

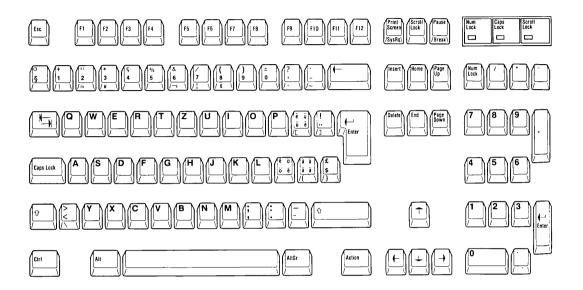

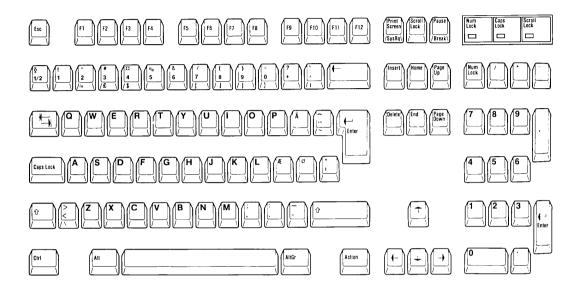

| 9-3.  | Switzerland Keyboard                                           | . 9-9 |

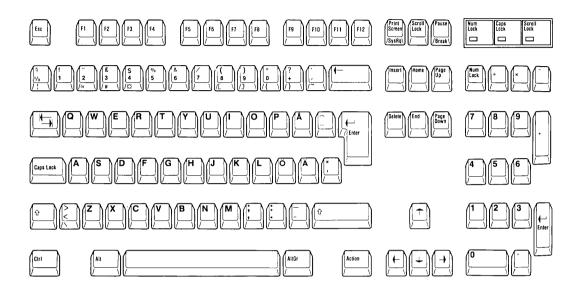

| 9-4.  | Canada (French) Keyboard                                       | 9-10  |

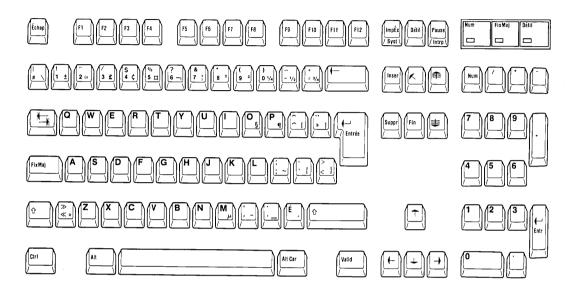

| 9-5.  | United Kingdom (English) Keyboard                              | 9-11  |

| 9-6.  | Norway Keyboard                                                | 9-12  |

| 9-7.  | Denmark Keyboard                                               | 9-13  |

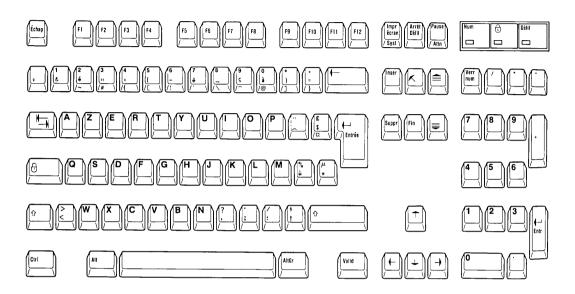

| 9-8.  | France Keyboard                                                | 9-14  |

| 9-9.  | Portugal Keyboard                                              | 9-15  |

| 9-10. | Spain Keyboard                                                 | 9-16  |

| 9-11. | Sweden and Finland Keyboard                                    | 9-17  |

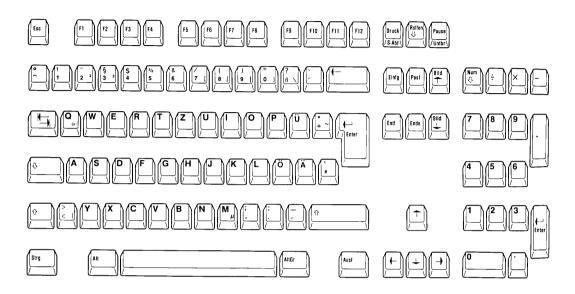

| 9-12. | Germany Keyboard                                               | 9-18  |

| 9-13. | Belgium (Dutch/French) Keyboard                                | 9-19  |

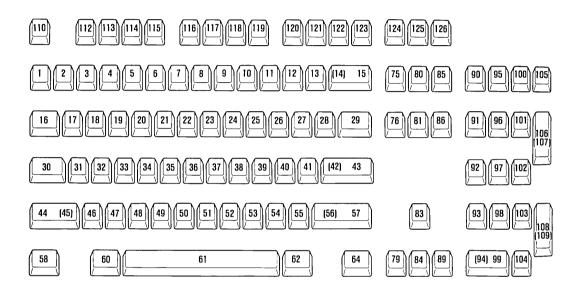

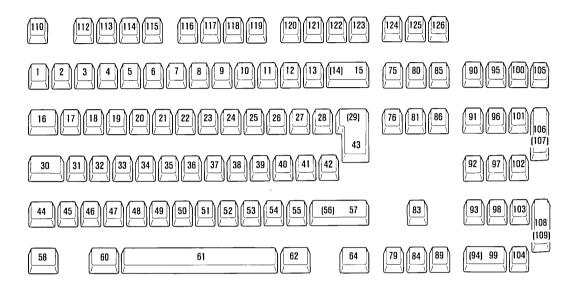

| 9-14. | US 101 Key Position Layout                                     | 9-20  |

| 9-15. | WT 102 Key Position Layout                                     | 9-21  |

| 9-16. | Scan Codes Table                                               | 9-22  |

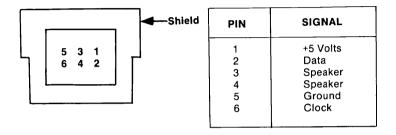

| 9-17. | Keyboard Cable Connector                                       | 9-23  |

| 9-18. | Locator Signal Levels                                          | 9-29  |

| 9-19. | Locator Cable Connector                                        | 9-29  |

| 9-20. | Operator Panel                                                 | 9-30  |

| 9-21. | IBM 6150 Battery Connector                                     | 9-32  |

| 10-1  | IRM 6151 Input Power                                           | 10-4  |

| 10-2.  | IBM 6150 Input Power                                                       |        |

|--------|----------------------------------------------------------------------------|--------|

| 10-3.  | IBM 6151 Power Connector Outputs                                           | . 10-5 |

| 10-4.  | IBM 6151 Power Output Capability                                           |        |

| 10-5.  | IBM 6150 Power Connector Outputs                                           | . 10-9 |

| 10-6.  | IBM 6150 Power Output Capability                                           | 10-11  |

| 11-1.  | System Processor Block Diagram                                             | . 11-8 |

| 11-2.  | Data Units in System Memory                                                | . 11-9 |

| 11-3.  | General-Purpose Registers                                                  | 11-12  |

| 11-4.  | General Purpose Register Pairs                                             | 11-13  |

| 11-5.  | SCR Organization                                                           | 11-14  |

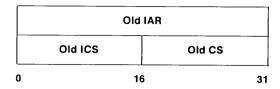

| 11-6.  | Old Program Status                                                         |        |

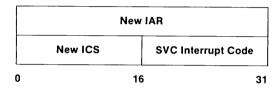

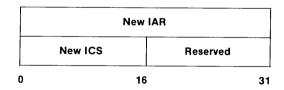

| 11-7.  | New Program Status                                                         | 11-23  |

| 11-8.  | SVC New Program Status                                                     | 11-23  |

| 11-9.  | Program Check Errors (Memory Protect and Address Translation Disabled)     | 11-89  |

| 11-10. | Program Check Errors (Memory Protect or Address Translation Enabled)       |        |

| 11-11. | Memory Management Unit Functional Partition                                |        |

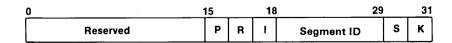

| 11-12. | Segment Register Format                                                    | 11-97  |

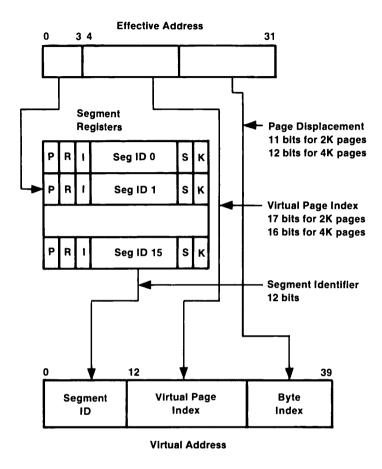

| 11-13. | Generation of Virtual Address                                              | 11-98  |

| 11-14. | Address Translation Mechanism                                              | 11-100 |

| 11-15. | TLB Contents. One of two TLBs shown.                                       | 11-101 |

| 11-16. | System Memory Inverted Page Table Entry Format                             | 11-102 |

| 11-17. | HAT/IPT Base Address Multiplier                                            | 11-103 |

| 11-18. | HAT/IPT Index Generation Source Fields                                     | 11-104 |

| 11-19. | Segment Protection Processing                                              | 11-109 |

| 11-20. | Protection Key Processing                                                  | 11-110 |

| 11-21. | Lockbit Processing                                                         | 11-111 |

| 11-22. | Reference and Change Bit Format                                            | 11-112 |

| 11-23. | I/O Base Address Register                                                  | 11-113 |

| 11-24. | RAM Specification Register                                                 | 11-114 |

| 11-25. | ROM Specification Register                                                 | 11-115 |

| 11-26. | Translation Control Register                                               | 11-118 |

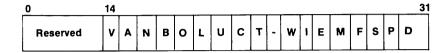

| 11-27. | Memory Exception Register                                                  | 11-120 |

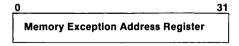

| 11-28. | Memory Exception Address Register                                          | 11-125 |

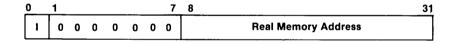

| 11-29. | Translated Real Address Register                                           | 11-126 |

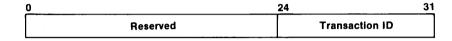

| 11-30. | Transaction Identifier Register                                            | 11-127 |

| 11-31. | Segment Register (One Of Sixteen)                                          | 11-127 |

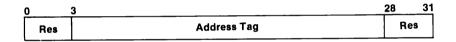

| 11-32. | TLB Address Tag Field (One Of Sixteen Per TLB)                             | 11-129 |

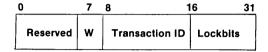

| 11-33. | TLB Real Page Number, Valid, and Key Bits (One of Sixteen Per TLB)         | 11-130 |

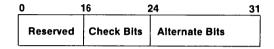

| 11-34. | Write Bit, Transaction ID, and Lockbits (One of Sixteen Per TLB)           | 11-131 |

| 11-35. | RAS Mode Diagnostic Register                                               | 11-132 |

| 11-36. | Address Space Recognized by Memory Management Unit During Initialization . |        |

| 11-37. | Check Bit Matrix For 32/40 ECC                                             | 11-141 |

# **Section 1. System Introduction**

## **CONTENTS**

| About this Section                    |      |

|---------------------------------------|------|

| General System Description            | 1-4  |

| IBM 6150 System Unit                  | 1-5  |

| IBM 6151 System Unit                  | 1-6  |

| System Overview                       | 1-7  |

| System Board                          |      |

| Processor Board                       |      |

| Memory Channel                        | 1-10 |

| Processor Channel                     | 1-10 |

|                                       | 1-10 |

|                                       | 1-10 |

|                                       | 1-11 |

|                                       | 1-11 |

| System Performance                    | 1-12 |

|                                       | 1-13 |

| Nomenclature                          | 1-13 |

|                                       | 1-16 |

| System Memory Conventions             | 1-18 |

|                                       | 1-19 |

|                                       | 1-20 |

|                                       | 1-21 |

|                                       | 1-22 |

|                                       | 1-23 |

|                                       | 1-24 |

|                                       | 1-26 |

|                                       | 1-26 |

|                                       | 1-28 |

|                                       | 1-29 |

|                                       | 1-31 |

| I/O MĂP                               | 1-31 |

|                                       | 1-31 |

| System Processor Address Map          | 1-34 |

| Interrupts                            | 1-36 |

|                                       | 1-36 |

|                                       | 1-36 |

|                                       | 1-37 |

| System Processor Interrupt Processing | 1-37 |

# **About this Section**

This section contains an introduction to the IBM RT PC System. The differences between the IBM 6150 System Unit and the IBM 6151 System Unit are described. The components that reside on the system board are discussed along with a description of how they transfer data throughout the system.

# **General System Description**

The IBM RT PC Product Family is a family of workstations supporting both stand-alone and clustered configurations. Each workstation offers significant computational power, coupled to all points addressable displays. The workstations have a common family appearance, use the same software and user interface. A wide range of options and adapters are offered for the workstations, such as data communications, color displays, quality printers, graphic printers, and color plotters. The IBM 6150 System Unit is a small floor standing console and an ergonomically packaged display monitor. The second system, the IBM 6151 System Unit, is a table-top workstation. Each has growth capabilities.

# **IBM 6150 System Unit**

The IBM 6150 System Unit is a 32-bit system unit packaged in a small floor standing console. A IBM 6150 can be configured by selecting one of the following displays and its appropriate adapter board:

- IBM 5151 Personal Computer Display

- IBM 6153 Advanced Monochrome Graphics Display

- IBM 5154 Enhanced Color Display

- IBM 6154 Advanced Color Graphics Display

- IBM 6155 Extended Monochrome Graphics Display.

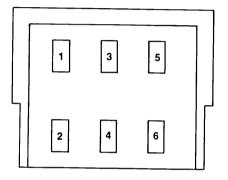

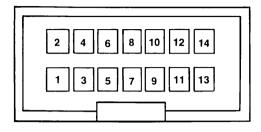

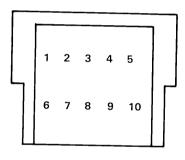

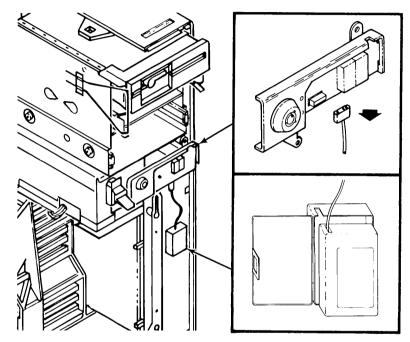

The system unit console contains the system board, power supply, fixed-disk drives, and diskette drives. The system board has unique pluggable slots for the processor board, the Floating-Point Accelerator board, and for two RT PC memory boards with addressing for up to 16M-bytes of system memory. In addition, eight slots are provided for optional I/O adapters. Two of these eight slots only accommodate adapters from the IBM PC-1 and the PC-XT. The remaining six slots accommodate RT PC adapters, PC-1 and PC-XT adapters, and PC-AT adapters identified in this manual.

A special Coprocessor board, Intel 80286 based, is available as an option for the IBM 6150. This board allows most existing PC applications to run on RT PC. The IBM Personal Computer AT 512 KB Memory Expansion Option can be used with this board.

The system unit accommodates up to five 5.25-inch storage device drives. Three full-high positions are provided, with two positions configured to accept either one or two 5.25-inch half-high diskette drives. The other three positions accommodate a maximum of three fixed-disk drives.

# **IBM 6151 System Unit**

The IBM 6151 System Unit is a 32-bit system unit packaged in a console designed for table top operation. A IBM 6151 can be configured by selecting one of the following displays and its appropriate adapter:

- IBM 5151 Personal Computer Display

- IBM 6153 Advanced Monochrome Graphics Display

- IBM 5154 Enhanced Color Display

- IBM 6154 Advanced Color Graphics Display

- IBM 6155 Extended Monochrome Graphics Display.

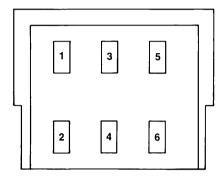

The system unit console contains the system board, power supply, fixed-disk drive and diskette drive. The system board has unique pluggable slots for the processor board, Floating-Point Accelerator, and two RT PC memory boards, with addressing for up to of 16M-bytes of system memory. In addition, six slots are provided for optional I/O adapters. One of these slots only accommodates adapters from the IBM PC and XT computers, while the remaining five accommodate RT PC adapters, PC-1 and PC-XT adapters, and IBM PC-AT adapters identified in this manual.

A special Coprocessor board, Intel 80286 based, is available as an option for the IBM 6151. This board allows most existing PC applications to run on RT PC. The IBM Personal Computer AT 512 KB Memory Expansion Option can be used with this board.

The IBM 6151 console accommodates one full high 5.25-inch fixed-disk drive and one half-high 5.25-inch diskette drive.

# **System Overview**

The IBM 6150 System Unit and the IBM 6151 System Unit are virtual memory 32-bit workstations. All units use the same processor board, system memory boards, optional Floating-Point Accelerator, and I/O adapters. A unique system board is used in each unit, and differs only in the number of I/O slots provided and in the built-in RS232C serial port capability.

The following section provides an overview of the RT PC system architecture. This section contains information for the IBM 6151 and and the IBM 6150. Features unique only to the IBM 6150 are also described.

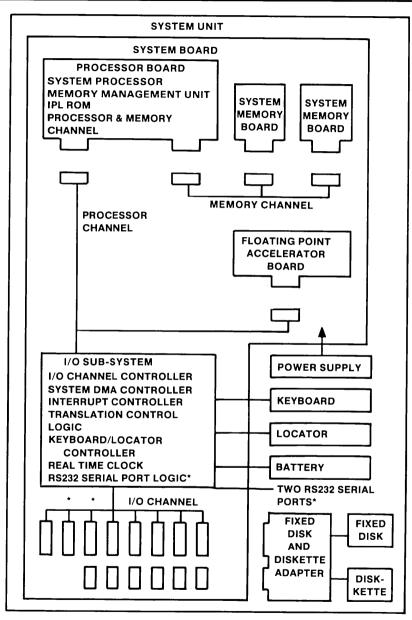

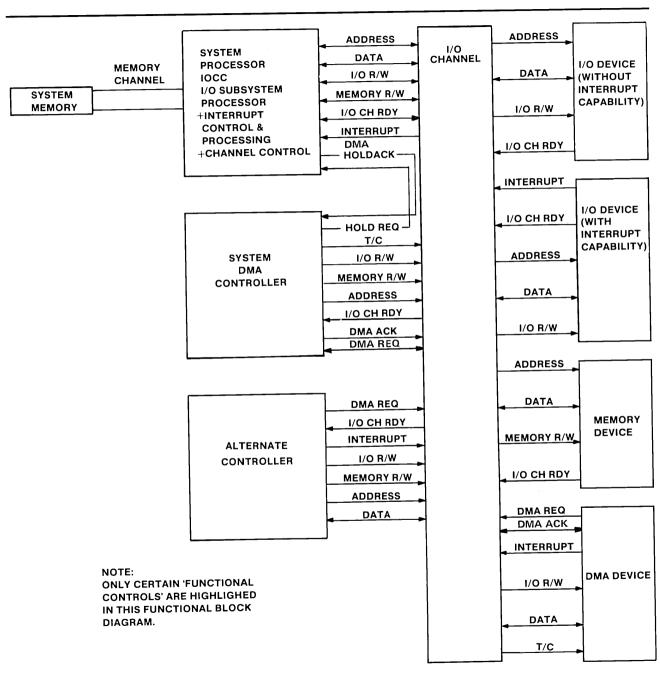

Figure 1-1. System Board Block Diagram

**Note:** \* = IBM 6150 only

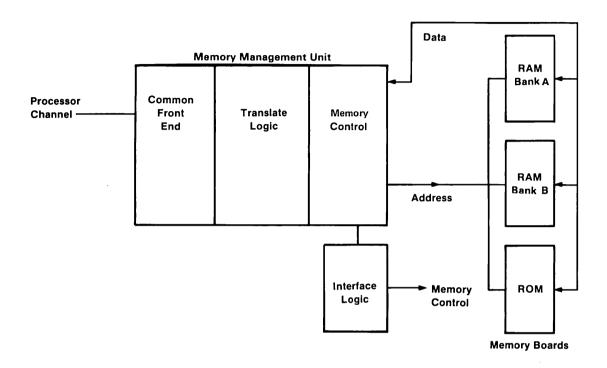

# **System Board**

The RT PC system board contains the I/O subsystem, I/O channel, and connectors for the processor board, system memory boards, and optional Floating-Point Accelerator. Unique system boards are used for the IBM 6151 and the IBM 6150, and differ only in the number of I/O slots provided and in the built-in RS232C serial port capability. The same processor board, system memory boards, Floating-Point Accelerator, and I/O adapters are used in both units.

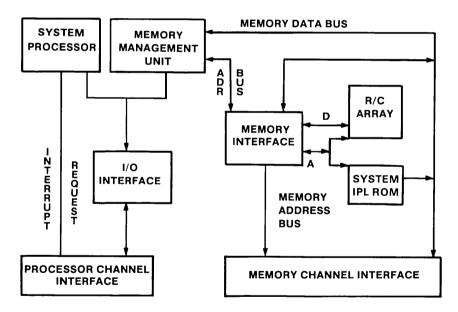

#### **Processor Board**

The processor board plugs into the system board and contains the following major components:

- A 32-bit microprocessor

- A memory management unit

- A 64K-byte read-only memory (ROM) for initial program load (IPL)

- Reference and change bits for virtual memory management

- Memory channel and processor channel control and interface logic.

The RT PC processor board includes a system processor and a memory management unit (MMU). Both components use Very Large Scale Integration (VLSI) technology. These two components form a 32-bit virtual memory processor unit, providing advanced memory management functions. The system processor provides sixteen 32-bit general purpose registers and 118 instructions. All internal address and data paths are 32 bits. The MMU provides virtual memory address translation functions, memory control, and error correct code (ECC) functions. The basic processor board clock rate is 170 nanoseconds.

The processor board also contains 64K-bytes of read-only memory (ROM) used for initial program load (IPL) and initial diagnostic functions. Five bipolar gate arrays and miscellaneous TTL logic are used for memory channel and processor channel interface. A bipolar (Random Access Memory (RAM) is used for the reference and change bits associated with virtual memory management support.

The processor board connects to both the memory channel and the processor channel. The memory channel connects only to system memory boards, with the processor channel connecting to both the I/O subsystem and the optional Floating-Point Accelerator.

#### **Memory Channel**

The memory channel connects system memory to the processor board. This channel provides a multiplexed address bus, a data bus, and control signals. The address bus supports up to 16M-bytes of system memory. The data bus provides 32 bits of data and 8 bits of error correcting code (ECC). The memory channel is capable of supplying 4 bytes of data every 170 nanoseconds, resulting in a bandwidth of 23.5 megabytes per second.

#### **Processor Channel**

The processor channel connects the processor board to the I/O subsystem and the optional Floating-Point Accelerator. This channel provides a multiplexed 32-bit address and data bus, plus control signals to allow access of system memory through the memory management unit by the I/O subsystem. This channel also allows transfer of floating point data and control from the processor board to the Floating-Point Accelerator. External interrupt lines are provided for use by the I/O subsystem.

## **System Memory Boards**

System memory boards plug into the memory channel on the system board and contain the address and buffer logic.

Memory on a board is divided into two banks, with one bank containing only even addresses, and the second bank containing only odd addresses. Interleaving of memory in this manner provides improved memory bandwidth to the processor board. Each memory word contains 32 bits of data and 8 bits of error correcting codes (ECC). The ECC allows correction of single bit errors and detection of all double bit errors. TTL logic is used for address and data buffers on the system memory boards.

#### Floating-Point Accelerator Board

The optional Floating-Point Accelerator board plugs into the processor channel on the system board and contains the following components:

- NS32081 Floating-Point Accelerator

- Floating point register sets

- Interface and control logic.

A National NS32081 Floating-Point Accelerator is used for floating point applications. Additional interface and control logic on the Floating-Point Accelerator Board allows floating point operations to be executed in parallel with other computations on the processor board.

#### I/O Subsystem

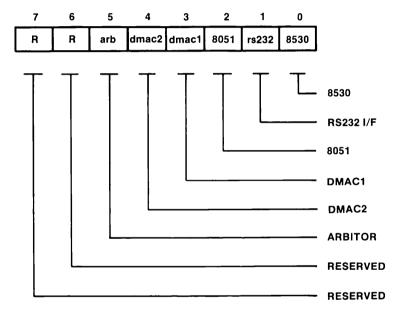

The I/O subsystem, located on the system board, consists of logic on the system board, and provides the following functions:

- I/O Channel Controller. The I/O channel controller converts the 32-bit processor channel to a standard 16-bit and 8-bit I/O channel.

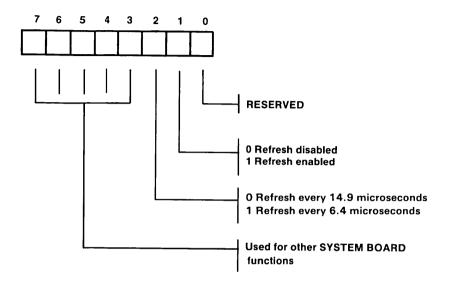

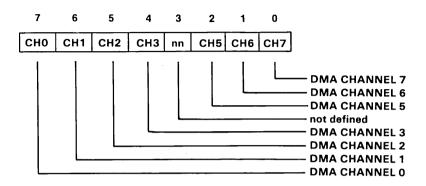

- System Direct Memory Access (DMA) Controller. The system DMA controller consists of two 8237 modules. They are used to provide 7 independent DMA channels. An eighth DMA channel exists for the optional RT PC 286 Coprocessor.

- Interrupt Controller. Two 8259 modules are used to provide 15 levels of priority interrupts.

- Translation Control Logic. The translation control logic determines the mapping of addresses from the I/O channel to system memory.

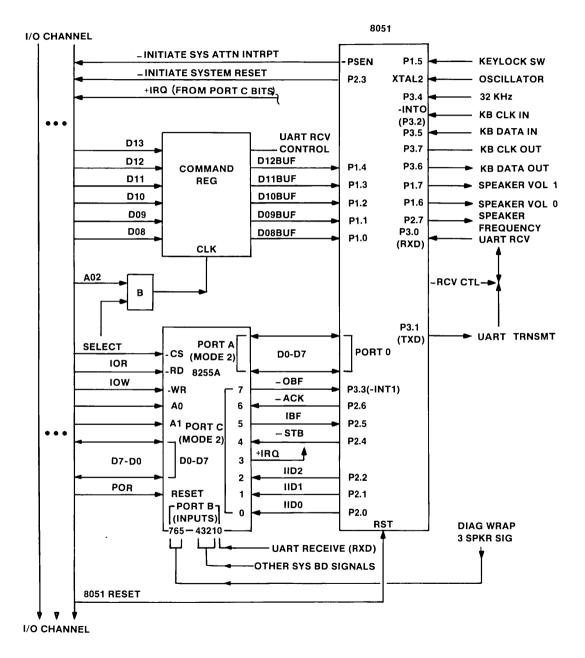

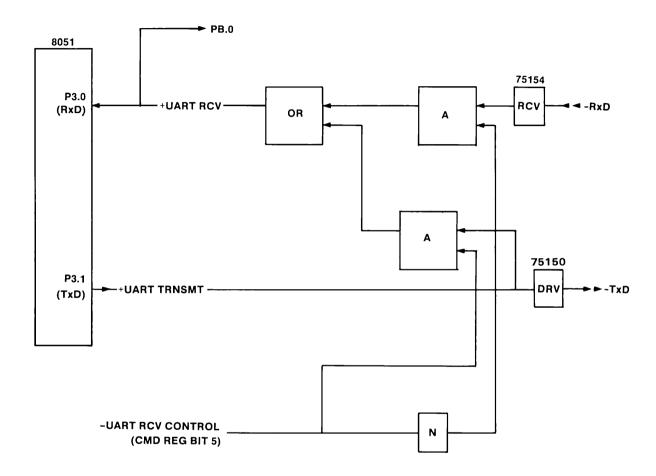

- Keyboard/Locator Controller. An 8051 microprocessor and 8255 peripheral interface are used for the keyboard controller. The 8051 microprocessor handles keyboard, locator (mouse or tablet) and speaker communications independent of the processor board.

- Real-Time Clock. A Motorola 146818 CMOS module is used for the real-time clock. The real-time clock is battery-powered and provides both time of day information and nonvolatile memory of certain system configuration information.

- RS232C Serial Port Logic. The IBM 6150 provides logic on the system board for two RS232C serial ports. The IBM 6151 does not provide these serial ports.

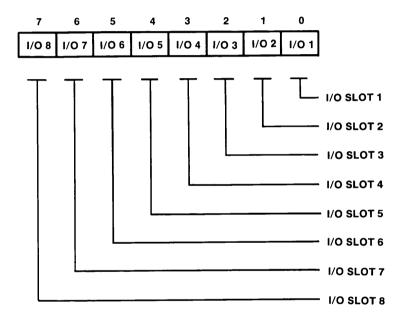

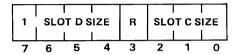

#### I/O Channel

The I/O channel provides a 16-bit and 8-bit data bus for attachment of standard I/O adapters. The IBM 6150 provides six 16-bit slots and two 8-bit slots, with the IBM 6151 providing five 16-bit slots and one 8-bit slot.

# **System Performance**

The RT PC processor board operates at a 170 nanosecond cycle time. Execution time for instructions is contained in Appendix A.

The memory channel can supply 4 bytes of data every 170 nanoseconds, which results in a bandwidth of 23.5M-bytes per second.

System memory refresh operations are controlled by the memory management unit (MMU), and normally occur during idle memory cycles. Typical refresh interference is about one percent of the available memory bandwidth.

# **System Hardware Overview**

The RT PC system hardware includes the system board, processor board, memory boards and Floating-Point Accelerator.

#### **Nomenclature**

This section discusses the conventions used on the processor channel and the conventions used on the I/O channel. The I/O Channel Controller (IOCC) provides the connection between the two different conventions.

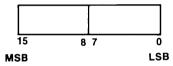

#### **Notes:**

- 1. MSB = Most Significant Bit

- 2. LSB = Least Significant Bit

#### **Data Names and Bit Conventions**

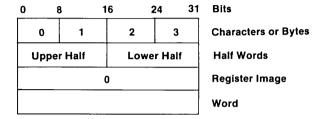

The RT PC system hardware includes both unique 32-bit system processor features and standard 16-bit I/O channel features. Standard System 370 terminology is used when discussing address quantities, data quantities, and bit numbering related to the 32-bit components. Standard vendor notation is used for the 16-bit I/O channel features.

The following terminology is used for the 32-bit components:

- Word A word is four consecutive bytes, or 32 consecutive bits.

- Halfword A halfword is two consecutive bytes, or 16 consecutive bits.

- Byte A byte is eight consecutive bits.

The following bit numbering is used for the 32-bit components:

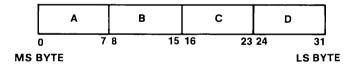

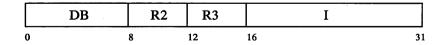

The following terminology is used when discussing address and data quantities related to the 16-bit I/O channel:

- Doubleword A doubleword is four consecutive bytes, or 32 consecutive bits.

- Word A word is two consecutive bytes, or 16 bits.

- Byte A byte is eight consecutive bits.

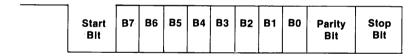

The following bit order is used for the 16-bit components:

#### **Hexadecimal Notation**

The notation X 'value' is used for all hexadecimal numbers. For example, X'A123' is the 16-bit hexadecimal value A123.

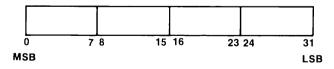

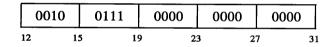

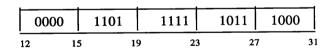

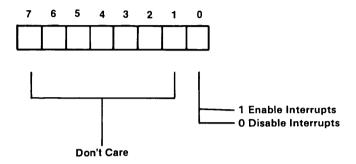

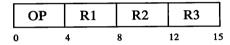

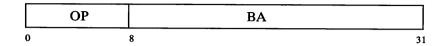

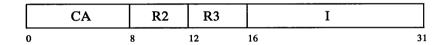

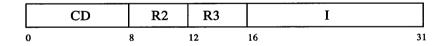

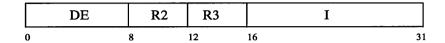

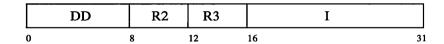

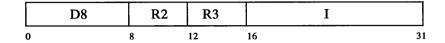

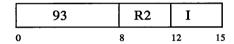

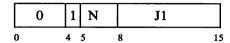

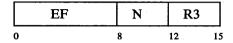

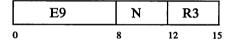

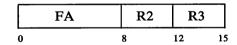

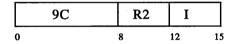

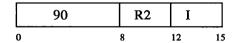

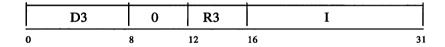

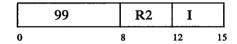

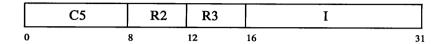

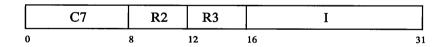

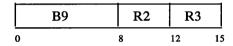

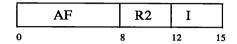

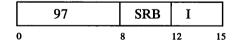

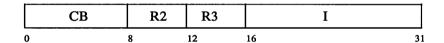

#### **Processor Channel Bit Convention**

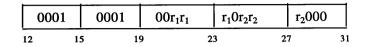

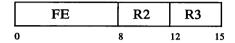

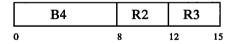

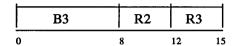

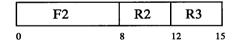

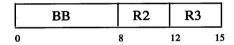

The processor channel bit convention is as follows:

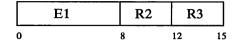

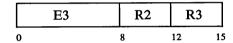

Figure 1-2. Processor Channel Bit Convention

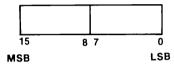

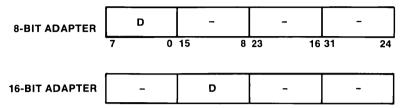

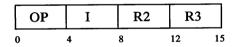

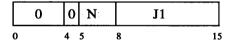

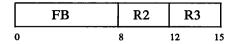

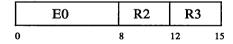

#### I/O Channel Bit Convention

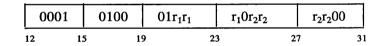

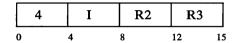

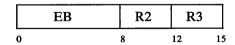

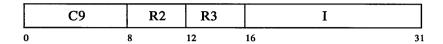

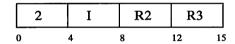

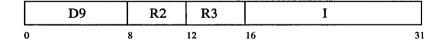

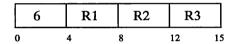

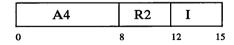

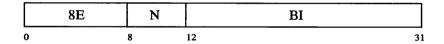

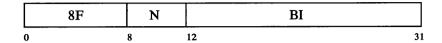

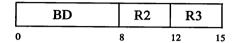

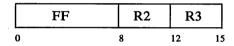

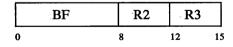

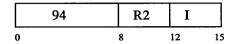

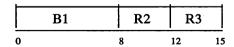

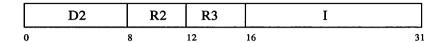

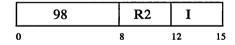

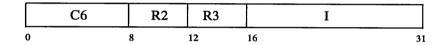

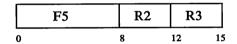

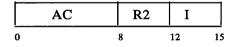

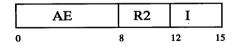

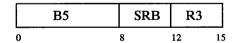

The I/O channel data bus uses the following convention for 8 bits.

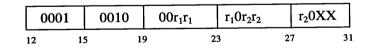

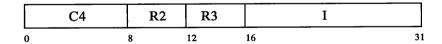

Figure 1-3. I/O Channel 8-Bit Convention

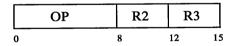

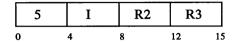

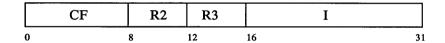

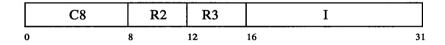

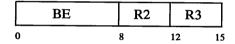

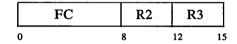

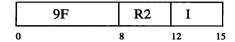

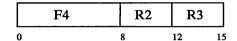

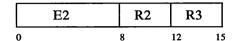

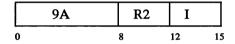

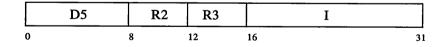

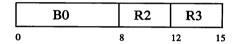

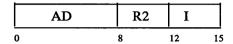

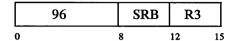

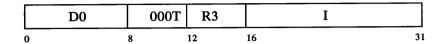

The I/O channel data bus uses the following convention for 16 bits.

Figure 1-4. I/O Channel 16-Bit Convention

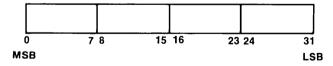

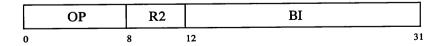

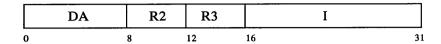

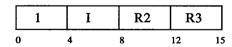

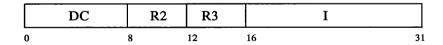

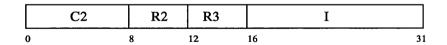

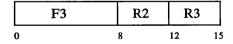

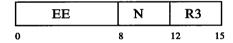

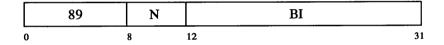

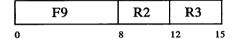

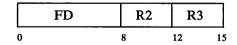

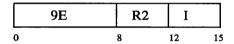

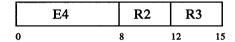

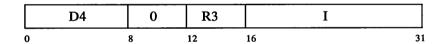

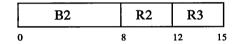

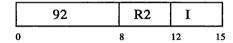

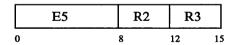

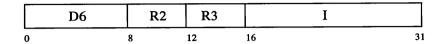

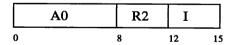

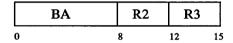

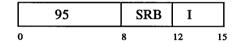

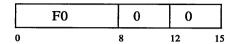

#### **Processor Channel Byte Convention**

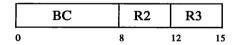

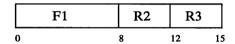

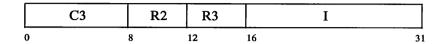

The processor channel uses the following convention.

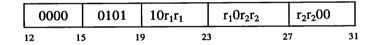

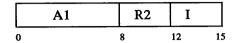

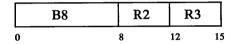

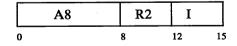

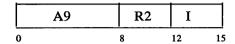

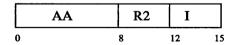

Figure 1-5. Processor Channel Byte Convention

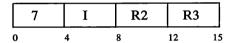

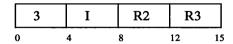

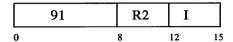

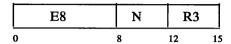

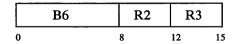

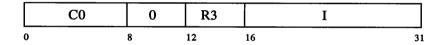

#### I/O Channel Byte Convention

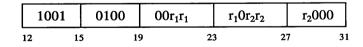

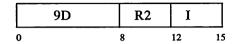

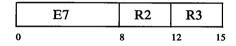

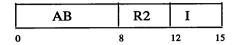

The I/O channel uses the following convention for a 2 byte (16 bit) channel:

Figure 1-6. I/O Channel Byte Convention

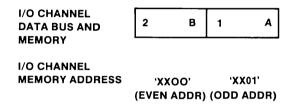

## Coprocessor to I/O Channel and Memory Byte Conventions

When the Coprocessor is attached to the I/O channel, its byte reversal characteristics must be considered. Programmers transferring data between the processor channel and the Coprocessor registers must understand this convention.

The following diagram shows the value X'1A2B' in the AX register of the Coprocessor.

When the AX register value X'1A2B'is sent to the I/O channel data bus, it will be as follows:

The Coprocessor stores the least significant byte in the even address and stores the most significant byte in the odd address.

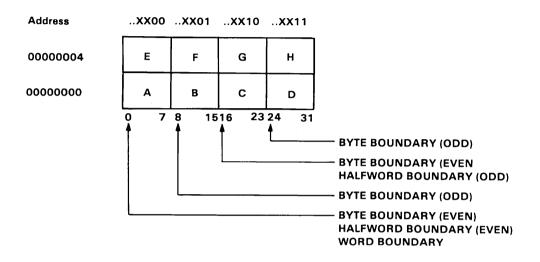

# **System Memory Conventions**

System memory is part of the 32-bit features in RT PC, and uses the following conventions:

A word is four consecutive bytes or 32 consecutive bits. Word

A halfword is two consecutive bytes, or 16 consecutive bits. Halfword

A byte is eight consecutive bits. **Byte**

Word address boundary A word address boundary is an address where the two least

significant address bits are zero (XX00).

A halfword address boundary is an address where the least Halfword address boundary

significant bit is zero (XXX0).

An even halfword address is an address where the two least Even halfword address

significant address bits are zero (XX00).

An odd halfword address is an address where the two least **Odd halfword address**

significant address bits are one and zero (XX01).

An even byte address is an address where the least significant Even byte address boundary

address bit is zero (XXX0).

An odd byte address is an address where the least significant Odd byte address boundary

address bit is one (XXX1).

# **System Memory Addressing Conventions**

Figure 1-7. System Memory Addressing Conventions

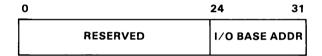

# **Processor Channel to I/O Address Bus Convention**

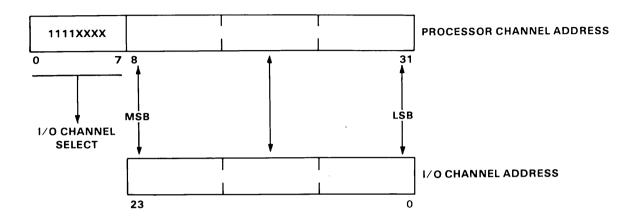

Figure 1-8. I/O Channel Address Bus Mapping

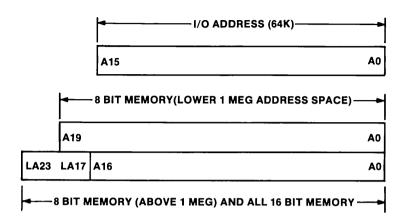

Bits 0-7 of the processor channel select the I/O channel as described in "Addressing Model" on page 1-26. X'F0' selects the I/O channel I/O address space and X'F4' selects the I/O channel memory address space. The low-order 24 bits are used as the I/O channel address.

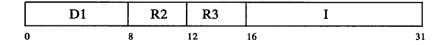

# **System Memory to Processor Channel Byte Positions**

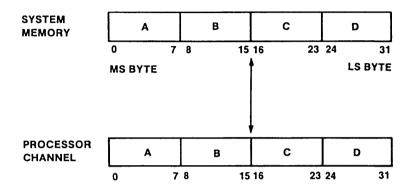

The following figure shows data movement between system memory and the processor channel.

Figure 1-9. System Memory to Processor Channel Bytes

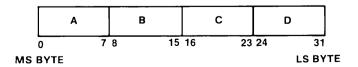

The IOCC always reads a word from system memory. Byte A is always aligned on a word address boundary. The processor channel contents are the same for the following:

- A word read

- An even halfword read (AB)

- An odd halfword read (CD)

- Any single byte read.

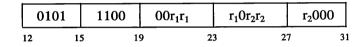

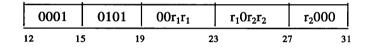

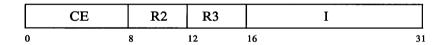

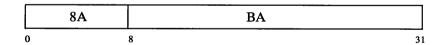

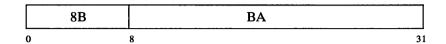

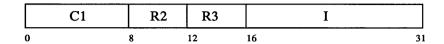

### Processor Channel to I/O Data Bus Conversion

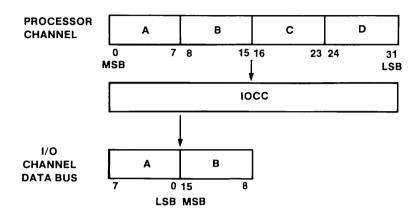

Figure 1-10. Processor Channel to I/O Data Bus Mapping

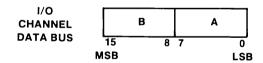

For a 16-bit transfer, the IOCC receives byte A (bits 0-7) from the processor channel and sends them to byte A (bits 7-0) on the I/O channel data bus. Simultaneously, the IOCC receives byte B (bits 8-15) from the processor channel and sends them to byte B (bits 15-8) on the I/O channel data bus. The actual I/O channel data bus format is as follows.

Figure 1-11. I/O Channel Data Bus

If processor channel bytes C and D were also requested, the IOCC would multiplex them onto the 16-bit I/O data bus. The IOCC sends processor channel byte C (bits 16-23) to I/O channel data bus A (bits 7-0) and processor channel byte D (bits 24-31) to I/O channel data bus byte B (bits 15-8).

## **IOCC** to I/O Channel Alignment

The I/O and memory maps on the I/O channel are a collection of 8-bit (byte) addressable elements. There are 16,777,216 such addressable elements within each map. Each transaction over the RT PC I/O Channel (Programmed Input/Output or Direct Memory Access) is capable of transferring 2 bytes (16 bits) of data. The number of bytes actually transferred over the channel during one channel cycle is determined jointly by both the adapter initiating the operation and the target adapter. The transfer defaults to a single byte if one of the adapters is an 8-bit adapter. Transfers of more than 16 bits are accommodated by multiple I/O channel operations.

Both the processor channel and I/O channel have control signals which indicate the amount of data transferred during the current transaction. Depending on the source initiating the transaction, one set of control signals dictates the transfer size while the other set will simply reflect that requirement.

On all system processor PIO operations, the actual data pattern transferred over the I/O channel and the number of channel cycles required is dependent on the amount of data transferred and the width of the selected I/O adapter. This means if the number of bytes transferred by one system processor instruction is larger (2 or 4 bytes) than the data width (1 or 2 bytes) of the selected I/O adapter the IOCC automatically performs multiple I/O operations. For example, a 32 bit microprocessor PIO operation to:

- An 8-bit wide adapter requires the IOCC to perform four distinct channel cycles with each cycle transferring 8 bits of data.

- An 16-bit wide adapter requires the IOCC to perform two distinct channel cycles with each cycle transferring 16 bits of data.

Boundary alignment is strictly enforced on all transfers through the IOCC. The low order address bits are modified by the IOCC so the resulting address conforms to the definitions stated in "System Memory Conventions" on page 1-18. The IOCC forces address bits A(1,0) to 00 on all 32-bit transfers through IOCC for system processor PIO. Similarly, the IOCC forces address bit A(0) to 0 on all halfword transfers through IOCC.

On the I/O channel a 2-byte transfer is flagged by the 'Byte High Enable' (SBHE) signal. The selected I/O adapter signals its data bus width through the 'IOCS16' or 'MEMC16' signal for a 16 bit adapter to either the I/O map or memory map respectively. On the processor channel, the transfer size information is encoded within 'DAB 2, 3' of the address cycle with data being positioned according to the value of the address bus. For a I/O channel byte transfer the two least significant address bits determine which one of the four bytes within the processor channel word participates in the transfer. Also for I/O channel word operations, the second least significant address bit determines which of the two halfwords within the processor channel is selected (with the least significant address bit not used).

The mapping within the IOCC of 8- and 16-bit adapters onto the 32-bit processor channel is accomplished through the multiplexer network on the I/O channel. The IOCC positions data correctly on the I/O channel for system processor PIO operations for 8- and 16-bit adapters on the initial I/O channel cycles based solely on the low order address bits and the transfer size. If the adapter's response indicated a width less than the transfer size then subsequent cycles are required. For these multiple cycles, the multiplexer control is a function of the cycle and adapter width. The IOCC activates the 'SBHE' signal for 16 and 32 bit PIO transfers. This signal is not changed through the duration of the complete operation (1, 2, or 4 I/O channel cycles).

Data alignment through the IOCC, and on both the processor channel and I/O channel, is independent of the device location initiating the operation (I/O or processor channel attached). Alignment is dependent only on the address and size of the transfer. Data is aligned identically for 16-, and 8-bit data flowing from the processor channel to the I/O channel on either a system processor write or DMA read. Data is also aligned identically for 32-, 16-, and 8-bit transfers flowing from the I/O channel to the system processor on either a I/O DMA write or a system processor read.

### **Programming Note**

The IOCC permits the programmer to perform a doubleword (32 bit) read or write to a byte wide adapter on the I/O channel. The IOCC converts this single transaction into either 2 or 4 I/O channel operations depending on the amount of data transferred and the characteristics of the selected adapter (16 or 8 bits). If the operation is directed to the memory map on the I/O channel, the IOCC increases the address between consecutive channel transfers. If the operation is directed to the I/O map on the I/O channel, the IOCC holds the address constant between consecutive channel transfers.

This facility can not be used without knowledge by the programmer of the characteristics of the addressed adapter. In particular, the adapter must be capable of handling back-to-back operations without violating any timing restrictions it may have. The responsibility for knowing the characteristics of the I/O adapter and not violating these restrictions resides with the programmer.

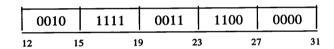

If a I/O adapter requests one byte (byte D), the processor channel presents the byte as shown in Figure 1-7 on page 1-19. The IOCC aligns the byte as shown below. This allows the adapter to get the byte in one cycle according to its data width.

#### **DATA ALIGNMENT REQUIRED FOR**

Figure 1-12. Data Alignment for 8- and 16-Bit Adapters

# **Addressing Model**

This section describes the addressing model of the RT PC system board. The addressing model is described from the view that the IOCC is attached to the processor channel.

This section further describes how the addresses move through the IOCC and what action the IOCC will take on addresses generated from both the processor channel and I/O channel. Detailed descriptions of hardware implementation found in other sections of this document are referred to throughout this section.

The nomenclature used in this section for bit numbering and data naming are described in "Nomenclature" on page 1-13.

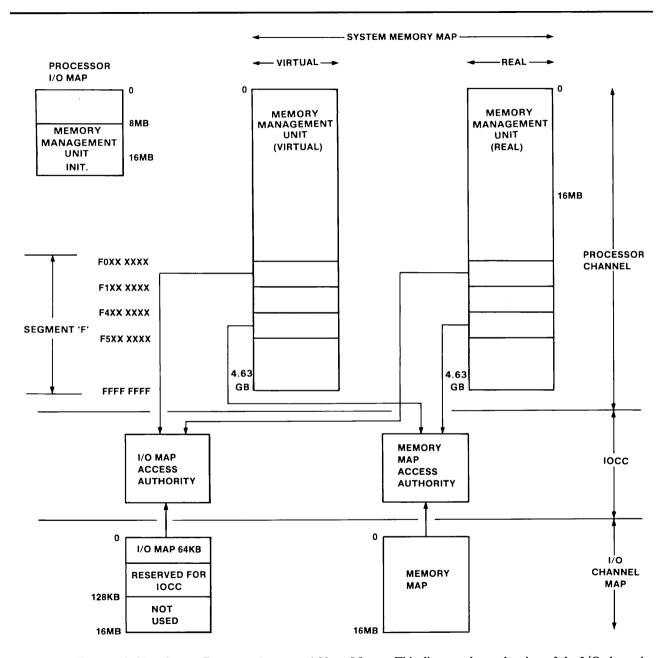

The system processor communicates with the system through the processor channel. The processor channel has both I/O and memory address space (maps) that are accessible from either the I/O channel or the system processor. The memory map on the processor channel is further divided into real and virtual accesses. The I/O Channel Controller (IOCC) is a device on the processor channel. The system processor has access to the I/O adapters through the IOCC and, conversely, I/O adapters have access to the system memory. The I/O channel has both I/O and memory maps. The following two sections describe the system processor's view of the I/O channel maps and an adapter's view of both the I/O channel and processor channel maps.

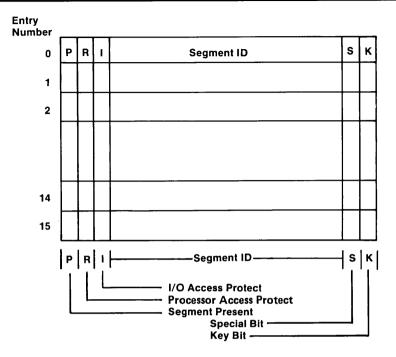

The term segment is used in the following sections to describe various address spaces on the processor channel. The most significant four bits of the 32-bit address on the processor channel select one of sixteen areas, which are called segments. These segments are numbered zero through fifteen and are called segments 0 through F. Segment F is assigned to the IOCC and is further decoded in the IOCC to select between the I/O channel I/O map and the I/O channel memory map as described in "I/O MAP" on page 1-28 and "Memory Map" on page 1-29.

### **Addressing From the System Processor**

This section covers access to both of the address maps on the I/O channel as viewed from the program executing system processor instructions. The view that the system processor has of these address maps is shown in Figure 1-13 on page 1-30.

The RT PC system configuration has four devices attached to the processor channel. These devices, along with their characteristics, are:

#### **System Processor**

The system processor can initiate an operation over the processor channel through the execution of the following commands:

- I/O read and write (IOR and IOW) instructions to control registers, translation buffers, and segment registers in the memory management unit.

- Load or store instructions to system memory, IOCC control registers, the I/O channel, or the floating point accelerator.

Use of the IOR and IOW instructions is described in "Input/Output" on page 11-83 and "Control Registers" on page 11-113. The various load and store instructions are described in "Load and Store Instructions" on page 11-31.

The system processor does not have any registers that are addressable over the processor channel. Thus, it never responds to processor channel requests.

### **Memory Management Unit**

The memory management unit (MMU) cannot initiate a processor channel operation. That is, it cannot generate an address. The memory management unit will either supply data in response to a read request or will receive data on a write operation. It responds to I/O space (IOR, IOW) operation for control functions and memory space (Memory Read, Write) for memory references.

### **Floating-Point Accelerator Option**

The Floating-Point Accelerator cannot initiate a processor channel operation. That is, it cannot generate an address. The Floating-Point Accelerator is always the target of an address. Thus, it will either supply data in response to a read request, or it will receive data on a write operation. It responds to memory space (Memory Read, Write) operations for referencing segment 'FF' of the address map.

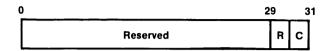

#### **IOCC**

The IOCC can both initiate operations on the processor channel as well as be the target of processor channel operations. IOCC initiates processor channel operations as a result of a DMA operation on the I/O channel. Furthermore, it is the target of a processor channel operation resulting from LOAD and STORE instructions executing in the system processor or from a system processor instruction fetch. The IOCC responds only to processor channel address cycles which are referencing segment 'F0' or 'F4' of either the real or virtual address map. All references to the I/O map on the processor channel are ignored.

For system processor access to the I/O channel (to either the I/O map or the memory map) the IOCC performs the number of I/O cycles (1,2, or 4) required to transfer the data. This is possible because the I/O adapter identifies its data width when selected. The IOCC first aligns the address to the appropriate boundary as indicated by the size of the transfer (for instance, forcing word or double word) address by modifying address bits A(1) and/or A(0) as required. Since boundary

alignment is strictly enforced, the address used for the second and subsequent channel cycles will differ from the first by the 2 low order address bits. Refer to "System Memory Conventions" on page 1-18.

The IOCC supports system processor access to the I/O channel address map for both data (Memory Read, Write) and instructions.

The rest of this section discusses access to the I/O map and memory map of the I/O channel. Refer to Figure 1-13 on page 1-30 and Figure 1-15 on page 1-34.

### I/O MAP

Access to the I/O address map of the I/O channel is through the first 16 M-bytes of the segment 'F'. Access to this map is controlled by the state of the I/O Map Access Authority (IMAA) latch.

Access attempts to the I/O address map of the I/O channel in unprivileged state with the IMAA set to privileged state are not allowed by the IOCC. A protection violation error will be reported. Refer to the "Channel Status Register (CSR)" on page 5-63. Access to the I/O address map of the I/O channel in privileged state is allowed regardless of the state of the IMAA.

Note: Access to the channel status register (CSR) within the IOCC is restricted to privileged state only.

The IOCC supports byte (8 bits), word (16 bits), and doubleword (32 bits) access to the I/O address map. The IOCC activates a control signal on the I/O channel to indicate the transfer size as stated by the system processor instruction executed. If the I/O adapter is not capable of transferring the requested number of bytes, multiple accesses are made to the same address until the requested amount of data has been transferred.

One characteristic of the system processor structure is that non-adjacent (order of execution) Read/Write instructions to external devices (memory management unit or IOCC) can (and often do) arrive at the device as if they were adjacent. That is, the programmer cannot guarantee the time period between consecutive accesses to an adapter simply by inserting some instructions between the two I/O channel references. The effect of this is that the I/O adapter may receive I/O commands at a rate faster than it can process them. The IOCC is not capable of ascertaining any performance limitations relative to 'wait' time between consecutive I/O operation associated with a given address in the I/O space. Thus, the responsibility for knowing the characteristics of the I/O adapter and not violating these restrictions resides with the programmer.

To aid software in generating wait time for those adapters that require a minimum time delay between consecutive accesses, a 'NOP like' I/O command has been provided that can be inserted between the I/O instructions to the adapter. Access to this I/O delay register between otherwise sequential accesses to I/O subsystem and I/O channel adapter options prevents the possible loss of data. The system board devices which should use this mechanism are: 8237s, 8259s, real time clock (RTC), and the keyboard adapter.

Boundary alignment is strictly enforced on the I/O channel. That is, the IOCC may alter the low order address bits as received from the processor channel before they are applied to the I/O channel. Refer to "IOCC to I/O Channel Alignment" on page 1-23.

### **Memory Map**

Access to the memory address map of the I/O channel is through to the fifth 16M-bytes of segment 'F'. Access to this map is controlled by the state of the Memory Map Access Authority (MMAA) latch.

Access attempts to the I/O channel memory address map in unprivileged state with the MMAA set to privileged state are not allowed by the IOCC, and a "protection violation" error will be reported. Access to the memory address map of the I/O Channel in privileged state is allowed regardless of the state of the MMAA.

The IOCC supports byte (8 bits), word (16 bits), and doubleword (32 bits) access to the memory address map. The IOCC activates a control signal on the I/O channel to indicate the transfer size as stated by the system processor instruction executed. If the I/O adapter is not capable of transferring the requested number of bytes, multiple access will be made to consecutive addresses until the requested data has been transferred. However, since none of the I/O subsystems use any portion of the memory address map, this function is not supported on the system board.

Boundary alignment is strictly enforced on the I/O channel. That is, the IOCC may alter the low order address bits as received from the processor channel before they are applied to the I/O channel. Refer to "IOCC to I/O Channel Alignment" on page 1-23.

Figure 1-13. System Processor Access to Address Maps. This diagram shows the view of the I/O channel, I/O and memory maps from the system processor and the access authority control.

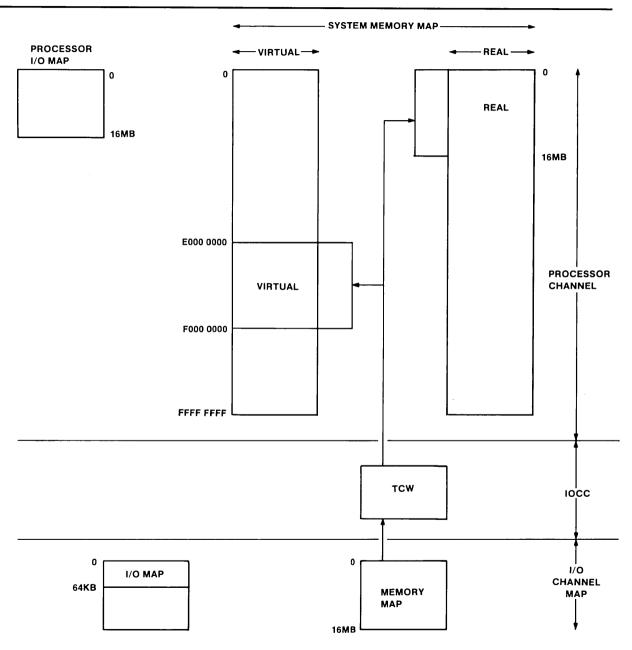

# Addressing From the I/O Channel

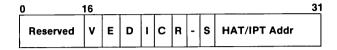

This section covers access to the maps on the I/O channel and access to system memory as viewed from an adapter on the I/O channel. The view that a alternate controller has of memory and its access path is shown in Figure 1-14 on page 1-33.

The IOCC responds to addresses originating on the I/O channel. I/O addresses are restricted to the I/O subsystem facilities. The I/O address is not propagated onto the processor channel. Access to the I/O subsystem by I/O adapters is controlled by three channel access control bits. Memory addresses to which the IOCC will respond are under program control. The IOCC does not contain any facilities within the memory map, but it will respond to the I/O channel operation for the processor channel.

### I/O MAP

An I/O adapter cannot access the I/O address map on the processor channel. However, it can access the other adapters on the I/O channel in the I/O map.

Most of the registers internal to the IOCC can be accessed from an alternate controller adapter operating in region mode. These registers are in the I/O map and are addressed with the IOR or IOW control lines. Access to this I/O map from the system processor can be controlled through the IMAA latch. A separate set of control latches must be used to control access by alternate controller adapters.

Note: Alternate controller adapters cannot address (and, therefore, cannot access) the channel status register (CSR) or the translation control word (TCW) RAM.

### **Memory Map**

The I/O channel architecture of RT PC permits a variety of adapter types to exist in the memory map:

- Memory board options

- I/O adapters with RAM addressable in the memory map

- I/O adapters with internal registers addressable in the memory map

- IOCC which permits access to system memory by alternate controller adapters.

RT PC system architecture requires the physical location of Random Access Memory (RAM) in the I/O memory map be transparent to the alternate controller adapter referencing it. For example, if performance of the 286 Coprocessor is important, then RAM should be located on the I/O channel. However, if low entry cost is desired, the 286 Coprocessor can execute out of system memory. The

application program is to be unaware (except for time dependent code) of the physical location of the memory out of which it is executing.

When a memory address is placed on the I/O channel, it is examined by all adapters, including the IOCC, to determine if the address is within the range covered by the adapter. If a match is found by one adapter, it responds with the appropriate channel control signals. To maintain the integrity of the data and to avoid damage to the channel interface circuitry, it is important that only one adapter responds to a given address.

One of the primary functions of the IOCC is to provide access to system memory. Thus, the IOCC must examine each reference to the memory map on the I/O channel to determine if the address was intended for system memory. The effect is that this requirement places an unusual burden on the IOCC not commonly found in I/O adapters. In general, I/O adapters have a fixed address range in the memory map to which they respond. The address range to which the IOCC responds is variable since it can differ for alternate controller and DMA devices as well as vary with application. This selection is controlled by the values written into the IOCC translation mechanism by the software. Refer to the section on IOCC translation mechanism.

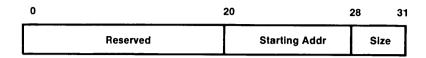

All addresses in the memory map applied to the I/O channel by adapters are processed by the IOCC under control of its TCW. This translation mechanism is a programmable facility controlling target memory location, memory protection, defining access mode, and reformatting the address. The central part of this mechanism is a 1K x 16 bit RAM.

Figure 1-14. Access to System Memory Maps from IOCC. This diagram shows how an I/O channel adapter views the system memory map IOCC address translation.

# **System Processor Address Map**

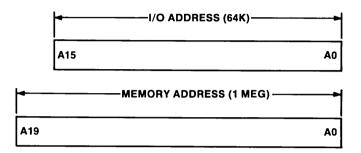

The system processor can directly address two completely independent address spaces. The address spaces are called memory and I/O. Access to these maps by the system processor is controlled by the instruction being executed (I/O or Memory Load/Store) and memory mode (real or virtual). The I/O address is 24 bits, while the system address is 32 bits. The address maps from the perspective of the system processor are given in Figure 1-13 on page 1-30 and Figure 1-14 on page 1-33.

Note: Even though the system processor supports a 32-bit real memory address, the RT PC system is limited to a 24-bit real memory address.

| Address Range     | Size    | Device                                     |

|-------------------|---------|--------------------------------------------|

| 00 0000 - 7F FFFF | 8 MB    | Not Defined                                |

| 80 0000 - 80 FFFF | 64 KB   | Processor Channel Device<br>Initialization |

| 81 0000 - 81 FFFF | 64 KB   | Memory Management Unit                     |

| 82 0000 - FF FFFF | 8064 KB | Not Defined                                |

Figure 1-15. System Processor Address I/O Map

| Address Range         | Size   | Device                     |

|-----------------------|--------|----------------------------|

| 0000 0000 - 00FF FFFF | 16 MB  | Memory Management Unit     |

| 0100 0000 - EFFF FFFF |        | Not Defined                |

| F000 0000 - F0FF FFFF | 16 MB  | I/O Channel I/O Map        |

| F100 0000 - F3FF FFFF | 48 MB  | Reserved                   |

| F400 0000 - F4FF FFFF | 16 MB  | I/O Channel Memory Map     |

| F500 0000 - FEFF FFFF | 158 MB | Reserved                   |

| FF00 0000 - FFFF FFFF | 16 MB  | Floating Point Accelerator |

Figure 1-16. System Processor Real Memory Address Map

| Address Range         | Size   | Device                     |

|-----------------------|--------|----------------------------|

| 0000 0000 - EFFF FFFF | 4 GB   | Memory Management Unit     |

| F000 0000 - F0FF FFFF | 16 MB  | I/O Channel I/O Map        |

| F100 0000 - F3FF FFFF | 48 MB  | Reserved                   |

| F400 0000 - F4FF FFFF | 16 MB  | I/O Channel Memory Map     |

| F500 0000 - FEFF FFFF | 158 MB | Reserved                   |

| FF00 0000 - FFFF FFFF | 16 MB  | Floating-Point Accelerator |

Figure 1-17. System Processor Virtual Memory Address Map

### **Interrupts**

The interrupt facility permits the system processor to change its status at the request of some other system element. The interrupting sources are:

- Software generated interrupt request from system processor's interrupt request buffer

- System component on the processor channel

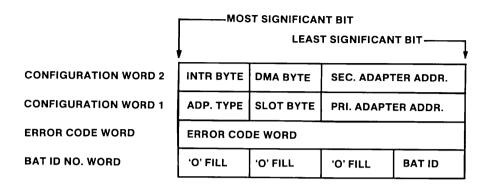

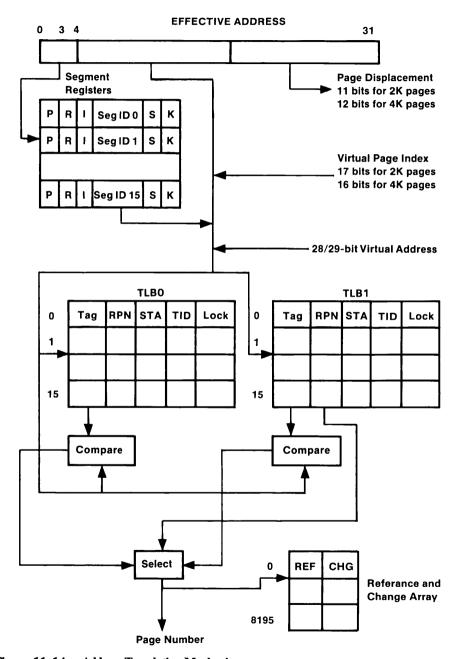

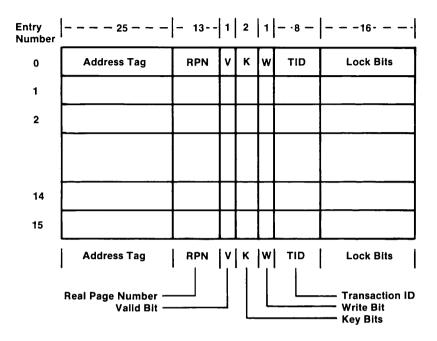

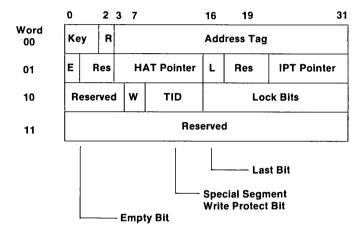

- I/O adapters on the I/O channel.