# Assembler Language Reference

**Programming Family**

Personal Computer Software

# Assembler Language Reference

**Programming Family**

Personal Computer Software

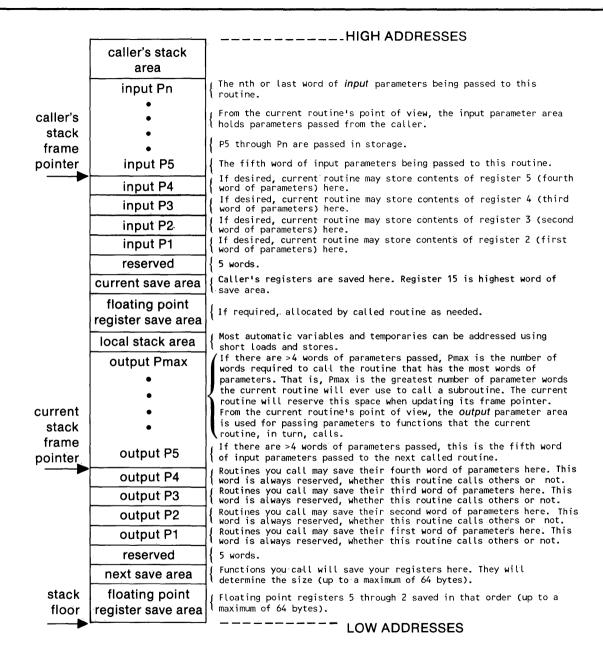

#### First Edition (November 1985)

Changes are made periodically to the information herein; these changes will be incorporated in new editions of this publication.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

International Business Machines Corporation provides this manual "as is," without warranty of any kind, either express or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this manual at any time.

Products are not stocked at the address given below. Requests for copies of this product and for technical information about the system should be made to your authorized IBM RT PC dealer.

A reader's comment form is provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Department 997, 11400 Burnet Road, Austin, Texas 78758. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

- © Copyright International Business Machines Corporation 1985

- © Copyright INTERACTIVE Systems Corporation 1984, 1985

## **About This Book**

This book discusses the RT PC implementation of the 032 Microprocessor assembler language on the AIX Operating System. The book contains 032 Microprocessor assembler language syntax and semantics, along with information on linking and running an 032 Microprocessor assembler language program. The book also shows how to link to programs written in the high-level languages supported by RT PC.

Programmers may prefer to use a high-level language for general-purpose programming instead of 032 Microprocessor assembler language because:

- The 032 Microprocessor has a reduced instruction set.

- The 032 Microprocessor was designed as an efficient target for compilers, but not for assembler language programming. For example, the assembler does not give an error message for undefined external symbols.

Note that this book does not teach assembler language programming. You should use this book for reference only.

## Who Should Read This Book

This book is intended for applications and systems programmers who know another assembler language. This book contains information about using 032 Microprocessor assembler language to write portions of application programs. For example, it might be appropriate to use the 032 Microprocessor assembler language to create small library routines to take advantage of architectural functions not available in the C language.

The 032 Microprocessor assembler language also allows you to write code for the Virtual Resource Manager (if it exists) and the AIX Operating System kernel. This book includes the processor instructions to perform these tasks, but does not discuss them in detail. If you want to write 032 Microprocessor assembler language programs to perform these tasks, or if you want information about RT PC architecture, you need to read books in addition to this one. (See "Related Publications" on page viii and "What Is Not in This Book" on page vi.)

This book assumes that you know how to use your RT PC system. You should be able to log in, create files, edit files, and use various other operating system commands. If you need information about these topics, see "Prerequisite Publications" on page vii.

## How This Book is Organized

- "Chapter 1. Overview of Processing and Storage on the 032 Microprocessor" briefly explains data representation and registers on the 032 Microprocessor.

- "Chapter 2. Assembler Language Concepts" discusses the syntax of statements, expressions, symbols, and constants. This chapter also explains the 032 Microprocessor assembler language's character set, along with the notational conventions used in this book.

- "Chapter 3. Addressing and Program Sectioning" explains how to combine lines of assembler code. This chapter includes information on addressing and on declaring base registers. This chapter also explains the assembler's location counter and the relationship between a.out segments and assembler language sections.

- "Chapter 4. 032 Microprocessor Instructions" describes the 032 Microprocessor instructions with both mnemonics and op codes. The instructions are listed by function, then described alphabetically by mnemonic.

- "Chapter 5. Pseudo-Ops" provides an alphabetical description of the directives programmers can send to the assembler itself.

- "Chapter 6. Assembling, Linking, and Running a Program" describes the AIX Operating System commands used to assemble, link, and run assembler language files. This chapter also describes the conventions you should use to link 032 Microprocessor assembler language files to files written in other languages.

- "Appendix A. Mnemonic and Op Code Tables" contains two tables. One table lists instructions alphabetically by mnemonic; a second table lists instructions numerically by op code.

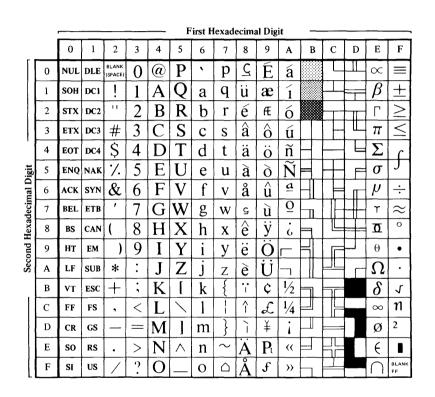

- "Appendix B. ASCII Character Codes" lists the numeric representations of valid characters on the RT PC.

The "Glossary" defines terms that are specific to 032 Microprocessor assembler language and to RT PC.

A Reader's Comment Form and Book Evaluation Form are provided at the back of this book. Use the Reader's Comment Form at any time to give IBM information that may improve the book. After you become familiar with the book, use the Book Evaluation Form to give IBM specific feedback about the book.

## What Is Not in This Book

As mentioned previously, this book does not teach readers how to program or to operate their RT PC system. Furthermore, this book contains little or no information about:

- Any commands, system calls, subroutines, or programming aids that are part of the AIX Operating System, except for the **as** (assembler) command; limited information is given about the **cc** (C compiler) and **ld** (link editor) commands.

- Error messages generated by as. These messages are shown in Messages Reference.

- Specific aspects of creating or running any code that exists in the Virtual Resource Manager (VRM).

- Any hardware features (except some registers).

- Details about 032 Microprocessor privileged instructions, including information about I/O and supervisor calls.

- Running 032 Microprocessor assembler language programs directly on the VRM, or creating programs that run directly on the VRM.

- Running 032 Microprocessor assembler language programs on any operating system other than AIX Operating System, or creating programs that run on any such operating system.

For information about these topics, see "Related Publications" on page viii.

## **Prerequisite Publications**

You should be familiar with the following books before you try to use this book:

- IBM RT PC Using and Managing the AIX Operating System describes using AIX Operating System commands, working with the file system, and developing shell procedures. This book also provides instructions for performing such system management tasks as adding and deleting user IDs, creating and mounting file systems. backing up the system, and repairing file system damage.

- IBM RT PC Guide to Operations describes the Model 10, Model 20, and Model 25 system units, the displays, keyboard, and other devices that can be attached. This guide also includes procedures for operating the hardware and moving the Model 10. Model 20, and Model 25 system units.

- IBM RT PC AIX Operating System Commands Reference lists and describes the AIX Operating System commands.

## **Related Publications**

This book refers to the following books:

- IBM RT PC AIX Operating System Programming Tools and Interfaces describes the programming environment of the AIX Operating System and includes information about using the operating system tools to develop, compile, and debug programs. In addition, this book describes the operating system services and how to take advantage of them in a program. This book also includes a diskette that includes programming examples, written in C language, to illustrate using system calls and subroutines in short, working programs. (Available optionally)

- IBM RT PC Virtual Resource Manager Technical Reference describes the Virtual Resource Manager (VRM) routines, how to use the VRM debugger, how to develop and install code into the VRM, and defines the interface to the VRM-supplied device drivers. This book also describes the Virtual Machine Interface (VMI) between the Virtual Resource Manager and the AIX Operating System and provides information about process control, memory management, the I/O subsystem, the minidisk manager, and device drivers. (Available optionally)

- The VRM section defines VRM routines, explains how to use the VRM debugger, explains how to develop and install code into the VRM, and defines the Virtual Machine Interface (VMI) to the VRM-supplied device drivers. The VMI section describes the interface between the RT PC and the VRM, and discusses process control, memory management, the I/O system, the minidisk manager, and device drivers.

- IBM RT PC Hardware Technical Reference is a two-volume set. Volume I describes how the system unit operates, including I/O interfaces, serial ports, memory interfaces, and CPU interface instructions. Volume II describes adapter interfaces for optional devices and communications and includes information about IBM Personal Computer family options and the adapters supported by Model 10, Model 20, and Model 25. (Available optionally)

- IBM RT PC AIX Operating System Technical Reference describes the system calls and subroutines that a C programmer uses to write programs. This book also provides information about the AIX file system, special files, miscellaneous files, and writing device drivers. (Available optionally)

- Both volumes may be relevant to programmers who are writing device drivers.

- IBM RT PC C Language Guide and Reference provides guide information for writing, compiling, and running C language programs and includes reference information about C language data structures, operators, expressions, and statements. (Available optionally)

- IBM RT PC Problem Determination Guide provides instructions for running diagnostic routines to locate and identify hardware problems. Also includes problem determination for software. Two high-capacity (1.2MB) diskettes containing the IBM RT PC diagnostic routines are included.

- IBM RT PC Messages Reference lists messages displayed by the IBM RT PC and explains how to respond to the messages.

- IBM RT PC Bibliography and Master Index provides brief descriptive overviews of the books and tutorial program that support the IBM RT PC hardware and the AIX Operating System. In addition, this book contains an index to the RT PC and AIX Operating System library.

## Ordering Additional Copies of This Book

To order additional copies of this publication, use either of the following sources:

- To order from your IBM representative, use Order Number SV21-8011.

- To order from your IBM dealer, use Part Number 55X-8930.

A binder is included with the order.

## **Contents**

| Chapter 1. Overview of Processing and Storage on the 032 |            |

|----------------------------------------------------------|------------|

| Microprocessor                                           | 1-1        |

| About This Chapter                                       | 1-3        |

| The 032 Microprocessor and its Protection States         |            |

| Data Representation in Main Storage                      |            |

| Data Representation in Registers                         | 1-7        |

| Chapter 2. Assembler Language Concepts                   | 2-1        |

| About This Chapter                                       | 2-3        |

| Notational Conventions                                   |            |

| Character Set                                            |            |

| Reserved Words                                           |            |

| Line Format                                              |            |

| Statements                                               |            |

| Symbols                                                  | 2-13       |

| Constants                                                | 2-16       |

| Expressions                                              | 2-18       |

| Chapter 3. Addressing and Program Sectioning             | <b>2_1</b> |

| About This Chapter                                       | 3 3<br>0-1 |

| Addressing                                               | 3-4        |

| Assembler Sections and Runtime Segments                  |            |

| Assembler Sections and Runtime Segments                  | 0-0        |

| Chapter 4. 032 Microprocessor Instructions               | 4-1        |

| About This Chapter                                       | 4-3        |

| Introduction to Instructions                             |            |

| Categories of Instructions                               |            |

| Notational Conventions for Instructions                  | 4-22       |

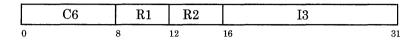

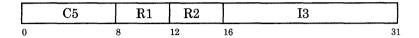

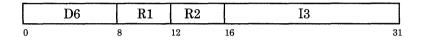

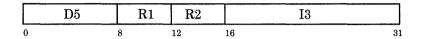

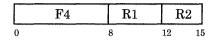

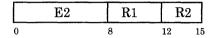

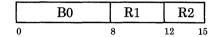

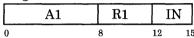

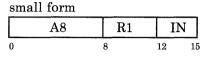

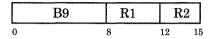

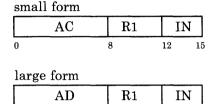

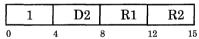

| Instruction Formats                                      | 4-26       |

| Directory of Instructions                                | 4-28       |

| Chapter 5. Pseudo-Ops                                    | 5-1        |

| About This Chapter                                       | 5-3        |

| What Is a Pseudo-Op?                                     | 5-4        |

| Categories of Pseudo-Ops                                 | 5-5        |

| Notational Conventions                                   |            |

| Directory of Pseudo-Ops                                  |            |

| Chapter 6. Assembling, Linking and Running a Program  About This Chapter | • • • | 6-1<br>6-3 |

|--------------------------------------------------------------------------|-------|------------|

| Assembling and Linking with cc                                           |       | 6-4        |

| Assembling and Linking with Two Separate Steps                           |       | 6-5        |

| Running the Program                                                      |       | 6-23       |

| Appendix A. Mnemonic and Op Code Tables                                  |       | A-2        |

| Appendix B. ASCII Character Codes                                        |       | B-1        |

| Figures                                                                  |       | X-1        |

| Glossary                                                                 |       | X-3        |

| Index                                                                    |       | X-9        |

## Chapter 1. Overview of Processing and Storage on the 032 Microprocessor

## **CONTENTS**

| About This Chapter                               |

|--------------------------------------------------|

| The 032 Microprocessor and its Protection States |

| Data Representation in Main Storage              |

| Data Representation in Registers                 |

| General Purpose Registers                        |

| System Control Registers                         |

## **About This Chapter**

The RT PC 032 Microprocessor assembler language is influenced by the characteristics of its machine's storage and processor. The capabilities of the processor and the nature of the available storage determine what the assembler language can do.

This chapter gives an overview of the 032 Microprocessor and tells you how data is stored on the RT PC in main storage and in registers. This information may help you understand how to use 032 Microprocessor instructions and pseudo-ops.

## The 032 Microprocessor and its Protection States

The 032 Microprocessor is a 32-bit *pipelined* processor. The 032 Microprocessor has a reduced instruction set, with few memory access instructions. Except for the memory access instructions, most instructions execute in a single processor cycle.

The 032 Microprocessor's assembler language is designed to support systems and application programming in high-level languages. Therefore, the 032 Microprocessor assembler language is intended primarily as an efficient target for compilers.

032 Microprocessor, the physical or "real" machine, has two protection states; privileged and unprivileged.

In privileged state, 032 Microprocessor accepts all instructions, including privileged *instructions*. Privileged instructions generally manipulate virtual machines (if they exist) or the memory manager, and are not discussed at length in this book. 032 Microprocessor assembler language programmers can access 032 Microprocessor privileged state with the Supervisor Call (svc) instruction.

The 032 Microprocessor's privileged state supports virtual machines. On RT PC, the Virtual Resource Manager (VRM) is the only entity that runs in privileged state. The VRM is a collection of processes, interrupt handlers, and runtime routines that support the Virtual Machine Interface by issuing privileged instructions to the hardware. The VRM redefines the processor's physical protection states for virtual machines and creates software emulations of the processor's physical registers. The Virtual Machine Interface (VMI) is the link between the operating system and the VRM programs that regulate system resources. See Virtual Resource Manager Technical Reference for information about how virtual machines work on RT PC.

In unprivileged state, 032 Microprocessor accepts only unprivileged instructions such as adds, shifts, and loads. Both the operating system and ordinary application programs run in unprivileged state. Virtual machines also run in 032 Microprocessor unprivileged state.

This book includes both privileged and unprivileged instructions, but emphasizes the unprivileged instructions. For more information on the context in which privileged instructions occur, see Virtual Resource Manager Technical Reference.

**Note:** Floating point support is available with optional hardware, or with floating point software emulation in the AIX Operating System. See Hardware Technical Reference for information on the floating point registers.

## Data Representation in Main Storage

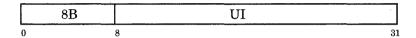

On the RT PC, main storage is organized as a series of eight-bit bytes with a maximum address of 2<sup>32</sup> - 1. Bytes in main storage are consecutively numbered, left to right, starting with zero. Four bytes make a word. The leftmost bit of a word is the high-order bit, or the most significant bit. The highest-order bit of a word is stored at a lower address in main storage than the lowest-order bit of the same word.

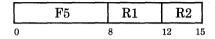

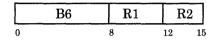

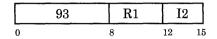

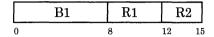

|         |            | F  | Registe | r    |        |       |  |

|---------|------------|----|---------|------|--------|-------|--|

|         | Upper Half |    |         | Lowe | r Half |       |  |

|         | CO         | C1 |         | C2   | C3     | -     |  |

| 0       | 8          |    | 16      |      | 24     | /31   |  |

| h-order |            |    |         |      |        | low-o |  |

Figure 1-1. Data Units in Main Storage. The highest-order byte, Co. is the first character.

The address of a word or halfword in main storage is the address of its leftmost byte. A word must lie on a 4-byte boundary; that is, the address of a word has zeroes in the two low-order bits. A halfword must lie on a 2-byte boundary; that is, the address of a halfword has a zero in the low-order bit.

All instructions must be located on halfword boundaries.

All storage accesses are for a byte or multiple bytes. Storage accesses for words ignore the low-order pair of bits of the effective address. Storage accesses for halfwords ignore the low-order bit of the effective address.

The assembler may give you an error message if you try to access data from or store data to an invalid memory location. Invalid memory accesses will also trigger a program check (see "Program Check Status (PCS)" on page 1-11). You especially need to watch for invalid memory locations if you use the absolute branch instructions, an .org pseudo-op with an absolute operand, or the .direct pseudo-op. For information on invalid memory locations, see Chapter 3.

Wraparound is allowed and occurs on a 32-bit basis. That is, main storage addressing wraps around from the architectural maximum byte address to address 0. For example, if an instruction added 5 to the maximum byte address, the result would be address 4.

The RT PC 032 Microprocessor assembler language supports effective addresses, that is, a base address plus a displacement. Depending on the instruction, the displacement is specified as immediate data or as the contents of a register. All effective addresses are computed as 32-bit quantities. See Chapter 3 for more information on addressing.

## **Data Representation in Registers**

The 032 Microprocessor has sixteen 32-bit general purpose registers and sixteen system control registers.

## **General Purpose Registers**

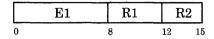

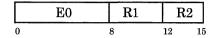

Instructions are provided to load or store a single character, word, or halfword into a *general purpose register* (GPR).

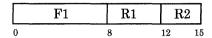

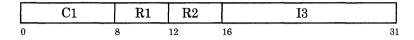

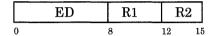

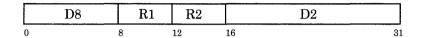

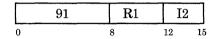

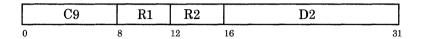

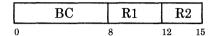

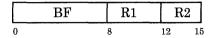

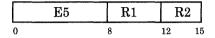

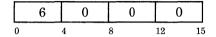

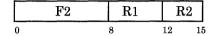

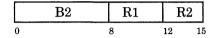

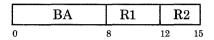

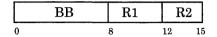

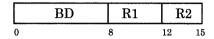

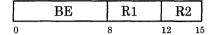

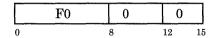

Each GPR consists of an upper and lower half of sixteen bits each. Each GPR may be separated into four eight-bit characters: C0, C1, C2, and C3. The organization of General Purpose Registers is shown in Figure 1-1 on page 1-5.

For computational purposes, the content of a GPR is treated as a signed algebraic quantity, an unsigned positive quantity, or an unstructured logical quantity, depending on the instruction that does the computation. In a GPR, an algebraic quantity is represented by 32 bits in two's complement form.

Since each register is 32 bits long, the largest positive signed number that can fit in a register is decimal 2<sup>31</sup> - 1. The largest negative number that can fit in a register is -2<sup>31</sup>. Numbers larger than these are wrapped around. (See "Arithmetic Constants" on page 2-16.)

GPRs are manipulated by most of the instructions in the 032 Microprocessor instruction set. For information about what these instructions are and how they affect GPRs, see Chapter 4.

To avoid the destruction of operands, the following instructions cause the result of the operation to be placed in the pair of one of the GPR operands:

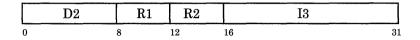

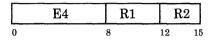

The pair of a given GPR has the name, in binary, of the given GPR with the low-order bit inverted. In this way, a pair consists of an even-numbered and an odd-numbered register. For example, GPR 5 (binary 0101) and GPR 4 (binary 0100) are pairs, and GPR 14 (binary 1110) and GPR 15 (binary 1111) are pairs. (See Figure 1-2.)

| 0 3 | 1 bits |     |      |

|-----|--------|-----|------|

|     | GPR 1  | 5   | pair |

|     | GPR 1  | 4   | nair |

|     | GPR 1  | 3   | pair |

|     | GPR 1  | 2   | pair |

|     | GPR 1  | 1   | pair |

|     | GPR 1  | 0   | ngir |

|     | GPR 9  | )   | pair |

|     | GPR 8  | 3   | pair |

|     | GPR 7  | 7   | pair |

|     | GPR 6  | 3   | nair |

|     | GPR 5  | 5   | puir |

|     | GPR 4  | ļ _ | pair |

|     | GPR 3  | 3   | pull |

|     | GPR 2  | 2   | pair |

|     | GPR 1  |     | pair |

|     | GPR C  | )   | nair |

Figure 1-2. General Purpose Register Pairs

## **System Control Registers**

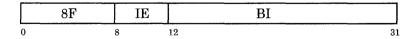

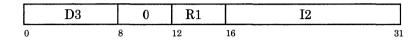

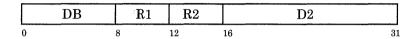

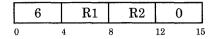

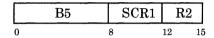

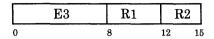

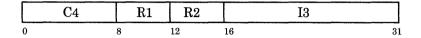

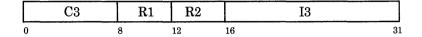

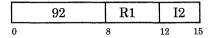

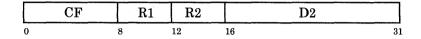

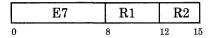

The 032 Microprocessor has sixteen 32-bit system control registers (SCRs). An entire SCR or fields within an SCR are generally set aside to be used by programs that control the system. Figure 1-3 on page 1-8 shows the different SCRs.

Some SCRs and bits inside SCRs are reserved and are not assigned to any system facility. Any attempt to set the reserved bits of an SCR will be ignored. When the reserved bits of an SCR are fetched, the resulting values are unpredictable.

| Reser<br>Reser               | SCR 3 |        |        |

|------------------------------|-------|--------|--------|

| Reser                        | SCR 5 |        |        |

| Counter Source               |       |        | SCR 6  |

| Counter                      |       |        | SCR 7  |

| Reserved                     | TS    | SCR 8  |        |

| Reserved                     |       |        | SCR 9  |

| Multipler Quotient           |       |        | SCR 10 |

|                              | MSC   | PCS    | SCR 11 |

| Reserved                     | IRB   |        | SCR 12 |

| Instruction Address Register |       |        | SCR 13 |

| Reserved                     | I     | SCR 14 |        |

| Reserved                     |       | SCR 15 |        |

0 8 16 24 31

TS = Timer Status IRB = Interrupt Request Buffer MCS = Machine Check Status ICS = Interrupt Control Status

Figure 1-3. System Control Registers

The SCRs can be manipulated with certain privileged instructions. (See "System Control Register Manipulation Instructions" on page 4-20.) Two of the SCRs can also be manipulated in unprivileged state: Multiplier Quotient (SCR 10) and Condition Status (SCR 15). The Instruction Address Register (SCR 13) cannot be directly manipulated in unprivileged state, but is affected by assembler instructions.

The following descriptions apply to SCRs in hardware. Virtual machines do not have hardware SCRs, but they have analogous virtual machine control registers. See Virtual Resource Manager Technical Reference for information about how virtual machines define virtual machine control registers.

Note: The processor dynamically changes SCRs, often asynchronously to instruction sequencing. Therefore, if you write to an SCR, then read from the same SCR, you may not read back the same data that you wrote in.

## Counter Source, Counter, and Timer Status Registers

SCRs 6 and 7 and the TS bits of SCR 8 help control the system timer. For more information on SCRs 6 and 7, see Hardware Technical Reference. For more information on SCR 8, see Virtual Resource Manager Technical Reference.

## Multiplier Quotient (MQ) Register

The MQ register holds the product of the Multiply Step (m) instruction or the dividend of the Divide Step (d) instruction. You can also manipulate the contents of the MQ register with the Move to SCR (mts) and Move From SCR (mfs) instructions. For more information about these instructions, see Chapter 4.

Note: The MQ is not preserved across subroutine calls. See "Subroutine Linkage and System Calls" on page 6-10 for more information.

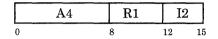

#### Machine Check Status (MCS)

The Machine Check Status occupies bits 16 through 23 of SCR 11. When a machine check error is detected by hardware, appropriate bits of the MCS are set to one. You cannot clear a Machine Check Level by clearing the bits in the MCS, nor can you cause a Machine Check by writing to the MCS. The MCS is only cleared when a Load Program Status (lps) instruction is executed to return from a Machine Check Level. The MCS includes the following bits:

- Processor channel check

- Parity check

- Instruction timeout

- Data timeout

- Processor channel timeout

- I/O trap.

For more information, see Hardware Technical Reference.

## **Program Check Status (PCS)**

The Program Check Status occupies bits 24 through 31 of SCR 11. The PCS provides a means for reporting the following programming errors:

- Program check with known origin

- Program check with unknown origin

- Program trap (bit 26)

- Privileged instruction exception

- Illegal op code

- Instruction address exception

- Data address exception.

Upon detection of a program check error, all bits of the PCS are cleared to zeroes. The appropriate bits of the PCS are then set to ones. You cannot clear a Program Check Level by clearing the bits in the PCS, nor can you cause a Program Check by writing to the PCS.

For more information, see *Hardware Technical Reference*.

## Interrupt Request Buffer (IRB)

Bits 16 through 31 of SCR 12 are the Interrupt Request Buffer. The IRB allows different levels of interrupt requests to be generated under program control. The interrupt request remains active until the bit is cleared by software.

For more information, see Hardware Technical Reference.

## Instruction Address Register (IAR)

The Instruction Address register, sometimes called the instruction pointer or program counter, contains the address of the next instruction to be executed. During instruction execution, the IAR is incremented, in bytes, by the length of the current instruction. If this instruction is a successful branch, the IAR is set to the address of the branch target instruction.

In privileged state, programs can use the Move to System Control Register (mts) instruction to load the IAR with a specified value. Application programs, however, can only change the contents of the Instruction Address register implicitly, by executing instructions.

Do not confuse the IAR with the assembler's location counter. See "The Location Counter" on page 3-11.

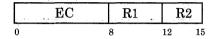

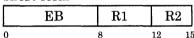

#### Interrupt Control Status (ICS)

Bits 16 through 31 of SCR 14 are the Interrupt Control Status. Bits 0 through 15 of SCR 14 are reserved. In hardware, the ICS contains the following defined bits:

- Parity error retry interrupt enable

- Storage protect

- Problem state

- Translate mode

- Interrupt mask

- Check stop mask

- Register set number

- Processor priority.

For more information on the ICS, see Hardware Technical Reference.

## Condition Status (CS) Register

Bits 16 through 31 of SCR 15 are the Condition Status register. However, only bits 24 through 31 are defined. Bits 0 through 23 in SCR 15 are reserved.

You can manipulate the entire contents of the CS register with the Move to System Control Register (mts) and the Move from System Control Register (mfs) instructions.

You can manipulate any single bit in the CS register with the Set Bit in the System Control Register (setcb) and Clear Bit in the System Control Register (clrcb) instructions.

The following instructions allow you to test any single CS bit, then branch or not branch, depending on the value of that bit:

- Branch on Condition Bit (**bb**)

- Branch on Condition Bit Using Register (bbr)

- Branch on Condition Bit with Execute (bbx)

- Branch on Condition Bit Using Register with Execute (bbrx)

- Branch on Not Condition Bit (bnb)

- Branch on Not Condition Bit Using Register (bnbr)

- Branch on Not Condition Bit with Execute (bnbx)

- Branch on Not Condition Bit Using Register with Execute (bnbrx).

Other instructions can test or set only one pre-defined bit in the CS register.

Bits 24 through 31 of the Condition Status register are defined as follows:

| $\operatorname{Bit}$ | 24        | Permanent Zero (PZ |

|----------------------|-----------|--------------------|

| $\operatorname{Bit}$ | 25        | Less Than (LT)     |

| $\operatorname{Bit}$ | <b>26</b> | Equal (EQ)         |

| $\operatorname{Bit}$ | 27        | Greater Than (GT)  |

| Bit                  | 28        | Carry Zero (C0)    |

| Bit                  | 29        | Reserved           |

| $\operatorname{Bit}$ | 30        | Overflow (OV)      |

| Bit                  | 31        | Test Bit (TB).     |

The Permanent Zero (PZ) bit is always set at zero; it cannot be set to one. The PZ bit is tested by the Branch (b) instruction.

The Less Than (LT) bit is set during the Compare (c) instruction to indicate the relative algebraic magnitudes of the numbers being compared. The LT bit is also set to one during logical, shift, and certain arithmetic instructions if the result of the instruction is negative or if the high-order bit of the result is one. Otherwise, LT is set to zero. The LT bit is tested by the Branch on Less Than (blt) and Branch on Greater Than or Equal (bge) instructions.

The Equal (EQ) bit is set during the Compare (c) instruction to indicate if comparands are equal. The EQ bit is also set to one during logical, shift, and certain arithmetic instructions if all bits of the result are zeros; otherwise it is set to zero. The EQ bit is tested by the Branch on Equal (beg) and Branch on Not Equal (bne) instructions.

The Greater Than (GT) bit is set during the Compare (c) instruction to indicate the true relative algebraic magnitudes of the comparands. The GT bit is also set to one during logical, shift, and certain arithmetic instructions if the sign bit of the result is zero and the result is non-zero. The GT bit is tested by the Branch on Greater Than (bgt) and Branch on Less Than or Equal (ble) instructions.

The Carry Zero (C0) bit is set to one during certain arithmetic instructions if the operation generates a carry out of a bit position zero; otherwise it is set to zero. The C0 bit is tested by the Branch and Carry Bit Set (bcs) and Branch and Carry Bit Clear (bcc) instructions.

The Overflow (OV) bit is set to one during certain arithmetic instructions if the signed result of the operation cannot be represented in 32 bits; otherwise it is set to zero. The OV bit is tested by the Branch on Overflow Set (bvs) and Branch on Overflow Clear (bvc) instructions.

The Test (TB) bit is set by the Move to Test Bit instructions (mttb and mttbi), where a specified bit of a register is moved to the test bit. It is also affected by instructions which load or directly alter data in the Condition Status register. The TB bit is tested by the Branch on Test Bit Set (bts) and Branch on Test Bit Clear (btc) instructions.

# Chapter 2. Assembler Language Concepts

## **CONTENTS**

| inout imp chapter                                      | 2-3 |

|--------------------------------------------------------|-----|

| Notational Conventions 2                               | 2-4 |

|                                                        | 2-5 |

|                                                        | 2-7 |

|                                                        | 2-8 |

|                                                        | 2-9 |

| Instruction Statements and Pseudo-Operation Statements | 2-9 |

| Null Statements 2-                                     |     |

| Symbols                                                | 13  |

| Defining a Symbol with a Label                         | 14  |

| Defining a Symbol with a Pseudo-op 2-                  | 14  |

| Using A Symbol Before Defining It 2-                   | 15  |

| Constants                                              | 16  |

| Arithmetic Constants 2-                                | 16  |

| Character Constants                                    | 17  |

| Symbolic Constants 2-                                  | 17  |

| Expressions                                            | 18  |

| Operators and Operator Precedence 2-                   | 18  |

| Types of Expressions                                   | 20  |

## **About This Chapter**

This chapter explains the syntax and semantics of 032 Microprocessor assembler language. It tells you what you need to know to write a single line of 032 Microprocessor assembler language code.

The following topics are discussed:

- Notational conventions used to describe syntax

- Character set

- Reserved words

- Line format

- Components of a statement

- Kinds of statements

- Symbols

- Constants

- Operators and expressions.

For information on combining lines of 032 Microprocessor assembler language code (addressing, segmenting, the location counter), see Chapter 3.

## **Notational Conventions**

Throughout this chapter, certain notational conventions describe aspects of the 032 Microprocessor assembler language.

- All spaces are required unless otherwise noted.

- In commands, capitalization is significant. All uppercase and lowercase letters should be entered exactly as shown.

- Optional parts of statements are shown in brackets. However, you do not type the brackets themselves. For example,

```

mnemonic operand1[,operand2]

means that you can type

mnemonic operand1 or

mnemonic operand1, operand2.

```

Brackets can be nested. For example, mnemonic [operand1[,operand2]] means that you can type mnemonic or mnemonic operand1 or mnemonic operand1, operand2.

## Character Set

All letters and numbers are allowed. However, the assembler discriminates between upper-case and lower-case letters. For example, the assembler sees the symbol Name as being different from the symbol name.

Some blank spaces are required; others are optional. (See "Statements" on page 2-9.) The assembler allows you to substitute tabs for spaces.

The following characters have a special meaning in 032 Microprocessor assembler language:

#### , (comma)

Operand separator. Commas are allowed only between operands. (See "Statements" on page 2-9.)

Example:

1r 2,15

#### # (pound sign)

Comments. Anything from # to the end of a line is a comment and is ignored by the assembler. A # can be the first character in a line, or it may be preceded by any number of characters, blank spaces, or both. (See "Comments" on page 2-11.)

#### Example:

```

# loads register 2 with contents

lr 2.15

# of register 15

```

#### : (colon)

Defines a label equal to the value contained in the current location counter. Always appears immediately after the last character of the label name. (See "Labels" on page 2-10.)

#### Example:

```

here: 1r 2,15 # makes here equal to the address

# where the 1r instruction is assembled

```

#### ; (semicolon)

Instruction separator. A semicolon separates two instructions that appear on the same line. Spaces around the semicolon are optional.

A single instruction on one line does not have to end with a semicolon.

#### Example:

```

1r 2,15

1r 15,3

# these two lines have

# the same effect as...

lr 2,15 ; lr 15,3 # ...this line

```

#### \$ (dollar sign)

Refers to the current value of the assembler's current location counter. (See "The Location Counter" on page 3-11.)

#### Example:

```

.long 1,2,3

.long $ - dino

dino:

size:

```

## **Reserved Words**

032 Microprocessor assembler language does not have any reserved words. The mnemonics for instructions and pseudo-ops are not reserved; they may be used in the same way as any other symbols.

There may be restrictions on the names of symbols that are passed to programs written in other languages. For information on these restrictions, see "Subroutine Linkage and . System Calls" on page 6-10.

## **Line Format**

On the RT PC, 032 Microprocessor assembler language is written in free format. There are no requirements for certain things to be in any particular column position.

The assembler language puts no limit on the number of characters that can appear on a single input line. If you write a longer code line than can display as one line on your terminal, line wrapping will depend on the editor you are using.

Blank lines are allowed; the assembler ignores them.

## **Statements**

032 Microprocessor assembler language has three kinds of statements: instruction statements, pseudo-operation statements, and null statements.

## **Instruction Statements and Pseudo-Operation Statements**

An instruction or pseudo-op statement has the following syntax:

[label: |mnemonic[ operand1[,operand2]] [#comment]

The assembler recognizes the end of a statement when one of the following occurs:

- An ASCII newline character

- A comment character (#)

- A semicolon (;).

## **Separator Character**

The separator characters are spaces, tabs, and commas. Commas separate operands. Spaces or tabs separate the other parts of a statement. A tab can be used wherever a space is shown in this book.

The spaces shown are required spaces. You can optionally put one or more spaces after a comma, before a pound sign (#), and after a #.

#### Labels

The label entry is optional. A line may have zero, one, or more labels. A line may have a label but no other contents.

To define a label, follow a symbol with a colon. The assembler gives the label the value contained in the assembler's current location counter. This value represents a relocatable address.

See "Symbols" on page 2-13 for information on defining symbols.

#### Example 1

```

here: 1r 2.15

# the label here receives a value

# of the address of the lr instruction.

# You can now use here in subsequent statements

# to refer to this address.

```

If the label is in a statement with an instruction that causes data alignment, the label receives its value before the alignment occurs.

#### Example 2

```

# assume that the location counter now

# contains the value of 98

place: .long expr

# When the assembler sees this statement, it

# sets place to address 98. But the

# .long is a pseudo-op that

# aligns expr on a fullword.

# the assembler puts expr at the next

# available fullword boundary, which is

# address 100. In this case place is

# not actually the address at which expr

# is stored; referring to place will not

# put you at the location of expr.

```

#### **Mnemonics**

The mnemonic field identifies whether a statement is an instruction statement or a pseudo-op statement. Each mnemonic requires a certain number of operands in a certain format.

For an instruction statement, the mnemonic field contains an abbreviation like ais or beq. This mnemonic describes an operation where the 032 Microprocessor processes a single machine instruction, which is associated with a numerical op code. Instructions vary in length, so the op code tells the assembler how long the instruction and its operands are going to be. When the assembler encounters an op code, the assembler increments the location counter by the required number of bytes.

For a pseudo-op statement, the mnemonic represents an instruction to the assembler program itself. There is no associated op code, and the mnemonic does not describe an operation to the processor. Some pseudo-ops increment the location counter; others do not.

#### **Operands**

The existence and meaning of the operands depends on the mnemonic used. Some mnemonics do not require any operands. Other mnemonics require one or more operands.

The assembler interprets each operand in context with the operand's mnemonic. Many operands are expressions that refer to registers or symbols. For instruction statements, operands can be immediate data that is to be directly assembled into the instruction.

#### Comments

Comments are optional and are ignored by the assembler. Every line of a comment must be preceded by a pound sign (#); there is no other way to designate comments.

#### **Null Statements**

A null statement does not have a mnemonic or any operands. It can contain a label, a comment, or both. Processing a null statement does not change the value of the location counter.

Null statements are useful mainly to make assembler source code easier for people to read.

A null statement has the following syntax:

```

[label:]

[#comment]

```

The spaces between the label and the comment are optional.

If the null statement has a label, the label receives the value of the next statement, even though that statement is on a different line. For example,

```

here:

cal16 3,'X

```

has the same effect as

here: cal16 3,'X

Note: Certain pseudo-ops may prevent a null statement's label from receiving the value of the next statement. See Example 2 on page 2-10.

## **Symbols**

A symbol is a single character or combination of characters used as a label or operand. Symbols may consist of numeric digits, underscores, periods, upper or lower case letters, or any combination of these. The symbol cannot contain any blanks or special characters. and cannot begin with a digit. Upper and lower case are distinct.

From the assembler and loader's perspective, the length of a symbol name is limited only by the amount of storage you have. However, only the first 32 characters are significant. Also note that other routines linked to assembler language files may have their own constraints on symbol length.

You can use a symbol to represent storage locations or arbitrary values. The value of a symbol is always a 32-bit quantity.

The following are examples of valid symbol names:

```

READER

A2345

result.a

resultA

balance old

_label9

.myspot

```

The following are examples of invalid symbol names:

```

7 - sum

(begins with a digit)

#ofcredits

(contains #, a special character)

aa*1

(contains *, a special character)

IN ARFA

(contains a blank)

```

You can define a symbol by using it in one of two ways:

- As a label for an instruction or pseudo-op

- As the **name** operand of a .set, .comm, or .lcomm pseudo-op.

### Defining a Symbol with a Label

You can define a symbol by using it as a label.

Example:

bali 1,cont

.using \$,1

dataval: .short 10

.

cont: 1h 2,dataval a 4,2

The assembler gives the symbol the value of the location counter at the instruction or pseudo-op's leftmost byte. In the example above, the object code for the lh instruction contains the location counter value for dataval.

At runtime, this value represents an address, and the contents of that address are used as an operand. In the example above, the **lh** instruction uses the 16 bits of data stored at **dataval**'s address.

Note that the value referred to by the symbol actually occupies a memory location. A symbol defined by a label is a relocatable value.

The symbol itself does not exist at runtime. However, you can change the value at the address represented by a symbol at runtime, if some code changes the contents represented by **dataval**.

### Defining a Symbol with a Pseudo-op

You can also define a symbol by using it as the **name** operand of a .set pseudo-op. This pseudo-op has the format .set name, exp. For example:

.set number,10 ... ais 4,number

The assembler evaluates the **exp** operand, then assigns the value and type of **exp** to the symbol **name**. When the assembler encounters that symbol in an instruction, the assembler puts the symbol's value into the instruction's object code. In the example above, the object code for the **ais** instruction contains the value assigned to **number**, that is, 10.

Note that the value of the symbol is assembled directly into the instruction, and does not occupy any storage space. A symbol defined with a .set can have an absolute or relocatable type, depending on the type of the exp operand. (See "Types of Expressions"

on page 2-20.) Also, you cannot change the value of the symbol at runtime; you must reassemble the file in order to give the symbol a new value.

You can also define a symbol by using it as the name operand of a .lcomm or .comm pseudo-op. In this case, the value assigned to the symbol does occupy storage space; see Chapter 5.

## Using A Symbol Before Defining It

It is possible to use a symbol before you define it. Using a symbol, and then defining it later in the same file, is called forward referencing. In other words, the following is acceptable:

1 5, ten

ten: .long 10

If the symbol is not defined in the file in which it occurs, it is called an external symbol. When the assembler finds external symbols, it does not give you an error message; it assumes that you will link in another file that defines the symbol.

For branch instructions only, the symbol and its definition must be, after linking, in the same runtime segment as all references to that symbol. (See Chapter 3 for information about runtime segments and their relation to assembler language sections.)

The only exception is for symbols that have been the subject of a .direct pseudo-op, which allows you to make a direct reference to an external symbol. If you use .direct, the symbol you refer to must occupy an address in the lowest 32K of memory at link time.

#### **Constants**

The 032 Microprocessor assembler language has three kinds of constants:

- Arithmetic constants

- Character constants

- Symbolic constants (symbols being used as constants).

When the assembler encounters an arithmetic or character constant that is being used as an instruction's operand, the value of that constant is assembled into the instruction. (This is why arithmetic and character constants are sometimes called self-defining terms.) When the assembler encounters a symbol being used as a constant, the value of the symbol is assembled into the instruction. (Symbolic constants are sometimes called data constants or ordinary symbols.)

The assembler eventually translates all constants, no matter how they are specified, into 32-bit integer constants.

#### **Arithmetic Constants**

There are three kinds of arithmetic constants: decimal, octal, and hexadecimal.

Because the 032 Microprocessor is a 32-bit processor, the largest signed positive number that any single register can hold is the decimal value  $2^{31}$ -1. The largest negative value allowed in a register is  $-2^{31}$ . If you specify an expression that evaluates to a constant with a value larger then these, the value wraps around at runtime. For example,

0x7FFFFFF8 + 0x14

yields a value of 0x8000000C (a large negative number).

The largest unsigned number that any single register can hold is  $2^{32}$ -1. For unsigned numbers, wraparound works like this:

0xFFFFFFFF8 + 0x14

yields a value of 0x0000000C.

#### **Decimal Constants**

Base 10 is the default base for arithmetic constants. If you want to specify a decimal number, just type the number in the appropriate place.

ai 5,10 # adds decimal value 10 to contents of GPR 5

Do not prefix decimal numbers with a zero. A leading zero denotes an octal number.

#### **Octal Constants**

To specify an octal number, prefix the number with the numeral 0.

```

ai 5.0377 # adds octal value 377 to contents of GPR 5

```

#### **Hex Constants**

To specify a hexadecimal number, prefix the number with **0X** or **0x**. You can use either uppercase or lowercase for the hex numerals A through F.

```

ais 5.0xF # adds hex value F to GPR 5

ais 3.0X5 # adds hex value 5 to GPR 3

```

#### **Character Constants**

To specify an ASCII character constant, prefix the constant with a ' (single quote mark). Character constants can appear anywhere an arithmetic constant is allowed, but you can only specify one character constant at a time. For example, 'A represents the ASCII code for the character A.

Character constants are convenient when you want to use the code for some character as a constant. For example,

```

call6 3,'X # Loads GPR 3 with the ASCII code for

# the character X (that is, hex 58).

# After the call6 instruction

# executes. the low-order 16 bits of

# GPR 3 contain

# binary 0000 0000 0101 1000.

```

#### Symbolic Constants

All symbols do not have to be used as constants. However, 032 Microprocessor assembler language allows you to use a symbol as a constant. Once you define a value, you can refer to that value by name, instead of using the value itself.

Using a symbol as a constant is convenient if you have a value that occurs frequently in your program. You define the symbolic constant once, by giving the value a name. If you decide to change the value, you only have to change its definition, not every reference to it in the program.

A symbolic constant can be defined by using it as a label or by using it in a .set statement. "Symbols" on page 2-13 discusses how to define symbols.

## **Expressions**

An expression is a constant, a symbol, or a combination of constants, symbols, and operators. The assembler evaluates each expression into a single value, then uses that value as an operand. Expressions have a type as well as a value.

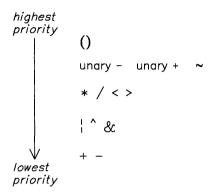

### **Operators and Operator Precedence**

032 Microprocessor assembler language allows the following operators:

- () control order of evaluation

- addition or unary +

- subtraction or unary two's complement

- multiplication

- division

- logical and

- inclusive or

- exclusive or

- logical left shift

- logical right shift

- unary bitwise complement

All these operators evaluate left to right, except for the unary operators, which evaluate right to left.

Operator precedence is as follows:

All the operators perform 32-bit signed integer operations.

The division operator, /, produces an integer result; the remainder has the same sign as the dividend. For example,

#### Operation Result

| 8/3       | <b>2</b> |

|-----------|----------|

| 8/-3      | -2       |

| (-8)/3    | -2       |

| (-8)/(-3) | 2        |

The left shift (<) and right shift (>) operators take an integer bit value for the right-hand operand. For example,

```

.set mydata,1

.set newdata,mydata<2 # shifts 1 left 2 bits,</pre>

# assigns result to newdata

```

### **Types of Expressions**

There are three types of expressions: absolute, relocatable, or external. The type of an expression depends on the type of its operands.

Expression types are important for two reasons. First, some pseudo-ops and instructions require expressions of a particular type. Second, only certain operators are allowed in certain types of expressions, as described below.

In the explanations below, "absolute" recursively refers to an absolute expression, and "relocatable" recursively refers to a relocatable expression. "A symbol set to ..." means a symbol that has appeared in a .set statement (.set name, ...).

#### **Absolute Expressions**

The value of an absolute expression is independent of any possible code relocation. The value of an absolute expression stays the same, no matter where the runtime segment containing the expression is loaded.

Absolute expressions must be one of the following:

- An integer or character constant

- A symbol set to an absolute

- absolute < operator > absolute , where < operator > is any arithmetic binary operator

- absolute

- ~absolute

- relocatable relocatable, where the two "relocatables" refer to the same assembler section.

The definitions of "absolute" and "relocatable" above are recursive. For example, absolute < operator > relocatable - relocatable is a valid absolute expression.

Any expression not covered by the above rules is invalid. An example of an invalid absolute expression is relocatable + relocatable.

#### **Relocatable Expressions**

The value of a relocatable expression depends on the location of the runtime segment containing the relocatable expression. If the runtime segment moves to a different storage location, the value of the relocatable expression changes accordingly.

Since the runtime segments can be relocated independently, the type of a relocatable expression includes the runtime segment. (See "Assembler Sections and Runtime Segments" on page 3-9.)

Relocatable expressions must be one of the following:

- A label

- A symbol set to a relocatable expression

- relocatable + absolute

- relocatable absolute

- absolute + relocatable.

The definitions of "absolute" and "relocatable" above are recursive. For example, absolute + (relocatable + absolute) is a valid relocatable expression.

Any expression not covered by the above rules is invalid. Examples of invalid relocatable expressions are relocatable\*absolute. absolute - relocatable.

All expressions that are based on the location counter are relocatable (for example, those used as operands for the **bnb** instruction and related instructions).

The final resolution of the value represented by a relocatable expression is performed at load time by ld.

#### **External Expressions**

External expressions refer to external symbols (symbols not defined in the current file).

If the external expression is used as a label, the expression is relocatable. An external expression cannot be used as the subject of a .set.

External expressions must be one of the following, where "external" refers to an external expression:

- A symbol declared .comm

- Any symbol not otherwise defined

- external + absolute

- external absolute

- absolute + external.

The definitions of "absolute" and "external" above are recursive. For example, absolute + (external + absolute) is a valid external expression.

Any expression not covered by the above rules is invalid. Examples of invalid external expressions are external+relocatable, absolute - external.

# Chapter 3. Addressing and Program Sectioning

## CONTENTS

| bout This Chapter 3                    | -3 |

|----------------------------------------|----|

| ddressing                              | -4 |

| Absolute Immediate Addresses           | -4 |

| Absolute Addresses                     | -4 |

| Relative Immediate Addresses           | -5 |

| Based Addresses                        | -5 |

| Special Addresses                      | -7 |

| ssembler Sections and Runtime Segments | -9 |

| The Text Section and Text Segment      | -9 |

| The Data Section and Data Segment      | 10 |

| The Bss Section in the Data Segment    |    |

| The Location Counter                   |    |

## **About This Chapter**

This chapter explains some things you need to know to combine lines of 032 Microprocessor assembler language code.

The first part of the chapter discusses addressing, base registers, the .using and .drop pseudo-ops, and addresses with a special meaning. The second part of the chapter discusses assembler language sections, the assembler's location counter, and how assembler language sections map to runtime segments in the executable object file.

## Addressing

Some addresses are already occupied by code that controls the RT PC system. These special addresses are discussed on page 3-7.

The 032 Microprocessor supports four basic kinds of addressing modes:

- Absolute immediate

- Absolute

- Relative immediate

- Based (short and long).

Since the first three addressing modes are used only by branch instructions, these modes are also discussed in "Branch Instructions" on page 4-9.

#### **Absolute Immediate Addresses**

An absolute immediate address is designated by immediate data. This addressing mode is absolute in the sense that it is not specified relative to the IAR.

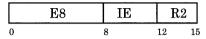

On the 032 Microprocessor, only the bala and balax instructions have an absolute immediate addressing mode. These instructions assemble a 24-bit immediate operand which is extended on the left with eight binary zeroes to become the branch target address. The immediate operand can be an absolute, relocatable, or external expression.

#### Absolute Addresses

An absolute address is represented by the contents of a register. This addressing mode is absolute in the sense that it is not specified relative to the IAR.

On the 032 Microprocessor, the absolute addressing mode is used by the instructions bbr[x], bnbr[x], extended branch instructions with the same op codes as these, and balr[x]. These instructions have a register as an operand; the contents of this register become the branch target address. The contents of the register can be determined by a relocatable, absolute, or external expression.

#### **Relative Immediate Addresses**

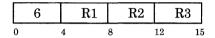

Relative immediate addresses are specified as immediate data within the object code, and are calculated relative to the IAR. On the 032 Microprocessor, all the instructions that use relative immediate addressing are branch instructions; **bb[x]**, **bnb[x]**, extended branch instructions with the same op codes as these, and bali[x]. These instructions have immediate data which is the displacement in halfwords from the current IAR. At execution, the immediate data is sign extended, logically shifted left one bit, and added to the address of the branch instruction to calculate the branch target address.

Relative immediate addresses are specified with either a 20-bit immediate field or an 8-bit immediate field, depending on the instruction. (See Chapter 4 for details.)

#### **Based Addresses**

In this book, the instructions that allow based addresses have a D2(R2) operand. (The 2's indicate the second operand in an instruction.) Some instructions require D2 to have a value that can be contained in 4 bits. Other instructions require **D2** to have a value that can be contained in 16 bits.

If an instruction does not have an operand of the form **D2(R2)**, then you cannot specify a based address for that instruction.

There are two ways to specify based addresses: explicitly, or implicitly.

#### **Explicit Based Addresses**

You write an explicit based address by specifying a base register number, (R2), and a displacement, D2 (also called an offset). The base register holds a base address. At runtime, the processor adds the displacement to the contents of the base register to obtain the effective address.

You must use an absolute expression to specify the base register itself. However, the contents of the base register can be specified by an absolute, relocatable, or external expression. If the base register holds a relocatable value, the effective address is relocatable. If the base register holds an absolute value, the effective address is absolute. If the base register holds a value specified by an external expression, the type of the effective address is absolute if the expression is eventually defined as absolute, and relocatable if the expression is eventually defined as relocatable.

The storage instructions have short and long forms, where **D2** can be either 4 or 16 bits. The assembler attempts to use a short form of a data reference wherever it can to save space. It only does so if it can determine the displacement in pass 1, that is, when the operand is an explicit based expression with a constant positive displacement.

#### Notes:

- 1. GPR 0 cannot be used as a base register. Specifying 0 tells the assembler not to use a base register at all.

- 2. Since **D2** occupies 16 bits at most, the maximum positive displacement is 2<sup>15</sup> 1, and the maximum negative displacement is 215. Therefore, the difference between the base address and the address of the item to which reference is made must be less than 215 bytes.

#### Implicit Based Addresses (.using and .drop)

To specify an implicit based address as an operand for an instruction, omit the (R2) operand and write the .using pseudo-op at some point before the instruction. After assembling the appropriate .using and .drop pseudo-ops, the assembler knows the register to use as the base register. At runtime, the processor computes the effective address, just as if you had explicitly specified the base in the instruction.

Implicit based addresses can be relocatable or absolute, depending on the type of expression used to specify the contents of R2 at runtime. Usually you specify the contents of **R2** with a relocatable expression, thus making a relocatable implicit based address. In this case, when the object module produced by the assembler is relocated, only the contents of the base register will change. The displacement remains the same, so D2(R2) still points to the correct address after relocation.

However, you can make an absolute implicit based address by specifying the contents of R2 with an absolute expression. In this case, R2 will not change when the object module is relocated.

In order to specify an implicit address, you must:

- 1. Write a .using statement to tell the assembler that one or more GPRs will now be used as base registers.

- 2. In this .using statement, tell the assembler the value each base register will contain at execution. Until it encounters a .drop, the assembler will use this base register value to process all instructions that require a based address.

- 3. Load each base register with the value you said it would have.

When you omit the (R2) operand, the D2 operand remains. D2 is a label or an expression containing a label.

**Note:** The .using and .drop pseudo-ops affect only based addresses.

Example of Implicit Based Addressing

```

.data

foo: .long 2,3,4,5,6

bar: .long 777

.text

.align 2

bali 10, yee

.long foo

yee: 110.0(10)

.using foo, 10 # now you only need to

# specify displacement

1 0, foo

# the assembler generates 10,0(10)

1 1, foo+4

# the assembler generates 11.4(10)

1 2,bar

# the assembler generates 12,20(10)

```

### Special Addresses

In virtual memory, user-made programs are always stored at hex addresses 1000 0000 or higher. However, this fact is not apparent to 032 Microprocessor assembler programs. because these programs are normally relocatable. You don't have to worry about referencing special memory locations (for example, the addresses occupied by the operating system).

The exceptions are for:

- Targets of an absolute branch-and-link instruction (bala or balax)

- Instructions covered by a .direct pseudo-op

- The .org pseudo-op when it has an absolute expression for an operand

- The load and store instructions (especially the store instructions st. stc. sth. and stm).

In these cases, you can specify addresses representing special memory locations that normally hold important pieces of code (i.e. the kernel). These addresses are not strictly reserved—you can reference them by using the appropriate instructions—but they are special in the sense that ordinary applications programs avoid them.

If you use .direct, an absolute .org, or an absolute immediate branch instruction (probably for AIX Operating System kernel programming), you need to know about special addresses. Figure 3-1 shows how virtual memory is laid out, and implies the addresses user programs must avoid.

| Segment<br>Register | Hex Addresses                  | Purpose                                                           |

|---------------------|--------------------------------|-------------------------------------------------------------------|

| 0                   | 0000 0000 through<br>0FFF FFFF | holds AIX Operating System kernel                                 |

| 1                   | 1000 0000 through<br>1FFF FFFF | holds program text                                                |

| 2                   | 2000 0000 through<br>2FFF FFFF | holds program data                                                |

| 3                   | 3000 0000 through<br>3FFF FFFF | holds the stack                                                   |

| 4 through 13        | 4000 0000 through<br>DFFF FFFF | holds shared data segments                                        |

| 14                  | E000 0000 through<br>EFFF FFFF | reserved by Virtual Resource Manager for direct memory access I/O |

| 15                  | F000 0000 through<br>FFFF FFFF | used to map I/O bus                                               |

Figure 3-1. Segment registers and their contents

Note: Programs must not access locations in the stack segment that are below the stack floor. See "The Stack Floor" on page 6-14.

## **Assembler Sections and Runtime Segments**

An 032 Microprocessor assembler language file may have up to three sections, which are specified with pseudo-ops:

- Text (for instructions)

- Data (for initialized data)

- Bss (for uninitialized data).

When you assemble a program with as or link edit a program with ld, the output goes into an object file called, by default, a.out. This executable object module has a fixed format. with segments that correspond to the text and data sections declared within an assembly language file. Assembler language sections are thus represented at runtime by a.out segments.

When the linker links two or more assembly language files, the linker puts the assembler sections together in the order required by the a.out format, even if parts of a section came from different files.

Sectioning may also be convenient for assembly language programmers. Without sectioning, you must write all the instructions in one chunk, and then write all the data. With sectioning, you can write instructions, data, then more instructions.

The text and data assembler language sections each have four location counters. These allow you to divide any section into up to four parts. You can specify the location counter with pseudo-ops. (See "The Location Counter" on page 3-11.)

#### Notes:

- 1. The branch instructions only allow branching within a segment, not branching between segments. (See "Branch Instructions" on page 4-9.)

- 2. For more information on a.out, including the use of segment registers to locate information in memory, see AIX Operating System Technical Reference.

## The Text Section and Text Segment

The assembler text section holds the instruction and pseudo-op statements that control the program's execution. By default, the assembler assumes .text 0, but you can explicitly declare the text section in the assembler source code by using the .text pseudo-op.

The linked text sections of the assembly language file become the text segment of the executable a.out file.

#### Notes:

- 1. If the .direct pseudo-op occurs in the source program, the assembler assumes that the program's text segment will be linked in the lowest 32K of address space. This feature may help kernel programmers by allowing 16-bit direct addresses to be used for text section references not covered by .using statements. (See "Special Addresses" on page 3-7.)

- 2. If you want your program to include traceback information for debuggers such as sdb. the text section must end with certain lines of assembler language code. See "Traceback" on page 6-21 for details.

### The Data Section and Data Segment

The data section of an assembler language program holds the data that will become the object module's initialized data. You declare the data section with the .data pseudo-op. The .data is typically followed by data alignment pseudo-ops such as .byte and .long.

The linked data sections of the assembly language file become the data segment of the a.out file.

### The Bss Section in the Data Segment

At runtime, the bss (block startup by symbol) section is space reserved for uninitialized external values. The bss section lies at the end of the data segment. At assembly, the bss section has space reserved for it, but it contains no values. Therefore, a bss section per se does not exist in the assembler language source file.

However, you should use the .lcomm pseudo-op to reserve space in the bss section. Unlike .text and .data, .lcomm is not followed by any instructions or data. The .lcomm pseudo-op simply tells the assembler to reserve an area.

Information that will be in the bss section is not part of the a.out file. However, .lcomm does pass information about the bss size via the a.out file's header.

The .comm pseudo-op also affects the bss section. With .comm, you define a common block with a symbol name. The linker then defines common blocks in the bss section of a linked program, unless you link in a module that defines the symbol. If you declare a common storage area with .comm without declaring it as a global label in the same or another file, the loader allocates memory from the bss section, and uses the largest size declared.

#### The Location Counter

Each section of an assembler language program has four location counters that assign storage addresses to your program's statements. As the instructions of a source module are being assembled, the location counter keeps track of locations in storage. You can use a dollar sign (\$) as an operand to refer to the current value of the location counter.

As each statement is read, the assembler increments the location counter in the following fashion:

- 1. After an instruction has been assembled, the location counter indicates the next available instruction. The next available instruction becomes the current instruction.

- 2. If the statement containing the current instruction has a label, the assembler gives this label the current value of the location counter.

- 3. Before assembling the current instruction, the assembler checks the boundary alignment for that instruction. If the instruction needs to be aligned, the assembler increments the location counter to indicate the proper boundary.

- 4. While the instruction is being assembled, the value contained in the location counter does not change. This value now indicates the location of the current data after boundary alignment.

- 5. After assembling the instruction, the assembler increments the location counter by the length of the assembled data. The location counter now holds the address of the next available location.

By default, the assembler assumes location counter 0 for each section. However, you can indicate the location counter you wish to use with the .text, .data, or .lcomm pseudo-ops for the text, data, and bss sections, respectively.

# Chapter 4. 032 Microprocessor Instructions

## **CONTENTS**

| About This Chapter                                | 4-3 |

|---------------------------------------------------|-----|

| Introduction to Instructions                      | 4-4 |

| Categories of Instructions                        | 4-5 |

| Storage Access Instructions                       | 4-6 |

| Address Computation Instructions                  | 4-8 |

| Branch Instructions                               |     |

| Trap Instructions 4                               | -15 |

| Move and Insert Instructions 4                    | -15 |

| Arithmetic Instructions 4                         | -16 |

| Logical Operation Instructions                    | -18 |

|                                                   | -19 |

| System Control Register Manipulation Instructions | -20 |

|                                                   | -20 |

| System Control Instructions                       | -21 |

|                                                   | -22 |

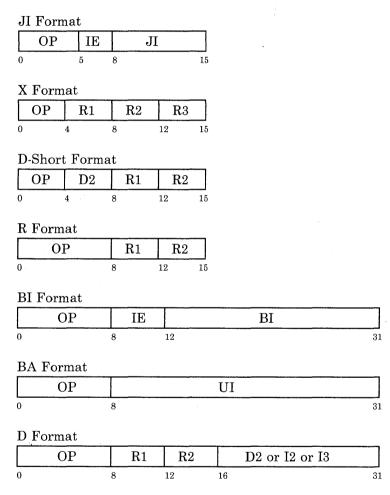

| Instruction Formats 4                             | -26 |

| Directory of Instructions 4                       | -28 |

## **About This Chapter**

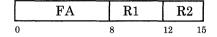

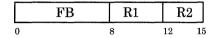

The first part of this chapter defines the 032 Microprocessor instructions, shows the categories and formats of instructions, and explains the notational conventions used to describe instructions.

The second part of this chapter lists the instructions in alphabetical order by mnemonic. For each instruction, both the mnemonic and op code or op codes are shown.

If you already know the mnemonic of the instruction, just find the appropriate page in the instruction directory. If you don't know the name of the instruction you want, but you know what the instruction should do, then look up the instruction name by its category. (See "Categories of Instructions" on page 4-5.)

#### Notes:

- 1. The extended branch instructions are not listed in alphabetical order. Instead, they are listed under the branch instruction that has the same op code. For example, beq is listed under bb.

- 2. Appendix A lists all the instructions by op code and by mnemonic.

#### Introduction to Instructions

Instructions are statements that the assembler translates into a machine-readable form. The assembler converts mnemonics to op codes, and operands to sequences of binary numbers, so that the processor can perform some operation. Do not confuse assembler instructions with pseudo-ops. (See Chapter 5.)

In RT PC 032 Microprocessor assembler language, some mnemonics have a single associated op code. Other mnemonics have two op codes. In this case, the assembler examines the instruction's immediate data and chooses the appropriate op code.

#### Notes:

- 1. Do not use an unassigned op code. If the processor encounters one of these reserved op codes, a program check error occurs. For more information on program checks, see Virtual Resource Manager Technical Reference.

- 2. The processor does not support dynamic instruction modification. Any attempt by software to modify an instruction may result in unpredictable operation.

## **Categories of Instructions**

Instructions are grouped into 11 classes:

- Storage access

- Address computation

- Branching

- Traps

- Moves and inserts

- Arithmetic

- Logical operations

- Shifts