## PowerPC An Inside View

International Technical Support Organization

Boca Raton Center

## PowerPC An Inside View

#### - Take Note! -

Before using this information and the product it supports, be sure to read the general information under "Special Notices" on page xiii.

#### First Edition (September 1995)

This edition applies to the IBM PC PowerPC hardware and software products currently announced at the date of publication.

Order publications through your IBM representative or the IBM branch office serving your locality. Publications are not stocked at the address given below.

An ITSO Technical Bulletin Evaluation Form for reader's feedback appears facing Chapter 1. If the form has been removed, comments may be addressed to:

IBM Corporation, International Technical Support Organization Dept. JLPC Building 014 Internal Zip 5220 1000 NW 51st Street Boca Raton, Florida 33431-1328

When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1995. All rights reserved. Note to U.S. Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

### **Abstract**

This document provides technical details on the PowerPC technology. It focuses on the features and advantages of the PowerPC Architecture and includes an historical overview of the development of the reduced instruction set computer (RISC) technology.

It also describes in detail the IBM Power Series product family based on PowerPC technology, including IBM Personal Computer Power Series 830 and 850 and IBM ThinkPad Power Series 820 and 850.

This book is intended for IBM customers, dealers, systems engineers and consultants who want a clear understanding of the advantages of the PowerPC Architecture and the capabilities of the IBM Power Series product family.

Some knowledge of general PC technology is assumed.

(220 pages)

## **Contents**

| Tables x                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tables                                                                                                                                                                                                           |

|                                                                                                                                                                                                                  |

| Special Notices xii                                                                                                                                                                                              |

| Preface       xvi         How This Document Is Organized       xvi                                                                                                                                               |

| Related Publications                                                                                                                                                                                             |

| International Technical Support Organization Publications xvii ITSO Redbooks on the World Wide Web (WWW) xix                                                                                                     |

| Acknowledgments xix                                                                                                                                                                                              |

| Chapter 1. PowerPC Concepts1.1 What Is an Architecture and Why Do We Need It?1.2 The RISC Story31.3 The PowerPC Alliance41.3.1 PowerPC Alliance, Goals and Objectives61.3.2 The History of the PowerPC Alliance8 |

| Chapter 2. Inside the PowerPC Technology                                                                                                                                                                         |

| 2.1 The POWER Architecture and the RISC System/6000                                                                                                                                                              |

| 2.1.1 The Driving Factors                                                                                                                                                                                        |

| 2.1.2 POWER - The Design Goals                                                                                                                                                                                   |

| 2.1.3 Inside the POWER Architecture                                                                                                                                                                              |

| 2.2 Some General Concepts                                                                                                                                                                                        |

| 2.2.1 Pipelining and Superscalar Dispatch                                                                                                                                                                        |

| 2.2.2 Load/Store Architecture                                                                                                                                                                                    |

| 2.2.3 Cache Coherency and Snooping                                                                                                                                                                               |

| 2.2.4 Cache Write Through and Write Back Policies 26                                                                                                                                                             |

| 2.2.5 Physical and Logical Memory                                                                                                                                                                                |

| 2.2.6 Virtual Memory and Demand Paging                                                                                                                                                                           |

| 2.2.7 Big- and Little-Endian Memory Organization                                                                                                                                                                 |

| 2.3 The PowerPC Architecture                                                                                                                                                                                     |

| 2.3.1 Design Goals of the PowerPC Architecture                                                                                                                                                                   |

| 2.3.2 Levels of PowerPC Architecture                                                                                                                                                                             |

| 2.3.4 A Comparison of POWER and PowerPC                         | 41  |

|-----------------------------------------------------------------|-----|

| 2.4 Elements of the PowerPC Architecture                        | 42  |

| 2.4.1 PowerPC Instruction Set                                   | 43  |

| 2.4.2 PowerPC Programming Model                                 | 47  |

| 2.4.3 PowerPC Memory Model                                      | 50  |

| 2.4.4 PowerPC Exception Model                                   | 58  |

| 2.5 The PowerPC Processor Family                                | 59  |

| 2.5.1 The PowerPC 601                                           | 61  |

| 2.5.2 The PowerPC 603                                           | 61  |

| 2.5.3 The PowerPC 604                                           | 62  |

| 2.5.4 The PowerPC 620                                           | 62  |

| 2.6 PowerPC Technology Details                                  | 62  |

| 2.6.1 The PowerPC 601                                           | 62  |

| 2.6.2 The PowerPC 603                                           | 68  |

| 2.6.3 The PowerPC 604                                           | 74  |

| 2.6.4 The PowerPC 620                                           | 79  |

|                                                                 |     |

| Chapter 3. RISC versus CISC                                     | 85  |

| 3.1 Features of RISC and CISC                                   | 85  |

| 3.1.1 Length and Format of Instructions                         | 85  |

| 3.1.2 Register-Oriented Operations                              | 86  |

| 3.1.3 Number of Addressing Modes                                | 86  |

| 3.1.4 Size of Register Sets                                     | 87  |

| 3.1.5 Size of Instruction Sets                                  | 87  |

| 3.2 Advantages and Disadvantages                                | 88  |

| 3.2.1 Execution Time                                            | 88  |

| 3.2.2 Pipelining                                                | 88  |

| 3.2.3 Optimizing Compilers                                      | 88  |

| 3.2.4 Code Compatibility                                        | 89  |

| 3.3 RISC and CISC Today                                         | 89  |

| 3.4 Feature Comparison of CISC and PowerPC Processors           | 90  |

| 3.5 Performance Comparison CISC versus PowerPC                  | 92  |

| o.o i onormanoo oompanoon oroo voroao i owon o                  | 02  |

| Chapter 4. PowerPC Strategy                                     | 95  |

| 4.1 PowerPC Reference Platform Specification                    | 96  |

| 4.1.1 Why PowerPC Reference Platform Specification?             | 97  |

| 4.2 PowerPC Reference Platform Specification Technology Details | 101 |

| 4.3 The New PowerPC Microprocessor Hardware Reference Platform  | 103 |

| 4.3.1 Current Environment                                       | 104 |

| 4.3.2 The Power Macintosh                                       | 104 |

| 4.3.3 The New Hardware Reference Platform                       | 105 |

| 4.3.4 What the PowerPC Microprocessor Hardware Reference        | .00 |

| Platform Offers Users                                           | 107 |

|                                                                 |     |

| 4.3.5 Initial PowerPC Microprocessor Hardware Reference Platform |     |

|------------------------------------------------------------------|-----|

| Implementation                                                   |     |

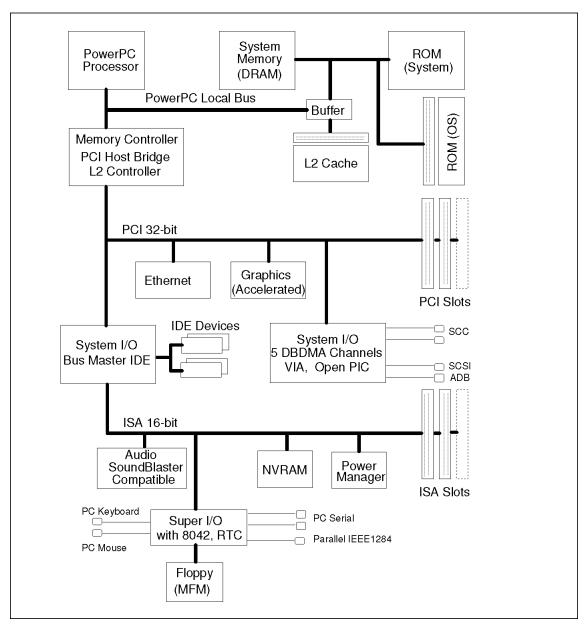

| 4.3.6 Processor                                                  | 108 |

| 4.3.7 System Memory (DRAM)                                       |     |

| 4.3.8 Level 2 (L2) Cache                                         |     |

| 4.3.9 Read-Only Memory (ROM)                                     |     |

| 4.3.10 Memory Controller and PCI Bridge                          |     |

| 4.3.11 I/O Subsystem                                             | 112 |

| 4.3.12 ISA Devices                                               |     |

| 4.3.13 Open Firmware                                             |     |

| 4.3.14 Summary                                                   | 116 |

| Chapter 5. PowerPC Software Environment                          |     |

| 5.1 Operating Systems for PowerPC                                |     |

| 5.1.1 IBM OS/2 Warp Connect (PowerPC Edition)                    | 118 |

| 5.1.2 IBM AIX                                                    | 122 |

| 5.1.3 Microsoft Windows NT                                       | 125 |

| 5.1.4 Sunsoft Solaris                                            | 127 |

| 5.1.5 PowerPC Operating Systems Comparison                       | 130 |

| 5.1.6 Apple System 7                                             | 131 |

| 5.2 PowerPC Application Support                                  | 132 |

| 5.2.1 PowerPC Application Compatibility and Porting              | 134 |

| 5.2.2 PowerPC Application Development Tools and Support          | 137 |

| 5.2.3 Development Support                                        | 141 |

| Chapter 6. PowerPC - Hardware and Product Overview               | 145 |

| 6.1 IBM Power Series Hardware Architecture                       | 145 |

| 6.1.1 Processor Subsystem                                        | 146 |

| 6.1.2 Memory Subsystem                                           |     |

| 6.1.3 Storage Subsystems                                         | 148 |

| 6.1.4 Human Interface Subsystem                                  |     |

| 6.1.5 Real-Time Clock Subsystem                                  |     |

| 6.1.6 Connectivity Subsystems                                    | 150 |

| 6.1.7 Bus Types                                                  | 150 |

| 6.1.8 Controllers                                                | 151 |

| 6.2 The IBM Power Series Product Line                            |     |

| 6.2.1 IBM Personal Computer Power Series 830 and 850             |     |

| 6.2.2 IBM ThinkPad Power Series 820 and 850                      |     |

| 6.3 Advanced Function Support                                    |     |

| 6.3.1 Additional Information on MPEG and Music Synthesis         |     |

| Annendix A. What Is Multiprocessing?                             | 177 |

| Appendix B. The PowerPC Instruction Set | 181 |

|-----------------------------------------|-----|

| Glossary                                | 191 |

| List of Abbreviations                   | 199 |

| Index                                   | 203 |

# Figures

| 1.  | The PowerPC Alliance                                           | . 7 |

|-----|----------------------------------------------------------------|-----|

| 2.  | The Definition of Execution Time                               | 13  |

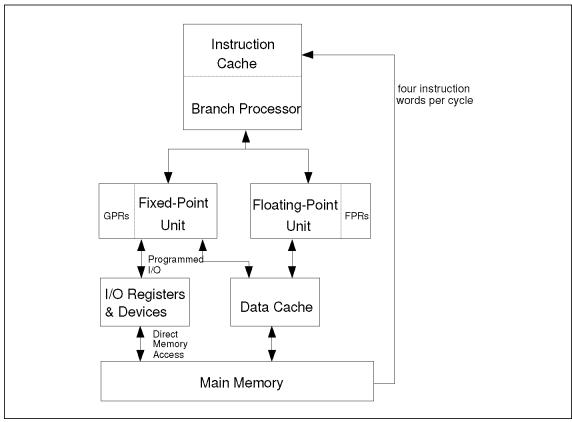

| 3.  | Block Diagram of the POWER Architecture                        |     |

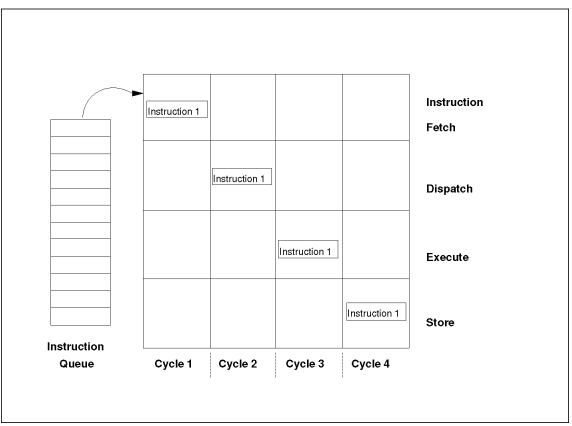

| 4.  | The Instruction Execution Process without Pipelining           | 19  |

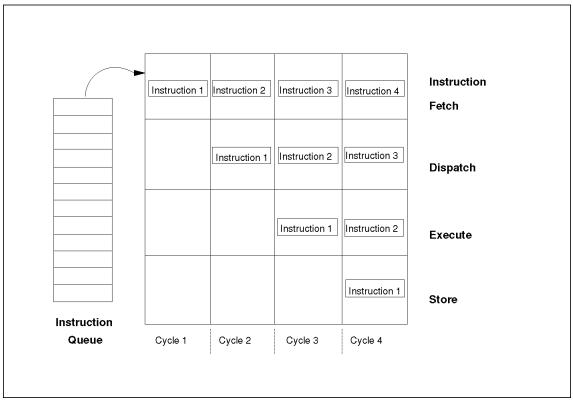

| 5.  | Basic Pipelining                                               | 20  |

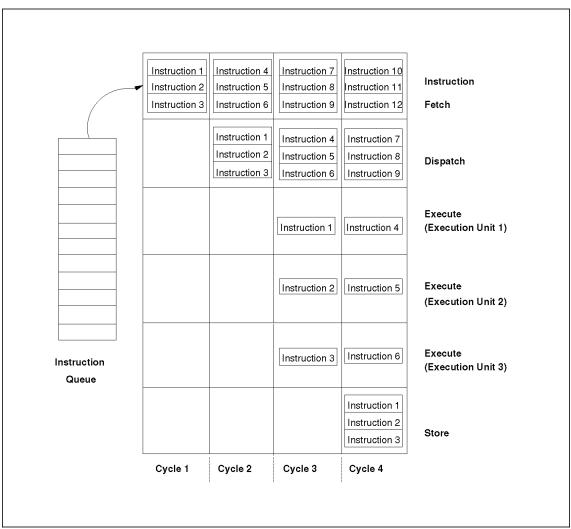

| 6.  | Pipelining with Superscalar Instruction Dispatch               | 21  |

| 7.  | Data Transfer Between CPU And Memory                           | 24  |

| 8.  | An Incoherent View of Memory                                   | 25  |

| 9.  | No Immediate Write Back                                        | 27  |

| 10. | Program Loading into Memory                                    |     |

| 11. | Physical and Logical Addresses                                 |     |

| 12. | Allocation of Free Pages                                       |     |

| 13. | Tracking Page Allocation with Page Tables                      | 33  |

| 14. | Virtual Memory and Swapping                                    |     |

| 15. | Big- and Little-Endian Byte Ordering                           |     |

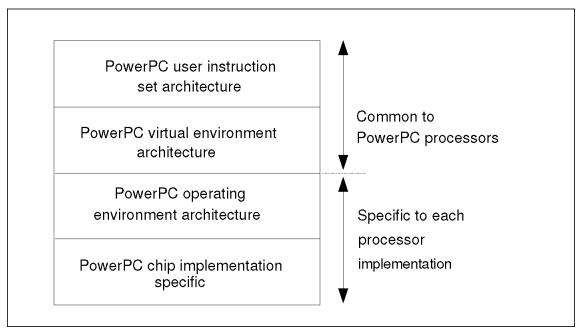

| 16. | Levels of the PowerPC Architecture                             |     |

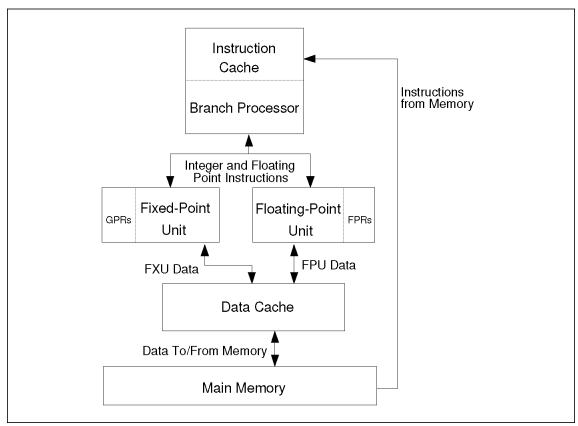

| 17. | PowerPC - The Basic Conceptual Processor Model                 |     |

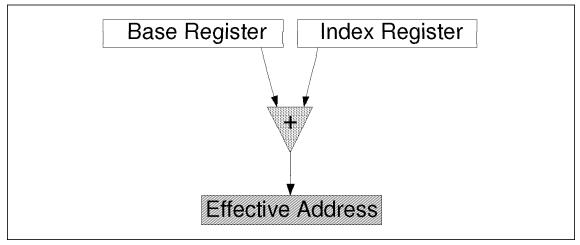

| 18. | Register Index Addressing Mode                                 | 46  |

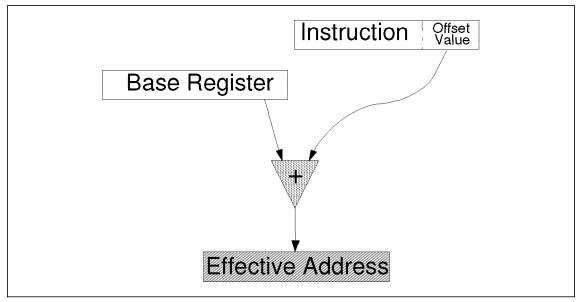

| 19. | Immediate Addressing Mode                                      | 46  |

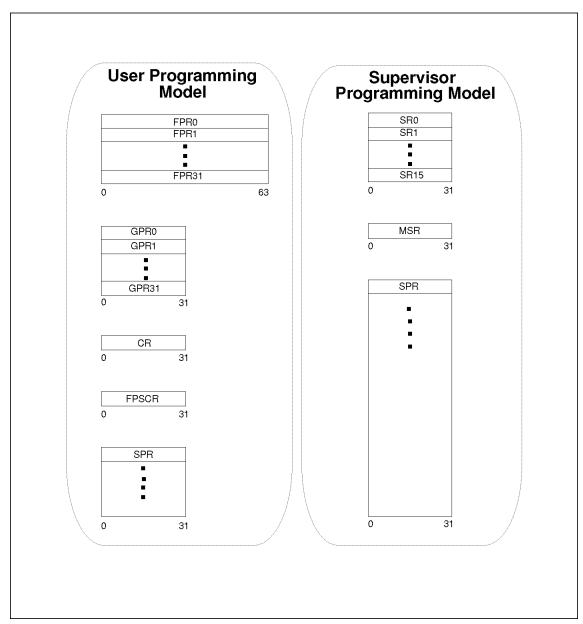

| 20. | The PowerPC Programming Model                                  | 48  |

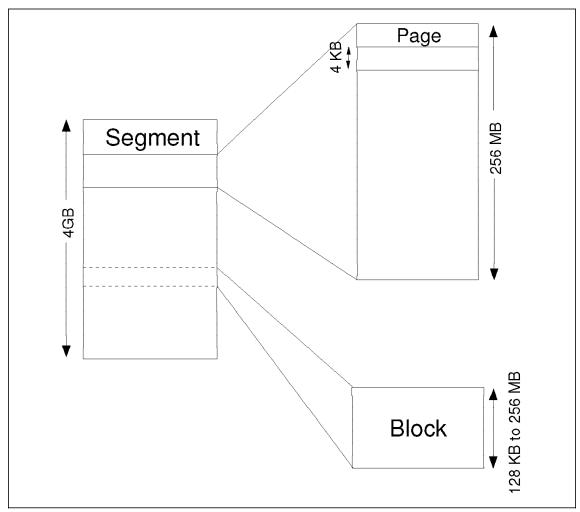

| 21. | How Memory Is Partitioned                                      | 51  |

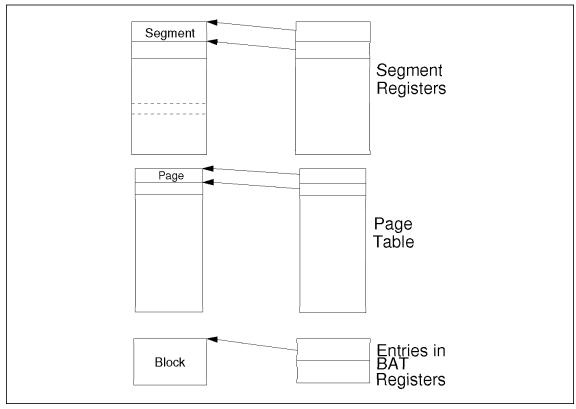

| 22. | How Memory Partition Locations Are Stored                      | 52  |

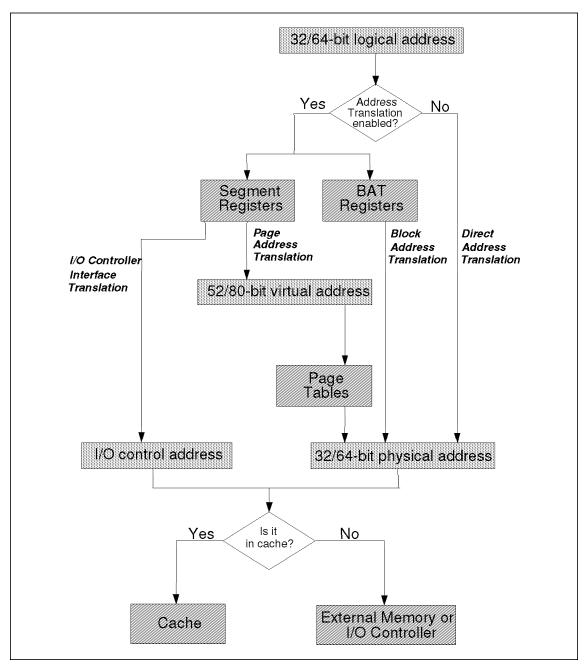

| 23. | The Address Translation Process                                | 55  |

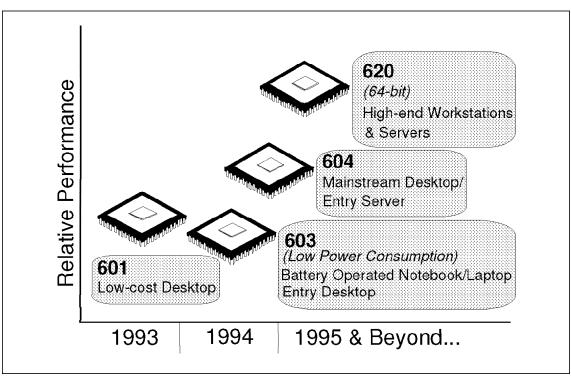

| 24. | The PowerPC Processor Road Map                                 | 60  |

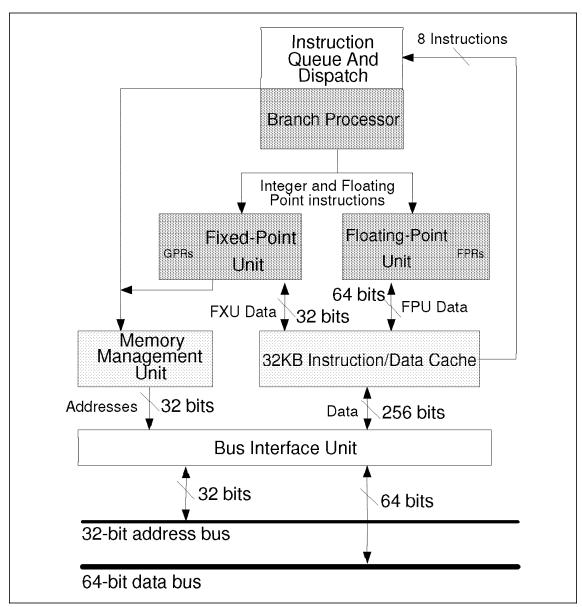

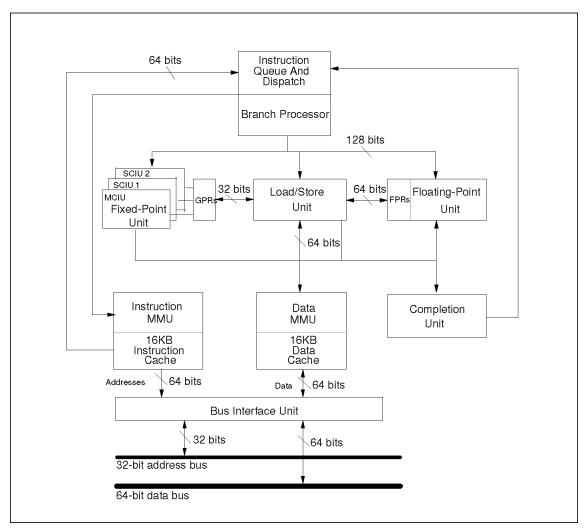

| 25. | The PowerPC 601 Microprocessor Block Diagram                   |     |

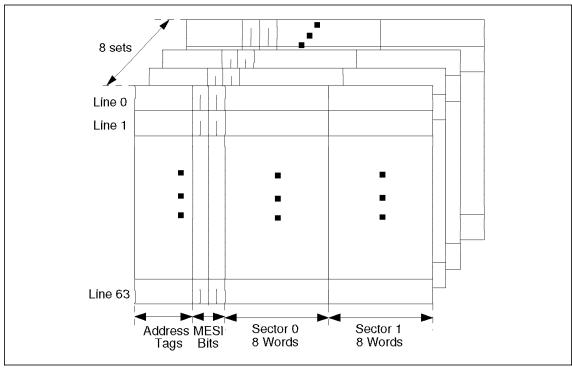

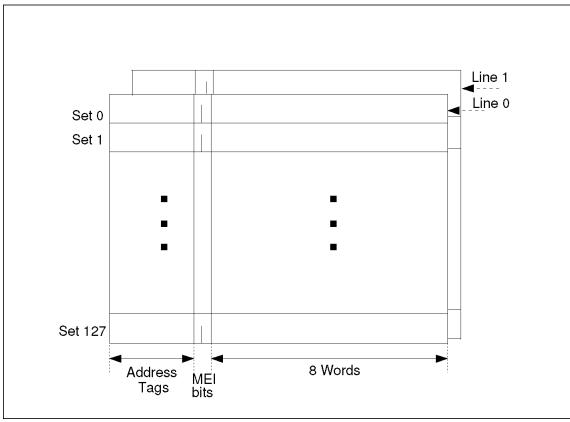

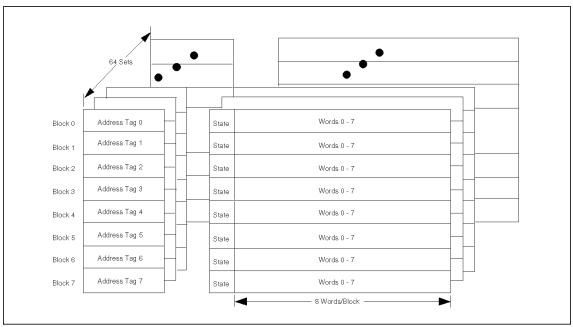

| 26. | PowerPC 601 Cache Organization                                 |     |

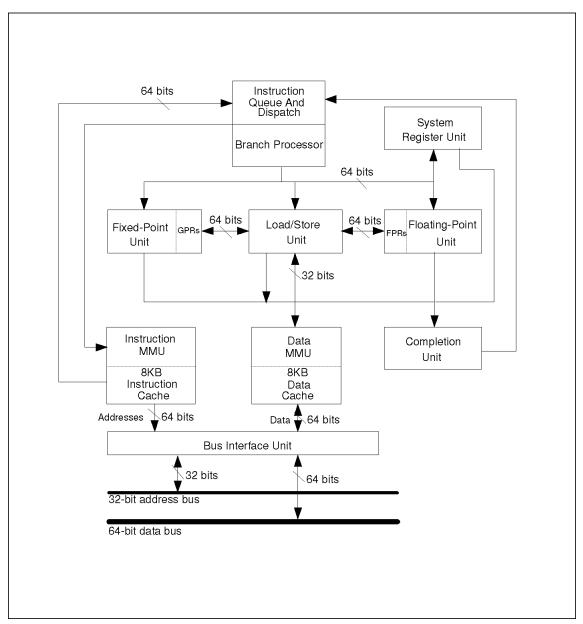

| 27. | The PowerPC 603 Microprocessor Block Diagram                   |     |

| 28. | PowerPC 603 Data Cache Organization                            |     |

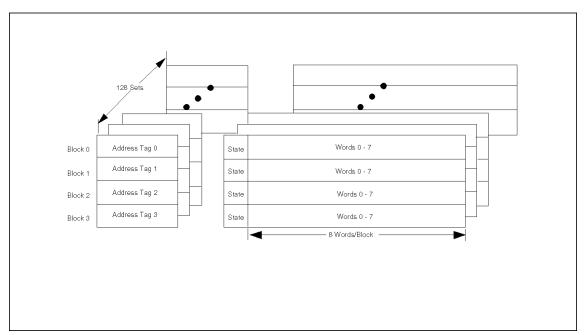

| 29. | The PowerPC 604 Microprocessor Block Diagram                   |     |

| 30. | The PowerPC 604 Data Cache Organization                        |     |

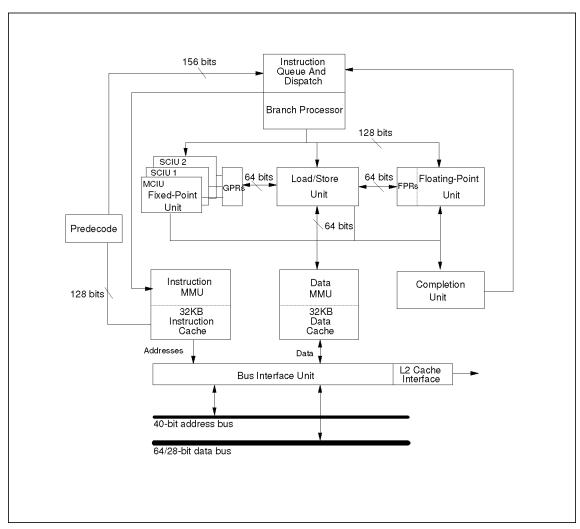

| 31. | The PowerPC 620 Microprocessor Block Diagram                   |     |

| 32. | The PowerPC 620 (L1) Data Cache Organization                   | 82  |

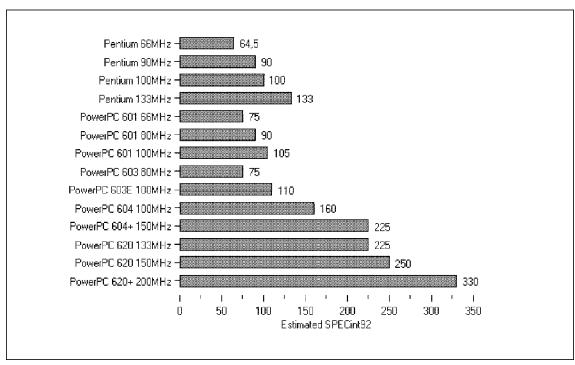

| 33. | Estimated SPECint92 Figures for PowerPC and Pentium Chips      |     |

|     | (Source, PowerPC Development Somerset, Austin TX)              | 93  |

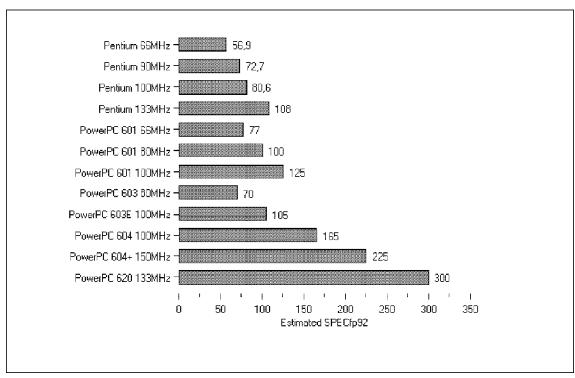

| 34. | Estimated SPECfp92 Figures for PowerPC and Pentium Chips       |     |

|     | (Source, PowerPC Development Somerset, Austin TX)              | 94  |

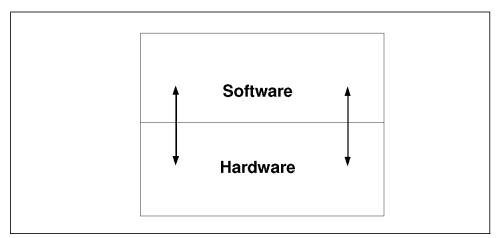

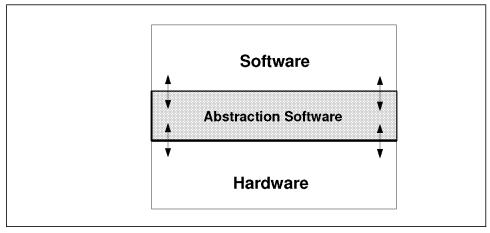

| 35. | Old Compatibility Model - Software Communicates Directly with  |     |

|     | Hardware                                                       | 98  |

| 36. | New Compatibility Model - Abstraction Software Layer Separates |     |

|     | Hardware and Software                                          | 98  |

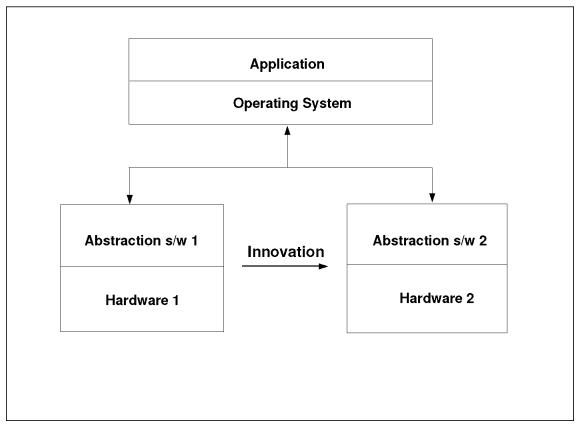

| 37. | PowerPC Reference Platform Specification Design Environment  | 99  |

|-----|--------------------------------------------------------------|-----|

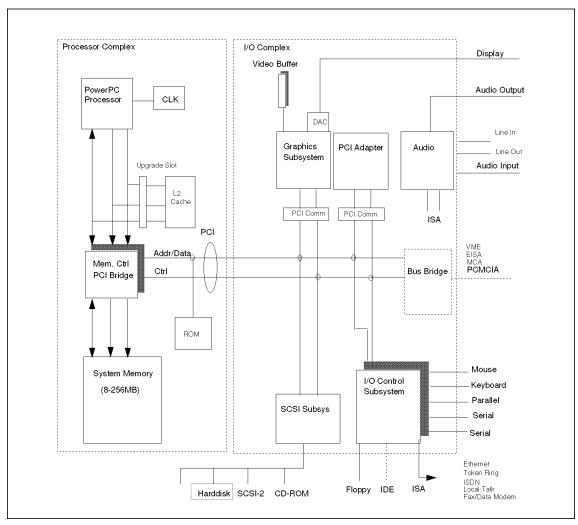

| 38. | Typical PowerPC Desktop System                               | 102 |

| 39. | PowerPC Hardware Reference Platform - Initial Implementation |     |

|     | Block Diagram                                                | 111 |

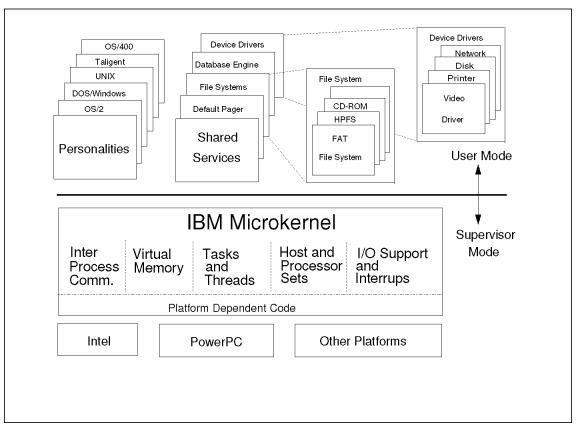

| 40. | The Microkernel Architecture                                 | 121 |

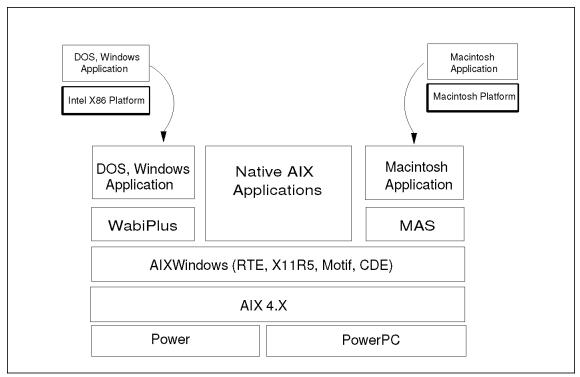

| 41. | DOS/Windows and Macintosh Applications on AIX                | 125 |

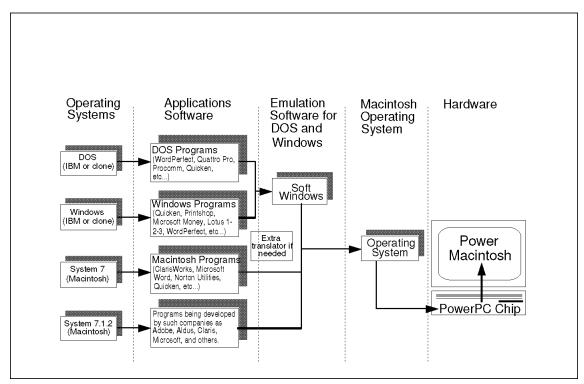

| 42. | The Apple System 7 on the Power Macintosh                    | 132 |

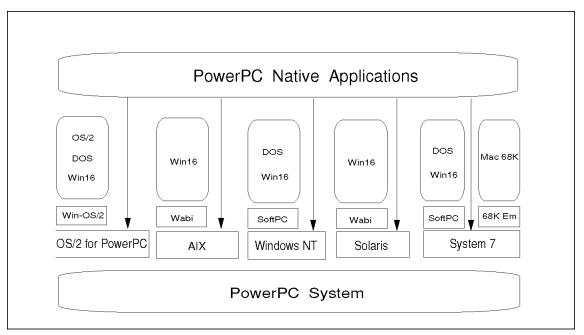

| 43. | The PowerPC Application Support                              | 135 |

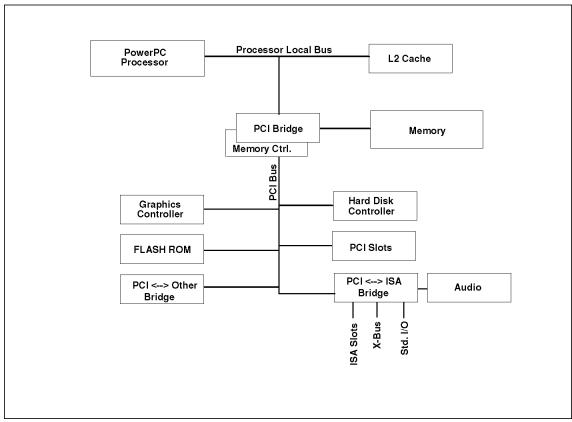

| 44. | Typical IBM Power Series Design                              | 146 |

| 45. | IBM Personal Computer Power Series 830 and 850               | 154 |

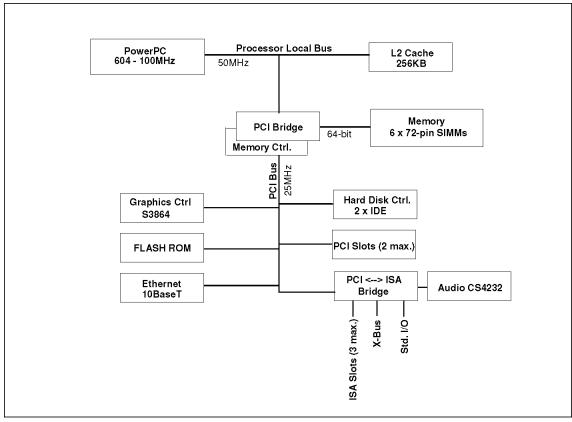

| 46. | Personal Computer Power Series 830 Design Diagram            | 158 |

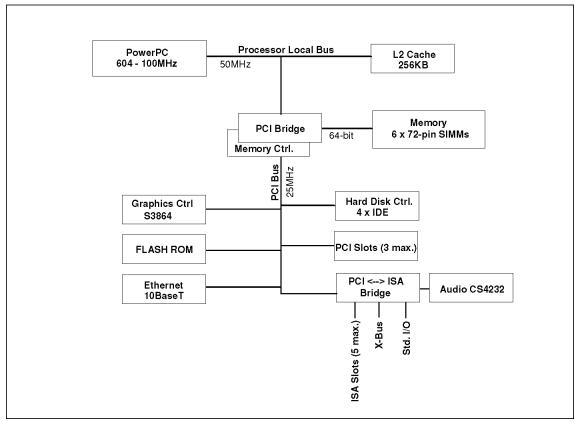

| 47. | Personal Computer Power Series 850 100MHz Design Diagram     | 160 |

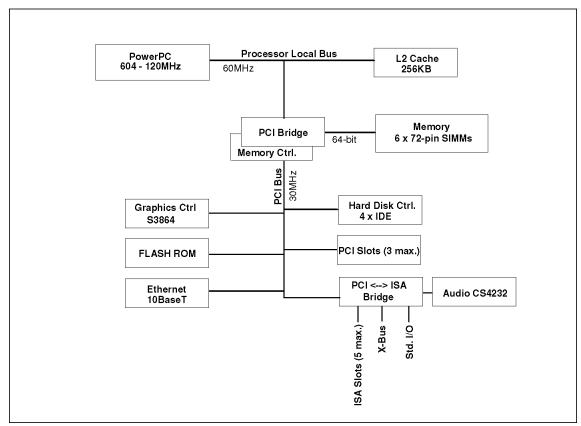

| 48. | Personal Computer Power Series 850 120MHz Design Diagram     | 161 |

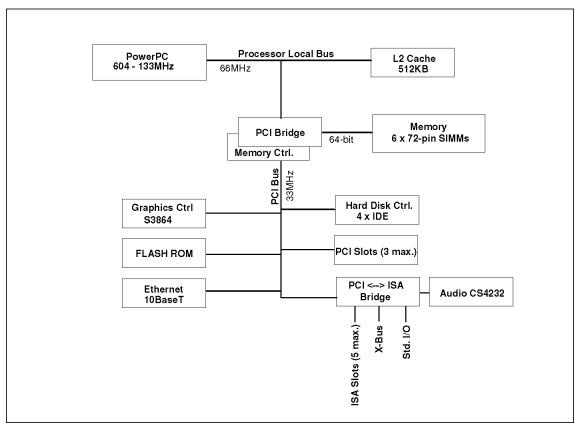

| 49. | Personal Computer Power Series 850 133MHz Design Diagram     | 162 |

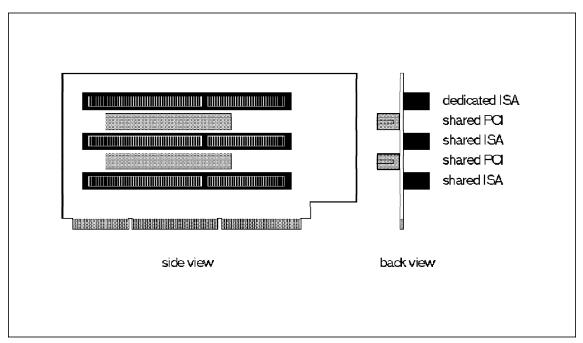

| 50. | 3-Slot Riser Card                                            | 164 |

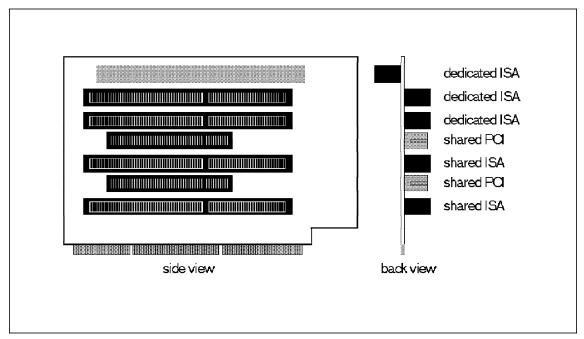

| 51. | 5-Slot Riser Card                                            | 165 |

| 52. | IBM ThinkPad Power Series 820 and 850                        | 166 |

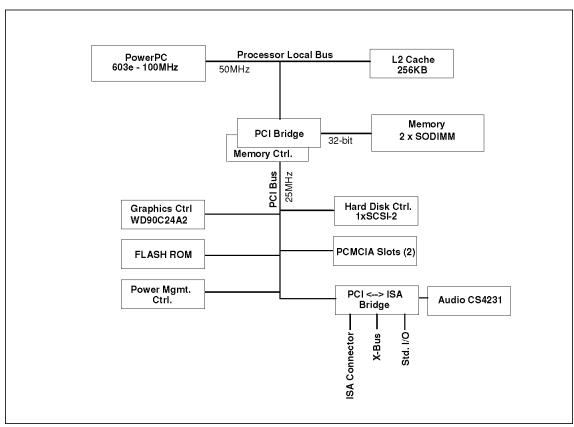

| 53. | ThinkPad Power Series 820 Design Diagram                     | 170 |

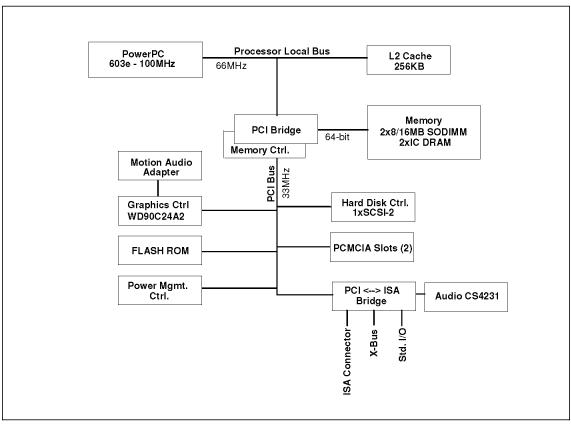

| 54. | ThinkPad Power Series 850 Design Diagram                     | 172 |

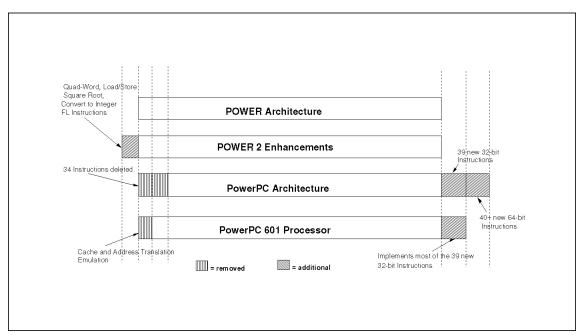

| 55. | Relationship between POWER, POWER2, PowerPC and the          |     |

|     | PowerPC 601 Instruction Set                                  | 182 |

## **Tables**

| 1.  | Elements of the PowerPC Architecture                         | 42  |

|-----|--------------------------------------------------------------|-----|

| 2.  | Page Access Protection Levels                                | 53  |

| 3.  | What the WIM Settings Mean                                   | 57  |

| 4.  | PowerPC Processor Overview                                   | 60  |

| 5.  | 601 Microprocessor Exception Classifications                 | 68  |

| 6.  | 603 Microprocessor Exception Classifications                 | 73  |

| 7.  | 604 Microprocessor Exception Classifications                 | 78  |

| 8.  | 620 Microprocessor Exception Classifications                 | 84  |

| 9.  | Comparison Between the PowerPC Processor 601/603 and Pentium | 90  |

| 10. | Operating System Comparison                                  | 130 |

| 11. | Personal Computer Power Series 830 Characteristics           | 158 |

| 12. | Personal Computer Power Series 850 Characteristics           | 162 |

| 13. | ThinkPad Power Series 820 Characteristics                    | 170 |

| 14. | ThinkPad Power Series 850 Characteristics                    | 173 |

| 15. | The PowerPC Instruction Set                                  | 182 |

| 16. | PowerPC Instructions not Supported by the PowerPC 601        |     |

|     | Processor                                                    | 188 |

| 17. | Power Instructions Deleted from the PowerPC Architecture     | 188 |

## **Special Notices**

This publication is intended to help IBM customers, dealers, system engineers and consultants to get a clear understanding on the capabilities of the IBM Power Series product line. The information in this publication is not intended as the specification of any programming interfaces that are provided by OS/2, AIX or any other operating system mentioned in this publication. See the PUBLICATIONS section of the IBM Programming Announcement for more information about what publications are considered to be product documentation.

References in this publication to IBM products, programs or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product, program, or service is not intended to state or imply that only IBM's product, program, or service may be used. Any functionally equivalent program that does not infringe any of IBM's intellectual property rights may be used instead of the IBM product, program or service.

Information in this book was developed in conjunction with use of the equipment specified, and is limited in application to those specific hardware and software products and levels.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Licensing, IBM Corporation, 500 Columbus Avenue, Thornwood, NY 10594 USA.

The information contained in this document has not been submitted to any formal IBM test and is distributed AS IS. The information about non-IBM (VENDOR) products in this manual has been supplied by the vendor and IBM assumes no responsibility for its accuracy or completeness. The use of this information or the implementation of any of these techniques is a customer responsibility and depends on the customer's ability to evaluate and integrate them into the customer's operational environment. While each item may have been reviewed by IBM for accuracy in a specific situation, there is no guarantee that the same or similar results will be obtained elsewhere. Customers attempting to adapt these techniques to their own environments do so at their own risk.

Any performance data contained in this document was determined in a controlled environment, and therefore, the results that may be obtained in other operating environments may vary significantly. Users of this document should verify the applicable data for their specific environment.

The following document contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples contain the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

Reference to PTF numbers that have not been released through the normal distribution process does not imply general availability. The purpose of including these reference numbers is to alert IBM customers to specific information relative to the implementation of the PTF when it becomes available to each customer according to the normal IBM PTF distribution process.

You can reproduce a page in this document as a transparency, if that page has the copyright notice on it. The copyright notice must appear on each page being reproduced.

The following terms are trademarks of the International Business Machines Corporation in the United States and/or other countries:

AIX C Set ++ CICS СТ DB2/2 IBM IMS

Micro Channel Operating System/2 OS/2 PAL

PowerPC Personal System/2 Power Series 830 Power Series 820 Power Series Power Series 850 PowerPC 601 PowerPC 603

PowerOpen PowerPC Architecture PowerPC Reference Platform **POWER Architecture** PowerPC 604 **POWER Team**

PowerPC 603e Presentation Manager

PS/ValuePoint PS/1 PS/2 RISC System/6000

RS/6000 System/360 System/370 ThinkPad TrackPoint VoiceType

400

The following terms are trademarks of other companies:

A/UX, Apple, Apple Desktop Bus, Finder, GeoPort, LocalTalk, Mac, Macintosh, and System 7 are trademarks of Apple Computer, Incorporated

Alliance is a trademark of American Telephone and Telegraph Company

ATM is a trademark of Adobe Systems Incorporated

C++ is a trademark of American Telephone and Telegraph Company, Incorporated

Canon is a trademark of Canon Kabushiki Kaisha

C-bus is a trademark of Corollary, Inc.

Centronics is a trademark of Centronics Data Computer Corporation

CORBA is a trademark of Object Management Group, Incorporated

DeskSet, Solaris, Sun, Sun Microsystems, SonOS, SunSoft and Wabi are trademarks of Sun Microsystems, Incorporated

Direct Access is a trademark of Fifth Generation Systems, Incorporated

Framework is a trademark of Ashton-Tate, Incorporated

Hewlett-Packard and HP are trademarks of Hewlett-Packard Company

Intel, Pentium, and 486 are trademarks of Intel Corporation

Kodak is a trademark of Eastman Kodak Company

Lotus is a trademark of Lotus Development Corporation

Microsoft, Windows, MS, MS-DOS, Windows NT, and Win32

are trademarks of Microsoft Corporation

MIPS is a trademark of MIPS Computer Systems, Incorporated

Motif, Open Software Foundation and OSF are trademarks of

of The Open Software Foundation, Incorporated

Motorola is a trademark of Motorola, Incorporated

NAP is a trademark of Automated Network Management, Incorporated

NetWare and Novell are trademarks of Novell, Incorporated

NuBus is a trademark of Texas Instruments, Incorporated

PC Direct is a trademark of Ziff Communications Company and is used by IBM Corporation under license.

Philips is a trademark of Philips Electronics N.V.

PIC is a trademark of Pacific Image Communications, Incorporated

POSIX is a trademark of Institute of Electrical and Electronic Engineers

Q & A is a trademark of Symantec Corporation

SoftPC is a trademark of Insignia Solutions, Incorporated

SPEC is a trademark of Systems Performance Evaluation Cooperative

SPECfp92 and SPECint92 are trademarks of Standard Performance Evaluation Corporation, Incorporated

Symantec is a trademark of Symantec Corporation

S3 is a trademark of S3 Incorporated

Taligent is a trademark of Taligent, Incorporated

UNIX is a registered trademark in the United States and other

countries licensed exclusively through X/Open Company Limited. UNIX System V is a trademark of AT&T Bell Laboratories Incorporated VESA is a trademark of Video Electronics Standards Association VL-Bus is a trademark of Video Electronics Standards Association Western Digital is a trademark of Western Digital Corporation

Other trademarks are trademarks of their respective companies.

#### **Preface**

This document is intended to provide technical details on the PowerPC Architecture and the capability of IBM Personal Computer Power Series and the IBM ThinkPad Power Series. It contains a detailed description of features, advantages of the PowerPC technology and the IBM PC product family based on PowerPC technology.

This document is intended for IBM customers, dealers, systems engineers and consultants.

## **How This Document Is Organized**

The document is organized as follows:

· Chapter 1, "PowerPC Concepts"

The introduction gives an overview of the personal computer market today, explains the market needs for PowerPC technology and defines the term "architecture." Furthermore, it provides information on the reduced instruction set computer (RISC) history, and the PowerPC alliance.

· Chapter 2, "Inside the PowerPC Technology"

This chapter describes the different levels of the PowerPC Architecture and provides details on the PowerPC technology.

· Chapter 3, "RISC versus CISC"

This provides details on the technology differences between the RISC and complex instruction set computer (CISC) technology as well as a road map on available CISC and PowerPC processors and performance details

· Chapter 4, "PowerPC Strategy"

The purpose of this chapter is to provide insights into the PowerPC Reference Platform specification and the PowerPC Microprocessor Hardware Reference Platform

· Chapter 5, "PowerPC Software Environment"

This chapter discusses the PowerPC software environment including the different PowerPC operating systems, PowerPC application support and PowerPC application development tools.

- · Chapter 6, "PowerPC Hardware and Product Overview" This provides detailed technical information on the IBM Power Series product line including the IBM Personal Computer Power Series and the IBM ThinkPad Power Series.

- · Appendix A, "What Is Multiprocessing?" This appendix is provided as an overview for readers who are not familiar with multiprocessing concepts.

- · Appendix B, "The PowerPC Instruction Set" This appendix provides a list of the PowerPC Architecture instruction set.

#### **Related Publications**

The publications listed in this section are considered particularly suitable for a more detailed discussion of the topics covered in this document.

- Inside the PowerPC Revolution, ISBN 1-883577-04-7

- PowerPC Computing, ISBN 1-56529-625-7

- PowerPC A Practical Companion, ISBN 0-7506-1801-9

- Computer Organization and Architecture, ISBN 0-02-946297-5

- PowerPC Processor Architecture, 52G7487

- PowerPC 601 Microprocessor User's Manual, 52G7484

- PowerPC System Technical Manual, 52G7490

- PowerPC AIX Hardware Dependencies Reference Guide, 52G7485

- IBM RISC System/6000 Technology, IBM SA23-2619-00

## International Technical Support Organization Publications

A complete list of International Technical Support Organization publications, with a brief description of each, may be found in International Technical Support Organization Bibliography of Redbooks, GG24-3070.

To get a catalog of ITSO redbooks, VNET users may type: TOOLS SENDTO WTSCPOK TOOLS REDBOOKS GET REDBOOKS CATALOG

A listing of all redbooks, sorted by category, may also be found on MKTTOOLS as ITSOCAT TXT. This package is updated monthly.

#### - How to Order ITSO Redbooks

IBM employees in the USA may order ITSO books and CD-ROMs using PUBORDER. Customers in the USA may order by calling 1-800-879-2755 or by faxing 1-800-284-4721. Visa and MasterCard are accepted. Outside the USA, customers should contact their local IBM office. For guidance on ordering, send a PROFS note to BOOKSHOP at DKIBMVM1 or E-mail to bookshop@dk.ibm.com.

Customers may order hardcopy ITSO books individually or in customized sets, called BOFs, which relate to specific functions of interest. IBM employees and customers may also order ITSO books in online format on CD-ROM collections, which contain redbooks on a variety of products.

## ITSO Redbooks on the World Wide Web (WWW)

Internet users may find information about redbooks on the ITSO World Wide Web home page. To access the ITSO Web pages, point your Web browser to the following URL:

http://www.redbooks.ibm.com/redbooks

IBM employees may access LIST3820s of redbooks as well. The internal Redbooks home page may be found at the following URL:

http://w3.itsc.pok.ibm.com/redbooks/redbooks.html

## Acknowledgments

This project was designed and managed by:

Michael Koerner

International Technical Support Organization, Boca Raton Center

The authors of this document are:

Michael Koerner IBM Germany

Chak Ming Fai IBM Singapore Joe Ruthven IBM South Africa

This publication is the result of a residency conducted at the International Technical Support Organization, Boca Raton Center.

Thanks to the following people for the invaluable advice and guidance provided in the production of this document:

Ricardo Aranda IBM Austin, TX

Arthur Adkins IBM Austin, TX

Robert Baker IBM Boca Raton, FL

Carmen Myers IBM Boca Raton, FL

Dan Molsberry IBM Somers, NY

Horst Oehler IBM Germany

Robert Paneque IBM Boca Raton, FL

## **Chapter 1. PowerPC Concepts**

When we look at the history of computers and, specifically, the personal computer market, it is not difficult to observe the change. In its short life span, the PC business has advanced exponentially. As prices have decreased, performance has continuously increased and advanced.

The microprocessor design has played a very important role in this technological boom. Ironically, the architecture that controlled all the hardware and software design was defined long ago. This architecture was designed for the technology of its time but it still drives most of our personal computers today. It is for this reason that the term "backward-compatible" has become part of our day-to-day vocabulary.

For the last decade there has been only one predominant choice of processor in the personal computer world: the complex instruction set computer (CISC) technology on which microprocessor design was based. The market is totally based on the Intel and Motorola technology, which are not even compatible with each other.

Microprocessor technology was invented in 1970 by Ted Hoff, a young Intel engineer. His work was done for a Japanese company called Busicom, which was in the hand-held calculator business. Intel itself thought at the time that this processor was too limited to be useful.

The breakthrough came when BASIC began to be widely used. BASIC, a simple programming language, demonstrated that such a microprocessor could act very well as the central processing unit (CPU) in a computer system. The real business breakthrough came with Visicalc, the first spreadsheet application.

Today more than 165 million PCs have been sold, based on Intel and Motorola microprocessors. New applications and technologies, such as 3-D graphics and multimedia, require more and more CPU power, and CISC processors are struggling to provide this.

#### Today we have:

- Computation (spreadsheets, CAD)

- · 2-D graphics

- · Video and audio

Tomorrow we will have:

- · Even more computation

- 3-D graphics

- · Voice and language services

- · Collaborative computing

Users today are expecting PCs to improve their productivity, but what we see

- · Proliferation of devices with unique functions

- · Multiple communication paths

- Restrictive human/system interface

Although today's personal computers are still driven by an architecture of the 70s, it is not because the field of computer architecture has not kept pace with technology. John Cocke from the IBM T. J. Watson Research Center started investigations in the mid-70s on approaches to improve processor performance. He found out that 80 percent of code was only using 20 percent of the available instructions in the processor. Eighty percent of the available instructions were either never used or could be replaced by using instruction strings of the 20 percent normally used.

As a result of this research and other projects of the time, a new approach to microprocessor design called reduced instruction set computer (RISC) evolved in the early 1980s.

A resounding testimonial to the importance of RISC is that all new processor designs over the last five years have been based on RISC technology.

The question today is no longer if personal computers will move to RISC technology, but when.

## 1.1 What Is an Architecture and Why Do We Need It?

Computer architecture refers to those attributes of a system that are visible to a programmer, or those attributes that have a direct impact on the logical execution of a program.

Historically, computer manufacturers have offered a family of computer models. These models all have had the same architecture although they may have had different components, price/performance values, etc. Architectures typically have survived many years while everything else around them has changed constantly.

One of the most successful systems on the market was the System/360 developed by IBM in the 60s. Revolutionary technology was to use integrated circuits (ICs); the instruction set was directly installed in the processor in the form of microcode.

Software compatibility across all System/360 models was the big advantage, since all System/360s had common instructions.

The System/360 was replaced by the IBM System/370 architecture. This architecture was first introduced in 1971 and included a number of models. IBM introduced many models over the years with improved technology offering the customer greater speed, lower cost or both. These newer models retained the same architecture as the other 370s so the customer's software investment was protected.

The term architecture is used to refer to a broad assortment of things in the computer industry. In the context of microprocessor architecture, it refers to the specifications upon which the design of a processor or family of processors is based. The architecture consists of the instruction set, the programming model, the exception model and other specifications that characterize a set of compatible processors. The need for a new architecture arises from the fact that the microprocessors in most of today's personal computers suffer from bottlenecks that are caused from outgrowing their original design.

In order to prevent the same situation that has happened with the original IBM Personal Computer, IBM has drawn up a document known as the PowerPC Reference Platform specification. This document gives guidelines and requirements for producing personal computer using PowerPC processors. Apple, IBM and Motorola have joined focus to produce the PowerPC Microprocessor Hardware Reference Platform. This architecture combines the Power Macintosh and PowerPC Reference Platform features. These documents are available free from IBM. For information on obtaining a copy of the PowerPC Reference Platform specification, refer to 4.1, "PowerPC Reference Platform Specification" on page 96.

### 1.2 The RISC Story

Contrary to popular belief, RISC architecture was born from an IBM project intended to solve a very specific problem. It was not created in an attempt to solve the fundamental problems of general purpose computing. Nor was it developed to provide a common architecture for a wide spectrum of processor requirements.

What really happened was that in 1974, IBM engineers needed a system to manage a telephone switching network. The network had to be capable of executing more than 20,000 instructions per call and 300 calls per second. No computer available at the time complied with this sort of real-time design criteria.

The absence of such a computer could cause arithmetic functions to quickly pile up, waiting to get access to the memory bus. This resulted in the memory bus becoming a tremendous bottleneck.

In order to meet the project specification, IBM engineers and designers envisioned a machine with simple instructions and extensive and well-placed on-chip memory. The latter are two fundamental characteristics of RISC technology today.

Reduced instruction set computing (RISC) consists of instructions that reduce operations into simpler tasks. These simple instructions each take approximately the same time to execute. In other words, reduce the instruction set and use a fixed length for the instruction so that in each clock cycle one instruction per computational unit can be executed. This makes it easier for the processor to interpret instructions, and it speeds up the execution while greatly simplifying processor design. Furthermore, once you have simple instructions, the compiler can optimize more easily the code to utilize the processor fully.

Although the telephone switching system was never built, the processor designers went on to explore further the possibilities presented by the project. The idea also created excitement in academic circles, and by the middle 70s there were several design projects underway:

• IBM 801 minicomputer

Further development of the telephone switching principle led to the design of the 801. The 801 was developed by John Cocke in the mid-1970s.

RISC-I and RISC-II

David Patterson and his colleagues at the University of California developed the RISC-I and RISC-II processors and coined the term RISC.

Stanford MIPS

This machine was developed by John Hennessy and colleagues at the Stanford University.

These three projects exploited the principle of IBM's telephone switching design by taking advantage of simple, fixed-length instructions. RISC offered an exciting alternative to the prevailing philosophy of complex instruction set computing (CISC) processor design.

The success of these projects sparked considerable interest on the part of major established computer manufacturers. The university projects brought RISC design principles out of the laboratories and into the research and development efforts of commercial chip manufacturers.

Today many types of RISC implementations exist. RISC design, however, is most closely associated with a handful of microprocessor manufacturers whose products are intended mostly for use in high-end workstations. RISC design is still maturing and taking hold in more and more environments. RISC designers are constantly capitalizing on other technological advances, and as manufacturing processes improve, so do the chips. Transistor miniaturization has made it possible to have more and more transistors per square millimeter. The combination of cheaper circuits and simpler instructions has moved RISC processors from multi-chip designs to single-chip processors with caches, parallel floating point units (FPUs) and main memory units (MMUs).

These designs have resulted in the availability of RISC processors on the desktop. With the development of the PowerPC 603 power-saving processor, even low-power battery-operated notebook systems and palm-top computers are now available with RISC technology.

## 1.3 The PowerPC Alliance

History has proven that being the technology leader does not guarantee a successful product. Probably the best example of this is Beta and VHS video recording technology. Beta, clearly the better technology, has lost out to the strength of marketing and alliance of VHS.

The computer industry has seen its own fair share of alliance and marketing effects. The best example is definitely Microsoft Windows 3.1. Although it is seen by few people as a technology leader, it has become a de facto standard for personal computers. This snowballing effect of its popularity was achieved with the marketing strength of Microsoft and the alliances it formed to promote Windows as the default operating system.

Customers are not buying machines anymore for performance only. It is also important to look at the long-term viability of the chosen architecture. The

viability of the architecture as a long-term solution relies on the acceptance of the direction of the technology and the ability of the alliance partners to promote these ideas in the market.

It is for this reason that the success of the PowerPC-based systems rests as much on market acceptance, openness and direction of the industry and alliances supporting the PowerPC initiatives as it does on the exciting advances embodied in the PowerPC family of processors and, more specifically, the IBM Power Series.

We will now briefly look at the alliance, its goals and objectives.

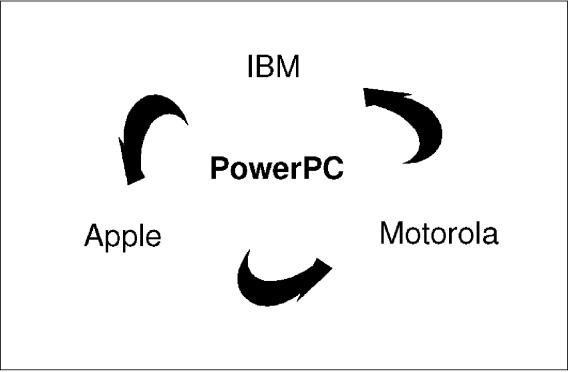

### 1.3.1 PowerPC Alliance, Goals and Objectives

The Somerset Design Center in Austin, Texas was created as a result of the alliance formed between IBM, Apple and Motorola in October 1991. It was on this date that the three companies announced they would jointly develop a new architecture that would form the basis of the next generation of personal computers.

The alliance recognized that the computer industry is one of the most rapidly growing industries in the world and that more and more computer power is required to fulfill customer application requirements.

The alliance set for itself the following objectives:

- · Object-oriented technology

- · Interconnectivity and networking

- · Open system environment

- Microprocessor technology

- Permit broad range of implementations

- Simplify to reduce design cycle time

- Allow for aggressive superscalar implementations

- Support symmetrical multiprocessors (SMP)

- Define a 64-bit superset architecture which provides binary compatibility for 32-bit POWER applications

The objectives were achieved when the first PowerPC microprocessor, the PowerPC 601, was announced to the industry in 1992 and began shipment in early 1993.

Figure 1. The PowerPC Alliance

The PowerPC alliance provides greater opportunities for compatibility and more efficient mixed network environments. One product of this collaboration is an IBM-certified Apple token-ring card. It also inspired the following joint efforts:

#### Kaleida Labs

Kaleida is a new company funded by IBM and Apple to create common standards for the fast-growing multimedia products.

#### Taligent

Taligent is also a new company funded by IBM and Apple that is developing an object-oriented operating system.

#### PowerOpen

PowerOpen is aimed towards developing a new version of the UNIX operating system that will combine features from IBM's AIX and Apple's A/UX operating systems. This platform will allow users access to AIX and Macintosh-based applications.

## 1.3.2 The History of the PowerPC Alliance

The following section will give chronological descriptions of the events surrounding and following the announcement of the PowerPC alliance.

In October 1991, IBM, Apple and Motorola jointly announced the formation of a new alliance. At that time, details were presented for the first time about the PowerPC Architecture and the PowerOpen environments.

Bull HN Information Systems, Inc., announced adoption of the new PowerPC Architecture for their server and workstation systems in January 1992.

During April 1992, Thomsonn-CSF CEITIA announced an agreement with IBM to develop products based on the PowerPC Architecture.

In May 1992, IBM, Apple and Motorola dedicated the Somerset Design Center in Austin, Texas.

The first processor was manufactured and unveiled by IBM, Apple and Motorola in October 1992. The chip was called the PowerPC 601.

The Harris corporation announced an agreement with IBM to develop real-time workstations based on the PowerPC Architecture in November 1992.

In December 1992 Tadpole Technology PLC announced an agreement with IBM to develop and produce notebook computers based on the PowerPC Architecture.

Thomson-CSF CETIA announced PowerPC VME systems and Lynx real-time software in January 1993.

In March 1993, Apple, Bull, Harris, Motorola, Tadpole Technology and Thomson-CSF announced the formal founding of the PowerOpen Association with the goal of providing an open system and compatibility.

During April of 1993 SunSoft announced plans to support Solaris on PowerPC based systems. In the same month Motorola announced general sampling of the PowerPC 601.

IBM and Motorola announced the availability of the PowerPC 601 tools catalog in May 1993, together with an announcement from Ford that the next generation of their Power Train Electronic Controller would be based on PowerPC Architecture.

Kaleida Labs, Scientific Atlanta and Motorola announced plans for interactive multimedia devices, developed using PowerPC processors in June 1993.

October 1993 was guite a busy month for the PowerPC alliance. An 80MHz version of the 601 was announced and the PowerPC 603 reached first silicon. CETIA, a subsidiary of Thomson-CSF, introduced a family of VME single-board computers and workstation based on the PowerPC 601 processor.

Bull also announced their first PowerPC-based system. Three systems configurations were made available: a compact desktop server, a desk side server and a single-user workstation. These systems are based on the PowerPC 601 processor.

Motorola's RISC Microprocessor division also announced in October five software development packages for optimizing performance of the PowerPC 603.

In the same month Apple announced the commitment from seven additional software developers. These developers also announced plans to ship upgraded versions of the software simultaneously with the first PowerPC systems.

IBM announced the PowerPC Personal System in November 1993. The PowerPC Reference Platform specification is a non-proprietary standard developed by the IBM Power Personal Systems Division, with participation from others in the industry. Operating systems planned to be ported to the PowerPC Reference Platform specification include AIX, OS/2, Windows NT, Solaris, and Taligent.

Also, in November 1993, Microsoft and Motorola announced that a port of Windows NT was jointly being developed with IBM's Power Personal Systems Division. The port to Windows NT, which conforms to the PowerPC Reference Platform specification, operates in Little-Endian mode and takes advantage of the PowerPC's Bi-Endian feature. A broad group of computer subsystem manufacturers announced support for the PowerPC Reference Platform specification.

In February 1994 Insignia Solutions and Apple announced an agreement to include SoftWindows in selected configurations of PowerPC-based Macintosh systems.

In November 1994, Apple, IBM and Motorola announced the PowerPC Microprocessor Hardware Reference Platform. This platform will combine features of the Power Macintosh and PowerPC Reference Platform specification.

## Chapter 2. Inside the PowerPC Technology

The PowerPC processor is a third-generation RISC architecture which has evolved from IBM's POWER (Performance Optimization With Enhanced RISC) architecture. Many features and design points of the POWER Architecture, such as superscalar design, zero-cycle branching and a highly optimized cache structure, have been retained in the PowerPC Architecture. These concepts will be explained in the next section, which starts the discussion of the PowerPC Architecture with a look at the POWER Architecture. Although the motivating factors that drive the design of the PowerPC Architecture differ from those for the POWER Architecture in many aspects, the decisions that were made in the design of the POWER architecture remain the same for the PowerPC processors. In order to understand the PowerPC, we first have to understand its heritage.

Next, we will discuss some general concepts of computer architecture that help us to understand the various features of the PowerPC Architecture.

Section 2.3, "The PowerPC Architecture" on page 36 and 2.4, "Elements of the PowerPC Architecture" on page 42 will examine the PowerPC Architecture in general and the elements defined by it.

We will conclude with a look at some current and planned implementations of PowerPC processors.

## 2.1 The POWER Architecture and the RISC System/6000

IBM introduced the RISC System/6000 family of products to the market in 1990. The goal then was to offer a series of products that would satisfy customer requirements for commercial and scientific applications. The first RS/6000 products were implementations of the POWER Architecture. The POWER Architecture is a second-generation RISC Architecture which contained many innovations for its time as well as major advances over existing RISC architectures. These innovations and advances were necessary to meet some design goals. These goals were motivated by various driving factors.

## 2.1.1 The Driving Factors

The POWER Architecture was designed to address the requirements of a UNIX-based system family and could effectively support both commercial application and scientific environments. This key objective arose out of several driving factors which occurred mainly in the late 1970s and early 1980s:

- · A growing market of commercial, engineering and scientific applications running on UNIX-based systems. In order to participate and lead in this growing market segment, IBM had to develop a very robust and flexible architecture on which good products could be built.

- Emergence of RISC designs and implementations from various manufactures.

- · Availability of 1 micron CMOS VLSI circuit technology that allowed 300,000 to one million devices per chip and projected clock cycles of 25 to 30MHz. Clearly, this technology advance could be exploited to develop a more powerful architecture.

- New developments in the fields of compiler technology and computer organization and architecture, both within and outside of IBM. Again, there was an opportunity to exploit these new discoveries to bring to market more advanced products.

### 2.1.2 POWER - The Design Goals

The key objective of the RS/6000 family of products was to be able to support both commercial and scientific application environments effectively. This implied that the underlying processor architecture had to efficiently fulfill the unique requirements of processing in both environments. In particular:

- Commercial environments generally feature more integer processing, transaction processing and file I/O. Therefore, the key components that would influence performance are the integer processing component of the CPU and the I/O subsystem.

- · Scientific and engineering environments usually require very high floating-point computation performance. To be able to support these environments effectively, the architecture must have a scheme to optimize floating-point performance.

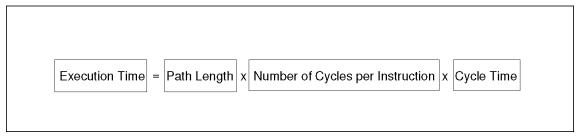

An important goal of any processor architecture design is to minimize execution time. In the design effort of the POWER Architecture, this was viewed as the product of three important factors: path length, cycles per instruction, and cycle time.

Figure 2. The Definition of Execution Time

- Execution Time is defined as Path Length times Cycles per Instruction times Cycle Time. An improvement in any of the three variables can result in a corresponding improvement in execution time.

- Path Length can be roughly defined as the number of instructions which

are needed to perform a certain piece of work. This variable is largely

influenced by the instruction set architecture and how well optimizing

compilers do their job.

- Cycles per Instruction can be viewed as the throughput of the CPU. It is the average number of clock cycles needed to complete executing one instruction. Generally, the factors influencing throughput are the processor architecture and the compiler technology.

- Cycle Time is the clock speed of the processor (the MHz). It is a

measure of how much time the processor takes to complete one clock

cycle. Much of this depends on the chip technology and the processor

architecture.

It is important to note that in the equation above, the three variables are not independent of each other. There are interactions between the factors that influence more than one of the three variables. For example, if the instruction set and processor architecture is very simple, it is probably easier to make the CPU run at a faster clock speed (reduced cycle time). But with a simple instruction set, more instructions would be needed to perform a piece of work compared to an architecture with a more complex instruction set (longer path length). These interdependences complicated the work of designing the architecture. Thus, a decision was made to focus the design work on reduced instruction set cycles, which was defined as the optimal value of Path Length times Cycles per Instruction. In this way, RISC was basically redefined to have the objective of reducing the execution time through reducing the instruction set cycles instead of simply reducing the instruction set.

## 2.1.3 Inside the POWER Architecture

The result of the design process to meet the goals stated above was the POWER Architecture, a highly concurrent, superscalar enhancement of early RISC architectures.

The POWER Architecture has many similar features to earlier, more traditional RISC architectures:

- · Register-oriented instruction set

- · Simple, fixed-length instructions

- · A hardwired, as opposed to microcoded, CPU

- · Strong pipelining features

These concepts will be explained in Chapter 3, "RISC versus CISC" on page 85.

Where POWER differs from first-generation RISC architectures is its use of advanced features, such as:

- · Multiple instruction dispatch

- · Multiple execution units, permitting simultaneous execution of different types of instructions

- · Separate instruction and data caches

- · Zero-cycle branches

Figure 3. Block Diagram of the POWER Architecture

Figure 3 shows a logical view of the basic POWER architecture. There are three main execution units in the CPU:

- The fixed-point unit (FXU) performs operations on whole numbers without a decimal point (for example, numbers like 3, 6 and 24) and numeric representations of text. It contains the general-purpose registers (GPRs) and the arithmetic logic unit, which does the actual execution. The FXU also carries out the duty of address translation. Address translation is the process of calculating the actual address in real memory of a piece of data from the virtual addresses which are used in programs to point to data. This process is necessary when the CPU needs to access data from main memory.

- The floating-point unit (FPU) performs mathematical operations on numbers with a decimal point. These kinds of numbers are common in scientific and engineering applications. Unlike typical floating-point coprocessors, the FPU in the POWER Architecture is closely coupled to

the rest of the CPU and can execute instructions independently of the other execution units. A unique feature of the POWER Architecture is that it implements the multiply-add floating-point instruction (an operation of the form AxB+C). This instruction is executed with the same delay as a single multiply or add instruction and is, effectively, two instructions in one.

The branch processor is implemented within the instruction cache unit (ICU). It independently executes all branch and condition register instructions. Branch instructions are instructions that cause the flow of the execution to be redirected to some other part of the program. Condition register operations are instructions that operate on information about the results of earlier calculations (for example, is A=B or X>Y?).

The basic POWER Architecture has a highly optimized cache structure which specifies separate instruction and data caches. Cache memory is very high-speed storage that buffers data and instructions between the slower main memory system and higher-speed CPU registers.

The instruction cache unit (ICU) reads four instructions at a time from main memory. This bandwidth is very important, as we will see later. It then dispatches the instructions to the respective execution units for execution. In a single cycle, the following mix of instructions can be dispatched simultaneously:

- One branch instruction (to the branch processor)

- One condition instruction (to the branch processor)

- One fixed-point instruction (to the FXU)

- One floating-point instruction (to the FPU)

It can be seen that a CPU based on the POWER architecture has a potential throughput of four instructions per clock cycle. This concept of dispatching multiple instructions per cycle to multiple execution units is called superscalar design.

An important concept in the design of the POWER architecture is the concept of zero-cycle branching. Traditionally, when a branch instruction directs the CPU to jump to a different section of the program code, the CPU wasted clock cycles getting the new target code from main memory while the execution units had no work to do. In the POWER Architecture, the branch processor is implemented in the ICU. It looks ahead to the stream of instructions which the ICU fetches from main memory, takes out the branch instructions and executes them, and in a lot of cases (especially unconditional branches), it can cause the new target instructions to be

fetched into the ICU in time to provide the FXU and FPU with an uninterrupted stream of instructions. This is termed zero-cycle branching.

The architecture also allows for schemes to perform branch prediction. Generally, these schemes use various methods to try and predict whether a conditional branch operation (for example, branch if A=B) will result in a branch or not. If the branch processor can get a correct prediction earlier, the instruction cache can fetch the necessary instructions from memory to feed the fixed-point and floating-point units with an uninterrupted stream of instructions to execute. Branch prediction schemes usually result in an improvement in execution time by reducing branch delay. Branch delay occurs when the instruction cache has to fetch instructions from a branch target area while the execution units are idle.

The set of instructions in the POWER Architecture was designed to have as much function as possible. This goes against the original spirit of RISC but the intent here is to optimize as much as possible the path length of programs. With more function in the instructions, fewer instructions are needed to do a piece of work. Chapter 3, "RISC versus CISC" on page 85 discusses this architectural decision and its bearing on the RISC versus CISC debate.

## 2.1.4 What Does All That Mean?

What aims do the various features of the POWER Architecture serve to achieve?

- 1. The instruction set was designed to optimize the path length of programs. This was one of the goals which would contribute to reducing instruction set cycles and hence execution time.

- 2. Multiple instructions can be dispatched and executed in the same clock cycle. This is aimed at reducing the cycles per instruction component. Together with objective number 1, the objective is to achieve reduced instruction set cycles which would in turn have a beneficial effect on execution time.

- 3. Zero-cycle branching also improves throughput and is aimed at reducing the cycles per instruction variable.

- 4. A tightly coupled FPU greatly improves performance for scientific and engineering applications. One important goal of designing the POWER Architecture was for it to effectively support both commercial and scientific environments.

## 2.2 Some General Concepts

The concepts and ideas below will help you to understand the various aspects of the PowerPC Architecture and their importance.

## 2.2.1 Pipelining and Superscalar Dispatch

Typical execution of a computer instruction requires a four-stage process:

- 1. Instruction Fetch involves fetching the instruction from main memory.

- 2. Dispatch or Decode is the process of decoding the instruction, getting the operands referred to in the instruction, and passing all these to the execution unit.

- 3. Execution involves the actual computation or execution of the instruction.

- 4. Store is the act of storing any results of the computation back into memory.

Each stage can be considered as taking up one CPU cycle. Of course, in a real implementation, different types of instructions go through different variations of the four-stage process and some of the stages may take more than one CPU cycle. But for ease of explanation, we can generalize here and say that there is a four-stage process with each stage using up one CPU cycle.

Figure 4. The Instruction Execution Process without Pipelining

Figure 4 shows how an instruction is processed through the four stages. This process achieves a throughput of one instruction every four cycles; that is, one instruction is completely processed every four cycles. We can see that this scheme can be easily made more efficient. While the instruction is going through one stage, the rest of the four stages are lying idle and not doing any work. This brought about the idea of pipelining.

Figure 5. Basic Pipelining

Figure 5 shows the four-stage process with simple pipelining implemented. This is a much more efficient scheme than the previous one. While one stage is processing an instruction, the other stages move on to the next instruction in the stream, like an assembly line. In this way, we can potentially achieve a throughput of one instruction per cycle.

Basic pipelining by itself can improve the performance of the instruction execution process. But the POWER and PowerPC Architectures scale this performance improvement even further with superscalar instruction dispatch. Superscalar design essentially adds one more dimension to pipelining.

Figure 6. Pipelining with Superscalar Instruction Dispatch

Figure 6 illustrates how the instruction execution process works with superscalar dispatch. There can be any number of independent execution units, but here we show an implementation with three execution units. Since up to three instructions can be executed in parallel, three instructions can be fetched every cycle. These instructions will be dispatched to the three execution units in parallel. If the execution units can be fed with an uninterrupted stream of instructions, such an implementation can achieve a potential throughput of three instructions per cycle.

The concepts explained above show how the PowerPC Architecture uses multiple parallel execution units and multiple instruction dispatch to achieve improved throughput.

### 2.2.2 Load/Store Architecture

Traditionally, RISC architectures used the load/store method of working with data instead of the large number of addressing modes favored by CISC architectures.

Instructions in CISC architectures usually have a large variety of addressing modes to specify the data which they are referring to (a discussion of these addressing modes are beyond the scope of this book). In an instruction that performs a computation on data, the data is usually referred to directly in their memory location using any one of the addressing modes.

Instructions in RISC architectures tended to have only a few modes of addressing data. In addition, when operations are performed on data, the data is usually first loaded into CPU registers. The computation is performed on the data in the registers and the results are then stored back into memory.

As an example, the instruction:

$$A = B + C$$

in a CISC architecture will be translated by a compiler in a RISC architecture to:

```

LOAD B into R1

LOAD C into R2

R3 = R1 + R2

STORE R3 into A

```

where A, B, C are locations of data in main memory and R1, R2, R3 are registers.

This method of moving all data between registers and main memory and only performing operations on data in the registers is called load/store architecture. The instructions that move data between the registers and main memory are called load/store instructions.

## 2.2.3 Cache Coherency and Snooping

Cache memory is high-speed memory that is used as a buffer between the CPU and main memory to speed up memory accesses. It is used because it is much faster than main memory. In all execution cycles, the CPU has to access memory at least once to fetch instructions. Usually, it has to access memory a few more times to fetch and store operands. In this way, memory access speed became a bottleneck to CPU performance because memory speed was far slower compared to CPU speed. One solution then was to build a high-speed buffer between the CPU and main memory. This buffer was built using more expensive technology than main memory but was also faster than main memory. This buffer, called cache, works because of what is known as the principle of locality. Whenever the CPU fetches an instruction or piece of data from memory, it takes what it wants word by word. A word is usually a two to four byte piece of data depending on the architecture. But when a CPU fetches something from memory, there is a good chance that the next piece of data it needs will be somewhere near the piece that was read earlier. This is the principle of locality.

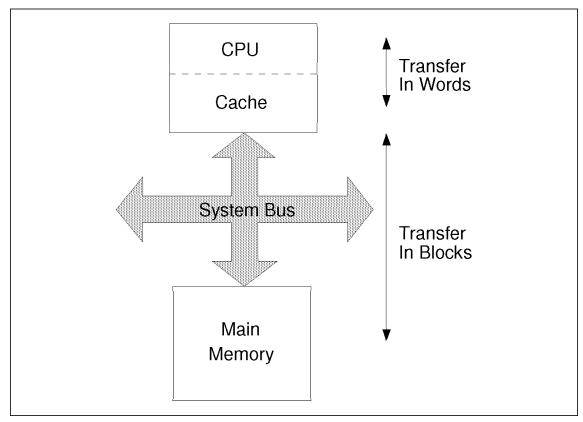

Figure 7. Data Transfer Between CPU And Memory

Figure 7 shows how cache memory takes advantage of the principle of locality to speed up memory accesses. When the CPU does a memory reference, entire blocks of data are brought into cache. These blocks can contain many bytes of data, maybe three or four times what the CPU actually needs. There is a good chance that the next piece of data that the CPU wants to access is in this block and already in the cache. Usually, if the data is to be updated by the CPU, the copy that is in cache is modified.

Cache memory is used widely today in CPU implementations to improve performance. But complications can arise in the case of multiprocessing.

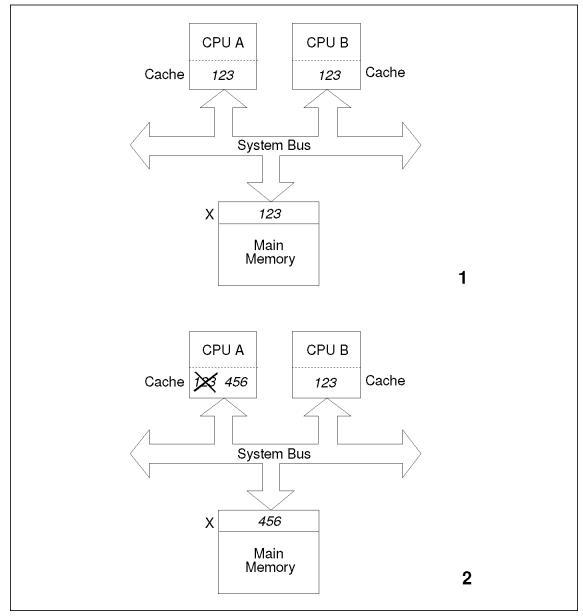

Figure 8. An Incoherent View of Memory

Figure 8 shows what can happen in a multiprocessor implementation. In a multiprocessor environment, a few CPUs, each with its own cache, share a single stack of main memory.

- 1. CPUs A and B are processing different instructions but it just happens that at some point in time they need data from the location in memory called X. X currently has a value of 123. So, X is brought into the caches of CPUs A and B.

- 2. Now, CPU A performs some operation that changes the value of X to 456 and writes out this value to main memory. We can see that A and B now have an incoherent view of memory; that is, their views of what X should be do not tally with each other.

Imagine what would happen if CPU B wanted to perform an arithmetic operation on X. It would be using the wrong value of X!

This is just a simple example to show what can possibly happen. There are many other possible scenarios which can occur. The term cache coherency is used to describe the situation when multiple caches sharing main memory agree with each other on what is in memory; that is, they all have an accurate view of memory. It is very important to put in techniques to ensure cache coherency when designing the cache subsystem. Snooping is one such technique.

The problem with the cache incoherency scenario above is that the individual caches are not aware of what each other are doing. If they were allowed to "see" what all the caches are doing, they could take the necessary action to maintain coherency. Bus snooping is a technique that allows them to do

When bus snooping is implemented, the caches keep a close watch on the activity going on along the system bus. In the scenario above, CPU B would have detected CPU A writing out the new value of X. It would have taken action to mark its own copy of X as being invalid. There are many other scenarios of incoherency that can arise and various other ways that bus snooping prevents incoherency. The important principle to keep in mind is that all the caches that share memory must watch the bus activity and take action accordingly to maintain coherency.

### 2.2.4 Cache Write Through and Write Back Policies

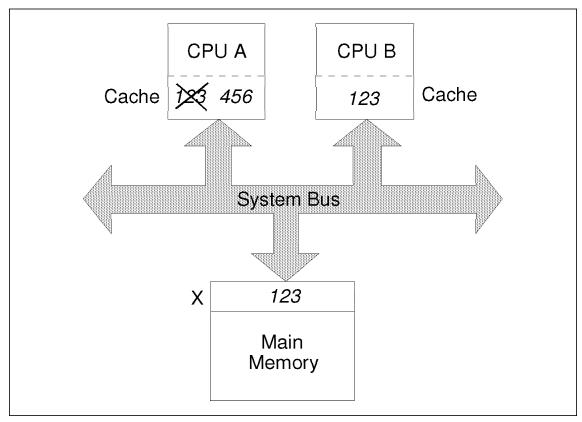

Now, think of what would happen if in the example shown in Figure 8 on page 25, CPU A did not write the new value of X out to memory immediately.

Figure 9. No Immediate Write Back

Figure 9 shows what happens in this case. Even if bus snooping were implemented, CPU B would not know that the value of X is changed because there is no activity on the system bus. This introduces two new concepts of cache behavior - *write through* and *write back*. These are policies that can be implemented to control the behavior of the cache system.

A write through policy states that any copy of data in cache that is modified by the CPU must be written out to memory immediately. This ensures that any changes to data in cache are always reflected in main memory as soon as possible. In addition, writing out of modified data generates system bus activity, which is useful for other caches that are snooping the bus. The disadvantage with this policy is the fact that any modification of data always requires movement of data to main memory. This takes time, generates additional bus traffic, and is not always necessary.

A write back policy is intended to overcome the main disadvantage of the write through policy. The write back method states that modified data can be kept in cache. It should be written to main memory when it is known that another processor is accessing or wants to access that piece of data in memory. In this way, modified data is only written out to memory when it is necessary.

## 2.2.5 Physical and Logical Memory

Main memory in most modern computer architectures are usually organized into small fixed size partitions. These partitions are called pages. The typical size of a page of memory is 2KB or 4KB.

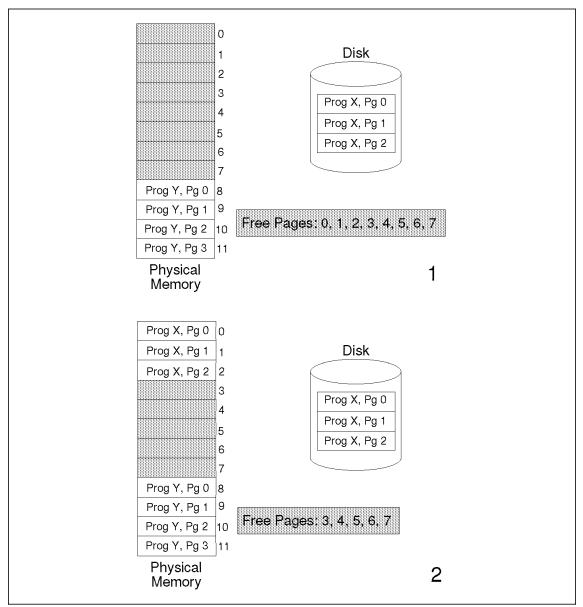

Figure 10. Program Loading into Memory

Figure 10 shows how a program is loaded into memory.

1. Program X, which occupies three pages, is to be loaded into memory. The program is stored on disk. There is a list of pages which are not

- occupied in memory. Program Y is already in memory, occupying four pages.

- 2. The three pages of Program X are loaded into three free pages in memory.

The pages that are loaded into memory contain instructions and data for Program X. There will be addresses in the code to refer to data and branch target locations. But Program X may not be loaded into the same location in memory every time. For example, next time, pages 0, 1 and 2 may be occupied by some other program and X may have to be loaded into pages 4, 5 and 6. The addresses in the program will have to be changed every time the program is loaded! How are addresses specified in the program so that wherever it is loaded, the addresses still point accurately at the correct locations?

The problem is solved by using two types of addresses - logical addresses and physical addresses. Logical addresses are used within a program to refer to other locations within the program. It is expressed as a displacement relative to the beginning of a program. When a program is loaded into memory, the physical address of the beginning of the program is called the base address. While the program is being executed, the CPU converts the logical addresses in memory into physical addresses. This process is called address translation. Address translation is done by adding the base address of the program to the logical addresses. Figure 11 on page 31 illustrates the difference between logical and physical addresses.

| Program | Logical<br>Address | Physical<br>Address |

|---------|--------------------|---------------------|

|         | 0                  | Base Address        |

|         | 1                  | Base Address + 1    |

|         | 2                  | Base Address + 2    |

|         | 3                  | Base Address + 3    |

|         | 4                  | Base Address + 4    |

|         | 5                  | Base Address + 5    |

|         | 6                  | Base Address + 6    |

|         |                    |                     |

Figure 11. Physical and Logical Addresses

In the examples so far, the programs have been loaded into memory into pages that are directly next to each other, or contiguous pages. In Figure 10 on page 29, the memory subsystem could find three free contiguous pages in which to load Program X. What would happen if there are not enough free contiguous pages in memory, as shown in Figure 12 on page 32?

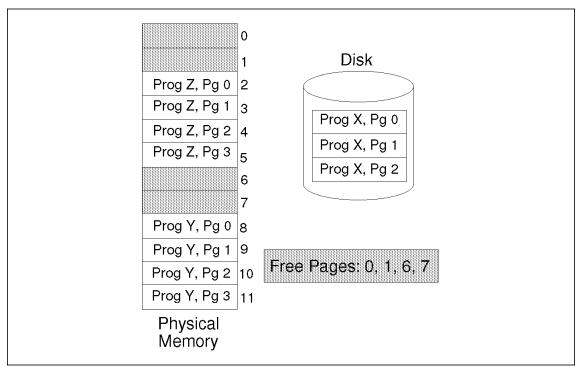

Figure 12. Allocation of Free Pages

One thing the memory subsystem could do is compact the memory. This involves rearranging the programs in memory such that all the free pages are together in one block. But to do this involves a lot of effort and time spent by the CPU.

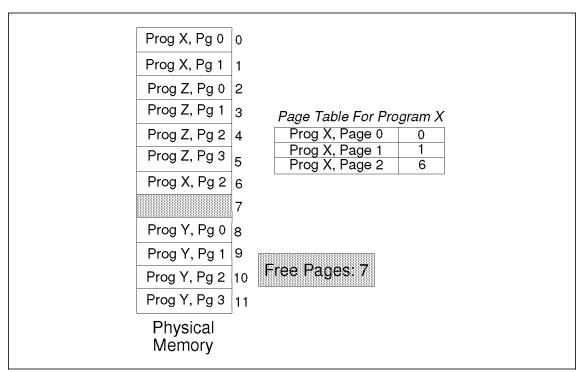

A more popular method is to place the pages of the program wherever there are free pages in memory. There is no need to place them in contiguous locations. The operating system keeps track of where the pages are by maintaining a page table.

Figure 13. Tracking Page Allocation with Page Tables

Figure 13 shows how Program X can be loaded without having to put it into contiguous pages of memory. A page table is maintained for X showing the pages and where they are kept in memory. By maintaining page tables like this for all the programs, pages can be loaded anywhere in memory.

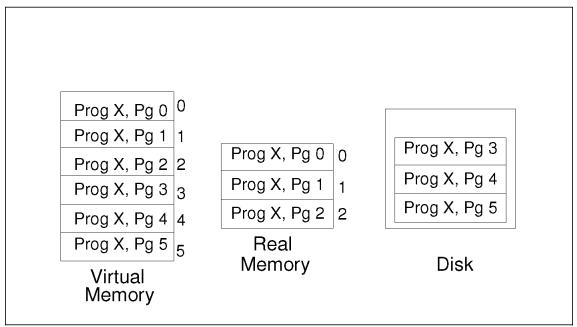

## 2.2.6 Virtual Memory and Demand Paging

Physical memory is relatively expensive to implement compared to fixed disks. Typically, the amount of real memory installed in modern personal computers amount to no more than tens of megabytes. Fixed disk sizes are typically hundreds of megabytes or even gigabytes.