# THEORY OF PROGRAMMING

**FOR**

# AN/FSQ-7 COMBAT DIRECTION CENTRAL AND AN/FSQ-8 COMBAT CONTROL CENTRAL

1 APRIL 1959

This document contains information of a proprietary nature. Any use or reproduction of this document for other than government purposes is subject to the prior consent of International Business Machines Corporation.

MILITARY PRODUCTS DIVISION

INTERNATIONAL BUSINESS MACHINES CORPORATION

KINGSTON, NEW YORK

Reproduction for non-military use of the information or illustrations contained in this publication is not permitted without specific approval of the issuing service (BuAer or USAF). The policy for use of classified publications is established for the Air Force in AFR 205-1 and for the Navy in Navy Regulations, Article 1509.

#### LIST OF REVISED PAGES-

#### INSERT LATEST REVISED PAGES. DESTROY SUPERSEDED PAGES.

NOTE: The portion of the text affected by the current revision is indicated by a vertical rule in the left margin of a left-hand page and in the right margin of a right-hand page.

#### **CONTENTS**

| Heading |                                           | Page |

|---------|-------------------------------------------|------|

| PART 1  | INTRODUCTION                              | . 1  |

| CHAPT   | ER 1 PURPOSE AND SCOPE                    | . 1  |

| 1.1     | Purpose                                   | . 1  |

| 1.2     | Scope                                     | . 1  |

| CHADT   | ER 2 DIGITAL COMPUTERS                    | 3    |

| 2.1     | History of Digital Computers              |      |

| 2.2     | Digital Computer Operation                |      |

| СНАРТ   | ER 3 NUMBER SYSTEMS                       | . 9  |

| 3.1     | General Description                       | . 9  |

| 3.2     | Decimal Number System                     | 9    |

| 3.3     | Binary Number System                      | 9    |

| 3.4     | Octal Number System                       | . 18 |

| СНАРТ   | ER 4 THE SAGE SYSTEM                      | 18   |

| 4.1     | The Air Defense Problem                   | 23   |

| 4.2     | Elements of SAGE                          | 23   |

| 4.3     | Logical Elements of AN/FSQ-7 and AN/FSQ-8 | 23   |

| PART 2  | 2 BASIC PROGRAMMING                       | 27   |

| CHAPT   | ER 1 INTRODUCTION                         | 27   |

| 1.1     | General                                   | 27   |

| 1.2     | Computer Word Description                 | 27   |

| 1.2.1   | Instruction Words                         | 27   |

| 1.2.2   | Data Words                                | 29   |

| 1.3     | Central Computer Timing                   | 29   |

| 1.3.1   | Machine Timing                            |      |

| 1.3.2   | Memory Timing                             |      |

| 1.3.3   | Instruction Timing                        |      |

| 1.4     | Central Computer System Analysis          | 31   |

| Heading |                                    | Page |

|---------|------------------------------------|------|

| 1.4.1   | Memory Element                     | 32   |

| 1.4.1.1 | General                            | 32   |

| 1.4.1.2 | Core Memory                        | 32   |

| 1.4.1.3 | Test Memory                        | 35   |

| 1.4.1.4 | Clock Register                     |      |

| 1.4.1.5 | Memory Buffer Register             | 35   |

| 1.4.1.6 | Memory Address Register            | 35   |

| 1.4.1.7 | Memory Addresses                   | 35   |

| 1.4.2   | Instruction Control Element        | 36   |

| 1.4.3   | Program Element                    | 36   |

| 1.4.3.1 | General                            |      |

| 1.4.3.2 | Program Counter                    | 36   |

| 1.4.3.3 | Address Register                   |      |

| 1.4.3.4 | Index Registers                    | 36   |

| 1.4.4   | Arithmetic Element                 |      |

| 1.4.4.1 | General                            | 36   |

| 1.4.4.2 | A Registers                        | 36   |

| 1.4.4.3 | Adders                             | 36   |

| 1.4.4.4 | Accumulators                       | 38   |

| 1.4.4.5 | B Registers                        | 38   |

| 1.4.5   | Selection Element                  |      |

| 1.4.6   | IO Element                         | 38   |

| 1.4.7   | Overall System Information Flow    | 38   |

| CHAPTER | 2 BASIC INSTRUCTIONS               | 39   |

| 2.1     | General                            | 39   |

| 2.2     | Halt Instruction                   | 39   |

| 2.3     | Clear and Add Instruction          | 39   |

| 2.4     | Add Instruction                    | 39   |

| 2.5     | Full Store Instruction             | 40   |

| 2.6     | Sample Programs Involving Addition | 40   |

| 2.7     | Clear and Subtract Instruction     | 41   |

| 2.8     | Subtract Instruction               | 41   |

| 2.9     | Twin and Add Instruction           | 41   |

| 2 10    | Twin and Subtract Instruction      | /1   |

| Head | ding     |                                                      | Page |

|------|----------|------------------------------------------------------|------|

|      | 2.11     | Sample Programs Involving Subtraction and Twinning   | 41   |

|      | 2.12     | Left Store Instruction                               | 42   |

|      | 2.13     | Right Store Instruction                              | 42   |

|      | 2.14     | Sample Programs Involving Half-Word Storage          | 42   |

|      | 2.15     | Branch Instructions                                  |      |

|      | 2.15.1   | General                                              | 43   |

|      | 2.15.2   | Branch on Left Minus Instruction                     |      |

|      | 2.15.3   | Branch on Right Minus Instruction                    |      |

|      |          | ,                                                    |      |

|      | 2.15.4   | Table Construction Program                           |      |

|      | 2.15.4.1 | Preliminary Flow Chart                               |      |

|      | 2.15.4.2 | Final Flow Chart                                     | 44   |

|      | 2.15.5   | Number-Sorting Program                               | 46   |

|      | 2.15.5.1 | Preliminary Flow Chart                               | 46   |

|      | 2.15.5.2 | Final Flow Chart                                     | 46   |

|      | 2.15.6   | Branch on Full Minus Instruction                     | 48   |

|      | 2.15.7   | Branch on Full Zero Instruction                      | 48   |

|      | 2.15.8   | Sample Program Using BFM and BFZ Instructions        | 49   |

|      | 2.16     | Add One Right Instruction                            | 50   |

|      | 2.16.1   | Uses of the AOR Instruction                          | 51   |

|      | 2.16.2   | Address Modification Using the AOR Instruction       | 51   |

|      | 2.16.3   | Counting by Use of the AOR Instruction               | 53   |

|      | 2.17     | Indexing                                             | 53   |

|      | 2.17.1   | General                                              | 53   |

|      | 2.17.2   | Reset Index Register Instruction                     | 56   |

|      | 2.17.3   | Branch on Positive Index Instruction                 |      |

|      | 2.17.3.1 | General                                              |      |

|      | 2.17.3.2 | Applications of the BPX Instruction                  | 57   |

|      | 2.17.4   | Using the BPX Instruction as an Unconditional Branch |      |

|      | 2.18     | Summary of Basic Instructions                        |      |

| PA   | ART 3    | PROGRAMMING THE CENTRAL COMPUTER SYSTEM              | 61   |

| C    | HAPTE    | R 1 GENERAL DESCRIPTION                              | 61   |

|      | 1.1      | Purpose of Central Computer System                   | 61   |

|      | 1,2      | System Requirements                                  | 61   |

| C    | HAPTE    | R 2 INDEXING TECHNIQUES                              | 63   |

|      | 2.1      | General                                              | 63   |

| Headin | g      |                                                         | Page |

|--------|--------|---------------------------------------------------------|------|

| 2.     | .2     | Additional Uses of the BPX Instruction                  | . 63 |

| 2.     | 3      | Reset Index Register from Right Accumulator Instruction | . 63 |

| 2.     | 4      | Using the Right Accumulator as an Index Register        | . 66 |

| 2.     | 4.1    | Table Lookup Procedure                                  | . 66 |

| 2.     | 4.2    | Table Makeup Procedure                                  | . 67 |

| 2.     | 5      | Store Address Instruction                               | . 68 |

| 2.     | 6      | Add Index Register Instruction                          | . 68 |

| 2.     | 6.1    | Instruction Analysis                                    | . 68 |

| 2.     | 6.2    | Programmed Use of the ADX Instruction                   | . 69 |

| 2.     | 7      | Summary of Indexing Techniques                          | 71   |

| CH     | APTER  | 3 INSTRUCTIONS                                          | . 73 |

| 3.     | 1      | Clear and Add Magnitude Instruction                     | . 73 |

| 3.     | 2      | Difference Magnitude Instruction                        | . 73 |

| 3.     | 3      | Program Example Using Absolute Magnitudes               | . 73 |

| 3.     | 4      | Add B Registers Instruction                             | . 74 |

| 3.     | 5      | Multiply Instruction                                    | . 74 |

| 3.     | 6      | Twin and Multiply Instruction                           | 74   |

| 3.     | 7      | Divide Instruction                                      | 74   |

| 3.     | 8      | Twin and Divide Instruction                             | . 76 |

| 3.     | 9      | Shift Left and Round Instruction                        | . 76 |

| 3.     | 9.1    | General                                                 | . 76 |

| 3.     | 9.2    | Execution                                               | . 76 |

| 3.     | 10     | Sample Programs Involving Multiplication and Division   | . 76 |

| 3.     | 10.1   | Multiplication Programs                                 | 76   |

| 3.     | 10.1.1 | Basic Multiplication                                    | 76   |

| 3.     | 10.1.2 | Function Evaluation Programs                            | 76   |

| 3.     | 10.1.3 | Co-ordinate Conversion Program                          | . 77 |

| 3.     | 10.2   | Division Programs                                       | . 78 |

| 3.     | 10.2.1 | Requirements for Division                               | . 78 |

| 3.     | 10.2.2 | Division Example                                        | . 78 |

| 3.     | 11     | Shift Instructions                                      |      |

| 3.     | 11.1   | General                                                 | . 79 |

| 3.     | 11.2   | Dual Shift Left Instruction                             | . 79 |

| 3.     | 11.3   | Dual Shift Right Instruction                            |      |

| Heading  |                                                 | Page |

|----------|-------------------------------------------------|------|

| 3.11.4   | Left Element Shift Right Instruction            | . 79 |

| 3.11.5   | Right Element Shift Right Instruction           | 79   |

| 3.11.6   | Accumulators Shift Left Instruction             | 80   |

| 3.11.7   | Accumulators Shift Right Instruction            | 81   |

| 3.11.8   | Program Examples of Shift Instruction           | 81   |

| 3.12     | Cycle Instructions                              | 83   |

| 3.12.1   | General                                         | 83   |

| 3.12.2   | Dual Cycle Left Instruction                     | 83   |

| 3.12.3   | Full Cycle Left Instruction                     | 83   |

| 3.12.4   | Examples of Cycle Instructions                  | 84   |

| 3.13     | Logical Instructions                            | 85   |

| 3.13.1   | General                                         | 85   |

| 3.13.2   | Extract Instruction                             | 85   |

| 3.13.2.1 | Execution                                       | 85   |

| 3.13.2.2 | Program Example                                 | 85   |

| 3.13.3   | Load B Registers Instruction                    | 86   |

| 3.13.4   | Deposit Instruction                             | 86   |

| 3.13.4.1 | Execution                                       | 86   |

| 3.13.4.2 | Program Example                                 | 87   |

| 3.13.4.3 | Summary of Deposit Instruction                  | 87   |

| 3.14     | Exchange Instruction                            | 88   |

| 3.14.1   | Execution                                       | 88   |

| 3.14.2   | Use of Exchange Instruction                     | 89   |

| 3.15     | Compare Instructions                            | 89   |

| 3.15.1   | General                                         | 89   |

| 3.15.2   | Basic Compare Instructions                      | 89   |

| 3.15.2.1 | Compare Left Half-Words Instruction             | 89   |

| 3.15.2.2 | Compare Right Half-Words Instruction            | 89   |

| 3.15.2.3 | Compare Full Words Instruction                  | 89   |

| 3.15.2.4 | Compare Masked Bits Instruction                 | 90   |

| 3.15.2.5 | Program Examples                                | 90   |

| 3.15.3   | Compare Difference Instructions                 | 91   |

| 3.15.3.1 | Compare Difference Left Half-Words Instruction  | 91   |

| 3.15.3.2 | Compare Difference Right Half-Words Instruction |      |

| Head | ding     |                                            | Page  |

|------|----------|--------------------------------------------|-------|

|      | 3.15.3.3 | Compare Difference Full Words Instruction  | 92    |

|      | 3.15.3.4 | Compare Difference Masked Bits Instruction | 92    |

|      | 3.15.3.5 | Program Examples                           | 92    |

|      | 3.16     | Test Bits Instruction                      | 93    |

|      | 3.16.1   | Test One Bit Instruction                   | 93    |

|      | 3.16.2   | Test Two Bits Instruction                  | 94    |

|      | 3.16.3   | Bit Selection for TOB and TTB Instructions | 94    |

|      | 3.16.4   | Program Examples                           | 94    |

|      | 3.17     | Clear and Add Clock Instruction            |       |

|      | 3.17.1   | Execution                                  | 96    |

|      | 3.17.2   | Interpretation of Clock Register Contents  | 96    |

|      | 3.17.3   | Program Example                            |       |

|      | 3.18     | Operate Instruction                        |       |

|      | 3.18.1   | Condition Lights (1-4)                     |       |

|      | 3.18.2   | Set Inactivity                             |       |

|      | 3.18.3   | Reset Inactivity                           |       |

|      | 3.18.4   | Intercommunication Flip-Flops (1-4)        |       |

|      | 3.18.5   | Test Clock Register                        |       |

|      | 3.18.6   | Inhibit Alarms                             |       |

|      | 3.18.7   | Reset Alarms                               | 100   |

|      | 3.18.8   | Generate Alarm 1 and 2                     |       |

|      | 3.19     | Branch on Sense Instruction                |       |

|      | 3.19.1   | Condition Lights ON (1-4)                  |       |

|      | 3.19.2   | Inactivity ON                              |       |

|      | 3.19.3   | Left Overflow ON                           |       |

|      | 3.19.4   | Right Overflow ON                          | . 101 |

|      | 3.19.5   | Memory Parity Error                        |       |

|      | 3.19.6   | Addressable Drum Parity Error              |       |

|      | 3.19.7   | Tape Parity Error                          |       |

|      | 3.19.8   | Sense Switch ACTIVE (1-4)                  |       |

|      | 3.19.9   | Status Drum Parity Error                   | . 102 |

|      | 3.19.10  | Duplex Switching Completed ACTIVE          | . 102 |

|      | 3.19.11  | Alarm 1 ON                                 | . 102 |

|      | 3.19.12  | Alarm 2 ON                                 |       |

|      | 3.19.13  | Intercommunication Flip-Flops ON (1-4)     | . 102 |

| Head | ling    |                                      | Page |

|------|---------|--------------------------------------|------|

| C    | HAPTER  | 4 17-BIT ADDRESS SELECTION           | 103  |

|      | 4.1     | General                              | 103  |

|      | 4.2     | Indexing Changes                     | 103  |

|      | 4.3     | Other Registers Changed              | 104  |

|      | 4.3.1   | Address Register                     | 104  |

|      | 4.3.2   | Program Counter                      | 104  |

|      | 4.3.3   | Right A Register                     | 104  |

|      | 4.4     | Instruction Options                  | 104  |

|      | 4.4.1   | STA Option                           | 104  |

|      | 4.4.2   | AOR Option                           | 104  |

|      | 4.4.3   | RST Option                           | 104  |

|      | 4.4.4   | ADD, SUB, and ADB Option             | 104  |

|      | 4.5     | Overflow Control                     | 104  |

|      | 4.6     | Instruction Summary                  | 105  |

|      | RT 4    | PROGRAMMING THE INPUT-OUTPUT SYSTEMS |      |

|      | 1.1     | General Information                  |      |

|      | 1.2     | Input-Output Element                 |      |

|      | 1.2.1   | Description                          |      |

|      | 1.2.2   | Break Cycles                         |      |

|      | 1.2.3   | Registers and Counters               | 108  |

|      | 1.2.3.1 | IO Register                          | 108  |

|      | 1.2.3.2 | IO Buffer Register                   | 108  |

|      | 1.2.3.3 | IO Address Counter                   | 108  |

|      | 1.2.3.4 | IO Word Counter                      | 109  |

|      | 1.2.4   | Control Circuitry                    | 109  |

|      | 1.2.4.1 | Break Command Generators             |      |

|      | 1.2.4.2 | Data Transfer Control Circuits       | 109  |

|      | 1.3     | IO Instructions                      | 109  |

|      | 1.3.1   | Select Instruction                   | 109  |

|      | 1.3.2   | Select Drums Instruction             | 109  |

|      | 1.3.3   | Load IO Address Counter Instruction  | 109  |

|      | 1.3.4   | Read Instruction                     | 109  |

| Head | ding    |                                             | Page |

|------|---------|---------------------------------------------|------|

|      | 1.3.5   | Write Instruction                           | 110  |

|      | 1.3.6   | Clear and Subtract Word Counter Instruction | 110  |

|      | 1.4     | IO Programming                              | 110  |

|      | 1.4.1   | General                                     | 110  |

|      | 1.4.2   | Normal Operation                            | 111  |

|      | 1.4.2.1 | Real-Time Considerations                    | 111  |

|      | 1.4.2.2 | Branch IF IO Interlock On Instruction       | 111  |

|      | 1.4.3   | 1O Pause                                    | 112  |

|      | 1.4.4   | IO Hangup                                   | 112  |

|      | 1.4.5   | Use of CSW Instruction                      | 113  |

|      | 1.4.6   | IO Test Instructions                        | 113  |

|      | 1.4.6.1 | General                                     | 113  |

|      | 1.4.6.2 | Select 10 Register Instruction              | 113  |

|      | 1.4.6.3 | Clear IO Interlock Instruction              | 114  |

|      | 1.4.6.4 | Lock IO Address Counter Instruction         | 114  |

| C    | HAPTER  | 2 PROGRAMMING THE AM DRUMS AND IC FIELDS    | 115  |

|      | 2.1     | Auxiliary Memory Drum Fields                | 115  |

|      | 2.1.1   | General                                     | 115  |

|      | 2.1.2   | Program Examples                            | 115  |

|      | 2.2     | Intercommunication Drum Fields              | 116  |

|      | 2.2.1   | General                                     | 116  |

|      | 2.2.2   | Selecting the IC Drum Fields                | 117  |

|      | 2.2.2.1 | Select IC (Other) Field                     | 117  |

|      | 2.2.2.2 | Select IC (Own) Field                       | 117  |

|      | 2.2.2.3 | Select IC (Own Test) Field                  | 117  |

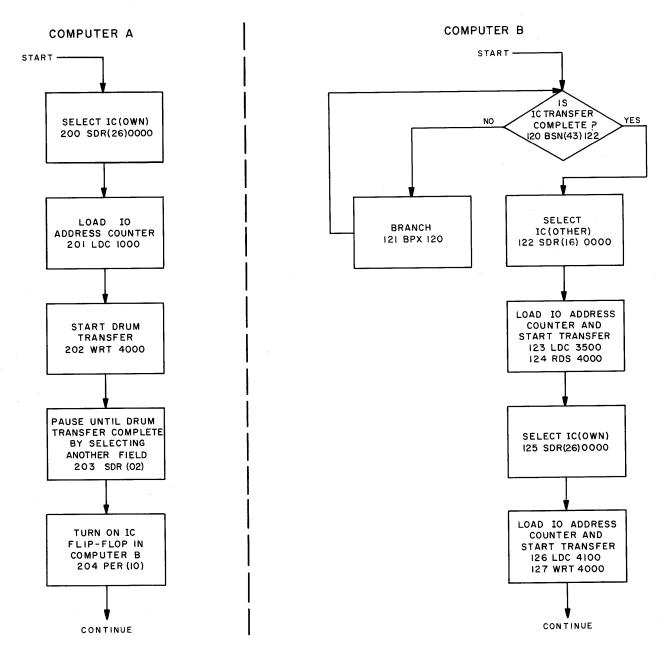

|      | 2.2.3   | Programming IC Transfers                    | 117  |

| C    | HAPTER  | 3 PROGRAMMING CARD MACHINES AND TAPES       | 121  |

|      | 3.1     | Introduction                                | 121  |

|      | 3.2     | Information Storage                         | 121  |

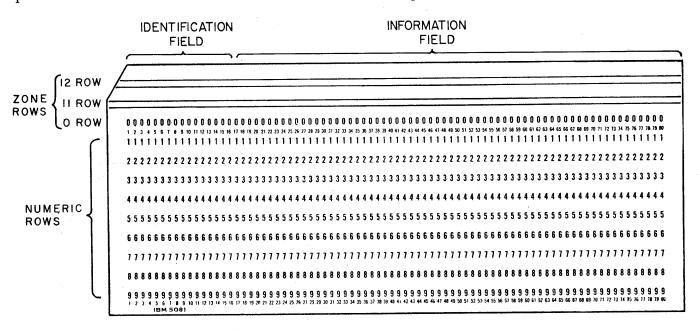

|      | 3.2.1   | Punched Cards                               | 121  |

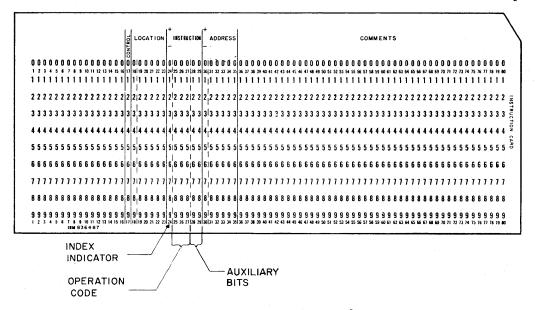

|      | 3.2.1.1 | Instruction Card                            | 122  |

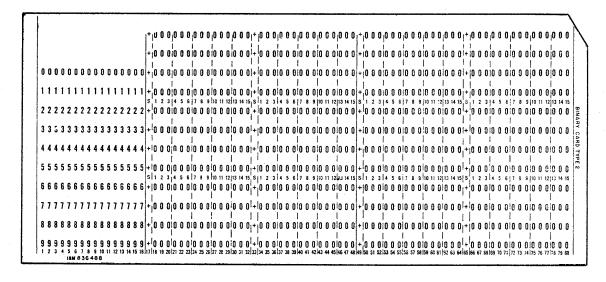

|      | 3.2.1.2 | Binary Card                                 | 122  |

|      | 3.2.1.3 | Octonary Card                               | 123  |

| Head | ding    |                                  | Page |

|------|---------|----------------------------------|------|

|      | 3.2.1.4 | Card Image                       | 125  |

|      | 3.2.2   | Line Printing                    | 125  |

|      | 3.2.3   | Magnetic Tape                    | 125  |

|      | 3.3     | Programming Techniques           | 126  |

|      | 3.3.1   | General                          | 126  |

|      | 3.3.2   | Card Reader                      | 126  |

|      | 3.3.2.1 | Description                      | 126  |

|      | 3.3.2.2 | Selection                        | 126  |

|      | 3.3.2.3 | Sense for Card Reader Not-Ready  | 126  |

|      | 3.3.2.4 | Reading                          | 126  |

|      | 3.3.2.5 | Program Example                  | 126  |

|      | 3.3.3   | Card Punch                       | 127  |

|      | 3.3.3.1 | Description                      | 127  |

|      | 3.3.3.2 | Selection                        | 128  |

|      | 3.3.3.3 | Sense for Card Punch Not-Ready   | 128  |

|      | 3.3.3.4 | Writing                          | 128  |

|      | 3.3.3.5 | Program Examples                 | 130  |

|      | 3.3.4   | Line Printer                     | 131  |

|      | 3.3.4.1 | Description                      | 131  |

|      | 3.3.4.2 | Selection                        | 132  |

|      | 3.3.4.3 | Sense for Line Printer Not-Ready | 133  |

|      | 3.3.4.4 | Writing                          | 133  |

|      | 3.3.4.5 | Program Example                  | 133  |

|      | 3.3.5   | Magnetic Tapes                   | 133  |

|      | 3.3.5.1 | Description                      | 133  |

|      | 3.3.5.2 | Selection                        | 134  |

|      | 3.3.5.3 | Sense for Tape Unit Not-Ready    | 134  |

|      | 3.3.5.4 | Sense for Tape Unit Not-Prepared | 135  |

|      | 3.3.5.5 | Reading                          | 135  |

|      | 3.3.5.6 | Writing                          | 135  |

|      | 3.3.5.7 | Tape Instructions                | 135  |

|      | 3.3.5.8 | Tape Programming                 |      |

| C    | HAPTER  | 4 PROGRAMMING THE INPUT SYSTEM   | 139  |

| •    | 4.1     | Description                      |      |

|      | 4.2     | Data Forms                       | 130  |

| Hea | ding    |                                                     | Page |

|-----|---------|-----------------------------------------------------|------|

|     | 4.2.1   | LRI Data Drum Word Layout                           | 139  |

|     | 4.2.2   | GFI Data Drum Word Layout                           | 140  |

|     | 4.2.3   | XTL Data Drum Word Layout                           | 141  |

|     | 4.3     | Drum Field Selection                                | 141  |

|     | 4.3.1   | LRI Drum Fields                                     | 141  |

|     | 4.3.1.1 | Reading by Status                                   | 142  |

|     | 4.3.1.2 | Reading by Identity                                 | 142  |

|     | 4.3.2   | GFI Drum Field                                      | 143  |

|     | 4.3.3   | XTL Drum Field                                      | 143  |

|     | 4.4     | Input Test Pattern Generator                        | 143  |

|     | 4.4.1   | LRI Testing                                         | 143  |

|     | 4.4.2   | GFI Testing                                         | 144  |

|     | 4.4.3   | XTL Testing                                         | 144  |

| C   | HAPTER  | 5 PROGRAMMING THE OUTPUT SYSTEM                     | 145  |

|     | 5.1     | Description                                         | 145  |

|     | 5.2     | Operation                                           | 145  |

|     | 5.3     | Information Forms                                   | 145  |

|     | 5.3.1   | Bursts                                              | 145  |

|     | 5.3.2   | Output Drum Word                                    | 146  |

|     | 5.4     | Drum Transfers                                      | 146  |

|     | 5.5     | Output Alarms                                       | 147  |

|     | 5.5.1   | Overall Output Alarm                                | 147  |

|     | 5.5.2   | Nonsearch Alarm                                     | 147  |

|     | 5.5.3   | OB Drum Parity Alarm                                | 147  |

|     | 5.5.4   | Illegal Address or Section Alarm                    | 147  |

|     | 5.5.5   | G/G Parity Alarm                                    | 147  |

|     | 5.5.6   | TTY Parity Alarm                                    | 147  |

|     | 5.5.7   | G/A-TD Parity Alarm                                 | 147  |

| (   | CHAPTER | 6 PROGRAMMING THE DISPLAY AND WARNING LIGHT SYSTEMS | 149  |

|     | 6.1     | Description                                         | 149  |

|     | 6.2     | Operation                                           | 149  |

|     | 6.2.1   | General                                             | 149  |

|     | 6.2.2   | Situation Displays                                  | 149  |

| Hea | ding             |                                           | Page |

|-----|------------------|-------------------------------------------|------|

|     | 6.2.3            | Digital Displays                          | 149  |

|     | 6.2.4            | Display Consoles                          | 149  |

|     | 6.2.5            | Manual Inputs                             | 149  |

|     | 6.2.5.1          | General                                   | 149  |

|     | 6.2.5.2          | Light Guns                                | 151  |

|     | 6.2.5.3          | Area Discriminator                        | 151  |

|     | 6.2.5.4          | Manual Input Matrix                       | 151  |

|     | 6.2.6            | Warning Light System                      | 151  |

|     | 6.3              | Message Types                             | 153  |

|     | 6.3.1            | Situation Displays                        | 153  |

|     | 6.3.1.1          | Radar Data Messages                       | 153  |

|     | 6.3.1.2          | Track Data Messages                       | 153  |

|     | 6.3.2            | Digital Displays                          | 154  |

|     | 6.3.3            | Manual Inputs                             | 154  |

|     | 6.3.4            | Warning Lights                            | 154  |

|     | 6.4              | Program Instructions                      | 156  |

|     | 6.4.1            | Situation Displays                        | 156  |

|     | 6.4.1.1          | RD and TD Drum Field Selection            | 156  |

|     | 6.4.1.2          | RD Scan Counter                           | 156  |

|     | 6.4.1.3          | Situation Display Test                    | 156  |

|     | 6.4.1.4          | SD Camera Modes                           | 157  |

|     | 6.4.1.5          | Sense Display                             | 157  |

|     | 6.4.2            | Digital Displays                          | 157  |

|     | 6.4.2.1          | DD Drum Field Selection                   | 157  |

|     | 6.4.2.2          | DD Drum Field Test Selection              | 157  |

|     | 6.4.2.3          | Start Digital Display Sections (1 and 2)  | 157  |

|     | 6.4.3            | Manual Inputs                             | 157  |

|     | 6.4.3.1          | MI Drum Field Selection                   | 157  |

|     | 6.4.3.2          | Area Discriminator Operation              | 157  |

|     | 6.4.3.3          | Manual Input Matrix Selection             | 157  |

|     | 6.4.4            | Warning Lights                            | 157  |

| C   | HAPTER           | 7 PROGRAMMING THE MARGINAL                |      |

|     | 7 1              | CHECKING SYSTEM Introduction              |      |

|     | 7.1<br>7.2       | Introduction Programmed Marginal Checking |      |

|     | / • <del>4</del> | 1081mined marginar checking               | エノソ  |

| Heading |                                 | Page |

|---------|---------------------------------|------|

| 7.2.1   | General                         | 159  |

| 7.2.2   | Excursion Application           | 159  |

| 7.2.3   | Excursion Removal               | 161  |

| 7.2.4   | Excursion Detection             | 162  |

| 7.2.5   | Use of the LS Bit               | 162  |

| 7.2.6   | Restarts                        | 162  |

| 7.2.7   | Time Duration                   | 163  |

| 7.2.8   | Polarity                        | 163  |

| 7.2.9   | Safe Limit                      | 163  |

| 7.2.10  | Excursion Magnitude             | 163  |

| 7.3     | Instruction Summary             | 163  |

| PART 5  | ADVANCED PROGRAMMING METHODS    | 165  |

| CHAPTE  | R 1 UTILITY SYSTEMS             | 165  |

| 1.1     | General                         | 165  |

| 1.2     | Lincoln Utility System          | 165  |

| 1.2.1   | Description and Purpose         | 165  |

| 1.2.2   | Operation                       | 166  |

| 1.2.3   | Internal Program Communication  | 166  |

| 1.2.3.1 | Internal Tags                   | 166  |

| 1.2.3.2 | Pseudo Instructions             | 167  |

| 1.2.3.3 | Location Tags                   | 167  |

| 1.2.3.4 | RC Tags                         | 167  |

| 1.2.3.5 | Temporary Storage Tags          | 167  |

| 1.2.4   | Communication between Programs  | 168  |

| 1.2.4.1 | System Tables                   | 168  |

| 1.2.4.2 | Items                           | 168  |

| 1.2.4.3 | Table Tags                      | 168  |

| 1.2.5   | Communication Tags              | 168  |

| 1.2.5.1 | Compool                         | 168  |

| 1.2.5.2 | Item Tags                       | 168  |

| 1.2.5.3 | Parameter Tags                  | 169  |

| 1.2.6   | Summary of Symbolic Expressions | 169  |

| Headin | ag .   |                                                | Page |

|--------|--------|------------------------------------------------|------|

| СН     | APTER  | 2 SCALING                                      | 171  |

| 2.     | .1     | Introduction                                   | 171  |

| 2.     | .1.1   | General                                        | 171  |

| 2.     | .1.2   | Pure Numbers and Physical Measurements         | 171  |

| 2.     | .1.3   | Scaling for Central Computer System            | 171  |

| 2.     | 1.3.1  | Principle of Scaling                           | 171  |

| 2.     | 1.3.2  | Scaling a Constant                             | 172  |

| 2.     | 1.3.3  | Scaling of Variable Numbers                    | 172  |

| 2.     | 2      | Arithmetic Requirements for Scaling            | 172  |

| 2.     | 2.1    | General                                        | 172  |

| 2.     | 2.2    | Addition and Subtraction                       | 173  |

| 2.     | 2.2.1  | Requirements                                   | 173  |

| 2.     | 2.2.2  | Numerical Example                              | 173  |

| 2.     | 2.2.3  | Other Considerations                           | 173  |

| 2.     | 2.3    | Multiplication                                 | 173  |

| 2.     | 2.3.1  | Requirements                                   | 173  |

| 2.     | 2.3.2  | Numerical Example                              | 174  |

| 2.2    | 2.3.3  | Other Considerations                           | 174  |

| 2.2    | 2.4    | Division                                       | 174  |

| 2.2    | 2.4.1  | Requirements                                   | 174  |

| 2.2    | 2.4.2  | Numerical Example                              | 175  |

| 2.2    | 2.4.3  | Other Considerations                           | 175  |

| 2.     | 3      | Scaling of Combined Operations                 | 175  |

| 2.3    | 3.1    | General                                        | 175  |

| 2.3    | 3.2    | Addition and Subtraction of Several Numbers    | 175  |

| 2.3    | 3.2.1  | Maximum Precision Scaling                      | 175  |

| 2.3    | 3.2.2  | Constant Scaling                               | 176  |

| 2.3    | 3.3    | Multiplication and Division of Several Numbers | 176  |

| 2.3    | 3.4    | Evaluation of a Function                       | 178  |

| 2.4    | í      | Summary                                        | 179  |

| APF    | PENDIX | K A ILLEGAL INSTRUCTIONS                       | 181  |

| A.     |        | C                                              | 181  |

| A.     |        |                                                | 181  |

| A.     | 3      | Illegal Add Class Instructions                 | 181  |

| Heading     |                                     | Page  |

|-------------|-------------------------------------|-------|

| A.4         | Illegal Multiply Class Instructions | . 181 |

| A.5         | Illegal Store Class Instructions    | . 181 |

| A.6         | Illegal Shift Class Instructions    | . 181 |

| <b>A.</b> 7 | Illegal Branch Class Instructions   | . 181 |

| A.8         | Illegal IO Class Instructions       | . 181 |

| A.9         | Illegal Reset Class Instructions    | . 181 |

| INDEX       |                                     | . 183 |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                                     |      |  |

|--------|-----------------------------------------------------------|------|--|

| 1-1    | Representation of Numbers in Digital and Analog Computers | 5    |  |

| 1-2    | Digital Computer, Block Diagram                           | 7    |  |

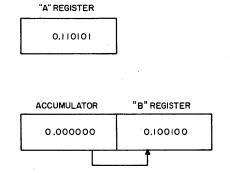

| 1-3    | Registers Used in Multiplication                          | 16   |  |

| 1-4    | Comparison of Binary and Octal Notation                   | 20   |  |

| 1-5    | SAGE System, Simplified Diagram                           | 24   |  |

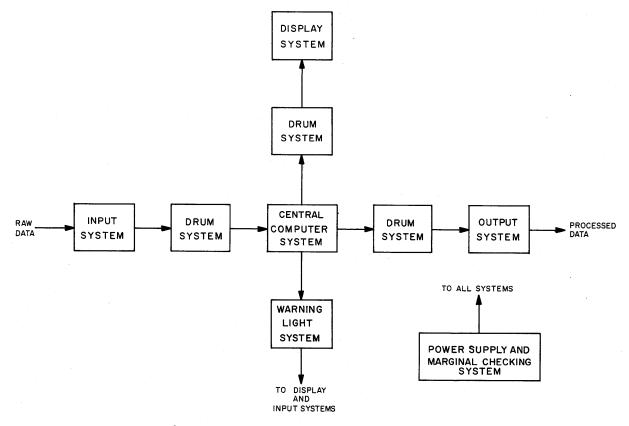

| 16     | AN/FSQ-7, Simplified Block Diagram                        | 25   |  |

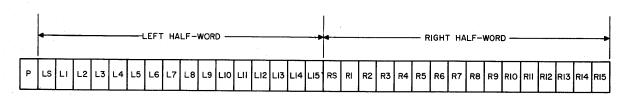

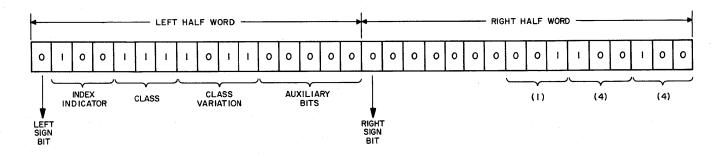

| 2-1    | Computer Word Layout                                      | 27   |  |

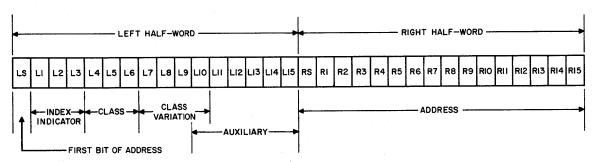

| 2-2    | Instruction Word Layout                                   | 28   |  |

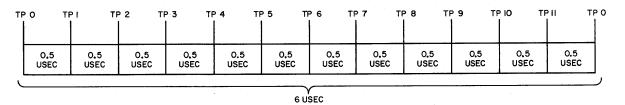

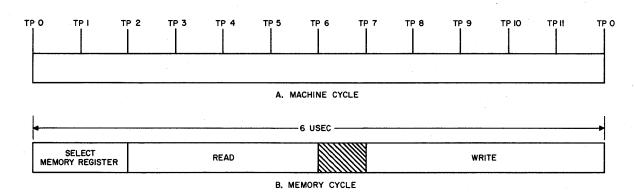

| 2-3    | Basic Machine Cycle                                       | 29   |  |

| 2 -4   | Relationship of Machine Cycle to Memory Cycle             | 30   |  |

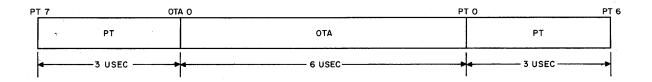

| 2-5    | Cycle Configuration for 2-Cycle Instruction               | 31   |  |

| 2-6    | Various Cycle Configurations for AN/FSQ-7 and AN/FSQ-8    | 31   |  |

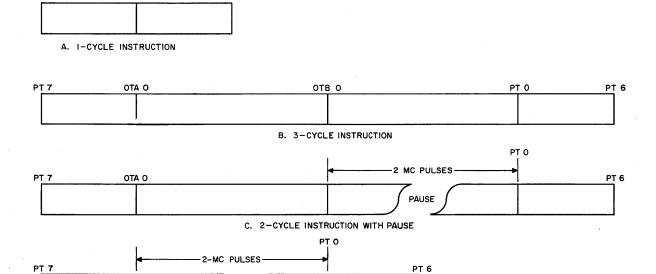

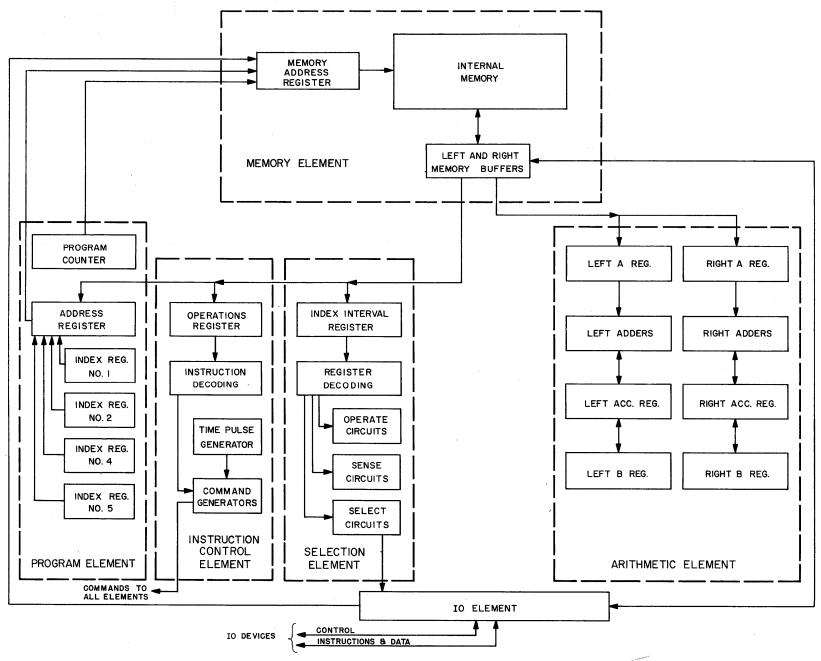

| 2-7    | Central Computer System                                   | 32   |  |

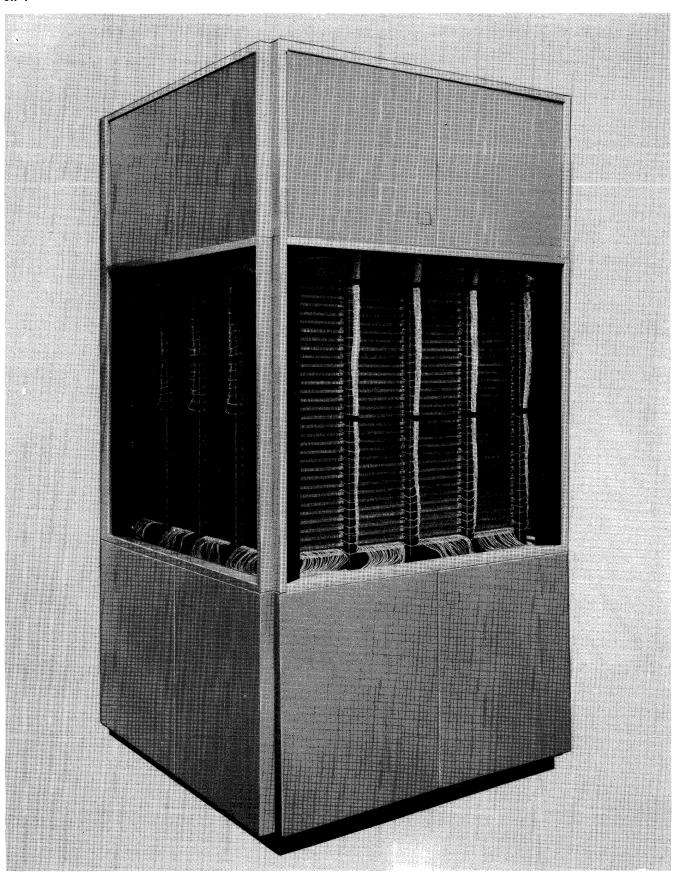

| 2-8    | 256 <sup>2</sup> Memory Unit                              | . 33 |  |

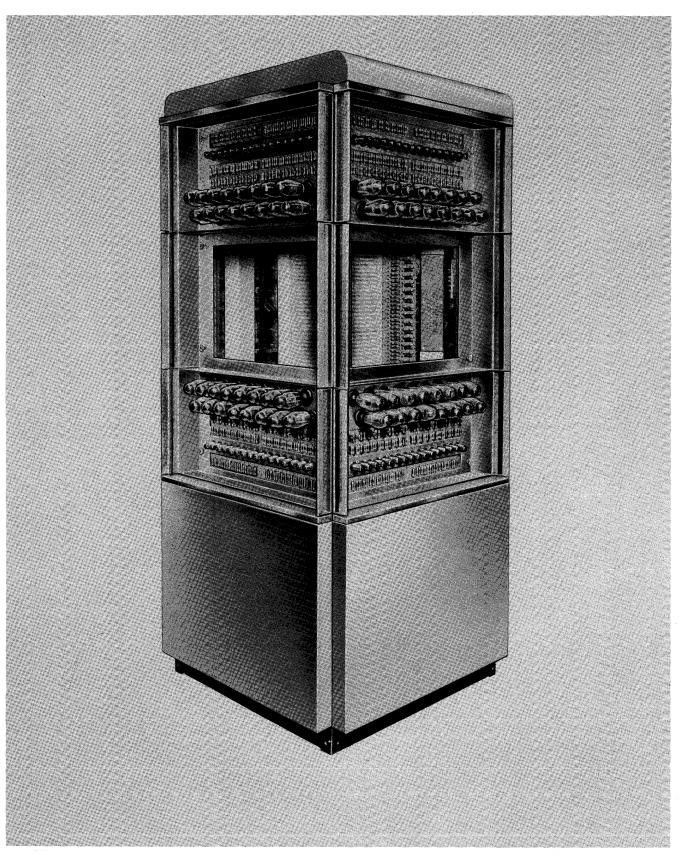

| 2-9    | 642 Memory Unit                                           | 34   |  |

| 2—10   | Overall Information Flow, Central Computer                | . 37 |  |

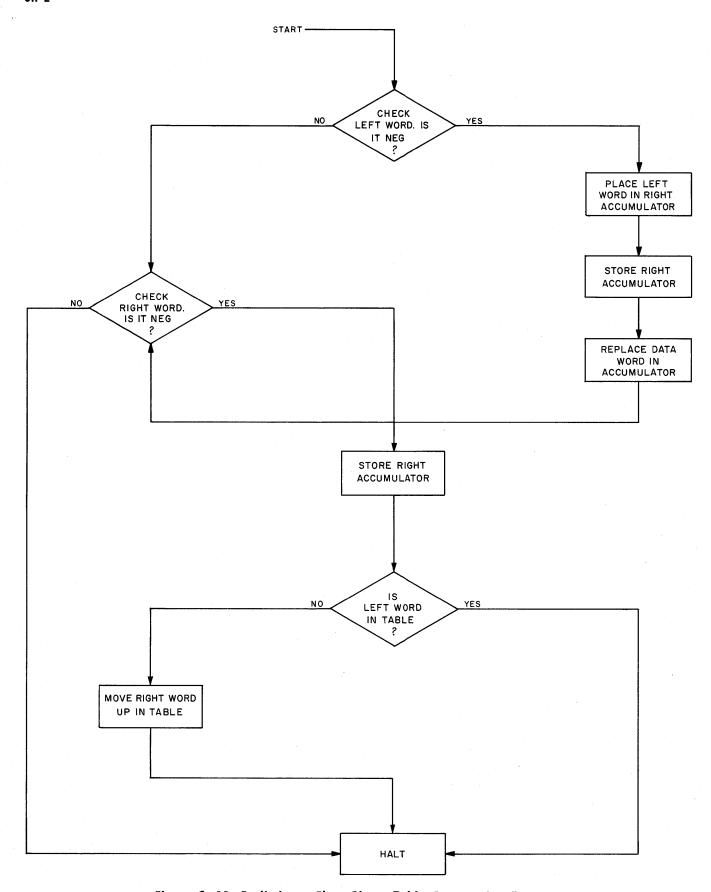

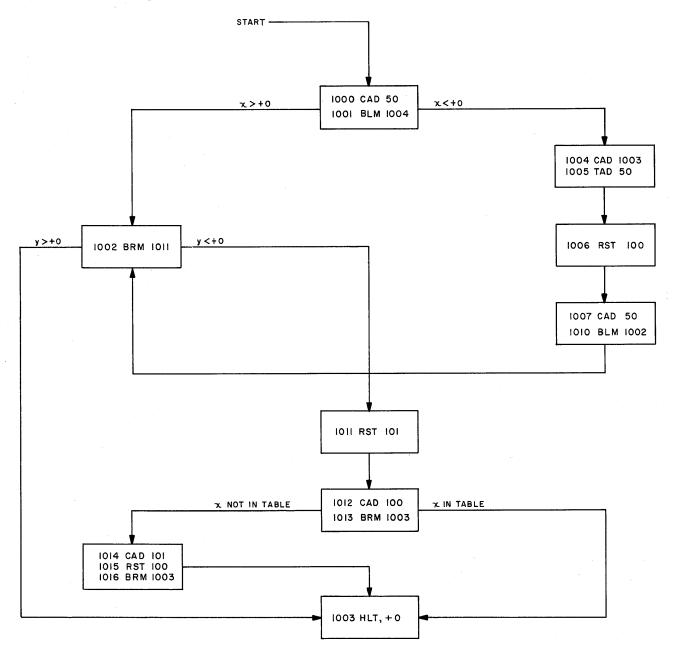

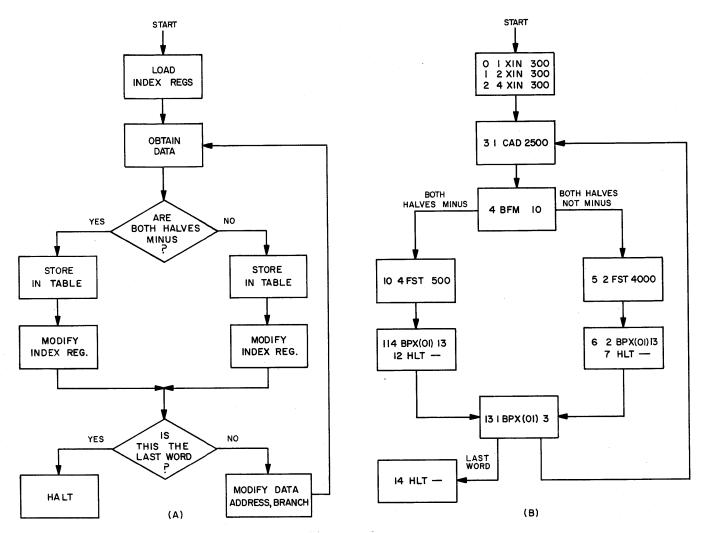

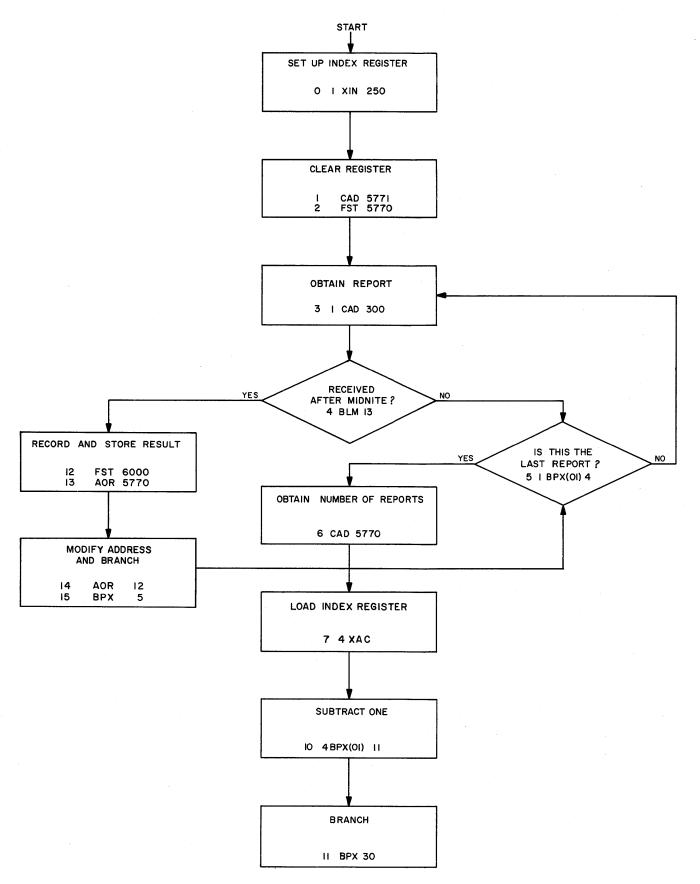

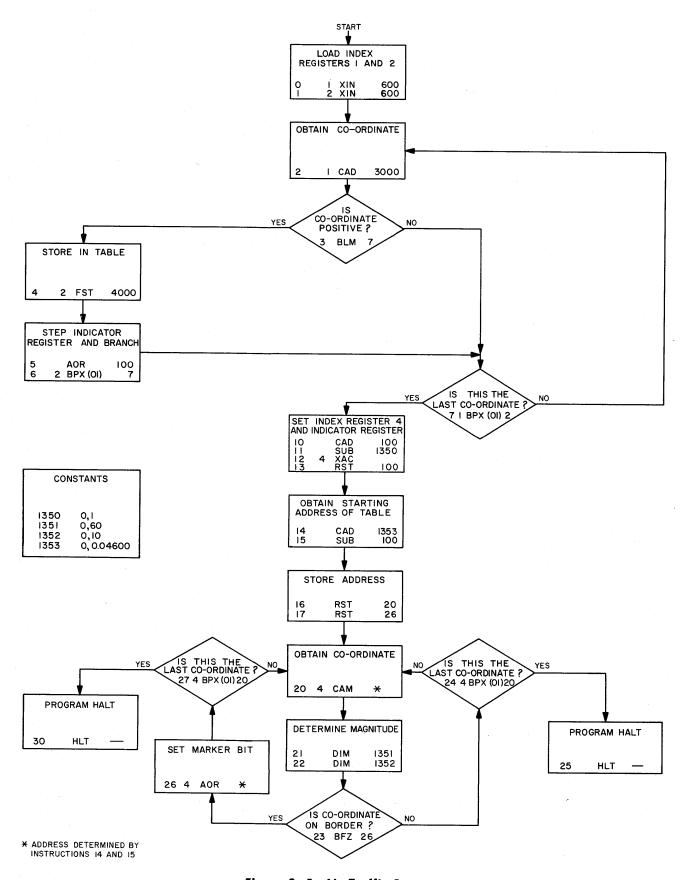

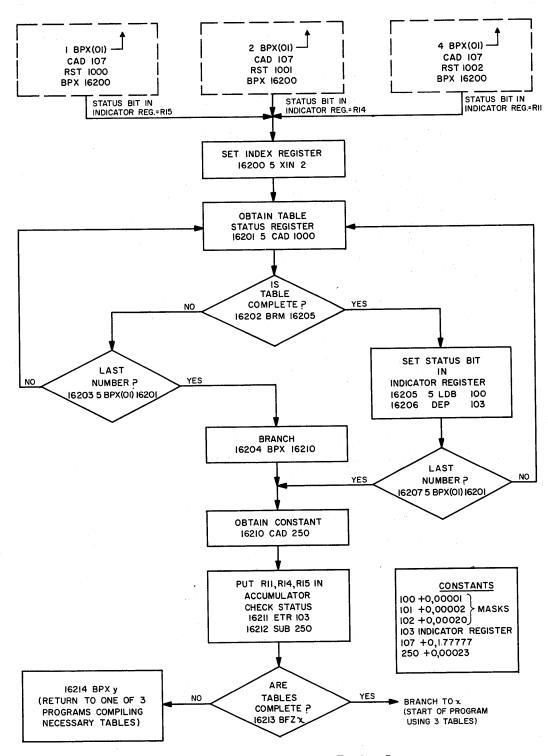

| 2-11   | Preliminary Flow Chart, Table Construction Program        | 45   |  |

| 2-12   | Final Flow Chart, Table Construction Program              | 46   |  |

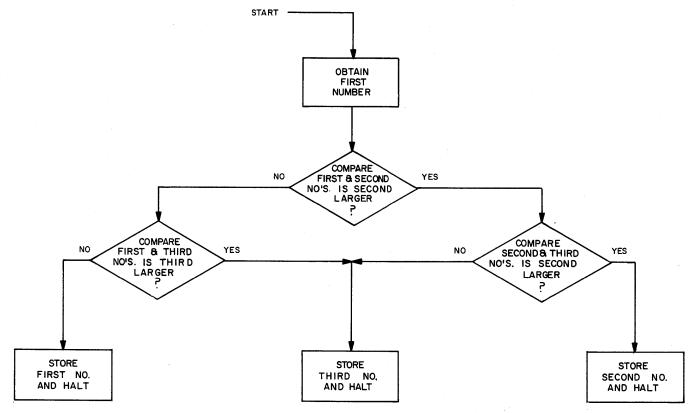

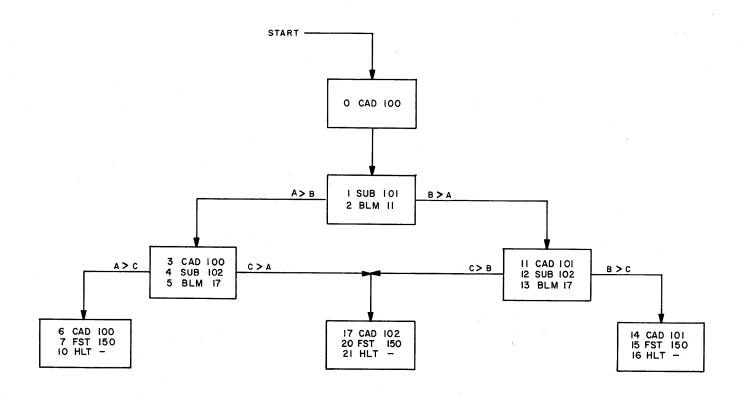

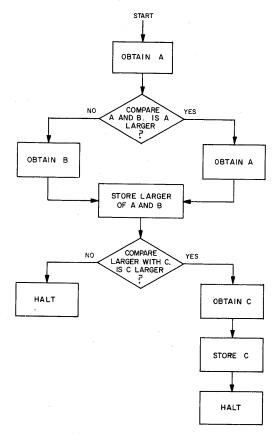

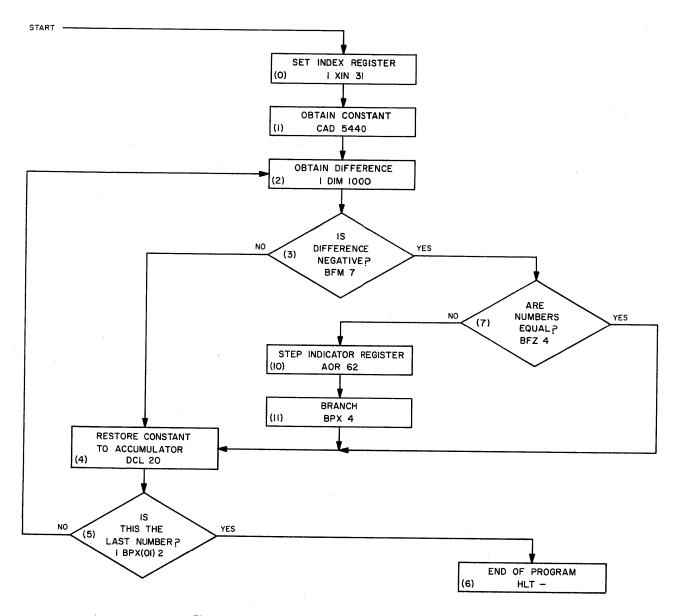

| 2-13   | Preliminary Flow Chart, Number-Sorting Program            | . 47 |  |

| 2-14   | Final Flow Chart, Number-Sorting Program                  | 47   |  |

# LIST OF ILLUSTRATIONS (cont'd)

| Figure | Title                                                                     | Page |

|--------|---------------------------------------------------------------------------|------|

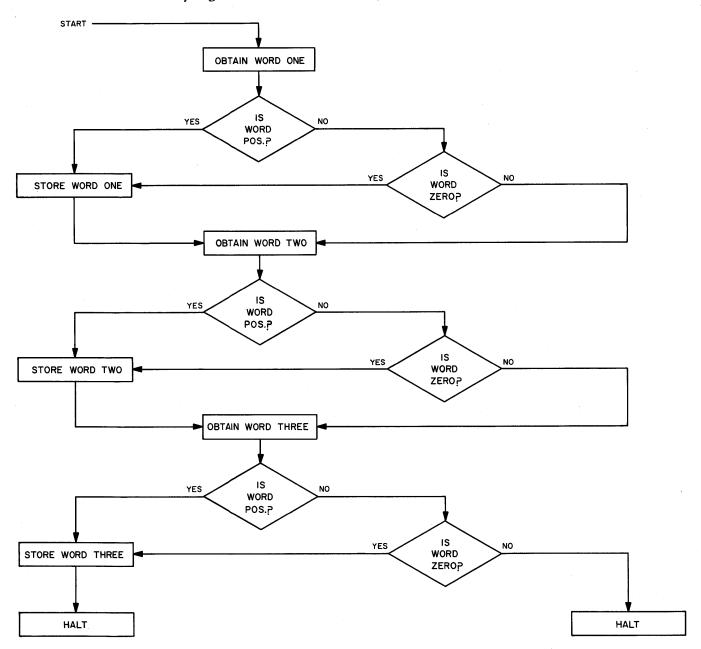

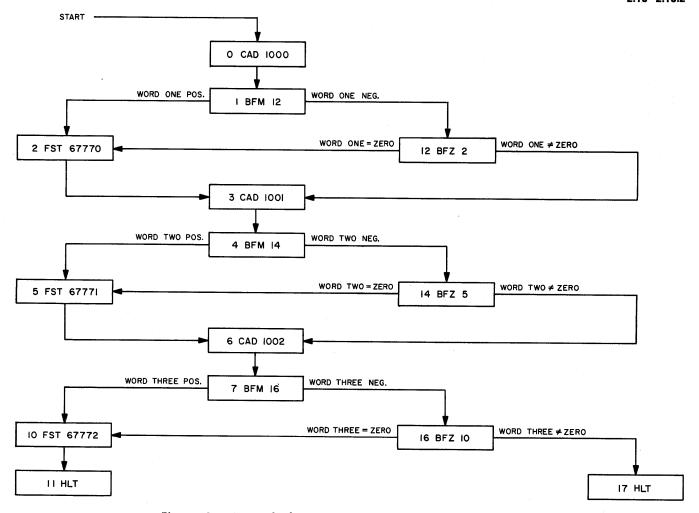

| 2-15   | Preliminary Chart Using Full Branch Instructions                          | 50   |

| 2-16   | Final Flow Chart Using Full Branch Instructions                           | 51   |

| 2-17   | Address Modification Using AOR Instructions                               | 52   |

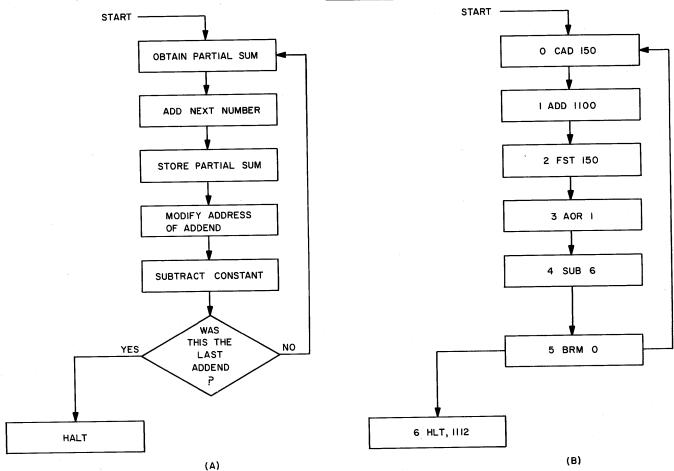

| 2-18   | Counting by Use of the AOR Instruction, Preliminary Flow Chart            | 54   |

| 2-19   | Counting by Use of the AOR Instruction, Final Flow Chart                  | 55   |

| 2-20   | Word Layout for XIN Instruction                                           | 56   |

| 2-21   | Table Sorting by Using the BPX Instruction                                | 58   |

| 2—22   | Number-Sorting Program Using Unconditional Branch, Preliminary Flow Chart | 59   |

| 2-23   | Number-Sorting Program Using Unconditional Branch,<br>Final Flow Chart    | 59   |

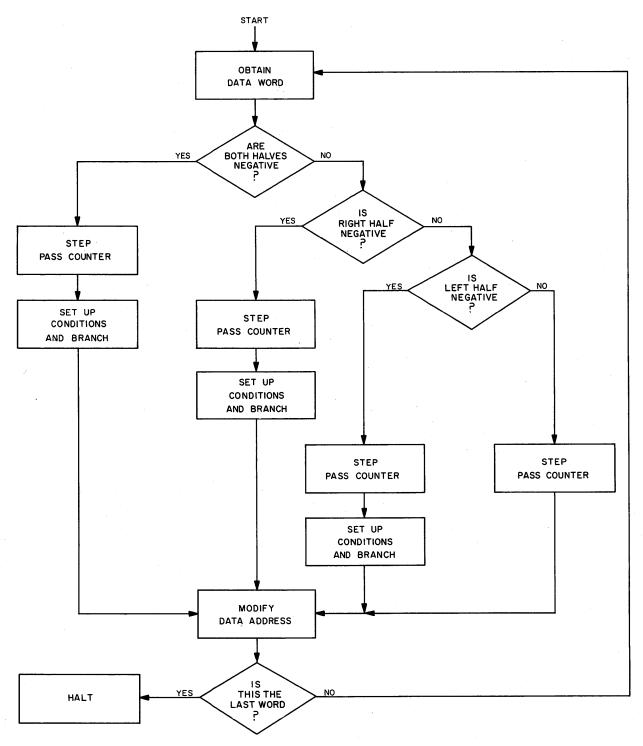

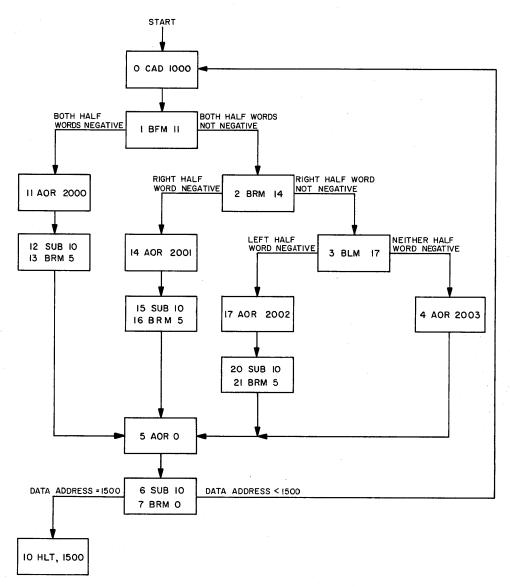

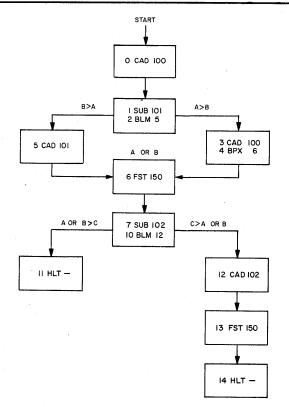

| 3-1    | Data Sorting and Counting Program Flow Chart                              | 65   |

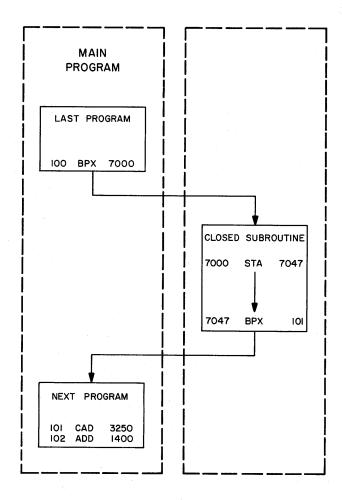

| 3-2    | Use of STA Instruction                                                    | 69   |

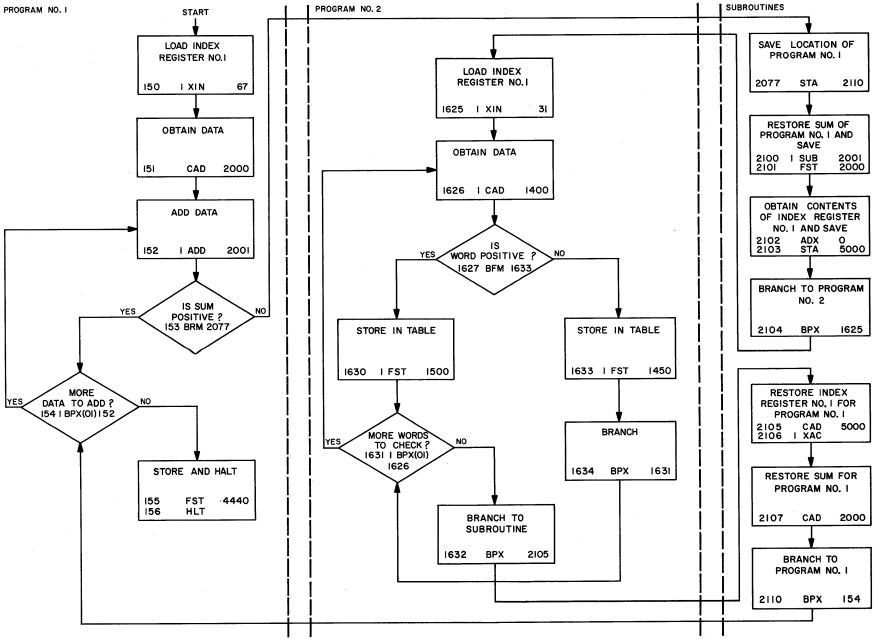

| 3-3    | Flow Chart Showing One Index Register Used in Two Programs                | 70   |

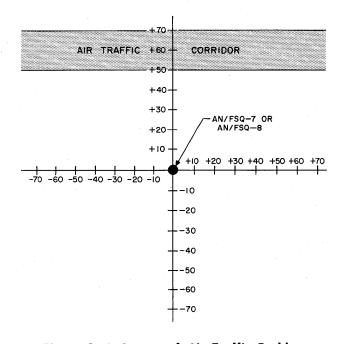

| 3-4    | Layout of Air Traffic Problem                                             | 73   |

| 3-5    | Air Traffic Program                                                       | 75   |

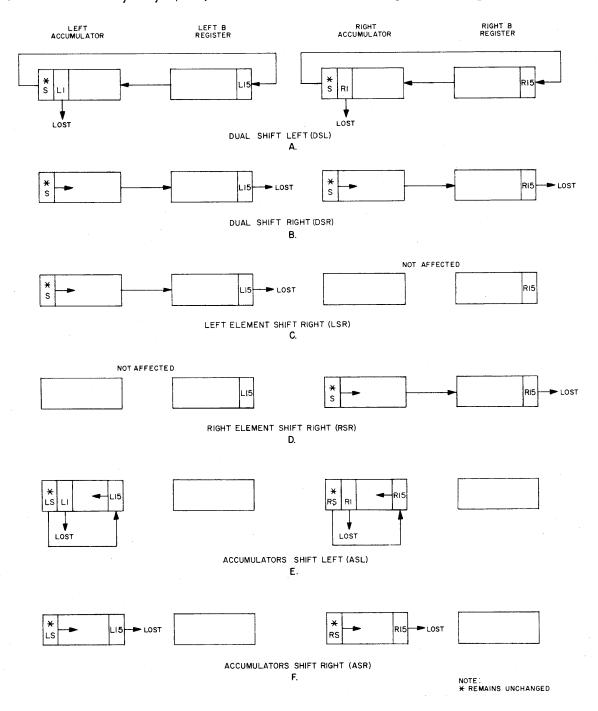

| 3-6    | Execution of Shift Instructions                                           | 80   |

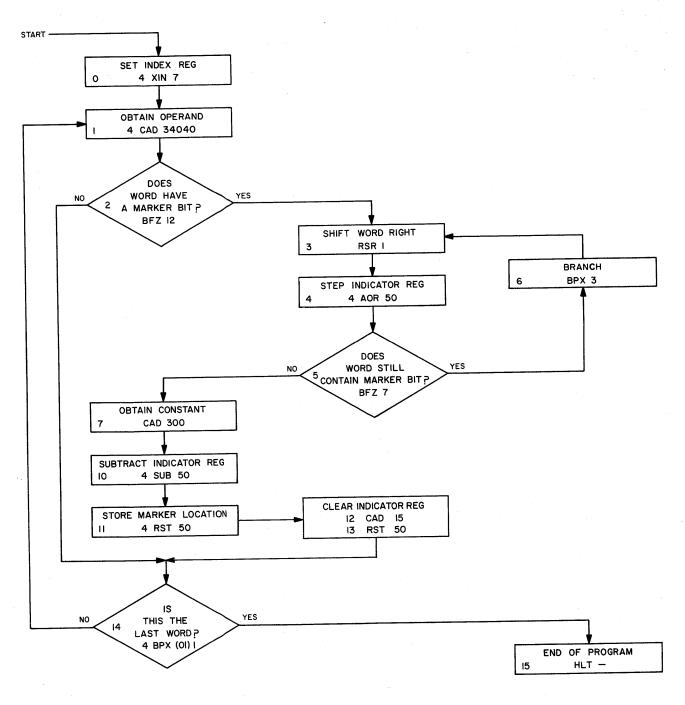

| 3-7    | Magnitude Sorting Program                                                 | 81   |

| 3-8    | Marker Bit Identification Program                                         | 82   |

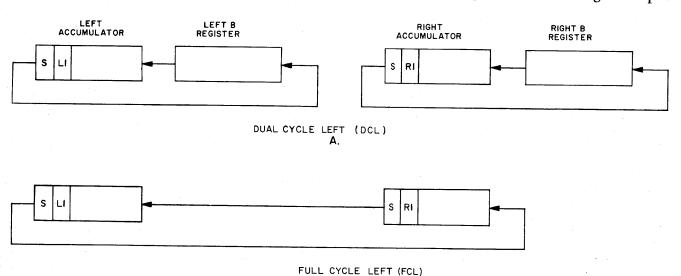

| 3-9    | Execution of Cycle Instructions                                           | 83   |

| 3-10   | Indicator Register Testing Program                                        | 88   |

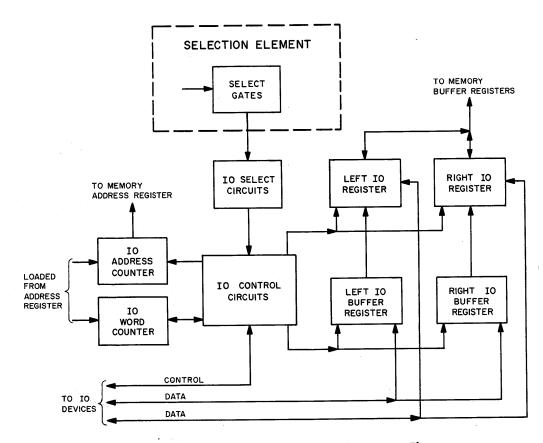

| 4-1    | Input-Output Element, Information Flow                                    | 108  |

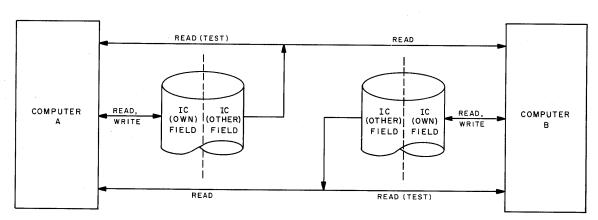

| 4-2    | Relationship of IC Drum Fields                                            | 117  |

| 4-3    | Intercommunication Routine                                                | 118  |

| 4-4    | IBM Card Showing Hollerith Code Zones and Field Division                  | 121  |

| 4-5    | Instruction Card                                                          | 123  |

| 4-6    | Binary Card                                                               | 123  |

| 4-7    | Relation of Card Image to IBM Card                                        | 124  |

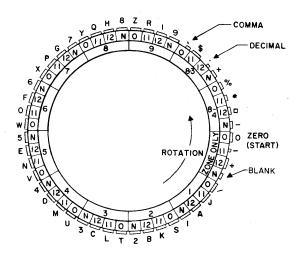

| 4-8    | Type Wheel, Pictorial Diagram                                             | 125  |

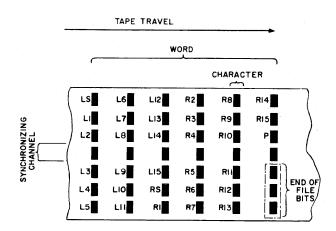

| 4-9    | Tape Word Bit Positions                                                   | 125  |

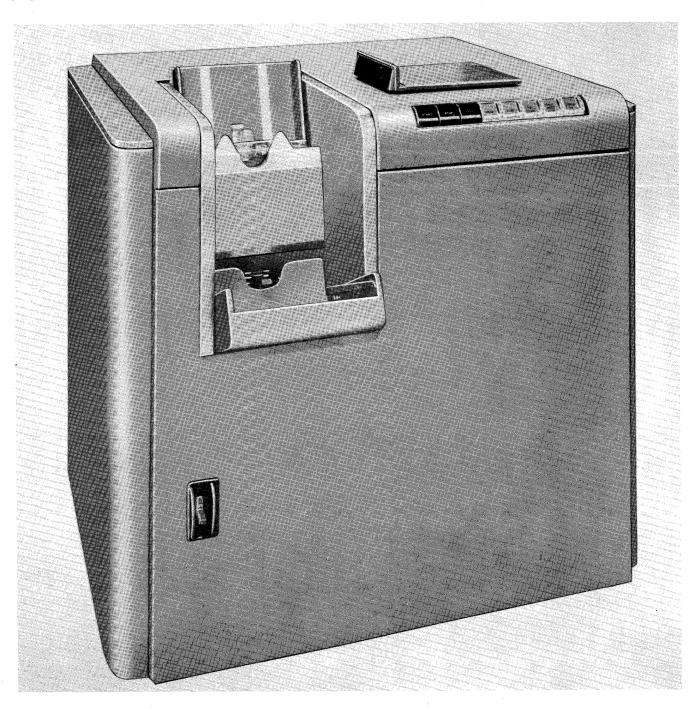

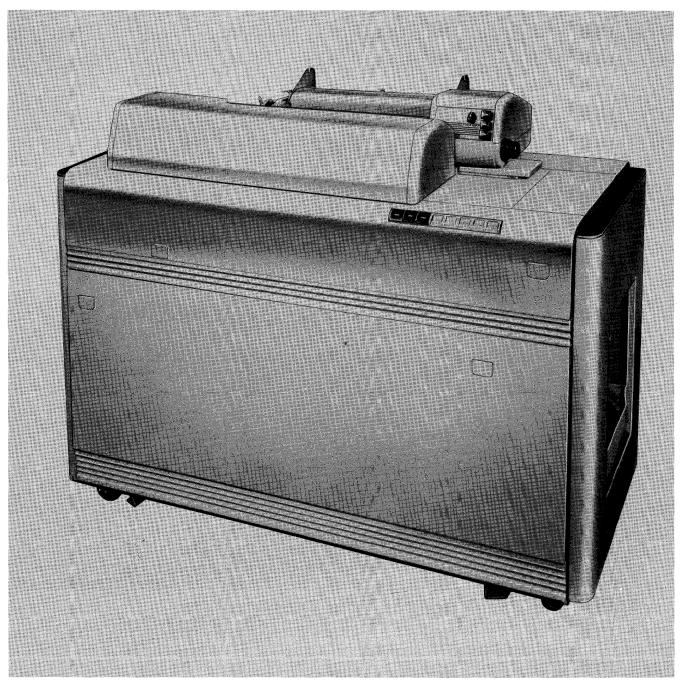

| 4-10   | Card Reader, Type 713                                                     | 127  |

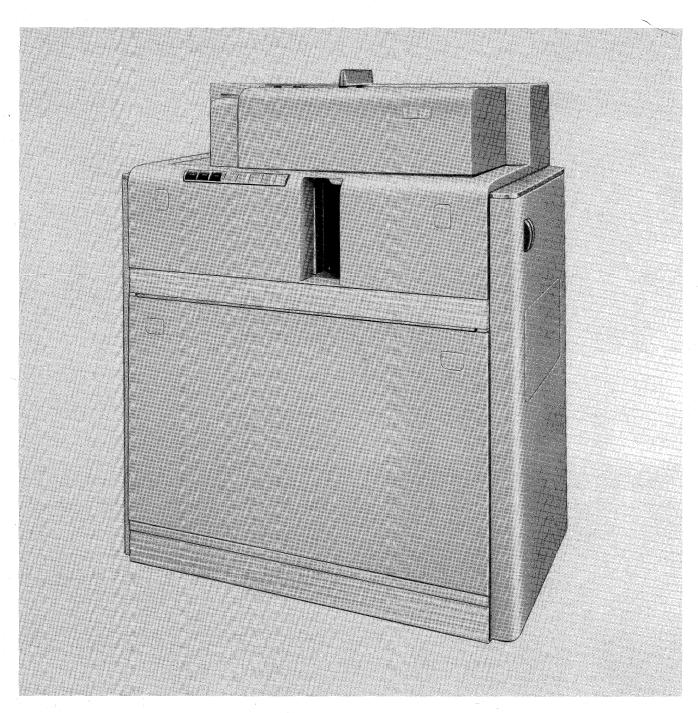

| 4-11   | Card Punch, Type 723                                                      | 129  |

| 4-12   | IBM Card Punched in Identity Field                                        | 131  |

#### LIST OF ILLUSTRATIONS (cont'd)

| Figure | Title                                                          | Page |

|--------|----------------------------------------------------------------|------|

| 4-13   | Line Printer, Type 718                                         | 132  |

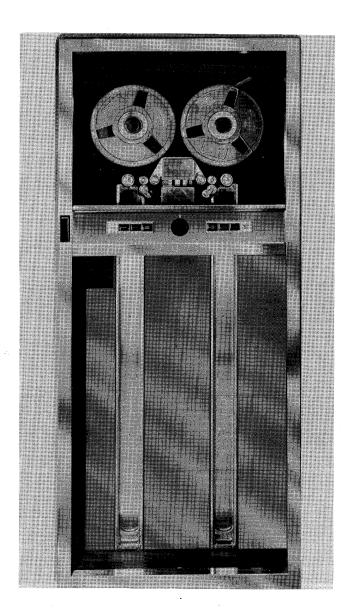

| 4-14   | Tape Drive Unit, Type 728                                      | 134  |

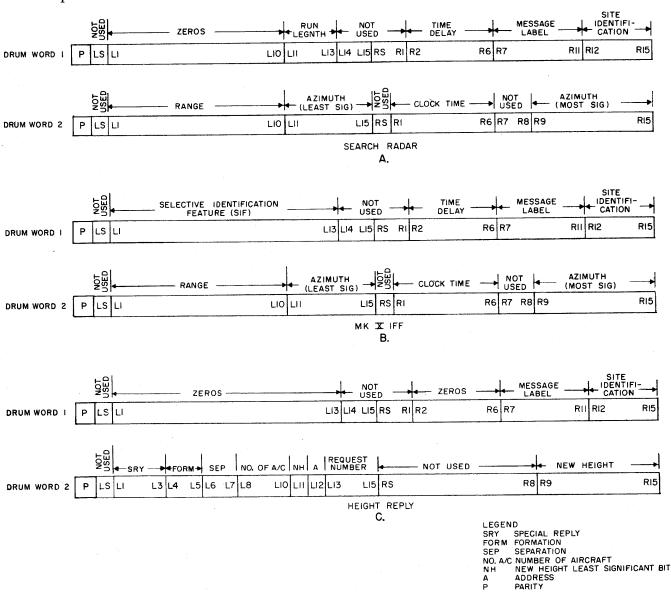

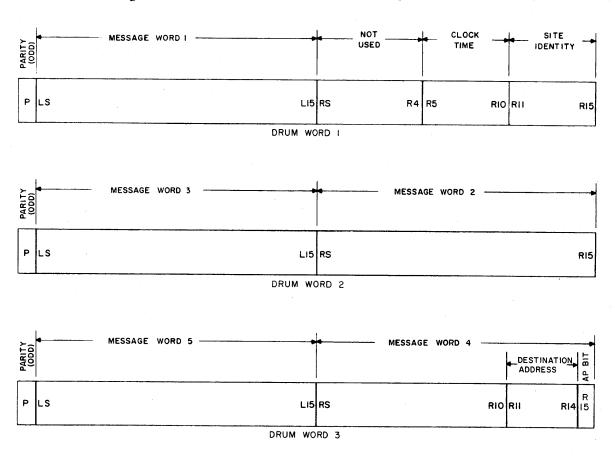

| 4-15   | LRI Message Drum Field Layout                                  | 140  |

| 4-16   | GFI Message Drum Field Layout                                  | 141  |

| 4-17   | XTL Message Drum Field Layout                                  | 142  |

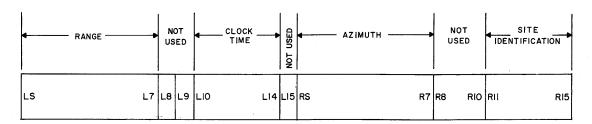

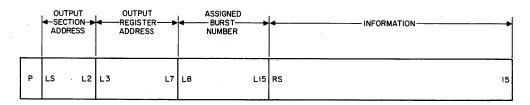

| 4-18   | Output Drum Word Layout                                        | 146  |

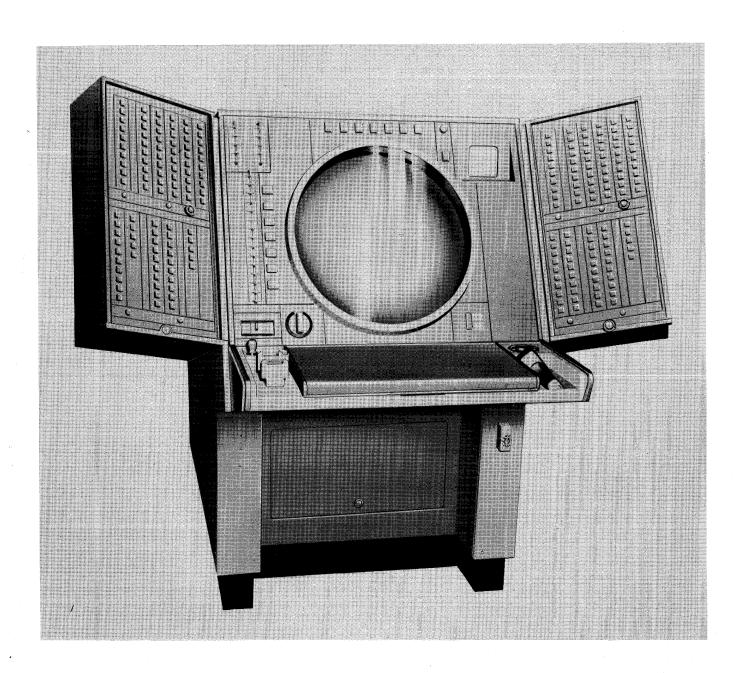

| 4-19   | Display Console                                                | 150  |

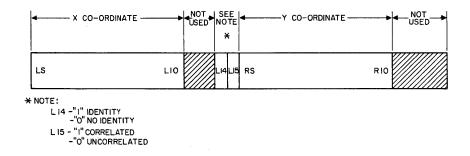

| 4-20   | Radar Data Message Drum Layout                                 | 152  |

| 4-21   | Tabular Message Drum Layout                                    | 152  |

| 4-22   | Vector Message Drum Layout                                     | 153  |

| 4-23   | Situation Display Tube Character Matrix and Octonary Addresses | 154  |

| 4-24   | Digital Display Message Drum Word Layout                       | 155  |

| 4-25   | Digital Display Tube Character Matrix and Octonary Addresses   | 155  |

| 4-26   | MDI Message Drum Field Layout                                  | 156  |

#### LIST OF TABLES

| Table | Title                                   | Page |

|-------|-----------------------------------------|------|

| 1-1   | Representation of Binary Digits         | . 10 |

| 1-2   | Binary and Decimal Equivalents          | . 11 |

| 1-3   | Powers of Two                           | . 11 |

| 1-4   | Rules of Binary Addition                | . 12 |

| 1-5   | Binary Addition with Carry of 1         | . 13 |

| 1-6   | Rules of Binary Multiplication          | . 15 |

| 17    | Multiplication by Addition and Shifting | . 16 |

| 1-8   | Division by Nonrestoration              | . 17 |

| 1-9   | Decimal, Octal, and Binary Equivalents  | . 18 |

| 1-10  | Powers of Eight                         | . 19 |

| 1-11  | Octal Addition                          | . 20 |

| 1-12  | Octal Multiplication                    | . 20 |

| 2-1   | AN/FSQ-7 Memory Addresses               | 35   |

|       |                                         |      |

# LIST OF TABLES (cont'd)

| Table | Title                                                            | Page       |

|-------|------------------------------------------------------------------|------------|

| 2-2   | AN/FSQ-8 Memory Addresses                                        | 35         |

| 2-3   | Basic Addition Program                                           | 40         |

| 2-4   | Memory Reference Program                                         | 41         |

| 2-5   | Sample Subtraction Program                                       | 42         |

| 2-6   | Sample Program Using Half-Word Store Instructions                | 42         |

| 2-7   | Additional Example of Half-Word Storage                          | 43         |

| 2-8   | Table Construction Program                                       | 44         |

| 2-9   | Number-Sorting Program                                           | 48         |

| 2-10  | Combinations Satisfying the Branch on Full Zero (BFZ) Conditions |            |

| 2—11  | Execution of Branch on Full Zero (BFZ) Instruction               | 49         |

| 2-12  | Program Using Full Branch Instructions                           | 49         |

| 2-13  | Address Modification Using the AOR Instruction                   | 52         |

| 2-14  | Straight Line Addition Program                                   | 53         |

| 2-15  | Program Using the AOR Instruction as a Step Counter              | 53         |

| 2-16  | Indexed Addition Program                                         | <b>5</b> 7 |

| 2-17  | Table-Sorting Program Using the BPX Instruction                  | <b>5</b> 7 |

| 2-18  | Programmed Delay Using the BPX Instruction                       | 58         |

| 2-19  | Sorting Program with Unconditional Branch                        | 59         |

| 2-20  | Summary of Basic Instructions                                    | 60         |

| 3-1   | BPX Instruction Configurations                                   | 63         |

| 3-2   | Data Sorting and Counting Program                                | 64         |

| 3-3   | Index Register Loading Routine                                   | 66         |

| 3-4   | XAC Instruction Configurations                                   | 66         |

| 3-5   | Table Lookup Program                                             | 67         |

| 3-6   | Table Makeup Program                                             | 67         |

| 3-7   | Basic Multiplication Program                                     | 77         |

| 3-8   | Function Evaluation Program                                      | 77         |

| 3-9   | Co-ordinate Conversion Program                                   | 78         |

| 3-10  | Division Program                                                 | 78         |

| 3-11  | Application of Cycle Instruction                                 | 84         |

| 3-12  | Display Makeup Program                                           | 85         |

| 3-13  | Number Determination Program                                     | 86         |

| 3-14  | Deposit Instruction Execution                                    | 87         |

| 3-15  | Relocation Program                                               | 89         |

| 3-16  | Compare Masked Bits Instruction Execution                        | 90         |

| 3-17  | Register Comparison Program                                      | 91         |

| 3-18  | Tape Program Search Routine                                      | 91         |

# LIST OF TABLES (cont'd)

| Table | Title                                                | Page |

|-------|------------------------------------------------------|------|

| 3-19  | Compare Difference Masked Bits Instruction Execution | 93   |

| 3-20  | Register Compare and Branch Routine                  | 93   |

| 3-21  | Partial Word Compare Program                         | 93   |

| 3-22  | TOB and TTB Bit Selection                            | 95   |

| 3-23  | Instruction Word Checking Program                    | 95   |

| 3-24  | Sample TTB Program                                   | 96   |

| 3-25  | Time Determination Routine                           | 97   |

| 3-26  | Equality Check Routine                               | 98   |

| 3-27  | Clock Register Stepping Routine                      | 99   |

| 3-28  | Overflow Alarm Suppression Routine                   | 105  |

| 3-29  | Summary of Central Computer System Instructions      | 105  |

| 4-1   | Interleave Code                                      | 110  |

| 4-2   | Data Read-In Program                                 | 112  |

| 4-3   | IO Pause Program                                     | 112  |

| 4-4   | Word Count Transfer Routine                          | 113  |

| 4-5   | Program to Clear 2562 Memory                         | 114  |

| 4–6   | Program to Load Memory with a Fixed Pattern          | 114  |

| 4-7   | Auxiliary Memory Drum Fields                         | 115  |

| 4-8   | Drum Loading Routine                                 |      |

| 4-9   | Drum Reading Routine                                 |      |

| 4-10  | Intercommunication Test Loop                         |      |

| 4-11  | Hollerith Code for Punched Cards                     |      |

| 4–12  | Card Reader Transfer Routine                         |      |

| 4-13  | Card Punch Transfer Routine                          |      |

| 4-14  | Gang-Punching Routine                                |      |

| 4-15  | Card Image for Identity Punching                     |      |

| 4–16  | Line Printer Routine                                 |      |

| 4-17  | Tape Unit Readiness Check                            |      |

| 4-18  | Tape Rewind Program                                  |      |

| 4-19  | Program to Rewind More Than One Tape                 |      |

| 4-20  | Tape Backspace Routine                               |      |

| 4-21  | Tape Record Location Program                         |      |

| 4-22  | Crosstell Marker Program                             |      |

| 4-23  | Output Section Address Codes                         | 146  |

| 4-24  | Marginal Checking Control Word Layout                |      |

| 4-25  | Summary of IO Instructions                           |      |

| 5-1   | Scaling Procedures for Fixed-Point Computation       |      |

# PART 1 INTRODUCTION

# CHAPTER 1 PURPOSE AND SCOPE

#### 1.1 PURPOSE

This manual explains the program instructions used in the AN/FSQ-7 and AN/FSQ-8. Although the manual is designed to be used primarily in the training of IBM field engineers, it also serves as a reference manual for IBM field engineers and other personnel assigned to the various air defense sites.

#### 1.2 SCOPE

The manual was written to serve as an introduction to programming digital computers in general and the AN/FSQ-7 and AN/FSQ-8 in particular. Some chapters apply to all the courses of instruction conducted by Field Engineering Education; others pertain only to one of the courses. A detailed description of each part of the manual follows.

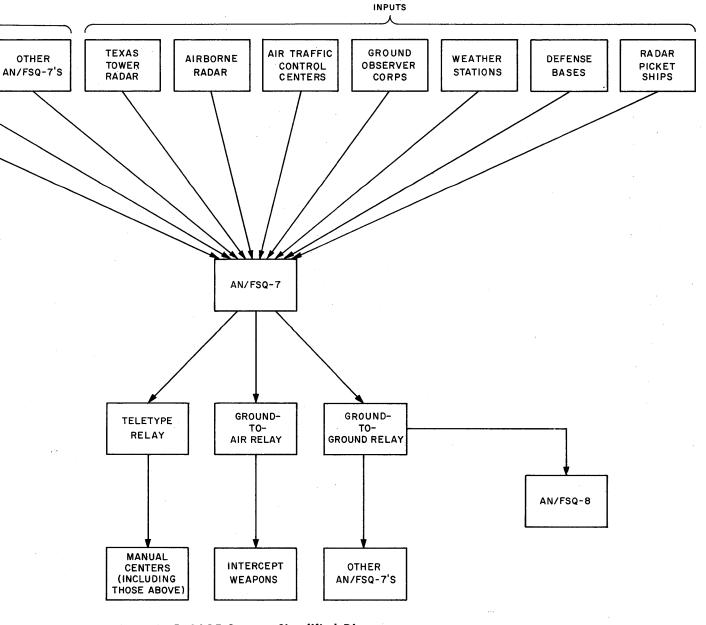

Part 1 covers the history of computing devices from the abacus to the modern digital computer. A description of the binary number system, which is used in many digital machines (including the AN/FSQ-7 and -8), is presented and examples of arithmetic operations using this system are given. This part also outlines the general organization and operation of the SAGE System employed in air defense. A brief introduction to the AN/FSQ-7 and AN/FSQ-8, the computing elements of the SAGE System, is presented.

Part 2 contains the information necessary for an understanding of the programmed operation of the AN/FSQ-7 and AN/FSQ-8. The various systems which make up the AN/FSQ-7 and AN/FSQ-8 are described and their overall relationship is discussed. Some of the

basic instructions of these two machines are described, and program examples of their use are given. In addition, techniques, such as indexing, which are useful in programming operations, are introduced.

The third part of the manual presents a detailed description of the instructions which are applicable to the Central Computer System of the AN/FSQ-7 and AN/FSQ-8. Wherever possible, examples of the application of these instructions are given. In addition, Part 3 explains some of the programming options which are available for the AN/FSQ-7 as a result of the installation of an expanded memory unit.

Part 4 describes the programming of equipment and systems which are external to the Central Computer System. The various instructions which are used to program these external systems are given, as are program examples. Each chapter within this part is concerned with the programmed operation of one of the logical groups of external equipment.

Advanced programming methods, such as the content and operation of utility systems and the scaling of fixed point numbers, are contained in Part 5. This part enables the reader to understand all of the operations necessary, in addition to the coding of a program to prepare it for entry into the AN/FSQ-7 and AN/FSQ-8.

Appendix A lists those codes which are referred to as illegal instructions within the AN/FSQ-7 and AN/FSQ-8. The effect that the execution of these illegal instructions has on the Central Computer System is described, and the use of some of them is presented.

#### **CHAPTER 2**

#### **DIGITAL COMPUTERS**

#### 2.1 HISTORY OF DIGITAL COMPUTERS

The word "computer" comes from the latin verb "computare" which means to reckon or think. Thus, a digital computer is a machine that reckons (or calculates) with digits. The following text contains a brief history of computing devices which brought about the modern digital machines.

Before the advent of large-scale digital computers, man had to rely on manual methods and slow mechanical calculators to perform arithmetic operations. No doubt the first devices used by man as an aid in computation were fingers, sticks, stones, and similar objects. These items served only as reminders or indicators of a particular quantity and could not themselves do any work; the actual computation was carried out in the mind of the individual. The abacus, originated sometime before 1200 A.D., evolved from the use of pebbles as counters, and has been highly touted as a computer; however, it is really nothing more than an indicating device.

After the abacus and the soroban (a refinement of the abacus) came into use, little progress was made in the field of computing devices for several years. Then, in 1642, Pascal, the French mathematician, invented what was perhaps the first actual accounting machine. This machine was used to figure currency in a customs house. It was basically a hand-operated, gear-driven counter, with addition performed by turning a wheel a distance equal to the currency to be added. Pascal's machine did not attract much attention, possibly because he was only 19 years old at the time. However it was noteworthy because it was the first instrument with provision for an automatic carry into the next higher order column when the sum of a column exceeded 9. In 1673, a German mathematician named Leibnitz developed a similar machine, which could multiply as well as add. Unfortunately, it did not work well enough to be of much value in computation.

After Leibnitz's machine, there was a period of inactivity until 1801, when another Frenchman named Joseph Jacquard came upon the idea of punched cards. Jacquard used a chain of perforated cards to control weaving of figured fabrics on a loom. This mechanism functioned quite successfully, and the Jacquard loom proved to be the basis for some remarkable developments, as we shall see later.

During the 19th century, several developments took place which furthered the use of automatic accounting machines. First, an American named Thomas invented a desk calculator in 1820 which utilized the same principles as Leibnitz's machinery and was also reliable. Improved models of Thomas' calculator were used in business and industry for the next 100 years. Two years later, Charles Babbage, a brilliant but highly unpopular English mathematician started work on what he called a "difference engine." This device was to be used to calculate mathematical tables to 20 places. Babbage's design was fundamentally sound, but production techniques at that time were not, and after many unsuccessful attempts to construct a working machine, the British government stopped supplying funds for this project. Despite the furor caused by his failure to produce the difference engine, Babbage was elected to a chair in mathematics at an English University. He distinguished himself in this position by refusing to deliver even one lecture in the 11 years he held the position. Then in 1833, the remarkable Mr. Babbage again received a grant from the British government to work on another computing machine, called the Babbage Analytical Engine. Elaborate plans were prepared for the construction of this computer, which differed largely from Babbage's first machine because it was controlled by punched cards and was capable of making logical decisions. Parts of it were completed and made to work, but the project failed as a whole because Babbage's design was still too advanced for the engineering techniques then in existence. Nevertheless, Babbage continued to work on his computer for another 10 years or so, until government funds were exhausted. Detailed descriptions of his machine were preserved, as were substantial parts of it, but Babbage's idea was soon forgotten.

In 1886, a very important milestone in computer history was reached when Dr. Herman Hollerith invented a machine using punched cards. Hollerith was head of the U. S. Bureau of Census at the time, and he discovered that the 1880 census was not yet completed, due largely to the fact that all calculations were being made by hand. He set to work to find a way by which all recording, tabulating, and analyzing of facts could be done by machine. His solution, which was based upon Jacquard's idea of punched cards, was to record the facts of any situation by punching holes in a definite

code in a piece of paper. Hollerith had originally planned to use strips of paper, but he found it necessary to rearrange the information, so he cut the strips into a standard size and shape and thus had a card for each situation. Once the card was developed, Dr. Hollerith developed a sorting device, using these cards, and opened up a whole new field of computing aids.

As business and industry grew during the first part of the 20th century, the demand for accounting machines grew steadily. In 1914, a mechanical key punch, a gang-punch, a vertical sorter, and a tabulator were available to meet the accounting needs of the nation. As time went on, more and more equipment was introduced which eased the task of calculations. However, all of this equipment was electromechanical in nature, and each machine could perform only one or two basic operations. What was needed was a machine that could perform a multitude of tasks at a high rate of speed.

The man who set about to design such a general-purpose machine was Dr. H. H. Aiken of Harvard University. He directed a project which started in 1939 and was climaxed by the construction of the automatic Sequence Controlled Computer in 1944. This computer, commonly referred to as the Mark I, was built by IBM for Harvard from components already in use in IBM's electromechanical business machines. It is believed that the Mark I is an outgrowth of Babbage's analytical engine, since his work was reviewed in great detail before the actual construction began. Although the Mark I was electromechanical in nature, and therefore was still quite slow, it marked the appearance of the first of a long line of large digital computers.

The first electronic computer was the Electronic Numerical Integrator and Calculator, or ENIAC, built in 1946 by Dr. J. W. Mauchley and Mr. J. P. Eckert of the Moore School of Engineering of the University of Pennsylvania. The ENIAC utilized 18,000 vacuum tubes as storage elements instead of the relays and switches used in the Mark I. The fact that vacuum tubes were used at all represented a considerable venture in computing techniques, since the performance of tubes at that time was not very reliable. However, ENIAC proved to be a highly successful digital computer, and is still in operation today, although it has been obsoleted for some time. As an example of the improvement in arithmetic speed between Mark I and ENIAC, let us consider the addition of two numbers. Mark I required 300 ms to perform this task, whereas ENIAC could do the same thing in two-tenths of a millisecond. or, roughly, 1,500 times faster. From this comparison, it is possible to see the tremendous boost given the computer field with the advent of vacuum tubes and electronic circuitry.

After ENIAC, the next big computer of significance was the Selective Sequence Electronic Calculator, or SSEC, built by IBM in 1948. This machine, installed at IBM World Headquarters, proved beyond a doubt that large-scale digital computers had commercial applications. The government, which was doing research in the atomic energy field, utilized the SSEC as an aid in solving some of its large problems. Other customers soon realized that the SSEC could solve problems which were never before attempted. The success of this computer prompted many manufacturers of electronic equipment to develop digital computers for commercial use.

About the same time, a group at Cambridge University in England built the first stored-program computer. The man in charge of the project was M. V. Wilkes, and he called the computer EDSAC. EDSAC was modest in size and capability, but Wilkes and his associates made significant contributions to the computer field by refining programming techniques and procedures. They were the first to make extensive use of program subroutines with an assembly system for making new programs.

In 1946, the designers of ENIAC, Dr. Mauchly and Mr. Eckert, resigned from the University of Pennsylvania and set up their own firm, called the Electronics Control Company. They began to develop an electronic computer which could handle alphabetic as well as numeric data, and which would be more versatile than any machine then in existence. This machine was called the Universal Automatic Computer, or UNIVAC, and was first produced in 1951 by the Remington-Rand corporation, which had made the Mauchly-Eckert firm one of their divisions. UNIVAC proved to be the nucleus for a new computer field; namely, the large-scale, general-purpose digital machine.

In addition to the UNIVAC, several other computers were developed at this time, most of them by the government and leading universities. For example, the MANIAC, built by Princeton; the SEAC, built by the Bureau of Standards; and the WHIRLWIND, built by the Massachusetts Institute of Technology. All of these machines aided the advancement of computers and computing techniques. At the same time, they confirmed the belief, started with the introduction of the SSEC, that large digital machines could prove a powerful tool to both science and industry.

The vast experience gained in the punched-card field enabled IBM to develop an entire "family" of large digital computers, known as the 700 series. First came the 701, a scientific computer with a memory composed of electrostatic storage tubes. This computer was extremely fast and reliable, and was used extensively

in the aircraft industry to perform design calculations. In 1955, the first 702 was installed at the Monsanto Chemical Company in St. Louis. This model was designed to handle mostly commercial data processing such as billing, stock inventory, payrolls, etc. These two machines were capable of handling any type of problem that could be reduced to some combination of the basic arithmetic processes. However, improvements were still being made in the computer field, mainly in the type of memory to be utilized with the computer. IBM introduced two computers in 1955 which contained magnetic cores as the high-speed memory device. The 705 was designed to replace the 702, and the 704 was the successor to the 701. Use of the new memory and other improvements enabled both machines to compute much faster than their predecessors. As an example, the 704 can select two numbers from core memory, add them together, and place the sum in a temporary storage register in 24 usec. Newest of the 700 series is the 709, also a scientific computer, which has the added capability of handling up to six input and output mediums at one time. Previously, computers had been limited in their speed of calculation because only one input or output unit at a time could be used to feed in or receive information, a disadvantage overcome by the 709.

Of particular interest are the AN/FSQ-7 and AN/FSQ-8 digital computers, also manufactured by IBM. These machines are the world's largest digital computers and form the center of a huge air defense network. The remainder of this manual is devoted primarily to a study of the techniques involved in programming these two computers.

This history of computers and computing devices is, of necessity, incomplete. Only those events which have been milestones in the development of today's digital computers have been included. Future developments in the field may radically change the operation of digital computers. These developments will probably occur in the use of bigger and faster memories, reduction in physical size of computers, and increased flexibility in programming. However, the basic concepts of Pascal, Babbage, and others who have contributed to this art will remain the same; that is, using machines to ease the task of computing and calculating.

#### 2.2 DIGITAL COMPUTER OPERATION

As was explained previously, a digital computer works with digits or numbers. To illustrate the method by which a digital computer handles a quantity, a comparison will be made with the other type of computer presently in use; namely, the analog machine. In contrast to the digital computer, a quantity in an analog computer is represented by a direct relation, or analogy, to some machine function such as voltage variations. As an example, suppose we wish to represent a quantity of

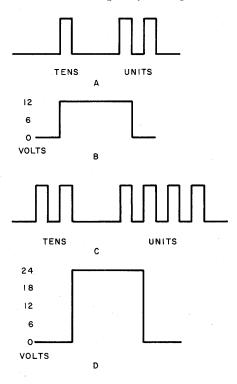

12 units in both types of machines. Figure 1–1, part A, shows a possible representation of 12 in a digital computer; part B shows the same quantity as it might be represented in an analog machine. Now, if we multiply 12 by a factor of 2, the resulting product (24) is shown in part C of figure 1–1 for the digital computer and in part D for the analog computer. In this example, pulses were used to represent digits, but this is only one of the many techniques available for digital representation.

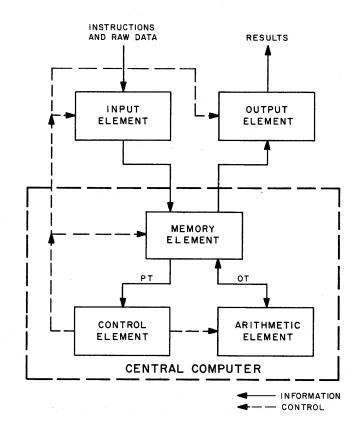

In order for a digital computer to operate, certain elements are required for the proper handling and manipulation of data, just as a man needs certain tools to perform arithmetic tasks. This comparison is easily supported by describing the elements of the computer that correspond to a man working at a desk. Assume that the man is a clerk working in a payroll office, computing the net pay of various individuals. The "in" box on his desk contains the pay rates of the personnel involved, plus miscellaneous data, such as the initiation of bond deductions, etc. A digital computer has an input element which is capable of accepting various types of data and of presenting it to the computing portion of the equipment. The clerk has several tables he refers to, such as tax deduction tables, standard weekly deductions, etc.; in addition, he has a pad and paper on which he notes the deductions applicable to each employee. In a digital computer, the memory element would serve as the temporary storage device for all

Figure 1—1. Representation of Numbers in Digital and Analog Computers

these facts. The actual computation of an individual salary is done in the payroll clerk's head, or, perhaps with a desk calculator; in either case, this function is the same as that performed by the arithmetic element of a digital machine. Once the net pay of each person has been calculated, the clerk fills out a standard form which contains the employee's name and the amount due. He then places all these forms in the "out" box on his desk, thus completing his job. The output element of a digital computer accepts the results of computation by the arithmetic element and presents the results in a form recognizable by the user. Of course, all the actions of the payroll clerk are controlled and co-ordinated by his nervous system. The control element co-ordinates the actions of a digital computer and is connected to all the other elements. From this discussion, we can see that a digital computer is essentially composed of the following elements:

- a. Input

- b. Output

- c. Memory

- d. Arithmetic

- e. Control

Each of these elements is discussed in detail below, and reference is made to the general organization and operation of each.

The input element is capable of accepting data in a variety of forms and converting it to a standard format which is used by the computing portion of the equipment. The type of inputs which constitute the input element for different machines vary a great deal; therefore, it is not possible to say that any one combination of units makes an input element. However, some of the more common types of input units are punched card readers, magnetic tapes, paper tapes, typewriters, and telephone lines which transmit data from remote locations. The input element provides 1-way communication between the computing elements and external sources: information is received through the input element, but no information or data is returned.

As might be expected, the output element is almost the opposite of the input element. The results of computer operation are fed through the element to designated locations, but no information is given back to the computing elements. Some examples of output units that might constitute a typical output element are line printers, card punches, magnetic tapes, and visual indicators. As with the input element, the output element makeup is flexible and varies widely from one computer to another.

The memory element comprises a large number of storage locations in which information can be stored until it is needed by one of the other elements. As a rule, memory elements have absolute addresses assigned to each location, and such an address is specified when information is needed. For instance, a typical computer instruction might be to "add the quantity which is stored in location 1000." The instruction which stated that address 1000 contained the desired operand is also stored in the memory element; this makes the memory element a "shared" device. Sometimes the instructions for performing a given operation are always contained in the same physical portion of the memory element; sometimes they may be located any place within the memory. Memory elements may be constructed of several types of mechanisms; however, some of these are rarely used because of new developments which have taken place. At present, magnetic cores are the most popular device, primarily because of their high speed and stability. Other devices which have been used include acoustic delay lines, electrostatic tubes, and magnetic drums. The AN/FSQ-7 and AN/FSQ-8 both utilize magnetic cores in the memory element.

The arithmetic element of a digital computer is basically a device which performs addition only; the other arithmetic functions are simply variations of the addition function. For example, multiplication in an arithmetic element is simply a repetitive addition. Arithmetic elements are, for the most part, made up of various vacuum-tube circuits and switches. The basic circuit in an arithmetic element is the flip-flop, which is used to store or transfer the results of computation. There are about 100 such flip-flop (FF) circuits in the arithmetic element of the AN/FSQ-7 and AN/FSQ-8.

The function of the control element is to generate the proper signals at the proper time which will cause a desired action to take place within the computer. Several decoders are used in the control elements, along with flip-flops and other switching devices. The control element keeps track of what instruction is to be decoded and performs part of the decoding. In addition, this element provides timing pulses which synchronize all elements of the computer.

Figure 1–2 shows the five elements we have been discussing arranged as a typical computer configuration. Information, which includes computer instructions as well as data, enters the computer through the input element, where it may be converted to a common form and placed in a buffer storage device. The memory element accepts this information at specific intervals and places it in the proper storage location. Notice that there are two paths leading out of the memory element; one to the control element and the other to the arithmetic element. Earlier, we spoke of the memory element as a shared device, and this is true because it serves as the memory for two other elements. The instructions are transferred from memory to the control element,

where they are decoded, and certain commands are set up by the control element. One of these commands is to go into memory again and transfer out the designated operand to the arithmetic element. Following the calculation in the arithmetic element, the results of a desired operation are usually programmed to be returned to memory and then transferred to the output element during an alloted time interval.

From this, we can see that a digital computer follows a basic flow pattern during its operation. The time when the instructions are decoded is known as program time (PT); the time when the calculation is performed is known as operate time (OT). Most of the operations that can be carried out by the AN/FSQ-7 and AN/FSQ-8 follow this PT-OT pattern, usually referred to as cycle configuration. The cycle configuration varies slightly among the various operations because more time is sometimes required for one operation than for another. In addition, the AN/FSQ-7 and AN/FSQ-8 are capable of performing a few operations which do not require any OT time; however, these are of a specialized nature and are explained in detail in the appropriate parts of the manual.

In figure 1–2, you will notice that the memory, control, and arithmetic elements are enclosed in a box, and referred to as the central computer. This has been done to clarify the use of the terms "computer" and "central computer." A computer comprises all the elements necessary for proper operations, including the input and output elements. The central computer refers only to that portion of the equipment which does the actual calculations. This distinction is necessary because

Figure 1-2. Digital Computer, Block Diagram

the two terms are used frequently throughout the manual, and it is important to know whether all or only a portion of the equipment is being referred to at any one time.

#### **CHAPTER 3**

#### **NUMBER SYSTEMS**

#### 3.1 GENERAL DESCRIPTION

When we speak of a "number," it usually brings to mind some combination of the decimal digits 0 through 9. This number may represent several different things, although in each case only the digits mentioned above are used. For instance, we might think of a 10-day course of instruction. In this case, the number 10 is used to represent a quantity of items namely, days. Therefore, one use of a number is as a quantity designator, or a number that specifies an amount. However, numbers do not always indicate an amount or a quantity. Consider a post office mail box. The number on the mail box does not indicate how many mail boxes are located in the post office nor does it tell how many letters are in the mail box. What the number does tell is the location of the mail box with respect to other mail boxes, or the address of the box. All incoming mail with that particular box number on it will be placed in that box. In this case, the number has told us only the location of the mail box, and nothing else. There is one more general use to which numbers are put; i.e., as an identification code. For instance, a telephone number does not indicate quantity or a location but merely tells the automatic dialing equipment what phone to ring when someone dials a particular number. In the above examples, the decimal system has been used simply because it is the one we are most familiar with. However, the fact that numbers can act as quantity designators, addresses, or identification codes holds true for all number systems.

All number systems have many properties in common, and these properties are explained, using the decimal systems as an example. The use of the decimal system will permit us to see exactly what effect each property has without giving us trouble with the mathematics involved, since we are all used to doing arithmetic in this system. Later on, each of the properties discussed will be used with the two other number systems covered in this chapter, and we will see that the same rules still apply.

#### 3.2 DECIMAL NUMBER SYSTEM

The decimal number system derives its name from the fact that it is composed of 10 different symbols. These symbols are, of course, 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. Any one of these symbols may appear in any position of a number. When we count in the decimal system, adding a 1 to any number 0 through 8 gives

the next higher number (e.g., 7+1=8, 3+1=4, etc.). However, adding a 1 to 9 does not give a higher number but, instead, causes a return to the lowest symbol and causes a 1 to be added to the next position to the left (9+1=0 plus a carry of 1 to the left, or 10). From this, we can see that 10 steps are required to use all the symbols in the decimal system and cause a return to the lowest order symbol. Also, there are 10 different symbols in the decimal system. These two facts can be stated by saying that the decimal number system has a radix or base of 10. The radix of any number system thus indicates the number of symbols in that system and the number of steps in the counting cycle.