A COPY FROM

MITRE ARCHIVES

## THEORY OF OPERATION

**OF**

### CENTRAL COMPUTER SYSTEM

**FOR**

AN/FSQ-7

COMBAT DIRECTION CENTRAL

AND

AN/FSQ-8

COMBAT CONTROL CENTRAL

**VOLUME II**

1 February 1959

This document contains information of a properiency nature. Any use or reproduction of this document for other than government purposes is subject to the guier content of International Business Machines Corporation.

MELITARY PRODUCTS DIVISION

MERCHAL MUNICIPAL MACHINES CORPORATION

EMPTON, NET YORK

# PART 7 MEMORY ELEMENT

## CHAPTER 1 INTRODUCTION

### 1.1 GENERAL

The memory element of the Central Computer is a computer-controlled, large-capacity, random-access, highspeed storage facility which provides for the semipermanent storage of all information (operating program, raw data, and processed results) required for or resulting from the normal operation of the central Computer. Since the memory storage circults do not differentiate between instruction words and data words (raw or processed), the theory of operation presented in this part is based on the two types of memory cycles that affect memory operations; that is, the memory readout and memory store cycles. The memory readout cycle (equivalent to PT, OTA, and BO machine cycles) results in the transfer of a memory word out of a specific memory location; the memory store cycle (equivalent to OTB and BI machine cycles) results in clearing the specified memory location and storing the desired memory word in the cleared location. Each type of memory cycle requires 6.0 uses for execution.

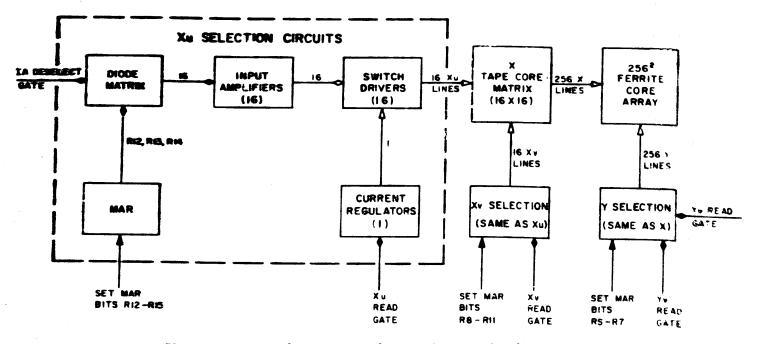

#### 1.2 PLOCK DIAGRAM ANALYSIS

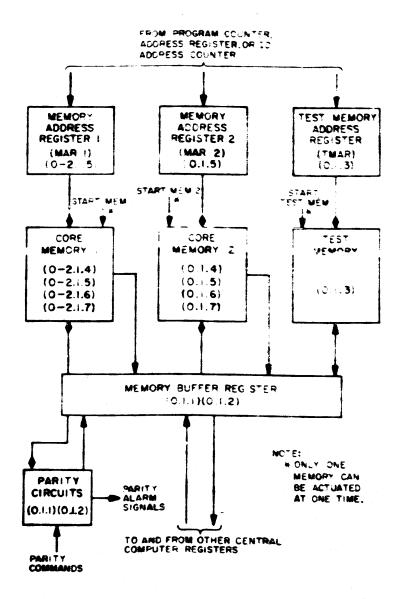

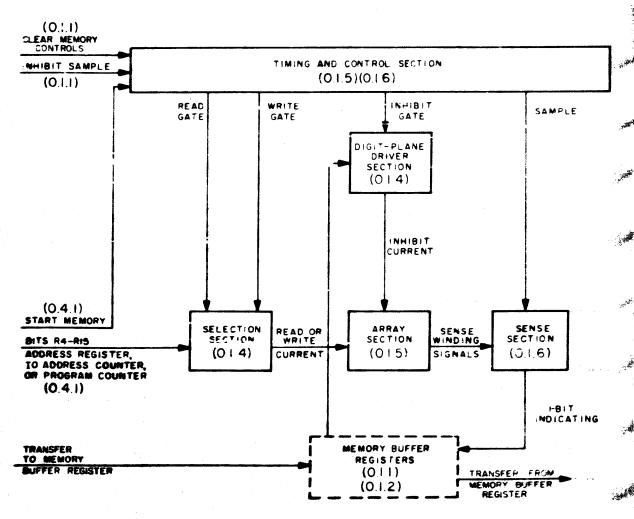

A block diagram of the memory element is shown in figure 7-1. Although the three memory address registers are shown as individual blocks, each register is actually an integral part of the associated memory device since it is used to condition the internal address selection circuits within that memory. Each of the three memory devices is capable of storing different quantities of information: core memory 1 has a storage capacity of 65,536:101 memory words, core memory 2 has a storage capacity of 4,096(10) memory words, and test memory has an effective storage capacity of 16.1111 memory words. The storage medium used in each of the core memory devices is a 3-dimensional ferrite care array. Test memory storage is accomplished by the use of a manually wised control panel, two toggle switch registers, and a flip-flop register.

During computer operation, each memory cycle is initiated by the transfer of the desired memory address to the three memory address registers, and the subse-

quent application of a start-memory pulse to initiate the internal operations in the selected device. Concurrently, the memory buffer registers are cleared to prepare them for the temporary storage of data to be transferred from either the selected memory location or from an external register, depending upon the type of cycle in process. During the execution of a memory

Figure 7—1. Memory Element, Black Diagram

readout cycle, the contents of the specified memory location are transferred to the memory buffer register approximately 3.0 usec after the cycle was initiated. The memory buffer register contents are then transferred to a specific computer register as directed by a computer command. Since the core memory devices operate on the principle of destructive readout (the information contained in the selected care register is erased), the latter portion of the memory readout cycle is used to store the memory buffer contents back into the specified core memory location. During the execution of a memory store cycle, the first 3.0 usec are used to erase the content of the specified memory location and to transfer the new word from one of the computer registers to the memory buffer register. During the latter portion of this memory cycle, the are information is stored in the cleared memory location.

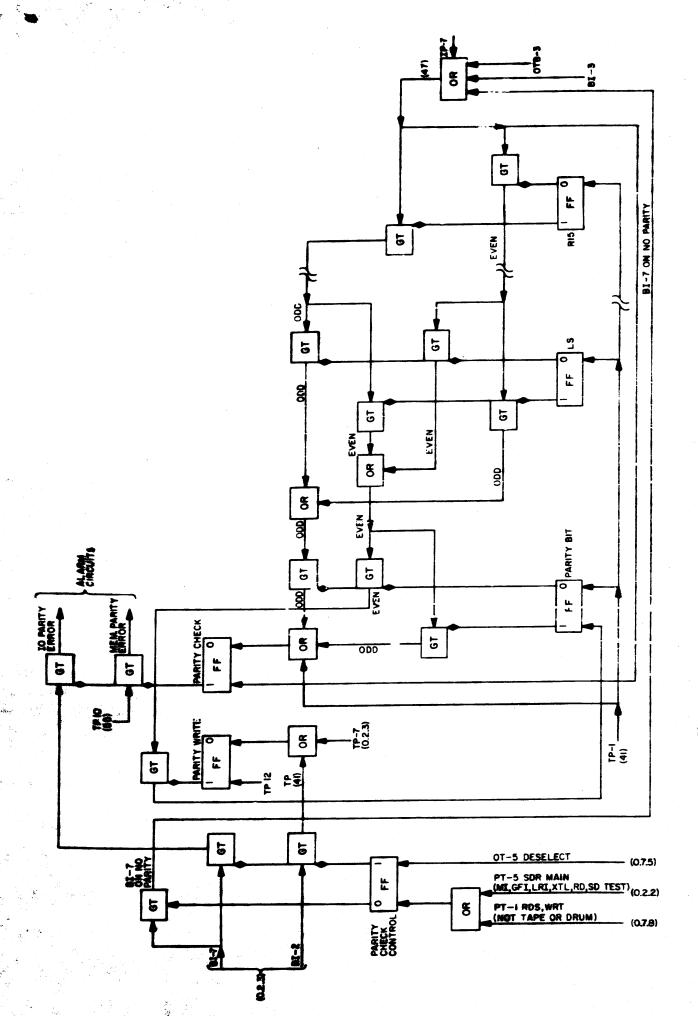

The parity circuits associated with the memory buffer register provide a means of checking the accuracy of information transfer into and out of either of the core memory devices. During each memory store cycle, a parity bit is assigned to the memory word (33rd bit of memory word) before it is stored into the specified core

the parity bit is checked to determine whether the initial transfer into and the present transfer out of the core memory were accurately accomplished. If the parity check shows that the memory word is in error, a parity-alarm signal is renerated to inform the operating personnel of the implunction.

Since the memory storage devices and the parity circuits operate independently of each other, the derailed analysis of each of these circuit groups is presented in suparate independent chapters of this part. Because the operating characteristics of the two core memor devices are identical, the principles of core mem storage are discussed separately in Chapter 2. This chapter, which analyzes in detail the characteristics of ferrite cores and ferrite array wiring, contains only a minimum amount of core memory circuit analysis. Conversely, Chapters 3 and 4, which contain the detailed theory of operation of the 64° and 256° core memory devices, respectively, do not include an analysis of the principles of fertite core storage and are dimited to an analysis of the logic circuits required to produce the desired results.

### **CHAPTER 2**

### PRINCIPLES OF CORE MEMORY OPERATION

### 2.1 ANALYSIS OF FERRITE CORES AND FERRITE CORE ARRAYS

#### 2.1.1 Characteristics of Ferrite Cores

The principal component of a magnetic core memory storage device is a ferrite core which possesses a square hysteresis loop, a low coercive force, and a short flux reversal or switching time. The ferrite core used in the two core memory devices is composed of a mixture of ferric and manganese oxide powders which are bonded together in the form of a toroid having an inside diameter of 0.050 inch (0.127 cm), an outside diameter of 0.060 inch (0.203 cm), and a thickness of 0.025 inch (0.0635 cm). A carefully controlled sintering or firing process imparts the desired characteristics to the core.

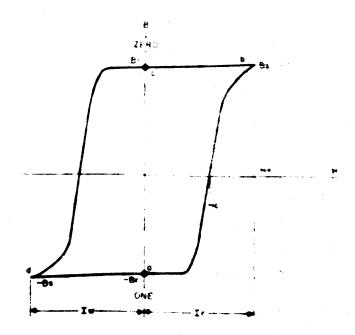

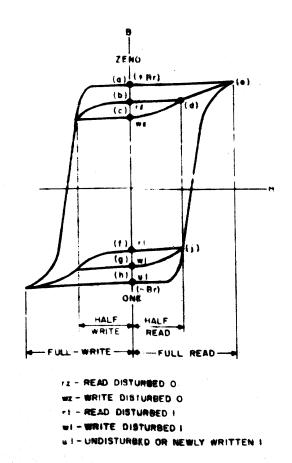

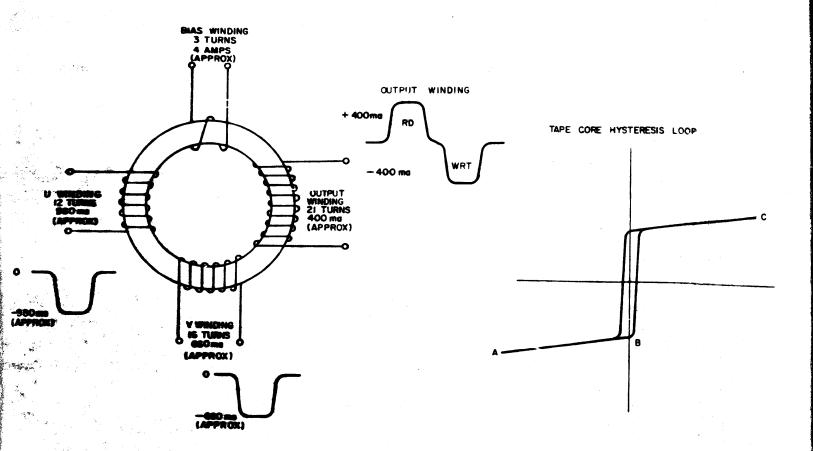

The usefulness of a ferrite core as a binary storage device depends upon four important characteristics: the ability of the core to remain in one of two stable magnetic states, the squareness ratio, the switching time, and the ratio of coercive force to applied field required to produce the major or saturation hysteresis loop. The major hysteresis loop of a typical ferrite core, which is a plot of flux density (B) versus applied magnetic field intensity (H), is shown in figure 7—2.

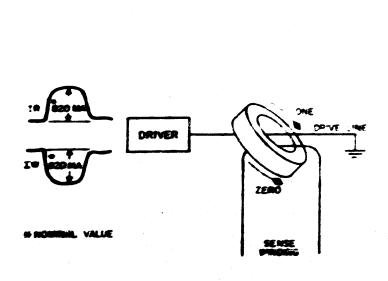

Storage of binary information in a ferrite core is dependent on the ability of the core to retain a relatively large value of residual or remnant flux upon the termination of a driving or switching pulse of current. As shown in figure 7-2, two primary states of residual or remnant flux density (B, and B) are possible, and these have been defined as the zero and one states respectively. To switch a core from one state to the other, it is necessary to apply a current pulse of L or 1, ma (depending on the initial content of the core) to the drive line that links the core. The resultant applied field of 820 ma-turns will saturate the core in the desired direction, causing the flux state to reverse by traversing the loop path a-b-c or c d-a.

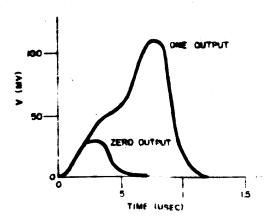

During core memory operation, the state of a core is determined by applying a read current pulse (1,) to the drive line, and detecting the resultant changes in flux density by measuring the voltage induced to the sense winding. If the core was initially in the one state, application of the read current pulse (1,) will core the core to be switched to the zero state (traversing path a-b-c in fig. 7-2), with the result that a relatively large change in flux density (2B) will be detected by the sense winding (one output signal). If the core was initially in the zero state, application of the read current pulse (1) will not switch the large to the cibic in fig. -2 is traversed), with the result that a relatively small change in flux density will be described. The sense wind!

Figure 7-2. Major Hysteresis Loop

21.1

output signal is dependent upon the ratio of the residual flux density (B<sub>r</sub>) to the saturation flux density (B<sub>r</sub>), which is defined as the squareness ratio (R<sub>r</sub> = B<sub>r</sub>/B<sub>r</sub>) of the core. This ratio is important in that it determines the relationship between the amplitudes of the one and zero output signals. The magnitude of the zero output signal decreases as the value of R<sub>r</sub> approaches 1, with the result that the difference between the amplitudes of the one and zero output signals becomes greater. Ferrite cores used in the two core memories have a squareness ratio greater than 0.95.

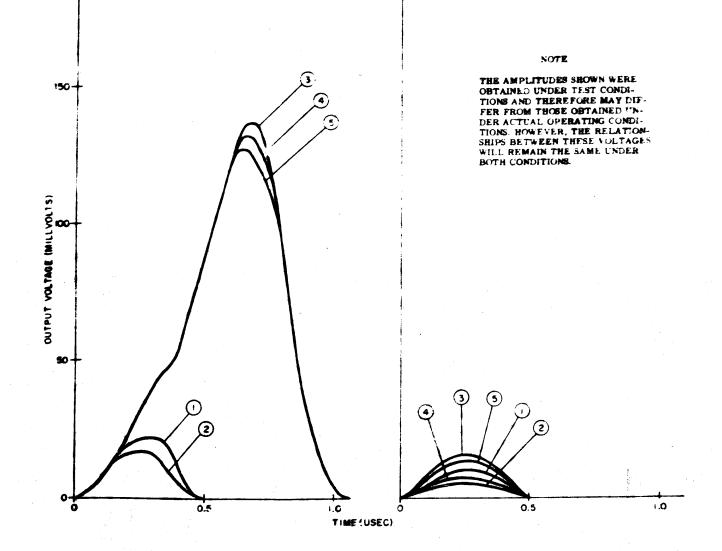

The time required to produce a flux change or flux

Figur: 7-3. Typical Response of a Ferrite Core

<sup>&</sup>quot; NOMINAL VALUE

reversal is of equal or greater importance than the squareness ratio. Figure 7-3 shows the typical output signals produced as the result of a read current pulse (L) being applied to a core in the one and zero states. As noted in the figure, the zero output signal is not only smaller in amplitude than the one signal, but also peaks earlier and is of shorter duration. Since these differences exist, it would appear that information detection could be accomplished by either a time-amplitude or a difference-amplitude sampling technique. However, in a practical core memory, a time-amplitude sampling technique must be used because the noise signals generated in the memory (discussed in 2.4) make the difference-amplitude sampling technique unfeasible. The time required for a core to switch from one state to the other is defined as the switching time, T. This time is actually measured as the elapsed time between the time that the driving current pulse reached 50 percent of its amplitude, and the time at which the one output signal has dropped to 10 percent of its peak amplitude. The switching time for cores used in the memories is approximately 1.2 usec for an applied field of 820 ma through a 1-turn drive winding.

The coercive force  $(H_c)$  of a magnetic material is defined as the maximum value of field intensity that can be applied without causing a change in flux polarity. The ratio of coercive force  $(H_c)$  to saturation field intensity  $(H_n)$  is as important to proper memory operation as the squareness ratio  $(R_n)$  and the switching time  $(T_n)$ . Since the coercive force  $(H_c)$  of the memory core in use is

greater than one half of the saturation field intensity (equivalent to  $I_{r}/2$  and  $I_{u}/2$  in fig. 7-4), it is not sufficient to cause the core to switch from one state to the other. As a result of this characteristic, the core switching function can be and is, performed by two separate 1-turn drive lines, each actuated with 15 the drive current required to switch a core. As noted in figure 7-4, the two single-turn drive lines, labeled X and Y, are wound through the core in the same direction so that the individual magnetic fields set up by these two windings will add directly when the drive lines are energized by current pulses of the same polarity. Since each drive line is supplied with half-amplitude current pulses (1/2 the current required to switch the core), both drive lines must be pulsed in coincidence in order to switch a core. A study of the hysteresis loop reveals that application of individual half-amplitude current pulses of either polarity does produce small changes in the flux density of a core (in fact, alternate polarity pulses produce the four remnant states of the two minor hysteresis loops); however, under no condition will a half-amplitude current pulse cause the core to switch from one state to the other. It is this important characteristic of the ferrite core that makes it possible to design a ferrite memory array that will operate on a coincident current method of address selection.

### 2.1.2 Characteristics of a Ferrite Core Array

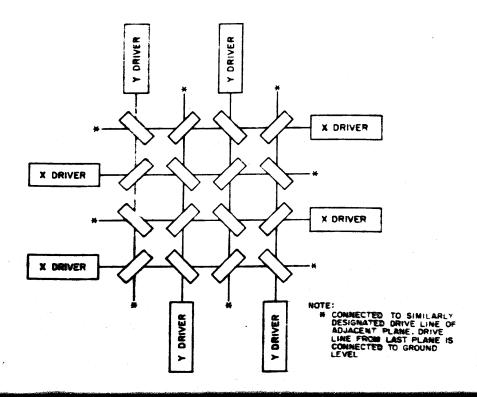

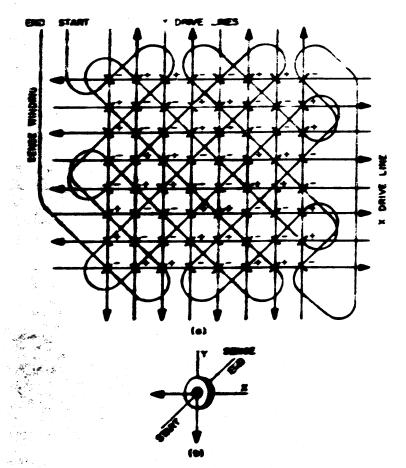

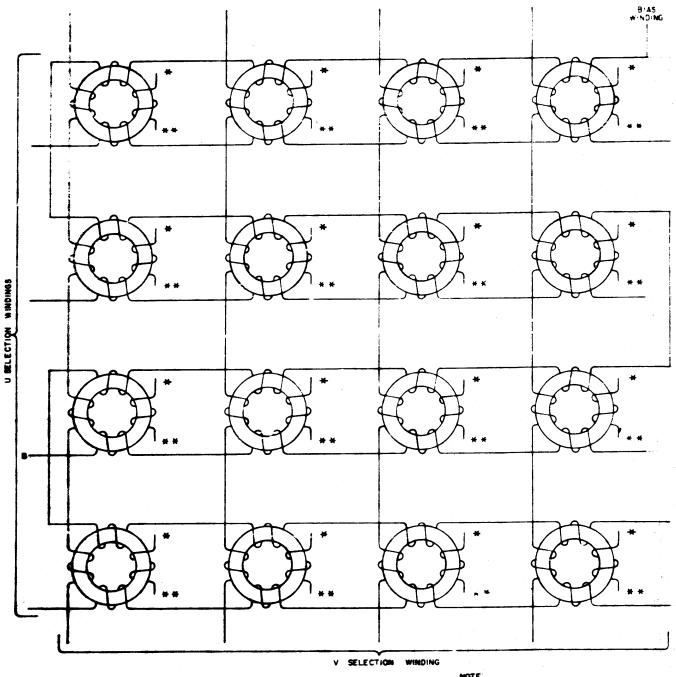

Figure 7-5 shows the square arrangement of ferrite cores in a memory plane (one of the 33 horizontal layers of a ferrite core array) which contains the simi-

larly designated bit of all the memory words stored in a core memory device. Although the drawing shows only the X and Y drive line wiring of 16 cores in a 4 x 4 matrix, it is representative of the core memory 2 plane, which contains 4,096 cores in a 64 x 64 matrix, and the core memory 1 plane, which contains 65,536 cores in a 256 x 256 matrix. In addition to being linked by the individual X and Y drive lines, all the cores of a memory plane are linked by two additional wires (not shown), a sense winding and an inhibit winding.

In constructing a ferrite core array, the 33 memory planes that comprise the array are stacked vertically and the X and Y drive lines of each plane are connected in series with the similarly positioned drive lines of adjacent planes so that one current driver can be used to control the associated X or Y drive line of the 33 planes. That is, the individual X and Y drive lines are seriesconnected so that one current driver will affect the similarly positioned row or column of cores in each of the 33 planes. As a result of this wiring scheme, each pair of mutually perpendicular drive lines (one X and one Y) intersects at the same point in each of the 33 planes to mutually link the similarly positioned core in each of the 33 planes of the array. That is, each pair of X and Y drive lines mutually links a specific vertical column of 33 cores (one in each plane).

During core memory operation, selection of a specific memory register (a vertical column of 33 cores) is accomplished by conditioning one X and one Y current driver. Subsequently, the two conditioned drivers are actuated so that they will simultaneously generate halfamplitude read and half-amplitude write current pulses in the sequence noted in figure 7-4. Since the two drive lines that link a core (fig. 7-5) are wound through the core in the same direction (with reference to the associated driver), the individual magnetic fields set up by these two selected drivers will add at the point of intersection. Because each current driver can only supply half-amplitude current pulses, only the cores at the 33 intersections of the two selected drive lines (one core in each plane) will be affected by sequentially applied magnetic fields of plus and minus 820 ma-turns (fully selected); all the other cores on these two drive lines will be affected by sequentially applied magnetic fields of plus and minus 410 ma-turns (half-selected). The sequential application of magnetic fields of plus and minus 410 maturns will not produce any change in the status of any of the half-selected cores (fig. 7-4). However, the sequential application of magnetic fields of plus and minus 820 ma-turns to the 33 selected cores (one core in each plane) will cause each of these cores to be switched first to the zero state and then to the one state. Since normal memory operation may require that individual cores of the selected memory register (one core in each plane) remain in the zero state at the end of a memory cycle, a

separate control is provided for each plane which when actuated will prevent the minus 820 ma-turn applied field from switching the associated selected core to the one state. This control to inhibit the writing of a 1 in the selected core of an individual memory plane is accomplished by a digit plane driver. When conditioned, the digit plane driver can be actuated to generate a negative current pulse of 410 ma on its associated one-turn inhibit winding in coincidence with the half-amplitude write current pulses that are applied to the selected X and Y driver lines. The inhibit winding, which link all the cores of a single memory plane, is wound so that its applied field opposes the individual magnetic fields set up by the X and Y drive lines when the latter are energized by half-amplitude write current pulses.

As a result, the coincident application of these three current pulses to the selected core of a plane will produce a resultant magnetic field of minus 410 ma-turns, which is not sufficient to switch the selected core from the zero to the one state. Although the inhibit current pulses also affect all the other cores of the plane, it will not produce any change in the status of any of these cores. The detailed analysis of how the digit plane driver is controlled to perform its function is given in 2.2.

### 2.2 CORE MEMORY CYCLE ANALYSIS

During normal computer operation, either of the two core memory devices can be individually selected to perform either of two distinct functions: to supply a previously stored word to the computer (readout cycle) or to store a new word supplied by the computer (store cycle). For either of these two cycles, the Central Computer must specify which particular memory register (vertical column of mies) is to be involved in the ubsequent memory operation and in which direction information is to be transferred. In addition, the Central Computer must also generate a start-memory pulse to actuate the internal memory circuits. As a result, at the beginning of every core memory cycle, the following sequence of events is performed by computer commands:

- a. At TP 0, the memory address register, the memory buffer register, and the internal memory control circuits are reset to a neutral or starting condition.

- b. At TP 1 (approximately), the desired address information is transferred to the memory address register, which functions to condition the pair of current drivers (one X and one Y) that are to be actuated during the subsequent portion of the cycle.

- c. At TP 1 (delayed), a start-memory pulse is applied to the memory pulse distributor (a tapped 5.5-usec delay line) which functions to control all the internal memory operations required to complete the memory cycle.

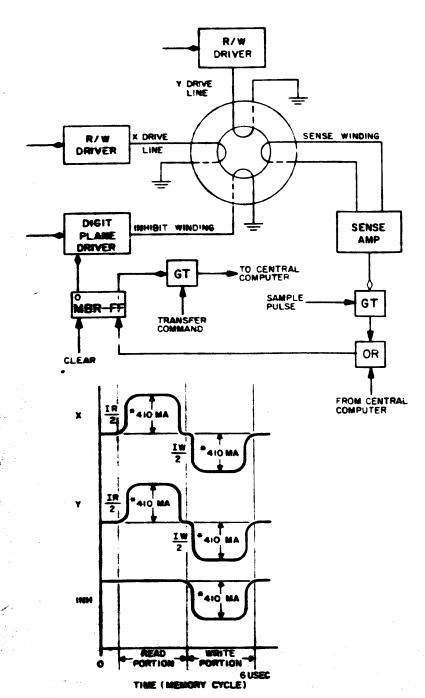

In performing its function, the memory pulse distributor provides delayed start-memory pulses to actuate the conditioned X and Y current drivers so that they will both generate a half-amplitude read and a half-amplitude write current pulse in the sequence noted in figure 7—4. In addition, delayed start-memory pulses are also supplied to the digit plane driver controls so that each conditioned digit plane driver will generate an inhibit current pulse in the sequence noted in figure 7—4. Because the read, write, and inhibit current pulses are generated in the same sequence for every core memory cycle, the analysis of internal memory operations consists of defining the function of the read and write portions of the cycle.

Since all memory cores function in the same manner, the following discussion on the details of the memory readout and store cycles will be based on the single core shown in figure 7—4, which represents the core at the intersection of the selected X and Y drive lines of one memory plane.

### 2.2.1 Memory Readout Cycle

The read portion of a core memory readout cycle is used to determine the status of the selected core. Since the magnetic fields set up by the selected X and Y drive lines add at their point of intersection, a magnetic field of +820 ma-turns will be applied to the selected core upon the generation of the coincident (X and Y) halfamplitude read current pulses (I,/2). If the selected core initially contains a 1, the applied field will cause the core to switch its magnetic state and the resultant flux change (approximately 2B<sub>r</sub>) will induce a one output signal (fig. 7-3) in the 1-turn sense winding that links all the cores of the associated memory plane. This signal, when amplified by the sense amplifier, will condition the associated gate tube. The gate tube is sensed by a sample pulse (delayed start-memory pulse) at a specific time (that is, at the peak of the amplified 1-output signal), and the resulting output pulse is used to set the associated memory buffer register flip-flop to the 1 state.

If the selected core initially contains a 0, the applied field cannot cause the core to switch, although a small flux change will result which induces a zero output signal (fig. 7-3) in the sense winding. However, since this induced signal is small, the associated gate tube will not be conditioned when sampled, and the memory buffer register flip-flop will remain in the zero state.

Thus, at the end of the read portion of the memory readout cycle, the selected core is in the zero state regardless of the initial contents of the core (destructive readout), and the associated memory buffer register flip-flop contains the initial contents of the selected core. The contents of the memory buffer flip-flop are then transferred to the specified Central Computer register by the appropriate computer-generated transfer command. Since a memory readout cycle requires that the initial

contents of the selected core be preserved for future reference, the write portion of the cycle is used to restore the selected core to its initial state.

Since the mem'ry buffer register flip-flop contains the information to be written into the selected core, this flip-flop is used to control whether the selected core will be switched to the one state or be made to remain in the zero state. This control is accomplished by supplying either a conditioning or a deconditioning level to the associated digit plane driver which, when actuated, will generate a negative current pulse of 410 ma on the 1turn inhibit winding that links all the cores of the as sociated nemory plane. If the memory buffer register flipflop comins a 1, its zero side output (= 30V level) will decondition the digit plane driver so that an inhibit current pulse will not be generated during the write portion of the cycle. Under this condition, the coincident (X and Y) half-amplitude write current pulses (1, 2) supplied to the selected X and Y drive lines, which result in the application of a magnetic field of = 820 maturns to the selected core, will cause the selected core to be switched to the one state.

If the memory buffer register flip-flop contains a 0, its zero side output (+10V level) will condition the digit plane driver so that an inhibit current pulse will be generated in coincidence with the half-amplitude write current pulses. Since the inhibit winding is wound so that its applied field will oppose the individual magnetic fields set up by the X and Y drive lines when the latter are energized by half-amplitude write current pulses, the inhibit current pulse, although actually negative, has the same effect as a half-amplitude read current pulse which is positive. Under this condition, the magnetic fields set up in the scienced core by the three coincident current pulses will add algebraically to produce a net applied field of -410 ma-turns (equivalent to haltwrite), which is not sufficient to switch the core to the one state. As a result, the selected core remains in the zero state.

### 2.2.2 Memory Store Cycle

The memory store cycle is very similar to the memory readout cycle in that the read, write, and inhibit current pulses are controlled and generated in exactly the same manner. In fact, these two types of memory cycles differ in only two respects. During the execution of a memory store cycle, the sense-amplifier-gate-tube sample pulse is not generated (inhibited by a computer command), and the memory buffer register flip-flop is loaded from an external source prior to the write portion of the cycle. Since the memory buffer register flip-flop cannot be made to reflect the status of the selected core, the read portion of the cycle effectively erases the initial contents of the core by ensuring that the selected core will be in the zero state prior to the write portion of the cycle. During the write portion of the store cy-

VOL II, PART 7

cle, the new information contained in the memory buffer register flip-flop is written into the selected cure in exactly the same manner described for the memory readout cycle.

### 2.3 ANALYSIS OF FERRITE CORE OUTPUT SIGNALS

To simplify the previous discussions of the principles of ferrite core operation, the simple waveforms of figure 7-3 were purposely used as examples of the output signals of both the selected ferrite core and the sense winding of a memory plane. However, since the sense winding links all the cores of a memory plane, the sense winding output voltage actually represents the summation of the selected core output voltage and the noise voltages generated by all the other cores in that plane. Since the output voltage characteristics (am. plitude, duration, and polarity) of each core depend on (1) the flux state of the core, (2) the amplitude, duration, rise and fall time, and polarity of the cuttent pulses that affect the core, and (3) the wiring geometry of the sense winding, the resultant amplitude and timing of the noise voltages generated during a specific memory cycle depend on many variable operating conditions. As a result, the sense winding output voltage wave. form is a complex variable in which the amplitude of noise spikes can exceed (depending on the operating conditions) the amplitude of a ONE output signal by a factor of 3 to 1. The present discussion is limited to an analysis of the individual ferrite core output signals produced under various operating conditions; the manner in which the individual cores affect the sense wind. ing output voltage is discussed in 2.4.

Since the output signal of a selected core is sampled during the read portion of a memory readout cycle, the following analysis of ferrite core output signals is based on the core response to read-current pulses only. He cause the noise voltage generated during this portion of the memory cycle is produced by the output signals from the half-selected cores (to be discussed in 2,4), this analysis includes the core response to both full-selected and half-selected cores.

An examination of the hysteresis loop of figure 7—4 shows that under normal core memory operation a ferrite core can be made to remain in one of five basic remaint flux states. (Actually, the ferrite core exhibits nine distinct flux states; however, only the five basic flux states will be considered in this discussion. The four flux states that are omitted are actually minor deviations of four of the five basic flux states.) The five remaint flux states shown in figure 7—4 are identified by symbols which designate the information status of the core (one or zero) and the polarity and amplitude of the last current pulse that was applied to the core prior to the memory cycle in process. (The manner in which a core is made to exhibit a specific remnant flux

state is discussed in 2.4.) If the last current pulse applied to a core was equivalent to a full-amplitude current pulse (summation of X and Y drive line current pulses applied to a selected core), the core is said to be in an undisturbed state (only the undisturbed one state is possible). If the last current pulse applied to a core was equal to a half implitude current pulse (read, write, or inhibit), the core is said to be in a disturbed state (17. wz, r1, and w1), and the half-amplitude current pulse is said to be a disturbing pulse. The disturbed flux states of a core are referred to as write disturbed or read disturbed, depending on whether the last disturbing pulse was a calf amplitude write or a half amplitude read current pulse. Since the inhibit current pulse is equivalent to a half-amplitude read current pulse, a core that is disturbed by an inhibit current pulse is considered to be read disturbed.

The output voltage generated by a core during the read portion of a memory cycle depends upon the initial magnetic state of the core and the characteristics of the read current pulse. Since each of the five remnant flux states can be affected by either half-amplitude or full-amplitude (fully selected) read current pulses, 10 distinct output voltages are possible Figure 7-6-lists these output voltages by name and symbol and shows the general waveshapes and voltage amplitudes that will be obtained for a typical core. In each case, the output voltage symbol subscripts fully define the initial state of the core as well as the amplitude of the read current pulse that produced the voltage. As an example, consider the symbol (V<sub>b</sub>). The subscripts r and z specify that the core was in the read disturbed zero state, and the subscript h specines that the core was actualed by a half amplitude read current pulse. Absence or the subscript spicifying current pulse amplitude indicates that the core is actuated by a full-amplitude (selected core) read current pulse.

A study of the hysteresis loop of figure 7-4 reveals that the remnant flux of a core in the read disturbed one (r1) or read disturbed zero (rz) state is not permanently changed by the application of a half-amplitude read current pulse in that the respective flux path f-j-f or b-d-b is traversed. As a result, the core output voltage that is produced under either of these two half-selected conditions is a result of completely reversible flux changes. Because these flux changes are reversible, the amplitude and duration of these two output voltages are directly related to the rise and fall time of the applied current pulse and the flux density of the core.

Since the flux density of a core in the read disturbed zero state (rz) is slightly greater than the flux density of a core in the read disturbed one state (r1), the amplitude of the half-select read disturbed one (N, ) output voltage is slightly greater than the half-select read disturbed zero (N<sub>in</sub>) output voltage (fig. 7-6).

|   | PRITIAL<br>STATE OF<br>COME | OUTPUT WHEN I <sub>r</sub> is applied                            | AMP.<br>SV<br>MV | OUTPUT WHEN 1 2 IS APPLIED                            | AMP<br>IN<br>MV |

|---|-----------------------------|------------------------------------------------------------------|------------------|-------------------------------------------------------|-----------------|

| 1 |                             | v <sub>z</sub> - Full selected<br>Write disturbed zero           | 22               | W bz - HALF SELECTED WRITE DISTURBED ZERO             | 10              |

| 2 | 72                          | <sub>F</sub> V <sub>g</sub> - FULL SELECTED  READ DISTURBED ZERO | 16               | r hz- half selected<br>read disturbed zero            | 5               |

| 3 | •                           | uV <sub>1</sub> - FULL SELECTED<br>UNDESTURBED ONE               | .31              | uv hi - HALF SELECTED<br>UNDISTURBED ONF              | 14              |

| 4 | rl                          | r <sup>V</sup> l - Full Selected<br>READ DISTURBED ONE           | 131              | r hi - Half selected<br>read distumbed one            | 7               |

| 5 | <b>₩</b> 1                  | v₁- Full selected write disturbed one                            | 135              | W <sub>N</sub> - HALF SELECTED<br>WRITE DESTURBED ONE | 12              |

Figure 7-6. Outputs of a Typical Ferrite Core

A further study of the hysteresis loop of figure 7-4 sevents that the application of a full-amplitude read cursent pulse to a cose in any of the five remnant flux states, or the application of a half-amplitude read current to a core in the undiscurbed one (u1), write disturbed one (w1), or write disturbed zero (wz) flux state will result in an irreversible flux change since the core flux does not return to its initial state upon the termination of the driving current pulse. Table 7-1, which refers to the hymeresis loop of figure 7-4, specifies the flux path that is traversed for each of the eight selected conditions that result in an irreversible flux change. Since a reversible component of flux change is also produced under the abovementioned selected conditions, the output voltage generated in the sense winding is actually a summation of reversible and irreversible components of voltage. Because the duration of the irreversible component of the custput voltage is dependent on the total amount of flux change and the switching time of the ferrite material (sefer to 2.1), the duration of the three full-selected 1-comput signals ( $_{\bullet}V_{-\bullet}V_{i}$ , and  $_{\bullet}V_{i}$  in fig. 7-3) is considerably longer in time and larger in amplitude than the five other irreversible output signals ( Vkt. ... Vkt.  $_{u}V_{bar}$   $_{u}V_{r}$  and  $_{i}V_{s}$  in fig. 7-6). Examination of the hysteresis loop of figure 7-4 shows that the same amount of irreversible flux change is produced when a halfamplitude read current pulse is applied to a core in either the write disturbed one state (w1) or the write disturb zero state (wz). However, since the flux switching rate is slightly slower when the flux density of a core is being decreased than when the flux density is being increased, the write disturbed half-selected zero (.V., output sigmai as slightly greater in amplitude and shorter in durasion than the wrise disturbed half elected one (.V.) output signal (fig. 7-6).

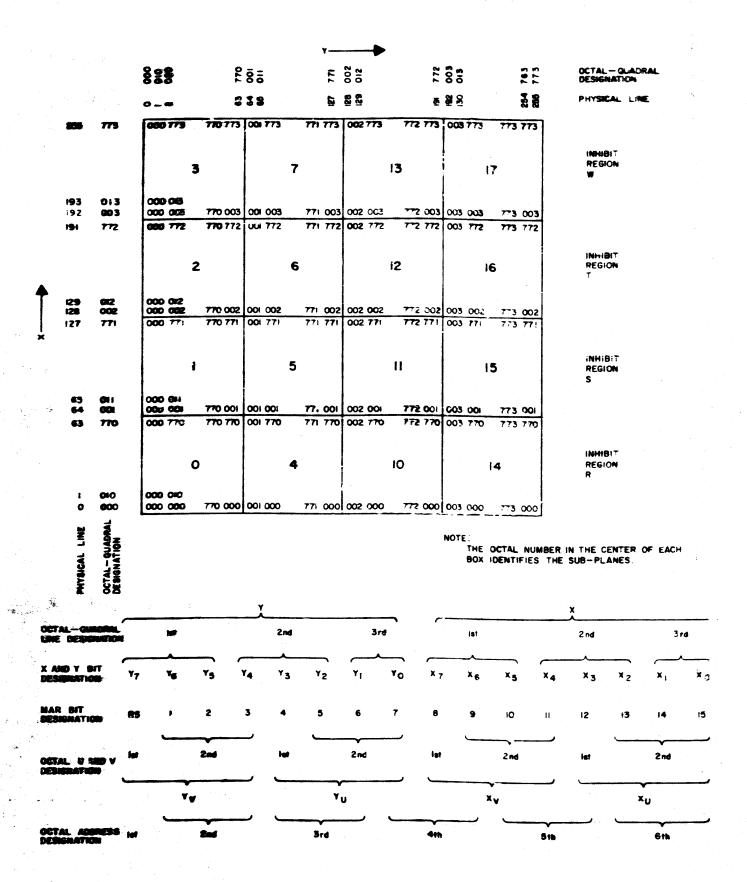

### 2.4 SINSE WINDOWS CONFIGURATION AND CUTPUT SIGNALS

As stated in 2.1, the sense winding of a memory plane in either of the two ferrite core arrays links all the coess in that plane. In the core memory 2 array this is accomplished by passing a single winding through all the coses of the 64 x 64 core matrix. Since the memory plane of the core memory array (fig. 7-7) is essentially composed of 16 core memory 2 planes (designated as subplanes), the sense winding of a core memory 1 plane is composed of 16 individual sense windings, one in each subplace. In a memory 1 plane, the individual subplane sense windings are connected in a series-parallel manner to form a single memory plane sense winding. Since the sense windings of both the memory 2 plane and the memory I subplane are essentially identical, the following discussion, which is based on the memory 2 plane, is applicable to both core memory arrays. The analysis of the sense winding output voltage is preceded by a discussion of the sense winding geometry and the

TABLE 7-1. IRREVERSIBLE FLUX CHANGES

| INITIAL REMNANT<br>STATE | READ CURRENT<br>PULSE | FLUX PATH       |

|--------------------------|-----------------------|-----------------|

| u1                       | Full amplitude        | h-j-e-a         |

| w·1                      | Full amplitude        | g-j-e-a         |

| r1                       | Full amplitude        | c-d- <b>e-a</b> |

| W.7                      | Full amplitude        | c-d-e-a         |

| f7                       | Full amplitude        | b-d-e-a         |

| ul                       | Half-amplitude        | h-j-f           |

| wl                       | Half-amplitude        | g.j.f           |

| wz                       | Half-amplitude        | c-d-b           |

manner in which the memory plane cores are affected by the read, write, and inhibit current pulses.

### 2.4.1 Sense Winding Geometry

The sense winding of a memory plane is wired in a specific pattern to provide for the optimum cancellation of the noise voltages generated during the execution of a memory cycle. These noise voltages must be minimized so that the associated sense amplifier can reliably distinguish whether the selected core contained a 0 or a 1. The present discussion is limited to an analysis of the sense winding geometry; the manner in which imise voltages are minimized is presented in 2.4.3:

Figure 7-8, A, which illustrates an 8 by 8 portion of the 64 x 64 memory 2 plane matrix, shows the arrangement of the ferrite cores and the manner in which the X, Y, and sense windings are wound through these cores. Although the inhibit winding which is wound in parallel to the Y drive ones to link all the cores in the plane, is referred to in subsequent discussions, it has been omitted in the diagram to improve drawing clarity The arrowheads on the X and Y drive lines indicate the direction of current flow for the half-amplitude read current pulses. The polarity sign associated with each core is used to indicate the polarity of the core output signal that is induced in the sense winding as a result of a read current pulse. The polarity of the core output signal is determined by using the right hand rule to determine the direction of flux change that results from the application of a read current pulse and then, using Lenr's law, to determine the direction of the induced voltage in the sense winding. In all cases, the polarity of the core output signal is referenced to the start terminal of the sense winding.

To illustrate the manner in which the sense winding polarity is determined, consider the core shown in figure 7-8, B, which is used to represent the core in the upper left hand corner of figure 7-8, A. To determine the direction of flux change produced in this core by a read current pulse, grasp the X or Y drive line in the

Figure 7-7. Comparison of 64° and 256° Core Memory Planes

right hand with the thumb pointing in the direction of correst flow. The fingers of the right hand indicate that the resultant flux change in the core is in a counterclack. wise direction. Lenz's law states that the current which flows as a result of an induced voltage is such that it will set up a field to oppose the original change of flux. Since, in this example, the direction of the flux shange has been determined to be counterclockwise, the field set up by the sense winding must be in the clockwise direction. To determine the direction of the resultant current flow in the sense winding, grasp the sense winding in the right hand so that the fingers point in the direction of the magnetic held set up by the sense winding (clockwise). The thumb of the right hand points toward the positive terminal of the sense winding. In this specific example, the end of the sense winding is the positive terminal and the start of the sense winding is the negative terminal. Since the polarity sign associated with a core is referenced to the start terminal of the sense winding the core in this example is assigned integritive reliarity. The polarity of all the other cores can be determined in the same manner. As noted in figure 7%8, A, the cores induce voltages in the sense morning is conting to a definite polarity pattern in which the sun ber of positive signs is equal to the number of negative signs. Although the figure only shows an 8 x 8 core matrix, this polarity pattern also exists in the 64 x 64 core matrix.

#### 2.4.2 Development of Disturbed Flux States

Prior to analyzing the sense winding output voltages produced during the execution of a memory readout cycle, it is first necessary to consider the manner in which the read, write, and inhibit current pulses will affect the cores of a plane. As previously stated, during

the execution of either type of memory cycle, a specific cose is selected for operation by the application of coincident half-read and half-write current pulses to the mutually perpendicular X and Y drive lines that link the selected core (to effectively produce the full-read and full-write current pulses required to switch the selected core). Reference to figure 7-8, A, shows that, because of the coincident current method of core selection, 7 coses (63 on an actual plane) on each of the selected lines will be affected by half-send and half-write current pulses, that is, they will be half-selected. The remainder of the cores that are not linked by the selected X and Y drive lines are not affected by read and write current pulses; therefore, these coms are designated as nonselected. Thus, during the execution of a memory cycle, the individual cores of a 642 memory plane are designated as fully selected (1 core), half-selected (126 cores), or nonselected (3,969 cores).

If the selected core is to contain a 1 at the end of a memory cycle, then during the execution of the memory cycle the selected core will effectively be actuated by full-read and full-write current pulses, and the 126 half-selected cores will be actuated by half-read and half-write current pulses. The nonselected cores will not be affected under this condition. However, if the selected core is to contain a 0 at the end of a memory cycle, then an inhibit current pulse (equivalent to a half-read current pulse), which is applied to the inhibit winding in

Figure 7-8. Subplace Wiring Geometry

coincidence with the write current pulses, will also be generated during the execution of the memory cycle. As a result, all cores (full-, half-, and nonselected) will be affected during the write portion of this memory cycle. Since the magnetic field set up by an inhibit current pulse is equal and opposite to the magnetic field set up by a half-amplitude write current pulse, the simultaneous application of these two current pulses to a core will result in the effective cancellation of the two fields; that is, the core will behave as if the two current pulses were not applied. Thus, if the selected core is to contain a 0, the selected core will be effectively actuated by a fullread and a half-write current pulse, the 126 half selected core will be effectively actuated by a half-read current pulse only, and the 3,969 nonselected cores will be actuated by an inhibit current pulse (effective half-read).

Table 7-2 provides a summary of the sequence of current pulses that are applied to the memory plane for the two conditions of selected core content. Since the table is based on the final content of the selected core, the current pulse sequences noted in the table are applicable for both the memory readout cycle and the memory store cycle.

Since the remnant flux state of a core is determined by the polarity and amplitude of the last applied current pulse, a study of table 7-2 and figure 7-4 will show how each core is affected under the two moditions of selected core content. If the selected core is to contain a 1 at the end of the memory cycle, the selected core will be left in the undisturbed one (v.t.) flux state, the individual half-selected cores will be left in the write disturbed one (w1) or write disturbed zero (w7) flux state (depending upon whether the individual core contains a Lor a u), and the 3,000 nonselected cores will remain static; that is, in their original flow scare. If the selected core is to contain a 0 at the end of the memory cycle, the selected core will be left in the write discurbed zero (wz) flux state and the individual half-selected cores and nonselected cores will be left in either the read disturbed zero (rz) or read disturbed one (r1) flux state (depending upon whether the individual core contains a 1 or a 0). From the above discussion, it can be seen that any cores in a plane can be made to exhibit any one of the five remnant flux states.

### 2.4.3 Analysis of Sense Winding Output Voltage

A study of the 64 x 64 core matrix (a part of which is shown in fig. 7-8, A) reveals that, when the selected X and Y drive lines are energized with half-amplitude read current pulses (to read out the contents of the selected core), a total of 127 cores are involved in producing the sense winding output voltage. That is, when a particular core is selected, the sense winding output represents the summation of the selected core output voltage and the noise voltages generated by the 126

half-selected cores (63 cores on the selected X and Y drive lines). A study of figure 7-8, A, shows that each X and Y drive line contains a number of positive and negative cores; therefore, in a 64 by 64 core matrix, each drive line will contain 32 positive and 32 negative cores. Thus, because of this sense winding polarity pattern, the application of coincident half-read current pulses to the selected X and Y drive lines of a memory plane will result in the generation of 62 (31 cores on the selected X and Y drive lines) half-selected output voltages whose polarity is the same as the polarity of the selected core output voltage, and 64 (32 cores on the selected X and Y drive lines) half-selected output voltages whose polarity is opposite to the polarity of the selected core output voltage. As a result, the half-selected output voltages of 124 of the 126 half-selected cores (62 positive and 62 acquive output voltages) will tend to cancel each other. However, complete cancellation of these 62 pairs of half-selected cores (a pair consists of one positive and one negative half-selected core) can only occur under specific conditions since the amplitude of the individual half-selected output voltages depends upon which flux state the core exhibits prior to the application of the half-read current pulse. The half-selected output voltages of 2 of the 64 half-selected cores whose pularity is opposite to the polarity of the selected core will not be cancelled; therefore, these two half-selected output voltages will subtract from the selected core output voltage. The equation to express the sense winding output voltage produced during the read portion of the memory cycle may be written as follows:

$$\mathbf{V}_{\rm cost} = \mathbf{V}_{\rm s} - 2\mathbf{V}_{\rm h} \pm 62\mathbf{V}_{\rm d}$$

where

$V_{ext}$  = the output voltage of the sense winding

$V_{a} =$  the output voltage of the selected core

V<sub>0</sub> = the average half-selected output voltage whose polarity is opposite to the selected core output voltage

V<sub>4</sub> = the difference between the average positive half-selected output voltage and the average negative half-selected output voltage.

The last seem of the equation, which deals with the summation of the half-selected output voltages that tend to cancel each other, is defined as the delta voltage of the sense winding output. The delta voltage may be either positive, negative, or zero, depending upon whether the average positive half-selected output voltage is larger than, smaller than, or equal to the average negative half-selected output voltage. Since the delta voltage is obtained from 62 pairs of half-selected cores, it follows that, if each core of a pair of cores is in the

same flux state (fig. 7—4) and if the characteristics of all the cores are considered to be exactly the same, the application of a half-read current pulse to the half-selected cores will cause each core of a pair of cores to generate a half-selected output voltage that is exactly equal to, but of opposite polarity to, its mate. If each of the 62 pairs of half-selected cores is thus balanced, the delta voltage will be equal to zero to provide for the maximum cancellation of half-selected output signals. In memory maintenance programming, this condition of maximum cancellation of half-select output voltages is obtained by using either a 1's or a 0's rest pattern whereit all the cores of a memory plane are in either the one or zero flux state.

A study of the equation reveals that the maximum value of delta voltage is obtained when alk the half-selected cores of one polarity produce the smallest halfselected output voltages, while all the half-selected cores of the opposite polarity produce the largest half-selected output voltages. Reference to figure: "-6 shows that the smallest half-selected output voltage is produced by a core in the read discurbed zero (17) flux state, and that the largest half-selected output voltage is produced by a core in the undisturbed one (u1) flux state. However, since it is only possible for one core on an X or Y drive line to exhibit the undisturbed one (u1) flux state at any particular time (an attempt to cause a second core to exhibit the undisturbed one flux state will cause the existing undistarted core to be write disturbed, refer to 2.3), this flux state does not enter into the determination of the maximum value of detta voltage. Instead, the maximum value of delta wiltage is obrined when all the half-scienced cures one pularity are in the read disturbed zero (rz) flux state, and all the had selected cores of the opposite primary are in the write disturbed one (w1) flux state.

Since the delta voltage can be of either polarity, the maximum value of delta voltage can be produced in

TABLE 7-2. EFFECTIVE CURRENT PULSE SEQUENCE APPLIED TO CORES OF ONE MEMORY PLANE

|               | SELECTED CORE IS TO CONTAIN |                   |

|---------------|-----------------------------|-------------------|

|               | <b>1</b>                    | •                 |

| Selected Core | Full-Read,                  | Full-Read,        |

| (1)           | Full-Write                  | Half-Write        |

| Half-selected | Half-Read,                  | Half-Read,        |

| Cores         | Half-Write                  | No Pulse          |

| (126)         |                             |                   |

| Nonselected   | No Pulse,                   | No Pulse,         |

| Cores         | No Pulse                    | Half-Read         |

| (3,969)       |                             | age of the second |

two different ways; that is, by two different test patterns. The maximum positive delta voltage is produced when all the plus half-selected cores are in the write disturbed one (wil) flux state and all the minus halfselected cores are in the read disturbed zero (12) flux state. If all the costs of the plane contain the pattern just described, the plane is said to contain a regular checkerboard passern. The maximum negative delta voltage is produced when all the plus half-selected cores are in the read disturbed zero (12) flux state and all the minus helf-refucted cases are in the write disturbed one (w1) flux state. The sest pattern that will produce this condition is defined as the inverted checkerboard pattern. Since the pulsarity of the delta and selected core output voltages can be individually positive or negative (fig. 7-4, A), eight separate conditions exist whereby the maximum value of delta voltage will either add to or subtract from the selected core output voltage to produce the meximum distortion of the selected core output voltage. A summery of the conditions under which the delta voltage affects the selected core output voltage to produce a smaller or a larger sense winding output voltage is given in table 7-3.

Reference to figure 7-6 shows that, if all the cores of a plane have identical characteristics, the maximum value of delta values produced under the abovemen-

tioned conditions will have a peak amplitude in excess of 400 mw and a duration of approximately 0.5 usec. Since the delta voltage and the selected core output woltage both start at the same time, the delta voltage always distorts the selected core output signal. If the selected core initially contained a 0, the delta voltage will completely mask the 0 output voltage since both voltages have the same duration. However, if the selected core initially contains a 1, the delta voltage will only distort the first 50 percent of the I output signal, and the 135-mv (approximate) peak of the 1 output signal will not be affected. It is because of this important timing f ctor that a time-amplitude sampling technique can be ...ed (during the execution of a memory readout cycle) to reliably determine whether the selected core contained a 0 or a 1. That is, although the peak amplitude of the delta voltage can be much greater than the amplitude of the selected core output signal, reliable memory operation is obtained by sampling (fig. 7-4) the sense amplifier output voltage at a specific time, namely, at the peak of the amplified I signal. Because the content of the selected core is sampled at a specific time. reliable discrimination between a 6 and a 1 output signal depends upon the ability of the sense amplifier to faithfully reproduce the relative raming of the sense winding waveform.

TABLE 7-3. MAXIMUM DELTA VOLTAGE COMBINATIONS

| SPLECTED CORE POLARIEY AND CONTENT | NEGATIVE<br>CORES | POSITIVE<br>CORES | RESULTANT<br>POLARITY | RESULTANT OUTPUT<br>SENSE WINDING<br>VOLTAGE |

|------------------------------------|-------------------|-------------------|-----------------------|----------------------------------------------|

| Positive 1                         | f2                | * l               | +                     | Larger positive !                            |

| Positive 1                         | <b>w1</b>         | 172               |                       | Smarrer positive !                           |

| Negative 1                         | 17                | wi                | <b>*</b>              | Smaller negative i                           |

| Negative 1                         | <b>w1</b>         | <b>72</b>         | -                     | Larger negative 1                            |

| Periode 8                          | <b>57</b>         | <b>w1</b>         | 4-                    | Larger positive 0                            |

| Pairie                             | wi                | n                 |                       | Smaller positive 0                           |

| Negative®                          | π                 | <b>w.1</b>        | <b>+</b>              | Smaller negative 0                           |

| Negative 0                         | <b>w1</b>         | n                 | ***                   | Larger negative 0                            |

### **CHAPTER 3**

### THEORY OF OPERATION OF CORE MEMORY 2 (642)

### SECTION 1

### 64º FERRITE CORE ARRAY

#### 1.1 COMPAL

The 66° ferrite core array contained in unit 11 (fig. 1-10) is the principal component of core memory 2 since it is the information storage center of this memory device. This section describes the physical characteristics of the ferrite core array to show the arrangement of its cores and windings, and to provide a definition of the terms used in the subsequent sections of this chapter.

The storage capacity of the 64° ferrite core array is equal to 4,096 words of 34 bits each. Since a single core can store one bit of information, the array contains 4.096 x 34 or 139,264 ferrite cores. These cores are arranged in a 3-dimensional array in which each horizontal layer or digit plane contains 4,096 (ores arranged in a 64 x 64 square formation. The 34 digit planes of this array are stacked vertically, and the X and Y selection windings of these planes are interconnected to form the X and Y selection windings of the erray. Actuation of the current drivers associated with one X and one Y selection winding will mutually affect the vertical column of 34 coses (one cire in each plane) that represent the selected memory register. Sunc only 33 of these digit planes are connected to sense amplifiers and digit plane drivers, only 33 planes can be active at any time. The 34th plane of the acray, which is required to provide for the symmetrical wining of the array, is used as a spare plane.

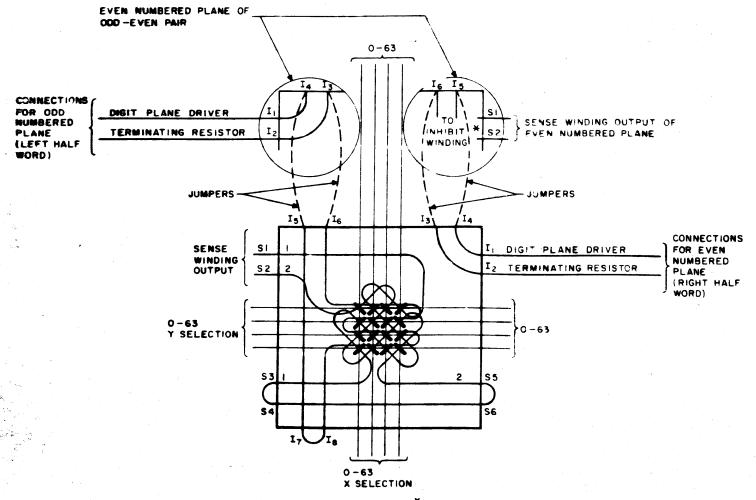

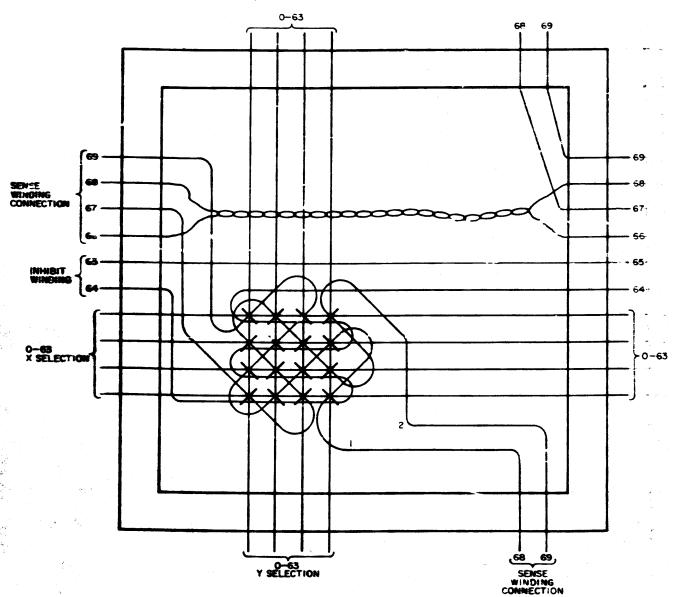

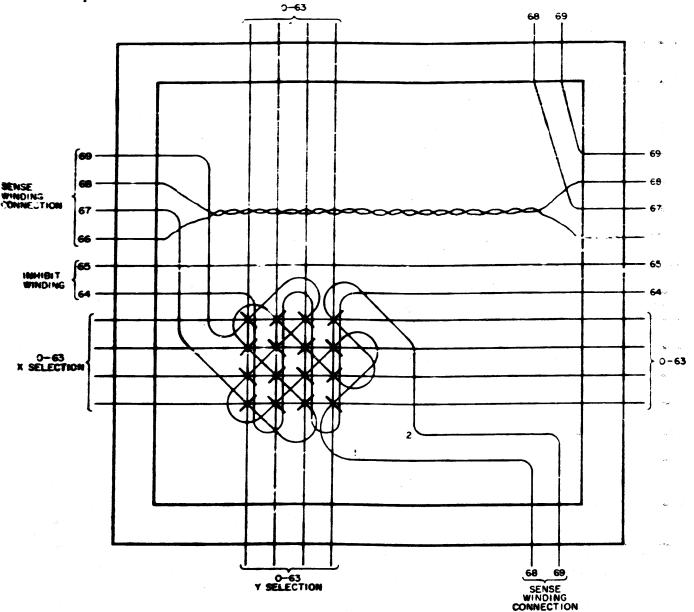

### 1.2 64º PLANE WIRING CONFIGURATION

All the digit planes used in the 64- ferrite core array are identical. Each plane contains 4,0% cores in a 64 x 64 formation and all the windings necessary for memory operation. Figure 7-9 shows an abbreviated version of a 64- digit plane using 16 cores in a 4 x 4 formation. Since the inhibit windings of an odd-even pair of planes are interconnected (although not interrelated), this drawing also shows a portion of the associated even-numbered plane. In all cases, the even-numbered plane of an odd-even pair is located beneath the odd-numbered plane and is turned upside down in relation to the odd-numbered plane. In general, the odd-numbered planes of the array represent the individual bits of the left half memory word, and the even-numbered

planes epresent the individual bits of the right half memory word. In all cases, the digit plane drivers and sense amplifiers associated with the left half-word are connected to the digit planes on the left side of the array. Conversely, the digit plane drivers and sense amplifiers associated with the right half-word are connected to the digit planes on the right side of the array

### 1.2.1 X and Y Selection Windings

As noted in figure "-9, each X selection winding is wired through a single column of cores, while each Y selection winding is wired through a single row of cores Selection of a particular core is accomplished by applying coincident half amplitude, read-write current pulses to the appropriate X and Y selection windings (those that link the desired core) in such a direction that the resultant magnetic fields will add at the intersection of the two windings. As a result of this requirement, and because of the manner in which the cores are positioned (fig. 7-9), the direction of the read-write current pulses that are applied to an X of Y mission wir ing must be of the apposite polarity (applied in the apposite direction) when compared with the current pulses that are applied to the adjacent X or Y selection windings of a memory plane. Since all the X and Y current drivers produce read-write current pulses of the same polarity pattern (fig. 7-4), the required reversal of current flow in adjacent selection windings is accomplished by connecting the current drivers to consecutive selection windings on alternate sides of the array

The manner in which the X and Y drivers are connected to the 64-core array to produce the desired result is discussed in 1.3. Included in 1.3 is a discussion of the manner in which the similarly numbered: X and Y selection windings of the 34 planes are interconnected to form the selection windings of the array.

### 1.2.2 Inhibit Winding

The inhibit winding of each active digit plane of the 64° ferrite core array is assocated with an individual digit plane driver. During the execution of a memory cycle, each digit plane driver is controlled so that a negative current pulse will be applied to the associated inhibit winding during the write postion of the cycle if it is required to inhibit the writing of a 1 in the selected core of the plane.

As noted in figure 7-9, the inhibit winding of each digit plane consists of a 1-turn winding which is wound through all the cores of a plane in parallel with the Y selection windings. Because the direction of this winding is alternated in adjacent rows of cores, the inhibit current pulse effectively flows in opposite directions through alternate rows of cores. Since write current pulses (negative) are applied to adjacent Y selection windings in opposing directions, the proper connection of the digit plane driver will cause the individual magnetic fields set up by the inhibit current pulse and the Y selection winding write current pulse in each core of the selected row of cores to completely cancel each other. To illustrate this point, consider the following example, which assumes that the digit plane shown in figure 7-9 represents the topmost plane of the array. Under this condition, a read-write current driver will be connected to the Y-O selection winding on the right side of the array so that the direction of this winding through this plane will be from right to left. The digit plane driver for this plane is connected to pin I1 of the next lower

plane. As a result of the internal array wiring (jumper wires serially connected from pin 11 of the even-numbered plane to pin 18 of the odd-numbered plane), the direction of the inhibit winding through the Y-O row of cores will be from left to right. Since the Y selection winding write current pulse and the inhibit current pulse are both of the same polarity (negative), the magnetic fields set up by these two windings will be in opposite directions for each core in the Y-O row of cores. The net result is that these two fields cancel each other in each of the mutually affected cores.

Because the X and Y array selection windings are formed by serially connecting the similarly numbered drive halfs of adjacent planes, the direction of readwrite current flow in the similarly numbered drive lines of adjacent digit planes will always be in mutually opposing directions. To compensate for the effects of the winding reversal of the similarly numbered X and Y drive lines of adjacent planes, the direction of the inhibit winding must also be reversed in adjacent planes. In the 64° ferrite core array, the inhibit winding reversal is accomplished by the physical inversion of alternate planes of the array. To illustrate the manner in which this is accomplished, consider the inhibit winding con-

FROM SENSE WINDING OF EVEN NUMBERED PLANE

Figure 7-9. Top View of 64<sup>2</sup> Digit Plane (Odd)

mections of the odd-even pair of planes shown in figure "-9. From the previous example, it was determined the inhibit winding of an odd-numbered plane is wound through the Y-O row of cores in a left to right direction. Thus, for an even-numbered plane, the inhibit winding must be wound through its Y-O row of cores in a right to left direction. Figure "-9 shows that the digit plane driver for an even-numbered plane is connected to pin I1 of the associated odd-numbered plane. As a result of the internal array wiring (jumper wires serially connected from pin I1 of an odd-numbered plane to pin I8 of an even-numbered plane) and because the plane is relatively upside down, the direction of the inhibit winding through the Y-O row of cores of the even-numbered plane will be from right to left.

### 1.2.3 Sense Winding

The sense winding of each active digit plane is associated with a differential input sense amplifier which functions to amplify the induced voltages produced by the switching action of each core in the plane. As noted in figure 7-9, each digit plane has two separate sense windings (labeled 1 and 2) which are connected in series by means of internal and external jumper wires to form one long winding. Each individual sense winding which passes through half of the cores of the plane follows a diagonal path in order to minimize the capacitive and inductive coupling between itself and the other windings of the plane. The two ends of the sense winding (S1 and S2) are connected to the differential input sense amplifier so that only the induced voltage will be amplified. That is, since capacitive-coupled voltages do not produce a difference voltage between these two terminals, they will be rejected by the amplifier.

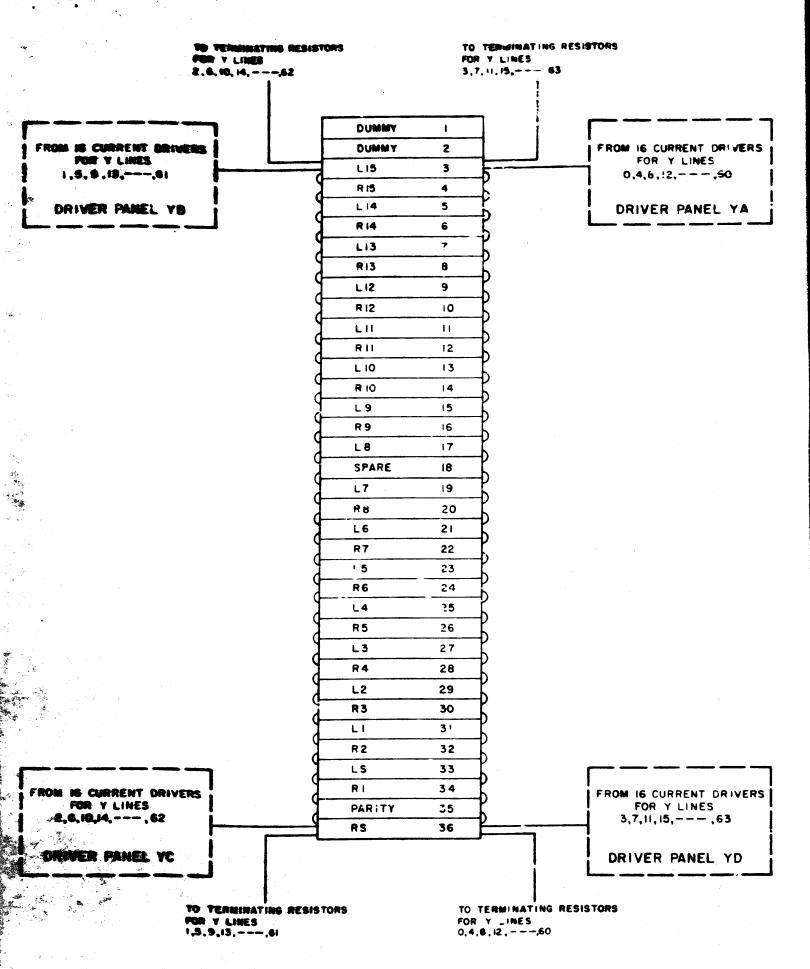

### 1.3 X AND Y CURRENT DRIVER CONNECTIONS

The complete 642 ferrite core array contains 34 digit planes (of the type described above) and 2 dummy planes. Figure 7-10 shows the overall arrangement of these planes to form the array and the word bit assignment of each plane. Although two dummy planes are not involved in the array wiring, they are included in this figure because they affect the plane identification numbering sequence. The two dummy planes do not contain any cores or windings and are only used as spacers in the array assembly. A study of figure 7-10 shows that the odd-numbered planes of the array (3, 5, 7, ..., 35) are associated with the left half memory word, and the even-numbered planes (4, 6, 8, . . . , 36) are associated with the right half memory word. Plane number 18 is designated the spare plane because, being in the approximate center of the array, it requires the shortest jumpers (for sense amplifier and digit plane driver connections) if it is used to replace one of the active planes.

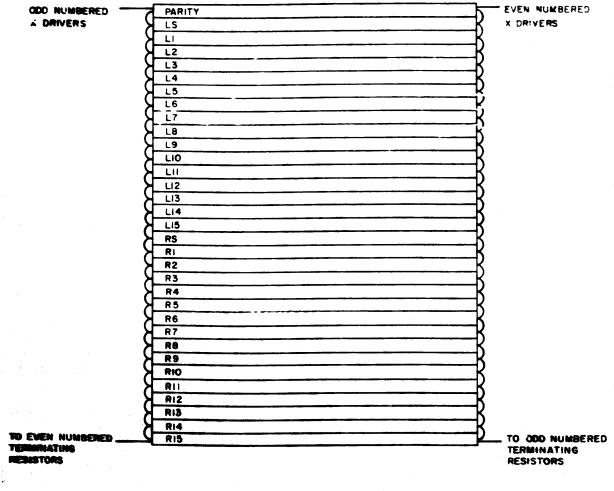

Because selection of a memory word involves the simultaneous application of read-write current pulses to similarly addressed cores in each plane, the corresponding X and Y drive lines in each of the 34 planes of the array will be involved in the operation. To provide a control so that one current driver can supply read-write curre t pulses to the corresponding X or Y drive line of each plane, the similarly numbered X and Y drive lines of all the planes are connected in series (by means of jumpers) so that common selection windings will be formed. One end of each of the 64 X and 64 Y selection windings is connected to a read-write current driver; the other end of each winding is connected to ground through a terminating resistor. In this ferrite core array, all the X selection line drivers (64) are connected to the front and back sides of the array and all the Y selection line drivers (64) are connected to the left and right sides of the array. Since the input and output connections of the X and Y selection windings are exactly the same, the following discussion will deal with Y selection windings only.

As noted in figure 7-10, the 64 Y line current drivers are divided into four equal groups. Each group of 16 drivers is contained in a pluggable driver panel which is connected to the array in a specific manner. The 16 Y line drivers of driver panel YA are connected (on the right side of the array) to every fourth Y selection line of plane 3, starting with line Y-O. Since the similarly numbered Y lines of each of the 34 digit planes are connected in series (by connecting the similarly numbered terminals of adjacent planes on alternate sides of the array), each of these Y lines will terminate on the right side of plane 36. To complete the circuit of each of these windings, the associated terminals of this plane are connected to ground through individual terminating resistors and a common 240-ohm resistor and a circuit breaker arrangement.

The 16 current drivers of each of the other Y driver panels are connected to the array in a similar manner; that is, the current drivers are connected to one end of the array and the associated terminating resistors are connected to the other end. Because the Y line current drivers are connected to the array in the sequence noted in figure 7–10, the direction of read-write current flow in the adjacent Y lines of each plane will be in mutually opposing directions.

The 64 X selection winding current drivers and terminating resistors are connected to the front and back sides of the array in exactly the same manner as described above. The current drivers contained in driver panels XA and XD are connected to the front side of the array, to every fourth X selection line, and the current drivers contained in driver panels XB and XC are connected to the rear side of the array.

Figure 7-10. Front View of 64º Ferrite Core Array

## SECTION 2 BLOCK DIAGRAM ANALYSIS

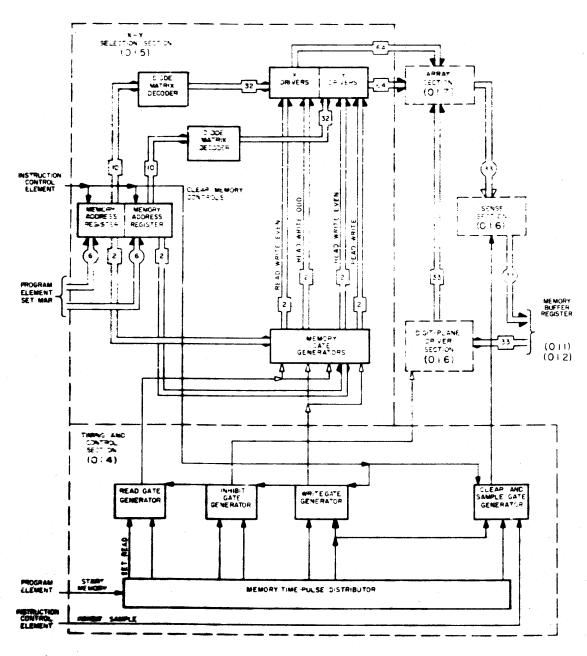

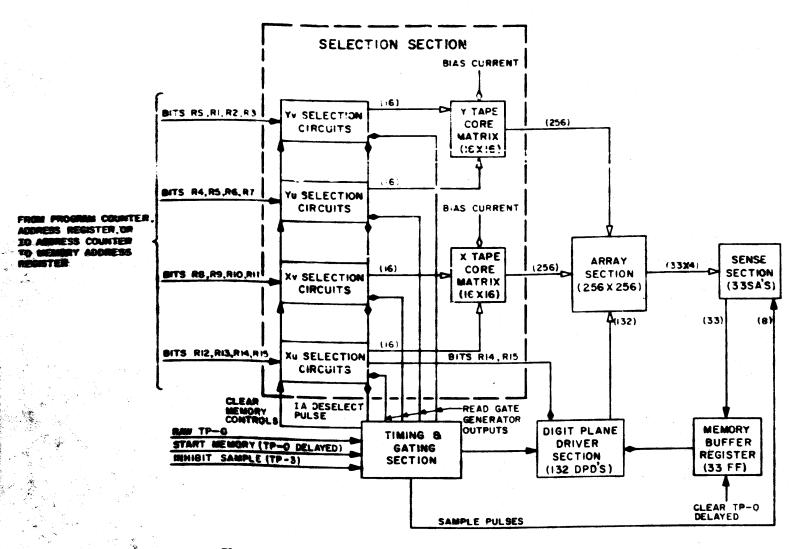

A simplified block diagram of the 64° core memory pulses is shown in figure 7–11. As noted in the figure, various input and output pulses and levels are generated during the execution of a memory cycle. The source and destination of these pulses and levels are tabulated in table 7–4.

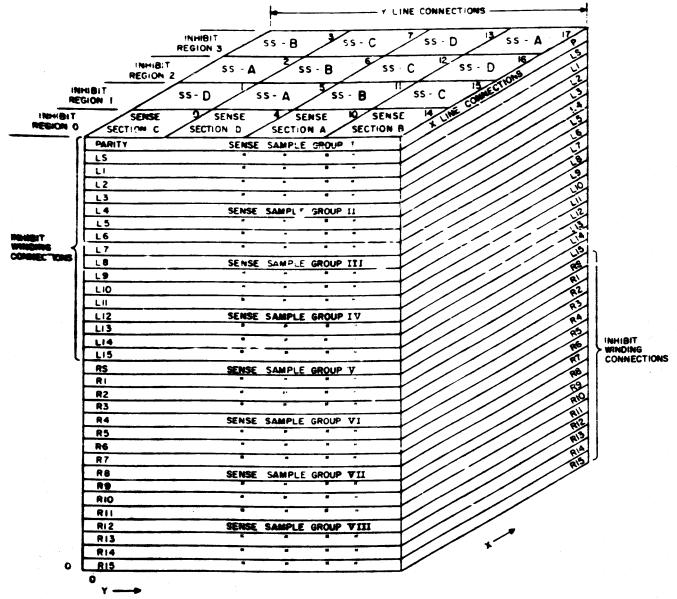

As indicated in figure 7-11, the 64<sup>2</sup> core memory is divided into five sections: the selection section, the array section, the sense section, the digit plane driver section, and the timing and gating section. The memory buffer register, although not exclusively a part of the 64<sup>2</sup> memory, is also shown in this simplified block diagram since it is the only path by which core memory can communicate with the rest of the Central Computer System.

The selection section of the 642 core memory is composed of two identical portions, an X portion and a

TABLE 7-4. SOURCE OR DESTINATION OF CONTROL

| CONTROL PULSE               | TO OR THE                             |

|-----------------------------|---------------------------------------|

| Clear memory control        | Instruction conts<br>element          |

| Set memory address register | Program elcments                      |

| Start memory                | Program elemental                     |

| Inhibit sample              | Instruction control command generator |

| Sense amplifier output      | Memory buffer resister                |

| Inhibit control levels      | Mcmory buffer and ster                |

Figure 7-11. 64º Memory Device, Block Diagram

Y portion. The selection section contains circuits which decode information received from the program counter, address register, and the 1O address counter. It also contains the memory address register, the memory gate generators, and the 64 X and 64 Y core memory drivers which generate the read and write current pulses that are applied to the selected X and Y lines in the array section.

As previously stated, the array section contains 33 active digit planes. Each digit plane contains a sense winding and an inhibit winding in addition to the 64 X and the 64 Y drive lines. The sense and inhibit windings of each active plane are connected to the sense amplifier and digit plane driver associated with a specific bit of the memory buffer register.

The sense section contains 33 individual sense amplifiers, one for each of the 33 active planes. Each sense amplifier amplifies the signal picked up from its associated sense winding and applies it to a sample gate tube which is sensed at the peak of an amplified 1-core output signal. The sampling pulse is developed in the timing and gating section and simultaneously samples all 33 gate tubes. If a specific gate tube is conditioned when it is sampled, the resulting output pulse will set the associated memory buffer register flip-flop to the 1 state. If a sense amplifier does not condition its sample gate tube, no output is produced when the tube is

sampled; therefore, the associated buffer register flipflop remains in the 0 state. During the execution of a memory store cycle, the sample pulse is inhibited so that none of the sample gate tubes can be sensed."

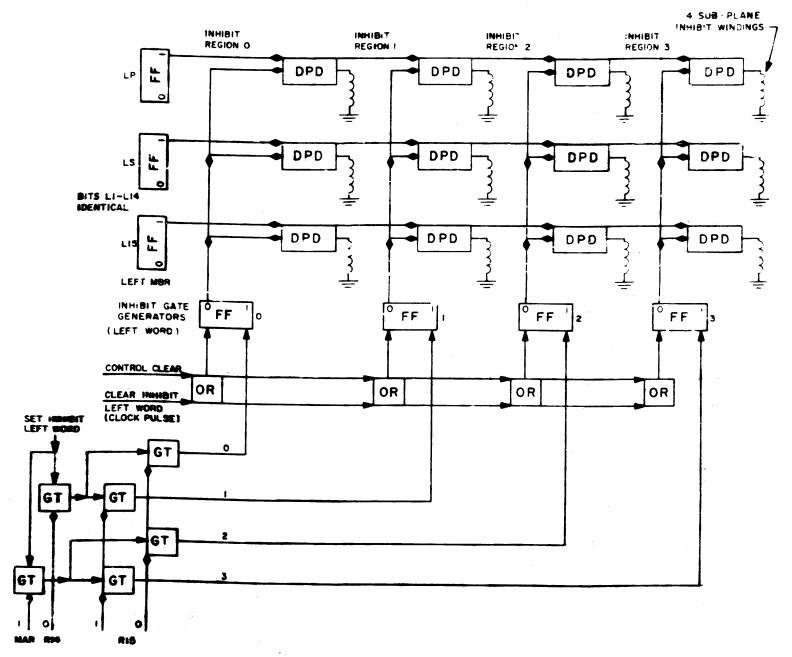

The digit plane driver section contains 33 digit plane drivers. Each digit plane driver is associated with a digit plane of the core memory array section and a particular flip-flop of the memory buffer register. Each individual driver is conditioned by its associated memory buffer register flip-flop and is controlled to generate an inhibit current pulse if the flip-flop contains a 1, the associated digit plane driver is not conditioned and therefore does not generate an inhibit current pulse.

The timing and gating section contains the memory pulse distributor, which is composed of series-connected delay lines interspersed with pulse amplifiers to amplify the signal between the output of one delay line and the input to another. These three types of control flip-flops contained in this section are used to generate dic gates which control the operation of the other sections of the 64° memory. These three gates which are obtained from the 1 side output of the control flip-flops are identified as the read gate, the write gate, and the inhibit gate. The input pulses which control the setting and clearing of these flip-flops are obtained from the memory pulse distributor.

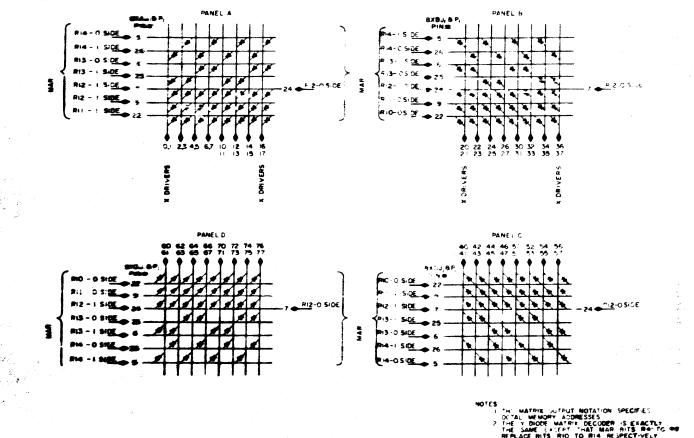

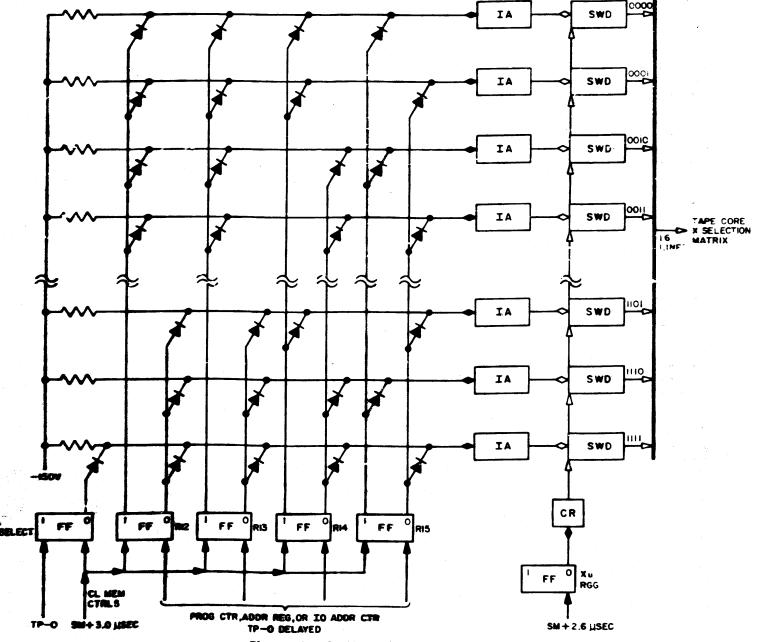

## SECTION 3 ADDRESS SELECTION

Selection of the 64<sup>2</sup> core memory register from which information is to be read, or into which information is to be stored, is controlled by the selection section. This section contains the flip-flop memory address register which is composed of 12 flip-flops. Six of these flip-flops and a diode matrix decoder are associated with the X portion of the selection section; the other six flip-flops and a second decoder are associated with the Y portion. The two portions operate similarly and

are controlled simultaneously to select one X and one Y core memory current driver. Since the two portions of the selection section are exactly the same, the following discussion will deal only with selection of an X driver.

At the beginning of each memory cycle, the memory address register flip-flops are cleared by a clear-memory-controls pulse from the instruction control element. Approximately 0.6 usec later, new address information is transferred to the memory address register from either

Figure 7-12. 64 Memory Selection Section

the program counter, the address register, or the 10 address counter (fig. 7-12). The output levels from both the 1 and 0 sides of five of the flip-flops (bits R10 through R14) are supplied to the diode matrix decoder, and the output of the sixth flip-flop (R15) is fed to the memory gate generator circuits. The information which the decoder accepts from the five flip-flops is decoded in a diode acquire AND circuit to select one of 32 output lines. (See fig. 7-13.) The 31 nonselected lines have an output level of +10V; the selected line has an output level of -30V. The selected output level is amplified to partially condition two adjacent core memory drivers, one for an even address and one for an odd address. One of these two drivers is then further selected by the proper memory gate generator.

#### Note

The memory game generators, shown in figure 7—12, are logical AND circuits, each requiring both a d-c level from the sixth memory address register flip-flop and a read or a write gate from the tianing and gating section. Four

memory hate generators are used, two for reading (read udd, read even) and two for writing (write odd, write even).

If the sixth memory address register flip-flop is in the cleared state, he d-c level from its 0 side is at +10V and conditions the read-even and write-even memory gate generators (fig. 7-14). When pulsed by a read or a write or a write gate from the timing and gating section, these generators activate the read or control lines of the 32 even-core memory drivers and cause the selected current driver to generate a read or write current puls: If the sixth flip-flop is set, it conditions the read-odd and write-odd memory gate generators, which, in turn, activate the read or write control lines of the 32 odd core memory drivers. When these gate generators are pulsed by a read or a write gate from the timing and gating section, the partially selected current driver will generate a read or write current pulse.

#### Note

In the Y selection section, the outputs of bits R4 through R8 are supplied to the diode ma-

Figure 7—13. Diade Matrix Decoders

trix decoder and the outputs of bit R9 are used to select the odd or even pair of memory gate generators.

The X and Y core memory drivers, which are partially conditioned by the diode matrix decoders through the matrix output amplifiers, are further conditioned at the proper time by a read or a write gate from the selected memory gate generators described above. The selected X and Y drivers supply current

pulses to an X and a Y co-ordinate line of the core memory array. These current pulses are of sufficient amplitude and duration to half-select the cores of the co-ordinate lines. As the intersection of the two co-ordinate lines, the individual half-select current pulses are algebraically added to apply a full-amplitude current pulse to the selected core. Overall operation of the core memory drivers is the same during the read and the write functions, except that the polarity of the output is reversed.

Figure 7-14. 64<sup>2</sup> Memory Driver Selection

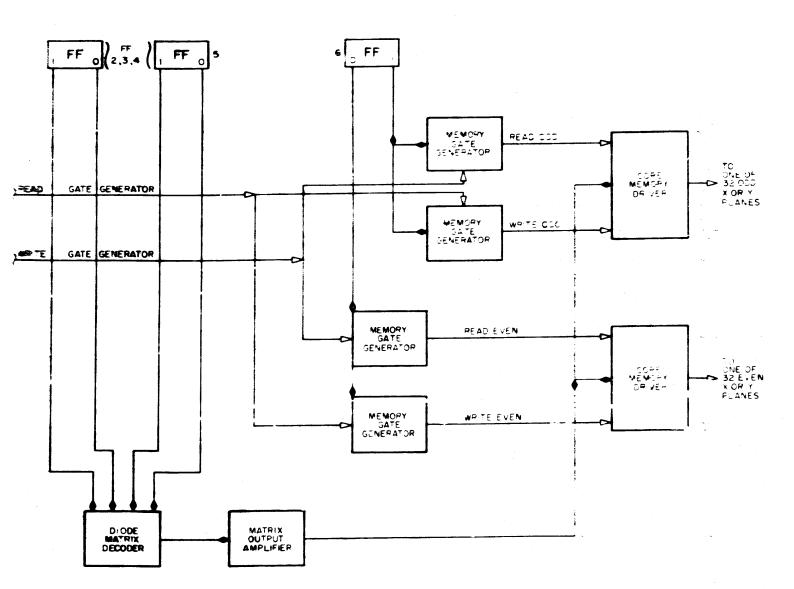

## SECTION 4 TIMING AND CONTROL

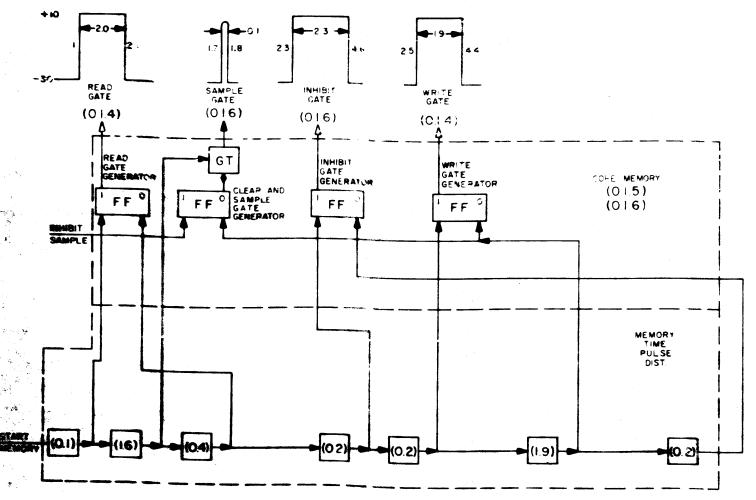

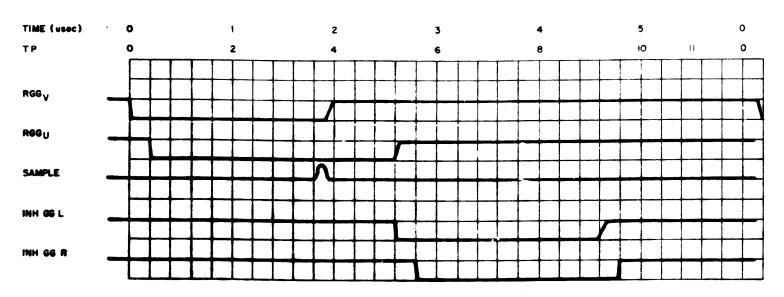

The timing and gating control section of the 642 cone memory receives the start-memory pulse from the program element for both types of memory cycles and, during the execution of a memory store cycle, this section also receives the inhibit-sample pulse from the instruction control element. The timing and gating section provides the three gate signals and the sample pulse to operate the various portions of the core memory in proper sequence. A block diagram of the timing and gating section showing typical timing notations is shown in figure 7-15.

ૈં .

As shown in figure "-15, the start-memory pulse is applied to the memory time pulse distributor, which is a chain of delay lines. The start-memory pulse delayed 0.1 usec is used to set the read-gate generator. This is subsequently cleared by the start-memory pulse delayed approximately 2.3 usec. The 1-side output of the

read gate generator, which is a positive pulse, is applied to the selection section and determines the timing and duration of the read-current pulse that is supplied to the selected X and Y driver lines.

The sample gate generator of the timing and gating section differs from the other gate generators in this section in that the 0-side output controls a gate tube which is sampled by the sample pulse from the memory time pulse distributor. During a memory readout cycle, the inhibit-sample pulse is not generated, and the clearand-sample gate generator remains in the 0 state. In this condition, the gate passes the sample pulse to the sense section approximately 1.9 usec after the start-memory pulse is initiated. During the memory store cycle, an inhibit-sample pulse from the instruction control element is supplied to the sample-gate-generator flip-flop, setting the flip-flop to the 1 state. Thus, the gate tube is deconditioned when sensed by the sample pulse.

Figure 7-15. 64º Timing and Gating Circuits

The write-gate-generator flip-flop receives a setwrite pulse from the memory time pulse distributor approximately 2.7 µsec after the start-memory pulse is initiated and receives a clear-write-gate-generator pulse approximately 1.9 µsec later. The resultant output pulse from the write-gate-generator flip-flop, which is approximately 1.9 µsec in duration, is applied to the selection section and determines the timing and duration of the write current pulse that is supplied to the selected X and Y driver lines.

The inhibit gate generator, shown in figure 7-13, is similar to the read and write gate generators in opera-

tion and function. The set-inhibit pulse is supplied by the memory time pulse distributor approximately 2.5 usec after the start-memory pulse is initiated. The clear-inhibit pulse (from the same source) is received approximately 4.8 usec after the start-memory pulse is initiated. The 1-side output pulse of the inhibit-gate-generator flip-flop is approximately 2.3 usec in duration and overlaps the write-gate-generator output. The inhibit gate is applied to the 33 digit plane drivers; however, only the drivers which are conditioned by the associated memory buffer register flip-flops can generate an inhibit current pulse.

Figure 7-16. 642 Sense and Inhibit Winding Pictorial

## SECTION 5 DIGIT PLANE CIRCUITRY

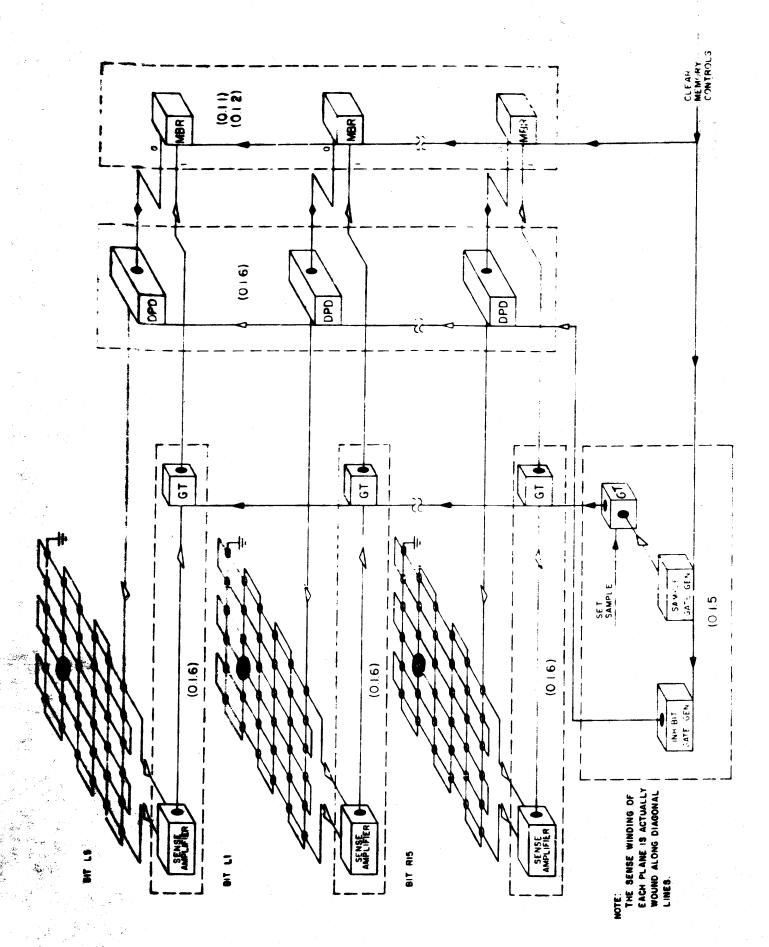

Figure 7-16 illustrates the relationship of the sense vection, the memory buffer register, and the digit plane driver section, which constitute the digit plane circuitry.

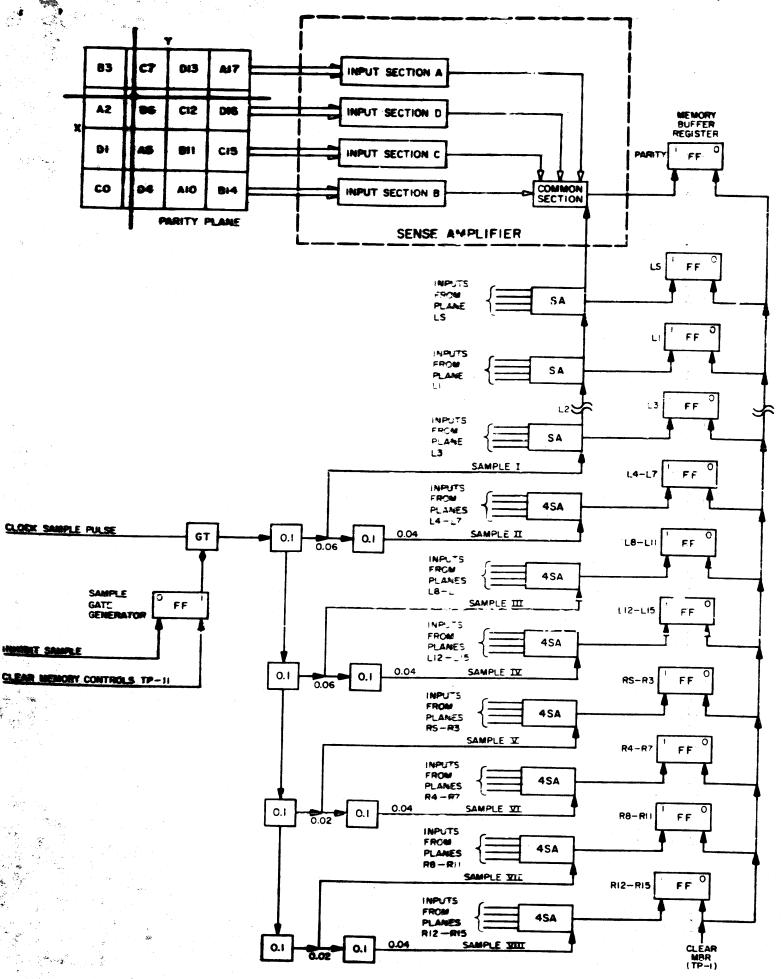

### 5.1 SENSE SECTION AND MEMORY BUFFER REGISTER

The sense section of the 64° core memory consists of 33 amplifiers and 33 gate tubes, one set for each plane of the core memory array. Each individual sense amplifier amplifies the output voltages induced in the sense winding of the associated plane.