# THEORY OF OPERATION

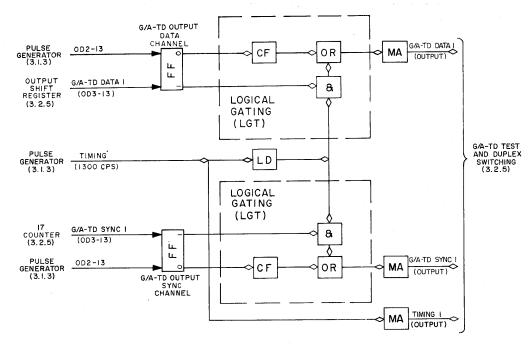

**OF**

# **OUTPUT SYSTEM**

**FOR**

AN/FSQ-7

COMBAT DIRECTION CENTRAL

**AND**

AN/FSQ-8 COMBAT CONTROL CENTRAL

1 December 1958

This document contains information of a proprietary nature. Any use or reproduction of this document for other than government purposes is subject to the prior consent of International Business Machines Corporation.

MILITARY PRODUCTS DIVISION

INTERNATIONAL BUSINESS MACHINES CORPORATION

KINGSTON, NEW YORK

Reproduction for non-military use of the information or illustrations contained in this publication is not permitted without specific approval of the issuing service (BuAer or USAF). The policy for use of classified publications is established for the Air Force in AFR 205-1 and for the Navy in Navy Regulations, Article 1509.

# and for the Navy in Navy Regulations, Article 1509. -LIST OF REVISED PAGES -INSERT LATEST REVISED PAGES. DESTROY SUPERSEDED PAGES. NOTE: The portion of the text affected by the current revision is indicated by a vertical rule in the left margin of a left-hand page and in the right margin of a right-hand page.

\*The asterisk indicates pages revised, added or deleted by the current revision.

#### **CONTENTS**

| Heading |                                                                 | Page |

|---------|-----------------------------------------------------------------|------|

| PART    | 1 INTRODUCTION                                                  | 1    |

| СНАР    | TER 1 GENERAL                                                   | . 1  |

| 1.1     | Function of Output System in AN/FSQ-7 Combat Direction Central  | 1    |

| 1.2     | Function of Output System in AN/FSQ-8 Combat<br>Control Central | 1    |

| 1.3     | Output Control Element                                          | 1    |

| 1.4     | Output Storage Element                                          | 2    |

| СНАР    | TER 2 OUTPUT MESSAGES                                           | 3    |

| 2.1     | General                                                         | 3    |

| 2.2     | Timing of Output Message Transmissions                          | 3    |

| 2.3     | Message Formation                                               | 3    |

| 2.3.1   | General                                                         | 3    |

| 2.3.2   | Left Half-Word                                                  | 4    |

| 2.3.3   | Right Half-Word                                                 | 4    |

| 2.3.4   | Parity Bit                                                      | . 6  |

| СНАР    | TER 3 DRUM STORAGE                                              | 7    |

| 3.1     | General                                                         | 7    |

| 3.2     | OB Fields Writing                                               | 7    |

| 3.3     | OB Fields Reading                                               | 7    |

| 3.4     | LOG Drum OD Timing Pulses                                       | 8    |

| СНАР    | TER 4 OUTPUT SYSTEM, BLOCK DIAGRAM ANALYSIS                     | 9    |

| 4.1     | General                                                         | 9    |

| 4.2     | Output Control Element, Block Analysis                          | 9    |

| 4.3     | Output Storage Element, Block Analysis                          | 11   |

| СНАР    | TER 5 HEART OF STORAGE SYSTEM                                   | 13   |

| 5.1     | Ferrite Core Array                                              | 13   |

| Heading |                                               | Page |

|---------|-----------------------------------------------|------|

| 5.2     | Array Read-In                                 | 14   |

| 5.3     | Array Readout                                 | 17   |

|         |                                               |      |

| PART 2  | OUTPUT CONTROL ELEMENT                        | 19   |

| CHAPTER | 1 INTRODUCTION                                | . 19 |

| 1.1     | General                                       | . 19 |

| 1.2     | Element Diagram Analysis                      | 19   |

| CHAPTER | 2 OUTPUT BUFFER SECTION                       | . 21 |

| 2.1     | Functions and Analysis of Output Drum Section | 21   |

| 2.1.1   | Operations Performed                          | . 21 |

| 2.1.2   | Entrance of Drum Word                         | . 21 |

| 2.1.3   | OD Timing Pulses                              | . 21 |

| 2.1.4   | Flip-Flop Registers                           | . 21 |

| 2.1.5   | Checking Drum Word for Acceptance             | . 22 |

| 2.1.5.1 | Acceptance Requirements                       | . 22 |

| 2.1.5.2 | Acceptance Checks Made in Output Drum Section | . 23 |

| 2.1.6   | Sequence of Operations in Output Drum Section | . 23 |

| 2.1.6.1 | Parity Bit                                    | . 23 |

| 2.1.6.2 | Burst Number                                  | . 24 |

| 2.1.6.3 | Section and Register Address Decoding         | . 24 |

| 2.1.6.4 | Illegal Address Detection                     | . 24 |

| 2.1.6.5 | Slot Detection                                | . 24 |

| 2.1.6.6 | Output Parity Bit                             | . 25 |

| 2.1.7   | Read-In Operation                             | 25   |

| 2.1.8   | Summary                                       | . 25 |

| 2.2     | Drum Word Entry                               | . 26 |

| 2.2.1   | Flip-Flop Register                            | . 26 |

| 2.2.1.1 | Right-Half Drum Word Register                 | . 26 |

| 2.2.1.2 | Burst Number Register                         | . 26 |

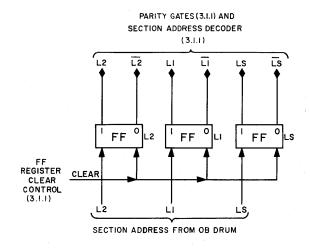

| 2.2.1.3 | Section Address Register                      | . 27 |

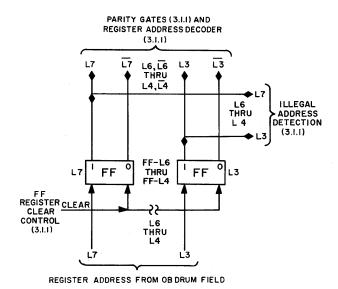

| 2.2.1.4 | Register Address Register                     | 27   |

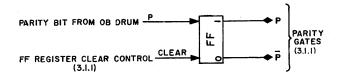

| 2.2.1.5 | Parity Register                               | . 28 |

| Hea | ding    |                                                     | Page |

|-----|---------|-----------------------------------------------------|------|

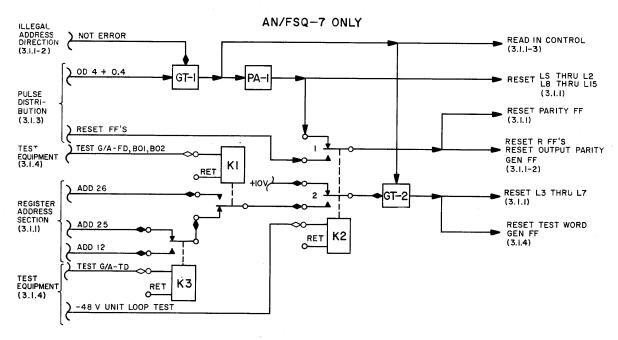

|     | 2.2.2   | Flip-Flop Register Clearing                         | 28   |

|     | 2.3     | Parity Checking                                     | 29   |

|     | 2.3.1   | Type of Parity Check                                | 29   |

|     | 2.3.2   | Drum Word Test Parity Generator                     | 29   |

|     | 2.3.3   | Drum Word Parity Gates                              | 31   |

|     | 2.3.4   | Output Word Parity Generator                        | 32   |

|     | 2.4     | Decoding                                            | 33   |

|     | 2.4.1   | Need for Decoding                                   | 33   |

|     | 2.4.2   | Section Address Decoder                             | 33   |

|     | 2.4.3   | Register Address Decoder                            | 34   |

|     | 2.4.4   | Slot Detection, Circuit Description                 | 34   |

|     | 2.5     | Illegal Address Detection                           | 37   |

|     | 2.5.1   | Introduction                                        | 37   |

|     | 2.5.2   | Illegal Section Address Detection                   | 37   |

|     | 2.5.3   | Illegal Register Address Detection                  | 37   |

|     | 2.6     | Storage Element                                     | 38   |

|     | 2.6.1   | Review of Operations                                | 38   |

|     | 2.6.2   | Read-In Control                                     | 40   |

|     | 2.6.3   | No-Compare Pulse Generator                          | 44   |

|     | 2.6.4   | Set Drivers                                         | 45   |

|     | 2.6.5   | Half-Write Current Generator                        | 46   |

|     | 2.6.5.1 | Flip-Flops and Reset-Inhibit Drivers                | 46   |

|     | 2.6.5.2 | Core Current Drivers                                | 47   |

|     | 2.6.5.3 | Timing Cycle                                        | 48   |

| _   | LADTED  | 2 CUITRUT COMPUTER SECTION                          |      |

|     |         | 3 OUTPUT COMPUTER SECTION                           | 51   |

|     | 3.1     | General Burnt Court Salassian and Transfer          | 51   |

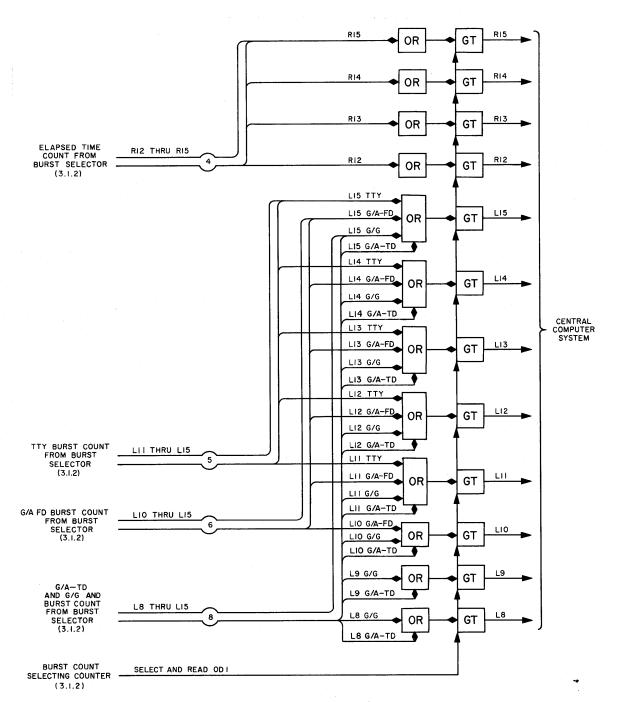

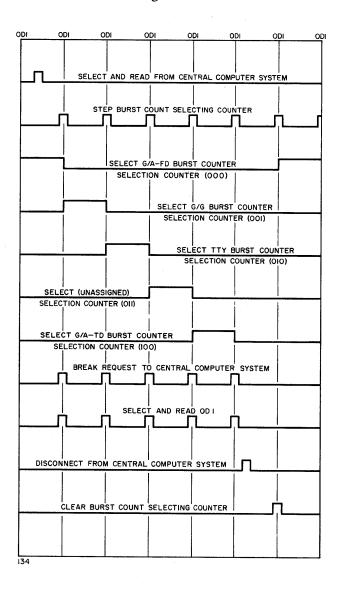

|     | 3.2     | Burst-Count Selection and Transfer                  | 51   |

|     | 3.2.1   | General                                             | 51   |

|     | 3.2.2   | Burst-Count Selecting Counter                       | 51   |

|     | 3.2.3   | Selecting Counter Decoder                           | 52   |

|     | 3.2.4   | Burst-Time Count Switch                             | 53   |

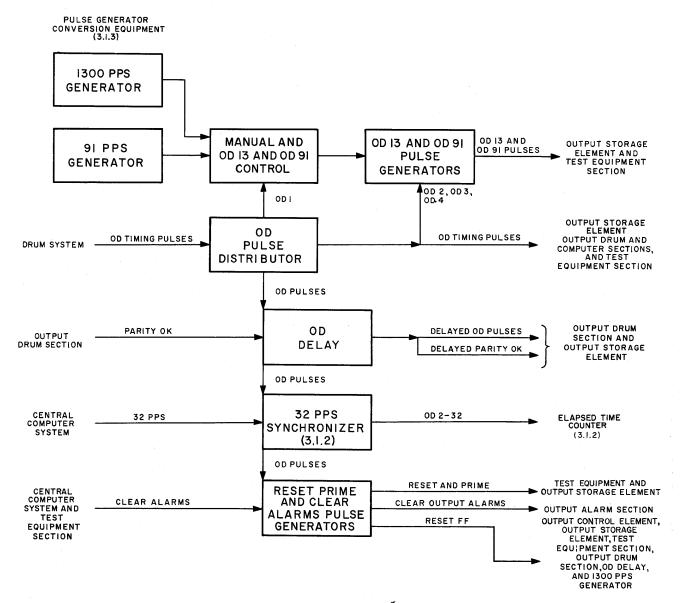

|     | 3.3     | Pulse Generator and Pulse Generator Conversion Unit | 56   |

|     | 3.3.1   | General                                             | 56   |

| Heading |                                                                                | Page       |

|---------|--------------------------------------------------------------------------------|------------|

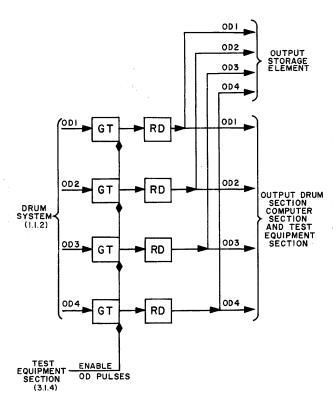

| 3.3.2   | OD Pulse Distributor                                                           | <b>5</b> 7 |

| 3.3.3   | 91-PPS Generator                                                               | 57         |

| 3.3.4   | OD 91 Pulse Control Circuit                                                    | 58         |

| 3.3.5   | OD 91 Pulse Generator                                                          | 58         |

| 3.3.6   | 1,300-PPS Generator                                                            | 59         |

| 3.3.7   | OD 13 Pulse Control Circuit                                                    | 59         |

| 3.3.8   | OD 13 Pulse Generator                                                          | 60         |

| 3.3.9   | OD Delay                                                                       | 61         |

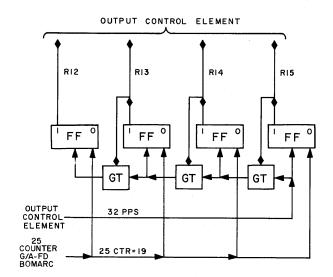

| 3.3.10  | 32-PPS Synchronizer                                                            | 61         |

| 3.3.11  | Reset Flip-Flop, Reset and Prime, and Clear-Alarms Pulse Generators            | 61         |

| 3.3.12  | Reset Drum Status Bit Generator                                                | 61         |

| CHAPT   | ER 4 OUTPUT ALARM SECTION                                                      | . 65       |

| 4.1     | Introduction                                                                   | . 65       |

| 4.2     | Alarm Control                                                                  | . 67       |

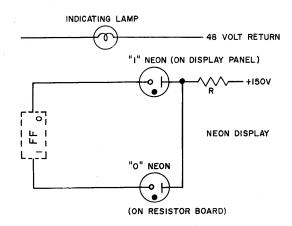

| 4.3     | Alarm Display                                                                  | . 67       |

| PART 3  | OUTPUT STORAGE ELEMENT                                                         | . 69       |

| CHAPT   | ER 1 INTRODUCTION                                                              | . 69       |

| 1.1     | General                                                                        | . 69       |

| 1.2     | Bursts                                                                         | 69         |

| 1.3     | Burst Period                                                                   | . 70       |

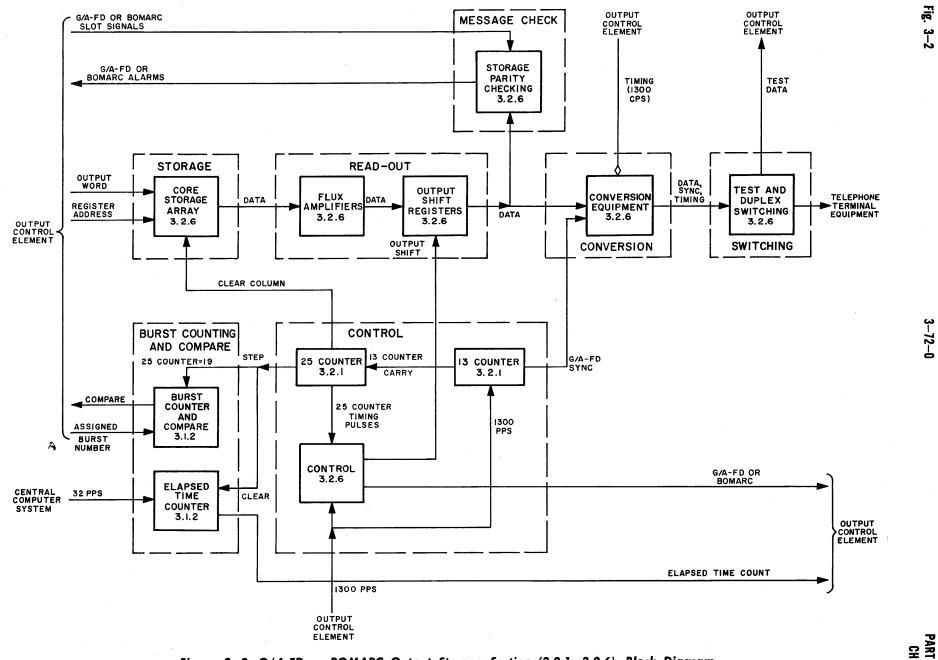

| СНАРТ   | ER 2 GROUND-TO-AIR FREQUENCY DIVISION, BOMARC 1, AND BOMARC 2 STORAGE SECTIONS | 71         |

| 2.1     | General                                                                        | 71         |

| 2.2     | Operation (G/A-FD, BOMARC)                                                     | 71         |

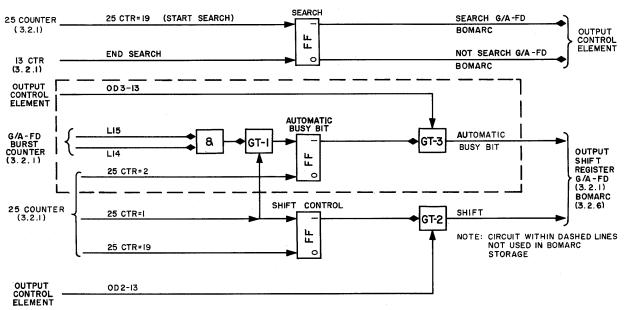

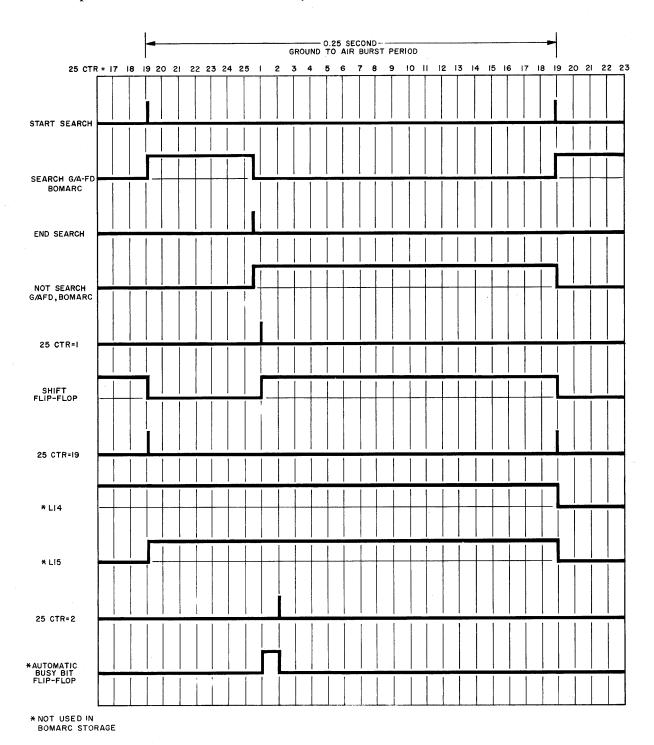

| 2.2.1   | Counter Operation                                                              | 71         |

| 2.2.2   | Search Time                                                                    | 71         |

| 2.2.3   | Readout Time                                                                   | 73         |

| 2.3     | Storage (G/A-FD, BOMARC)                                                       | 73         |

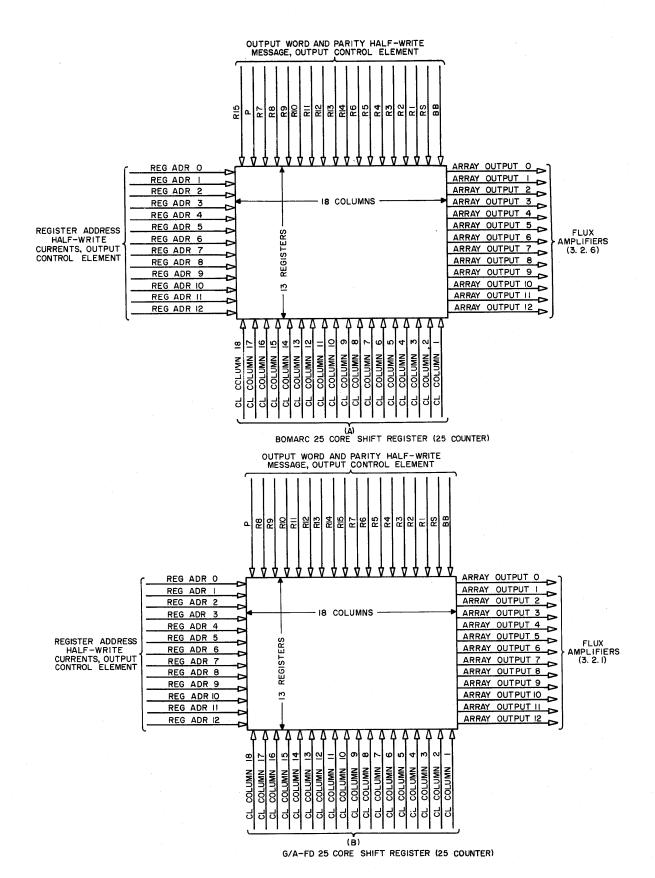

| 2.3.1   | Core Storage Array                                                             | 73         |

| Heading |                                            | Pag  |

|---------|--------------------------------------------|------|

| 2.3.2   | Core Array Read-In                         | . 75 |

| 2.4     | Control (G/A-FD, BOMARC)                   | . 76 |

| 2.4.1   | Timing                                     | . 76 |

| 2.4.2   | 13 Counter                                 | . 76 |

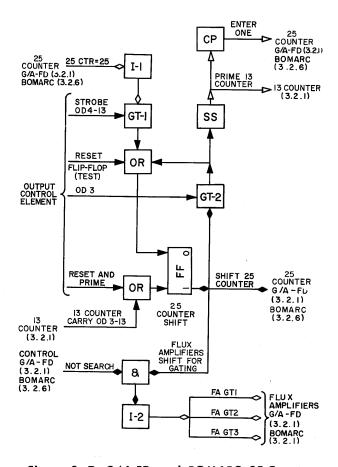

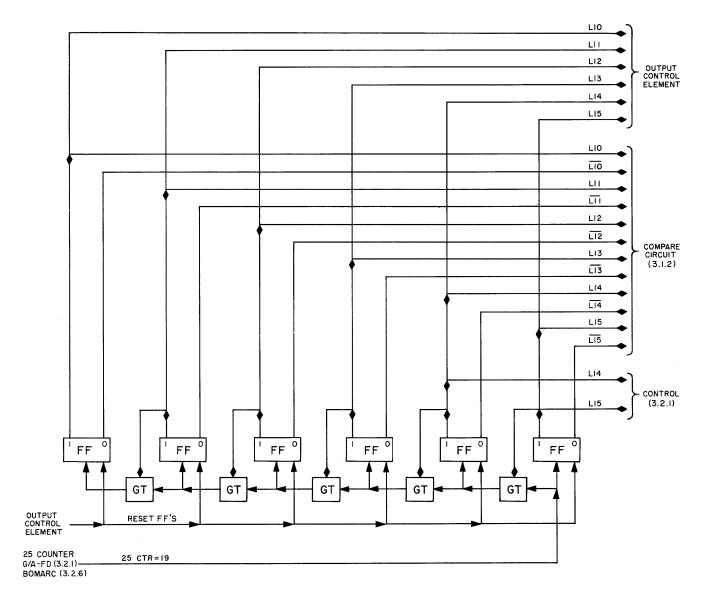

| 2.4.3   | 25 Counter                                 | . 79 |

| 2.4.4   | Control                                    | . 83 |

| 2.5     | Readout (G/A-FD, BOMARC)                   | . 85 |

| 2.5.1   | General                                    | . 85 |

| 2.5.2   | Core Array Readout                         | . 85 |

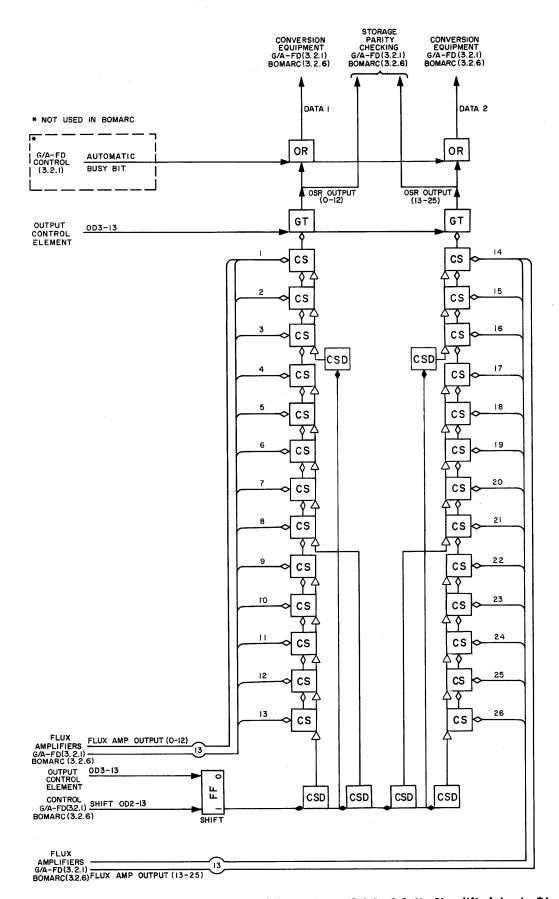

| 2.5.3   | Output Shift Register (OSR)                | 87   |

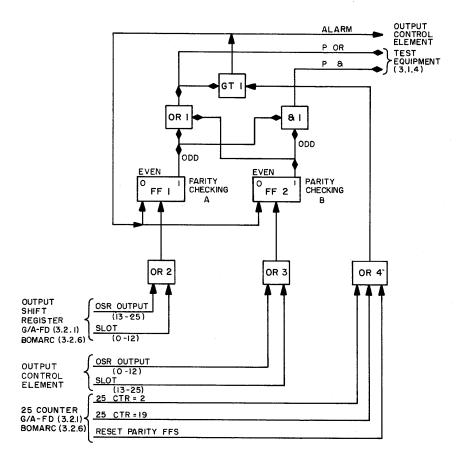

| 2.6     | Message Check (G/A-FD, BOMARC)             | 87   |

| 2.6.1   | Purpose                                    | 87   |

| 2.6.2   | Busy Bit Check                             | 87   |

| 2.6.3   | Output Message Parity                      | 89   |

| 2.7     | Burst Sequence and Timing (G/A-FD, BOMARC) | 90   |

| 2.7.1   | General                                    | 90   |

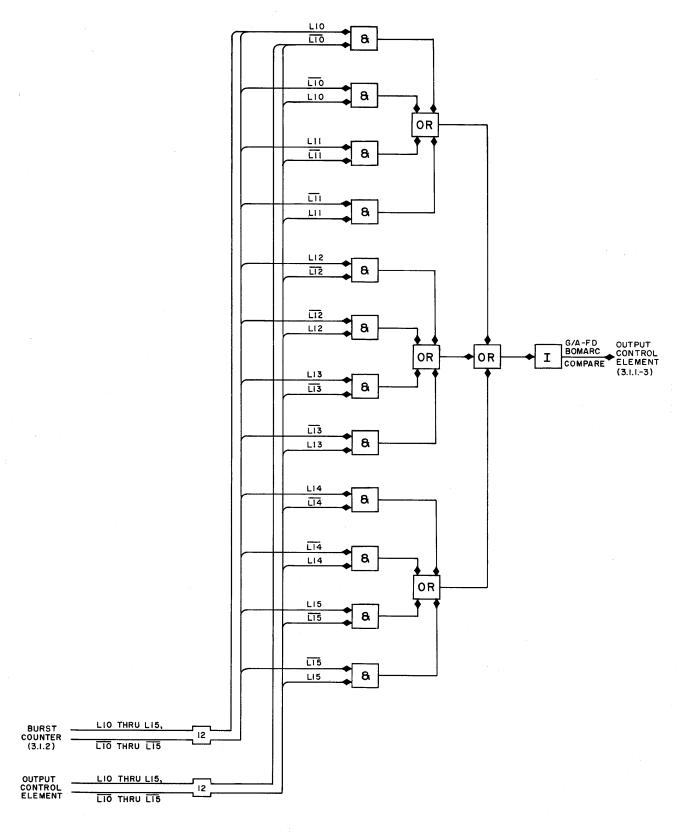

| 2.7.2   | Burst Counter and Compare Circuit          | 90   |

| 2.7.3   | Elapsed-Time Counter (G/A-FD Only)         | 91   |

| 2.8     | Conversion (G/A-FD, BOMARC)                | 93   |

| 2.8.1   | General                                    | 93   |

| 2.8.2   | Conversion Equipment                       | 93   |

| 2.8.2.1 | General                                    | 93   |

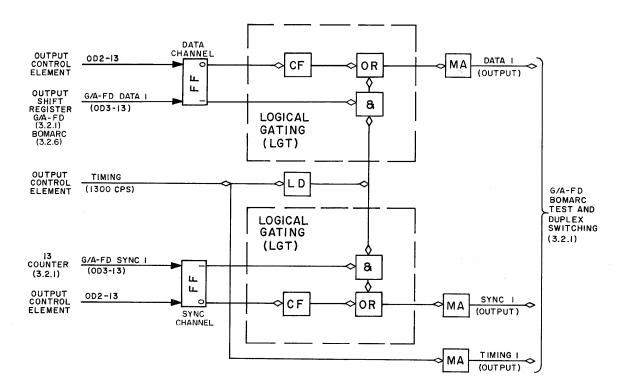

| 2.8.2.2 | Data Conversion Channel                    | 93   |

| 2.8.2.3 | Sync Conversion Channel                    | 95   |

| 2.9     | Switching (G/A-FD, BOMARC)                 | 96   |

| CHAPTER | 3 GROUND-TO-GROUND STORAGE SECTION         | 97   |

| 3.1     | General                                    | 97   |

| 3.2     | System Operation                           | 97   |

| 3.2.1   | Counter Operation                          | 97   |

| 3.2.2   | Read-In                                    | 97   |

| 3.2.3   | Readout                                    | 99   |

| 3.3     | Storage                                    | 99   |

| 3.3.1   | Core Storage Arrays                        | 00   |

| Heading | ?            | I                                             | Page  |

|---------|--------------|-----------------------------------------------|-------|

| 3.3     | 3.2          | Core Array Read-In                            | 99    |

| 3.4     | í            | Control                                       | 100   |

| 3.4     | <b>í</b> .1  | General                                       | 100   |

| 3.4     | 4.2          | 5 Counter                                     | 100   |

| 3.4     | 4.3          | 19 Counter                                    | 101   |

| 3.4     | 4.4          | G/G Control                                   | 103   |

| 3.      | 5            | G/G Readout                                   | 105   |

| 3.      | 5.1          | General                                       | 105   |

| 3.      | 5.2          | Core Array Readout                            | 106   |

| 3.      | 5.3          | Output Shift Register (OSR)                   | 106   |

| 3.      | 5.4          | Completed Message Shift Register              |       |

| 3.      | 6            | Message Check                                 | 107   |

| 3.      | 7            | Burst Sequence and Timing                     | 108   |

| 3.      | 7.1          | Purpose                                       | 108   |

| 3.      | 7.2          | Burst Counter                                 | 108   |

| 3.      | 7.3          | Burst Number Comparison                       | 108   |

| 3.      | 8            | Conversion                                    | 109   |

| 3.      | .9           | Switching                                     | 111   |

| CH      | APTER        | 4 GROUND-TO-AIR TIME DIVISION STORAGE SECTION | 113   |

| 4.      | .1           | General                                       | 113   |

| 4       | .2           | System Operation                              | 113   |

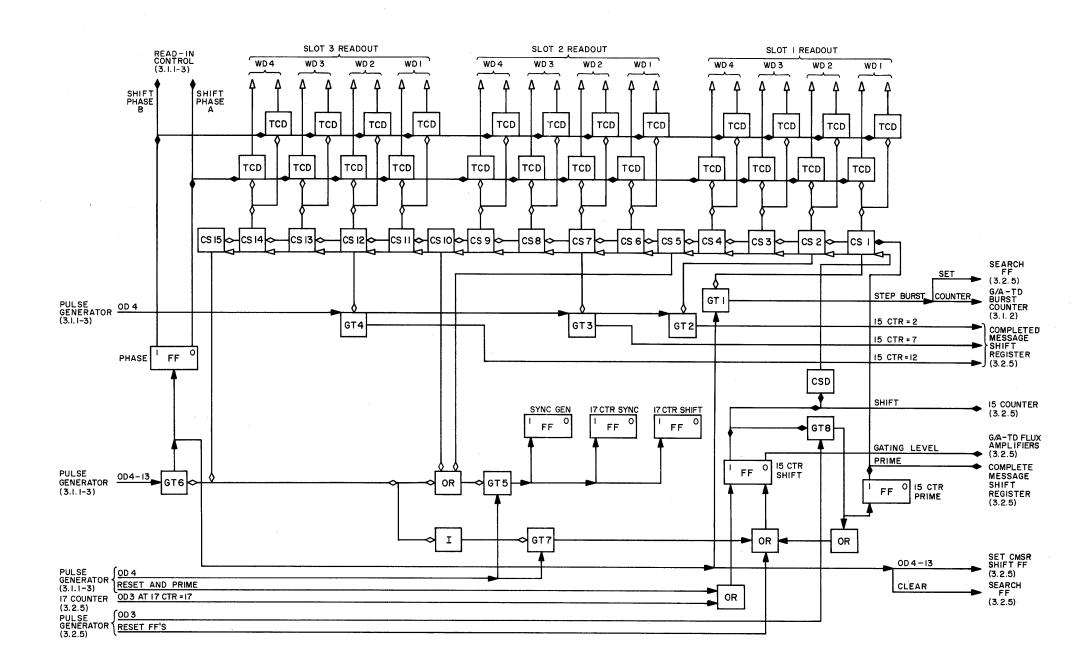

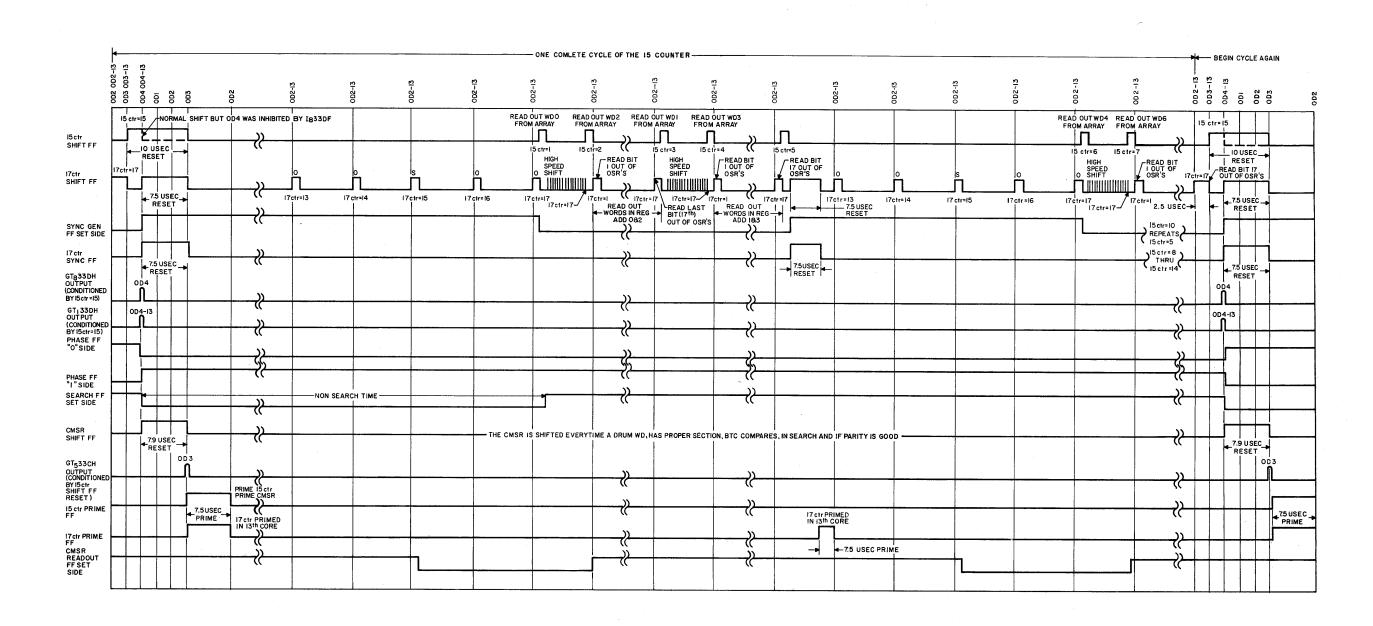

| 4       | .2.1         | Counter Operation                             | 113   |

| 4       | .2.2         | Read-In                                       | 113   |

| 4       | .2.3         | Readout                                       | 115   |

| 4       | .3           | Storage                                       | 115   |

| 4       | .3.1         | Core Storage Arrays                           | 115   |

| 4       | .3.2         | Core Array Read-In                            | 116   |

| 4       | .4           | Control                                       | 116   |

| 4       | .4.1         | General                                       | 116   |

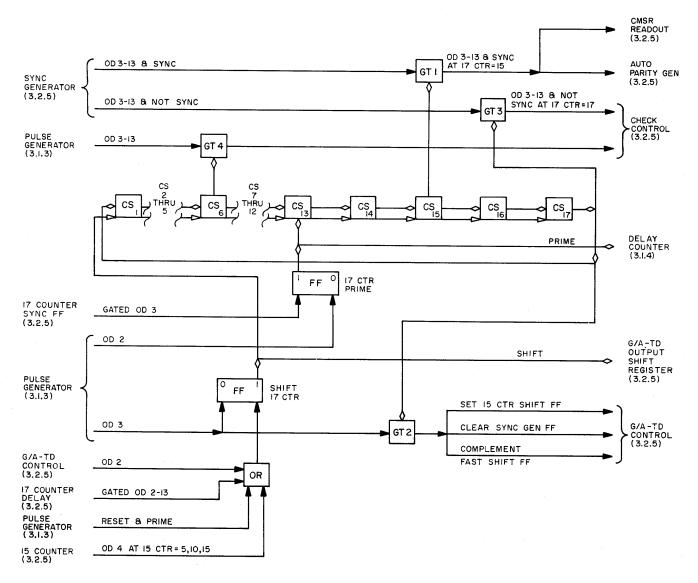

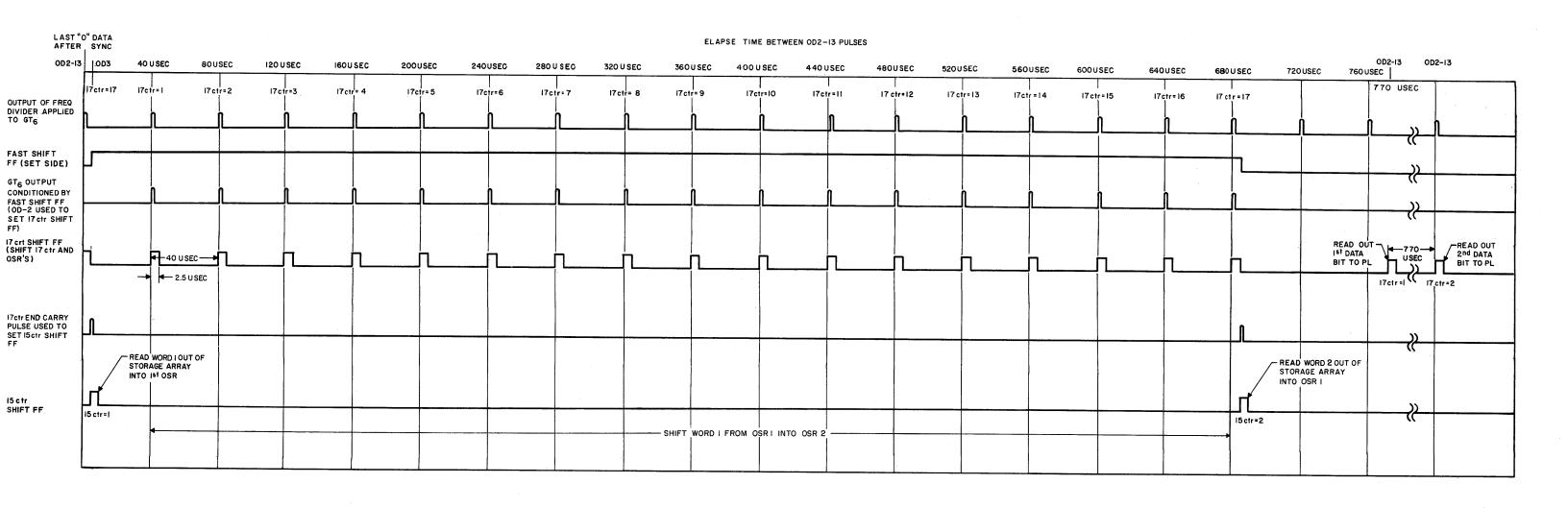

| 4       | 4.4.2        | 17 Counter                                    | 116   |

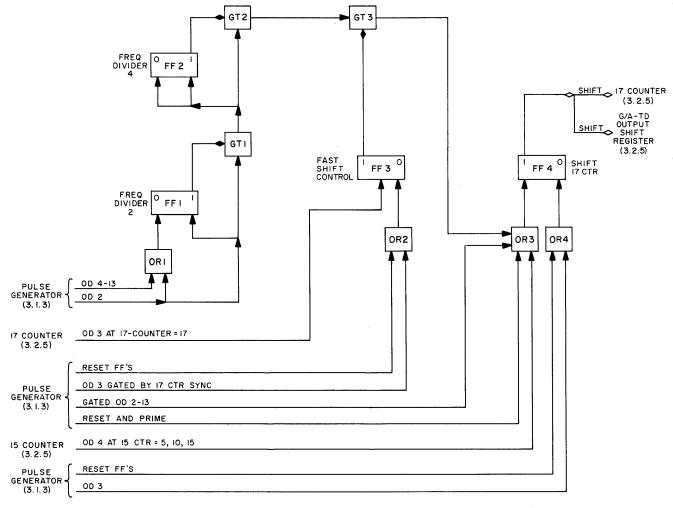

| 4       | <b>i.4.3</b> | Frequency Divider                             | . 117 |

|         | <b>1.4.4</b> | Fast-Shift Control                            |       |

| He | ading   |                                         | Page |

|----|---------|-----------------------------------------|------|

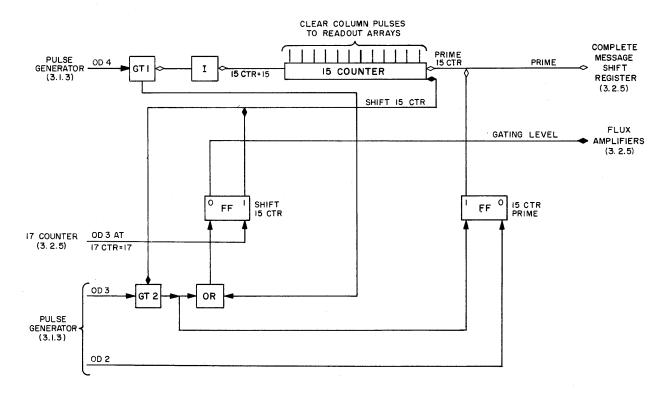

|    | 4.4.5   | 15 Counter                              | 117  |

|    | 4.4.6   | Associated Control Circuits             | 119  |

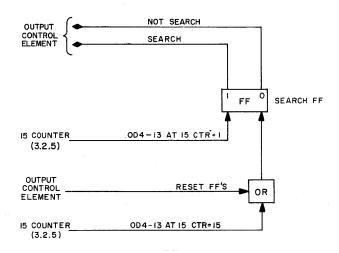

|    | 4.4.6.1 | G/A-TD Search and Not-Search            | 119  |

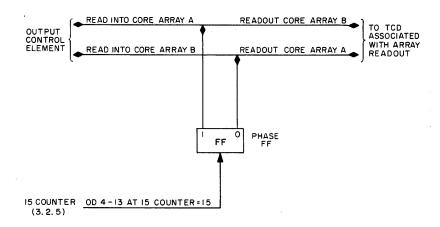

|    | 4.4.6.2 | Array Selection                         | 119  |

|    | 4.4.6.3 | 15-Counter Shift Control                | 119  |

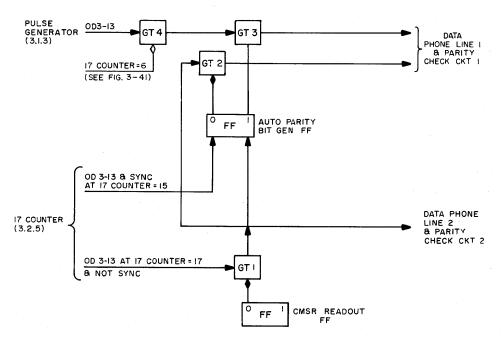

|    | 4.4.6.4 | Automatic Parity Bit Generation         | 121  |

|    | 4.4.6.5 | Associated Control Circuits, 17 Counter | 122  |

|    | 4.5     | Readout                                 | 123  |

|    | 4.5.1   | General                                 | 123  |

|    | 4.5.2   | Core Array Readout                      | 123  |

|    | 4.5.3   | Output Shift Registers (OSR's)          | 124  |

|    | 4.5.4   | Completed Message Shift Register        | 125  |

|    | 4.6     | Parity Check                            | 127  |

|    | 4.7     | Burst Sequence and Timing               | 127  |

|    | 4.7.1   | General                                 | 127  |

|    | 4.7.2   | Burst Counter                           | 128  |

|    | 4.7.3   | Burst Number Comparison                 | 128  |

|    | 4.8     | Conversion                              | 129  |

|    | 4.8.1   | General                                 | 129  |

|    | 4.8.2   | Conversion Equipment                    | 131  |

|    | 4.8.2.1 | General                                 | 131  |

|    | 4.8.2.2 | Data Conversion Channel                 | 131  |

|    | 4.8.2.3 | Sync Conversion Channel                 | 132  |

|    | 4.9     | Switching                               | 132  |

|    | CHAPTE  | R 5 TELETYPE STORAGE SECTION            | 135  |

|    | 5.1     | General                                 | 135  |

|    | 5.2     | Operation                               | 136  |

|    | 5.2.1   | Counter Operation                       | 136  |

|    | 5.2.2   | Search Time                             | 136  |

|    | 5.2.3   | Readout Time                            | 136  |

|    | 5.3     | Storage                                 | 139  |

|    | 5.3.1   | General                                 | 139  |

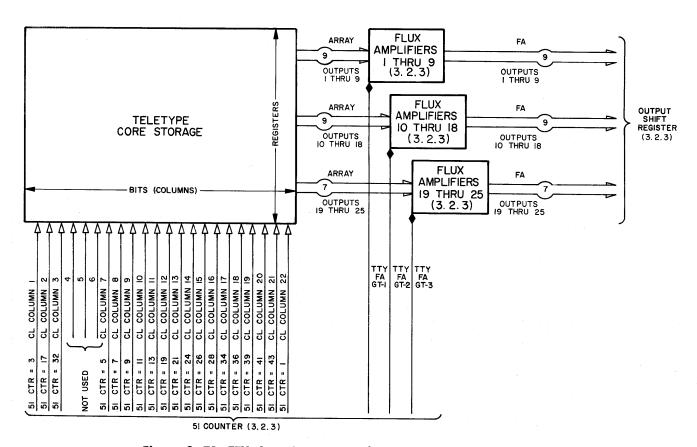

|    | 5.3.2   | Core Storage Array                      | 130  |

| Head | ing    |                                                                   | Page |

|------|--------|-------------------------------------------------------------------|------|

|      | 5.3.3  | Core Array Read-In                                                | 139  |

|      | 5.4    | Control                                                           | 139  |

|      | 5.4.1  | General                                                           | 139  |

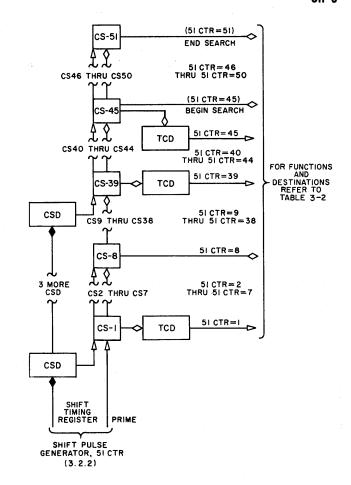

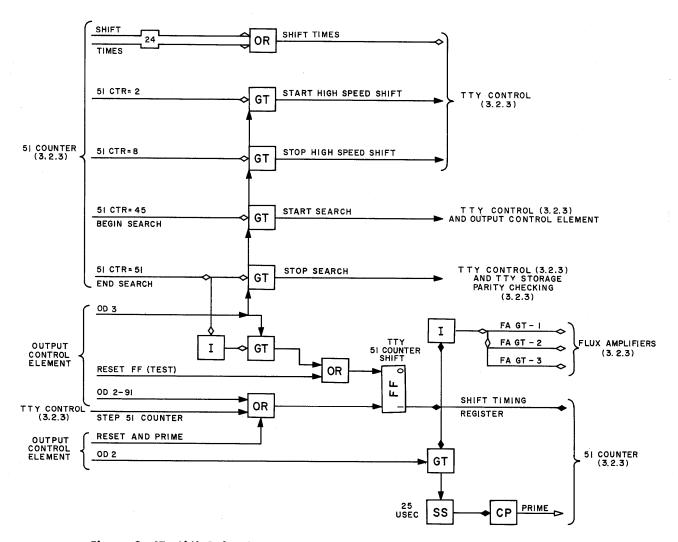

|      | 5.4.2  | 51 Counter                                                        | 139  |

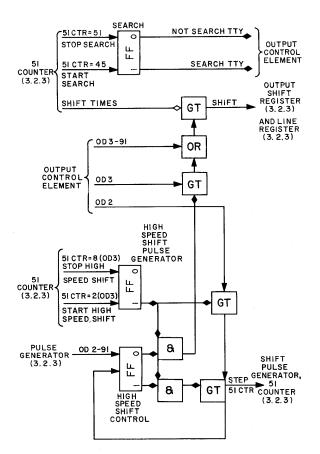

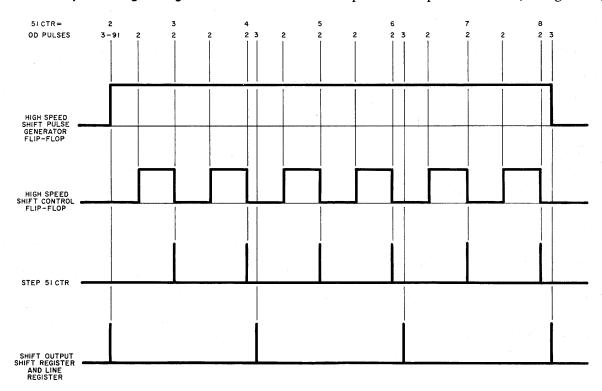

|      | 5.4.3  | Teletype Control                                                  | 143  |

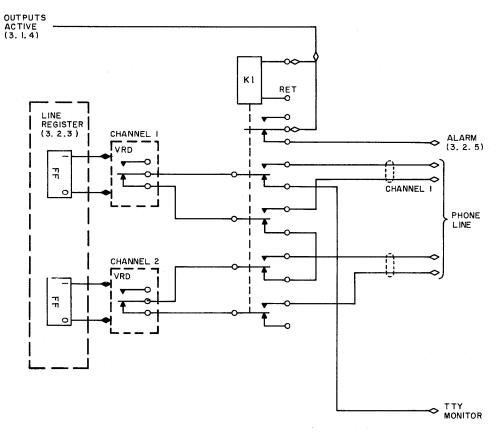

|      | 5.5    | Teletype Readout                                                  | 144  |

|      | 5.5.1  | General                                                           | 144  |

|      | 5.5.2  | Core Array Readout                                                | 144  |

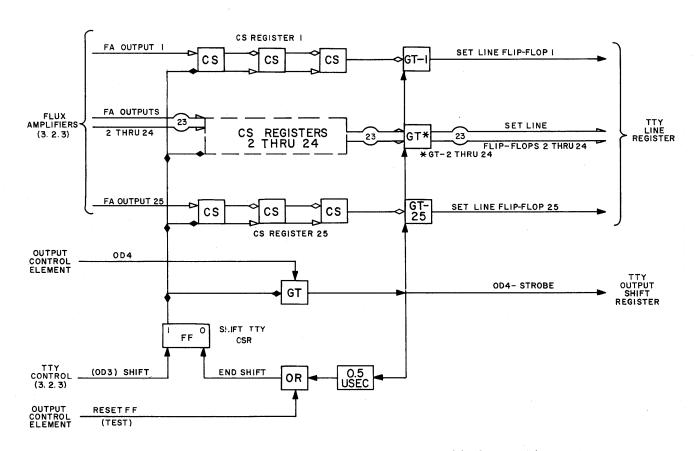

|      | 5.5.3  | Flux Amplifiers (FA's)                                            | 144  |

|      | 5.5.4  | Output Shift Register                                             | 146  |

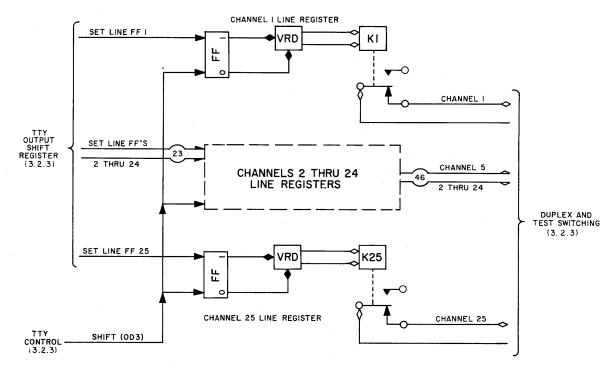

|      | 5.5.5  | Line Register                                                     | 147  |

|      | 5.6    | Message Check                                                     | 147  |

|      | 5.7    | Burst Sequence and Timing                                         | 149  |

|      | 5.8    | Switching                                                         | 149  |

|      |        | TEST EQUIPMENT SECTION                                            |      |

|      | 1.1    | General                                                           | 153  |

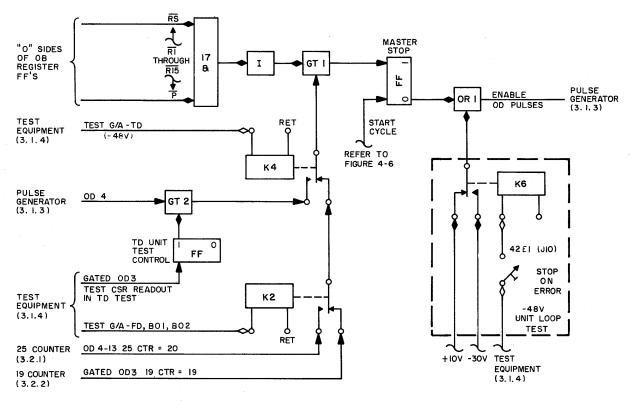

|      | 1.2    | Unit Loop Control, Error Detection                                | 154  |

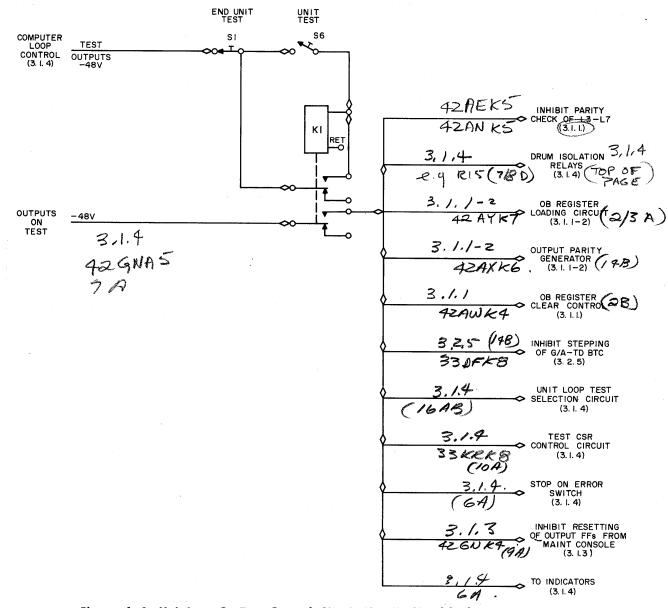

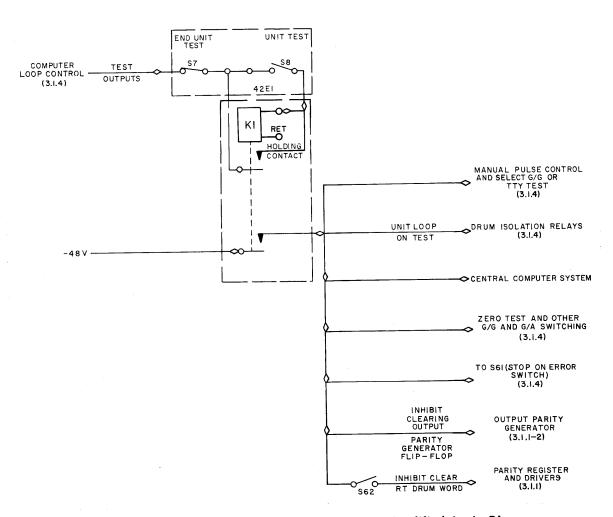

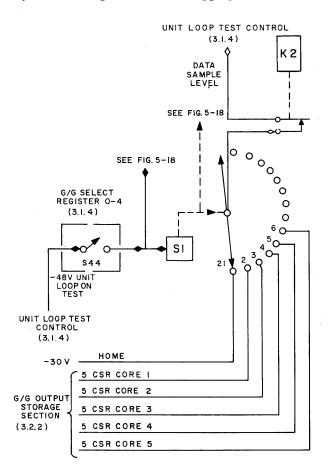

|      | 1.2.1  | Unit Loop Test Switching                                          | 154  |

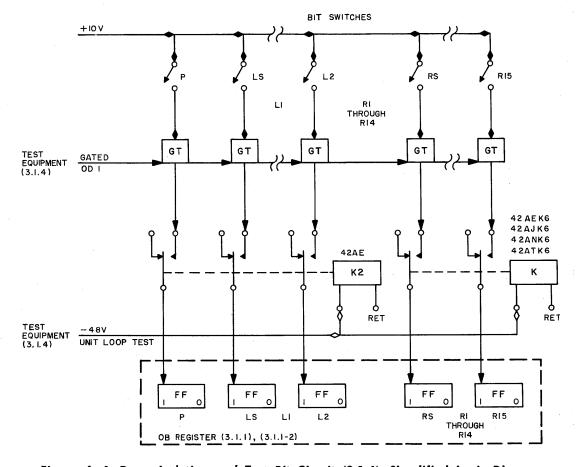

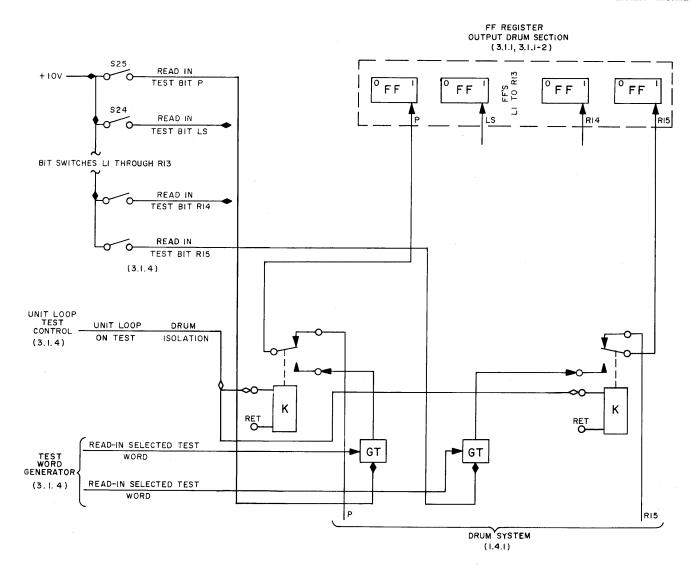

|      | 1.2.2  | Drum Isolation and Test, Bit Circuits                             | 154  |

|      | 1.2.3  | Inhibit Resetting of Right Drum Word                              | 155  |

|      | 1.2.4  | Clearing Alarms and Resetting Flip-Flops                          | 156  |

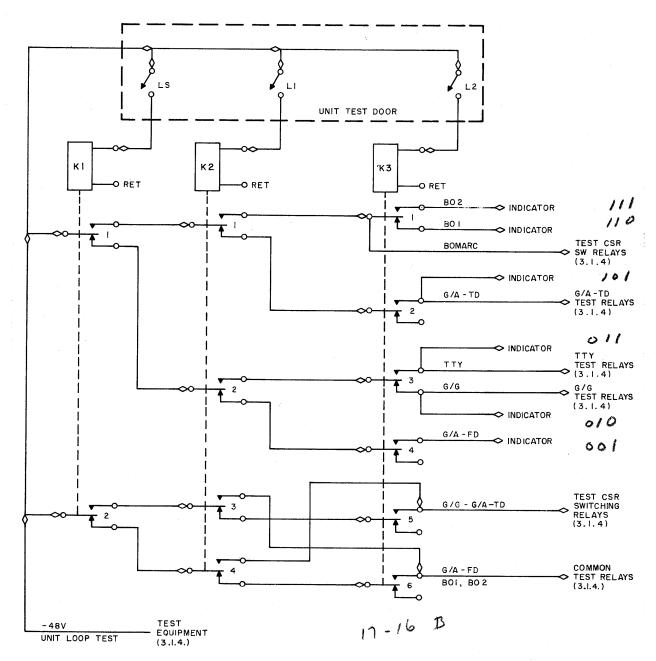

|      | 1.2.5  | Unit Loop Test Selection Circuit                                  | 156  |

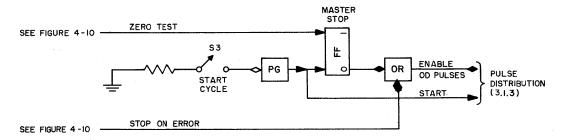

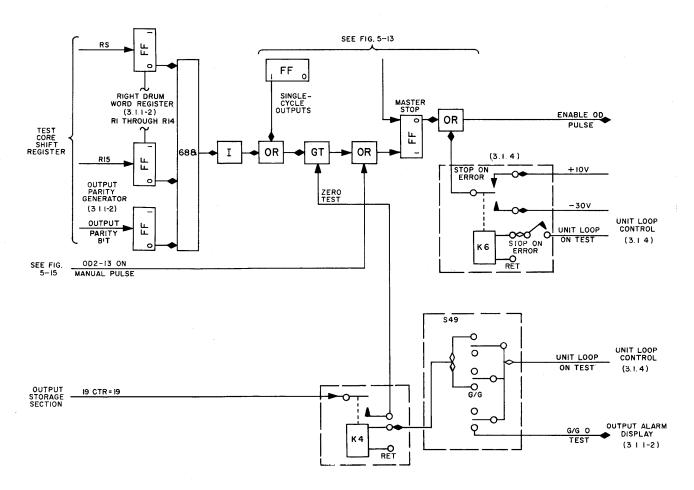

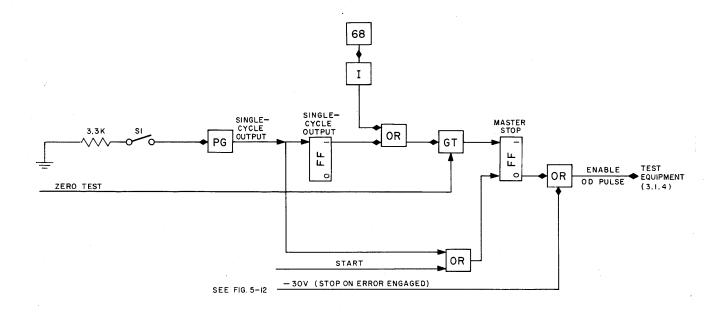

|      | 1.2.6  | Test Start Control                                                | 157  |

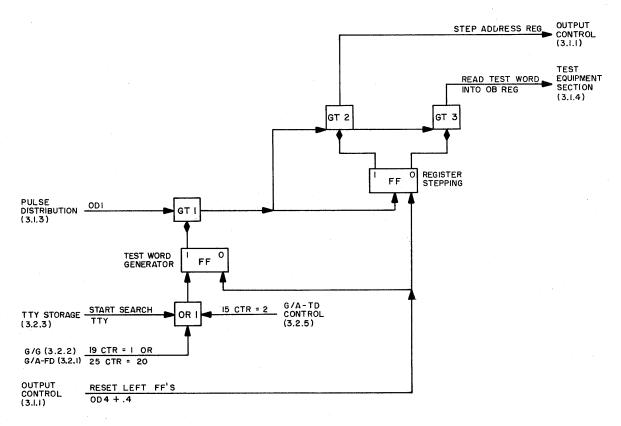

|      | 1.2.7  | Test Word Read-In                                                 | 158  |

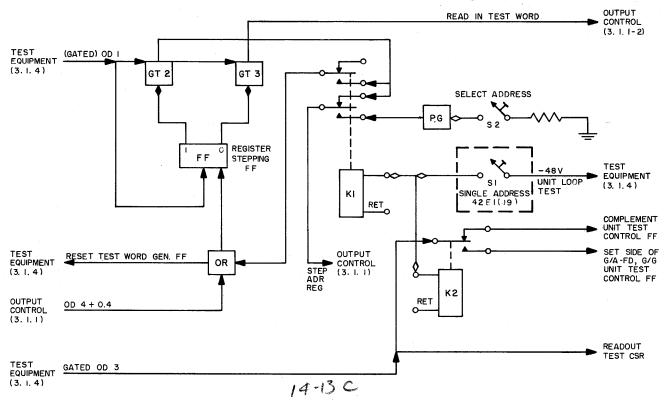

|      | 1.2.8  | Single-Address Stepping                                           | 159  |

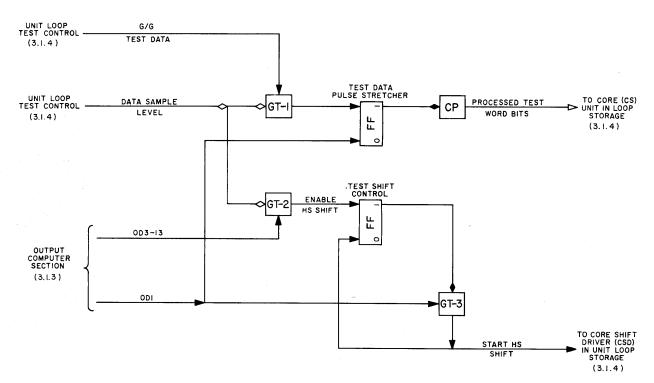

|      | 1.2.9  | Transfer of Word from Output Storage Section to Test Circuits CSR | 159  |

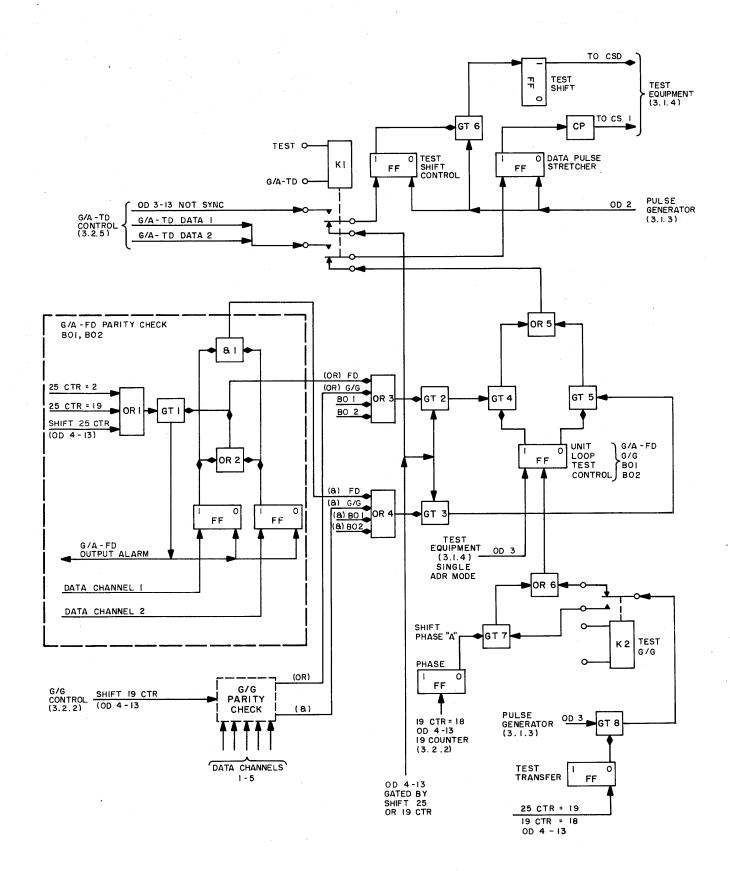

|      | 1.2.10 | Data Bit Generator Check (G/A-FD, BO1, and BO2)                   | 160  |

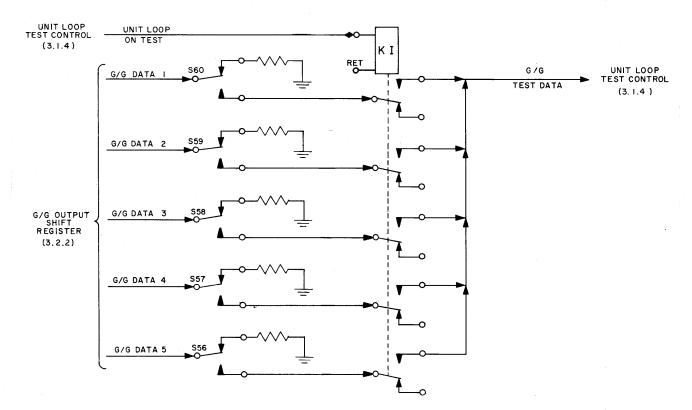

|      | 1.2.11 | Data Bit Generator Error Check (G/G)                              | 162  |

|      | 1.2.12 | G/A-TD Test Word Transfer                                         | 163  |

|      | 1 2 13 | Error-Detection AND Circuit                                       | 163  |

| Heading |                                                     | Pag |

|---------|-----------------------------------------------------|-----|

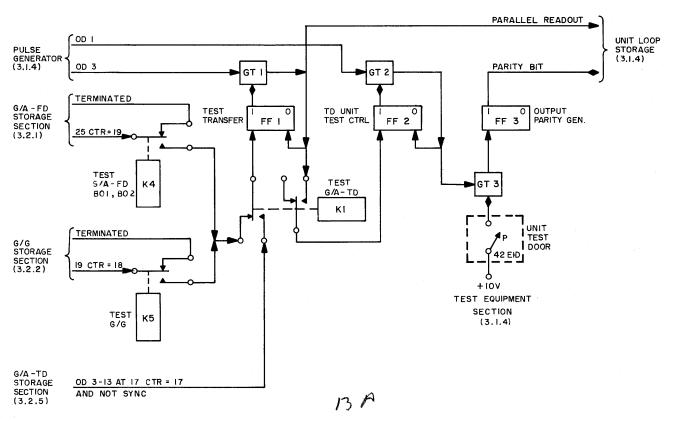

| 1.3     | Unit Loop Storage                                   | 164 |

| 1.3.1   | Parallel Readout Control                            | 164 |

| 1.3.2   | Core Register Circuit                               | 166 |

| 1.4     | Specific Unit Loop Tests                            | 166 |

| 1.4.1   | Ground-to-Air Frequency Division and BOMARC 1-2     | 166 |

| 1.4.2   | Ground-to-Ground                                    | 167 |

| 1.4.3   | Ground-to-Air Time Division                         | 168 |

| 1.4.4   | Teletype Monitor Test                               | 168 |

| CHAPTI  | ER 2 COMPUTER LOOP TEST                             | 171 |

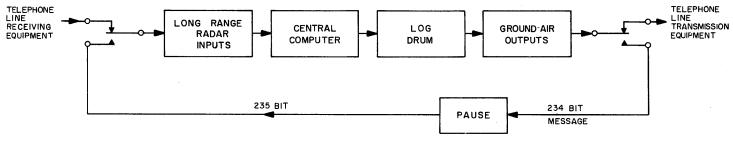

| 2.1     | General                                             | 171 |

| 2.1.1   | Ground-to-Ground to XTL Loop                        | 171 |

| 2.1.2   | G/A-FD, BOMARC, and G/A-TD to LRI Loop              | 171 |

| 2.1.3   | TTY Monitor Test                                    | 171 |

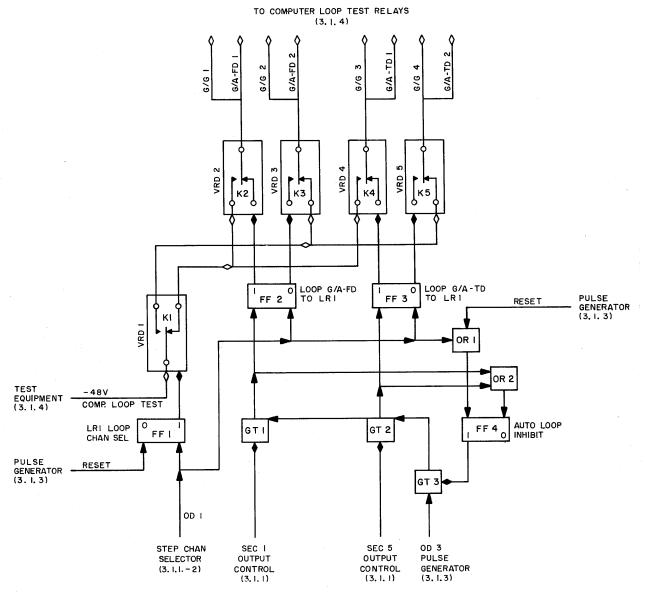

| 2.2     | Computer Loop Control                               | 173 |

| 2.2.1   | G/A-FD, BOMARC, and G/A-TD to LRI Channel Selection | 173 |

| 2.2.2   | G/G to XTL Channel Selection                        | 174 |

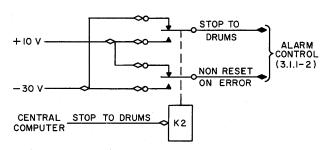

| 2.2.3   | Stop to Drums                                       | 174 |

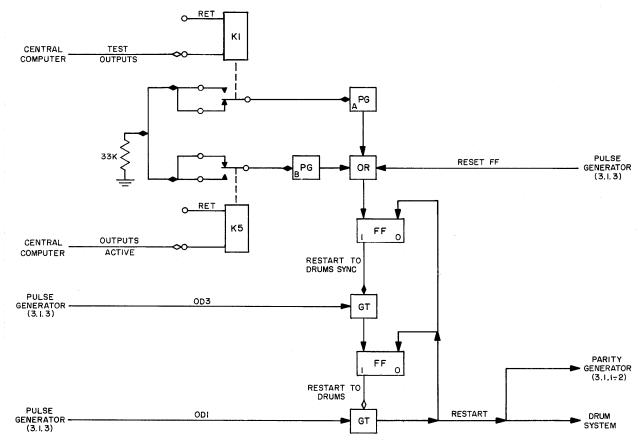

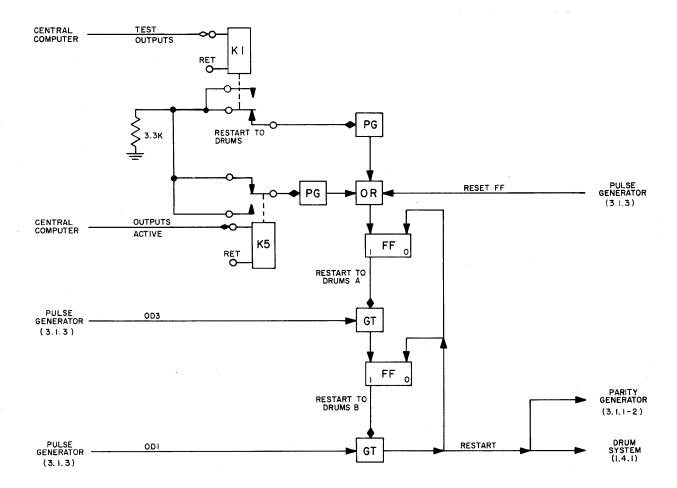

| 2.2.4   | Restart-to-Drums Circuit                            | 175 |

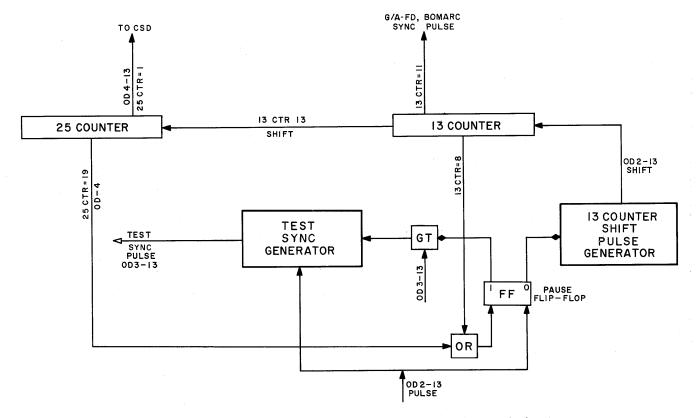

| 2.2.5   | Pause-and-Sync-Control Circuit                      | 175 |

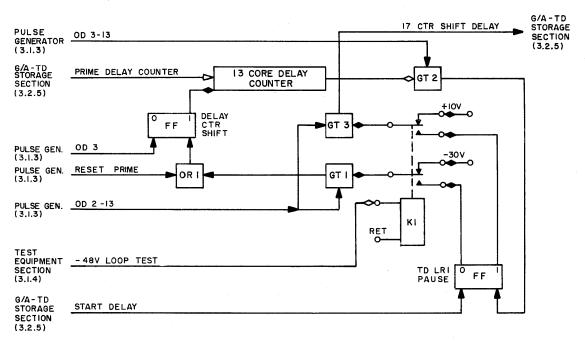

| 2.2.6   | 13-Core Delay Counter                               | 176 |

| PART 5  | AN/FSQ-8 COMBAT CONTROL CENTRAL                     | 179 |

| CHAPTI  | ER 1 INTRODUCTION                                   | 179 |

| 1.1     | General                                             | 179 |

| 1.2     | Output System in AN/FSQ-8 Combat Control Central    | 179 |

| СНАРТІ  | ER 2 DIFFERENCE DATA                                | 181 |

| 2.1     | Description                                         | 181 |

| 2.2     | Circuit Differences, Output Control Element         | 181 |

| 2.2.1   | Flip-Flop Register Clearing                         | 181 |

| 2.2.2   | Output-Word Parity Generator                        | 182 |

| Headin | g       | ·                                                                | Page |

|--------|---------|------------------------------------------------------------------|------|

| 2.     | 3       | Circuit Differences, Output Storage Element                      | 182  |

| 2.     | 4       | Circuit Differences, Test Equipment Section                      | 182  |

| 2.     | .5      | Introduction, Test Equipment Section                             | 182  |

| 2.     | .6      | Unit Loop Test                                                   | 183  |

| 2.     | 6.1     | General                                                          | 183  |

| 2.     | 6.2     | Unit Loop Control, Error Detection                               | 184  |

| 2.     |         | Unit Loop Test Switching                                         |      |

| 2.     |         | Drum Isolation and Test-Bit Circuits                             |      |

| 2.     | .6.2.3  | Inhibit Resetting of Right Drum Word                             | 186  |

| 2.     | .6.2.4  | Clearing Alarms and Resetting Flip-Flops                         | 186  |

| 2.     | .6.2.5  | Test Start Control                                               | 186  |

| 2.     | .6.2.6  | Transfer of Word from Output Storage Section to Test Circuit CSR | 187  |

| 2.     | .6.2.7  | Data-Sample Level Generator                                      | 187  |

| 2.     | .6.2.8  | Test-Data Pulse Generator                                        | 188  |

| 2.     | .6.2.9  | Error-Detection AND Circuit                                      | 188  |

| 2.     | .6.2.10 | Optional Operation Control Circuits                              | 189  |

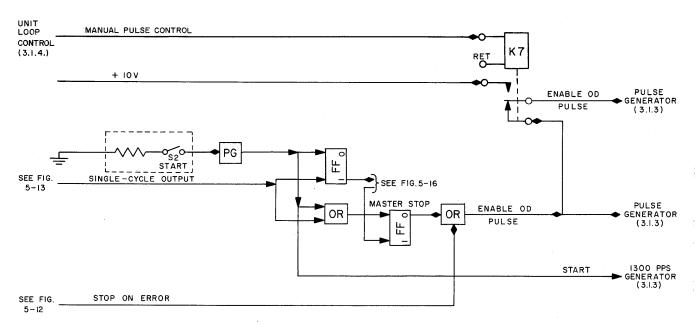

| 2.     | .6.2.11 | Single-Cycle Mode                                                | 189  |

| 2.     | .6.2.12 | Manual-Pulse Mode                                                | 191  |

| 2      | .6.3    | Unit Loop Control, Test-Word Generator                           | 191  |

| 2.     | .6.4    | Unit Loop Storage                                                | 192  |

| 2      | .6.4.1  | Parallel Readout Control                                         | 192  |

| 2      | .6.4.2  | Core Register Circuit                                            | 192  |

| 2      | .6.5    | Specific Unit Loop Tests                                         | 193  |

| 2      | .6.5.1  | Ground-to-Ground                                                 | 195  |

| 2      | .6.5.2  | Teletype Monitor Test                                            | 195  |

| 2      | .7      | Computer Loop Test                                               | 196  |

| 2      | .7.1    | General                                                          | 196  |

| 2      | .7.2    | Ground-to-Ground to XTL Input Loop                               | 196  |

| 2      | .7.3    | Teletype Monitor Test                                            | 197  |

| 2      | .8      | Computer Loop Control                                            | 197  |

| 2      | .8.1    | General                                                          | 197  |

| 2      | .8.2    | Stop to Drums                                                    | 197  |

| 2      | .8.3    | Restart to Drum Circuit                                          | 198  |

| IN     | DEX     |                                                                  | 209  |

#### LIST OF ILLUSTRATIONS

| Figure | Title                                                                               | Page |

|--------|-------------------------------------------------------------------------------------|------|

| 1-1    | Remote Sites, Block Diagram                                                         | . 1  |

| 1-2    | Output Message Flow, Block Diagram                                                  | . 1  |

| 1-3    | Output System, Block Diagram                                                        | . 2  |

| 1-4    | 33-Bit Word                                                                         | . 3  |

| 1-5    | Left Half-Word                                                                      | . 4  |

| 1–6    | Teletype Right Half-Word                                                            | . 6  |

| 1—7    | OD Cycle, Timing Chart                                                              | . 8  |

| 1-8    | Output System (3.0), Simplified System Diagram                                      | . 9  |

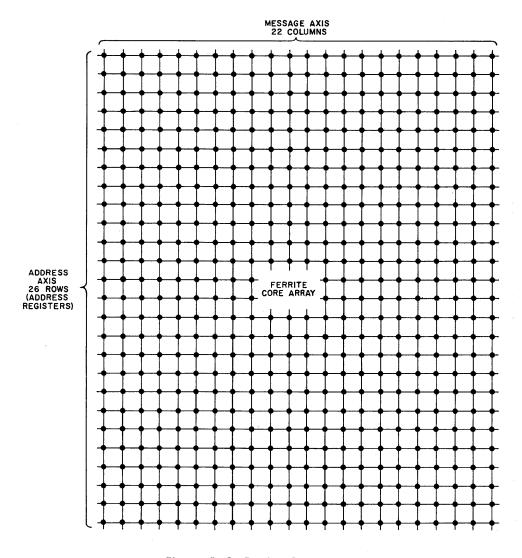

| 1-9    | Ferrite Core Array                                                                  | 13   |

| 1—10   | Core Current Coincidence for Read-In, Simplified Diagram                            | 14   |

| 1-11   | Core Windings, Simplified Diagram                                                   | 14   |

| 1-12   | Readout by Columns, Simplified Diagram                                              | 14   |

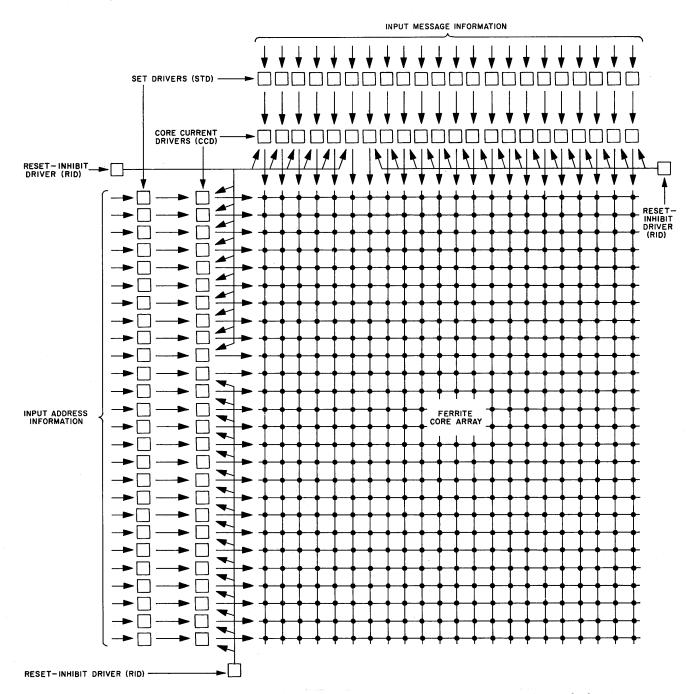

| 1-13   | Ferrite Core Array with Associated Special Circuit Used for Read-In, Block Diagram  | 15   |

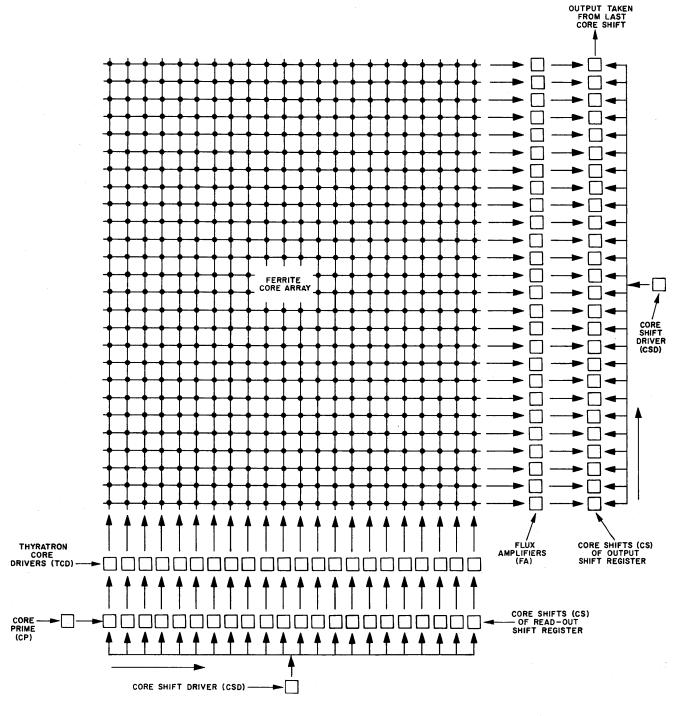

| 1-14   | Ferrite Core Array with Associated Special Circuits Used for Readout, Block Diagram | 16   |

| 2-1    | Output Control Element, Block Diagram                                               | 20   |

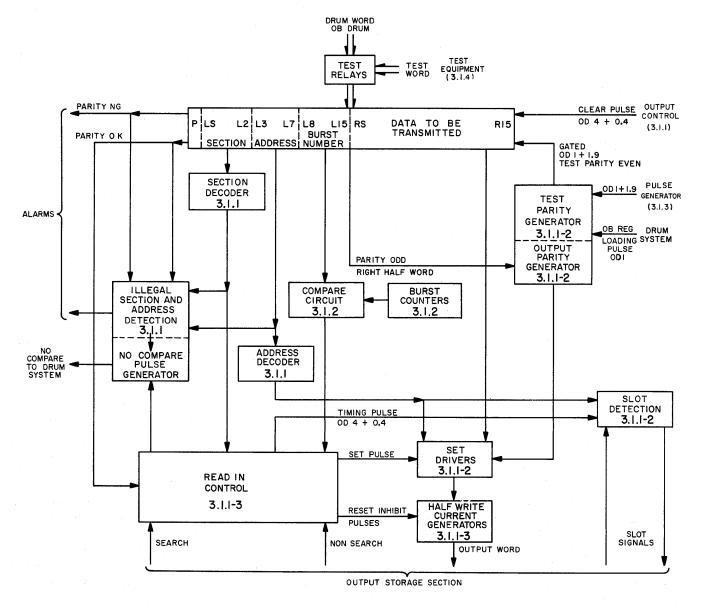

| 2-2    | Output Buffer Section (3.1.1), Block Diagram                                        | 22   |

| 2-3    | Drum Word Structure                                                                 | 23   |

| 2–4    | Right Drum Word Register (3.1.1.2), Simplified Logic Diagram                        | 26   |

| 2-5    | Burst Number Register (3.1.1), Simplified Logic Diagram                             | 27   |

| 2–6    | Section Address Register (3.1.1), Simplified Logic Diagram                          | 27   |

| 2-7    | Register Address Register (3.1.1), Simplified Logic Diagram                         | 28   |

| 2-8    | Parity Register (3.1.1), Simplified Logic Diagram                                   | 28   |

| 2-9    | Flip-Flop Register Clear Control (3.1.1), Simplified Logic Diagram                  | 29   |

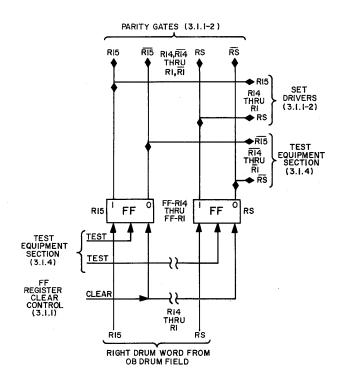

| 2-10   | Drum Word Test Parity Generator (3.1.1-2),<br>Simplified Logic Diagram              | 30   |

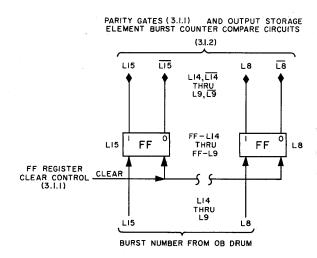

| 2-11   | Drum Word Parity Gates (3.1.1, 3.1.1-2), Simplified Logic Diagram                   | 31   |

| 2—12   | Output Parity Generator (3.1.1-2), Simplified Logic Diagram                         |      |

| Figure | Title                                                                                     | Page      |

|--------|-------------------------------------------------------------------------------------------|-----------|

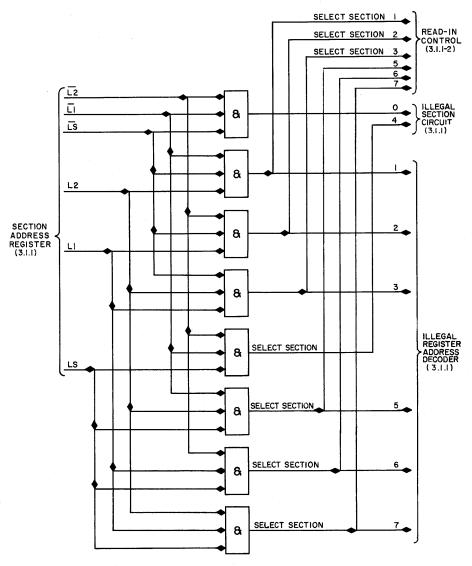

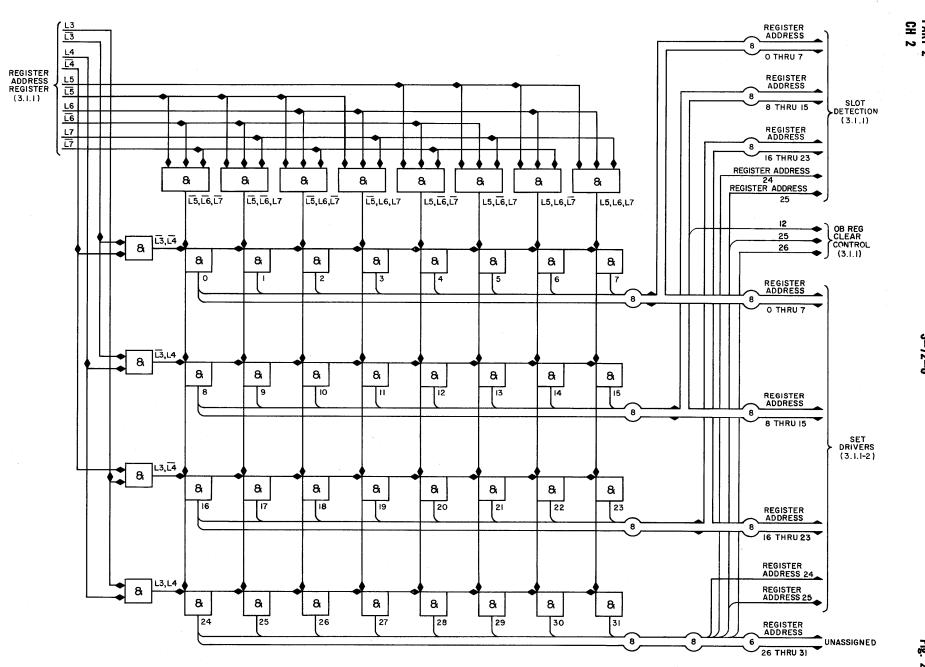

| 2-13   | Section Address Decoder (3.1.1), Simplified Logic Diagram                                 | . 33      |

| 2-14   | Register Address Decoder (3.1.1), Simplified Logic Diagram                                | . 35      |

| 2—15   | Slot Detection Circuit (3.1.1), Simplified Logic Diagram                                  | . 199/200 |

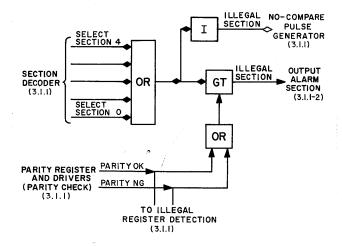

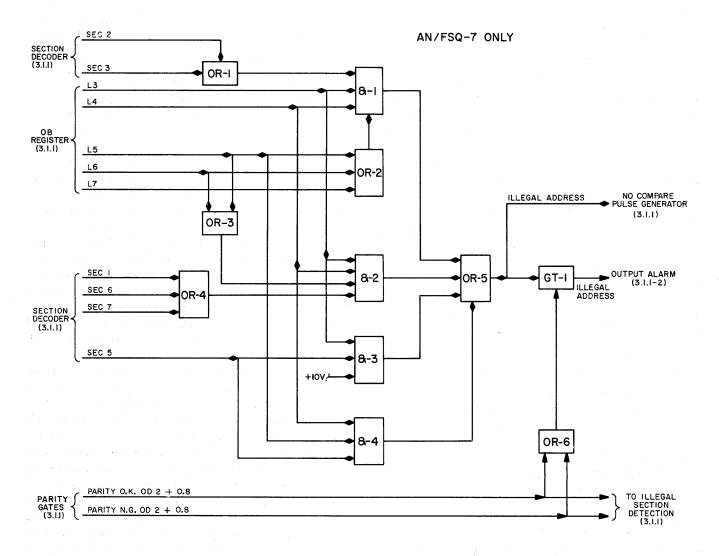

| 2–16   | Illegal Section Address Detection (3.1.1), Simplified Logic Diagram                       | 37        |

| 2-17   | Illegal Register Address Detection (3.1.1), Simplified Logic Diagram                      | 38        |

| 2-18   | Read-In to Storage Element, Simplified Logic Diagram                                      | 39        |

| 2-19   | G/A-FD and BOMARC Read-In Control Circuits (3.1.1-3), Simplified Logic Diagram            | 41        |

| 2-20   | G/G Read-In Control (3.1.1-3), Simplified Logic Diagram                                   | 42        |

| 2-21   | TTY Read-In Control (3.1.1-3), Simplified Logic Diagram                                   | 43        |

| 2-22   | Read-In Control Common Equipment (3.1.1-3), Simplified Logic Diagram                      | 43        |

| 2-23   | No-Compare Pulse Generator (3.1.1-3), Simplified Logic Diagram                            | 44        |

| 2-24   | Set Drivers (3.1.1-2), Simplified Logic Diagram                                           | 46        |

| 2-25   | Half-Write Current Generator Flip-Flops (3.1.1-3)                                         | 47        |

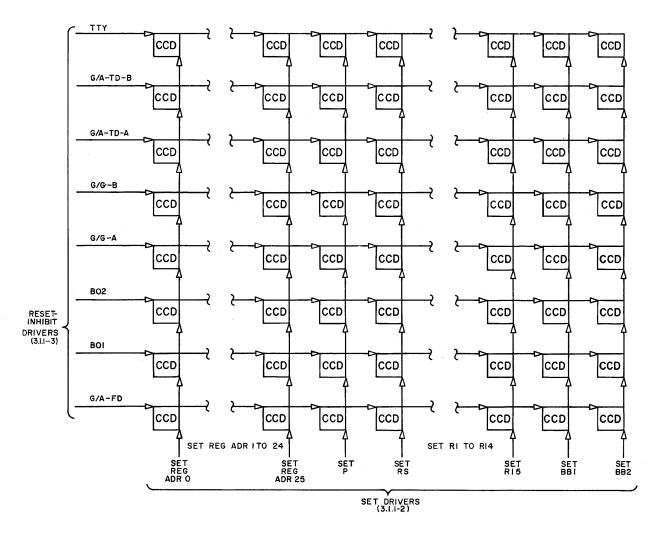

| 2–26   | Half-Write Current Generator Matrix (3.1.1-3), Simplified Logic Diagram                   | 48        |

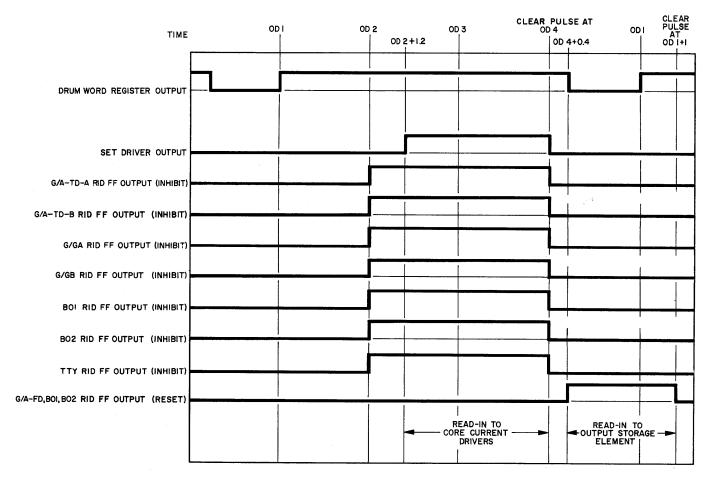

| 2-27   | Half-Write Current Generator Timing for G/A-FD Word, Functional Representation            | 49        |

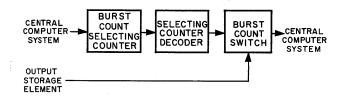

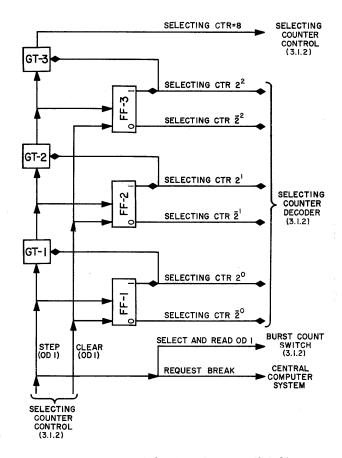

| 2-28   | Burst Count Selection and Transfer, Block Diagram                                         | 51        |

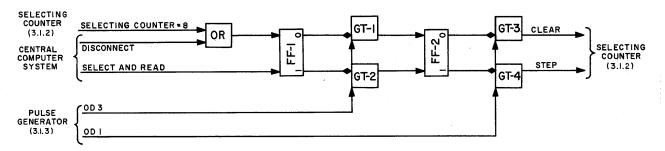

| 2-29   | Selecting Counter Control (3.1.2), Simplified Logic Diagram                               | <b>52</b> |

| 2-30   | Selecting Counter (3.1.2), Simplified Logic Diagram                                       | 52        |

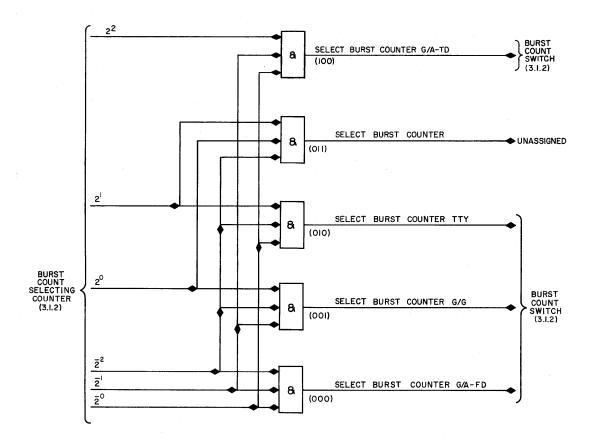

| 2-31   | Selecting Counter Decoder (3.1.2), Simplified Logic Diagram                               | 53        |

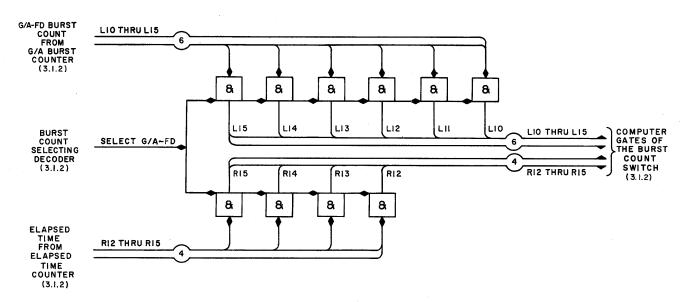

| 2-32   | G/A-FD Burst Selector of the Burst-Time Count<br>Switch (3.1.2), Simplified Logic Diagram | 54        |

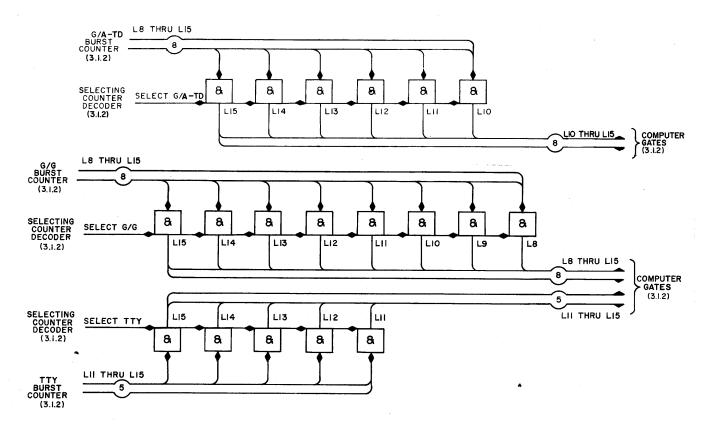

| 2-33   | G/A-TD, G/G, and TTY Burst Selectors of the Burst-Time Count Switch                       | 54        |

| 2-34   | Computer Gates of the Burst-Time Count Switch (3.1.1-3), Simplified Logic Diagram         | 55        |

| Figure Title |                                                                                                          |              |  |

|--------------|----------------------------------------------------------------------------------------------------------|--------------|--|

| 2-35         | Burst Counter Read Cycle, Timing Chart (Functional Representation)                                       | . 56         |  |

| 2-36         | Pulse Generators (3.1.3), Block Diagram                                                                  | . 57         |  |

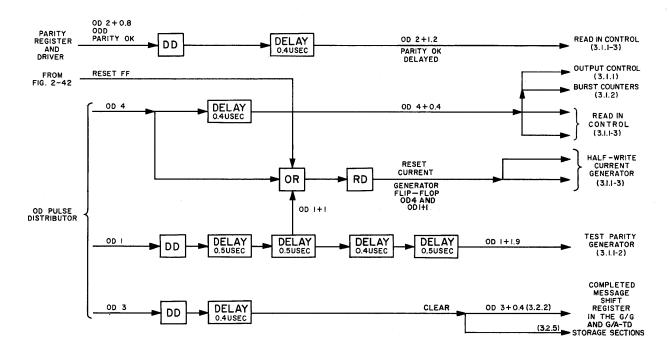

| 2-37         | OD Pulse Distributor (3.1.3), Simplified Logic Diagram                                                   |              |  |

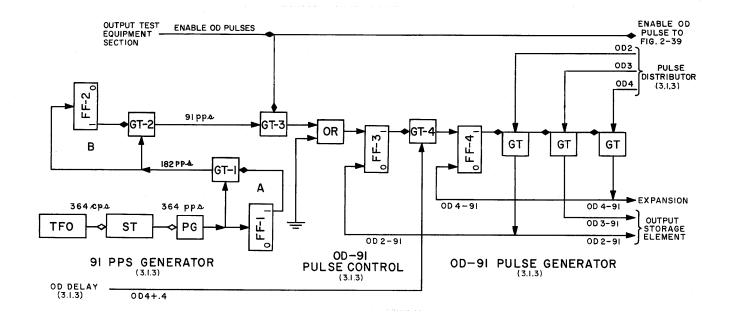

| 2-38         | 91-PPS Generator, OD 91 Control, and OD 91 Pulse<br>Generators (3.1.3), Simplified Logic Diagram         | . 59         |  |

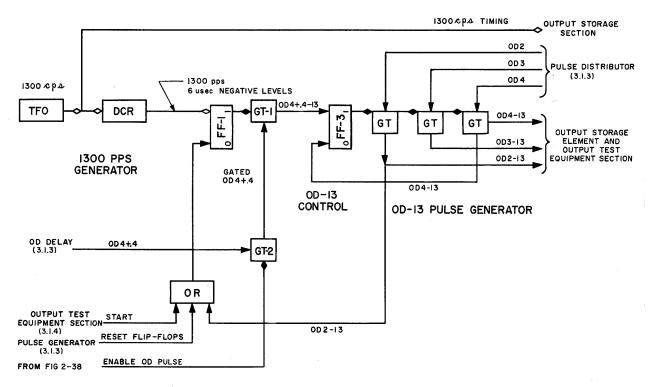

| 2-39         | 1,300-PPS Generator, OD 13 Control, and OD 13 Pulse<br>Generator (3.1.3), Simplified Logic Diagram       | . 60         |  |

| 2-40         | OD Delay (3.1.3), Simplified Logic Diagram                                                               | 60           |  |

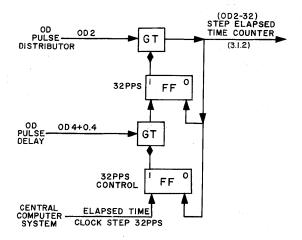

| 2-41         | 32-PPS Synchronizer (3.1.2), Simplified Logic Diagram                                                    | 61           |  |

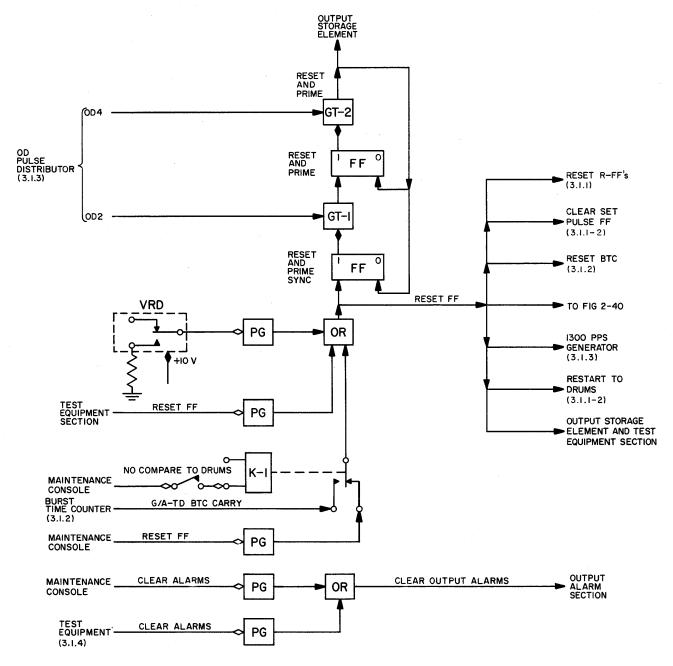

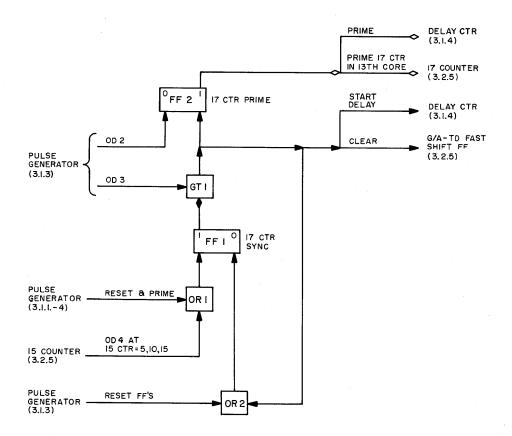

| 2–42         | Reset Flip-Flop, Reset-and-Prime, and Clear-Alarms Pulse<br>Generators (3.1.3), Simplified Logic Diagram | . 62         |  |

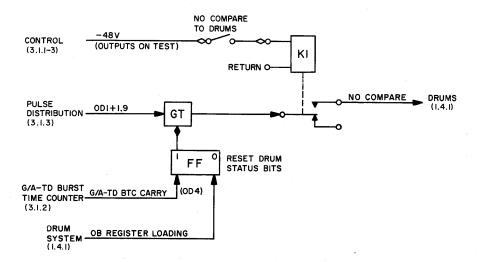

| 2–43         | Reset-Drum Status Bits Generator, Simplified Logic Diagram                                               | . 63         |  |

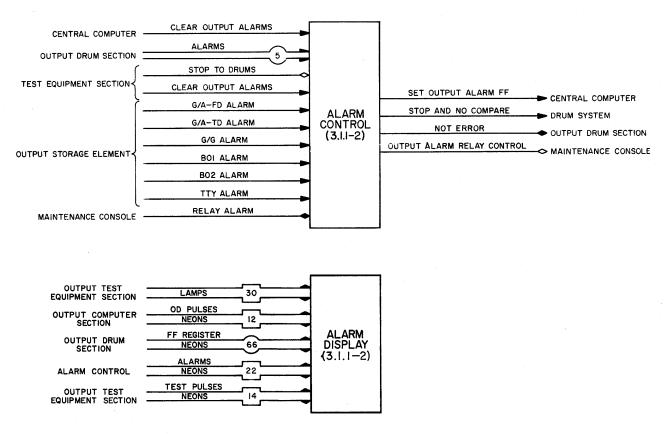

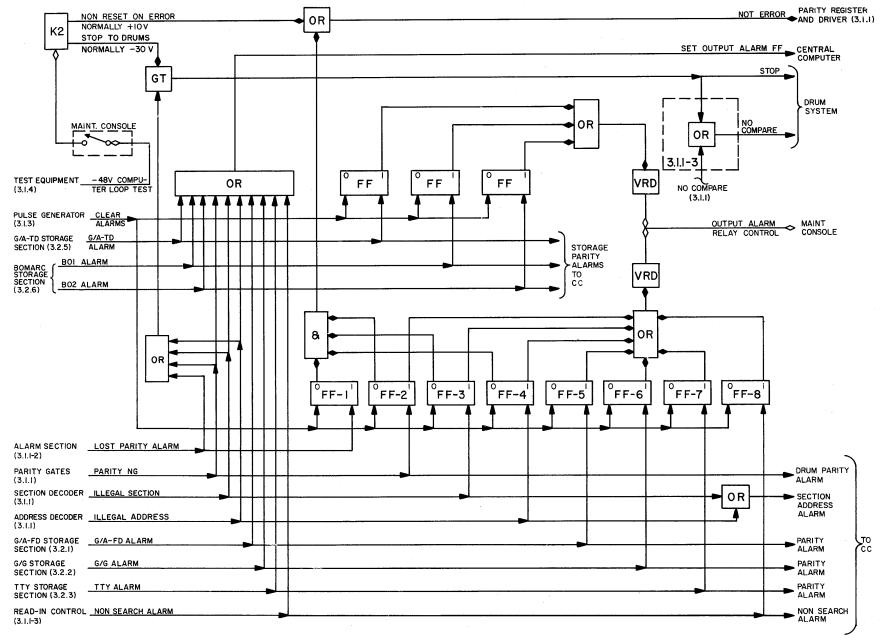

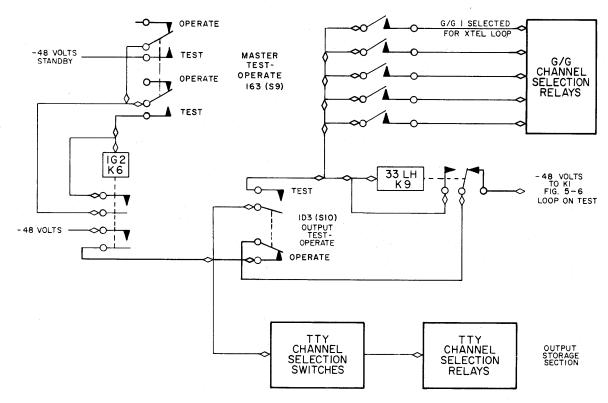

| 2-44         | Output Alarm Section, Block Diagram                                                                      | 65           |  |

| 2-45         | Output Alarm Control (3.1.1-2), Simplified Logic Diagram                                                 | . 66         |  |

| 2-46         | Alarm Display (3.1.1-2), Simplified Block Diagram                                                        | . 67         |  |

| 3-1          | Output Storage Element, Block Diagram                                                                    |              |  |

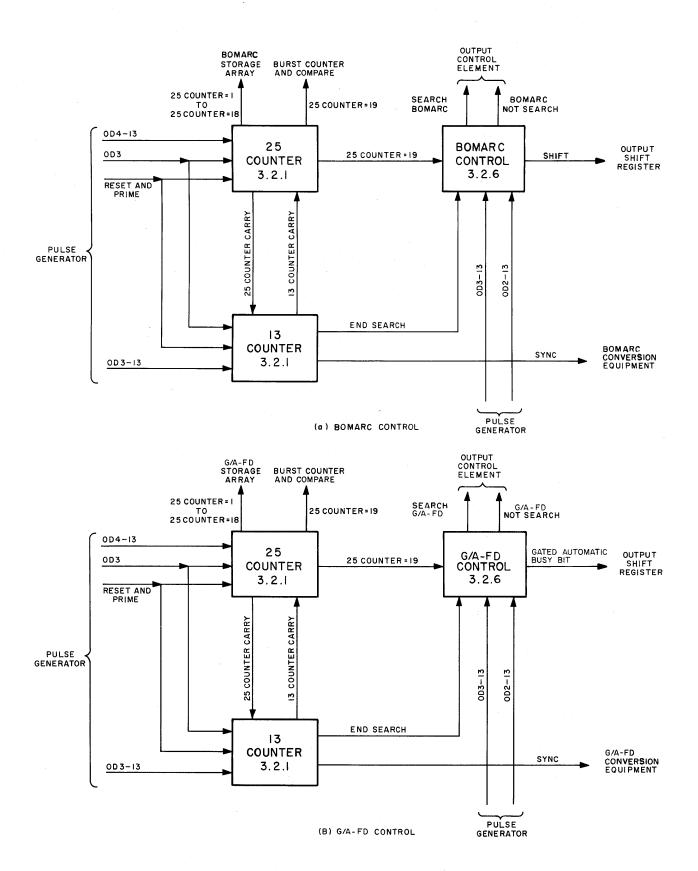

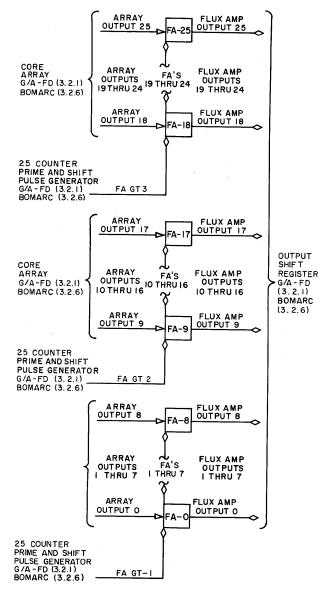

| 3–2          | G/A-FD or BOMARC Output Storage Section (3.2.1, 3.2.6), Block Diagram                                    | . 72         |  |

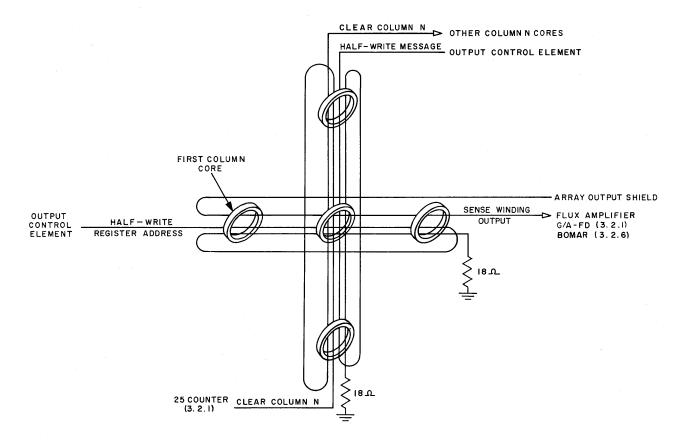

| 3-3          | G/A-FD and BOMARC Core Storage Arrays (3.2.1, 3.2.6), Slot 1, Simplified Logic Diagram                   | . 7 <b>4</b> |  |

| 3-4          | Core Windings, Simplified Diagram                                                                        | . 75         |  |

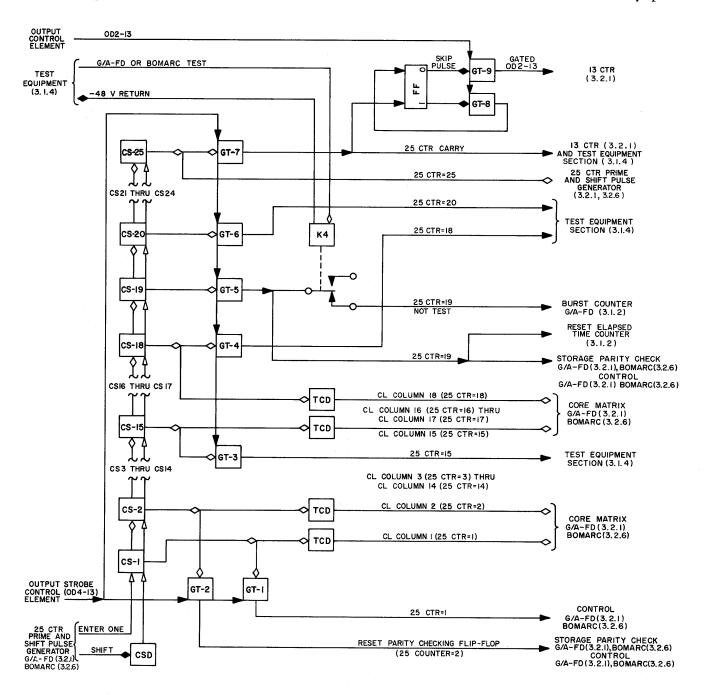

| 3-5          | G/A-FD and BOMARC Control Circuits (3.2.1), Block Diagram                                                | . 77         |  |

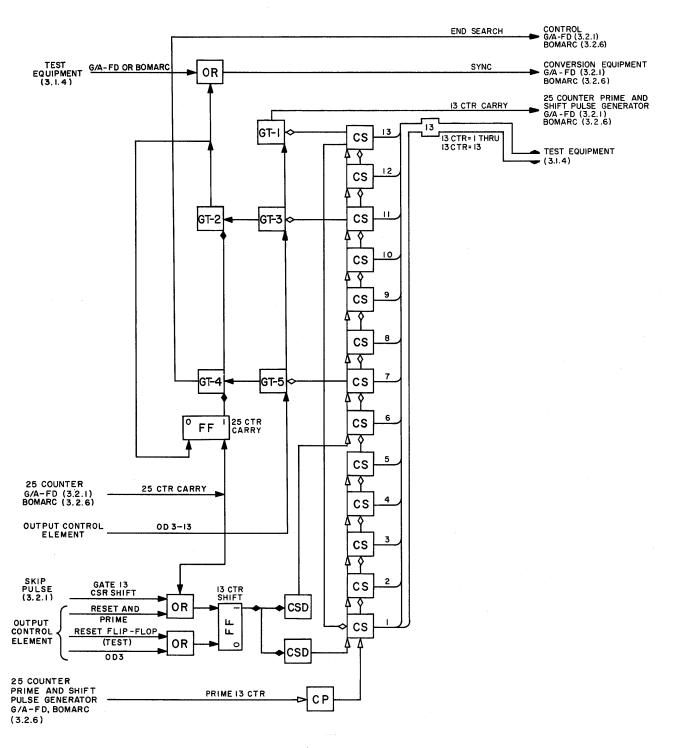

| 3–6          | G/A-FD and BOMARC 13 Counter (3.2.1), Simplified Logic Diagram                                           | . 78         |  |

| 3-7          | G/A-FD and BOMARC 25-Counter Prime and Shift Pulse<br>Generator (3.2.1, 3.2.6), Simplified Logic Diagram | . 79         |  |

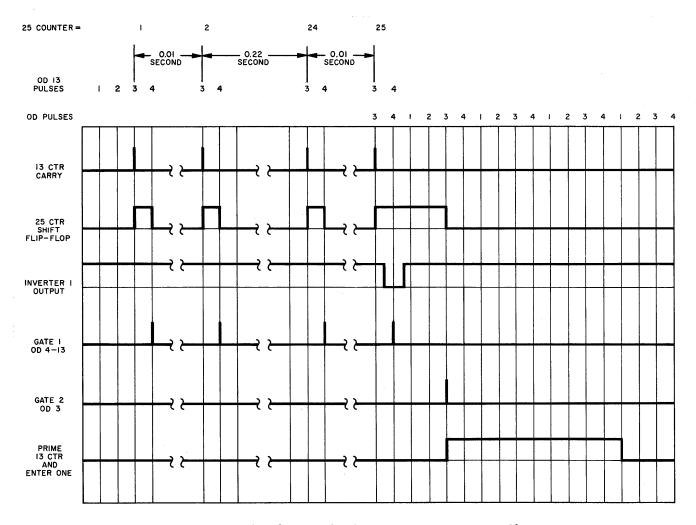

| 3-8          | Shift, Clear, and Prime 25 Counter, Timing Chart                                                         | . 80         |  |

| 3–9          | G/A-FD and BOMARC 25 Counter (3.2.1), Simplified Logic Diagram                                           | . 81         |  |

| 3—10         | G/A-FD and BOMARC Control (3.2.1, 3.2.6), Simplified Logic Diagram                                       | . 82         |  |

| 3-11         | G/A-FD and BOMARC Control, Timing Chart                                                                  | . 84         |  |

| 3-12         | G/A-FD or BOMARC Readout, Block Diagram                                                                  | . 85         |  |

| Figure | Title                                                                                        |     |  |

|--------|----------------------------------------------------------------------------------------------|-----|--|

| 3—13   | G/A-FD and BOMARC Flux Amplifiers (3.2.1, 3.2.6),<br>Simplified Block Diagram                | 85  |  |

| 3–14   | G/A-FD and BOMARC Output Shift Register (3.2.1, 3.2.6),<br>Simplified Logic Diagram          | 86  |  |

| 3–15   | G/A-FD and BOMARC Storage Parity Checking (3.2.1, 3.2.6), Simplified Logic Diagram           | 88  |  |

| 3–16   | G/A-FD and BOMARC Burst Counter (3.1.2), Simplified Logic Diagram                            | 91  |  |

| 3-17   | G/A-FD and BOMARC Compare (3.1.2), Simplified Logic Diagram                                  | 92  |  |

| 3–18   | G/A-FD and BOMARC Elapsed-Time Counter (3.1.2), Simplified Logic Diagram                     | 93  |  |

| 3–19   | G/A-FD and BOMARC Conversion, Message 1 (3.2.1, 3.2.6), Simplified Logic Diagram             | 93  |  |

| 3-20   | G/A-FD and BOMARC Input and Output Signals                                                   |     |  |

| 3–21   | G/A-FD and BOMARC Test and Duplex Switching,<br>Message 1 (3.2.1, 3.2.6), Simplified Diagram | 95  |  |

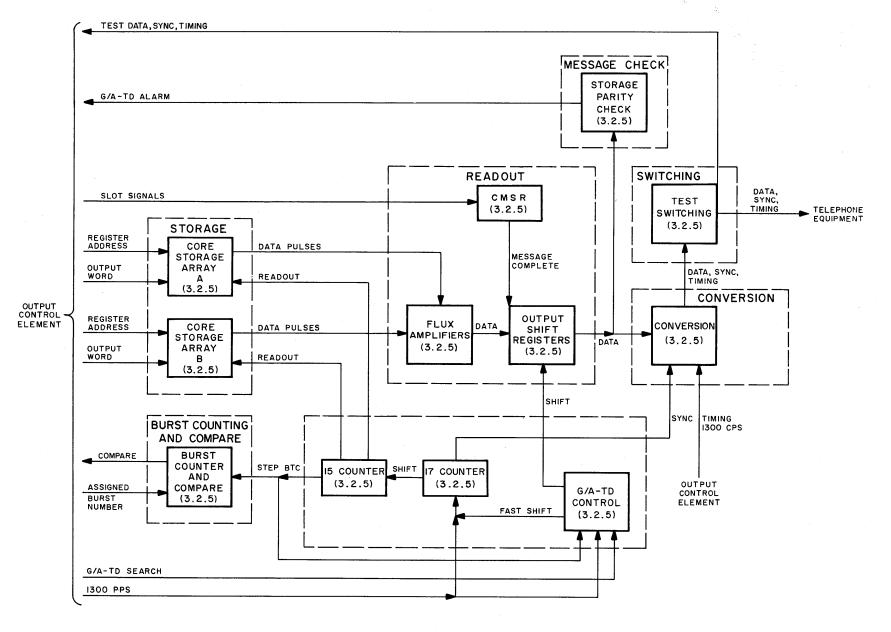

| 3–22   | G/G Output Storage Section (3.2.2), Simplified Block Diagram                                 | 98  |  |

| 3-23   | G/G Message, Serially Interleaved Form                                                       | 99  |  |

| 3–24   | G/G Core Storage Array (3.2.2),<br>Simplified Block Diagram                                  | 100 |  |

| 3-25   | Portion of G/G Core Storage Array (3.2.2), Simplified Diagram                                | 100 |  |

| 3-26   | Output Wiring of G/G Core Arrays A and B, Simplified Diagram                                 | 101 |  |

| 3-27   | 5 Counter (3.2.2), Simplified Logic Diagram                                                  | 101 |  |

| 3-28   | 19 Counter (3.2.2), Simplified Logic Diagram                                                 | 102 |  |

| 3-29   | G/G Control (3.2.2), Simplified Logic Diagram                                                | 104 |  |

| 3-30   | G/G Control Timing Chart                                                                     | 105 |  |

| 3-31   | Flux Amplifiers (3.2.2), Simplified Block Diagram                                            | 106 |  |

| 3-32   | G/G Output Shift Register (3.2.2), Simplified Logic Diagram                                  | 107 |  |

| 3-33   | Completed Message Shift Register (3.2.2), Simplified Logic Diagram                           | 108 |  |

| 3-34   | G/G Storage Parity Checking (3.2.2), Simplified Logic Diagram                                | 109 |  |

| 3-35   | G/G Burst Counter (3.1.2), Simplified Logic Diagram                                          | 109 |  |

| Figure | Title                                                                                                | Page    |

|--------|------------------------------------------------------------------------------------------------------|---------|

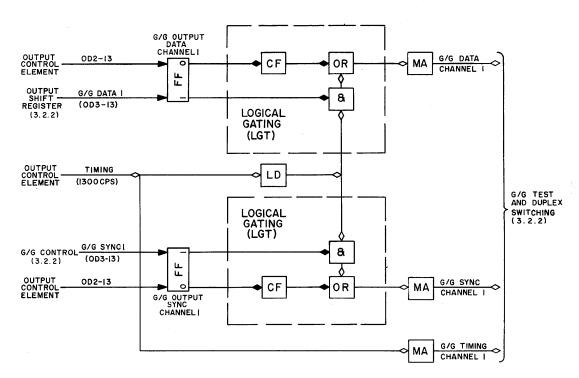

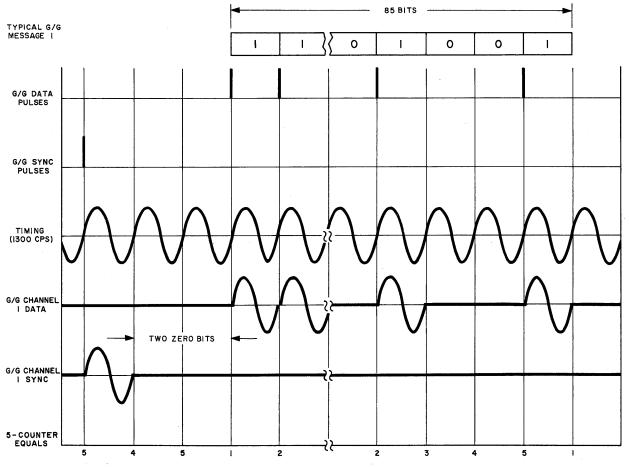

| 3-36   | G/G Conversion, Message 1 (3.2.2), Simplified Logic Diagram                                          | 110     |

| 3-37   | G/G Conversion, Input and Output Signals                                                             | 110     |

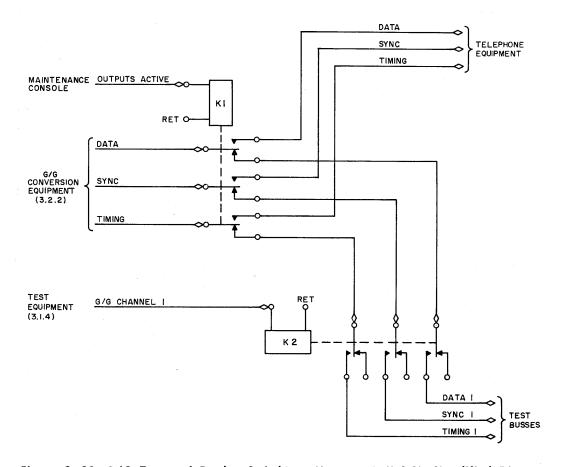

| 3-38   | G/G Test and Duplex Switching, Message 1 (3.2.2), Simplified Diagram                                 | 111     |

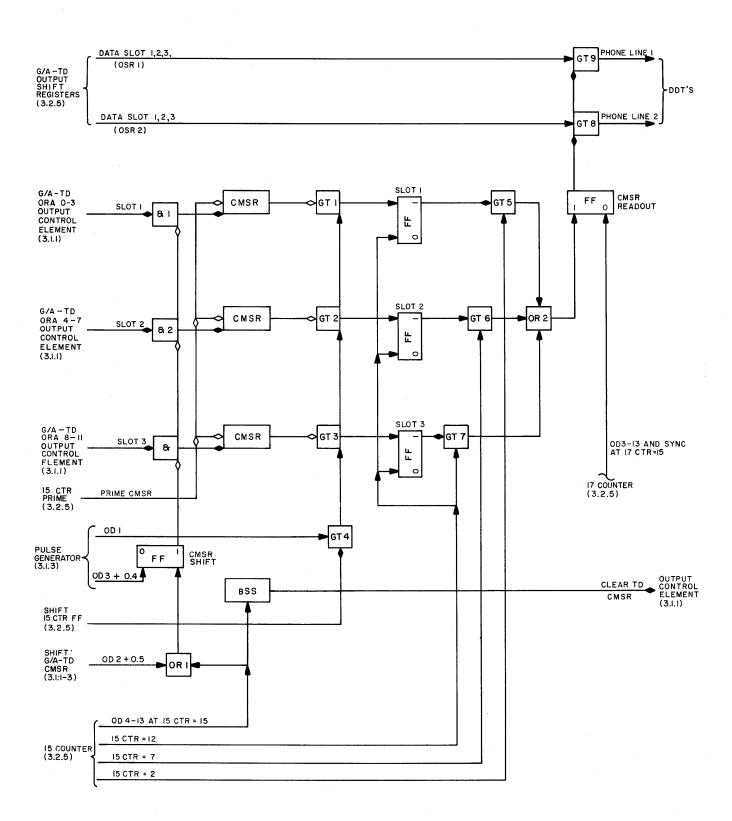

| 3-39 - | G/A-TD Output Storage Section, Simplified Block Diagram                                              | 114     |

| 3-40   | G/A-TD Core Storage Array, Simplified Logic Diagram                                                  | 115     |

| 3-41   | G/A-TD 17 Counter (3.2.5), Simplified Logic Diagram                                                  | 116     |

| 3-42   | G/A-TD Frequency Divider, Fast-Shift Control, 17-Counter<br>Shift Circuits, Simplified Logic Diagram | 118     |

| 3-43   | G/A-TD High-Speed Shift Timing Chart                                                                 | 201/202 |

| 3-44   | G/A-TD 15 Counter (3.2.5), Simplified Logic Diagram                                                  | 203/204 |

| 3-45   | Overall Timing Chart, G/A-TD Storage Section                                                         | 205/206 |

| 3-46   | G/A-TD Search Flip-Flop, Simplified Logic Diagram                                                    | 119     |

| 3-47   | G/A-TD Array Selection (3.2.5), Simplified Logic Diagram                                             | 120     |

| 3-48   | G/A-TD 15-Counter Control Circuits (3.2.5), Simplified Logic Diagram                                 |         |

| 3-49   | G/A-TD Auto Parity Bit Generator, Simplified Logic Diagram                                           | 121     |

| 3-50   | G/A-TD Word Message Layout                                                                           | 122     |

| 3-51   | Associated Control Circuits, 17 Counter, Simplified Logic Diagram                                    | 123     |

| 3-52   | G/A-TD Flux Amplifiers (3.2.5), Simplified Logic Diagram                                             | 124     |

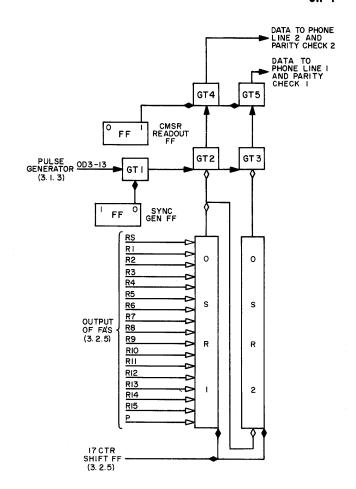

| 3-53   | G/A-TD Output Shift Register, Simplified Logic Diagram                                               | 124     |

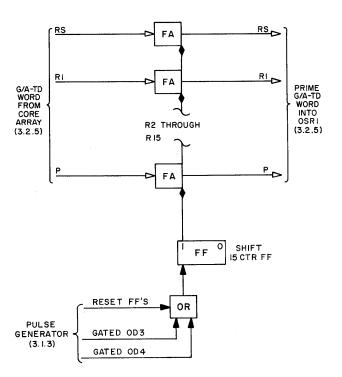

| 3-54   | G/A-TD Completed Message Shift Register (3.2.5), Simplified Logic Diagram                            | 126     |

| 3-55   | G/A-TD Parity Check Circuit (3.2.5), Simplified Logic Diagram                                        | 128     |

| 3-56   | G/A-TD Burst Counter (3.1.2), Simplified Logic Diagram                                               | 129     |

| 3-57   | G/A-TD Compare (3.1.2), Simplified Logic Diagram                                                     | 130     |

| 3-58   | G/A-TD Conversion, Message 1 (3.2.5), Simplified Logic Diagram                                       | 131     |

| 3-59   | G/A-TD Conversion, Input and Output Signals                                                          |         |

| 3-60   | G/A-TD Test and Duplex Switching, Message 1 (3.2.5),                                                 | 133     |

| Figure | Title                                                                                    |       |  |  |

|--------|------------------------------------------------------------------------------------------|-------|--|--|

| 3-61   | Composition of TTY Signals                                                               | . 135 |  |  |

| 3-62   | Composition of TTY Output Word                                                           | . 136 |  |  |

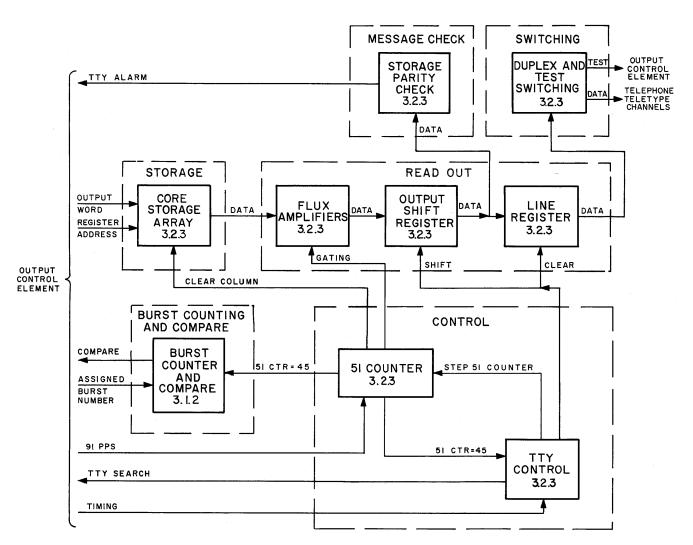

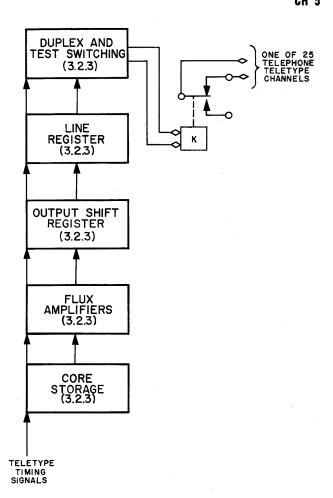

| 3-63   | TTY Output Storage Section (3.2.3), Simplified Block Diagram                             | . 137 |  |  |

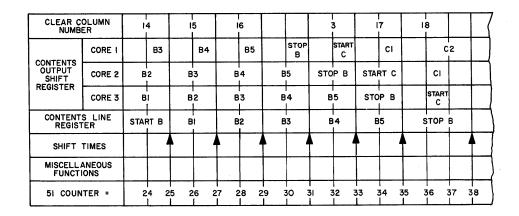

| 3-64   | Timing of TTY Storage Section Operations                                                 | . 138 |  |  |

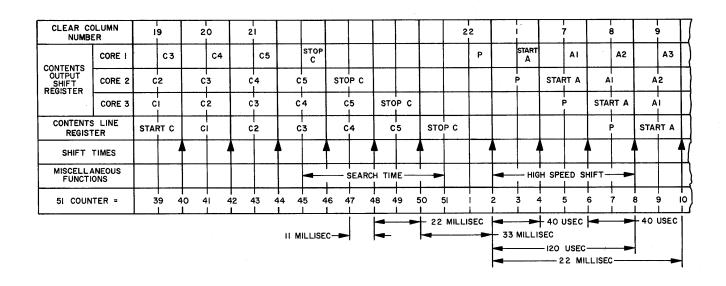

| 3-65   | TTY Core Storage Array (3.2.3), Simplified Logic Diagram                                 | . 139 |  |  |

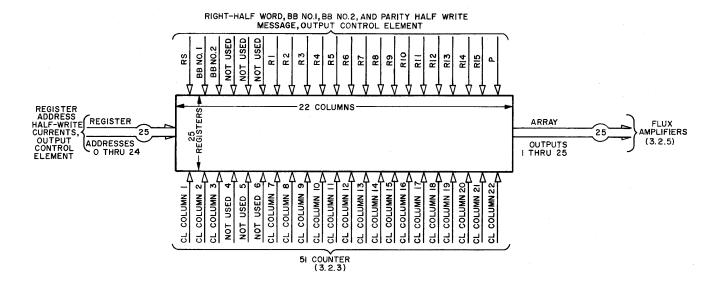

| 3-66   | 51 Counter (3.2.3), Simplified Logic Diagram                                             | . 140 |  |  |

| 3–67   | Shift-Pulse Generator, 51 Counter (3.2.3), Simplified Logic Diagram                      | . 142 |  |  |

| 368    | TTY Control (3.2.3), Simplified Logic Diagram                                            | . 143 |  |  |

| 3-69   | High-Speed Shift Timing                                                                  | . 143 |  |  |

| 3-70   | TTY Readout Flow of Data, Block Diagram                                                  | . 144 |  |  |

| 3-71   | TTY Core Storage Readout, Simplified Block Diagram                                       | . 145 |  |  |

| 3-72   | TTY Output Shift Register (3.2.3), Simplified Logic Diagram                              | . 146 |  |  |

| 3-73   | Line Register (3.2.3), Simplified Logic Diagram                                          | . 147 |  |  |

| 3-74   | TTY Storage Parity Checking (3.2.3), Simplified Logic Diagram                            | . 147 |  |  |

| 3-75   | TTY Burst Counter (3.1.2), Simplified Logic Diagram                                      | . 148 |  |  |

| 3–76   | Comparison Circuit, Teletype Burst Counter (3.1.2), Simplified Logic Diagram             | . 148 |  |  |

| 4-1    | Test Control Panel, Unit 42                                                              | . 151 |  |  |

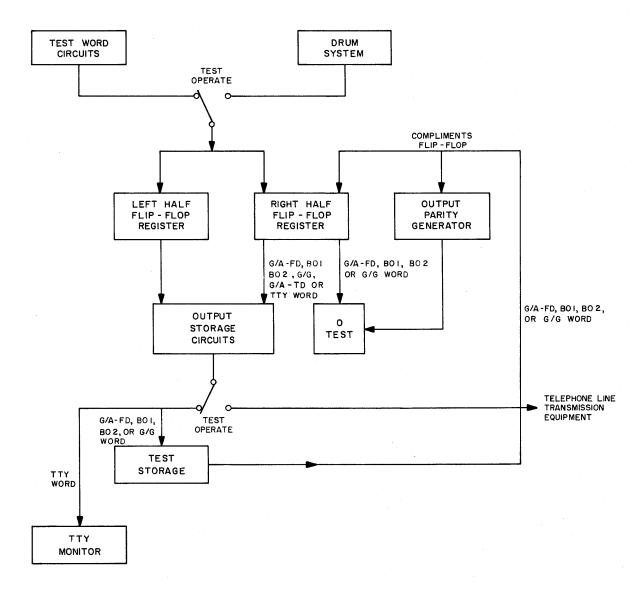

| 4-2    | Unit Loop Test Data Flow, Block Diagram                                                  | . 153 |  |  |

| 4-3    | Unit-Loop-On-Test Control Circuit (3.1.4), Simplified Logic Diagram                      | . 155 |  |  |

| 4-4    | Drum Isolation and Test Bit Circuit (3.1.4), Simplified Logic Diagram                    | . 156 |  |  |

| 4-5    | Unit Loop Test Selection Circuit (3.1.4)                                                 | . 157 |  |  |

| 4-6    | Test Start Control (3.1.4), Simplified Logic Diagram                                     | . 158 |  |  |

| 4-7    | Test Word Generator and Address Register Stepping, Simplified Logic Diagram              |       |  |  |

| 4-8    | Single-Address Stepping Circuit (3.1.4), Simplified Logic Diagram                        | . 159 |  |  |

| 4–9    | Test CSR Data-Bit Generator and Error Check Circuit (3.1.4),<br>Simplified Logic Diagram | . 161 |  |  |

| 4–10   | Zero Test and Master Stop Circuit (3.1.4), Simplified Logic Diagram                      | . 164 |  |  |

| Figure | Title                                                                                | Page    |

|--------|--------------------------------------------------------------------------------------|---------|

| 4–11   | Parallel Readout Control Circuit (3.1.4), Simplified Logic Diagram                   | 165     |

| 4-12   | Core Register (3.1.4), Simplified Logic Diagram                                      | 207/208 |

| 4-13   | TTY Duplex and Test Switching for Messages 1 and 2 (3.2.3), Simplified Logic Diagram | 167     |

| 4–14   | Computer Loop Test, Flow of Data, Simplified Block Diagram                           | 172     |

| 4-15   | Long-Range Radar Input Message                                                       | 173     |

| 4–16   | Computer Loop Test Channel Selection Circuit (3.1.4), Simplified Logic Diagram       | 174     |

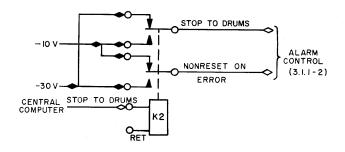

| 4-17   | Stop-to-Drums Circuit (3.1.4), Simplified Logic Diagram                              | 175     |

| 4–18   | Restart-to-Drums Circuit (3.1.1-2), Simplified Logic Diagram                         | 175     |

| 4-19   | Pause-and-Sync-Control Circuit (3.1.4), Simplified Block Diagram                     | 176     |

| 4–20   | G/A-TD 13-Core Delay Counter (3.2.5), Simplified Logic Diagram                       | 177     |

| 5-1    | Output System, Block Diagram                                                         | 179     |

| 5-2    | Flip-Flop Register Clear Control (3.1.1), Simplified Logic Diagram                   | 181     |

| 5-3    | Output Parity Generator (3.1.1-2), Simplified Logic Diagram                          | 182     |

| 5-4    | Test Control Panel, Unit 42                                                          | 182     |

| 5-5    | Unit Loop Test Data Flow, Block Diagram                                              | 183     |

| 5–6    | Unit-Loop-on-Test Test Circuit (3.1.4), Simplified Logic Diagram                     | 184     |

| 5-7    | Drum Isolation and Test-Bit Circuit (3.1.4), Simplified Logic Diagram                | 185     |

| 5-8    | Test Start Control Circuit (3.1.4), Simplified Logic Diagram                         | 186     |

| 5–9    | Test Core Shift Register Control Circuit (3.1.4), Simplified Logic Diagram           | 187     |

| 5-10   | Data-Sample Level Generator (3.1.4), Simplified Logic Diagram                        | 188     |

| 5–11   | Test-Data Pulse Generator (3.1.4), Simplified Logic Diagram                          | 189     |

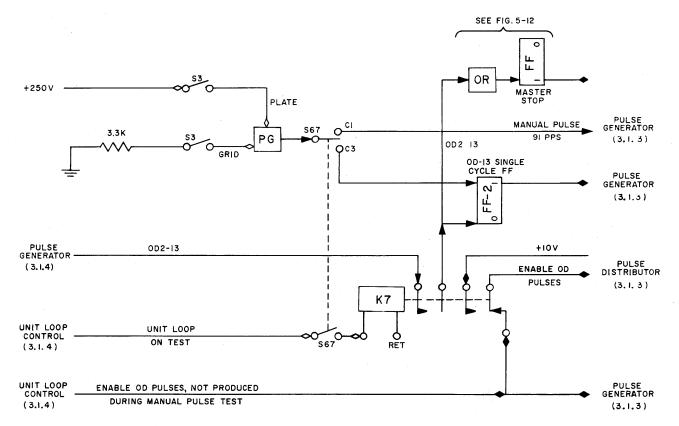

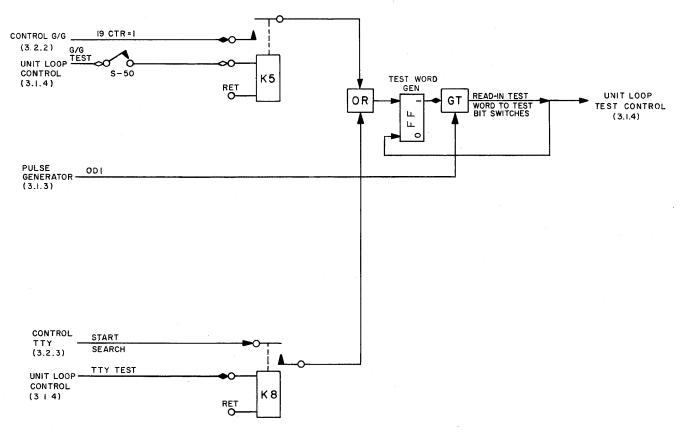

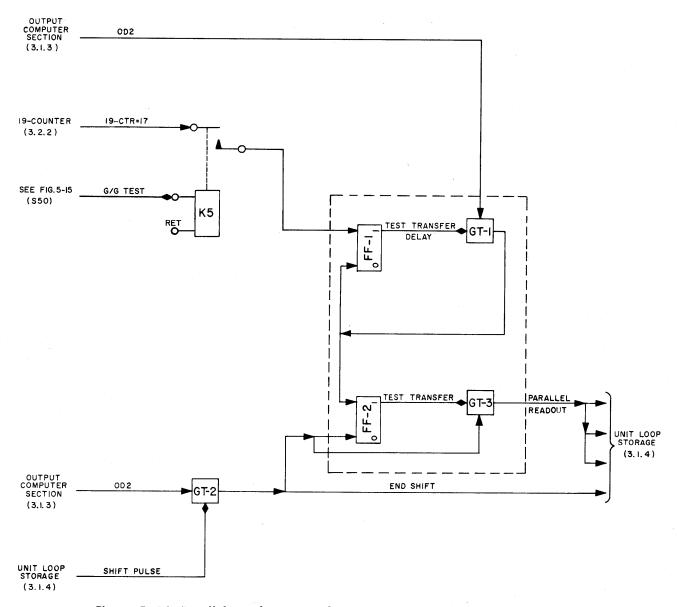

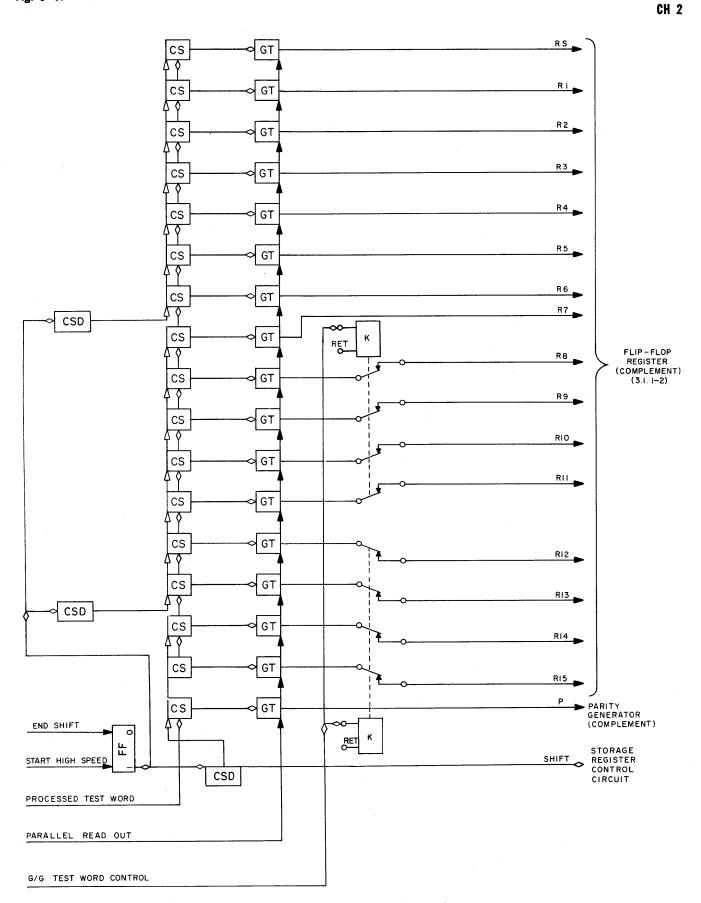

| 5—12   | Error Detection Circuit and Master Stop (3.1.4), Simplified Logic Diagram            | 190     |

| 5-13   | Single-Cycle Control Circuit (3.1.4), Simplified Logic Diagram                       | 190     |

| Figure | Title                                                                | Page |

|--------|----------------------------------------------------------------------|------|

| 5-14   | Manual-Pulse Control Circuit (3.1.4), Simplified Logic Diagram       | 191  |

| 5-15   | Test Word Generator (3.1.4), Simplified Logic Diagram                | 192  |

| 5–16   | Parallel Readout Control Circuit (3.1.4), Simplified Logic Diagram   | 193  |

| 5-17   | Core Register (3.1.4), Simplified Logic Diagram                      | 194  |

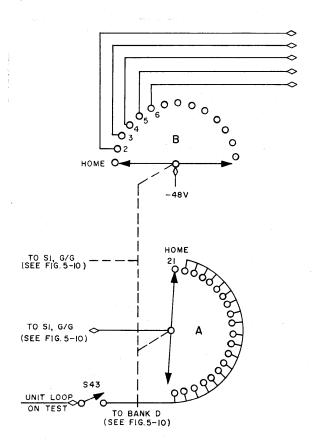

| 5-18   | Stepping Switch Home Control (3.1.4), Simplified Logic Diagram       | 195  |

| 5-19   | TTY Unit Loop Test Control Circuit (3.1.4), Simplified Logic Diagram | 196  |

| 5-20   | Computer Loop Test, Flow of Data, Block Diagram                      | 196  |

| 5-21   | Computer Loop Test Relaying and Switching, Simplified Block Diagram  | 197  |

| 5-22   | Stop-to-Drums Circuit (3.1.4), Simplified Logic Diagram              | 197  |

| 5-23   | Restart-to-Drums Circuit (3.1.1-2), Simplified Logic Diagram         | 198  |

#### LIST OF TABLES

| Table | Title                                                 | Page  |

|-------|-------------------------------------------------------|-------|

| 1-1   | Teletype Code                                         | . 5   |

| 2-1   | Conditions for Acceptance or Rejection of a Drum Word | . 23  |

| 2-2   | Section Address Assignment                            | . 34  |

| 2-3   | Register Address Assignment                           | . 36  |

| 2-4   | Tabular Summary, No-Compare Pulse Generator           | . 45  |

| 3-1   | Interleaving of G/A-FD and BOMARC Messages            | . 89  |

| 3-2   | Destination and Function of 51-Counter Pulses         | . 140 |

| 3-3   | Assignment of Bits in TTY Core Storage                | . 145 |

# PART 1 INTRODUCTION

# CHAPTER 1 GENERAL

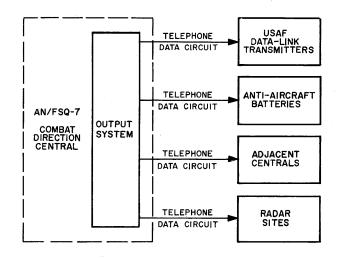

# 1.1 FUNCTION OF OUTPUT SYSTEM IN AN/FSQ-7 COMBAT DIRECTION CENTRAL

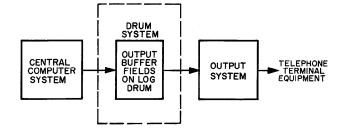

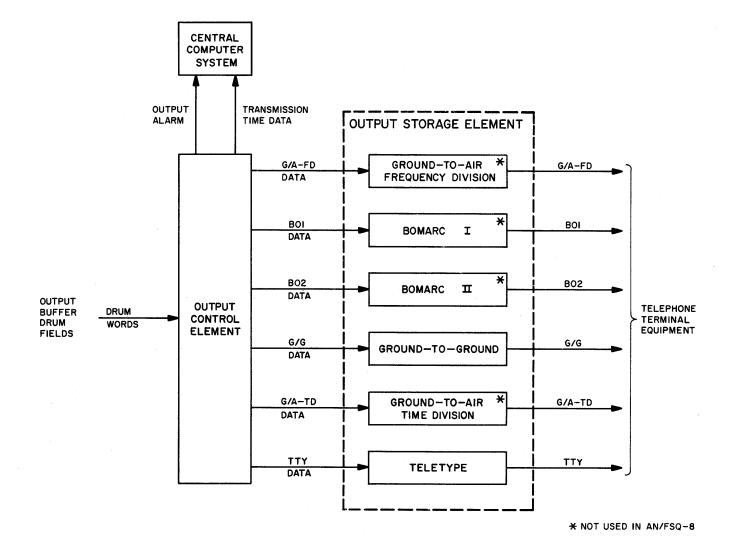

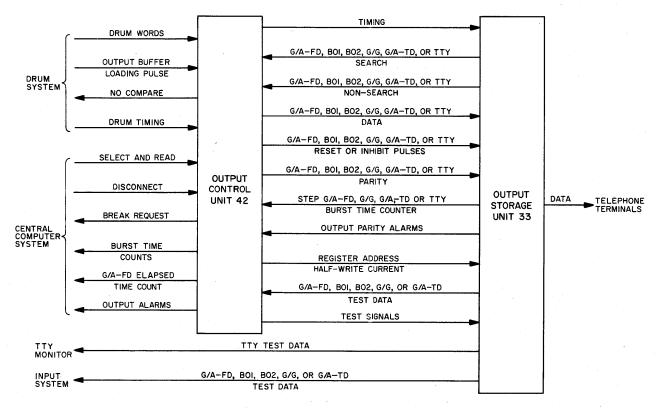

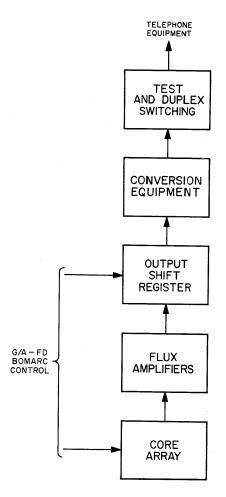

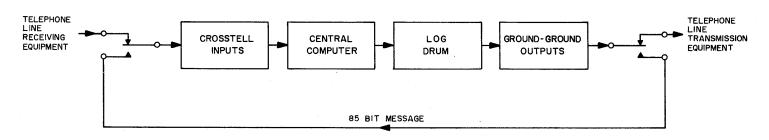

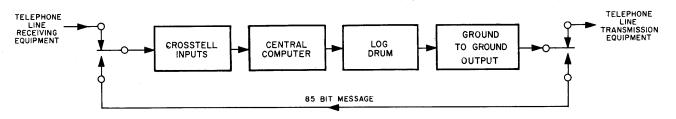

The Output System in the AN/FSQ-7 Combat Direction Central transfers output messages from the Central to adjacent Centrals and remote sites through telephone facilities. (See fig. 1-1.) After forming an output message, the Central Computer System stores it on the output buffer (OB) fields of the LOG drum in the Drum System for eventual transfer to the Output System. The Output System accepts the output message from the OB fields and transfers the message to telephone facilities for transmission to its intended destination(s). The path followed by the output message from the Central Computer System to the telephone facilities is shown in figure 1-2. The general manner in which the Output System accepts output messages from the OB fields and transfers them to telephone facilities is discussed below. Because the Output System is logically divided into two elements, the output control element and the output storage element, as shown in figure 1-3, the following general description of the operations performed by the Output System is treated by referring to these two elements.

Figure 1-1. Remote Sites, Block Diagram

Figure 1-2. Output Message Flow, Block Diagram

# 1.2 FUNCTION OF OUTPUT SYSTEM IN AN/FSQ-8 COMBAT CONTROL CENTRAL

The operational function (tactical) of a Combat Control Central is exclusively concerned with monitoring and directing the operational activities of Combat Direction Centrals. A Combat Control Central has no provision for conducting ground-to-air communications with manned or unmanned interceptors; hence, certain facilities in the equipment complex (Output) of a Combat Control Central are not utilized.

The Output System facilities that are part of the equipment complex in a Combat Direction Central but are not required for use in the tactical activity of a Combat Control Central are the ground-to-air-FD, BOMARC 1, BOMARC 2, and the ground-to-air-TD storage sections. The Output System facilities utilized in a Combat Control Central are the ground-to-ground and the teletype storage sections.

Nevertheless, the function of the Output System in an AN/FSQ-8 Combat Control Central is similar to the function outlined for that of an AN/FSQ-7 Combat Direction Central, and is discussed in Part 5.

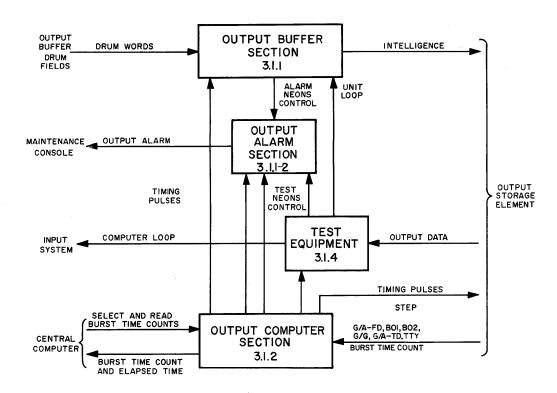

#### 1.3 OUTPUT CONTROL ELEMENT

The output control element primarily controls the flow of output message words from the OB fields of the LOG drum to the output storage element. Another function of the output control element is to make available to the Central Computer System specific data which is used by the Air Defense program as an aid in con-

trolling the transmission time of output messages. The output control element also provides visual indications of alarm conditions that might occur in the Output System and, in addition, contains Output System test equipment which can be used both as an aid in detecting the sources of trouble within the Output System and as an aid in checking certain elements of the Input System.

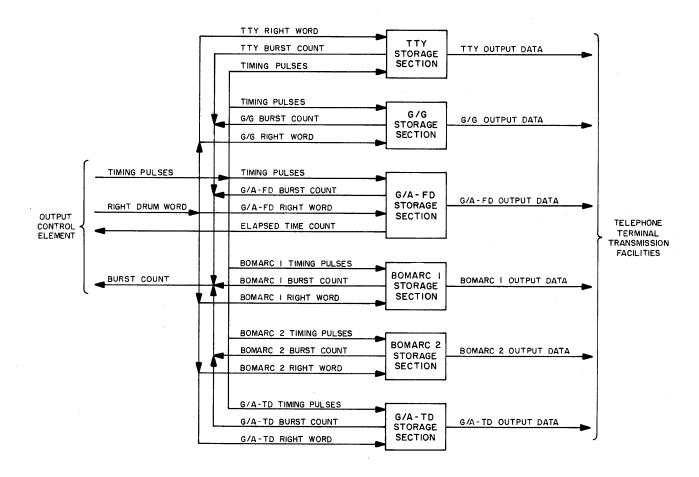

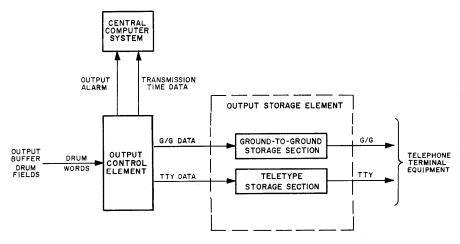

#### 1.4 OUTPUT STORAGE ELEMENT

The output storage element temporarily stores the words of an output message and then, at the completion of read-in (when the complete message is present in the output storage element), transfers the message serially to telephone terminal equipment. This element contains six storage sections; each accommodates a different class of output messages. Output messages are grouped into six classes: ground-to-air frequency division (G/A-FD), BOMARC 1 (BO1), BOMARC 2 (BO2), ground-to-air

time division (G/A-TD), ground-to-ground (G/G), and teletype (TTY). The storage sections are labeled accordingly: the G/A-FD storage section, the BO1 storage section, the BO2 storage section, the G/G storage section, the G/A-TD storage section, and the TTY storage section. These storage sections receive and store output messages and then transfer them serially to the telephone terminal equipment. However, the transfer rate employed by the storage sections differs and depends upon the class of output message handled. Output messages in the G/A-FD, BO1, BO2, G/G, and G/A-TD classes are sent over telephone data channels to sites equipped with automatic input equipment. Sites not equipped with automatic input devices are supplied with teletypewriter receivers. Output messages destined for such sites are in the TTY message class and are transferred by the TTY storage section to telephone equipment at the standard TTY rate of 60 words per minute (wpm).

Figure 1-3. Output System, Block Diagram

# CHAPTER 2 OUTPUT MESSAGES

#### 2.1 GENERAL

An output message is a communication sent from an AN/FSQ-7 Combat Direction Central to adjacent Centrals or remote units. The Central Computer System performs various operations, controlled by the air defense program, upon air defense situation data supplied to the Central Computer System by radar sites, adjacent Centrals, and by personnel (manually) through the Input System. If the results of these operations are to be transmitted to remote units, such results are formed into output messages. As previously indicated, an output message falls into one of six classes: G/A-FD, BO1, BO2, G/G, G/A-TD, and TTY. The data used to form each message class and the purpose or purposes of each class are described below.

Ground-to-air-FD and -TD messages are composed of data which will help manned fighter aircraft intercept assigned enemy targets. The G/A-FD and -TD messages are transmitted from the Central to the remote G/A-FD and -TD data-link transmitters which provide the radio link with the aircraft. BOMARC 1 and BOMARC 2 messages are used specifically to control unmanned interceptors (missiles).

A G/G message is composed of either crosstelling (XTL) data, forwardtelling data, or a height-finder request. Ground-to-ground XTL messages are transmitted to adjacent AN/FSQ-7 Combat Direction Centrals, and G/G forwardtelling messages are sent to an AN/FSQ-8 Combat Control Central. Crosstelling information is data that aids the receiving Central in performing its assigned function. Forwardtelling data is a report on the overall situation in the area of the sending Central. The remaining type of G/G message is composed of a height-finder request which is sent to height-finding equipment at a radar site. A height-finder request message is employed whenever the altitude of a specific target is required.

Teletype messages are formed of either information intended for higher headquarters, information for non-

automatic adjacent sectors (sectors not equipped with AN/FSQ-7 Combat Direction Centrals), or early warning information intended for antiaircraft batteries. Forwardtelling information sent to higher headquarters is a summary tabulation of the up-to-the-minute air defense situation. The TTY messages sent to nonautomatic adjacent sectors contain information similar to the data in G/G messages. Teletype messages sent to the antiaircraft batteries are composed of early warning radar data.

# 2.2 TIMING OF OUTPUT MESSAGE TRANSMISSIONS

The time for the transmission of each output message is selected in the Central Computer System, and certain Output System circuits ensure that the message is transmitted at the selected time. The reasons for this control and the means by which it is accomplished are described in the following text.

Output messages must be transmitted in correct sequence within each of the six classes: G/A-FD, BO1, BO2, G/G, G/A-TD, and TTY. In addition, certain types of messages in each class must be transmitted at the proper times.

#### 2.3 MESSAGE FORMATION

#### 2.3.1 General

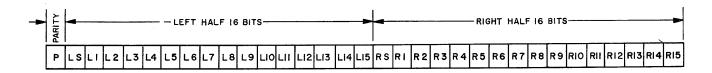

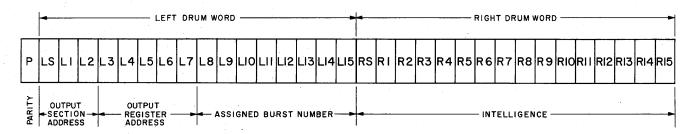

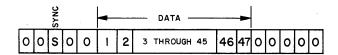

An output message as formed by the Central Computer System is composed of several words; the exact number of words used to form each message varies with the class of the message. G/A-FD, BO1, and BO2 messages contain a maximum of 13 words; a G/G message contains five words; a G/A-TD message, four words; and a TTY message, an indefinite number of words. Each drum word is composed of 32 bits and is divided into halves, the left half-word and the right half-word (fig. 1–4). The right half-word contains output data to be transmitted, and the left half-word is made up of address data and a burst number. After formation and

Figure 1-4. 33-Bit Word

prior to storing the word on the OB fields for eventual transfer to the Output System, a parity bit is added, increasing the total number of bits to 33.

#### 2.3.2 Left Half-Word

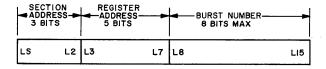

The left half-word of each word contains a 3-bit section address, a 5-bit register address, and a burst number which may contain as many as eight bits (fig. 1-5). This data is used to inform the Output System of the output storage section that is to transmit the right half-word, the storage register in the selected output storage section where the right half-word is to be stored, and the burst period during which the right half-word is to be accepted from the OB fields and transmitted by the selected storage section. The combination of the section address and register address determines the group of remote sites to which the right half-word is transmitted. In order to understand how the section and register addresses are used to accomplish this, a short discussion pertaining to the logical composition of the storage device employed in the output storage sections and to the telephone facility connections is required.

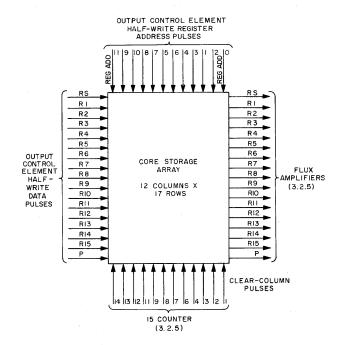

The output storage sections employ ferrite core arrays as storage devices. An array is composed of 26 core registers, each of which has the capacity to store a right half-word. An array within an output storage section is logically divided into slots, each formed by the number of registers required to accommodate the right half-words of one output message. Therefore, a slot can store one output message. Since the number of words forming an output message varies according to the output message class, the number of registers forming a slot differs in each output storage section. A G/A-FD, a BO1, or a BO2 slot is composed of 13 registers; a G/G slot, of five registers; a G/A-TD slot, of four registers; and a TTY slot, of only one register. The TTY slot requires only one register because only one word of a teletype message is transmitted during a teletype burst period.

During the formation of an output message, the remote site intended to receive this message is known as a result of the Central Computer System operations performed on air defense situation data. A binary code for a storage section is selected and assigned as a section address. This section address is assigned to each left half-word of the output message. The section address is a general address because it merely specifies the output

Figure 1-5. Left Half-Word

storage section that is to transmit the message. In order to complete the addressing of the output message, the words of the message must be addressed to those registers composing the slot in the selected output storage section array that supplies the telephone circuit connected to the intended destination of the message. Therefore, successive words in the output message are sequentially assigned the register addresses of the registers in the slot concerned.

The remaining portion of a left half-word is the burst number. The burst number that is assigned to a message indicates the burst period during which the words of the message are to be accepted by the Output System from the OB fields and then transmitted. The same burst number is assigned to each left half-word of the message (or messages, if there is more than one in a burst).

#### 2.3.3 Right Half-Word

The right half-word of each output message word is formed by the Central Computer System, using only a part of the data composing a complete output message. The remaining output message data is used to form the right halves of the other words in the message. The G/A-FD messages contain a maximum of 13 right half-words which are used by the Central to carry required data to manned airborne interceptors. A right half-word in a G/A-FD message contains interceptor address bits RS through R3, message label bits R4 through R7, and actual data bits R8 through R15. The message label of each right half-word of a G/A-FD message identifies the data contained therein.

The G/A-FD messages are transferred from the Central through telephone data circuits to G/A-FD datalink transmitter sites. A G/A-FD data-link receiver at the site receives the messages from one telephone data circuit and provides radio communication to many airborne interceptors. Each of the right half-words in a G/A-FD message is used by the G/A-FD data link transmitter to modulate one of 13 subcarrier frequencies. In this manner, separate subcarriers are modulated by a different right half-word of the G/A-FD message; that is, right half-word 1 modulates the first subcarrier, right half-word 2 modulates the next subcarrier, etc.

BOMARC messages contain a maximum of 13 right half-words which are used by the Central to carry required data to unmanned interceptors (missiles). A right half-word in a BOMARC message contains missile address bits RS through R2, message label bits R3 through R6, and command data bits R7 through R14. The BOMARC messages are handled in the manner described for G/A-FD messages.

A G/G message contains five right-half drum words (a total of 80 bits) employed by the Central to carry

2.3.3

either XTL information to an adjacent Central, forwardtelling data to an AN/FSQ-8 Combat Control Central, or a height-finder request to a radar site. The data used to form a G/G XTL or forwardtelling message can be varied by the air defense program in the Central Computer System. Therefore, the amount of XTL or forwardtelling data used to form each right half-word of a G/G message is not fixed.

Each right half-word of a typical XTL or forward-telling message is formed by the Central Computer System. The last (third) type of G/G message is employed to carry height-finder requests to radar sites.

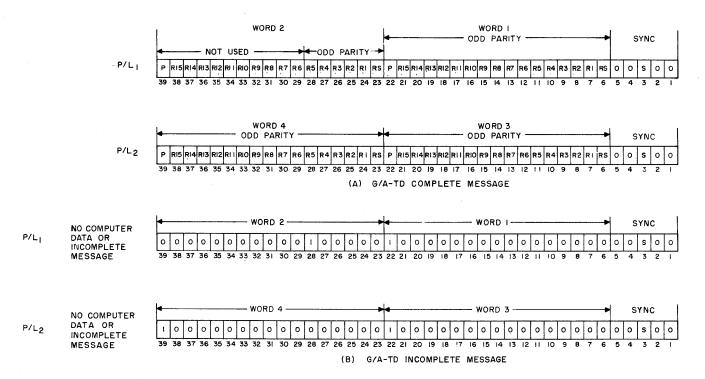

A G/A-TD message is composed of four right halfwords that are separated into groups of two right halfwords and transmitted over separate telephone channels to manned interceptors via data-link transmitters. Two data phone lines are used to transmit the G/A-TD message to the manned interceptor. One data phone line handles information relating to site address, aircraft address, and the message label, whereas the command data associated with the G/A-TD message is transmitted over the other data phone line. One G/A-TD message contains four commands. The G/A-TD messages are sent from the Central via data-link transmitters that are located within a given area, with each transmitter operating on the same assigned frequency. Selection of a particular data-link transmitter is established by the site address portion of the G/A-TD message. If a G/A-TD message is addressed to a particular aircraft in a group of aircraft, only that aircraft will take action on the transmitted message.

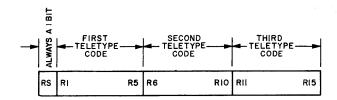

A TTY message is employed by the Central to carry information to remote sites not equipped with automatic input devices through telephone TTY circuits. Each right half-word of a TTY message contains the binary equivalent of three TTY code symbols. A TTY code symbol represents either a letter, a figure, or a TTY operation. Table 1-1 shows the TTY letter, figure, or operation associated with a 5-bit binary code symbol. As shown in table 1-1, a binary code may represent either a letter or a figure. Because of this, a code symbol representing either of the TTY operations, entitled letters or figures, must be transmitted prior to the group of letter or figure codes. The three 5-bit code symbols employed to form a right half-word of a TTY message depend upon the data to be transmitted. The 15 bits of the three 5-bit code symbols occupy bit positions R1 through R15 of a TTY right drum word. Bit RS is always a 1 (fig. 1-6). The TTY transmission procedure is described in greater detail in Part 3, Chapter 5.

TABLE 1-1. TELETYPE CODE

| CHARACTERS |          |              |

|------------|----------|--------------|

| LETTERS    | FIGURES  | CODE SIGNALS |

| A          | _        | 00111        |

| В          | ?        | 01100        |

| C          | :        | 10001        |

| D          | \$       | 01101        |

| E          | 3        | 01111        |

| F          | !        | 01001        |

| G          | &        | 10100        |

| H          | #        | 11010        |

| I          | 8        | 10011        |

| J          | ,        | 00101        |

| K          | (        | 00001        |

| L          | )        | 10110        |

| M          | •        | 11000        |

| N          | ,        | 11001        |

| О          | 9 '      | 11100        |

| P          | 0        | 10010        |

| Q          | 1        | 00010        |

| R          | 4        | 10101        |

| S          | Bell     | 01011        |

| T          | 5        | 11110        |

| U          | 7        | 00011        |

| V          | ;        | 10000        |

| W          | 2        | 00110        |

| X          | / /      | 01000        |

| Y          | 6        | 01010        |

| Z          | "        | 01110        |

| Sp         | ace      | 11011        |

| Carriag    | e return | 11101        |

| _          | feed     | 10111        |

| Fig        | ures     | 00100        |

| _          | ters     | 00000        |

| Blank      |          | 11111        |

#### 2.3.4 Parity Bit

A parity bit is added to the drum word to cause the sum of the 1's in a word to be odd if odd parity is desired and to be even if even parity is desired.

A parity check for the correctness of the drum word is accomplished by counting the number of 1 bits of the drum word which are stored in the OB register and affecting odd parity.

In the Central Computer System, after the left and right halves of a word are formed, a count is made of the 1 bits in the word. When an odd total is discovered, a 0 parity bit is assigned; however, should an even total result, a 1 parity bit is added. In both cases, the total number of 1 bits in the word plus the parity bit is odd. Therefore, the number of 1 bits in a word, together with its parity bit, when placed on the OB fields, should always be odd. The 32-bit word plus the

parity bit is referred to as a 33-bit drum word. When the Output System reads a drum word from the OB fields, it performs a parity count during which the 1 bits in the drum word are added. If the result is an odd total, the drum word is assumed to contain no errors, but if an even total results, the drum word contains an error and is effectively destroyed by the Output System.

Figure 1-6. Teletype Right Half-Word

#### **CHAPTER 3**

#### **DRUM STORAGE**

#### 3.1 GENERAL

There are three OB fields on the LOG drum in the Drum System upon which drum words are stored by the Central Computer System for eventual transfer to the Output System. These OB fields are used consecutively and therefore may be thought of as one triple-size drum field. One restriction upon this concept is the fact that a continued reading from, and writing onto, these fields is interrupted because a delay of 120 usec is introduced when switching from one field to the next. These OB fields are divided into 6,144 drum-word registers (2,048 per field); however, only 2,036 registers per field are used to store drum words because 120 µsec are required at the beginning of each field to allow for switching fields. Thus, 12 drum registers per field have no usable information in them (dead registers); consequently, only 2,036 drum-word registers are used. The drum rotation is such that successive registers are spaced 10 usec apart.

The drum words of an output message are written onto the OB fields at the maximum rate of 50,000 drum words per second. They remain on the OB fields until the arrival of the burst period, during which the output message is intended for transmittal by the Output System. At the start of this burst period, the drum words of the output message are accepted by the Output System from the OB fields at the maximum rate of 100,000 drum words per second, but not for the same section.

In addition to transferring drum words stored on the OB fields to the Output System, the Drum System supplies the Output System with OD LOG drum timing pulses. The Output System utilizes these timing pulses to synchronize its operations with those of the Drum System.

#### 3.2 OB FIELDS WRITING

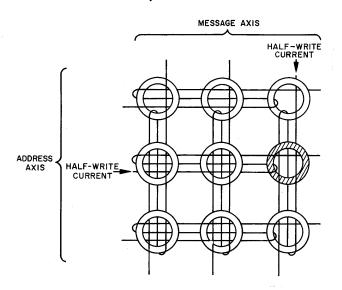

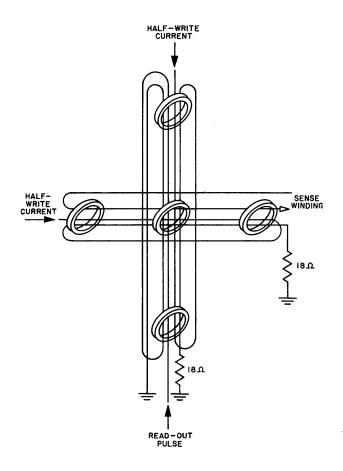

The drum words of an output message are written on either all odd or all even drum-word registers of the OB fields, as specified by the Central Computer System. Since there is a 10-µsec interval between successive registers, the minimum interval between the writing of successive drum words of an output message onto the OB fields is 20 µsec; i.e., writing cannot occur at a rate greater than 50,000 drum words per second. The drum words of the same output message are intended for a specific storage section of the Output System,

which receives them at the same rate at which they are written onto the OB fields. The maximum rate at which information can be placed in a ferrite core array employed by an output storage section is 50,000 pulses per second (pps). Thus, limiting the writing of successive drum words onto only odd or even drum registers ensures that the rate at which the drum words of a message are transferred to a particular core array never exceeds 50,000 drum words per second.

Successive drum words of one message are not necessarily written onto these drum fields in successive odd or even registers. Instead, each drum word is written onto the first odd or even drum-word register that is made available to the drum word.

A drum-word register is considered to be available if its contents have been accepted by the Output System; it is considered unavailable when it stores a drum word that has not yet been accepted by the Output System. Thus, when a drum word is accepted by the Output System, the status of its associated drum-word register is changed to indicate an available register. In like manner, the status of a register is changed to unavailable when a drum word is written onto the register. No separate erasing procedure is performed when a drum word is accepted by the Output System because the action of writing a new drum word onto an available register effectively erases the old drum word as part of the write-in process.

Frequently, each successive drum word must wait for a register to become available; consequently, successive drum words are often placed on the OB fields several drum-word registers apart. Therefore, the interval between the writing of successive drum words of the same message may be greater than 20 µsec (but the interval is always a multiple of 20 µsec).

#### 3.3 OB FIELDS READING

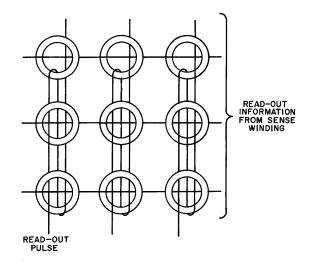

The contents of the drum-word registers on the OB fields are read consecutively and transferred to the Output System. Since there is a 10-usec interval between drum-word registers, the drum words cannot be read at a rate greater than 100,000 drum words per second. Each drum word received by the Output System is examined and either accepted, rejected for being in error, or rejected for arriving too soon. The statuses of the registers associated with the drum words that are either accepted or rejected for being in error are changed to

"available." The drum words that are rejected for arriving too soon remain on the OB fields. These rejected drum words contain good information and will be accepted at a later time. Consequently, the statuses of the registers containing the rejected drum words remain unchanged to prevent the writing of new drum words over still useful information.

#### 3.4 LOG DRUM OD TIMING PULSES

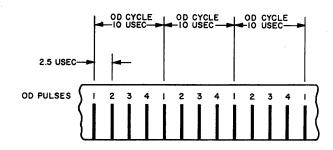

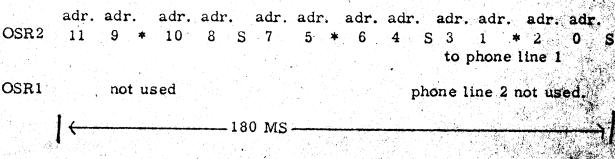

The LOG drum OD timing pulses are used to synchronize the transfer operations of the Drum System with the processing operations of the Output System. There are four OD timing pulses, designated OD 1, OD 2, OD 3, and OD 4. These pulses occur in sequence from OD 1 through OD 4 with a spacing of 2.5 usec between successive pulses. Therefore, an OD cycle,

which is the interval between an OD 1 pulse and a following OD 1 pulse, is 10 µsec. The OD pulses are generated continuously, with every OD 4 pulse followed 2.5 µsec later by an OD 1 pulse (fig. 1-7).

Figure 1-7. OD Cycle, Timing Chart

#### **CHAPTER 4**

#### **OUTPUT SYSTEM, BLOCK DIAGRAM ANALYSIS**

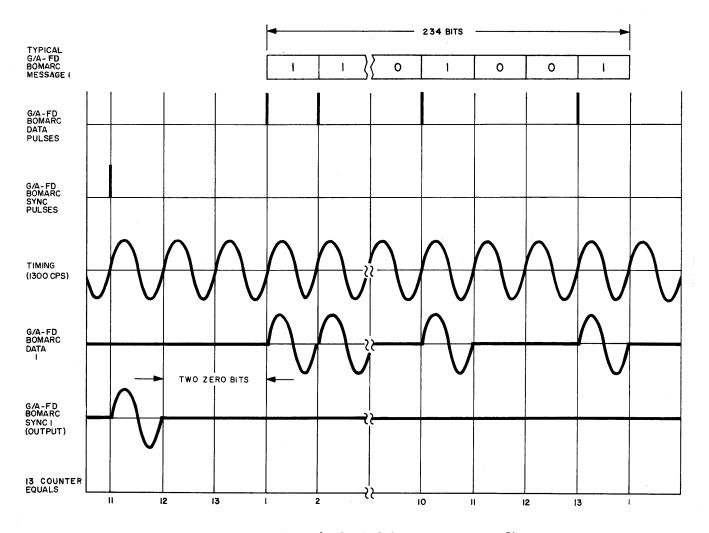

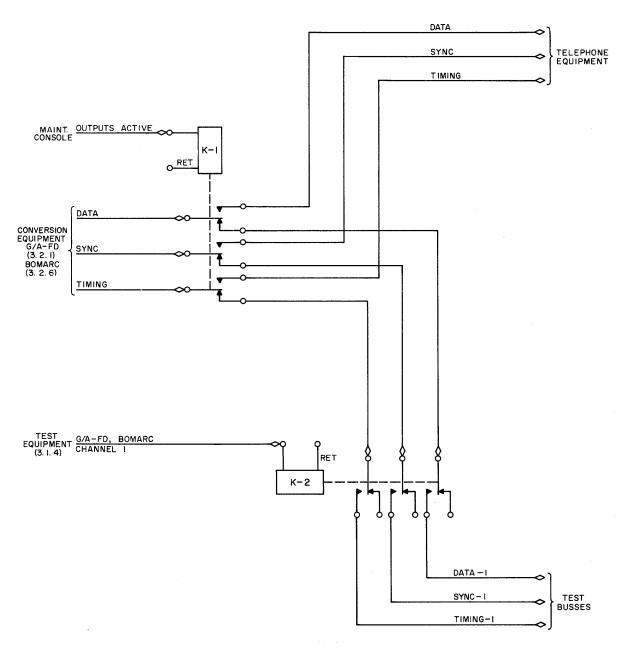

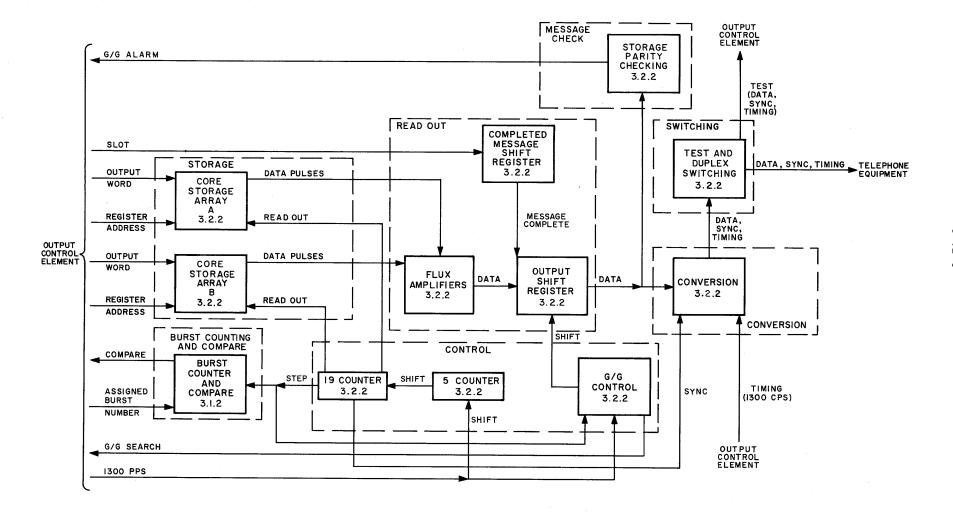

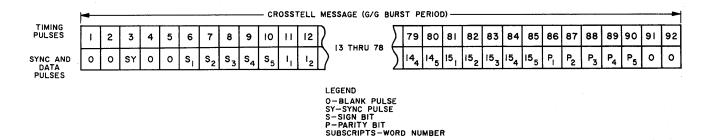

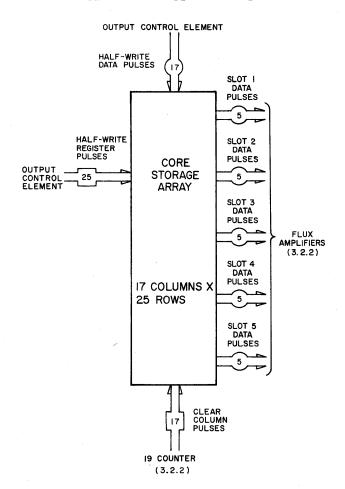

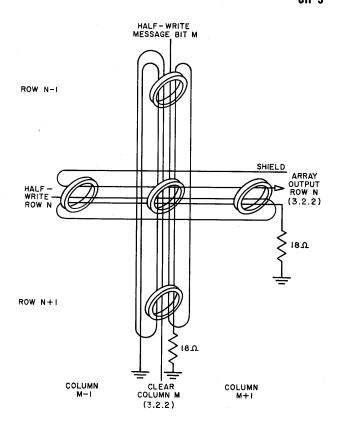

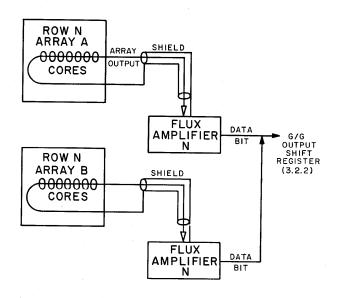

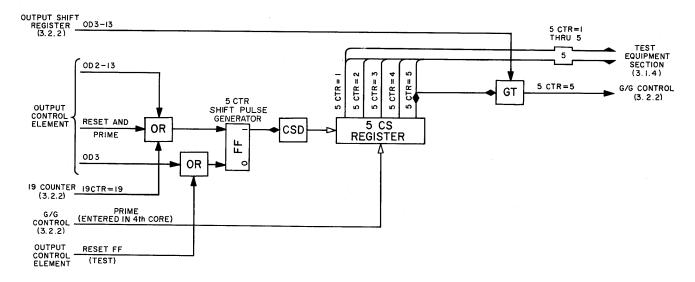

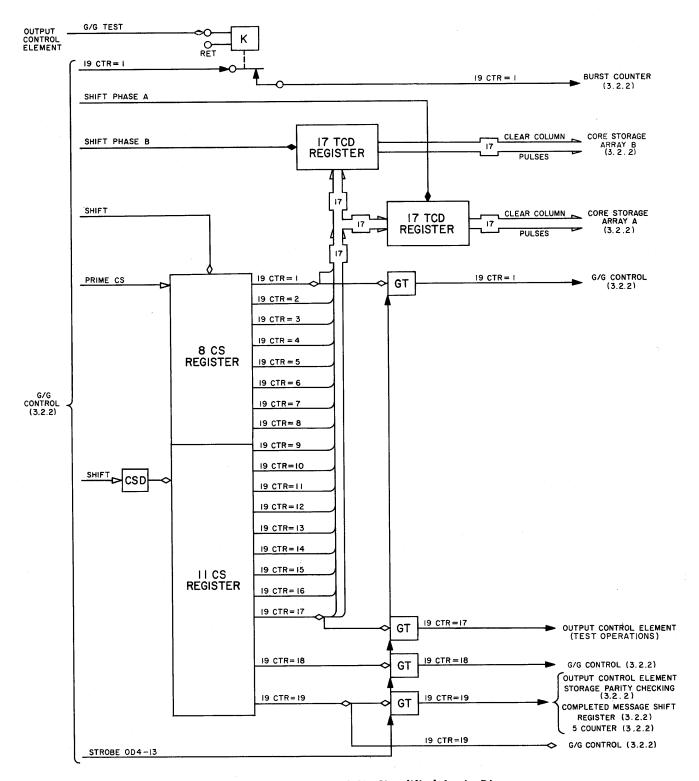

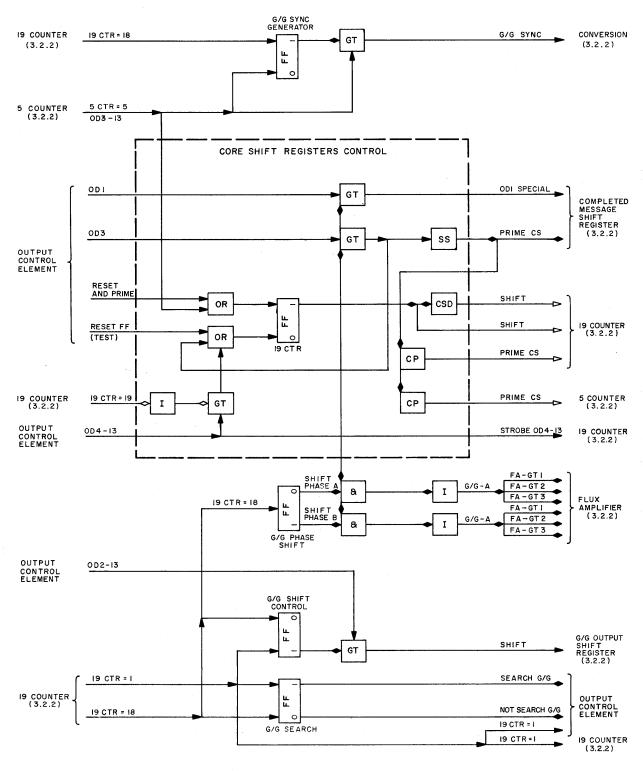

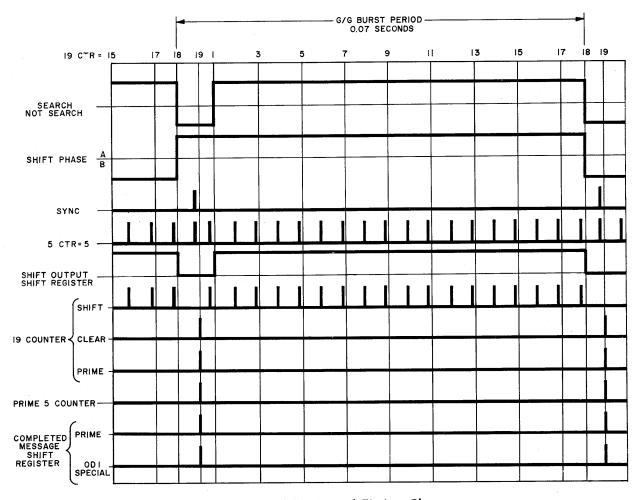

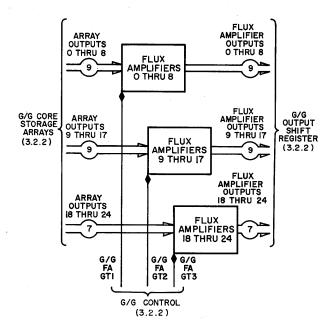

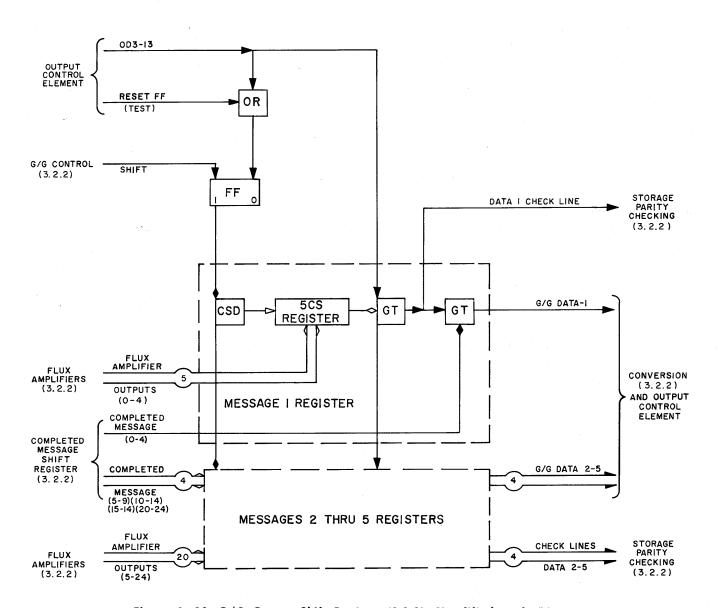

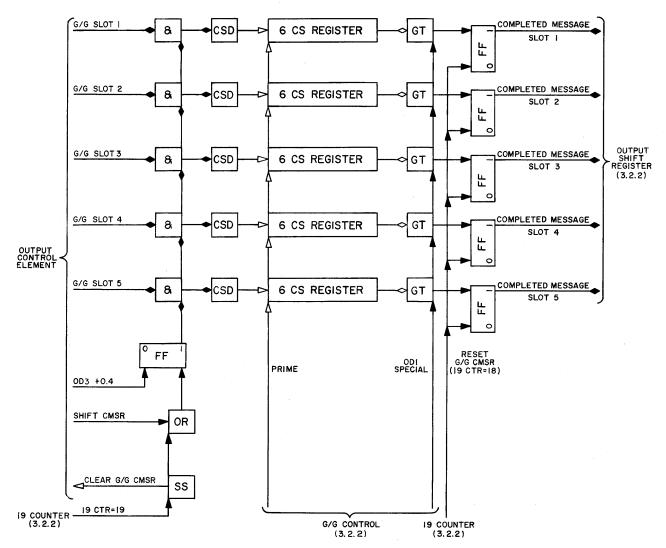

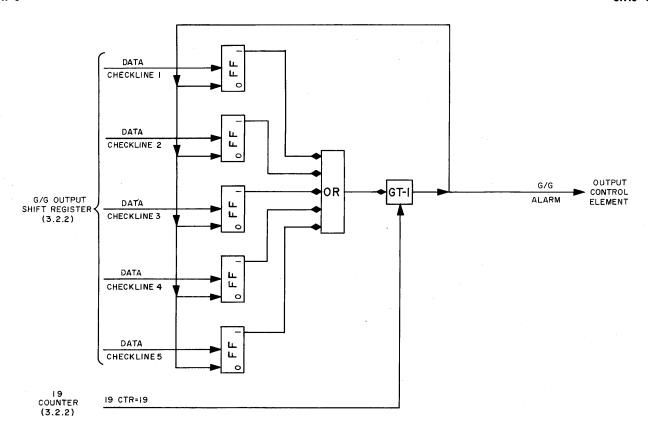

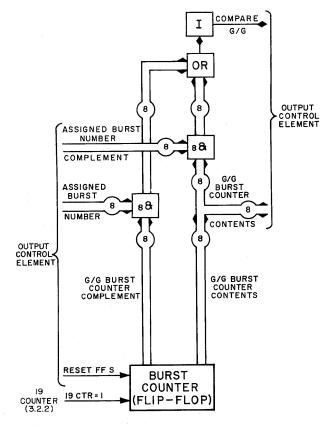

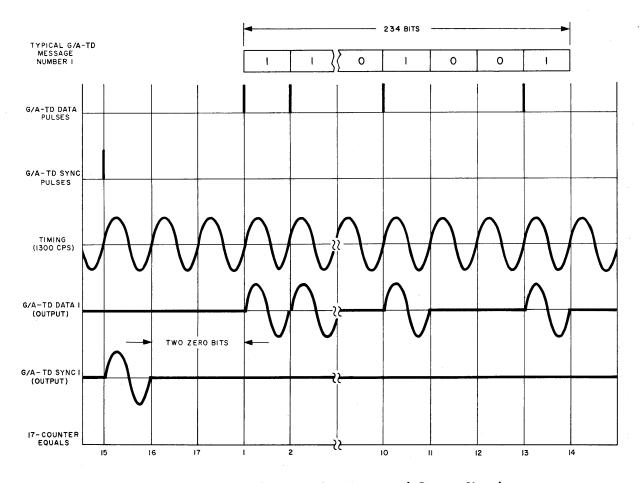

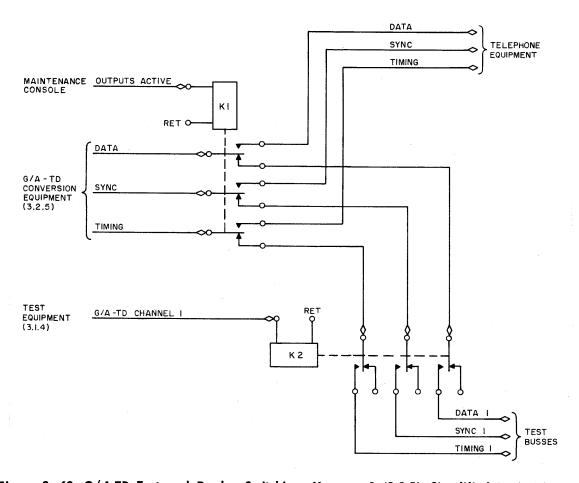

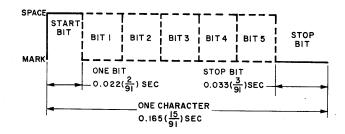

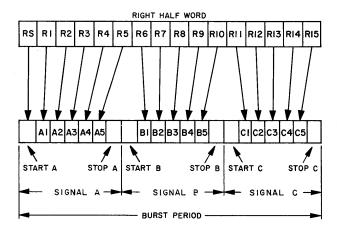

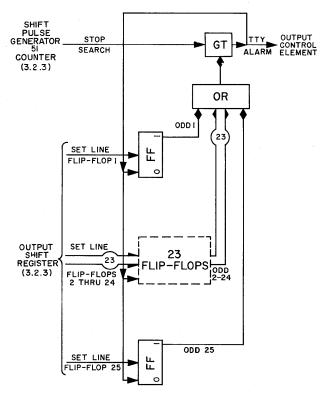

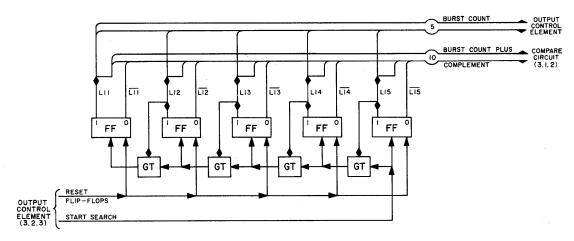

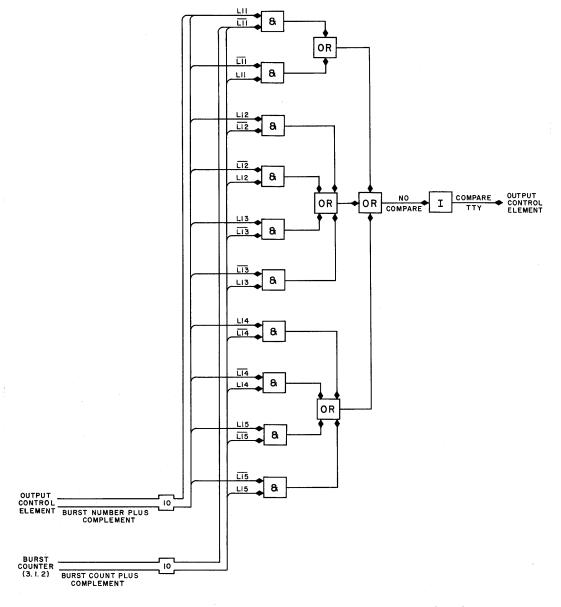

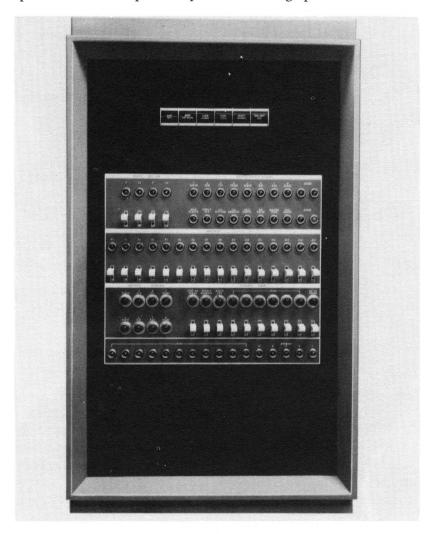

#### 4.1 GENERAL