Series/1 Model 5

4955 Processor

and Processor Features

Description

# First Edition (November 1976)

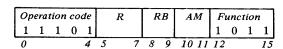

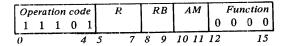

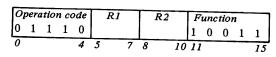

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

Text for this manual has been prepared with the IBM Magnetic Tape Selectric® Composer.

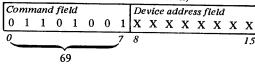

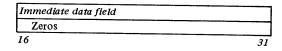

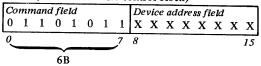

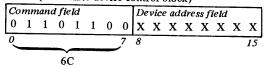

Some illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.

Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, send your comments to IBM Corporation, Systems Publications, Department 27T, P. O. Box 1328, Boca Raton, Florida 33432. Comments become the property of IBM.

©Copyright International Business Machines Corporation 1976

# Contents

| Preface ix                                                      |                                                                               |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------|

| Summary of Publication ix                                       | Processor Status Word 3-5                                                     |

| Related Publications x                                          | Program Check Conditions 3-5                                                  |

| A A A A A A A A A A A A A A A A A A A                           | Program Check or Soft Exception Trap Condition 3-5                            |

| Chapter 1. Introduction 1-1                                     | Soft Exception Trap Condition 3-5                                             |

| IBM 4955 Processor 1-1                                          | Machine Check Conditions 3-6                                                  |

| D 0 11 1 m                                                      | Status Flags 3-6                                                              |

| Processor Optional Features 1-1 Processor Description 1-1       | Power/Thermal Warning Condition 3-6                                           |

| T                                                               | Class Interrupts 3-6                                                          |

| Communications Features 1-4                                     | Priority of Class Interrupts 3-7                                              |

|                                                                 | Execution of Class Interrupts 3-7                                             |

| Sensor Input/Output Options 1-5 Packaging and Power Options 1-5 | Recovery from Error Conditions 3-9                                            |

| Other Options 1-5                                               | Program Check 3-10                                                            |

| other Options 1-5                                               | Storage Parity Check 3-10                                                     |

| Chapter 2. Processing Unit Description 2-1                      | CPU Control Check 3-10                                                        |

| Main Storage 2-1                                                | I/O Check 3-10                                                                |

| Addressing Main Storage 2-1                                     | Soft Exception Trap 3-10                                                      |

| Registers 2-3                                                   | Program Controlled Level Switching 3-10                                       |

| Console Address Key Register 2-3                                | Selected Level Lower Than Current Level and In-process                        |

| Console Data Buffer 2-3                                         | Flag On 3-11                                                                  |

| Current-Instruction Address Register (CIAR) 2-3                 | Selected Level Equal to Current Level and In-process                          |

| Mask Register 2-3                                               | Flag On 3-11                                                                  |

| Processor Status Word (PSW) 2-4                                 | Selected Level Higher Than Current Level and In-process                       |

| Storage Address Register (SAR) 2-4                              | Flag On 3-12                                                                  |

| Address Key Register (AKR) 2-4                                  | Selected Level Lower Than Current Level and In-process                        |

| General Registers 2-4                                           | Flag Off 3-12                                                                 |

| Instruction Address Register (IAR) 2-4                          | Selected Level Equal to Current Level and In-process                          |

| Level Status Register (LSR) 2-5                                 | Flag Off 3-12                                                                 |

| Arithmetic and Logic Unit (ALU) 2-5                             | Selected Level Higher Than Current Level and In-process                       |

| Numbering Representation 2-5                                    | Flag Off 3-13                                                                 |

| Indicators 2-7                                                  | Interrupt Masking Facilities 3-13                                             |

| Even, Negative, and Zero Result Indicators 2-8                  | Summary Mask 3-13                                                             |

| Even, Carry, and Overflow Indicators—Condition                  | Interrupt Level Mask Register 3-14                                            |

| Code for Input/Output Operations 2-8                            | Device Mask (1-bit) 3-14                                                      |

| Carry and Overflow Indicators—Add and Subtract                  | Chamber 4 C                                                                   |

| Operations 2-8                                                  | Chapter 4. Console 4-1                                                        |

| Carry and Overflow Indicator - Shift Operations 2-13            | Basic Console 4-2                                                             |

| Testing Indicators with Conditional Branch and Jump             | Keys and Switches 4-2                                                         |

| Instructions 2-13                                               | Indicators 4-2                                                                |

| Indicators Affected by Compare Operations 2-14                  | Programmer Console 4-2                                                        |

| Indicators—Multiple Word Operands 2-14                          | Console Display 4-3                                                           |

| Program Execution 2-15                                          | Indicators 4-4                                                                |

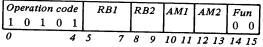

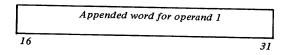

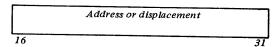

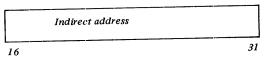

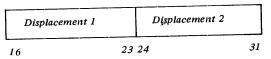

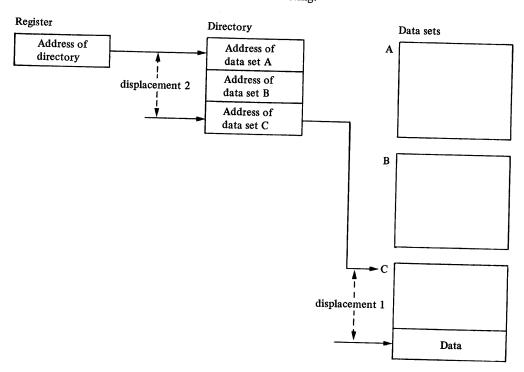

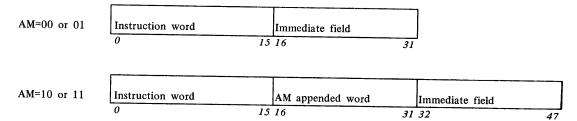

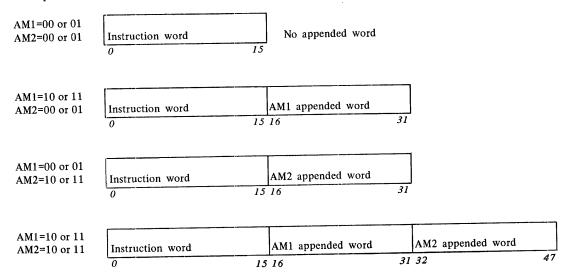

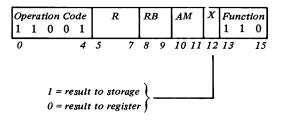

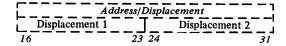

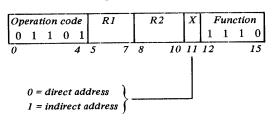

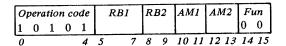

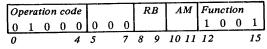

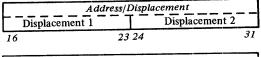

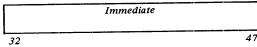

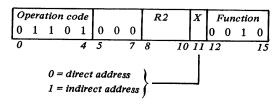

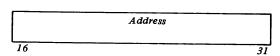

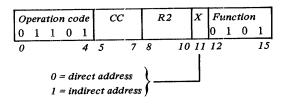

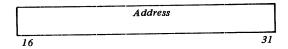

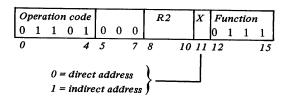

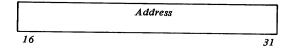

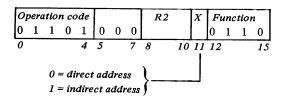

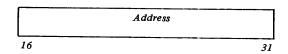

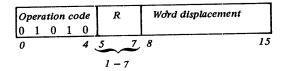

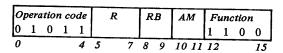

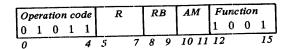

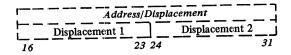

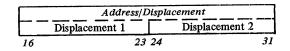

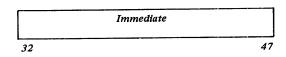

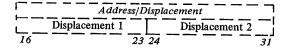

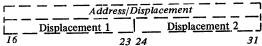

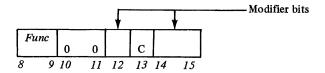

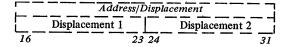

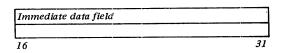

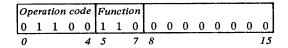

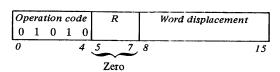

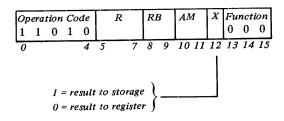

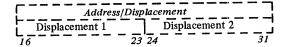

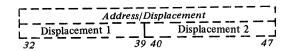

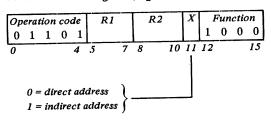

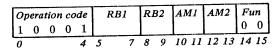

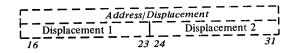

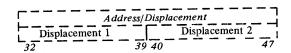

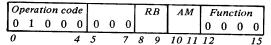

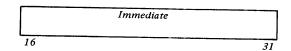

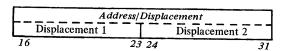

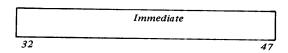

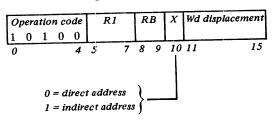

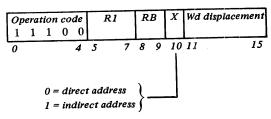

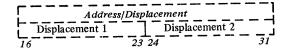

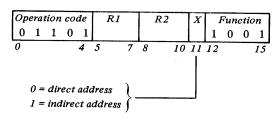

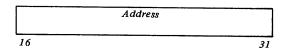

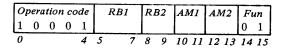

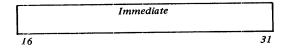

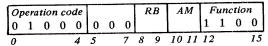

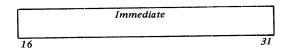

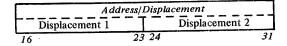

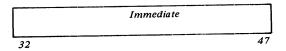

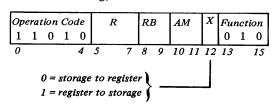

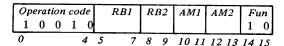

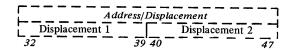

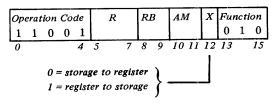

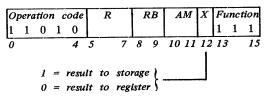

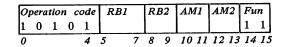

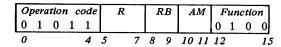

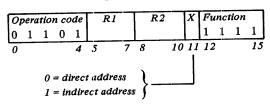

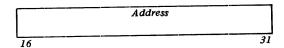

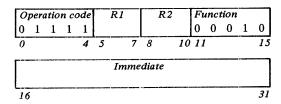

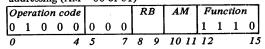

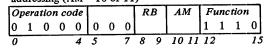

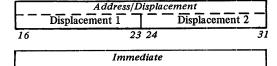

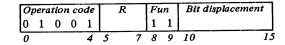

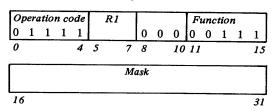

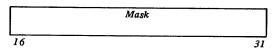

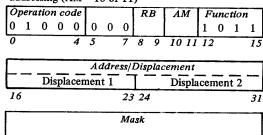

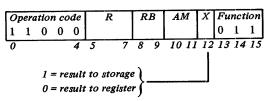

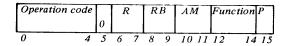

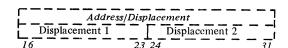

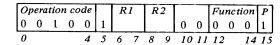

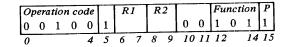

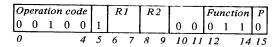

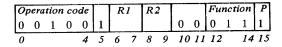

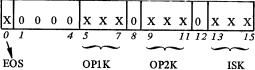

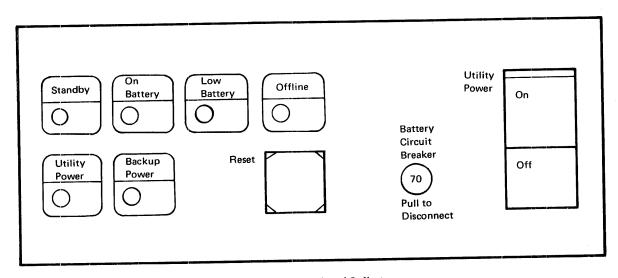

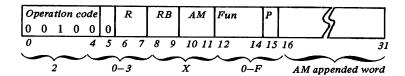

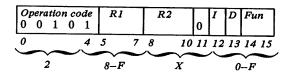

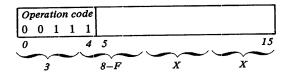

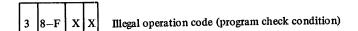

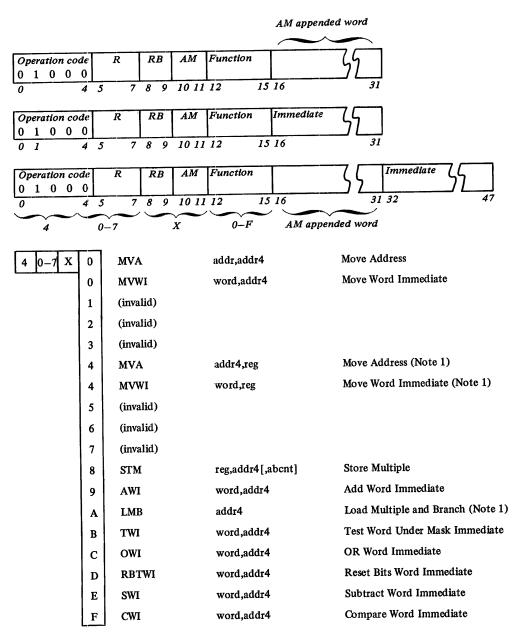

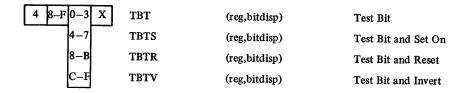

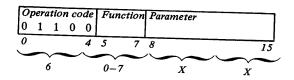

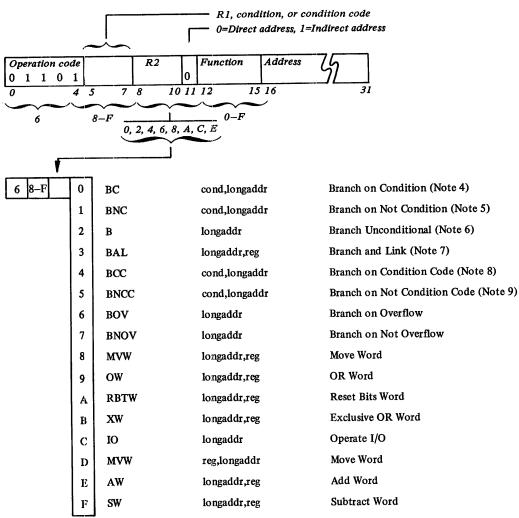

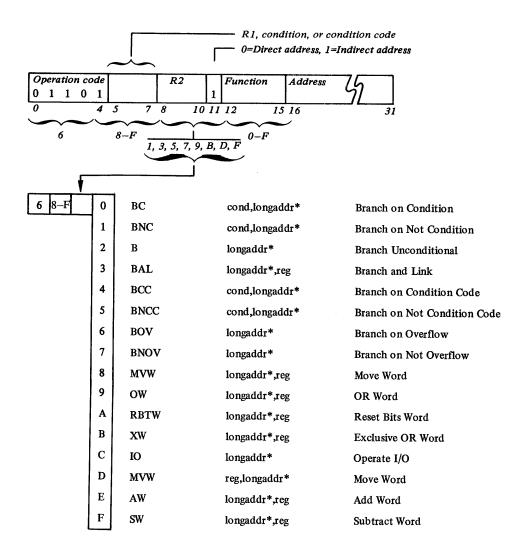

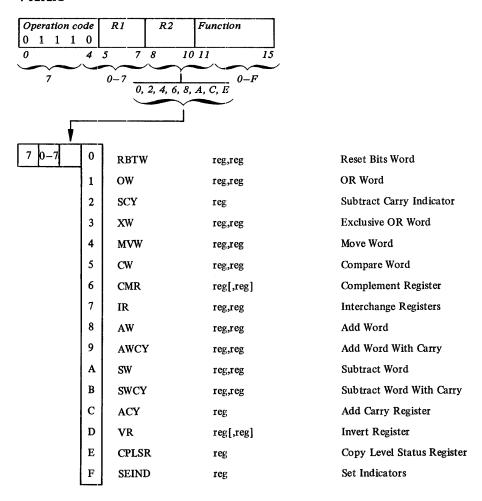

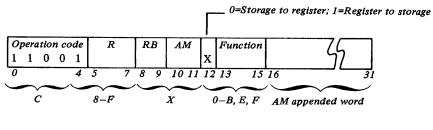

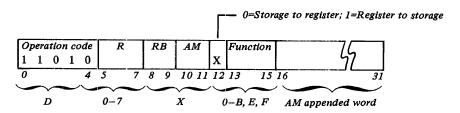

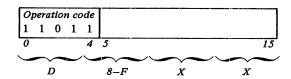

| Instruction Formats 2-15                                        | Combination Keys/Indicators 4-5                                               |

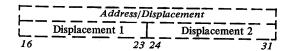

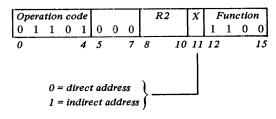

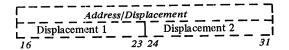

| Effective Address Generation 2-17                               | Keys and Switches 4-7                                                         |

| Processor State Control 2-24                                    | Displaying Main Storage Locations 4-10                                        |

| Initial Program Load (IPL) 2-26                                 | Storing Into Main Storage 4-10                                                |

| Sequential Instruction Execution 2-27                           | Displaying Registers 4-11 Storing Into Registers 4-11                         |

| Jumping and Branching 2-27                                      | Storing Into Registers 4-11                                                   |

| Level Switching and Interrupts 2-27                             | Chapter 5. Instructions 5-1                                                   |

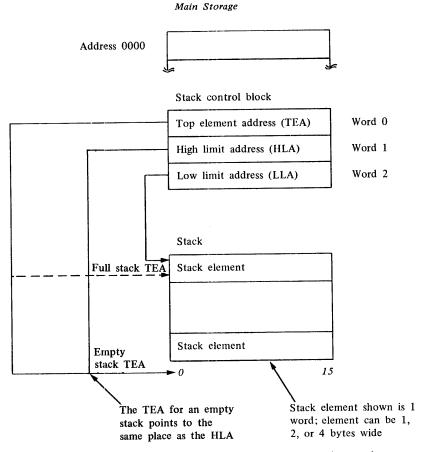

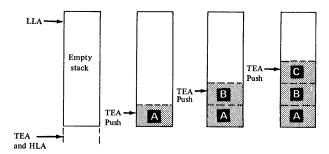

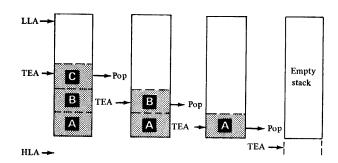

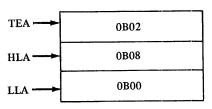

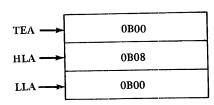

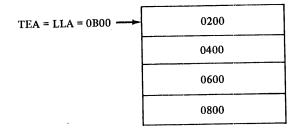

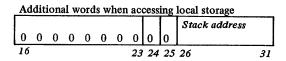

| Stack Operations 2-28                                           | Exception Conditions 5-1                                                      |

|                                                                 | D                                                                             |

| Chapter 3. Interrupts and Level Switching 3-1                   | C. C. T                                                                       |

| Introduction 3-1                                                | Soft Exception Trap Conditions 5-1 Instruction Termination or Suppression 5-2 |

| Interrupt Scheme 3-1                                            |                                                                               |

| Automatic Interrupt Branching 3-2                               | Instruction Descriptions 5-2                                                  |

| I/O Interrupts 3-3                                              | Add Byte (AB) 5-2                                                             |

| Prepare I/O Device for Interrupt 3-3                            | Add Grant Product (ASI) 5-3                                                   |

| Present and Accent Interrupt 2.2                                | Add Carry Register (ACY) 5-3                                                  |

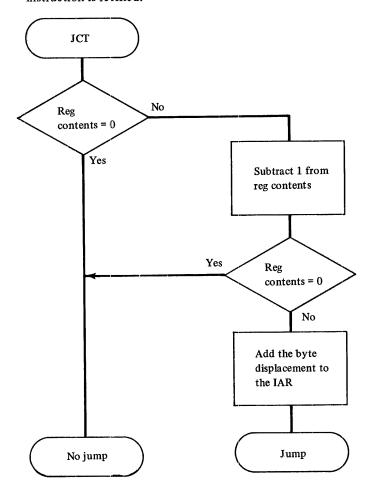

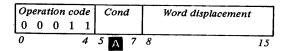

| Add Doubleword (AD) 5-4                                                           | Jump On Count (JCT) 5-42                  |

|-----------------------------------------------------------------------------------|-------------------------------------------|

| Register/Storage Format 5-4                                                       | Jump On Not Condition (JNC) 5-43          |

| Storage/Storage Format 5-4                                                        | Level Exit (LEX) 5-44                     |

| Add Word (AW) 5-5                                                                 | Load Multiple and Branch (LMB) 5-44       |

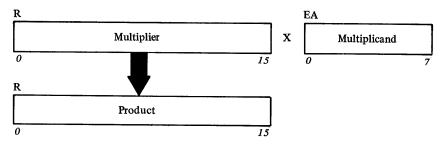

| Register/Register Format 5-5                                                      | Multiply Byte (MB) 5-45                   |

| Register/Register Format 5-5 Register/Storage Format 5-5                          | Multiply Doubleword (MD) 5-46             |

| Storage to Register Long Format 5-6                                               | Move Address (MVA) 5-47                   |

| Storage to Register Long Pormat 5-6                                               | Storage Address to Register Format 5-47   |

| Dtoruge over-the                                                                  | Storage Immediate Format 5-47             |

| Add Wold With Cally (                                                             | Move Byte (MVB) 5-48                      |

| Add Word Immediate (Fig. 1)                                                       | Register/Storage Format 5-48              |

| Register Intinediate Zerig                                                        | Storage/Storage Format 5-48               |

| Storage Immediate Format 5-8                                                      | Move Byte Immediate (MVBI) 5-49           |

| Branch Unconditional (B) 5-9                                                      | Move Byte and Zero (MVBZ) 5-49            |

| Branch and Link (BAL) 5-10                                                        | Move Doubleword (MVD) 5-50                |

| Branch and Link Short (BALS) 5-10                                                 | Register/Storage Format 5-50              |

| Branch On Condition (BC) 5-11                                                     | Storage/Storage Format 5-50               |

| Branch On Condition Code (BCC) 5-12                                               | Move Doubleword and Zero (MVDZ) 5-51      |

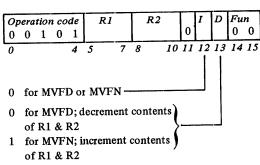

| Branch On Not Condition (BNC) 5-13                                                | Move Byte Field and Decrement (MVFD) 5-52 |

| Branch On Not Condition Code (BNCC) 5-14                                          | Move Byte Field and Increment (MVFN) 5-52 |

| Branch On Not Overflow (BNOV) 5-15                                                | Move Word (MVW) 5-53                      |

| Branch On Overflow (BOV) 5-15                                                     | Register/Register Format 5-53             |

| Branch Indexed Short (BXS) 5-16                                                   | Register/Storage Format 5-53              |

| Compare Byte (CB) 5-17                                                            | Register to Storage Long Format 5-53      |

| Register/Storage Format 5-17                                                      | Storage to Register Long Format 5-54      |

| Storage/Storage Format 5-17                                                       | Storage/Storage Format 5-54               |

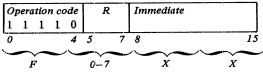

| Compare Byte Immediate (CBI) 5-18                                                 | Move Word Immediate (MVWI) 5-55           |

| Compare Doubleword (CD) 5-19                                                      | Storage to Register Format 5-55           |

| Register/Storage Format 5-19                                                      | Storage Immediate Format 5-55             |

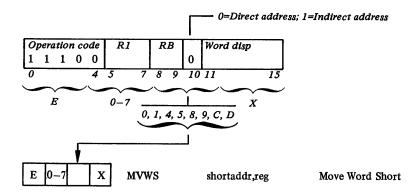

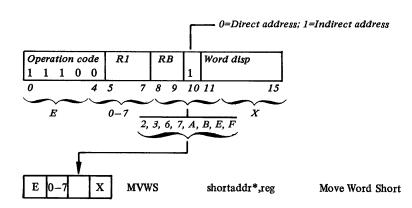

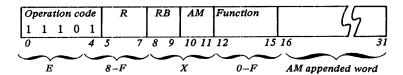

| Storage/Storage Format 5-19                                                       | Move Word Short (MVWS) 5-56               |

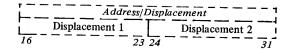

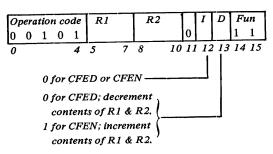

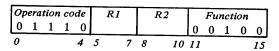

| Compare Byte Field Equal and Decrement (CFED) 5-20                                | Register to Storage Format 5-56           |

| Compare Byte Field Equal and Increment (CFEN) 5-20                                | Storage to Register Format 5-56           |

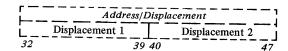

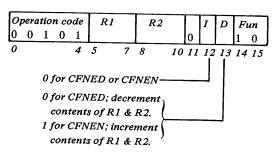

| Compare Byte Field Not Equal and Decrement (CFNED) 5-21                           | Move Word and Zero (MVWZ) 5-57            |

| Compare Byte Field Not Equal and Increment (CFNEN) 5-21                           | Multiply Word (MW) 5-58                   |

| Complement Register (CMR) 5-22                                                    | No Operation (NOP) 5-59                   |

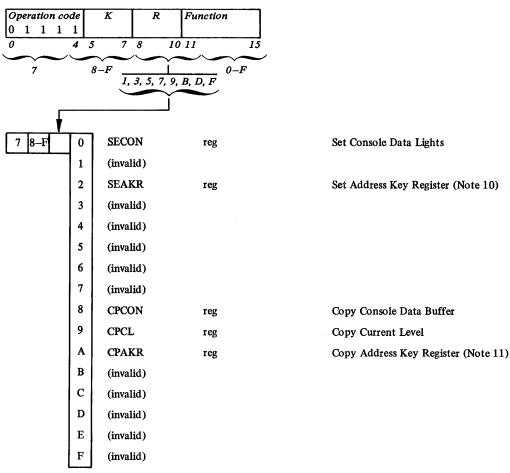

| Copy Address Key Register (CPAKR) 5-23                                            | AND Word Immediate (NWI) 5-59             |

| System Register/Storage Format 5-23                                               | OR Byte (OB) 5-60                         |

| System Register/Register Format 5-23                                              | Register/Storage Format 5-60              |

| Copy Current Level (CPCL) 5-24                                                    | Storage/Storage Format 5-60               |

| Copy Console Data Buffer (CPCON) 5-24                                             | OR Doubleword (OD) 5-61                   |

| Copy Interrupt Mask Register (CPIMR) 5-25                                         | Register/Storage Format 5-61              |

| Copy In-process Flags (CPIPF) 5-25                                                | Storage/Storage Format 5-61               |

| Copy Level Block (CPLB) 5-26                                                      | OR Word (OW) 5-62                         |

| Copy Level Status Register (CPLSR) 5-26                                           | Register/Register Format 5-62             |

| Copy Processor Status and Reset (CPPSR) 5-27                                      | Register/Storage Format 5-62              |

| Copy Storage Key (CPSK) 5-27                                                      | Storage to Register Long Format 5-63      |

| Copy Segmentation Register (CPSR) 5-28                                            | Storage/Storage Format 5-63               |

| Compare Word (CW) 5-29                                                            | OR Word Immediate (OWI) 5-64              |

| Register/Register Format 5-29                                                     | Register Immediate Format 5-64            |

| Register/Storage Format 5-29                                                      | Storage Immediate Format 5-64             |

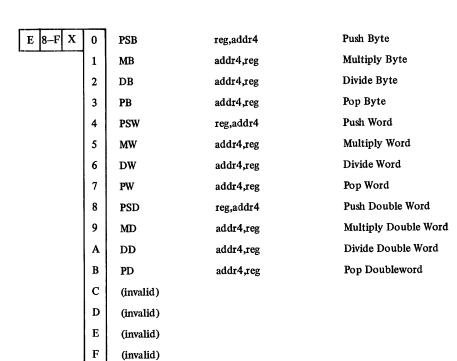

| Storage/Storage Format 5-29                                                       | Pop Byte (PB) 5-65                        |

| Compare Word Immediate (CWI) 5-30                                                 | Pop Doubleword (PD) 5-65                  |

| Register Immediate Long Format 5-30                                               | Push Byte (PSB) 5-66                      |

| Storage Immediate Format 5-30                                                     | Push Doubleword (PSD) 5-66                |

| Divide Byte (DB) 5-31                                                             | Push Word (PSW) 5-67                      |

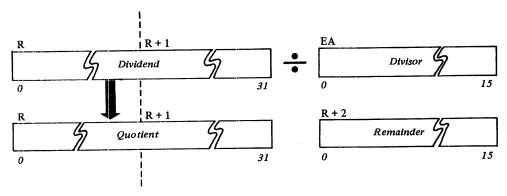

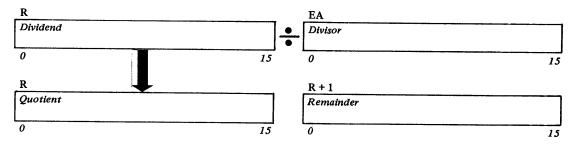

| Divide Doubleword (DD) 5-32                                                       | Pop Word (PW) 5-67                        |

| Diagnose (DIAG) 5-33                                                              | Reset Bits Byte (RBTB) 5-68               |

| Disable (DIS) 5-34                                                                | Register/Storage Format 5-68              |

| Divide Word (DW) 5-35                                                             | Storage/Storage 5-68                      |

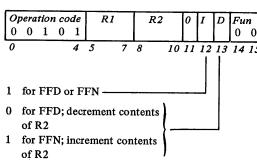

| Enable (EN) 5-36  Fill Byte Field and Decrement (FFD) 5-37                        | Reset Bits Doubleword (RBTD) 5-69         |

| Fill Byte Field and Decrement (FFD) 5-37 Fill Byte Field and Increment (FFN) 5-37 | Register/Storage Format 5-69              |

|                                                                                   | Storage/Storage Format 5-69               |

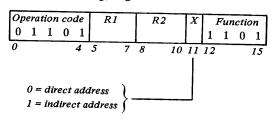

| Operate I/O (IO) 5-38 Interchange Operand Keys (IOPK) 5-38                        | Reset Bits Word (RBTW) 5-70               |

| Interchange Registers (IR) 5-39                                                   | Register/Register Format 5-70             |

| Jump Unconditional (J) 5-39                                                       | Register/Storage Format 5-70              |

| Jump and Link (JAL) 5-40                                                          | Storage to Register Long Format 5-71      |

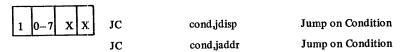

| Jump On Condition (JC) 5-41                                                       | Storage/Storage Format 5-71               |

| Reset Bits Word Immediate (RBTWI) 5-72               | <b>—</b>                                      |

|------------------------------------------------------|-----------------------------------------------|

| Register Immediate Long Format 5-72                  | Exclusive OR Byte (XB) 5-102                  |

| Storage Immediate Format 5-72                        | Exclusive OR Doubleword (XD) 5-103            |

| Subtract Byte (SB) 5-73                              | Exclusive OR Word (XW) 5-104                  |

| Subtract Carry Indicator (SCY) 5-73                  | Register/Register Format 5-104                |

| Subtract Doubleword (SD) 5-74                        | Register/Storage Format 5-104                 |

| Register/Storage Format 5-74                         | Storage to Register Long Format 5-105         |

| Storage/Storage Format 5-74                          | Exclusive OR Word Immediate (XWI) 5-105       |

| Set Address Key Register (SEAKR) 5-75                |                                               |

| System Register/Storage Format 5-75                  | Chapter 6. Floating-Point Feature 6-1         |

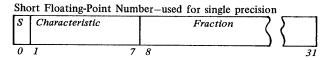

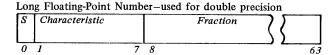

| System Register/Register Format 5-75                 | Data Format 6-1                               |

| Set Console Data Lights (SECON) 5-76                 | Number Representation 6-1                     |

| Cat Internal 186 1 B. T. Campana                     | Floating-Point Numbers 6-1                    |

| C 4 T 11 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4             | Binary Integers in Main Storage 6-2           |

| CAT AND A AND A                                      | Normalization 6-2                             |

| 0 . 0.                                               | Programming Considerations 6-2                |

| Cat Car All San Land                                 | Floating-Point Feature Not Installed 6-2      |

| Coon Device Field F                                  | Floating-Point Registers 6-2                  |

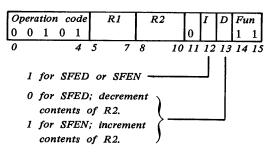

| Scan Byte Field Equal and Decrement (SFED) 5-81      | Arithmetic Indicators 6-2                     |

| Scan Byte Field Equal and Increment (SFEN) 5-81      | Floating-Point Exceptions 6-2                 |

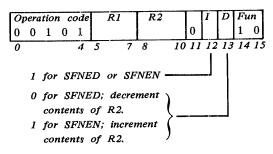

| Scan Byte Field Not Equal and Decrement (SFNED) 5-82 | Level Control 6-3                             |

| Scan Byte Field Not Equal and Increment (SFNEN) 5-82 | Instruction Termination or Suppression 6-3    |

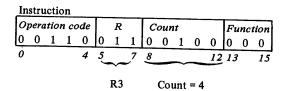

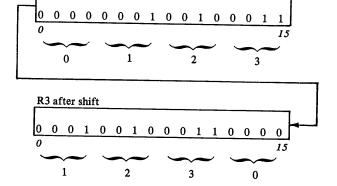

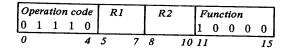

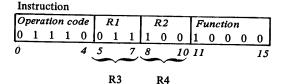

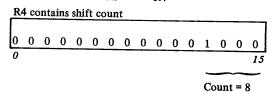

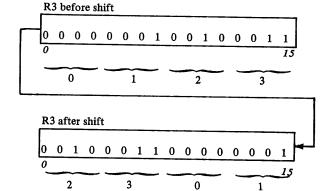

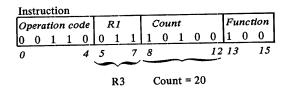

| Shift Left Circular (SLC) 5-83                       | Floating-Point Instructions 6-3               |

| Immediate Count Format 5-83                          | Instruction Formats 6-3                       |

| Count in Register Format 5-83                        | Exception Conditions 6-4                      |

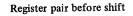

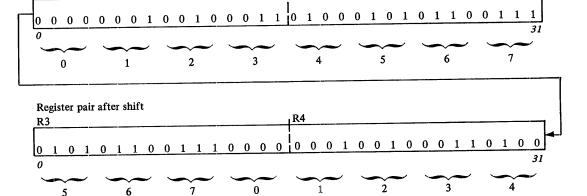

| Shift Left Circular Double (SLCD) 5-84               | Program Check Conditions 6-4                  |

| Immediate Count Format 5-84                          | Soft Exception Trap Condition 6-4             |

| Count in Register Format 5-85                        |                                               |

| Shift Left Logical (SLL) 5-86                        | Instruction Descriptions 6-5                  |

| Immediate Count Format 5-86                          | Copy Floating Level Block (CPFLB) 6-5         |

| Count in Register Format 5-86                        | Floating Add (FA) 6-6                         |

| Shift Left Logical Double (SLLD) 5-87                | General Description (Short precision) 6-6     |

| Immediate Count Format 5-87                          | Storage/Register Format 6-6                   |

| Count in Register Format 5-87                        | Register to Register Format 6-6               |

| Shift Left and Test (SLT) 5-88                       | Floating Add Double (FAD) 6-7                 |

| Shift Left and Test Double (SLTD) 5-88               | General Description (double precision) 6-7    |

| Shift Right Arithmetic (SRA) 5-89                    | Storage/Register Format 6-7                   |

| Immediate Count Format 5-89                          | Register to Register Format 6-7               |

| Count in Register Format 5-89                        | Floating Compare (FC) 6-8                     |

| Shift Right Arithmetic Double (SRAD) 5-90            | Floating Compare Double (FCD) 6-8             |

| Immediate Count Format 5-90                          | Floating Divide (FD) 6-9                      |

| Count in Register Format 5-90                        | Storage/Register Format 6-9                   |

| Shift Right Logical (SRL) 5-91                       | Register to Register Format 6-9               |

| Immediate Count Format 5-91                          | Floating Divide Double (FDD) 6-10             |

| Count in Register Format 5-91                        | Storage/Register Format 6-10                  |

| Shift Right Logical Double (SRLD) 5-92               | Register to Register Format 6-10              |

| Immediate Count Format 5-92                          | Floating Multiply (FM) 6-11                   |

| Count in Register Format 5-92                        | General Description (Short precision) 6-11    |

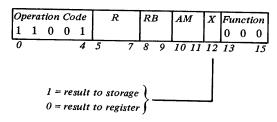

| Store Multiple (STM) 5-93                            | Storage/Register Format 6-11                  |

| Stop (STOP) 5-94                                     | Register to Register Format 6-11              |

| Supervisor Call (SVC) 5-94                           | Floating Multiply Double (FMD) 6-12           |

| Subtract Word (SW) 5-95                              | General Description (Double precision) 6-12   |

| Register/Register Format 5-95                        | Storage/Register Format 6-12                  |

| Register/Storage Format 5-95                         | Register to Register Format 6-12              |

| Storage to Register Long Format 5-96                 | Floating Move (FMV) 6-13                      |

| Storage/Storage Format 5-96                          | Storage to Register Format 6-13               |

| Subtract Word with Carry (SWCY) 5-97                 | Register to Storage Format 6-13               |

| Subtract Word Immediate (SWI) 5-98                   | Register to Register Format 6-13              |

| Register Immediate Long Format 5-98                  | Floating Move and Convert (FMVC) 6-14         |

| Storage Immediate Format 5-98                        | Storage to Register Format 6-14               |

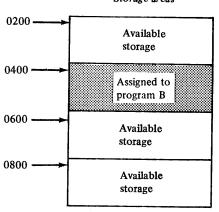

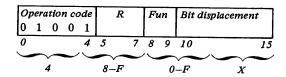

| Fest Bit (TBT) 5-99                                  | Register to Storage Format 6-14               |

| Cest Bit and Reset (TBTR) 5-99                       | Floating Move and Convert Double (FMVCD) 6-15 |

| Fest Bit and Set (TBTS) 5-100                        | Storage to Register Format 6-15               |

| Fest Bit and Invert (TBTV) 5-100                     | Register to Storage Format 6-15               |

| Fest Word Immediate (TWI) 5-101                      | Floating Move Double (FMVD) 6-16              |

| Dominton Income 11 / Y                               | Storage to Register Format 6-16               |

| Storage Immediate Long Format 5-101                  | Register to Storage Format 6-16               |

| nvert Register (VR) 5-102                            | Register to Register Format 6-16              |

|                                                      |                                               |

| Floating Subtract (FS) 6-17                                                                              | Read ID 10-5                                                                           |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| General Description (Short precision) 6-17                                                               | Read Timer Value 10-5                                                                  |

| Storage/Register Format 6-17                                                                             | Read Timer Mode 10-5                                                                   |

| Register to Register Format 6-17                                                                         | Condition Codes Reported for an I/O Instruction 10-5                                   |

| Floating Subtract Double (FSD) 6-18                                                                      | I/O Interrupt 10-6                                                                     |

| General Description (Double precision) 6-18                                                              | Condition Codes Reported for an I/O Interrupt 10-7                                     |

| Storage/Register Format 6-18                                                                             | Status After Resets 10-7                                                               |

| Register to Register Format 6-18                                                                         | D. W. W. D. L. W.                                  |

| Set Floating Level Block (SEFLB) 6-19                                                                    | Chapter 11. Teletypewriter Adapter Feature 11-1                                        |

|                                                                                                          | Addressing 11-2                                                                        |

| Chapter 7. Input/Output Operations 7-1                                                                   | Commands 11-3                                                                          |

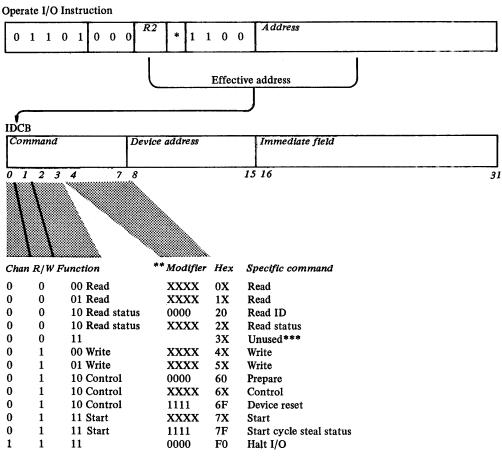

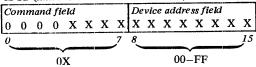

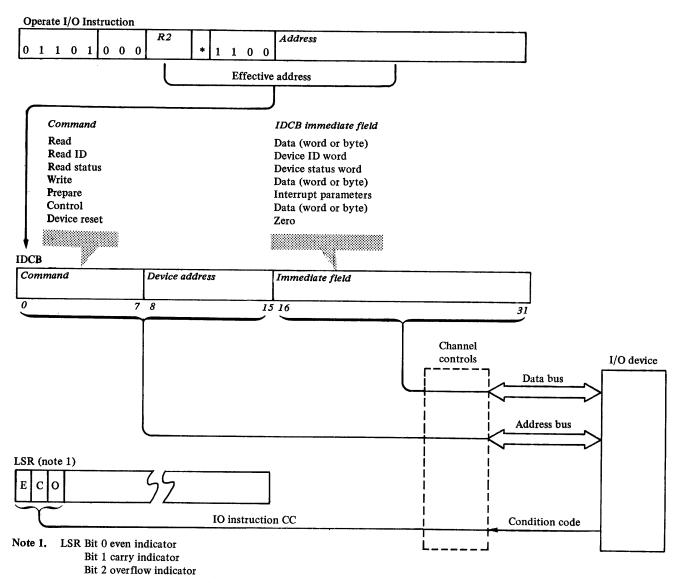

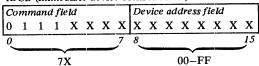

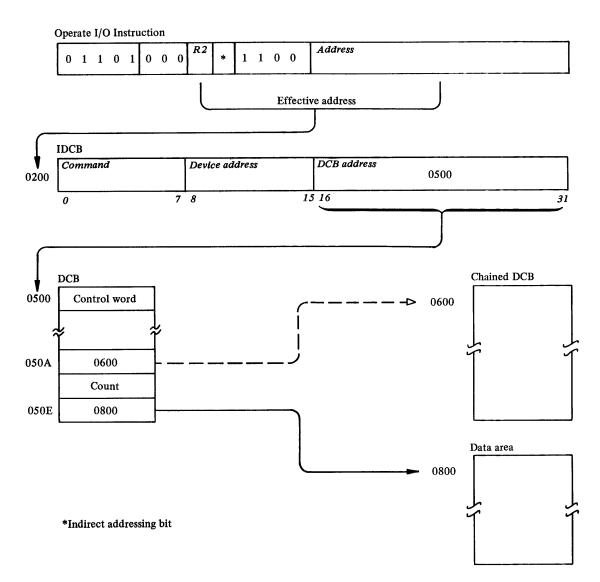

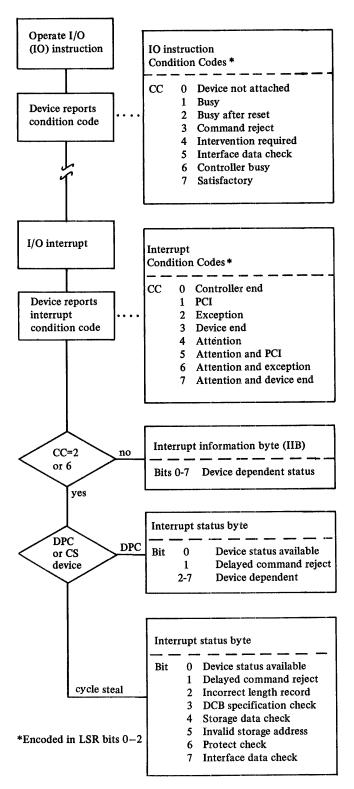

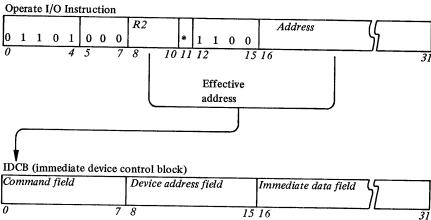

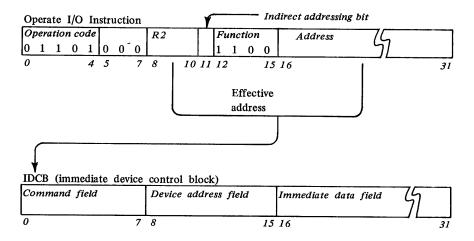

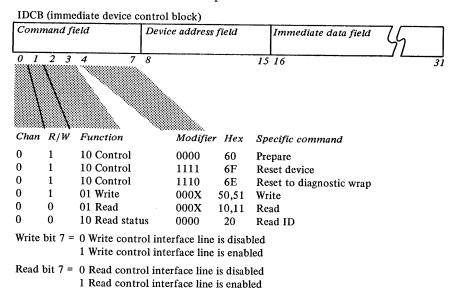

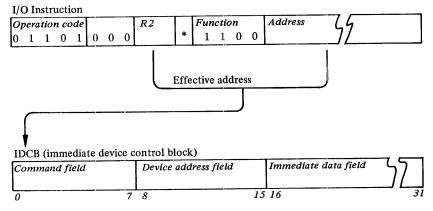

| Operate I/O (IO) Instruction 7-1                                                                         | Prepare 11-4                                                                           |

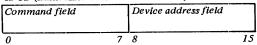

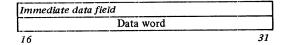

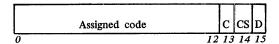

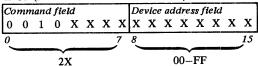

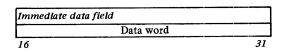

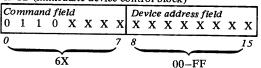

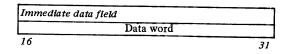

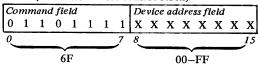

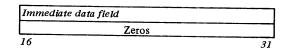

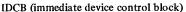

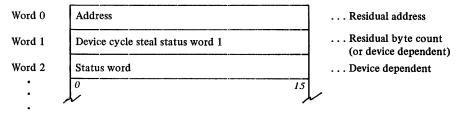

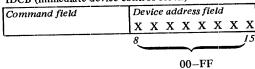

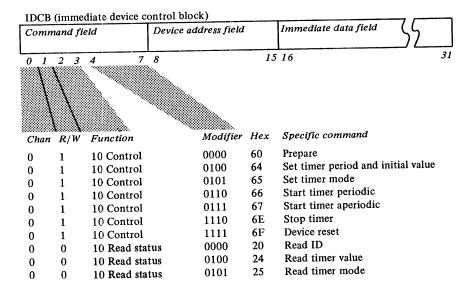

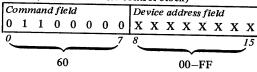

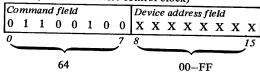

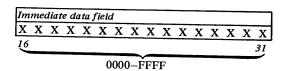

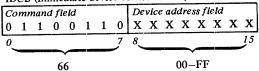

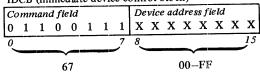

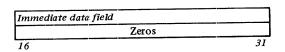

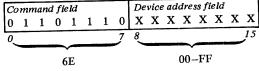

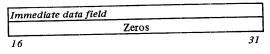

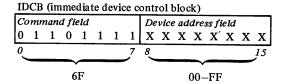

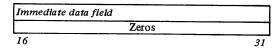

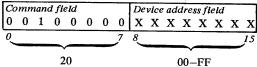

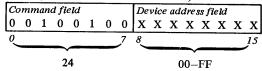

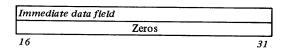

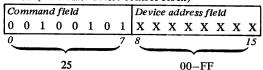

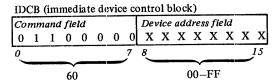

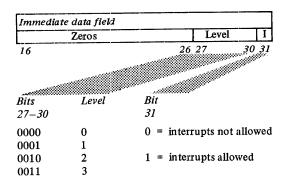

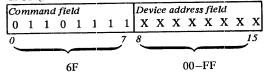

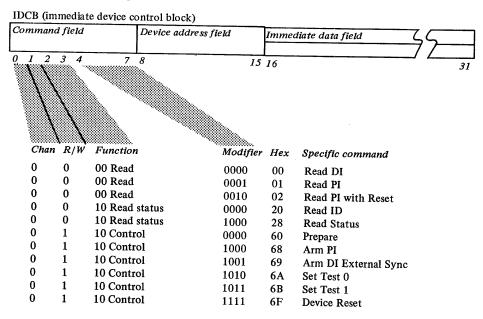

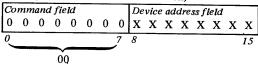

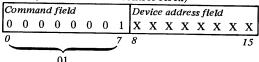

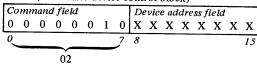

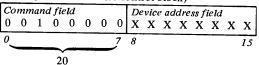

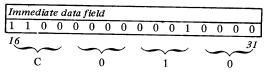

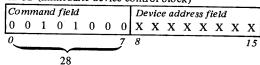

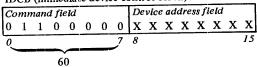

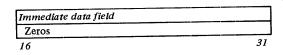

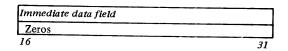

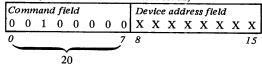

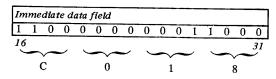

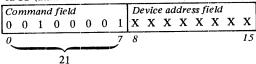

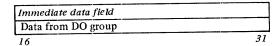

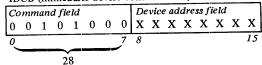

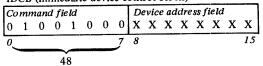

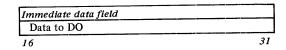

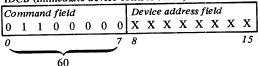

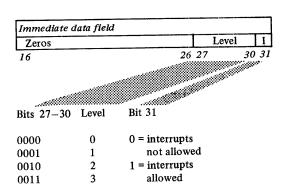

| Immediate Device Control Block (IDCB) 7-2                                                                | Reset Device 11-4                                                                      |

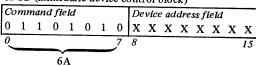

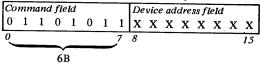

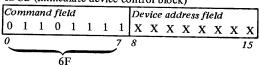

| I/O Commands 7-4                                                                                         | Reset to Diagnostic Wrap 11-4                                                          |

| DPC Operation 7-6                                                                                        | Write 11-4                                                                             |

| Cycle Steal 7-8                                                                                          | Read 11-5                                                                              |

| Start Command 7-8                                                                                        | Read ID 11-5                                                                           |

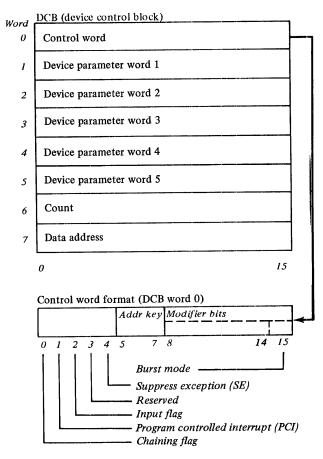

| Device Control Block (DCB) 7-8                                                                           | Condition Codes Reported for an I/O Instruction 11-5                                   |

| Cycle Steal Operation 7-10                                                                               | I/O Interrupt 11-6                                                                     |

| Start Cycle Steal Status Operation 7-12                                                                  | Condition Codes Reported for an I/O Interrupt 11-6                                     |

| Termination Conditions 7-13                                                                              | Status After Resets 11-6                                                               |

| I/O Condition Codes and Status Information 7-14                                                          |                                                                                        |

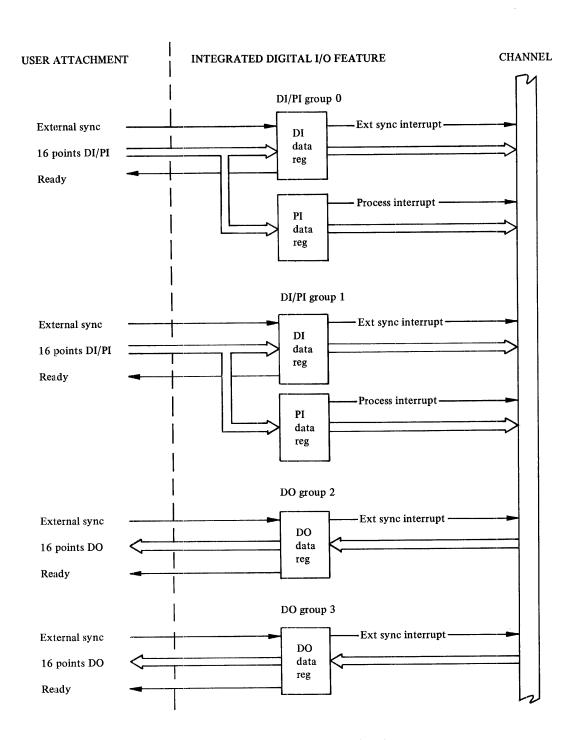

| I/O Instruction Condition Codes 7-15                                                                     | Chapter 12. Integrated Digital Input/Output Non-                                       |

| Interrupt Condition Codes 7-15                                                                           | Isolated Feature 12-1                                                                  |

| I/O Status Information 7-16                                                                              | Digital Input (DI) 12-3                                                                |

| Chaining 7-17                                                                                            | DI External Sync 12-3                                                                  |

| DCB Command Chaining 7-17                                                                                | Process Interrupt (PI) 12-3                                                            |

|                                                                                                          | Digital Output (DO) 12-3                                                               |

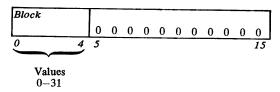

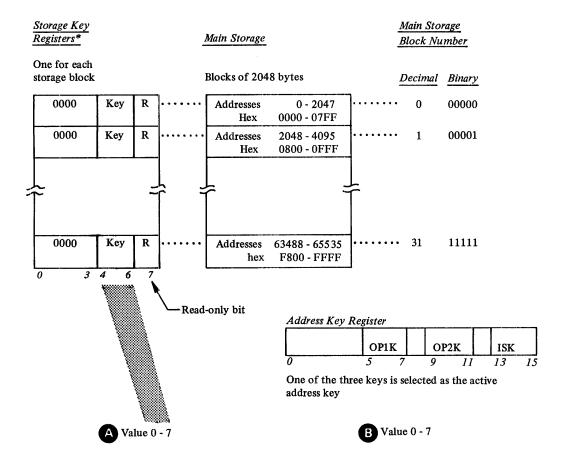

| Chapter 8. Storage Protection 8-1                                                                        | DO External Sync 12-4                                                                  |

| Storage Protection During Initial Program Load 8-3                                                       | Commands 12-4                                                                          |

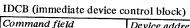

| Storage Protection in Supervisor State 8-3                                                               | Addressing 12-5                                                                        |

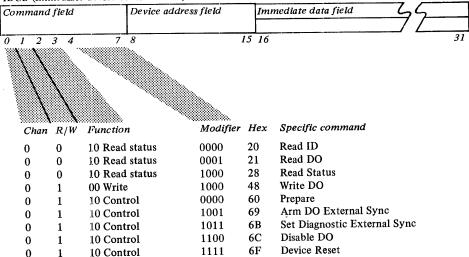

| Address Space Management 8-3                                                                             | Summary of Digital Input Commands 12-5                                                 |

| Address Space 8-3                                                                                        | Summary of Digital Output Commands 12-6                                                |

| Active Address Key 8-4                                                                                   | Condition Codes Reported During the Operation I/O                                      |

| Address Key Values After Interrupts 8-4                                                                  | Instruction 12-6                                                                       |

| Equate Operand Spaces (EOS) 8-5                                                                          | Digital Input Command Description 12-7                                                 |

| - Delegation Translator                                                                                  | Read DI 12-7                                                                           |

| Chapter 9. Storage Address Relocation Translator                                                         | Read PI 12-7                                                                           |

| Feature 9-1                                                                                              | Read PI with Reset 12-7                                                                |

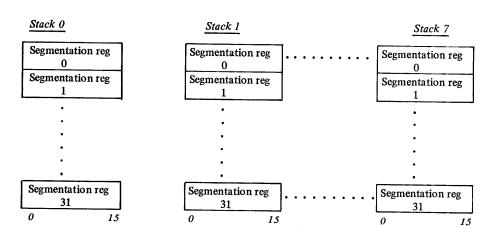

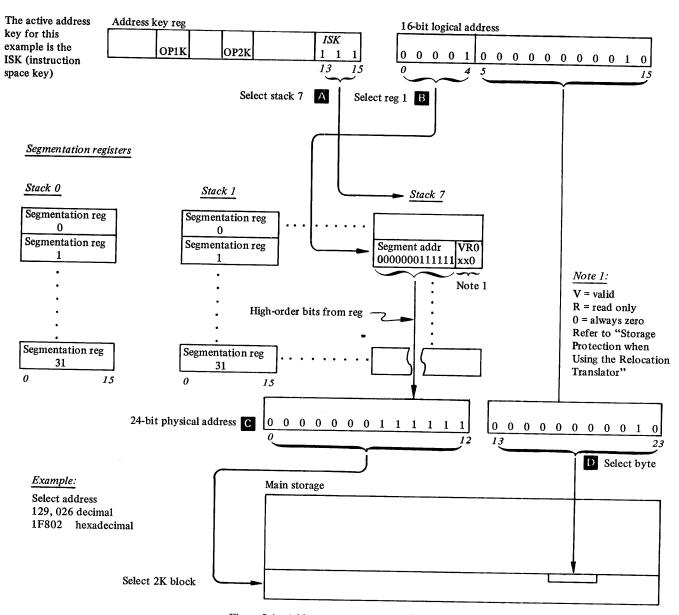

| Translator Description 9-1  Relocation Addressing 9-3                                                    | Read ID 12-7                                                                           |

| Relocation Addressing 9-3 Storage Protection When Using the Relocation Translator 9-4                    | Read Status 12-7                                                                       |

| Storage Protection when Using the Relocation Translator 9-4                                              | Prepare 12-8                                                                           |

| I/O Storage Access Using the Relocation Translator 9-4 Compability Between the Relocation Translator and | Arm PI 12-8                                                                            |

| the Storage Protection Mechanism 9-4                                                                     | Arm DI External Sync 12-8                                                              |

| Characteristics That Are Similar 9-5                                                                     | Set Test 0 12-9                                                                        |

| Characteristics That Are Dissimilar 9-5                                                                  | Set Test 1 12-9                                                                        |

| Error Recovery Considerations 9-5                                                                        | Device Reset 12-9  Digital Output Command Descriptions 12-9                            |

| Invalid Storage Address 9-5                                                                              | Digital Output Command 2 company                                                       |

| Protect Check 9-5                                                                                        | Read ID 12-9                                                                           |

| Status of Translator After Power Transitions and Resets 9-5                                              | Read DO 12-10                                                                          |

| Instruction Execution Time When Using the Translator 9-5                                                 | Read Status 12-10                                                                      |

| mistraction production time with coars and and                                                           | Write DO 12-10                                                                         |

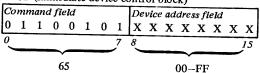

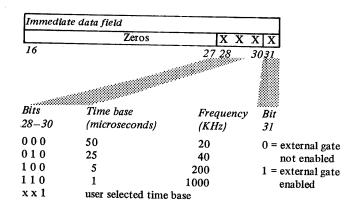

| Chapter 10. Timer Feature 10-1                                                                           | Prepare 12-10 Arm DO External Sync 12-11                                               |

| Addressing 10-2                                                                                          | Arm DO External Sync 12-11 Set Diagnostic External Sync 12-11                          |

| Commands 10-2                                                                                            |                                                                                        |

| Prepare 10-3                                                                                             | Disable DO 12-11 Device Reset 12-11                                                    |

| Set Timer Period and Initial Value 10-3                                                                  | Device Reset 12-11 Interrupt Presentation and Status Words 12-12                       |

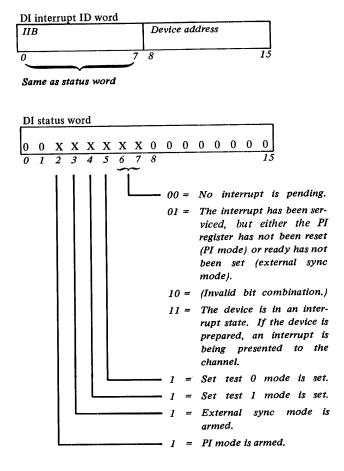

| Set Timer Mode 10-3                                                                                      | DI Status Word and Interrupt ID Word 12-12                                             |

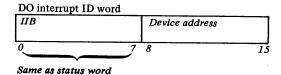

| Start Timer, Periodic 10-4                                                                               | DO Status Word and Interrupt ID Word 12-12  DO Status Word and Interrupt ID Word 12-13 |

| Start Timer Aperiodic 10-4                                                                               | Status After Power Transitions and Resets 12-13                                        |

| Stop Timer 10-4                                                                                          |                                                                                        |

| Device Reset 10-5                                                                                        |                                                                                        |

| DA1120 12000 TO 0                                                                                        | DO Resets 12-13                                                                        |

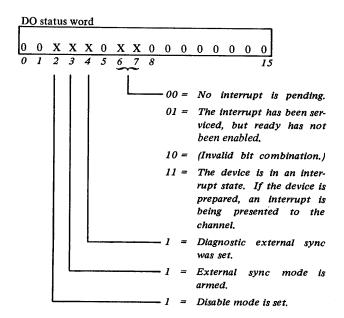

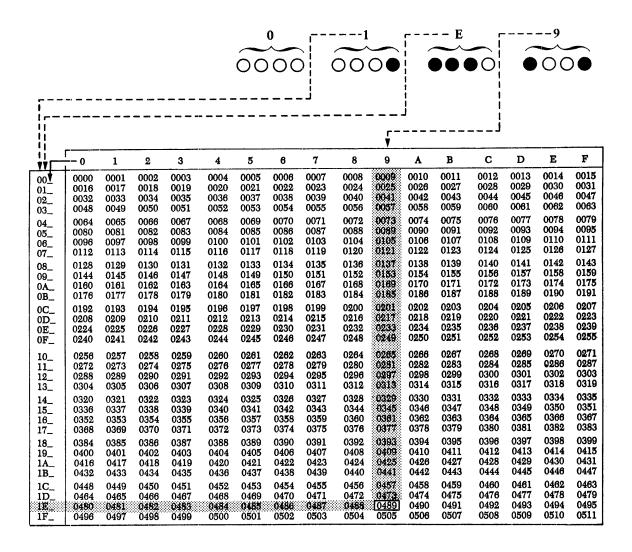

Chapter 13. IBM 4999 Battery Backup Unit 13-1 Introduction 13-1 Functional Description 13-1 Line Voltage Sensing 13-2 Battery Voltage Sensing 13-2 Controls and Indicators 13-2 Utility Power Switch 13-2 Battery Circuit Breaker 13-3 Reset Switch 13-3 Utility Power Indicator 13-3 Backup Power Indicator 13-3 Standby Indicator 13-3 On Battery Indicator 13-3 Low Battery Indicator 13-3 Offline Indicator 13-3 Processor Power/Thermal Warning 13-3 Appendix A. Instruction Execution Times A-1 Table 1. Instruction Times-Relocation Translator Not Installed or Disabled A-4 Table 2. Instruction Times-Relocation Translator Enabled A-13 Appendix B. Instruction Formats B-1 Appendix C. Assembler Syntax C-1 Coding Notes C-1 Legend for Machine Instruction Operands C-1 Appendix D. Numbering Systems and Conversion Tables D-1 Binary and Hexadecimal Number Notations D-1 Binary Number Notation D-1 Hexadecimal Number System D-1 Hexadecimal – Decimal Conversion Tables D-2 Appendix E. Character Codes E-1 Index X-1 Index of Instructions by Format X-13 Index of Instructions by Name X-16

This publication describes the functional characteristics of the IBM 4955 Processor and the features associated with this processor. It assumes that the reader understands data processing terminology and is familiar with binary and hexadecimal numbering systems. The publication is intended primarily as a reference manual for experienced programmers who require machine code information to plan, correct, and modify programs written in the assembler language.

#### SUMMARY OF PUBLICATION

- Chapter 1. Introduction is an introduction to the system architecture. It contains a general description of the processor, storage, features, and a list of attachable I/O devices.

- Chapter 2. Processing Unit Description contains a description of the processor hardware including registers and indicators. The section on indicators includes examples of indicator results when dealing with signed and unsigned numbers.

Main storage data formats and addressing are presented in this chapter.

A section titled "Program Execution" is included and covers:

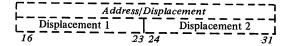

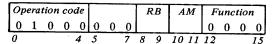

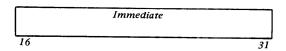

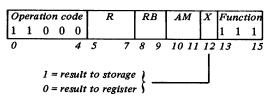

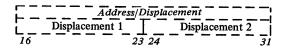

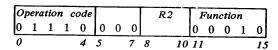

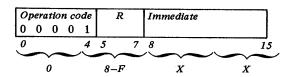

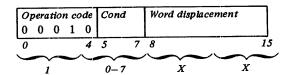

- Basic instruction formats

- Effective address generation

- Processor state control

- Initial program load (IPL)

- Jumping and branching

- Level switching and interrupts

- Stack operations

- Chapter 3. Interrupts and Level Switching describes the priority interrupt levels and the interrupt processing for (1) I/O devices, and (2) class interrupts. Related topics are:

- Program controlled level switching

- Interrupt masking facilities

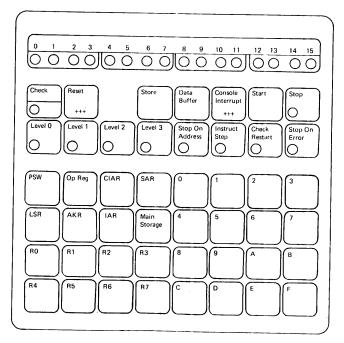

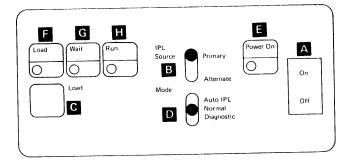

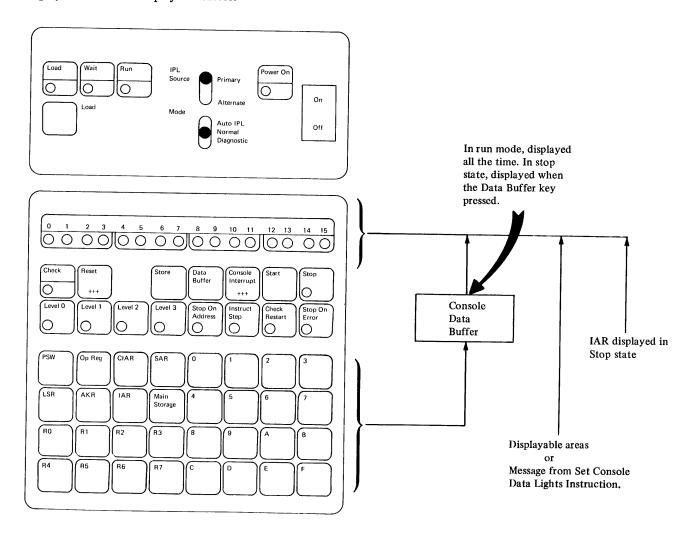

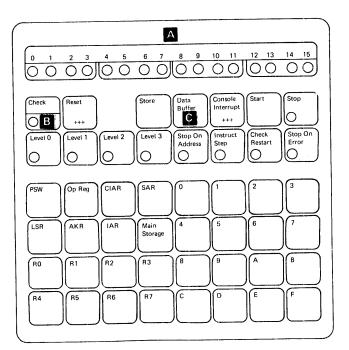

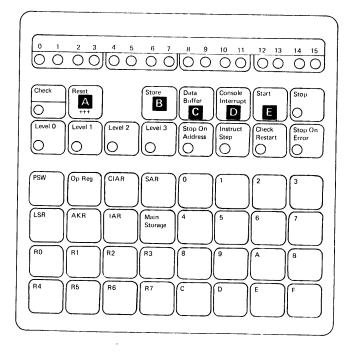

- Recovery from error conditions

- Chapter 4. Console describes the keys, switches, and indicators for the basic console and the optional programmer console. Typical manual operations such as storing into and displaying main storage are presented.

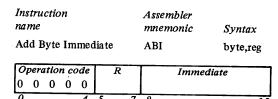

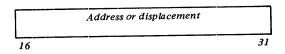

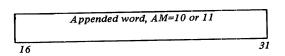

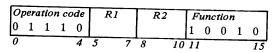

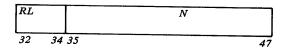

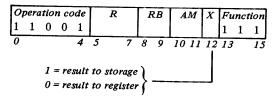

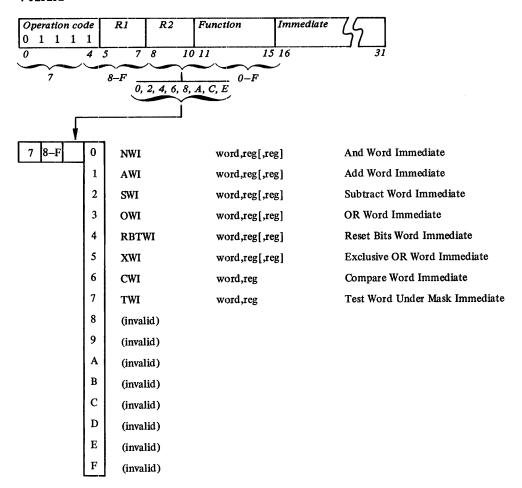

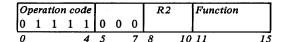

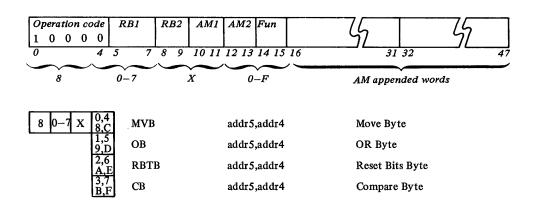

- Chapter 5. Instructions describes the basic instruction set, including indicator settings and possible exception conditions. Individual instruction word formats are included and contain bit combinations for the operation code and function fields. The instructions are arranged in alphabetical sequence based on assembler mnemonics.

- Chapter 6. Floating-Point Feature describes the optional floating-point feature including the floating-point instruction set.

- Chapter 7. Input/Output Operations describes the I/O commands and control words that are used to operate the I/O devices. Condition codes and status information relative to the I/O operation are also explained. Specific command and status-word bit structures are contained in the I/O device description books.

- Chapter 8. Storage Protection describes the operation of the storage protection mechanism.

- Chapter 9. Storage Address Relocation Translator Feature describes the optional relocation translator feature including:

- Relocation addressing

- Effects on storage protection mechanism

- Error recovery considerations

- Chapter 10. Timer Feature describes the optional timer feature including:

- Data flow within the attachment

- I/O commands

- Condition codes and status information

- Chapter 11. Teletypewriter Adapter Feature describes the use of this optional attachment with an input or output device. The topics covered are:

- Bit transfer rates

- I/O commands

- Condition codes and status information

- Chapter 12. Integrated Digital Input/Output Non-Isolated Feature provides a description of the commands and operations associated with this feature.

- Chapter 13. IBM 4999 Battery Backup Unit describes the components and operation of this feature.

- Appendixes:

- Instruction execution times

- Instruction formats

- Assembler syntax

- Numbering systems and conversion tables

- Character codes

# RELATED PUBLICATIONS

- IBM Series/1 System Summary, GA34-0035.

- IBM Series/1 Physical Planning Manual, GA34-0029.

- IBM Series/1 4964 Diskette Unit Description, GA34-0023.

- IBM Series/1 4962 Disk Storage Unit Description, GA34-0024.

- IBM Series/1 4974 Printer Description, GA34-0025.

- IBM Series/1 4979 Display Station Description, GA34-0026.

- IBM Series/1 4982 Sensor Input/Output Unit Description, GA34-0027.

- IBM Series/1 Communications Features Description, GA34-0028.

- IBM Series/1 User's Attachment Manual, GA34-0033.

The IBM 4955 Processor is a compact, general purpose computer and has the following general characteristics:

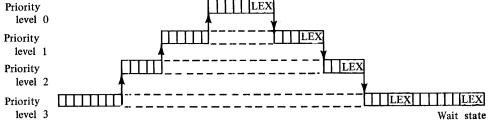

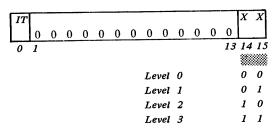

- Four priority interrupt levels-independent registers and status indicators for each level. Automatic and program controlled level switching.

- FET (field effect transistor) main storage-16K bytes basic. Additional storage available in 16K increments (128K bytes maximum). Read or write time is 300 nanoseconds (660 nanoseconds required between two storage access cycles). Odd parity by byte is maintained throughout storage.

- TTL (transistor-transistor logic) processor technology.

- Microprogram control-microcycle nanoseconds.

- Instruction set that includes: stacking and linking facilities, multiply and divide, variable field-length byte operations, and a variety of arithmetic and branching instructions.

- Supervisor and problem states.

- Packaged in a 19-inch rack mountable unit-full width.

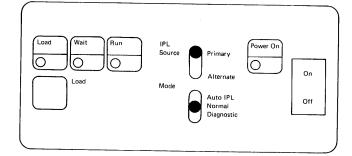

- Basic console standard in processor unit. Programmer console optional.

- Channel capability.

- Asynchronous, multidropped channel.

- 256 I/O (input/output) devices can be addressed.

- Direct program control and cycle steal operations.

- Maximum aggregate burst data rate is 1.6 megabytes (800K words) per second. When multiple cycle stealing devices are interleaved, the aggregate data rate is also 1.6 megabytes per second.

The processor unit contains power and space for additional features and storage. The IBM 4959 Input/Output Expansion Unit is available for additional features.

The processor unit is described in the following sections of this chapter.

#### **IBM 4955 PROCESSOR**

### **Processor Optional Features**

- Storage Address Relocation Translator (permits addressing of main storage larger than 64K bytes).

- Storage Addition-16,384 bytes.

- provides additional storage in 16K byte increments.

- without storage address relocation translator: an additional 48K bytes (64K bytes total for processor).

- with storage address relocation translator: 64K bytes beyond normal expansion (128K bytes total for processor).

- Programmer Console.

- Floating-Point.

### **Processor Description**

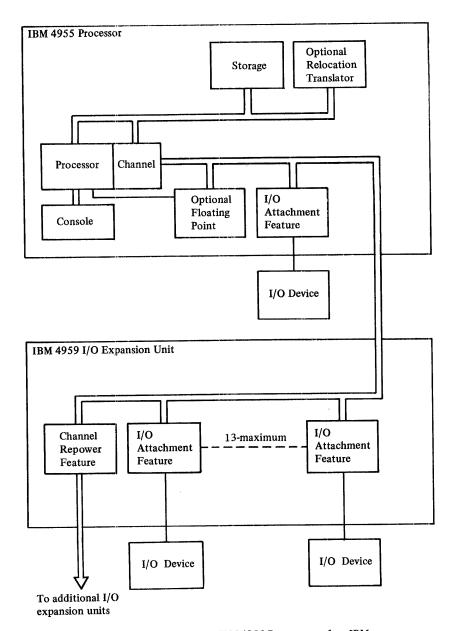

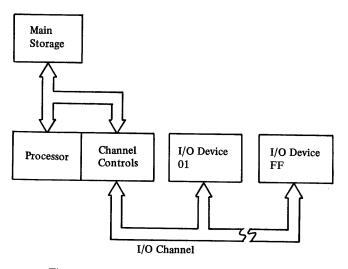

The basic IBM 4955 Processor includes the processor, 16K bytes of storage, and a basic console. These items are packaged in a unit, called the processor unit. Figure 1-1 shows a block diagram of an IBM 4955 Processor and an IBM 4959 Input/Output Expansion Unit.

Figure 1-1. Block diagram of an IBM 4955 Processor and an IBM 4959 Input/Output Expansion Unit

The processor is microprogram controlled, utilizing a 220 nanosecond microcycle. Circuit technology is TTL (transistor-transistor logic).

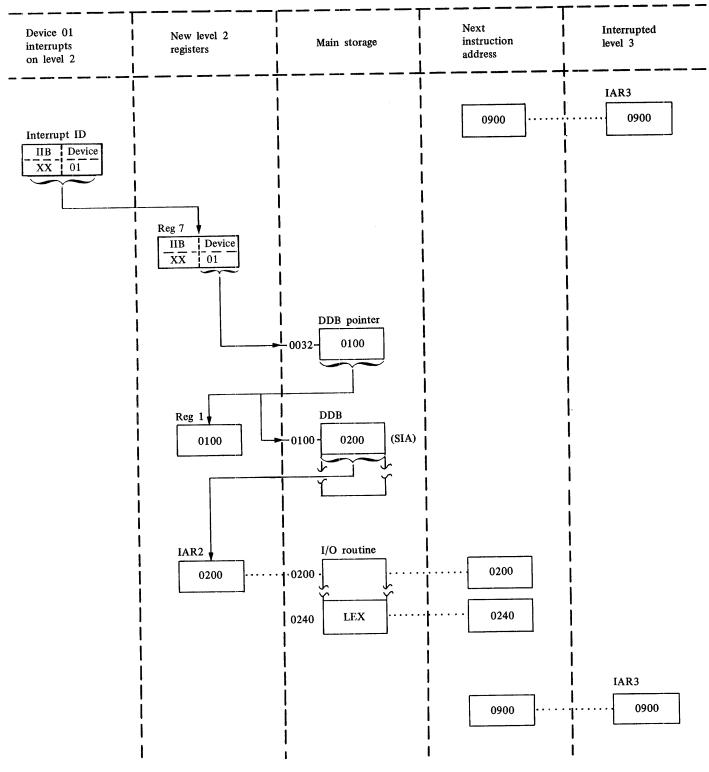

Four priority interrupt levels are implemented in the processor. Each level has an independent set of machine registers. Level switching can occur in two ways: (1) by program control, or (2) automatically upon acceptance of an I/O interrupt request. The interrupt mechanism provides 256 unique entry points for I/O devices.

The processor instruction set contains a variety of instruction types. These include: shift, register to register, register immediate, register to (or from) storage, bit manipulation, multiple register to storage, variable byte field, and storage to storage. Supervisor and problem states are implemented, with appropriate privileged instructions for the supervisor.

A floating-point feature is available that supplements the standard instruction set. The floating-point instructions include single and double precision types for: add, subtract, multiply, divide, compare, and move.

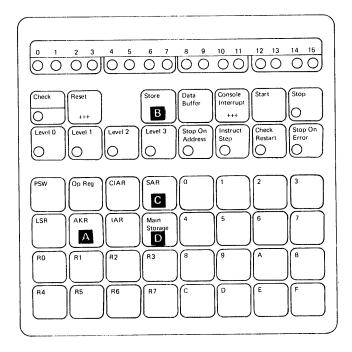

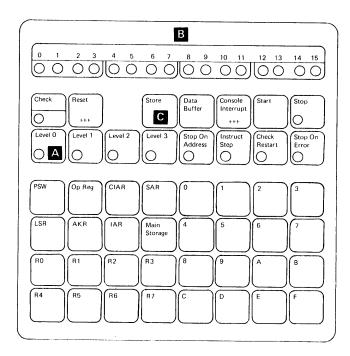

The basic console is intended for dedicated systems that are used in a basically unattended environment. Only minimal controls are provided. A programmer console can be added as a feature; this console provides a variety of indicators and controls for operator-oriented systems.

Main storage technology is FET (field-effect transistor). Basic storage supplied is 16K bytes. The storage addition feature is additional storage in 16K byte increments. The maximum total storage is 64K bytes unless the storage address relocation translator feature is installed. This feature increases the addressing capability beyond 64K bytes. The maximum total storage in an IBM 4955 processor is 128K bytes. The read/write access time for main storage is 300 nanoseconds. However, the minimum duration of time between successive storage cycles is 660 nanoseconds. Storage protection is standard. It protects against (1) access (reading and writing) to defined blocks of storage by software or by an I/O operation, and (2) writing in an undesired location within a defined block by software.

I/O devices are attached to the processor through the processor I/O channel. The channel directs the flow of information between the I/O devices, the processor, and main storage. This channel accommodates a maximum of 256 addressable devices.

The channel supports:

- Direct program control operations. Each Operate I/O instruction transfers a byte or word of data between main storage and the device. The operation may or may not terminate in an interrupt.

- Cycle steal operations. Each Operate I/O instruction initiates multiple data transfers between main storage and the device (65,535 bytes maximum). Cycle steal operations are overlapped with processing operations and always terminate in an interrupt.

- Interrupt Servicing. Interrupt requests from the devices, along with cycle steal requests, are presented and polled on the interface concurrently with data transfers.

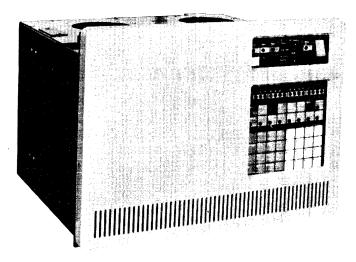

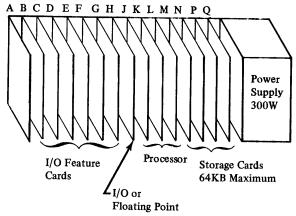

The processor is packaged in a standard 48.3 cm (19 inch) rack-mountable unit, called the processor unit. All processor units contain an integral power supply, fans, and the basic console. Refer to the Series/1 Physical Planning Manual, GA34-0029, for environmental characteristics. Two processor models are available. Figure 1-2 shows the IBM 4955 Processor Model A and Figure 1-3 shows the IBM 4955 Processor Model B.

### IBM 4955 Processor Model A

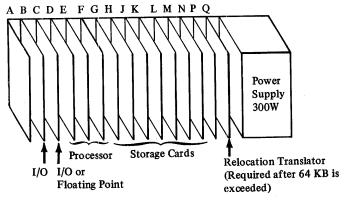

This model occupies the full width of the standard rack. It has the capacity for up to 64K bytes of storage and eight I/O feature cards. The floating-point feature can be substituted for one of the I/O feature cards.

BR2960

4955 Model A Card Plugging Assignments

The A position is reserved for the I/O cables or (due to voltage limitations) one of the following I/O feature cards:

- Teletypewriter Adapter Feature using TTL voltage levels

- Teletypewriter Adapter Feature using isolated current loop where customer supplies external ±12V power

- Timer Feature

- Customer Direct Program Control Adapter Feature

- 4982 Sensor Input/Output Unit Attachment Feature

- Integrated Digital Input/Output Non-Isolated Feature

- Channel Repower Feature

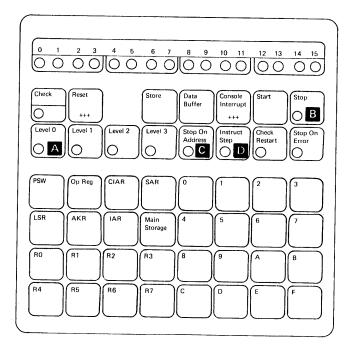

Figure 1-2. IBM 4955 Processor Model A with a Programmer Console

#### IBM 4955 Processor Model B

This model occupies the full width of the standard rack. It has the capacity for up to 128K bytes of storage (including the storage address relocation translator feature) and three I/O feature cards. The floating-point feature can be substituted for one of the I/O feature cards.

BR2960

### 4955 Model B Card Plugging Assignments

The A position is reserved for the I/O cables or (due to voltage limitations) one of the following I/O feature cards:

- Teletypewriter Adapter Feature using TTL voltage levels

- Teletypewriter Adapter Feature using isolated current loop where customer supplies external ±12V power

- Timer Feature

- Customer Direct Program Control Adapter Feature

- 4982 Sensor Input/Output Unit Attachment Feature

- Integrated Digital Input/Output Non-Isolated Feature

- Channel Repower Feature

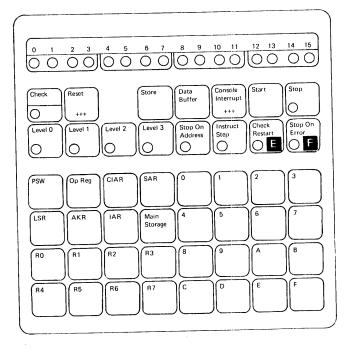

Figure 1-3. IBM 4955 Processor Model B with a Programmer Console

# Input/Output Units and Features

- IBM 4962 Disk Storage Unit (4 models)

- 4962 Disk Storage Unit Attachment Feature

- IBM 4964 Diskette Unit

- 4964 Diskette Unit Attachment Feature

- IBM 4979 Display Station

- 4979 Display Station Attachment Feature

- IBM 4974 Printer

- 4974 Printer Attachment Feature

- Timers Feature (2 timers)

- Teletypewriter Adapter Feature

- Customer Direct Program Control Adapter Feature

The feature cards for attaching the I/O units can be housed in either the processor unit or the I/O expansion unit.

The timer feature and the teletypewriter adapter feature are described in separate chapters of this manual. Information about the other units can be found in separate publications. The order numbers for these publications are listed in the preface of this manual.

### Communications Features

- Asynchronous Communications Single Line Control

- Binary Synchronous Communications Single Line Control

- Binary Synchronous Communications Single Line Control/High Speed

- Synchronous Data Link Control Single Line Control

- Asynchronous Communications 8 Line Control

- Asynchronous Communications 4 Line Adapter

- Binary Synchronous Communications 8 Line Control

- Binary Synchronous Communications 4 Line Adapter

- Communications Power Feature

- Communications Indicator Panel

Refer to the publication, *IBM Series/1 Communications Features Description*, GA34-0028, for a description of these features.

### Sensor Input/Output Options

- Integrated Digital Input/Output Non-Isolated Feature

- IBM 4982 Sensor Input/Output Unit

- 4982 Sensor Input/Output Unit Attachment Feature

- Features for the 4982 Sensor I/O Unit

- Digital Input/Process Interrupt Non-Isolated

- Digital Input/Process Interrupt Isolated

- Digital Output Non-Isolated

- Analog Input Control

- Amplifier Multirange

- Analog Input Multiplexer—Reed Relay

- Analog Input Multiplexer-Solid State

- Analog Output.

The integrated digital input/output non-isolated feature provides digital sensor I/O and simple original equipment manufacturer (OEM) access. The feature card can be housed in either the processor unit or the I/O expansion unit. The integrated digital input/output non-isolated feature is explained in Chapter 12.

The 4982 sensor input/output attachment unit feature card is housed in either the processor or the I/O expansion unit. Refer to the publication, Series/1 4982 Sensor Input/ Output Unit Description, GA34-0027, for a description of the 4982 and associated features.

### Packaging and Power Options

- IBM 4959 Input/Output Expansion Unit

- IBM 4999 Battery Backup Unit

- IBM 4997 Rack Enclosure

The IBM 4959 Input/Output Expansion Unit is available for adding I/O feature cards beyond the capacity of the processor unit. The capacity of the I/O expansion unit is either (1) fourteen I/O feature cards, or (2) thirteen I/O feature cards plus a channel repower card. A channel repower card is required to power each additional I/O expansion unit.

The IBM 4999 Battery Backup Unit permits the processor unit (excluding external devices) to operate from a user-supplied battery when a loss or dip in line power occurs. The battery backup unit is explained in Chapter 13.

### Other Options

Additional options such as communications cables, customer access panel, and a channel socket adapter are also available. For a list and description of system units and features, refer to the Series/1 System Summary, GA34-0035.

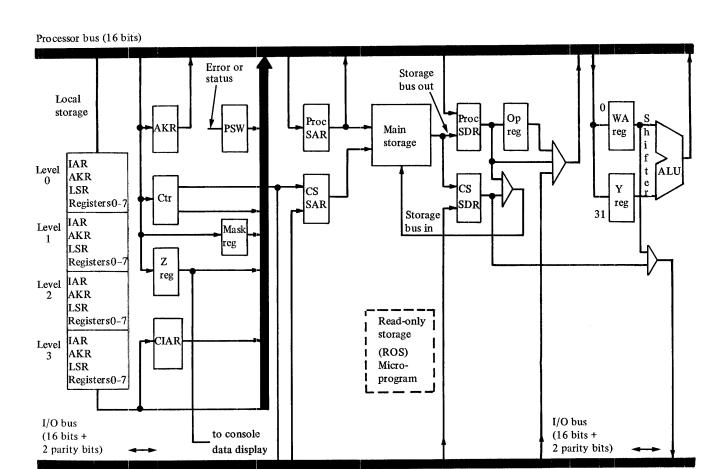

Figure 2-1 shows the general data flow for the IBM 4955 Processor. The major functional units shown in the data flow are discussed in the following sections.

#### MAIN STORAGE

Main storage holds data and instructions for applications to be processed on the system. The data and instructions are stored in units of information called a byte. Each byte consists of eight binary data bits. Associated with each byte is a parity bit. Odd parity by byte is maintained throughout storage; even parity causes a machine check error. Formats shown in this manual exclude the parity bit(s) because they are not a part of the data flow manipulated by the instructions.

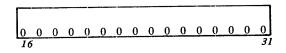

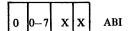

The bits within a byte are numbered consecutively, left to right, 0 through 7. When a format consists of multiple bytes, the numbering scheme is continued; for example, the bits in the second byte would be numbered 8 through 15. Leftmost bits are sometimes referred to as high-order bits and rightmost bits as low-order bits.

Bytes can be handled separately or grouped together. A word is a group of two consecutive bytes, beginning on an even address boundary, and is the basic building block of instructions. A doubleword is a group of four consecutive bytes beginning on an even address boundary.

| By             | /te |   |   |   |   |   |   |   |

|----------------|-----|---|---|---|---|---|---|---|

| 0              | 0   | 0 | 0 | 0 | 0 | 0 | 1 |   |

| $\overline{a}$ |     |   |   |   |   |   | 7 | • |

| W | ord |   |   |   |   |   |   |   |   |   |   |   |   |   |    |

|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|----|

| 0 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0  |

| 0 |     |   |   |   |   |   | 7 | 8 |   |   |   |   |   |   | 15 |

#

### Addressing Main Storage

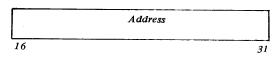

Each byte location in main storage is directly addressable. Byte locations in storage are numbered consecutively, starting with location zero; each number is considered the address of the corresponding byte. Storage addresses are 16-bit unsigned binary numbers. This permits a direct addressing range of 65,536 bytes:

| Address Range         |             |         |

|-----------------------|-------------|---------|

| 16-bit binary address | Hexadecimal | Decimal |

| 0000 0000 0000 0000   | 0000        | 0       |

| to                    | to          | to      |

| 1111 1111 1111 1111   | FFFF        | 65,535  |

**Note:** Addresses that overflow or underflow the addressing range address wrap modulo 65,536.

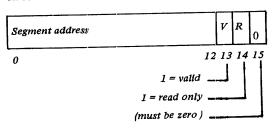

When the Storage Address Relocation Translator Feature is installed, the 16-bit address is used as a logical address to generate a 24-bit physical address.

# Instruction and Operand Address Boundaries

As previously stated, all storage addressing is defined by byte location. Instructions can refer to bits, bytes, byte strings, words, or doublewords as data operands. All word and doubleword operand addresses must be on even byte boundaries. All word and doubleword operand addresses point to the most significant (leftmost) byte in the operand. Bit addresses are specified by a byte address and a bit displacement.

### Legend:

AKR - Address key register

ALU - Arithmetic and logic unit

I/O address bus (16 bits)

CIAR - Current instruction address register

CS - Cycle steal Ctr - Counter

IAR - Instruction address register

LSR - Level status register

Mask - Interrupt level mask register

Op - Operation register

Proc - Processor

PSW — Processor status word

SAR — Storage address register

SDR — Storage data register

WA — Work/shift register

Y — Work/shift register

Z — Console data

Figure 2-1. Data flow for the IBM 4955 Processor

I/O address bus (16 bits)

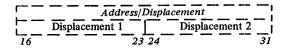

To provide maximum addressing range, some instructions refer to a word displacement that is added to the contents of a register. In these cases, the operand is a word and the register must contain an even byte address for valid results. Effective address generation is described in a subsequent section of this chapter.

All instructions must be on an even byte boundary. This implies that the effective address for all branch type instructions must be on an even byte boundary to be valid.

If any of the aforementioned rules are violated, a program check interrupt occurs with *specification check* set in the processor status word (PSW). The instruction is suppressed.

#### REGISTERS

Registers in the processor are provided in two categories:

- 1. Per-level register (the register is duplicated for each priority interrupt level)

- 2. Per-system register (the register is provided only once and is used by all priority interrupt levels)

Information that must be saved when a level is preempted is retained in registers supplied for a specific level. Information that pertains only to the current process is kept in registers common to all levels. The registers in each category are listed in this section. Descriptions for each of the registers appear in subsequent sections. Only registers accessible to the program or the operator (via console operations) are discussed.

Registers supplied on a per-system basis:

- Console address key register

- Console data buffer

- Current-instruction address register (CIAR)

- Mask register (interrupt level)

- Processor status word (PSW)

- Segmentation registers (optional) see Chapter 9, Storage Address Relocation Translator Feature.

- Storage address register (SAR)

Registers supplied on a per-level basis:

- Address key register (AKR)

- Floating-point registers (optional) see Chapter 6. Floating-Point Feature.

- General registers (8 per level)

- Instruction address register (IAR)

- Level status register (LSR)

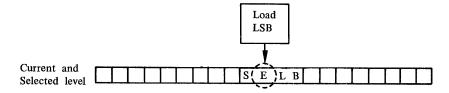

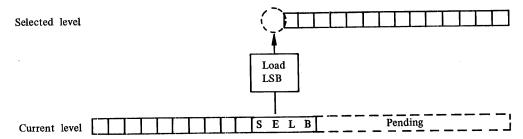

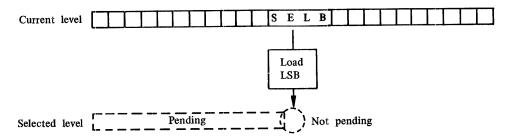

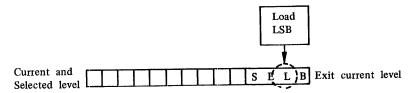

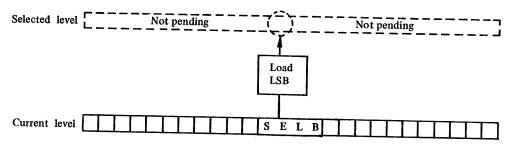

Note. For a specific level, the contents of the AKR, IAR, LSR, and the general registers are known as a level status block (LSB). The LSB is a 22 byte entity used by hardware and software for task control and task switching.

### Console Address Key Register

The Console AKR is not addressable by software. When the programmer console is installed, this register is used for certain console operations. Refer to *Programmer Console* in Chapter 4.

### Console Data Buffer

The console data buffer is a 16-bit register associated with the programmer console feature. Details of how the buffer is used are explained in the programmer console section of Chapter 4. The contents of the console data buffer can be loaded into a specified general register by using the Copy Console Data Buffer (CPCON) instruction (see Chapter 5).

### Current-Instruction Address Register (CIAR)

When the processor enters the stop state, the current-instruction address register (CIAR) contains the address of the last instruction that was executed. The CIAR is not addressable by software. It may be displayed from the optional programmer console. Refer to *Stop State* in this chapter for methods of entering stop state.

### Mask Register

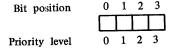

The mask register is a 4-bit register used for control of interrupts. Bit 0 controls level 0, bit 1 controls level 1, and so on.

A one bit enables interrupts on a level, while a zero bit disables interrupts. For example if bit 3 is set to a one, interrupts are enabled on level 3.

#### Processor Status Word (PSW)

The processor status word (PSW) is a 16-bit register used to (1) record error or exception conditions that may prevent further processing, and (2) hold certain flags that aid in error recovery. Error or exception conditions recorded in the PSW result in a class interrupt. Each bit in the PSW is described in detail in Chapter 3. The PSW can be accessed by using the Copy Processor Status and Reset (CPPSR) instruction (see Chapter 5).

The contents of the PSW are as follows:

| Bit | Contents                 |

|-----|--------------------------|

| 0   | Specification check      |

| 1   | Invalid storage address  |

| 2   | Privilege violate        |

| 3   | Protect check            |

| 4   | Invalid function         |

| 5   | Floating-point exception |

| 6   | Stack exception          |

| 7   | (not used, always zero)  |

| 8   | Storage parity check     |

| 9   | (not used, always zero)  |

| 10  | CPU control check        |

| 11  | I/O check                |

| 12  | Sequence indicator       |

| 3   | Auto-IPL                 |

| 14  | Translator enabled       |

| 15  | Power/thermal warning    |

#### Storage Address Register (SAR)

The storage address register (SAR) is a 16-bit register that contains the main-storage address for the last attempted processor storage cycle. This register is addressable by the Diagnose instruction and may be altered or displayed from the optional programmer console.

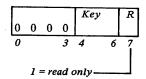

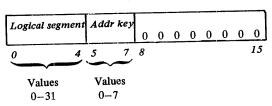

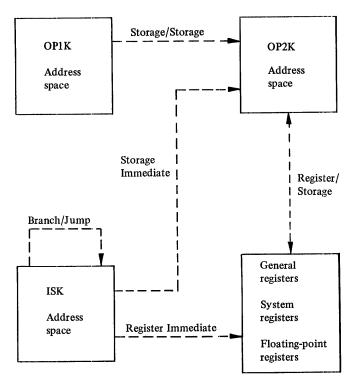

### Address Key Register (AKR)

The address key register (AKR) is a 16-bit register that contains three address keys and an address-key control bit. This register is associated with the storage protection mechanism. Separate 3-bit fields contain an address key for (1) instruction address space, (2) operand-1 address space, and (3) operand-2 address space. Refer to Storage Protection and Address Space Management in Chapter 8 for further information.

| Bits | Contents                      |

|------|-------------------------------|

| 0    | Equate operand spaces         |

| 1    | (not used, always zero)       |

| 2    | (not used, always zero)       |

| 3    | (not used, always zero)       |

| 4    | (not used, always zero)       |

| 5    | Operand-1 key (bit 0)         |

| 6    | Operand-1 key (bit 1)         |

| 7    | Operand-1 key (bit 2)         |

| 8    | (not used, always zero)       |

| 9    | Operand-2 key (bit 0)         |

| 10   | Operand-2 key (bit 1)         |

| 11   | Operand-2 key (bit 2)         |

| 12   | (not used, always zero)       |

| 13   | Instruction space key (bit 0) |

| 14   | Instruction space key (bit 1) |

| 15   | Instruction space key (bit 2) |

### General Registers

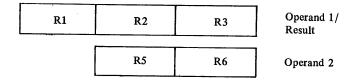

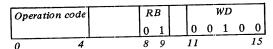

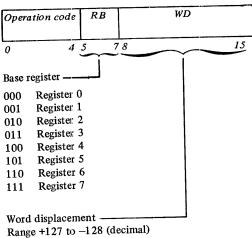

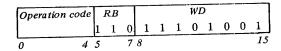

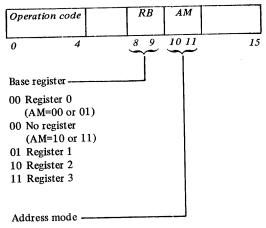

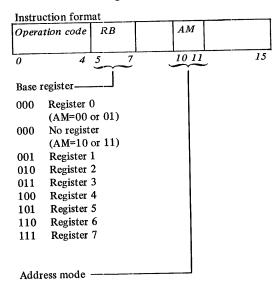

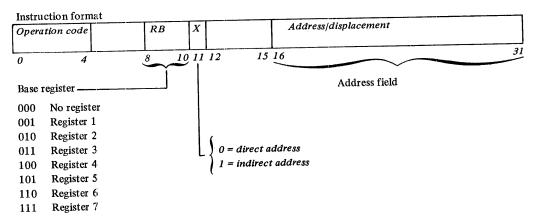

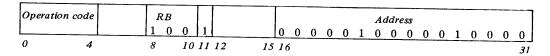

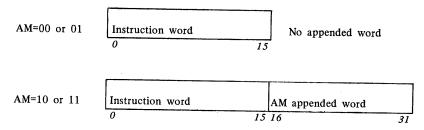

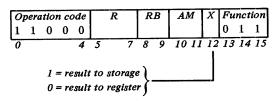

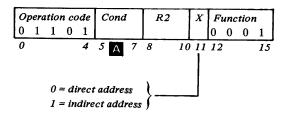

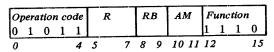

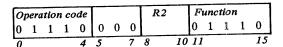

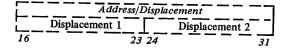

Subsequently referred to simply as registers, the general registers are 16-bit registers available to the program for general purposes. Eight registers are provided for each level. The R and RB fields in the instructions control the selection of these registers:

| R or RB* field value | Register selected |

|----------------------|-------------------|

| 000                  | Register 0        |

| 001                  | Register 1        |

| 010                  | Register 2        |

| 011                  | Register 3        |

| 100                  | Register 4        |

| 101                  | Register 5        |

| 110                  | Register 6        |

| 111                  | Register 7        |

\*The RB field sometimes contains only the two low-order bits. In this case, registers 4 through 7 cannot be specified.

### Instruction Address Register (IAR)

The instruction address register (IAR) is a 16-bit register that holds the main storage address used to fetch an instruction. After an instruction has been fetched, the IAR is updated to point to the next instruction to be fetched.

Note. These registers are sometimes referred to as IAR0, IAR1, IAR2, and IAR3. The numbers represent the priority level associated with the register.

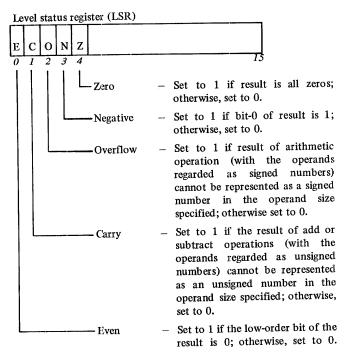

### Level Status Register (LSR)

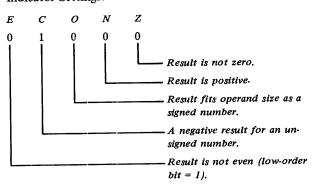

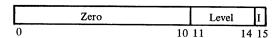

The level status register (LSR) is a 16-bit register that holds the following information for its associated level:

Contents 0 Even indicator 1 Carry indicator 2 Overflow indicator 3 Negative result indicator 4 Zero result indicator 5 (not used, always zero) (not used, always zero) 6 7 (not used, always zero) 8 Supervisor state In process 10 Trace 11 Summary mask 12 (not used, always zero) (not used, always zero) 13 14 (not used, always zero) 15 (not used, always zero)

Indicators (bits 0-4). These bits are set to reflect the result of certain types of instructions; for example: arithmetic, logical, move, and shift instructions. Bits 0, 1, and 2 are also used to hold the condition code following an Operate I/O instruction or after an I/O interrupt. See Arithmetic and Logic Unit in this chapter for additional information about the indicators. Also, specific indicator information for each instruction is provided in Chapter 5.

Supervisor State (bit 8). This bit when set to one indicates that the processor is in the supervisor state. This state allows privileged instructions to be executed. It is set by any of the following:

- 1. Class interrupt

- a. Machine check condition

- b. Program check condition

- c. Power/thermal warning

- d. Supervisor Call (SVC) instruction

- e. Soft exception trap condition

- f. Trace

- g. Console interrupt

- 2. I/O interrupt

- 3. Initial program load (IPL)

The supervisor state bit can be altered by a Set Level Block (SELB) instruction. For additional information, refer to *Processor State Control* in this chapter.

Class interrupts and I/O interrupts are described in Chapter 3. IPL is discussed in a subsequent section of this chapter.

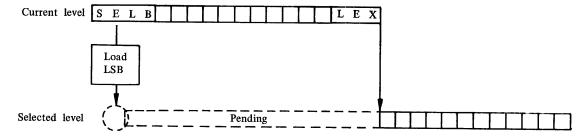

In Process (bit 9). This bit, when set to one, indicates that a level is currently active or was preempted by a higher priority level before completing its task. Bit 9 is turned off by a Level Exit (LEX) instruction. Bit 9 can also be turned on or off by a Set Level Block (SELB) instruction. Refer to Chapter 3. Interrupts and Level Switching.

Trace (bit 10). This bit, when set to one, causes a trace class interrupt at the beginning of each instruction. The bit can be turned on or off with the Set Level Block (SELB) instruction. The trace bit aids in debugging programs. See *Class Interrupts* in Chapter 3.

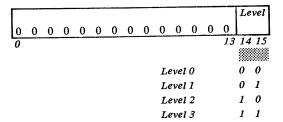

Summary mask (bit 11). This bit, when set to zero (disabled), inhibits all priority interrupts on all levels. When this bit is set to one (enabled), normal interrupt processing is allowed. Refer to Summary Mask in Chapter 3 for details relating to control of the summary mask.

# ARITHMETIC AND LOGIC UNIT (ALU)

The arithmetic and logic unit (ALU) contains the hardware circuits that perform: addition; subtraction; and logical operations such as AND, OR, and exclusive OR. The ALU performs address arithmetic as well as the operations required to process the instruction operands. Operands may be regarded as signed or unsigned by the programmer. However, the ALU does not distinguish between them. Numbering representation is discussed in a subsequent section of this chapter. For many instructions, indicators are set to reflect the result of the ALU operation. The indicators are discussed in a subsequent section of this chapter.

#### NUMBERING REPRESENTATION

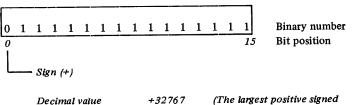

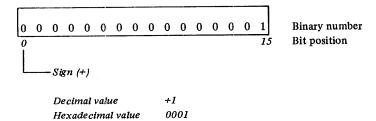

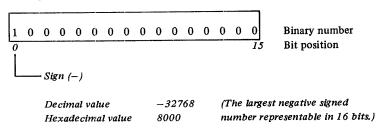

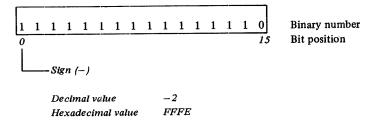

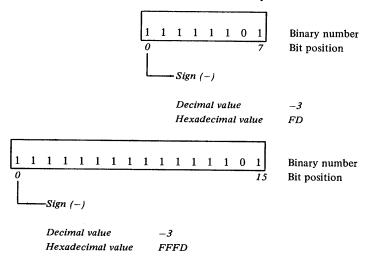

Operands may be signed or unsigned depending on how they are used by the programmer. An unsigned number is a binary integer in which all bits contribute to the magnitude. A storage address is an example of an unsigned number. A signed number is one where the high-order bit is used to indicate the sign, and the remaining bits define the magnitude. Signed positive numbers are represented in true binary notation with the sign bit (high-order bit) set to zero. Signed negative numbers are represented in two's complement notation with the sign bit (high-order bit) set to one. The two's complement of a number is obtained by inverting each bit of the number and adding a one to the low-order bit position. Two's complement notation does not include a negative zero. The maximum positive number consists of an all-one integer field with a sign bit of zero; whereas, the maximum negative number (the negative number with the greatest absolute value) consists of an all-zero integer field with a one-bit for the sign.

The following examples show: (1) an unsigned 16-bit number, (2) a signed 16-bit positive number, and (3) a signed 16-bit negative number.

### Example of an unsigned 16-bit number:

Decimal value Hexadecimal value 65535 FFFF (The largest unsigned number representable in 16 bits.)

Example of a signed 16-bit positive number:

Decimal value Hexadecimal value +32767 7FFF (The largest positive signed number representable in 16 bits.)

When the number is positive, all bits to the left of the most significant bit of the number, including the sign bit, are zero:

Example of a signed 16-bit negative number:

Note. This form of representation yields a negative range of one more than the positive range.

When the number is negative, all bits to the left of the most significant bit of the number, including the sign bit, are set to one:

When a signed-number operand must be extended with high-order bits, the expansion is achieved by prefixing a field in which each bit is set equal to the high-order bit of the operand.

Example of an 8-bit field extended to a 16-bit field:

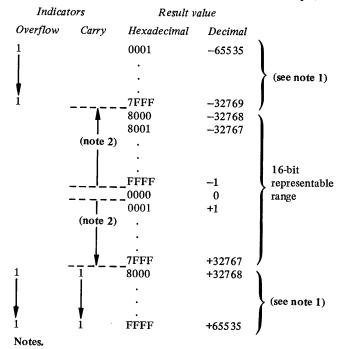

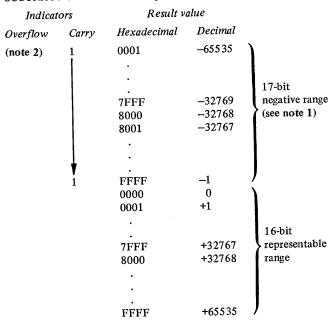

It must be emphasized that when performing the add and subtract operations, the machine does not regard the number as either signed or unsigned, but performs the designated operation on the values presented. Whether a given add or subtract operation is to be regarded as a signed operation or an unsigned operation is determined by the programmer's view of the values being presented as operands. The carry indicator and the overflow indicator of the LSR are changed on various operations to reflect the result of that operation. This allows the programmer to make result tests for the number representation involved. The carry and overflow indicator settings are explained in the following section.

#### **INDICATORS**

The indicators are located in bits 0-4 of the level status register (LSR). Bits 5-7 of the LSR are not used and should be zero. Figure 2-2 shows the indicators and how they are set. The indicator bits are changed or not changed depending on the instruction being executed. Some instructions do not affect the indicators, other instructions change all of the indicators, and still other instructions change only specific indicators. Refer to the individual instruction descriptions in Chapter 5 for the indicators changed by each instruction.

Figure 2-2. How indicators are set for signed and unsigned (logical) operations

The indicators are changed in a specialized manner for certain operations. These operations are described briefly. Additional information is provided in subsequent sections for those operations where more detail is required.

- Add, subtract, or logical operations. The even, negative, and zero indicators are result indicators. For add and subtract operations, the carry and overflow indicators are changed to provide information for both signed and unsigned number representations.

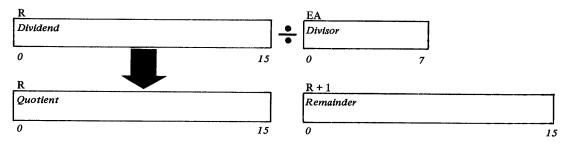

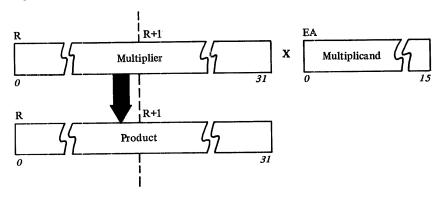

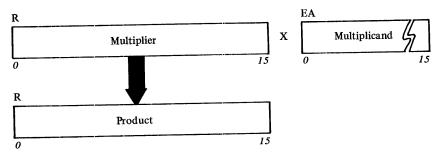

- Multiply and divide operations. Signed number operands are always assumed for these operations. The carry indicator is used to provide a divide by zero indication for the divide instruction. The overflow indicator defines an unrepresentable product for multiply operations. Refer to the individual instruction descriptions in Chapter 5.

- Priority interrupts and input/output operations. The even, carry and overflow indicators are used to form a three-bit condition code that is set as a binary value.

- Compare operations. The indicators are set in the same manner as a subtract operation.

- Shift operations. The carry and overflow indicators have a special meaning for shift left logical operations.

- Complement operations. The overflow indicator is set if an attempt is made to complement the maximum negative number. This number is not representable.

- Set Indicators (SEIND) and Set Level Block (SELB) instructions. All indicators are changed by the data associated with these instructions.

- Floating-point operations. The optional floating-point instructions set the indicators as described in Chapter 6, Floating-Point Feature.

# Even, Negative, and Zero Result Indicators.

The even, negative, and zero indicators are called the result indicators. A positive result is indicated when the zero and negative indicators are both off (set to zero). These indicators are set to reflect the result of the last arithmetic, or logical operation performed. A logical operation in this sense includes data movement instructions. See the individual instruction descriptions in Chapter 5 for the indicators changed for specific instructions.

# Even, Carry, and Overflow Indicators—Condition Code for Input/Output Operations

The even, carry, and overflow indicators contain the I/O condition code: (1) following the execution of an Operate I/O instruction and (2) following and I/O interrupt.

These indicators are used to form a three-bit binary number that results in a condition code value.

| Indica | itors |          | Condition code |

|--------|-------|----------|----------------|

| Even   | Carry | Overflow | value          |

| 0      | 0     | 0        | 0              |

| 0      | 0     | 1        | 1              |

| 0      | 1     | 0        | 2              |

| 0      | 1     | 1        | 3              |

| 1      | 0     | 0        | 4              |

| 1      | 0     | 1        | 5              |

| 1      | 1     | 0        | 6              |

| 1      | 1     | 1        | 7              |

For additional information about condition codes, refer to:

- Branch on Condition Code (BCC) and Branch on Not Condition Code (BNCC) instructions in Chapter 5.

- 2. Condition codes in Chapter 7.

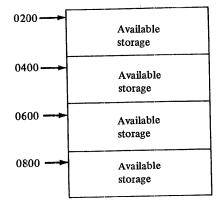

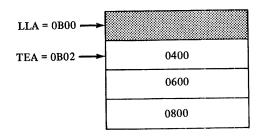

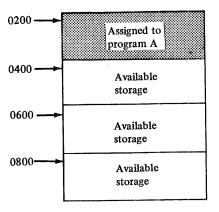

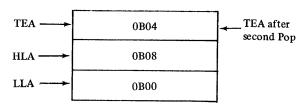

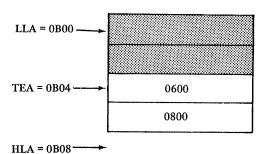

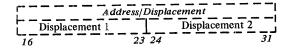

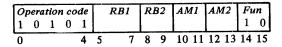

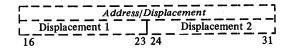

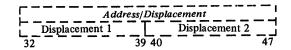

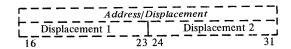

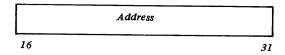

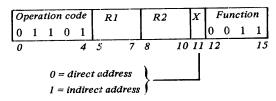

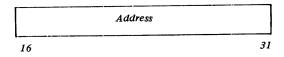

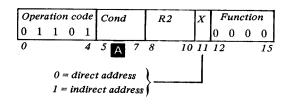

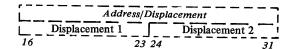

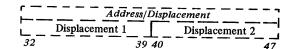

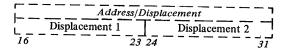

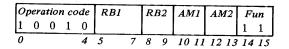

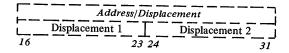

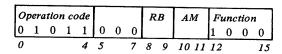

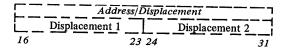

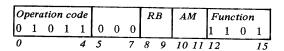

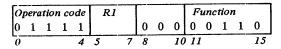

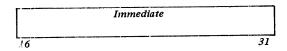

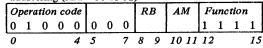

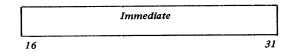

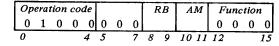

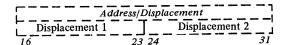

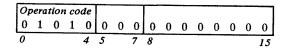

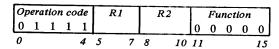

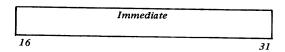

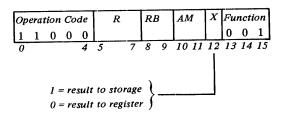

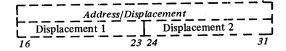

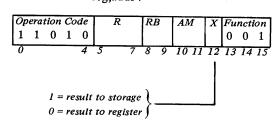

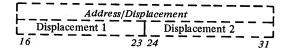

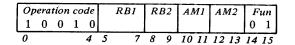

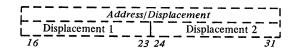

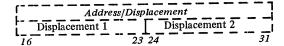

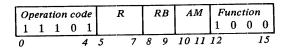

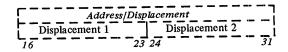

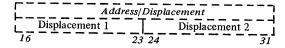

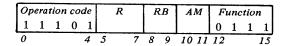

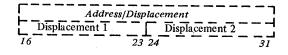

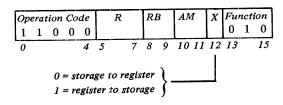

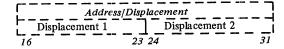

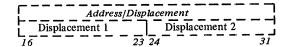

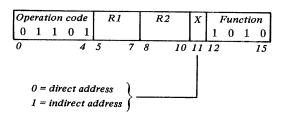

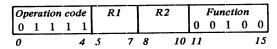

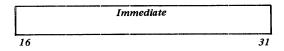

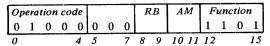

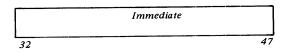

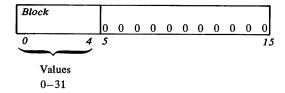

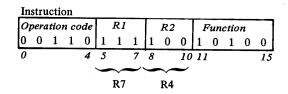

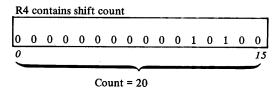

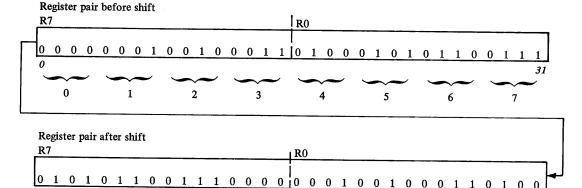

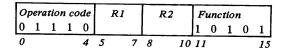

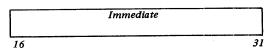

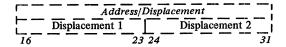

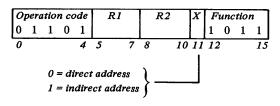

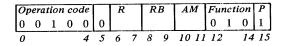

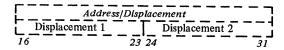

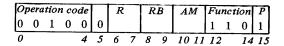

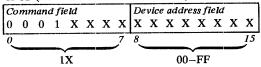

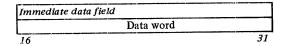

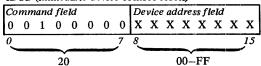

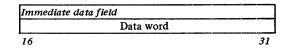

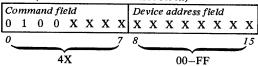

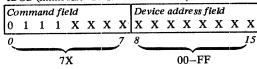

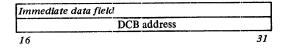

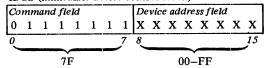

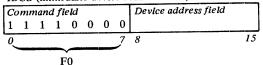

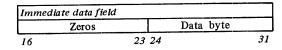

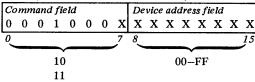

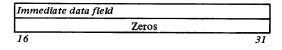

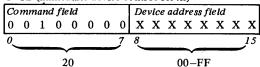

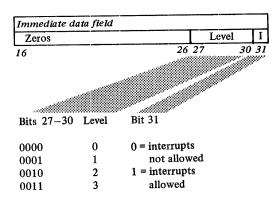

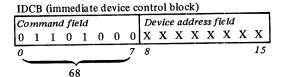

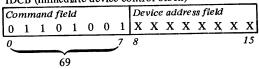

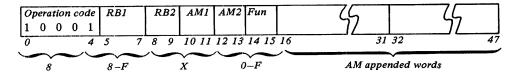

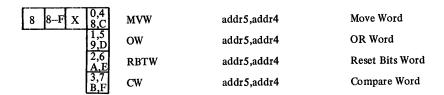

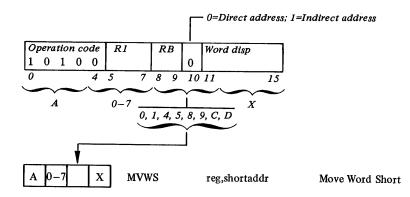

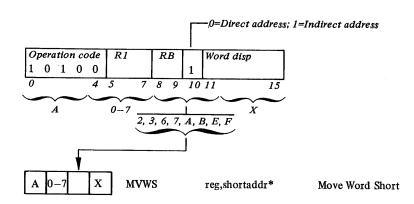

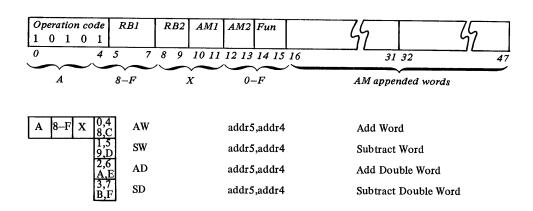

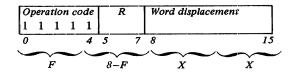

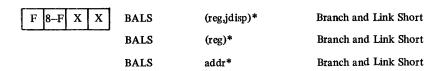

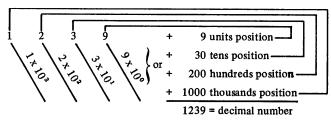

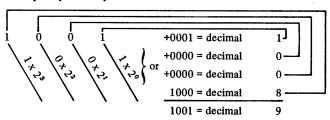

# Carry and Overflow Indicators—Add and Subtract Operations