Series/1

GA34-0021-1 File No. S1-01

GA34-0021-1 File No. S1-01

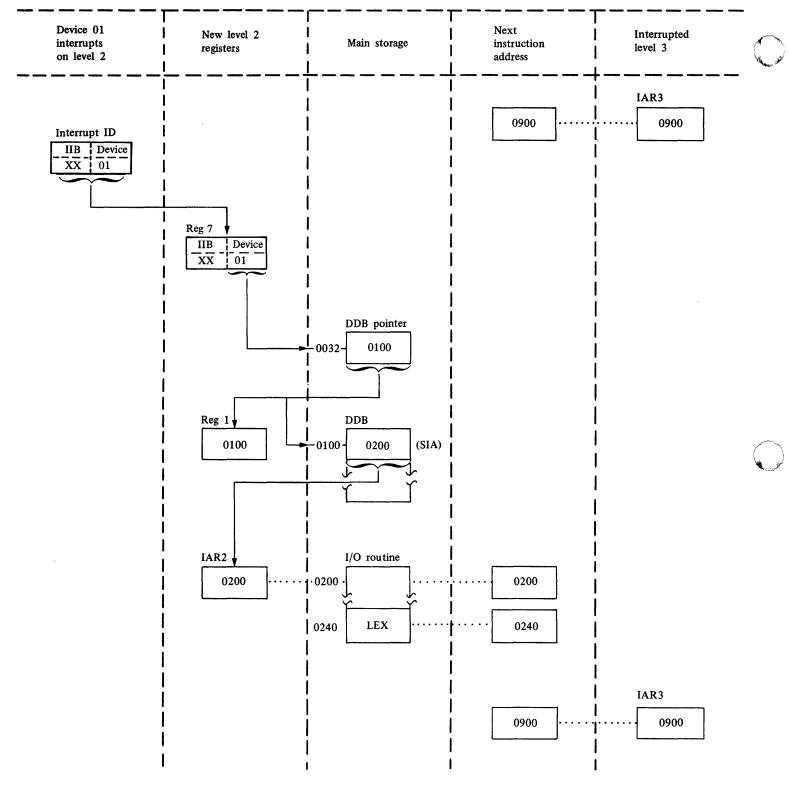

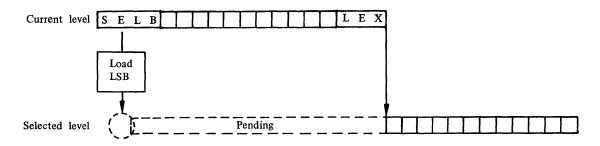

IBM Series/1 Model 5 4955 Processor and Processor Features Description

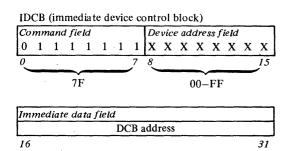

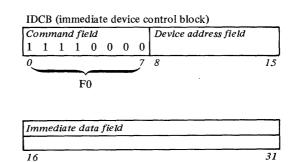

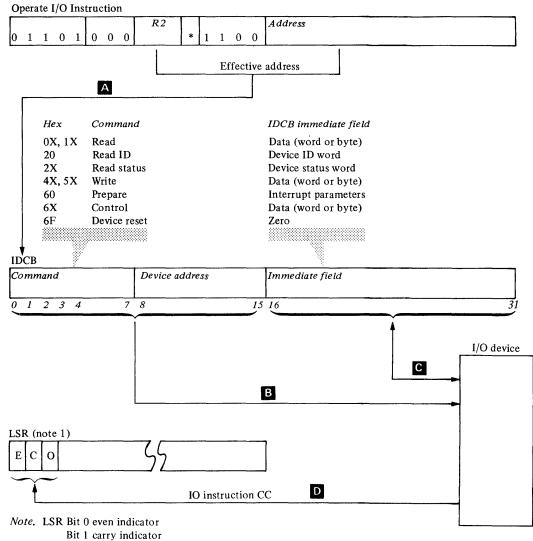

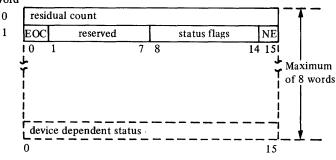

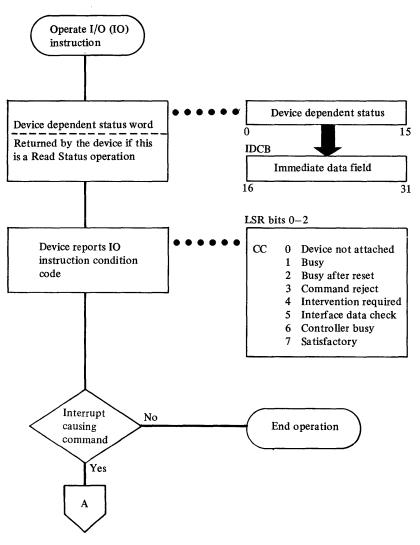

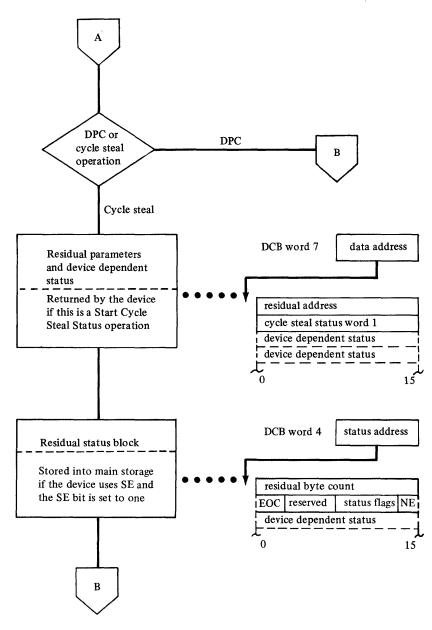

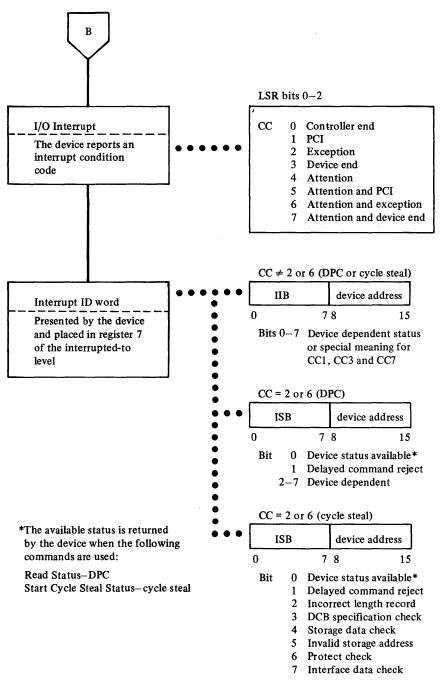

#### Second Edition (March 1977)

This is a major revision of, and obsoletes GA34-0021-0. Significant changes in this new edition include (1) rearrangement of the chapters to provide a more logical flow of information and (2) removal of certain information (four chapters) that is now included in other publications.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters. Before using this publication in connection with the operation of IBM systems, have your IBM representative confirm editions that are applicable and current.

Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, send your comments to IBM Corporation, Systems Publications, Department 27T, P.O. Box 1328, Boca Raton, Florida 33432. Comments become the property of IBM.

©Copyright International Business Machines Corporation 1976, 1977

ii GA34-0021

# Contents

Preface vii Summary of Publication vii Related Publications viii

Chapter 1. Introduction 1-1 IBM 4955 Processor 1-1 Processor Optional Features/Storage Addition 1-1 Processor Description 1-1 Input/Output Units and Features 1-5 Communications Features 1-5 Sensor Input/Output Options 1-5 Packaging and Power Options 1-5 Other Options 1-5

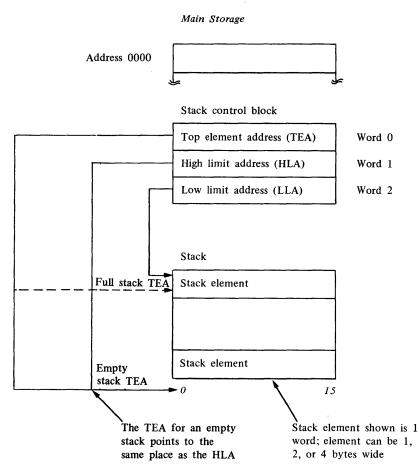

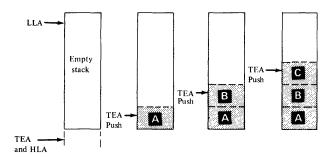

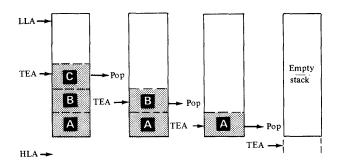

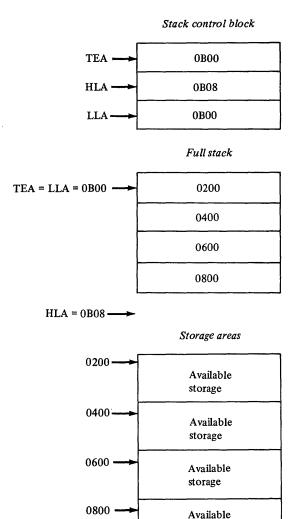

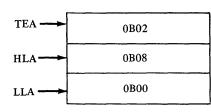

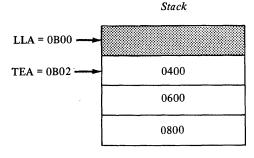

Chapter 2. Processing Unit Description 2-1 Main Storage 2-1 Addressing Main Storage 2-1 Arithmetic and Logic Unit (ALU) 2-3 Numbering Representation 2-3 Registers 2-4 Per-system Registers 2-4 Per-level Registers 2-5 Indicator Bits 2-5 Even, Negative, and Zero Result Indicators 2-6 Even, Carry, and Overflow Indicators - Condition Code for Input/Output Operations 2-6 Carry and Overflow Indicators - Add and Subtract Operations 2-6 Carry and Overflow Indicators - Shift Operations 2-7 Indicators - Compare Operations 2-7 Indicators - Multiple Word Operands 2-8 Testing Indicators with Conditional Branch and Jump Instructions 2-8 Supervisor State Bit 2-10 In-process Bit 2-10 Trace Bit 2-10 Summary Mask Bit 2-10 Program Execution 2-10 Instruction Formats 2-10 Effective Address Generation 2-12 Processor State Control 2-19 Initial Program Load (IPL) 2-22 Sequential Instruction Execution 2-22 Jumping and Branching 2-23 Level Switching and Interrupts 2-23 Stack Operations 2-23

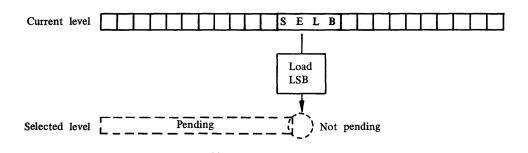

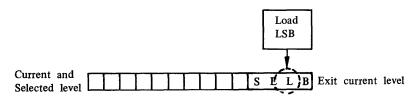

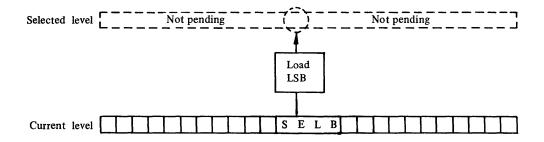

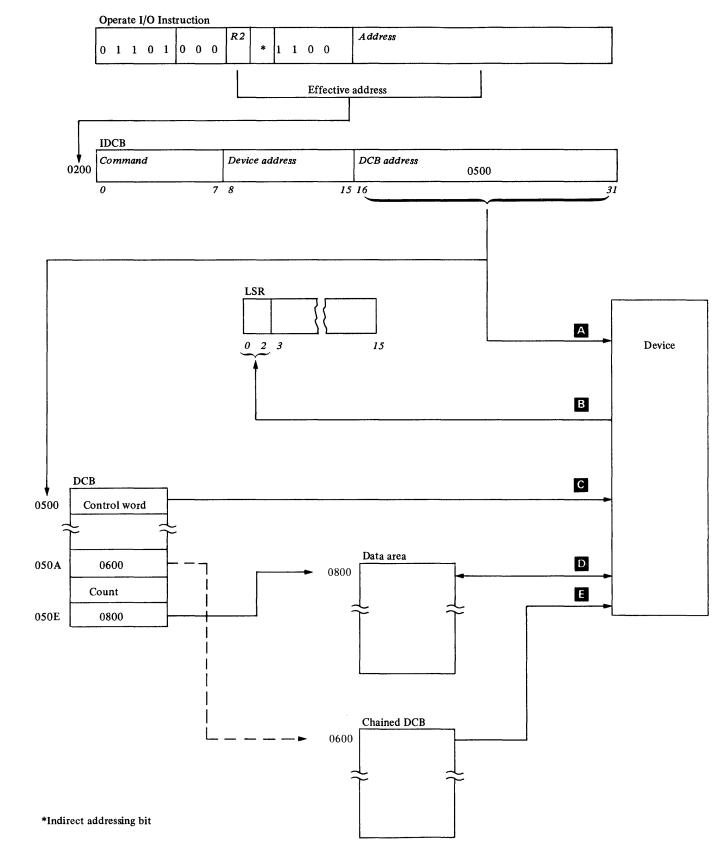

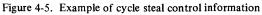

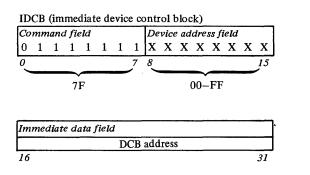

Chapter 3. Interrupts and Level Switching 3-1 Introduction 3-1 Interrupt Scheme 3-1 Automatic Interrupt Branching 3-2 I/O Interrupts 3-3 Prepare I/O Device for Interrupt 3-3 Present and Accept I/O Interrupt 3-3 Class Interrupts 3-5 Priority of Class Interrupts 3-5 Present and Accept Class Interrupt 3-6 Summary of Class Interrupts 3-9 Recovery from Error Conditions 3-9 Program Check 3-9 Storage Parity Check 3-10 CPU Control Check 3-10 I/O Check 3-10 Soft Exception Trap 3-10 Processor Status Word 3-10 Program Controlled Level Switching 3-12 Selected Level Lower Than Current Level and In-process Flag On 3-13 Selected Level Equal to Current Level and In-process Flag On 3-13 Selected Level Higher Than Current Level and In-process Flag On 3-13 Selected Level Lower Than Current Level and In-process Flag Off 3-14 Selected Level Equal to Current Level and In-process Flag Off 3-14 Selected Level Higher Than Current Level and In-process Flag Off 3-14 Interrupt Masking Facilities 3-15 Summary Mask 3-15 Interrupt Level Mask Register 3-15 Device Mask (I-bit) 3-15 Chapter 4. Input/Output Operations 4-1 Operate I/O Instruction 4-2 Immediate Device Control Block (IDCB) 4-3 Device Control Block (DCB) 4-5 I/O Commands 4-6 DPC Operation 4-8 Cycle Steal 4-10 Start Operation 4-10 Start Cycle Steal Status Operation 4-12 Cycle-Steal Device Options 4-13 Burst Mode 4-13 Chaining 4-13 Programmed Controlled Interrupt (PCI) 4-13 Suppress Exception (SE) 4-14 Cycle-Steal Termination Conditions 4-15 I/O Condition Codes and Status Information 4-15 IO Instruction Condition Codes 4-19 Interrupt Condition Codes 4-19 I/O Status Information 4-20

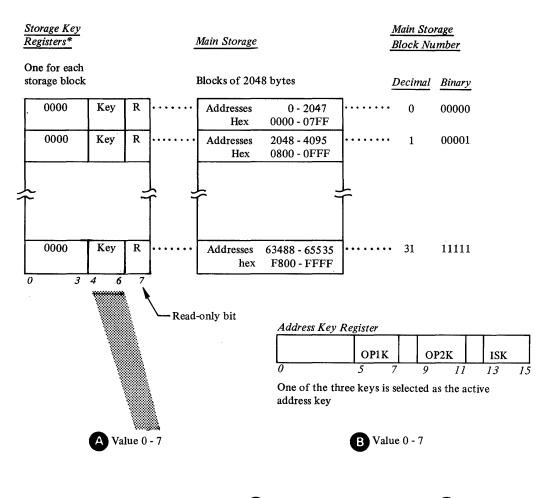

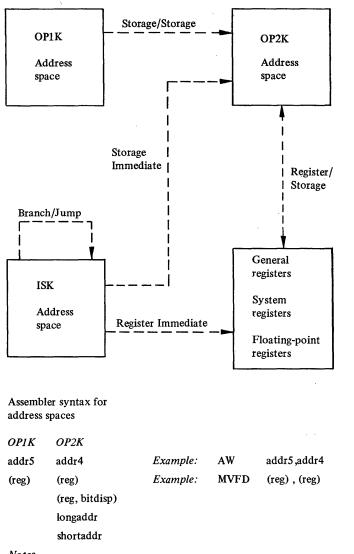

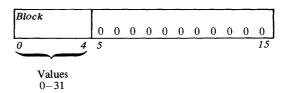

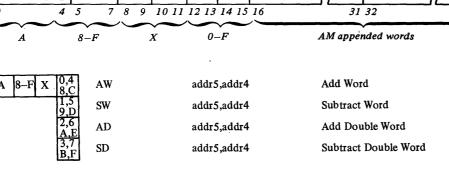

Chapter 5. Storage Protection 5-1 Storage Protection During Initial Program Load 5-3 Storage Protection in Supervisor State 5-3 Address Space Management 5-3 Active Address Key 5-3 Equate Operand Spaces (EOS) 5-3 Address Space 5-4 Address Key Values After Interrupts 5-5

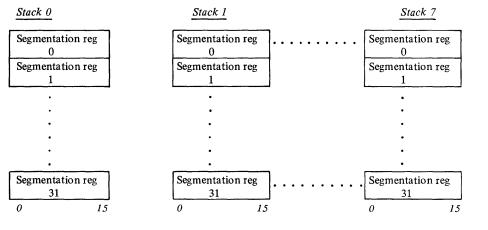

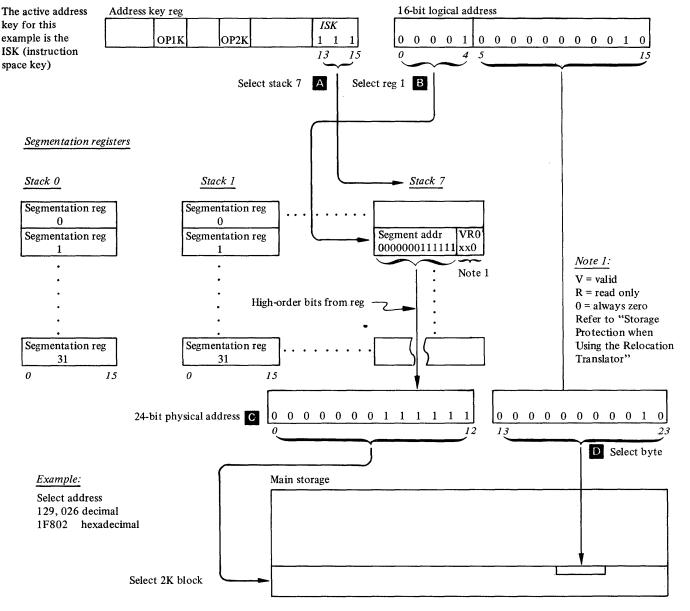

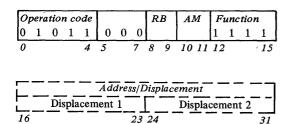

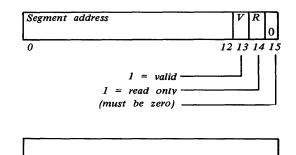

Chapter 6. Storage Address Relocation Translator Feature6-1Translator Description6-1Storage Mapping6-2Relocation Addressing6-4

$\square$

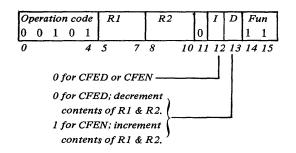

Storage Protection When Using the Relocation Translator 6-5 I/O Storage Access Using the Relocation Translator 6-5 Compatibility Between the Relocation Translator and the Storage Protection Mechanism 6-5 Characteristics That Are Similar 6-6 Characteristics That Are Dissimilar 6-6 Error Recovery Considerations 6-6 Invalid Storage Address 6-6 Protect Check 6-6 Status of Translator After Power Transitions and Resets 6-6 Instruction Execution Time When Using the Translator 6-7 Chapter 7. Console 7-1 Basic Console 7-2 Keys and Switches 7-2 Indicators 7-2 Programmer Console 7-3 Console Display 7-3 Indicators 7-4 Combination Keys/Indicators 7-5 Keys and Switches 7-7 Displaying Main Storage Locations 7-10 Storing Into Main Storage 7-10 Displaying Registers 7-11 Storing Into Registers 7-11 Chapter 8. Instructions 8-1 Exception Conditions 8-1 Program Check Conditions 8-1 Soft Exception Trap Conditions 8-1 Instruction Termination or Suppression 8-2 Instruction Descriptions 8-2 Add Byte (AB) 8-2 Add Byte Immediate (ABI) 8-3 Add Carry Register (ACY) 8-3 Add Doubleword (AD) 8-4 Register/Storage Format 8-4 Storage/Storage Format 8-4 Add Word (AW) 8-5 Register/Register Format 8-5 Register/Storage Format 8-5 Storage to Register Long Format 8-6 Storage/Storage Format 8-6 Add Word With Carry (AWCY) 8-7 Add Word Immediate (AWI) 8-7 Register Immediate Long Format 8-7 Storage Immediate Format 8-8 Branch Unconditional (B) 8-9 Branch and Link (BAL) 8-10 Branch and Link Short (BALS) 8-10 Branch on Condition (BC) 8-11 Branch on Condition Code (BCC) 8-12 Branch on Not Condition (BNC) 8-13 Branch on Not Condition Code (BNCC) 8-14 Branch on Not Overflow (BNOV) 8-15 Branch on Overflow (BOV) 8-15 Branch Indexed Short (BXS) 8-16 Compare Byte (CB) 8-17 Register/Storage Format 8-17 Storage/Storage Format 8-17 Compare Byte Immediate (CBI) 8-18 Compare Double Word (CD) 8-19 Register/Storage Format 8-19 Storage/Storage Format 8-19 Compare Byte Field Equal and Decrement (CFED) 8-20 Compare Byte Field Equal and Increment (CFEN) 8-20

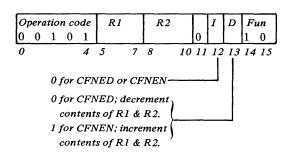

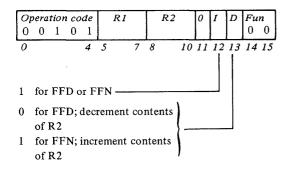

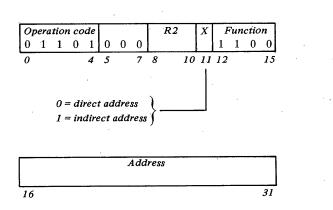

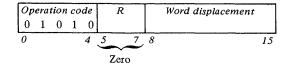

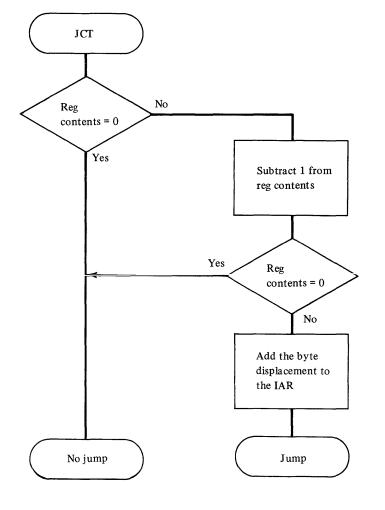

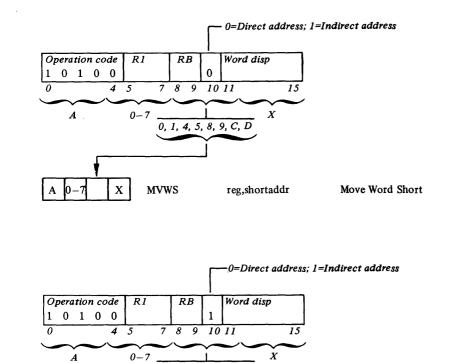

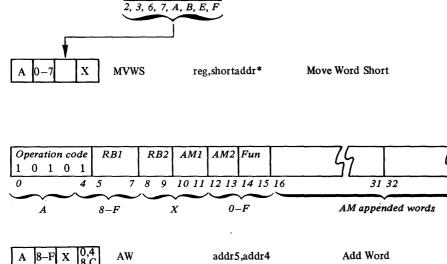

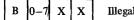

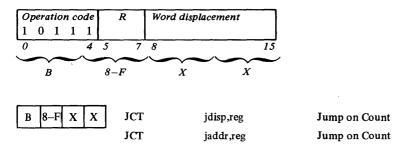

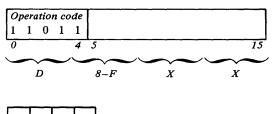

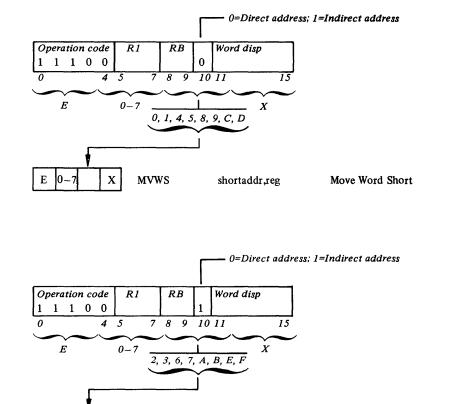

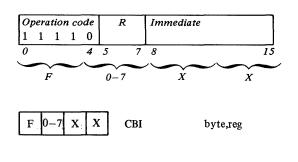

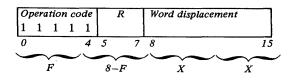

Compare Byte Field Not Equal and Increment (CFNEN) 8-21 Complement Register (CMR) 8-22 Copy Address Key Register (CPAKR) 8-23 System Register/Storage Format 8-23 System Register/Register Format 8-23 Copy Current Level (CPCL) 8-24 Copy Console Data Buffer (CPCON) 8-24 Copy Interrupt Mask Register (CPIMR) 8-25 Copy In-process Flags (CPIPF) 8-25 Copy Level Block (CPLB) 8-26 Copy Level Status Register (CPLSR) 8-26 Copy Processor Status and Reset (CPPSR) 8-27 Copy Storage Key (CPSK) 8-27 Copy Segmentation Register (CPSR) 8-28 Compare Word (CW) 8-29 Register/Register Format 8-29 Register/Storage Format 8-29 Storage/Storage Format 8-29 Compare Word Immediate (CWI) 8-30 Register Immediate Long Format 8-30 Storage Immediate Format 8-30 Divide Byte (DB) 8-31 Divide Doubleword (DD) 8-32 Diagnose (DIAG) 8-33 Disable (DIS) 8-34 Divide Word (DW) 8-35 Enable (EN) 8-36 Fill Byte Field and Decrement (FFD) 8-37 Fill Byte Field and Increment (FFN) 8-37 Operate I/O (IO) 8-38 Interchange Operand Keys (IOPK) 8-38 Interchange Registers (IR) 8-39 Jump Unconditional (J) 8-39 Jump and Link (JAL) 8-40 Jump on Condition (JC) 8-41 Jump on Count (JCT) 8-42 Jump on Not Condition (JNC) 8-43 Level Exit (LEX) 8-44 Load Multiple and Branch (LMB) 8-44 Multiply Byte (MB) 8-45 Multiply Doubleword (MD) 8-46 Move Address (MVA) 8-47 Storage Address to Register Format 8-47 Storage Immediate Format 8-47 Move Byte (MVB) 8-48 Register/Storage Format 8-48 Storage/Storage Format 8-48 Move Byte Immediate (MVBI) 8-49 Move Byte and Zero (MVBZ) 8-49 Move Doubleword (MVD) 8-50 Register/Storage Format 8-50 Storage/Storage Format 8-50 Move Doubleword and Zero (MVDZ) 8-51 Move Byte Field and Decrement (MVFD) 8-52 Move Byte Field and Increment (MVFN) 8-52 Move Word (MVW) 8-53 Register/Register Format 8-53 Register/Storage Format 8-53 Register to Storage Long Format 8-53 Storage to Register Long Format 8-54 Storage/Storage Format 8-54 Move Word Immediate (MVWI) 8-55 Storage to Register Format 8-55 Storage Immediate Format 8-55 Move Word Short (MVWS) 8-56

Compare Byte Field Not Equal and Decrement (CFNED) 8-21

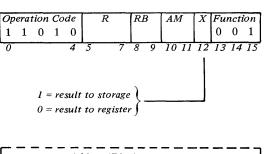

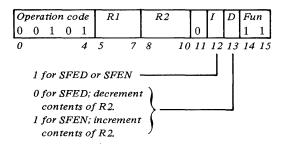

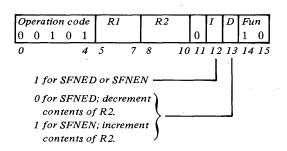

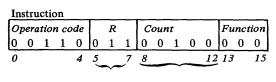

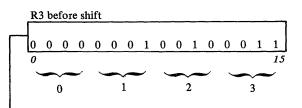

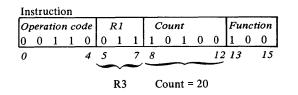

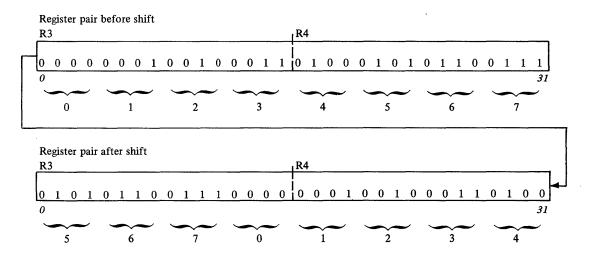

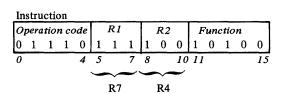

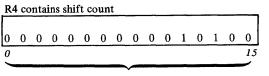

Register to Storage Format 8-56 Storage to Register Format 8-56 Move Word and Zero (MVWZ) 8-57 Multiply Word (MW) 8-58 No Operation (NOP) 8-59 AND Word Immediate (NWI) 8-59 OR Byte (OB) 8-60 Register/Storage Format 8-60 Storage/Storage Format 8-60 OR Double Word (OD) 8-61 Register/Storage Format 8-61 Storage/Storage Format 8-61 OR Word (OW) 8-62 Register/Register Format 8-62 Register/Storage Format 8-62 Storage to Register Long Format 8-63 Storage/Storage Format 8-63 OR Word Immediate (OWI) 8-64 Register Immediate Format 8-64 Storage Immediate Format 8-64 Pop Byte (PB) 8-65 Pop Doubleword (PD) 8-65 Push Byte (PSB) 8-66 Push Doubleword (PSD) 8-66 Push Word (PSW) 8-67 Pop Word (PW) 8-67 Reset Bits Byte (RBTB) 8-68 Register/Storage Format 8-68 Storage/Storage Format 8-68 Reset Bits Doubleword (RBTD) 8-69 Register/Storage Format 8-69 Storage/Storage Format 8-69 Reset Bits Word (RBTW) 8-70 Register/Register Format 8-70 Register/Storage Format 8-70 Storage to Register Long Format 8-71 Storage/Storage Format 8-71 Reset Bits Word Immediate (RBTWI) 8-72 Register Immediate Long Format 8-72 Storage Immediate Format 8-72 Subtract Byte (SB) 8-73 Subtract Carry Indicator (SCY) 8-73 Subtract Doubleword (SD) 8-74 Register/Storage Format 8-74 Storage/Storage Format 8-74 Set Address Key Register (SEAKR) 8-75 System Register/Storage Format 8-75 System Register/Register Format 8-75 Set Console Data Lights (SECON) 8-76 Set Interrupt Mask Register (SEIMR) 8-76 Set Indicators (SEIND) 8-77 Set Level Block (SELB) 8-78 Set Storage Key (SESK) 8-79 Set Segmentation Register (SESR) 8-80 Scan Byte Field Equal and Decrement (SFED) 8-81 Scan Byte Field Equal and Increment (SFEN) 8-81 Scan Byte Field Not Equal and Decrement (SFNED) 8-82 Scan Byte Field Not Equal and Increment (SFNEN) 8-82 Shift Left Circular (SLC) 8-83 Immediate Count Format 8-83 Count in Register Format 8-83 Shift Left Circular Double (SLCD) 8-84 Count in Register Format 8-85 Shift Left Logical (SLL) 8-86 Immediate Count Format 8-86 Count in Register Format 8-86

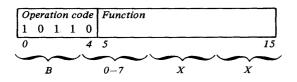

Shift Left Logical Double (SLLD) 8-87 Immediate Count Format 8-87 Count in Register Format 8-87 Shift Left and Test (SLT) 8-88 Shift Left and Test Double (SLTD) 8-88 Shift Right Arithmetic (SRA) 8-89 Immediate Count Format 8-89 Count in Register Format 8-89 Shift Right Arithmetic Double (SRAD) 8-90 Immediate Count Format 8-90 Count in Register Format 8-90 Shift Right Logical (SRL) 8-91 Immediate Count Format 8-91 Count in Register Format 8-91 Shift Right Logical Double (SRLD) 8-92 Immediate Count Format 8-92 Count in Register Format 8-92 Store Multiple (STM) 8-93 Stop (STOP) 8-94 Supervisor Call (SVC) 8-94 Subtract Word (SW) 8-95 Register/Register Format 8-95 Register/Storage Format 8-95 Storage to Register Long Format 8-96 Storage/Storage Format 8-96 Subtract Word With Carry (SWCY) 8-97 Subtract Word Immediate (SWI) 8-98 Register Immediate Long Format 8-98 Storage Immediate Format 8-98 Test Bit (TBT) 8-99 Test Bit and Reset (TBTR) 8-99 Test Bit and Set (TBTS) 8-100 Test Bit and Invert (TBTV) 8-100 Test Word Immediate (TWI) 8-101 Register Immediate Long Format 8-101 Storage Immediate Format 8-101 Invert Register (VR) 8-102 Exclusive OR Byte (XB) 8-102 Exclusive OR Doubleword (XD) 8-103 Exclusive OR Word (XW) 8-104 Register/Register Format 8-104 Register/Storage Format 8-104 Storage to Register Long Format 8-105 Exclusive OR Word Immediate (XWI) 8-105 Chapter 9. Floating-Point Feature 9-1 Data Format 9-1 Number Representation 9-1 Floating-Point Numbers 9-1 Binary Integers in Main Storage 9-2 Normalization 9-2 Programming Considerations 9-2 Floating-Point Feature Not Installed 9-2 Floating-Point Registers 9-2 Arithmetic Indicators 9-2 Floating-Point Exceptions 9-2 Level Control 9-3 Instruction Termination or Suppression 9-3 Floating-Point Instructions 9-3 Instruction Formats 9-4 Exception Conditions 9-4 Program Check Conditions 9-4 Soft Exception Trap Conditions 9-5 Instruction Descriptions 9-6 Copy Floating Level Block (CPFLB) 9-6 Floating Add (FA) 9-7

General Description (Short Precision) 9-7 Storage/Register Format 9-7 Register to Register Format 9-7 Floating Add Double (FAD) 9-8 General Description (Double Precision) 9-8 Storage/Register Format 9-8 Register to Register Format 9-8 Floating Compare (FC) 9-9 Floating Compare Double (FCD) 9-9 Floating Divide (FD) 9-10 Storage/Register Format 9-10 Register to Register Format 9-10 Floating Divide Double (FDD) 9-11 Storage/Register Format 9-11 Register to Register Format 9-11 Floating Multiply (FM) 9-12 General Description (Short Precision) 9-12 Storage/Register Format 9-12 Register to Register Format 9-12 Floating Multiply Double (FMD) 9-13 General Description (Double Precision) 9-13 Storage/Register Format 9-13 Register to Register Format 9-13 Floating Move (FMV) 9-14 Storage to Register Format 9-14 Register to Storage Format 9-14 Register to Register Format 9-14 Floating Move and Convert (FMVC) 9-15 Storage to Register Format 9-15 Register to Storage Format 9-15 Floating Move and Convert Double (FMVCD) 9-16 Storage to Register Format 9-16 Register to Storage Format 9-16 Floating Move Double (FMVD) 9-17 Storage to Register Format 9-17 Register to Storage Format 9-17 Register to Register Format 9-17 Floating Subtract (FS) 9-18 General Description (Short Precision) 9-18 Storage/Register Format 9-18 Register to Register Format 9-18 Floating Subtract Double (FSD) 9-19 General Description (Double Precision) 9-19 Storage/Register Format 9-19 Register to Register Format 9-19 Set Floating Level Block (SEFLB) 9-20

Appendix A. Instruction Execution Times A-1 Table 1. Instruction Times – Relocation Translator Not Installed or Disabled A-4 Table 2. Instruction Times – Relocation Translator Enabled A-14

Appendix B. Instruction Formats B-1

Appendix C. Assembler Syntax C-1 Coding Notes C-1 Legend for Machine Instruction Operands C-1

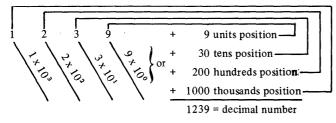

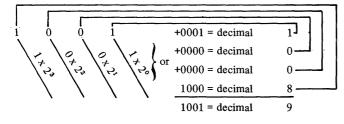

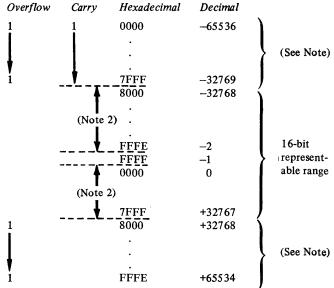

Appendix D. Numbering Systems and Conversion Tables D-1

Binary and Hexadecimal Number Notations D-1 Binary Number Notation D-1 Hexadecimal Number System D-1

Hexadecimal – Decimal Conversion Tables D-2

Appendix E. Character Codes E-1

Appendix F. Carry and Overflow IndicatorsF-1Signed NumbersF-1Unsigned NumbersF-2Carry Indicator SettingF-3Add Operation ExamplesF-3Subtract Operation ExamplesF-4Overflow Indicator SettingF-4ExamplesF-5

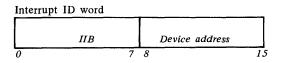

Appendix G. Reference InformationG-1Address Key Register (AKR)G-1Condition CodesG-1I/O Instruction Condition CodesG-1Interrupt Condition CodesG-1General RegistersG-1Interrupt Status Byte (ISB)G-1DPC DevicesG-1Cycle Steal DevicesG-2Level Status Register (LSR)G-2Processor Status Word (PSW)G-2

Index X-1

Index of Instructions by Format X-12

Index of Instructions by Name X-15

This publication describes the functional characteristics of the IBM 4955 Processor and the processor optional features. It assumes that the reader understands data processing terminology and is familiar with binary and hexadecimal numbering systems. The publication is intended primarily as a reference manual for experienced programmers who require machine code information to plan, correct, and modify programs written in the assembler language.

# **Summary of Publication**

- Chapter 1. Introduction is an introduction to the system architecture. It contains a general description of the processor, storage, features, and a list of attachable I/O devices.

- Chapter 2. Processing Unit Description contains a description of the processor hardware including registers and indicators.

Main storage data formats and addressing are presented in this chapter.

- A section titled "Program Execution" is included and covers:

- Basic instruction formats

- Effective address generation

- Processor state control

- Initial program load (IPL)

- Jumping and branching

- Level switching and interrupts

- Stack operations

- Chapter 3. Interrupts and Level Switching describes the priority interrupt levels and the interrupt processing for (1) I/O devices, and (2) class interrupts. Related topics are:

- Program controlled level switching

- Interrupt masking facilities

- Recovery from error conditions

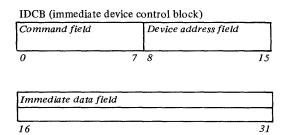

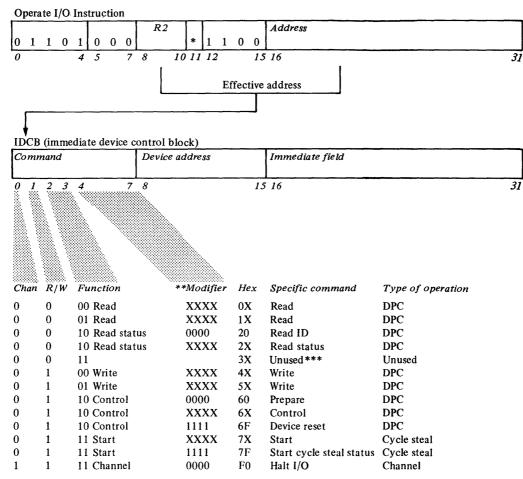

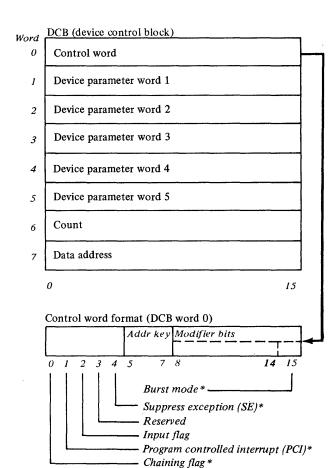

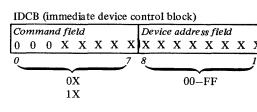

- Chapter 4. Input/Output Operations describes the I/O commands and control words that are used to operate the I/O devices. Condition codes and status information relative to the I/O operation are also explained. Specific command and status-word bit structures are contained in the I/O device description books.

- Chapter 5. Storage Protection describes the operation of the storage protection mechanism.

- Chapter 6. Storage Address Relocation Translator Feature describes the optional relocation translator feature including:

- Relocation addressing

- Effects on storage protection mechanism

- Error recovery considerations

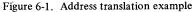

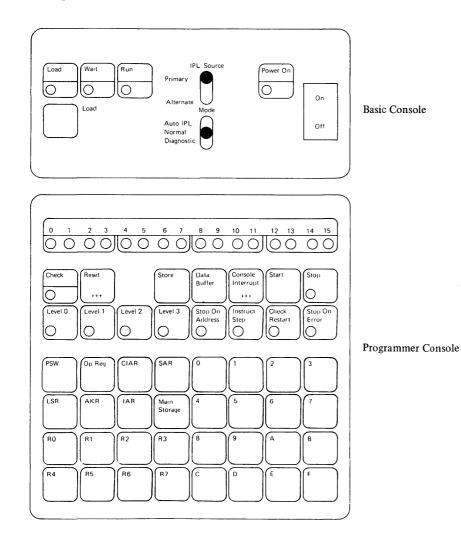

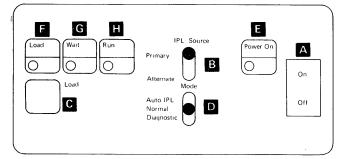

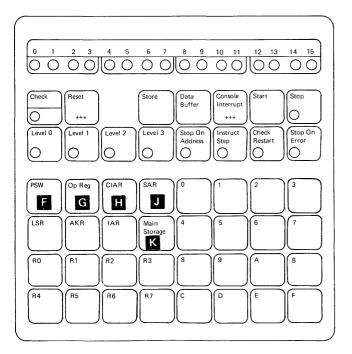

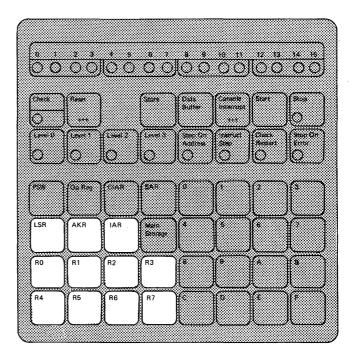

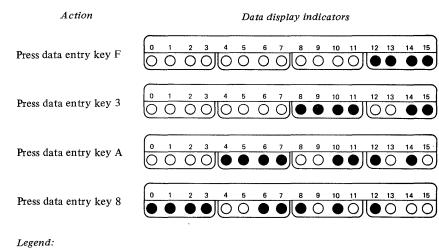

- Chapter 7. Console describes the keys, switches, and indicators for the basic console and the optional programmer console. Typical manual operations such as storing into and displaying main storage are presented.

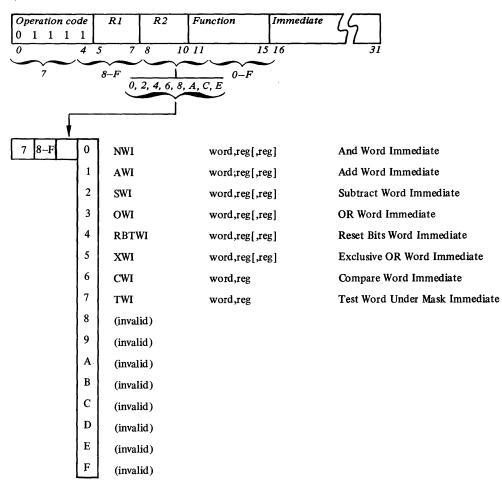

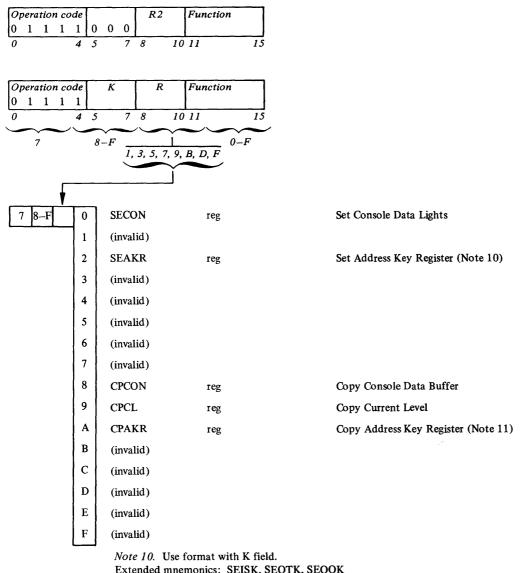

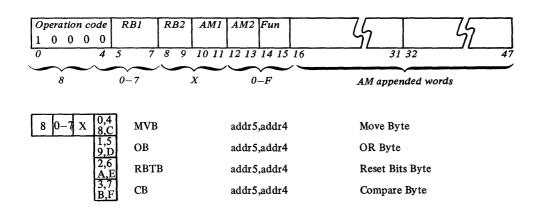

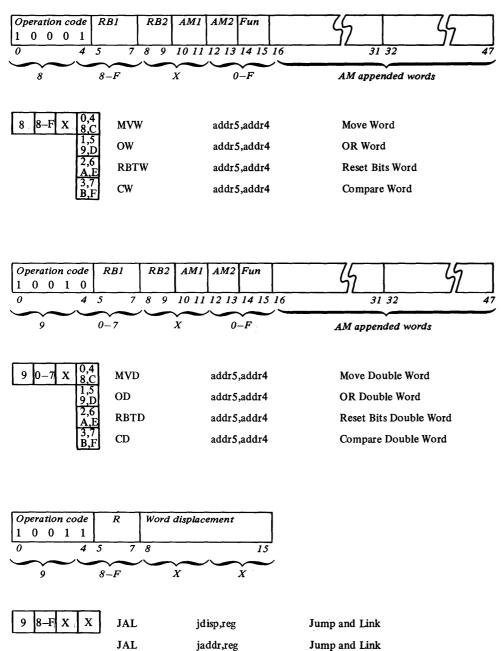

- Chapter 8. Instructions describes the basic instruction set, including indicator settings and possible exception conditions. Individual instruction word formats are included and contain bit combinations for the operation code and function fields. The instructions are arranged in alphabetical sequence based on assembler mnemonics.

- Chapter 9. Floating-Point Feature describes the optional floating-point feature including the floating-point instruction set.

- Appendixes:

- Instruction execution times

- Instruction formats

- Assembler syntax

- Numbering systems and conversion tables

- Character codes

- Carry and overflow indicators

- Reference information

# **Related Publications**

- IBM Series/1 System Summary, GA34-0035

- IBM Series/1 Installation Manual Physical Planning, GA34-0029

- IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit Description, GA34-0024

- IBM Series/1 4973 Line Printer Description, GA34-0044

- IBM Series/1 4974 Printer Description, GA34-0025

- IBM Series/1 4979 Display Station Description, GA34-0026

- IBM Series/1 4982 Sensor Input/Output Unit Description, GA34-0027

- IBM Series/1 Communications Features Description, GA34-0028

- IBM Series/1 Attachment Features Description, GA34-0031

- IBM Series/1 Battery Backup Unit Description, GA34-0032

- IBM Series/1 User's Attachment Manual, GA34-0033

# Chapter 1. Introduction

The IBM 4955 Processor is a compact, general purpose computer and has the following general characteristics:

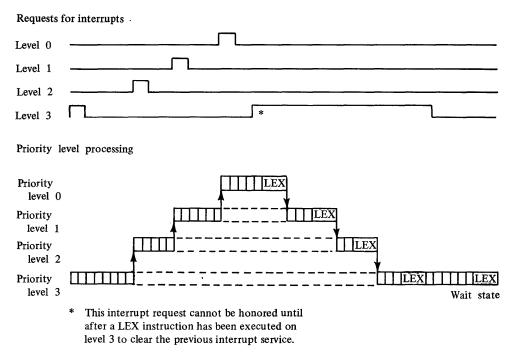

• Four priority interrupt levels – independent registers and status indicators for each level. Automatic and program controlled level switching.

- Four processor models are available:

- Model A: 16K bytes basic storage. Additional storage in 16K byte increments up to 64K bytes maximum.

- Model B: 16K bytes basic storage. Additional storage in 16K byte increments up to 128K bytes maximum.

- Model C: 32K bytes basic storage. Additional storage in 32K\* byte increments up to 64K bytes maximum.

- Model D: 32K bytes basic storage. Additional storage in 32K\* byte increments up to 128K bytes maximum.

- FET (field effect transistor) main storage. Read or write time is 300 nanoseconds (660 nanoseconds required between two storage access cycles). Odd parity by byte is maintained throughout storage.

- TTL (transistor-transistor logic) processor technology.

- Microprogram control microcycle time: 220 nanoseconds.

- Instruction set that includes: stacking and linking facilities, multiply and divide, variable field-length byte operations, and a variety of arithmetic and branching instructions.

- Supervisor and problem states.

- Packaged in a 19-inch rack mountable unit full width.

- Basic console standard in processor unit. Programmer console optional.

- Channel capability.

- Asynchronous, multidropped channel.

- 256 I/O (input/output) devices can be addressed.

- Direct program control and cycle steal operations.

- Maximum burst data rate is 1.8 megabytes per second for storage input cycles, and 1.5 megabytes per second for storage output cycles. When multiple cycle stealing devices are interleaved, the maximum aggregate data rate is 1.65 megabytes per second.

The processor unit contains power and space for additional features and storage. The IBM 4959 Input/Output Expansion Unit is available for additional features.

The processor unit is described in the following sections of this chapter.

#### IBM 4955 Processor

#### **Processor Optional Features/Storage Addition**

- Storage Address Relocation Translator (permits addressing of main storage larger than 64K bytes).

- Storage Addition 16,384 bytes.

- provides storage in 16K byte increments for all processor models.

- Model A has a limit of four 16K cards (64K bytes total).

- Model B has a limit of eight 16K cards (128K bytes total).

- Models C and D have a limit of one 16K card and it must be installed as the last storage card. That is: any 32K cards would be installed between the 16K card and the processor cards.

- Storage Addition -32,768 bytes.

- provides storage in 32K byte increments for processor Models C and D.

- Model C has a limit of two 32K cards (64K bytes total).

- Model D has a limit of four 32K cards (128K bytes total).

- Programmer Console.

- Floating-Point.

# **Processor Description**

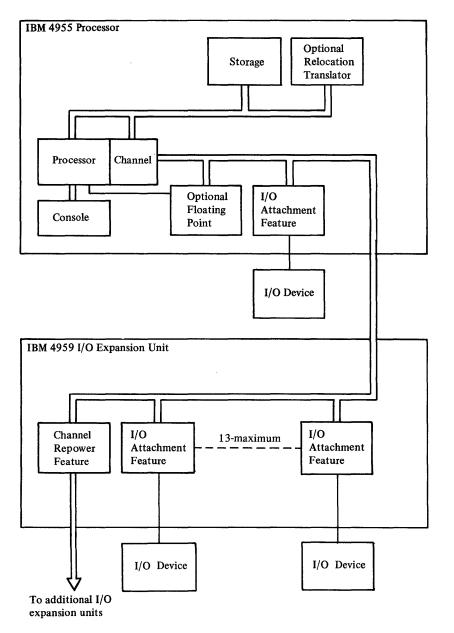

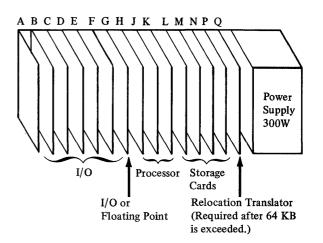

The basic IBM 4955 Processor includes the processor, basic storage, and a basic console. These items are packaged in a unit, called the processor unit. Figure 1-1 shows a block diagram of an IBM 4955 Processor and an IBM 4959 Input/Output Expansion Unit.

<sup>\*</sup>Models C and D may have one 16K byte storage card installed as the last storage card.

The processor is microprogram controlled, utilizing a 220 nanosecond microcycle. Circuit technology is TTL (transistor-transistor logic).

Four priority interrupt levels are implemented in the processor. Each level has an independent set of machine registers. Level switching can occur in two ways: (1) by program control, or (2) automatically upon acceptance of an I/O interrupt request. The interrupt mechanism provides 256 unique entry points for I/O devices.

The processor instruction set contains a variety of instruction types. These include: shift, register to register, register immediate, register to (or from) storage, bit manipulation, multiple register to storage, variable byte field, and storage to storage. Supervisor and problem states are implemented, with appropriate privileged instructions for the supervisor.

A floating-point feature is available that supplements the standard instruction set. The floating-point instructions include single and double precision types for: add, subtract, multiply, divide, compare, and move.

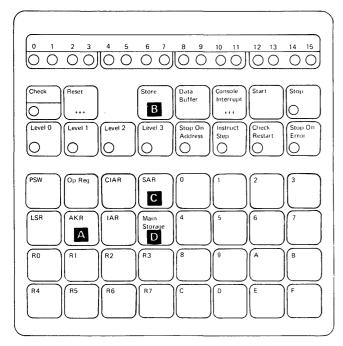

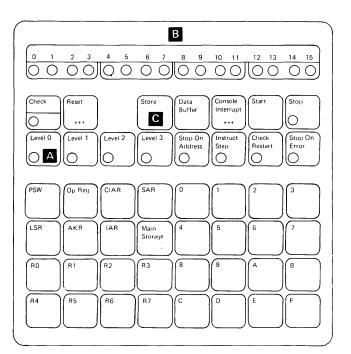

The basic console is intended for dedicated systems that are used in a basically unattended environment. Only minimal controls are provided. A programmer console can be added as a feature; this console provides a variety of indicators and controls for operator-oriented systems.

Main storage technology is FET (field-effect transistor). Basic storage supplied is model dependent. Two storage additions provide additional storage in 16K or 32K byte increments. The maximum total storage is model dependent. Beyond 64K bytes the storage address relocation translator feature is required. This feature increases the addressing capability beyond 64K bytes and allows a maximum total storage of 128K bytes. The read/write access time for main storage is 300 nanoseconds. However, the minimum duration of time between successive storage cycles is 660 nanoseconds. Storage protection is standard. It protects against (1) access (reading and writing) to defined blocks of storage by software or by an I/O operation, and (2) writing in an undesired location within a defined block by software.

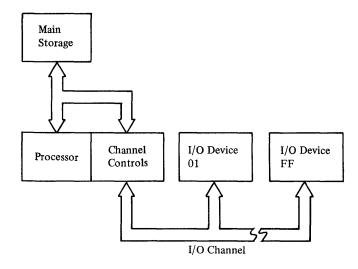

I/O devices are attached to the processor through the processor I/O channel. The channel directs the flow of information between the I/O devices, the processor, and main storage. This channel accommodates a maximum of 256 addressable devices.

The channel supports:

- Direct program control operations. Each Operate I/O instruction transfers a byte or word of data between main storage and the device. The operation may or may not terminate in an interrupt.

- Cycle Steal operations. Each Operate I/O instruction initiates multiple data transfers between main storage and the device (65,535 bytes maximum). Cycle steal operations are overlapped with processing operations and always terminate in an interrupt.

- *Interrupt Servicing*. Interrupt requests from the devices, along with cycle steal requests, are presented and polled concurrently with data transfers.

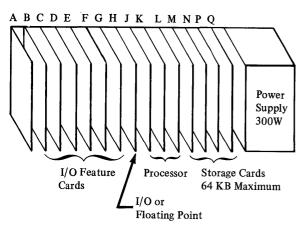

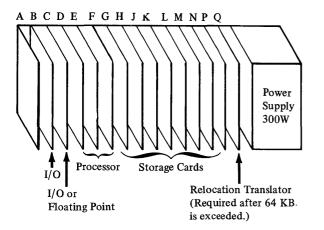

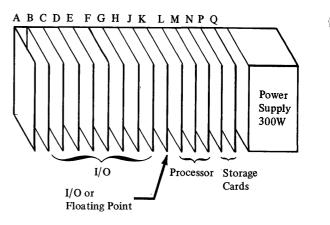

The processor is packaged in a standard 48.3 cm (19 in) rack-mountable unit, called the processor unit. All processor units contain an integral power supply, fans, and the basic console. Refer to the *Series/1 Installation Manual – Physical Planning*, GA34-0029, for environmental characteristics. Four processor models are available. Figure 1-2 shows the IBM 4955 Processor models and the card plugging assignments.

#### **IBM 4955 Processor Models**

| Model                     | A   | B    | С   | D    |

|---------------------------|-----|------|-----|------|

| Storage capacity (bytes)* | 64K | 128K | 64K | 128K |

| I/O feature cards**       | 8   | 3    | 10  | 7    |

- \* The relocation translator feature is required when the total storage exceeds 64K bytes.

- \*\* The floating-point feature can be substituted for one of the I/O feature cards and must be installed adjacent to the processor.

4955 Model A Card Plugging Assignments

4955 Model B Card Plugging Assignments

4955 Model C Card Plugging Assignments

4955 Model D Card Plugging Assignments

The A position for all models is reserved for the I/O cables or (due to voltage limitations) one of the following I/O feature cards:

- Teletypewriter Adapter Feature using TTL voltage levels

- Teletypewriter Adapter Feature using isolated current loop where customer supplies external ±12V power

- Timer Feature

- Customer Direct Program Control Adapter Feature

- 4982 Sensor Input/Output Unit Attachment Feature

- Integrated Digital Input/Output Non-Isolated Feature

- Channel Repower Feature

# Input/Output Units and Features

- IBM 4962 Disk Storage Unit (4 models)

- Requires 4962 Disk Storage Unit Attachment Feature

IBM 4964 Diskette Unit

- Requires 4964 Diskette Unit Attachment Feature

- IBM 4979 Display Station

Requires 4979 Display Station Attachment Feature

- IBM 4973 Line Printer (2 models) - Requires 4973 Printer Attachment Feature

- IBM 4974 Printer

- Requires 4974 Printer Attachment Feature

- Timers Feature (2 timers)

- Teletypewriter Adapter Feature

- Customer Direct Program Control Adapter Feature

The feature cards for attaching the I/O units can be housed in either the processor unit or the I/O expansion unit.

Information about these units and features can be found in separate publications. The order numbers for these publications are listed in the preface of this manual.

# **Communications Features**

- Asynchronous Communications Single Line Control

- Asynchronous Communications 8 Line Control

- Asynchronous Communications 4 Line Adapter

- Binary Synchronous Communications Single Line Control

- Binary Synchronous Communications Single Line Control/High Speed

- Synchronous Data Link Control Single Line Control

- Binary Synchronous Communications 8 Line Control

- Binary Synchronous Communications 4 Line Adapter

- Communications Power Feature

- Communications Indicator Panel

Refer to the publication, *IBM Series/1*, *Communications Features Description*, GA34-0028, for a description of these features.

# Sensor Input/Output Options

- Integrated Digital Input/Output Non-Isolated Feature

- 4982 Sensor Input/Output Unit Attachment Feature

The integrated digital input/output non-isolated feature provides digital sensor I/O and simple attachment for non-IBM equipment. The feature card can be housed in either the processor unit or the I/O expansion unit. Refer to the publication, *IBM Series/1 Attachment Features Description*, GA34-0031, for a description of this feature.

The 4982 sensor input/output attachment unit feature card is housed in either the processor or the I/O expansion unit. Refer to the publication, *IBM Series/1*, 4982 Sensor Input/Output Unit Description, GA34-0027, for a description of the 4982 and associated features.

# Packaging and Power Options

- IBM 4959 Input/Output Expansion Unit

- IBM 4999 Battery Backup Unit

- IBM 4997 Rack Enclosure (1 metre) 2 models

- IBM 4997 Rack Enclosure (1.8 metre) 2 models

The IBM 4959 Input/Output Expansion Unit is available for adding I/O feature cards beyond the capacity of the processor unit. I/O cables (for the I/O channel) are used to attach this unit to the processor. The capacity of the I/O expansion unit is either (1) fourteen I/O feature cards, or (2) thirteen I/O feature cards plus a channel repower card. A channel repower card is required to power each additional I/O expansion unit.

The IBM 4999 Battery Backup Unit permits the processor unit (excluding external devices) to operate from a usersupplied battery when a loss or dip in line power occurs. The battery backup unit is explained in a separate publication. Refer to the preface of this manual for the order number.

# **Other Options**

Additional options such as communications cables, customer access panel, and a channel socket adapter are also available. For a list and description of system units and features, refer to the *IBM Series/1 System Summary*, GA34-0035.

1-6 GA34-0021

.

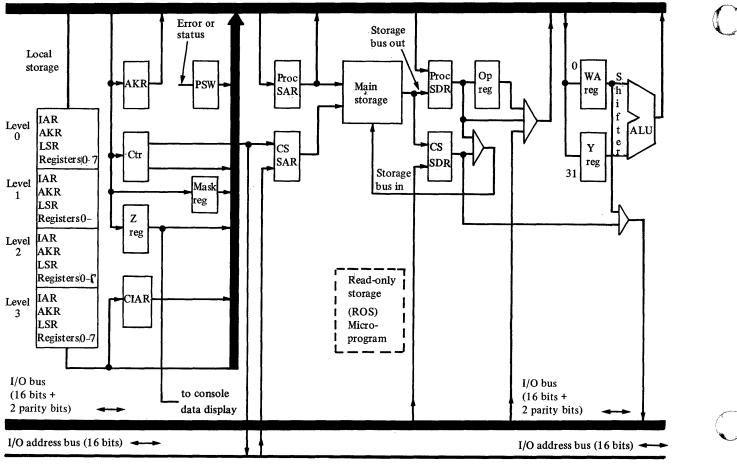

Figure 2-1 shows the general data flow for the IBM 4955 Processor. The major functional units shown in the data flow are discussed in the following sections.

## Main Storage

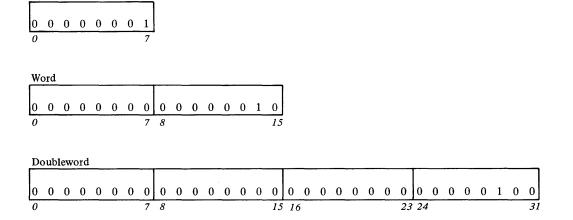

Main storage holds data and instructions for applications to be processed on the system. The data and instructions are stored in units of information called a byte. Each byte consists of eight binary data bits. Associated with each byte is a parity bit. Odd parity by byte is maintained throughout storage; even parity causes a machine check error. Formats shown in this manual exclude the parity bit(s) because they are not a part of the data flow manipulated by the instructions.

The bits within a byte are numbered consecutively, left to right, 0 through 7. When a format consists of multiple bytes, the numbering scheme is continued; for example, the bits in the second byte would be numbered 8 through 15. Leftmost bits are sometimes referred to as high-order bits and rightmost bits as low-order bits.

Bytes can be handled separately or grouped together. A *word* is a group of two consecutive bytes, beginning on an even address boundary, and is the basic building block of instructions. A *doubleword* is a group of four consecutive bytes beginning on an even address boundary.

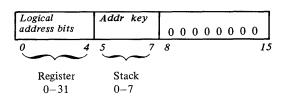

#### Addressing Main Storage

Each byte location in main storage is directly addressable. Byte locations in storage are numbered consecutively, starting with location zero; each number is considered the address of the corresponding byte. Storage addresses are 16-bit unsigned binary numbers. This permits a direct addressing range of 65,536 bytes:

#### Address Range

| 16-bit binary address | Hexadecimal | Decimal |  |  |  |

|-----------------------|-------------|---------|--|--|--|

| 0000 0000 0000 0000   | 0000        | 0       |  |  |  |

| to                    | to          | to      |  |  |  |

| 1111 1111 1111 1111   | FFFF        | 65,535  |  |  |  |

*Note.* Addresses that overflow or underflow the addressing range address wrap modulo 65,536.

When the *Storage Address Relocation Translator Feature* is installed, the 16-bit address is used as a logical address to generate a 24-bit physical address.

#### Instruction and Operand Address Boundaries

As previously stated, all storage addressing is defined by byte location. Instructions can refer to bits, bytes, byte strings, words, or doublewords as data operands. All word and doubleword operand addresses must be on even byte boundaries. All word and doubleword operand addresses point to the most significant (leftmost) byte in the operand. Bit addresses are specified by a byte address and a bit displacement.

#### Processor bus (16 bits)

Legend:

- AKR Address key register

- ALU Arithmetic and logic unit

- CIAR Current instruction address register

- CS Cycle steal

- Ctr Counter

- IAR Instruction address register

- LSR Level status register

- Mask Interrupt level mask register

- Op Operation register

- Proc Processor

- PSW Processor status word

- SAR Storage address register

- SDR Storage data register

- WA Work/shift register

- Y Work/shift register

- Z Console data

Figure 2-1. Data flow for the IBM 4955 Processor

C

To provide maximum addressing range, some instructions refer to a word displacement that is added to the contents of a register. In these cases, the operand is a word and the register must contain an even byte address for valid results. Effective address generation is described in a subsequent section of this chapter.

All instructions must be on an even byte boundary. This implies that the effective address for all branch type instructions must be on an even byte boundary to be valid.

If any of the aforementioned rules are violated, a program check interrupt occurs with *specification check* set in the processor status word (PSW). The instruction is suppressed.

#### Arithmetic and Logic Unit (ALU)

The arithmetic and logic unit (ALU) contains the hardware circuits that perform: addition; subtraction; and logical operations such as AND, OR, and exclusive OR. The ALU performs address arithmetic as well as the operations required to process the instruction operands. Operands may be regarded as signed or unsigned by the programmer. However, the ALU does not distinguish between them. Numbering representation is discussed in a subsequent section of this chapter. For many instructions, indicators are set to reflect the result of the ALU operation. The indicators are discussed in a subsequent section of this chapter.

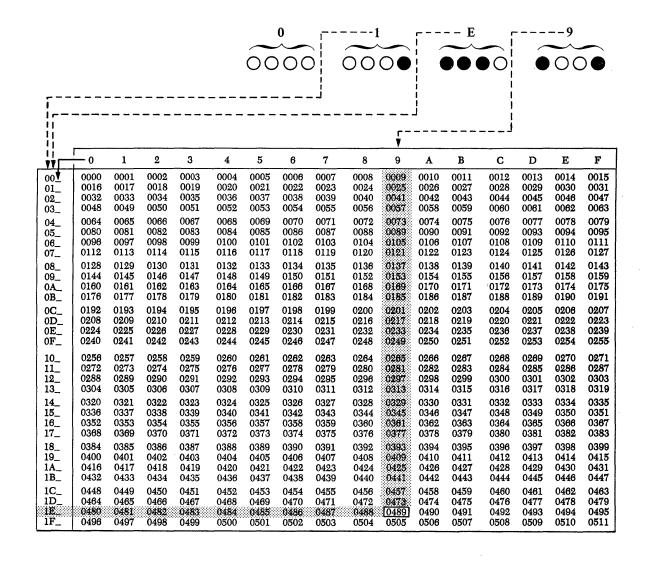

#### Numbering Representation

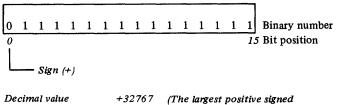

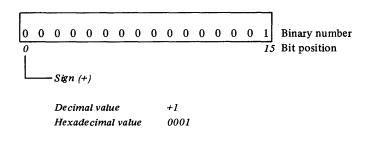

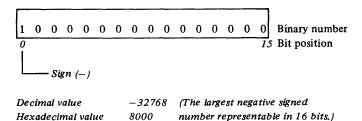

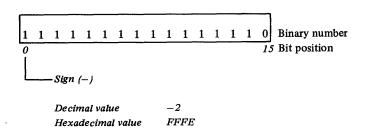

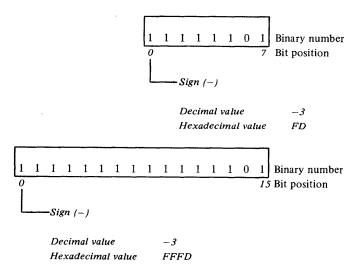

Operands may be signed or unsigned depending on how they are used by the programmer. An unsigned number is a binary integer in which all bits contribute to the magnitude. A storage address is an example of an unsigned number. A signed number is one where the high-order bit is used to indicate the sign, and the remaining bits define the magnitude. Signed positive numbers are represented in true binary notation with the sign bit (high-order bit) set to zero. Signed negative numbers are represented in two's complement notation with the sign bit (high-order bit) set to one. The two's complement of a number is obtained by inverting each bit of the number and adding a one to the low-order bit position. Two's complement notation does not include a negative zero. The maximum positive number consists of an all-one integer field with a sign bit of zero; whereas, the maximum negative number (the negative number with the greatest absolute value) consists of an all-zero integer field with a one-bit for the sign.

The following examples show: (1) an unsigned 16-bit number, (2) a signed 16-bit positive number, and (3) a signed 16-bit negative number.

Example of an unsigned 16-bit number:

| 1<br>0    | 1 | 1 | 1 | 1 | 1  | 1 | 1 | 1         | 1 | 1 | 1 | 1 | 1 | 1 | <br>Binary number<br>5 Bit position |

|-----------|---|---|---|---|----|---|---|-----------|---|---|---|---|---|---|-------------------------------------|

| De<br>He: |   |   |   |   | ue |   |   | 535<br>FF | • |   |   |   | - |   | igned number<br>16 bits.)           |

Example of a signed 16-bit positive number:

Hexadecimal value 7FFF number representable in 16 bits.)

When the number is positive, all bits to the left of the most significant bit of the number, including the sign bit, are zero:

Example of a signed 16-bit negative number:

*Note.* This form of representation yields a negative range of one more than the positive range.

When the number is negative, all bits to the left of the most significant bit of the number, including the sign bit, are set to one:

When a signed-number operand must be extended with high-order bits, the expansion is achieved by prefixing a field with each bit set equal to the high-order bit of the operand.

Example of an 8-bit field extended to a 16-bit field:

It must be emphasized that when performing the add and subtract operations, the machine does not regard the number as either signed or unsigned, but performs the designated operation on the values presented. Whether a given add or subtract operation is to be regarded as a signed operation or an unsigned operation is determined by the programmer's view of the values being presented as operands. The carry indicator and the overflow indicator of the LSR are changed on various operations to reflect the result of that operation. This allows the programmer to make result tests for the number representation involved. The carry and overflow indicator settings are explained in a subsequent section.

# Registers

Registers in the processor are provided in two categories:

- 1. Per-system register (the register is provided only once and is used by all priority interrupt levels)

- 2. Per-level register (the register is duplicated for each priority interrupt level)

Information that must be saved when a level is preempted is retained in registers supplied for a specific level. Information that pertains only to the current process is kept in registers common to all levels. The registers in each category are listed in this section. Descriptions for each of the registers appear in subsequent sections. Only registers accessible to the program or the operator (via console operations) are discussed.

Registers supplied on a per-system basis:

- Console address key register

- Console data buffer

- Current-instruction address register (CIAR)

- Mask register (interrupt level)

- Processor status word (PSW)

- Segmentation registers (optional) see Chapter 6, Storage Address Relocation Translator Feature.

- Storage address register (SAR)

Registers supplied on a per-level basis:

- Address key register (AKR)

- Floating-point registers (optional) see Chapter 9, *Floating-Point Feature.*

- General registers (8 per level)

- Instruction address register (IAR)

- Level status register (LSR)

*Note.* For a specific level, the contents of the AKR, IAR, LSR, and the general registers are known as a level status block (LSB). The LSB is a 22 byte entity used by hardware and software for task control and task switching.

#### Per-system Registers

#### **Console Address Key Register**

The Console AKR is not addressable by software. When the programmer console is installed, this register is used for certain console operations. Refer to *Programmer Console* in Chapter 7.

#### **Console Data Buffer**

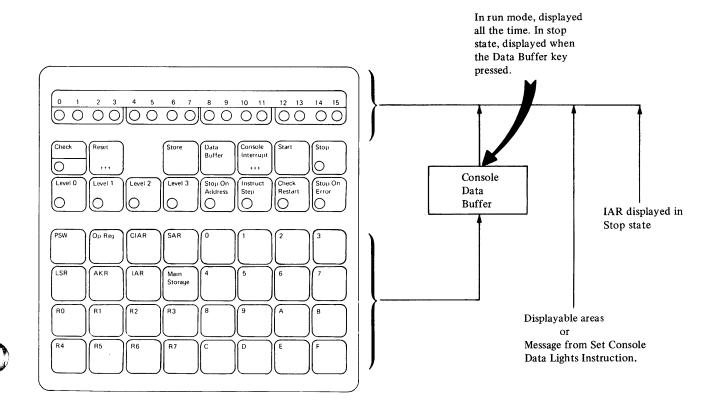

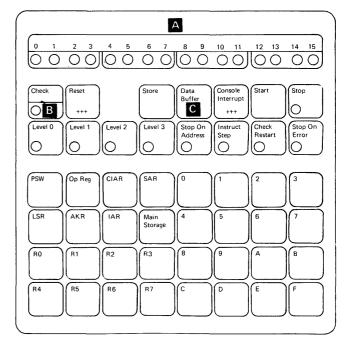

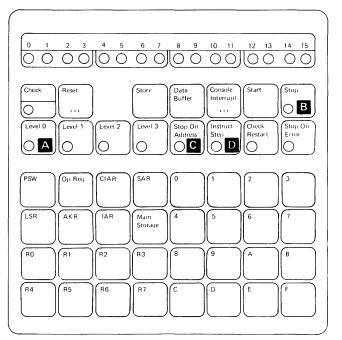

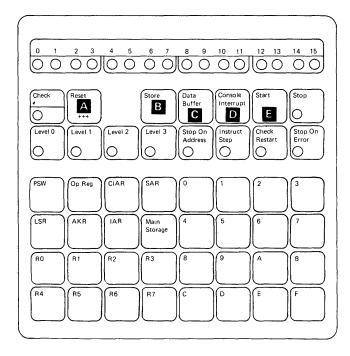

The console data buffer is a 16-bit register associated with the programmer console feature. Details of how the buffer is used are explained in the programmer console section of Chapter 7. The contents of the console data buffer can be loaded into a specified general register by using the Copy Console Data Buffer (CPCON) instruction (see Chapter 8).

## Current-Instruction Address Register (CIAR)

When the processor enters the stop state, the currentinstruction address register (CIAR) contains the address of the last instruction that was executed. The CIAR is not addressable by software. It may be displayed from the optional programmer console. Refer to *Stop State* in this chapter for methods of entering stop state.

#### Mask Register

The mask register is a 4-bit register used for control of interrupts. Bit 0 controls level 0, bit 1 controls level 1, and so on.

A one bit enables interrupts on a level, while a zero bit disables interrupts. For example if bit 3 is set to a one, interrupts are enabled on level 3.

# Processor Status Word (PSW)

The processor status word (PSW) is a 16-bit register used to (1) record error or exception conditions that may prevent further processing, and (2) hold certain flags that aid in error recovery. Error or exception conditions recorded in the PSW result in a class interrupt. Each bit in the PSW is described in detail in Chapter 3. The PSW can be accessed by using the Copy Processor Status and Reset (CPPSR) instruction (see Chapter 8).

## Storage Address Register (SAR)

The storage address register (SAR) is a 16-bit register that contains the main-storage address for the last attempted processor storage cycle. This register is addressable by the Diagnose instruction and may be altered or displayed from the optional programmer console.

# Per-level Registers

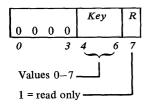

#### Address Key Register (AKR)

The address key register (AKR) is a 16-bit register that contains three address keys and an address-key control bit. This register is associated with the storage protection mechanism. Separate 3-bit fields contain an address key for (1) instruction address space, (2) operand-1 address space, and (3) operand-2 address space. Refer to *Storage Protection* and *Address Space Management* in Chapter 5 for further information.

## **General Registers**

Subsequently referred to simply as registers, the general registers are 16-bit registers available to the program for general purposes. Eight registers are provided for each level. The R and RB fields in the instructions control the selection of these registers.

## Instruction Address Register (IAR)

The instruction address register (IAR) is a 16-bit register that holds the main storage address used to fetch an instruction. After an instruction has been fetched, the IAR is updated to point to the next instruction to be fetched.

Note. These registers are sometimes referred to as IARO, IAR1, IAR2, and IAR3. The numbers represent the priority level associated with the register.

#### Level Status Register (LSR)

The level status register (LSR) is a 16-bit register that holds:

- Indicator bits

- Set as a result of arithmetic, logical, or I/O operations

- A supervisor state bit

- An in-process bit

- A trace bit

- A summary mask bit

These bits are further discussed in the following sections. Seven other bits in the LSR are not used and are always set to zero.

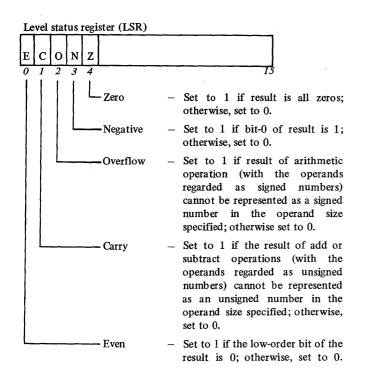

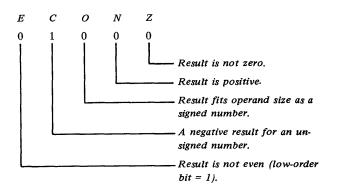

# **Indicator Bits**

The indicators are located in bits 0-4 of the level status register (LSR). Figure 2-2 shows the indicators and how they are set for arithmetic operations. The indicator bits are changed or not changed depending on the instruction being executed. Some instructions do not affect the indicators, other instructions change all of the indicators, and still other instructions change only specific indicators. Refer to the individual instruction descriptions in Chapter 8 for the indicators changed by each instruction.

Figure 2-2. How indicators are set for signed and unsigned (logical) operations

The indicators are changed in a specialized manner for certain operations. These operations are described briefly. Additional information is provided in subsequent sections for those operations where more detail is required.

- Add, subtract, or logical operations. The even, negative, and zero indicators are *result* indicators. For add and subtract operations, the carry and overflow indicators are changed to provide information for both signed and unsigned number representations.

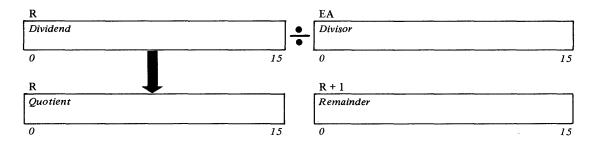

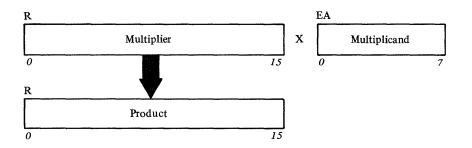

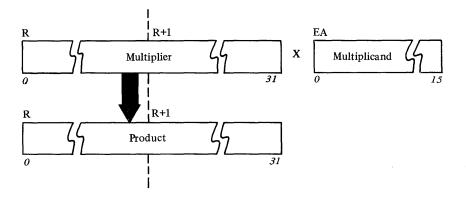

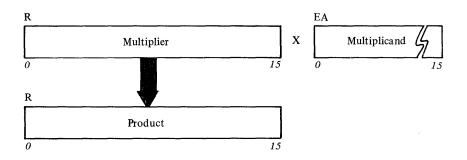

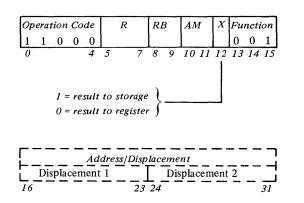

- Multiply and divide operations. Signed number operands are always assumed for these operations. The carry indicator is used to provide a divide by zero indication for the divide instruction. The overflow indicator defines an unrepresentable product for multiply operations. Refer to the individual instruction descriptions in Chapter 8.

- Priority interrupts and input/output operations. The even, carry and overflow indicators are used to form a three-bit condition code that is set as a binary value.

- Compare operations. The indicators are set in the same manner as a subtract operation.

- Shift operations. The carry and overflow indicators have a special meaning for shift left logical operations.

- Complement operations. The overflow indicator is set if an attempt is made to complement the maximum negative number. This number is not representable.

- Set Indicators (SEIND) and Set Level Block (SELB) instructions. All indicators are changed by the data associated with these instructions.

- Floating-point operations. The optional floating-point instructions set the indicators as described in Chapter 9, Floating-Point Feature.

## Even, Negative, and Zero Result Indicators

The even, negative, and zero indicators are called the result indicators. A positive result is indicated when the zero and negative indicators are both off (set to zero). These indicators are set to reflect the result of the last arithmetic, or logical operation performed. A logical operation in this sense includes data movement instructions. See the individual instruction descriptions in Chapter 8 for the indicators changed for specific instructions.

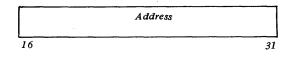

# Even, Carry, and Overflow Indicators – Condition Code for Input/Output Operations

The even, carry, and overflow indicators contain the I/O condition code: (1) following the execution of an Operate I/O instruction and (2) following an I/O interrupt.

These indicators are used to form a 3-bit binary number that results in a condition code value. For additional information about condition codes, refer to:

- 1. Branch on Condition Code (BCC) and Branch on Not Condition Code (BNCC) instructions in Chapter 8.

- 2. Condition codes in Chapter 4.

# Carry and Overflow Indicators – Add and Subtract Operations

A common set of add and subtract integer operations performs both signed and unsigned arithmetic. Whether a given add or subtract operation is to be regarded as a signed operation or an unsigned operation is determined by the programmer's view of the values being presented as operands. The carry and overflow indicators are set to reflect the result for both cases.

#### **Carry Indicator Setting**

The carry indicator is used to signal overflow of the result when operands are presented as *unsigned* numbers.

#### **Overflow Indicator Setting**

The overflow indicator is used to signal overflow of the result when the operands are presented as *signed* numbers.

*Note.* Appendix F explains the meaning of these indicators for signed and unsigned numbers. The appendix also provides examples for setting the carry indicator and for setting the overflow indicator.

# Carry and Overflow Indicators – Shift Operations

The carry and overflow indicators are changed for shift left logical operations and shift left and test operations. These operations affect the indicators as follows:

- 1. The carry indicator is set to reflect the value of the last bit shifted out of the target register (register where bits are being shifted).

- 2. The overflow indicator is set to one if bit-0 of the target register was changed during the shift. Otherwise it is set to zero.

## Indicators – Compare Operations

A compare operation sets the indicators in the same manner as a subtract operation. The even, negative, and zero indicators reflect the result. The carry and overflow indicators are set as described previously.

Compare instructions provide a test between two operands (without altering either operand) so that conditional branch and jump instructions may be used to control the programming logic flow. The conditions specified in branch and jump instructions are named such that, when the condition of the "subtracted from" operand relative to the other operand is true the jump or branch occurs. Otherwise, the next sequential instruction is executed. This is illustrated in the following example.

• Compare operation example

| nan | Instruction<br>name<br>Compare word |     |      |    |   | A ss<br>mn<br>CW | em |   |    |    |    | <i>Op</i><br>R3, |      |     |    |

|-----|-------------------------------------|-----|------|----|---|------------------|----|---|----|----|----|------------------|------|-----|----|

| OF  | pera                                | tio | n cc | de |   | R1               |    | Γ | R2 |    |    | Fu               | inct | ion |    |

| 0   | 1                                   | 1   | 1    | 0  | 0 | 1                | 1  | 1 | 0  | 0  | 0  | 0                | 1    | 0   | 1  |

| 0   |                                     |     |      | 4  | 5 | ~                | 7  | 8 | ~  | 10 | 11 | _                |      |     | 15 |

|     |                                     |     |      |    |   | R 3              |    |   | R4 |    |    |                  |      |     |    |

In this example, the contents of register 3 are subtracted from register 4:

|               |           |      |      | Decin     | nal        |

|---------------|-----------|------|------|-----------|------------|

|               |           |      |      | Unsig     | ned Signed |

| R4 contents   | 0000 0000 | 0000 | 0010 | 2         | +2         |

| R3 contents   | 1111 1111 | 1111 | 1011 | 65531     | 5          |

| Subtract resu | ılt       |      |      | -65529    | +7         |

| Machine ope   | ration:   |      |      |           |            |

| Minuend       | 0000 0000 | 0000 | 0010 |           |            |

| Subtrahend    | 0000 0000 | 0000 | 0100 | one's con | nplement   |

| Constant      |           |      | 1    | for two's | complement |

| Result        | 0000 0000 | 0000 | 0111 |           |            |

#### Indicator Settings:

If the programmer is comparing *unsigned* numbers, such as storage addresses, he should use the logical conditional tests (refer to Figure 2-3). In this example, assuming unsigned number representation, R4 is logically less than R3 and unequal to R3. Therefore, the following branch instructions would cause a transfer to symbolic location A (assuming register values shown in the example).

| CW   | R3,R4 |

|------|-------|

| BLLT | A     |

| CW   | R3,R4 |

| BNE  | A     |

or

or

The complementary tests (BLGT and BE) would not cause a transfer in this case.

If the programmer is comparing *signed* numbers, he should use the arithmetic conditional tests (refer to Figure 2-3). In the previous compare word example, assuming signed number representation, R4 is greater than R3 and unequal to R3. The following branch instructions would cause a transfer to symbolic location A.

| CW  | R3,R4 |

|-----|-------|

| BGT | A     |

| CW  | R3,R4 |

| BNE | A     |

The complementary tests (BLT and BE) would not cause a transfer.

*Note.* Jump instructions are also available for the logical and arithmetic conditional tests.

It must be emphasized again that the machine does not regard the numbers as either signed or unsigned. The compare word instruction results in a subtract operation being performed on the values presented. The programmer must then choose the correct conditional test (logical or arithmetic) for the number representation involved.

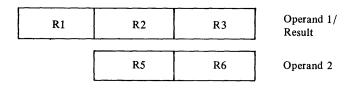

## Indicators – Multiple Word Operands

A programmer may desire to work with numbers that cannot be represented in one word or in a doubleword. It may take three or more words to represent the number.

Certain register to register instructions allow the programmer to add or subtract these multi-word operands and then have the indicators reflect the multi-word result. These instructions are:

Add Carry Register (ACY) Add Word With Carry (AWCY) Subtract Carry Register (SCY) Subtract Word With Carry (SWCY)

The following two examples show how the add instructions are used. A subtract operation would be similar. See Chapter 8 for details of the individual instructions.

Example 1. (Equal length operands)

| R1 | R2 | R3 | Operand 1/<br>Result |  |  |  |

|----|----|----|----------------------|--|--|--|

| R4 | R5 | R6 | Operand 2            |  |  |  |

Program steps:

AW R6,R3 AWCY R5,R2 AWCY R4,R1

#### Explanation:

- Step 1:The contents of R6 are added to the contents of R3.Step 2:The contents of R5 are added to the contents of R2

- plus any carry from the previous operation. Step 3: The contents of R4 are added to the contents of R1 plus any carry from the previous operation.

Example 2. (Unequal length operands)

*Note.* In this example, operand 2 must be an unsigned number or must be positive.

#### **Program Steps:**

| AW   | R6,R3 |

|------|-------|

| AWCY | R5,R2 |

| ACY  | R1    |

#### Explanation:

- Step 1: The contents of R6 are added to the contents of R3.

- Step 2: The contents of R5 are added to the contents of R2 plus any carry from the previous operation.

- Step 3: Any carry from the previous operation is added to the contents of R1.

Note. In both examples the final indicator settings reflect the status of the 3-word result.

- Even Set on if the result low-order bit of R3 is zero.

- Carry Set on if the result cannot be represented as an unsigned 3-word number.

- Overflow Set on if the result cannot be represented as a signed 3-word number.

- Negative Set on if the result high-order bit of R1 is one.

- Zero Set on if all three result registers contain zeros.

# Testing Indicators with Conditional Branch and Jump Instructions

The indicators are tested according to a selected condition when a conditional branch or a conditional jump instruction is executed. The conditions and the indicators tested for each condition are shown in Figure 2-3.

The conditional instructions are:

- Branch on Condition (BC)

- Branch on Not Condition (BNC)

- Jump on Condition (JC)

- Jump on Not Condition (JNC)

The assembler also provides extended mnemonics for the conditions shown in Figure 2-3. Refer to the individual instructions in Chapter 8.

|                              |                    |   | dica<br>stea   |                                       | 5                                      |   |

|------------------------------|--------------------|---|----------------|---------------------------------------|----------------------------------------|---|

| Condition tested by          | Assembler          | 0 | 1              | 2                                     | 3                                      | 4 |

| conditional branch or        | extended           | E | $\overline{C}$ | 0                                     | N                                      | Z |

| jump instruction             | mnemonics          |   | C              |                                       | IV                                     |   |

| Zero or equal                | BE, BZ, JE, JZ     |   |                |                                       |                                        | 1 |

| Not zero or unequal          | BNE, BNZ, JNE, JNZ |   |                |                                       |                                        | 0 |

| Positive and not zero        | BP, JP             |   |                |                                       | 0                                      | 0 |

| Not positive                 | BNP, JNP           |   |                |                                       |                                        | 1 |

|                              |                    |   |                |                                       | 1                                      |   |

| Negative                     | BN, JN             |   |                |                                       | 1                                      |   |

| Not negative                 | BNN, JNN           |   |                |                                       | 0                                      |   |

| Even                         | BEV, JEV           | 1 |                |                                       |                                        |   |

| Not even                     | BNEV, JNEV         | 0 |                |                                       |                                        |   |

| Arithmetically less than     | BLT, JLT           |   |                | 0                                     | $\begin{array}{c} 1\\ 0\end{array}$    |   |

| Arithmetically less than     | BLE, JLE           | + |                | 0                                     | 1                                      |   |

| or equal                     |                    |   |                | 1                                     | 0                                      |   |

|                              |                    |   |                |                                       |                                        | 1 |

| Arithmetically greater than  | BGE, JGE           |   |                | 1                                     | 1                                      |   |

| or equal                     |                    |   |                | 0                                     | 0                                      |   |

| Arithmetically greater than  | BGT, JGT           |   |                | $\begin{vmatrix} 1\\ 0 \end{vmatrix}$ | $\begin{vmatrix} 1 \\ 0 \end{vmatrix}$ | 0 |

|                              |                    |   | 1              | -                                     | 0                                      |   |

| Logically less than or equal | BLLE, JLLE         |   | 1              |                                       |                                        | 1 |

| Logically less than (carry)  | BLLT, JLLT         |   | 1              |                                       |                                        |   |

| Logically greater than       | BLGT, JLGT         |   | 0              |                                       |                                        | 0 |

| Logically greater than or    | BLGE, JLGE         | 1 | 0              |                                       |                                        |   |

| equal (no carry)             |                    |   |                |                                       |                                        |   |

| Legend: | LSR bit |

|---------|---------|

|         | 0       |

|         | 1       |

|         | 2       |

|         | 3       |

|         | 4       |

| bit | Indicator                    |

|-----|------------------------------|

|     | $\mathbf{E} - \mathbf{Even}$ |

|     | C – Carry                    |

|     | 0 – Overflow                 |

|     | N – Negative                 |

|     | Z – Zero                     |

Figure 2-3. Indicators tested by conditional branch and jump instructions

# Supervisor State Bit

LSR bit 8, when set to one, indicates that the processor is in the supervisor state. This state allows privileged instructions to be executed. It is set by any of the following:

- 1. Class interrupt

- a. Machine check condition

- b. Program check condition

- c. Power/thermal warning

- d. Supervisor Call (SVC) instruction

- e. Soft exception trap condition

- f. Trace

- g. Console interrupt

- 2. I/O interrupt

- 3. Initial program load (IPL)

When LSR bit 8 is set to zero, the processor is in problem state. For a selected priority level, the supervisor can alter the supervisor state bit by using a Set Level Block (SELB) instruction. For additional information, refer to *Processor State Control* in this chapter.

Class interrupts and I/O interrupts are described in Chapter 3. IPL is discussed in a subsequent section of this chapter.

# **In-process Bit**

LSR bit 9, when set to one, indicates that a priority level is currently active or was preempted by a higher priority level before completing its task. Bit 9 is turned off by a Level Exit (LEX) instruction. Bit 9 can also be turned on or off by a Set Level Block (SELB) instruction. The inprocess bit also affects level switching under program control. Refer to *Chapter 3*. *Interrupts and Level Switching*.

# **Trace Bit**

LSR bit 10, when set to one, causes a trace class interrupt at the beginning of each instruction. The bit can be turned on or off with the Set Level Block (SELB) instruction. The trace bit aids in debugging programs. See *Class Interrupts* in Chapter 3.

# Summary Mask Bit

LSR bit 11, when set to zero (disabled), inhibits all priority interrupts on all levels. When this bit is set to one (enabled), normal interrupt processing is allowed. Refer to *Summary Mask* in Chapter 3 for details relating to control of the summary mask.

# Program Execution

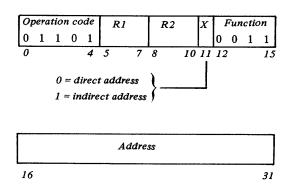

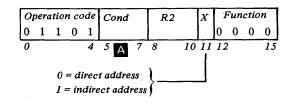

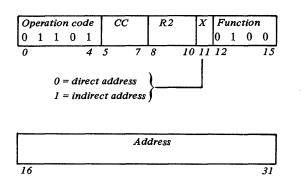

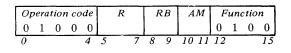

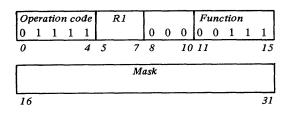

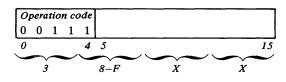

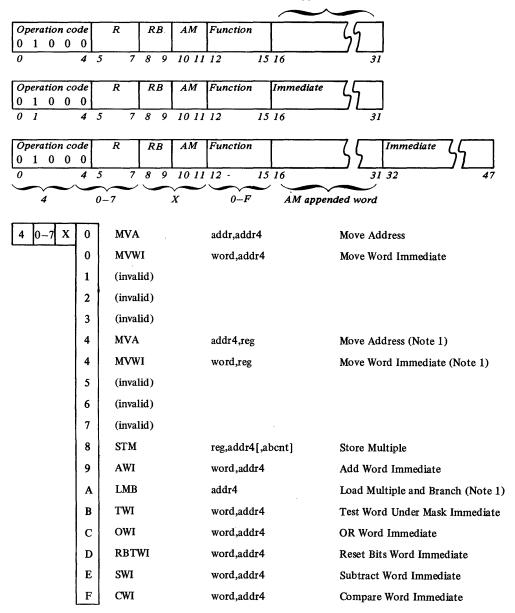

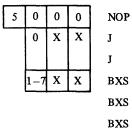

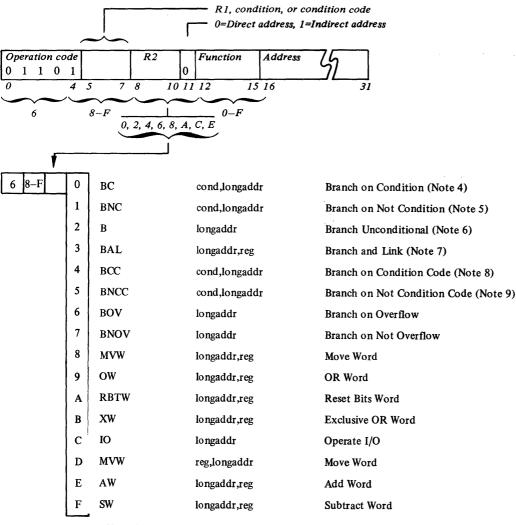

# Instruction Formats

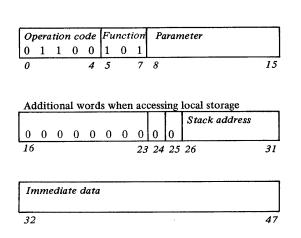

The processor instruction formats are designed for efficient use of bit combinations to specify the operation to be performed (operation code) and the operands that participate. Some formats also include (1) an immediate data field or word, (2) an address displacement or address word, and (3) a function field that further modifies the operation code. Various combinations of these fields are used by the individual instructions. Some typical instruction formats are presented in this section. All formats are shown in the section *Instruction Formats* in Appendix B.

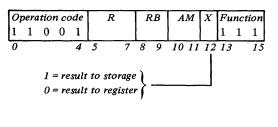

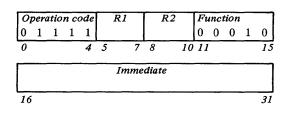

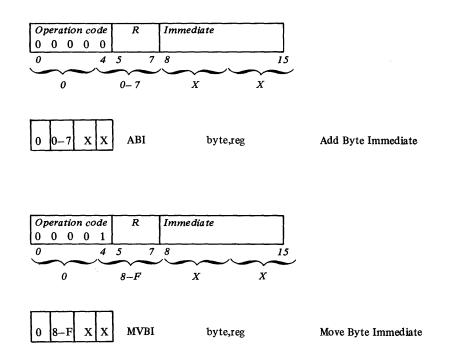

## **One Word Instructions**

The basic instruction length is one word (16 bits). The operation code field (bits 0-4) is the only common field for all formats. This field, unless modified by a function field, specifies the operation to be performed. For a format without a function field, bits 5-15 specify the location of operands or data associated with an operand:

#### Example:

| name               | mnemonic | <i>Syntax</i> |

|--------------------|----------|---------------|

| Add Byte Immediate | ABI      | byte,reg      |

| Operation code R   | Imme     | ediate        |

Bits 0-4 Operation code (specifies ABI instruction).

Bits 5-7 General register (0-7).

This register contains data for the second operand.

Bits 8–15 Immediate data for the first operand.

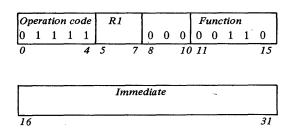

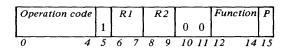

In some cases the operation code is the same for a group of instructions. The format for this group includes a function field. The bit combinations in the function field then determine the specific operation to be performed. Example:

| Instruction<br>name<br>Add Word |     | Assembler<br>mnemonic<br>AW |                     |

|---------------------------------|-----|-----------------------------|---------------------|

| Operation code                  | R1  | R2                          | Function            |

| $0 \ 1 \ 1 \ 1 \ 0$             |     |                             | $0 \ 1 \ 0 \ 0 \ 0$ |

| 0 4                             | 5 7 | 8 10                        | 11 15               |

| Bits 0-4   | Operation code for a group of instructions.                                            |

|------------|----------------------------------------------------------------------------------------|

| Bits 5–7   | General register $(0-7)$ .<br>This register contains data for the first operand.       |

| Bits 8-10  | General register $(0-7)$ .<br>This register contains data for the second operand.      |

| Bits 11–15 | Function field.<br>Modifies the operation code to specify the Add<br>Word instruction. |

*Note.* For other instruction groups, the function'field may vary as to location within the format, and also the number of bits used.

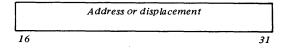

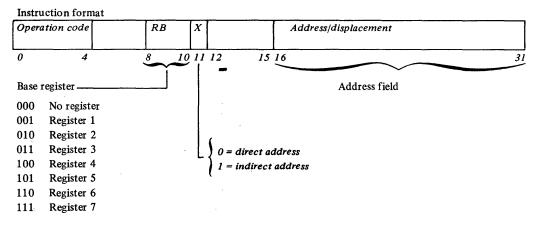

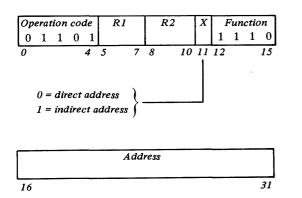

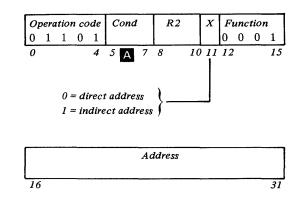

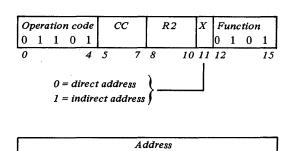

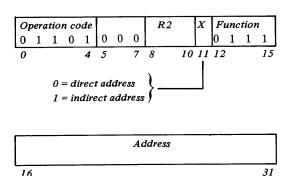

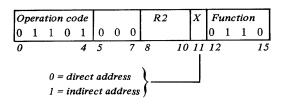

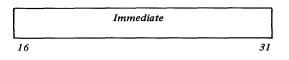

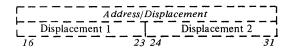

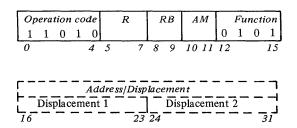

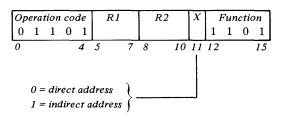

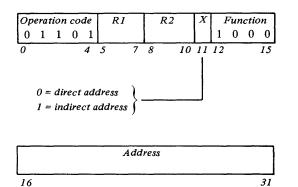

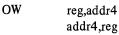

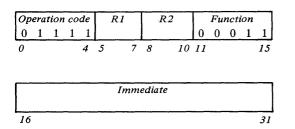

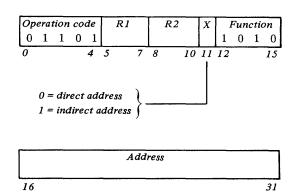

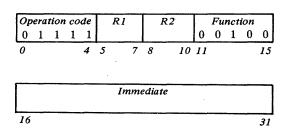

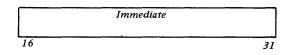

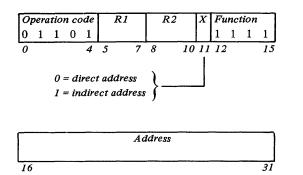

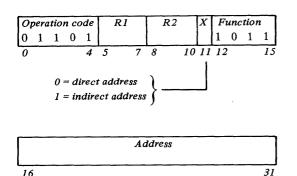

#### **Two Word Instructions**

The first word of this format is identical to the one-word format. The second word (bits 16-31) contains either immediate data, an address, or a displacement. This word is used to (1) provide data for an operand, or (2) provide a main storage address or displacement for effective address generation (see *Effective Address Generation* in this chapter).

Example:

| Instruction<br>name         |     | Assembler<br>mnemonic |    | Syntax              |  |  |  |

|-----------------------------|-----|-----------------------|----|---------------------|--|--|--|

| Branch and Link             |     | BAL                   |    | longaddr,reg        |  |  |  |

| Operation code<br>0 1 1 0 1 | R1  | R2                    | X  | Function<br>0 0 1 1 |  |  |  |

| 0 4                         | 5 7 | 8 10                  | 11 | 12 15               |  |  |  |

Bits 0-4 Operation code.

Bits 5-7 General register (0-7) for the second operand.

Bits 8-10 General register (0-7) for the first operand.

Bit 11 Indirect addressing bit.

Bits 12–15 Function field.

Bits 16-31 A main storage address used for the first operand. Note. In this example, the register designated R1 is associated with the second operand in assembler syntax.

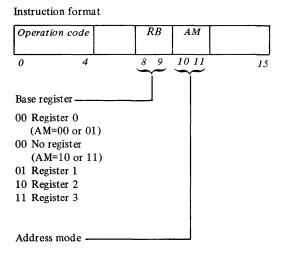

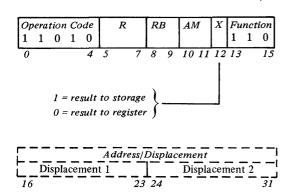

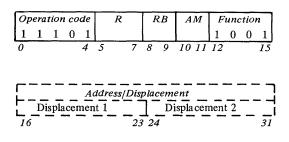

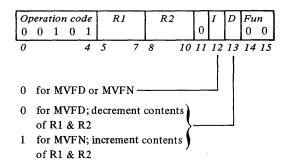

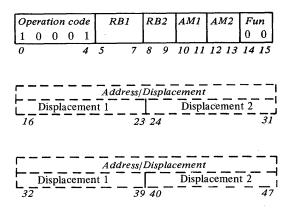

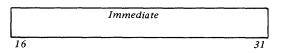

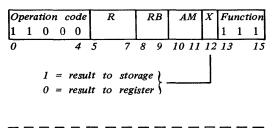

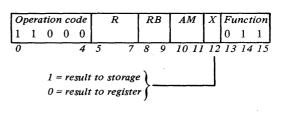

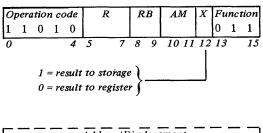

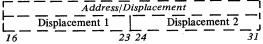

#### Variable Length Instructions

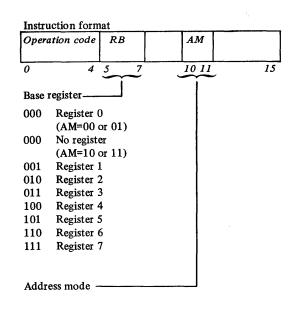

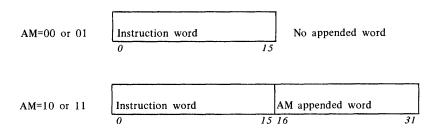

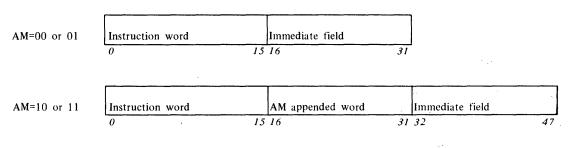

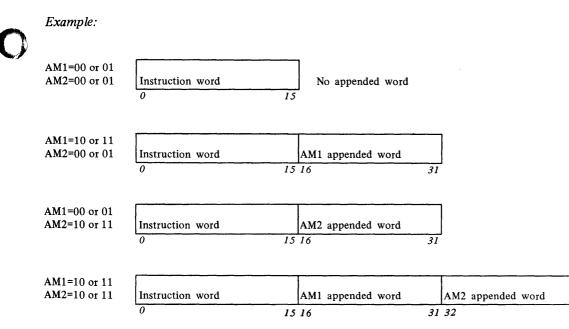

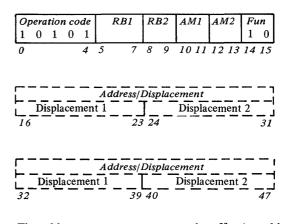

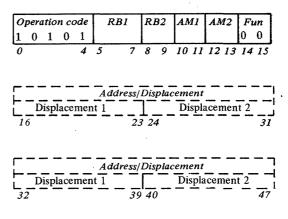

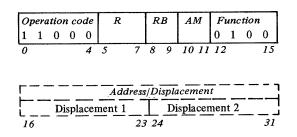

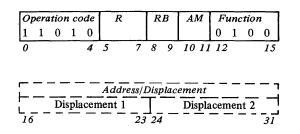

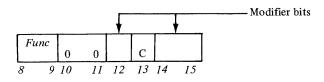

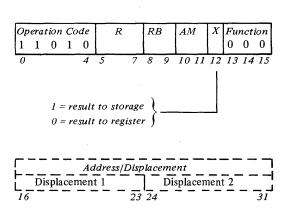

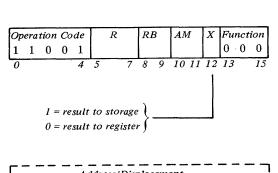

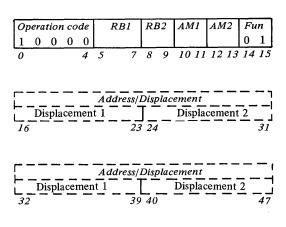

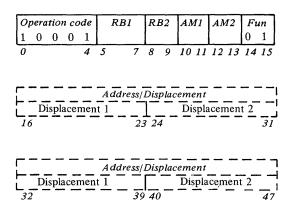

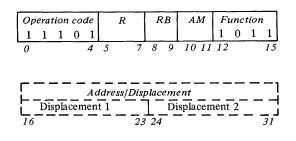

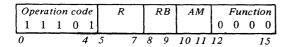

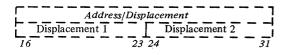

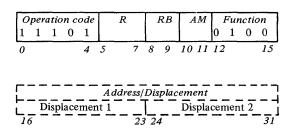

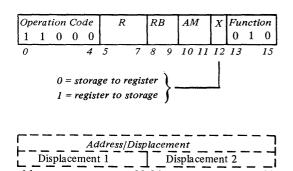

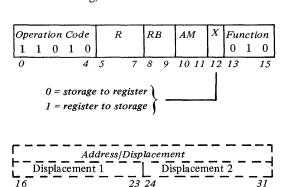

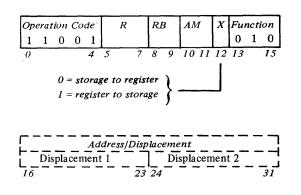

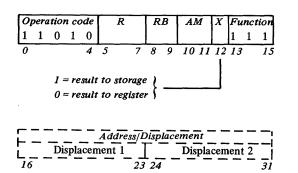

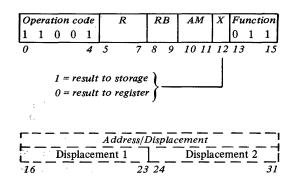

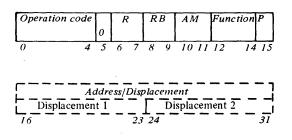

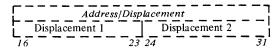

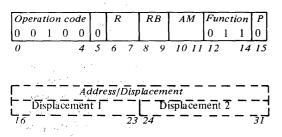

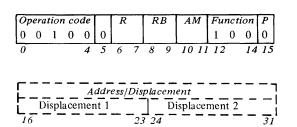

Some instructions use a selectable encoded technique for generating effective addresses. This method is referred to as an address argument technique in subsequent sections. These instruction formats contain a base register (RB) field and an address mode (AM) field. If both operands are using this technique, the format contains an RB and associated AM field for each. These fields are in the first instruction word. The AM field consists of two bits and is referred to in binary notation (AM=00, 01, 10, or 11). If AM is equal to 10 or 11 an additional word is appended to the normal instruction word. For a format that contains two AM fields, two additional words may be appended. See *Effective Address Generation* in this chapter for a description of the appended words and how they are used.

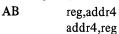

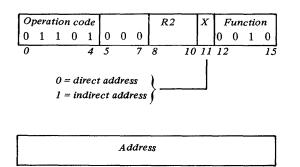

For instructions with a single storage address argument, the RB field consists of two bits. An RB field of two bits with its associated AM field of two bits are referred to as a 4-bit address argument or *addr4* in assembler syntax.

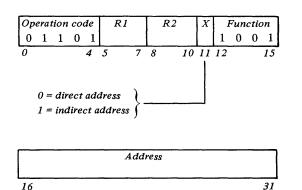

#### Example:

| Instruction<br>name | Syntax    |        |            |    |     |     |   |

|---------------------|-----------|--------|------------|----|-----|-----|---|

| Compare byte        | СВ        |        | addr4, reg |    |     |     |   |

| Operation code      | R         | RB     | AM         | Fu | nct | ion |   |

| 1 1 0 0 0           |           |        |            | 0  | 1   | 0   | 0 |

| 0 4                 | 5 7       | 89     | 10 11      | 12 |     |     | 1 |

| Appe<br>16          | nded word | I, AM= | =10 or 1   | 1  |     |     | 3 |

Bits 0–4 Operation code.

Bits 5-7 General register (0-7) for the second operand.

Bits 8-9 Base register (0-3).

Bits 10-11 Address mode.

Bits 12–15 Function.

Bits 16-31 Appended word for the first operand.

*Note.* The register specified by the RB field is a general register that is used as a base register for effective address generation.

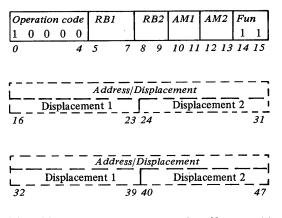

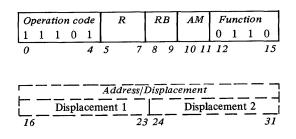

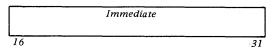

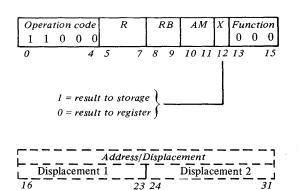

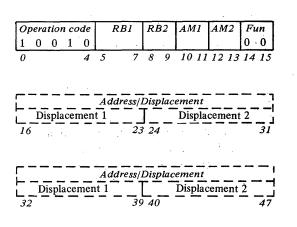

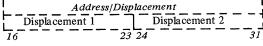

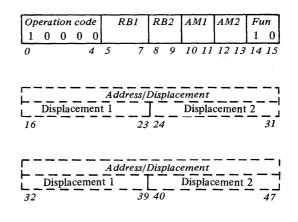

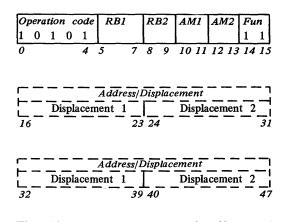

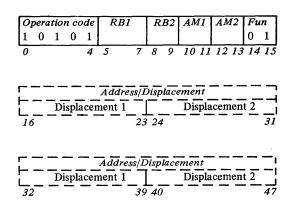

Some instruction formats have two storage address arguments. In this case, the first operand has a 3-bit RB field giving a 5-bit address argument (*addr5* in assembler syntax) and the second operand has a 4-bit address argument.

Example:

| na me        | truction<br>me<br>Id Word |           | menmonic |       |      |      |     |        | <i>Syntax</i><br>addr5,addr4 |                   |  |  |

|--------------|---------------------------|-----------|----------|-------|------|------|-----|--------|------------------------------|-------------------|--|--|

| Opera<br>1 0 | tior<br>1                 | 1 cc<br>0 | ode<br>1 | R     | B1   | RE   | 32  | AM1    | AM2                          | <i>Fun</i><br>0 0 |  |  |

| 0            |                           |           | 4        | 5     | 7    | 8    | 9   | 10 11  | 12 13                        | 14 15             |  |  |

|              |                           | ***       | Ap       | pende | d wo | rd j | for | operan | d 1                          |                   |  |  |

| 16           |                           |           |          |       |      |      |     |        |                              | 31                |  |  |

| Appended word for operand 2 |    |

|-----------------------------|----|

| 32                          | 47 |

Bits 0-4 Operation code.

- Bits 5-7 Base register (0-7) for the first operand.

- Bits 8-9 Base register (0-3) for the second operand.

- Bits 10-11 Address mode for the first operand.

- Bits 12-13 Address mode for the second operand.

- Bits 14–15 Function.

- Bits 16-31 Appended word for the first operand.

- Bits 32-47 Appended word for the second operand.

#### Notes.

- 1. If there is no appended word for the first operand (AM1=00 or 01), the second operand word is appended to the instruction word in bits 16-31.

- 2. Registers specified by the RB fields are general registers.

#### Names of Instruction Formats

Names have been established for several categories of instructions. Each category has the same basic instruction format, therefore, the name is related to the format. In most cases, the name indicates the location of the operands or the type of instruction.

#### Examples:

- Register/Register Instructions. General registers are used by both operands.

- Storage/Storage Instructions. Both operands reside in main storage.

- Register/Storage Instructions. One operand uses a general register. The other operand resides in main storage.

- Register Immediate Instructions. One operand uses a general register. The other operand uses an immediate data field. The immediate data field is the low order byte of a one-word format or the second word of a two-word (long) format.

- Shift Instructions with Immediate Count. This is a shift instruction with the count field contained within the instruction word.

- Storage Immediate Instructions. One operand is in main storage. The other operand uses an immediate data field. The immediate data field is the second word of a two-word format.

- Parametric Instructions. For this instruction format, a parameter field (bits 8–15) is contained within the instruction word.

# Effective Address Generation

For purposes of storage efficiency, certain instructions formulate storage operand addresses in a specialized manner. These instructions have self-contained fields that are used when generating effective addresses. Standard methods for deriving effective addresses are included in this section. Other methods such as bit displacements, are explained in the individual instruction descriptions in Chapter 8.

**Programming note:** For certain instructions, the effective address points to a control block rather than an operand. These instructions are:

- Copy Floating Level Block (CPFLB) (optional floating-point feature)

- Copy Level Block (CPLB)

- Load Multiple and Branch (LMB)

- Pop Byte (PB)

- Pop Doubleword (PD)

- Push Byte (PSB)

- Push Doubleword (PSD)

- Push Word (PSW)

- Pop Word (PW)

- Set Floating Level Block (SEFLB) (optional floating point feature)

- Set Level Status Block (SELB)

- Store Multiple (STM)

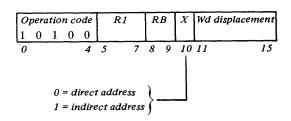

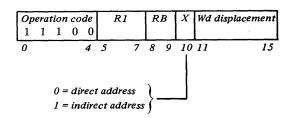

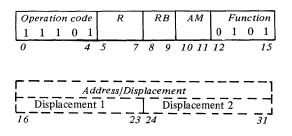

**Base Register Word Displacement Short**

Range 0 to 31 (decimal)

The five-bit unsigned integer (WD) is doubled in magnitude to form a byte displacement then added to the contents of the specified base register to form the effective address. The contents of the base register must be even.

Example:

| Operation code |            | n code RB  |   |   | WD  |      |     |      |    |      |      |      |

|----------------|------------|------------|---|---|-----|------|-----|------|----|------|------|------|

|                |            |            | 0 | 1 |     | 0    | 0   | 1    | 0  | 0    |      |      |

| 0              | 4          |            | 8 | 9 |     | 11   |     |      |    | 15   |      |      |

|                |            |            |   |   |     |      |     |      |    |      | Hex  | Dec  |

| Content        | s of regis | ter 1 (RB) |   |   | 000 | )0 ( | 000 | 0 01 | 10 | 0000 | 0060 | 0096 |

| Word dis       | splaceme   | nt (WD)    |   |   |     |      |     |      |    |      |      |      |

| double         | d          |            |   | - | ł   |      |     |      | 0  | 1000 | 8    | 8    |

| Effective      | e address  |            |   | - | 000 | 00 ( | 000 | ) 01 | 10 | 1000 | 0068 | 0104 |

#### **Base Register Word Displacement**

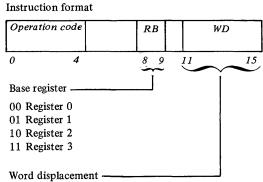

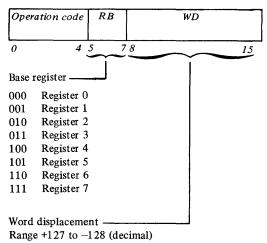

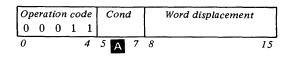

Instruction format

The eight-bit *signed* integer (WD) is doubled in magnitude to form a byte displacement then added to the contents of the specified base register to form the effective address. The contents of the base register must be even.

The word displacement can be either positive or negative; bit 8 of the instruction word is the sign bit for the displacement value. If this high-order bit of the displacement field is a 0, the displacement is positive with a maximum value of +127 (decimal). If the high-order bit of the displacement field is a 1, the displacement is negative with a maximum value of -128. The negative number is represented in two's complement form.

Example:

| Operation | code |   | RB |   | WD |   |   |   |   |   |   |    |

|-----------|------|---|----|---|----|---|---|---|---|---|---|----|

|           |      | 1 | 1  | 0 | 1  | 1 | 1 | 0 | 1 | 0 | 0 | 1  |

| 0         | 4    | 5 |    | 7 | 8  |   |   |   |   |   |   | 15 |

Note. This example uses a negative word displacement (-17 hex) shown in two's complement. Hex Dec

| _                                 |                      |      | 2    |

|-----------------------------------|----------------------|------|------|

| Contents of register 6 (RB)       | 0000 0000 1000 0110  | 0086 | 0134 |

| Word displacement (WD)<br>doubled |                      |      |      |

| (sign bit is propagated left)     | +1111 1111 1101 0010 | 2E   | - 46 |

| Effective address                 | 0000 0000 0101 1000  | 0058 | 0088 |

#### Four-Bit Address Argument

The Address Mode (AM) has the following significance:

AM=00. The contents of the selected base register form the effective address.

AM=01. The contents of the selected base register form the effective address. After use, the base register contents are incremented by the number of bytes in the operand. For some instructions, the effective address points to a control block rather than an operand. When the effective address points to a control block, the base register contents are incremented by two.

Example:

| Operat | ion code | RB  | AM    |    |

|--------|----------|-----|-------|----|

|        |          | 0 1 | 01    |    |

| 0      | 4        | 89  | 10 11 | 15 |

|                                               |                     | Hex  | Dec  |

|-----------------------------------------------|---------------------|------|------|

| Effective address<br>(contents of register 1) | 0000 0000 1000 0000 | 0080 | 0128 |

| Contents of register 1                        |                     |      |      |

| after instruction execution                   |                     |      |      |

| Byte operand                                  | 0000 0000 1000 0001 | 0081 | 0129 |

| Word operand                                  | 0000 0000 1000 0010 | 0082 | 0130 |

| Double word operand                           | 0000 0000 1000 0100 | 0084 | 0132 |

|                                               |                     |      |      |

Notes.

- 1. For register to storage instructions, if the specified register is the same for both operands, then the register is incremented prior to using it as an operand.

- 2. Certain instructions (storage to storage) have two address arguments. Operand 1 has a 3-bit RB field with its associated AM field. Operand 2 has a 2-bit RB field with its associated AM field. If both RB fields specify the same register and both AM fields are equal to 01, the base register contents are incremented prior to fetching operand 2 and again after fetching operand 2. Assuming the same conditions but with the operand 2 AM field not equal to 01, the base register contents are increments are increments are incremented prior to 2 AM field not equal to 01, the base register contents are incremented prior to 2 address for operand 2.

- 3. If the effective address points to a control block rather than an operand, the base register contents are incremented by two.

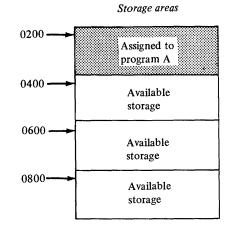

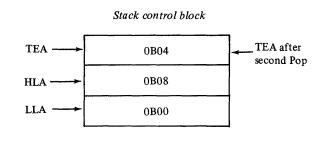

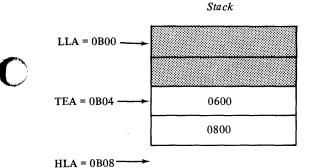

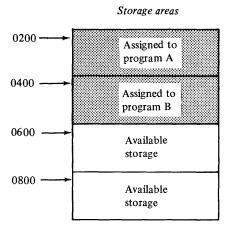

С

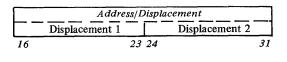

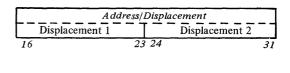

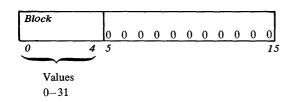

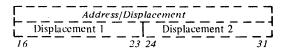

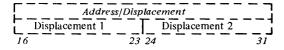

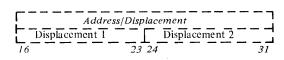

AM=10. An additional word is appended to the instruction. The word has the following format.

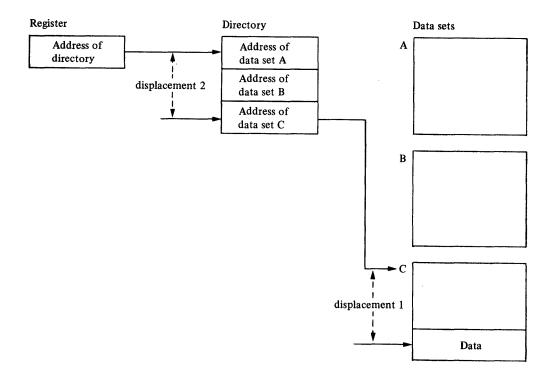

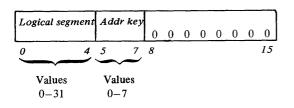

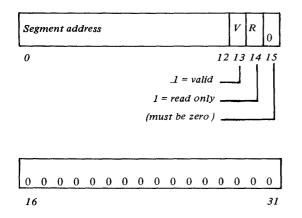

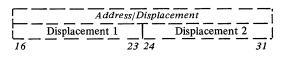

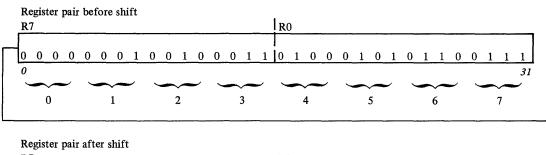

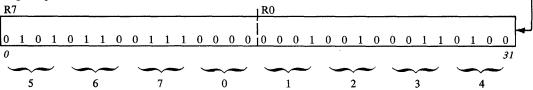

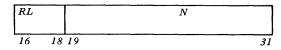

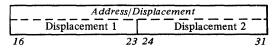

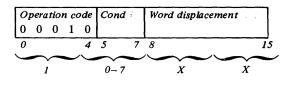

|    | Address or displacement |    |

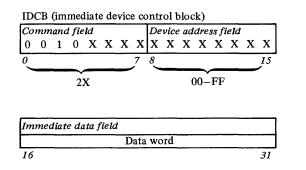

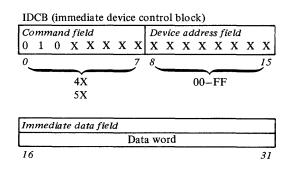

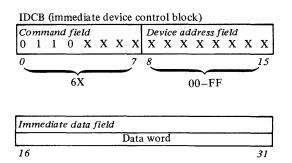

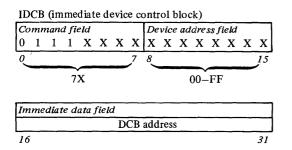

|----|-------------------------|----|