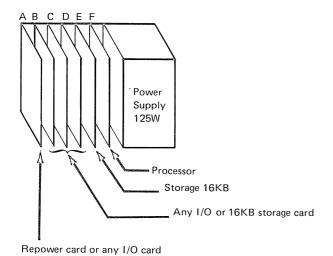

Figure 1-2. IBM 4953 Processor Model A with a Programmer

If the A position is not used for the Channel Repower card, the following feature cards may be plugged in this position:

- Teletypewriter Adapter Feature using TTL voltage levels

- Teletypewriter Adapter Feature using isolated current loop where user supplies external ±12V power

- Timer Feature

- Customer Direct Program Control Adapter Feature

- 4982 Sensor Input/Output Unit Attachment Feature

- Integrated Digital Input/Output Non-Isolated Feature

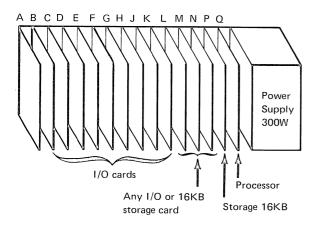

Figure 1-3. IBM 4953 Processor Model B with a Programmer Console

Repower card or any 1/0 card

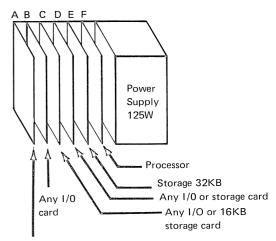

Figure 1-4. IBM 4953 Processor Model C with a Programmer Console

If the A position is not used for the Channel Repower card, the following feature cards may be plugged in this position:

- Teletypewriter Adapter Feature suing TTL voltage levels

- Teletypewriter Adapter Feature using isolated current loop where user supplies external ±12V power

- Timer Feature

- Customer Direct Program Control Adapter Feature

- 4982 Sensor Input !Output Unit Attachment Feature

- Integrated Digital Input/Output Non-Isolated Feature

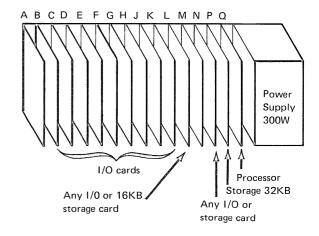

Figure 1-5. IBM 4953 Processor Model D with a Programmer Console

| Sequence |        | Part    | EC 374831 |  |  |

|----------|--------|---------|-----------|--|--|

| 0423AA   | 1 of 2 | 6826698 | 7-1-78    |  |  |

| Sequence |        | Part    | EC 374831 | ` |  |

|----------|--------|---------|-----------|---|--|

| 0423AA   | 2 of 2 | 6826698 | 7-1-78    |   |  |

COPYRIGHT IBM CORPORATION 1976

### **Condition Codes**

#### I/O Instruction Condition Codes

These codes are reported during execution of an Operate I/O instruction.

| Condi-<br>tion<br>code (CC)<br>value | LSR p | oosition<br>Carry | Over-<br>flow | Reported<br>by | Meaning               |

|--------------------------------------|-------|-------------------|---------------|----------------|-----------------------|

| 0                                    | 0     | 0                 | 0             | channel        | Device not attached   |

| 1                                    | 0     | 0                 | 1             | device         | Busy                  |

| 2                                    | 0     | 1                 | 0             | device         | Busy after reset      |

| 3                                    | 0     | 1                 | 1             | chan/dev       | Command reject        |

| 4                                    | 1     | 0                 | 0             | device         | Intervention required |

| 5                                    | 1     | 0                 | 1             | chan/dev       | Interface data check  |

| 6                                    | 1     | 1                 | 0             | controller     | Controller busy       |

| 7                                    | 1     | 1                 | 1             | chan/dev       | Satisfactory          |

### **Interrupt Condition Codes**

These condition codes are reported by the device or controller during priority interrupt acceptance.

| Condi-<br>tion<br>code (CC) | LSR p | oosition | Over- | Reported   |                                    |

|-----------------------------|-------|----------|-------|------------|------------------------------------|

| value                       | Even  | Carry    | flow  | by         | Meaning                            |

| 0                           | 0     | 0        | 0     | controller | Controller end                     |

| 1                           | 0     | 0        | 1     | device     | Program controlled interrupt (PCI) |

| 2                           | 0     | 1        | 0     | device     | Exception                          |

| 3                           | 0     | 1        | 1     | device     | Device end                         |

| 4                           | 1     | 0        | 0     | device     | Attention                          |

| 5                           | 1     | 0        | 1     | device     | Attention and PCI                  |

| 6                           | 1     | 1        | 0     | device     | Attention and exception            |

| 7                           | 1     | 1        | 1     | device     | Attention and device end           |

## **Processor Status Word (PSW)**

| ,Bit | Contents                                               |

|------|--------------------------------------------------------|

| 0    | Specification check                                    |

| 1    | Invalid storage address -                              |

| 2    | Privilege violate <                                    |

| 3    | (not used, always zero)                                |

| 4    | Invalid function                                       |

| 5    | (not used, always zero)                                |

| 6    | Stack exception                                        |

| 7    | (not used, always zero) — Failures that can be trapped |

| 8    | Storage parity check with stop on error switch:        |

| 9    | (not used, always zero)                                |

| 10   | CPU control check                                      |

| 11   | I/O check                                              |

| 12   | Sequence indicator                                     |

| 13   | Auto-IPL                                               |

| 14   | (not used, always zero)                                |

| 15   | Power/thermal warning <                                |

# General Registers

| R or RB* field value | Register selected |

|----------------------|-------------------|

| 000                  | Register 0        |

| 001                  | Register 1        |

| 010                  | Register 2        |

| 011                  | Register 3        |

| 100                  | Register 4        |

| 101                  | Register 5        |

| 110                  | Register 6        |

| 111                  | Register 7        |

<sup>\*</sup>The RB field sometimes contains only the two low-order bits. In this case, registers 4 through 7 cannot be specified.

### Interrupt Status Byte (ISB)

### **DPC** Devices

| Bits | Contents                |

|------|-------------------------|

| 0    | Device status available |

| 1    | Delayed command reject  |

| 2    | Device dependent        |

| 3    | Device dependent        |

| 4    | Device dependent        |

| 5    | Device dependent        |

| 6    | Device dependent        |

| 7    | Device dependent        |

|      |                         |

#### Cycle Steal Devices

| Bits | Contents                |

|------|-------------------------|

| 0    | Device status available |

| 1    | Delayed command reject  |

| 2    | Incorrect length record |

| 3    | DCB specification check |

| 4    | Storage data check      |

| 5    | Invalid storage address |

| 6    | (not used, always zero) |

| 7    | Interface data check    |

|      |                         |