## STATUS AFTER RESETS

| Condition      | Reset             |                   |                |             |                       |                    |               |             |

|----------------|-------------------|-------------------|----------------|-------------|-----------------------|--------------------|---------------|-------------|

|                | Timer             | Auto-load<br>reg  | Prepare<br>reg | Mode<br>reg | Pending<br>interrupts | Timer<br>run state |               | 8           |

| Power on reset | X<br>(to all 1's) | X<br>(to all 1's) | X              | X           | X                     | X                  |               |             |

| System reset   |                   |                   | X              | X           | ×                     | X                  |               |             |

| Halt I/O       |                   |                   |                | X           | X                     | X                  | _             | 1           |

| Device reset   |                   |                   |                | Υ           | Υ                     | Υ                  | B02 polarized |             |

| •              | ı                 |                   |                |             |                       |                    |               | Row B Row A |

X = reset in both timers

Y = reset in address timer only

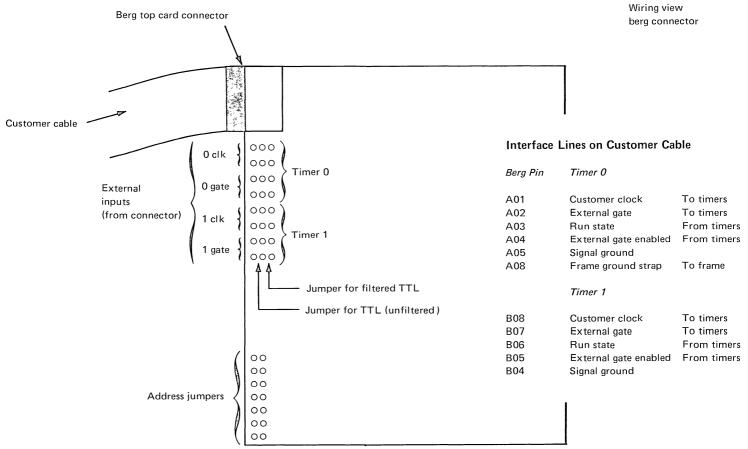

\* No Jumper for least significant address bit.

One device address for both timers (device address must be even). Bit 15 of address bus selects one of the two timers.

| Sequence |        | Part    | EC 374831 |  |  |

|----------|--------|---------|-----------|--|--|

| 1050AA   | 1 of 2 | 6826706 | 7-1-78    |  |  |

| Sequence |        | Part    | EC 374831 |  |  |

|----------|--------|---------|-----------|--|--|

| 1050AA   | 2 of 2 | 6826706 | 7-1-78    |  |  |

COPYRIGHT IBM CORPORATION 1976

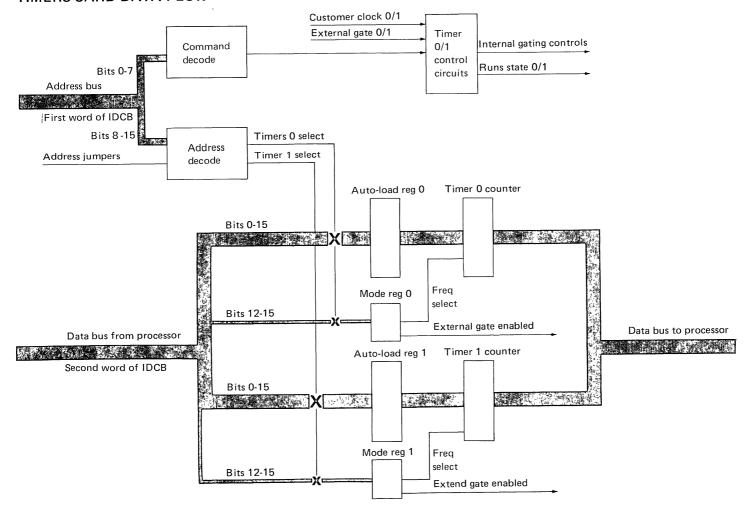

## **TIMERS CARD DATA FLOW**