# Contents

| CHAPTER 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System Components 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5410 Processing UnitaCPU) 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5424 MFQU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5203 Printer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5444 Disk Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Machine Language 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Number Systems 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Number Conversions 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CPU Operation 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bridge Basic Storage Module 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Instruction and Execute Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Sequential Instruction Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Branching 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Addressing 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

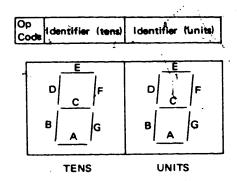

| Instruction Rormats . 1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Instructions 1-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Data Flow 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Parity Checking 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHAPTER 2. FUNCTIONAL UNITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CPU Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Cycle Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bridge Basic Storage Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Storage Principles 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5410 BSMs *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Addressing System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Readout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16K or 32K BSM Byte Control 2-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| in the second se |

# FRAME LOCATION TABLE

| . /          | <u> </u> | <b></b>          |

|--------------|----------|------------------|

| Page         | Frame    | Card 💀           |

| 11           | ~ A14    | 1-1              |

| 1-2          | A15,     | 1-1              |

| 1-3          | A16      | , 1 <b>-</b> 1 🏄 |

| 1-5          | A18      | 1-1/             |

| 1-6          | B01      | 1-1              |

| 1-7          | B02      | (j. 1-1)         |

| 1 <b>-</b> 8 | B03      | 1-1              |

| 1-9          | B04      | 1-1              |

| 1-10         | B05      | 1-1              |

| 1-11         | B06      | 1-1              |

| 1-12         | B07      | 1-1              |

| ]-14         | B09      | 1-1              |

| 1-16         | B11      | 1-1              |

| 2-1          | B15 *    | 1-1              |

| 7-21         | B16      | 1-1              |

| 2-10         | C08      | 1-1              |

| <b>2-15</b>  | . 41     | 1-1              |

| 2-17.        |          | 1:-1             |

|              |          |                  |

|              |          | 1                |

|              |          |                  |

|              |          |                  |

|              |          |                  |

|              |          |                  |

|              |          | ŀ                |

|              | Y        |                  |

# FRAME POCATION, TABLE

| Write (Store):                            | · 2-18 · · · / · /       |

|-------------------------------------------|--------------------------|

| Storage Cycle Timing                      | 2-18.                    |

| Chained BSMs                              | 2-19                     |

| Interface                                 |                          |

|                                           | <b>2</b> -21             |

| Power-Supply and Temperature Compensation | 2-23                     |

| Storage Data Register (SDR)               | 2-23                     |

| Storage Address Register (SAR)            | 2-23                     |

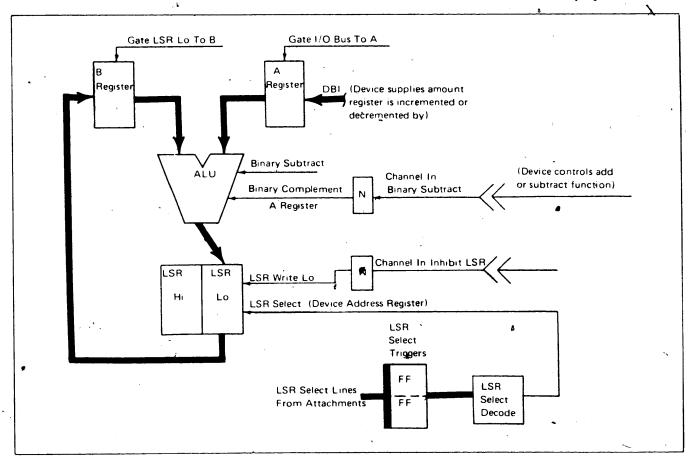

| B Register                                | 2-23                     |

| A Register                                | . 2-23                   |

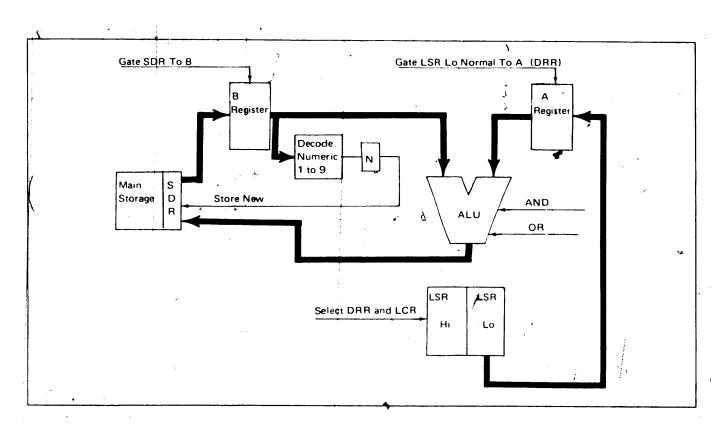

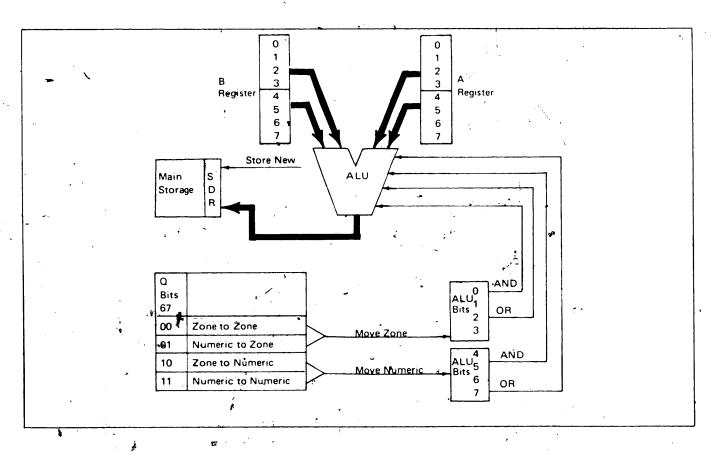

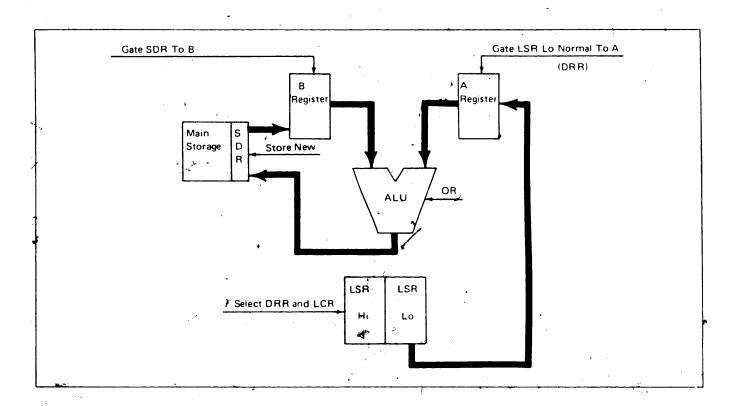

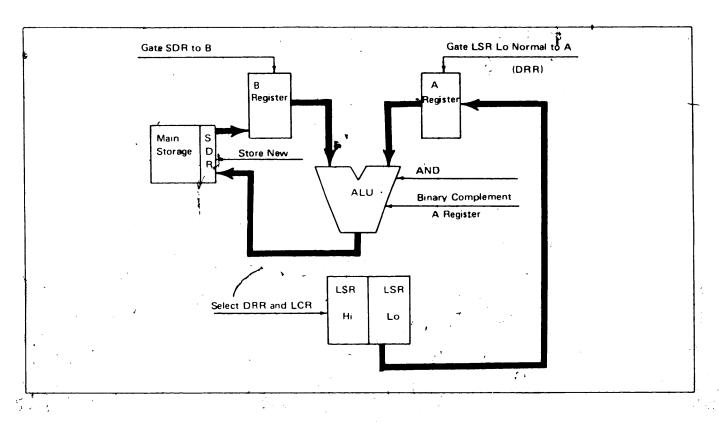

| ALU                                       | 2-24                     |

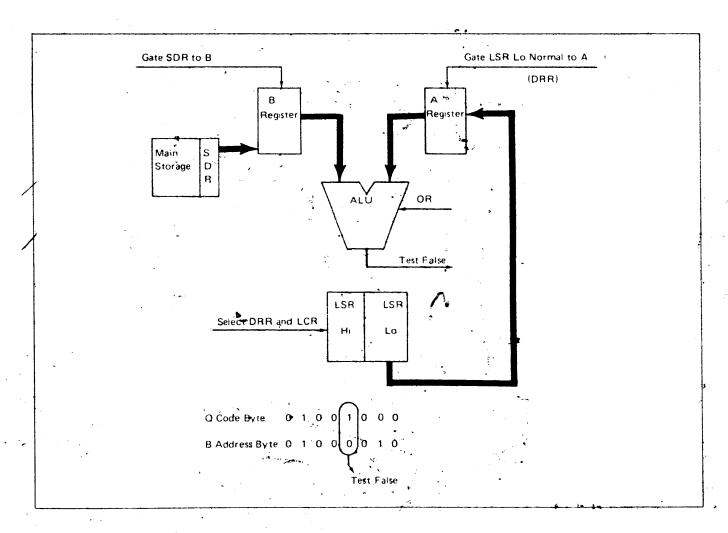

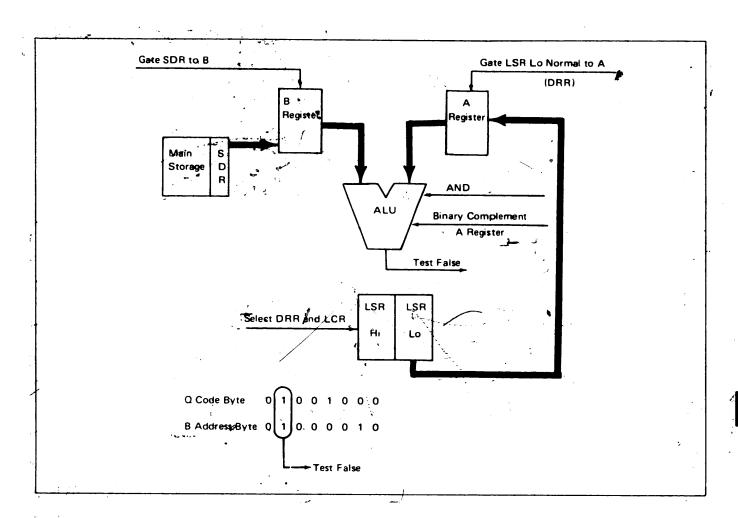

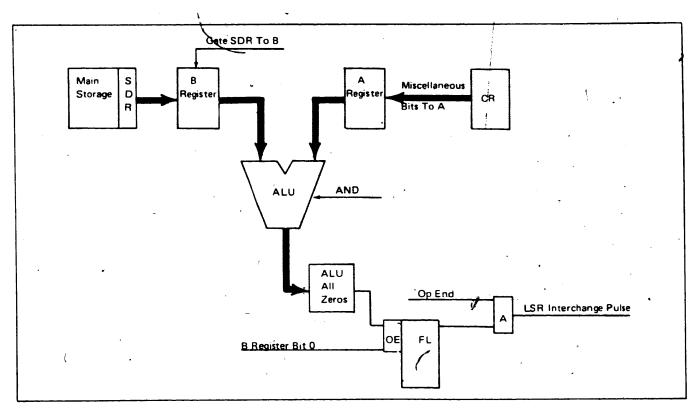

| AND/OR and Test False                     | 2-25                     |

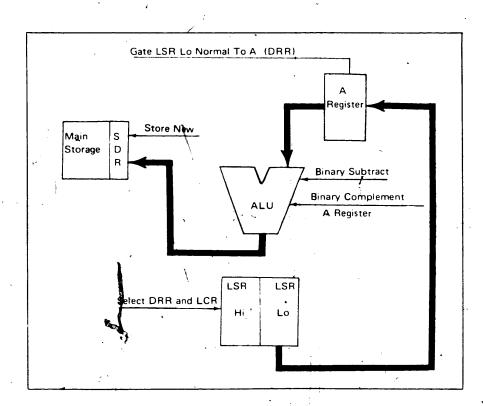

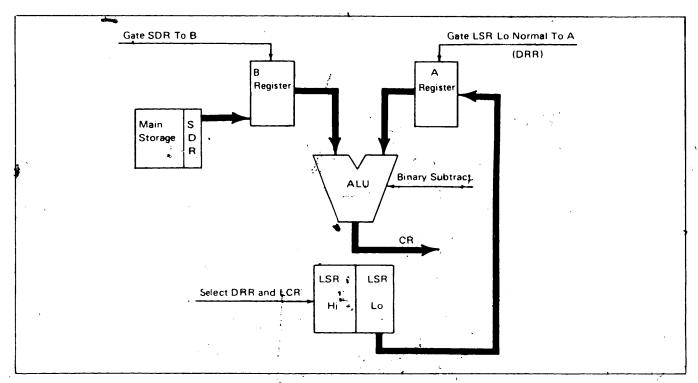

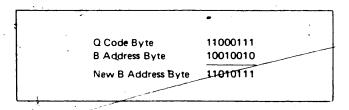

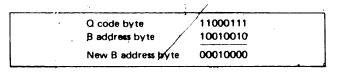

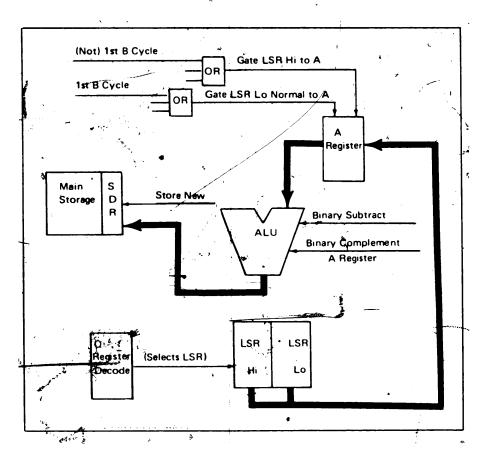

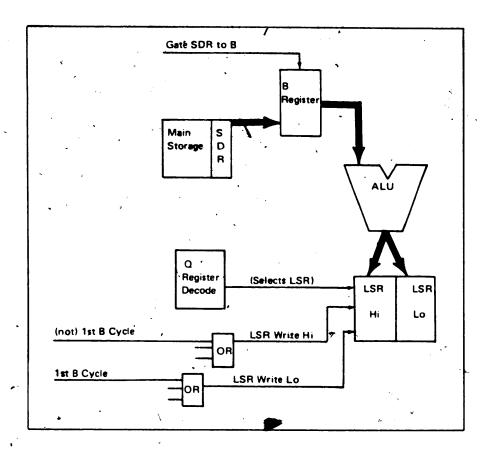

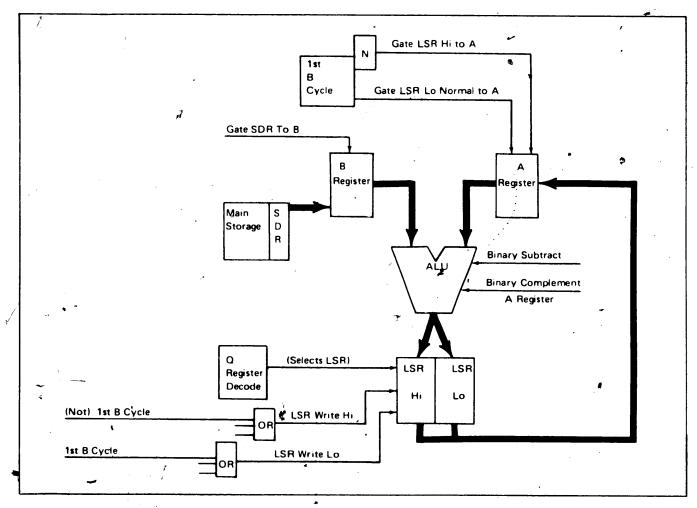

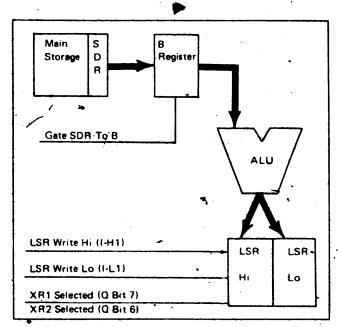

| Binary Subtraction                        | 2-26                     |

| Binary Addition                           | . 2-28                   |

| Decimal Subtraction                       | . 2-28                   |

| Decimal Addition                          | 2-30                     |

| Recomplement                              | 2-31                     |

| Check ALU                                 | . 2-32                   |

| Parity Generation and Parity Check        | . 2-32                   |

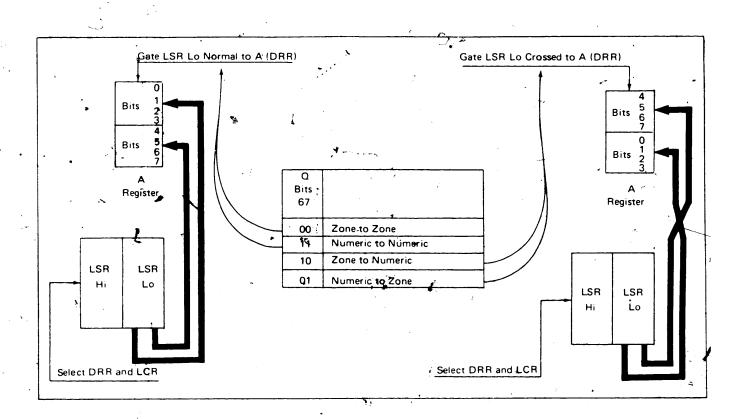

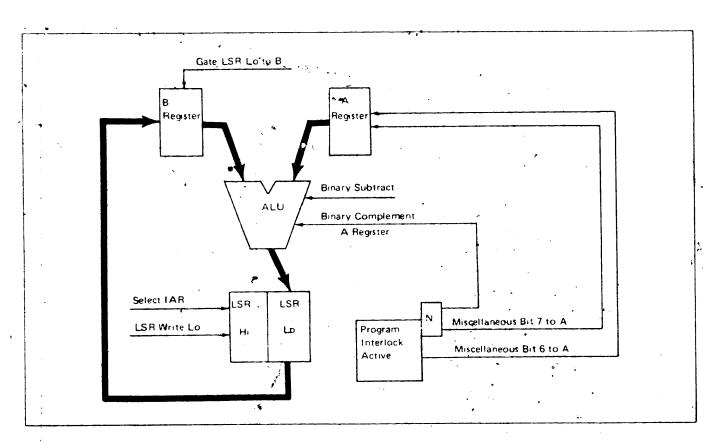

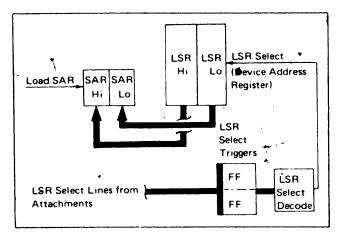

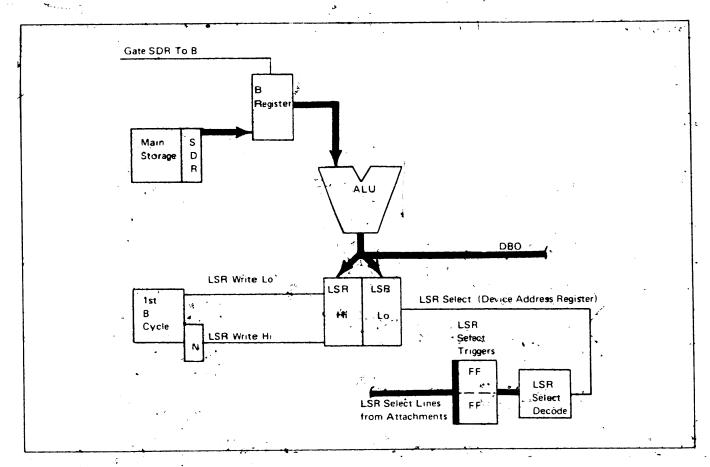

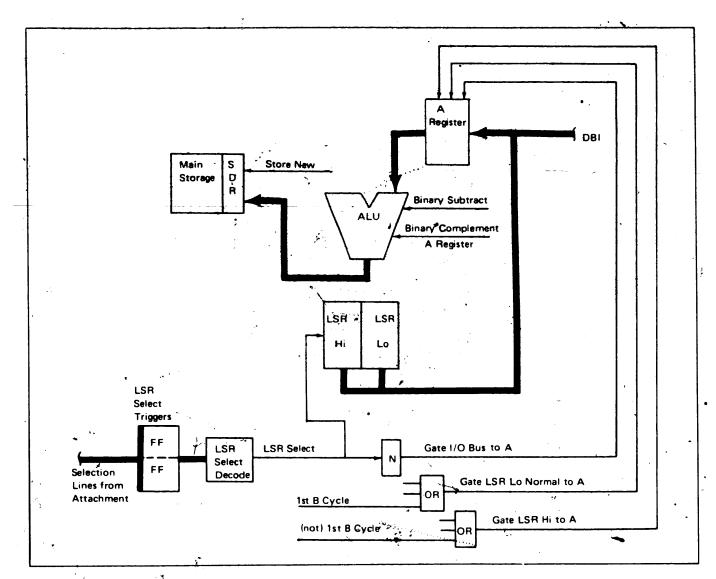

| Local Storage Registers (LSR)             | 2-34                     |

| Op Register                               | 2-36                     |

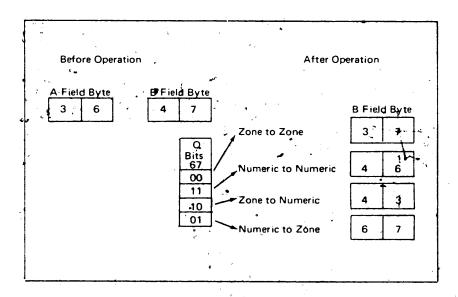

| O Register                                | . 2-36                   |

| Condition Register (CR)                   | . 2-36                   |

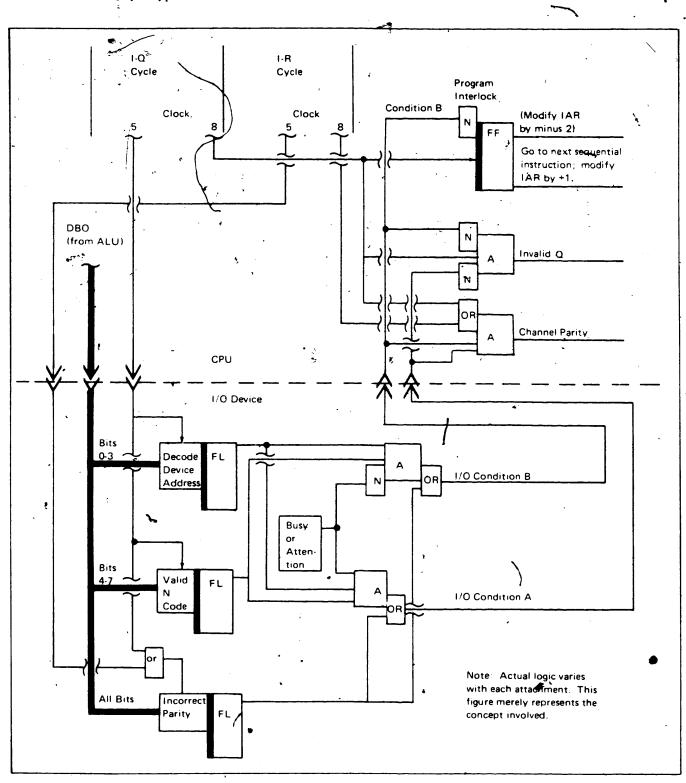

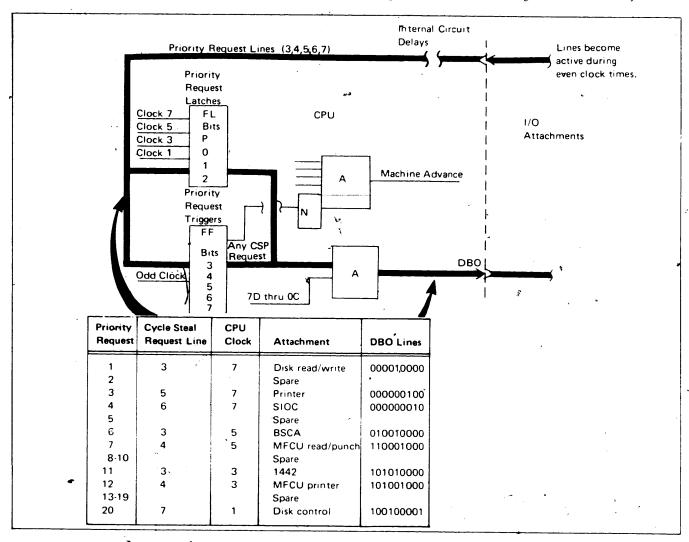

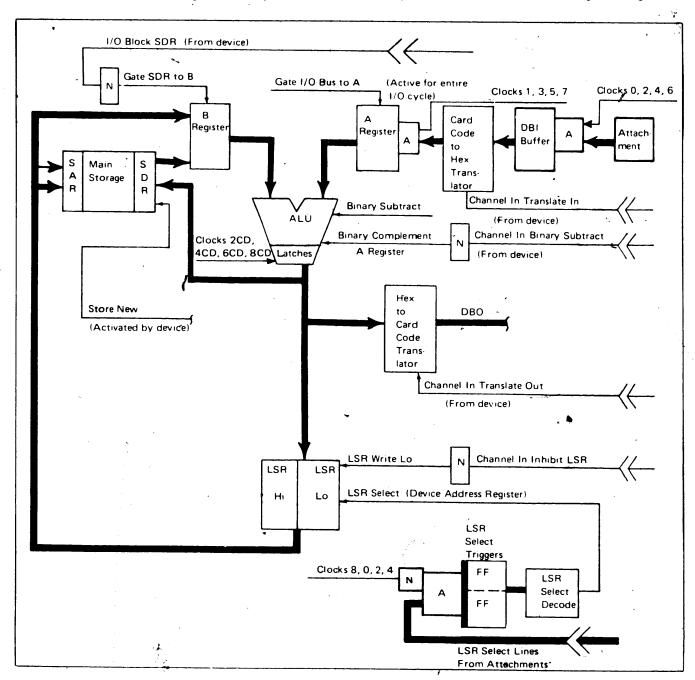

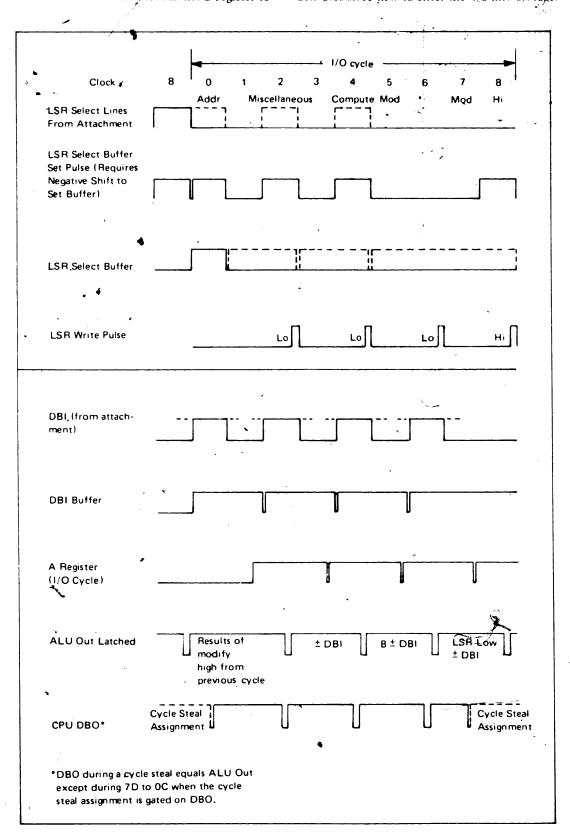

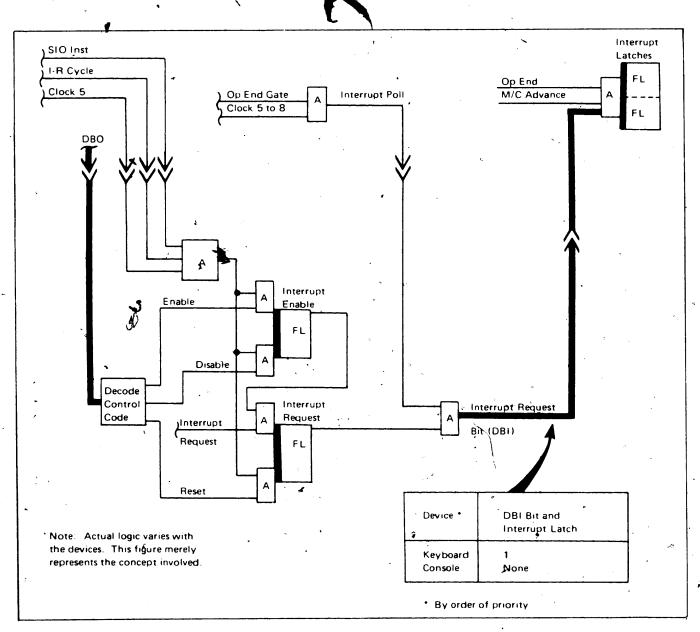

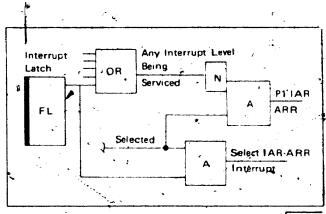

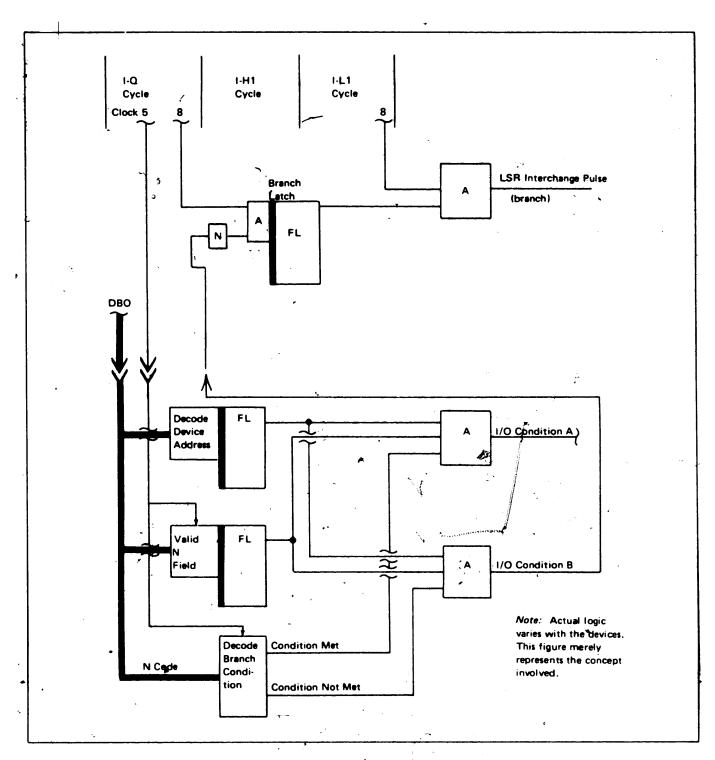

| I/O Interface                             | 2-38                     |

|                                           |                          |

| CHAPTER 3. THEORY OF OPERATION            | FR <sub>2</sub> E02, 1-1 |

| Two Address Instruction                   | 3-1                      |

| I-Cycles                                  | 3-1                      |

| Indexing                                  | , 3-4                    |

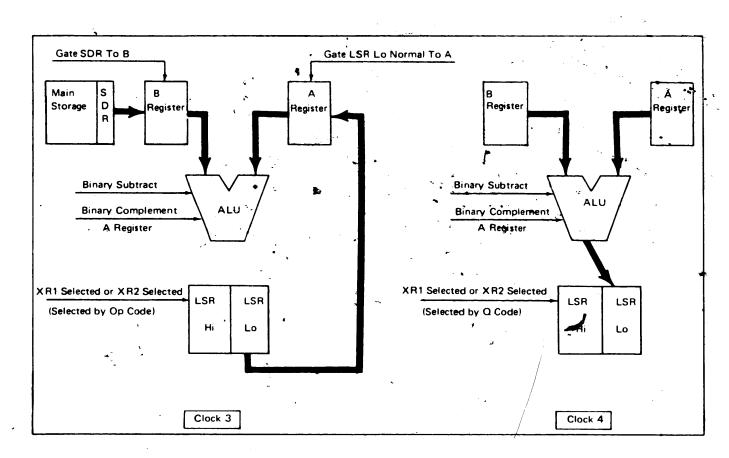

| Execution Cycles                          | 3-6                      |

| Add Logical Characters-ALC                | 3-8 .                    |

| Subtract Logical Characters-SLC           | 3-10                     |

| Page          | Frame       | Card               |

|---------------|-------------|--------------------|

| 2-18          | C14         | ें ती हो ें        |

| 2-19          | C15         | 1-1                |

| 2-21          | C17         | 1-1                |

| 2-23          | D01         | 1-1                |

| 2-24          | DQ2         | 1-1                |

| 2-25          | D03         | 1-1 .              |

| 2-26          | D <b>04</b> | 1-1                |

| 2-28          | D06         | 1-1                |

| 2-30          | D08         | 1-1                |

| 2-31          | D09         | 1-1                |

| 2-32          | Ď1Q         | 1-1                |

| 2-34          | Ď12         | \ <sub>2</sub> 1−1 |

| 2 <b>-3</b> 6 | D14         | · 1'-1             |

| 2-38          | D16         | 1-1                |

| 3-1           | E02         | 1-1                |

| 3-4 .         | E05         | 1-h                |

| 3-4 · 3-6     | E07         | 1-1                |

| 3-8           | E09         | - 1-1              |

| 3-10          | E11.        | 1-1                |

|               |             |                    |

|               |             | :                  |

|               |             |                    |

|               |             |                    |

|               |             |                    |

|               |             |                    |

|               |             |                    |

|               | ŧ           | -                  |

# Contents

|       | Compare Logical Characters-CLC     |          |               |     |              | 3-10         |

|-------|------------------------------------|----------|---------------|-----|--------------|--------------|

|       | Move Characters-MVC                |          |               |     |              | <b>3</b> -10 |

|       | Add or Subtract Zoned Decimal-AZ-  | -SZ      | •.            |     | . /.         | 3-12         |

| /     | Zero and Add Zoned-ZAZ             | •        |               |     |              | 3-15         |

| محمهر | Édit-ED                            |          |               |     |              | 3-15         |

| !     | Insert and Test Character-ITC      | • •      |               | •   |              | 3-18         |

|       | Move Hex Character-MVX             | •        |               |     |              | 3-18         |

| O     | ne Address Instructions            |          |               |     |              | 3-20         |

|       | I-Cycles                           |          |               |     |              | 3-20         |

|       | Move Logical Immediate-MVI .       |          |               |     |              | 3-21         |

|       | Compare Logical Immediate-CLI      | •        |               |     |              | 3-22         |

|       | Set Bits On Masked-SBN             |          |               |     |              | 3-22         |

|       | Set Bits Off Masked-SBF            |          |               | •   | ٠,           | 3-24         |

|       | Test Bits On Masked-TBN .          |          |               |     | <i>.</i> ′′. | . 3-2€       |

|       | Test Bits Off Masked-TBF           |          |               | , · |              | . 3-2€       |

|       | Store Register-ST                  | •        | $\cdot_{j}$ . |     |              | . 3-27       |

|       | Load Register-L                    | • /      | /<br>· · ·    |     |              | . 3-28       |

|       | Add to Register-A                  |          |               |     |              | 3-29         |

|       | Load Address-LA                    | . ,      | į .           | . 1 | Pi           | 3-30         |

|       | Branch On Condition-BC             |          |               |     |              | . 3-32       |

| C     | ommand Instructions                |          |               | -   | •            | 3-32         |

|       | Jump On Condition—JC /             |          |               |     |              | . 3-32       |

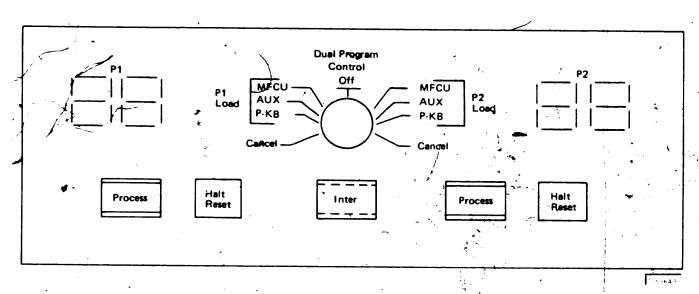

|       | Halt Program Level (Basic Machine) | . ,      |               |     |              | 3-34         |

|       | Halt Program Level (Dual Programmi | ng F     | eatu          | re) |              | . 3-34       |

| 1/    | O Instructions                     |          |               |     |              | . 3-34       |

|       | Start I/O-SIO                      | :<br>. ¥ |               | • ` | •            | . 3-34       |

|       | Load I/O-LIO                       |          |               |     |              | . 3-44       |

| •     | Sense I/O-SNS                      |          |               |     | •            | . 3-45       |

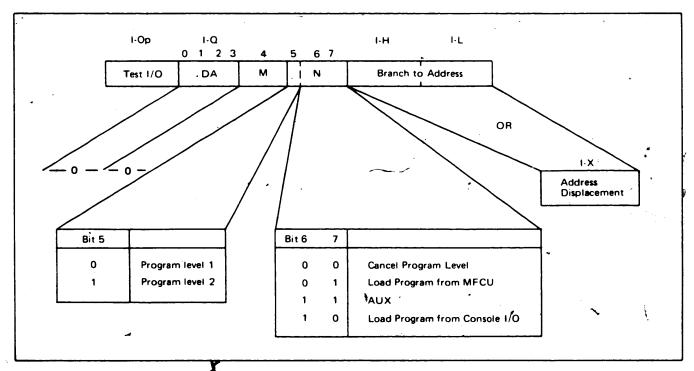

|       | Test I/O and Branch-TIO            | .·       |               |     |              | . 3-45       |

|       | Advance Program Level_APL          |          | ٠ ٠.          |     |              | . 3-47       |

|       | Initial Program Load-IPL           | •        | · ;·          |     |              | . 3-47       |

|       |                                    |          |               |     |              |              |

# FRAME LOCATION TABLE

| Pąge | Frame       | Card |

|------|-------------|------|

| 3-10 | Ell         | 1-1  |

| 3-12 | E13         | 1-1  |

| 3-15 | E16         | 1-1  |

| 3-18 | A10         | 1-2  |

| 3-20 | A12         | 1-2  |

| 3-21 | A13         | 1-2  |

| 3-22 | A14         | 1-2  |

| 3-24 | A16         | 1-2  |

| 3-26 | A18         | 1-2  |

| 3-27 | B01         | 1-2  |

| 3-28 | B02         | 1-2  |

| 3-29 | BQ3         | 1-2  |

| 3-30 | В04         | 1-2  |

| 3-32 | B06         | 1-2  |

| 3-34 | B08         | 1-2  |

| 3-44 | B18         | 1-2  |

| 3-45 | C01         | 1-2  |

| 3-47 | <b>C</b> 03 | 1-2  |

| •    | •           |      |

| •    | • 6         |      |

|      | ,           | ·    |

| *    | ,           |      |

|      |             | •    |

|      |             | ·    |

|      |             |      |

| 2    |             |      |

|      |             |      |

# Contents

| CHAPTER 4. FEATURES                                                                 | FR Ç06, 1-2.            |

|-------------------------------------------------------------------------------------|-------------------------|

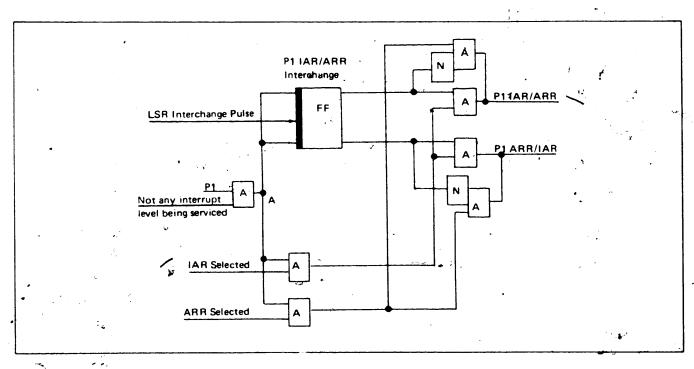

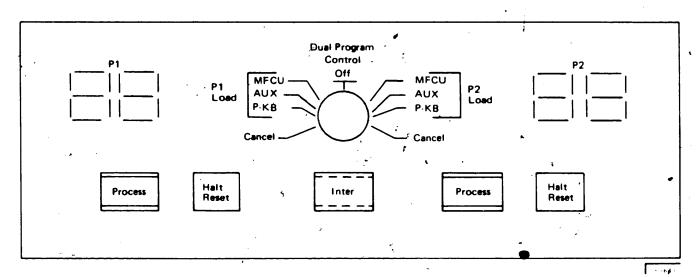

| Dual Program Feature (DPF)                                                          | 4-1                     |

| Advance Program Level-APL                                                           | 4-2                     |

| Binary Synchronous Communications Adapter                                           | 4-3                     |

| Serial Input/Output Channel Attachment                                              | <b>4-3</b> <sup>3</sup> |

| 547 Printer Keyboard Attachment                                                     | 4-4                     |

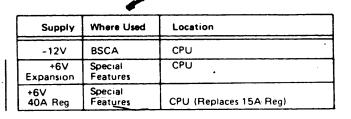

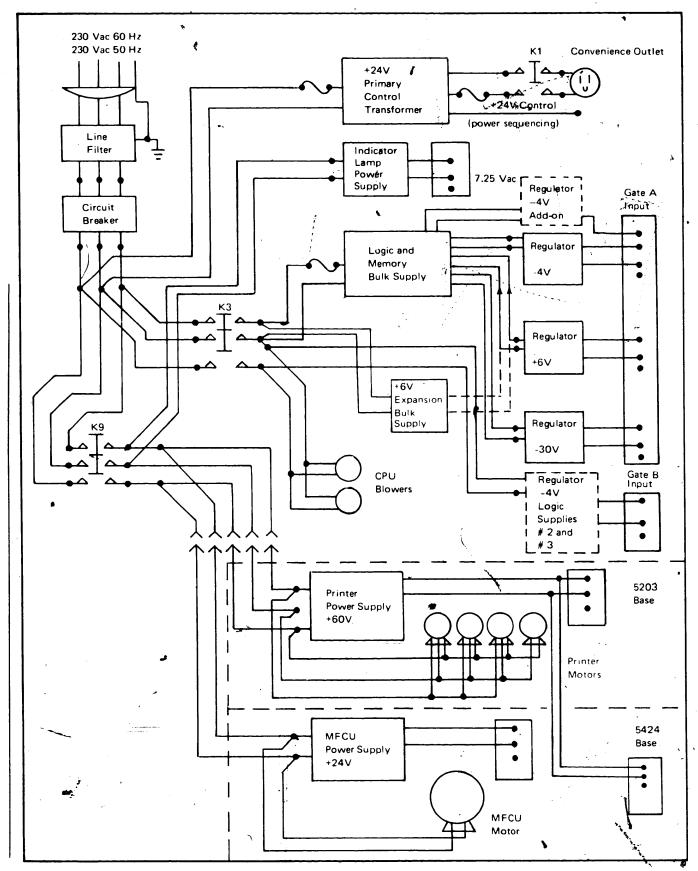

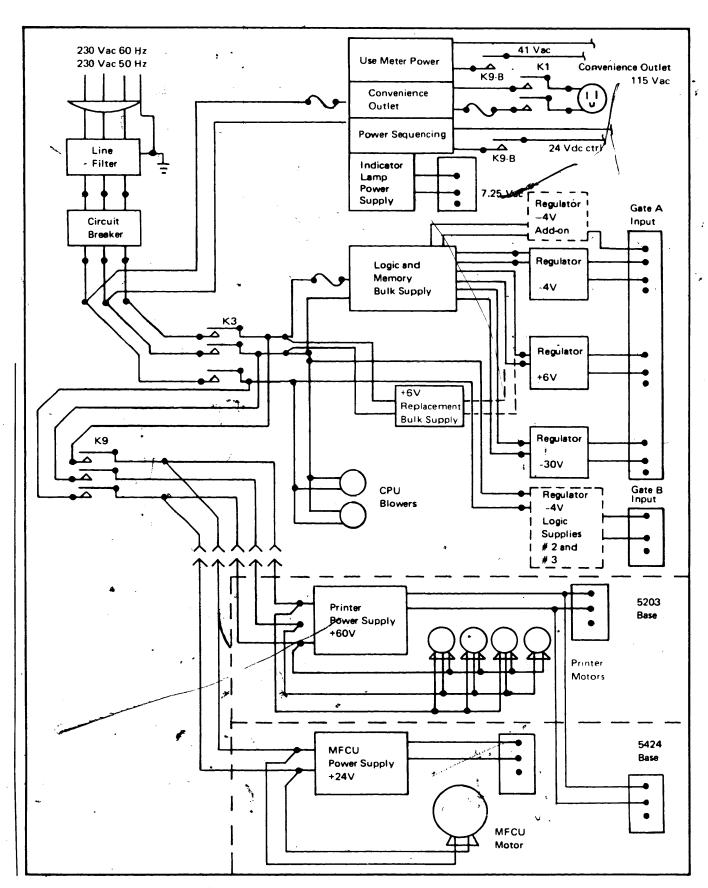

| CHAPTER 5. POWER SUPPLIES AND CONTROLS                                              | FR C11, 1-2             |

| SECTION I BASIC UNIT                                                                | 5-1                     |

| Power Supplies , ;                                                                  | 5-1                     |

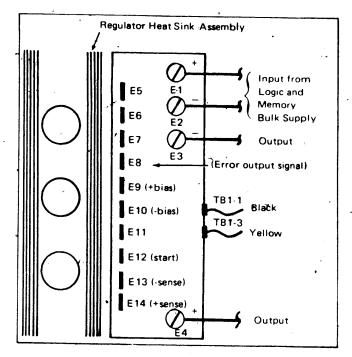

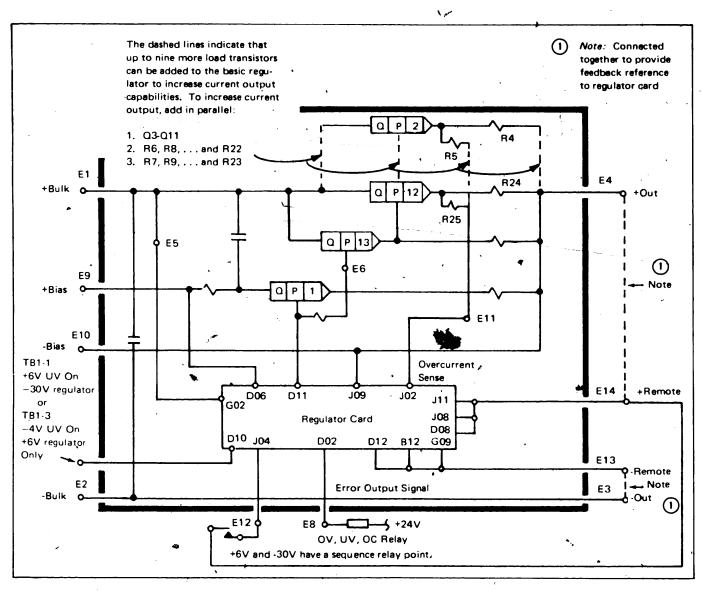

| Power Supply Regulators                                                             | 5-4                     |

| Voltage Regulation                                                                  | 5-4                     |

| Overvoltage Protection                                                              | 5-4                     |

| Overcurrent Protection                                                              | 5-4                     |

| Undervoltage Protection                                                             | 5-5                     |

| Normal Power On Sequence (Early Design Power Control)                               | . 5-6                   |

| Normal Power Off (Early Design Power Control)                                       | 5-6                     |

| Normal Power On Sequence (Redesigned Power Control-<br>Printed Circuit Relay Panel) | 5-7                     |

| Normal Power Off (Redesigned Power Control)                                         | 5-7                     |

| Abnormal Power Off                                                                  | 5-7                     |

| Test Points (TPs)                                                                   | 5-8                     |

| SECTION 2. FEATURES                                                                 | 5-9                     |

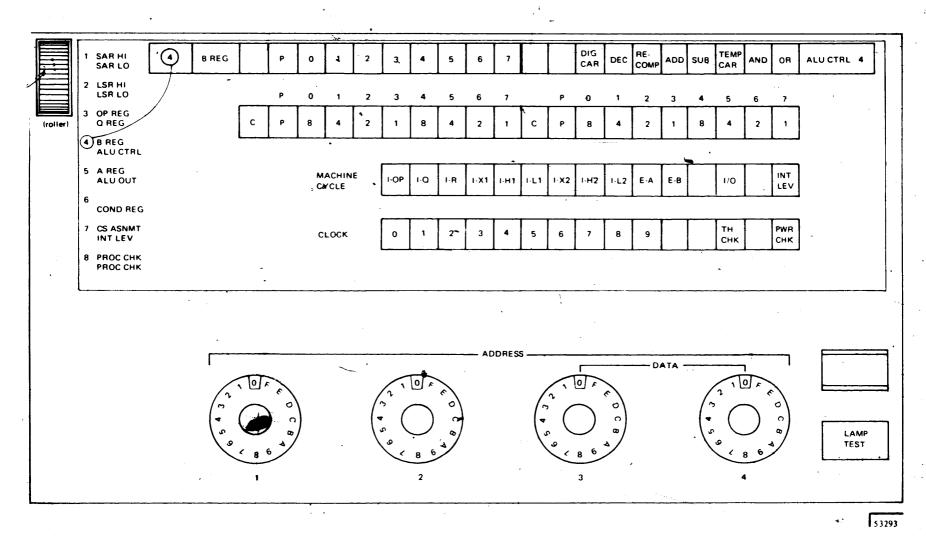

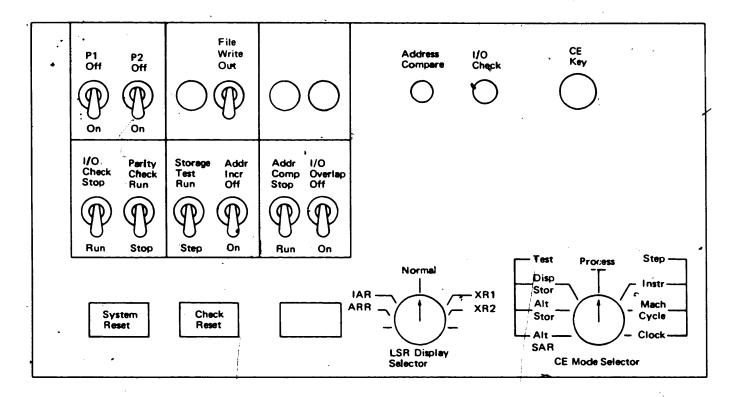

| CHAPTER 6. CONSOLE AND MAINTENANCE FEATURES.                                        | FR D03. 1-2             |

| SECTION 1, CONSOLE                                                                  | 6-1                     |

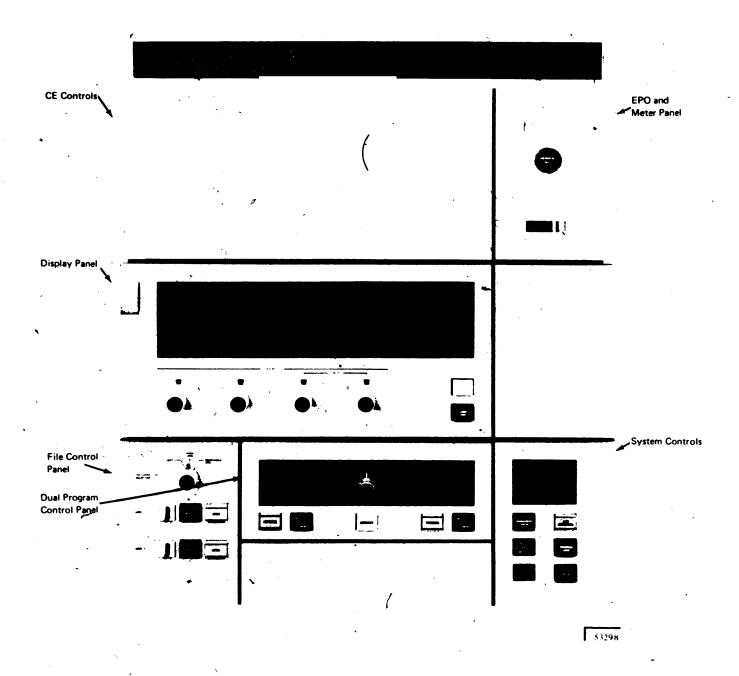

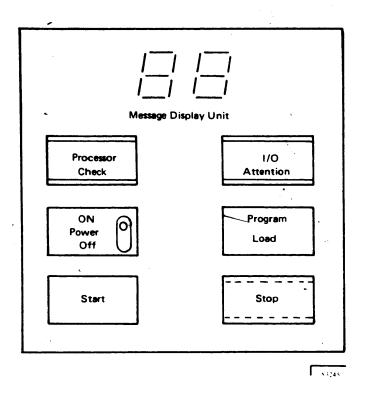

| System Control Panel                                                                | 6-1                     |

| Operator Controls                                                                   | 6-1                     |

| CE Controls                                                                         | 6-9                     |

| ČE Key Switch                                                                       | 6-9                     |

| Console Display                                                                     | 6-12                    |

| SECTION 2. MAINTENANCE FEATURES                                                     | 6-14                    |

| APPENDIX A. UNIT CHARACTERISTICS                                                    | FR D18, 1-2             |

# FRAME LOCATION TABLE

| Page             | Frame | Card  |

|------------------|-------|-------|

| 4-1              | C06   | 1-2   |

| 4-2              | C07   | 1-2   |

| 4-3              | C08   | 1-2   |

| 4-4              | C09   | 1-2   |

| 5-               | C11   | 1-2   |

| 5-4              | C14   | 1-2   |

| 5 <b>-</b> 5     | C15   | 1-2   |

| 5 <del>-</del> 6 | C16   | 1-2   |

| 5-7              | C17   | 1-2   |

| 5 <del>-</del> 8 | C18   | 1-2   |

| 5-9              | D01   | 1-2   |

| 6-1              | D03   | 1-2   |

| 6 <b>-</b> 9 *   | וווס  | 1-2   |

| 6-12             | D14   | 1-2   |

| 6-14             | D16   | 1-2   |

| A -1             | D18   | 1-2   |

|                  |       | -     |

|                  |       | y<br> |

| ÷ .              |       |       |

| •                |       |       |

|                  |       |       |

|                  |       |       |

|                  |       |       |

|                  |       | į     |