### FRAME LOCATION TABLE

| FRAME L | OCATIO!         | V TABLE  |

|---------|-----------------|----------|

| Page    | Frame           | Card     |

| 1-1     | All -           | 2-1      |

| 1-2     | Al2 -           | 2-1      |

| 1-3     | Al3 -           | 2-1      |

| 1-4     | Al4 -           | 2-1      |

| 1-6     | :- A16 -        | 2-1      |

| 1 3     | - A17 -         |          |

| 1-9     | - B01 -         | 2-1      |

| 1-10    | - B02 -         | 2-1      |

| l-11    | - B03 -         | 2-1      |

| 4       | - B05 -         | t t      |

| 2-1     | /B <u>0</u> 9 - | 2-1      |

| 2-2     | - B10 -         | 2-1      |

|         | - Bll -         |          |

|         | - B12,-         |          |

|         | - B14'          | 1        |

| •       | - B15 -         | /        |

| 2-8     | •               | - 2-1    |

|         | - B17           | - 2-/1   |

|         | - B18           | - 4      |

|         | C01             |          |

| 2-12    |                 |          |

| 2-14    |                 | 2-1      |

|         | C06             |          |

| 2-18    |                 | 1        |

|         | ~ ~             |          |

|         | C12             | - 42 - 1 |

| . )                             |     |     |     |      |      |          |     |     |    |      |     |

|---------------------------------|-----|-----|-----|------|------|----------|-----|-----|----|------|-----|

| CHAPTER I: INTRODUCTIO          | N.  |     | . , |      |      |          |     |     |    | FR.  | A11 |

| \$203 Line Printer              |     |     |     |      |      |          |     |     | _  | 1-1  |     |

| The Printer.                    |     |     |     |      |      |          |     |     | Ī  | 1-2  |     |

| Carriage                        |     |     |     |      |      | Ĭ.       | •   | •   |    | 1-2  |     |

| Printer Timing Devices          |     | ٠,  | Ċ   |      |      |          |     | •   | •  | 1-2  |     |

| Incrementer Emitter             | •   | • • | •   | •    | •    | •        | ٠   | •   | •  | 1-2  |     |

| Chain Entitter                  | •   | •   | •   | •    | ·    | •        | •   | •   | ٠. | 1-2  |     |

| Emitter (USC Peature)           | •   | •   | •   | •    | •    | •        | •   | •   | •  |      |     |

| Carriage Emitter                | •   | , . | •   | •    | ٠    | •        | ٠   | •   | •  | 1-3  |     |

| 5203 Principles of Ghain Printi | •   | •   | •   | •    | •    | •        | •   | ٠   |    | 1-3  |     |

| Theory                          | ııR | •   | ٠,  | •    | •    | •        | . 1 | ٠.  |    | 1-4  |     |

| Theory Incrementer and Hammer A | • . | • . | •   | •    | ٠- , | <i>.</i> | ٠   | ٠   | .4 | 14   |     |

| Continued and Hammer A          | иg  | nm  | ent |      | • !  | •        | •   | ٠   | •  | 14   |     |

| Subscans                        | •   |     | •   | •    |      |          | •   | •   | ٠  | 1-6  |     |

| Instruction Format              | •   | •   | •   | •    |      | •        | ٠.  |     |    | 1-7  |     |

| 1/U instruction Format          |     |     |     |      |      |          |     |     |    | 1-7  |     |

| a Start I/O (SIO) Instruction   |     | •   |     |      |      |          |     |     |    | 1-7  |     |

| Load I/O (LIO) Instruction      |     | . • |     |      |      |          |     | . • |    | 1-9  |     |

| Test I/O (TIO) Instruction      |     | , . |     |      |      |          |     |     |    | 1-10 |     |

| Advance Program Level (Al       | L)  | ins | tru | ctic | n    |          |     |     |    | 1-11 |     |

| Sense I/O (SNS) Instruction     | 1   |     |     |      |      |          |     |     |    | 1-13 |     |

| CHAPTER 2. FUNCTION                                                                                                      | AT TI  | NITC         |         |          | - '     | FR.   | В09 |

|--------------------------------------------------------------------------------------------------------------------------|--------|--------------|---------|----------|---------|-------|-----|

| THE HEIGHT PRINCIPLE                                                                                                     |        |              |         |          |         |       | 100 |

| Data Bus Out Register . Circuit Objectives Data Registers 1 and 2 .                                                      | •      | •            | • . •   | · ·      | •       | . 2-1 |     |

| Virguit Objectives                                                                                                       | •      |              | • •     |          | •       | . 2-1 |     |

| Data Pegisters 1 and 2                                                                                                   | 1 -    |              |         |          | •       | . 2-2 |     |

| Circuit Objectives                                                                                                       | • •    |              | • •     |          | •       | . 2-2 |     |

| Circuit Objectives . Q Register                                                                                          |        |              | ٠.,     |          | ٠,٠     | . 2-3 |     |

| Circuit Objectives .                                                                                                     |        |              | . •     | · ·      | . • . • | . 2-  |     |

| Circuit Objectives .                                                                                                     | • •    |              | •       | • • •    | • • •   | . 2-4 |     |

| Sense Bit Assembler .                                                                                                    | • •    |              | • •     | ,        |         | . 2-6 |     |

| Circuit Objectives .                                                                                                     |        |              | • •     |          | ٠. ٠    | 2-6   |     |

| Data Bus In Assembler Circuit Objectives Cycle Steal Counter Circuit Objectives Print Subscan Counter Circuit Objectives | • •    |              |         |          |         | . 2-7 |     |

| Circuit Objectives .                                                                                                     | • •    | • .          | •       | •        |         | . 2-7 |     |

| Cycle Steal Counter                                                                                                      | ;      |              | ,       | ·        |         | . 2-8 |     |

| Circuit Objectives                                                                                                       | •      |              |         |          |         | 2-8   |     |

| Print Subscan Counter .                                                                                                  |        |              |         | 1 .      |         | 2-8   |     |

| Circuit Objectives .                                                                                                     |        | 4.           |         |          |         | 2-9   |     |

| Mechanical Position Count                                                                                                | er     |              |         | F        | . ,     | 2-10  |     |

|                                                                                                                          |        |              |         |          | À       | 2-10  |     |

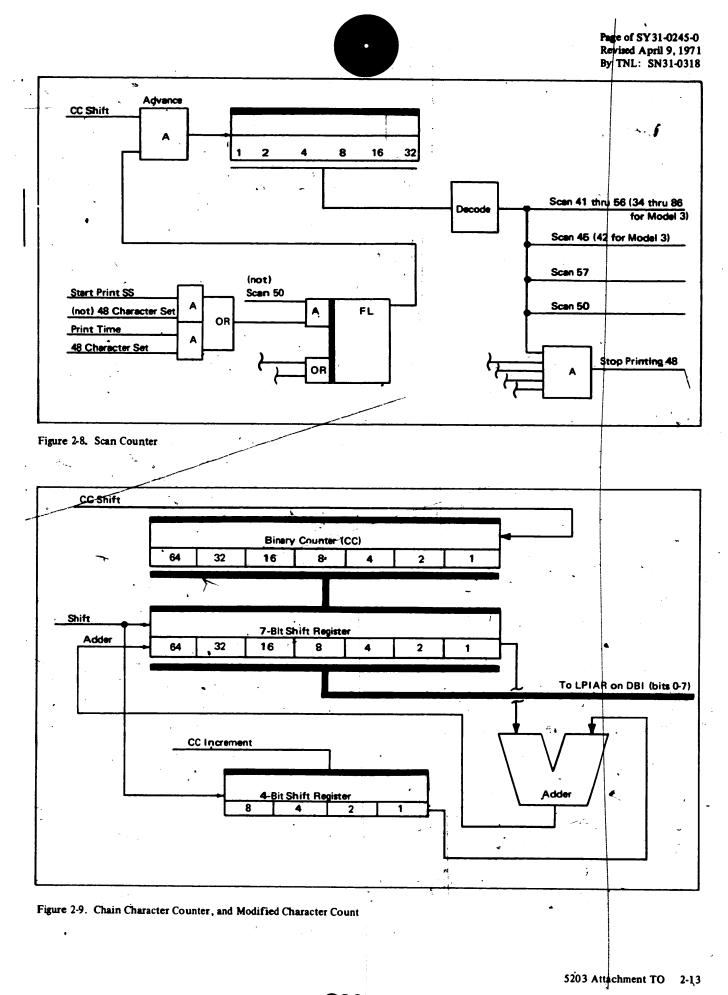

| Scan Counter                                                                                                             |        |              |         |          | . ,.    | 2-11  |     |

| Circuit Objectives                                                                                                       |        |              | : .     |          |         | 2-12  |     |

| Chain Character Counter                                                                                                  | Ź.     | , <b>4</b> . |         | <b>E</b> |         | 2-12  |     |

| Scan Counter Circuit Objectives Chain Character Counter Character Counter                                                |        |              |         |          |         | 2-12  |     |

| 7-Bit Shift Register, 4-E                                                                                                | it Shi | ft Regis     | ter. A  | lder     |         | 2-12  |     |

| Circuit Objectives                                                                                                       |        | •            | ,       |          | • •     | 2.12  |     |

| Circuit Objectives Overflow • Hammer Clock                                                                               |        | 4            | •       | • •      | • •     | 2.14  |     |

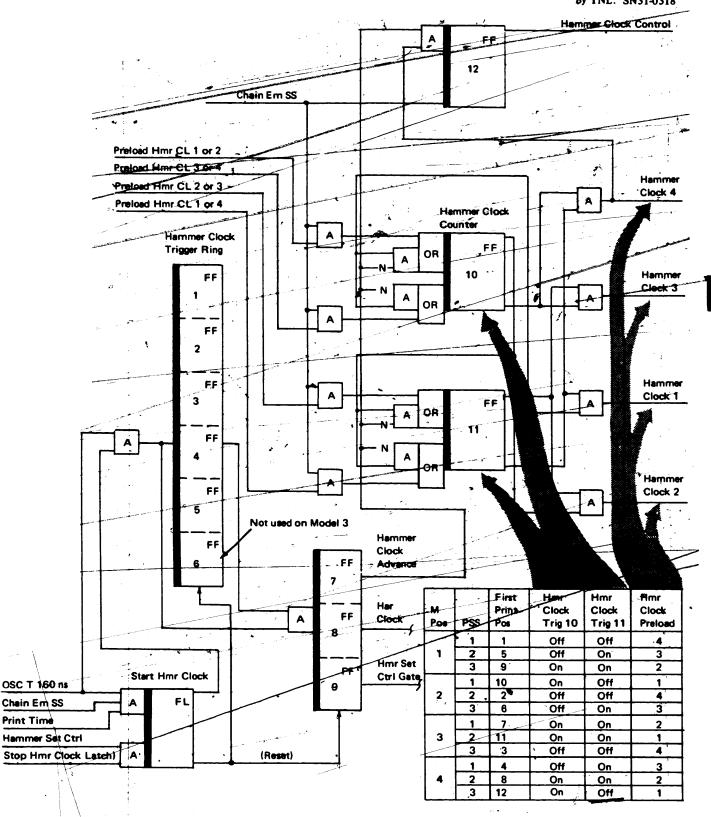

| Hammer Clock                                                                                                             |        | •            | • •     |          |         | 2-14  |     |

| Hammer Clock 1 Time                                                                                                      |        | • •          | ' .     | • •      |         | 2.16  |     |

| Hammer Clock 2 Time                                                                                                      | • •    | • •          | • •     |          |         | 2.16  |     |

| Hammer Clock 3 Time                                                                                                      | 4      |              |         |          |         | 216   |     |

| Hammer Clock 4 Time                                                                                                      |        |              | •       | A        | • , •   | 2-16  |     |

| Circuit Objectives                                                                                                       | •      | <i>:, :</i>  | • •     | •        |         | 2-10  |     |

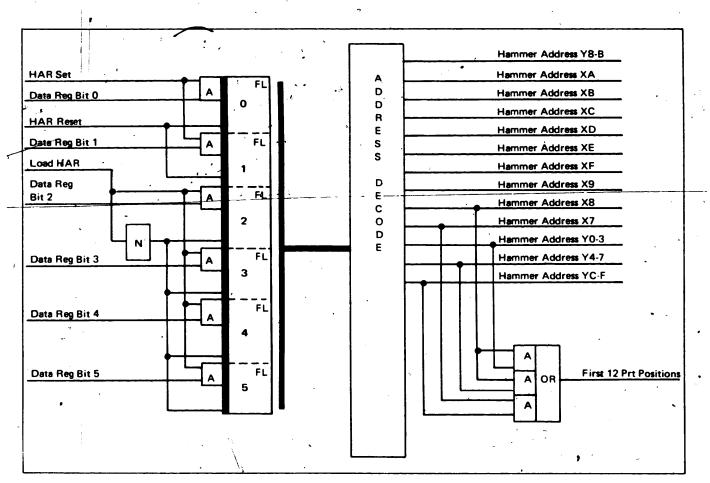

| Hammer Clock 4 Time Circuit Objectives Hammer Address Register Circuit Objectives Hammer Check LSR Ciscuit Objectives    | • • •  |              | •       | • :      |         | 2-10  |     |

| Circuit Objectives                                                                                                       | •      | •            | • •     | ٠.       |         | 2.10  |     |

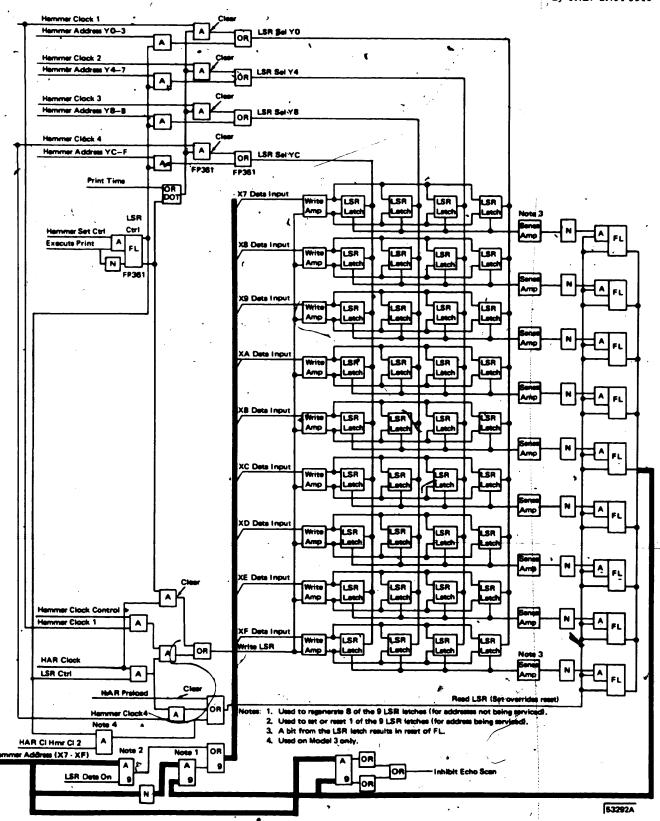

| Hammer Check I SD                                                                                                        | • ,    | • 1          | • . •   |          | •       | 2-18  |     |

| Ciscuit Objectives                                                                                                       | • •    | • •          | <u></u> | · ·      | i}      | 2-19  |     |

| - Carcuit Objectives , .                                                                                                 | • •    | ٠ مر         | • . •   | . ,      |         | 2-22  |     |

### FRAME LOCATION TABLE

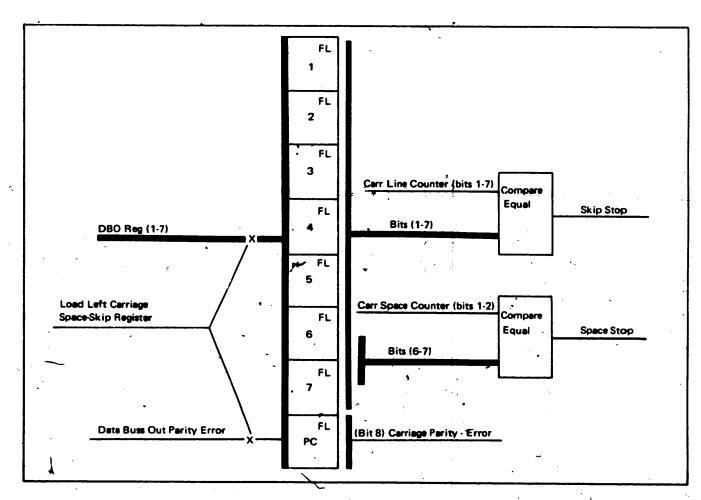

| SECTION 2. CARRIAGE                       | . 2-23         |       |

|-------------------------------------------|----------------|-------|

| Carriage Space-Skip Register              | . 2-23         |       |

| · C: : 1. O1 : :                          | . 2-23         |       |

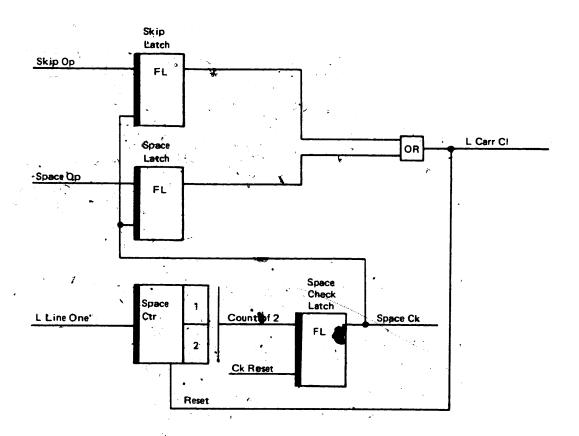

| Space Operation                           | 2-24           |       |

| Skip Operation                            | 2-24           |       |

| Skip Operation                            | 2.24           |       |

|                                           | . 2-24         |       |

|                                           | . 2-24         |       |

|                                           |                |       |

|                                           | . 2-26         |       |

|                                           | . 2-28         |       |

|                                           |                |       |

| Space Check Counter                       | . 2-28         |       |

|                                           | . 2-28         |       |

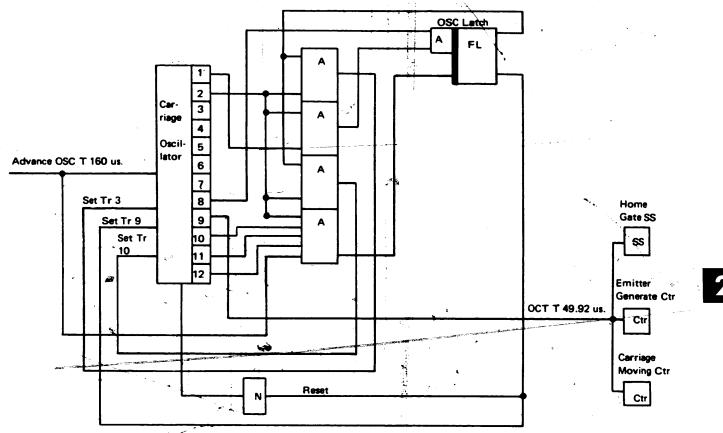

| Carriage Oscillator                       | . 2-30         |       |

| Circuit Objectives                        | . 2-30         |       |

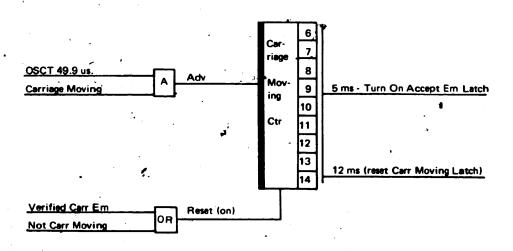

| Carriage Moving Counter                   | . 2-30         |       |

|                                           | . 2-30         |       |

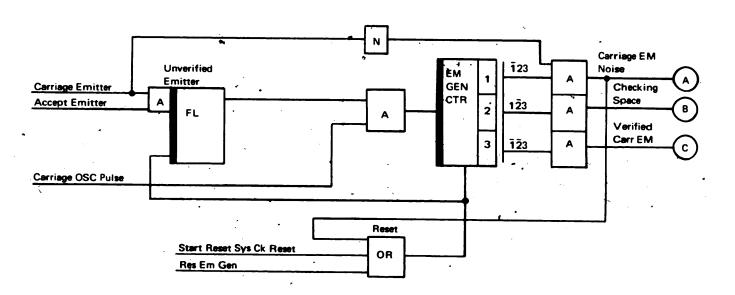

| Emitter Generate Counter                  | . 2-32         |       |

| Circuit Objectives                        | . 2-32         |       |

| •                                         |                |       |

| CHAPTER 3. PRINCIPLES OF OPERATION        | .FR.           | D06   |

|                                           | . 3-1          |       |

| Print Cycle Steals                        | 3-1            |       |

| Initial Cycle Steal (PC0)                 | 34             | *     |

| Initialize Attachment Circuitry           | . 3-2          |       |

| First Cycle Steal (PC1)                   | 3-2            |       |

|                                           | . 3-3          |       |

| Third Cycle Steal (PC3)                   | . 3-3          |       |

| Third Cycle Steal (PC3)                   | 3-4            |       |

| Hammer Driver Reset (No Data, or No Print | . 374          |       |

| Compare)                                  | 2.5            |       |

| Cycle Regeneration and Ending Operation   | . 3-5<br>. 3-5 |       |

| Unprintable Character                     |                |       |

| Carriage Operations                       | . 3-5          |       |

|                                           | . 3-5          |       |

| Carriage Space                            | . 3-5          |       |

| Carriage Skip                             | 3-6<br>3-7     |       |

| Manual Carriage Operations                |                |       |

| I/O Instructions                          |                |       |

| Start I/O Instruction                     |                |       |

| Load I/O Instruction                      | . 3-10         | •     |

| Test I/O Instruction                      | . 3-10         |       |

| Advance Program Level Instruction         | 3-12           |       |

| Sense I/O Instruction                     | . 3-12         |       |

|                                           | T D            | E03   |

| CHAPTER 4. FEATURES                       | • -            | E02   |

| Dual Feed Carriage                        |                |       |

| 120 and 132 Print Positions               | 4-1            |       |

| Circuit Objectives                        | . 4-2          |       |

| 200 LPM                                   | ·i. 4-2        |       |

| 300 LPM                                   | . 4-2          |       |

| Universal Character Set                   |                |       |

| Overflow (UCS)                            | . 4-3 .        |       |

| CHAPTER 5. POWER SUPPLIES AND CONTROLS    | FR.            | E07   |

| CHAPTER 6. CONSOLE AND MAINTENANCE        | ED             | E00   |

| FEATURES                                  | FR.            | EUY   |

| ADDENING                                  | מים            | E-11  |

| APPENDIX                                  | FR.            | LII   |

|                                           |                |       |

| miden                                     | $_{\star}$ FR. | A 0,3 |

|                                           |                |       |

| •                                         |                |       |

| Page                 | Frame Card |

|----------------------|------------|

| 2-23-                | C13 2-1    |

| 2-24-                | C14 2-1    |

| 2-26-                | C16 2-1    |

| 2 <sup>2</sup> -28 - | C18 2-1    |

| 2-30-                | D02 2-1    |

| 2-32-                | D04 2-1    |

| 3-1 -                | D06 2-1    |

| 3-2 -                | D07 -2-1   |

|                      | D08 2-1    |

| 3-4 -                | D09 2-1    |

| _                    | D10 2-1    |

|                      | DN 2-1     |

| 3-7                  | D12 2-1    |

|                      | - D15 2-1  |

| 3-12                 |            |

| 4-1                  | - E02 2-1  |

| 4-2                  | - E03 2-1  |

| 4-3                  | - E04 2-1  |

| INDEX                | - A03 2-1  |

|                      |            |

|                      |            |

|                      |            |

|                      |            |

|                      |            |

|                      |            |

| <u> </u>             |            |

| ADVANCE PROGRAM LEVEL INSTRUCTION FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                            | CARD                                                                                                                             | FR.                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| PARITY 1-12  Q BYTE 1-12  STORAGE ADDRESS 1-12  APL OPERATION 3-12                                                                                                                                                                                                                                                                                                                                                                                                  | TC C2+1<br>TC C2+1<br>TO C2-1<br>TO C2-1                                                                                         | 804<br>804<br>804<br>D17                               |

| CARRIAGE FORMS LENGTH REGISTER 2-24 CARRIAGE FORMS LENGTH REGISTER 2-25 CARRIAGE LINE COUNTER 2-26 CARRIAGE LINE COUNTER 2-27 CARRIAGE MOVING COUNTER 2-31 CARRIAGE MOVING COUNTER 2-31 CARRIAGE CPERATION 3-5 CARRIAGE CPERATION 3-5 CARRIAGE SCILLATOR 2-30 CARRIAGE SKIP 3-6 CARRIAGE SPACE 3-5. CARRIAGE SPACE COUNTER 2-28 CARRIAGE SPACE COUNTER 2-28 CARRIAGE SPACE COUNTER 2-23 CHAIN CHARACTER COUNTER 2-12 CHAIN CHARACTER COUNTER AND MUDIFIED CHARACTER | TO C2-1<br>TO C2-1 | C15<br>C16<br>C17<br>D01C<br>D110<br>D110<br>C13<br>CC |

| CYCLE STEAL COUNTER 2-a CYCLE STEAL ONE (PC1) 3-2 CYCLE STEAL THREE (PC3) 3-3 CYCLE STEAL TWO (PC2) 3-3 CYCLE STEAL ZERO (PCC) 3-1 CYCLE STEALS 3-1                                                                                                                                                                                                                                                                                                                 | TO 22-1<br>TO 22-1<br>TO 22-1<br>TO 22-1<br>TO 22-1<br>TO 32-1                                                                   | DC8<br>DC8<br>DC8<br>DC6                               |

| DATA BUS' IN ASSEMBLER 2-7 DATA BUS OUT REGISTER 2-1 DATA REGISTER 1 AND 2 2-2 DUAL FEED CARRIAGE 4-1                                                                                                                                                                                                                                                                                                                                                               | TC C2-1<br>TO C2-1<br>TC C2-1<br>TC C2-1                                                                                         | 809                                                    |

| EMITTER GENERATE COUNTER 2-32                                                                                                                                                                                                                                                                                                                                                                                                                                       | TC 22-1                                                                                                                          | UC4_                                                   |

| FEATURES 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  | E 72                                                   |

| HAMMER ADDRESS REGISTER 2-18 HAMMER ALIGNMENT 1-4 HAMMER CHECK LSF 2-19 HAMMER CLCCK 2-16 HAMMER CLCCK 2-17 HAMMER RESET 3-4                                                                                                                                                                                                                                                                                                                                        | TO C2-1                                                                          | 8<br>A14<br>CCC7<br>DC                                 |

| INSTRUCTION FORMAT OP CODE 1-7 PARITY 1-7 O PYTE 1-7 I/U INSTRUCTIONS 3-7                                                                                                                                                                                                                                                                                                                                                                                           | 70 02-1<br>10 02-1<br>10 02-1<br>10 02-1                                                                                         | A 1 7                                                  |

| LINE PRINTER DESCRIPTION CARRIAGE 1-2 PRINTER 1-1 PRINTER 1-2 LDAD I/C INSTRUCTION FORMAT                                                                                                                                                                                                                                                                                                                                                                           | TC 'c2-1<br>TC 'c2-1<br>TC 'C2-1                                                                                                 | ·                                                      |

| LSR MAIN STORAGE AREAS 1-10 PARITY 1-10 O RYTE 1-10 STORAGE ADDRESS DESCRIPTION 1-10 EDAD I/O N FIELD C BYTE DECCUE 3-11 LOAD I/O UPERATIONS E-B CYCLES 3-10 I-D CYCLES 3-10                                                                                                                                                                                                                                                                                        | TC C2-1                                                                          | 002<br>002<br>016<br>015                               |

| A POSITION COUNTER AND DECCEE 2-10 MANUAL CARRIAGE UPERATION 3-7. MANUAL RESTORE 3-7. MANUAL SPACE/ 3-7. MECHANICAL POSITION CLUNTER 2-10.                                                                                                                                                                                                                                                                                                                          | TO C2-1<br>TO C2-1<br>TO C2-1<br>TO C2-1                                                                                         | D12+                                                   |

| •   |                                    |                                                           | INDEX                 |         |       | AKU                                          | FR                   |

|-----|------------------------------------|-----------------------------------------------------------|-----------------------|---------|-------|----------------------------------------------|----------------------|

|     | NO DATA<br>NO PRINT                | 3-4 . COMPARE 3-                                          | 4                     | • • •   | • • • | TU 02-1<br>TO 02-1                           | DU9<br>D09           |

|     | OVERFLOW                           | 2-14                                                      | • • •                 | • • • • |       | N_22-1                                       | CC 4                 |

|     | PRINCIPLE                          | 5-1.<br>ES OF CHAIN P<br>ERATION                          | KINTING .             | 1-4 : . | • • • | TO 02-1<br>TO 02-1                           | E37                  |

|     | C YÛ LE<br>ENDÎN                   | REGENERATION                                              | 3-6                   | 2       | • • • | TC 02-1<br>TC 02-1<br>TO 02-1                | 010<br>013<br>07     |

|     | HAMMEI<br>HAMMEI<br>INITI          | R FIRING 3-4<br>R RESET 3-4<br>AL CYCLE STEA              | 4 ;                   | 3-1.    |       | TC 02-1<br>TJ 02-1                           | D19<br>D19           |

|     | THIPD                              | D CYCLE STEAL<br>CYCLE STEAL                              | (PCA) 3-              | 3-3     |       | TU 02-1<br>TU 02-1<br>TU 02-1                | 018<br>018           |

|     | PKINTER                            | BSCAN COUNTER                                             | ∠ <b>-</b> と •        | • • •   | • • • | TC 02-1.                                     | 316                  |

|     | CARF<br>CHA<br>INC                 | G DEVICES<br>PIAGE EMITTER<br>IN EMITTER<br>REMENTER EMIT | 1+2<br>TEK 1-2        |         |       | TC 02-1<br>TO 02-1<br>TC 02-1                | A13<br>A12<br>A12    |

| í   | PRINTING<br>PSS COUN               |                                                           | 3                     |         | 3     | TC 52-1<br>TC 52-1<br>TC 52-1<br>TC 52-1     | A13<br>A15<br>E17    |

|     | Q REGISTI<br>Q REGISTI             | ER 2-4<br>ER AND DECÇUE                                   | 2-5                   | • • •   | • • • | TO 02-1<br>TO 02-1                           | #12<br>#13           |

|     | SCAN COUL<br>SCAN COUL<br>SENSE BI |                                                           |                       | • • •   |       | TC 02-1<br>TC 02-1<br>TC 02-1                | C01<br>C13<br>314    |

|     | PARIT                              | Y 1-15                                                    |                       | 1-14    |       | TO 02-1<br>TO 02-1<br>TO 02-1                | 817<br>818<br>818    |

|     |                                    | MC L f D 11 f                                             | • • •                 | • • •   | • • • | Tu 22-1                                      | ∋18                  |

|     | SPACE CHI                          | ECK CCU <b>Æ</b> IFA                                      | -20<br>-25<br>-45κΜΔΤ |         |       | TO 02-1<br>TO 02-1<br>TO 02-1                | 017<br>C18<br>011    |

|     | CCNTRI<br>PARITI                   | (L (CDE 1-8<br>Y (1-9 ).<br>E 1-8                         |                       |         |       | The C2-1<br>The C2-1<br>The C2-1<br>The C2-1 | 419<br>871<br>410    |

|     | START I/O<br>START I/O<br>I-G C    | ON FIELD C FOUND FRATION N                                | va : .                | 3-9.    | • •   | $\frac{1}{1}, \frac{3z-1}{z^2-1}$            | $\frac{014}{013}$    |

|     | I-R C'<br>Subscan (                | YCLE 3-8 .                                                |                       | /       |       | $\frac{12-1}{12-1}$                          | 115<br>116           |

| • . | TEST 170<br>PARITY                 |                                                           | FERMAT                |         |       | T 22-1<br>T 22-1                             | PC4<br>RCZ           |

|     | STORAL<br>TEST 1/6                 | GE ADDRESS DE<br>N FIELD C CY<br>CPERATION                | <b>きこしょりじ</b> しじとし    | 1-10    |       | 10 02-1<br>10 02-1<br>10 02-1                | 1018<br>1018<br>1015 |

|     | UNIVERSĂ                           | L CHARACTER S                                             | ET . 4-2.             |         | •     | T 22-1                                       | EUR                  |

|     |                                    |                                                           |                       |         |       |                                              |                      |

# CONTINUED ON FRAME \_\_ ^07\_\_

CONTINUED ON FRAME \_\_A07 \_\_

# Maintenance Library

| Chapter 1. Introduction FR.A1]                     |  |

|----------------------------------------------------|--|

| Chapter 2. Functional Units FR.809                 |  |

| Chapter 3. Principles of Operation FR.D06          |  |

| Chapter 4. Features FR.E02                         |  |

| Chapter 5. Power Supplies and Controls FR.E07      |  |

| Chapter 6. Console and Maintenance Features FR.E09 |  |

| Appendix FR.E11                                    |  |

**Printer Attachment** for System/3: Theory of Operation

### **Preface**

This manual explains the operation of the IBM 5203 Printer Attachment.

Other manuals needed to understand and service the printer attachment are:

- The IBM Maintenance Library 5203 Printer Attachment for System/3: Diagrams, SY31-0240.

- The IBN 5203 Printer, Field Engineering Theory of Operation Manual, SY33-1045.

- The IBM \$203 Printer, Field Engineering Maintenance Manual, \$Y33-1046.

- The IBM 5410 Central Processing Unit, Field Engineering Theory of Operation Manual, SY31-0207.

- The IBM Maintenance Library 5410 Processing Unit for System/3: Diagrams, SY31-0202.

- The IBM 5410 Central Processing Unit, Field Engineering Maintenance Manual, SY31-0244.

For machine characteristics, refer to the IBM System/3 Installation Manual – Physical Planning, GA21 4884.

FE Supplement No. SN31-0318 dated April 9, 1971 has been added to this manual on Microfiche.

### **Summary of Amendments**

Information about the 5203 Model 3 theory is included in this TNL. Also, this TNL updates the title to: IBM Maintenance Library 5203 Printer Attachment for System/3: Theory of Operation.

### First Edition

Some illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.

Changes are continually made to the specifications herein; any such change will be reported in subsequent revisions or technical newsletters.

A Reader's Comment Form is at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Product Publications, Department 245, Rochester, Minnesota 55901.

C Copyright International Business Machines Gorporation 1969

### **Abbreviations**

Arithmetic Logic Unit? **ALU APL** Advance Program Level CCCharacter Counter **CPU Processing Unit** Device Address DA Data Bus In DBI **DBO** Data Bus Out **EOL** End of Line Hammer Address Register HAR

HAK Hammer Address Registe

I/O Input/Output UO Load Input/Output

LPDAR Line Printer Data Address Register

LPTAR Line Printer Image Address Register

LPM ■ Lines Per Minute

LSR Local Store Register

M Mechanical Position

MAP Maintenance-Analysis Procedure

MST Monolithic Systems Technology

PC Print Cycle Steal

POR Power On Reset

PSS Print Subscan

SDR Storage Data Register

SIO Start Input/Output

SLD Solid Logic Dense

SNS Sense

SS Single Shot

TIO Test Input/Output

TP Test Point

UPC Universal Character Set

UPC Unprintable Character

WO With Out

# INTRODUCTION

A10

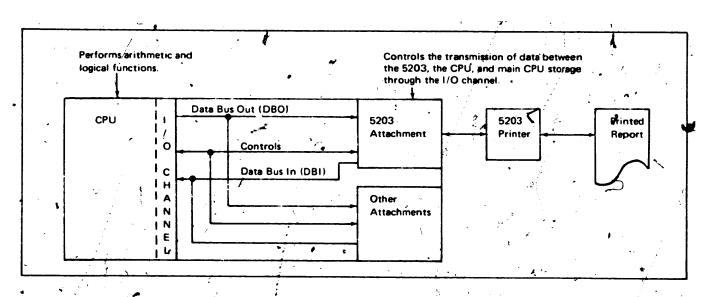

The IBM 5203 Printer Attachment provides a means for the attached 5203 Printer to use the facilities of the IBM 5410 Central Processing Unit (CPU) to communicate with main storage. The attachment provides the communication lines between the printer and the CPU and controls the transfer of all information between the two (Figure 1-1).

The attachment circuitry is MST-1 logic, physically located on gate A, board B1 in the 5410 CPU. The control interface lines between the attachment board and the electronics board are SLD-100 levels. Conversion to MST occurs at the attachment board.

The communications path between the CPU and the printer attachment is through the I/O channel. Using this channel, data and control information is transferred from the CPU, and status is sent to the CPU under control of stored program instructions.

During the process of exchanging information, the printer and CPU operate together in multiplexer mode. This means the information transfer takes place between CPU, cycles on a priority basis with other devices.

By means of a fixed-cycle steal priority, I/O cycles may be interleaved between any two CPU cycles to fetch or store data to and from the attachment. The 5203 Printer Attachment may be granted as many as three I/O cycles in a row.

### **5203 LINE PRINTER**

\*

- The 5203 Line Printer has 96, 120, or 132 print positions.

- Four print positions are served by one print hammer.

- The printer has four mechanical print positions per print line.

- The printer uses a type chain that travels at a constant speed.

- The printer has a paper-handling tapeless carriage.

Figure 1-1. 5203 Data Flow

### The Printer

The standard printer has 96 print positions, with a 100 LPM throughput, and a paper-handling tapeless carriage controlled by the attachment. Features available are 200 and 300 LPM throughput, 120 print positions, 132 print positions, a dual feed carriage, and a universal character set. This manual describes the 132-position printer unless otherwise stated.

The printer uses a 240-character type chain. A set of 48 characters repeated five times on the chain permits the rated throughput on the 100, 200, and 300 LPM models. A universal character set (UCS) of 120 characters repeated twice on the chain results in reduced throughput. The standard printer uses 24 hammers spaced four print positions apart. The four positions are called the four mechanical positions M1-M4. The hammers are held in one M position until all 48 characters are optioned to print. Then they are cam driven to cover the other three print positions ('hammer shift clutch' line to printer) under control of the attachment. With the UCS feature, the hammers are held in one position until end of line is detected by the attachment. The chain travels at a constant speed and is not stopped during printing. This means that a character is impressed as well as rubbed off on the form.

The printer supplies timed pulses to the attachment. One of these pulses is the home pulse which marks the beginning of each character set. Following the home pulse, another pulse is sent when character 1 is aligned with print position 1. This is the first subscan pulse. With a 48-character set, 144 subscan pulses are sent before the next home pulse occurs; this means that three subscan pulses are sent for each character. The home pulse, in conjunction with the character set and subscan pulses, allows the attachment to trace each character in relation to optioned positions.

### Carriage

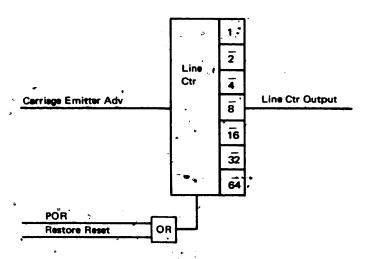

The carriage is a tapeless device controlled by the printer attachment circuitry. Forms movement is synchronized to the print line by the carriage emitter which generates a pulse for each line of print.

Before starting a print operation, the number of printable lines used is loaded into a carriage forms length register.

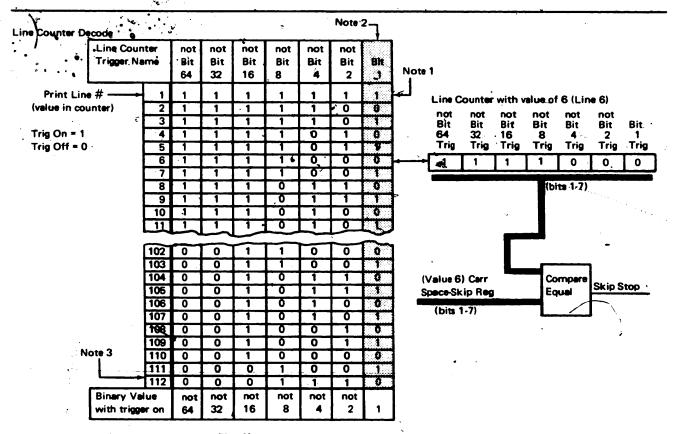

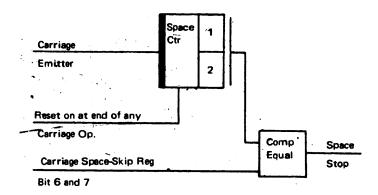

Carriage motion, space or skip, is determined by the start I/Q instruction.

### **Printer Timing Devices**

The printer informs the using system about all mechanical motions that the system must take into consideration to exert logical control. The printer indicates the chain slug alignments (options to print), and mechanical position (M position). There are four basic timing devices. These are:

- 1. The incrementer emitter.

- 2. The chain emitter. •

- 3. The UCS emitter (UCS feature).

- 4. The carriage emitter.

The actual timing devices are magnetic emitters, (chain, UCS, and carriage), and a photo cell (incrementer emitter). The magnetic emitters consist of transducers which sense that a timing slot, or steel tip passes by.

### Incrementer Emitter

The incrementer uses a slot wheel that exposes or covers a light source as the incrementer rotates. A photo cell opposite the light generates a pulse each time the light beam hits the photo cell. These pulses are sent to a counter in the attachment to determine the mechanical position of the hammer unit.

### Chain Emitter

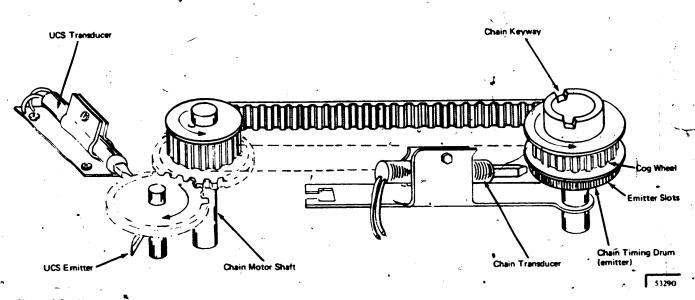

The chain is driven by a three-phase synchronous motor via gears and a cog belt (Figure 1-2) Fr. A13. One of the gear shafts bears the chain timing drum. This drum is divided into 144 evenly spaced slots. A 145th slot resides between the 144th and the first slot; this 145th slot represents the home pulse.

The gear ratio is such that the chain timing drum completes five revolutions for each chain revolution. This means the home pulse appears before each of the five (standard 48) character sets and each home pulse is then followed by subscan pulses. There are 144 subscan pulses: three subscans are required to offer one character to each print position and, since the basic character set consists of 48 different characters, we have  $48 \times 3 = 144$  subscans per character set.

If this pulse scheme is examined independent of character sets, it is obvious there are three subscan pulses for every character on the chain; the chain is composed of 240 character positions. The chain drum performs five revolutions for each chain revolution (for each passing of 240 characters), so it generates five times 144 subscan pulses which results in 720 subscan pulses. Dividing these 720 subscan pulses by 240 characters results in three pulses per character as required; however, the five home pulses are used as such only with the standard character set.

### Emitter (UCS Feature)

Any character set larger than 48 different characters is defined as a universal character set (UCS). The size of the set may dry from 49 to 120 different characters per set, with some graphics repeated until a 120 - character set is defined.

Whenever any type of UCS chain is installed on the printer, an additional chain drum is installed; this "drum" consists of a gear driven shaft with a steel tip attached (UCS emitter). This steel tip rotates 6-times per chain revolution (Figure 1-2) supplying 6 UCS home pulses. One chain emitter pulse and one UCS home pulse coincide once per chain revolution and this pulse is recognized as the home pulse. A microswitch activated by a stud on the UCS cartridge indicates to the attachment that single home pulses must be ignored because a UCS chain is installed.

### Carriage Emitter

A carriage emitter pulse is generated during every carriage operation as each printable line is passed. The attachment counts the number of pulses and stops the carriage clutch as required.

Figure 1-2. Chain and UCS Emitter

### **5203 PRINCIPLES OF CHAIN PRINTING**

- One print cycle consists of 4 mechanical positions (M positions) for printing one line.

- The printer attachment options 132 print positions in one print cycle (132 position feature).

- The printer has 33 print hammers (132 position feature).

- A hammer bar moves the hammers to M positions 1, 2, 3, and 4.

- The printer attachment options 33 hammers to all 48 characters to fire in one M position.

- The printer attachment options 33 print, positions (addresses) to print in one M position.

- A subscan is the time required to option one-third of the hammers (11) with 11 print positions.

- A scan is the time required to option all 33 hammers with 33 print positions (three subscans).

- 50 scans option 48 characters for one M position. The last 2 scans are for checking.

- The UCS feature needs 121 or fewer scans.

### Theory

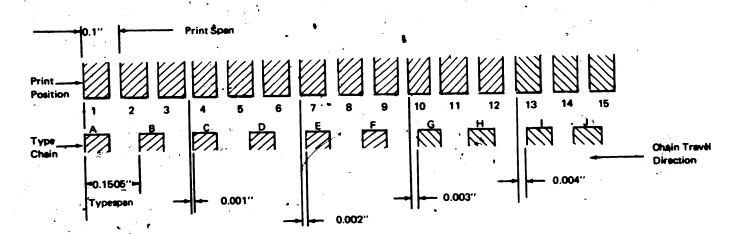

Like many chain printers, the distance between one type slug on the chain and its adjacent slug is 50% ± 0.0005" greater than between adjacent print positions (Figure 1-3). This arrangement offers these combined advantages:

- Because of sequential alignment, simultaneous printing in adjacent positions is avoided.

- 2. Sufficient compare time is available to determine whether or not a hammer should be fired.

Because we have a continuously moving type chain, we need some means of determining when to fire a particular hammer to print the proper character. Using Figure 1-4 Fr. A15 as reference, observe the relationship between the moving type chain and the print-hammer positions. The figure shows the character A aligned with print position 1. In the 5203, if the character A is aligned to print in print position one, and in print position 13 is the next character aligned to print. Between the A alignment and the I alignment, the chain will travel 0.004 inch. On Models 1 and 2, this makes 31 microseconds available to determine whether or not a hammer should be fired. The time is decreased to 19.39 microseconds on the Model 3.

### Incrementer and Hammer Alignment

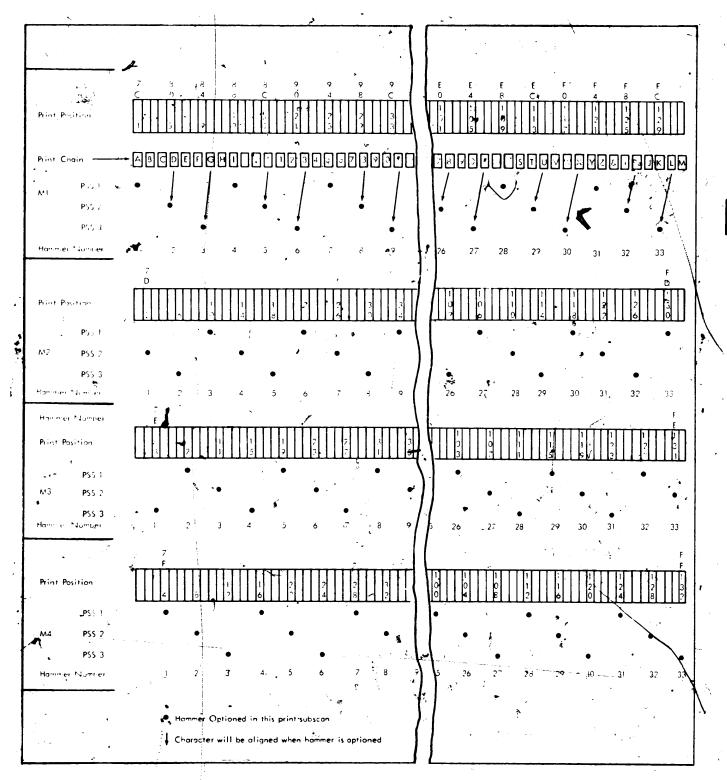

The following is a description of hammer incrementing and aligning that applies to the 5203 Printer (four-position hammer unit) with 132 print positions and 33 hammers.

Home position after power-on or error-reset operation places the hammers in the extreme right position of the incrementer (M4).

The print operation begins with hammer 1 facing print position 4, hammer 2 facing print position 8, hammer 3 facing print position 12, etc. (Figure 1-4)Fr. A15 First, consider that 44 print positions become aligned during one subscan (one third of the 132 print positions).

Figure 1-3. Actual Print Scan to Type Span Relationship

Figure 1-4. 5203 Printing Sequence

Page of SY31-0245-0 Revised April 9, 1971 By TNL: SN31-0318

Because there is only one hammer for every 4 print positions, only 11 of the 44 print positions that become aligned can be optioned to print during each subscan. In one print scan, 33 print positions are optioned to print. A print scan Imust be taken for each character in the particular character Let being used. For example, if the character set contains 48 characters, 48 print scans (144 subscans) must be taken to option each of the 33 print positions. Optioning each of the 33 print positions that face a hammer to every character in the character set, is called an increment scan. The initial increment scan with the hammers in mechanical position 4 (M4) is called increment scan 4. At the end of increment scan 4, the hammers are decremented (moved left one print position) so that hammer 1 faces print position 3, hammer 2 faces print/position 7, hammer 3 faces print position 33, etc.. The hammers are now facing a second group of 33 print positions. Again, a print scan is taken for each character in the character set. This sequence is called increment scan 3.

At the end of increment scan 3, the hammers are decremented so that hammer 1 sces print position 2, hammer 2 faces print position 6, hammer 3 faces print position 10, etc. The hammers are now facing a third group of 33 print positions. Again, a print scan is taken for each character in the character set. This sequence is called increment scan 2.

Finally, the hammers are decremented so that hammer 1 faces print position 1, hammer 2 faces print position 5, hammer 3 faces print position 9, etc. When the print scans are complete for increment scan 1, all of the 132 print positions have been optioned to print every character in the character set, and a print line is complete.

If the 200 or 300 LPM feature is installed, the sequence for the next print line is similar, but the increment scans are reversed. Because hammer 1 was facing print position 1 at the end of the previous print line, the next print line starts with increment scan 1. Then increment scans 2, 3, and 4, and another print line is complete. Because hammer 1 is facing position 4, this print line will start with increment scan 4. When increment scan 4 is complete, the hammers are decremented so that hammer 1 faces print position 3, hammer 2 faces print position 7, etc. Increment scan 3 is followed by increment scan 2, which, in turn, is followed by increment scan 1. For increment scan 1, hammer 1 is again facing print position 1. Thus, printing of the lines alternates between a progression (1, 2, 3, 4) and a regression (4, 3, 2, 1) of the increment scans.

If the printer and attachment are 100 LPM, the hammers are returned to M position 4, after printing in M position 1. This is done before a new print line is started. Increment scans will always regress (4, 3, 2, 1).

It is now apparent that 4 increment scans are required for one complete line of print. Using a character set of 48 characters, 192 print scans (576 subscans) are required to print one line. A position in the print line is printed only when the hammer faces the position and the correct character is aligned.

### Subscans

For this explanation of subscans, assume a 200 line-perminute printer with 132 positions (33 hammers) and assume that the hammer unit is at position M1.

Subscan 1 starts when any chain character (in this case an A) is aligned with print position 1 (Figure 1-4)Fr. A15 (It does not matter which character starts scan 1, because all characters become aligned with print position 1.) Subscan 1 lasts until the next character on the chain is aligned with print position 2. During subscan 1, the first alignment occurs at print position 1, the next alignment occurs at the third position (counting from 1) which is print position 4, and so forth. Thus, the alignment progresses through the following print positions: 1, 4, 7, 10, 13, 16, 19, 22, 25, etc. Figure 1 -4Fr. A15 shows that hammers are allocated to print positions 1, 5, 9, 13, 17, 21, 15, 29, etc. Note that the alignment is useful only for positions 1, 13, 25, 37, etc. ending with position 121 during subscan 1. This means that of the 44 theoretical alignments to print that occur during subscan 1, only 11 useful options to print occur. Three subscans provide 33 options to print. This can be seen by examining the next subscan in detail. During subscan 2, chain characters are aligned with print positions 2, 5, 8, 11, 14, 17, etc. (with every third position). Again, only 11 print positions (5, 17, 29, 41 and every subsequent 12th position) are aligned while hammers are in position for printing.

By now, the scanning scheme should be apparent; three subscans are required to offer a single character to 33 print positions. Since three subscans make up one print scan, 48 print scans are required to offer each character contained in a 48 character set to the 33 print positions. For this feason, 48 print scans for more with UCS feature) are termed one increment scan, or M position. To print an entire 132-position print line requires 4 increment scans = 192 print scans = 576 subscans (based on a 48 character set).

Our explanation started with the hammer unit at position M1; note that the first 48 print scans (the first increment scan) occurred without cam motion. The clutch now unlocks the cam and the hammer bar begins to move until the next M position, M2, is reached. This lasts long enough to allow the next 48 print scans. After three positions have passed, the right home position (M4) is reached, and forms movement can be initiated. Then, the same action occurs right to left. It can now be seen that the printer must signal the attachment (1) when a useful option to print exists (the PSS chain emitter), and (2) when the hammers have moved to the next M position (increment emitter). The attachment can then tell the CPU to compare the chain character with the character in storage and decide whether or not to print.

### **INSTRUCTION FORMAT**

### I/O Instruction Format

The CPU stored program uses five I/O instructions to control the printer attachment:

- 1. Start I/O

- 2. Load I/O

- 3. Test I/O

- 4. Advance Program Level

- 5. Sense I/O

### Op Code

The first byte of each instruction is the op code. During the I-OP cycle, the CPU decodes the op code and informs the printer attachment of the presence of the instruction. This information is sent to the attachment on the channel tag out lines 'SNS instr', 'LIO instr', 'TIO instr'. and 'SIO instr'. The channel uses the 'TIO instr' tag lines for both test I/O and advance program level instructions,

### Q Byte .

The second byte of each instruction is the Q byte. During the I-Q cycle, this byte is placed on the DBO lines at clock 5 time. All attachments on the channel receive the Q byte and check its parity (correct parity is odd) for all I/O instructions regardless of the condition of the I/O device or the device address of the Q byte.

### Parity

If an attachment finds the parit of the Q byte is even, it raises both 'I/O condition A' and 'I/O condition B' at clock 5 of the I-Q cycle.

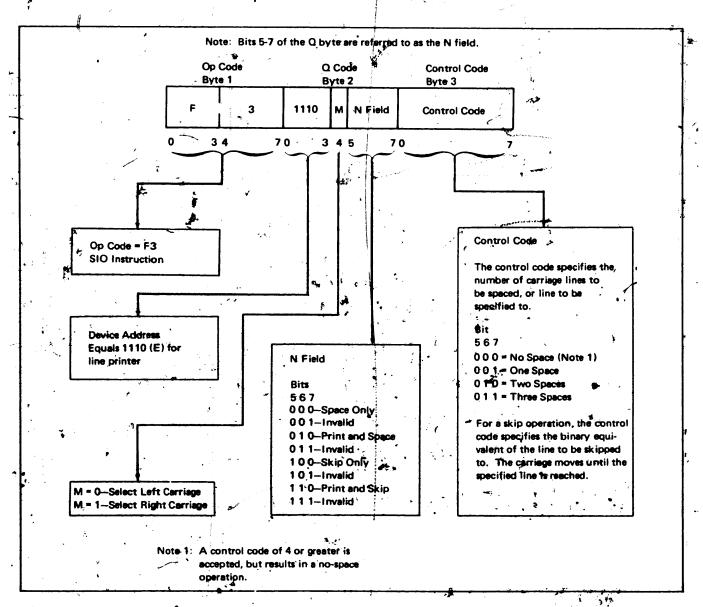

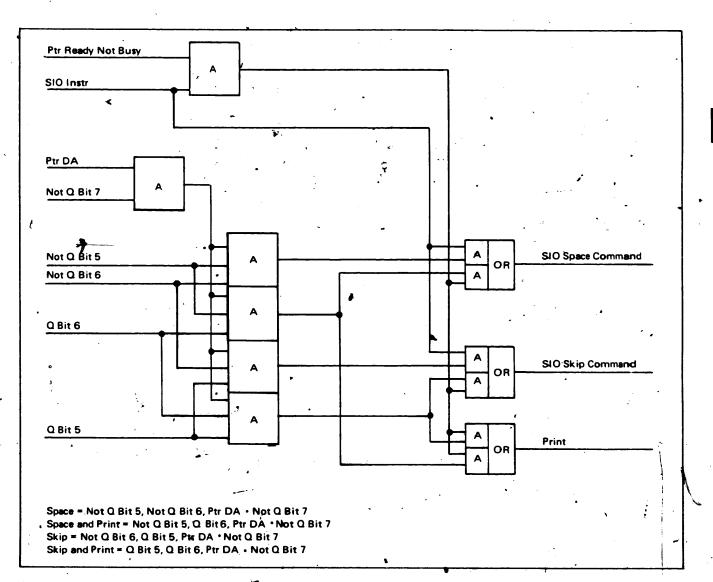

### Start I/O (SIO) Instruction

- Three bytes make up the SIO instruction.

- The SIO instruction selects the line printer whenever the device address equals E (hexadecimal).

- The SIO instruction can select either the right or the left carriage.

- The N field of the SIO instruction specifies one of the following operations:

- 1. Space only.

- 2. Print and space.

- 3. Skip only.

- 4. Print and skip.

- Both carriages can operate simultaneously (with dual feed carriage feature installed), but a separate SIO instruction is required for each carriage.

The SIO instruction is composed of three bytes (Figure 1-5). The first byte is the op code, an F3 (hexadecimal). The second byte contains the device address (a hexadecimal E for the line printer), a primary or secondary modifier (M bit), and an N field. The third byte specifies carriage spacing.

### 'Q Byte Description

Bits 0-3 specify the device address of the line printer. Bit 4 is the M field and specifies the carriage used—an M bit of 0 specifies the left carriage, and an M bit of 1 specifies the right carriage,

Note: If the dual feed carriage feature is not installed, an M field of 1 results in a processor check stop and the INV-Q light comes on

Bits 5-7 hold the N field. Refer to Figure 1-5 for the N field code. An invalid N field causes a processor check stop, and causes the INV-Q light to come on.

### Control Code

The control code specifies carriage spacing. A 0, 1, 2, or 3 specifies the carriage to space 0, 1, 2, or 3 spaces, respectively. A control code of 4 or greater is accepted, but results in a space 0 operation.

Figure 1-5. SIO Instruction Format

CONTINUED ON FRAME BOI

For a skip operation, the control code specifies the binary equivalent of the line to which the form must skip. The carriage moves the form until the specified line is reached.

### Parity and Error Conditions

The SIO instruction must maintain odd parity. If even parity is detected by the attachment circuitry, a processor check stop occurs and the DBO parity light comes on. The attachment ignores the instruction and sets a No-Op status bit if a device error exists when the SIO instruction is received. Program interlock occurs whenever a printer busy condition is detected, or operator intervention is required as indicated by the I/O attention light.

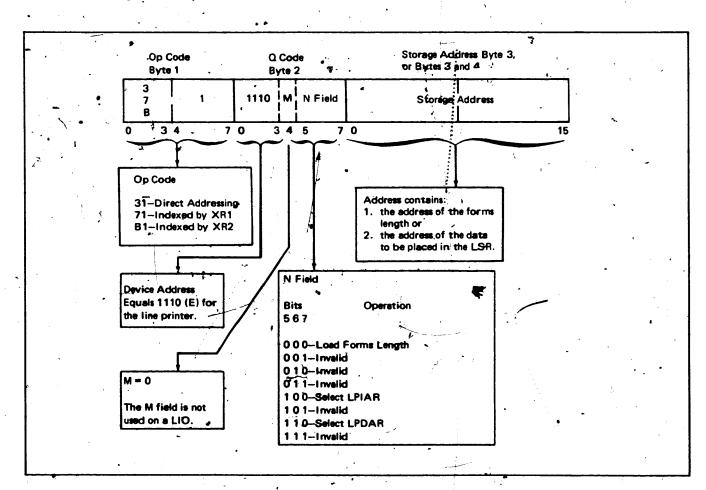

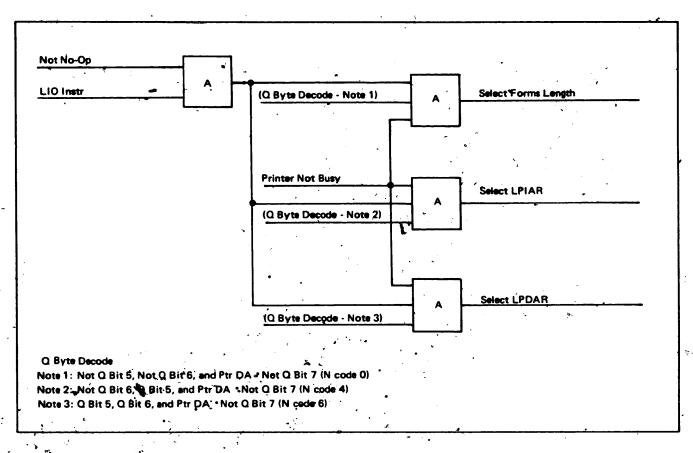

### Load I/O (LIO) Instruction

- Three or four bytes make up the LIO instruction (direct addressing, 4 bytes; indexing, 3 bytes).

- The LIO instruction selects the line printer when the device address equals E (hexadecimal).

- The M field of the LIO is insignificant (that is, not necessary to select a carriage).

- The N code of the LIO instruction is used to:

- 1. Select the forms length register in the attachment to be loaded, or

- 2. Select the LPIAR in the CPU for preloading, or

- 3. Select the LPDAR in the CPU for preloading.

The LIO instruction is composed of 3 bytes if the op code indicates indexing, or 4 bytes if the op code indicates direct addressing (Figure 1-6). The first byte is the op code. The second byte contains the device address (a hexadecimal E for the printer), a primary or secondary modifier (M bitnot significant for this instruction), and an N field. The third, or third and fourth, specifies one of the following:

- 1. The address of the storage location containing the forms length.

- 2. The storage location of the data (address) to be placed in the selected LSR.

Figure 1-6. LIO Instruction Format

### Q Byte Description

Bits 0-3 specify the address of the line printer. Bit 4 is the M field and is not used for an LIO instruction.

Bits 5-7 are the N field. Refer to Figure 1-6 Fr. B01 for the N code. An invalid N field causes a processor check stop, and causes the INV-Q light to come on.

### Storage Address Description

The storage address portion contains the storage address of the 2-byte main storage field where information specified by the N field is located. If the N field specifies that the forms-length registers are to be loaded, (1) the data at the specified address is placed into the right-carriage forms length register (dual carriage feature) and (2) the data at the specified address minus 1 is placed into the left-carriage forms length register. If the N field specifies the preloading of the line printer data address register (LPDAR), the 2-byte field specified is placed into the LPDAR. If the N field specifies preloading the line printer image address register (LPIAR), the 2-byte field specified is placed in the LPIAR.

### LSR Main Storage Areas

The core area addressed by the two address registers is as follows:

- 48 character set image must be in the 48 bytes of core location XV00 through XV2F.

- 120 character set image must be in the 120 bytes of core location XW00 through XW77.

- Line printer data for 96 print positions must be in the 96 bytes of core location XX7C through XXDB.

- Line printer data for 120 print positions must be in the 120 bytes of core location XY7C through XYF3.

- Line printer data for 132 print positions must be in the 132 bytes of core location XZ7C through XZFF.

- The addresses XV, XW, XX, XY, or XZ are assigned by the programmer and may or may not be the same.

The line printer data field in core beginning at location XX7C corresponds character to character to the print line beginning at print position one.

### Parity and Error Conditions

The LIO instruction is accepted only if the printer is not busy. A parity error detected by the attachment results in a processor check stop, and the DBO parity check light comes on. If the No-Op status bit is on from a previous SIO instruction, the instruction is ignored by the attachment.

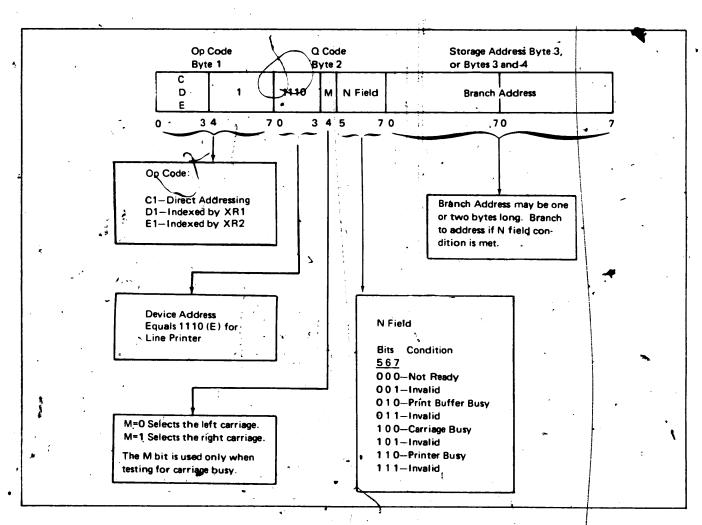

### Test I/O (TIO) Instruction

- Three or four bytes make up the TIO instruction (direct addressing 4 bytes, indexing 3 bytes).

- The TIO instruction selects the line printer when the device address equals E (hexadecimal).

- Either the right or the left carriage is selected during the TIO instruction execution.

- The N code of the TIO instruction specifies a test for one of the following:

- 1. Not ready.

- 2. Print buffer busy.

- 3. Carriage busy.

- 4. Printer busy.

The TIO instruction is composed of three or four bytes (Figure 1-7) Fr. BO3 The first byte is the op code. The second byte contains the device address (a hexadecimal E for the line printer), a primary or secondary modifier (M bit), and an N field. The third byte, or third and fourth bytes, contains the branch to address if the N field condition is met.

### Q Byte Description

Bits 0-3 specify the data address of the line printer. Bit 4 is the M field and specifies the carriage used. An M bit of 0 specifies the left carriage, and an M bit of 1 specifies the right carriage.

Bits 5-7 are the N field. Refer to Figure 1-7 Fr. BO3 for the N field code. An invalid N field causes a processor check stop, and the INV-Q light comes on. The N field contains the condition code that determines the test to be performed.

### Storage Address Description -

The storage address portion of the TIO instruction contains the branch to address if the condition tested for (as specified by the N field) is met.

### Parity and Error Conditions

The TIO instruction must maintain odd parity. A parity error detected by the attachment results in \*processor check stop, and the DBO parity check light comes on. If the No-Op status bit is on from a previous LIO instruction, the instruction is ignored by the attachment.

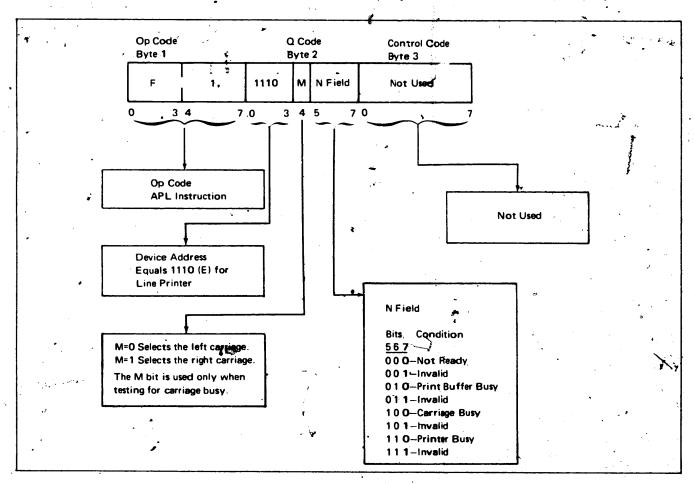

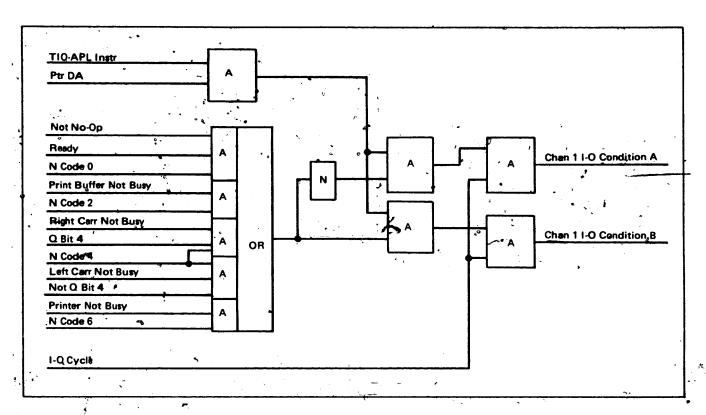

### Advance Program Level (APL) Instruction

- Three bytes make up the APL instruction (byte 3 not used).

- The APL instruction selects the line printer whenever the device address equals E (hexadecimal).

- Either the right or the left carriage is selected during the APL instruction execution.

- The N code of the APL instruction specifies a test for one of the following:

- 1. Not ready.

- 2. Print buffer busy.

- 3. Carriage busy.

- 4. Printer busy.

- The APL instruction is used on machines that have the dual program feature installed.

- The format of the APL instruction is similar to the TIO instruction.

Figure 1-7. TIO Instruction Format

The APL instruction is composed of three bytes (Figure 1-8). The first byte is the op code, an F1 (hexadecimal) for an APL instruction. The second byte contains the device address (a hexadecimal E for the line printer), a primary or secondary modifier (M bit), and an N field. The third byte is not used.

If the Dual Program Feature is installed in the CPU, the APL instruction determines whether the program should proceed to the next sequential instruction or change levels.

### Q Byte Description

Bits 0-3 specify the address of the line printer. Bit 4 is the M field and specifies the carriage used. An M bit of 0 specifies the left carriage, and an M bit of 1 specifies the right carriage.

Bits 5-7 are the N field. Refer to Figure 1-8 for the N field code. An invalid N field causes a processor check stop and the INV-Q light comes on. The N field contains the condition code that determines the test to be performed.

### Storage Address Description

The storage address portion of the APL instruction is not used; that is, it is ignored by both the CPU and the attachment.

### Parity and Error Conditions

Odd parity must be maintained in the APL instruction. A parity error detected by the attachment results in a processor check stop, and the DBO parity check light comes on. If the No-Op status bit is on from a previous APL instruction, the instruction is ignored by the attachment.

Figure 1-8. APL Instruction Format

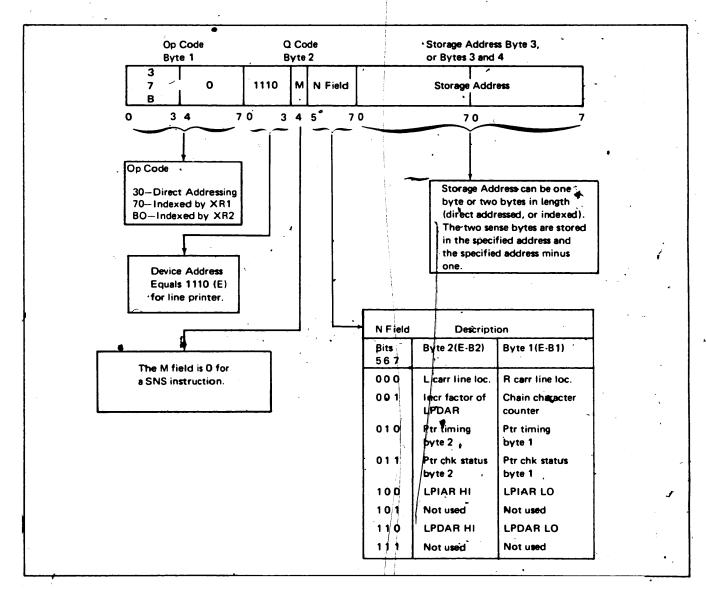

### Sense I/O (SNS) Instruction

- Three or four bytes make up the SNS instruction (direct addressing 4 bytes, indexing, 3 bytes).

- The SNS instruction selects the line printer whenever the device address equals E (hexadecinal).

- The M field of the SNS instruction is insignalicant (that is, not necessary to select a carriage).

- The N code of the SNS instruction is decoded to obtain the following sense information:

- 1. Right or left carriage line location.

- 2. The increment factor of the LPDAR.

- The value in the chain character counter.

- 4. Printer timing bytes.

- 5. Printer check status bytes.

- . LPIAR or LPDAR high or low order bytes.

- The SNS instruction can be used at any time, whether the printer or attachment is busy or not.

The SNS instruction is composed of three or four bytes (Figure 1-9). The first byte is the op code. The second byte contains the device address (a hexadecimal E for the line printer), a primary or secondary modifier (M bit—not significant for this instruction), and an N field. The third, or third and fourth bytes, contains the address of the storage area in which sense bytes will be stored.

Figure 1-9. SNS Instruction Format

### **Q** Byte Description

Bits 0-3 specify the data address of the line printer. Bit 4 (M field) is not used for an SNS instruction.

Bits 5-7 are the N field. Refer to Figure 1-9 Fr. 805 for the N field code. An invalid N field causes a processor check stop, and the INV-Q light comes on.

### Storage Address Description

The storage address portion of the instruction contains the storage address of the 2-byte field in main storage where the sense information specified by the N field is to be stored. Byte 1 is stored at the storage address specified. Byte 2 is stored at the storage address specified minus 1.

The following is a breakdown of each byte specified by the N field:

N Code Q: 000—Carriage print line location. This instruction should be preceded by a TIO for busy to ensure that the carriage location sensed is static.

N Code 1: 001—These bytes are provided for MTAP diagnostics.

Byte 1—When not printing, this is the value of the chain character counter indicating the character in print position one.

When printing, this is the value of the chain character counter indicating the character in the next print position being addressed.

Note: Because the chain character counter is being advanced asynchronously to the SNS instruction, an SNS made at the time the chain character counter is in transition from one count to another may result in an invalid count.

Byte 2-This indicates the binary amount to add to or subtract from the LPDAR when printing.

N Code 2: 010-Prifiter timing. These bytes are provided for MTAP diagnostics.

Byte 1 Bit 0: Hammer increment clutch—indicates clutch, control is active in the attachment. The SNS bit is not latched.

- Bit 1: Print start SS—incrementer emitter pulse indicating hammers are positioned to print in new dwell. The SNS bit is not latched.

- Bit 2: Left or right carriage clutch—indicates that one or both of the clutch controls are active in the attachment. The SNS bit is not latched.

- Bits 3-5: These bits correspond to the first, second, and third print cycle steals respectively.

The bits are latched and reset with the SNS instruction.

- Bit 6: Hammer set pulse—timing pulse which turns the hammer driver latches on. The bit is latched and reset with the SNS instruction.

- Bit 7: Right shift position—output of reed relay that senses when the hammer unit is in the extreme right position. The SNS bit is not latched.

- Byte 2 Bit 0: Left or right carriage emitter—indicates the forms have moved from one print line to the next print line for each emitter pulse. The SNS bit is not latched.

- Hit 1: Execute print latch—defines the execution time of the print instruction. The SNS bit is not latched.

- Bit 2: Chain emitter—includes home emitter pulse has been received from the printer indicating alignment to print. The bit is latched and reset with the SNS instruction.

- Bit 3: PSS1 pulse—this is the first of three subscans in any given print scan. The SNS bit is not latched.

- Bit 4: Print time—indicates chain synchronization with the instruction. The SNS bit is not latched.

- Bit 5: CE sense bit-not latched.

- Bit 6: Mechanical position one—hammer unit is at leftmost mechanical position. The SNS bit is not latched.

- Bit 7: Home gate-indicates the end of a character set on the chain installed. The SNS bit is not latched.

N Code 3: 011—Printer check status. These bytes are for program interrogation. The SNS bits are latched and reset by pressing the printer start key or the system check reset key, unless otherwise noted.

Byte 1 Bit Q: Chain sync check—indicates the loss of synchronization between the chain and the chain character counter.

Bit 1: Incrementer sync check—indicates the loss of synchronization between the incrementer and the mechanical position counter.

Bit 2: Thermal check—indicates excessive temperature in the hammer area. The SNS bit is not latched.

Bits 3 and 4: Not used.

Bit 5: 48 character set chain—indicates that the standard 48 character set chain is installed.

The SNS bit is not latched.

Bit 6: Unprintable character—indicates that an unprintable character exists in the print data area. The SNS bit is latched and reset with each new SIO print instruction.

Bit 7: CE sense bit—this bit can be temporarily wired at the board level to monitor available signals. The SNS bit is not latched.

Byte 2 Bit 0: Carriage sync check—indicates loss of synchronization between the forms line, and the carriage line counter. This condition occurs as a result of a missing carriage emitter pulse.

Bit 1: Carriage space check—indicates that the carriage has moved farther than the command specified. This condition occurs as a result of an extra chain emitter pulse.

Bit 2: Forms jam check-indicates paper is not feeding properly.

Bit 3: Incrementer failure check—indicates the hammer incrementing unit failed to respond when the clutch control was activated.

Bit 4: CE sense bit latched—this bit can be temporarily wired at the board level to monitor available signals.

Bit 5: Hammer echo check-indicates improper response of hammer driver during print time.

Bit 6: Any hammer on check—indicates a hammer or the check circuit is defective, when not in print time.

Bit 7: No-Op-indicates that the instruction was accepted but not executed because of an error. This condition is reserve an SNS instruction.

N Code 4: 100-Selects the LPIAR (selects the LSR used as the line printer image address register).

N Code 5: 101-Invalid.

N Code 6: 110-Selects the LPDAR (selects the LSR used as the line printer data address register).

N Code 7: 111-Invalid.

### Parity and Error Conditions

The SNS instruction which is accepted at all times by the printer attachment

### Parity and Error Conditions 🤜

The SNS instruction, which is accepted at all times by the printer attachment, must maintain odd parity. A parity error detected by the attachment results in a processor check stop, and the DBO parity check light comes on. If the no-op status bit is on from a previous SNS instruction, the attachment ignores the current instruction.

### FUNCTIONAL

### UNITS

**B08**

### Section 1. Printer

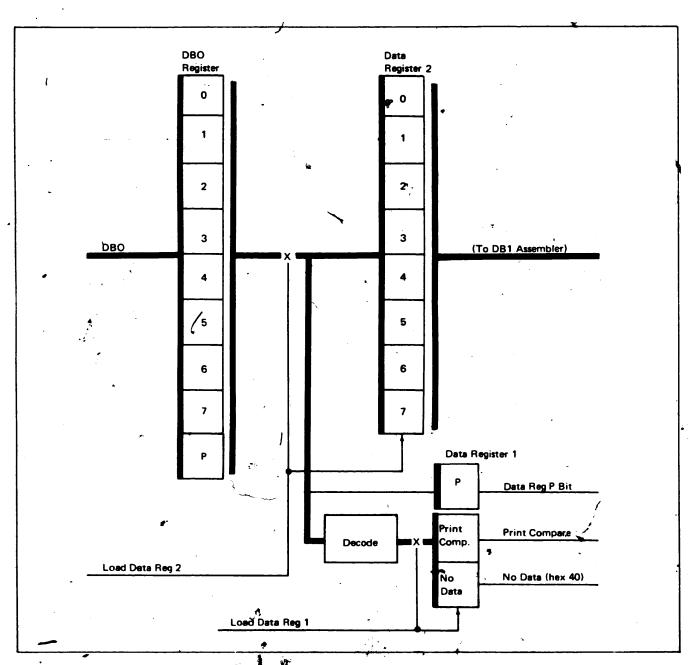

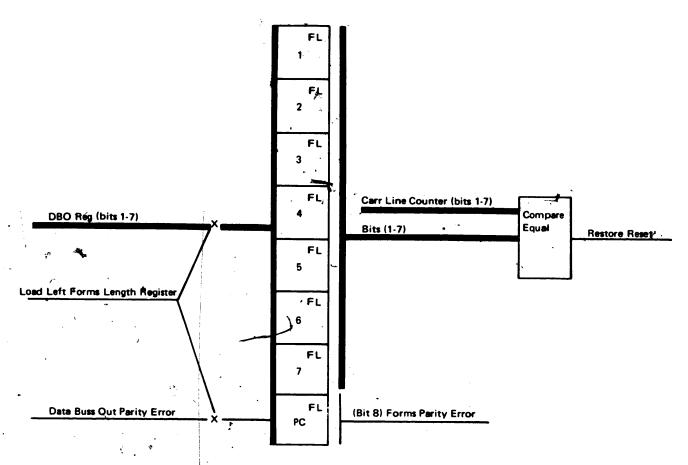

### **DATA BUS OUT REGISTER**

- The data bus out (DBO) register has nine flip latches.

- All print data from the CPU enters the attachment through the data bus out register setting the appropriate flip latches.

- The latches remain set if there is a parity error, so the CE can observe the contents of the register.

- Data from the data bus out register loads the data register, carriage space-skip register, carriage forms length register, Q register, and the hammer address register.

### **Circuit Objectives**

Refer to FEMD 4-015 and Figure 2-1. The DBQ register output follows the input. The latches remain set if a parity check occurs so the CE can observe the contents of the register.

### **DATA REGISTERS 1 AND 2**

- The data registers sample the DBO register to store and decode cycle steal data.

- The data registers have a total of eleven flip latches (eight for storing a data character and three for decoding).

Figure 2-1. DBO and Data Register

### On print cycle steal zero:

- 1. Data register 2 stores the main storage address of the first data character to be optioned for printing.

- 2. Data register 2 preloads the hammer address register with the same data character address.

- On print cycle steal one:

- 1. Data register 2 stores a data character from the main storage location addressed by the LPDAR.

- Data register 1 decodes it to see if it is a blank(hexadecimal 40) or data.

- On print cycle steal two:

- 1. Data register 2 places the data character in the data bus in (DBI) assembler.

- Data register 1 decodes the results of ALU subtraction to check for a print compare (no bits active).

### Circuit Objectives

Refer to FEMD 4-015 and Figure 2-1 Fr. B10 The data register flip latches are set by the outputs of the data bus out Tlip latches and by activating the 'load data reg 1' or 'load data reg 2' lines.'

During PCO, the data register accepts the main storage address of the character that is going to be optioned first for printing. The data register latches are set by 'load data reg 2' at 'sample DBO cl 3'. At clock 4, the data address is loaded into the hammer address register.

During PC1, the data character to be optioned for printing is loaded into the data register. Data register latches are set by 'load data reg 2' at 'sample DBO of 5'. At the same time, the data character is decoded to see if it is a blank character (hexadecimal 40). If it decodes as a hexadecimal 40, the 'no data' data register latch is set. Setting this latch activates 'pc group end' and no more print cycles are taken. If any code other than a hexadecimal 40 is decoded, the 'no data' latch does not set and PC2 will be requested.

During PC2, the data character is put into the DBI assembler at 'pc2 • cl 1' and taken to the A register in the CPU. An image character, addressed by the LPIAR, is subtracted in the ALU from the A-register character and the results are 'returned to the data register. At 'sample DBO cl 5' the 'load data reg 1' line is activated to decode the results of This subtraction. If all the returning data bits are inactive, the 'compare' latch in the data register sets and 'print compare' becomes active. If any of the returning data bits are active, the 'compare' latch will not be set and 'pc group end' will become active, and no more cycle steals will be taken.

If the 'compare' latch was set, PC3 occurs and the character is printed.

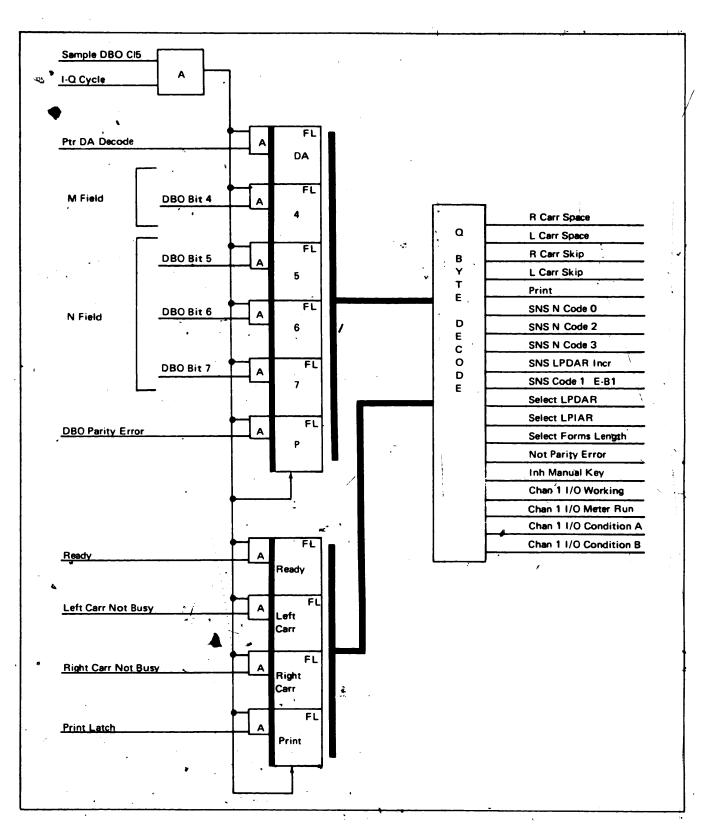

### **Q REGISTER**

- Consists of a six-position Q register, a four-position status register, and a Q byte decode.

- The six-position Q register samples the DBO register to determine the contents of the Q byte of the instruction.

- The four-position status register records whether or not

(1) the left carriage is busy, (2) the right carriage is busy,

(3) the print buffer is busy, and (4) the printer is ready at the time the Q register is loaded.

- The Q byte decode decodes the outputs of the Q register and the status register.

The Q register (Figure 2-2) Fr. B13 decodes the instruction Q byte to determine printer status and to select the appropriate printer response.

During the I-Q cycle, the Q register samples the Q byte data stored in the DBO register. The printer DA bits are decoded and recorded as one bit in the Q register.

The status register is also sampled during the I-Q cycle. Conditions checked for are left carriage busy, right carriage busy, print buffer busy, and printer ready. The outputs of the Q register and the status register are decoded to determine the channel condition (A or B) and the appropriate select or sense lines are activated in the attachment.

### Circuit Objectives

Refer to FEMD 4-020. At sample DBO clock 5 time of an I-Q cycle, 'sample Q byte' is activated. With this line active, the contents of both the Q register and status register are sampled and decoded. The appropriate select, sense, and condition lines are activated in the Q byte decode circuits.

Figure 2-2. Q Register and Decode

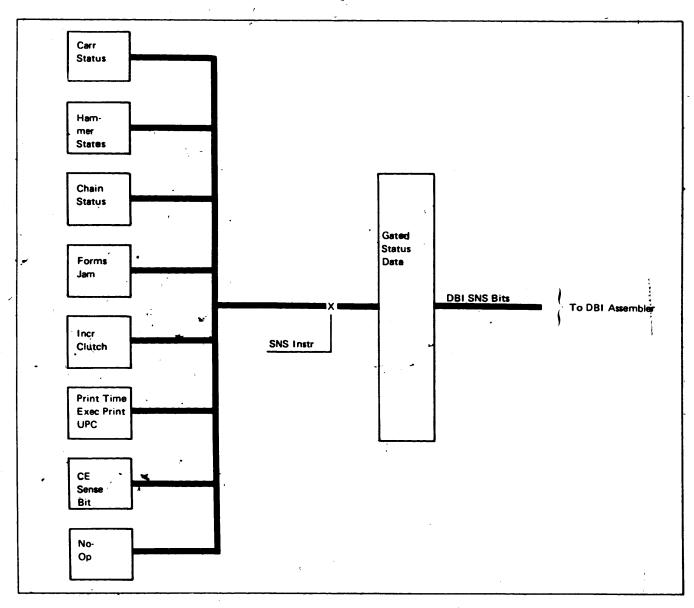

### SENSE BIT ASSEMBLER

- The SNS bit assembler contains the status of the printer attachment logic.

- The SNS bits are placed in the DBI assembler and sent to the CPU on E-B cycles.

- The sense bit assembler (Figure 2-3) gates the status of the printer attachment logic circuitry. This status information is available at any time an SNS instruction is received by the printer. The SNS is accepted by the attachment whether or not the printer is busy. The status is decoded into DBI SNS bits, placed in the DBI assembler, and sent to the CPU.

### Circuit Objectives

Refer to FEMD 4-025 through 4-045.

Figure 2-3. Sense Bit Assembler

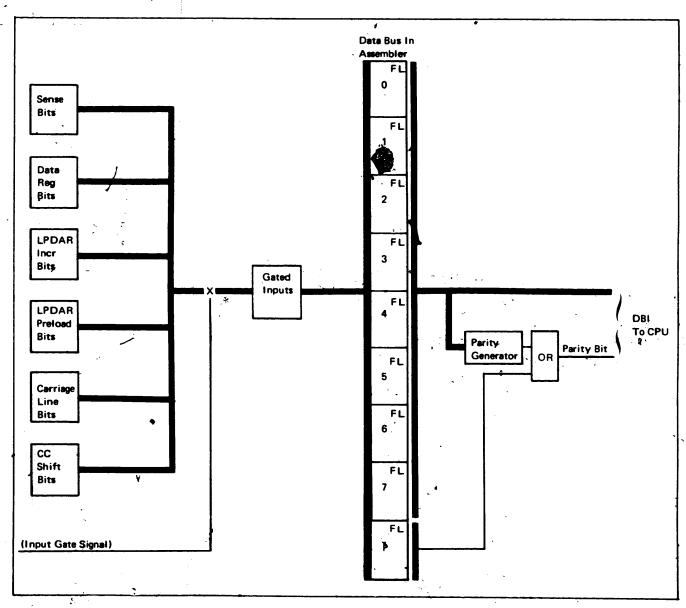

### DATA BUS IN ASSEMBLER

- The data bus in (DBI) assembler consists of eight latches. These latches are encoded to combine the data SNS bits that are sent to the CPU into separate data bytes.

- All data bytes sent to the CPU pass through the DBI assembler. For example:

- 1. Sense bits.

- 2. Data register bits.

- 3. LPDAR increment bits.

- 4. LPDAR preload bits.

- 5. Carriage line bits.

- CC shift bits. 6.

### -Circuit Objectives

See Figure 2-4. Data lines entering the DBI assembler are gated to set the appropriate flip latches. Upon activating A the charinel gate line, the channel DBI lines are made active.

Refer to FEMD 4-050 through 4-060.

Figure 2-4. Data Bus In Assembler

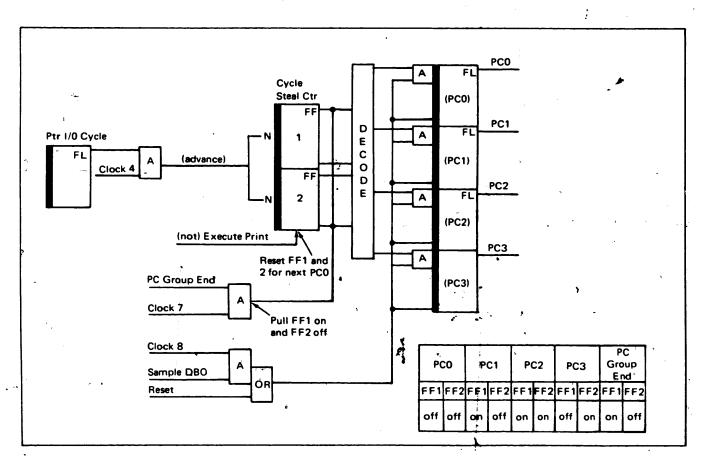

### CYCLE STEAL COUNTER

The cycle steal counter has two triggers that determine the proper print cycle steal latch (PC0 through PC3).

The print cycle steal counter ensures that the correct sequence of cycle steals is maintained. Print cycle steals occur in groups of 3, 2, or 1, depending on the attachment, detecting one of the following conditions:

- 1. Change of mechanical position.

- 2. Data found.

- 3. Data not found.

- 4. Print compare.

- 5. No print compare.

The triggers in the cycle steal counter keep track of which cycle steal is in process and which one should be next. The counter turns on the print cycle latches (PCO, PC1, PC2, and PC3). Refer to Figure 2-5.

### **Circuit Objectives**

Both cycle steal triggers are reset off by (not) 'execute print' when (because of a change in M position) the next cycle steal taken will be PCO. During clock 4 of PCO, trigger 1 is turned on to ensure that the next cycle steal taken will be PC1. The same sequence is repeated for PC2 and PC3, if requested. At the end of a PC group, 'PC group end' is brought up at clock 7 to turn trigger 1 on and turn trigger 2 off. This starts the next group of cycle steals, starting with PC1. This sequence is repeated until the next change in mechanical position.

Refer to FEMD 4-070.

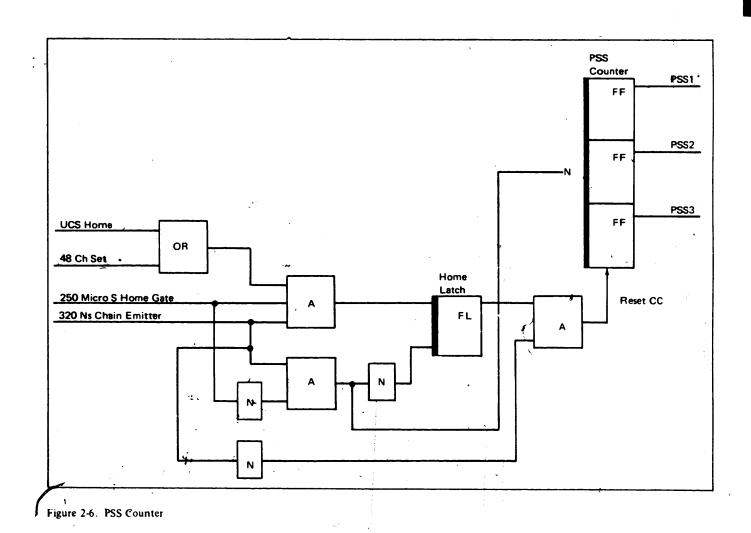

### PRINT SUBSCAN COUNTER

- The print subscan counter is a three-position trigger ring that identifies the print subscan in process.

- A chain emitter pulse from the printer advances the print subscan counter.

Ligure 2-5. Cycle Steal Controls

The print operation is divided into four increment print scans (one in each of the four mechanical print positions). Each increment print scan has 50 print scans. Each print scan is further divided into three subscans. The print subscan trigger ring (Figure 2-6) identifies the subscan in process. Each ring position corresponds to one of the three subscans of a print scan. At the start of any subscan, the trigger ring identifies which of the first three print positions has a type array character aligned with it. When the attachment receives a print subscan (PSS) emitter pulse from the printer, the subscan ring advances. The PSS pulses are generated from a magnetic emitter in conjunction with a drum with 144 equally-spaced slots around its circumference. A pulse is generated by each slot to identify the

start of each subscan within the print line. An additional slot (145th) is located halfway between the 144th slot and the first slot. The 145th slot (home pulse) identifies the next emitter pulse as representing the first character on the chain. The first emitter pulse after the home pulse indicates that a character is aligned with print position one.

### Circuit Objectives

Refer to FEMD 4-080. The PSS counter ring is advanced by '320 Ns Chain emitter' and (not) '300 micro S home gate'. The PSS counter ring is reset by 'reset CC'.

**BI7**

### MECHANICAL POSITION COUNTER

- The mechanical position counter (M counter) has six triggers.

- The triggers are advanced by the 'print start' singleshot at the completion of each mechanical print position change in the printer.

- M counter output is decoded to determine the mechanical position (M position) of the incrementer cam.