IBM System/32 **Functions Reference Manual**

IBM System/32

Functions

Reference Manual

### **Preface**

This reference manual is intended for persons interested in the operation and characteristics of the IBM System/32 at the machine code level. Readers should be familiar with data processing techniques and understand stored program control at the machine code level.

Similar reference manuals present mnemonics for all instructions; this manual does not include mnemonics because there is no assembler language for System/32.

Readers familiar with IBM System/3 programming may notice a similarity between many System/32 and System/3 instructions. Some instructions are identical; however, there are distinct differences in some areas. For example: in System/3, all I/O operations are initiated by issuing start I/O instructions; in System/32, some I/O instructions use the familiar hex F3 operation code and other I/O operations are initiated by branching to a location in main storage.

### Related Publications

- IBM System/32 System Control Programming Reference Manual, GC21-7593

- IBM System/32 Operator's Guide, GC21-7591

- General Information: Binary Synchronous Communications, GA27-3004

Titles and abstracts of other related publications are listed in the *IBM System/32 Bibliography*, GC20-0032.

# Second Edition (May 1975)

This is a major revision of and replaces GA21-9176-0. A chapter has been added to describe the binary synchronous communications adapter (BSCA) functions on System/32, and numerous miscellaneous changes have been made throughout the manual. Additions and changes are denoted by a vertical line at the left of the addition or change.

Changes to the information herein are made periodically; before using this publication in connection with the operation of an IBM System/32, consult the latest IBM System/32 Bibliography, GC20-0032, for the editions that are applicable and current

Request for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form is missing, comments may be addressed to IBM Corporation, Publications, Department 245, Rochester, Minnesota 55901.

© Copyright International Business Machines Corporation 1975

# Contents

| ABBREVIATIONS AND ACRONYMNS       | vii         Move Inverse (Not Used in U.S.A.)                 |

|-----------------------------------|---------------------------------------------------------------|

| CHAPTER 1. INTRODUCTION           | I-1 Insert and Test Characters                                |

|                                   | 1-2 Move Logical Immediate                                    |

|                                   | 1-2 Set Bits On Masked                                        |

|                                   | 1-2 Set Bits Off Masked                                       |

|                                   |                                                               |

|                                   |                                                               |

|                                   |                                                               |

|                                   |                                                               |

|                                   |                                                               |

|                                   |                                                               |

|                                   |                                                               |

|                                   | Compare Logical Characters                                    |

|                                   | Compare Logical minieulate                                    |

| Pinary Formet / Lorisol Detail    | 1-3 Test Bits On Masked                                       |

|                                   | -3 Test Bits Off Masked                                       |

|                                   | -3 Branch On Condition                                        |

|                                   | -3 Jump On Condition                                          |

|                                   | INPUT/OUTPUT HANDLING INSTRUCTIONS 3-38                       |

|                                   | Load Print Belt Image Register                                |

|                                   | -5 Load Character Set Size Register                           |

|                                   | Load Printer Data Address Register                            |

|                                   | Load Forms Length and Current Line Number 3-39                |

|                                   | -5 Start Printer IOB                                          |

| Two-Address Instructions          | -6 Sense Forms Length and Current Line Number 3-41            |

|                                   | Sense Printer Status                                          |

| CHAPTER 2. PROCESSOR AND OPERATOR | Start Keyboard/Display Screen IOB                             |

|                                   | 2-1 Disable Keyboard                                          |

|                                   | 2-1 Disable Keyboard, Start IOB, and Call Operator 3-43       |

|                                   | Load Keyboard/Display Screen IOB Address 3-43                 |

|                                   | Load Keyboard/Display Screen Interrupt Handler                |

|                                   | <sup>2-1</sup> Address                                        |

|                                   | <sup>2-1</sup> Sense Address/Data Switches                    |

|                                   | 2-1 Load Diskette Control Field Address Register 3-45         |

|                                   | <sup>2-1</sup> Load Diskette Data Field Address Register 3-45 |

|                                   | -1 Seek Diskette Track or Recalibrate Diskette 3-46           |

|                                   | P-1 Read Diskette Data and Control Record                     |

|                                   | <sup>2-2</sup> Write and Verify Diskette Data                 |

|                                   | Write and Verify Diskette Control Address Marker 3-49         |

|                                   | Read Diskette ID                                              |

|                                   | -2 Read Diskette Data                                         |

|                                   | -2 Write and Verify Diskette Record ID                        |

|                                   | Test Diskette Drive and Branch                                |

|                                   | -2 Sense Diskette Status                                      |

| System Controls                   | -2 Sense Diskette Control Field Address Register 3-54         |

| Operator's Console                | -3 Sense Diskette Data Address Register                       |

| CE Panel                          | -4 Reset Interrupt                                            |

|                                   | Wait for IOB                                                  |

|                                   | Disable BSCA, Keyboard, and Inquiry Interrupts 3-57           |

| ARITHMETIC INSTRUCTIONS           | -2 Start Disk IOB                                             |

| Zero and Add Zoned                | -2   Enable BSCA, Keyboard, and Inquiry Interrupts 3-59       |

| Add Zoned Decimal                 | -4 Initialize Diskette Drive                                  |

| Subtract Zoned Decimal            | -6 Queue/Dequeue Printer IOB                                  |

| Add Logical Characters            | -8 Queue/Dequeue Keyboard/Display Screen IOB 3-62             |

| Subtract Logical Characters       |                                                               |

| Add to Register                   | 001110120011                                                  |

| DATA HANDLING INSTRUCTIONS        | Start BSCA Receive Only                                       |

| Move Hexadecimal Character        | 0.0000000000000000000000000000000000000                       |

| Move Characters                   |                                                               |

|                                   | 1 =200 2001 Citt Domittion Tuble Register 3-00                |

| - 1 | Load BSCA Current Address Register         |   | 3-66           | CHAPTER 7. KEYBOARD/DISPLAY SCREEN                     |       |

|-----|--------------------------------------------|---|----------------|--------------------------------------------------------|-------|

|     | Load BSCA Interrupt Address Register       |   | 3-67           | FUNCTIONS                                              |       |

|     | Load BSCA Stop Address Register            |   | 3-67           | Alphameric and Special Character Keys                  |       |

| ı   | Load BSCA Transition Address Register      |   |                | Ten-Key Numeric Keyboard                               |       |

|     | Sense BSCA Current Address                 |   | 3-68           | Function Keys                                          |       |

|     | Sense BSCA Status                          |   | 3-69           | Command Keys                                           |       |

|     | Initialize BSCA for EBCDIC Mode            |   |                | Physical Characteristics                               | 7-1   |

|     | Initialize BSCA for ASCII Mode             |   | 3-71           | Operational Characteristics — Keyboard Key             |       |

|     | Queue/Dequeue BSCA IOB                     |   |                | Functions                                              | 7-2   |

|     | Advance Program Level                      |   |                | Character Display Format                               |       |

|     | Enable Start Light                         |   |                | Display Screen                                         |       |

|     | Disable Start Light                        |   | 3-74           | IOB Definition and Usage                               | 7-3   |

|     | Disable State Light 1                      |   |                | Keyboard Operation                                     | 7-6   |

|     | CHAPTER 4. PROGRAMMING CONSIDERATIONS      |   | 4-1            | Modes                                                  | 7-6   |

|     |                                            |   |                | Programming Considerations for Keyboard                |       |

|     | Instruction Timings                        |   |                | Keyboard Hardware Characteristics                      | 7-6   |

|     | Conditioning the Program Status Register   |   |                | Keystroke Encoding                                     | 7-6   |

|     | OUADTED E DOINTED EUNCTIONS                |   | 5-1            | Data Handling and Interrupts                           | 7-7   |

|     | CHAPTER 5. PRINTER FUNCTIONS               |   | _              | Manual Operating Procedures                            |       |

|     | Printer Character Sets                     |   |                | Displaying Data Stored in Registers and Main Storage . | 7-7   |

|     | Operational Characteristics                |   |                | Altering Contents of Main Storage                      |       |

|     | Print Data Area                            |   |                | Altering Contents of Instruction Registers             | 7-8   |

|     | Line Printer Character-Set Image and Size  |   |                | Error Recovery Procedures                              | 7-8   |

|     | Forms Control, Continuous-Forms Mode       |   |                |                                                        |       |

|     | Forms Control, Single Form/Ledger Cards    |   | _              | CHAPTER 8. DISKETTE DRIVE FUNCTIONS                    | 8-1   |

|     | End-of-Operation Interrupts, Printer       |   |                | Physical Characteristics                               |       |

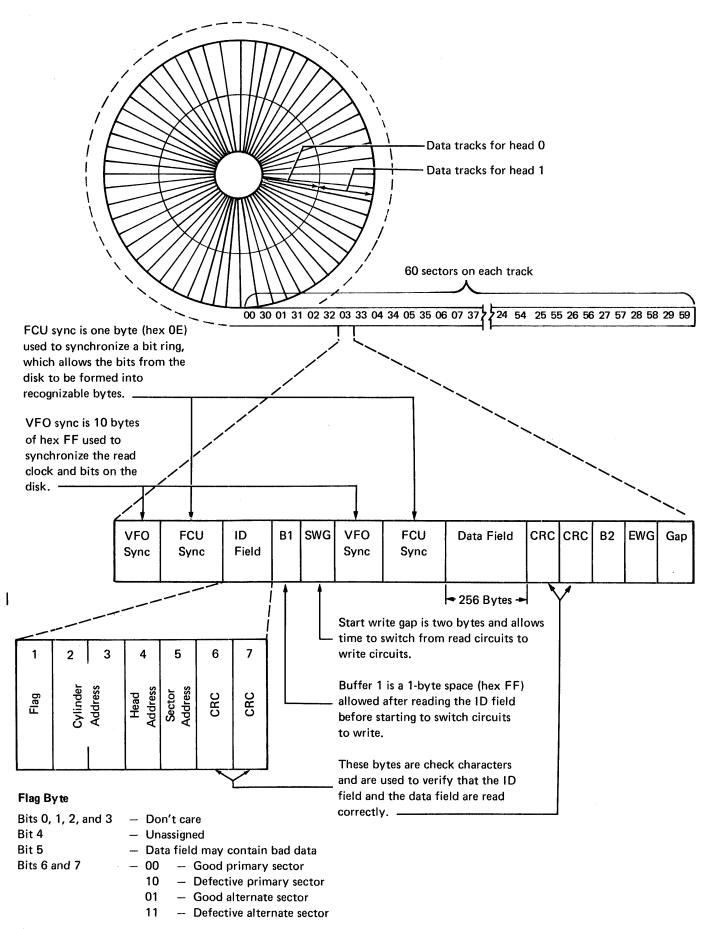

|     | Print Buffer                               |   |                | Record Format                                          | _     |

|     | Printer Function Keys                      |   |                | Diskette Drive Operating Characteristics               |       |

|     | Printer Status Bytes                       |   |                | Diskette Control Fields and Data Fields                |       |

|     | Printer IOB and NCPODSW                    | • | . 5-8          | Control Address Register                               |       |

|     |                                            |   |                | Data Address Register                                  |       |

|     | CHAPTER 6. DISK STORAGE DRIVE FUNCTIONS    |   |                | Diskette Operations                                    |       |

|     | Physical Characteristics                   |   |                | Diskette Seek                                          |       |

|     | File Organization                          | • | . 6-1          | Read Data                                              |       |

|     | Operational Characteristics                |   | . 6-3          | Read Data and Control Record                           |       |

|     | Initiating a Disk Operation                |   | . 6-3          | Read ID (Identifier)                                   |       |

|     | Disk Addressing, Relative Sector Addresses |   | . 6-3          | Write/Verify Data                                      |       |

|     | Disk Addressing, Actual Sector Addresses   |   | . 6-3          | Write/Verify Control Address Mark                      |       |

|     | Disk Operations                            |   | . 6-10         | Write/Verify ID (Identifier)                           |       |

|     | Control Seek                               |   | . 6-10         | Check Condition and Status Information                 |       |

|     | Control Recalibrate                        |   | . <b>6</b> -10 |                                                        | 0.0   |

|     | Read Data                                  |   | . 6-10         | IMPL (Initial Microprogram Load) and IPL (Initial      | 0 10  |

|     | Read ID (Identifier)                       |   |                | Program Load)                                          | 0 10  |

|     | Read Data Diagnostic                       |   |                | Suggested Diskette Error Recovery Procedures           |       |

|     | Read Verify                                |   | . 6-11         | Initialization Procedures                              |       |

|     | Write Data                                 |   | . 6-11         | Surface Defect Procedures                              | 8-14  |

|     | Write ID (Identifier)                      | - | . 6-11         |                                                        |       |

|     | Scan Equal                                 |   |                | CHAPTER 9. TELECOMMUNICATIONS FUNCTIONS .              | . 9-1 |

|     | Scan Low or Equal                          |   |                | Point-to-Point Communications Networks                 | , 9-1 |

|     | Scan High or Equal                         |   |                | Multipoint Communications Networks                     | . 9-1 |

|     | Disk Check Conditions and Status           |   |                | Data Rates ,                                           | . 9-1 |

|     |                                            |   |                | Modems                                                 | . 9-1 |

|     | Disk Operating Procedures                  |   |                | Transmission Rate Control                              | . 9-1 |

|     | Disk Program Load Procedure                |   |                | Transmission Codes                                     |       |

|     | Alternate Sector Assignment Procedure      |   |                | Standard BSCA Capabilities                             |       |

|     | Alternate Sector Processing                |   |                | Special Features                                       |       |

|     | Sector Initialization Procedure            |   |                | EIA Interface                                          |       |

|     | Error Recovery Procedure                   |   |                | Internal Clock                                         |       |

|     | Error Recovery by IBM IOS                  | • | . 6-18         | IBM 1200 BPS Integrated Modem                          |       |

|     |                                            |   |                | IBM 2400 BPS Integrated Modem                          |       |

|     |                                            |   |                |                                                        |       |

| Switched Network Bac                                        | kuı  | 0    |      |       |      |     |    |   |   |   | 9-3  |

|-------------------------------------------------------------|------|------|------|-------|------|-----|----|---|---|---|------|

| Switched Network Bac                                        | kui  | o w  | ith  | Aut   | oar  | swi | er | _ |   |   | 9-3  |

| Control Storage Registers                                   |      |      |      |       |      |     |    |   |   | • | •    |

| Adapter                                                     |      |      |      |       |      |     |    |   |   |   | 9-3  |

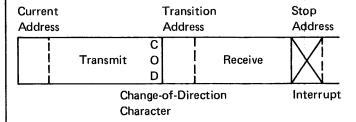

| Current Address Regist                                      | or   | •    | •    | •     |      |     |    |   |   | • | 9-3  |

| Transition Address Reg                                      |      | •    | •    | •     | ٠    |     |    | • |   | • |      |

| Chan Address Reg                                            | HSU  | er   |      |       |      |     |    |   |   | • | 9-4  |

| Stop Address Register                                       | •    |      | ٠    | •     | •    |     |    | • |   |   | 9-4  |

| Unit Definition Table F                                     | ₹eg  | iste | r    | ٠     | •    | •   | •  | • | • | • | 9-4  |

| BSCA Terminal Control Control Characters and Pad Characters | •    | •    | •    | •     | •    | •   | •  | • | • | • | 9-4  |

| Control Characters and                                      | Se   | que  | nce  | es    | •    | •   | •  | ٠ | ٠ | • | 9-4  |

|                                                             | •    | •    | •    | •     | •    | •   | •  | • | • | • | 9-6  |

| BSCA Synchronization                                        |      | •    | •    |       |      |     |    |   |   |   | 9-6  |

| Framing the Message .                                       |      |      |      |       |      |     |    |   |   |   | 9-7  |

| Op-End Interrupt                                            |      |      |      |       |      |     |    |   |   |   | 9-7  |

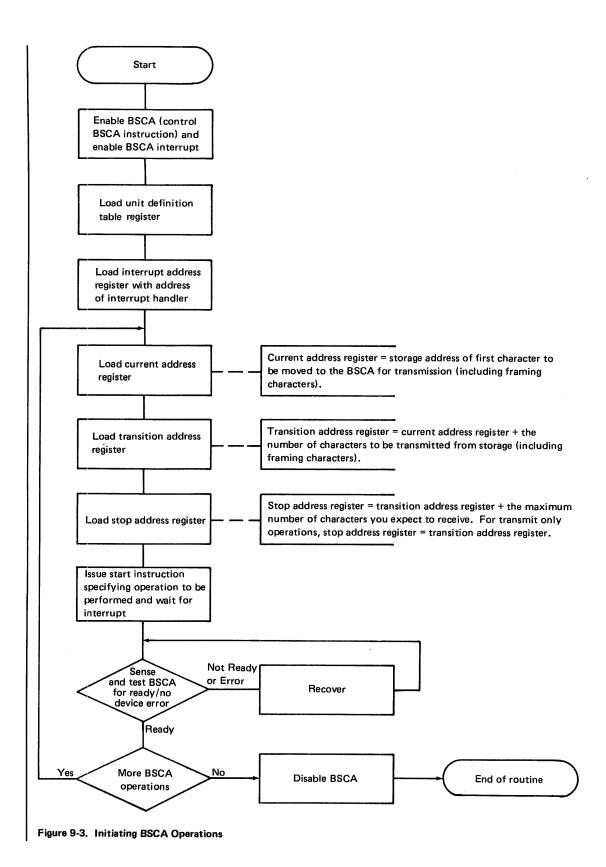

| BSCA Operations                                             |      |      |      |       |      |     |    |   |   |   | 9-7  |

| Enable/Disable BSCA                                         |      |      |      |       |      |     |    |   |   |   | 9-7  |

| Initialization Sequences                                    | S    |      |      |       |      |     |    |   |   |   | 9-7  |

| Transmit and Receive C                                      | ) pe | rati | on   |       |      |     |    |   |   |   | 9-9  |

| Disconnect Operation                                        |      |      |      |       |      |     |    |   |   |   | 9-10 |

| Receive Operation .                                         |      |      |      |       |      |     |    |   |   |   | 9-11 |

| Two-Second Timeout                                          | •    | :    | Ċ    |       |      |     |    | : |   |   | 9-11 |

| Loading the Registers                                       | •    | •    |      | •     | •    | •   | •  | ٠ | • | • | 9-11 |

| Sensing                                                     | •    | •    | •    | •     | •    | •   | •  | • | • | • |      |

| Sensing                                                     | •    | •    | •    | •     | •    | •   | •  | • | • | • | 0-11 |

| Data Checking Suggested Error Recove                        | •    | D    | •    | •<br> |      | •   | •  | • | • | • | 9-11 |

| Suggested Error Recove                                      | ry   | Pro  | cec  | ure   | S    | •   | •  | • | • | • | 9-12 |

| System and Error Statis                                     | STIC | S    | •    | •     | •    | •   | •  | • | ٠ | • | 9-14 |

| ADDENIDAY A ANOTOLIOT                                       |      |      |      |       |      |     |    |   |   |   |      |

| APPENDIX A. INSTRUCT                                        | 10   | N    | ·OF  | {IVI} | ATS  | •   | •  | • | • | • | A-1  |

|                                                             |      |      |      |       |      |     |    |   |   |   |      |

| APPENDIX B. EBCDIC CO                                       | DD   | E M  | IEA  | NI    | NGS  | 5   | •  | ٠ | • | • | B-1  |

|                                                             |      |      |      |       |      |     |    |   |   |   |      |

| APPENDIX C. POWERS O                                        | F    | rwe  | T C  | AB    | LE   | •   | •  | • | • | • | C-1  |

|                                                             |      |      |      |       |      |     |    |   |   |   |      |

| APPENDIX D. BINARY A                                        |      |      |      |       |      |     |    |   |   |   |      |

| NUMBER NOTATIONS                                            |      |      |      |       |      |     |    |   |   |   | D-1  |

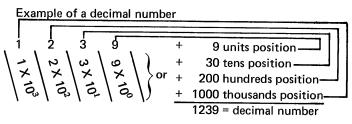

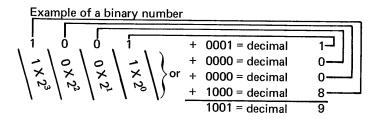

| Binary Number Notation                                      |      |      |      |       |      |     |    |   |   |   | D-1  |

| Hexadecimal Number System                                   | em   |      |      |       |      |     |    |   |   |   | D-1  |

|                                                             |      |      |      |       |      |     |    |   |   |   |      |

| <b>APPENDIX E. HEXADEC</b>                                  | IM.  | AL-  | DE   | CIN   | 1AL  |     |    |   |   |   |      |

| CONVERSION TABLES                                           |      |      |      |       |      |     |    |   |   |   | E-1  |

|                                                             |      |      |      |       |      |     |    |   |   |   |      |

| APPENDIX F. POLLING                                         | ٩N   | D A  | DE   | RE    | SSI  | NG  |    |   |   |   |      |

| CHARACTERS FOR SYS                                          |      |      |      |       |      |     |    | , |   |   |      |

| STATIONS                                                    |      |      |      |       |      | •   |    |   |   |   | F-1  |

| EBCDIC Code                                                 | :    |      |      |       |      |     |    | • | • | • | F-1  |

|                                                             |      |      |      |       |      | •   |    | • | ٠ | • | F-1  |

| ASCII Code                                                  | •    | •    | •    | •     | •    | •   | •  | • | • | • | r-1  |

| INDEX                                                       |      |      |      |       |      |     |    |   |   |   | X-1  |

| INDEX                                                       | •    | •    | •    | •     | •    | •   | •  | • | • | • | A-1  |

| INDEV OF INSTRUCTION                                        | VIC. | οv   | R.A. |       | 1181 | E ^ | ^- |   |   |   |      |

| INDEX OF INSTRUCTION SEQUENCE                               |      |      |      |       |      |     |    |   |   |   | X-9  |

| >=( )  (  =  \)    '  =                                     |      |      |      |       |      |     |    |   |   |   | v.a  |

vi

# Abbreviations and Acronymns

|   | μs     | microseconds                                   | KEYBD     | keyboard                                     |

|---|--------|------------------------------------------------|-----------|----------------------------------------------|

|   | AM     | address mark                                   | LS        | logical sector                               |

|   | ARR    | address recall register                        | LSR       | = ;                                          |

|   |        |                                                | LON       | local storage register                       |

|   | BCC    | block check character                          | MAR       | microprocessor address register (not used by |

|   | BDE    | basic data entry (keyboard operation)          |           | program)                                     |

| ı | BPS    | bits per second                                | ms        | millisecond                                  |

| l | BSCA   | binary synchronous communications adapter      |           |                                              |

|   |        |                                                | NFCCHS    | bytes in disk control field                  |

|   | CAR    | control address register                       | ns        | nanosecond                                   |

|   | CC     | cylinder number bytes                          |           |                                              |

|   | CE     | customer engineer                              | op code   | operation code                               |

|   | CHK    | check                                          | op end    | operation end                                |

|   | CHRNX  | bytes in diskette control field                | op 1      | operand 1                                    |

|   | CRC    | cyclic redundancy check                        | op 2      | operand 2                                    |

|   | CSDE   | controlled sequential data entry (keyboard     |           | - Portuna E                                  |

|   |        | operation)                                     | PCR       | processor condition register (not used by    |

|   |        | •                                              |           | program)                                     |

|   | DAR    | data address register                          | PROC      | processor                                    |

|   | DBI    | data bus in                                    | PS        | physical sector                              |

|   | DBO    | data bus out                                   | PSR       | program status register                      |

|   | Disp   | displacement                                   | PWR       | power                                        |

|   | DPLY   | display                                        |           | power                                        |

|   | DTF    | define the file                                | RDY       | ready                                        |

|   |        |                                                | RIB       | request indicator byte                       |

|   | EBCDIC | extended binary coded decimal interchange      | RPM       | rotations per minute                         |

|   |        | code                                           | 1 111 141 | rotations per minute                         |

|   | ERMAP  | error map                                      | S         | byte in disk control field                   |

|   | EWG    | end write gap                                  | SCP       | system control program                       |

|   |        | • .                                            | SD        | seek displacement, in tracks                 |

|   | FCCHS  | identifier field in logical disk address       | SDE       | sequential data entry (keyboard operation)   |

|   |        | •                                              | SDLC      | synchronous data link control                |

|   | Н      | one of the bytes in the diskette control field | SS        | relative sector address                      |

|   | hex    | hexadecimal                                    | STOR      | storage                                      |

|   |        |                                                | SWG       | start write gap                              |

|   | IAR    | instruction address register                   | sync      | <u> </u>                                     |

|   | INSN   | instruction                                    | SYS       | synchronous, synchronization, synchronize    |

|   | IMPL   | initial microprocessor program load            | 010       | system (on CE panel, SYS INSN STEP means     |

|   | IOB    | input/output block                             |           | a single instruction step from your control  |

|   | IOS    | input/output system                            |           | program)                                     |

|   | IPL    | initial program load                           | TH        | 4h awas al                                   |

|   | IRPT   | interrupt                                      | TIO       | thermal                                      |

|   | 1/0    | input/output                                   | , 110     | test input/output instruction                |

|   | 1/0    | πραγουτρατ                                     |           |                                              |

|   | K      | 1,024 bytes                                    | VTAM      | virtual telecommunications access method     |

|   |        |                                                | XR        | index register                               |

|   |        |                                                |           |                                              |

System/32

The IBM System/32 is an operator-oriented, desk-size data processing system. The system has an operator console through which the operator enters data to the system, controls the operation of the system, and communicates with the system program. Integral parts of the console are the keyboard and display screen. The primary output unit is a system printer. Programs and data files reside on a nonremovable disk. Diskettes, which are removable, serve as a load/dump medium for creating backup files from information on the disk, as a data interchange medium for exchanging data with other systems, and as a medium for offline preparation of data and programs.

The system operates under control of programs stored in main storage and under control of a microprocessor. The microprocessor serves as a control unit and assists in control of system input and output functions. The microprocessor has a dedicated storage area called control storage. The system overlaps input/output operations of most I/O devices with each other and with processor operations.

The models of System/32 differ in printing speeds and disk storage capacities. Figure 1-1 lists the available System/32 models. Though each model is listed with a main storage capacity of 16,384 bytes (16K - K = 1,024 bytes), main storage capacities of 24,576 bytes (24K) and 32,768 bytes (32K) are available for all models.

| System Model | Main Storage Capacity | Serial Printer Speed | Line Printer Speed                   | Disk Data Storage Capacity |

|--------------|-----------------------|----------------------|--------------------------------------|----------------------------|

| A12          | 16,384 bytes          | 40 chars/sec         |                                      | 5,053,440 bytes            |

| A13          | 16,384 bytes          | 40 chars/sec         |                                      | 9,169,920 bytes            |

| A22          | 16,384 bytes          | 80 chars/sec         |                                      | 5,053,440 bytes            |

| A23          | 16,384 bytes          | 80 chars/sec         |                                      | 9,169,920 bytes            |

| B12          | 16,384 bytes          | · .                  | 50 lines/min                         | 5,053,440 bytes            |

| B13          | 16,384 bytes          | <del></del>          | 50 lines/min                         | 9,169,920 bytes            |

| B22          | 16,384 bytes          | <b></b>              | 100 lines/min                        | 5,053,440 bytes            |

| B23          | 16,384 bytes          | <del></del>          | 100 lines/min                        | 9,169,920 bytes            |

| B32          | 16,384 bytes          | <del></del>          | 120 or 155<br>lines/min <sup>1</sup> | 5,053,440 bytes            |

| B33          | 16,384 bytes          | :                    | 120 or 155<br>lines/min <sup>1</sup> | 9,169,920 bytes            |

<sup>1</sup> Print speed is 120 lines per minute for 64-character print belts, 155 lines per minute for 48-character print belts.

Figure 1-1. System Models

### **ELEMENTS OF THE SYSTEM**

### **Processor and Main Storage**

Main storage holds 16,384 eight-bit data bytes. The processor, with an integrated microprocessor, provides all the arithmetic, logical, and input/output control functions for the entire system.

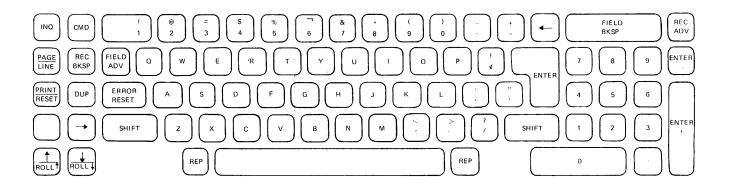

### Keyboard

The system keyboard contains a set of alphameric keys (arranged in the standard typewriter format), a set of adding machine keys (arranged in the 10-key keyboard format), and a set of function keys used by the operator to select system functions.

#### **Display Screen**

The display screen displays data and messages. Through programming, characters can be stored in main storage as they are keyed, or up to 240 characters can be held in the display screen (and altered as required) before they are sent to main storage. Under program control or operator control, main storage data and the contents of registers can be displayed and, if desired, altered by use of the keyboard.

### **Printer**

Depending on the model, the system has one of two different integrated printers:

- The serial printer uses a wire matrix to print characters serially. It operates at either 40 or 80 characters per second (maximum), depending on the model specified. The serial printer has a standard 64-character set of graphics. The standard serial printer processes both continuous forms and single form/ledger cards.

- The line printer operates at either 50, 100, or 155 lines per minute (maximum), depending on the model. It has standard character sets of 48 and 64 characters.

The line printer processes continuous forms only.

### Disk Storage

Every model has a disk drive with a nonremovable disk. Depending on the model, the disk stores either 5,053,440 or 9,169,920 bytes. Like the other units discussed, the disk drive unit is an integral part of the system.

#### **Diskette Drive**

Each model has a diskette drive unit. The system uses the IBM standard data interchange diskette (or equivalent). This allows the system to read diskettes written by IBM 3741 Data Stations and similar devices and to exchange data with other systems. Data can also be written on diskettes and stored offline for backup data and programs. Data on diskettes that will not be used on other systems need not be formatted like data on standard data interchange diskettes.

### **Additional Main Storage Capacity**

The system can be equipped with either 8, 192 or 16,384 positions of additional main storage as a special feature, bringing the total main storage capacity to either 24K or 32K bytes.

### **Telecommunications Feature**

Each model of the system can be equipped with either the binary synchronous communications adapter (BSCA) as a special feature or with the synchronous data link control (SDLC) feature. The BSCA allows communication between System/32 and a remote system or terminal at data rates of from 600 to 7200 bits per second.

SDLC allows communication between System/32 and a System/370 operating with the virtual telecommunications access method (VTAM). Data rates can be from 600 to 7200 bits per second. Detailed information about SDLC will be contained in a future revision of this publication.

### **Keylock Power Switch**

This feature is a key-operated switch that replaces the standard POWER ON/OFF switch on the operator panel. When the key is inserted and turned, power is supplied to the system. The feature helps restrict system operation to key-holders.

#### **DATA FORMATS**

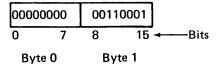

Data resides in main storage in 8-bit (plus parity) bytes. The instruction the system is executing determines how the data is interpreted. A byte holds either decimal, alphabetic, or special characters; or binary numbers (logical data).

The system uses EBCDIC (extended binary coded decimal interchange code) for storing characters in main storage and for processing data.

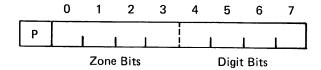

#### **Character Format**

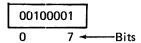

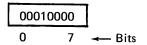

In character format, each byte of data is divided into two groups of four bits each. Bits 0-3 compose the zone portion, and bits 4-7 compose the digit portion. The character format represents a decimal digit, a special control character, or one of the characters that can be printed or displayed by the system (these characters are called *graphics*). The illustration below shows the byte as interpreted for character format.

For decimal arithmetic operations, the zone bit of the rightmost byte in the field indicates the sign of the number. (The system ignores the zone bits in all other bytes during the operation.) Zones containing hex B or D (binary 1011 or 1101) designate a negative number. Any other hex digit in the zone designates a positive number.

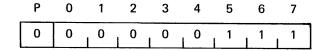

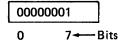

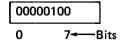

### **Binary Format (Logical Data)**

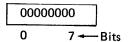

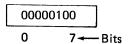

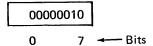

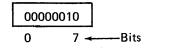

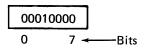

In binary format, bits in a byte define a digit, and the entire byte is an unsigned binary number (a binary integer). Binary bits are said to be on if 1, off if 0. The illustration below shows decimal 7 as a binary integer. Notice that the parity bit is set to 0 (see *Parity* in this chapter).

Unsigned Binary Integer

### **Hex Code**

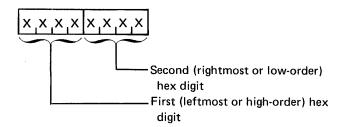

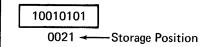

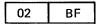

Each byte can be divided into two groups of four bits, and each of these groups can be represented as a single hex digit, as shown below:

The hex value of each combination of binary bits is:

| Binary<br>Bits | Hex<br>Digit | Binary<br>Bits | Hex<br>Digit |

|----------------|--------------|----------------|--------------|

| 0000           | 0            | 1000           | 8            |

| 0001           | 1            | 1001           | 9            |

| 0010           | 2            | 1010           | Α            |

| 0011           | 3            | 1011           | В            |

| 0100           | 4            | 1100           | С            |

| 0101           | 5            | 1101           | D            |

| 0110           | 6            | 1110           | E            |

| 0111           | 7            | 1111           | F            |

Throughout this manual, values stored in bytes are often expressed in hex notation.

#### **Parity**

Each byte contains a parity bit that is developed by the system (and checked by the system during various operations). This bit ensures that the number of bits set to 1 in each byte is an odd number. (If the binary number or data code developed by the system has an even number of bits that are 1, the system sets the parity bit to 1 to make the entire byte contain an odd number of 1-bits. If the binary number or data code has an odd number of bits, the system sets the parity bit to 0 to maintain an odd number of bits in the entire byte.)

### **ADDRESSING**

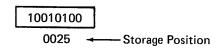

Main storage is addressed in binary, using hex notation. Its positions are consecutively numbered from hex 0000 to the upper limit of storage. The location of any field or group of bytes is specified by the address of the rightmost (low-order or highest-numbered storage position) byte in the field. The exception is the insert and test character instruction, which specifies the leftmost byte.

Chaps the offer control address craited had a sold from higher of windred from

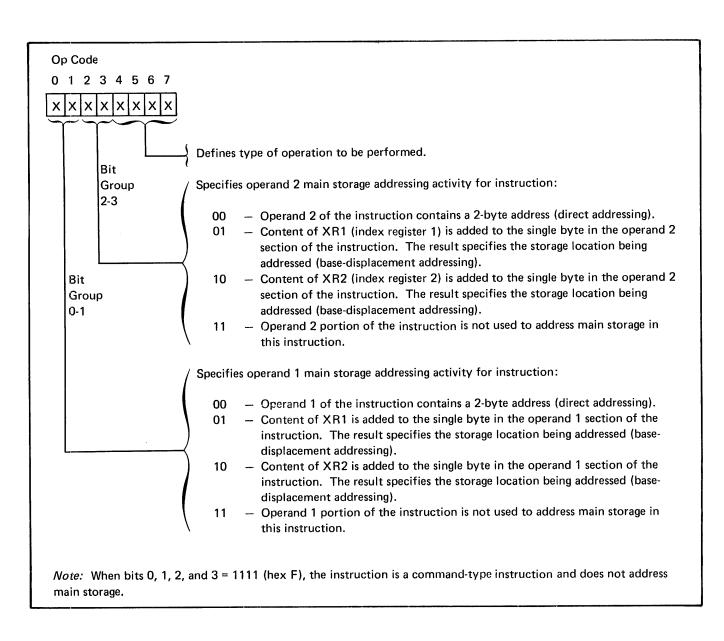

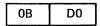

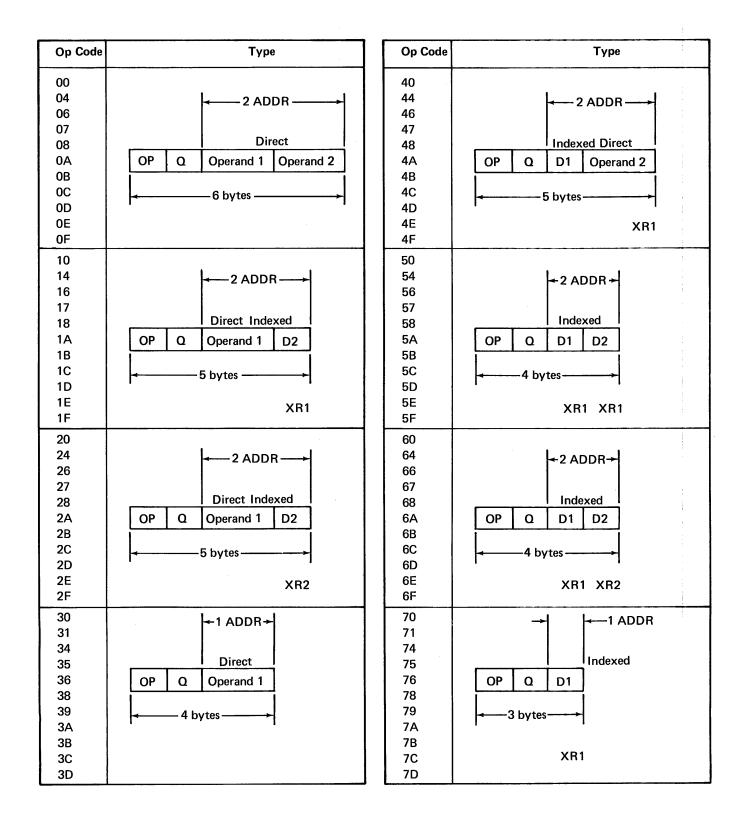

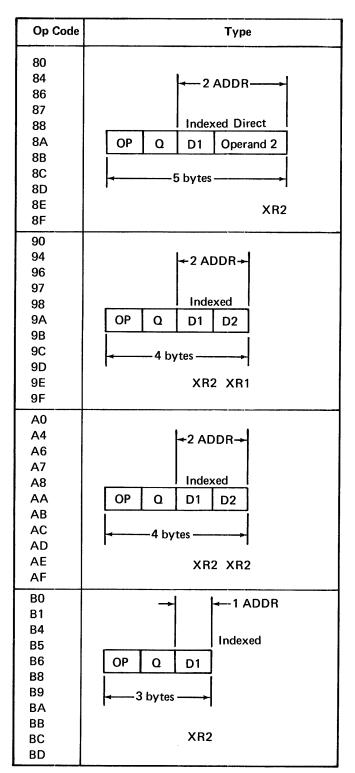

An address used to refer to main storage can be specified by either of two methods: direct addressing or base-displacement addressing. The type of addressing to be used is specified by bits 0-3 of the first byte (the operation code) of the instruction. These four bits are treated as two groups of two bits each: group 0-1 and group 2-3. Bits 0 and 1 control addressing for operand 1; bits 2 and 3 control addressing for operand 2. When bits for group 0-1 = 11, operand 1 is not used; when bits for group 2-3 = 11, operand 2 is not used. Figure 1-2 is an explanation of op code functions in addressing main storage.

Figure 1-2. Op Code Function in Addressing Main Storage

### **Direct Addressing**

When either or both of bit groups 0-1 or 2-3 = 00, the specified operand uses direct addressing.

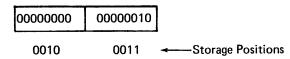

When direct addressing is used, the storage address is taken directly from the instruction. The address in the instruction is two bytes long.

### **Base-Displacement Addressing**

A specified operand uses base-displacement addressing when either or both of the bit groups have one bit = 1 and the other bit = 0.

In base-displacement addressing, the contents of the 1-byte address in the instruction are added to the contents of a 2-byte address in an index register. The index register to be used is determined by the bit of the bit group that is 1 (Figure 1-2). Both bit groups can use the same index register during the execution of an instruction.

Any one value of an index register allows access to 256 storage positions.

### **INSTRUCTION FORMATS**

Instruction formats are distinguished by their ability to address storage. The length of each instruction is determined by the type of addressing being performed.

All instruction formats have two elements in common: the op code and the Q-byte. Each of these elements is one byte. The op code determines the type of addressing (thereby the length of the instruction) and the operation to be performed. The function of the Q-byte is determined by the instruction and is discussed with each individual instruction.

### **Command-Type Instructions**

Command-type instructions are always three bytes long. In a command-type instruction, the Q-byte contains the following information, depending on the instruction:

Device address and function specification Jump condition The command instruction is distinguished by bits 0-3 of the op code being all 1's.

### Command Instruction

| Op Code | Q-Byte | Command |

|---------|--------|---------|

| 1111    |        |         |

| 0 3     |        |         |

| Rite    |        |         |

#### **One-Address Instructions**

One-address instructions can be either three or four bytes long. These instructions are distinguished by having either bits 0-1 or bits 2-3 of the op code byte both 1's. The two bits that are not both 1 (0 and 1, or 2 and 3) can be 01, 10, or 00. If these bits are 00, addressing is direct and the instruction is four bytes long. If the bits are 01 or 10, addressing is base-displacement; the instruction is three bytes long; and XR1 (01) or XR2 (10) is used. The Q-byte of a one-address instruction can contain:

An immediate operand A mask A branch condition A data selection

### One-Address Instruction-Base-Displacement Addressing

| 1 | Op Code      |         |                 |

|---|--------------|---------|-----------------|

|   | 1110<br>1101 | O Purto | Displace-       |

|   | 1011         | Q-Byte  | ment<br>Operand |

|   | 0111         |         |                 |

0 3 Bits

### One-Address Instruction—Direct Addressing

| Op Code<br>0011<br>1100 | Q-Byte | (High-<br>Order<br>Byte of<br>Address)<br>Operand | (Low-<br>Order<br>Byte of<br>Address)<br>Operand |

|-------------------------|--------|---------------------------------------------------|--------------------------------------------------|

|-------------------------|--------|---------------------------------------------------|--------------------------------------------------|

0 3 Bits

# **Two-Address Instructions**

Two-address instructions can be four, five, or six bytes long. This instruction type is distinctive in that *neither* bit group 0-1 *nor* bit group 2-3 of the op code byte are 1's. If all four of bits 0-3 are 0's, addressing is direct, and the instruction is six bytes long. If any *one* of bits 0-3 is 1, one of the addresses is direct; the other address is base-displacement, and the instruction is five bytes long. If one bit from each of the bit groups is 1, all addressing is base-displacement and the instruction is four bytes long.

The index register to be used in base-displacement addressing for either operand is determined by the bit in the bit group that is 1. If the bit group = 01, XR1 is used; if the bit group = 10, XR2 is used. Both addresses can use the same index register during one instruction.

Two-Address Instruction—Both Addresses Base Displacement

| Op Code<br>0101<br>0110<br>1001<br>1010 | Q-Byte | Operand 1<br>Displace-<br>ment | Operand 2<br>Displace-<br>ment |

|-----------------------------------------|--------|--------------------------------|--------------------------------|

|-----------------------------------------|--------|--------------------------------|--------------------------------|

0 3 Bits

# Two-Address Instruction—Operand 1 Address Direct

| 0010 Byte) Byte) |  | Op Code<br>0001 | Q-Byte | (High<br>Order<br>Address | (Low-<br>Order<br>Address | Operand 2<br>Displace-<br>ment |

|------------------|--|-----------------|--------|---------------------------|---------------------------|--------------------------------|

|------------------|--|-----------------|--------|---------------------------|---------------------------|--------------------------------|

0 3 Bits

# Two-Address Instruction—Operand 2 Address Direct

| Op Code | Q-Bvte | Operand 1<br>Displace- |         | Operand 2<br>(Low-<br>Order |

|---------|--------|------------------------|---------|-----------------------------|

| 0100    |        | •                      | Address | Address                     |

| 1000    |        |                        | Byte)   | Byte)                       |

0 3 Bits

# Two-Address Instruction—Both Address Direct

0 3 Bits

# Chapter 2. Processor and Operator Controls

The processor controls the flow of input into the system, performs the operations on the data, and controls the output from the system.

#### MODES OF SYSTEM OPERATION

The system operates in three modes: burst, interrupt, and process.

#### **Burst Mode**

The system operates in *burst mode* while it transfers data between main storage and the disk. In burst mode the system provides a dedicated data path and, once data transfer starts, data moves rapidly between the disk and main storage until all the specified data has been transferred.

### Interrupt Mode

At the end of most input and output operations, the microprocessor is signaled that the operation has ended and that the program should branch to a special interrupt handler routine. While the system is processing data in the interrupt routine, it is said to be operating in the *interrupt mode*.

#### **Process Mode**

The system is free to handle normal I/O control and data processing operations when it is not operating in either the burst mode or interrupt mode. At this time the system operates in *process mode*.

#### **INSTRUCTION REGISTERS**

# Instruction Address Register (IAR)

The instruction address register holds the address of the first byte of the next sequential instruction in the stored program.

# Address Recall Register (ARR) Mix the the throughout of Knowley MIX

The system places the next sequential address (that is, the address of the instruction that follows the test-and-branch or branch-on-condition instruction in the program) in the address recall register whenever the program branches. At the end of the branch routine, the program can load the contents of the address recall register into the instruction address register; this returns the program to the point at which the branch occurred.

The address recall register is also affected by load-register, add-to-register, decimal-add-and-subtract, and insert-and-test-characters instructions. (All instructions are described in Chapter 3.)

### Index Registers 1 and 2 (XR1 and XR2)

Each of these index registers holds a base address for basedisplacement addressing.

### **INTERRUPT OPERATIONS**

Certain I/O functions require special routines to handle data within a limited period of time. To provide for these special routines, the system uses interrupts. Generally, an interrupt implies that the processor must interrupt a current instruction sequence; perform an intervening instruction sequence requested by the interrupting keyboard, disk drive, printer, or BSCA; then return to the interrupted program. The interrupts for the disk drive, printer, and BSCA are handled entirely by the hardware; the program must provide interrupt handler routines for the keyboard.

An interrupt can occur for the keyboard unless the program disables the interrupt function. If the program disables an interrupt, it remains disabled until the program again enables it or until an initial program load (IPL) routine is performed.

Interrupts are discussed in *General I/O Operations* in this chapter.

### INPUT/OUTPUT BLOCKS (IOBs)

Each input and output function has certain parameters that the program must define before the operation is performed. For some functions, the parameters are loaded into registers; for others, the parameters are moved into IOBs (that is, input/output blocks, which are consecutive main storage positions into which parameters are placed in defined fields).

Whenever an IOB is used to define the operation, the program must present the address of the leftmost byte of the IOB to the system (in XR1) at the start of the operation.

If an IOB is required for a function, this manual describes that IOB in the chapter that discusses the function.

#### GENERAL I/O OPERATIONS

The following paragraphs briefly discuss how each I/O unit functions with the user program.

### Disk

The program sets up a disk IOB and branches to location 0008 (via a start-disk IOB instruction). The system performs its own queueing and dequeueing functions. The program need not issue any load, sense, or test instructions.

# Printer

The program sets up a printer IOB; loads the character set size and image (line printer only) and the printer data field address; and places the IOB on the system queue.

The program issues a start-printer IOB instruction with XR1 pointing to the IOB. (At the end of the operation, the system automatically removes the IOB from the queue.)

### Keyboard/Display Screen

The program sets up a keyboard/display screen IOB and loads the address of the IOB. For keyboard only, the program queues the keyboard IOB with XR1 pointing to the IOB address.

The program issues various instructions which enable and disable the keyboard and control the image on the display screen. The program also supplies an interrupt handler, which dequeues the IOB and disables the keyboard.

### Diskette

The program loads the diskette control code from disk. (There is no IOB interface for the diskette.) The program loads the diskette data field address and diskette control field address and issues a start-diskette instruction to perform the function. The program also does its own sensing and testing.

### **BSCA**

The program loads the BSCA control code for EBCDIC or ASCII mode and places a pseudo-IOB (three unexamined bytes — there is no true IOB interface) on the system queue with XR1 pointing to the IOB. The program also loads the current address register, transition address register, stop address register, and interrupt address register as required; loads the unit definition table; and enables and disables BSCA interrupts.

The program issues the BSCA control instruction to enable/ disable the BSCA and/or the 2-second timeout, and issues the appropriate start instruction. The program senses the BSCA status bytes and responds to the status bit settings, and also senses the current address register. When the BSCA is disabled, the program removes the BSCA IOB from the system queue.

#### SYSTEM CONTROLS

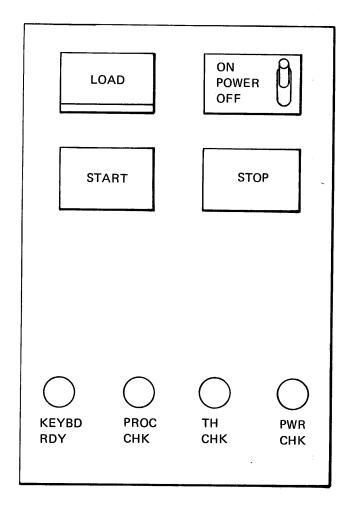

The System/32 operator controls are situated on the operator's console (Figure 2-1); the CE controls are situated on the CE panel (Figure 2-2).

The operator's console consists of the keyboard/display screen and the operator processor controls. The CE panel serves as a diagnostic aid for locating machine and program malfunctions.

Figure 2-1. Operator's Console

#### **Operator's Console**

### LOAD Key/Light

This is a combination key and light which resets the system, turns the LOAD light on, and turns on the nine event indicators on the CE panel. Releasing the key initiates the IPL routine, during which the system reads the initial program into storage from either the diskette or the disk, depending on the setting of the IPL switch on the CE panel.

During an IPL routine, the LOAD light turns off.

Note: The LOAD key is always effective, and resets the system any time it is pressed. Before performing an IPL, set the MODE SELECTOR switch (on the CE panel) to PROC RUN and the IPL switch (on the CE panel) to the appropriate setting.

# POWER ON/OFF Switch

Setting this switch to on turns on system power and resets the system. After about 10 seconds, the STOP light comes on, indicating that the initial program can be loaded. Setting the power switch to off turns off system power.

### **CAUTION**

Removing power from the system destroys data stored in main storage.

### START Key/Light

This is a combination key and light. Pressing START starts the system if it is stopped because:

- The STOP key was pressed.

- The MODE SELECTOR switch is in the SYS INSN STEP position.

- A main storage address compare stop has occurred.

The START light comes on during IPL procedures and stays on until:

- A disable-start-light instruction is issued by the program.

The START light can be turned back on by an enable-start-light instruction followed by an I/O operation.

- The STOP key is pressed. The START light can be turned on again by pressing the START key.

- A main storage address compare stop condition occurs.

The START light can be turned on again by pressing the START key.

- The MODE SELECTOR switch is in the SYS INSN STEP position. The START light can be turned on again by setting the MODE SELECTOR switch to PROC RUN and pressing the CE START key (on CE panel).

# STOP Key/Light

This is a combination key and light that stops the system at the end of the operation in progress. The STOP light comes on at this time. The STOP light also comes on at the end of each power-up sequence (when the system is ready for the IPL operation) and during instruction-step and address-step operations. Pressing the LOAD key or the START key turns the STOP light off.

### KEYBD RDY Light

This light indicates that the keyboard is enabled and is ready for operation. (The INQ, LINE, PAGE, PRINT, RESET, and ERROR RESET keys on the keyboard are always enabled.)

### PROC CHK Light

This light indicates that an unrecoverable error (one requiring operator or CE attention) has occurred. Restart from an unrecoverable error requires that the initial program be loaded again.

### TH CHK Light

If one of the system thermal sensors detects an overtemperature condition, the system turns off system power and turns on the thermal check light. The light remains on until the over-temperature condition is corrected and the POWER switch is turned off. Power can then be restored to the system by turning the POWER switch on.

### PWR CHK Light

This light indicates that the system has shut off power because there is a problem in the power circuits. If this light is on, notify the IBM customer engineer. The CE panel display indicates which power level failed.

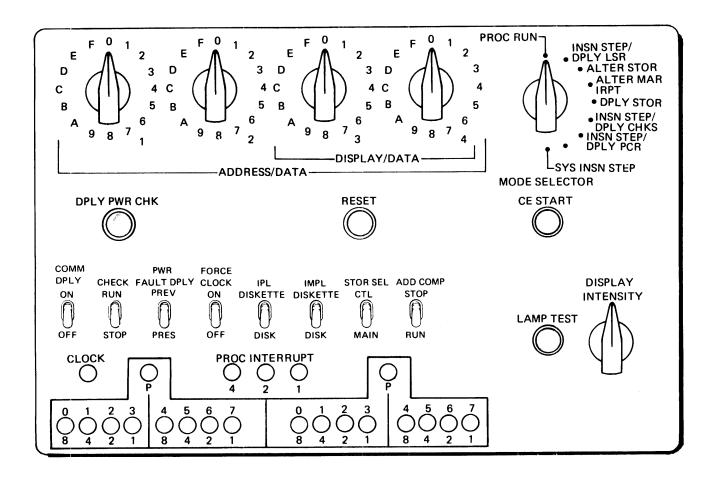

### **CE Panel**

Although this is called a CE panel, some of the switches on the panel are used by the operator and the programmer. These switches are described in this section. CE panel switches not described in this section are used only by the IBM customer engineer.

Figure 2-2. CE Panel

# ADDRESS/DATA Switches

These four 16-position rotary switches are used to enter, alter, or display data stored in main storage or local storage registers when they are used in conjunction with other switches on the CE panel. (See *Manual Operating Procedures* in Chapter 7.)

# Console Display Indicators

This group of lights displays the contents of certain system registers and presents system status information. The MODE SELECTOR switch selects the type of information to be displayed.

### **MODE SELECTOR Switch**

During regular processing operations, the MODE SELECTOR switch must be set to the PROC RUN position. All other positions are associated with diagnostic procedures, and are specified in those procedures. (See *Manual Operating Procedures* in Chapter 7.)

### Toggle Switches

Except for the COMM DPLY (communications display) switch, which can be set on when running BSCA programs, the toggle switches should all be set to the lower settings during normal processing operations.

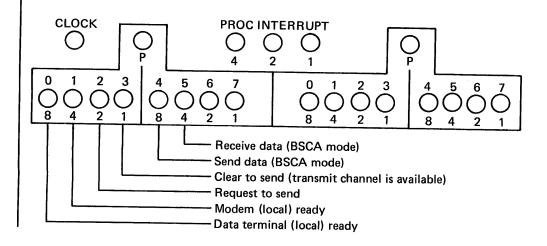

The COMM DPLY switch is on the panel if the BSCA is installed on the system. When set at the ON position, the switch activates the leftmost six lights at the bottom of the CE panel. The lights indicate the following about the BSCA when the lights are on:

# LAMP TEST Switch

Pressing the LAMP TEST switch tests all the electric bulbs on the CE panel and operator's console. If one of them does not light, notify the IBM customer engineer.

# DISPLAY INTENSITY Control

This control regulates the intensity of the image on the display screen.

Each System/32 instruction is described here in detail. The instructions are organized into four groups:

- Arithmetic

- Data handling

- Logical

- Input/output handling

### **Arithmetic Instructions**

### **ZERO AND ADD ZONED**

| Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) |            | Operand Add<br>(hex)  | resses <sup>2</sup>   |                       |        |

|------------------|------------------------------|------------|-----------------------|-----------------------|-----------------------|--------|

| Byte 1           | Byte 2                       |            | Byte 3                | Byte 4                | Byte 5                | Byte 6 |

| 04               | L1-L2                        | L2-1       | Operand 1             | address               | Operand 2 address     |        |

| 14               | L1-L2                        | L2-1       | Operand 1 address     |                       | Op 2 disp<br>from XR1 |        |

| 24               | L1-L2                        | L2-1       | Operand 1 address     |                       | Op 2 disp<br>from XR2 |        |

| 44               | L1-L2                        | L2-1       | Op 1 disp<br>from XR1 | Operand 2             | address               |        |

| 54               | L1-L2                        | <br>  L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       |        |

| 64               | L1-L2                        | L2-1       | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                       |        |

| 84               | L1-L2                        | L2-1       | Op 1 disp<br>from XR2 | Operand 2             | address               |        |

| 94               | L1-L2                        | <br>  L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |        |

| A4               | L1-L2                        | <br> L2-1  | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       | 1      |

<sup>&</sup>lt;sup>1</sup> The Q-byte designates operand length:

# Operation

This instruction moves data from the second operand, byte by byte starting with the rightmost byte, into the first operand. If the first operand is longer than the second operand, the processing unit fills the extra positions with high-order decimal zeros (hex F0).

The processing unit sets the zone bits of all bytes except the rightmost byte in the first operand to hex F (binary 1111). It sets the zone bits of the rightmost byte in the first operand to (1) hex F if the value transferred is either zero or positive, or (2) hex D (binary 1101) if the value transferred is negative.

#### **Program Note**

The second operand remains unchanged unless the fields overlap.

# **CAUTION**

Overlapping the operands with the rightmost byte of the first operand to the left of the rightmost byte of the second destroys part of the second operand before it is used in the operation.

L1-L2 (4 bits) = the number of bytes in operand 1 minus the number of bytes in operand 2.

L2-1 (4 bits) = the number of bytes in operand 2 minus 1.

Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes.

<sup>&</sup>lt;sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

# **Resulting Program Status Byte Settings**

| Bit | Name             | Condition Indicated |

|-----|------------------|---------------------|

| 7   | Equal            | Zero result         |

| 6   | Low              | Negative result     |

| 5   | High             | Positive result     |

| 4   | Decimal overflow | Bit not affected    |

| 3   | Test false       | Bit not affected    |

| 2   | Binary overflow  | Bit not affected    |

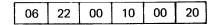

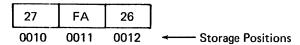

# Example

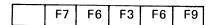

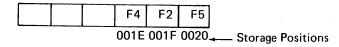

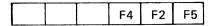

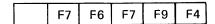

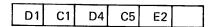

Instruction

| l | 04 | 22 | 00 | 10 | 00 | 20 |

|---|----|----|----|----|----|----|

|   |    |    |    |    |    |    |

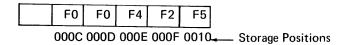

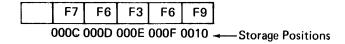

Operand 1 Before Operation

000C 000D 000E 000F 0010 --- Storage Positions

Operand 2 Before and After Operation

Operand 1 After Operation

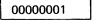

Program Status Register Before Operation

Program Status Register After Operation

| Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) | l           | Operand Add           | resses <sup>2</sup>   |                       |         |

|------------------|------------------------------|-------------|-----------------------|-----------------------|-----------------------|---------|

| Byte 1           | Byte 2                       |             | Byte 3                | Byte 4                | Byte 5                | Byte 6  |

| 06               | L1-L2                        | L2-1        | Operand 1             | address               | Operand 2             | address |

| 16               | L1-L2                        | L2-1        | Operand 1 address     |                       | Op 2 disp<br>from XR1 |         |

| 26               | L1-L2                        | L2-1        | Operand 1 address     |                       | Op 2 disp<br>from XR2 |         |

| 46               | L1-L2                        | <br>  L2-1  | Op 1 disp<br>from XR1 | Operand 2             | address               |         |

| 56               | L1-L2                        | <br>  L2-1  | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       |         |

| 66               | L1-L2                        | L2-1        | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                       | _       |

| 86               | L1-L2                        | L2-1        | Op 1 disp             | Operand 2             | address               |         |

| 96               | L1-L2                        | I<br>  L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |         |

| A6               | L1-L2                        | L2-1        | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       |         |

<sup>&</sup>lt;sup>1</sup> The Q-byte designates the operand length:

# Operation

This instruction algebraically adds the second operand to the first operand and stores the result in the first operand.

The processing unit sets the zone bits of all bytes except the rightmost byte in the first operand to hex F (binary 1111). It sets the zone bits of the rightmost byte in the first operand to (1) hex F if the result of the operation is either positive or zero, or (2) hex D if the result is negative.

# **Program Notes**

The second operand remains unchanged unless the fields overlap.

### CAUTION

Overlapping the operands with the rightmost byte of the first operand to the left of the rightmost byte of the second operand destroys part of the second operand before it is used in the operation.

- The system does not check for valid decimal digits in either operand.

- The decimal overflow condition indicator, which may be set during this operation, is reset by:

- A system reset

- Testing decimal overflow with a branch-oncondition or jump-on-condition instruction

- Loading a 0 in bit 4 of the program status register using the load-register instruction

- The system saves the starting address of operand 1 in the address recall register.

L1-L2 (4 bits) = the number of bytes in operand 1 minus the number of bytes in operand 2.

L2-1 (4 bits) = the number of bytes in operand 2 minus 1.

Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes.

<sup>&</sup>lt;sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

# **Resulting Program Status Byte Settings**

| Bit | Name             | Condition Indicated                                    |

|-----|------------------|--------------------------------------------------------|

| 7   | Equal            | Zero result                                            |

| 6   | Low              | Negative result                                        |

| 5   | High             | Positive result                                        |

| 4   | Decimal overflow | Carry occurred from the leftmost position of operand 1 |

| 3   | Test false       | Bit not affected                                       |

| 2   | Binary overflow  | Bit not affected                                       |

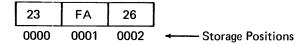

### Example

Instruction

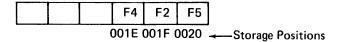

Operand 1 Before Operation

000C 000D 000E 000F 0010 ← Storage Positions

Operand 2 Before and After Operation

001E 001F 0020 ← Storage Positions

Operand 1 After Operation

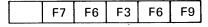

Program Status Register Before Operation

0 7 <del>← Bits</del>

Program Status Register After Operation

0 7 <del>← Bits</del>

| Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) |      | Operand Addresses <sup>2</sup> (hex) |                       |                       |         |

|------------------|------------------------------|------|--------------------------------------|-----------------------|-----------------------|---------|

| Byte 1           | Byte 2                       |      | Byte 3                               | Byte 4                | Byte 5                | Byte 6  |

| 07               | L1-L2                        | L2-1 | Operand 1                            | address               | Operand 2             | address |

| 17               | L1-L2                        | L2-1 | Operand 1                            | Operand 1 address     |                       |         |

| 27               | L1-L2                        | L2-1 | Operand 1 address                    |                       | Op 2 disp<br>from XR2 |         |

| 47               | L1-L2                        | L2-1 | Op 1 disp<br>from XR1                | Operand 2             | address               |         |

| 57               | L1-L2                        | L2-1 | Op 1 disp<br>from XR1                | Op 2 disp<br>from XR1 |                       |         |

| 67               | L1-L2                        | L2-1 | Op 1 disp<br>from XR1                | Op 2 disp<br>from XR2 |                       |         |

| 87               | L1-L2                        | L2-1 | Op 1 disp<br>from XR2                | Operand 2             | address               |         |

| 97               | L1-L2                        | L2-1 | Op 1 disp<br>from XR2                | Op 2 disp<br>from XR1 |                       | ·<br>:  |

| A7               | L1-L2                        | L2-1 | Op 1 disp<br>from XR2                | Op 2 disp<br>from XR2 |                       |         |

<sup>&</sup>lt;sup>1</sup> The Q-byte designates the operand length:

# Operation

This instruction algebraically subtracts operand 2 from operand 1, byte by byte, and stores the result in operand 1. The processing unit sets the zone bits of all operand 1 bytes except the rightmost byte to hex F (binary 1111). It sets the zone bits of the rightmost byte in operand 1 to (1) hex F if the result of the operation is either positive or 0, or (2) hex D (binary 1101) if the result is negative.

### **Program Notes**

The second operand remains unchanged unless the fields overlap.

# **CAUTION**

Overlapping the operands with the rightmost byte of the first operand to the left of the rightmost byte of the second operand destroys part of the second operand before it is used in the operation.

- The system does not check for valid decimal digits in either operand.

- The decimal-overflow-condition indication, which may be set during this operation, can be reset by:

- A system reset

- Testing decimal overflow with a branch-on-condition or jump-on-condition instruction

- Loading a 0 in bit 4 of the program status register using the load-register instruction

- The system saves the starting address of operand 1 in the address recall register.

L1-L2 (4 bits) = the number of bytes in operand 1 minus the number of bytes in operand 2.

L2-1 (4 bits) = the number of bytes in operand 2 minus 1.

Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes.

<sup>&</sup>lt;sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

# **Resulting Program Status Byte Settings**

| Bit | Name             | Condition Indicated                                         |

|-----|------------------|-------------------------------------------------------------|

| 7   | Equal            | Zero result                                                 |

| 6   | Low              | Negative result                                             |

| 5   | High             | Positive result                                             |

| 4   | Decimal overflow | Carry occurred from the left-<br>most position of operand 1 |

| 3   | Test false       | Bit not affected                                            |

| 2   | Binary overflow  | Bit not affected                                            |

# Example

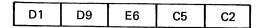

Instruction

| 07 22 00 10 00 2 | 0 |

|------------------|---|

|------------------|---|

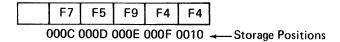

**Operand 1 Before Operation**

Operand 2 Before and After Operation

**Operand 1 After Operation**

**Program Status Register Before Operation**

Program Status Register After Operation

### **ADD LOGICAL CHARACTERS**

| Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) | Operand Add           | lresses <sup>2</sup>  |                       |           |

|------------------|------------------------------|-----------------------|-----------------------|-----------------------|-----------|

| Byte 1           | Byte 2                       | Byte 3                | Byte 4                | Byte 5                | Byte 6    |

| 0E               | L-1                          | Operand 1             | address               | Operand 2             | 2 address |

| 1E               | L-1                          | Operand 1             | Operand 1 address     |                       |           |

| 2E               | L-1                          | Operand 1             | address               | Op 2 disp<br>from XR2 |           |

| 4E               | L-1                          | Op 1 disp<br>from XR1 | Operand 2             | 2 address             |           |

| 5E               | L-1                          | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       |           |

| 6E               | L-1                          | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                       | _         |

| 8E               | L-1                          | Op 1 disp             | Operand 2             | 2 address             |           |

| 9E               | L-1                          | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |           |

| AE               | L-1                          | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       |           |

<sup>&</sup>lt;sup>1</sup> The Q-byte designates the operand length:

### Operation

This instruction adds the binary number in operand 2 to the binary number in operand 1 and stores the result in operand 1.

### **Program Notes**

### CAUTION

Overlapping the operands with the rightmost byte of the first operand to the left of the rightmost byte of the second operand destroys part of the second operand before it is used in the operation.

The system resets the binary-overflow bit during this operation.

### **Resulting Program Status Byte Settings**

| Bit | Name             | Condition Indicated                                             |

|-----|------------------|-----------------------------------------------------------------|

| 7   | Equal            | Zero result                                                     |

| 6   | Low              | No carry occurred from the                                      |

|     |                  | high-order byte and result not<br>zero                          |

| 5   | High             | Carry occurred from the high-<br>order byte and result not zero |

| 4   | Decimal overflow | Bit not affected                                                |

| 3   | Test false       | Bit not affected                                                |

| 2   | Binary overflow  | Carry occurred from the high-<br>order byte                     |

L-1 = the number of bytes in either operand minus 1.

Maximum length of each operand is 256 bytes; both operands must be the same length.

<sup>&</sup>lt;sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

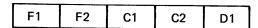

# Example

Instruction 5E 03 00 10 Note: Index register 1 = 0CC0 Operand 1 Before Operation 00110101 11001011 11101101 01100100 0CBD 0CBE 0CBF 0CC0 Storage Positions Operand 2 Before and After Operation 01011011 01010101 01111000 11001101 0CCD 0CCE OCCF , 0CD0 ← Storage Positions Operand 1After Operation 10010001 00100001 01100110 00110001 0CBD 0CBE Storage Positions 0CBF 0000 Program Status Register Before Operation 00000001 0 7 <del>←</del>Bits

Program Status Register After Operation

00000010 0 7 <del>←</del>Bits

| Op Code<br>(hex) | Q-Byte <sup>1</sup> (hex) | Operand Add           | Operand Addresses <sup>2</sup> (hex) |                       |         |  |  |

|------------------|---------------------------|-----------------------|--------------------------------------|-----------------------|---------|--|--|

| Byte 1           | Byte 2                    | Byte 3                | Byte 4                               | Byte 5                | Byte 6  |  |  |

| 0F               | L-1                       | Operand 1             | address                              | Operand 2             | address |  |  |

| 1F               | L-1                       | Operand 1             | address                              | Op 2 disp<br>from XR1 |         |  |  |

| 2F               | L-1                       | Operand 1             | Operand 1 address Op 2 disp from XR2 |                       |         |  |  |

| 4F               | L-1                       | Op 1 disp<br>from XR1 | Operand 2                            | address               | ,       |  |  |

| 5F               | L-1                       | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1                |                       |         |  |  |

| 6F               | . L-1                     | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2                |                       | _       |  |  |