# **Systems**

# System/7 Functional Characteristics

This reference manual contains basic programming information for the IBM System/7 processor and I/O devices, and describes the operating characteristics of the system. The specific topics covered are:

- Processor functional characteristics

- Priority interruptions

- Operator console

- Instruction set

- I/O commands and device status

- Interval timers

- Operator station

- Asynchronous communications control

- 1130 attachment

- Analog input and output

- Digital input and output

- 2790 control

This manual is intended as a reference for designing a System/7 configuration and programming the applications of the system. Therefore, it is assumed that the reader has a background in basic data processing concepts and programming, especially those that are pertinent to sensor-based systems and applications.

Prerequisite to this publication is *IBM System/7 System Summary*, Order No. GA34-0002. Information on customer interfaces to the I/O modules (analog, digital, and 2790 control) appears in *IBM System/7 Installation Manual-Physical Planning*, Order No. GA34-0004.

# First Edition (September 1970)

Changes are periodically made to the information herein. Before using this publication in connection with the operation of IBM systems, refer to the latest SRL Newsletter for the editions that are applicable and current.

The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter. IBM System/7 units shown herein are at development level and may be subsequently modified in appearance.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form for readers' comments is provided at the back of this publication. If the form has been removed, send your comments to IBM Corporation, General Systems Division, Product and Programming Publications, Department 707, Boca Raton, Florida 33432.

© Copyright International Business Machines Corporation 1970

# **Contents**

| Introduction                         |   |   |   |   | 1  | Shifting Instructions                          | 41   |

|--------------------------------------|---|---|---|---|----|------------------------------------------------|------|

| I/O Modules                          |   |   |   |   | 1  | Shift Left Logical                             | 41   |

| System/7 Configurations              |   |   |   |   | i  | Shift Left Circular                            | 42   |

| System// Configurations              | • | • | • | • | •  | Shift Right Logical                            | 43   |

| IBM 5010 Processor Module            |   |   |   |   | 3  | Shift Right Arithmetic                         | 44   |

|                                      |   |   |   |   |    | Branching Instructions                         | 45   |

| General Functional Description       |   |   |   |   | 3  | Branch                                         | 45   |

| System Data Flow                     |   |   |   |   | 3  | Branch and Link                                | 46   |

| Data Formats                         |   |   |   |   | 3  | Branch and Link Long                           | 48   |

| Numeric Data Formats for Arithmetic  |   |   |   |   |    | Branch on Condition                            | 50   |

| Operations                           |   |   |   |   | 4  | Skip on Condition                              | 52   |

| Storage Addresses                    |   |   | • |   | 6  | Add to Storage and Skip                        | 54   |

| Registers                            |   |   |   | • | 6  | No Operation                                   | 56   |

| Instruction Address Register (IAR) . |   |   |   |   | 6  | Register-to-Register Instructions              | 57   |

| Index Registers (XR1-XR7)            |   |   |   |   | 8  | Store to Register                              | 57   |

| Accumulators (ACC0-ACC3)             |   |   |   |   | 8  | Load from Register                             | 58   |

| Interruption Mask Register (IMR) .   |   |   |   |   | 9  | Interchange Register                           | 59   |

| Miscellaneous Machine Registers      |   |   |   |   | 9  | Load Processor Status                          | 59   |

| Program Indicators                   |   |   |   |   | 9  | Inspect IAR Backup                             | 60   |

| Carry Indicator                      |   |   |   |   | 9  | AND to Mask                                    | 60   |

| Overflow Indicator                   |   |   |   |   | 10 | OR to Mask                                     | 61   |

| Result-Zero Indicator                |   |   |   |   | 10 | Sense Level and Mask                           | 61   |

| Result-Even Indicator                |   |   |   |   | 10 | State Control Instruction                      | 62   |

| Result-Positive Indicator            |   |   |   |   | 10 | Level Exit                                     | 62   |

| Result-Negative Indicator            |   |   |   |   | 10 | Input/Output Instruction                       | 62   |

| Parity                               |   |   |   |   | 10 | Execute I/O                                    | 62   |

| Power Failure and Thermal Warning    |   |   |   |   | 11 | DACOULO 1/O                                    | 02   |

| Priority Interruption System         |   |   |   |   | 11 | Direct Control Channel                         | 63   |

| Priority Interruptions               |   |   |   |   | 12 |                                                | 05   |

| Interruption Levels                  |   |   |   |   | 12 | Internal Interface                             | 63   |

| Interruption Level Switching         |   |   |   |   | 12 | I/O Instruction Commands                       | 63   |

| Interruption Level Stacking          |   |   |   |   | 12 | I/O Instruction Format                         | 64   |

| Interruption Sublevel Branching      |   |   |   |   | 13 | I/O Commands                                   | 65   |

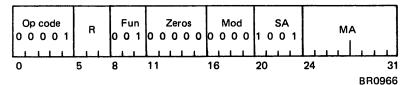

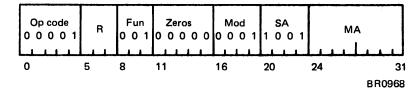

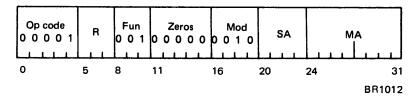

| Interruption Mask Register           |   |   |   |   | 13 | Immediate Write (Fun = 001)                    | 65   |

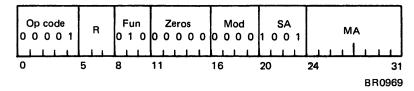

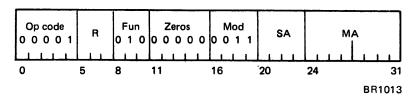

| Interval Timer Interruptions         |   |   |   |   | 14 | Immediate Read (Fun = 010)                     | 66   |

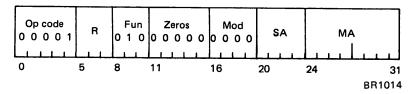

| Class Interruptions                  |   |   |   |   | 14 | Prepare I/O (Fun = 011)                        | 66   |

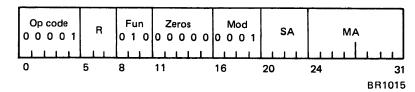

| Program Checks                       |   |   |   |   | 14 | Halt I/O (Fun = 100)                           | 67   |

| Machine Checks                       |   |   |   |   | 15 | Set Interrupt (Fun = 101)                      | 67   |

| Power/Thermal Failure                |   |   |   |   | 15 | Interruption Mechanism                         | 68   |

| Reserved Storage Locations           |   |   |   |   | 15 | Presenting an Interruption Request             | 68   |

| Reserved Storage Docations           | • | • | • | • | 15 | Set Interrupt Command Requests                 | 68   |

| Instruction Set                      |   |   |   |   | 19 | Host Attachment Interruptions                  | 69   |

|                                      |   |   |   |   |    | Device Status Word (DSW)                       | 69   |

| Instruction Classes                  |   |   |   |   | 19 | Interrupt Status Word (ISW)                    |      |

| Instruction Formats                  |   |   |   |   | 21 | Direct Control Channel Status Word             | 70   |

| Effective Address Generation         |   | • |   |   | 22 | Interval Timers                                | 71   |

| Instruction Descriptions             |   |   | • |   | 23 | I/O Commands                                   | 71   |

| Load and Store Instructions          | • | • | ٠ | • | 23 | Timer Interruptions                            | 72   |

| Load Accumulator                     | • | • |   | • | 23 | **************************************         | ′-   |

| Load and Zero                        |   |   |   | • | 24 | Operator Console                               | 73   |

| Load Immediate                       | • |   | • |   | 25 |                                                |      |

| Load Index Long                      | • |   |   | • | 26 | Tag Lights                                     | 73   |

| Store Accumulator                    |   |   |   |   | 27 | Level Lights                                   | 73   |

| Store Index                          | • | • | • | • | 28 | LS Pty (Local Store Parity) Light              | 73   |

| Arithmetic Instructions              |   |   |   |   | 29 | SDR Pty (SDR Parity) Light                     | 73   |

| Add                                  |   |   |   |   | 29 | Ctl Chk (Control Check) Light                  | 73   |

| Subtract                             |   |   |   |   | 30 | I/O Chk (I/O Check) Light                      | 73   |

| Add Register                         | • | • | ٠ | • | 31 | Seq (Sequence) Light                           | 73   |

| Subtract Register                    |   |   |   |   | 32 | Inv Op (Invalid Operation) Light               | 75   |

| Complement Register                  |   |   |   |   | 33 | Inv Adr (Invalid Address) Light                | 75   |

| Add Immediate                        |   |   |   |   | 34 | Inv Ct (Invalid Count) Light                   | . 75 |

| Logical Instructions                 |   |   |   |   | 35 | IF1 Req (Instruction Fetch Request) Light      | 75   |

| AND                                  |   |   |   |   | 35 | E1 Req and E2 Req (Execution Request) Lights . | 75   |

| OR                                   |   | • |   |   | 36 | Cry (Carry) Light                              | 75   |

| Exclusive OR                         |   |   |   |   | 37 | Ovrflw (Overflow) Light                        | 75   |

| AND Register                         |   |   |   |   | 38 | Skp (Skip) Light                               | 75   |

| OR Register                          |   |   |   |   | 39 | Stp (Stop) Light                               | 75   |

| Exclusive OR Register                |   |   |   |   | 40 | Wt (Wait) Light                                | 75   |

| Ld (Load) Light                              | 76  | Initiate Write                                |

|----------------------------------------------|-----|-----------------------------------------------|

| Tst (Test) Light                             | 76  | Sense Interrupt 95                            |

| Data Lights                                  | 76  | Sense Device                                  |

| Address Lights                               | 76  | Device Status Word (DSW) 96                   |

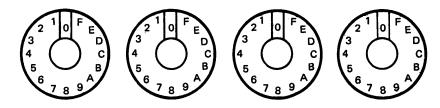

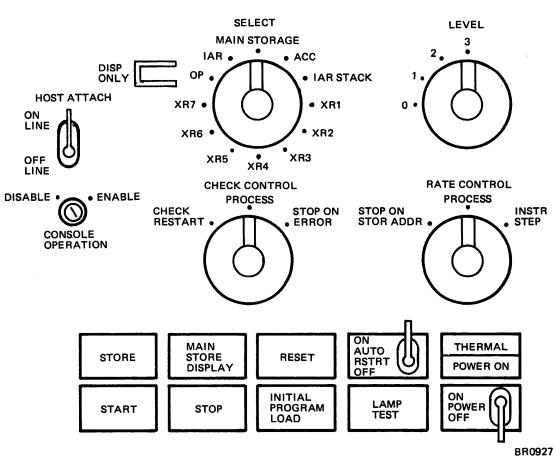

| Storage Data/Address Switches                | 76  | 1130 Attachment Interruptions 97              |

| Host Attach Switch                           | 76  | Electronic Initial Program Load (EIPL) 98     |

| Store/Display Select Switch                  | 76  |                                               |

| Store/Display Level Switch                   | 77  | IBM 5014 Analog Input Module Model B01 99     |

| Console Operation Switch                     | 77  |                                               |

| Check Control Switch                         | 77  | Status Words                                  |

| Rate Control Switch                          | 77  | Device Status Word (DSW) 100                  |

| Store Key                                    | 77  | Interrupt Status Word (ISW) 100               |

| Main Store Display Key                       | 77  | I/O Commands                                  |

| Reset Key                                    | 78  | Immediate Write Commands 101                  |

| Auto Rstrt (Automatic Restart) On/Off Switch | 78  | Immediate Read Commands                       |

| Thermal/Power On Lights                      | 78  | IDM FORA A male is brough Mandala Mandala OOA |

| Start Key                                    | 78  | IBM 5014 Analog Input Module Model C01 107    |

| Stop Key                                     | 78  | Status Words                                  |

| Initial Program Load (IPL) Key               | 78  | Device Status Word (DSW)                      |

| Lamp Test Key                                | 78  | Interrupt Status Word (ISW) 109               |

| Power On/Off Switch                          | 78  | I/O Commands                                  |

|                                              | , 0 | Immediate Write Commands                      |

| IBM 5028 Operator Station                    | 79  | Immediate Read Commands                       |

|                                              |     |                                               |

| Operator Station Adapter ISW                 | 80  |                                               |

| Initial Program Load (IPL)                   | 80  | IBM 5012 Multifunction Module Model A01 115   |

| I/O Commands                                 | 80  | Device Status Word (DSW),                     |

| Turn On Motor                                | 81  | Common I/O Commands                           |

| Turn Off Motor and Lock Keyboard             | 81  | Read DSW                                      |

| Print Only                                   | 81  | Read ID                                       |

| Punch Only                                   | 82  | Read ID Extension                             |

| Print and Punch                              | 82  | Subaddresses                                  |

| Feed Tape and Print                          | 82  | Analog Input Control Model B01                |

| Feed Tape and No Print                       | 83  |                                               |

| Keyboard Entry and Print                     | 83  |                                               |

| Keyboard Entry and No Print                  | 84  |                                               |

| Read Character With Tape Feed                | 84  | Immediate Write Commands                      |

| Read Character Without Tape Feed             | 85  |                                               |

| Read ISW                                     | 85  | Analog Input Control Model C01                |

|                                              |     | Interrupt Status Word (ISW)                   |

| Asynchronous Communications Control          | 87  | I/O Commands                                  |

|                                              | 87  | Immediate Write Commands                      |

| Line Control Characters                      | •   |                                               |

| IBM Communication Line Adapters              | 88  | Digital Input Control                         |

| Interrupt Status Word (ISW)                  | 89  | Process Interrupt Feature                     |

| I/O Commands                                 | 90  | I/O Commands                                  |

| Transmit Control                             | 90  | Digital Output Control                        |

| Transmit Character                           | 90  | I/O Commands                                  |

| Read Character                               | 90  | Analog Output Control                         |

| Reset ACC Attachment                         | 91  | I/O Commands                                  |

| Read ISW                                     | 91  | 2790 Control                                  |

| Read LRC                                     | 91  | Data Transmission                             |

|                                              |     | Interrupt Status Word (ISW) 139               |

| 1130 Attachment                              | 93  | I/O Commands                                  |

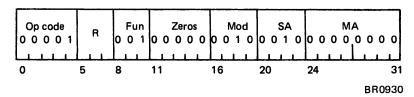

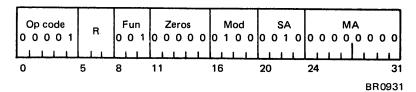

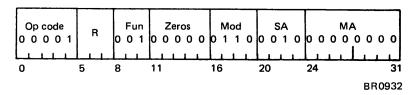

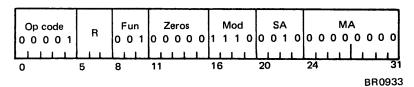

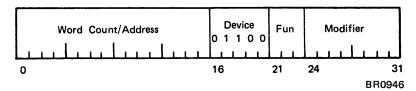

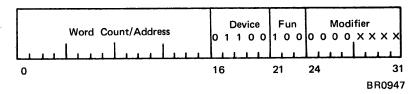

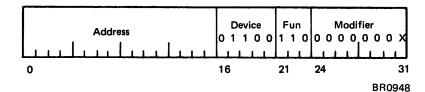

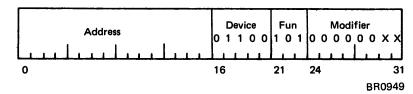

| I/O Control Commands (IOCC)                  | 93  |                                               |

| Control                                      | 94  |                                               |

| Initiate Read                                | 95  | Index                                         |

|                                              |     |                                               |

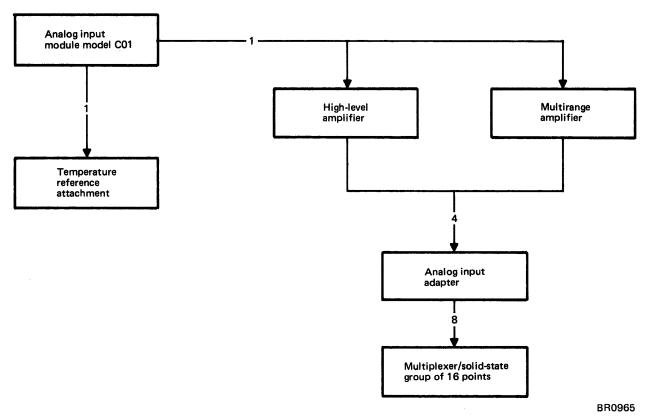

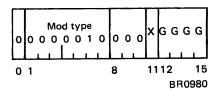

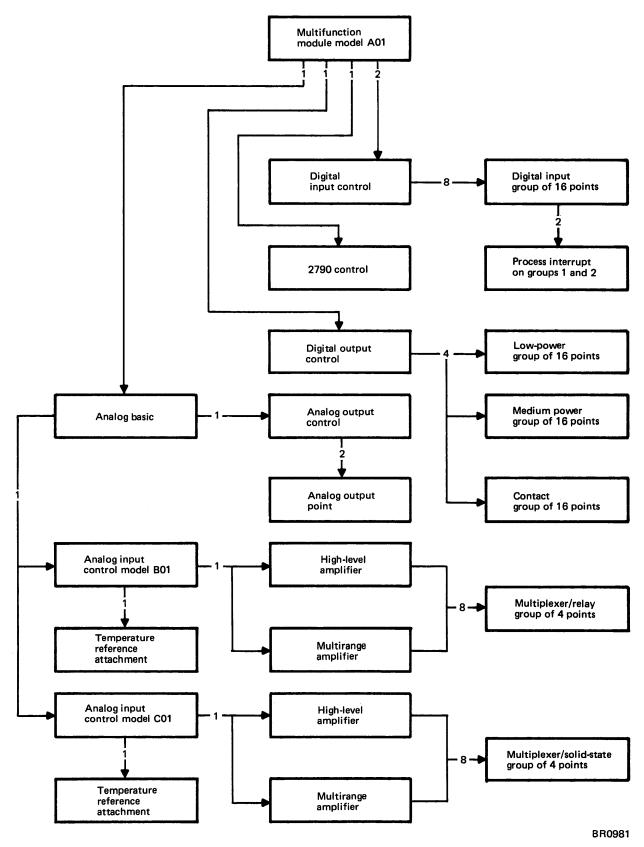

#### I/O MODULES

The System/7 is designed as a real-time system dedicated to applications requiring the use of sensor-based I/O devices. For this purpose, the I/O modules are provided. I/O module operations are controlled by the processor module. The functions of the processor module are described in a subsequent section. The I/O modules are:

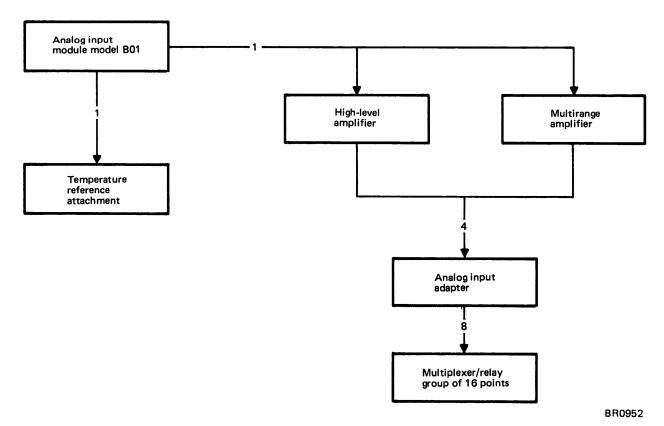

- IBM 5014 Analog Input Module Models B01 and C01. Both can have as many as 128 analog input points, but they operate at different rates of speed (points per second).

- IBM 5012 Multifunction Module Model A01. Special features within this module are:

- As many as 32 analog input points. All must be of the same speed. Performance of the analog input facility in this module is identical to that of the analog input module (models B01 and C01).

- As many as two analog output points.

- As many as 128 digital input points, of which the first two groups (of 16 points each) can have a process interrupt feature which generates an interruption from a change in status of a point.

- As many as 64 digital output points.

- One 2790 control feature for attaching a single loop of the IBM 2790 Data Communication System.

#### SYSTEM/7 CONFIGURATIONS

The System/7 is designed so that both its functional and physical structure are highly modular. This permits great flexibility in designing configurations for a broad spectrum of applications. Furthermore, the modularity allows easy expansion of a small initial installation to a more powerful configuration as future needs require.

System/7 can operate as a standalone computing system, or it can function as a satellite processor linked to a host processor which is on-site or at a remote distance.

However, the System/7 is structured independently of any host processor, and is designed to provide modular data acquisition and sensor-based I/O functions independent of the processor to which it may be linked. Therefore, the host processor can be modified or replaced without affecting the sensor-based I/O modules. This gives an installation more flexibility in its overall system planning and minimizes the disturbance to its machine interfaces.

The System/7 can be configured in any one of the following ways:

- A standalone system with one I/O module of any type. (See Figure 1.)

- 2. A standalone system with as many as 11 I/O modules in any combination. Each system configuration includes programming support for one 2790 control feature.

- One or more of the configurations discussed in items 1 and 2 can operate as satellite processors linked to the IBM System/360 (model 25 and up), the IBM System/370, or the IBM 1800 Data Acquisition and Control System. To accomplish this, each System/7 must have the asynchronous communications control

- Any one of the configurations discussed in items 1 and 2 can be attached directly to an IBM 1130 Computing System via the 1130 storage access channel. It is possible to initial program load (IPL) the System/7 from the 1130.

BR0712

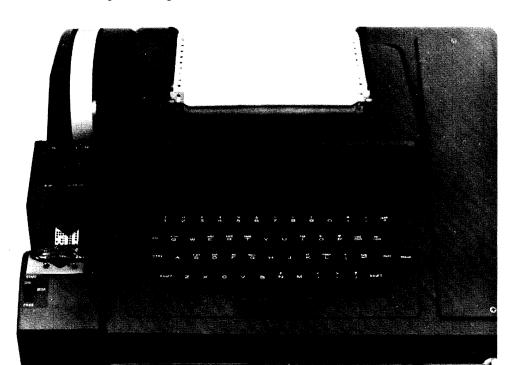

Figure 1. IBM 5026 Model A02 Enclosure and IBM 5028 Operator Station

In all configurations, the IBM 5028 Operator Station is used for communication between the operator and the System/7. Input is presented via the keyboard or paper tape reader. Output is via the printer or paper tape punch. Preparation of programs and IPL of the system can be accomplished through the operator station.

# GENERAL FUNCTIONAL DESCRIPTION

Every System/7 configuration has a 5010 Processor Module which controls the system, performing data processing operations and issuing I/O instructions to the sensor-based I/O modules. The main elements of the processor module are a processor, a monolithic storage, and a direct control channel.

The processor is a compact, 16-bit binary computer with a 400-ns storage cycle time. Sixty-four priority interruptions are organized on four priority levels, with 16 sublevels for each level. Interruption status-switching time is minimized by four sets of machine registers and program indicators, one set for each of the four interruption levels. Interruptions also occur for program check, machine check, and power failure conditions.

Performance is enhanced by the use of monolithic storage technology. Storage is organized into words of 16 bits (two bytes), plus a parity bit for each byte. The basic machine has 2k (2,048) words. Additional storage can be obtained in increments of 2k words to a maximum of 16k (16,384) words. Power to the system must be maintained to keep data in storage.

The direct control channel is the interface between the processor and the sensor-based I/O modules. It controls the System/7 internal interface to the attached I/O modules by interpreting I/O commands and transferring data to and from the I/O modules.

The direct control channel contains two standard interval timers. They function as separate program-controlled 16-bit binary counters that decrement at 50- $\mu$ s intervals. The channel also contains the adapter for attaching the operator station; the optional asynchronous communications control for communicating with a System/360, a System/ 370, or an 1800 Data Acquisition and Control System; or the optional adapter for attachment to an 1130.

#### SYSTEM DATA FLOW

Data can enter or leave the System/7 by the operator station, the I/O modules, or a host system.

Data entered through the operator station can consist of programs to be executed, data to be used by the program, or direct commands from the operator to the system. Data leaving the system through the operator station can consist of messages to the operator requesting information or a specific action, or data to be placed on the printer and/or paper tape.

Data from the I/O modules, which requires processing or specific action by the System/7, represents the status of the attached devices. The data might be stored for future action by the System/7 itself or for future action by a host system. Data sent to the I/O modules causes them to perform control operations that affect the application.

Generally, a host system transmits, to the System/7, control programs, data, and parameters within which certain processes are to be maintained. In turn, the System/7 sends, to the host system, collected data for processing, status information, or requests for new routines to handle situations which cannot be serviced by the routines that reside in the System/7.

## **DATA FORMATS**

To be accessible to the program during processing, data must be in storage (or a register). Thus, input job data is read by an input device, placed in storage, and then processed. Results (output data) are sent to an output device.

Input data can be represented in a variety of ways depending upon the input medium used. A medium is the material on which data is recorded. For example, a paper tape that is punched with holes (which represent data) is a medium; the paper tape can be read by a paper tape reader.

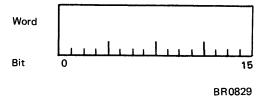

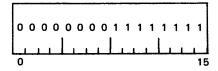

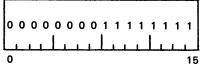

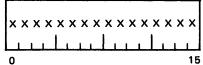

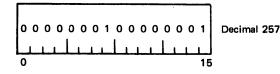

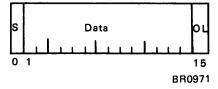

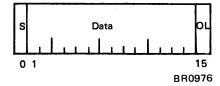

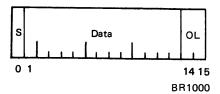

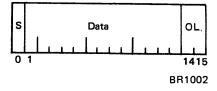

In the System/7, data is read from or stored in storage on a word basis. A word is made up of 16 bits, numbered 0 to 15.

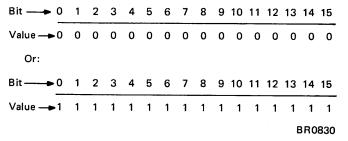

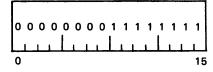

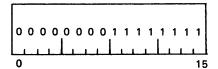

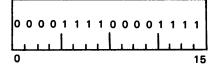

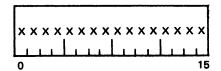

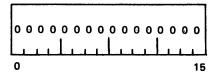

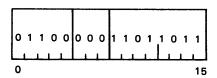

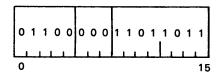

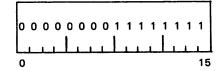

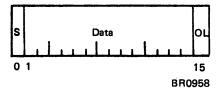

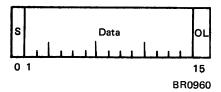

The leftmost bit (0) is the high-order bit; the rightmost bit (15) is the low-order bit. Each bit can be set to either a binary 1 (on value) or a binary 0 (off value). For example, a word can contain:

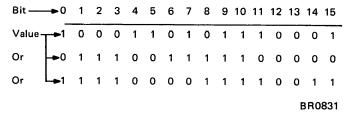

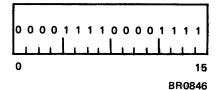

Or, any combination is possible:

Numeric, alphabetic, special character, or logical information can be represented by the bit values in a word, as determined by the combination of the bits in a word and the intention of the programmer who organizes the program and data in storage.

# **Numeric Data Formats for Arithmetic Operations**

Numeric computations in the System/7 are performed in binary arithmetic by the arithmetic instructions. In other words, the System/7 operates on binary data to produce binary results.

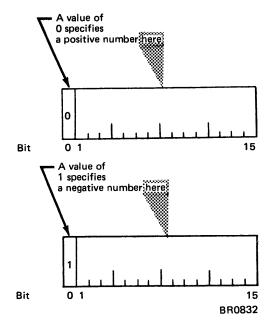

The value of bit 0 (the high-order bit) of a word specifies whether the word represents a positive or negative number. If the value of bit 0 is 0, the number represented in the word is positive; if the value of bit 0 is 1, the number represented in the word is negative.

The assumption has been made that the reader can, when given a numeric value represented by the symbols in the binary, hexadecimal, or decimal numbering system, convert those symbols to an equivalent numeric value in either of the other two systems. For example, the reader should be able to convert the binary symbols 11100010 to the hexadecimal representation E2, or to decimal representation 226. The reader should also be able to do simple addition or subtraction with numeric values represented by binary or hexadecimal symbols. (Refer to Number Systems, Order No. GC20-1618, for basic information on binary and hexadecimal numbering systems.)

The ranges of numeric values that can be represented in a 16-bit word are shown in binary and decimal system symbology as follows:

| 16-bit word  |                                |      |      |      |         |

|--------------|--------------------------------|------|------|------|---------|

|              | Ві                             | nary |      |      | Decimal |

| Bit 0 (sign) | ign) Bits 1-15 (numeric value) |      |      |      |         |

| 0            | 000                            | 0000 | 0000 | 0000 | 00000   |

| +            | to                             |      |      |      | to      |

| О            | 111                            | 1111 | 1111 | 1111 | 32,767  |

| 1            | 000                            | 0000 | 0000 | 0000 | -32,768 |

| -            | to                             |      |      |      | to      |

| 1            | 111                            | 1111 | 1111 | 1111 | -00001  |

**BR0833**

Negative numbers are represented in twos-complement binary form; the sign bit, containing a 1, signifies the negative number. For example, the number 1111 1111 1111 1111 is shown as having an equivalent decimal value of -00001. (The left 0's are shown since 16 binary bits can represent a five-digit decimal number.) This binary value is really the twos complement of negative 1. The absolute form can be obtained as follows:

Invert (change each position from 1 to 0):

1111 1111 1111 1111 becomes 0000 0000 0000 0000

## 2. Add 1 to the inverted number:

0000 0000 0000 0000

+1 0000 0000 0000 0001

Negative results are always represented in twos-complement form, which specifically excludes a negative zero. Positive numbers are always represented in true binary notation with a 0 sign bit.

#### STORAGE ADDRESSES

Storage capacity ranges from 2k (2,048) words to 16k (16,384) words. Storage between these limits can be obtained in 2k increments. The address for any storage location in System/7 can be contained in a 16-bit word:

| Binary Address (16 bits) | Hexadecimal Address | Decimal Address |

|--------------------------|---------------------|-----------------|

| 0000 0000 0000 0000      | 0000                | 00000           |

| 0000 1111 1111 1111      | 0FFF                | 4,095           |

| 0001 1111 1111 1111      | 1FFF                | 8,191           |

| 0011 1111 1111 1111      | 3FFF                | 16,383          |

#### **REGISTERS**

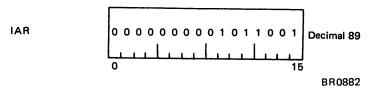

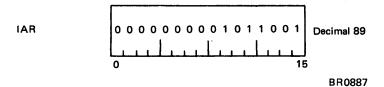

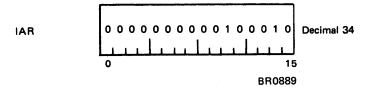

#### Instruction Address Register (IAR)

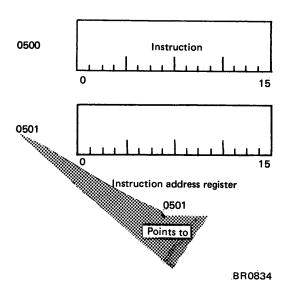

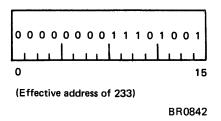

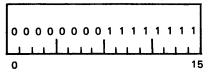

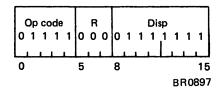

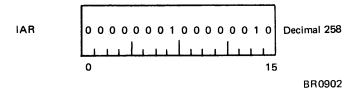

The instruction address register (shown on Figure 2) holds the address of the next instruction to be executed. For example, assume that the following instruction is being executed:

# Storage address

The 16-bit IAR contains the address of the storage word immediately following the instruction being executed. In most cases, this next word is the next instruction to be executed. Sometimes, however, the contents of the instruction address register are changed as a result of the instruction being executed. Execution of a branch instruction, for example, can cause accessing of the next instruction from a storage location other than the one immediately following the current instruction.

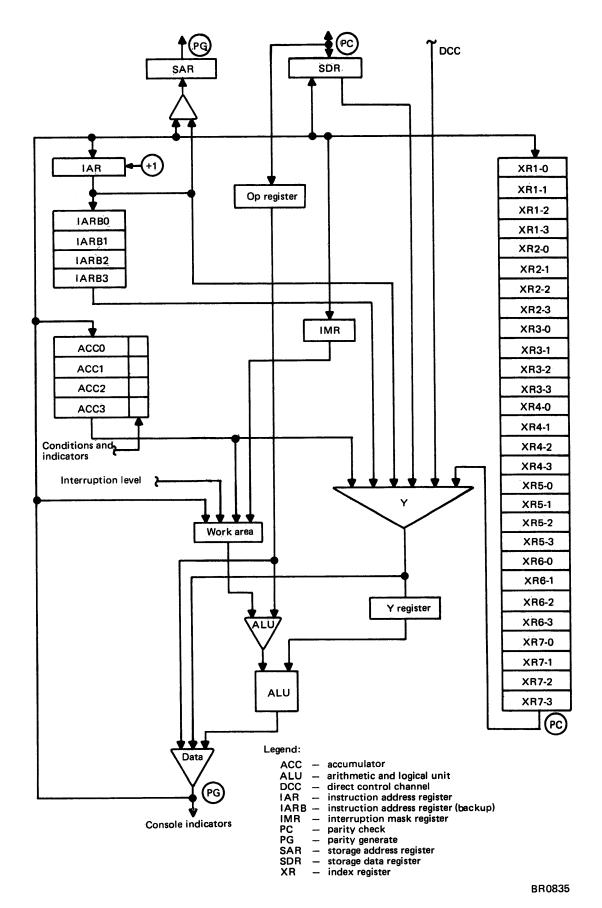

Figure 2. Processor Data Flow

The System/7 processor also has four backup instruction address registers (IARB0-IARB3), one for each priority interruption level. When a change of interruption levels occurs, the instruction address is automatically saved in the IARB for the level that is interrupted. When a return is made to that level, processing can be resumed at the location specified by the saved address.

The contents of any selected IAR or IARB can be displayed on the operator console, or console switches can be used to store a word into a selected IAR or IARB.

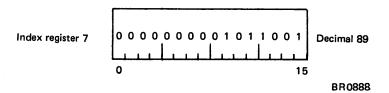

#### Index Registers (XR1-XR7)

The System/7 processor has seven index registers for each of the four priority interruption levels, for a total of 28. (See Figure 2.) Each index register has 18 bits (16 data bits plus 2 parity bits). This bit structure can represent either positive or negative numbers. (Refer to "Effective Address Generation" for a description of addressing concepts and how index registers can be used in generating effective addresses. Refer to the detailed instruction descriptions under "Instruction Set" for discussions of the ways in which the contents of the index registers can be manipulated in arithmetic and logical operations.)

The contents of any selected index register can be displayed on the operator console, or console switches can be used to store a word into a selected index register.

#### Accumulators (ACC0-ACC3)

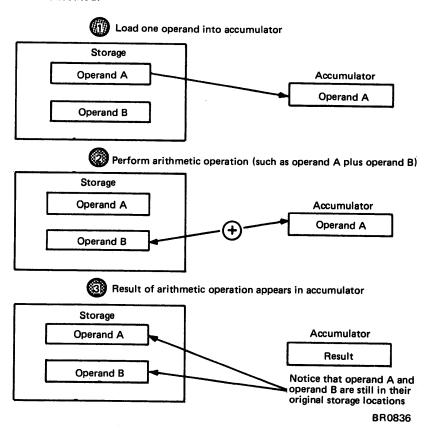

The System/7 processor has four accumulators (ACC0-ACC3), one for each priority interruption level. (See Figure 2.) These 16-bit registers are used in arithmetic and logical operations. In general, instruction execution is performed using one specified operand (from storage or an index register) and one implied operand (from the value previously loaded into the accumulator). The result is in the accumulator at the end of the operation. This result is obtained by a machine function that depends upon the instruction that is executed.

The contents of any selected accumulator can be displayed on the operator console, or console switches can be used to store a word into a selected accumulator.

#### Interruption Mask Register (IMR)

This four-bit register (shown on Figure 2) has a bit corresponding to each of the four (0-3) priority interruption levels. The appropriate bit in the mask register is set on (given a 1) value) to enable the corresponding priority interruption level (i.e., interrupting sources assigned to that priority level can present interruptions to the system if their priority is higher than the current operating program). The contents of the register can be examined or modified by three instructions: AND to mask, OR to mask, and sense level and mask.

#### Miscellaneous Machine Registers

The four registers described in the following paragraphs function automatically as required by the operation in process. (See Figure 2.)

# Storage Data Register (SDR)

Every word of data transferred to or from main storage by the processor passes through the SDR. The register holds 16 data bits and two parity bits.

#### Operation Register

This 16-bit register holds the first word of each instruction fetched from storage. The contents of the operation register can be displayed by the data lights on the operator console.

#### Storage Address Register (SAR)

The 16-bit storage address register contains the address of each location that is accessed in main storage by the processor. The SAR is displayed by the console address lights.

#### Y Operand Register

This 16-bit register holds the first operand of an instruction. The Y register can shift its contents to either the left or the right, for use in shift instructions.

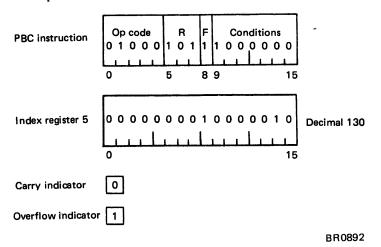

#### PROGRAM INDICATORS

The System/7 has six indicators that show the status of a data operation result field. At the completion of most instructions, the result is automatically tested for certain conditions, and indicators are set accordingly. Some of the branching instructions can test the indicators for conditional branching situations.

Once an instruction sets the indicators either on or off, they remain in this state (and can be tested) until the execution of another instruction changes the indicators according to the result of the operation. (Refer to the detailed description of the individual instructions to determine the effect of each instruction on the setting of these six program indicators.)

Each of the four priority interruption levels has a set of program indicators.

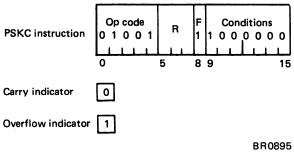

# Carry Indicator

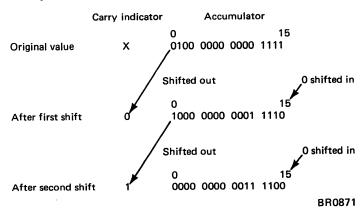

The carry indicator is set on when an operation produces a result that exceeds the physical capacity of the 16-bit data flow. This happens when a 1 is shifted or carried out of bit 0 (the sign bit) by an add or shift left logical instruction. It can also occur when a subtract operation attempts a borrow beyond bit 0.

#### **Overflow Indicator**

The overflow indicator is set on if the result of an arithmetic operation exceeds the logical capacity of the 16-bit data flow. This happens when an add or subtract operation produces a result greater than  $2^{15}$  – 1 or less than  $-2^{15}$ . This range is from +32,767 to -32,768 in decimal notation and from 7FFF to 8000 in hexadecimal notation.

#### Result-Zero Indicator

An operation result field has a zero value when all of its bits are set to 0's. Such a condition sets this indicator on.

#### **Result-Even Indicator**

If the low-order bit (bit 15) of a result is 0, this indicator is set on to indicate that the operation has produced an even number.

#### **Result-Positive Indicator**

The high-order bit (bit 0) of a result is the sign bit. A 0 sign bit signifies a positive number, which causes this indicator to be set on. If the numeric value of the entire result field is zero, this indicator is set off because the result-positive definition does not include a zero value.

#### Result-Negative Indicator

The result-negative indicator is set on when the result of an operation is a negative number. This occurs when the sign bit (bit 0) is set to 1. A negative zero is not represented in the System/7.

#### **PARITY**

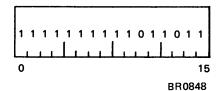

A System/7 word, whether used to hold data or an instruction, consists of 16 information bits. To ensure internal accuracy in data transmission and manipulation, System/7 has an internal checking system of odd parity. Every 16-bit word (bits 0-15) contains two 8-bit bytes (bits 0-7 and 8-15). Each byte must have an odd number of bits set on (having a value of 1) at all times. Obviously, this does not occur at all times because it is valid for data or instructions to be represented with an even number of bits set on. For example, 00000000 00001001 has no bits set on in the first byte and two bits set on in the second byte. Also, 11111111 111111111 has eight bits set on in each byte.

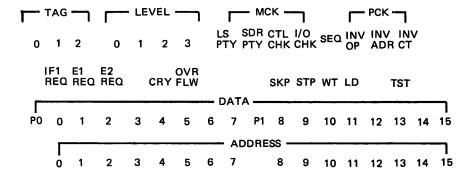

The ability for odd parity checking is designed into the system by adding two additional bits (called parity bits,  $P_0$  and  $P_1$ ) to each word. So, in reality, each word in the System/7 contains 18 bits. Each parity bit is associated only with its corresponding byte as shown by the following bit organization of a System/7 word:

Each parity bit is used to maintain odd parity in its associated byte by the following method. If the 8-bit byte already has odd parity, its parity bit is set to a 0 value. If the 8-bit byte has even parity, its parity bit is set to a 1 value to give the entity (byte plus parity bit) odd parity. The two previous examples would appear in main storage as:

| $P_0$ |          | $\mathbf{P}_{1}$ |          |

|-------|----------|------------------|----------|

| 1     | 00000000 | 1                | 00001001 |

| 1     | 11111111 | 1                | 11111111 |

During program execution, any time that the value (contents) of a word is intentionally changed, the machine automatically modifies the parity bits to maintain odd parity.

Words entering the System/7 are analyzed to determine whether each byte has odd or even parity. Parity bits are then added to the word to maintain odd parity.

Every time a word is used in the system, each byte plus its parity bit is checked to ensure that an odd number of bits are set on. If an even number is detected (parity error) in the processor, a machine-check interruption occurs. A parity error detected within the direct control channel or I/O modules is recorded in the device status word.

All data used by a program flows through the storage data register. Data coming from a source (e.g., main storage) which already has parity bits is checked for odd parity. Data coming from a source (e.g., the accumulator) without parity bits is checked and parity bits are added to maintain odd parity.

Figure 2 shows the locations of the parity check and parity generate circuits in the processor.

#### POWER FAILURE AND THERMAL WARNING

Power failure detection, coupled with automatic restart, is a special feature that offers an early warning of possible power failures due to low voltage or loss of primary voltage. AC power falling below 90 percent of nominal voltage triggers the power failure detection circuit which signals the processor of the possibility of an imminent shutdown. The signal remains in effect for the duration of the low-voltage condition.

If the power failure detection—auto restart feature is installed, automatic restart can be enabled by an operator console switch selection.

The auto-restart switch is a two-position toggle console switch that can be set by the operator. In the off position, operator intervention is necessary to restart the system if power fails. When set in the on position, if a power failure occurs, the system is automatically reset and an attempt is made to restore power. If power is restored, automatic IPL takes place if the IPL tape is loaded and positioned correctly in the operator station.

The System/7 can operate in a temperature range from 40°F to 122°F (4.4°C to 50°C). Overtemperature or undertemperature conditions are shown by a console indicator which remains active until the condition is terminated.

Power failures caused by thermal conditions result in the same action as those caused by low voltage.

#### PRIORITY INTERRUPTION SYSTEM

System configurations can have a large number of devices and attachments capable of sending and receiving data. Information gathered from various sources can have different data rates. Handling requests for attention from I/O devices in serial fashion does not necessarily result in optimum response or throughput. Data sources that have rapidly changing information, or that require minimum processing per change, should have a higher processing priority than those sources that have slowly changing information, or that require longer processing time. A priority system is required to coordinate the realtime servicing of many varied I/O devices.

System/7 has such a system, whereby an executing program can be interrupted by another program with a higher priority. Status of the interrupted program is saved in the machine registers, the higher-priority program is performed, and then control of the system is restored to the interrupted program.

A program can be interrupted by some external condition such as a sensor-based I/O device's signaling its readiness to transmit data, or by an internal machine condition such as a parity error or an invalid machine operation-code.

The interruption system can stop the program in progress in such a way that it can be resumed quickly after the interruption has been analyzed and serviced. To accomplish this in a minimum of time, all registers and indicators that are pertinent to program operation are duplicated on each priority interruption level.

#### **Priority Interruptions**

Briefly, the priority interruption scheme works in the following manner. As long as no higher priority device requests attention, current program processing and communication with I/O devices continues to completion. The last instruction executed in the current program must be a level exit instruction. If no interruptions are pending, the machine goes into the wait state. In the wait state, no instruction processing is done, but the machine can recognize and accept any type of interruption for which it is enabled.

If interruptions are pending on the same or lower priority levels, upon completion of the current program and execution of the level exit instruction, the machine does not enter the wait state, but immediately transfers to service the highest pending priority interruption.

If a priority interruption occurs that is higher than the currently executing program, the current program's status is automatically saved in the machine registers assigned to the level that was interrupted, and processing transfers to the routine that services the higher-priority request. This program can, in turn, also be interrupted by a higher-priority interruption. The machine can accept interruptions between the execution of each instruction. The original program is not resumed until all higher-priority interruptions are serviced.

# Interruption Levels

The System/7 priority interruption system has four levels of priority interruptions, designated as levels 0, 1, 2, and 3. System/7 design allows the user to assign each interrupting source a level and sublevel (there are 16 sublevels per level) dynamically via program control. This permits the user to easily restructure the priority organization as the application changes.

An interruption level designation of 0 is recognized as the highest priority by the System/7; level 3 has the lowest priority.

If processing is not being performed on any of the four interruption levels, the System/7 enters the wait state. A wait light and four level lights on the operator console indicate the operating status of the system.

# **Interruption Level Switching**

System/7 is designed to facilitate program switching from one level to another with minimum overhead. This system overhead time would be significant if programming were required to save the status of an interrupted program each time a switch is made.

However, as shown on Figure 2, System/7 design provides each of the four interruption levels with its own set of registers (an accumulator, a set of six program indicators, an instruction address register, and a set of seven index registers). Program switching in System/7 is performed in less than  $1 \mu s$ .

#### Interruption Level Stacking

Interruptions from devices are not serviced immediately if processing is taking place at the same, or at a higher, priority level. The system is capable of stacking or queueing pending interruptions.

Each of the four interruption levels has one buffer in the direct control channel. The first request for any particular level is placed in its corresponding buffer. For machine control to pass to that level, the request is moved out of the buffer and honored. If another request is pending at that level, it enters the buffer where it is available for servicing when the present program is completed and system control is returned to that level.

When the buffer is full (i.e., occupied by a request not yet honored), another device at the same level requesting service cannot be recognized. This interruption is stacked and must compete with any other requests made to access the buffer at that level, when the buffer becomes available again.

No matter how many interruptions are pending from devices on a particular priority level, the next one to be serviced when control returns is the request in the buffer.

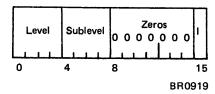

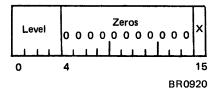

#### Interruption Sublevel Branching

An I/O device can be assigned to the same interruption level as other I/O devices, i.e., given the same priority number. Although the I/O devices share a common priority, the user determines whether they are to share the same servicing routines. The user can choose to have them share routines or use their own routines.

The user decides the priority of the various I/O devices by assigning them a level number (by a prepare I/O command). The level determines which branch table in storage is to be accessed for the starting address of the appropriate routine. One branch table must be established in main storage for each interruption level that is assigned (maximum of four).

Another parameter, the sublevel, is assigned by the user program to each device (by a prepare I/O command) so that the system can locate which address in the branch table is used to access the desired routine.

Upon detecting an interruption (from a level enabled for interruptions), the system examines the priority level to determine whether the interruption is to be permitted. If the same level or a higher level is processing, the request remains in the buffer. If not, the interruption request is honored. Using the level number, the system accesses the branch table reserved for that level. Using the sublevel as a displacement value, the system locates the desired address in the branch table and then branches to that address, which is the location of the first instruction in the routine that the user has established in main storage to service the interrupting source. This total interruption process is performed in less than 1 μs. (Refer to "Reserved Storage Locations.")

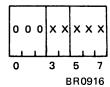

System/7 design allows for multiple interrupting sources (I/O devices) to be assigned to the same interruption level and sublevel. This permits a common interruption servicing routine to be used for multiple similar I/O devices. The device (out of two or more assigned to the same interruption level and sublevel) that actually caused the interruption is determined by the program's examining the accumulator contents immediately after the interruption.

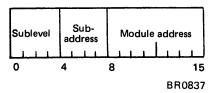

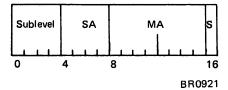

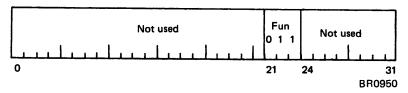

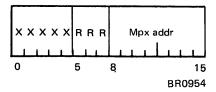

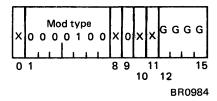

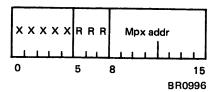

The accumulator (associated with the level) contains the address of the I/O device causing the interruption, in the following format:

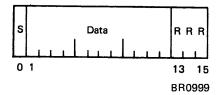

During interruption presentation, an I/O device also presents a summary status bit, which is placed into the carry indicator associated with the interruption level. This summary status bit is 0 if a normal interruption condition occurred, or 1 if an exception or error interruption condition occurred.

#### Interruption Mask Register

To give the user additional control over the automatic interruption system, a 4-bit interruption mask register is provided. This register has a bit (0, 1, 2, or 3) corresponding to each of the four interruption levels.

With this register the user can further modify, in a preplanned manner, the sequence in which the priority interruptions are serviced. The appropriate bit in the mask register is set on if its corresponding interruption level is enabled (i.e., devices assigned to that priority level can interrupt the system). Setting the bit off disables the level so that no interruptions are honored on that level.

The contents of the mask register can be examined or modified by three instructions: AND to mask, OR to mask, and sense level and mask.

#### **Interval Timer Interruptions**

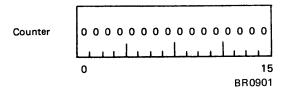

Two 16-bit interval timers are standard system features housed within the direct control channel. Each timer presents an interruption request to the system after counting a user-specified number of 50-µs time intervals. Though not strictly an I/O device, the timers present interruption requests to the system in the same manner as I/O devices and compete with them for system attention.

#### **CLASS INTERRUPTIONS**

Some internal machine conditions can also interrupt a processing program. Three types of class interruptions can occur in the system: program checks caused by invalid machine instructions, machine checks due to machine errors, and power/thermal failures.

Class interruptions cannot be disabled (i.e., masked off so that they do not interrupt the system). Conditions that cause class interruptions are serious enough that they must always be capable of interrupting system operations. Class interruptions automatically disable all four priority interruption levels and do not save the contents of machine registers. Therefore, the program that services the class interruptions must save register contents by storing, and must re-enable the mask register.

Class interruptions cause an interruption branch, allowing entry into error recovery routines to service the condition. The starting addresses of these routines are stored in fixed locations in reserved lower main storage. (Refer to "Reserved Storage Locations.")

Priority I/O interruptions cause movement (up or down) in priority but class interruptions do not (i.e., they remain on the same priority level as the interrupted program).

Lights on the operator console indicate the cause of a class interruption during machine stop state.

#### **Program Checks**

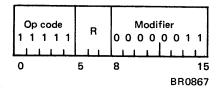

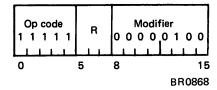

Program-check interruptions occur upon detecting a machine instruction that is invalid for any of the following reasons:

- 1. Invalid operation-code.

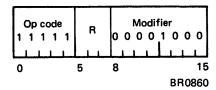

- 2. Invalid modifier field contents (hexadecimal values D through F) in instructions with operation code of 11111.

- 3. Invalid address (i.e., a main-storage address that exceeds the limits of the storage installed in the system).

- 4. Invalid function field in an execute I/O instruction.

- Invalid shift count value in shift instructions.

Operator console lights indicate (when the machine is in the stop state) the cause of a program check, which can occur on one or more of the four priority interruption levels.

When a program-check interruption occurs, the IAR contents (address of the next instruction in the interrupted program) are saved automatically in the first word of the appropriate level table. The starting address of the program-check servicing routine is loaded into the IAR from storage location 9 (its fixed address) and the servicing routine is given control. (Refer to "Reserved Storage Locations.")

#### **Machine Checks**

Machine-check interruptions occur when machine malfunctions are detected by errorchecking circuitry. Malfunctions can be caused by:

- 1. A parity error in a register.

- 2. More than one type of storage cycle requested or taken simultaneously.

- More than one interruption level being executed simultaneously.

Operator console lights indicate the cause of a machine check when the machine is in the stop state. Only one machine check can occur at any one time in the system.

When a machine-check interruption occurs, the IAR contents (address of the next instruction in the interrupted program) are saved automatically in storage location 13. The starting address of the machine-check servicing routine is loaded into the IAR from storage location 11 (its fixed address) and the servicing routine is given control. (Refer to "Reserved Storage Locations.")

#### Power/Thermal Failure

Power/thermal failure interruptions result when the power control system senses that power has fallen to below 90 percent of nominal voltage. This condition is caused by voltage or temperature changes that border on the operating limits of the system. (Refer to "Power Failure and Thermal Warning.")

When a voltage or temperature condition causes a power failure interruption, the IAR contents (address of the next instruction in the interrupted program) are saved automatically in storage location 12. The starting address of the power failure servicing routine is loaded into the IAR from storage location 10 (its fixed address) and the servicing routine is given control. (Refer to "Reserved Storage Locations.")

#### RESERVED STORAGE LOCATIONS

In main storage, an area is reserved for:

- 1. The restart instruction.

- Addresses required for processing class interruptions. 2.

- Address pointers to the level tables. 3.

These storage locations should not be used for purposes other than those for which they are intended; otherwise, required system operating data can be destroyed. (See Figure 3.)

|                  | Storage<br>location<br>(decimal) | Contents                                                                                                                                                                                                       |

|------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level<br>vectors | 17<br>16<br>15<br>14             | Level 3 start instruction address pointer<br>Level 2 start instruction address pointer<br>Level 1 start instruction address pointer<br>Level 0 start instruction address pointer                               |

| Class<br>vectors | 13<br>12<br>11<br>10<br>9<br>8   | Machine-check old instruction address Power failure old instruction address Machine-check start instruction address Power failure start instruction address Program-check start instruction address Reserved 、 |

|                  | 7<br>6<br>5<br>4<br>3<br>2       | Unassigned                                                                                                                                                                                                     |

|                  | 1 }                              | Restart instruction                                                                                                                                                                                            |

Figure 3. Reserved Storage Locations

**BR0838**

Variable-size level tables (one table for each priority interruption level specified by the user) are also necessary, but need not be placed in fixed locations in lower storage. (See Figure 4.)

|                             | Table word<br>(decimal)                                                                                           | Contents<br>(decimal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ascending storage locations | n+16<br>n+15<br>n+14<br>n+13<br>n+12<br>n+11<br>n+10<br>n+9<br>n+8<br>n+7<br>n+6<br>n+5<br>n+4<br>n+3<br>n+1<br>n | Level 0 sublevel 15 interrupt routine address Level 0 sublevel 14 interrupt routine address Level 0 sublevel 13 interrupt routine address Level 0 sublevel 12 interrupt routine address Level 0 sublevel 11 interrupt routine address Level 0 sublevel 10 interrupt routine address Level 0 sublevel 9 interrupt routine address Level 0 sublevel 8 interrupt routine address Level 0 sublevel 7 interrupt routine address Level 0 sublevel 6 interrupt routine address Level 0 sublevel 6 interrupt routine address Level 0 sublevel 3 interrupt routine address Level 0 sublevel 3 interrupt routine address Level 0 sublevel 1 interrupt routine address Level 0 sublevel 0 interrupt routine address Level 0 sublevel 0 interrupt routine address Level 0 program-check old instruction address |

Figure 4. Priority Level Table Format

BR0839

The reserved storage locations are described in detail as follows:

| Storage Location | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-1              | The restart instruction. After loading the IPL routine from the operator station, the machine automatically branches to location 0 to initiate processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2-7              | Unassigned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8                | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9-11             | The addresses of the first instructions in the routines that service program-check, power failure, and machine-check interruptions, respectively. When a class interruption occurs, the appropriate start instruction address (SIA) is loaded into the IAR and a branch is made to the servicing routine.                                                                                                                                                                                                                                                                                                                                        |

| 12-13            | The IAR contents (address of the next instruction in the interrupted program), after a power failure or machine-check interruption, respectively. This is the old instruction address (OIA). Control can then be returned to the correct instruction in the interrupted program after successful completion of the interruption servicing routine. Only one word is required to save the interrupted program address for each type of interruption because only one power failure or machine check can occur at any one time (it is not possible to have a machine check or power failure at more than one interruption level at the same time). |

| 14-17            | The addresses of the first word in the level displacement tables for interruption levels 0-3, respectively. Following a priority I/O interruption, this area is accessed to find the start instruction address of the level table assigned to the interruption level that is to be serviced.                                                                                                                                                                                                                                                                                                                                                     |

Locations 0-17 are fixed as to size and function of contents, However, additional storage is required for the level displacement tables assigned to each of the priority interruption levels (0, 1, 2, and 3). These tables are variable both in number (from 1 to 4) and individual size (from 2 to 17 words). They can be located elsewhere in main storage. (See Figure 4 for the typical format of a priority level table.)

The storage space required for the level displacement tables is dependent, firstly, upon the number of priority interruption levels needed, i.e., the number of different priorities assigned to I/O devices by the user. If only two different priority levels are used (e.g., interruption levels 0 and 1), only two level displacement tables need be established in

Secondly, storage space required for each of the two tables, in the preceding example, depends upon the number of sublevels assigned to I/O devices on the same priority level. For instance, six sublevels could be assigned to devices that are on priority level 0, while 12 sublevels could be assigned to devices that are on priority level 1. This would require seven words for the level 0 table and 13 words for the level 1 table.

Each interrupting source in the system must be assigned both a level and a sublevel, so that the system can locate the starting address of its servicing routine. The system accesses the correct branch address by adding the sublevel to the address of the second word in the table corresponding to the particular level.

The first word in any defined level table is reserved to hold the contents of the IAR if a program-check interruption occurs on that particular level. Each table can then have from 1 to 16 additional words, one for each unique sublevel assigned to interrupting sources on that level.

One table must be established in storage (need not be contiguous) for each priority level assigned. The words must be in ascending order of storage locations, i.e., if word 1 is at storage location 123, word 17 is at storage location 123 + 16, or location 139. Each table need be only as long as required by the current assignment of sublevels.

Every System/7 configuration has a data processing element that fetches and executes instructions in order to perform operations on data (such as testing, arithmetic, movement, and logical decision operations).

In the System/7, the processor is the data processing element of the system. It is a compact, 16-bit binary computer with a set of machine instructions that can manipulate data in a wide variety of ways.

#### INSTRUCTION CLASSES

For purposes of discussion and clarification, the instruction set is divided into eight classes that describe, in general, the type of data operation that is performed.

Mnemonics are used to abbreviate the instruction names when programming in assembler language. All mnemonics begin with P to indicate that the instructions are for execution by the System/7, although the instructions may be assembled on a different computer. The System/7 instructions, along with their mnemonics, operation codes, and execution times, are:

|                        |          | Operation | Execution Time |

|------------------------|----------|-----------|----------------|

| Instruction            | Mnemonic | Code      | in Nanoseconds |

| Load and store         |          |           |                |

| Load accumulator       | PL       | 11000     | 800            |

| Load and zero          | PLZ      | 11001     | 1200           |

| Load immediate         | PLI      | 01100     | 400            |

| Load index long        | PLXL     | 10001     | 1200           |

| Store accumulator      | PST      | 11010     | 800            |

| Store index            | PSTX     | 01101     | 800            |

| Arithmetic             |          |           |                |

| Add                    | PA       | 10000     | 800            |

| Subtract               | PS       | 10010     | 800            |

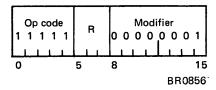

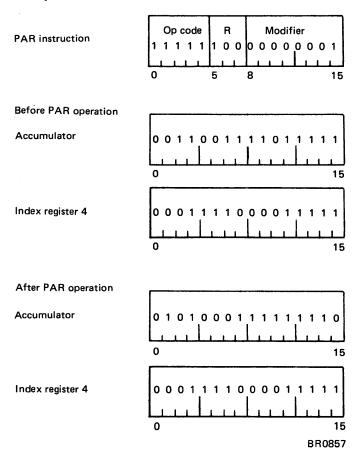

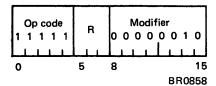

| Add register           | PAR      | 11111     | 400            |

| Subtract register      | PSR      | 11111     | 400            |

| Complement register    | PCR      | 11111     | 400            |

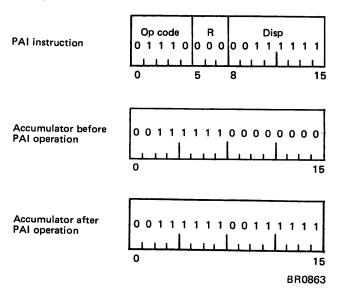

| Add immediate          | PAI      | 01110     | 400            |

| Logical                |          |           |                |

| AND                    | PN       | 11100     | 800            |

| OR                     | PO       | 11101     | 800            |

| Exclusive OR           | PX       | 11110     | 800            |

| AND register           | PNR      | 11111     | 400            |

| OR register            | POR      | 11111     | 400            |

| Exclusive OR register  | PXR      | 11111     | 400            |

| Shifting               |          |           |                |

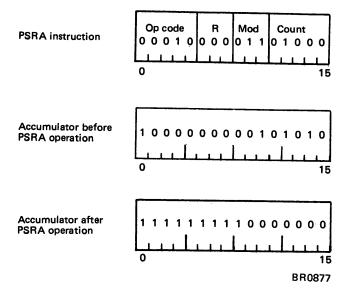

| Shift left logical     | PSLL     | 00010     | 400 + 50N      |

| Shift left circular    | PSLC     | 00010     | 400 + 50N      |

| Shift right logical    | PSRL     | 00010     | 400 + 50N      |

| Shift right arithmetic | PSRA     | 00010     | 400 + 50N      |

|                        |          |           |                |

(N is the number of bits shifted.)

| Instruction             | Mnemonic | Operation<br>Code | Execution Time in Nanoseconds |

|-------------------------|----------|-------------------|-------------------------------|

| Branching               |          |                   |                               |

| Branch                  | PB       | 00111             | 400                           |

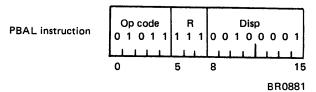

| Branch and link         | PBAL     | 01011             | 400                           |

| Branch and link long    | PBALL    | 01010             | 800                           |

| Branch on condition     | PBC      | 01000             | 400-no branch                 |

|                         |          |                   | 800-branch taken              |

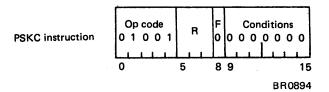

| Skip on condition       | PSKC     | 01001             | 400                           |

| Add to storage and skip | PAS      | 01111             | 1200                          |

| No operation            | PNOP     | 11111             | 400                           |

| Register-to-register    |          |                   |                               |

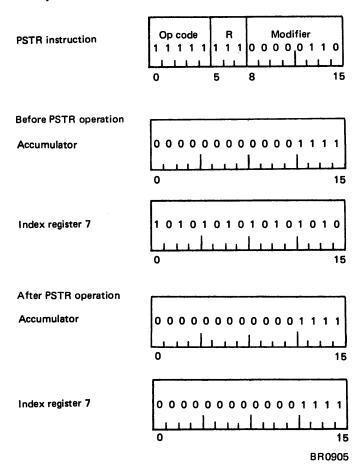

| Store to register       | PSTR     | 11111             | 400                           |

| Load from register      | PLR      | 11111             | 400                           |

| Interchange register    | PIR      | 11111             | 400                           |

| Load processor status   | PLPS     | 11111             | 400                           |

| Inspect IAR backup      | PIIB     | 11111             | 400                           |

| AND to mask             | PNM      | 10110             | 400                           |

| OR to mask              | POM      | 10110             | 400                           |

| Sense level and mask    | PSLM     | 11111             | 400                           |

| State control           |          |                   |                               |

| Level exit              | PLEX     | 00110             | 400                           |

| Input/output            |          |                   |                               |

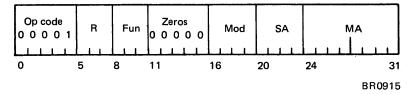

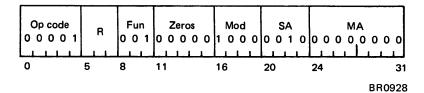

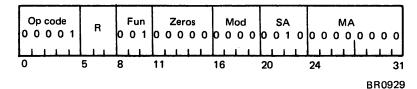

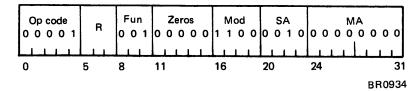

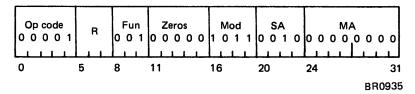

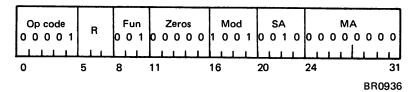

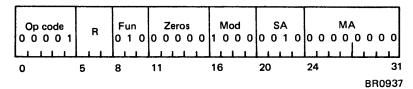

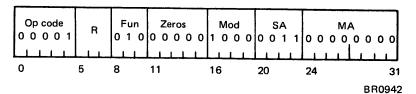

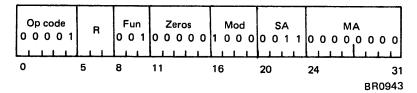

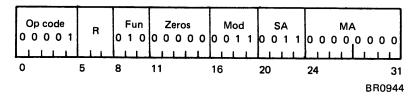

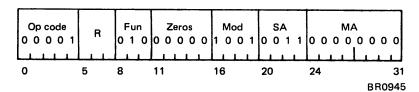

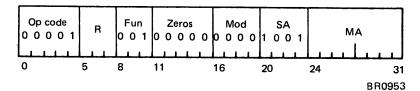

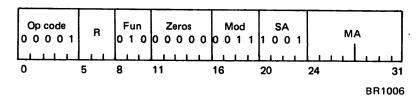

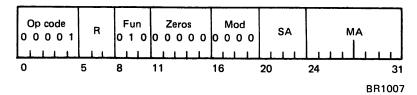

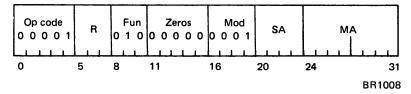

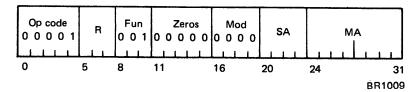

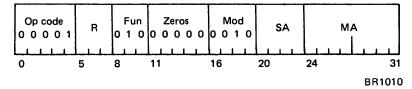

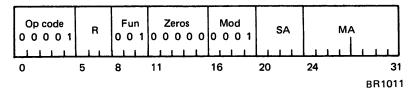

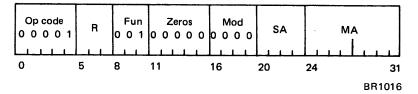

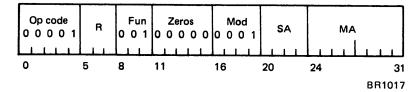

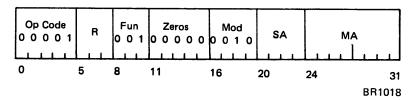

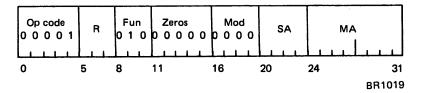

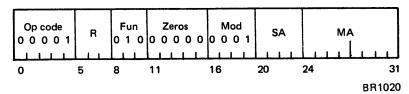

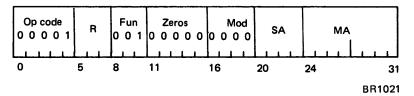

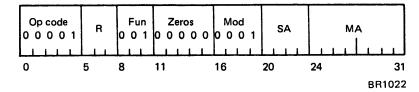

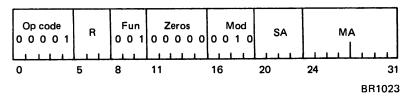

| Execute I/O             | PIO      | 00001             | 800 + I/F                     |

<sup>(</sup>I/F is the internal interface delay time. It varies from 450 to 1800 ns depending on the physical location of the I/O module concerned.)

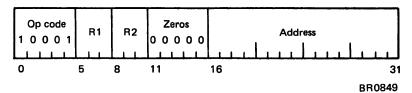

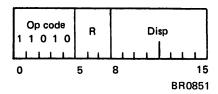

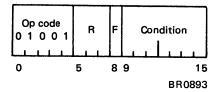

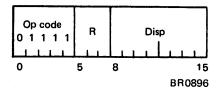

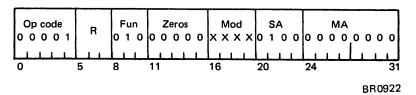

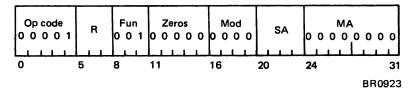

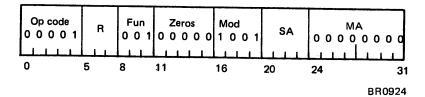

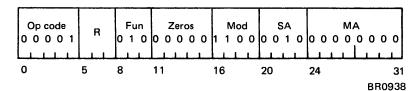

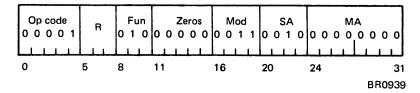

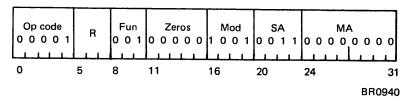

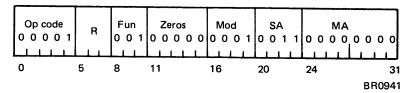

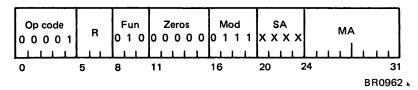

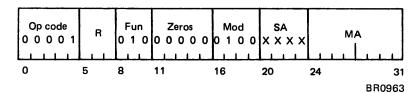

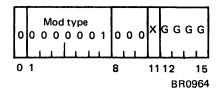

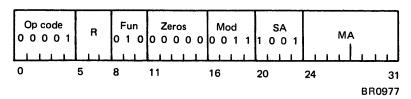

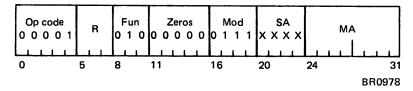

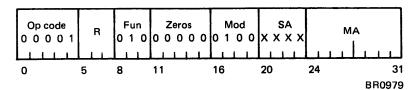

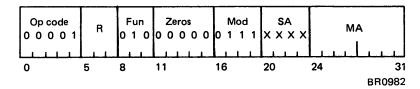

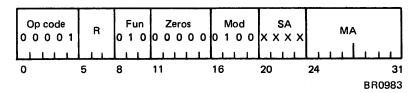

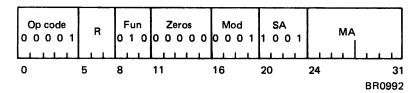

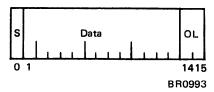

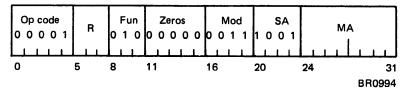

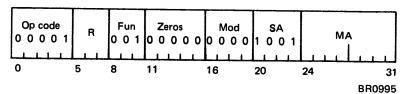

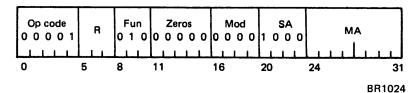

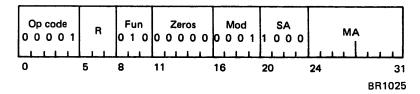

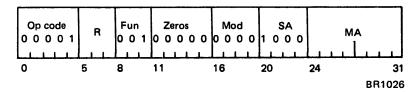

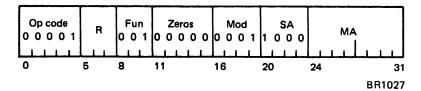

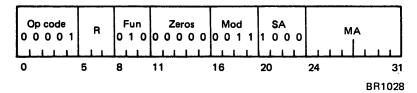

#### **INSTRUCTION FORMATS**

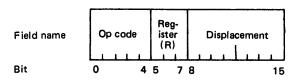

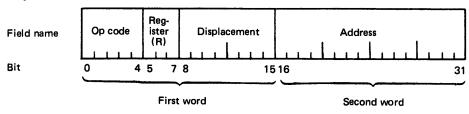

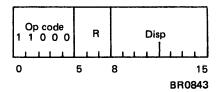

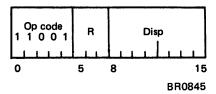

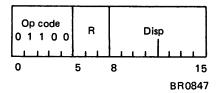

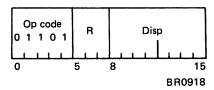

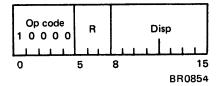

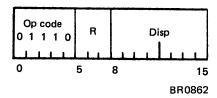

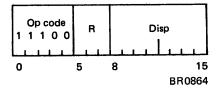

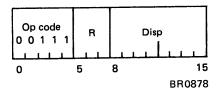

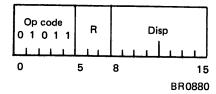

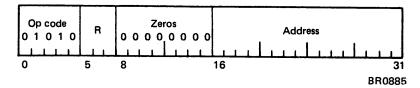

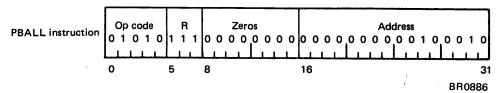

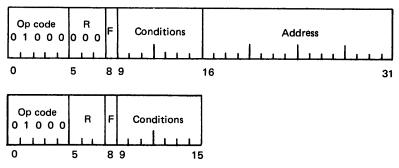

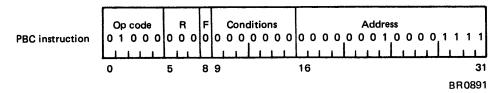

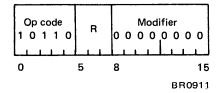

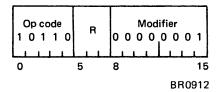

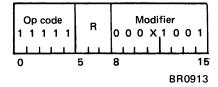

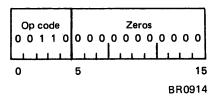

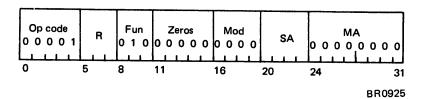

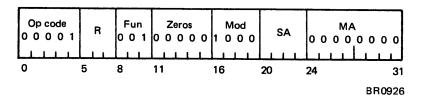

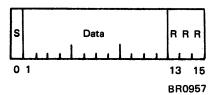

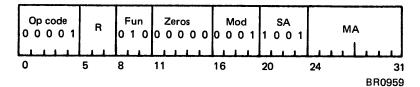

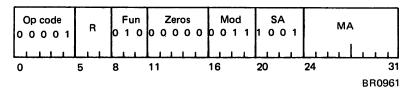

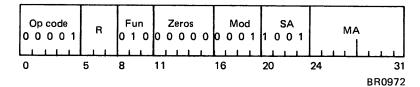

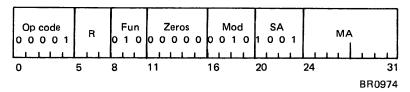

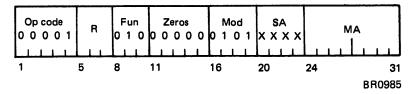

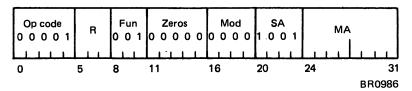

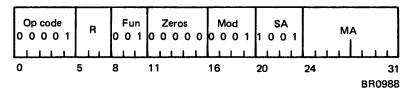

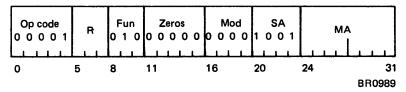

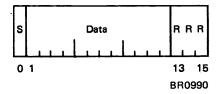

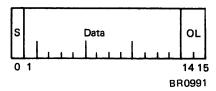

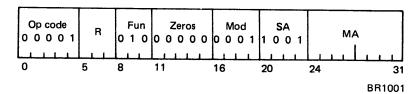

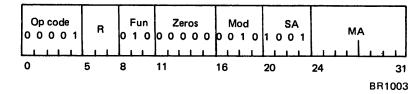

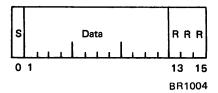

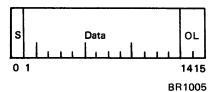

Two instruction formats are used in the System/7. A short-format instruction is 16 bits in length (one word); a long-format instruction is 32 bits in length (two words).

Both instruction formats are divided into several fields whose contents specify the operation to be performed and the location of the data to be processed. Most format fields have the same meaning from one instruction to the next; some, however, have special meanings dependent upon the instruction. These exceptions are discussed in the detailed description of the instruction.

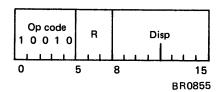

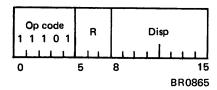

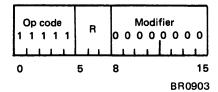

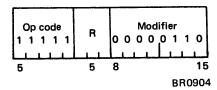

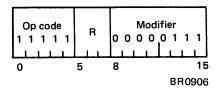

#### Short format

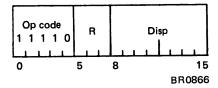

#### Long format

**BR0840**

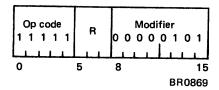

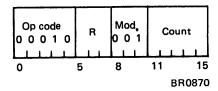

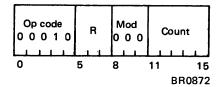

The operation-code (Op code) field is five bits that specify which instruction is to be performed.

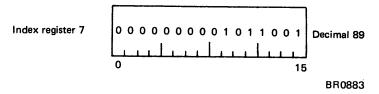

The register (R) field is three bits that indicate whether the accumulator, instruction address register, or one of the index registers is to take part in the instruction execution. An R field of 000 specifies either the accumulator or the instruction address register (IAR) depending on the instruction. The index registers are specified by the following R fields:

001-Index register 1

010-Index register 2

011-Index register 3

100-Index register 4

101-Index register 5

110-Index register 6

111-Index register 7

The contents of the register specified in the R field can be used for generating an effective address to locate the operand, as an instruction operand, or as data sent to an I/O device.

The displacement field is eight bits long. Its function is determined by the instruction to be performed, as indicated in the operation-code field. The displacement field can contain data that is to be manipulated in some fashion by the instruction. Bits may also be set in the displacement field to modify the operation code so that a particular instruction is executed. This is necessary because some instructions (such as the shifting instructions) have the same operation code. The most common use of the displacement field is to hold data that takes part in generating an effective address to locate the operand.

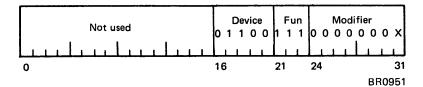

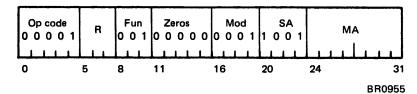

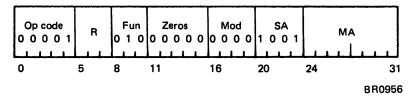

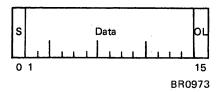

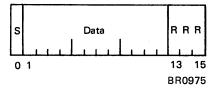

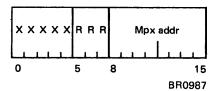

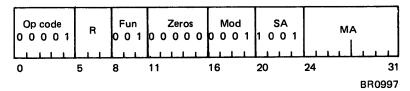

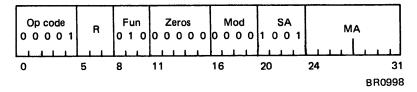

The address field is 16 bits long. Its contents are used in generating an effective address to locate the operand in three of the four long-format instructions (load index long, branch and link long, and branch on condition). With execute I/O, the fourth long-format instruction, the address field is used to specify the I/O instruction modifier and the address of the I/O device.

#### **EFFECTIVE ADDRESS GENERATION**

Storage addresses are expressed internally in 16-bit binary numbers, ranging from zero (16 bits set to 0) to a maximum value determined by the storage size of the System/7 configuration. Any attempt to address a location that is beyond the limits of the storage installed in the system causes a program-check interruption due to the invalid storage address.

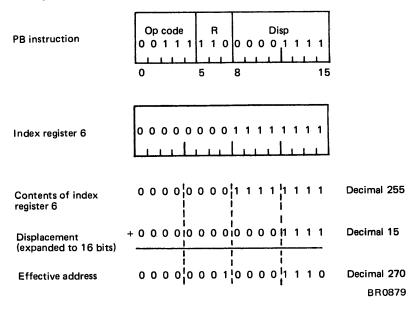

Most instructions refer to a storage address to locate the data that is to be used. This storage address is called the effective address (EA). The System/7 operates on a base register-displacement principle for storage addressing.

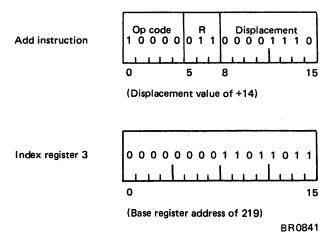

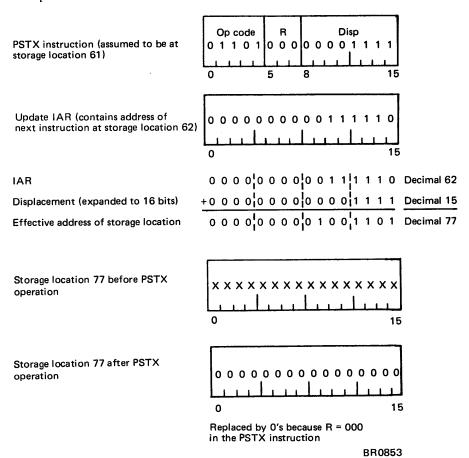

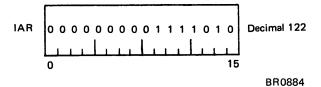

In a short-format instruction, the effective address is derived by adding algebraically the contents of the displacement field to the contents of the register indicated by the R field. The R field specifies the contents of the instruction address register (R = 000) or one of the index registers (R = 001 to 111) for this purpose. For example:

The algebraic sum of the displacement field in the instruction and the contents of index register 3 is the effective address of the data that is to be used by the add instruction. In this case:

The displacement can be either positive or negative, with bit 8 of the instruction word as the sign bit. If this high-order bit of the displacement field is a 0, the displacement is positive with a maximum value of +127 (decimal). If the high-order bit of the displacement field is a 1, the displacement is negative with a maximum value of -128. The negative number is represented in twos-complement form.

The use of the address field varies for each long-format instruction. (Refer to the detailed descriptions of the four long-format instructions—load index long, branch and link long, branch on condition, and execute I/O.)

#### INSTRUCTION DESCRIPTIONS

Each machine instruction is discussed in detail, in the order listed in "Instruction Classes." Following each instruction name is its mnemonic, execution time in nanoseconds (ns), instruction format, and description.

#### LOAD AND STORE INSTRUCTIONS

Six instructions are provided to move data between storage and the index registers/accumulator in the processor module.

#### **Load Accumulator**

PL-800 ns

The contents of the storage location specified by the effective address replace the contents of the accumulator. The storage contents are unchanged.

An R field of 000 means that the effective address is formed using the IAR (instead of an index register) as a base register.

The carry and overflow indicators are not changed. The result indicators are changed to reflect the final contents of the accumulator.

#### Example:

Before PL operation

Addressed storage word

Accumulator

After PL operation

Addressed storage word

Accumulator

Unchanged by operation

BR0844

#### Load and Zero

PLZ-1200 ns

The contents of the storage location specified by the effective address replace the contents of the accumulator. The storage contents are set to zero.

An R field of 000 means that the effective address is formed using the IAR (instead of an index register) as a base register.

The carry and overflow indicators are not changed. The result indicators are changed to reflect the final contents of the accumulator.

# Example:

#### Before PLZ operation

Addressed storage word

Accumulator

After PLZ operation

Addressed storage word

Accumulator

#### **Load Immediate**

PLI-400 ns

The contents of the index register specified by the contents of R, or the accumulator if R = 000, are replaced by the contents of the displacement field. Before loading, the 8-bit displacement field is expanded to 16 bits by propagating the displacement sign-bit (bit 8) through the high-order bits (i.e., bits 0-7 take on the value of the sign bit). The instruction word is unchanged.

The carry and overflow indicators are not changed. The result indicators are changed to reflect the final contents of the accumulator or index register.

# Example:

Before PLI operation

PLI instruction

Accumulator

After PLI operation

**PLI** instruction

Accumulator

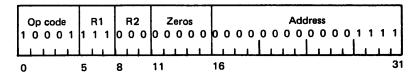

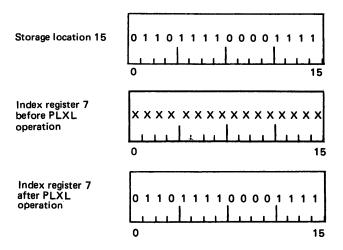

#### Load Index Long

PLXL-800 ns

The contents of the storage location specified by the effective address replace the contents of the index register specified by the R1 field. R1 = 000 specifies the accumulator. The storage contents are unchanged.

If R2 = 000, the address field contains the effective address. If  $R2 \neq 000$ , the effective address is the algebraic sum of the contents of the index register (specified by R2) and the address field.

Bits 11-15 of the instruction must be 0's.

The carry and overflow indicators are not changed. The result indicators are changed to reflect the final contents of the accumulator or index register.

# Example:

Since R2 = 000, the data is in storage location 15 (value of address field)

BR0850

#### **Store Accumulator**

PST-800 ns

The contents of the accumulator replace the contents of the storage location specified by the effective address. The contents of the accumulator are unchanged.

If R = 000, the effective address is formed using the IAR (instead of an index register) as a base register.